# SCALABLE FORMAL VERIFICATION OF FINITE FIELD ARITHMETIC CIRCUITS USING COMPUTER ALGEBRA TECHNIQUES

by

Jinpeng Lv

A dissertation submitted to the faculty of The University of Utah in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Department of Electrical and Computer Engineering

The University of Utah

December 2012

Copyright © Jinpeng Lv 2012

All Rights Reserved

## The University of Utah Graduate School

## STATEMENT OF DISSERTATION APPROVAL

| The dissertation of                                               | Jinpeng Lv                   |                             |  |  |  |

|-------------------------------------------------------------------|------------------------------|-----------------------------|--|--|--|

| has been approved by the following supervisory committee members: |                              |                             |  |  |  |

|                                                                   |                              |                             |  |  |  |

| Priyank Kalla                                                     | , Chair                      | 07/28/2012<br>Date Approved |  |  |  |

|                                                                   |                              | Date Approved               |  |  |  |

| Ganesh Gopalakrishnan                                             | , Member                     | 07/28/2012                  |  |  |  |

|                                                                   |                              | Date Approved               |  |  |  |

| Chris Myers                                                       | , Member                     | 07/28/2012                  |  |  |  |

|                                                                   |                              | Date Approved               |  |  |  |

| Kenneth Stevens                                                   | , Member                     | 07/28/2012                  |  |  |  |

|                                                                   |                              | Date Approved               |  |  |  |

| Rongrong Chen                                                     | , Member                     | 07/28/2012                  |  |  |  |

| tong ong onen                                                     | ,                            | Date Approved               |  |  |  |

|                                                                   |                              |                             |  |  |  |

| and by Giar                                                       | nluca Lazzi                  | , Chair of                  |  |  |  |

| the Department of Ele                                             | ectrical and Computer Engine | ering                       |  |  |  |

|                                                                   |                              |                             |  |  |  |

and by Charles A. Wight, Dean of The Graduate School.

## ABSTRACT

With the spread of internet and mobile devices, transferring information safely and securely has become more important than ever. Finite fields have widespread applications in such domains, such as in cryptography, error correction codes, among many others. In most finite field applications, the field size – and therefore the bit-width of the operands – can be very large. The high complexity of arithmetic operations over such large fields requires circuits to be (semi-) custom designed. This raises the potential for errors/bugs in the implementation, which can be maliciously exploited and can compromise the security of such systems. Formal verification of finite field arithmetic circuits has therefore become an imperative.

This dissertation targets the problem of *formal verification of hardware implementations of combinational arithmetic circuits over finite fields of the type*  $\mathbb{F}_{2^k}$ . Two specific problems are addressed: i) verifying the correctness of a custom-designed arithmetic circuit implementation against a given word-level polynomial specification over  $\mathbb{F}_{2^k}$ ; and ii) gate-level equivalence checking of two different arithmetic circuit implementations.

This dissertation proposes polynomial abstractions over finite fields to model and represent the circuit constraints. Subsequently, decision procedures based on modern computer algebra techniques – notably, Gröbner bases-related theory and technology – are engineered to solve the verification problem efficiently. The arithmetic circuit is modeled as a polynomial system in the ring  $\mathbb{F}_{2^k}[x_1, x_2, \cdots, x_d]$ , and computer algebrabased results (Hilbert's Nullstellensatz) over finite fields are exploited for verification.

Using our approach, experiments are performed on a variety of custom-designed finite field arithmetic benchmark circuits. The results are also compared against contemporary methods, based on SAT and SMT solvers, BDDs, and AIG-based methods. Our tools can verify the correctness of, and detect bugs in, up to 163-bit circuits in  $\mathbb{F}_{2^{163}}$ , whereas contemporary approaches are infeasible beyond 48-bit circuits.

To Ruina, Andrew and Emma.

## CONTENTS

| ABS | STRACT                                                                                                                                                                                                                              | iii                             |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| LIS | T OF FIGURES                                                                                                                                                                                                                        | vii                             |

| LIS | T OF TABLES                                                                                                                                                                                                                         | viii                            |

| AC  | KNOWLEDGEMENTS                                                                                                                                                                                                                      | ix                              |

| CH  | APTERS                                                                                                                                                                                                                              |                                 |

| 1.  | INTRODUCTION                                                                                                                                                                                                                        | 1                               |

|     | <ul> <li>1.1 Hardware Verification</li></ul>                                                                                                                                                                                        | 1<br>3<br>4<br>5<br>6<br>7<br>7 |

| 2.  | PREVIOUS WORK AND LIMITATIONS                                                                                                                                                                                                       | 9                               |

|     | <ul> <li>2.1 BDDs and Their Variants</li> <li>2.2 SAT Solvers and SMT Solvers</li> <li>2.2.1 Circuit-Based Solvers</li> <li>2.3 Computer Algebra-Based Approaches</li> <li>2.4 Verification of Finite Field Applications</li> </ul> | 9<br>11<br>13<br>14<br>15       |

| 3.  | PRELIMINARIES                                                                                                                                                                                                                       | 17                              |

|     | 3.1 Rings, Fields and Polynomials3.2 Finite Fields3.2.1 Construction of Finite Fields $\mathbb{F}_{2^k}$ 3.2.2 Hardware Implementations of Arithmetic Operations Over $\mathbb{F}_{2^k}$                                            | 17<br>20<br>21<br>23            |

| 4.  | COMPUTER ALGEBRA FUNDAMENTALS                                                                                                                                                                                                       | 30                              |

|     | <ul> <li>4.1 Monomials and Their Orderings</li> <li>4.2 Varieties and Ideals</li> <li>4.3 Gröbner Bases</li> <li>4.4 Hillbert's Nullstellensatz</li> <li>4.5 Concluding Remarks</li> </ul>                                          | 30<br>33<br>35<br>39<br>41      |

| 5.  | IMPLEMENTATION VERIFICATION USING IDEAL MEMBERSHIP                                                                                                                                                                                  | 40                              |

|     | <b>TESTING</b> 5.1 Problem Statement5.2 Verification Setup and Polynomial Modeling5.3 Verification Formulation as Ideal Membership Testing                                                                                          | <b>42</b><br>42<br>44<br>47     |

|    | 5.3.1 Generating $I(V_{\mathbb{F}_{2^k}}(J))$                            | 47           |

|----|--------------------------------------------------------------------------|--------------|

|    | 5.4 Obviating Buchberger's Algorithm                                     | 51           |

|    | 5.5 Our Overall Approach                                                 | 55           |

|    | 5.6 Experimental Results                                                 | 56           |

|    | 5.6.1 Evaluation of SAT, SMT, BDD, AIG-Based Methods                     | 57           |

|    | 5.6.2 Evaluation of Our Approach                                         | 57           |

|    | 5.7 Conclusions                                                          | 59           |

| 6. | GATE-LEVEL EQUIVALENCE CHECKING OF ARITHMETIC CIRCU                      | U <b>ITS</b> |

|    | <b>OVER</b> $\mathbb{F}_{2^K}$                                           | 62           |

|    | 6.1 Problem Statement and Modeling                                       | 63           |

|    | 6.1.1 Verification Problem Formulation as Weak Nullstellensatz           | 66           |

|    | 6.2 Verification Using a Minimum Number                                  |              |

|    | of S-polynomial Computations                                             | 70           |

|    | 6.3 Improving Polynomial Division Using $F_4$ -style Reduction           | 73           |

|    | 6.4 Experimental Results                                                 | 82           |

|    | 6.4.1 Equivalence Checking of Structurally Similar Circuits              | 82           |

|    | 6.4.2 Equivalence Checking of Structurally Dissimilar Circuits           | 84           |

|    | 6.5 Limitation of Our Approach                                           | 84           |

| 7. | VERIFICATION OF COMPOSITE FIELD ARITHMETIC CIRCUITS                      | 87           |

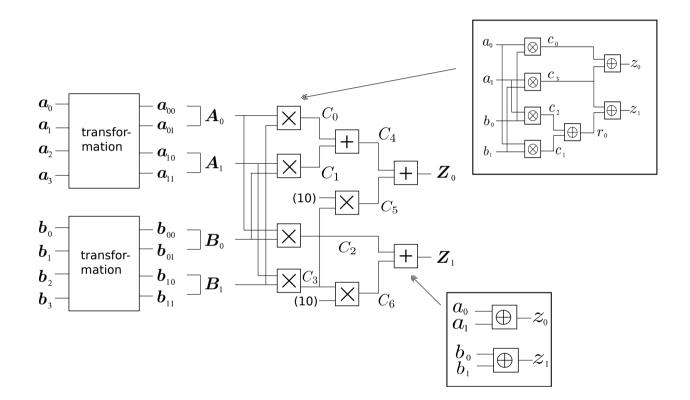

|    | 7.1 Circuit Designs over Composite Fields                                | 87           |

|    | 7.2 Problem Formulation and Hierarchy Verification                       | 93           |

|    | 7.3 Experimental Results                                                 | 95           |

|    | 7.4 Conclusions                                                          | 97           |

| 8. | CONCLUSIONS AND FUTURE WORK                                              | 99           |

| 0. |                                                                          |              |

|    | 8.1 Computer Algebra-Based Approaches for Equivalence Checking of Arith- |              |

|    | metic Circuit over $\mathbb{F}_{2^k}$                                    | 99<br>100    |

|    |                                                                          | 100          |

|    |                                                                          | 100          |

|    | 8.2.2 Extraction of Circuit Abstraction                                  | 101          |

|    | 6.2.5 Simulation-Dased vernication of Circuits                           | 102          |

| RE | FERENCES                                                                 | 103          |

## LIST OF FIGURES

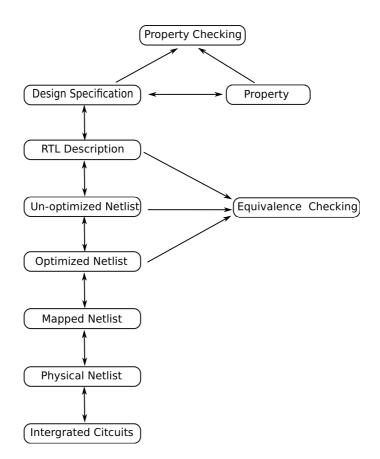

| 1.1 | Typical circuit design and verification flow.                                                                                                                               | 2  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

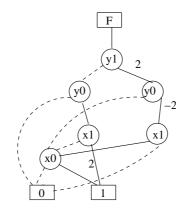

| 2.1 | BMD for $F = x * y$ ; $x, y$ are 2-bit wide, $F$ is 4-bit wide                                                                                                              | 10 |

| 2.2 | BMD for $F = x * y$ ; $x, y, F$ are all 2-bit wide                                                                                                                          | 11 |

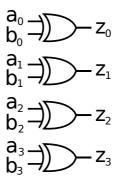

| 3.1 | 4-bit adder over $\mathbb{F}_{2^4}$                                                                                                                                         | 24 |

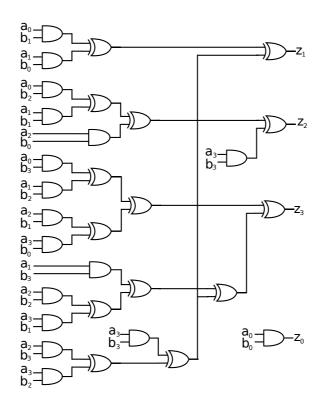

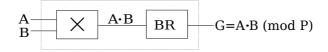

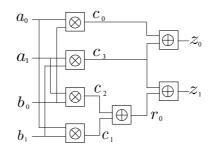

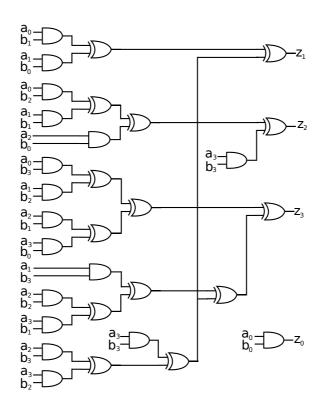

| 3.2 | Mastrovito multiplier over $\mathbb{F}_{2^4}$                                                                                                                               | 25 |

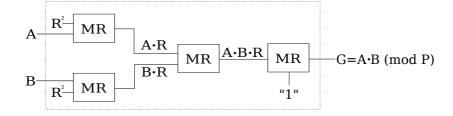

| 3.3 | <i>Montgomery</i> multiplier over $\mathbb{F}_{2^k}$                                                                                                                        | 26 |

| 3.4 | Barrett multiplier over $\mathbb{F}_{2^k}$                                                                                                                                  | 27 |

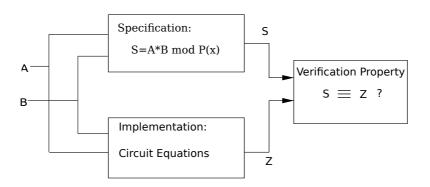

| 5.1 | The verification setup.                                                                                                                                                     | 44 |

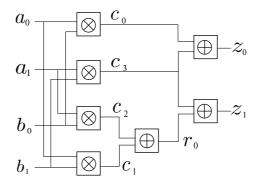

| 5.2 | A 2-bit multiplier over $\mathbb{F}(2^2)$                                                                                                                                   | 46 |

| 5.3 | A 2-bit multiplier over $\mathbb{F}(2^2)$ . The gate $\otimes$ corresponds to AND-gate, i.e., bit-level multiplication modulo 2. The gate $\oplus$ corresponds to XOR-gate, |    |

|     | i.e., addition modulo 2                                                                                                                                                     | 52 |

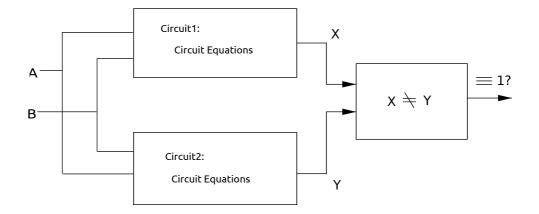

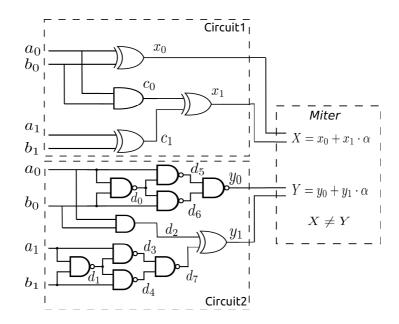

| 6.1 | The equivalence checking setup: miter                                                                                                                                       | 65 |

| 6.2 | Miter for 2-bit circuit equivalence.                                                                                                                                        | 65 |

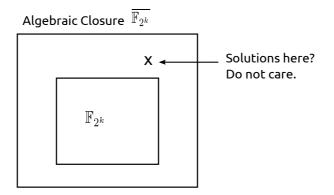

| 6.3 | A solution (bug) in $(\overline{\mathbb{F}_{2^k}} - \mathbb{F}_{2^k})$ is a "don't care".                                                                                   | 68 |

| 7.1 | Mastrovito multiplier over $\mathbb{F}_{(2^2)^2}$                                                                                                                           | 92 |

| 7.2 | Mastrovito multiplier over $\mathbb{F}_{2^4}$                                                                                                                               | 93 |

## LIST OF TABLES

| 3.1 | Additive and multiplicative inverses in $\mathbb{Z}_5$                                                                                                                                                  | 20        |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 3.2 | Bit-vector, exponential and polynomial representation of elements in $\mathbb{F}_{2^4} = \mathbb{F}_2[x] \pmod{x^4 + x^3 + 1}$                                                                          | 22        |

| 5.1 | Runtime for verification of Montgomery versus Mastrovito multipliers<br>over $\mathbb{F}_{2^k}$ for BDDs, SAT, SMT-solver and AIG/ABC-based methods. TO<br>= timeout of 10hrs. Time is given in seconds | 58        |

| 5.2 | Verification of Mastrovito multipliers by computing Gröbner bases using SINGULAR. <i>MO</i> =out of 8G memory. Time is given in seconds                                                                 | 58        |

| 5.3 | Runtime for verifying bug-free and buggy Mastrovito multipliers using our approach. TO = timeout of 10hrs. Time is given in seconds                                                                     | 59        |

| 5.4 | Runtime for verifying bug-free and buggy Montgomery multipliers using our approach. TO = timeout of 10hrs. Time is given in seconds                                                                     | 60        |

| 5.5 | Runtime for verifying bug-free and buggy Barrett multipliers using our approach. TO = timeout of 10hrs. Time is given in seconds                                                                        | 60        |

| 5.6 | Verification of ECC point addition. Run-time given is seconds. TO = timeout of 24hrs.                                                                                                                   | 60        |

| 5.7 | Verification of ECC point doubling. Run-time given is seconds. TO = timeout of 24hrs.                                                                                                                   | 60        |

| 6.1 | Matrix representation for polynomials.                                                                                                                                                                  | 75        |

| 6.2 | Matrix subtraction of polynomials.                                                                                                                                                                      | 75        |

| 6.3 | Matrix reduction for polynomials: representation                                                                                                                                                        | 76        |

| 6.4 | Matrix reduction for polynomials: subtraction                                                                                                                                                           | 76        |

| 6.5 | Matrix created for polynomial reduction for Example 6.8                                                                                                                                                 | 81        |

| 6.6 | Subtraction result of the matrix created for polynomial reduction                                                                                                                                       | 83        |

| 6.7 | Verification of Mastrovito multiplier vs. Barrett multiplier. $TO=10$ hrs.<br>*=Out of variable limitation. Time is given in seconds                                                                    | 85        |

| 6.8 | Verification of Barrett multiplier vs. Montgomery multiplier. $TO=10$ hrs. $\star=0$ of variable limitation. Time is given in seconds                                                                   | Dut<br>85 |

| 6.9 | Verification of Mastrovito multiplier vs. Montgomery multiplier. TO=10hrs<br>Time is given in seconds.                                                                                                  | 85        |

| 7.1 | Verification setup over $\mathbb{F}_{(2^2)^2}$                                                                                                                                                          | 96        |

| 7.2 | Statistics of designs over $\mathbb{F}_{2^m}$                                                                                                                                                           | 98        |

| 7.3 | Verification of Mastrovito multiplier over $\mathbb{F}_{(2^m)^n}$ using proposed approach.<br>All times are given in seconds.                                                                           | 98        |

## ACKNOWLEDGEMENTS

I am grateful to many people, without whose support I could not have completed this Ph.D. study and dissertation. First and foremost, I would like to thank my advisor, Professor Priyank Kalla. He has been patient enough to teach me everything I need to learn. I have learned many things from him, not only the knowledge itself, but also the way to organize the knowledge and apply it to real-world problems. Moreover, he is always available to discuss questions with me and provided perspectives based on his experience. I especially enjoy brainstorming with him. Actually, the most important result of my Ph.D. research is achieved by brainstorming. Next, I would like to thank Professor Florian Enescu for his extensive help and contribution to this work. I would also like to thank the other members of my committee - Ganesh Gopalakrishnan, Chris Myers, Ken Stevens and Rongrong Chen for their help and support. Finally, I would like to thank my friends: Arun Jay, Sammer Merchant and Brandt Hammer for all the good times we spent together.

## CHAPTER 1

## **INTRODUCTION**

With the rapidly increasing complexity of hardware systems, verification of the correctness of designs poses serious challenges. Design flaws can be extremely costly. For example, the Intel Pentium floating point divide bug resulted in 475 million dollars of extra costs in 1993. In many safety-critical applications, such as cryptography systems, arithmetic bugs can be especially catastrophic. In [10], it is shown that incorrect (buggy) hardware can lead to full leakage of the secret key, which can compromise the security of such systems. Therefore, it is of utmost importance to verify the correctness of hardware designs.

## **1.1 Hardware Verification**

Today, hardware verification averages about 70 percent of the overall hardware design effort and is believed to be the largest source of risk and cost. Hardware verification is becoming even more challenging as the design complexity increases.

The hardware design flow typically starts with a high-level specification or a property of the design. This specification is then translated into a register-transfer-level (RTL) description, which is further optimized and translated to its corresponding netlist representation. Then, the logic-level netlist is translated to a physical layout, which is subsequently fabricated into integrated circuits. Fig. 1.1 shows a typical design flow for realizing a hardware system. The design flow can be automated by Computer-Aided Design (CAD) tools available from both academia and industry. However, one critical question emerges: how to prove equivalent functionality between the different levels of representations. This is the objective of hardware verification. For example, after the RTL description is transformed into a gate-level netlist, it is important to ensure that its functionality remains the same. Similarly, after logic optimization is performed on the gate-level unoptimized netlist, it has to be ensured that the optimization process does not introduce a bug in the original design. Therefore, as shown in Fig. 1.1, verification is needed between different levels of abstractions, i.e., between design specification and

Figure 1.1. Typical circuit design and verification flow.

the "golden model", RTL-level model and netlist-level model, and between unoptimized and optimized netlists, etc.

There are two main methodologies applied to hardware verification: simulation and formal verification. In a traditional design flow, simulation is the primary methodology for design validation. The effectiveness of simulation is achieved by exhaustive assignments of inputs to excite all possible behaviors of the system and then by analyzing the output values. However, the increasing complexity of designs makes it impossible for simulation to provide complete coverage.

In recent years, formal verification has emerged as an alternative technique to ensure the correctness of hardware designs, overcoming some of the limitations of simulation. Formal verification is the process of utilizing mathematical theory to reason about the correctness of hardware designs. Formal verification in hardware usually takes one of two forms: property checking and equivalence checking. Property checking is a process of checking whether a design conforms to its given behavior or properties. Equivalence checking is conducted to prove the equivalent functionality of two given designs. Usually, equivalence checking is applied at various stages of the design cycle to verify correctness of the applied transformations. Figure 1.1 shows the role of equivalence checking in a typical hardware design flow.

Techniques utilized by property checking include model checking, theorem proving and approaches that integrate both. Equivalence checking makes use of Binary Decision Diagrams (BDDs), Satisfiability (SAT) solvers, and And-Inverter-Graph (AIG)-based reductions, among others. As an emerging technique for equivalence checking, computer algebra-based decision procedures are gaining popularity. This kind of verification technique is believed to be more sophisticated in verifying arithmetic hardware designs in that they exploit the powerful applications of mathematics rather than ad-hoc techniques.

#### 1.1.1 Property Checking

Property verification refers to proving the correspondence between designs and given properties. Usually, property verification is achieved by two main formal methods: theorem proving and model checking.

*Theorem proving* [60] requires the existence of mathematical descriptions for both the specification and implementation, allowing these descriptions to be manipulated in a formal mathematical framework. Theorem provers apply primitive proof (mathematical) rules to a specification in order to derive new properties of a specification. Through this method, theorem proving can reduce a proof goal to simpler subgoals that can be easily proved/disproved automatically by primitive proof steps. The benefit of this approach is its generality and completeness. However, despite several advances, generating the proof requires extensive guidance from the user. As a result, theorem proving lacks the level of automation that is desirable for a CAD framework to be practically useful. Theorem proving has gained commercial use in verifying that division and other operations are correctly implemented in processors at AMD and Intel.

*Model checking* [21] is an approach to formally verifying finite-state systems. Properties of the system are modeled as temporal logic formulas, and the model defined by the system is traversed to check if the properties hold or not. Therefore, model checking consists of specifying the desired properties of the system and checking if there are violations of specified properties for all possible behaviors of the system.

*Model checking* is one of the most successful approaches for property verification to date. Model checking tools [12] [63] [40] have achieved a significant level of automation and maturity and are widely in use in both academia and industry. A good

aspect of model checking that is extremely important in practice is the ability to generate counterexamples. Such counterexamples provide a way to trace the incorrect behaviors (bugs). However, these tools tend to be memory intensive and are more applicable to at most medium sized designs or at the block-level, rather than at the system-level.

#### 1.1.2 Equivalence Checking

Equivalence checking is used to formally prove that two representations of circuit designs have exactly equivalent functionality. As shown in Fig. 1.1, once a high-level representation is validated (by simulation or property checking), it is transformed into a gate-level netlist so that logic synthesis tools can be used to optimize the design according to the desired area/delay/power constraints. Then, the design proceeds through a varied set of optimization and transformation operations. During various transformation stages, different implementations of the design, or parts of the design, are examined depending upon the constraints, such as area, performance, testability, etc. As the design is modified by replacing one of its components by another equivalent implementation, it needs to be verified whether or not the modified design is functionally equivalent to the original one.

Equivalence checking has important applications in arithmetic circuit verification. Hardware designs contain a large number of custom-designed circuits such as adders, multipliers, dividers, and so on. Such circuits are usually not synthesized by CAD tools because of area and performance constraints. Therefore, this raises the potential for errors/bugs in the implementation. Consequently, it remains a challenge to conduct equivalence checking for these large-scale arithmetic circuits.

As an intensively investigated topic, techniques and approaches for equivalence checking have been well established. With various techniques employed for equivalence checking, BDDs and SAT-based techniques are the two dominant approaches widely used in both academia and industry. BDD-based approaches try to construct canonical representations of given circuits and conduct a linear comparison to determine whether they are equivalent or not. SAT-based equivalence checking approaches try to find the unsatisfiability of a "miter" representing two designs.

There are also many promising generalizations of SAT and BDDs: Binary Moment Diagrams (BMDs), which have shown their superiority for verifying integer multipliers [16], and Satisfiability Modulo Theories (SMT) solvers, which are the next generation of SAT. These approaches, to some extent, have gained some successes in equivalence checking. However, these approaches are beginning to show signs of inadequacy in two cases. First, large-scale hardware designs still hinder the equivalence checking as the level of design complexity grows rapidly. For example, the verification of a 16-bit modular multiplier becomes infeasible for the current SAT/BDD-based approaches. Secondly, for structurally similar circuits, this problem can be efficiently solved using the techniques of AIG-based reductions [11] and subsequent use of circuit-SAT solvers [53]. However, when the circuits are functionally equivalent but structurally very dissimilar, none of the contemporary techniques, including BDDs, SAT and AIG-based approaches, are able to prove equivalence.

Ideally, approaches for equivalence checking should maintain a high-level of abstraction while still retaining sufficient information so as to not lose lower-level functional details [37]. For instance, implementing arithmetic functions at bit-level can provide highly optimized implementations while word-level abstraction usually has much less structural information for solvers to analyze.

Arithmetic Bit Level (ABL) [85] abstraction techniques come close to achieving these requirements by extracting an arithmetic bit level representation from a given circuit. Then, the method can use the ABL information to prune the search space of SAT solvers. The drawback of this approach is that it can only identify ABL information locally when analyzing the given circuit, which results in an exponential blowup when looking at sophisticated circuits consisting of several arithmetic blocks.

In this dissertation, we focus on equivalence checking problems for finite field arithmetic circuits. Such circuits are found in many applications such as in cryptography, coding theory, signal processing, among others. We utilize the theory of computeralgebra and algebraic-geometry, notably, Gröbner bases-related theory and technology, as the underlying verification engines. Our approach is sophisticated enough to take into account both high-level (word-level) specifications and low-level (bit-level) implementation details.

#### **1.2 Computer Algebra-Based Formal Verification**

The first computer algebra-based verification technique dates back to 1996 when Gröbner bases were utilized for SAT solving and formal verification [23]. Indeed, there have been many attempts to solve verification problems using Gröbner basis formulations [4] [24] [87]. The standard flow of these approaches is:

1. The verification problem is first formulated as a polynomial system.

2. The polynomial system is fed into a Gröbner basis engine to check whether the desired property is satisfied.

The critical step of this approach is the Gröbner basis computation. Unfortunately, the computation is known to have worst-case double-exponential complexity in the input data. In practice, Gröbner basis algorithms have not been capable of satisfactorily solving problems derived from real-world applications. Besides, these methods are employed for verification by modeling constraints over the Boolean level  $\mathbb{Z}_2$ ; word-level abstractions, which can be powerfully modeled in algebra, are not utilized.

Recent advances [88] [56] [73] [58] [57] suggest a new direction of utilizing computer algebra theory to conduct hardware verification. These works show that it is feasible to overcome the complexity of Gröbner basis algorithm by efficiently engineering the integration of Gröbner bases theory and circuit analysis techniques.

#### **1.3** Objective and Contributions of this Dissertation

This dissertation focuses on verification of hardware implementations of arithmetic circuits over finite fields of the type  $\mathbb{F}_{2^k}$ . Specifically, the following verification problems are addressed:

- 1. Formal verification of a custom-designed finite field arithmetic circuit implementation against its given word-level polynomial specification.

- 2. Gate-level equivalence checking of two finite field arithmetic circuit implementations.

Verification of only *combinational logic circuits* over finite fields is considered in this work. Sequential circuit verification is a very different problem for arithmetic circuits – and it is beyond the scope of this dissertation.

The *motivation* for this work stems from applications in cryptography circuits, though our techniques can be applied to verify arbitrary finite field arithmetic circuits. In cryptosystems, the datapath size (operand size) k in the circuits can be very large. For example, the U.S. National Institute for Standards and Technology (NIST) recommends the use of finite fields corresponding to datapath sizes of k = 163-bit or more. The large size and high complexity of such circuits makes design verification quite challenging. Indeed, contemporary combinational verification techniques are unable to verify such large arithmetic circuits.

#### **1.3.1** Contributions of this Dissertation

We propose the application of *computer-algebra techniques*, notably, *Gröbner bases*related theory and technology [17] [3], as the underlying verification framework for our applications. The advantage of using computer-algebra techniques is that it allows us to integrate finite field arithmetic, circuit models and algebraic reasoning in a common verification framework. The circuits are modeled as a system of multivariate polynomials in the field  $\mathbb{F}_{2^k}$ . The formal verification problem is then formulated using *Hilbert's Nullstellensatz* [25] as ideal membership testing. A Gröbner basis engine is subsequently employed as a decision procedure to solve this verification problem.

Gröbner basis theory is very powerful as it enables one to solve many polynomial decision questions. Unfortunately, the computational algorithms are known to have worst-case double-exponential complexity in the input data. Therefore, in order to make verification practical and scalable, we engineer efficient application of Gröbner basis by integrating it with circuit analysis techniques. Specifically, we analyze the topology of the given circuit and derive efficient variable and term orders to systematically represent and manipulate the polynomials. Subsequently, using the theory of Gröbner bases over finite fields, we prove that our term orderings impose specific constraints on the polynomials that can obviate the need to compute a Gröbner basis. Under this term ordering, either the polynomials themselves constitute a Gröbner basis, or the term ordering allows us to identify a minimum number of computations in the Gröbner basis algorithm that are sufficient for verification. This significantly scales verification - we are able to verify circuits for which contemporary verification methods are infeasible. To further improve our approach, we implement an efficient polynomial reduction (division) algorithm that operates on a matrix-based representation of the polynomial system.

Experiments are conducted over various custom-designed arithmetic circuits over  $\mathbb{F}_{2^k}$ . These include three different modulo-multiplier architectures and point-addition circuits used in elliptic curve cryptosystems. Using our approach and tools, we can verify the correctness of, and detect bugs in, up to 163-bit finite field arithmetic circuits, whereas contemporary approaches are infeasible.

#### **1.4 Thesis Organization**

The rest of this dissertation is organized as follows. Chapter 2 reviews previous approaches and highlights their drawbacks with respect to the given verification problem. Chapter 3 briefly describes the construction and properties of finite fields  $\mathbb{F}_{2^k}$ . Arithmetic circuit design over such fields is also reviewed to shed some light on the difficulty of the verification problem. Chapter 4 covers preliminary theoretical background related to computer-algebra, algebraic-geometry and Gröbner bases. Chapter 5 describes our approach to verify a circuit implementation against a word-level polynomial specification using ideal membership testing. We show how the Gröbner basis computation can be obviated using efficient term orderings derived from the given circuit. Chapter 6 presents our approach to equivalence checking of two arithmetic circuit implementations. Efficient term orderings and matrix-based polynomial reduction procedures are derived. Chapter 7 describes a hierarchical verification methodology to verify arithmetic circuits over composite fields  $\mathbb{F}_{(2^m)^n}$ , where  $k = m \cdot n$ . Finally, Chapter 8 concludes the dissertation with a perspective on current and future research directions on computer algebra methods for verification.

## **CHAPTER 2**

## **PREVIOUS WORK AND LIMITATIONS**

Equivalence checking has been extensively investigated and many well-developed theories and techniques have been successfully applied in both academica and industry. The fundamental techniques used in equivalence checking include BDDs [15] and SAT solvers [26]. Recently, Gröbner bases-based approaches are also gaining popularity. This chapter reviews widely used techniques in the equivalence checking domain and discusses their limitations.

#### **2.1 BDDs and Their Variants**

Reduced Ordered Binary Decision Diagrams (ROBDDs or BDDs) are a canonical Directed Acyclic Graph (DAG) representation of a Boolean function. Circuits are usually described as a DAG. Two functionally equivalent circuits can be represented by the same BDDs. Therefore, equivalence checking between two circuits can be simply achieved by a comparison of their BDDs.

BDDs have found wide applications in many verification problems, including equivalence checking of arithmetic circuits, symbolic model checking [33] [63], among many others. However, along with the increasing complexity of designs, the size-explosion problem of BDDs becomes a bottleneck for many applications. This problem becomes especially serious when applied on designs containing large arithmetic data-path units. For example, BDD representation of multipliers requires memory that is exponential in the number of variables. As a result, BDDs fail to represent multipliers beyond 16-bit. As an attempt to control the exponential size, partitioned BDDs [70] introduce intermediate variables to represent sub-BDDs, thus partitioning the original BDD. Unfortunately, it is an intractable problem to find an optimum partition. This issue renders partitioned ROBDDs impractical for general verification problems.

Other efforts to extend the capabilities of BDDs are derived from generic Word Level Decision Diagrams (WLDDs), which are graph-based representations for functions with a Boolean domain and an integer range. These representations include ADDs [5], \*BMDs [16], etc. A thorough review of WLDDs can be found in [41].

Algebraic decision diagrams (ADDs) [5] provide an efficient means for representing and performing arithmetic operations on functions from the binary domain ( $\{0, 1\}$ ) to the integer domain, i.e.,  $\{0, 1\} \rightarrow \mathbb{Z}$ . However, the mapping/decomposition at each node/variable is still binary and leads to exactly two terms. Restricting the decomposition to a binary type limits the abstraction of integer variables, as they have to be decomposed into their constituent bits. Consequently, ADDs face the same problem that BDDs do: the exponential size of the number of input bits.

BMDs [16] and their variants, such as HDDs [22], K\*BMD [30], among others, perform a moment-based decomposition of a linear function. BMDs represent binary variables as (0, 1) integers instead of Boolean variables. Moment diagrams provide a concise representation of integer-valued functions defined over vectors of bits, or words, such as  $X = 2^{n-1}x_{n-1} + \ldots + 2x_1 + x_0$ , for an *n*-bit word *X*, where each  $x_i$  is a binary variable. BMDs are linear in size for integer multiplier circuits, as shown in Figure 2.1. The multiplicative constants of this representation reside in the terminal nodes. Moreover, the constants can also be represented as multiplicative terms and assigned to the edges of the graph, giving a rise to the Multiplicative Binary Moment Diagram (\*BMD) [16]. Several rules for manipulating edge weights are imposed on the graph to ensure canonicity.

One of the main limitations of BMDs is that performing some arithmetic operations on functions represented by BMDs is very expensive. For example, for an *n*-bit vector X, the BMD for  $X^k$  requires  $O(n^k)$  nodes. In addition, BMDs for modular operations

Figure 2.1. BMD for F = x \* y; x, y are 2-bit wide, F is 4-bit wide.

on bit-vectors are distorted, losing the compactness of word-level expression. One such example is depicted in Fig. 2.2.

Taylor Expansion Diagrams (TEDs) [20] [19] [45] [44] are derived from Taylor series and canonical DAG representations for functions that can be abstracted as polynomials. TEDs represent bit-vectors  $(x_0, x_1, \ldots, x_{n-1})$  as algebraic symbols (X[0 : n-1]), raising the abstraction from bits (Boolean) to words (integers). Let  $f(x, y, \ldots)$ be a real differentiable function. Using the Taylor series expansion with respect to a variable x, the function f can be represented as

$$f(x, y, \ldots) = f(x = 0, y, \ldots) + x \cdot f'(x = 0, y, \ldots) + (1/2)x^2 \cdot f''(x = 0, y, \ldots) + \cdots$$

(2.1)

The derivatives of f at x = 0 are independent of x, and can be further decomposed w.r.t the remaining variables, one variable at a time. This resulting recursive decomposition can be represented using a nonbinary tree called the TED, with memory requirements much smaller than other representations. TEDs are applicable to modeling, symbolic simulation and equivalence verification, provided that a polynomial abstraction is feasible. For binary operations, the diagram reduces to a \*BMD, inheriting all its limitations. Besides, TEDs cannot model modulo operations over bit-vectors. Therefore, TEDs are incapable of solving the equivalence problems presented in this dissertation.

### 2.2 SAT Solvers and SMT Solvers

The SAT problem is a decision-problem. In principle, any decidable decision problem can be modeled in terms of SAT, and because of this, SAT solvers are used in an enormous variety of applications.

Figure 2.2. BMD for F = x \* y; x, y, F are all 2-bit wide.

The objective of SAT solvers is to find variable assignments such that the given constraints (formulas) can be satisfied. If this is not possible, SAT solvers have to prove that no assignments satisfy the constraints (UNSAT).

Solving SAT-instances of any useful size was not possible until the introduction of the Davis-Putnam (DP) [27] algorithm. The DP algorithm works by eliminating variables through deriving new constraints from the original constraints containing the variables. Still, this has its limitations: though the variable is eliminated, the cost of elimination can be large because of the clauses needed to represent the variable in its absence. As a result, the algorithm did not see much use, but was used as a stepping stone for a more versatile techniques based on searching.

The foundation of nearly all modern SAT solvers lies in the DPLL approach [26]. The DPLL algorithm adopts a technique called backtracking search, whereby variables are recursively assigned, simplifying the formula at each step, building candidates to the solutions, abandoning each partial solution that can not possibly be completed to a valid solution (backtracking). The DPLL algorithm also utilizes rules such as unit-propagation and pure-literal elimination to reduce formula size and reduce the number of decisions needed. However, in essence, the DPLL algorithm is an exhaustive search for satisfying assignment.

Based on the basic DPLL framework, many improvements have been proposed. A major advance is conflict driven clause learning [79]. Conflict driven clause learning takes a strategy that new clauses are learned from conflicts during backtrack search and the structure of conflicts is exploited during clause learning. With this technique, the size of problem search space is greatly reduced and SAT solvers achieve the performance improvement by orders of magnitude. However, there are still many problems that are intractable for SAT solvers, such as problems from cryptography domain where the designs often involve tens of millions of variables. One major drawback that limits the capacity of SAT solvers is the lack of ability for word-level reasoning. To resolve this limitation, satisfiability modulo theories (SMT) are proposed and have gained significant popularity since 2003. The SMT problem is to decide the satisfiability of a formula expressed in a first-order background theory, such as linear inequalities, bit vectors, linear arithmetic and uninterpreted functions, etc. In fact, SMT can be considered as an extension of SAT to first-order logic. In other words, SMT solvers first apply highly optimized decision procedures for different first-order theories and then check the satisfiability using SAT solvers. For example,  $X > Y \land Y = Z$  is

first interpreted into X > Z and then X > Z is fed into a SAT solver to check the satisfiability.

For our problems of interest, bit-vector (BV) theories have been shown to be useful and important for hardware equivalence checking. In our case, equivalence checking problems are first compiled into the formula. Then, decision procedures for bit-vector theories, such as term rewriting techniques, are applied on the compiled formula to obtain further optimization. Next, the optimized formula is bit-blasted to an equisatisfiable Boolean formula. Finally, an integrated SAT solver is used to enumerate assignments to the Boolean formula to find a satisfying assignment.

One advantage of bit-vector theories in SMT is that all problems are described and operated upon word-level (bit-vector), proving to be effective for computationally intensive designs, such as arithmetic circuits. For example, at word level, a 32-bit multiplication can be represented as one term with two 32-bit words, while at bit-level, it is represented as thousands of Boolean variables. Moreover, some instances can be fully decided on the word-level, thus achieving a high performance.

As mentioned above, SMT formulas obviously provide a much richer modeling language than what is possible with Boolean SAT formulas, even allowing word-level representations of datapath operations. Solvers based on these theories [31] [14] [13] [43] have improved abilities to represent arithmetic computations, but ultimately rely on SAT tools to solve the verification instance, making them prone to the same limitations, as shown in our experiments. For equivalence checking of gate-level circuits, word-level information is not available. Then, SMT solvers have no benefits as they have to rely on SAT solvers to solve the bit-level verification instance.

#### 2.2.1 Circuit-Based Solvers

The above SAT and SMT solvers do not take into consideration circuit topology, so they are inefficient in verifying circuit designs. Instead, circuit-based solvers, such as C-SAT [53] [54], focus specifically on the mechanics of checking the equivalence of pairs of combinational circuits. The main strategy utilized by C-SAT solvers is signal correlation guided learning, which attempts to identify common subcircuit structure. In other words, an internal node in the first circuit may be equivalent to an internal node in the second circuit, thus combining the identical subcircuit as one node. This way, if two circuits are structurally similar, the original problem becomes a problem with much smaller space. To identify the common subcircuits, a technique called *structural*  *hashing* [11] is used. This is achieved by random simulation: first sending random vectors through the two circuits and then collecting pairs of candidate equivalent nodes. Practical use [11] has shown that this technique can detect potentially many, high probability, candidate equivalent nodes.

AIG [49], on the other hand, is a pseudo canonical representation of a circuit. One good property of AIGs is that the operations based on AIG are fast, such as adding nodes or merging nodes. By representing the circuit with AIGs, many equivalent nodes over a large circuit can be identified quickly.

When coupled with AIG as the circuit representation and techniques used in C-SAT, circuit-based SAT solvers can achieve remarkable speedups in solving a wide variety of circuit equivalence checking problems.

When two circuits are structurally very dissimilar, structural hashing is able to identify the common subcircuits, thus reducing the problem size. However, these techniques are infeasible when verifying structurally dissimilar circuits. For example, in our experiments, we have shown that equivalence checking of Mastrovito versus Montgomery multipliers using ABC [11] and C-SAT [53] is infeasible beyond 16-bit circuits.

## 2.3 Computer Algebra-Based Approaches

Computer algebra-based approaches were first proposed in 1996 for SAT solving and formal verification [23] [4]. The principle idea of these approaches is to reason about the existence of solutions in the polynomial domain: verification problems are first formulated as polynomials; then the polynoial system is fed into a Gröbner basis engine to check the existence of solutions. There have been many attempts to solve verification problems using this Gröbner basis formulation [87]. Instead of analyzing the entire problem for proof-refutation, the work of [24] utilized Gröbner bases to preprocess SAT instance to obtain additional information about the problem. This information is then fed back into the SAT solver, thus benefiting the SAT solving.

One limitation of these approaches is that the Gröbner basis computation is known to have worst-case double-exponential complexity in the input data. Besides, in practice, the implementations of Gröbner basis algorithm have not been capable of satisfactorily solving problems derived from real-world applications.

Recent advances [88] [73] suggest a new direction of utilizing computer algebra theory to conduct hardware verification. It is feasible to overcome the complexity of Gröbner basis algorithm by efficiently engineering Gröbner bases theory and integration of circuit analysis techniques.

The work described in [88] addresses verification of finite precision integer datapath circuits using the concepts of Gröbner bases over the ring  $\mathbb{Z}_{2^k}$ . They model the circuit constraints by way of arithmetic-bit-level (ABL) polynomials ({G}), and formulate the verification test as an equivalent variety subset problem. To solve this, first they derive a term order that already makes {G} a Gröbner basis. Then, they compute a normal form f of the specification g w.r.t. {G}. If f is a vanishing polynomial over  $\mathbb{Z}_{2^k}$  [76], circuit correctness is established. In [73], the authors further show that the vanishing polynomial test can be omitted by formulating the problem directly over  $Q := \mathbb{Z}_{2^k}[X]/\langle x^2 - x : x \in X \rangle$ .

However, such approaches are effective only over ring  $\mathbb{Z}_{2^k}$  while our problems are derived from finite fields  $\mathbb{F}_{2^k}$ . The mathematical theories differ significantly in these two domains. Therefore, these approaches cannot be applied for our problems.

### 2.4 Verification of Finite Field Applications

There has not been much research by the design verification community to verify finite field applications. The following works specifically targeted automated decision procedures for verification of finite field applications: [67] [69] [74].

The theorem-proving approach of [67] verifies a finite field  $\mathbb{F}_{2^k}$  implementation against a given polynomial specification. They devise a decision procedure-based on polynomial division, variable elimination, term rewriting, etc., and demonstrate a correctness proof of a sub-block of a Reed-Solomon decoder. Their decision procedures were partly built upon BDDs (requiring decision over  $\mathbb{F}_2$ ), and that is infeasible for large circuits.

The work of [69] solves similar problems as those of [67]. However, they make use of OKFDDs [29] to canonically represent the circuit constraints. Moreover, instead of verifying circuit over  $\mathbb{F}_{2^k}$  directly, [69] verifies the circuit over its equivalent composite field  $\mathbb{F}_{(2^m)^n}$  representation, where a *nonprime*  $k = m \cdot n$ . Their approach has no benefit if k is prime – say, when k = 163 for elliptic curves. Moreover, the size-explosion of FDDs limits their approach to 16-bit ( $\mathbb{F}_{2^{16}}$ ) circuits, as shown in their experiments.

MODDs [42] were proposed as a canonical representation of the characteristic function of a circuit over finite field  $\mathbb{F}_{2^k}$ . However, as each node in the DAG may

have up to k children, MODDs have been shown to be exponential in the number of variables, thus infeasible beyond 32-bit circuits.

None of the above approaches provide a scalable and efficient solution to the problem of verification of large finite field arithmetic circuits.

## CHAPTER 3

### PRELIMINARIES

This chapter gives an account of basic communicative algebra objects, such as modular arithmetic, groups, rings, fields and polynomials. Emphasis is placed on finite fields and hardware design over such fields as these applications are the focus of this dissertation. The material is referred from [62] [75] [51] for finite field concepts and [61] [65] [48] [89] [46] for hardware design over finite fields.

#### **3.1 Rings, Fields and Polynomials**

**Definition 3.1** An abelian group is a set S and a binary operation '+' satisfying:

- Closure Law: For every  $a, b \in S, a + b \in S$ .

- Associative Law: For every  $a, b, c \in S, a + (b + c) = (a + b) + c$ .

- Commutativity: For every  $a, b \in S, a + b = b + a$ .

- Existence of Identity: There is an identity element  $0 \in S$  such that for all  $a \in S$ ; a + 0 = a.

- Existence of Inverse: If  $a \in S$ , then there is an element  $a^{-1} \in S$  such that  $a + a^{-1} = 0$ .

The set of integers  $\mathbb{Z}$ , for instance, forms an abelian group under addition.

**Definition 3.2** Given two binary operations '+' and '.' on the set  $\mathbb{R}$  as well as two distinguished elements  $0, 1 \in \mathbb{R}$ , the system  $\mathbb{R}$  is called a **ring** if the following properties hold:

- $\mathbb{R}$  forms an abelian group under the '+' operation with additive identity element 0.

- Distributive Laws: For all  $a, b, c \in \mathbb{R}$ ,  $a \cdot (b + c) = a \cdot b + a \cdot c$ .

• Associative Law of Multiplication: For every  $a, b, c \in \mathbb{R}$ ,  $a \cdot (b \cdot c) = (a \cdot b) \cdot c$ .

If there is an identity element  $1 \in \mathbb{R}$  such that for all  $a \in \mathbb{R}$ ,  $a \cdot 1 = a = 1 \cdot a$ , then  $\mathbb{R}$  is said to be a **ring with unity**.

The ring  $\mathbb{R}$  is **commutative** if the following law also holds:

• Commutative Law of Multiplication: For every  $a, b \in \mathbb{R}$ ,  $a \cdot b = b \cdot a$ .

Henceforth, we consider only commutative rings with unity, as defined above. The set of integers,  $\mathbb{Z}$ , and the set of rational numbers,  $\mathbb{Q}$ , are examples of commutative rings with unity.

**Definition 3.3** The modular number system with base n is a set of positive integers  $Z_n = \{0, 1, ..., n - 1\}$ , with the two operations '+' and '.' satisfying the properties below:

- $(a+b) \pmod{n} \equiv (a \pmod{n} + b \pmod{n}) \pmod{n}$  (3.1)

- $(a \cdot b) \pmod{n} \equiv (a \pmod{n} \cdot b \pmod{n}) \pmod{n}$  (3.2)

$$(-a) \pmod{n} \equiv (n-a) \pmod{n} \tag{3.3}$$

**Example 3.1** The set  $Z_8 = \{0, 1, ..., 7\}$  denotes the modular number system with base 8. Examples of some operations performed (mod 8) are:

| 3 + 6 | = | 9     | $\pmod{8} = 1$ | $2 \cdot 4$    | = | 8             | $\pmod{8} = 0$ |

|-------|---|-------|----------------|----------------|---|---------------|----------------|

| 5 + 7 | = | 12    | $\pmod{8} = 4$ | $3 \cdot 5$    | = | 15            | $\pmod{8} = 7$ |

| (-3)  | = | 8 - 3 | $\pmod{8} = 5$ | $3 \cdot (-3)$ | = | $(3 \cdot 5)$ | $\pmod{8} = 7$ |

The modular number system  $\mathbb{Z}_n = \{0, 1, ..., n-1\}$ , where *n* is a natural number, forms a commutative ring with the identity elements 0 and 1. This type of a ring is a *finite integer ring*, where addition and multiplication are defined *modulo n* (mod *n*). Many hardware and software applications perform bit-vector arithmetic. Arithmetic over *k*-bit vectors manifests itself as algebra over the finite integer ring  $\mathbb{Z}_{2^k}$ , as a *k*-bit vector represents integer values from  $\{0, ..., 2^k - 1\}$ .

**Example 3.2** Consider the following hardware description given in Verilog. It takes as inputs two 4-bit vectors, and computes the sum, which is also represented with a 4-bit wide vector. Therefore, addition is performed modulo  $2^4$ . **module** Adder(A, B, sum);

```

input [3:0] A;

input [3:0] B;

output [3:0] sum;

reg [3:0] sum;

always @ (A or B)

begin

sum <= A + B;

end

```

#### endmodule

This code exemplifies arithmetic computations over the ring  $Z_{2^k}$  implemented at bit-vector level.

**Definition 3.4** A field  $\mathbb{F}$  is a commutative ring with unity, where every non-zero element in  $\mathbb{F}$  has a multiplicative inverse; i.e.,  $\forall a \in \mathbb{F} - \{0\}, \exists \hat{a} \in \mathbb{F}$  such that  $a \cdot \hat{a} = 1$ .

A field is defined over a ring with an extra condition: the presence of a multiplicative inverse for all non-zero elements. Therefore, a field must be a ring while a ring is not necessarily a field. For example, the set  $\mathbb{Z}_{2^k} = \{0, 1, \dots, 2^k - 1\}$  forms a finite ring. However,  $\mathbb{Z}_{2^k}$  is not a field because not every element in  $\mathbb{Z}_{2^k}$  has a multiplicative inverse.

In general, fields can be infinite, or contain a finite number of elements. For example, fractions  $\mathbb{Q}$ , complex numbers  $\mathbb{C}$ , are infinite fields. In our applications, we focus on finite fields, which are described later in Section 3.2.

**Definition 3.5** Let  $\mathbb{R}$  be a ring. A polynomial over  $\mathbb{R}$  in the indeterminate x is an expression of the form:

$$a_0 + a_1 x + a_2 x^2 + \dots + a_k x^k = \sum_{i=0}^k a_i x^i, \forall a_i \in \mathbb{R}.$$

(3.4)

The constants  $a_i$  are the coefficients and k is the degree of the polynomial. For example,  $4x^2 + 6x$  is a polynomial in x over Z, with coefficients 4 and 6 and degree 2.

**Definition 3.6** The system consisting of the set of all polynomials in the indeterminate x with coefficients in the ring  $\mathbb{R}$ , where addition and multiplication are defined accordingly, forms a ring called the **ring of polynomials**  $\mathbb{R}[x]$ . Similarly,  $\mathbb{R}[x_1, x_2, \dots, x_n]$  represents the ring of multivariate polynomials with coefficients in  $\mathbb{R}$ .

For example,  $\mathbb{Z}_{2^3}[x]$  stands for the system of all polynomials in x with coefficients in  $\mathbb{Z}_{2^3}$ ;  $4x^2 + 6x$  is an instance of a polynomial belonging to  $\mathbb{Z}_{2^3}[x]$ .

## 3.2 Finite Fields

Finite fields find widespread applications in computer engineering, such as in error correcting codes, elliptic curve cryptography, digital signal processing, testing of VLSI circuits, among others. We describe the relevant finite field concepts [62] [75] [51] and hardware designs over such fields [61] [65] [48] [89] [46].

**Definition 3.7** A finite field, also called a Galois field, is a field with a finite number of elements. The number of elements q of the finite field is a power of a prime integer – *i.e.*,  $q = p^k$ , where p is a prime integer, and  $k \ge 1$ . Finite fields are denoted as  $\mathbb{F}_q$  or  $\mathbb{F}_{p^k}$ .

**Definition 3.8** The characteristic of a finite field  $\mathbb{F}$  with unity element 1 is the smallest integer n such that  $1 + \cdots + 1$  (n times) = 0.

**Lemma 3.1** The characteristic of a finite field  $\mathbb{F}_{p^k}$  is the prime integer p.

**Lemma 3.2** The finite integer ring  $\mathbb{Z}_n$  forms a finite field if and only if n is prime. Such fields are customarily denoted as  $\mathbb{Z}_p = \mathbb{F}_p$ .

**Example 3.3** Consider the field  $\mathbb{Z}_5$ . The additive and multiplicative inverses of each element in  $\mathbb{Z}_5$  (except 0) are also elements in  $\mathbb{Z}_5$ , as shown in Table 3.1. In contrast,  $\mathbb{Z}_4$  is not a field, as 2 does not have a multiplicative inverse in  $\mathbb{Z}_4$ .

While  $\mathbb{Z}_{2^k}$  is not a field, there do exist fields  $\mathbb{F}_{p^k}$  with nonprime cardinality. Such fields are called extension fields. We are interested in extension fields  $\mathbb{F}_{p^k}$ , where p = 2 and k > 1. As these are algebraic extensions of the binary field  $\mathbb{F}_2$ , they are generally

| element | additive inverse | multiplicative inverse |

|---------|------------------|------------------------|

| 0       | 0                | undefined              |

| 1       | 4                | 1                      |

| 2       | 3                | 3                      |

| 3       | 2                | 2                      |

| 4       | 1                | 4                      |

**Table 3.1**. Additive and multiplicative inverses in  $\mathbb{Z}_5$ .

termed as *binary extension fields*  $\mathbb{F}_{2^k}$ . Such fields are most widely used in digital hardware applications as the computation can be universally encoded in binary form for practical reasons.

#### **3.2.1** Construction of Finite Fields $\mathbb{F}_{2^k}$

To construct and describe the properties of finite fields  $\mathbb{F}_{2^k}$ , the concept of **irreducible polynomials** is required:

**Definition 3.9** A polynomial  $P(x) \in \mathbb{F}_2[x]$  is **irreducible** if P(x) is nonconstant with degree k and it cannot be factored into a product of polynomials of lower degree in  $\mathbb{F}_2[x]$ .

Therefore, a polynomial with degree k is irreducible over  $\mathbb{F}_2$  if and only if it has no roots in  $\mathbb{F}_2$ . For example,  $x^2 + x + 1$  is an irreducible polynomial, because  $x^2 + x + 1 = 0$ has no roots in  $\mathbb{F}_2$ . Irreducible polynomials of any arbitrary degree always exist in  $\mathbb{F}_2[x]$ .

To construct  $\mathbb{F}_{2^k}$ , we take the polynomial ring  $\mathbb{F}_2[x]$  and an irreducible polynomial  $P(x) \in \mathbb{F}_2[x]$  of degree k, and construct  $\mathbb{F}_{2^k} \equiv \mathbb{F}_2[x] \pmod{P(x)}$ . Let  $\alpha$  be a root of P(x), i.e.,  $P(\alpha) = 0$ . Note that P(x) is irreducible in  $\mathbb{F}_2[x]$ ; however, the root lies in the algebraic extension  $\mathbb{F}_{2^k}$ . Any element  $A \in \mathbb{F}_{2^k}$  can therefore be represented as:

$$A = \sum_{i=0}^{k-1} (a_i \cdot \alpha^i) = a_0 + a_1 \cdot \alpha + \dots + a_{k-1} \cdot \alpha^{k-1}$$

(3.5)

where  $a_i \in \mathbb{F}_2$  are the coefficients and  $P(\alpha) = 0$ . The degree of any element A in  $\mathbb{F}_{2^k}$  is always less than k. This is because A is always computed modulo P(x), and P(x) has degree k. The remainder  $( \pmod{P(x)})$  can be of degree at most k-1. For this reason, the field  $\mathbb{F}_{2^k}$  can be viewed as a k-dimensional vector space over  $\mathbb{F}_2$ . The equivalent bit vector representation for element A is given below:

$$A = (a_{k-1}a_{k-2}\cdots a_0) \tag{3.6}$$

The example below explains the construction of the finite field  $\mathbb{F}_{2^4}$ .

**Example 3.4** Let us construct  $\mathbb{F}_{2^4}$  as  $\mathbb{F}_2[x] \pmod{P(x)}$ , where  $P(x) = x^4 + x^3 + 1 \in \mathbb{F}_2[x]$  is an irreducible polynomial of degree k = 4. Let  $\alpha$  be the root of P(x), i.e.,  $P(\alpha) = 0$ .

Any element  $A \in \mathbb{F}_2[x] \pmod{x^4 + x^3 + 1}$  has a representation of the type:  $A = a_3x^3 + a_2x^2 + a_1x + a_0$  (degree < 4) where the coefficients  $a_3, \ldots, a_0$  are in  $F_2 = \{0, 1\}$ .

Since there are only 16 such polynomials, we obtain 16 elements in the field  $\mathbb{F}_{2^4}$ . Each element in  $\mathbb{F}_{2^4}$  can then be viewed as a 4-bit vector over  $\mathbb{F}_2$ :  $\mathbb{F}_{2^4} = \{(0000), (0001), \dots, (1110), (1111)\}$ . If  $\alpha$  is the root of P(x), then each element also has an exponential representation; all three representations are shown in Table 3.2. For example, consider the element  $\alpha^{12}$ . Computing  $\alpha^{12} \pmod{\alpha^4 + \alpha^3 + 1} = \alpha + 1 = (0011)$ ; hence, we have the three equivalent representations.

There may exist more than one irreducible polynomials with degree k. In such cases, any degree k irreducible polynomial can be used for field construction. For example, both  $x^3 + x^2 + 1$  and  $x^3 + x + 1$  are irreducible in  $\mathbb{F}_2$  and either one can be used to construct  $\mathbb{F}_{2^3}$ . This is due to the following result:

**Theorem 3.1** There exists a **unique** field  $\mathbb{F}_{p^k}$ , for any prime p and any positive integer k.

Theorem 3.1 implies that finite fields with the same number of elements are isomorphic to each other up to the labeling of the elements.

**Lemma 3.3** Let A be any element in  $\mathbb{F}_q$ , then  $A^{q-1} = 1$ .

As a consequence of Lemma 3.3, the following is a very important result that we will use to investigate solutions to polynomial equations in  $\mathbb{F}_q$ .

**Theorem 3.2** [Generalized Fermat's Little Theorem] Given a finite field  $\mathbb{F}_q$ , each element  $A \in \mathbb{F}_q$  satisfies:

| $a_3 a_2 a_1 a_0$ | Exponential   | Polynomial              | $a_3 a_2 a_1 a_0$ | Exponential   | Polynomial                         |

|-------------------|---------------|-------------------------|-------------------|---------------|------------------------------------|

| 0000              | 0             | 0                       | 1000              | $\alpha^3$    | $\alpha^3$                         |

| 0001              | 1             | 1                       | 1001              | $\alpha^4$    | $\alpha^3 + 1$                     |

| 0010              | α             | α                       | 1010              | $\alpha^{10}$ | $\alpha^3 + \alpha$                |

| 0011              | $\alpha^{12}$ | $\alpha + 1$            | 1011              | $\alpha^5$    | $\alpha^3 + \alpha + 1$            |

| 0100              | $\alpha^2$    | $\alpha^2$              | 1100              | $\alpha^{14}$ | $\alpha^3 + \alpha^2$              |

| 0101              | $\alpha^9$    | $\alpha^2 + 1$          | 1101              | $\alpha^{11}$ | $\alpha^3 + \alpha^2 + 1$          |

| 0110              | $\alpha^{13}$ | $\alpha^2 + \alpha$     | 1110              | $\alpha^8$    | $\alpha^3 + \alpha^2 + \alpha$     |

| 0111              | $\alpha^7$    | $\alpha^2 + \alpha + 1$ | 1111              | $\alpha^6$    | $\alpha^3 + \alpha^2 + \alpha + 1$ |

**Table 3.2.** Bit-vector, exponential and polynomial representation of elements in  $\mathbb{F}_{2^4} = \mathbb{F}_2[x] \pmod{x^4 + x^3 + 1}$

$$A^{q} \equiv A$$

$$A^{q} - A \equiv 0$$

(3.7)

As a polynomial extension of the above consequence, let  $x^q - x$  be a polynomial in  $\mathbb{F}_q[x]$ . Every element  $A \in \mathbb{F}_q$  is a solution to  $x^q - x = 0$ . Therefore,  $x^q - x$  always *vanishes* in  $\mathbb{F}_q$ , and such polynomials are called **vanishing polynomials** of the field  $\mathbb{F}_q$ .

**Example 3.5** Given  $\mathbb{F}_{2^2} = \{0, 1, \alpha, \alpha + 1\}$  with  $P(x) = x^2 + x + 1$ , where  $P(\alpha) = 0$ .

$$0^{2^2} = 0$$

$$1^{2^2} = 1$$

$$\alpha^{2^2} = \alpha \pmod{\alpha^2 + \alpha + 1}$$

$$(\alpha + 1)^{2^2} = \alpha + 1 \pmod{\alpha^2 + \alpha + 1}$$

#### **3.2.2** Hardware Implementations of Arithmetic Operations Over $\mathbb{F}_{2^k}$

In some cases, finite field (primitive) computations such as ADD, MUL, etc., are implemented in hardware, and algorithms are then implemented in software (e.g., cryp-toprocessors [84] [47]). In other cases, the entire design can be implemented in hardware – such as a one-shot Reed-Solomon encoder-decoder chip [66] [50], or the point multiplication circuitry [38] used in elliptic curve cryptosystems. Therefore, there has been a lot of research in VLSI implementations of finite field arithmetic. We describe the design of such primitive computations below to shed some light on the architectures and their design and verification complexity.

Addition in  $\mathbb{F}_{2^k}$  is performed by correspondingly adding the polynomials together, and reducing the coefficients of the result modulo the characteristic 2.

**Example 3.6** Given  $A = \alpha^3 + \alpha^2 + 1 = (1101)$  and  $B = \alpha^2 + 1 = (0101)$  in  $\mathbb{F}_{2^4}$ ,

$$A + B = (\alpha^3 + \alpha^2 + 1) + (\alpha^2 + 1) = (\alpha^3) + (\alpha^2 + \alpha^2) + (1 + 1) = \alpha^3 = (1000)$$

**Example 3.7** A 4-bit adder in  $\mathbb{F}_{2^4}$  is given in Figure 3.1. It takes as inputs two 4-bit vectors:  $A = (a_3a_2a_1a_0)$ ,  $B = (b_3b_2b_1b_0)$  and computes the result  $Z = (z_3z_2z_1z_0)$ . Note, an adder circuit is trivial and only consists of XOR gates.

Conceptually, the multiplication  $Z = A \times B \pmod{P(x)}$  in  $\mathbb{F}_{2^k}$  consists of two steps. In the first step, the multiplication  $A \times B$  is performed, and in the second step,

**Figure 3.1**. 4-bit adder over  $\mathbb{F}_{2^4}$ .

the result is reduced modulo the irreducible polynomial P(x). Multiplication procedure is shown in Example 3.8.

**Example 3.8** Consider the field  $\mathbb{F}_{2^4}$ . We take as inputs:  $A = a_0 + a_1 \cdot \alpha + a_2 \cdot \alpha^2 + a_3 \cdot \alpha^3$ and  $B = b_0 + b_1 \cdot \alpha + b_2 \cdot \alpha^2 + b_3 \cdot \alpha^3$ , along with the irreducible polynomial  $P(x) = x^4 + x^3 + 1$ . We have to perform the multiplication  $Z = A \times B \pmod{P(x)}$ . The coefficients of  $A = \{a_0, \ldots, a_3\}, B = \{b_0, \ldots, b_3\}$  are in  $\mathbb{F}_2 = \{0, 1\}$ . Multiplication can be performed as shown below:

| ×               |                 |                 | $a_3 \\ b_3$           | $egin{array}{c} a_2 \ b_2 \end{array}$ | $a_1 \\ b_1$           | $a_0 \\ b_0$                |                                             |

|-----------------|-----------------|-----------------|------------------------|----------------------------------------|------------------------|-----------------------------|---------------------------------------------|

|                 |                 |                 | $a_3 \cdot b_0$        | $a_2 \cdot b_0$                        | $a_1 \cdot b_0$        |                             | -                                           |

|                 |                 | $a_3 \cdot b_1$ | $a_2 \cdot b_1$        | $a_1 \cdot b_1$                        | $a_0 \cdot b_1$        |                             |                                             |

|                 | $a_3 \cdot b_2$ | $a_2 \cdot b_2$ | $a_1 \cdot b_2$        | $a_0 \cdot b_2$                        |                        |                             |                                             |

| $a_3 \cdot b_3$ | $a_2 \cdot b_3$ | $a_1 \cdot b_3$ | $a_0 \cdot b_3$        |                                        |                        |                             |                                             |

| $s_6$           | $s_5$           | $s_4$           | $s_3$                  | $s_2$                                  | $s_1$                  | $s_0$                       | -                                           |

| he resu         | lt Sum =        | $= s_0 + s_1$   | $1 \cdot \alpha + s_2$ | $_2 \cdot \alpha^2 + s$                | $s_3 \cdot \alpha^3 +$ | $s_4 \cdot \alpha^4 \dashv$ | $+ s_5 \cdot \alpha^5 + s_6 \cdot \alpha^5$ |

|                 |                 |                 |                        |                                        |                        |                             |                                             |

$$s_{0} = a_{0} \cdot b_{0}$$

$$s_{1} = a_{0} \cdot b_{1} + a_{1} \cdot b_{0}$$

$$s_{2} = a_{0} \cdot b_{2} + a_{1} \cdot b_{1} + a_{2} \cdot b_{0}$$

$$s_{3} = a_{0} \cdot b_{3} + a_{1} \cdot b_{2} + a_{2} \cdot b_{2} + a_{3} \cdot b_{1}$$

$$s_{4} = a_{1} \cdot b_{3} + a_{2} \cdot b_{1} + a_{3} \cdot b_{1}$$

$$s_{5} = a_{2} \cdot b_{3} + a_{3} \cdot b_{2}$$

$$s_{6} = a_{3} \cdot b_{3}$$

Here the multiply "·" and add "+" operations are performed modulo 2, so they can be implemented in a circuit using AND and XOR gates. Note that unlike integer multipliers, there are no carry-chains in the design, as the coefficients are always reduced modulo p = 2. However, the result is yet to be reduced modulo the primitive polynomial  $P(x) = x^4 + x^3 + 1$ . This is shown below, where higher degree coefficients are reduced (mod P(x)).

|       | ( ))  |       |        |                                                                                        |

|-------|-------|-------|--------|----------------------------------------------------------------------------------------|

| $s_3$ | $s_2$ | $s_1$ | $s_0$  |                                                                                        |

| $s_4$ | 0     | 0     | $s_4$  | $s_4 \cdot \alpha^4 \pmod{P(\alpha)} = s_4 \cdot (\alpha^3 + 1)$                       |

| $s_5$ | 0     | $s_5$ | $s_5$  | $s_5 \cdot \alpha^5 \pmod{P(\alpha)} = s_5 \cdot (\alpha^3 + \alpha + 1)$              |

| $s_6$ | $s_6$ | $s_6$ | $s_6$  | $s_6 \cdot \alpha^6 \pmod{P(\alpha)} = s_6 \cdot (\alpha^3 + \alpha^2 + \alpha + 1)$   |

| $z_3$ | $z_2$ | $z_1$ | $z_0$  |                                                                                        |

| The   | final | resi  | ılt (o | utput) of the circuit is: $Z = z_0 + z_1 \alpha + z_2 \alpha^2 + z_3 \alpha^3$ ; where |

$z_0 = s_0 + s_4 + s_5 + s_6; \ z_1 = s_1 + s_5 + s_6; \ z_2 = s_2 + s_6; \ z_3 = s_3 + s_4 + s_5 + s_6.$

The above multiplier design is called the *Mastrovito multiplier* [61], which is the most straightforward way to design a multiplier over  $\mathbb{F}_{2^k}$ . A logic circuit for a 4-bit *Mastrovito* multiplier over *finite field*  $\mathbb{F}_{2^4}$  is illustrated in Fig. 3.2.

Modular multiplication is at the heart of many public-key cryptosystems, such as Elliptic Curve Cryptography (ECC) [64]. Due to the very large field size (and hence the datapath width) used in these cryptosystems, the above *Mastrovito* multiplier architecture is inefficient, especially when exponentiation and repeat multiplications are performed. Therefore, efficient hardware and software implementations of modular

**Figure 3.2**. Mastrovito multiplier over  $\mathbb{F}_{2^4}$ .

multiplication algorithms are used to overcome the complexity of such operations. These include the Montgomery reduction [65] [48] and the Barrett reduction [46].

Montgomery Reduction: Montgomery reduction (MR) computes:

$$G = MR(A, B) = A \cdot B \cdot R^{-1} \pmod{P(x)}$$

(3.8)