# IMPROVED DATA TRANSMISSION VIA INDUCTIVE LINK FOR NEURAL RECORDING DEVICES

by

William Anthony Smith

A thesis submitted to the faculty of The University of Utah in partial fulfillment of the requirements for the degree of

Master of Science

Department of Electrical and Computer Engineering

The University of Utah

August 2011

Copyright  $\bigodot$  William Anthony Smith 2011

All Rights Reserved

## The University of Utah Graduate School

## STATEMENT OF THESIS APPROVAL

| The thesis of     | Willia                        | am Anthony Smith     |                             |

|-------------------|-------------------------------|----------------------|-----------------------------|

| has been approved | l by the following supervisor | ry committee members | :                           |

|                   | Reid Harrison                 | , Chair              | 04/12/2011 Date Approved    |

|                   | Darrin Young                  | , Member             | 04/12/2011 Date Approved    |

| ]                 | Bradley Greger                | , Member             | 04/12/2011<br>Date Approved |

| and by            | Gianluca L                    | azzi                 | , Chair of                  |

| the Department of | Electrical                    | and Computer Engin   | ieering                     |

and by Charles A. Wight, Dean of The Graduate School.

## ABSTRACT

Fully integrated, implantable, and wireless neural interface systems typically require a forward data link in addition to the telemetry link that transmits data from the chip. One popular way to create this forward data link is to amplitude modulate the magnetic field of the inductive link that provides the device with wireless power. However, the limitations of these channels when loaded with a rectifier and amplitude modulated have not previously been characterized, and this lack of understanding caused previous versions of the Integrated Neural Interface (INI) to have forward data communication issues, which needed to be corrected for the next generation of the device, INIR8. This thesis first develops an analytical method of characterizing this sort of wireless channel. It then shows measurement data that verifies the validity of the model in the desired region of operation. The available bandwidth as determined by this analytical method, and confirmed by simulation, is insufficient for many applications. Therefore, the next subject of this thesis is to increase the data rate beyond what the bandwidth of the system can intrinsically support by using an equalization technique. This technique is shown to support very robust data recovery under a variety of operating conditions and to data rates much higher than otherwise possible. Another way to improve the reliability of data recovery is to develop a robust digital control system with error detection capabilities. This was done for INIR8, and works very reliably. The end result of this effort is a very robust forward data communication in INIR8, as well as a new analytical method for characterizing inductively coupled channels with certain loads and modulation techniques.

## CONTENTS

| AB  | BSTRACT                                                                                                                                                                                                                                                                                                                                                                                                                               | iii                                                      |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| LIS | ST OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                         | vi                                                       |

| LIS | ST OF TABLES                                                                                                                                                                                                                                                                                                                                                                                                                          | viii                                                     |

| AC  | CKNOWLEDGEMENTS                                                                                                                                                                                                                                                                                                                                                                                                                       | ix                                                       |

| CH  | IAPTERS                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                          |

| 1.  | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                          | 1                                                        |

|     | <ul> <li>1.1 Review of Inductive Link Technology</li> <li>1.2 INI Project Previous Work</li> <li>1.3 Scope of this Thesis</li> </ul>                                                                                                                                                                                                                                                                                                  | $egin{array}{c} 3 \ 5 \ 6 \end{array}$                   |

| 2.  | CHARACTERIZING THE INDUCTIVE LINK CHANNEL                                                                                                                                                                                                                                                                                                                                                                                             | 8                                                        |

|     | <ul> <li>2.1 Inductive Power and Data Transmission</li></ul>                                                                                                                                                                                                                                                                                                                                                                          | $9 \\ 10 \\ 10 \\ 14 \\ 16 \\ 17 \\ 18 \\ 22$            |

| 3.  | INCREASING INDUCTIVE LINK DATA RATE                                                                                                                                                                                                                                                                                                                                                                                                   | <b>23</b>                                                |

|     | <ul> <li>3.1 General Approach</li> <li>3.2 Implementation</li> <li>3.2.1 Filter Stage</li> <li>3.2.2 High-Frequency Attenuation</li> <li>3.2.3 Comparator Stage</li> <li>3.3 Measurement</li> <li>3.3.1 Robustness to Smoothing Capacitor</li> <li>3.3.2 Robustness to Load Resistance</li> <li>3.3.3 Robustness to Modulation Depth</li> <li>3.3.4 Maximum Input Frequency</li> <li>3.3.5 Reliability of Recovered Pulses</li> </ul> | 25<br>26<br>27<br>30<br>31<br>33<br>34<br>35<br>38<br>38 |

|     | 3.4 Results                                                                                                                                                                                                                                                                                                                                                                                                                           | 40                                                       |

| 4. | DIGITAL CONTROL SYSTEM FOR THE INI-R8          | 42 |

|----|------------------------------------------------|----|

|    | 4.1 Wireless Data Transmission System Overview | 43 |

|    | 4.1.1 Priming Bits                             | 47 |

|    | 4.1.2 Header                                   | 47 |

|    | 4.1.3 Op-codes                                 | 47 |

|    | 4.1.4 Footer                                   | 48 |

|    | 4.2 Converting the Pulse Train to a Bit Stream | 48 |

|    | 4.2.1 Specifications for Operation             | 50 |

|    | 4.3 Hamming Encoding                           | 51 |

|    | 4.4 Addressable Components                     | 52 |

|    | 4.4.1 Diagnostic Register                      | 53 |

|    | 4.4.2 Spike Detector Threshold Control         | 53 |

|    | 4.4.3 Spike Detector Polarity Registers        | 54 |

|    | 4.4.4 RF Transmitter Control                   | 54 |

|    | 4.4.5 ADC Amplifier Select                     | 54 |

|    | 4.5 Wired Command Protocol                     | 55 |

|    | 4.6 Results                                    | 55 |

| 5. | CONCLUSIONS                                    | 56 |

| AF | PPENDIX: ADDITIONAL DATA RECOVERY FIGURES      | 59 |

| RE | CFERENCES                                      | 63 |

## LIST OF FIGURES

| SEM Image of the Utah Electrode Array                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A fully-integrated INI device.                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Circuit diagram of inductively powered RLC system with diode bridge<br>rectifier load. (a) shows the circuit with series parasitic resistance; (b)<br>shows the narrowband equivalent circuit with parallel parasitic resis-<br>tance.                                                                                                                                                                                                                                                 | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ASK waveform viewed at the amplifier output $(V_A)$ , the transmit inductor $(V_T)$ and the receive tank $(V_R)$ .                                                                                                                                                                                                                                                                                                                                                                     | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

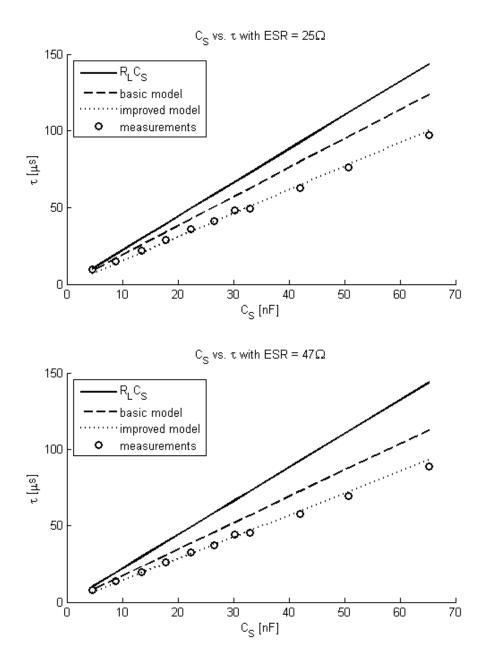

| Sweep of smoothing capacitor values for two different inductor equiva-<br>lent series resistances. The circles are the measured data points. The<br>solid line represents the time constant predicted by just considering the<br>load resistance and smoothing capacitance. The dashed line represents<br>the time constant predicted by the basic model developed in Section<br>2.2.1. The dotted line represents the improved model that accounts for<br>power lost in the rectifier | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Sweep of load resistance values for two different inductor equivalent series resistances. The circles are the measured data points. The solid line represents the time constant predicted by just considering the load resistance and smoothing capacitance. The dashed line represents the time constant predicted by the basic model developed in Section 2.2.1. The dotted line represents the improved model that accounts for power lost in the rectifier.                        | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

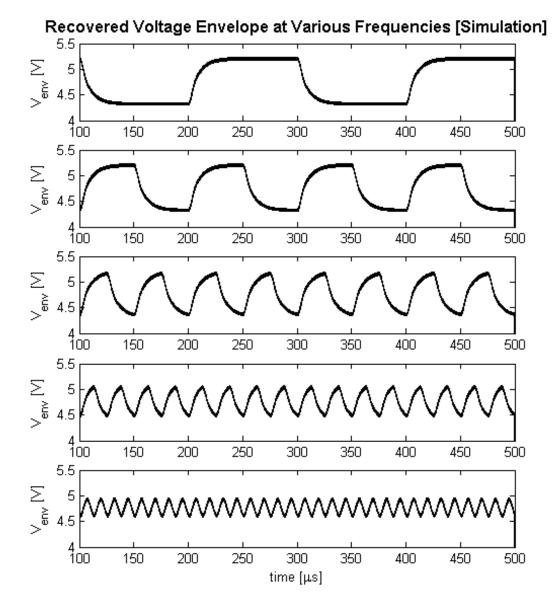

| Recovered voltage envelope for square wave modulation of transmit coil voltage. Modulation frequencies are 5 kHz, 10 kHz, 20 kHz, 40 kHz, and 80 kHz respectively.                                                                                                                                                                                                                                                                                                                     | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

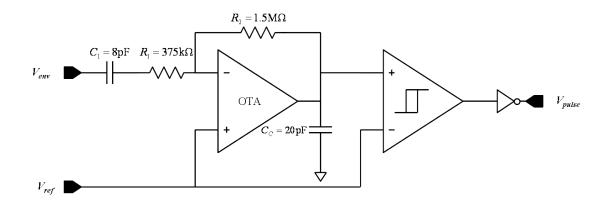

| Design of the Data Recovery Filter Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                             | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

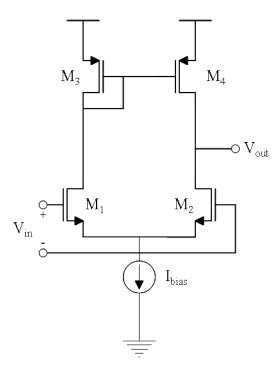

| Single-stage amplifier used for the high pass filter. $M_1 = M_2$ have $W = 3 \mu\text{m}, L = 0.7 \mu\text{m}, \text{ and } M = 2.$ $M_3 = M_4$ have $W = 3 \mu\text{m}, L = 0.7 \mu\text{m}, \text{ and } M = 1.$ $I_{bias} = 40 \mu\text{A}, \text{ and } V_{DD} = 2.5 \text{V}.$                                                                                                                                                                                                   | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

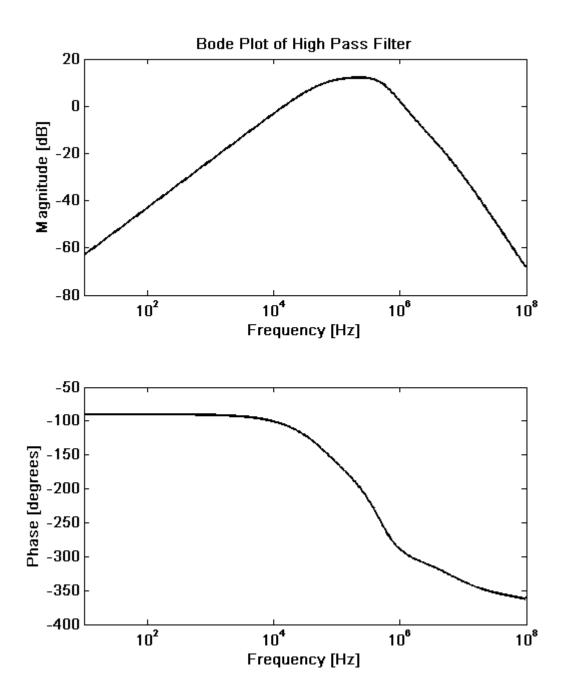

| Bode plot of the data recovery circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | A fully-integrated INI device.<br>Circuit diagram of inductively powered RLC system with diode bridge<br>rectifier load. (a) shows the circuit with series parasitic resistance; (b)<br>shows the narrowband equivalent circuit with parallel parasitic resis-<br>tance.<br>ASK waveform viewed at the amplifier output $(V_A)$ , the transmit induc-<br>tor $(V_T)$ and the receive tank $(V_R)$ .<br>Sweep of smoothing capacitor values for two different inductor equiva-<br>lent series resistances. The circles are the measured data points. The<br>solid line represents the time constant predicted by just considering the<br>load resistance and smoothing capacitance. The dashed line represents<br>the time constant predicted by the basic model developed in Section<br>2.2.1. The dotted line represents the improved model that accounts for<br>power lost in the rectifier.<br>Sweep of load resistance values for two different inductor equivalent<br>series resistances. The circles are the measured data points. The solid<br>line represents the time constant predicted by just considering the load<br>resistance and smoothing capacitance. The dashed line represents the<br>time constant predicted by the basic model developed in Section<br>2.2.1. The dotted line represents the improved model that accounts for<br>power lost in the rectifier.<br>Sweep of load resistance values for two different inductor equivalent<br>series resistances and smoothing capacitance. The dashed line represents the<br>time constant predicted by the basic model developed in Section 2.2.1.<br>The dotted line represents the improved model that accounts for power<br>lost in the rectifier.<br>Recovered voltage envelope for square wave modulation of transmit coil<br>voltage. Modulation frequencies are 5 kHz, 10 kHz, 20 kHz, 40 kHz, and<br>80 kHz respectively.<br>Design of the Data Recovery Filter Circuit<br>Single-stage amplifier used for the high pass filter. $M_1 = M_2$ have<br>$W = 3 \mu m$ , $L = 0.7 \mu m$ , and $M = 2$ . $M_3 = M_4$ have $W = 3 \mu m$ ,<br>$L = 0.7 \mu m$ , and $M = 1$ . $I_{bias} = 40 \mu A$ , and $V_{DD} = 2.5 V$ . |

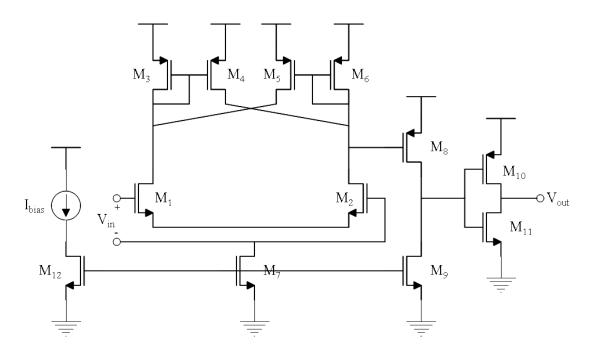

| 3.5 | Transistor level schematic for the data recovery comparator. $M_1 = M_2$<br>have $W = 2.4 \mu\text{m}$ , $L = 0.55 \mu\text{m}$ , and $M = 2$ . $M_3 = M_4 = M_5 = M_6$<br>have $W = 2.2 \mu\text{m}$ , $L = 0.55 \mu\text{m}$ , and $M = 2$ . $M_7 = M_9 = M_{12}$<br>have $W = 5.5 \mu\text{m}$ , $L = 0.55 \mu\text{m}$ , and $M = 1$ . $M_8$ has $W = 13.5 \mu\text{m}$ ,<br>$L = 0.55 \mu\text{m}$ , and $M = 1$ . $M_{10}$ has $W = 4.4 \mu\text{m}$ , $L = 0.35 \mu\text{m}$ , and<br>$M = 1$ . $M_{11}$ has $W = 2.2 \mu\text{m}$ , $L = 0.35 \mu\text{m}$ , and $M = 1$ . $I_{bias} = 1 \mu\text{A}$ ,<br>and $V_{DD} = 2.5 \text{V}$ | 31 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

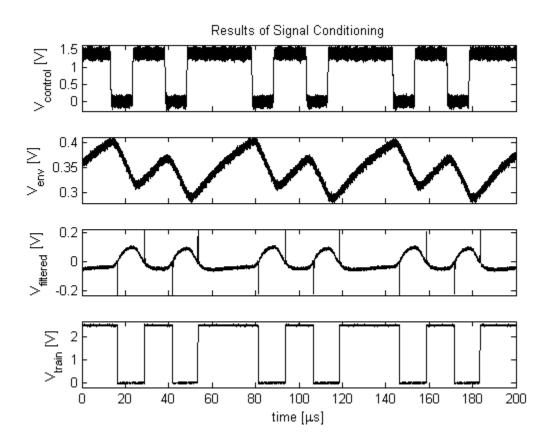

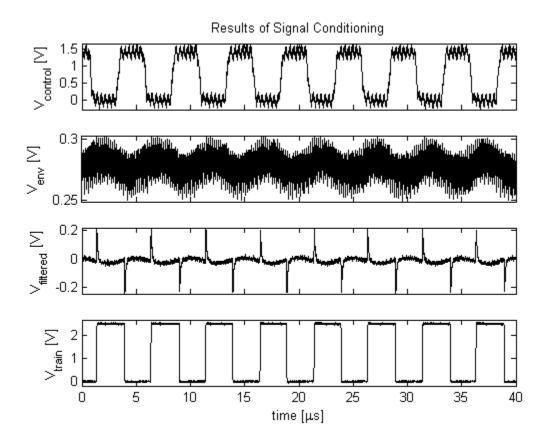

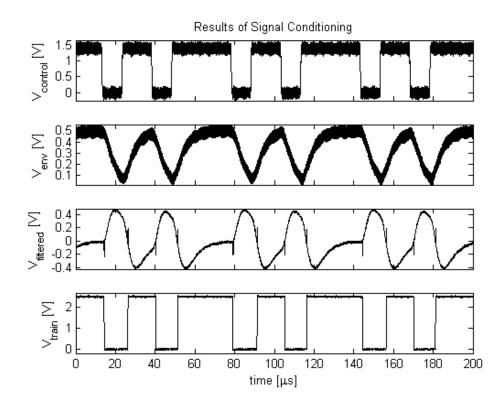

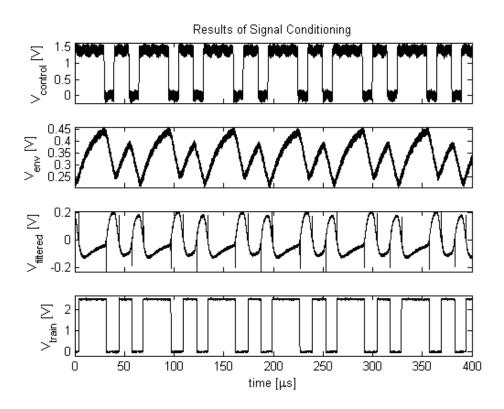

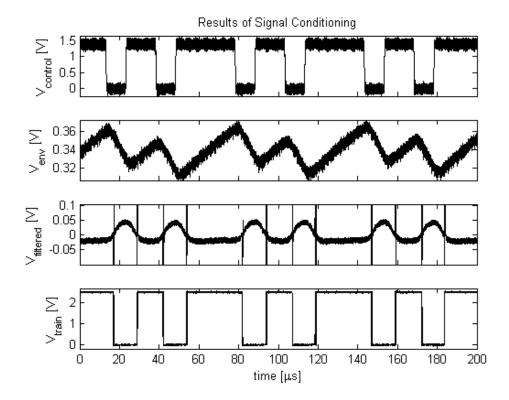

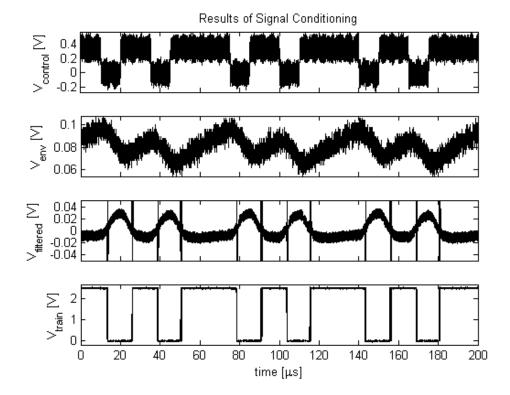

| 3.6 | Sample test chip output with default setup. Alternating '1' and '0' pulsetrain.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 33 |

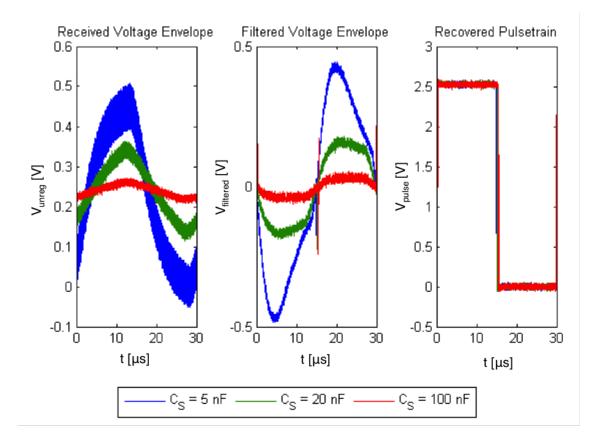

| 3.7 | Parametric sweep of $C_S$ for small [5 nF], moderate [20 nF], and large [100 nF] smoothing capacitors for one period of a 33.3 MHz square wave modulation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 35 |

| 3.8 | Pulse train recovery at 200 kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 39 |

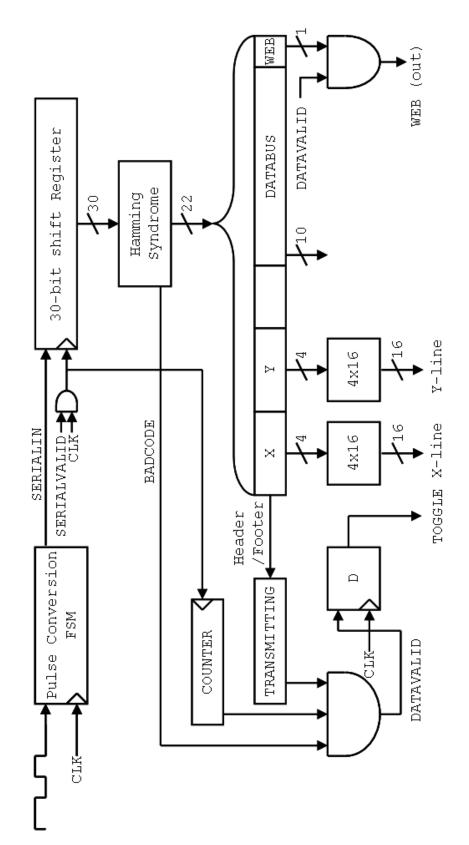

|     | INI8 digital controller block diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 44 |

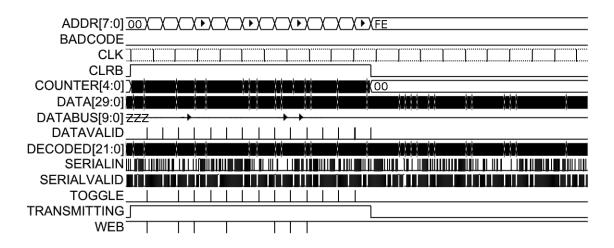

| 4.2 | Large scale simulation of serial data being parallelized and decoded                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 46 |

| 4.3 | Simulation of serial data during the completion of parallelization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 46 |

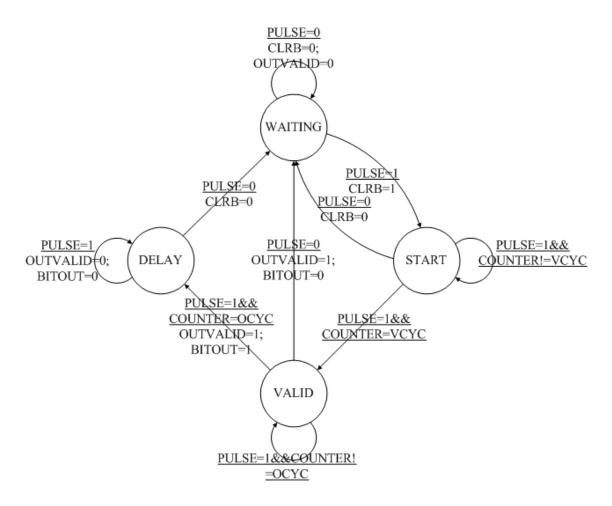

| 4.4 | State diagram for pulse train to bit stream conversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 49 |

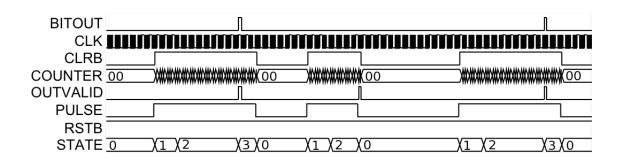

| 4.5 | Simulation of State Machine for '101' bit stream. For the simulation<br>both $1$ and $0$ pulses are given the same period. This dramatically<br>simplifies testbench design, but the low period following a pulse can be<br>any duration longer than a single clock cycle, at least from the digital<br>logic perspective.                                                                                                                                                                                                                                                                                                                     | 49 |

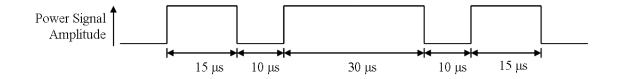

| 4.6 | Timing of a transmission of '010' using the INIR8 modulation scheme $% \mathcal{A}^{(1)}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 51 |

| A.1 | Pulse train recovery with a $5 \mathrm{nF}$ smoothing capacitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 59 |

| A.2 | Pulse train recovery with a $20\mathrm{nF}$ smoothing capacitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 60 |

| A.3 | Pulse train recovery with a $100 \mathrm{nF}$ smoothing capacitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 61 |

| A.4 | Pulse train recovery with a 50 nF smoothing capacitor and a 5% trans-<br>mitted modulation depth.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 62 |

## LIST OF TABLES

| 3.1 | Received Modulation Depth by Transmitted Modulation Depth | 36 |

|-----|-----------------------------------------------------------|----|

| 3.2 | SNR by Transmitted Modulation Depth                       | 36 |

| 3.3 | Reliability of Recovered Pulses at Several Frequencies    | 41 |

| 3.4 | Data Recovery Circuit Specifications                      | 41 |

| 4.1 | Summary of Addressable Components in INIR8 System.        | 53 |

## ACKNOWLEDGEMENTS

I would first like to thank my adviser, Reid Harrison, for his support and patience as I asked innumerable questions. The immense amount of knowledge I have gained during this process is primarily due to his influence. Also I thank those who supported me in testing: Dave Warren for his extensive support in testing and developing the MATLAB code for the INIR8, and Asha Sharma who answered many questions, especially when I was new to the project. I would also like to thank the rest of my committee, Darrin Young and Bradley Greger, for their support and encouragement. Finally, I would like to thank my parents for instilling in me the value and importance of education, and for their support of my undergraduate studies.

## CHAPTER 1

## INTRODUCTION

The study of devices that interface with the brain and nervous system is quickly becoming one of the most important topics in electrical engineering. These devices can be used for a variety of purposes, from the diagnosis of diseases, to exploratory neuroscience research, to the development of brain-machine interfaces that will allow unresponsive or prosthetic limbs to function by observing the neural activity in certain parts of the brain.

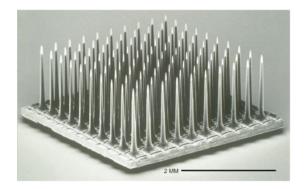

In order to observe and stimulate neural activity while limiting the risk of infection in study subjects, it is important to develop neural recording systems that can be surgically implanted without the need for transcutaneous wires. It is also desirable to have a large number of electrodes, such as the Utah Electrode Array (UEA) shown in Fig. 1.1, that simultaneously record neural activity [1]. Achieving these goals is a very complex task that has been the focus of significant research in universities around the world in the past decade.

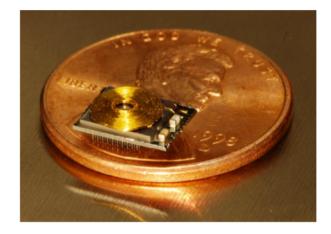

The Integrated Neural Interface (INI) project is one attempt at solving this problem. The INI is a fully wireless system that sends and receives all power and data signals wirelessly, and without a battery (see Fig. 1.2). In achieving this goal, the device must perform amplification and signal processing on-chip, and then wirelessly transmit the data off-chip. Additionally, the device must be wirelessly powered and forward control data must also somehow be wirelessly transmitted. All of these must be done without effecting damage to the surrounding tissue, so stringent power requirements must be obeyed.

The developed integrated circuit is then is flip-chip bonded to a 100-electrode UEA and requires only three additional off-chip components, namely a coil to receive power and data via inductive coupling, a resonating capacitor used to increase the coupling

Figure 1.1. SEM Image of the Utah Electrode Array.

Figure 1.2. A fully-integrated INI device.

efficiency of the power transfer, and a smoothing capacitor to be used with the rectifier circuit. The small form factor that results from this high level of integration is ideal for implantation in the body.

Four fundamental components must be wirelessly transmitted and received: forward control data, reverse telemetry data, power, and a clock signal, to be used by the digital electronics. This thesis concerns itself with the reliable transmission of control data via modulation of the inductive link used for power transmission. This method is desirable because it simplifies implant design. The power receive coil serves dual purposes for both power and data recovery, eliminating the need for an additional antenna. There is little power expended in signal recovery, since the envelope of the modulation is recovered automatically by the chip's voltage rectifier when amplitude modulation (AM) is utilized.

The use of inductive links for wireless power and data transmission has been a significant worldwide research effort, and some of that research will be discussed in Section 1.1. The current state of the INI project, especially that concerned with forward data transmission and the issues that it currently has will be discussed in Section 1.2. The reliable transmission of control data has been a serious problem in the INI project, and the primary purpose of this thesis is to address these issues. Section 1.3 will discuss how this thesis plans to address these issues.

### 1.1 Review of Inductive Link Technology

One of the primary methods of generating power wirelessly is the use of two magnetically coupled inductors. On one end, a power amplifier generates an oscillating sinusoidal waveform across one of the inductors. This amplifier is typically a Class-E power amplifier [2]. This amplifier configuration has efficiency approaching 100% for well designed amplifiers, because the current and voltage waveforms are nonzero only half of the period and can be offset by 180°.

The inductor that receives power is magnetically coupled to the transmitting inductor that is part of the Class-E amplifier. The transmitting inductor is typically large, but the receiving coil is typically quite small so that it can be surgically implanted. As a result, the coupling coefficients of these amplifiers are usually low, and a large voltage must appear across the transmitting coil. This occurs naturally in a Class-E amplifier, since the amplifier always drives a high-Q LC tank circuit in order to produce a robust sinusoid. This type of configuration is seen in [3, 4, 5].

Although the Class-E power amplifier is desirable due to its high efficiency operation, one of the major drawbacks is the vulnerability to variations in inductor and capacitor value, since it relies on a large resonant peak to achieve high efficiency. This is especially troublesome because they inductor value can vary with environmental factors, such as nearby metal objects. As a result, there have been efforts to implement a closed-loop system to compensate for variability in capacitor and inductor values [6, 7, 8], typically by varying the carrier frequency to ensure it is always at the peak of resonance.

It is also common to transmit data using the inductive link. By modulating the power carrier in some fashion, data can be transmitted to the device with low overhead. Modulation has been done in a variety of ways, most commonly using some form of amplitude-shift keying (ASK) or frequency-shift keying (FSK). Amplitudeshift keying has historically been the primary means of data transmission across inductive links. This is primarily due to the ease of implementation for both the transmitter and receiver [9, 10, 11]. Frequency-shift keying the magnetic field is an alternative to ASK, and has two primary advantages. First, it does not suffer from the smoothing capacitor charging effects that are the subject of Chapter 2 of this thesis, and it also is more robust against noise and interference [12, 13].

All of the previously mentioned literature discusses the use of a single inductive link to transmit both power and data, but more recent research has begun to explore the possibilities of using multiple carriers by utilizing multiple carriers. In [14, 15], two inductors are used to recover power and data links at different frequencies. They are placed orthogonally to minimize the interference between the two coils. In both cases, the power transmission coil is placed in the traditional configuration to receive the maximum magnetic field, and an additional coil is wrapped around the transmit coil, where both the transmit and receive data coils are in the same plane.

A third use of the multiple carrier technique is seen in [16]. Instead of using geometric alignment to eliminate interference between the power and data band, Zhao et al. have both transmit and receive coils geometrically coaxial, and utilize a differential phase-shift keying (DPSK) demodulation technique to cancel interference between the two coils.

A fourth use of the multiple carrier technique is presented in [17]. Simard et. al. choose to use a coplanar technique, where the coils are in the same plane but are not coaxial. Data is modulated using offset quadrature phase-shift keying (OQPSK) to achieve very high data rates (4.16 Mb/s) with low bit error rates ( $2 \times 10^{-6}$ ). They also include a coplanar back-telemetry link, making the system bidirectional.

## 1.2 INI Project Previous Work

The INI project is an attempt to develop fully integrated neural recording and stimulation devices that can be flip-chip bonded to a Utah Electrode Array. The first two attempts at developing this system were the INI1 and INI2 devices, documented in [18]. These devices had issues with digital interference and required several off chip components, so a second major revision, INI3, was developed as discussed in [19]. Since that time, several minor revisions have been made, and the newest attempt is INIR8, which has been redesigned for the  $0.35 \,\mu$ m process and contains the changes indicated in this thesis.

One of the primary issues that still plagues the INI devices is the reliable wireless transmission of forward control data. Existing devices up to INIR7 have seen significant problems for two reasons.

First, the wireless data is transmitted via ASK, and there were significant data attenuation issues due to a lack of complete understanding of channel behavior. The result was that square wave modulation of the power signal resulted in a received triangle wave modulation. This, in combination with noise and small dc offsets caused the device to recover data unreliably because the transitions between high and low modulation were unreliably recovered. One attempt was made to reduce this problem by changing the waveform of the ASK envelope. By creating a large initial voltage at the beginning of the amplitude shift, modest improvements in performance were seen. However, it was still clear that a better solution was needed.

The other issue with transmission of control data was the way that control data was interpreted by the device. As discussed in [18], control of the device is achieved by transmitting a very long string of bits (1024 bits for the INIR7), which essentially means that the entire device is reprogrammed every time a single change is desired. When using a wireless channel to transmit this data that already has significant reliability issues, this large amount of data means that it becomes very difficult to successfully transmit an entire string of bits. The result is that when changing one control register, a pseudo-random change in another register is likely to occur. Additionally, because there is no error detection capability, these changes may go unnoticed, and the chip may operate in an undesired state. A more robust technique for controlling the device and error detection are clearly both desirable.

## 1.3 Scope of this Thesis

The purpose of this thesis is to address the concerns identified in Section 1.2. When determining how to address the problem, several approaches were identified. There are clearly several ways to transmit data with inductive links, as discussed in Section 1.1, and most are more reliable and robust than ASK. The need for clock recovery from the power transmission frequency eliminates the possibility of using a singlecarrier FSK system without requiring a power-hungry phase-locked loop. Dual-carrier systems have a lot of advantages, but they require considerable additional fabrication complexity. As a result, ASK was still determined to be the most appropriate choice for this project.

Although there has been significant prior work done using the inductive link as a data carrier, the bandwidth of this using ASK has never been characterized. In fact, many papers assume that the bandwidth is directly related to the quality factor (Q) of the transmit and receive coils, while in reality the Q factor is only a second order concern for AM. This assumption caused previous implementations of the INI chip to overestimate the available bandwidth for transmitting data across the inductive link, which resulting in very unreliable transmission. Chapter 2 concerns itself with characterizing the bandwidth of this inductive link channel.

The resulting bandwidth derived from Chapter 2 is relatively small, and while it could be utilized for neural recording applications with some success, it would cause data transmission times that could become large enough to be perceptible by operators for longer command sequences. Additionally, this same system could be used for stimulation chips that require a much larger forward data bandwidth. Thus, a solution for increasing the bandwidth of the system was needed. The solution implemented in the INIR8 is presented in Chapter 3.

As discussed, the existing INI system requires a complete transmission of the entire set of control data across the inductive link for each change in parameter. Chapter 4 discusses a new digital control interface that eliminates this need, which also increases the reliability of the forward data link.

In Chapter 5 the results of all work are reviewed and discussed.

## CHAPTER 2

# CHARACTERIZING THE INDUCTIVE LINK CHANNEL

The steady state behavior of inductively powered systems is well understood [3, 20]. However, an understanding of their transient behavior is relatively unexplored, and is very important when the inductive coupling is also used for data transmission, as is the case with the INI project. A power efficient and simple method for achieving low data rate wireless transmission to an inductively powered biological implant is through amplitude modulation of the magnetic field [19, 21, 7].

Intuitively, an understanding of transient behavior should possible with knowledge of standard second order LC systems; however, real systems loaded with voltage rectifiers and ripple smoothing capacitors can have dramatically altered behavior, as will be demonstrated in this paper. Unfortunately, direct linear circuit analysis of a system with a rectifier is not possible due to the nonlinearities introduced by the diodes. Instead, another approach must be taken to develop an understand the transient behavior. In this chapter a method is developed that characterizes and models the transient response and the resulting bandwidth of a rectifier-loaded inductively powered system that uses amplitude-shift keying (ASK) for data transmission.

This chapter is organized as follows: Section 2.1 gives the reader a general understanding of power and ASK data transmission using inductive coupling; Section 2.2 will develop an analytical model for the behavior of this type of system; Section 2.3 will show measurement results that confirm the accuracy of this model; and Section 2.4 will discuss the impact of these results.

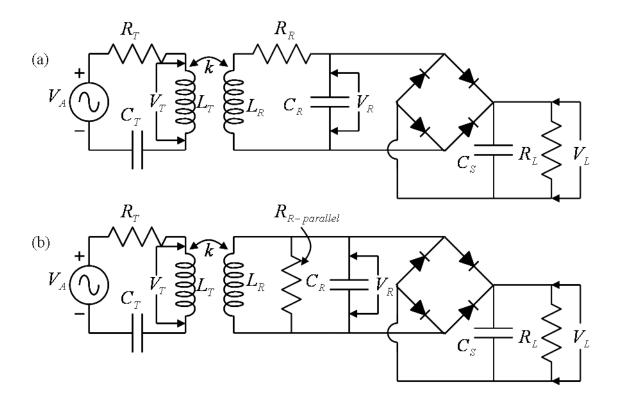

## 2.1 Inductive Power and Data Transmission

Fig. 2.1(a) is an example of an inductively powered system. The voltage transmitted by  $V_A$  can be amplitude modulated, which produces an amplified voltage on  $L_T$ ,  $(V_T)$  that may be attenuated by the bandwidth of the transmitting LC tank.  $L_T$  is magnetically coupled to  $L_R$ , and some percentage of the transmitted voltage is received across  $L_R$  (see [3, 20]). The attenuation of the received voltage is not primarily determined by the bandwidth of the receive coil and resonanting capacitor. Instead, the various load resistances,  $(R_L, R_R, \text{ and the loss in the diodes})$ , and the size of the smoothing capacitor  $C_S$  turn out to be the dominant parameters.

One method of evaluating system bandwidth is simply to ignore losses other than the load resistance. This would result in a recovered voltage with an envelope described by the time constant  $\tau_{env} = R_L C_S$ , and from that time constant the bandwidth of the system could easily be derived. In most cases; however, this

**Figure 2.1**. Circuit diagram of inductively powered RLC system with diode bridge rectifier load. (a) shows the circuit with series parasitic resistance; (b) shows the narrowband equivalent circuit with parallel parasitic resistance.

method is overly conservative and can dramatically underestimate system bandwidth. Instead, a method was developed to describe the time constant accounting for the entire system, a task made more complex by the nonlinear nature of rectification.

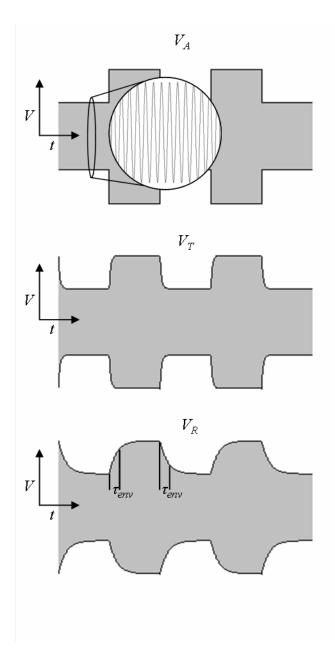

Fig. 2.2 shows a typical ASK waveform at various locations in the circuit seen in Fig. 2.1(a). The first waveform is of the ASK modulation created by the amplifier, which is essentially ideal in most cases. The second waveform shows the shape of the waveform across  $L_T$ . The shape of this waveform depends on  $L_T$ ,  $C_T$ , and  $R_T$ , and may have overshoot in an underdamped system. However, this transient is also typically negligible when compared to  $V_R$ , the received voltage across the parallel LCtank. Understanding this third waveform is an important goal for this thesis, and the question is explored here.

Values predicted by the standard equations for a linear second order system tell us almost nothing about how that system will respond to amplitude modulation when rectification is added. In fact, for conditions typical of devices developed for the INI project, the standard second order equations predict a time constant of the received voltage envelope that is between one and two orders of magnitude removed from the measured value.

## 2.2 Modeling the Transient Response

The first concern is the development of an analytical model that will attempt to characterize the transient response of the system. The purpose of this model is to be simple and intuitive, and some accuracy is sacrificed in achieving this goal.

#### 2.2.1 Basic Model

Analysis of the circuit in Fig. 2.1(a) cannot be done using standard linear circuit analysis, because the diodes create nonlinear behavior. Instead, a fundamental definition of the quality factor Q of a second order RLC circuit is used as a basis for analysis of the circuit behavior. This definition is given in Equation 2.1 [22].

$$Q = \omega_{res} \frac{energy \ stored}{average \ power \ dissipated} \tag{2.1}$$

**Figure 2.2**. ASK waveform viewed at the amplifier output  $(V_A)$ , the transmit inductor  $(V_T)$  and the receive tank  $(V_R)$ .

By considering the total energy stored and the total power dissipated in the system, a  $Q_{pseudo}$  can be obtained that reasonably describes the transient behavior of the system. This has been done in Equation 2.2.

$$Q_{pseudo} \equiv \omega_{res} \frac{\frac{1}{2}C_R V_{R-peak}^2 + \frac{1}{2}C_S V_L^2}{\frac{V_L^2}{R_L} + P_{rect} + \frac{V_{R-rms}^2}{R_{R-parallel}}}$$

(2.2)

The energy stored in the receive side of the circuit can be completely described by the numerator of Equation 2.2. Energy is stored in two places in the circuit shown in Fig. 2.1: oscillating between  $L_R$  and  $C_R$ , and in the smoothing capacitor  $C_S$ . The energy stored in the tank can be described by  $\frac{1}{2}C_R V_{R-peak}^2$  because at the peak voltage all of the energy is stored in the capacitor. The energy stored in  $C_S$  is described by  $\frac{1}{2}C_S V_L^2$ .

The average power dissipated in the circuit is given by the denominator of Equation 2.2. There are three terms that represent the primary sources of power dissipation in the circuit: the load, represented by  $R_L$  in Fig. 2.1; loss in the diode bridge rectifier; and coil loss, represented by  $R_R$  in Fig. 2.1(a). Because the power dissipated in the rectifier circuit is nonlinear and varies considerably, it is noted simply as  $P_{rect}$  in this equation. Also, while the receive LC tank's resistance is due to the resistance of the coil, and is thus a series resistance, it can be converted to a narrowband equivalent parallel resistance by considering that  $R_{R-parallel} \approx Q_R^2 R_R$  [22]. This can be seen in Fig. 2.1(b) and results in the approximate direct expression for  $R_{R-parallel}$  given in Equation 2.3.

$$R_{R-parallel} \approx \frac{\omega_{res}^2 L_R^2}{R_R} \tag{2.3}$$

At this point the expression for  $Q_{pseudo}$  is still fairly complicated, but a few simplifications can still be made. First, since the size of the resonating capacitor of the receive coil  $C_R$  is determined by  $C_R = (\omega_0^2 L_R)^{-1}$ , when  $f_0$  is on the order of a few megahertz and  $L_R$  is a few tens of microhenries, a smoothing capacitor on the order of tens of nanofarads will completely dominate  $C_R$ , since  $V_{R-max}$  and  $V_L$  are similarly valued. The next simplification, which will be shown to reduce the accuracy of the model, is to completely idealize the diodes, giving them no power dissipation. Also, the voltage drop across the diodes are neglected, so  $V_{R-max} = V_L$  is assumed. Neglecting the diode drop will cause the power dissipated in the load to be somewhat overestimated. The diode drop could be as high as 1 V, depending on what type of diode is selected. So, for a typical  $V_{R-max}$  of 5 V, this can result in as much as a 20% error in calculating the power in the load. The complete neglect of the power dissipated in the diode drop has an even larger effect, and in the opposite direction. Nevertheless, both of these components are ignored in order to obtain a first order expression that, as will be shown, does a reasonably good job of modeling the results.

The resulting equation from these simplifications is shown here:

$$Q_{pseudo} \approx \frac{\omega_{res} C_S}{1/R_{R-parallel} + 2/R_L} \tag{2.4}$$

Then, by considering that  $\tau_{env} = 2Q/\omega_{res}$ , a simple and interesting expression can be derived for the time constant of the envelope, which is shown here:

$$\tau_{env} \approx \frac{C_S}{1/(2R_{R-parallel}) + 1/R_L} \tag{2.5}$$

$\tau_{env}$  describes the rate that the envelope of voltage seen at  $V_R$  can change, as noted on the  $V_R$  waveform in Fig. 2.2 This value is fundamental in determining the bandwidth of the system.

This expression for  $\tau_{env}$  shows that the loss in the coil takes the form of a resistance in parallel.  $R_{R-parallel}$  is doubled because it has an oscillating voltage across it and half power is dissipated with respect to the peak voltage of oscillation  $(V_L)$ . There would be another term if the power lost in the diodes were included, and as the coil loss and diode loss become smaller the expression simplifies to the time constant of the simple RC circuit defined by the smoothing capacitor and load resistance. So, for very efficient coils with negligible diode power lost, the transient response of the voltage envelope is dominated by the simple first order RC system load, and the inductive link behaves as an ideal current source. For a conceptual understanding of the dominance of the load in determining the transient response of the LC tank, consider that when the receive coil is being charged by the transmit coil, a large portion of the charge that would otherwise resonate in the system is being discharged into the smoothing capacitor. Additionally, there is reflected resistance into the tank system from the power lost in the diodes and the load. As soon as the voltage  $V_R$  across the resonating capacitor increases above the voltage on the smoothing capacitor (at one diode drop above  $V_L$ ), current flows into the  $C_S$ . This happens every cycle, so the charge buildup is dramatically slowed in the LC tank.

As  $V_R$  is reduced, the smoothing capacitor must induce a current that flows through the load resistance and then through the diodes and LC tank, so a net charge is introduced into the tank from the load, slowing the rate of decay. The rising edge transient has the same time constant as the falling edge, though it should be noted that when there is no charge in the LC tank, such as when the system is turned off, the time constant becomes simply  $\tau_{env} = R_L C_S$ .

Because the charge required on  $C_S$  does not contribute to the resonating charge in the coil,  $Q_{pseudo}$  is not a true quality factor. It can accurately predict the bandwidth of the system, and thus the time constant of the amplitude transient, but it cannot be used to predict the actual amplitude of the voltage at resonance.

#### 2.2.2 Accounting for a Nonideal Rectifier

A reasonable intuition can be gained about a system using Equation 2.5; however, if more accurate results are needed, the rectifier must be more carefully considered. Most importantly, the power dissipated in the rectifer must be accounted for. However, because diodes are nonlinear, understanding the power dissipated in them is not trivial.

In order to account for the diode power, the current passing through the rectifier must be approximated. The current through the rectifier is driving some load resistance  $R_L$  and the smoothing capacitor  $C_S$ . For a parallel RC system driven by a stepped current response, the voltage response will be exponential with a time constant  $\tau$ . Thus, if the  $\tau$  is approximated as simply the RC time constant of the load resistance and smoothing capacitor, the rectifier behaves like a step-response current source, so the current through the load can be assumed to be approximately constant and given by the steady state current through the resistor. This results in Equation 2.6.

$$i_{avg} \approx \frac{V_{L-max}}{R_L} \tag{2.6}$$

Making this approximation eliminates the need to calculate a numerical solution and greatly simplifies the resulting expression. Of course,  $\tau$  is not actually governed by the load resistance and smoothing capacitance alone. Because  $\tau$  will actually be smaller than the value used here, the current drawn by the load actually spikes and then decays exponentially. As a result, the predicted power dissipation will also be underestimated. This effect is small enough to be neglected when the power dissipation in the load is dominant, but becomes significant as the power dissipation in the rectifier and in the coil become more significant. The results can be seen in the measurements section.

Now that a reasonable estimation of the average current is known, the power dissipation can be easily derived by considering the voltage drop in the diodes and the current through them, as shown in Equation 2.7. (There are two diodes in the path for a diode bridge rectifier.)

$$P_{avg} \approx 2V_{diode} \frac{V_{L-max}}{R_L} \tag{2.7}$$

Finally, it would be useful to consider Equation 2.7 with units of admittance instead of power, so that it matches the denominator terms in Equations 2.4 and 2.5 and can be added easily as an additional term. In order to accomplish this,  $1/V_L^2$ must be factored. This results in Equation 2.8.

$$\frac{1}{R_{diode}} \approx \left[\frac{2V_{diode}}{V_{L-max}}\right] \frac{1}{R_L}$$

(2.8)

The voltage ratio defines the relative significance of this term. For large load voltages, this term will become negligible, as expected. The value of  $V_{L-max}$  depends