# ALGORITHMS AND METHODOLOGY TO DESIGN ASYNCHRONOUS CIRCUITS USING SYNCHRONOUS CAD TOOLS AND FLOWS

by

Vikas S. Vij

A dissertation submitted to the faculty of

The University of Utah

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Department of Electrical and Computer Engineering

The University of Utah

December 2013

Copyright © Vikas S. Vij 2013

All Rights Reserved

# The University of Utah Graduate School

## STATEMENT OF DISSERTATION APPROVAL

| This dissertation of                                | Vikas S. Vij |                          |

|-----------------------------------------------------|--------------|--------------------------|

| has been approved by the following                  |              | e members:               |

| Kenneth S. Stevens                                  | , Chair      | 11/5/2013 Date Approved  |

| Chris Myers                                         | , Member     | 10/31/2013 Date Approved |

| Erik Brunvand                                       | , Member     | 11/5/2013 Date Approved  |

| Priyank Kalla                                       | , Member     | 10/31/2013 Date Approved |

| Christos Sotiriou                                   | , Member     | Date Approved            |

| and by Gianluca La the Department of Electrical and |              | , Chair of               |

|                                                     |              |                          |

and by David B. Kieda, Dean of the Graduate School.

#### **ABSTRACT**

Asynchronous design has a very promising potential even though it has largely received a cold reception from industry. Part of this reluctance has been due to the necessity of custom design languages and *computer aided design* (CAD) flows to design, optimize, and validate asynchronous modules and systems. Next generation asynchronous flows should support modern programming languages (e.g., Verilog) and *application specific integrated circuits* (ASIC) CAD tools. They also have to support multifrequency designs with mixed synchronous (clocked) and asynchronous (unclocked) designs. This work presents a novel *relative timing* (RT) based methodology for generating multifrequency designs using synchronous CAD tools and flows.

Synchronous CAD tools must be constrained for them to work with asynchronous circuits. Identification of these constraints and characterization flow to automatically derive the constraints is presented. The effect of the constraints on the designs and the way they are handled by the synchronous CAD tools are analyzed and reported in this work.

The automation of the generation of asynchronous design templates and also the constraint generation is an important problem. Algorithms for automation of reset addition to asynchronous circuits and power and/or performance optimizations applied to the circuits using logical effort are explored thus filling an important hole in the automation flow. Constraints representing cyclic asynchronous circuits as *directed acyclic graphs* (DAGs) to the CAD tools is necessary for applying synchronous CAD optimizations like sizing, path delay optimizations and also using *static timing analysis* (STA) on these circuits. A thorough investigation for the requirements of cycle cutting while preserving timing paths is presented with an algorithm to automate the process of generating them.

A large set of designs for 4 phase handshake protocol circuit implementations with early and late data validity are characterized for area, power and performance. Benchmark circuits with automated scripts to generate various configurations for better understanding of the designs are proposed and analyzed. Extension to the methodology like addition of scan

insertion using *automatic test pattern generation* (ATPG) tools to add testability of datapath in bundled data asynchronous circuit implementations and timing closure approaches are also described. Energy, area, and performance of purely asynchronous circuits and circuits with mixed synchronous and asynchronous blocks are explored. Results indicate the benefits that can be derived by generating circuits with asynchronous components using this methodology.

| This dissertation |                |                |                |    |

|-------------------|----------------|----------------|----------------|----|

|                   | have always mo | otivated me an | a supported me | ). |

|                   |                |                |                |    |

|                   |                |                |                |    |

|                   |                |                |                |    |

|                   |                |                |                |    |

|                   |                |                |                |    |

|                   |                |                |                |    |

|                   |                |                |                |    |

|                   |                |                |                |    |

# **CONTENTS**

| AB  | STRACT                                             | iii            |

|-----|----------------------------------------------------|----------------|

| LIS | ST OF FIGURES                                      | X              |

| LIS | ST OF TABLES                                       | xii            |

| AC  | KNOWLEDGEMENTS                                     | xvii           |

| СН  | APTERS                                             |                |

| 1.  | INTRODUCTION                                       | 1              |

|     | 1.1 Related Work                                   |                |

|     | 1.3 Contributions of this Work                     | 6              |

| •   | 1.4 Overview of this Dissertation                  |                |

| 2.  | BACKGROUND                                         | 10             |

|     | 2.1 Asynchronous Circuit Basics                    | 10<br>10<br>11 |

|     | 2.1.2 2-Phase and 4-Phase Signaling Protocol       | 12<br>12       |

|     | 2.1.2.2 4-Phase Protocol                           | 12             |

|     | 2.1.3.1 Handshake Channel Type                     | 13<br>14       |

|     | 2.2 Relative Timing                                | 15             |

|     | 2.3 Synchronous CAD Tool Flow                      | 16             |

| 3.  | ASYNCHRONOUS CAD TOOLS AND FLOWS                   | 18             |

|     | 3.1 Key Contributions                              | 19             |

|     | 3.2 Background                                     | 19             |

|     | 3.3 Clock Compatible Multifrequency IC Flow        |                |

|     | 3.3.1.1 Element Design                             |                |

|     | 3.3.1.2 Automatic Sequential RT Characterization   | 23             |

|     | 3.3.2 Clocked Design Flow Using RT Sequentials     | 27             |

|     | 3.3.3 Mapping RT Constraints Onto Design Instances | 27             |

|     | 3.3.4 Timing Closure                               | 28<br>30       |

|     | 3.3.3 Final KI Vandation                           | 3(<br>20       |

|    | 3.5 Summary                                                   | 32 |

|----|---------------------------------------------------------------|----|

| 4. | AUTOMATIC RESET ADDITION BASED ON POWER/PERFORMANCE           |    |

|    | OPTIMIZATION                                                  |    |

|    | 4.1 Key Contributions                                         |    |

|    | 4.2 Background                                                |    |

|    | 4.3 Algorithm                                                 |    |

|    | 4.3.1 Generate Cycles to Reset when PI's are Defined          |    |

|    | 4.3.2 Generate Paths to Reset when PIs are Undefined          |    |

|    | 4.3.3 Gate Modifications for Reset Insertion                  | 41 |

|    | 4.3.4 Optimization Heuristics for Selecting the Best Solution | 42 |

|    | 4.3.4.1 Delta Logical Effort                                  |    |

|    | 4.3.4.2 Relative Load on a Gate                               | 45 |

|    | 4.3.4.3 Performance or Power Optimization                     | 45 |

|    | 4.4 Examples                                                  | 46 |

|    | 4.4.1 Example 1                                               | 46 |

|    | 4.4.2 Example 2                                               | 47 |

|    | 4.5 Results                                                   | 50 |

|    | 4.6 Summary                                                   | 52 |

| _  |                                                               |    |

| 5. | TIMING PATH DRIVEN CYCLE CUTTING FOR SEQUENTIAL               |    |

|    | CIRCUITS                                                      | 54 |

|    | 5.1 Key Contributions                                         | 55 |

|    | 5.2 Related Work                                              | 56 |

|    | 5.3 Background                                                |    |

|    | 5.3.1 Timing Constraint Paths                                 | 57 |

|    | 5.3.2 Classification of Cycles                                |    |

|    | 5.3.3 Benefits of Correct Cycle Cutting                       | 60 |

|    | 5.3.4 Generality of Approach                                  | 61 |

|    | 5.4 Rules for Timing Path Driven Cycle Cutting                |    |

|    | 5.4.1 Gate Sizing                                             | 64 |

|    | 5.4.2 Architectural Cycles are Cut                            | 64 |

|    | 5.4.3 Timing Arc Fidelity                                     | 65 |

|    | 5.4.4 Specifying the Correct Causal Path                      | 65 |

|    | 5.4.5 Defining Causal Paths that are Not GCPs                 | 67 |

|    | 5.5 Algorithm                                                 | 68 |

|    | 5.5.1 Adjacency List Creation                                 | 69 |

|    | 5.5.2 Finding All the Cycles Present in the Circuit           | 69 |

|    | 5.5.3 Timing Constraint Paths with Noncausal Path Removal     | 71 |

|    | 5.5.4 Generating Cycle Cuts                                   | 72 |

|    | 5.5.5 Uncut Cycles                                            | 75 |

|    | 5.6 Results                                                   | 75 |

|    | 5.6.1 Four-cycle Handshake Controllers                        | 75 |

|    | 5.6.2 Benchmark Circuits                                      | 81 |

|    | 5.7 Summary                                                   | 82 |

| <b>6.</b> | CHARACTERIZATION OF FAMILY OF 4-PHASE LATE PROTOCOLS.                         | 86       |

|-----------|-------------------------------------------------------------------------------|----------|

|           | 6.1 Key Contributions                                                         | 87       |

|           | 6.2 Background                                                                | 87       |

|           | 6.3 Late Data Validity Protocols                                              | 89       |

|           | 6.3.1 Concurrency Reduction on MAX with Cuts                                  | 90       |

|           | 6.3.1.1 Concurrency Reduction from Right Cuts $\mathscr{R}$                   | 90       |

|           | 6.3.1.2 Concurrency Reduction from Left Cuts $\mathscr{L}$                    | 91       |

|           | 6.3.1.3 Untimed Protocol Family                                               | 92       |

|           | 6.3.1.4 $\mathscr{L}$ and $\mathscr{R}$ Cut Lattices                          | 93       |

|           | 6.4 Results                                                                   | 94       |

|           | 6.5 Hand-optimized Handshake Controller                                       | 97<br>99 |

|           | 6.6 Summary                                                                   | 99       |

| 7.        | CASE STUDIES                                                                  | 106      |

|           | 7.1 Key Contributions                                                         | 106      |

|           | 7.2 Toy Example                                                               |          |

|           | 7.2.1 Constraint Specification                                                |          |

|           | 7.2.2 Delay Controllability in Pipelines with Variable Frequency of Operation |          |

|           | 7.2.3 Wireload Models and its Impact on RT Methodology                        |          |

|           | 7.2.4 Automatic Scan Insertion using Tetramax                                 |          |

|           | 7.3 FIFO Design Automation for Template Characterization                      |          |

|           | 7.3.1 Linear FIFO                                                             |          |

|           | 7.3.2 Parallel FIFO                                                           |          |

|           | 7.3.4 Square FIFO                                                             |          |

|           | 7.4 OCP-IP Case Study for Synchronous and Asynchronous Domain Interfacing     |          |

|           | 7.4.1 Open Core Protocol (OCP) Background                                     |          |

|           | 7.4.2 Designs                                                                 |          |

|           | 7.4.3 Asynchronous OCP Implementation                                         |          |

|           | 7.4.4 Domain Interface Designs                                                |          |

|           | 7.4.4.1 The <i>sync-sync</i> Domain Interface FIFO                            |          |

|           | 7.4.4.2 The <i>async-sync</i> Domain Interface FIFO                           | 138      |

|           | 7.4.4.3 The <i>sync-async</i> Domain Interface FIFO                           | 140      |

|           | 7.4.5 Results                                                                 |          |

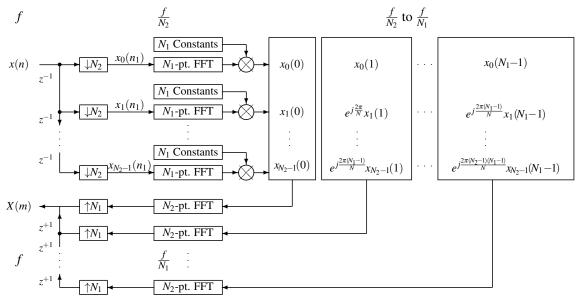

|           | 7.5 Asynchronous 64-point FFT Example                                         |          |

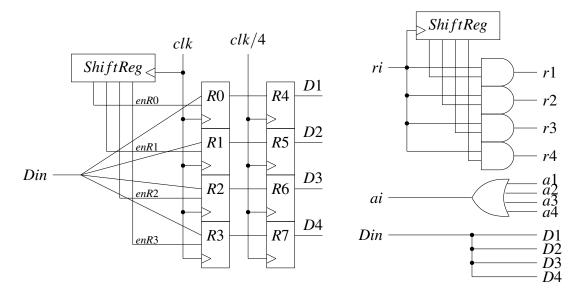

|           | 7.5.1 FFT Architecture                                                        |          |

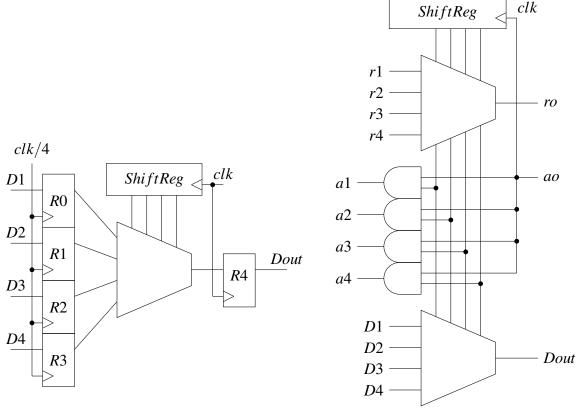

|           | 7.5.2 FFT Design                                                              |          |

|           | 7.5.2.1 Asynchronous Design                                                   |          |

|           | 7.5.2.2 Synchronous Design                                                    |          |

|           | 7.5.3 Results                                                                 |          |

|           | 7.5.4 Timing Closure Approaches for Asynchronous Circuits                     |          |

|           | 7.6 Summary                                                                   |          |

| <b>8.</b> | CONCLUSIONS AND FUTURE WORK                                                   | 162      |

|           | 8.1 Conclusions                                                               | 162      |

|           | 8.2 Future Work                                                               | 164      |

## **APPENDICES**

| Α. | RESULTS FOR CHAPTER 4 | 166 |

|----|-----------------------|-----|

| В. | RESULTS FOR CHAPTER 5 | 187 |

| RE | FERENCES              | 201 |

# LIST OF FIGURES

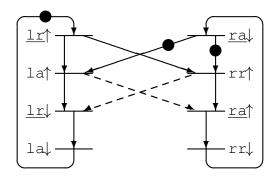

| 2.1  | 2-Phase protocol                                                                                                                                                                             | 13 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2  | 4-Phase protocol                                                                                                                                                                             | 13 |

| 2.3  | Timed (bundled data) handshake design. Delay sized by RT constraint $req_i \uparrow \mapsto L_{i+1}/d + s \prec L_{i+1}/clk \uparrow. \dots$                                                 | 14 |

| 2.4  | 4-phase protocol: data validity schemes [1]                                                                                                                                                  | 15 |

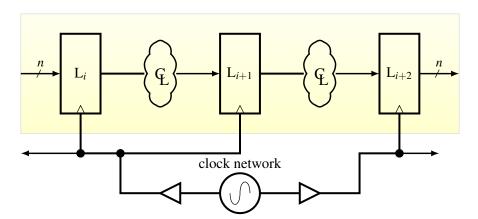

| 2.5  | Frequency based (clocked) design. Clock frequency and datapath delay of first pipeline stage is constrained by $L_i/clk \uparrow_i \mapsto L_{i+1}/d + s \prec L_{i+1}/clk \uparrow_{i+1}$ . | 16 |

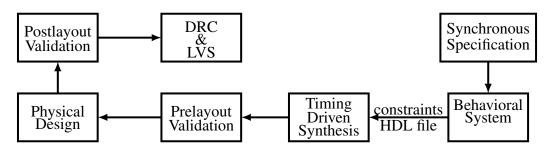

| 2.6  | Synchronous CAD tool flow                                                                                                                                                                    | 17 |

| 3.1  | CCS specification of pipeline controller                                                                                                                                                     | 20 |

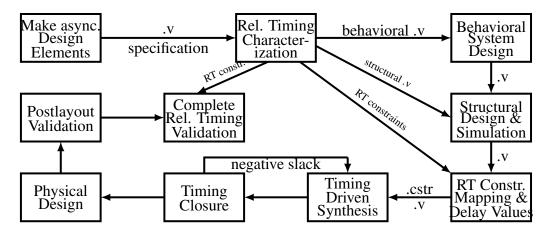

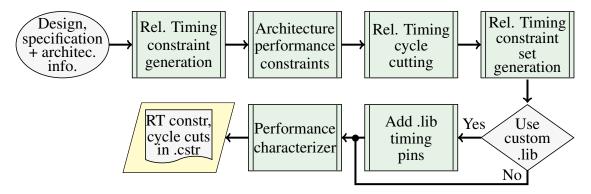

| 3.2  | Simplified relative timing multifrequency design flow                                                                                                                                        | 21 |

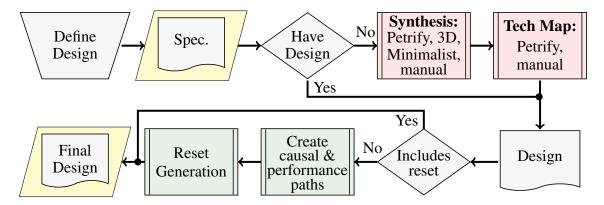

| 3.3  | Design element creation flow                                                                                                                                                                 | 23 |

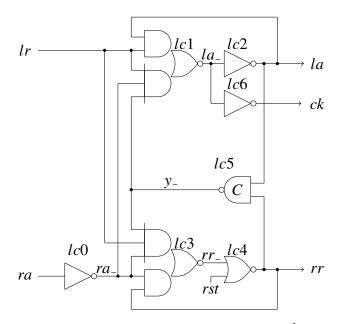

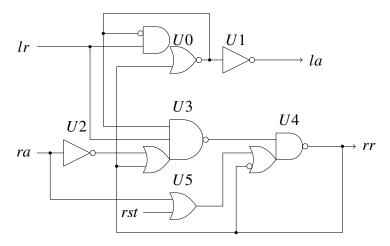

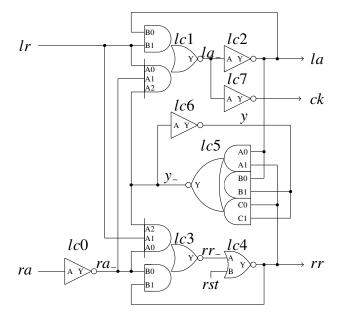

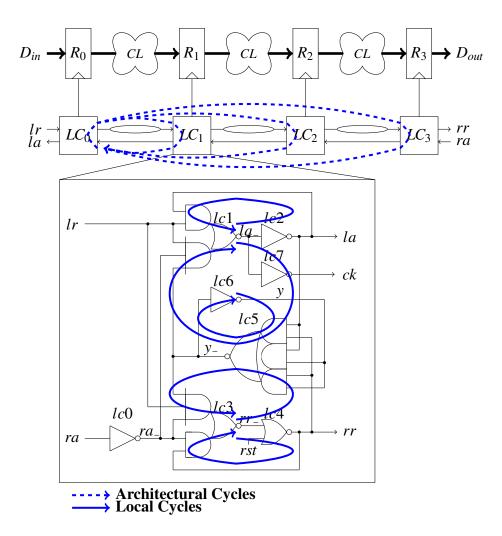

| 3.4  | LC circuit implementation                                                                                                                                                                    | 23 |

| 3.5  | Structural Verilog in 65nm Artisan library                                                                                                                                                   | 24 |

| 3.6  | Automated sequential RT characterization flow                                                                                                                                                | 24 |

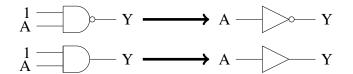

| 3.7  | The semimodular specification of a 2-input NAND gate. Inputs that would disable an output are not permitted                                                                                  | 25 |

| 3.8  | RT constraints for pipeline controller                                                                                                                                                       | 25 |

| 3.9  | Verilog code snippet for simple adder pipeline stage                                                                                                                                         | 28 |

| 3.10 | An SDC example for simple adder pipeline stage                                                                                                                                               | 29 |

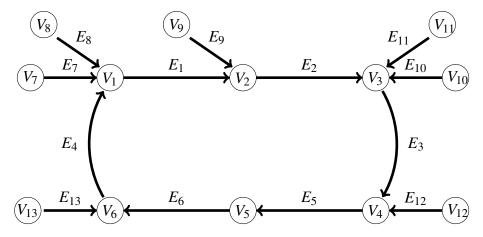

| 4.1  | A cyclic directed graph example                                                                                                                                                              | 38 |

| 4.2  | Gate conversion example for Lemma 1                                                                                                                                                          | 39 |

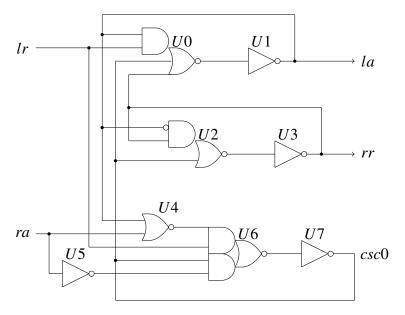

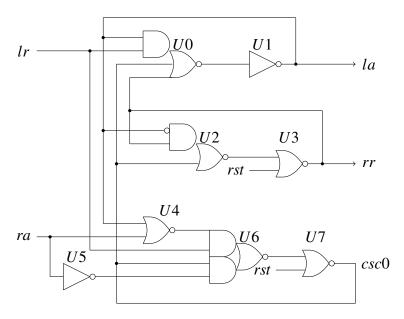

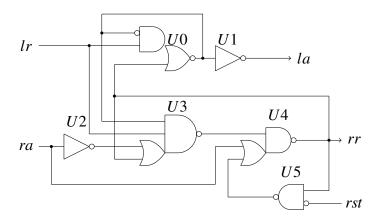

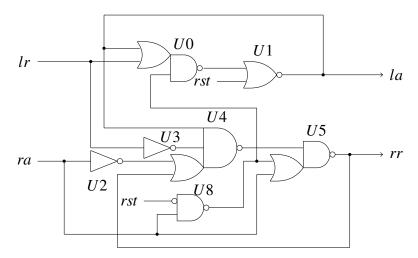

| 4.3  | Example 1: Circuit implementation before reset                                                                                                                                               | 43 |

| 4.4  | Example 1: Circuit implementation with power optimization                                                                                                                                    | 43 |

| 4.5  | Example 1: Circuit implementation with performance optimization                                                                                                                              | 44 |

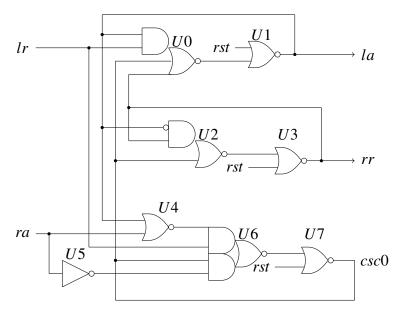

| 4.6  | Example 2: Circuit implementation before reset                                                                                                                                               | 44 |

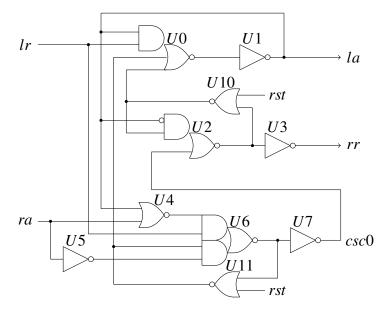

| 4.7  | Example 2: Circuit implementation with power/performance optimization                                                                                                                        | 44 |

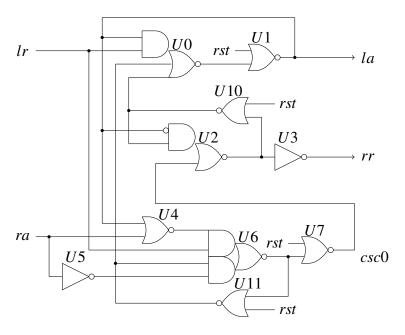

| 4.8  | Example 1: Power optimization with undefined inputs                                                                                                                                          | 48 |

| 4.9  | Example 1: Performance optimization with undefined inputs                                                                                                                                    | 48 |

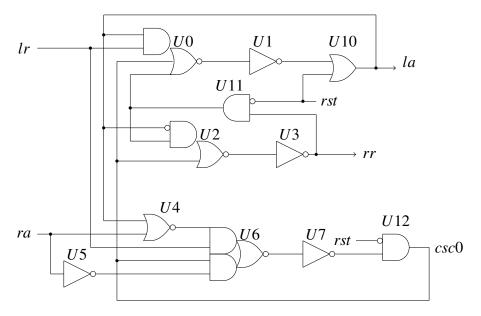

| 1.10 | Example 1: Circuit implementation using Petrify                                                                                                                                              | 49 |

| 4.11 | Example 2: Circuit implementation using Petrify                                                                                                                 | 49  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

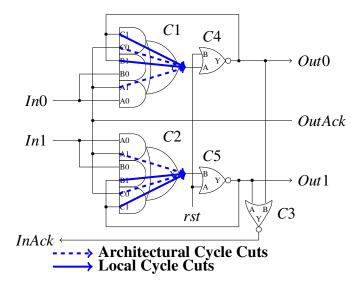

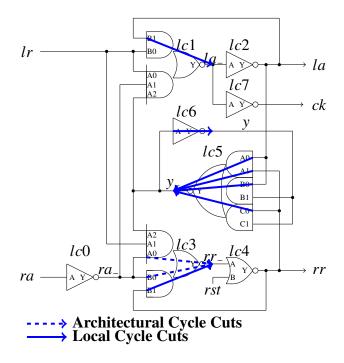

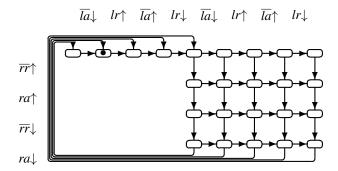

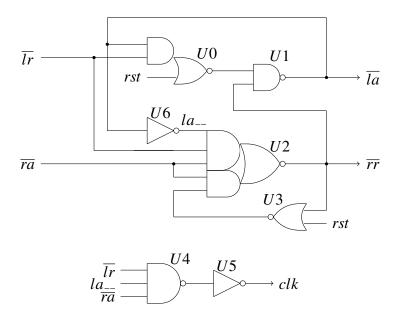

| 5.1  | LC circuit implementation                                                                                                                                       | 58  |

| 5.2  | Classification of cycles example                                                                                                                                | 59  |

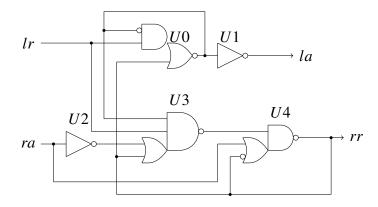

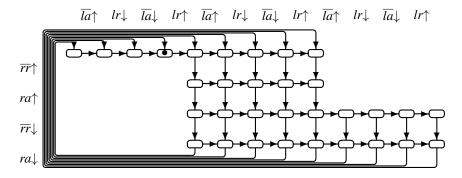

| 5.3  | WCHB circuit                                                                                                                                                    | 62  |

| 5.4  | WCHB circuit with cycle cuts                                                                                                                                    | 63  |

| 5.5  | Cycle cut constraints for WCHB circuit                                                                                                                          | 63  |

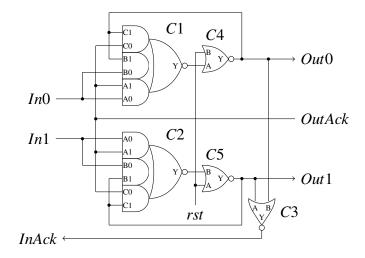

| 5.6  | L0000_R0044 circuit implementation                                                                                                                              | 68  |

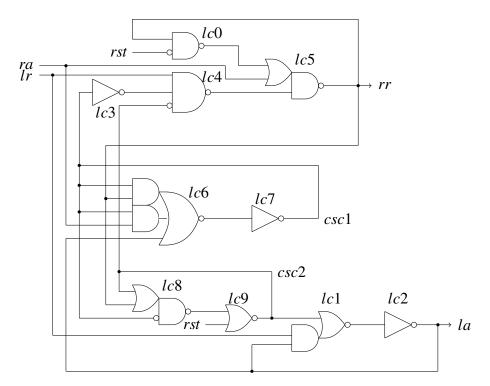

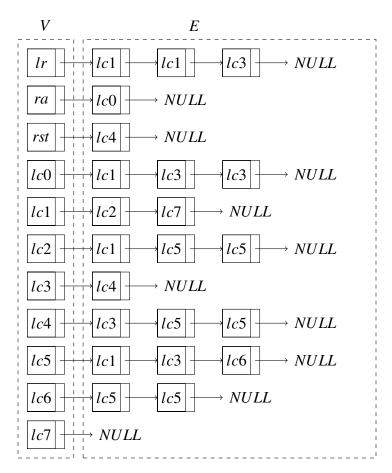

| 5.7  | Adjacency list for LC circuit of Fig 5.1                                                                                                                        | 70  |

| 5.8  | Covering table for LC circuit.                                                                                                                                  | 73  |

| 5.9  | Local cycle cut constraints for LC circuit of Fig 5.1                                                                                                           | 74  |

| 5.10 | LC circuit with cycle cuts                                                                                                                                      | 74  |

| 5.11 | Architectural cycle cut constraints for LC circuit of Fig. 5.1                                                                                                  | 76  |

| 6.1  | Minimized state graph of <i>max</i> , configured as a shape for early data validity protocols                                                                   | 89  |

| 6.2  | STG for the abstracted <i>max</i> protocol for early data validity protocols                                                                                    | 89  |

| 6.3  | Minimized state graph of <i>max</i> , configured as a shape for late data validity protocols                                                                    | 91  |

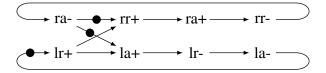

| 6.4  | STG for the abstracted <i>max</i> protocol for late data validity protocols                                                                                     | 91  |

| 6.5  | Right cut $\mathcal R$ denotation and range for late data validity protocols                                                                                    | 91  |

| 6.6  | The shape resulting from cutaway R2200                                                                                                                          | 91  |

| 6.7  | Left cut $\mathcal{L}$ denotation and range. The top row is duplicated at the bottom of the shape to more easily show the left cut ordering                     | 92  |

| 6.8  | The shape (above the duplicated line) resulting from cutaway L0011                                                                                              | 93  |

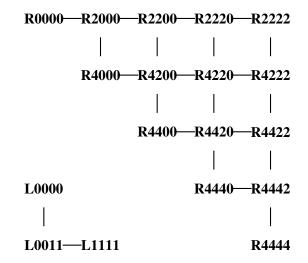

| 6.9  | The symmetric lattices of untimed DI/SI left and right cuts                                                                                                     | 95  |

| 6.10 | L0011 ° R4220 circuit implementation using Petrify                                                                                                              | 105 |

| 6.11 | Hand-optimized L0011 ° R4220 circuit implementation                                                                                                             | 105 |

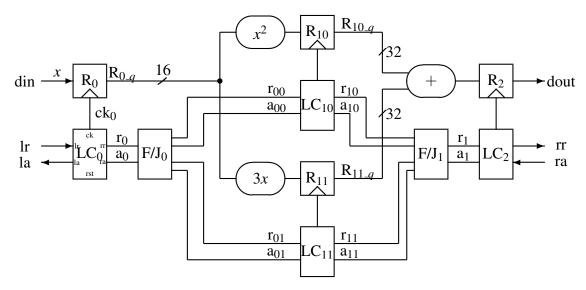

| 7.1  | Example design: a simple ASIC mathematical pipeline segment computing dout = $x^2 + 3x$                                                                         | 107 |

| 7.2  | The synthesized arithmetic Verilog for our toy example                                                                                                          | 110 |

| 7.3  | Petri net specification of linear control                                                                                                                       | 111 |

| 7.4  | Loop breaking constraints                                                                                                                                       | 112 |

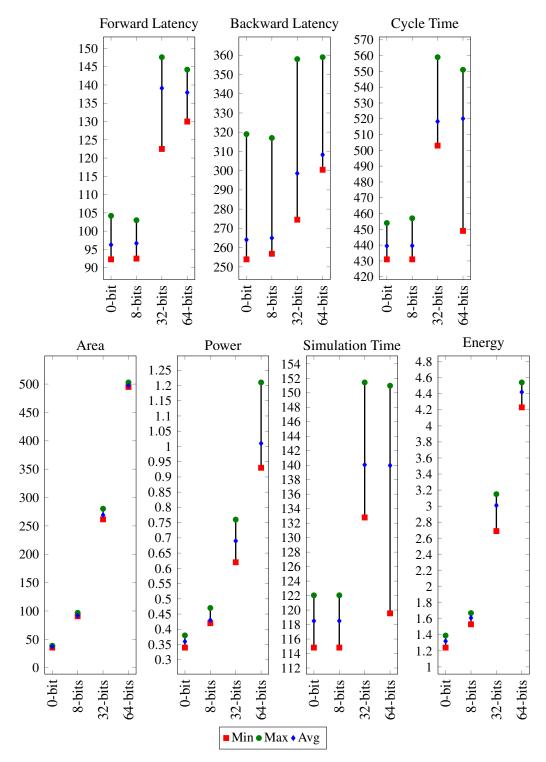

| 7.5  | Comparison of results for linear FIFO. All reported numbers are averages with respect to the buffering depth of FIFO except for cycle time and simulation time. | 122 |

|      |                                                                                                                                                                 |     |

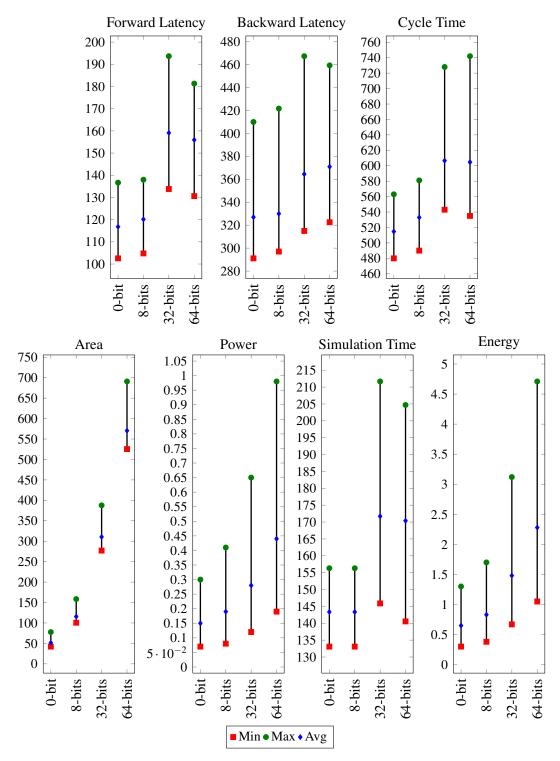

| 7.6  | Comparison of results for parallel FIFO. All reported numbers are averages with respect to the buffering depth of FIFO except for cycle time and simulation time. | 124 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

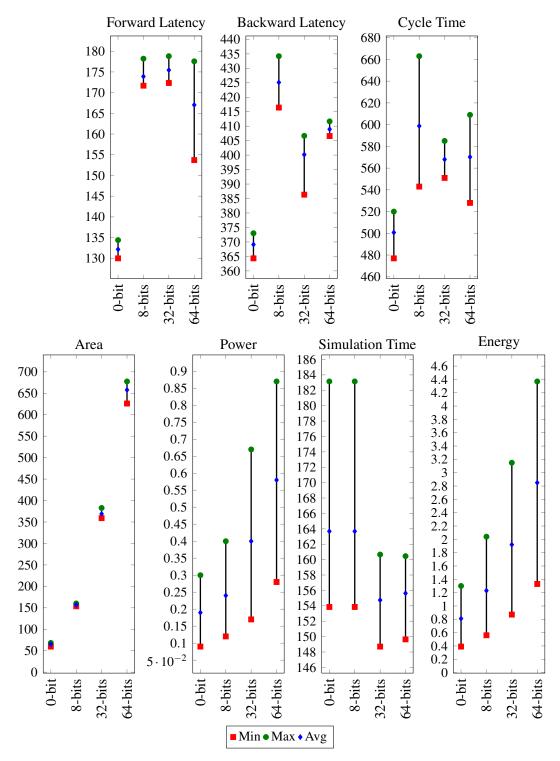

| 7.7  | Comparison of results for tree FIFO. All reported numbers are averages with respect to the buffering depth of FIFO except for cycle time and simulation time      | 126 |

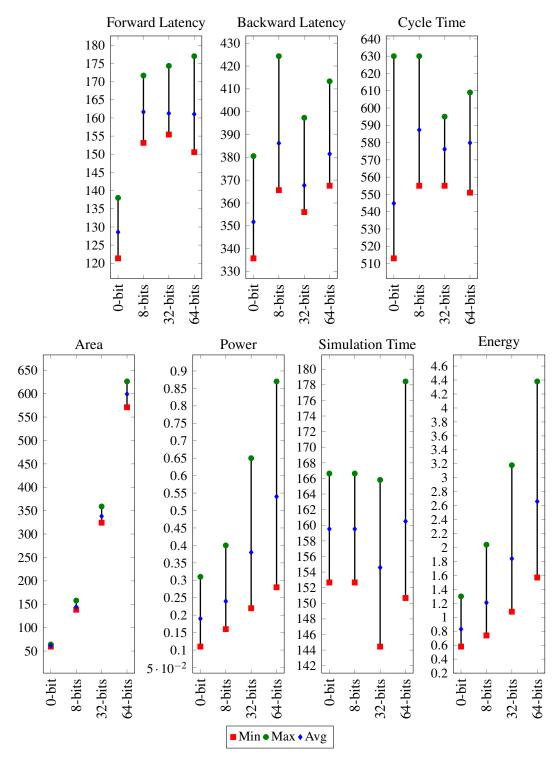

| 7.8  | Comparison of results for square FIFO. All reported numbers are averages with respect to the buffering depth of FIFO except for cycle time and simulation time.   | 127 |

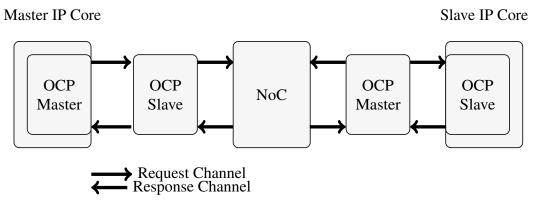

| 7.9  | OCP implementation block diagram with native OCP master and slave                                                                                                 | 130 |

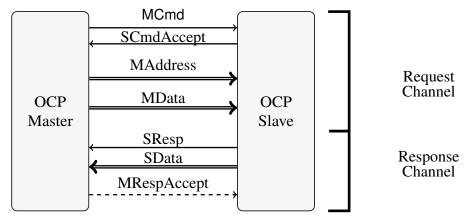

| 7.10 | Basic OCP master and slave interface                                                                                                                              | 130 |

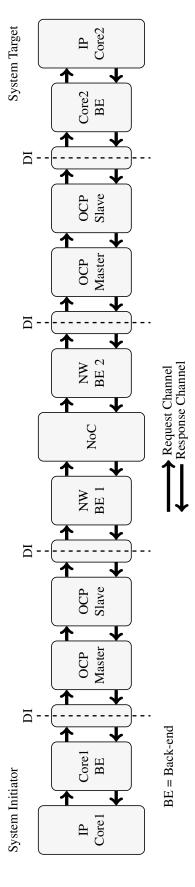

| 7.11 | OCP implementation block diagram with domain interface (DI) and back-end (BE) modules                                                                             | 133 |

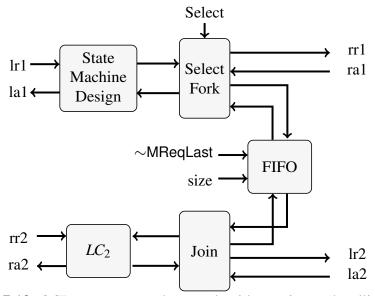

| 7.12 | State machine control network                                                                                                                                     | 135 |

| 7.13 | OCP master control network with steering and stalling block                                                                                                       | 135 |

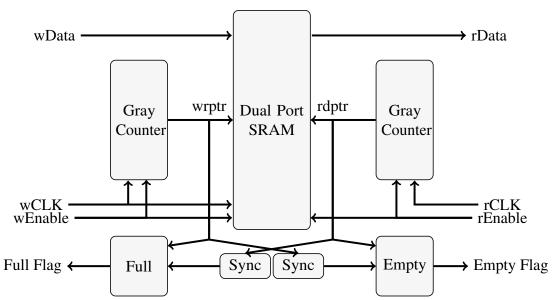

| 7.14 | sync-sync domain interface FIFO                                                                                                                                   | 138 |

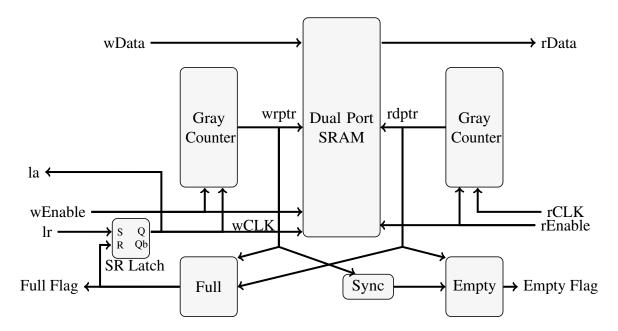

| 7.15 | async-sync domain interface FIFO                                                                                                                                  | 139 |

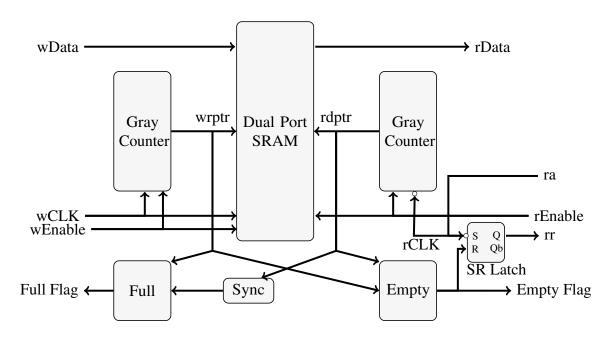

| 7.16 | sync-async domain interface FIFO                                                                                                                                  | 140 |

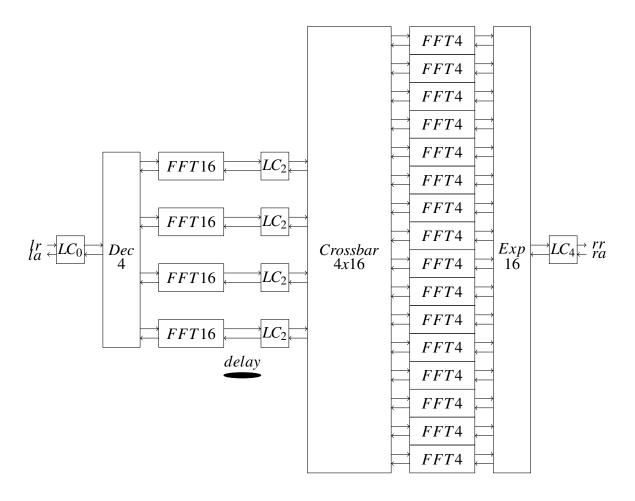

| 7.17 | Multirate FFT architecture                                                                                                                                        | 146 |

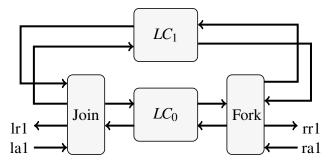

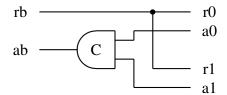

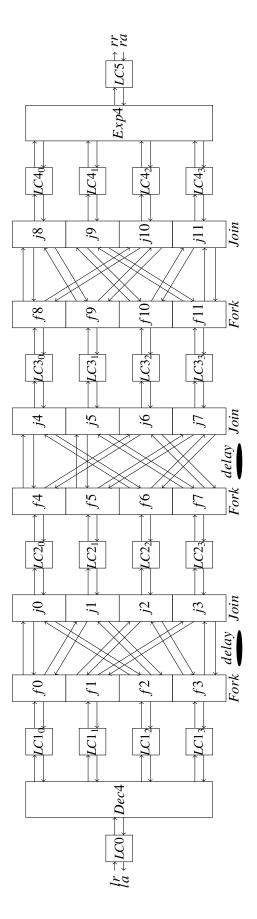

| 7.18 | Fork/Join template                                                                                                                                                | 148 |

| 7.19 | Synchronous decimator                                                                                                                                             | 148 |

| 7.20 | Asynchronous decimator                                                                                                                                            | 148 |

| 7.21 | Synchronous expander                                                                                                                                              | 149 |

| 7.22 | Asynchronous expander                                                                                                                                             | 149 |

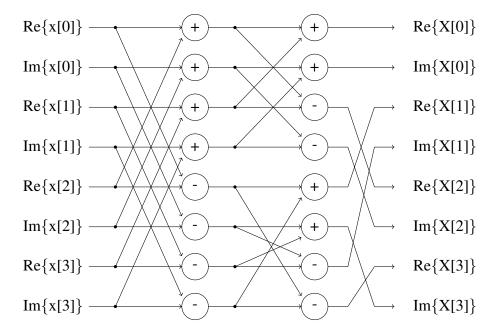

| 7.23 | Data flow graph of 4-point FFT calculation                                                                                                                        | 150 |

| 7.24 | 4-point FFT design                                                                                                                                                | 151 |

| 7.25 | Verilog code snippet for FFT_64                                                                                                                                   | 152 |

| 7.26 | 64-point FFT design                                                                                                                                               | 153 |

# LIST OF TABLES

| 4.1  | Results comparison for benchmark circuits                                                                                                                         | <b>5</b> 1 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 4.2  | Controller circuit comparison                                                                                                                                     | 52         |

| 5.1  | Comparison of performance metrics using timing path cycle cutting versus the algorithm in a commercial CAD tool                                                   | 62         |

| 5.2  | Comparison of performance metrics using timing path cycle cutting versus the algorithm in a commercial CAD tool for WCHB example                                  | 64         |

| 5.3  | Total number of cycles found                                                                                                                                      | 77         |

| 5.4  | Cycles left uncut for V1 algorithm                                                                                                                                | 78         |

| 5.5  | Unsized gates for V1 algorithm                                                                                                                                    | 79         |

| 5.6  | e	au ratio of cycle cutting done by the commercial CAD tool and V1 algorithm.                                                                                     | 80         |

| 5.7  | Comparison of performance metrics using the algorithm in a commercial CAD tool versus timing path based cycle cutting (V1) (Commercial CAD tool number/V1 number) | 81         |

| 5.8  | Benchmark circuits design comparison (*Number of gates with all the input to output paths cut)                                                                    | 83         |

| 5.9  | Results comparison for benchmark circuits                                                                                                                         | 84         |

| 6.1  | Number of gates before adding reset                                                                                                                               | 96         |

| 6.2  | Total number of cycles found                                                                                                                                      | 96         |

| 6.3  | Forward latency (ps/pipestage) (Power optimization)                                                                                                               | 97         |

| 6.4  | Forward latency ( <i>ps/pipestage</i> ) (Performance optimization)                                                                                                | 97         |

| 6.5  | Backward latency (ps/pipestage) (Power optimization)                                                                                                              | 98         |

| 6.6  | Backward latency (ps/pipestage) (Performance optimization)                                                                                                        | 98         |

| 6.7  | Cycle time (ps) (Power optimization)                                                                                                                              | 99         |

| 6.8  | Cycle time (ps) (Performance optimization)                                                                                                                        | 99         |

| 6.9  | Buffering depth for circuits                                                                                                                                      | 100        |

| 6.10 | Routed core area $(um^2)$ (Power optimization)                                                                                                                    | 101        |

| 6.11 | Routed core area $(um^2)$ (Performance optimization)                                                                                                              | 101        |

| 6.12 | Power consumed (mW) (Power optimization)                                                                                                                          | 102        |

| 6.13 | Power consumed (mW) (Performance optimization)                                                                                                                    | 102        |

| 6.14 | Simulation time ( <i>ns</i> ) (Power optimization)                                                                                                                                                                                                            |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.15 | Simulation time (ns) (Performance optimization)                                                                                                                                                                                                               |

| 6.16 | Energy consumed $(pJ/token)$ (Power optimization)                                                                                                                                                                                                             |

| 6.17 | Energy consumed $(pJ/token)$ (Performance optimization)                                                                                                                                                                                                       |

| 7.1  | Example comparing flop and latch based design with identical pipeline frequency. The ICS column uses an incomplete constraint set. Energy reported in pJ per token, clock period in nsec                                                                      |

| 7.2  | Version with variable pipeline frequencies                                                                                                                                                                                                                    |

| 7.3  | Latch based time borrowing versions with and without variable pipeline frequencies using incomplete and complete timing path constraints                                                                                                                      |

| 7.4  | Data check timing report summary on some RT constraints. Listed slacks are all worst case                                                                                                                                                                     |

| 7.5  | Timing report summary for constraints between pipeline stages. The latches in datapath borrow time from the next stages with LSup (library setup time), MxTB (maximum time borrowing) and TB (real time borrowing) listed. All the numbers are in nanoseconds |

| 7.6  | Results for toy example using different wireload models                                                                                                                                                                                                       |

|      | Scan insertion coverage and stuck at fault summary                                                                                                                                                                                                            |

|      | Energy, performance and area comparison for design with no domain crossing.142                                                                                                                                                                                |

| 7.9  | Energy, performance and area comparison for design with domain crossing 143                                                                                                                                                                                   |

| 7.10 | The 16-point FFT comparison result (* constant field scaled to 65 nm technology)                                                                                                                                                                              |

| 7.11 | The 64-point FFT comparison result (* constant field scaled to 65 nm technology, + nominal process voltage)                                                                                                                                                   |

| 7.12 | Design comparisons (+ The nominal process voltage)                                                                                                                                                                                                            |

| 7.13 | Comparison of Timing Closure Approaches on 64-point FFT 160                                                                                                                                                                                                   |

| A.1  | Forward latency $(ps/pipestage)$ for circuits with $lr\rightarrow la$ and $lr\rightarrow rr$ constraints (Performance optimization)                                                                                                                           |

| A.2  | Backward latency $(ps/pipestage)$ for circuits with $lr\rightarrow la$ and $lr\rightarrow rr$ constraints (Performance optimization)                                                                                                                          |

| A.3  | Cycle time $(ps)$ for circuits with $lr \rightarrow la$ and $lr \rightarrow rr$ constraints (Performance optimization)                                                                                                                                        |

| A.4  | Routed core area $(um^2)$ for circuits with $lr \rightarrow la$ and $lr \rightarrow rr$ constraints (Performance optimization)                                                                                                                                |

| A.5  | Power consumed ( $mW$ ) for circuits with $lr \rightarrow la$ and $lr \rightarrow rr$ constraints (Performance optimization)                                                                                                                                  |

| A.6  | Simulation time (Post-APR with SDF back-annotation) ( $ns$ ) for circuits with $lr \rightarrow la$ and $lr \rightarrow rr$ constraints (Performance optimization)                                                                                             |

| A.7  | Energy consumed $(pJ/token)$ for circuits with $lr \rightarrow la$ and $lr \rightarrow rr$ constraints (Performance optimization)                     |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| A.8  | Forward latency $(ps/pipestage)$ for circuits with $lr\rightarrow la$ and $lr\rightarrow rr$ constraints (Power optimization)                         |

| A.9  | Backward latency $(ps/pipestage)$ for circuits with $lr\rightarrow la$ and $lr\rightarrow rr$ constraints (Power optimization)                        |

| A.10 | Cycle time $(ps)$ for circuits with $lr \rightarrow la$ and $lr \rightarrow rr$ constraints (Power optimization)                                      |

| A.11 | Routed core area $(um^2)$ for circuits with $lr \rightarrow la$ and $lr \rightarrow rr$ constraints (Power optimization)                              |

| A.12 | Power consumed $(mW)$ for circuits with $lr \rightarrow la$ and $lr \rightarrow rr$ constraints (Power optimization)                                  |

| A.13 | Simulation time (Post-APR with SDF back-annotation) (ns) for circuits with $lr\rightarrow la$ and $lr\rightarrow rr$ constraints (Power optimization) |

| A.14 | Energy consumed $(pJ/token)$ for circuits with $lr \rightarrow la$ and $lr \rightarrow rr$ constraints (Power optimization)                           |

| A.15 | Forward latency $(ps/pipestage)$ for circuits with $lr\rightarrow la$ and $lr\rightarrow rr$ constraints (Petrify)                                    |

| A.16 | Backward latency $(ps/pipestage)$ for circuits with $lr\rightarrow la$ and $lr\rightarrow rr$ constraints (Petrify)                                   |

| A.17 | Cycle time (ps) for circuits with $lr\rightarrow la$ and $lr\rightarrow rr$ constraints (Petrify) 182                                                 |

| A.18 | Routed core area ( $um^2$ ) for circuits with $lr \rightarrow la$ and $lr \rightarrow rr$ constraints (Petrify).183                                   |

| A.19 | Power consumed (mW) for circuits with $lr\rightarrow la$ and $lr\rightarrow rr$ constraints (Petrify).184                                             |

| A.20 | Simulation time (Post-APR with SDF back-annotation) (ns) for circuits with $lr\rightarrow la$ and $lr\rightarrow rr$ constraints (Petrify)            |

| A.21 | Energy consumed $(pJ/token)$ for circuits with $lr\rightarrow la$ and $lr\rightarrow rr$ constraints (Petrify)                                        |

| B.1  | Forward latency (ps) for circuits with cycle cuts generated by my algorithm. 187                                                                      |

| B.2  | Forward latency ( <i>ps</i> ) for circuits with cycle cuts generated by commercial CAD tool                                                           |

| B.3  | Backward latency (ps) for circuits with cycle cuts generated by my algorithm. 189                                                                     |

| B.4  | Backward latency (ps) for circuits with cycle cuts generated by commercial CAD tool                                                                   |

| B.5  | Cycle time (ps) for circuits with cycle cuts generated by my algorithm 191                                                                            |

| B.6  | Cycle time (ps)for circuits with cycle cuts generated by commercial CAD tool.192                                                                      |

| B.7  | Routed core area $(um^2)$ for circuits with cycle cuts generated by my algorithm. 193                                                                 |

| B.8  | Routed core area (um²) for circuits with cycle cuts generated by commercial CAD tool                                                                  |

| B.9  | Power consumed $(mW)$ for circuits with cycle cuts generated by my algorithm. 19                                       | 5  |

|------|------------------------------------------------------------------------------------------------------------------------|----|

| B.10 | Power consumed (mW) for circuits with cycle cuts generated by commercial CAD tool                                      | 96 |

| B.11 | Simulation time (Post-APR with SDF back-annotation) (ns) for circuits with cycle cuts generated by my algorithm        | )7 |

| B.12 | Simulation time (Post-APR with SDF back-annotation) (ns) for circuits with cycle cuts generated by commercial CAD tool | 8  |

| B.13 | Energy consumed $(pJ/token)$ for circuits with cycle cuts generated by my algorithm                                    | 9  |

| B.14 | Energy consumed $(pJ/token)$ for circuits with cycle cuts generated by commercial CAD tool                             | 00 |

#### **ACKNOWLEDGEMENTS**

I would like to thank Dr. Ken Stevens for his guidance, understanding, patience, and most importantly, his assistance through my graduate studies at the University of Utah. His mentorship, expertise and humor provided me with the motivation to pursue my doctoral research. His support and encouragement were crucial through this whole experience. I would like to thank Dr. Chris Myers, Dr. Erik Brunvand, Dr. Priyank Kalla, and Dr. Christos Sotiriou for their constructive reviews of my work and for their constant assistance through my graduate studies.

I wish to thank my friends in the research group: William Lee, Shomit Das, Raghu Prasad Gudla, Krishnaji Desai, Dan Gebhardt and Junbok You for having all those constructive discussions and presentations to learn from and teach each other. Their reviews and critical comments on my manuscripts and work helped improve the quality immensely.

I would like to thank the Electrical and Computer Engineering Department at the University of Utah, especially Lori Sather for guiding me through the administrative stuff at the University and always being there to help. The long stay in Salt Lake City would not have been fun without the presence and help of my friends. Special thanks to Sai and Hemang for always being there to motivate me. Last but not the least my parents, my brother, my sister-in-law and my nephews for sticking by me through all this time and making this whole journey a fun filled one.

#### **CHAPTER 1**

#### INTRODUCTION

Integrated circuits continue to grow in performance and transistor count, with current designs exceeding a few billion transistors. Distributing the clock to the entire chip in such designs poses significant design effort and energy. Power consumed by the chip increases from generation to generation because total chip area remains constant or grows. This results in power hungry clock drivers that require high slew rates in order to distribute a high frequency clock with limited skew. This has resulted in designs where nearly 40 percent of the total on chip power consumption is due to the clock generation and distribution network [2, 3]. Earlier, performance and area were the metrics around which VLSI designers would build and optimize their chips, but in the last decade power has arguably become the most important metric.

The presence of a large number of transistors has also resulted in different approaches to design which involve different *intellectual property* (IP) blocks characterized and optimized for a specific frequency of operation. These IP blocks being integrated together to create a chip with multiple clock frequency domains is called multisynchronous design. The overhead of clock domain crossing and also the increase in design complexity of the system are becoming a big issue in terms of power and also performance.

Asynchronous circuits are a potential solution to all these problems, as they switch only to do useful work. The frequency of operation of asynchronous circuits is dynamic and is dependent on the amount of logic in the pipeline as well as on the operating frequency of the pipelines adjacent to it. Since there is no global clock and all the communication is local, there is no need for power hungry low skew drivers. These circuits are based on handshake protocols, which enhance the modularity and composability of the designs and thus assist in supporting multiple frequency designs without the need for synchronization. By operating the asynchronous system at frequencies that best optimize the power and performance of

each individual asynchronous modules an overall better design is achieved. One of the better silicon examples of such an architecture is the Pentium Processor front end, which operates at three frequencies: 720MHz for instruction decode, 3.6GHz for instruction selection, and 900MHz for instruction steering and issue [4]. This design was fabricated in the same foundry as its commercial counterpart, and achieved an 17 fold improvement in  $e\tau^2$  (energy delay squared product).

If the timing models employed in the clocked design style can be leveraged by general multifrequency design, the same tools, languages, and flows can be used with all methods of timing for design and architecture optimization. Relative timing (RT) does just that; it bridges the gap between the incompatible timing used by unclocked design styles by expressing the timing in a form used by commercial clocked *electronic design automation* (EDA) tools. Once timing compatibility is achieved, common design languages, standard cell libraries, and tool flows become common to all design styles. This compatibility enhances productivity, reduces the cost of adopting multifrequency design methodologies and results in power and performance advantages. A flow based on RT to generate multifrequency designs using commercial clocked EDA tools is described in this dissertation.

#### 1.1 Related Work

The convergence of asynchronous design approaches and the synchronous (clocked) computer aided design (CAD) tools and flows has been an actively researched topic. Based on different timing models used for the asynchronous design, different approaches are proposed to use the synchronous CAD tools and flows either partially or fully.

Flows related to approaches that use *delay insensitive* (DI) encoding use only the clocked synthesis CAD tool like *Synopsys Design Compiler* (DC) [5]. The synthesized design output is then mapped to specific DI gate implementations, which preserve the hazard properties of the design. Since timing is inherent in the DI systems, there is no requirement to specify timing constraints for functional correctness. The *NULL Convention Logic* (NCL) designs by Theseus Logic ([6]), the Proteus flow by University of Southern California and Fulcrum Microsystems ([7]) and the phased logic ([8]) approach to design circuit using the *level encoded two-phase dual rail* (LEDR) encoding follow this partial use of synchronous CAD tools and flows.

Commercial companies like Silistix working on DI design also have attempted to address this problem for *network-on-chip* (NoC) designs with their toolflow, which requires a precharacterized technology library [9]. The library contains adapters for their IP interface protocols and hard macroblocks for the CHAIN interconnect ([10]), which is used to connect the system blocks. The toolflow is named CHAINarchitect and it converts the network specified in a custom language called the *connect specification language* (CSL) into an on-chip network implementation. The benefits of this toolflow are its completeness in terms of all the general CAD flow steps like place and route, testing and *static timing analysis* (STA). This flow applies only to NoC designs developed using the technology library precharacterized by Silistix. Hence, it is not a general design flow. Also, the synchronous CAD tool optimizations are not applied because of the use of precharacterized hard macroblocks.

Desynchronization approach is the most complete existing method for generating an asynchronous bundled data design using the synchronous CAD flows [11, 12, 13, 14, 15]. It also uses standard library cells and hardware description languages (HDLs) to specify the circuit. This approach is built on the marked graph theory and hence proves the liveness, safeness and flow equivalence properties of the circuits. It accomplishes a direct mapping of the synchronous design into an asynchronous equivalent by removing the clock network and replacing it with an asynchronous handshake network. Postsilicon numbers for the ASPIDA DLX processor and a DES core were published for comparison of the asynchronous design with its synchronous counterpart [11, 12, 13, 14, 15]. Desynchronization provides significant benefits in *electromagnetic interference* (EMI) improvements and shorter design cycles. However, design results show little or no power improvement over the initial clocked design. The asynchronous design operates at average case speed as compared to worst case speed for the synchronous design, thus resulting in performance benefits for the fabricated desynchronized DLX processor. The base of the timing constraint specification for this approach is first to divide each flip-flop into a pair of latches which are individually controlled by a handshake controller. Then, a virtual clock is created to enable each latch for timing. This approach restricts the design to the clock paradigm, thus preventing the application of asynchronous architectural and design optimizations, which are important to

gain the benefits similar to the Pentium front-end example. The benefit of this approach is that the representation is completely like the clocked definition.

The application of synchronous synthesis tools for high-level timed asynchronous bundled-data design has also been investigated by using a channel-level VHDL code [16]. The circuit implementation was shown on a *field programmable gate array* (FPGA). The asynchronous control circuit for this implementation is derived using the ATACS tool [17], while the FPGA synthesis tool synthesizes the datapath. The benefit of this approach is the use of an HDL language to generate the asynchronous circuit and the concept of utilizing synchronous CAD tools to synthesize the combinational logic in the datapath. The timing and sizing algorithms of the synchronous CAD tools are not used to optimize the asynchronous design, hence delay elements are created by manually adding buffers based on the delay requirement.

Another approach that addresses generation of asynchronous bundled data as well as *quasi delay insensitive* (QDI) Micropipeline designs is the Weaver flow [18]. It modifies the library to make it compatible with DC, thus enabling synthesis of asynchronous circuits. The application of this approach is presented for deterministic as well as data dependent token propagation which enables its application to a large set of asynchronous circuits. The major drawback of this approach, however, is that it requires modifying the standard cell libraries to make it compatible with the flow. Hence, knowledge of library characterization and modification is required to derive the benefits.

A detailed study of the limitations of the synchronous CAD tools and flows with respect to applying them on an on-chip network is presented in [19]. These limitations are as follows:

- There is no mechanism to ensure that delays are matched on different paths in a circuit, thus making the use of bundled-data infeasible for large networks, since each path would require manual consideration. Due to this inability to specify relative delay constraints, there is no automated hazard (glitch) avoidance available.

- The CAD tools do not tolerate combinational feedback paths, hence they are unable to infer sequential circuits built from combinational gates. Because of this restriction, circuits that create sequential elements that are not explicitly defined in the standard cell library cannot be optimized using automatic gate sizing or repeater insertion.

- For automatic circuit optimization, each path must be referenced to a common global clock. If this reference cannot be made, the tool simply ignores the path and the delay on that path is not optimized.

- The circuit optimization tools are only designed to insert repeaters to manage wire delays. They do not have the ability to insert sequential elements.

The presence of these limitations resulted in the selection of DI circuit over bundled data implementation. Hence, if these problems can be addressed then bundled data designs could be developed using synchronous CAD tools.

Timing is the key to generation of complex asynchronous systems, which show improvements in terms of power, performance and even area. But to leverage timing in the CAD flows, there needs to be a representation that describes it in both the synchronous and asynchronous domains similarly. Relative timing is one such unifying approach. It defines the timing as a sequence of competing events that have a specific order of arrival at a point in the circuit [20]. Hence the problem of timing is simplified into a problem of ordering.

#### 1.2 Motivation

Asynchronous circuits have a lot of benefits like modularity, composability, low power, and robustness against *process*, *voltage and temperature* (PVT) variations. For a long time, they have been proposed as the solution for most of the design challenges faced by synchronous designs, but this promise has not materialized commercially. Design examples like the Pentium front-end, the low power asynchronous ARM, the desynchronized DLX and many other examples have shown these benefits exist and can be derived [4, 21, 22, 23, 11, 12, 13, 14, 15]. The approaches to achieve these benefits are specific to a certain asynchronous design style which uses noncommercial research tools and custom specification languages. The flexibility in terms of design approaches and the vast choices of asynchronous design styles prevent us from achieving these benefits due to the lack of a unifying methodology.

The asynchronous protocol-based interfaces between design elements are one of the most efficient multifrequency designs, since this reactive design style requires no overhead to synchronize between frequency domains. Thus, one might expect the design of unclocked multifrequency architectures to exhibit reasonable design productivity due to their modularity; however, that has not been shown to be the case when compared with similar clocked

design flows. The primary reason for this lack of productivity is related to the difference in the timing models between clocked and unclocked architectures and the clocked commercial CAD that has been developed to support design productivity.

The primary goal of this work is to present a multifrequency methodology that develops pure asynchronous designs or both synchronous and asynchronous designs together. The existing mature CAD tools and flows available for synchronous designs can be leveraged to generate asynchronous circuits, thus enhancing the acceptance of asynchronous circuits. This work also assists in an easy transition from the traditional synchronous designs with discrete-time domain into asynchronous design domain with continuous-time and reactive systems.

The new multifrequency methodology must facilitate in deriving the above mentioned benefits for any design style. It must give the designers the freedom necessary to choose any design style and easily develop a working system with either asynchronous or mixed asynchronous and synchronous timing domains.

#### 1.3 Contributions of this Work

The goal of this research is to develop a multifrequency flow which addresses one of the major bottlenecks related to development and acceptance of asynchronous designs. Major contributions of this work are as follows:

- A methodology is presented to enable design of asynchronous circuits using synchronous CAD tools and flows. It facilitates an easy transition for any circuit designer/company to adopt asynchronous methodology.

- A flow for the characterization of asynchronous circuit templates has been defined, which enables their use with synchronous CAD tools and flows. This flow provides a systematic way of characterizing the asynchronous designs to be used with the overall methodology.

- Algorithms have been developed and presented for reset addition and cycle cutting

for automatic characterization of asynchronous design templates to be used with

synchronous CAD tools and flows. Understanding reset addition and a systematic

approach for its addition for power/performance optimization of the overall design is

necessary and is often a manual step in designing asynchronous circuits. The algorithm

presented in this dissertation addresses these issues. Similarly, the cycle cutting algorithm is an indispensable component of the methodology and flow presented here. It enables the use of timing and STA algorithms of synchronous CAD tools for sizing, validation and optimization of asynchronous circuits.

- Benchmark circuit templates have been developed and provided for rapid characterization of bundled-data asynchronous designs with respect to power, performance and area. Also, CAD has been developed to automate the generation of the characterization results. Comparison results for 4-phase protocols with early and late data validity, as well as asynchronous *first in first out* (FIFO) structures, with respect to energy, performance and area, are presented by using the tool flow presented in this dissertation. These results assist in quick selection of asynchronous templates based on the design requirements.

- The application of the tool flow and methodology on 16-point and 64-point *fast Fourier transform* (FFT) circuit are presented. Also, synchronous, asynchronous, *globally asynchronous locally synchronous* (GALS) and *locally asynchronous globally synchronous* (LAGS) implementations of the *open core protocol* (OCP) are implemented and compared. These case studies show that this methodology can be applied to large circuits as well as to circuits with mixed timing schemes i.e., synchronous and asynchronous.

- This dissertation presents approaches for timing closure for designing better asynchronous designs. The increase in the number of constraints result in an increase in the effort to achieve no negative slack for all the paths in the circuit. The timing closure approaches address a key manual step for rapid development of large asynchronous designs. Its applicability is shown on the 64-point FFT example. Wireload models are explored to understand their effects on timing and application of optimizations on asynchronous bundled-data circuits. Also, automatic scan insertion is applied using Tetramax to explore datapath testability and application of ATPG on bundled-data circuits.

#### 1.4 Overview of this Dissertation

This dissertation describes a methodology to generate asynchronous circuits as well as circuits with both synchronous and asynchronous blocks using synchronous CAD tools and flows. The methodology consists of two parts: the first part develops the asynchronous circuit templates and characterizes them for timing and cycle cut constraints. These circuit templates and their constraints are then used in the second part with the synchronous CAD flows to apply timing driven optimization and sizing on the asynchronous design and synthesize the combinational logic for the datapath. The application of the methodology is described to design asynchronous circuit templates; additionally, some case studies to show the applicability of the methodology to derive asynchronous and mixed timed circuits are detailed.

Chapter 2 describes the concept of asynchronous circuits, RT, and synchronous CAD tool flow. Chapter 3 presents the approach and methodology of designing asynchronous circuits using synchronous CAD tools and flows. The generation of constraints and their applicability to allow timing driven sizing and optimizations on asynchronous designs are also described. The reset algorithm, which assists in automatic addition of the reset signal in an asynchronous circuit, is explained in Chapter 4. Additionally, the relationship between cycles and the addition of a reset signal as well as power or performance optimization is detailed. Use of STA algorithms and performing timing driven optimization on asynchronous designs requires the asynchronous circuit to be specified as a *directed acyclic graph* (DAG) to the synchronous CAD tools. Chapter 5 gives an algorithm to generate the cycle cuts constraints while preserving timing paths, thus representing asynchronous circuits as a DAG. Automatic generation of the cycle cut constraints and the addition of the reset signal enables automation of asynchronous circuit design and its characterization. Chapter 6 explains the application of the tool flow to generate results for a family of 4-phase handshake protocol with data valid at the falling edge of the request signal which are also known as 4-phase handshake protocols with late data validity. Any methodology and tool flow needs to be explored by generating circuits of varying complexity to show the merits of the approach. Chapter 7 describes the applicability of the tool flow on pure asynchronous designs like a simple 3-stage pipeline computing  $x^2 + 3x$ , 4 types of asynchronous FIFO configurations of varying depths and datapath widths, a 16-point and a 64-point asynchronous FFT design,

and also synchronous, asynchronous OCP and OCP design with both clocked and unclocked domains. Chapter 8 concludes this work with proposals for future extensions.

#### **CHAPTER 2**

#### **BACKGROUND**

Asynchronous design is becoming increasingly attractive because of its potential benefits such as lower power, modularity, composability, ease of global timing issues, robustness against *process*, *voltage and temperature* (PVT) variations, and elasticity to name a few [24, 25]. This chapter gives an overview of asynchronous design approaches and an overview of the various terminologies used throughout this dissertation. A detailed understanding of asynchronous circuit design can be gained through following reference books: [26, 1, 27]. The basics of relative timing and an overview of the synchronous CAD (computer aided design) flows are also presented.

## 2.1 Asynchronous Circuit Basics

Asynchronous designs remove the discrete time assumption from the synchronous design approach and are continuous in terms of time. The presence of flexibility in terms of design style and approaches leads to a vast number of solutions to any given problem. They can be designed with or without any timing assumptions with respect to a specific delay model.

### 2.1.1 Asynchronous Circuit Classification

Different classes of asynchronous circuits can be defined based on the various assumptions they make on timing and environment. These assumptions are made with respect to how delays are modeled, i.e., as fixed, bounded and unbounded. The fixed delay model assumes the delay to have a fixed value. The bounded delay model considers delay to be bounded by a time interval. The unbounded delay model does not restrict the delay in any bounds and hence it can have any finite value. Based on these models, the following classification of circuits is defined.

• *Delay insensitive* (DI) - These circuits operate correctly irrespective of the delays on its gates and wires. An unbounded delay model is assumed while designing these

- circuits. These designs are the most conservative and are limited to a small set of circuits [28].

- *Quasi delay insensitive* (QDI) The unbounded delay model for DI circuits is relaxed for a specific case with wire forks considered to have exactly the same delay, also known as "isochronic forks." This assumption leads to wider applicability of these circuits [29].

- Speed independent (SI) These circuits assume arbitrary gate delays, but the wire

delays are considered to be zero or negligible. Hence these circuits also consider wire

forks to be isochronic.

- Timed circuits These circuits are designed using the bounded delay model with specific minimum and maximum delays for each gate. The presence of defined bounds leads to more timing constraints and hence greater effort in timing verification. These circuits are generally faster, smaller, and consume less power [30].

The addition of timing assumptions can lead to performance benefit as well as simpler and lower power circuits, but this benefit is gained at the cost of robustness against PVT variation [31]. This occurs due to the reduction in functional redundancy in the circuits with the increase in the timing assumptions. It is helpful to keep these timing assumptions local so that they can be easily controlled. One of the design styles which exploits this is the bundled data design. Thus, to derive the maximum benefit in terms of power, performance and area, approaches to handle timing need to be explored.

#### 2.1.2 2-Phase and 4-Phase Signaling Protocol

Asynchronous communication between two asynchronous entities is generally indicated by transitions on a request (*req*) and an acknowledge (*ack*) signal. These transitions indicate the initiation and the end of a valid transaction. The ordering of the events in a transaction is governed by the transitions on these signals, and this ordering results in the handshake protocol between two asynchronous entities. There are two signaling protocols that are commonly used, the 2-phase protocol and 4-phase protocol.

#### 2.1.2.1 2-Phase Protocol

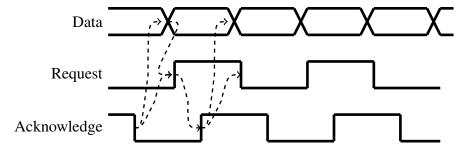

The 2-phase protocol, also known as *non-return to zero* (NRZ) protocol or *transition signaling* protocol, consists of two transitions for any valid transaction as shown in Fig. 2.1. One transition is on the request line, and it indicates the presence of a new data word and the other transition is on the acknowledge line, and it indicates the acceptance of the new data and also the end of the transaction. Each transition on the request and acknowledge line (i.e., from high to low and from low to high) indicates a new transaction [32]. 2-phase protocols are considered to be more efficient, as each transaction consists of only two transitions. The circuit implementation of the 2-phase protocols tend to be large due to the edge detection requirements of the protocol and at the register storage level. The family of untimed 2-phase protocols consists of a very small set of eight protocols [33].

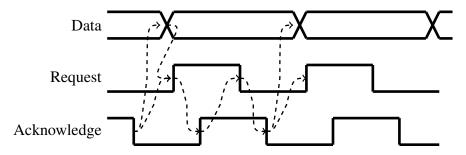

#### 2.1.2.2 4-Phase Protocol

The 4-phase protocol, also known as *return to zero* (RZ) protocol or *level signaling* protocol, consists of four transitions for any valid transaction as shown in Fig. 2.2. Since each transaction consists of four transitions, there is a greater flexibility in terms of selection of edges when the data word is valid, but there is greater overhead of the reset phase in the protocol which is a performance bottleneck. This results in lower throughput, which is one of the reason why asynchronous network-on-chip implementations use 2-phase protocols for long wires instead of 4-phase [34]. For designs whose delays are dominated by logic delays and not by wire delays, this protocol presents a wide variety of options with respect to data validity schemes employed (Sec. 2.1.3.2). The characterization of a family of untimed 4-phase early data validity protocols resulted in 131 different circuit implementations [35, 36]. Similarly, a family consisting of 32 untimed 4-phase late data validity protocols is reported in this dissertation in Chapter 6.

#### 2.1.3 Bundled Data Protocols

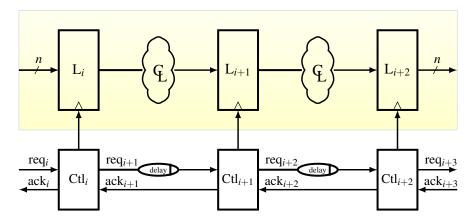

A general 4-stage "bundled data" asynchronous linear pipeline design is shown in Fig. 2.3. Bundled data represents the data signals as normal Boolean levels, and separate request and acknowledge wires are required with the data signals to control the flow of data [1]. Hence, it consists of a datapath similar to a clock design and an asynchronous control

Figure 2.1: 2-Phase protocol.

Figure 2.2: 4-Phase protocol.

path. The datapath contains acyclic *combinational logic* (*CL*) and registers (*L*). The control path consists of *linear control* (*LC*) blocks, which to ensure the functional correctness of a bundled data design, the setup and hold time constraints at the registers must be fulfilled. The setup time constraint is the time before the arrival of the clock signal at any register that the data must be stable. To fulfill the setup time constraint at the registers, the latency through the control logic must be greater than the maximum delay of the combinational logic. Thus, delay elements may be required between LC blocks. Similarly, the hold time constraint is the time after the arrival of the clock signal at any register that the data must be stable. To fulfill the hold time constraint at the registers, the reset phase of the protocol must be longer than the hold time requirements.

#### 2.1.3.1 Handshake Channel Type

The channel on a handshake network generally consists of a request signal and an acknowledge signal. Different protocols can be derived by analyzing the sequence of transitions on a request and an acknowledge signal on a handshake channel. Handshake

**Figure 2.3**: Timed (bundled data) handshake design. Delay sized by RT constraint  $req_i \uparrow \mapsto L_{i+1}/d + s \prec L_{i+1}/clk \uparrow$ .

channels can be characterized as *push* or *pull* channels based on whether the sender or the receiver initiates the handshake [37]. The side initiating the request is termed active while the passive side generally responds with an acknowledge signal.

- Push channel Channel with a sender being active and the receiver being passive.

- Pull channel Channel with a sender being passive and the receiver being active.

The handshake controllers interfacing between different channels considered in this dissertation are of a specific type. Any handshake controller interfaces two channels i.e., left and right channel. Both channels are of the push types with the handshake controller being the passive entity on the left channel and the active entity on the right channel.

#### 2.1.3.2 Data Validity in Bundled Data Protocols

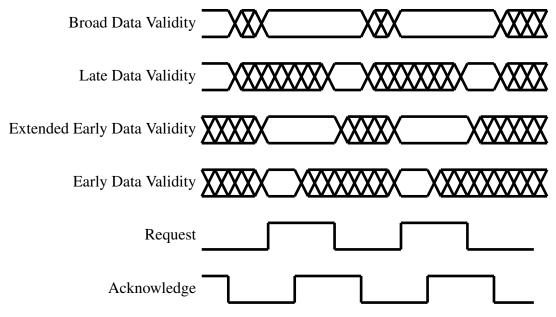

Data validity information in a protocol describes the specific transitions which initiate and end any transaction. Thus, it describes the band where the data remains stable and where it can change. 2-phase protocols have a fixed data validity scheme with the data valid between the transition on the request and the acknowledge. But 4-phase protocols have much more flexibility when using the data validity schemes to its benefit. Fig. 2.4 shows the different schemes which are described below [37]:

- Early data validity A data word is valid before the rising edge of the request (*req*) signal and it has to stay stable until the rising edge of the acknowledge (*ack*) signal.

- Late data validity A data word is valid before the falling edge of the request (*req*) signal and it has to stay stable until the falling edge of the acknowledge (*ack*) signal.

**Figure 2.4**: 4-phase protocol: data validity schemes<sup>1</sup>[1]

- Broad data validity A data word is valid before the rising edge of the request (*req*) signal and it has to stay stable until the falling edge of the acknowledge (*ack*) signal.

- Extended early data validity A data word is valid before the rising edge of the request (req) signal and it has to stay stable until the falling edge of the request (req) signal.

# 2.2 Relative Timing

Timing is the fundamental difference between clocked and asynchronous design flows. The effect of time on a system is to order and sequence events. In this work the relative timing (RT) concept is extended into a methodology that enables the representation of the sequencing that timing imposes on circuits [20]. A RT constraint consists of a common timing reference and a pair of events that are ordered in time for correct circuit operation. The common reference is called the *point-of-divergence* (pod), and each ordered event is called a *point-of-convergence* (poc). A constraint is represented as pod  $\mapsto$  poc<sub>1</sub>+ $m \prec$  poc<sub>0</sub>, where poc<sub>1</sub> must occur in time before poc<sub>0</sub> with a margin of m. Hence, the maximum path delay from pod to poc<sub>1</sub> must be less than the minimum path delay from pod to poc<sub>0</sub>.