# METAL-OXIDE-SEMICONDUCTOR FIELD EFFECT NANOSTRUCTURE SPIN LATTICE DEVICES

by

Jun Yang

A dissertation submitted to the faculty of The University of Utah in partial fulfillment of the requirements of the degree of

Doctor of Philosophy

Department of Electrical and Computer Engineering

The University of Utah

May 2013

Copyright © Jun Yang 2013

All Rights Reserved

### The University of Utah Graduate School

#### STATEMENT OF DISSERTATION APPROVAL

| The dissertation of Jun Yang    |                      |                  |                             |

|---------------------------------|----------------------|------------------|-----------------------------|

| has been approved by the follow | ving supervisory con | nmittee members: |                             |

| Mark Mille                      | r                    | , Chair          | 12/31/2012<br>Date Approved |

| Ian Harvey                      |                      | , Member         | 1/2/2013<br>Date Approved   |

| Loren Rieth                     | 1                    | , Member         | 1/2/2013<br>Date Approved   |

| Florian Solzba                  | cher                 | , Member         | 1/2/2013<br>Date Approved   |

| Craig Pryor                     | r                    | , Member         | 1/2/2013<br>Date Approved   |

| and by                          | Gianluca Lazzi       |                  | , Chair of                  |

| the Department of               | Electrical and       | Computer Engi    | neering                     |

and by Donna M. White, Interim Dean of The Graduate School.

#### ABSTRACT

This dissertation explored and developed technologies for silicon based spin lattice devices. Spin lattices are artificial electron spin systems with a periodic structure having one to a few electrons at each site. They are expected to have various magnetic and even superconducting properties when structured at an optimal scale with a specific number v of electrons. Silicon turns out to be a very good material choice in realizing spin lattices. A metal-oxide-semiconductor field-effect nanostructure (MOSFENS) device, which is closely related to a MOS transistor but with a nanostructured oxide-semiconductor interface, can define the spin lattices potential at the interface and alter the occupation v with the gate electrode potential to change the magnetic phase. The MOSFENS spin lattices engineering challenge addressed in this work has come from the practical difficulty of process integration in modifying a transistor fabrication process to accommodate the interface patterning requirements.

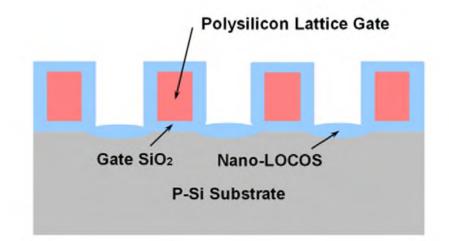

Two distinct design choices for the fabrication sequences that create the nanostructure have been examined. Patterning the silicon surface before the MOS gate stack layers gives a "nanostructure first" process, and patterning the interface after forming the gate stack gives a "nanostructure last process." Both processes take advantage of a nano-LOCOS (nano-local oxidation of silicon) invention developed in this work. The nano-LOCOS process plays a central role in defining a clean, sharp confining potential for the spin lattice electrons.

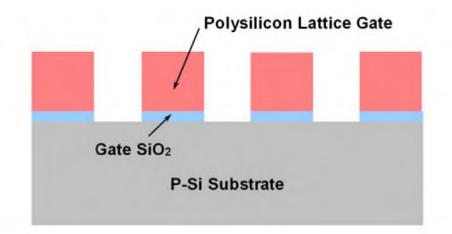

The MOSFENS process required a basic transistor fabrication process that can accommodate the nanostructures. The process developed for this purpose has a gate stack with a 15 nm polysilicon gate electrode and a 3 nm thermal gate oxide on a p-type silicon substrate. The measured threshold voltage is 0.25 V. Device processes were examined for either isolating the devices with windows in the field oxide or with mesas defined by the etched trenches filled with oxide.

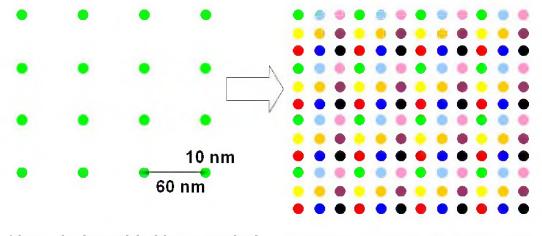

The nanostructrure patterning processes combined electron beam lithography, reactive ion etching and the nano-LOCOS in a nanostructure last fabrication sequence. The electron beam tool produced holes with diameters down to 10 nm and lattice periods down to 50 nm for defining the spin lattices. The dry etching process was able to transfer the pattern into the polysilicon gate material, and the depth was controlled using the measured etching rate. These dimensions are sufficiently small for spin lattices properties to be important at low temperatures.

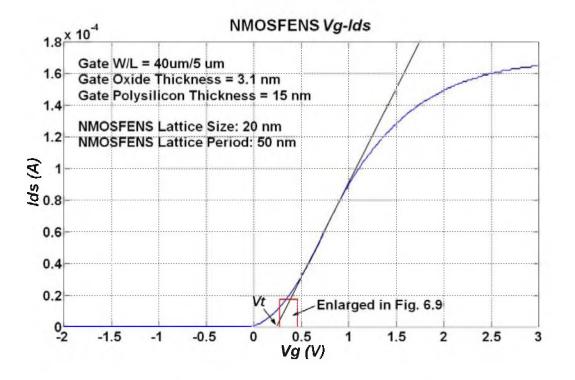

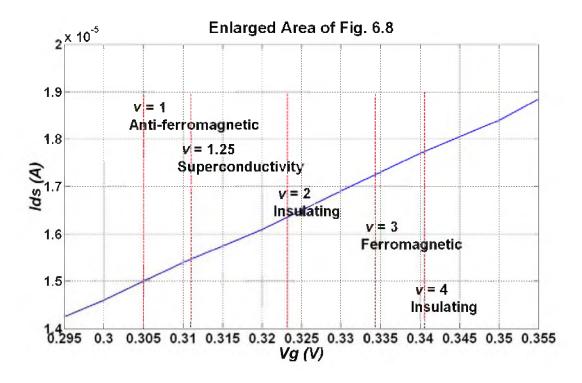

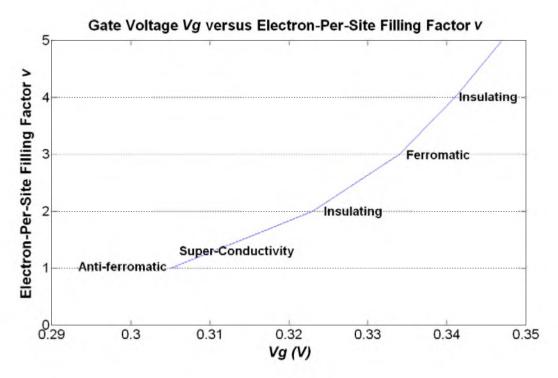

Upon combining the NMOS and the nanostructure last processes, MOSFENS spin lattice devices were successfully fabricated. The gates are patterned with lattices having a 50 nm period and 20 nm holes, which is the optimal, targeted ratio of 2.5 for superconductivity. The room temperature current-voltage characteristics of these devices show that the lattice nanostructures significantly reduce the average channel mobility, as expected. However, the essentially unchanged threshold voltage indicates the nano-LOCOS process has given a low-defect nanostructure interface. At room temperature, a change in gate potential of approximately of 18 mV changes the lattice electron occupation from v = 1 to v = 2. For these devices, the predicted temperature scale for superconductivity is approximately at 9 K. I dedicate this dissertation to my wife Jin for her support, patience, and encouragement, and to our beloved daughter Gianna.

## CONTENTS

|   | P                                                                                                                                                                                      | age                  |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| A | BSTRACT                                                                                                                                                                                | iii                  |

| L | IST OF FIGURES                                                                                                                                                                         | viii                 |

| L | IST OF TABLES                                                                                                                                                                          | . xi                 |

| A | CKNOWLEDGMENTS                                                                                                                                                                         | xii                  |

| 1 | INTRODUCTION                                                                                                                                                                           | . 1                  |

|   | <ul> <li>1.1 Spin Lattices</li> <li>1.2 Material Selection for Spin Lattices</li> <li>1.3 MOS Spin Lattices Technology Challenges</li> <li>1.4 Outline of This Dissertation</li> </ul> | 5<br>6               |

| 2 | TECHNICAL BACKGROUND                                                                                                                                                                   | 10                   |

|   | <ul> <li>2.1 Spin Lattices Material Selection</li> <li>2.2 MOS Models</li> <li>2.3 Strong Coupling Length in Silicon MOS</li> </ul>                                                    | . 12                 |

| 3 | FABRICATION PROCESS AND DEVICE DESIGN                                                                                                                                                  | 16                   |

|   | <ul> <li>3.1 Nanostructure-First and Nanostructure-Last</li> <li>3.2 Nano-LOCOS</li> <li>3.3 Window Isolation and Mesa Isolation</li> </ul>                                            | 18                   |

| 4 | NMOS PROCESS DEVELOPMENT                                                                                                                                                               | 22                   |

|   | <ul> <li>4.1 Mask Layout</li></ul>                                                                                                                                                     | . 24<br>. 33<br>. 42 |

| 5 | NANOSTRUCTURE PROCESS DE VELOPMENT                                                                         | . 45 |

|---|------------------------------------------------------------------------------------------------------------|------|

|   | <ul><li>5.1 Thin Oxidation for Gate Oxide and Nano-LOCOS</li><li>5.2 Thin Polysilicon Deposition</li></ul> |      |

|   | 5.3 Thin Polysilicon RIE                                                                                   |      |

|   | 5.4 Electron Beam Lithography                                                                              | 52   |

|   | <ul><li>5.5 Chemical Mechanical Polishing</li><li>5.6 Summary And Conclusions</li></ul>                    |      |

| 6 | NANOSTRUCTURE FABRICATION AND CHARACTERIZATION                                                             | 57   |

|   | 6.1 Nanostructure Last Fabrication Process                                                                 | 57   |

|   | 6.2 MOSFENS Spin Lattice Devices Characterization                                                          |      |

|   | 6.3 Conclusions                                                                                            |      |

| 7 | SUMMARY AND RECOMMENDATIONS                                                                                | . 67 |

|   | 7.1 Summary                                                                                                | 67   |

|   | 7.2 Conclusions                                                                                            |      |

|   | 7.3 Future Work and Recommendations                                                                        | 69   |

| A | <b>APPENDICES</b>                                                                                          |      |

| A | SI-SIO <sub>2</sub> INTERFACE CHARGES AND TRAPS                                                            | 73   |

| B | B LITHOGRAPHY PROCESS                                                                                      | 76   |

| C | <b>C NANOSTRUCTURE FIRST PROCESS</b>                                                                       | . 78 |

| D | NANOSTRUCTURE LAST WINDOW PROCESS FLOW                                                                     | . 82 |

| F | REFERENCES                                                                                                 | . 85 |

## **LIST OF FIGURES**

| gure | P                                                                                                                                                                                                                                                                                                                                                                                                                                                | age |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

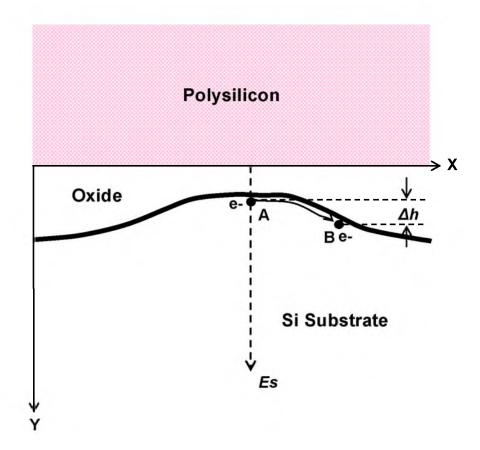

| 1.1  | Engineering strongly-coupled electrons by undulating topography at the Si-SiO <sub>2</sub> interface in a MOSFENS: The electron is held tightly to the thinnest portion of the oxide (position A) where the lowest potential resides. The electron has to overcome the perpendicular electrical field $E_s$ to move in a distance of $\Delta h$ to another location (position B) where the potential is higher.                                  | 2   |

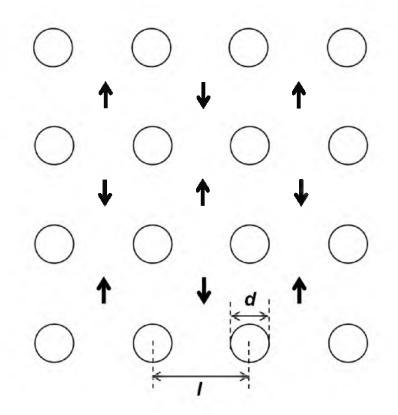

| 1.2  | The diagram shows single occupation anti-dot square spin lattices. The spin lattices are occupied by the electrons which are represented in arrows with a spin direction in parallel. The circles represent the holes separating the sites with the size of $d$ and the period in $l$ .                                                                                                                                                          | 4   |

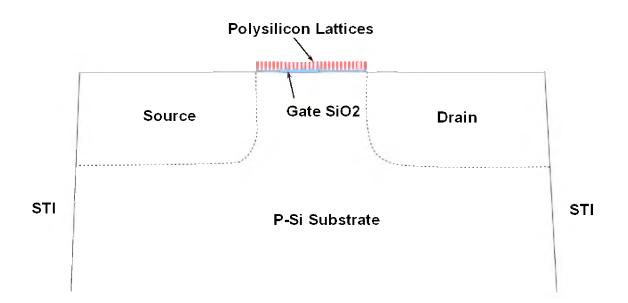

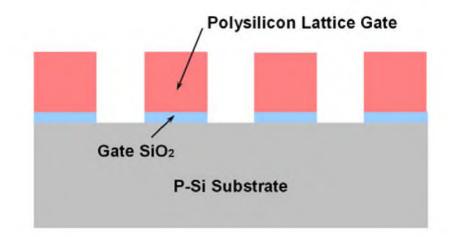

| 1.3  | Schematic cross-section view of a MOSFENS spin lattice device, which has 3 nm gate oxide and 15 nm gate polysilicon. The gate is patterned with lattice holes.                                                                                                                                                                                                                                                                                   | 8   |

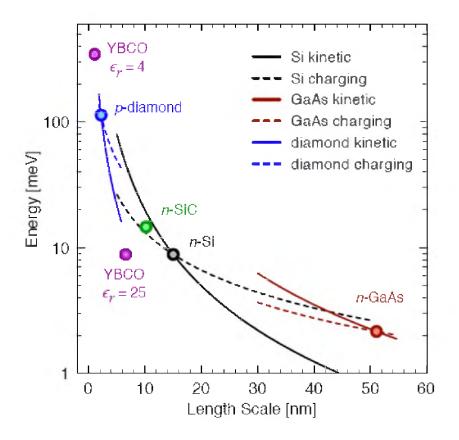

| 2.1  | The strong-coupling energy scale plotted versus length scale for several candidate spin lattices materials. Solid lines plot the kinetic energy Et and dashed lines the charging energy $E_U$ dependence on length scale for <i>p</i> -diamond, <i>n</i> -Si, and <i>n</i> -GaAs, with line colors corresponding to the a point for each material. The two points for YBCO (yttrium barium copper oxide) assume two values for the permittivity. | 12  |

| 2.2  | Inversion layer 2DEG density versus gate voltage at 77 K spanned by two doping densities. A gray dashed line plots an estimate for the fixed interface charge density $N_{f}$ . The right axis scale gives a corresponding length scale estimate per single electron of $a \approx 1/\sqrt{\varepsilon_{Si}}$ , with the strong coupling length scale for silicon $a_{Si}^*$ plotted with a red dashed line                                      | 15  |

| 3.1  | Cross-sections of the nanostructure last design and the nanostructure first design with the hole size = $d$ and the period = $l$                                                                                                                                                                                                                                                                                                                 | 17  |

| 3.2  | Formation of the window isolation and the mesa isolation. The active region<br>of the window isolation is lower than the oxide, while the active region of<br>the mesa isolation is higher than the oxide in the trench                                                                                                                                                                                                                          | 19  |

Fig

| 3.3  | The step height between the active regions and the isolation regions causes<br>underexposure, and consequently, current shortage for the window isolation<br>but not for the mesa isolation | 21 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

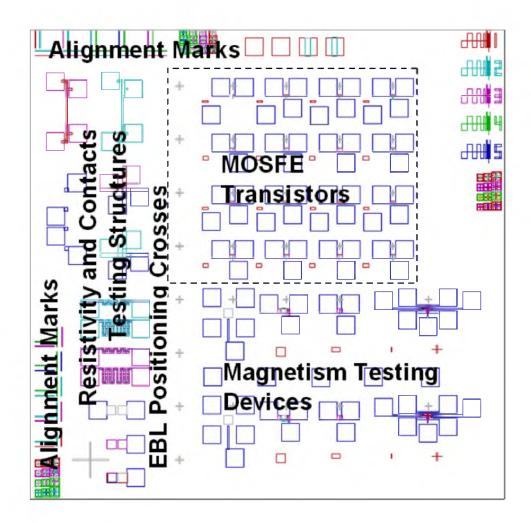

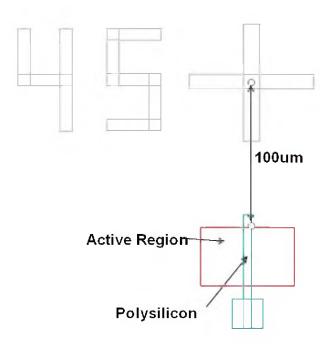

| 4.1  | Mask layout of a die                                                                                                                                                                        | 23 |

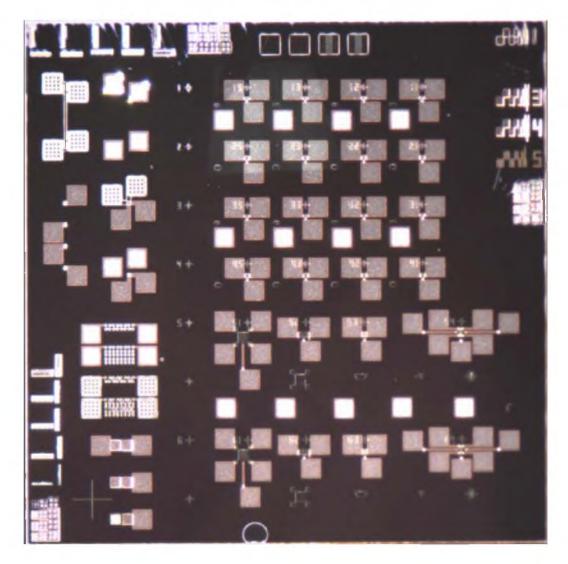

| 4.2  | Image of a die of an NMOS window isolation device wafer                                                                                                                                     | 31 |

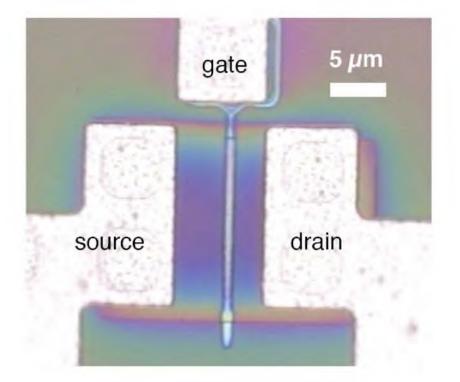

| 4.3  | Top view of a polysilicon gate NMOS window isolation transistor                                                                                                                             | 32 |

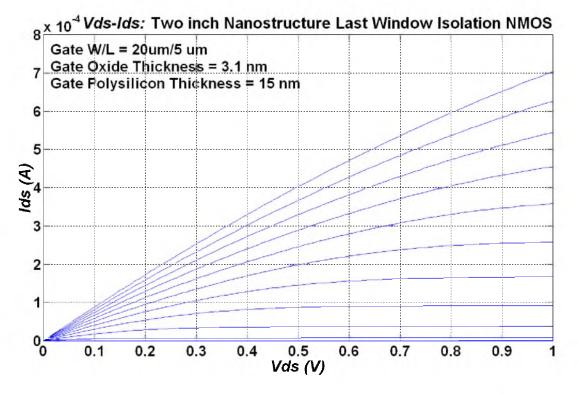

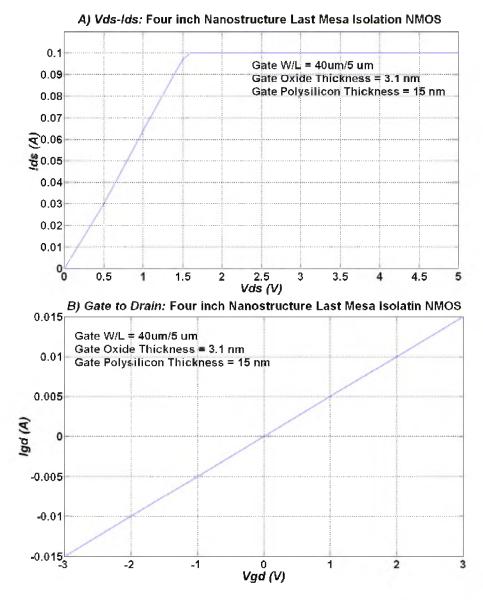

| 4.4  | Two inch nanostructure last window isolation NMOS $V_{ds}$ - $I_{ds}$                                                                                                                       | 32 |

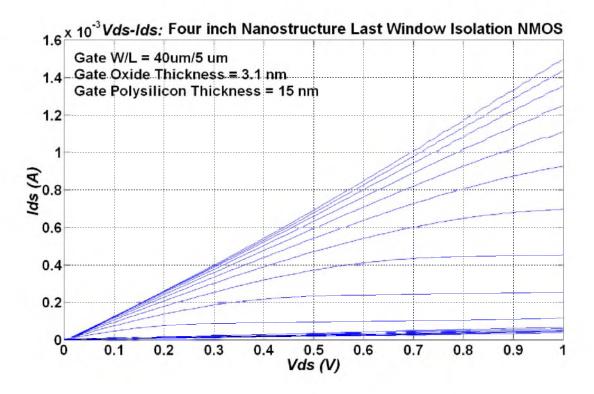

| 4.5  | Four inch nanostructure last window isolation NMOS $V_{ds}$ - $I_{ds}$                                                                                                                      | 33 |

| 4.6  | NMOS mesa isolation: mask one lithography                                                                                                                                                   | 34 |

| 4.7  | NMOS mesa isolation: silicon trench via RIE                                                                                                                                                 | 35 |

| 4.8  | NMOS mesa isolation: field oxide growth                                                                                                                                                     | 35 |

| 4.9  | NMOS mesa isolation: CMP                                                                                                                                                                    | 35 |

| 4.10 | Four inch NMOS mesa isolation characteristics                                                                                                                                               | 38 |

| 4.11 | Reasons for the mesa isolation transistors failure                                                                                                                                          | 39 |

| 4.12 | Comparison between the mesa process and a STI process, steps 1 to 5                                                                                                                         | 40 |

| 4.13 | Comparison between the mesa process and a STI process, steps 6 to 10                                                                                                                        | 41 |

| 4.14 | Thin polysilicon gate and the nano-LOCOS compatibility experiment: $V_g$ - $I_{ds}$                                                                                                         | 43 |

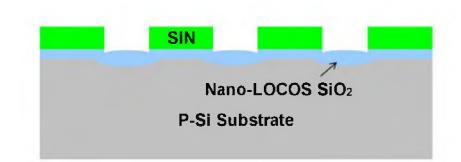

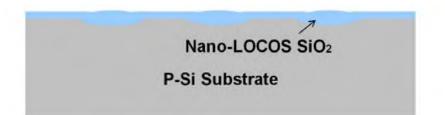

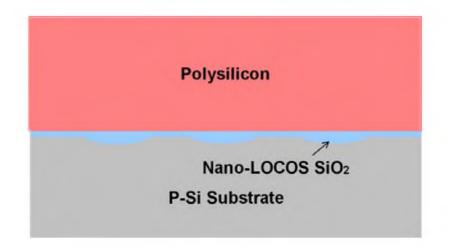

| 5.1  | Creating nanoscale isolation by using the nano- LOCOS process                                                                                                                               | 46 |

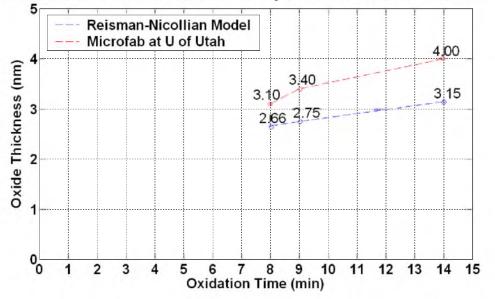

| 5.2  | Thin oxidation thickness versus Reisman-Nicollian model                                                                                                                                     | 47 |

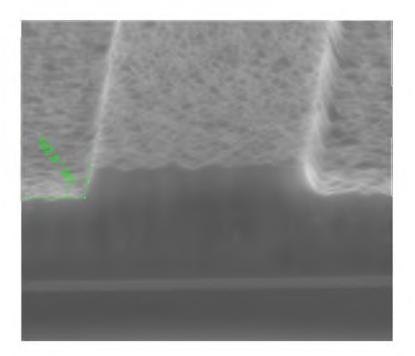

| 5.3  | Anisotropic profile via the polysilicon RIE                                                                                                                                                 | 51 |

| 5.4  | Successful imaging of 10 nm holes by FEI Nova NanoSEM 630 (Courtesy of R. Polson, the Physics Department, The University of Utah)                                                           | 53 |

| 5.5  | Successful imaging of 15 nm holes with 100 nm spacing by FEI Nova NanoSEM 630 (Courtesy of R. Polson, the Physics Department, The University of Utah).                                      | 53 |

| 5.6         | EBL alignment mark for individual device                                                                                           | 54 |

|-------------|------------------------------------------------------------------------------------------------------------------------------------|----|

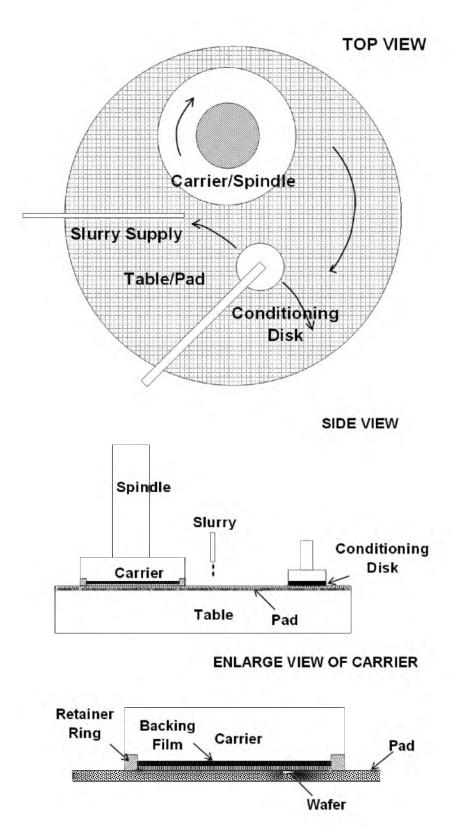

| 5.7         | Top view and side view of a CMP tool and enlarged view of the carrier                                                              | 55 |

| 6.1         | The nanostructure last lattice formation: EBL                                                                                      | 58 |

| 6.2         | The nanostructure last lattice formation: the spin lattices polysilicon via RIE                                                    | 59 |

| 6.3         | Patterning on the polysilicon gate by EBL before the spin lattices undergo RIE                                                     | 59 |

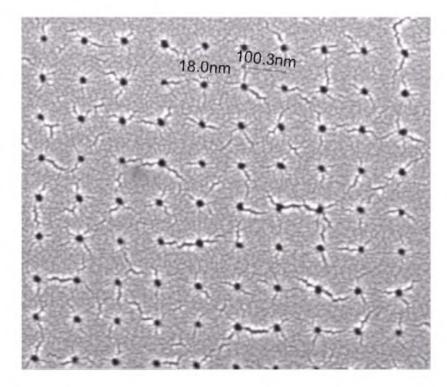

| 6.4         | Spin lattices holes (20 nm in size with 50 nm in period) on the polysilicon gate after the spin lattices RIE and PMMA resist strip | 60 |

| 6.5         | The nanostructure last lattice formation: the nano-LOCOS                                                                           | 61 |

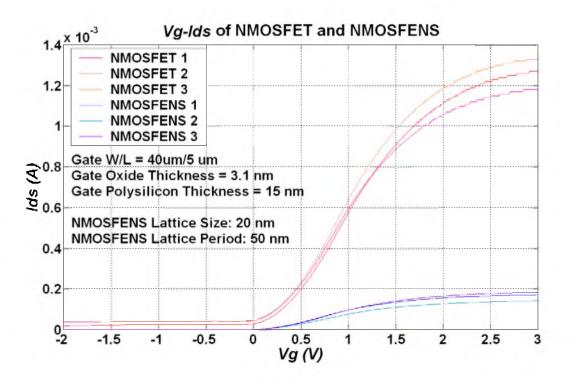

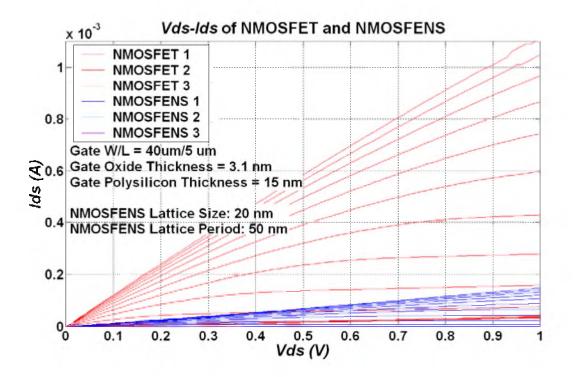

| 6.6         | $V_g$ - $I_{ds}$ of standard MOSFETs and MOSFENS spin lattice devices                                                              | 62 |

| 6.7         | $V_{ds}$ - $I_{ds}$ of standard MOSFETs and MOSFENS spin lattice devices                                                           | 62 |

| 6.8         | Average $V_{ds}$ - $I_{ds}$ of MOSFENS spin lattice devices $V_t = 0.25$ V                                                         | 64 |

| 6.9         | Enlarged area of Fig. 6.8 with electron-per-site filling factor v denoted                                                          | 64 |

| 6.10        | The gate voltage $V_g$ versus the electron-per-site filling factor v                                                               | 65 |

| 7.1         | Achieving 20 nm period by repeating EBL of 60 nm period                                                                            | 71 |

| <b>A</b> .1 | The Si-SiO <sub>2</sub> interface charges                                                                                          | 74 |

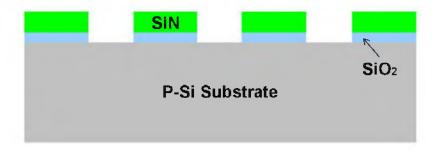

| <b>C</b> .1 | The nanostructure first lattices formation: nitride deposition                                                                     | 79 |

| C.2         | The nanostructure first lattices formation: nitride RIE                                                                            | 79 |

| C.3         | The nanostructure first lattices formation: nano-LOCOS                                                                             | 80 |

| C.4         | The nanostructure first lattices formation: nitride wet etching                                                                    | 80 |

| C.5         | The nanostructure first lattices formation: polysilicon deposition                                                                 | 81 |

## LIST OF TABLES

| Table | ]                                                                                                                                                 | Page |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2.1   | Two-dimensional electron gas densities in a MOSFET that correspond to those needed to achieve one-electron-per-site for a given lattice scale $a$ | 15   |

| 4.1   | Four inch wafers polysilicon doping experiment results                                                                                            | 28   |

| 4.2   | The field oxide thickness of the NMOS window isolation                                                                                            | 28   |

| 4.3   | Trench oxide thickness of the NMOS mesa isolation                                                                                                 | 37   |

| 4.4   | Step height of the NMOS mesa isolation                                                                                                            | 37   |

| 4.5   | Thin polysilicon gate and the nano-LOCOS compatibility experiment splits                                                                          | 42   |

| 5.1   | The polysilicon RIE recipe                                                                                                                        | 51   |

| 6.1   | The gate voltage $V_g$ at different electron-per-site filling factors $v$                                                                         | 65   |

#### ACKNOWLEDGMENTS

It would not have been possible to write this doctoral thesis without the help and support of the kind people around me, to only some of whom it is possible to give particular mention here.

Above all, this thesis would not have been possible without the help, support and instruction of my principal supervisor, Dr. Mark Miller.

The good advice and support of my other supervisors, Dr. Ian Harvey, Dr. Florian Solzbacher, Dr. Loren Rieth and Dr. Craig Pryor, have been invaluable on both an academic and a personal level, for which I am extremely grateful.

I would like to express my greatest appreciations to Nanofab staff of The University of Utah, Brian Baker, Tony Olson, Kevin Hensley, Charles Fisher, surely the associate director of Nanofab, Dr. Ian Harvey, for their diligent and long-lasting support to make this project ever possible.

Last, but by no means least, I would like to thank my friend Randy Polson in Physics Department of The University of Utah, for his talents and skills in electron beam lithography which made this project successful.

#### **CHAPTER 1**

#### **INTRODUCTION**

Silicon nanostructures structured at an optimal dimension scale are promising for implementing magnetic and superconducting systems, and such periodic structures have been referred to as spin lattices [1, 2, 3]. We propose a nanostructure that is similar to the MOS (metal-oxide-semiconductor) transistor but with a patterned, undulating oxidesemiconductor interface to serve as a platform for spin lattice applications. The fieldeffect perpendicular electric filed at the interface is able to modulate and engineer the inplane two-dimensional electron gas (2DEG) (Fig. 1.1) [2, 4]. This nanostructure is referred to as "metal-oxide-semiconductor field-effect nanostructure (MOSFENS)," One of the great challenges for MOSFENS engineering is the process integration of how to modify an established MOSFET (metal-oxide-semiconductor field-effect transistor) fabrication process to accommodate the interface patterning requirements [5].

As illustrated in Fig. 1.1, the gate-to-substrate perpendicular surface electric field  $E_s$ in a MOSFENS device pushes the inversion layer electron gas in the silicon up against a patterned oxide interface. The undulating Si-SiO<sub>2</sub> interface gives a local effective inplane electric field  $E_p$  [2]. Take the average interface plane to be the *x* plane, with *y* into the substrate, and describe the surface topography by its height in the *y*-direction, h(y). For the moment, neglect the different permittivity for silicon and silicon dioxide. Setting the electron potential energy at the lowest *h*-point to zero, the potential energy along *h*

Fig. 1.1: Engineering strongly-coupled electrons by undulating topography at the Si-SiO<sub>2</sub> interface in a MOSFENS: The electron is held tightly to the thinnest portion of the oxide (position A) where the lowest potential resides. The electron has to overcome the perpendicular electrical field  $E_s$  to move in a distance of  $\Delta h$  to another location (position B) where the potential is higher.

varies as  $qhE_s$ , and the local in-plane effective electric field is:

$$E_{v} = E_{s} \nabla h \tag{1.1}$$

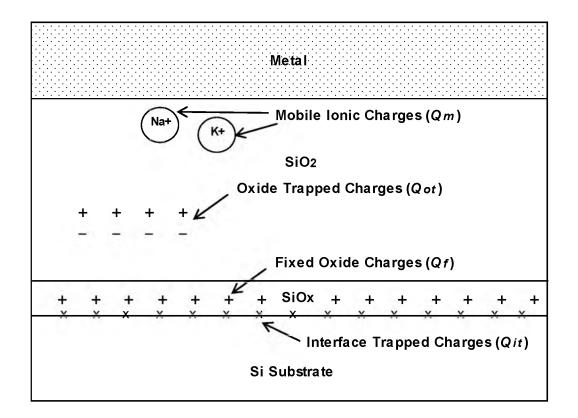

Taking  $E_s = 1$  MV/cm, for h = 3 nm, the scale of the effective in-plane electric field over a half-period is about 0.3 MV/cm, a significant fraction of  $E_s$  for such a modest perturbation of the Si-SiO<sub>2</sub> interface. The corresponding potential energy increases over a half period to 300 meV. It is important to have a smooth Si-SiO<sub>2</sub> interface and high quality oxide of minimum interface traps and fixed charges to prevent oxide tunneling. In this chapter, section 1.1 presents the concept of spin lattices and their various magnetic and superconductivity properties related to the electron-per-site filling factor v. Section 1.2 introduces material selection to meet the requirement of spin lattices. Section 1.3 gives the technology challenges in realizing spin lattices by using MOS structures. In section 1.4, the outline of this dissertation is described.

#### **1.1 Spin Lattices**

One important application of MOSFENS devices should be to realize spin lattices. Spin lattices are artificial electron spin systems with a periodic structure having one to a few electrons at each site, and the electrons are confined within a small island. Spin lattices can show atom-like behavior, but they have two characteristics that are very different from those of actual atoms. The first characteristic is that the distance between the lattice structures is unchangeable when the electrons are strongly tied to the sites, while the bond length of atoms can be varied. The second characteristic is that the number of electrons at each engineered site can be altered, whereas in atoms this is fixed. Spin lattice structures are not susceptible to lattice deformations; therefore, they can be designed freely without considering potential lattice instabilities [6].

Koskinen and others showed that because of the interplay between electron charge, motion, spin, exchange, and correlation, spin lattices have rich magnetic properties, depending on the lattice constant and the electron number [7]. The electron-per-site filling factor v is defined as the number of electrons bound to each site, and Fig. 1.2 depicts anti-dot single occupation square spin lattices with v = 1. Theorems by Lieb predict that v = 1 gives an anti-ferromagnetic phase, and v = 3 a ferromagnetic phase, while v = 2 and 4 result in quantum insulating phases [6].

Fig. 1.2: The diagram shows single occupation anti-dot square spin lattices. The spin lattices are occupied by the electrons, which are represented in arrows with a spin direction in parallel. The circles represent the holes separating the sites with the size of d and the period in l.

One of the most fascinating potential applications of spin lattices engineering is high temperature (high-T<sub>c</sub>) superconductivity [8, 9, 10, 11]. Although the energy scales or the transition temperature is smaller than the conventional CuO<sub>2</sub> high-T<sub>c</sub> superconductors [12], superconductivity in spin lattices might be possible. Single-electron band calculations also suggest that an anti-dot geometry of spin lattices with optimal dimensions should have a ratio between the lattice period *l* and the hole size *d* of 2.5. For instance, for a hole size at 10 nm and lattice period at 25 nm, the gap energy scale estimation is 19 K. For a hole size at 20 nm and lattice period at 50 nm, the gap energy scale should be 7 K [2].

Spin lattices may be adapted for use in a number of device applications, including spintronics, fast processing and high-density bit storage, magnetic field sensors, and switches for logic circuits, etc.

Importantly, the theoretical predictions for the magnetic phases rely on particular assumptions, and approximations that are often in disagreement; and the underlying models are notoriously hard to solve. Working MOSFENS spin lattice devices should help to set some boundaries for choosing between theoretical approaches, in addition to any technological benefits from these devices.

#### **1.2 Material Selection for Spin Lattices**

There have been several efforts undertaken to realize spin lattices based on different materials, like carbon networks [13, 14], graphite ribbon [15], As [16], GaAs atomic wires [17, 18], and InAs lattices [19]. However, there is no clear evidence so far of the observation of ferromagnetism. Because it is difficult to form the lattices using these materials and the lattice distortion would destabilize ferromagnetism [20].

Silicon turns out to be a very good material choice in realizing spin lattices because of a good compromise between the conflicting goals of a small dielectric constant and a small effective mass (see section 2.1) [2]. With their gate electrodes patterned with holes at the optimal scale and period, MOSFENS devices provide a platform for realizing spin lattices with advantages. The first advantage is that the electron-per-site filling factor vand accordingly the magnetic phases can be controlled by changing the gate potential. The second advantage is that the Si-SiO<sub>2</sub> interface gives a smooth confinement barrier for defining the spin lattices. The properties of Si-SiO<sub>2</sub> interface are well studied. Furthermore, effective approaches to minimize the interface traps are available for use (see Appendix A) as it is critical for MOSFENS spin lattice devices to have a significantly lower number of interface traps compared to the overall spin lattice sites [2]. The third advantage is that there is an immense and still growing semiconductor technology base for fine-scale structures like MOSFENS.

#### **1.3 MOS Spin Lattices Technology Challenges**

The central MOSFENS spin lattices engineering challenges come from the great difficulties in modifying an established transistor fabrication process to accommodate the interface patterning requirements [5]. These modifications make it difficult to fabricate MOSFENS spin lattice devices in a foundry service. To better understand this, it is beneficial to briefly introduce the advanced processes used in contemporary deep sub-micron MOSFET structures.

Because direct tunneling increases exponentially with decreasing oxide thickness, it may not be feasible to use SiO<sub>2</sub> with thickness smaller than 1.5 nm. A wide variety of high-*k* materials have been studied as the alternative to SiO<sub>2</sub> (k = 3.9) for deep submicron MOSFET, like Ta<sub>2</sub>O<sub>5</sub> (k = 23) [21], Al<sub>2</sub>O<sub>3</sub> (k = 10) [22], ZrO<sub>2</sub> (k = 23) [23] and HfO<sub>2</sub> (k = 20) [24]. The ideal gate dielectric stack has an interface consisting of a few atomic layers of Si-O (and possibly nitride), containing a pseudo-binary oxide. This oxide layer could preserve the critical high quality characteristics of the SiO<sub>2</sub> interface while providing a higher k value. Then a different, higher-*k* material could be used on top of this interfacial layer.

The replacement gate process architecture avoids the problems of work function material stability seen in the gate first architecture. The original deposited polysilicon will be removed and be replaced by metal gate (like Al alloys), which has much lower resistivity [25].

Self-aligned process does not require any additional masking steps, and it forms silicide (like  $TiSi_2$ , NiSi or  $CoSi_2$ ) on the source and the drain regions only to achieve low resistivity [26]. On the traditional gate first process, the silicide is also formed at the same time on the polysilicon gate.

Shallow trench isolation (STI) isolates the transistors by the oxide buried in deep trenches, and it provides better isolation between the devices compared to the conventional LOCOS (local oxidation of silicon) by minimizing the channel current leakage under the field oxide. Meanwhile, STI offers superior latch-up immunity, smaller channel-width encroachment and much better planarity [27].

Strained silicon is a layer of silicon in which the silicon atoms are stretched beyond their normal interatomic distance. This can be accomplished by putting the layer of silicon over a substrate of silicon germanium (SiGe). In this way, higher mobility in the channel consequently leads to a larger channel current [28].

Fig. 1.3 shows a cross-section view of a MOSFENS spin lattice device. It uses ALD (atomic layer deposition) technique to grow a SiO<sub>2</sub>-SiN stack of gate dielectric (see section 7.3), and the mesa isolation (see section 3.3) using STI technologies. Ultra-thin gate oxide instead of high-*k* materials is used for MOSFENS spin lattice devices, because the ultra-thin oxide provides a stronger perpendicular electric field at the interface. In addition, the thin oxidation technique is also applied to the nano-LOCOS (nano-local oxidation of silicon) process, which will be introduced in section 3.2.

Fig. 1.3: Schematic cross-section view of a MOSFENS spin lattice device, which has 3 nm gate oxide and 15 nm gate polysilicon. The gate is patterned with the lattice holes.

#### **1.4 Outline of This Dissertation**

Chapter 2 provides an overview of two distinct design choices for the fabrication sequences of the nanostructure formation. Patterning the silicon surface before the MOS gate stack layers gives a "nanostructure first" process, and patterning the interface after forming the gate stack gives a "nanostructure last" process. Both processes take advantage of a nano-LOCOS invention developed in this work. The nano-LOCOS process plays a central role in defining a confining potential for the spin lattice electrons.

The MOSFENS process requires a basic transistor fabrication process that can accommodate the nanostructures. In Chapter 3, the developments, the fabrication process flow and the characterizations of an NMOS (*n*-type metal-oxide-semiconductor) process are presented. In addition, the processes are examined for either isolating the devices with the windows in the field oxide or with the mesas defined by the etched trenches filled with oxide.

Chapter 4 introduces the nanostructrure patterning processes that combine the electron beam lithography (EBL), the reactive ion etching (RIE) and the nano-LOCOS in a nanostructure last fabrication sequence. The electron beam tool gives holes with diameters down to 20 nm and lattice periods down to 50 nm for defining the spin lattices. The RIE process is able to transfer the pattern into the polysilicon gate material. These dimensions are sufficiently small for the spin lattices properties to be prominent at low temperatures.

Upon combining the NMOS and the nanostructure last processes, MOSEFENS spin lattice devices were successfully fabricated. Chapter 5 lists the fabrication process flow of MOSFENS spin lattice devices and along with the characterization results.

Chapter 6 is devoted to the summary, the future tasks and the recommendations for the development of next generation MOSFENS devices.

#### **CHAPTER 2**

#### **TECHNICAL BACKGROUND**

In this chapter, the technical background and the models are presented. In section 2.1, a method based on a strong coupling electrons system is used to identify good materials for the spin lattice implementation. In section 2.2, a MOS model used to calculate the 2DEG concentration at the Si-SiO<sub>2</sub> interface is introduced. In section 2.3, the 2DEG concentration based on various lattice length scales is calculated for comparison with the typical value of the fixed oxide charge concentration  $N_{f}$ .

#### 2.1 Spin Lattices Material Selection

Strong coupling requirement for the spin lattices asks the semiconductor material to balance between the kinetic energy and the charging energy [2]. The kinetic energy  $E_t$  can be calculated by the lowest confinement energy of a carrier in that material to a sphere of radius a,

$$E_t = \frac{\pi^2 \hbar^2}{2m^* a^2}$$

(2.1)

with  $m^*$  the effective mass and  $\hbar$  Planck's constant.

The charging energy  $E_U$  for a spherical region radius *a* can be obtained as:

$$E_U = \frac{q^2}{4\pi\varepsilon a} \tag{2.2}$$

with q the elementary charge and  $\varepsilon$  the permittivity. These energies balance at the strong coupling [29] length scale:

$$a^{*} = \frac{2\pi^{3}\hbar^{2}\varepsilon}{q^{2}m^{*}}$$

(2.3)

For an electron of mass  $m_0$ , and permittivity  $\varepsilon_0$  in vacuum, the strong coupling length  $a^* = 261$  pm, which is about five times of the Bohr radius. For spin lattices, a larger length scale is easier to fabricate and a larger strong coupling energy gives higher operation temperature.

Fig. 2.1 plots the strong coupling energies of several materials versus their strongcoupling length scales reproduced from Mark's calculation [2]. III-V semiconductor materials have small effective masses, but small masses generally come with larger permittivity and consequently, smaller strong coupling energies  $E^*$ . For GaAs, of which electron effective mass  $m^*_n = 0.067 m_0$  and  $\varepsilon_r = 13.1$ , the scales are  $a^*_{GaAs} = 51.1$  nm and  $E^*_{GaAs} = 2.15$  meV. As another example, InAs, of which  $m^*_n = 0.023 m_0$  and  $\varepsilon_r = 14.6$ , has a larger  $a^*_{InAs} = 166$  nm but even smaller  $E^*_{InAs} = 0.59$  meV. For *n*-type Si, taking  $m^*_t$  $= 0.19 m_0$  and  $\varepsilon_r = 10.9$ , it has  $E^*_{Si} = 8.8$  meV and  $a^*_{Si} = 15.0$  nm. This energy corresponds with the thermal energy scale for liquid nitrogen at 6.6 meV, and the length scale lies well within the reach of present fine patterning technologies including EBL. Overall, this analysis suggests that silicon is an ideal candidate to realize strong coupling spin lattice systems, since it has both a large practical  $E^*$  and  $a^*$  giving rise to spin lattices operating within reach of liquid nitrogen temperature.

Fig. 2.1: The strong-coupling energy scale plotted versus length scale for several candidate spin lattices materials. Solid lines plot the kinetic energy Et and dashed lines the charging energy  $E_U$  dependence on length scale for *p*-diamond, *n*-Si, and *n*-GaAs, with line colors corresponding to the a point for each material. The two points for YBCO (yttrium barium copper oxide) [30] assume two values for the permittivity [2].

#### 2.2 MOS Models

A positive gate voltage will form an inversion layer of 2DEG at the Si-SiO<sub>2</sub> interface on *p*-type material MOS structures. For a MOSFENS spin lattice device with sites the size of *a*, the occupation of the lattice sites is approximately  $n_s a^2$ , where  $n_s$  is the 2DEG concentration for a given gate bias potential. Therefore, when the inversion layer of 2DEG begins to form at the Si-SiO<sub>2</sub> interface, the gate potential  $V_g$  equals to the threshold potential  $V_t$ , and it can be calculated as:

$$V_g = V_t = V_{fb} + 2\psi_B + \frac{\sqrt{2\varepsilon_{si}qN_a(2\psi_B + V_{bs})}}{C_{ox}}$$

(2.4)

where  $N_a$  is substrate doping concentration  $N_a$ .

The flat-band voltage  $V_{fb}$  is taken to be the work function difference between the gate polysilicon and semiconductor, and the oxide has a capacitance per area of  $C_{ox} = \varepsilon_{ox}/t_{ox}$ , with  $\varepsilon_{ox}$  and  $t_{ox}$  the oxide permittivity and thickness. The bulk potential is defined as  $\psi_B = V_{th} ln(N_a/n_i)$ , with  $n_i$  the silicon intrinsic carrier concentration, and  $V_{th} = k_B T/q$  the thermal potential, with  $k_B$  Boltzmann's constant. The body bias potential  $V_{bs}$ , applied from the substrate to the inversion layer, can shift the threshold voltage. Above threshold, the two-dimensional inversion layer electron concentration is approximately [34]:

$$n_s = \frac{C_{ox}}{q} (V_g - V_t) \tag{2.5}$$

Below threshold, the 2DEG concentration varies exponentially with the gate potential as [31]:

$$n_{s} = \frac{V_{th}N_{a}}{E_{s}}e^{\frac{(V_{g}-V_{t})}{mV_{th}}}$$

(2.6)

where m is the body effect coefficient.

The surface electric field at the Si-SiO<sub>2</sub> interface is:

$$E_{s} = \sqrt{\frac{2qN_{a}(2\psi_{B} + V_{bs})}{\varepsilon_{si}}}$$

(2.7)

This electric field has a characteristic scale of 1 MV/cm in silicon based MOS. Together with the gate potential, the back gate potential  $V_{bs}$  provides a means to independently vary the inversion layer concentration as well as the surface electric field  $E_s$  in the semiconductor at the interface.

#### **2.3 Strong Coupling Length in Silicon MOS**

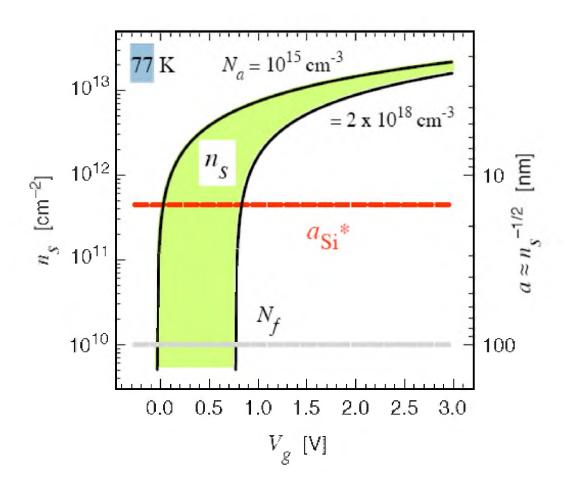

According to Mark's calculation [2], Fig. 2.2 plots representative ranges of the 2DEG concentration  $n_s$  versus the gate potential  $V_g$  for *p*-type substrate at 77 K. Take the substrate doping concentration  $N_a$  from  $1 \times 10^{15}$  cm<sup>-3</sup> to  $2 \times 10^{18}$  cm<sup>-3</sup>, and with gate oxide thickness  $t_{ox} = 3$  nm giving threshold voltages of 40 mV to 800 mV. The gray dotted line represents the typical value at  $10^{10}$  cm<sup>-2</sup> of the fixed oxide charge concentration  $N_f$  for contemporary advanced MOSFETs [32]. The right Y axis in Fig. 2.2 gives the length scale a estimation based on  $n_s$ , and  $a \approx 1/\sqrt{\varepsilon_{s_1}}$ . For the silicon strong-coupling length scale of  $a^*_{Si} = 15.0$  nm mentioned in section 2.1, it corresponds approximately to ns at  $4 \times 10^{11}$  cm<sup>-2</sup> (Table 2.1) for single electron occupation spin lattices.

In summary, silicon is found to be a very good material in realizing spin lattices due to its considerably high strong coupling energy with length scale that are within the reach of contemporary technologies. By comparing the 2DEG concentration, which is calculated by a silicon based MOS model, a guide is given to select the appropriate length scale in order to have significantly higher electrons at the Si-SiO<sub>2</sub> interface than the fixed oxide charge concentration  $N_{f}$ .

Fig. 2.2: Inversion layer 2DEG density versus gate voltage at 77 K spanned by two doping densities. A gray dashed line plots an estimate for the fixed interface charge density  $N_{f}$ . The right axis scale gives a corresponding length scale estimate per single electron of  $a \approx 1/\sqrt{\varepsilon_{Si}}$ , with the strong coupling length scale for silicon  $a_{Si}^*$  plotted with a red dashed line [2].

Table 2.1: Two-dimensional electron gas densities in a MOSFET that correspond to those needed to achieve one-electron-per-site for a given lattice scale a.

| Lattice Length Scale <i>a</i> (nm) | 2DEG Density $n_s$ (cm <sup>-2</sup> ) |

|------------------------------------|----------------------------------------|

| 1000                               | 10 <sup>8</sup>                        |

| 100                                | 10 <sup>9</sup>                        |

| 50                                 | $4	imes 10^{10}$                       |

| 15                                 | $4	imes 10^{10}$                       |

| 10                                 | 10 <sup>12</sup>                       |

#### **CHAPTER 3**

# FABRICATION PROCESS AND DEVICE DESIGN

In this chapter, two distinct choices of forming nanostructures are introduced. Both processes take advantage of a nano-LOCOS invention developed in this work, described in section 3.2. Nano-LOCOS process provides a realistic processing route to engineer and manipulate the profile of the electrons at the Si-SiO<sub>2</sub> interface. In section 3.3, two approaches of devices isolation are compared and discussed.

#### **3.1 Nanostructure First and Nanostructure Last**

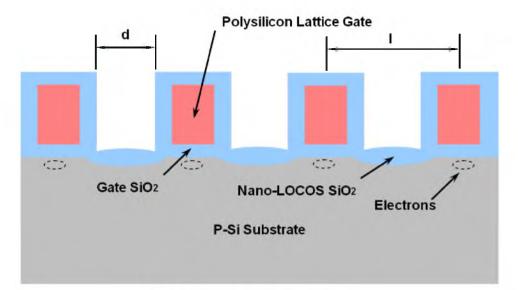

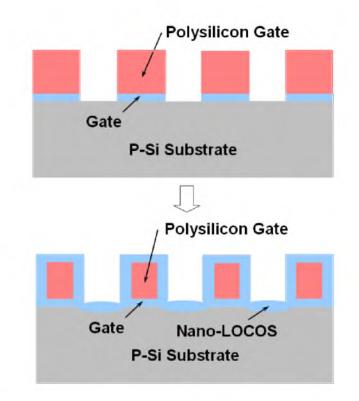

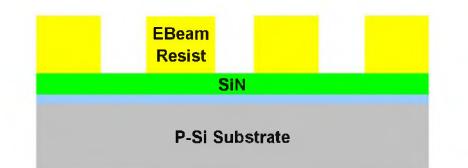

Our implementation of MOSFENS uses an NMOS transistor structure with patterned lattices at the Si-SiO<sub>2</sub> interface to connect the inversion layer electrons. A potential applied to the patterned gate electrode changes the concentration of the 2DEG. There are two choices to form the nanostructures, either before the gate stack formation (the nanostructure first) or after the gate stack formation (the nanostructure last). As schematically indicated in Fig. 3.1, for both designs, the hole size is denoted as d while the period is denoted as 1, and the gate electrode is taken to be highly-doped n-type polysilicon. The nanostructure last design has the contact holes vertically etched though the thin polysilicon gate and the initial gate oxide, and subsequently, an oxidation step is used to form smooth interface, with the resulting holes extending a depth of a few

## Nanostructure Last

## Nanostructure First

Fig. 3.1: Cross-sections of the nanostructure last design and the nanostructure first design with the hole size = d and the period = l.

nanometers into the silicon body through the inversion layer region. The nanostructure first design has the oxide obliquely extending into the silicon surface before the gate oxide formation and the lateral undulations combined with the perpendicular electric field confine the electrons near the thinnest oxide regions.

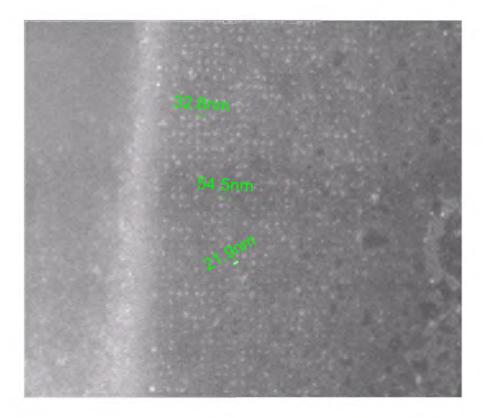

#### 3.2 Nano-LOCOS

Whether forming the nanostructures prior to or after the gate structure formation, both the nanostructure last and the nanostructure first architectures have an undulating Si-SiO<sub>2</sub> interface to confine the electrons to the sites by a perpendicular electrical field. This undulating interface is formed by the nano-LOCOS process, which was invented and developed in this work. The nano-LOCOS process plays a central role in defining a clean, sharp confining potential for the spin lattice electrons, and it grows a 3 nm oxide isolation at the open areas between the nanostructures. After oxidation, POA (post-oxidation annealing) in nitrogen is carried out to minimize the traps and the fixed charges at the Si-SiO<sub>2</sub> interface since it is essential to control the concentration of those traps and charges well below the number of the electrons bound to the sites. This process is very similar to the conventional LOCOS process [33], but it is implemented on a much smaller nanometers scale. Meanwhile, a thin gate oxide is desired to achieve a strong perpendicular electric field  $E_s$  [34], and a thin polysilicon layer is required to keep a low aspect ratio during the polysilicon RIE.

#### **3.3 Window Isolation and Mesa Isolation**

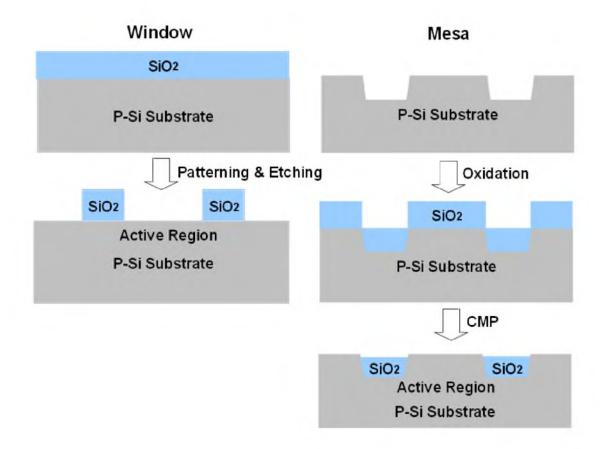

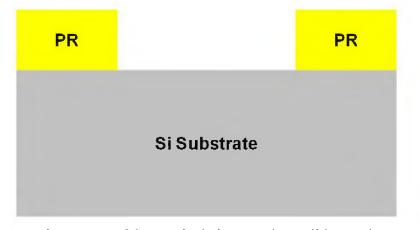

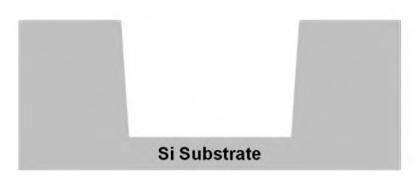

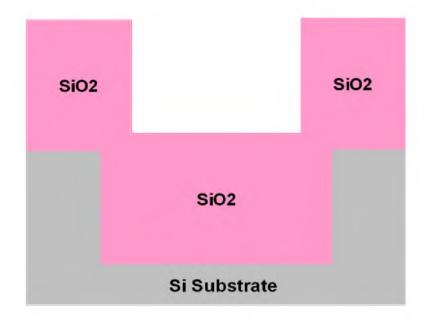

Two approaches for the isolation between the transistors are pursued in this work (Fig. 3.2). The first one is named "window isolation," and the devices are isolated by the

Fig. 3.2: Formation of the window isolation and the mesa isolation. The active region of the window isolation is lower than the oxide, while the active region of the mesa isolation is higher than the oxide in the trench.

patterned field oxide that is grown above the substrate, so the field oxide is higher than the active regions. The second one is referred to as "mesa isolation," and the devices are isolated by the oxide filled in the trenches that are etched into the substrate, so the trench oxide is lower than the active regions.

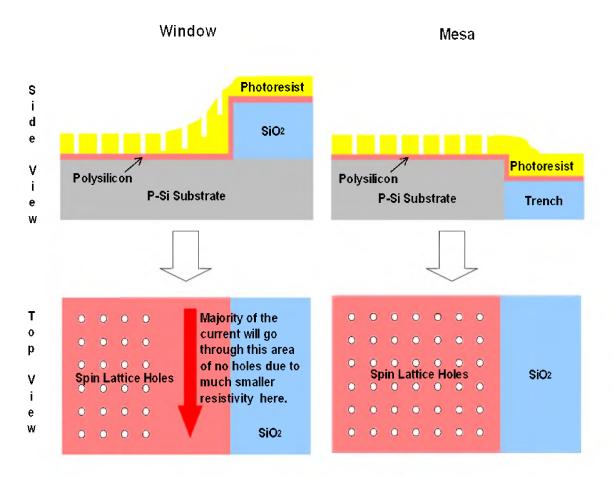

For the window isolation, the wafer is coated with the photoresist, and the photoresist covers the steps between the active regions and the isolation regions; thus, the photoresist is thicker at the corners of the active regions. It is anticipated that this thicker photoresist area could be subjected to under-exposure due to the DOF (depth of focus) limit of lithography, and the holes would not be opened all the way to the polysilicon gate beneath. After the polysilicon RIE, the active regions close to the corner will not have the holes open, and consequently the channel current will be shorted by this area of much smaller resistivity (Fig. 3.3). For the mesa isolation, the photoresist thickness inside the active regions is uniform since all the active regions are elevated above the trenches filled with oxide (Fig. 3.3); thus, the under-exposure and shortage issue could be circumvented.

It was decided to use EBL instead of optical lithography for MOSFENS spin lattice devices, and it was demonstrated that this hypothetical issue becomes invalid since the EBL system has much bigger DOF compared to the conventional optical lithography systems [35], and the step height of the window isolation (~300 nm) is well within the DOF range.

In summary, the nano-LOCOS process is designed to use the selective oxidation technique to grow thin oxide between the nanostructures. The nanostructures can be formed either before or after the polysilicon gate formation, and there are two device options: the window isolation and the mesa isolation. All these designs will be applied to the device fabrication in the following chapters.

Fig. 3.3: The step height between the active regions and the isolation regions causes underexposure, and consequently, current shortage for the window isolation but not for the mesa isolation.

#### **CHAPTER 4**

#### NMOS PROCESS DEVELOPMENT

The MOSFENS process required a basic transistor fabrication process that could accommodate the nanostructures. In this chapter, as the foundation of MOSFENS devices fabrication, an NMOS process is introduced along with its development, fabrication process flow and characterization results. In section 4.1, the mask design and the layout are introduced, followed by a step-by-step process flow and the characterization results of NMOS processes with the window isolation and the mesa isolation approaches in section 4.2 and 4.3, respectively. In section 4.4, the experimental result of the compatibility between the thin polysilicon and the nano-LOCOS process is presented and discussed.

Engineering the Si-SiO<sub>2</sub> interface topography requires several modifications to the standard MOSFET gate stack in order to implement MOSFENS devices. In a typical NMOS process, the gate oxide is deposited on the silicon substrate where the channel is to be formed, and then the POA is carried out to minimize the traps and the fix charges at the interface. The gate stack continues with a doped polysilicon film and then a silicide layer. These layers are patterned to define the gate features, which are later used as the mask for the self-aligned ion implantation for the source and drain doping.

#### 4.1 Mask Layout

The mask is designed to have eight rows by eight columns, a total sixty four die on a four inch wafer. Each die contains sixteen transistors with the different gate width, and

along with the testing structures of resistivity, contacts and magnetism (Fig. 4.1).

The mask includes five levels. Level one is to define the source and the drain area, and level two is to define the polysilicon gate. Level three is to form the first contact holes on the substrate which will be etched to go through the SOG (spin on glass) layer and the field oxide underneath. Level four is to form the second contact holes on the sources, the drains and the polysilicon gates. Finally, level five is to define the aluminum interconnections and the contact pads.

Fig. 4.1: Mask layout of a die

### 4.2 NMOS Window Isolation Process Flow

#### and Characterization

In this section, the process flow of the NMOS window isolation is presented followed by the characterization results.

#### 4.2.1 NMOS Window Isolation Process Flow

The process steps of the NMOS window isolation for four inch wafers are described step-by-step below. Some important changes made for the migration from two inch wafers are also introduced and discussed.

Step 1 is wafer start. Four inch p type CZ (Czochralski) silicon substrates with boron dopants and <100> crystal orientation were used. The resistivity of the substrates is between 1 to 5  $\Omega$ -cm.

Step 2 is field oxide growth. A 370 nm field oxide is thermally grown in a lateral oxidation furnace at  $1000^{\circ}$ C for 70 minutes by using the wet oxidation technique.

Step 3 is mask one lithography. The purpose of this step is to define the active regions and the nonactive regions. For the window isolation, the active regions will be selectively exposed without the photoresist protection. A negative photoresist is used, and Appendix B details the process steps.

Step 4 is BOE (buffered oxide etchant) etching. The wafer is dipped in 1:6 BOE agent in a wet bench at room temperature for 6 minutes to remove the field oxide at the opened active regions. The etching rate is approximately 92 nm per minute at room temperature. After the BOE etching, the active regions are measured for the oxide thickness on an optical thickness measurement system to make sure there are no oxide

residuals. It is critical to make sure there is no oxide left in the open active regions. Since any oxide residuals will be added to the gate oxide, which will cause an increase in the overall gate oxide thickness, and consequently shifts the actual device performance. Since it is impossible for the microscopic inspection to discover such subtle oxide residuals in nanometers scale, sufficient over-etching and the optical thickness measurement are applied to make sure the oxide has been completely removed. The photoresist is then stripped in acetone and IPA (isopropyl alcohol).

Step 5 is DHF etching. The wafer is dipped in 1:104 DHF (diluted hydrofluoric acid) at room temperature for 3 minutes prior to the gate oxidation to remove the native oxide. It is known that a thin native oxide will grow within a matter of seconds upon exposure to an oxygen-containing ambient or an oxidizing solution. The etching rate of 1:104 DHF at room temperature for 1000°C grown wet oxide is approximately 3.9 nm per minute.

Step 6 is gate oxide growth and annealing. A 3 nm gate oxide is grown in a lateral oxidation furnace at 800°C for 8 minutes by using the dry oxidation technique. After the oxidation, the furnace is ramped up to 1050°C in ambient nitrogen, and stays at 1050°C for 10 minutes to anneal the fixed oxide charges at the Si-SiO<sub>2</sub> interface (see section 4.3 for the details).

Step 7 is polysilicon deposition. A 40 nm polysilicon film is deposited at 630 C with a slow deposition rate around 4 nm per minute in a lateral LPCVD (low pressure chemical vapor deposition) furnace (see section 5.2 for the details). The polysilicon thickness will be later reduced to 15 nm after the phosphorous doping.

Step 8 is mask two lithography. The purpose of this step is to pattern the gates. A positive photoresist is used, and Appendix B details the process steps. Mask two has

transistors with a gate width of 2  $\mu$ m, 3  $\mu$ m and 5  $\mu$ m. For small features like 2  $\mu$ m, the exposure time needs to be short enough (2.5 seconds) to ensure the features can be transferred successfully.

Step 9 is DHF etching. Once the wafer has completed the polysilicon deposition, it is exposed to the ambient, and the native oxide starts to grow on the surface of the polysilicon. For the polysilicon etching recipe with high selectivity to the oxide, the unevenly grown native oxide on the surface leads to poor uniformity during the polysilicon etching. Modern RIE systems have a pre-clean chamber to remove the native oxide before etching the polysilicon in another chamber. However, this function is not available for the LAM490 system in the Nanofab at The University of Utah; therefore, DHF is used instead to remove the native oxide. The wafer is dipped in 1:104 DHF at room temperature for 3 minutes. With an etching rate of the wet oxide at 3.9 nm per minutes, it is sufficient to remove the native oxide, which normally has the thickness of 2 to 3 nm.

Step 10 is polysilicon RIE. In this step, the polysilicon gates are patterned on the LAM490 etching system. The etching process has an etching rate of 20 nm per minute, an approximately 77 degree sidewall angle, and greater than 125 selectivity over the oxide (see section 4.3 for the details). The photoresist is stripped in acetone and IPA after the etching. The thickness of the polysilicon is so thin it is difficult to detect the polysilicon residuals by microscopic inspection. However, the polysilicon residuals will lead to shorts between the gates and the sources/drains, and cause the devices to fail. The field oxide is beneath the etched polysilicon, so once the polysilicon is cleared, the field oxide will be exposed. After the polysilicon etching, the etched regions are measured on

an optical thickness measurement system by using an oxide measurement recipe. If the GOF (goodness of fit) of the measurement is high, it indicates there are polysilicon residuals, and additional etching is needed. If the GOF is close to zero, it means that there are no polysilicon residuals, and the field oxide is fully exposed.

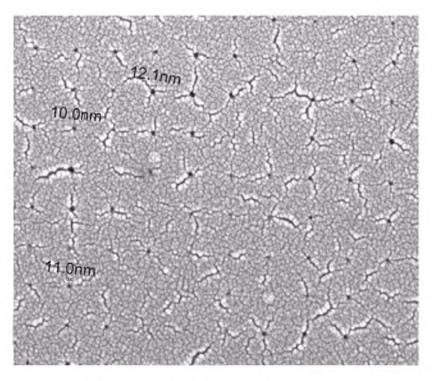

Step 11 is phosphorous doping. After the gate patterning, the polysilicon gates and the active regions are doped with phosphorous in a lateral diffusion furnace, and the gates act as the self-aligned mask to prevent the doping from going through the channel beneath. Two inch wafers are loaded and unloaded into a manual diffusion furnace at 1000°C without any temperature ramping cycle. Four inch wafers use an automatic diffusion furnace, and they are loaded and unloaded at 500°C with a temperature ramping cycle to 1000°C. The thickness of the polysilicon has been increased from 15 nm for two inch wafers to 40 nm for four inch wafers since the ramping cycle also consumes the polysilicon. The consumption of the polysilicon by the doping cycle was investigated (Table 4.1). There are three solid phosphorous doping wafers available in the furnace, and the silicon wafers are placed next to each doping wafer. Apparently longer diffusion time generates lower sheet resistance, and thicker phosphosilicate oxide. On average, 20 minutes diffusion can grow about 25 nm phosphosilicate oxide, and the phosphosilicate oxide thickness is measured by the ellipsometer thickness measurement system.

Step 12 is phosphosilicate glass removal. During the phosphorous doping, a layer of phosphosilicate glass is formed on the surface of the polysilicon. After the phosphorous doping, the wafer is dipped in 1:104 DHF at room temperature for 3 minutes to remove the phosphosilicate glass. The etching rate is greater than 20 nm per minute. Final field oxide thickness is measured after the phosphosilicate glass removal. After the filed oxide

is grown, the field oxide is thinned during the later steps like all the DHF etching steps, the poly gate etching step, the phosphorous doping step and the phosphosilicate glass removal step. Table 4.2 lists the field oxide thickness measured at each major step for the NMOS window isolation process.

Step 13 is SOG deposition. The SOG is used as the interlayer dielectrics. The ACCUGLASS SOG by Honeywell is applied to the wafer at 2000 RPM (rotation per minute) for 40 seconds, then the wafer is baked on the hotplate at 125°C for 3 minutes. Then the wafer is loaded into the Lindberg Blue burn-box at 250°C, and the temperature is ramped up to 400°C. At 400°C the wafer is hard-baked with nitrogen flow at 1 slpm for 60 minutes.

| Split                                | Sheet Resistance Before<br>Doping Sheet Resistance | Sheet Resistance After<br>Doping | Phosphosilicate<br>Oxide |  |

|--------------------------------------|----------------------------------------------------|----------------------------------|--------------------------|--|

| 10 minutes Wafer 1                   | 34.4 Ohm/square                                    | 915.1 Ohm/square                 | 11.0 nm                  |  |

| 10 minutes Wafer 2   35.3 Ohm/square |                                                    | 724.8 Ohm/square                 | 12.1 nm                  |  |

| 10 minutes Wafer 3                   | 34.0 Ohm/square                                    | 715.7 Ohm/square                 | 12.5 nm                  |  |

| 20 minutes Wafer 1                   | 34.4 Ohm/square                                    | 271.8 Ohm/square                 | 22.5 nm                  |  |

| 20 minutes Wafer 2                   | 38.1 Ohm/square                                    | 201.6 Ohm/square                 | 25.0 nm                  |  |

| 20 minutes Wafer 3                   | 22.2 Ohm/square                                    | 194.8 Ohm/square                 | 26.0 nm                  |  |

Table 4.1: Four inch wafers polysilicon doping experiment results

Table 4.2: The field oxide thickness of the NMOS window isolation

| Step                                    | Wafer 1  | Wafer 2  | Wafer 3  |

|-----------------------------------------|----------|----------|----------|

| After the field oxide growth            | 377.2 nm | 374.5 nm | 377.1 nm |

| After the gate polysilicon RIE          | 364.1 nm | 354.9 nm | 353.7 nm |

| After the phosphosilicate glass removal | 278.9 nm | 261.6 nm | 271.2 nm |

Step 14 is mask three lithography. The purpose of this step is to create contact holes from the metal contact pads to the substrate; the contact holes act as body contacts for the transistors. Since the dialectics (SOG + field oxide) thicknesses at the gates, and the active regions and the isolation regions are different, if all the contact holes in those areas are open at the same time, either the holes at the gates and the active regions are overetched, or the holes at the isolation regions are under-etched. So it is necessary to open the contact holes at the different regions by using different masks. A positive photoresist is used at this step, and Appendix B details the process steps.

Step 15 is BOE etching. The wafer is bathed in 1:6 BOE at room temperature for 4.5 minutes. After the etching, an optical thickness measurement system is used to measure the oxide thickness at the open features to decide whether there are oxide residuals or not. The reading of the measurements should be close to zero. The photoresist is then stripped in acetone and IPA.

Step 16 is mask four lithography. The purpose of this step is to create the contact holes at the gates and the active regions. A positive photoresist is used in this step, and Appendix B details the process steps.

Step 17 is BOE etching. The wafer is bathed in 1:6 BOE at room temperature for 5.5 minutes. After the etching, an optical thickness measurement system is used to measure the oxide thickness at the open features to decide whether there are oxide residuals or not. The reading of the measurements should be close to zero. The photoresist is then stripped in acetone and IPA.

Step 18 is DHF etching. The wafer is dipped in 1:104 DHF at room temperature for 3 minutes to remove the native oxide before the aluminum sputtering. Before the metal is

deposited into the contact holes, it is necessary to ensure that the exposed silicon surface is as free as possible of contaminations and the native oxide. The native oxide can represent an impediment to the current that flows through the contact interface, resulting in high resistance for the ohmic contacts. The native oxide layer can grow thicker in 30 to 60 minutes if the silicon is exposed to the atmosphere at room temperature [36]. Consequently, the native oxide layers must be removed, and the metal must be deposited quickly enough after the pre-metal cleaning that the native oxide does not have enough time to regrow.

Step 19 is aluminum sputtering. A 500 nm aluminum (with 1 wt% silicon) is deposited by using the Denton Discovery 18 Sputtering System at  $2 \times 10^{-6}$  torr pressure, 100W RF power with argon flow for 20 minutes. The deposition rate is about 25 nm per minute. The thickness of the aluminum film is measured by the Tencor P-10 Profilometer.

Step 20 is mask five lithography. The purpose of this step is to define the aluminum interconnections between the gates, the sources, the drains and the substrate. A positive photoresist is used, and Appendix B details the process steps.

Step 21 is aluminum etching. The aluminum is etched in an etchant mixed with phosphoric acid, nitric acid, acetic acid, and DI water at a ratio of 16:1:1:2 at room temperature for 5 minutes. The photoresist is then stripped in acetone and IPA.

Step 22 is contact annealing. In this step, the contacts are annealed in the Lindberg lateral furnace at 400°C for 40 minutes with a forming gas (2% hydrogen, 98% argon). Besides, this annealing step with a forming gas can reduce the level of the interface trap density,  $D_{it}$  (see Appendix A).

Fig. 4.2 shows an image of a die on a completed device wafer.

Fig. 4.2: Image of a die of an NMOS window isolation device wafer

#### 4.2.2 NMOS Window Isolation Characterization

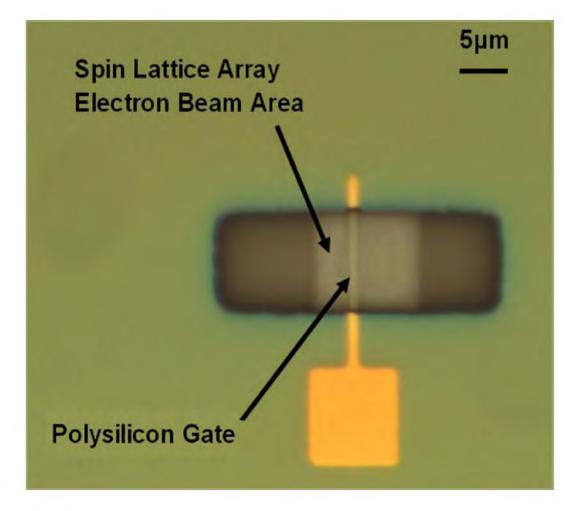

The NMOS window isolation transistors were fabricated by using both the two inch and the four inch NMOS processes. Fig. 4.3 shows the image of a fabricated NMOS transistor.

The  $V_{ds}$ - $I_{ds}$  characteristics are shown in Fig. 4.4 and Fig. 4.5, and this lays the foundation for the future MOSFENS device fabrication.

Fig. 4.3: Top view of a polysilicon gate NMOS window isolation transistor

Fig. 4.4: Two inch nanostructure last window isolation NMOS  $V_{ds}$ -  $I_{ds}$

Fig. 4.5: Four inch nanostructure last window isolation NMOS  $V_{ds}$ -  $I_{ds}$

#### **4.3 NMOS Mesa Isolation Process Flow**

#### and Characterization

In this section, the process flow of the NMOS mesa isolation is presented, followed by the characterization results.

#### 4.3.1 NMOS Mesa Isolation Process Flow

The process steps of the NMOS mesa isolation for the four inch wafers are described step-by-step below.

Step 1 is wafer start. Four inch *p* type CZ (Czochralski) silicon substrates with boron dopants and <100> crystal orientation are used. The resistivity of the substrates is between 1 to 5  $\Omega$ -cm.

Step 2 is DHF sip. The wafer is dipped in 1:104 DHF at room temperature for 2 minutes to remove the native oxide.

Step 3 is mask one lithography. The purpose of this step is to define the active regions and the nonactive regions (the trenches) as shown in Fig. 4.6. A positive photoresist is used, and Appendix B details the process steps.

Step 4 is silicon trench RIE. After mask one lithography the active regions are protected by the photoresist. The wafer is etched by the LAM490 system using  $SF_6$  gas at an 80 sccm flow rate with inert helium gas at a 120 sccm flow rate. The chamber pressure is set at 2 torr and the RF (radio frequency) top power is set at 200W. The depth of the trenches is about 290 nm after 45 seconds of etching. Fig. 4.7 shows the cross-section view post silicon trench RIE. The photoresist is then stripped in acetone and IPA.

Step 5 is field oxide growth. A 370 nm field oxide is thermally grown in a lateral oxidation furnace by using the wet oxidation technique at  $1000^{\circ}$ C for 70 minutes to fill the trenches (Fig. 4.8).

Step 6 is CMP (chemical mechanical polishing): The CMP technique is used to flatten the trenches (Fig. 4.9). A silica-based oxide slurry, DCM-D37 with 1:1 dilution

Fig. 4.6: NMOS mesa isolation: mask one lithography

Fig. 4.7: NMOS mesa isolation: silicon trench via RIE

Fig. 4.8: NMOS mesa isolation: field oxide growth

Fig. 4.9: NMOS mesa isolation: CMP

with DI water on a dual stacked X-Y grid-grooves polishing pad is used. The process has a polishing rate of approximately 135 nm per minute on  $1000^{\circ}$ C grown wet oxide. The process uses 50 RPM on the chuck and the platen rotation, 5 psi downforce and the slurry flowrate is 175 ml per minute (see section 5.5).

An optical thickness measurement tool is used to measure the oxide remaining on the active regions after CMP. The purpose is to make sure the oxide on the active region particles, metal contaminants, all undesirable for the remaining steps; therefore, the wafer is subjected to the post-CMP cleaning steps to return the wafer surface to an acceptable cleanliness level. For the post-CMP cleaning, 1:104 DHF solution at room temperature is used to remove the slurry particles and the metallic contaminations.

Step 7 is sacrifice oxidation. A 30 nm wet oxide is grown to get rid of the CMP introduced defects. The wafer is loaded and unloaded at 500°C, and the oxidation is performed at 1000°C for 2 minutes.

Step 8 is DHF etching. The wafer is dipped in 1:104 DHF at room temperature for 12 minutes to remove the sacrifice oxide. The reason for using DHF not BOE, is to have a better control of over-etching. It is critical to completely remove the sacrifice oxide on the active regions before the gate oxidation, but it is also very important to reduce the amount of over-etching as much as possible to minimize the step height. As mentioned above, any residual oxide before the gate oxidation will be added to the 3 nm gate oxide, which will cause an increase in overall gate oxide thickness which would cause shifts between the predicted and the actual performance. Since it is impossible for microscopic inspection to detect the nanometer scales oxide residuals, an optical thickness measurement is applied to make sure the oxide thickness readings on the future gate

regions are zero.

From the next step (the gate oxidation) on, all the steps are exactly the same as the ones of the NMOS window isolation process of section 4.2.

Table 4.3 and 4.4 show the field oxide thickness measured at each step and the final step height before the EBL. As shown above, the CMP introduced step height is actually much smaller compared to the step height generated by the sacrifice oxide removal and the gate polysilicon RIE. The reason is that both steps use sufficient over-etching to make sure the oxide and the polysilicon are cleared.

Table 4.3: Trench oxide thickness of the NMOS mesa isolation

| Step                                | Wafer 1  | Wafer 2  | Wafer 3  |

|-------------------------------------|----------|----------|----------|

| After Trench Oxide Growth           | 378.3 nm | 387.8 nm | 397.0 nm |

| After CMP                           | 293.9 nm | 307.0 nm | 311.6 nm |

| After Gate Polysilicon RIE          | 223.0 nm | 243.9 nm | 219.2 nm |

| After Phosphosilicate Glass Removal | 181.6 nm | 200.7 nm | 175.6 nm |

Table 4.4: Step height of the NMOS mesa isolation

| Step                                  | Wafer 1 Wafer 2 |           | Wafer 3   |

|---------------------------------------|-----------------|-----------|-----------|

| After STI Trench RIE (= Trench Depth) | -327.3 nm       | -323.2 nm | -327.6 nm |

| After CMP                             | -33.4 nm        | -16.2 nm  | -16.0 nm  |

| After Sacrifice Oxide Removal         | -120.5 nm       | -74.4 nm  | -78.4 nm  |

| After Gate Polysilicon RIE            | -163.7 nm       | -159.6 nm | -129.4 nm |

| After Phosphosilicate Glass Removal   | -173.1 nm       | -174.5 nm | -192.2 nm |

#### 4.3.2 NMOS Mesa Isolation Characterization

The NMOS mesa isolation transistors were also fabricated, but all the transistors failed. The measurement results are plotted in Fig. 4.10.

The  $V_{ds}$  vs.  $I_{ds}$  characteristics of the mesa isolation transistors show that the channel current does not change when the gate voltage varies, and there is no isolation between the gates and the drains/sources. However, the window isolation transistors show good

Fig. 4.10: Four inch NMOS mesa isolation characteristics

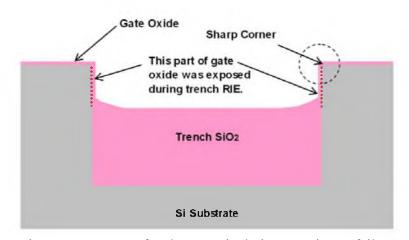

isolation between the gates and the drains/sources, and these transistors are working fine. Since the window isolation transistors and the mesa isolation transistors grow the gate oxide and the gate polysilicon in the same batch, this indicates that the gate oxide and the gate polysilicon have no problems. Hence, for the mesa isolation, we conclude that the gate polysilicon is shorted with the substrate caused by the following mechanisms. Firstly, the sharp corners at the top of the trenches generate a higher electrical field [37], and it tends to grow thinner oxide [38], which is susceptible to break-down and consequently leads to a short between the gate polysilicon and the substrate (Fig. 4.11). Secondly, the substrate of the upper portion of the trenches was exposed during the trench RIE etching, and it was subjected to plasma damage. Thus, the gate oxide grown there could contain more traps and defects, and consequently lead to oxide break-down and a short between the gate polysilicon and the substrate (Fig. 4.11).

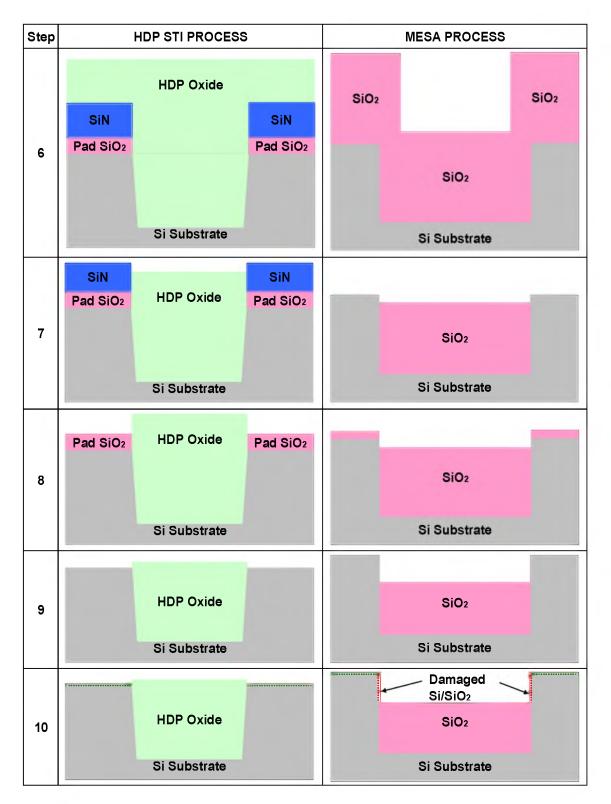

To solve this issue, a trench filling technique with HDP (high density plasma) oxide [39] needs to be used. The comparison between a standard STI process using HDP filling and the mesa isolation process are schematically illustrated in Fig. 4.12 and Fig. 4.13.

Fig. 4.11: Reasons for the mesa isolation transistors failure

Fig. 4.12: Comparison between the mesa process and a STI process, steps 1 to 5

Fig. 4.13: Comparison between the mesa process and a STI process, steps 6 to 10

#### 4.4 Thin Polysilicon Gate and Nano-LOCOS

#### **Compatibility Experiment**

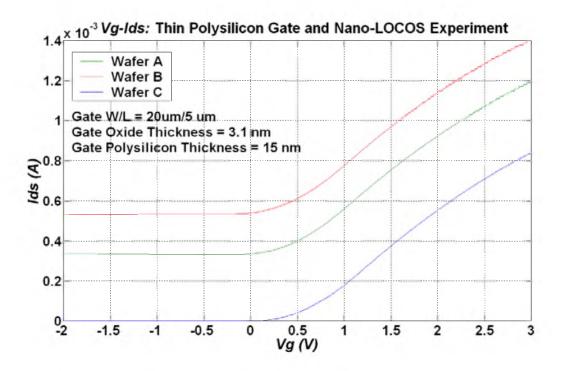

As mentioned above, both the nanostructure last and the nanostructure first have an undulating  $Si-SiO_2$  interface to confine the electrons to the sites, which will be created by the nano-LOCOS process. An experiment was carried out to examine the compatibility between the thin gate polysilicon and the nano-LOCOS process.

Table 4.5 shows the information of the experimental splits. Wafer C was processed with all the steps, and wafer A did not have the in-situ POA after the nano-LOCOS. Wafer B did not have nano-LOCOS and the following in-situ POA, and wafer D only has the gate oxide and the unthinned polysilicon gate electrode.

The transistors of wafer D failed due to contact failure. As shown in Fig. 4.14, the transistors of wafer A, B and D are functioning but have significant differences in the sub-threshold current. Single oxidation and annealing split, wafer B has the biggest subthreshold channel current, while double oxidation and single annealing split, wafer A has a slightly reduced sub-threshold current. The split of double oxidation and double annealing split, wafer C has the smallest sub-threshold current in the range of 1  $\mu$ A.

| Step | Wafer                         | Α            | В            | С            | D            |

|------|-------------------------------|--------------|--------------|--------------|--------------|

| 1    | 3 nm gate oxide growth        | $\checkmark$ | $\checkmark$ | $\checkmark$ |              |

| 2    | In-situ POA                   | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| 3    | 40 nm gate polysilicon growth | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| 4    | 25 nm polysilicon thinning    | $\checkmark$ | $\checkmark$ | $\checkmark$ | ×            |

| 5    | Nano-LOCOS                    | $\checkmark$ | ×            | $\checkmark$ | ×            |

| 6    | In-situ POA                   | ×            | ×            | $\checkmark$ | ×            |

Table 4.5: Thin polysilicon gate and the nano-LOCOS compatibility experiment splits

Fig. 4.14: Thin polysilicon gate and the nano-LOCOS compatibility experiment:  $V_g$ - $I_{ds}$