# DESIGN AND OPTIMIZATION OF ASYNCHRONOUS NETWORK-ON-CHIP

by

Junbok You

A dissertation submitted to the faculty of The University of Utah in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Department of Electrical and Computer Engineering

The University of Utah

December 2011

Copyright  $\bigodot$  Junbok You 2011

All Rights Reserved

### The University of Utah Graduate School

## STATEMENT OF THESIS APPROVAL

| This dissertation of                 | Junbok You                                                   |                                           |

|--------------------------------------|--------------------------------------------------------------|-------------------------------------------|

| has been approved by th              | he following supervisory committee memb                      | pers:                                     |

| Kenneth S. Steve                     | <u>ns</u> , Chair                                            | $\frac{03/02/2011}{\text{Date Approved}}$ |

| Erik Brunvand                        | , Member                                                     | 03/02/2011<br>Date Approved               |

| Ganesh Gopalakri                     | <b>ishnan</b> , Member                                       | 03/02/2011<br>Date Approved               |

| Chris Myers                          | , Member                                                     | 03/03/2011<br>Date Approved               |

| Priyank Kalla                        | , Member                                                     | 03/02/2011<br>Date Approved               |

| and by<br>the Department of <b>F</b> | <u>Gianluca Lazzi</u><br>Electrical and Computer Engineering | , Chair of                                |

and by Charles A. Wight, Dean of the Graduate School.

#### ABSTRACT

The bandwidth requirement for each link on a network-on-chip (NoC) may differ based on topology and traffic properties of the IP cores. Available bandwidth on an asynchronous NoC link will also vary depending on the wire length between sender and receiver. This work explores the benefit to NoC performance, area, and energy when this property is used to optimize bandwidth on specific links based on its bandwidth required by a target SoC design.

Three asynchronous routers were designed for implementing of asynchronous NoCs. Simple routing scheme and single-flit packet format lead to performance- and areaefficient router designs. Their performance was evaluated in consideration of link wire delay.

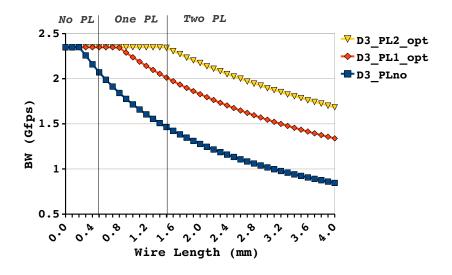

Comprehensive analysis of pipeline latch insertion in asynchronous communication links is performed in regard to link bandwidth. Optimal placement of pipeline latch for maximizing benefit to increase of bandwidth is described.

Specific methods are proposed for performance, area and energy optimization, respectively. Performance optimization is achieved by increasing bandwidth of high trafficked and high utilized links in an NoC, as inserting pipeline latches in those links. Through decrease of bandwidth of links with low traffic and low utilization by halving data-path width, reduction of wire area of an NoC is accomplished. Energy optimization is performed using wide spacing between wires in links with high energy consumption.

An analytical model for asynchronous link bandwidth estimation is presented. It is utilized to deploy NoC optimization methods as identifying adequate links for each optimization method.

Energy and latency characteristics of an asynchronous NoC are compared to a similarly-designed synchronous NoC. The results indicate that the asynchronous network has lower energy, and link-specific bandwidth optimization has improved NoC performance.

Evaluation of proposed optimization methods by employing to an asynchronous NoC shows achievements of performance enhancement, wire area reduction and wire energy saving.

## CONTENTS

| AB  | BSTRACT                                                      | iii             |

|-----|--------------------------------------------------------------|-----------------|

| LIS | ST OF FIGURES                                                | viii            |

| LIS | ST OF TABLES                                                 | xi              |

| CH  | IAPTERS                                                      |                 |

| 1.  | INTRODUCTION                                                 | 1               |

|     | 1.1 Asynchronous Network-on-Chip                             | 2               |

|     | 1.2 Related Work                                             | 4               |

|     | 1.3 Motivation                                               | 6               |

|     | 1.4 Dissertation Structure                                   | 9               |

|     | 1.5 Contributions                                            | 9               |

| 2.  | ASYNCHRONOUS NOC DESIGN                                      | 11              |

|     | 2.1 Asynchronous Router Module Designs                       | 12              |

|     | 2.1.1 Switch Module Design                                   | 13              |

|     | 2.1.2 Merge Module Design                                    | 15              |

|     | 2.1.3 Asynchronous Circuit Design Methodology                | 17              |

|     | 2.2 Asynchronous Router Design                               | 19              |

|     | 2.2.1 Router Performance Evaluation                          |                 |

|     | with Link Wire Length                                        | 22              |

|     | 2.2.1.1 Performance Evaluation of Asynchronous Router D1     | 23              |

|     | 2.2.1.2 Performance Evaluation of Asynchronous Router D2     | $25 \\ 27$      |

|     | 2.2.1.3 Performance Evaluation of Asynchronous Router D3     | 27              |

| 3.  | PIPELINE LATCH IN ASYNCHRONOUS NOC                           | <b>29</b>       |

|     | 3.1 Design of 2-phase Linear Controller                      | 29              |

|     | 3.2 Pipeline Latch Impact on Link Bandwidth                  | 29              |

|     | 3.3 Optimal Position of One Pipeline                         |                 |

|     | Latch Placement                                              | 32              |

|     | 3.3.1 Optimal Position of One Pipeline Latch                 |                 |

|     | with Router D1                                               | 33              |

|     | 3.3.1.1 Maximum Bandwidth Range of D1_PL1<br>with Optimal PL | 35              |

|     | 3.3.1.2 Estimation of Optimal PL Position in D1_PL1          | $\frac{35}{36}$ |

|     | 3.3.2 Optimal Position of One Pipeline Latch                 | 00              |

|     | with Router D2                                               | 39              |

|    | 3.3.2.1 Maximum Bandwidth Range of D2_PL1                                                                             |              |

|----|-----------------------------------------------------------------------------------------------------------------------|--------------|

|    | with Optimal PL                                                                                                       | 40           |

|    | 3.3.2.2 Estimation of Optimal PL Position in D2_PL1                                                                   | 40           |

|    | 3.3.3 Optimal Position of One Pipeline Latch                                                                          |              |

|    | with Router D3                                                                                                        | 43           |

|    | 3.3.3.1 Maximum Bandwidth Range with Optimal                                                                          |              |

|    | PL in D3_PL1                                                                                                          | 43           |

|    | 3.3.3.2 Estimation of Optimal PL Position with Router D3                                                              | 44           |

|    | 3.3.4 Results of One Pipeline Latch Insertion                                                                         | 44           |

|    | 3.4 Optimal Positions of Two Pipeline                                                                                 |              |

|    | Latches Placement                                                                                                     | 47           |

|    | 3.4.1 Optimal Position of Two Pipeline Latch                                                                          | . –          |

|    | with Router D1                                                                                                        | 47           |

|    | 3.4.2 Optimal Position of Two Pipeline Latches                                                                        | •            |

|    | with Router D2                                                                                                        | 52           |

|    | 3.4.3 Optimal Position of Two Pipeline Latches                                                                        | F 4          |

|    | with Router D3                                                                                                        | 54           |

|    | 3.5 Link BW Comparison with Different                                                                                 | FF           |

|    | PL Configurations                                                                                                     | 55           |

|    | 3.6 Summary                                                                                                           | 58           |

| 4. | ASYNCHRONOUS NOC OPTIMIZATON                                                                                          | 60           |

|    | 4.1 Analytical Model for Link BW Estimation                                                                           | 60           |

|    | 4.2 Performance-Critical Link Optimization:                                                                           |              |

|    | PL Insertion                                                                                                          | 68           |

|    | 4.3 Area Critical Link Optimization:                                                                                  |              |

|    | Narrow Data-Path                                                                                                      | 71           |

|    | 4.4 Energy-Critical Link Optimization:                                                                                |              |

|    | Double Spacing                                                                                                        | 78           |

|    | 4.5 Summary                                                                                                           | 79           |

| 5. | EVALUATION                                                                                                            | 81           |

| э. |                                                                                                                       |              |

|    | 5.1 Evaluation Methodologies                                                                                          | 81           |

|    | 5.2 Evaluation of Asynchronous NoC                                                                                    |              |

|    | with MPEG4 SOC                                                                                                        | 82           |

|    | 5.2.1 Synchronous Router Design                                                                                       | 82           |

|    | 5.2.2 Comparison of Asynchronous and pSELF NoC                                                                        |              |

|    | with MPEG4 Design                                                                                                     | 83           |

|    | 5.3 TI Design                                                                                                         | 91           |

|    | 5.3.1 Asynchronous NoC for TI Design                                                                                  | 91<br>07     |

|    | 5.3.2 Asynchronous NoC Optimization for TI Design                                                                     | 97<br>07     |

|    | 5.3.2.1 Performance-critical Link Optimization for TI Design<br>5.3.2.2 Area-critical Link Optimization for TI Design | 97<br>102    |

|    | 5.3.2.2 Area-critical Link Optimization for TI Design<br>5.3.2.3 Energy-critical Link Optimization for TI Design      | 102<br>106   |

|    | 5.3.2.4 Results of Optimized NoCs for TI Design                                                                       | $100 \\ 107$ |

|    | · · · ·                                                                                                               | 107          |

|    | 5.4 Summary                                                                                                           | 114          |

| 6. | CONCLUSION AND FUTURE WORK           | 113 |

|----|--------------------------------------|-----|

|    | 6.1 Conclusion       6.2 Future Work |     |

| BE | FERENCES                             |     |

| пĿ |                                      | Т   |

# LIST OF FIGURES

| 1.1  | Typical asynchronous handshake protocol                                                                     | 3  |

|------|-------------------------------------------------------------------------------------------------------------|----|

| 1.2  | Router dynamic energy per flit, including idle-cycles, with various flit transfer rates                     | 3  |

| 1.3  | Link wire length effect on asynchronous communication links through-<br>put compared with synchronous links | 6  |

| 2.1  | Architecture of a three-port asynchronous router                                                            | 11 |

| 2.2  | Design of switch module.                                                                                    | 13 |

| 2.3  | Timing diagram of 2-to-4 phase converter                                                                    | 14 |

| 2.4  | Petri-Net specification of 4-phase linear controller.                                                       | 14 |

| 2.5  | Circuit implementation of 4-phase linear controller                                                         | 14 |

| 2.6  | Design of merge module                                                                                      | 15 |

| 2.7  | Design of MUTEX.                                                                                            | 16 |

| 2.8  | Petri-Net specification of merge controller.                                                                | 16 |

| 2.9  | Implementation of merge controller                                                                          | 17 |

| 2.10 | Asynchronous circuit design flow                                                                            | 18 |

| 2.11 | Router D1                                                                                                   | 19 |

| 2.12 | Router D2                                                                                                   | 19 |

| 2.13 | Router D3                                                                                                   | 20 |

| 2.14 | Handshake cycles in asynchronous communication link                                                         | 22 |

| 2.15 | Handshake cycles in D1 router.                                                                              | 23 |

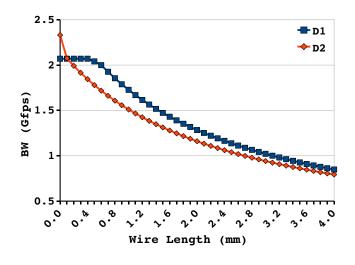

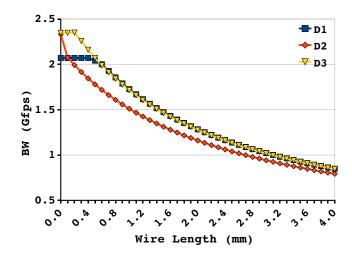

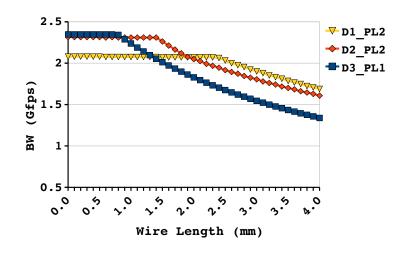

| 2.16 | Impact of link wire delay on link BW with router D1                                                         | 25 |

| 2.17 | Handshake cycles in D2 router                                                                               | 26 |

| 2.18 | Impact of link wire delay on link BW with router D1 and router D2                                           | 26 |

| 2.19 | Handshake cycles in router D3 design                                                                        | 27 |

| 2.20 | Impact of link wire delay on link BW with router D1, D2 and D3                                              | 28 |

| 3.1  | Design of 2-phase linear controller                                                                         | 30 |

| 3.2  | PL insertion and handshake cycles                                                                           | 30 |

| 3.3  | Link of D1 router with a PL: $D1_PL1$                                                                       | 31 |

| 3.4  | Impact of link wire delay on link BW with router D1 and one PL 3                                |    |  |

|------|-------------------------------------------------------------------------------------------------|----|--|

| 3.5  | Wire length of $hc_2$ and $hc_3$ in $D1_PL1$                                                    |    |  |

| 3.6  | PL impact on link throughput in total 2.0 mm link wire                                          |    |  |

| 3.7  | PL impact on link throughput in total 1.0 mm link wire                                          | 36 |  |

| 3.8  | Link BW improvement in a link with D1 routers and one optimal PL                                | 39 |  |

| 3.9  | Link of D2 router with one PL: <i>D2_PL1</i>                                                    | 40 |  |

| 3.10 | Link BW improvement of $D2\_PL1$ with optimal PL placement                                      | 42 |  |

| 3.11 | Link of D3 router with a PL: $D3_PL1$                                                           | 43 |  |

| 3.12 | Link BW improvement of $D3_PL1$                                                                 | 45 |  |

| 3.13 | Link BW of three PLno and three PL1_opt links.                                                  | 46 |  |

| 3.14 | Link of D1 router with two PLs: <i>D1_PL2</i>                                                   | 47 |  |

| 3.15 | Three PL2 Cases depending on Total WL.                                                          | 49 |  |

| 3.16 | Link BW improvement of a link with router D1 and two optimal posi-<br>tioned PLs                | 51 |  |

| 3.17 | Link of D2 router with two PLs: <i>D2_PL2</i>                                                   | 52 |  |

| 3.18 | Link BW improvement with two optimal PLs in D2 link                                             | 53 |  |

| 3.19 | Link of D3 router with two PLs: $D3_PL2$                                                        | 54 |  |

| 3.20 | Link BW improvement of $D3_PL2$                                                                 | 55 |  |

| 3.21 | BW comparison of three links of <i>TYPE 2</i>                                                   | 56 |  |

| 3.22 | BW comparison of three links of <i>TYPE 3</i>                                                   | 58 |  |

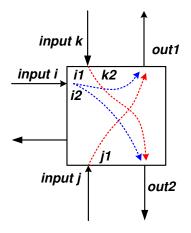

| 4.1  | Flows of $input i$ and other two related inputs, $input k$ and $input j$ in a three-port router | 61 |  |

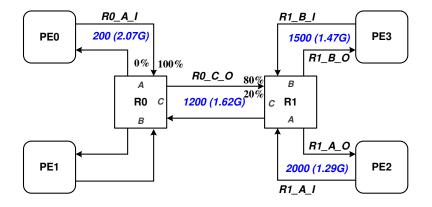

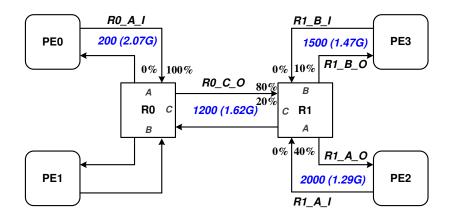

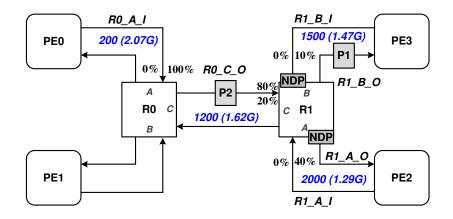

| 4.2  | NoC example with traffic pattern for BW estimation model without stall condition                | 65 |  |

| 4.3  | Simulation result of $R\thetaCO$ link BW without stall condition                                | 66 |  |

| 4.4  | NoC example for BW estimation with stall conditions                                             | 66 |  |

| 4.5  | Simulation result of BW estimation with stall condition                                         | 68 |  |

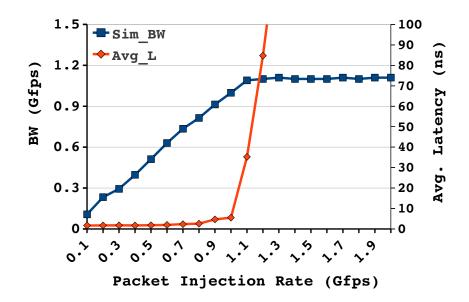

| 4.6  | NoC example with PL insertion for performance optimization: NoC_PL $$                           | 69 |  |

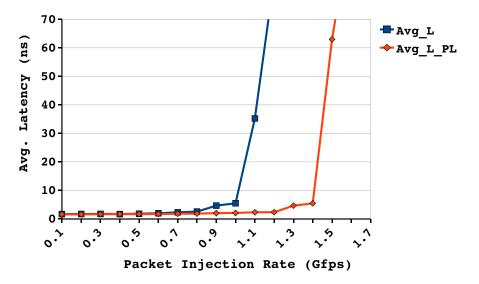

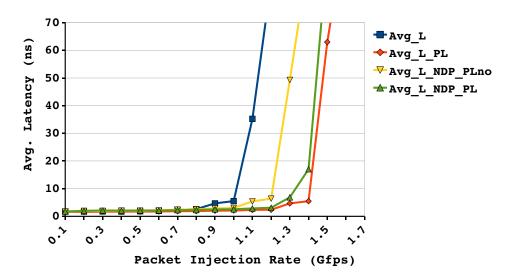

| 4.7  | NoC performance comparison between NOC_Init and NOC_PL                                          | 70 |  |

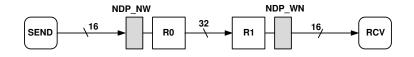

| 4.8  | Usage of NDP modules                                                                            | 72 |  |

| 4.9  | NDP_NW                                                                                          | 73 |  |

| 4.10 | NDP_WN                                                                                          | 73 |  |

| 4.11 | Link BW reduction by NDP module insertion.                                                      | 75 |  |

| 4.12 | NoC example for NDP optimization method: NOC_NDP_PLno                                           | 76 |  |

|      |                                                                                                 |    |  |

| 4.13 | Simulation result for BW estimation                                                                                                                                                                         | 77  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

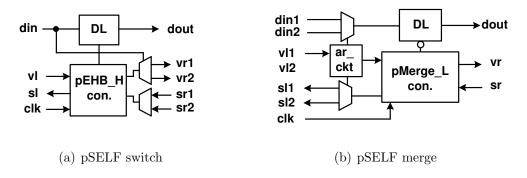

| 5.1  | Implementation of switch and merge modules for pSELF router design                                                                                                                                          | 83  |

| 5.2  | MPEG4 CTG graph. Edge weights are in MBytes/s                                                                                                                                                               | 84  |

| 5.3  | MPEG4 network topology.                                                                                                                                                                                     | 85  |

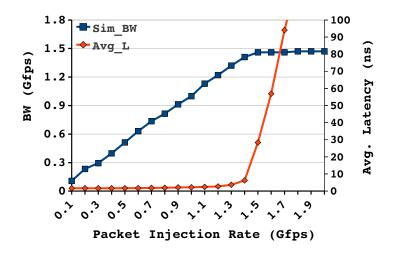

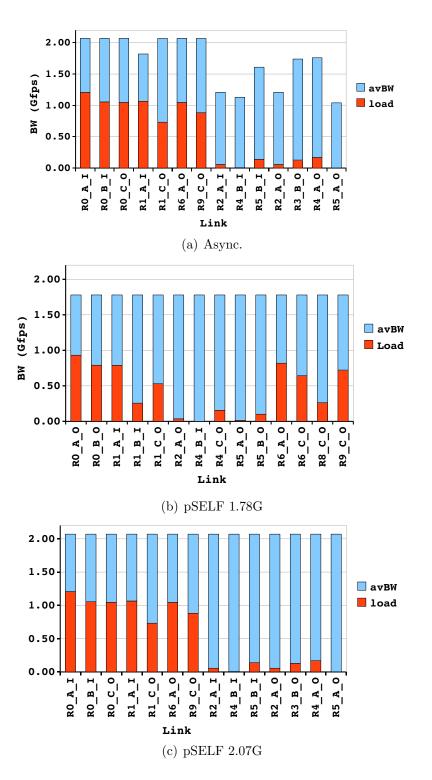

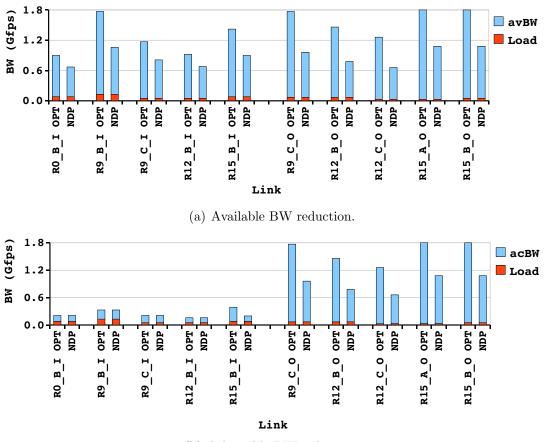

| 5.4  | Available BW ( $avBW$ ) and traffic load ( <i>Load</i> ) of 14 links in the asynchronous, pSELF 1.78G and pSELF 2.07G NoCs in $4\times$ offered traffic load.                                               | 86  |

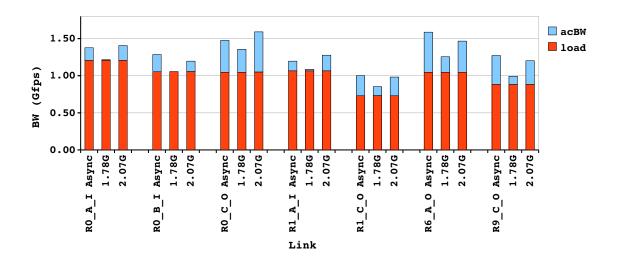

| 5.5  | Link utilization in the asynchronous, pSELF 1.78G and pSELF 2.07G NoCs in $4 \times$ offered traffic load. $acBW$ is an achievable link BW, and <i>Load</i> is traffic load of each link labeled on X-axis. | 87  |

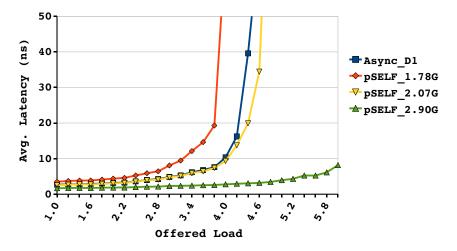

| 5.6  | Average latency comparison between the asynchronous and pSELF net-<br>works in various offered loads.                                                                                                       | 88  |

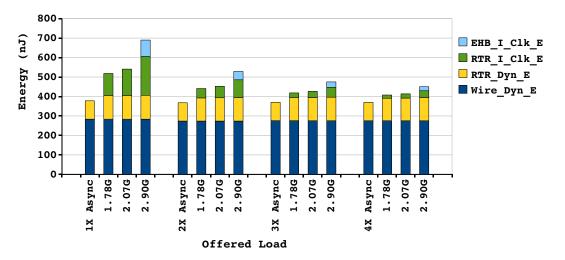

| 5.7  | Energy distribution at $1 \times$ , $2 \times$ , $3 \times$ and $4 \times$ offered loads                                                                                                                    | 89  |

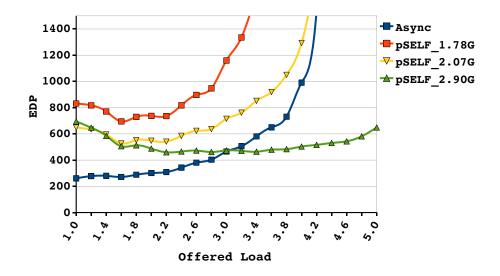

| 5.8  | EDP comparison between four NoC designs in various offered loads                                                                                                                                            | 91  |

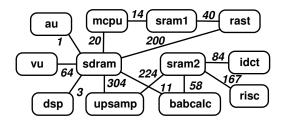

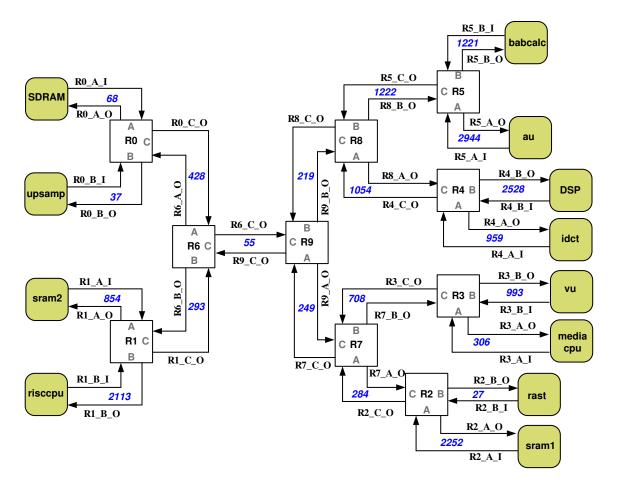

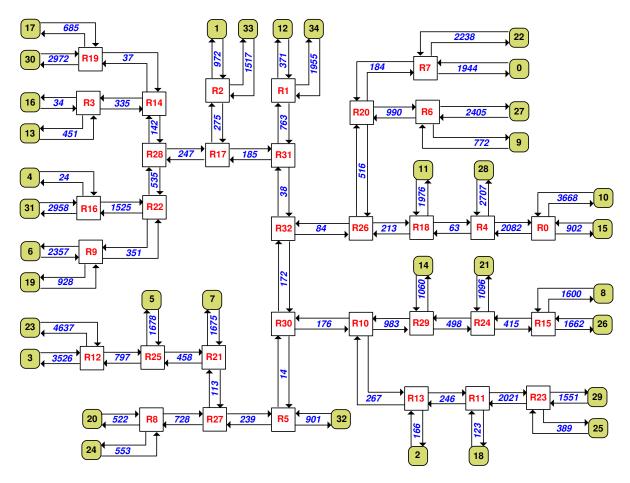

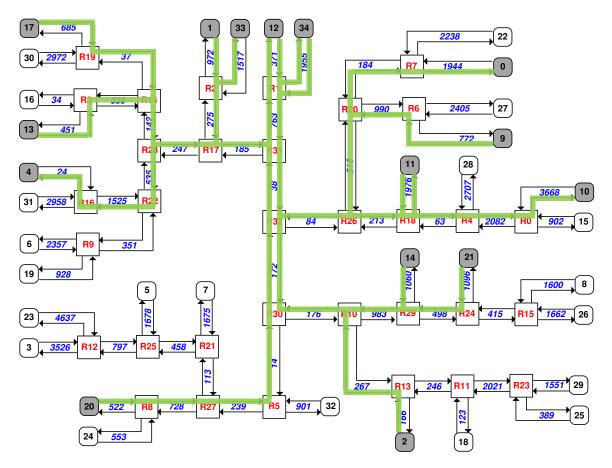

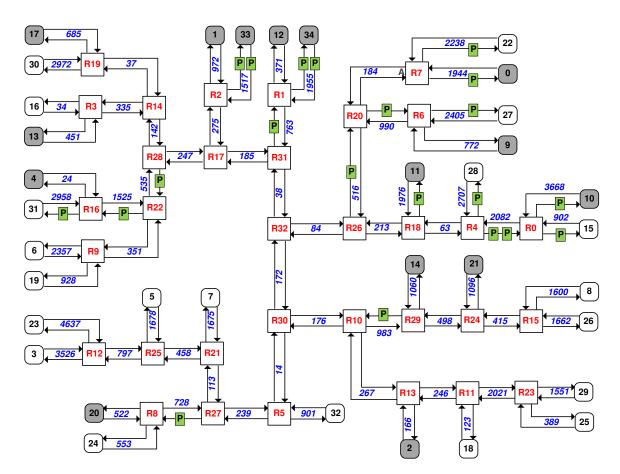

| 5.9  | TI example network topology. PEs are in rounded-square boxes and routers in square boxes, numbers are link wire lengths in $\mu$ m                                                                          | 92  |

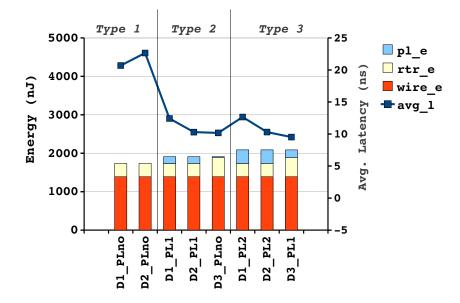

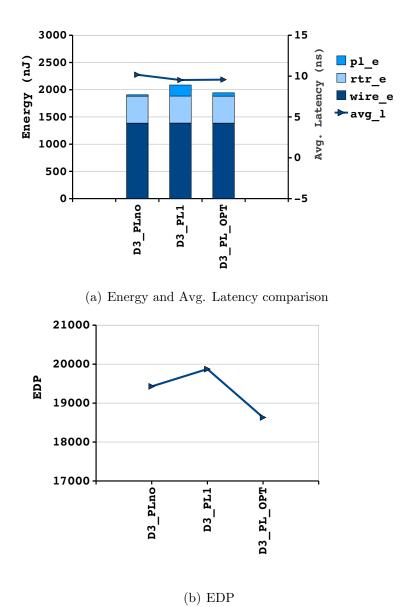

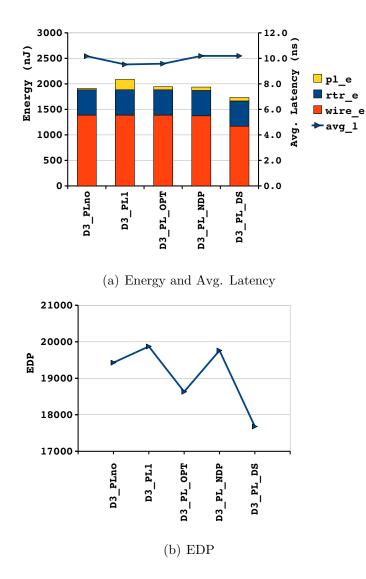

| 5.10 | Comparison of asynchronous NoCs in energy and average latency with TI example.                                                                                                                              | 93  |

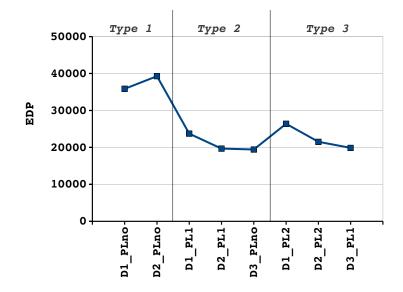

| 5.11 | EDP of asynchronous NoCs with TI example                                                                                                                                                                    | 94  |

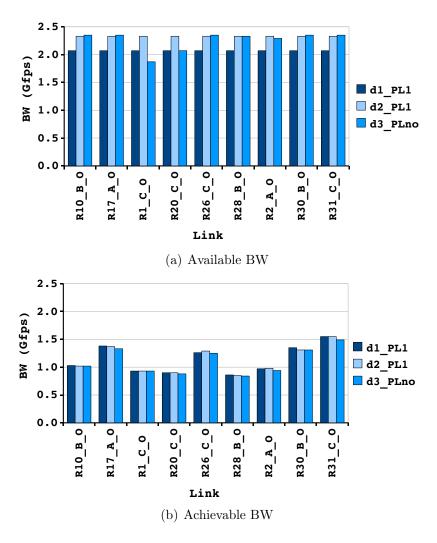

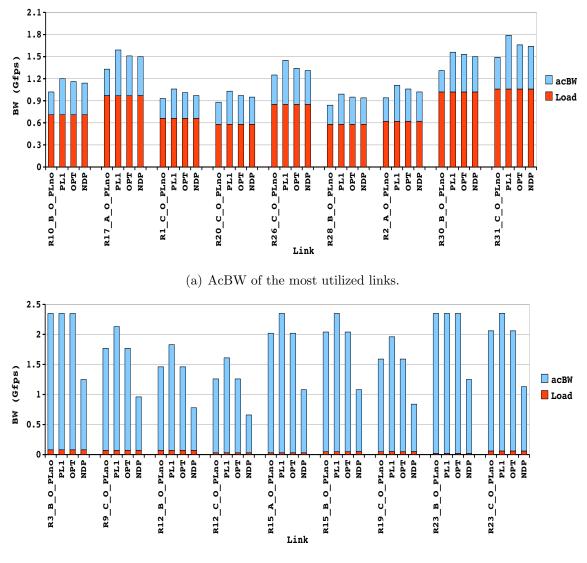

| 5.12 | Available BW and achievable BW of the most utilized links in <i>Type 2</i> designs                                                                                                                          | 95  |

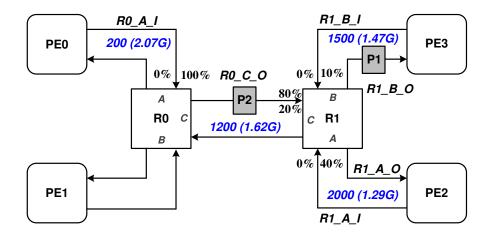

| 5.13 | Performance-critical links in D3_PLno                                                                                                                                                                       | 98  |

| 5.14 | Strategy of PL insertion in $D3_PL_OPT$                                                                                                                                                                     | 99  |

| 5.15 | PL insertion in $D3_PL_OPT$ design                                                                                                                                                                          | 99  |

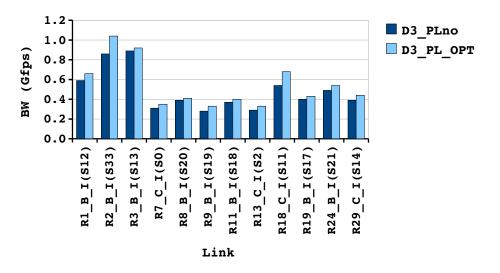

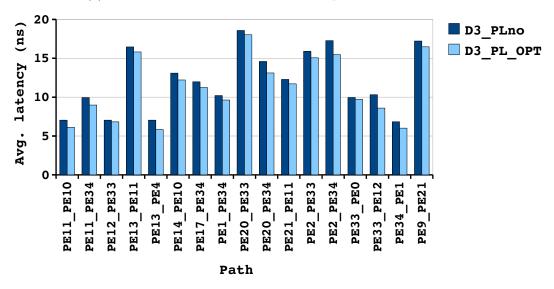

| 5.16 | $D3\_PL\_OPT$ design improvement in a<br>cBW and path average latency. $% D3\_PL\_OPT$ .                                                                                                                    | 100 |

| 5.17 | $D3_PL_OPT$ design improvement in energy, latency and EDP                                                                                                                                                   | 101 |

| 5.18 | AvBW and acBW reduction by NDP module in five sender links and five receiver links.                                                                                                                         | 105 |

| 5.19 | AcBW comparison between all D3 designs in the most utilized and the least utilized links                                                                                                                    | 109 |

| 5.20 | Five D3 designs comparison.                                                                                                                                                                                 | 111 |

## LIST OF TABLES

| 2.1 | Design results of three asynchronous routers                                      | 21  |

|-----|-----------------------------------------------------------------------------------|-----|

| 3.1 | Optimal PL position of $D1\_PL1$ link up to $2000\mu\mathrm{m}$ total wire length | 38  |

| 3.2 | Optimal PL position of $D2\_PL1$ link up to $2000\mu\mathrm{m}$ total wire length | 42  |

| 3.3 | Comparison of three PLno and three PL1_opt links. $\ldots \ldots \ldots$          | 47  |

| 3.4 | Eight asynchronous link designs with different routers and PL numbers.            | 55  |

| 4.1 | Design summary of NDP modules: 32-bit data and 2-bit address in wide data-path.   | 74  |

| 4.2 | Reduction of wire area and acBW by NDP modules                                    | 76  |

| 4.3 | Comparison of SSPACE and DSPACE links with 34-bit link width                      | 79  |

| 5.1 | Asynchronous D1 router and synchronous router design summary                      | 83  |

| 5.2 | 17 Paths which most contribute NoC average latency.                               | 97  |

| 5.3 | $D3_PL_OPT$ design result comparison                                              | 102 |

| 5.4 | Routing area of links with NDP module.                                            | 104 |

| 5.5 | $D3_PL_NDP$ design result comparison                                              | 106 |

| 5.6 | Wire energy ratio of 23 DS links to total wire energy consumption                 | 107 |

| 5.7 | Design summary of five NoCs.                                                      | 108 |

| 5.8 | Design summary: wire area and energy comparison.                                  | 110 |

### CHAPTER 1

## INTRODUCTION

More multicore and heterogeneous IP cores can be integrated in a System-on-Chip (SoC) thanks to the ever decreasing feature size in deep sub-micron (DSM) technology. Likewise, core to core communication is getting more complicated and is now a dominant factor in determining SoC performance [1].

Network-on-Chips (NoCs) are segmented where shared on-chip interconnect systems are based on a network topology. Because of their multiple concurrent communications, NoCs have become a preferable interconnect solution for many SoC designs by replacing the traditional SoC interconnect structures of shared buses and point-to-point links, which are limited by their scalability. NoCs provide increased communication capability, such as low latency, high throughput and power efficiency [2, 3].

An NoC primarily consists of routers, network adapters and physical links. The router is an intermediate node in the path of data from a source IP to a destination IP. Network adapters are interface circuits adapting communication between IP cores and an NoC through protocol conversion, synchronization and packetization. Physical links are global wires of communication links. The NoC architecture and implementation are influenced by several design parameters which include topology (mesh, butterfly, torus, tree, and irregular), routing (centralized, source, and distributed) and switching (circuit, packet) schemes, flow control (buffering, virtual channel), and others.

Design-time specialization is one of distinct facets of NoC designs. Unlike micronetworks which focus more on general-purpose communication and modularity, NoC designs can be specialized with their own design restrictions. SoCs can be classified by their application domains into general-purpose on-chip multiprocessor (MPSoC), application-specific SoCs, and platform SoCs [1]. The MPSoC is commonly built with a homogeneous set of processing units and memory systems to support various applications, usually with no domain boundary. The application-specific SoCs are dedicated to a specific application. They are composed of domain-specific hardware accelerators along with processors and controllers. The platform SoCs are intended for a family of application in a specific domain. Thus, the platform SoCs can be used in a larger variety of applications. Meanwhile, they also contain some domain-specific coprocessors like application-specific SoCs. These specialized application domains, in particular application-specific SoCs and platform SoCs, lead to specific traffic patterns. Therefore bandwidth (BW) requirements of all or some links are available when an NoC is designed. This prior information can be used effectively to design NoCs for SoCs.

Globally Asynchronous and Locally Synchronous (GALS) design is being increasingly used for SoC implementation. In a GALS system, each timing domain is locally clocked and an asynchronous communication scheme is used for communication between timing domains. This trend of asynchronous communication in NoCs is derived from three important factors [4, 5]. First, in the emerging era of nanotechnology, the clock frequency is increasing which exacerbates the difficulty of achieving global clocking across the entire chip. Second, each IP in a SoC has its own optimal operating frequency, so redesigning the IPs for a global clock frequency is inefficient for SoC performance. Finally, increasing energy consumption of the clock buffer and clock tree is a growing concern. Additionally, asynchronous NoCs have several profitable aspects, such as no need for global clock distribution, zero dynamic power consumption, fast forward latency, and robustness to variations when compared to synchronous NoCs.

#### 1.1 Asynchronous Network-on-Chip

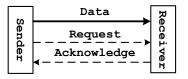

Data communication in an asynchronous link is based on a handshake protocol between a sender and receiver. Without global signaling for a data validity, like a clock signal in synchronous systems, asynchronous communication is executed by special signals, typically *request* and *acknowledge* signals, seen in Figure 1.1, for representing

Figure 1.1: Typical asynchronous handshake protocol.

the data validity. The sender generates the request signal to notify that new data are ready, and the receiver responds with the acknowledge signal indicating that the data have been safely stored and to let the sender start a new operation with the next data.

There are two traditional types of the asynchronous handshake protocols: 2-phase Non-Return to Zero (NRZ) and 4-phase Return to Zero (RZ). The 2-phase NRZ protocol uses signal transitions, and this protocol does not necessitate that the two control signals to be returned to zero after each transfer. Two signal transitions, one on the request and the other on the acknowledge signal, are necessary for one data transfer. In the 4-phase RZ protocol, control signals are detected based on their levels and all signals need to be returned to zero after each data transfer.

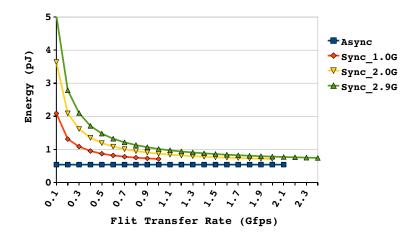

Fig. 1.2 reports dynamic energy per flit, including the idle-cycle energy, used to send the same amount of data at various rates. One asynchronous router, *Async*, is compared against one synchronous router operating with a 1 GHz, 2 GHz, and 2.90 GHz clock. As can be seen, the asynchronous router uses the same dynamic

Figure 1.2: Router dynamic energy per flit, including idle-cycles, with various flit transfer rates.

energy per flit regardless of the link idle times. However, dynamic energy per flit in clocked routers is sensitive to the ratio of active versus idle cycles. As clock frequency increases and the flit transfer rate decreases, more aggregate energy is consumed by the clock gating logic in the idle time. When the flit transfer rate equals the clock frequency of the synchronous router, there is no energy consumed by idle time clocking. Simulation results are based on the design of the asynchronous router and synchronous router presented in Section 2.2 and Section 5.2.1.

#### 1.2 Related Work

NoC designs are presented mainly in terms of their router architecture, support for Guaranteed Service (GS) and Best Effort (BE), virtual channel (VC) [6] implementation, handshake protocol, and performance evaluation.

MANGO is an asynchronous router which supports both GS and BE packet transfer [7, 8]. Connection-oriented GS transfer is accomplished through VC links, while BE traffic uses connectionless transfers with source-routing. BE packets are also used for programming GS connections. Two types VC implementation, lock-based and credit-based, are proposed [9, 10]. The lock-based VC is used in a GS connection due to its simple circuitry, while BE connections employ a credit-based protocol for high performance. A MANGO router with 5-bidirectional port and 33 bit data-path width was implemented using the 4-phase bundle-data (BD) asynchronous handshake protocol in 130 nm technology. The maximum BW is 650 Mflits/s (Mfps).

CHAIN was developed at the University of Manchester and uses delay insensitive 1-of-4 encoding [11]. It services BE packets with source routing and wormhole switching. Its network fabric is composed of steering blocks and arbiter blocks with separate command and response paths in an irregular network topology. The startup company, Silistix, sells NoC design solutions including circuits and EDA tools based on the CHAIN implementation.

QNOC is also an asynchronous router design aimed at quality of service with multiple service levels using a 2-dimensional, priority VC implementation and dynamic VC allocation [12, 13, 14]. A 4-phase BD protocol is used for the router's internal and external links. A router implementation in 180 nm technology has throughput of 205 Mfps.

Both ANOC and DSPIN are designed for the FAUST architecture, which is a SoC platform for telecommunications [15]. They commonly use wormhole switching and a 5-port router architecture and target a mesh topology. The ANOC is an asynchronous NoC with source routing, and was implemented using the STMicroelectronics standard cell and the TIMA TAL library [16]. A quasi delay-insensitive 4-phase protocol is applied to its asynchronous circuit design. DSPIN is a synchronous router using an x-first routing algorithm. To handle clock phase skew in communication between routers, bisynchronous FIFOs are used [17]. Comparison between the two implementations shows that DSPIN has 33% less area than ANOC, but ANOC consumes 37% less power.

The AETHREAL NOC developed by Phillips provides both GS and BE. GS packets have connection-oriented guaranteed throughput and latency by a time-division multiplexed circuit switching approach, while BE packets are transferred through a round-robin arbitration scheme [18].

Communication link properties are critical issues in NoC designs in that the wire-delay of links increases relative to gate-delay and becomes more significant for communication performance as technology scales down. Power and performance of communication protocols have been modeled and compared, including 4-phase and 2-phase asynchronous handshake protocols, delay-insensitive encodings, and clocked communications [19, 20]. Using analytical models, the properties of each protocol are compared in energy and bandwidth. A simple latency model for the asynchronous handshake channel with long wires and twin request/acknowledge control scheme to increase throughput of asynchronous communication links are presented in [21]. In [22], a link capacity allocation algorithm of application-specific NoCs is presented. An analytical packet delay model for wormhole switching is developed and its realization using QNOC router through controlling the number of VC is described as well.

#### **1.3** Motivation

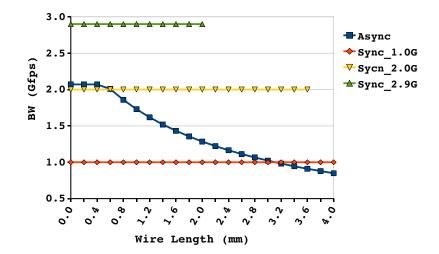

Asynchronous communication links inherently possess an unfavorable property when used in NoC design, especially in view of performance. In a network chip, the largest delay is commonly associated with the time-of-flight of a signal down the communication link. Therefore, the maximum cycle time of a 2-phase asynchronous handshake on a communication link is limited in performance by the propagation delay of the request and acknowledge signals. This can reduce the bandwidth of that link by almost a factor of two. In the 4-phase RZ protocol, four times flight for signal exchange are inevitable for one data transfer, and this protocol has a four times wire-delay penalty. Consequently, selecting asynchronous links in NoC designs could be the wrong design decision since they easily show less communication link performance, due to their two- or four-times wire-delay penalty when compared to synchronous links. Figure 1.3 depicts how asynchronous communication performance degrades with increasing wire length due to handshake control signal propagation delay. The degradation is due to the overhead of the transit time of acknowledgment signal from the receiver to the sender in a 2-phase protocol. On the other hand, the throughput of the synchronous routers is not changed by the link wire length since it is determined only by its clock frequency. However, the synchronous links do have

Figure 1.3: Link wire length effect on asynchronous communication links throughput compared with synchronous links.

a maximum wire length that can be supported for any given frequency with which they can operate without link pipelining.

Nevertheless, this wire-delay property of asynchronous communication links gives NoC designers a new distinct design flexibility. As mentioned previously, the BW of an asynchronous link is impacted by the link wire-delay. In other words, the available BW of an asynchronous link can be controlled by the link wire-delay as inversely proportional to the wire-delay between two asynchronous controllers. Placing controllers in closer proximity increases the link BW by reducing the link wire-delay. Therefore, the BW of each asynchronous link can be adequately specified based on its respective requirement by simply adjusting controller locations. This enables one to design a link BW optimized NoC exploiting specialized link BW requirements, and leads to an NoC design with the multibandwidth link property, which synchronous NoCs are unable to easily provide.

In synchronous NoCs, link BW is primarily determined by clock frequency, so all links basically have the same BW in accordance with the global clock frequency. Although it is possible to realize synchronous NoC links with different bandwidths, e.g. using a different data-path width per each link or a different clock frequency in each router, the realization might be neither simple nor efficient enough to expect any benefit.

Customizing link BW in an asynchronous NoC may be best leveraged when link BW requirements are known at NoC design time. Specialized functionality of application-specific SoCs makes it possible for the BW requirements of all links to be known at NoC design time. In most cases, the required BW of one link is not identical to the others. Some highly trafficked links need to have much higher BW, while other links have very low network traffic. Thus, if each link BW of an NoC is set respectively as much as required, it is substantially beneficial to the effective NoC design by meeting the performance requirement while minimizing hardware resources (power and area).

From a different point of view, the multibandwidth property of asynchronous links can be considered as an efficient method for traffic congestion resolution in NoCs. Traffic congestion occurs when the requested data transfer rate exceeds the capacity of the shared resource, the available link BW, and significantly affects NoC performance. Increasing available BW on congested links can relieve congestion which results in better NoC performance. The ability to control an asynchronous link BW can address the congestion problem at the physical link level in a much simpler way than with synchronous NoCs. On the contrary, because all links in synchronous NoCs operate at the global clock speed, the frequency may become escalated by the most highly congested link. This causes wasteful usage of design resources. The majority of links in an NoCs are much less congested than the highest congested link, so it is of little value to increase the BW of those links.

Interestingly enough, congestion resolution can be seen as an example of the average-case operation of asynchronous circuits versus the worst-case operation of synchronous circuits. The average-case operation of an asynchronous circuit design is generally recognized as one of its advantages, as compared with a worst-case operation of the synchronous design where a clock frequency is limited by the critical, longest logic delay of a design. This average case feature has previously been applied only to functional logic block designs, and not directly applied to communication links in NoC designs since there is no functional block (combinational logic) in the links. However, the worst-case operation characteristic of synchronous systems also exists in synchronous NoCs which originates from network traffic congestion rather than any functional block design complexity, due to the fact that all link BWs are set to the same value as the highest congested links. Contrarily, asynchronous links can realize the average-case performance in NoCs by tuning the BW of only the congested point without affecting other points unnecessarily.

Many recently proposed asynchronous NoC prototype implementations have focused on the performance of an asynchronous router architecture itself, but there is no known published research addressing the multibandwidth property of asynchronous links and exploiting its distinct benefits.

The primary goal of my dissertation research is to analyze and characterize the properties of asynchronous communication links and consequently, to achieve efficient NoC design implementations in which link bandwidths are respectively optimized.

#### **1.4** Dissertation Structure

Chapter 2 presents designs of a proposed asynchronous NoC. Three different asynchronous router designs are introduced and their performance compared against link wire delay.

Chapter 3 introduces the benefits of pipeline latches in asynchronous communication links. Optimal placement of pipeline latches for further improvement of link bandwidth is discussed.

Chapter 4 describes asynchronous NoC design optimization. Three optimization methods are presented for performance, area, and energy improvement respectively. An analytical model for link bandwidth estimation is also presented.

Chapter 5 demonstrates advantages of asynchronous NoCs by the evaluation of two example NoC designs. Features of the asynchronous NoC are presented by comparison with a similarly-designed synchronous NoC. The optimization methods proposed in Chapter 4 are applied to an NoC design and their benefits are presented.

Finally, Chapter 6 summarizes optimization of the asynchronous NoC design and results, and areas of further research are discussed.

#### **1.5** Contributions

The major contributions of this dissertation include the following:

- 1. An asynchronous NoC was designed for efficiency and simplicity. Thanks to simple routing scheme and single-flit packet format, it achieves performanceand energy-efficient asynchronous router design.

- 2. Three distinctive asynchronous routers were designed and presented their properties in conjunction with link wire delay impact on their performance. Many asynchronous routers have been implemented in several research studies and generally the maximum throughput of router designs were discussed. However, the maximum throughput of an asynchronous router is only valid with no link wire delay and thus, restrictive. Designing asynchronous routers with consideration of link wire delay is necessary and results in better router performance in wider range of operation condition (link wire length).

- 3. The primary advantage of asynchronous communication, that is, customizing individual link BW based on its requirement by simply adjusting controller location, was exploited for asynchronous NoC design optimization.

- 4. Benefits of pipeline latch insertion on asynchronous communication links are presented. Usefulness of pipeline latches in asynchronous communication link is widely known in asynchronous circuit domain. But, this work is distinctive in that optimal position of pipeline latches for maximizing its benefit was proposed, and detailed analysis of advantages of pipeline latches in regard to managing link BW of asynchronous NoCs was presented.

- 5. Analytical link bandwidth model was proposed for an NoC composed of threeport routers. NoC design optimization can be expected only when adequate optimization method is applied to proper links. Accordingly, it is necessary to identify properties of each link in an NoC.

- 6. Three specific optimization methods were proposed for performance improvement, wire area reduction and saving wire energy consumption, respectively. The realization of NoC design optimization was presented using an SoC design.

## CHAPTER 2

## ASYNCHRONOUS NOC DESIGN

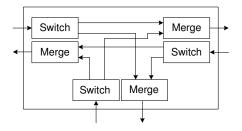

The NoC design introduced here is intended for *efficiency through simplicity*. To achieve this, a somewhat unconventional set of parameters is chosen including: a) simple source-routing, b) single-flit packet and c) simple high throughput and low latency network router design. The router, the main component of the NoC, is composed of three switch and three merge modules, as shown in Fig. 2.1. Each switch and merge module has one set of latches providing a 1-flit buffer on each input and output port. Note that from the second design parameter, a single-flit packet, there is no difference between a 'flit' and a 'packet' and they are used interchangeably in this thesis.

The switch directs a flit to one of two output ports. With bidirectional channels, this results in a three-ported "T" router. The packet format consists of a single flit containing source-routing bits in parallel, on separate wires, with the data bits. The packet is switched through a simple demultiplexer controlled by the most-significant routing bit. The address bits are simply rotated, or swizzled, for the output packet to place the next routing bit in the most significant position. The number of required routing bits is determined by the maximum hop count of a network generated for a specific SoC design. The flit width must be determined based on required throughput,

Figure 2.1: Architecture of a three-port asynchronous router.

power, and area constraints. This format has the overhead of requiring routing bits with every flit.

The merge module arbitrates between two input channels to an output channel, granting access to the first-to-arrive request signal. This effectively alternates between the two input channels, assuming each provides the next packet within an output channel's cycle-time.

This simplicity of the router produces some interesting trade-offs. The simple routing logic has such a low latency that single-flit packets may be advantageous. These packets greatly reduce buffering requirements at each router node. There is no need to have extra logic to calculate packet lengths, and no need to set up or free routes beforehand. Links will only be blocked if all the buffers are full at a router, and streams sharing links will be interleaved.

### 2.1 Asynchronous Router Module Designs

Asynchronous protocols normally fall into two categories: quasi delay-insensitive (QDI) and bundled-data (BD). Generally, QDI is more robust to variations while BD allows simpler circuits. BD has a lower wire count compared to QDI's common encodings (e.g., 1-of-4 and dual-rail). This is potentially more energy-efficient due to reduced wire repeater leakage, especially with wide links [20]. The choice of 4-phase or 2-phase protocol impacts performance and circuit complexity.

The throughput across long links is limited by link wire delay, and thus a 2-phase protocol achieves almost twice the throughput as a 4-phase protocol thanks to half the total time-of-flight link delay per transition. However, a 4-phase, level-sensitive protocol typically allows more simple circuits. In particular, MUTEX elements for arbitrating the shared output channels are level sensitive 4-phase circuits [23, 24]. Thus, the internal control logic of these asynchronous NoC routers is best designed using a 4-phase protocol.

With this in mind, the asynchronous router was designed to internally operate using a BD 4-phase protocol, while a BD 2-phase protocol is used on links between routers.

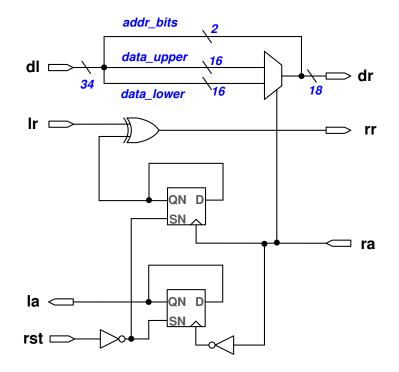

#### 2.1.1 Switch Module Design

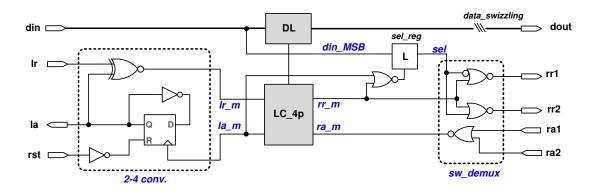

The design of the router's switch module is shown in Figure 2.2. A 2-to-4 phase converter (2-4 conv) is implemented on the input control channel (signals lr and la). This handshakes with a BD 4-phase burst-mode asynchronous controller ( $LC_{-4}p$ ) to pipeline the data with a data latch (DL). The output request is steered to one of two channels (rr1 or rr2) based on the most significant route bit with a demultiplexer ( $sw_{-demux}$ ). The route-bits are rotated and passed to the merge module of the router. The routing logic occurs concurrently with the handshake.

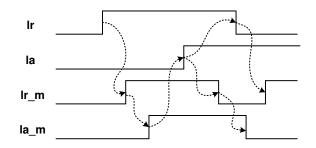

The 2-to-4 phase converter was designed manually and its timing diagram is shown in Figure 2.3. The 2-phase signals, lr and la are converted to a 4-phase protocol on wires  $lr_m$  and  $la_m$  which are inputs to the 4-phase linear controller.

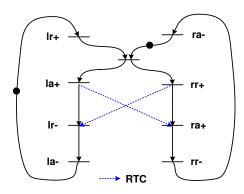

The linear controller connected with the 2-to-4 phase converter has the same specification and timing assumptions as the one used in [25]. Its specification is shown in Eq. 2.1 as a CCS process logic [26] and Figure 2.4 with Petri-Net [27] where the RTC indicates a *relative timing constraint* that enables a specific timing optimization for this asynchronous circuit [25]. The circuit implementation of the linear controller is presented in Figure 2.5.

$$LEFT = \underline{lr.cl.la.c2.lr.la.} LEFT$$

RIGHT = c1.rr.c2.ra.rr.ra.RIGHT

$$LC = (LEFT|RIGHT) \setminus \{c1, c2\}$$

(2.1)

Figure 2.2: Design of switch module.

Figure 2.3: Timing diagram of 2-to-4 phase converter.

Figure 2.4: Petri-Net specification of 4-phase linear controller.

Figure 2.5: Circuit implementation of 4-phase linear controller.

#### 2.1.2 Merge Module Design

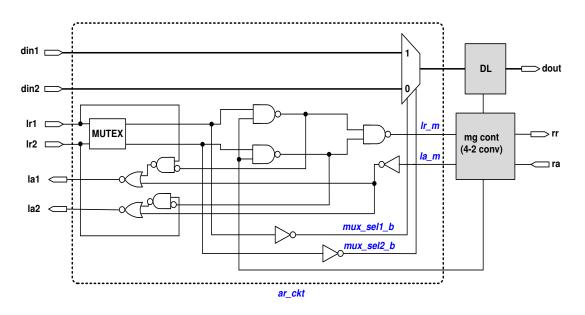

The merge module is composed of the arbitration circuit  $(ar\_ckt)$  and merge controller  $(mg \ cont)$  shown in Figure 2.6. The arbitration circuit contains a MUTEX element that serializes requests to the shared output channel. The output of the MUTEX element also controls a MUX that selects which input data to store in the output latch. Each transaction of the arbitration circuit requests a data transfer via the 4-phase handshake signal  $lr\_m$ . This request passes through the merge controller to generate the 2-phase network link handshake on signals rr and ra, as well as store the data in a data latch.

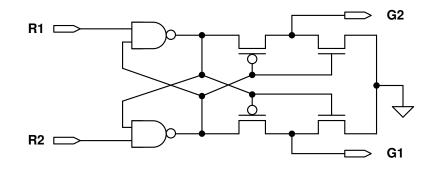

The MUTEX element is a special cell which is not part of the standard cell library used for the circuit implementation. Thus, a specific MUTEX design in [24] (shown in Figure 2.7) was characterized as a separate library cell through manual layout and HSPICE simulation.

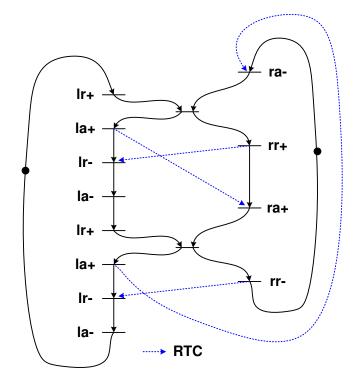

The merge controller was specified in CCS (Eq. 2.2) and by Petri-Net (Figure 2.8). The circuit implementation is shown in Figure 2.9.

Figure 2.6: Design of merge module.

Figure 2.7: Design of MUTEX.

Figure 2.8: Petri-Net specification of merge controller.

Figure 2.9: Implementation of merge controller.

$$LEFT = \underline{lr.c1.la.c2.\underline{lr.la.LEFT}}$$

RIGHT = c1.rr.c2.ra. RIGHT

$$MG\_CON = (LEFT|RIGHT) \setminus \{c1, c2\}$$

(2.2)

#### 2.1.3 Asynchronous Circuit Design Methodology

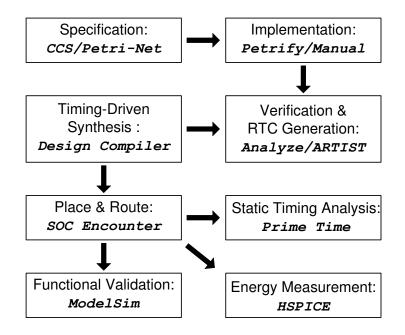

All of the circuits were designed with the static, regular  $V_{th}$ , Artisan cell library on IBM's 65nm 10sf process. The asynchronous circuit design process uses a clocked CAD flow in a methodology similar to [28], and it is shown in Figure 2.10.

**Implementation** - Circuit implementation of asynchronous modules was done with *Petrify* [27] or manual design. The input to *Petrify* are Petri-Nets, which are equivalent to the process-based specification such as CCS.

Figure 2.10: Asynchronous circuit design flow.

**Verification and RTC Generation** - The implemented circuits were verified using the Asynchronous Formal Verification tool, *Analyze* [29]. Another tool, *ARTIST* [30], generated the relative timing constraints (RTCs) that allow the circuit to be proven conformant to its specification, and thus operate correctly.

**Timing-Driven Synthesis** - The RTCs from *ARTIST* were converted into Synopsys Design Constraints (SDC) format, and the asynchronous modules and full asynchronous router design were synthesized with Synopsys Design Compiler.

**Place and Route** - The synthesized asynchronous router was physically placed and routed with Cadence SOC Encounter.

Static Timing Analysis - The placed and routed designs were timing-verified by Static Timing Analysis with Synopsys PrimeTime against the constraints generated by the verification tools.

**Functional Validation** - Functionality and performance were validated in the design with ModelSim using back annotated pre- and post-layout delays.

**Energy Measurement** - Energy was measured using HSPICE simulations of the design's spice netlist using parasitic extraction from Mentor Graphics Calibre PEX.

#### 2.2 Asynchronous Router Design

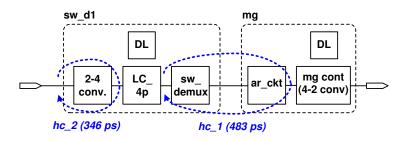

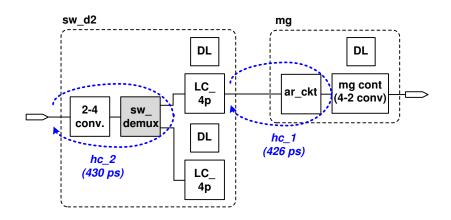

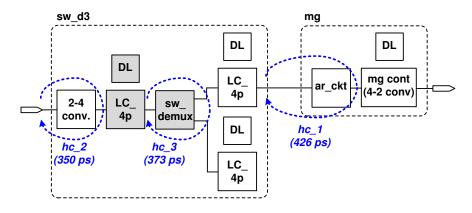

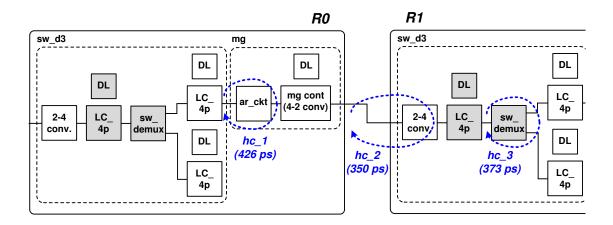

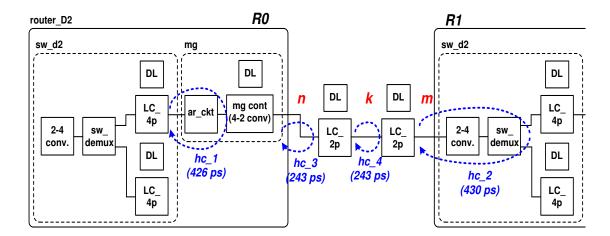

Three different asynchronous routers, D1, D2 and D3, were designed with the identical architecture shown in Figure 2.1 using the switch and merge module designs of the previous section. They are shown in Figure 2.11, Figure 2.12 and Figure 2.13 where numbers in parenthese are cycle times of the corresponding handshake cycles.

The asynchronous routers consist of three switch and three merge modules shown in Figure 2.1. However, for the sake of simplicity, each router design is presented with only one switch and merge module. The other two switch and merge modules are identical to those shown in the figure.

The merge modules are identical in all three routers and their architecture is shown in Figure 2.6 whereas the switch modules are distinctive in each router design. Meanwhile, the submodules inside the switch modules, 2-4 conv.,  $sw\_demux$ , and  $LC\_4p$  are identical in the three different switch module designs. In other words, each switch design distinguishes itself by the different placement of the submodules.

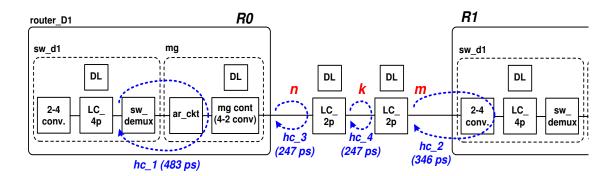

Figure 2.11: Router D1.

Figure 2.12: Router D2.

Figure 2.13: Router D3.

Asynchronous communication transfers data by a handshake protocol and hence there is one handshake cycle between any two connected data latches. So, the D1 and D2 routers have two handshake cycles, while the D3 router has three handshake cycles. The maximum throughput of each router design is determined by the handshake cycle which has the longest cycle time.

The three different router designs were intended to improve the router throughput by reducing handshake cycle time, using the placement of the submodules or adding one more data latch. The D1 router is the base design which uses the initial design of the switch module as in Figure 2.2 and the other routers were improved designs based on the D1 router.

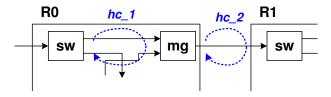

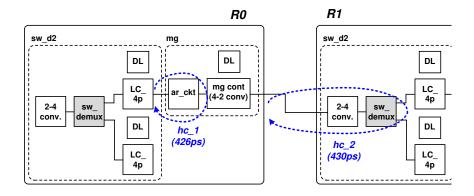

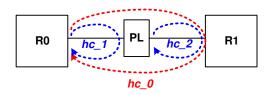

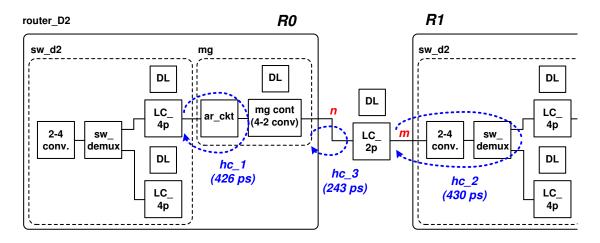

In the switch module of the D1 router, the  $sw\_demux$  is located after the  $LC\_4p$ and connected with the  $ar\_ckt$  in the merge module. It leads to the connection of two combinational blocks in the  $hc\_1$ . Consequently, the long cycle time of the  $hc\_1$  (483 ps) limits the throughput of the D1 router as 2.07 Gflits/s (Gfps).

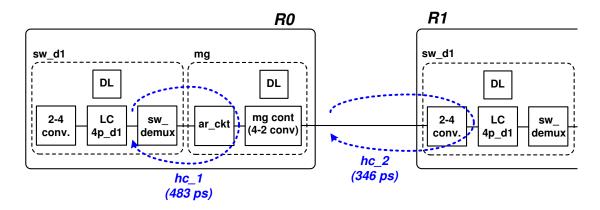

The D2 router achieves better router throughput by separating the  $sw\_demux$  and the  $ar\_ckt$  with the pipeline latch. The  $sw\_demux$  is located in front of the  $LC\_4p$ and only the  $ar\_ckt$  exists in the  $hc\_1$  cycle of the D2 router. As a result, the D2 router has a smaller cycle time in the  $hc\_1$  cycle (426 ps) than that of the D1 router. However, shifting the location of the pipeline latch leads to a different connection of two combinational blocks, 2-4 conv. and  $sw\_demux$  in the  $hc\_2$  cycle, resulting in the increase of its cycle time to (430 ps). In consequence, the throughput of the D2 router is limited by the  $hc\_2$  handshake cycle at 2.32 Gfps. Meanwhile, one more data latch is required after the  $sw\_demux$  for storing packets for different output ports separately.

Another data latch stage is inserted into the D3 router design between the two combinational blocks in the  $hc_2$  cycle of the D2 router to reduce the cycle time of  $hc_2$ . As a result, the  $hc_1$  cycle determines the router throughput at 2.35 Gfps.

Table 2.1 summarizes design results for the three routers. Router area and dynamic energy consumption per flit were measured with a 44-bit link width; 32-bit data-path and 12-bit routing address. The D1 router used the fewest resources in both area and energy, but it shows the lowest throughput. The D2 design has higher performance but with larger area than the D1 router. Dynamic energy dissipated per flit is not very different between the D1 and D2 router, because the majority of dynamic energy is consumed by data latches, and each flit passes through two data latches inside the routers equally in both router designs. The D3 router shows the highest router throughput. However, the performance benefit comes at the expense of the largest area and highest energy consumption per flit.

Area is dominated by data latches and the data MUXes used in the merge modules. The controllers ( $LC_4p$  in the switch modules and mg cont in merge modules) make a very small contribution to the total area. Dynamic energy is consumed when one data word passes a router from an input port to an output port. Energy is measured using HSPICE simulations with the spice netlist generated from the design using parasitic extraction from Mentor Graphics Calibre PEX. The same simulation was used in both HSPICE and ModelSim. The HSPICE control file was generated by converting a vcd file generated from the ModelSim simulation. This allowed us to more easily validate switching activity on the data and control paths. A 25% data switching activity factor was applied to the data bits for the energy simulations.

|    | Max. Throughput (Gfps) | Area $(\mu m^2)$ | Energy/flit (pJ) |

|----|------------------------|------------------|------------------|

| D1 | 2.07                   | 3136             | 1.127            |

| D2 | 2.32                   | 4043             | 1.158            |

| D3 | 2.35                   | 4990             | 1.575            |

Table 2.1: Design results of three asynchronous routers

The maximum throughput of the routers is measured by inserting data into an input port at the maximum rate while alternating packet output port, and allowing two output ports to communicate with other routers with no wire delay. The router's low power and area are due to its simple architecture and the use of latches, rather than flip-flops, for storage elements. Latches are about half the size and use less power than flip-flops. Since much of the area and power of many router architectures derives from memory elements, this advantage makes a significant difference. Furthermore, the simplicity of the control circuits also contributes to high throughput. These routers employ a bundled data protocol rather than delay insensitive codes which results in fewer wires per channel and efficient use of standard cell libraries. However, the cost to this is that the circuit timing must be carefully specified and controlled, similar to clocked design, to ensure correct operation.

## 2.2.1 Router Performance Evaluation with Link Wire Length

A path from a source to a destination in an asynchronous NoC is normally composed of several routers and several links. Subsequently, there exist several handshake cycles other than the handshake cycle inside a router, and the maximum path throughput is determined by the longest handshake cycle time among several handshake cycles.

Figure 2.14 shows a link from router R0 to R1 in an NoC. (One more handshake cycle exists inside R1 if it is a D3 router.) One handshake cycle  $(hc_{-1})$  exists between the switch and merge modules inside the router R1. The other handshake cycles  $(hc_{-2})$  are external, between routers. The cycle time of the internal handshake cycle,  $hc_{-1}$ , is not changed after the router design is fixed. On the other hand, the cycle time

Figure 2.14: Handshake cycles in asynchronous communication link.

of the external handshake cycle is affected by their link wire length, determined by the placement of adjacent two routers. Simply, if the link wire length is long enough so that the external handshake cycle has longer cycle time than that of the internal handshake cycle due to the link wire delay, the router performance is decided by the external handshake cycle, rather than the internal handshake cycle. Therefore, it is required to take into account of the impact of link wire delay on the router performance together, particularly in asynchronous communication links.

In this section, the router performance with link wire delay is evaluated and its properties are presented. For simplicity of explanation in following sections, some terms are defined:

ICT = Initial cycle time of a handshake cycle with no link wire delay,

DCT = Delayed cycle time of a handshake cycle from it ICT, by link wire delay,

WL = Wire length of a link,

WD = Wire delay of a link.

Link wire delay is estimated using a linear regression equation, Eq. 2.3, which is driven based on the simulation results presented in [31]:

$$WD = 0.1 \times WL + 16 \tag{2.3}$$

#### 2.2.1.1 Performance Evaluation of Asynchronous Router D1

A link which connects two D1 routers is depicted in Figure 2.15 with two handshake cycles. Cycle  $hc_1$  is the internal handshake cycle of the D1 router and  $hc_2$  is an external cycle between two routers.

Figure 2.15: Handshake cycles in D1 router.

Link BW is determined the longer cycle time of either  $hc_{-1}$  or  $hc_{-2}$ . First, the maximum link BW is achieved with no consideration of link wire length between two routers. So,  $hc_{-1}$  determines the maximum link BW, 2.07 Gfps, with the longer cycle time of 483 ps than that of  $hc_{-2}$  (346 ps). The maximum link BW is exactly the maximum throughput of the D1 router presented in Table 2.1.

As link wire length increases, the cycle time of the  $hc_2$  is affected by the link wire delay and consequently increases proportionally. Meanwhile, the cycle time of the  $hc_1$  is unaffected by the link wire delay as it is inside the router. Link BW begins to decrease when the delayed cycle time (DCT) of the  $hc_2$  is greater than the initial cycle time (ICT) of  $hc_1$ .

Accordingly, there is a link length range where the link BW is determined by the ICT of  $hc_1$ , rather than the DCT of  $hc_2$ , because the ICT of  $hc_2$  is smaller than that of  $hc_1$ . The link length range can be calculated with Eq. 2.4 using Eq. 2.3:

$$ICT_{hc_{-1}} \leq DCT_{hc_{-2}}$$

(2.4)

$$ICT_{hc_{-1}} \leq ICT_{hc_{-2}} + 2 \times WD$$

$$WD \leq (ICT_{hc_{-1}} - ICT_{hc_{-2}})/2$$

with  $ICT_{hc_{-1}} = 483$  and  $ICT_{hc_{-2}} = 346$

$$WD \leq 68.5 \text{ ps}$$

$$WL = (WD - 16) \times 10$$

$$WL = 525 \,\mu\text{m}$$

where the external router handshake uses a 2-phase protocol, so that  $2 \times$  wire delay is applied in the calculation of DCT<sub>hc\_2</sub>.

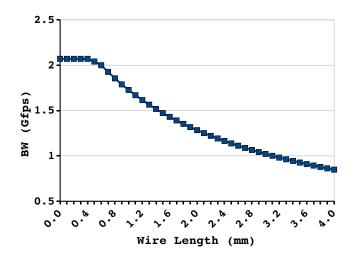

Consequently, up to a wire length of  $525 \,\mu\text{m}$ , the ICT<sub>hc\_1</sub> determines the link BW at 2.07 Gfps, while DCT<sub>hc\_2</sub> is still less than the ICT<sub>hc\_1</sub>. Above  $525 \,\mu\text{m}$ , the link BW is degraded by the longer DCT<sub>hc\_2</sub> influenced by the link wire delay.

Such a link length range is different according to the router designs in a link, as it depends on the relation between the longest ICT and the ICTs of external handshake cycles. So, it can be used as one of the characteristics of a router design and link BW and hereafter is referred to the Maximum Bandwidth wire length Range (MBR). The MBR of a link exists only when there is a difference between the ICT of the longest handshake cycle and the wire delay sensitive handshake cycle. Furthermore, as the difference is larger, the size of range increases.

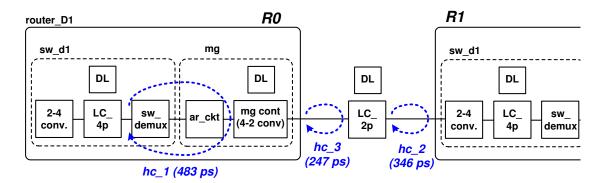

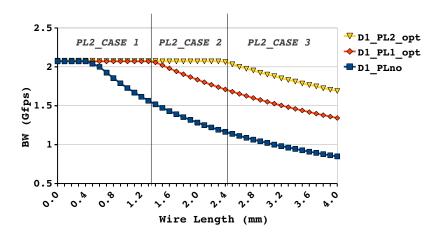

Figure 2.16 shows simulation results measuring link BW by varying link length from  $0\,\mu\text{m}$  to  $4000\,\mu\text{m}$ . The link length is measured from the output of R0 to the input of R1. Link BW begins to decrease only after the MBR of the link.

#### 2.2.1.2 Performance Evaluation of Asynchronous Router D2

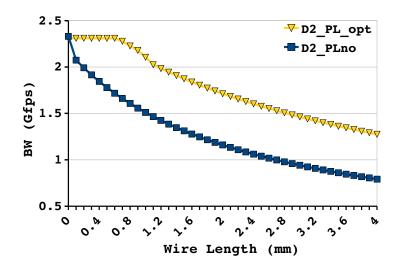

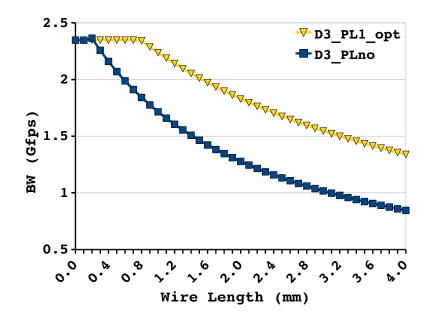

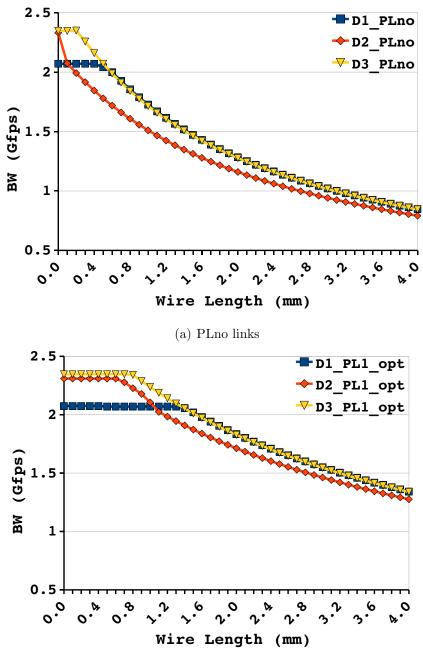

Similarly with the D1 router, the D2 router has two handshake cycles:  $hc_{-1}$  is an internal handshake cycle and  $hc_{-2}$  is an external handshake cycle, as depicted in Figure 2.17. However, the cycle time of each handshake cycle of the D2 router is different from that of the corresponding handshake cycle of the D1 router.

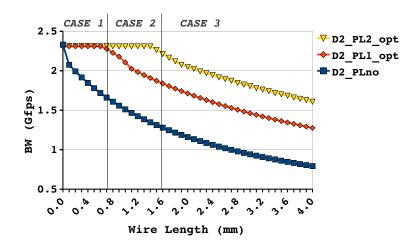

Unlike the D1 router, the longest ICT of D2 is for  $hc_2$ , an external handshake cycle, rather than the internal handshake cycle,  $hc_1$ , in the D1 design. This difference leads to distinctive characteristics of wire delay impact on link BW with the D2 router, and it is shown in Figure 2.18 along with the link BW of the D1 router. There is no MBR where the maximum link BW is maintained while unaffected by the link wire delay. This is because the  $hc_2$  cycle determines the maximum throughput with no wire delay, as well as is the external handshake cycle which is sensitive to the link wire delay. Therefore, the DCT<sub> $hc_2$ </sub> is always the one which determines link BW

Figure 2.16: Impact of link wire delay on link BW with router D1.

Figure 2.17: Handshake cycles in D2 router.

Figure 2.18: Impact of link wire delay on link BW with router D1 and router D2.

regardless of link wire length. Link BW is degraded by even a very small length of link wire. Moreover, the ICT of cycle  $hc_2$  of the D2 router is greater than that of the D1 router and subsequently, the DCT<sub> $hc_2$ </sub> of D2 is always longer than that of the D1. As a result, the link BW with the D2 router is worse than that of D1 router for the full range of wire length in the simulation, except for wire length less than 100  $\mu$ m. Thanks to the higher maximum throughput of the D2 router, the link BW is better than that of D1 router until 100  $\mu$ m wire length.

Although the design change in the D2 router achieves higher maximum throughput, it makes the router more vulnerable to the link wire delay penalty, and thereby provides worse throughput than the D1 design.

### 2.2.1.3 Performance Evaluation of Asynchronous Router D3

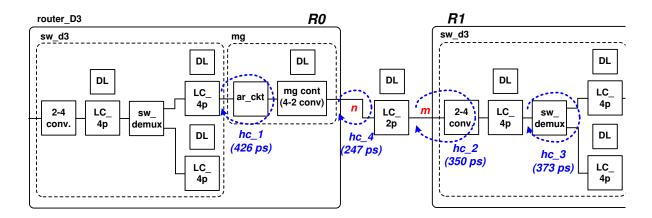

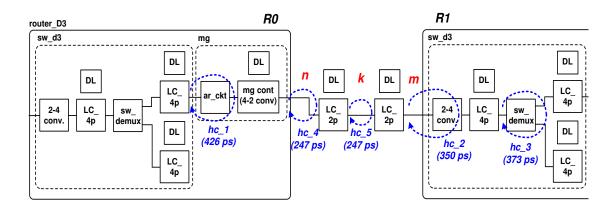

Instead of two handshake cycles in a link with D1 or D2 router, the D3 router has three handshake cycles in a connection of two routers as shown in Figure 2.19.

Cycle  $hc_{-1}$  determines the maximum throughput of the D3 router with the longest ICT. Cycle  $hc_{-2}$  is the external handshake cycle affected by the link wire delay. Meanwhile, cycle  $hc_{-3}$  does not impact router performance in any condition, since it has a smaller ICT than  $hc_{-1}$  and it is not influenced by the link wire delay as an internal handshake cycle.

Similarly to the D1 design, the D3 router has an MBR, and it can be calculated as  $220 \,\mu\text{m}$  in Eq. 2.5.

$$ICT_{hc_{-1}} \leq DCT_{hc_{-2}}$$

(2.5)

$$ICT_{hc_{-1}} \leq ICT_{hc_{-2}} + 2 \times WD$$

$$WD \leq (ICT_{hc_{-1}} - ICT_{hc_{-2}})/2$$

with  $ICT_{hc_{-1}} = 426$  and  $ICT_{hc_{-2}} = 350$

$$WD = 38 \text{ ps}$$

$$WL = (WD - 16) \times 10$$

$$WL = 220 \,\mu\text{m}$$

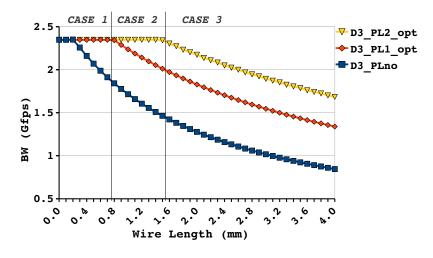

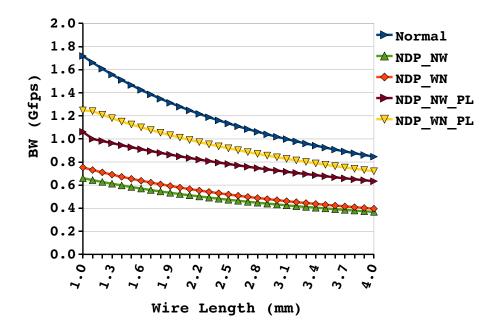

Figure 2.20 compares link BW of the three router designs. The D3 router has the highest link BW and can maintain it until  $220 \,\mu$ m. In addition, the impact of

Figure 2.19: Handshake cycles in router D3 design.

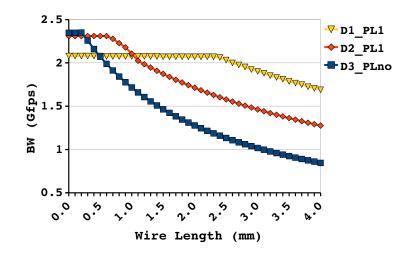

Figure 2.20: Impact of link wire delay on link BW with router D1, D2 and D3.

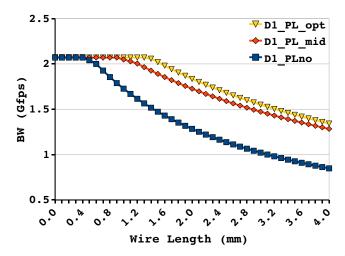

link wire delay on the link BW of the D3 router is very similar to that of the D1 router, especially, after 500  $\mu$ m of link length. This is because the wire delay sensitive handshake cycle,  $hc_2$ , of both D1 and D3 routers, are almost identical to each other.

As link wire length increases, the link wire delay is a dominating factor in determining the DCT of the wire delay sensitive handshake cycle in all three designs and subsequently, the link BW gets closer each other.

Overall, given the distinctive characteristics of each router design, the selection of the best router design depends on link wire length. With zero wire length, the D2 router is the best, since it performs as well as D3, while consuming less energy than D3, similar to D1. But, its link BW degrades rapidly and it becomes the worst design only after 100  $\mu$ m of wire length. The D3 router would be a preferable design when high link BW is required with short wire length, like under 500  $\mu$ m. It, however, consumes more energy than the others. Above 500  $\mu$ m of link wire length, the D1 router is the most energy- and area-efficient design with the same link BW with the D3, better than the D2, as well as the least energy consumption.

## CHAPTER 3

## PIPELINE LATCH IN ASYNCHRONOUS NOC

Pipeline latches (PLs) in asynchronous communication links are more beneficial than in synchronous ones, since they act not only as data buffers but also to improve link BW, whereas they are for buffering only in synchronous links.

## 3.1 Design of 2-phase Linear Controller

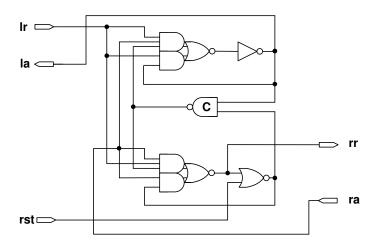

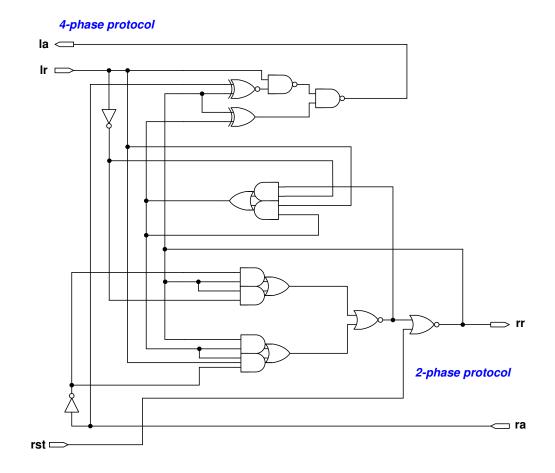

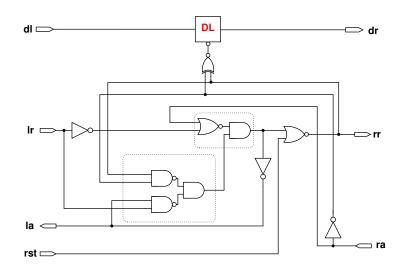

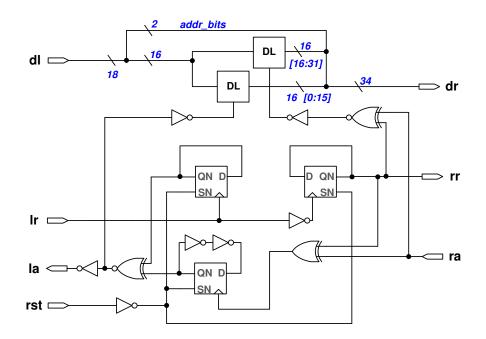

The three routers in the previous section were designed to handshake externally with a 2-phase protocol. Thus, a PL should use the same 2-phase protocol. A 2-phase linear controller was designed, following the asynchronous circuit design procedure described in the Section 2.1.3. The CCS specification and circuit implementation of the 2-phase linear controller are shown in Eq. 3.1 and Figure 3.1, respectively.

LEFT =

$$\underline{\text{lr.c1.la.}}$$

LEFT

RIGHT =  $\underline{\text{c1.rr.ra.}}$ .RIGHT

LC\_2p = (LEFT|RIGHT)\{c1} (3.1)

### **3.2** Pipeline Latch Impact on Link Bandwidth

A PL in an asynchronous link divides one handshake cycle  $(hc_{-}\theta)$  into two other handshake cycles,  $hc_{-}1$  and  $hc_{-}2$ , as it adds an additional data latch stage between two routers, depicted in Figure 3.2. Subsequently, the link wire length is also divided into two short lengths and therefore, the link BW is determined by the DCT of either cycle  $hc_{-}1$  or  $hc_{-}2$  with shorter wire lengths, rather than the DCT of  $hc_{-}\theta$  with the whole link wire length. For instance, if the PL is inserted into the center of the link, the total wire length is evenly divided into two half length wires, and the link BW is affected by only half of the link wire delay.

Figure 3.1: Design of 2-phase linear controller.

Figure 3.2: PL insertion and handshake cycles.

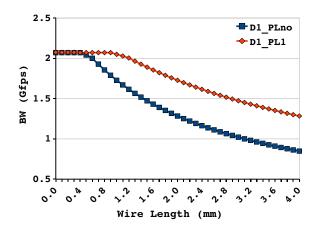

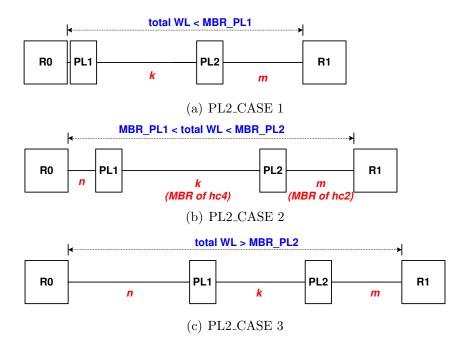

Figure 3.3 shows a link,  $D1_PL1$ , with one PL between two D1 routers. It is identical to the link shown in Figure 2.15 except the PL. For the brevity of explanation, hereafter, the link in Figure 2.15 is referred as  $D1_PLno$ , a link between two D1 routers with no PL.

The  $D1\_PL1$  link has three handshake cycles, one more than  $D1\_PLno$ , as the PL in  $D1\_PL1$  divides cycle  $hc\_2$  of  $D1\_PLno$  into two handshake cycles,  $hc\_2$  and  $hc\_3$ . Hence, the  $D1\_PL1$  link has two external handshake cycles of which DCTs are affected by link wire lengths. Meanwhile, inserting a PL in a link does not affect the ICTs of the handshake cycles inside routers, so  $hc\_1$  is identical in the two links. The ICT of cycle  $hc\_1$  is the longest one and determines the maximum link BW with zero wire length.

The benefit of inserting a PL in  $D1_PLno$  is shown in Figure 3.4 where link BW variation of two links,  $D1_PLno$  and  $D1_PL1$ , are compared as a function of varying

Figure 3.3: Link of D1 router with a PL: D1\_PL1.

Figure 3.4: Impact of link wire delay on link BW with router D1 and one PL.

total link wire length. In  $D1_PL1$ , the PL is placed exactly in the middle of the link so that the divided link wire length is half of the total wire length.

Comparing the DCTs of the two external handshake cycles,  $hc_2$  and  $hc_3$ , of the link  $D1_PL1$ , the DCT of  $hc_2$  is always longer than that of  $hc_3$  and subsequently determines the link BW, since the total link wire length is evenly divided in two and the ICT of  $hc_2$  is longer than the ICT of  $hc_3$ .

Thanks to the PL insertion, the effective wire length of  $hc_2$  of  $D1_PL1$  is cut in half, compared to  $D1_PLno$ . So, the link BW of the  $D1_PL1$  is always better than that of  $D1_PL0$ . The link BW of  $D1_PL1$  with a 2000  $\mu$ m wire length is 1.73 Gfps which is exactly same with that of  $D1_PLno$  at 1000  $\mu$ m. Compared to the link BW of the  $D1_PLno$  at 2000  $\mu$ m, 1.28 Gfps, it is improved by 35%. Furthermore, the MBR of the  $D1_PL1$  link is determined by the relation between the ICT of  $hc_1$  and the DCT of  $hc_2$  and calculated in Eq. 3.2 and Eq. 3.3. It is twice as far as that of the  $D1_PLno$  link at  $525 \,\mu$ m.

$$ICT_{hc_{-1}} \leq DCT_{hc_{-2}}$$

$$ICT_{hc_{-1}} \leq ICT_{hc_{-2}} + 2 \times WD_{MBR}$$

$$WD_{MBR} \leq (ICT_{hc_{-1}} - ICT_{hc_{-2}})/2$$

with  $ICT_{hc_{-1}} = 483$  and  $ICT_{hc_{-2}} = 346$

$$WD_{MBR} \leq 68.5 \,\mathrm{ps}$$

$$(3.2)$$

$$WL_{MBR}/2 \leq (WD_{MBR} - 16) \times 10$$

$$WL_{MBR} \leq 525 \times 2 = 1050 \,\mu \mathrm{m}$$

(3.3)

# 3.3 Optimal Position of One Pipeline Latch Placement

As aforementioned, the BW of a  $D1\_PL1$  link is always determined by the DCT of cycle  $hc\_2$ , rather than  $hc\_3$ , as  $hc\_2$  has a larger ICT for the same link wire length. Eq. 3.4 calculates the DCT of two handshake cycles and their link BW when a PL is inserted at the center of a link with a 2000  $\mu$ m long wire.

$$DCT_{hc_{-2}} = ICT_{hc_{-2}} + 2 \times WD$$

$$= 346 + 2 \times (0.1 \times 1000 + 16)$$

$$= 578 \text{ ps} \rightarrow 1.78 \text{ Gfps}$$

$$DCT_{hc_{-3}} = ICT_{hc_{-3}} + 2 \times WD$$

$$= 247 + 2 \times (0.1 \times 1000 + 16)$$

$$= 479 \text{ ps} \rightarrow 2.08 \text{ Gfps}$$

(3.4)

The link BW of  $D1_PL1$  is 1.78 Gfps due to the larger DCT of  $hc_2$ . Meanwhile, the higher throughput of cycle  $hc_3$ , 2.08 Gfps, is limited by  $hc_2$  and can not be utilized. The unbalanced throughput between two handshake cycles comes from the difference of ICTs with the same wire length.

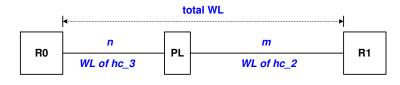

Instead of dividing total link wire equally, if the PL is inserted in consideration of the unbalanced ICTs of two handshake cycles, by giving more wire length to the shorter ICT of cycle  $hc_3$ , the DCT of  $hc_2$  would be reduced with a shorter wire length which results in further link BW improvement by the PL insertion.

Overall, if two handshake cycles, which handshake through a PL inserted in a link, have different ICTs, the handshake cycle with smaller ICT has the capability to handle more wire delay than the other. Therefore, there exists an optimal position of a PL where the DCTs of two handshake cycles are balanced resulting in the maximum link BW that can be achieved by PL insertion.

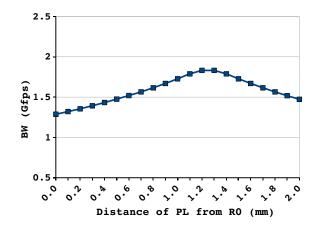

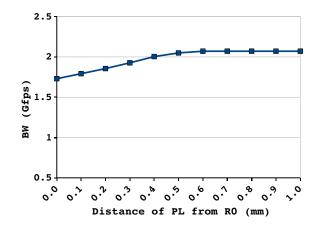

## 3.3.1 Optimal Position of One Pipeline Latch with Router D1

In order to see how the link BW is affected by the PL position in  $D1\_PL1$ , a simulation was performed. Figure 3.5 depicts the  $D1\_PL1$  link again with only link wire length variables, n and m, and Figure 3.6 shows the link BW variance by sweeping the PL position between router R0 to R1 with  $2000 \,\mu\text{m}$  of total wire length. The x-axis is the distance of the PL from R0, which is n (WL of  $hc\_3$ ) in Figure 3.5. If the distance is  $0 \,\mu\text{m}$ , the PL is placed just after the output of the R0 router without any link length assigned to the  $hc\_3$ .