# VERIFICATION METHODOLOGIES FOR FAULT-TOLERANT NETWORK-ON-CHIP SYSTEMS

by

Zhen Zhang

A dissertation submitted to the faculty of

The University of Utah

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Department of Electrical and Computer Engineering

The University of Utah

May 2016

Copyright © Zhen Zhang 2016

All Rights Reserved

## THE UNIVERSITY OF UTAH GRADUATE SCHOOL

## STATEMENT OF DISSERTATION APPROVAL

| The dissertation of             | Zł                 | nen Zhang     |                  |

|---------------------------------|--------------------|---------------|------------------|

| has been approved by the follow | wing supervisory c | ommittee memb | ers:             |

| Chris J. M                      | yers               | , Chair       | October 26, 2015 |

|                                 |                    |               | Date Approved    |

| Wendelin Se                     | erwe               | , Member      | October 26, 2015 |

|                                 |                    |               | Date Approved    |

| Hao Zher                        | ıg                 | , Member      | October 26, 2015 |

|                                 |                    |               | Date Approved    |

| Kenneth S. S                    | tevens             | , Member      | October 26, 2015 |

|                                 |                    |               | Date Approved    |

| Priyank Ka                      | alla               | , Member      | October 26, 2015 |

|                                 |                    |               | Date Approved    |

|                                 |                    |               |                  |

| and by                          | Gianluca Lazz      | i             | , Chair of       |

| the Department of               | Electrical and     | Computer Eng  | ineering         |

|                                 |                    |               |                  |

| and by David B. Kieda, Dean     | of The Graduate S  | chool.        |                  |

### ABSTRACT

Over the last decade, cyber-physical systems (CPss) have seen significant applications in many safety-critical areas, such as autonomous automotive systems, automatic pilot avionics, wireless sensor networks, etc. A CPs uses networked embedded computers to monitor and control physical processes. The motivating example for this dissertation is the use of fault-tolerant routing protocol for a Network-on-Chip (NoC) architecture that connects electronic control units (ECus) to regulate sensors and actuators in a vehicle. With a network allowing ECus to communicate with each other, it is possible for them to share processing power to improve performance. In addition, networked ECus enable flexible mapping to physical processes (e.g., sensors, actuators), which increases resilience to ECu failures by reassigning physical processes to spare ECus. For the on-chip routing protocol, the ability to tolerate network faults is important for hardware reconfiguration to maintain the normal operation of a system. Adding a fault-tolerance feature in a routing protocol, however, increases its design complexity, making it prone to many functional problems. Formal verification techniques are therefore needed to verify its correctness.

This dissertation proposes a link-fault-tolerant, multiflit wormhole routing algorithm, and its formal modeling and verification using two different methodologies. An improvement upon the previously published fault-tolerant routing algorithm, a link-fault routing algorithm is proposed to relax the unrealistic node-fault assumptions of these algorithms, while avoiding deadlock conservatively by appropriately dropping network packets. This routing algorithm, together with its routing architecture, is then modeled in a process-algebra language LNT, and compositional verification techniques are used to verify its key functional properties. As a comparison, it is modeled using channel-level VHDL which is compiled to labeled Petri-nets (LPNs). Algorithms for a partial order reduction method on LPNs are given. An optimal result is obtained from heuristics that trace back on LPNs to find causally related enabled predecessor transitions. Key observations are made from the comparison between these two verification methodologies.

# CONTENTS

| AB  | STRACT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | iii                                                                      |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| LIS | T OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | V                                                                        |

| LIS | T OF TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ix                                                                       |

| LIS | T OF ALGORITHMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | X                                                                        |

| AC  | KNOWLEDGMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | X                                                                        |

| СН  | APTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                          |

| 1.  | INTRODUCTION  1.1 Model Checking                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1<br>1<br>3<br>4                                                         |

| 2.  | MODELS OF CONCURRENT SYSTEMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6                                                                        |

|     | 2.1 A Brief Introduction to Process Algebra 2.2 Behavioral Modeling and Verification in CADP 2.2.1 LNT Module 2.2.2 LNT Process 2.2.3 Channel-Level Communication in LNT 2.2.4 Nondeterministic Choice in LNT 2.2.5 Conditional Behaviors and Repetition in LNT 2.3 Behavioral Modeling and Verification in LEMA 2.3.1 Channel-Level Communication in VHDL 2.3.2 Probe and Parallel Communication 2.3.3 VHDL Control Structures 2.3.4 LPN Syntax and Semantics 2.4 Conclusion and Discussion | 6<br>9<br>11<br>12<br>13<br>15<br>18<br>21<br>22<br>26<br>30<br>32<br>38 |

| 3.  | NOC ARCHITECTURE AND ROUTING ALGORITHM                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 40                                                                       |

|     | 3.1 NoC and Fault-tolerant Routing                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 40<br>42<br>46<br>50<br>53                                               |

| 4.            | FORMAL ANALYSIS USING CADP                                       | <b>58</b> |

|---------------|------------------------------------------------------------------|-----------|

|               | 4.1 Background and Related Work                                  | 58        |

|               | 4.2 Evolution of Formal NoC Models                               | 63        |

|               | 4.2.1 One Direction Routing                                      | 64        |

|               | 4.2.2 Removing Arbiter's Buffering Ability                       | 67        |

|               | 4.2.3 Finding Data Abstractions                                  | 68        |

|               | 4.3 Removing Livelock to Improve Routing                         | 70        |

|               | 4.3.1 Potential Livelock Problem                                 | 71        |

|               | 4.3.2 Eliminating Livelock                                       | 75<br>70  |

|               | 4.4 Verification Results                                         | 79<br>81  |

|               | 4.4.1 Deadlock Freedom and Single-link-rault Tolerance           | 83        |

|               | 4.4.3 Livelock Freedom                                           | 83        |

|               | 4.5 Conclusion and Discussion                                    | 85        |

|               |                                                                  |           |

| <b>5.</b>     | FORMAL ANALYSIS USING LEMA                                       | <b>87</b> |

|               | 5.1 Background and Related Work on Por                           | 88        |

|               | 5.2 Por with LPNs                                                | 89        |

|               | 5.2.1 Preparations                                               | 90        |

|               | 5.2.2 Dependent Set                                              | 92        |

|               | 5.2.3 Necessary Set                                              | 93        |

|               | 5.2.4 Correctness and Time Complexity                            | 96        |

|               | 5.2.5 Evaluation of Trace-Back                                   | 99        |

|               | 5.2.6 Comparisons Between POR-TB with Compositional Minimization |           |

|               | 5.3 Vhdl Model for the Two-by-Two NoC                            | 105       |

|               | 5.3.2 Router Models                                              |           |

|               | 5.4 Verification Observations                                    |           |

|               | 5.5 Conclusion and Discussion                                    |           |

|               |                                                                  |           |

| <b>6.</b>     | CONCLUSION                                                       | 112       |

|               | 6.1 Summary                                                      | 112       |

|               | 6.2 Future Work                                                  |           |

|               | 6.2.1 Large-scale NoC Verification Using CADP                    | 114       |

|               | 6.2.2 Combining Static Analysis with Dynamic Analysis            |           |

|               | 6.2.3 Improving Partial Order Reduction on LPNs                  |           |

|               | 6.2.4 Stochastic Analysis                                        | 117       |

| $\mathbf{RE}$ | FERENCES                                                         | 118       |

# LIST OF FIGURES

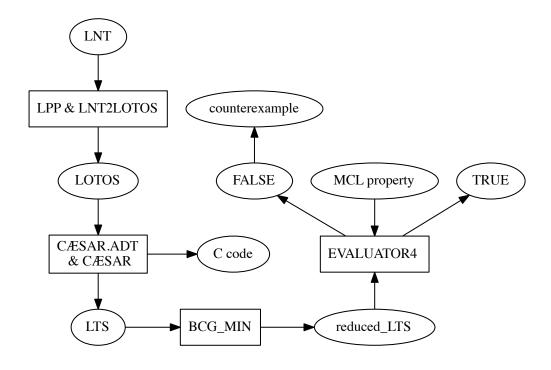

| 2.1  | CADP tool flow                                                                                | 10 |

|------|-----------------------------------------------------------------------------------------------|----|

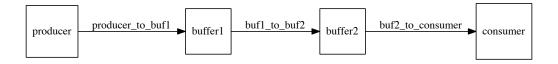

| 2.2  | Block diagram for the producer-consumer example                                               | 14 |

| 2.3  | Top-level Lnt process for the producer-consumer example                                       | 16 |

| 2.4  | Producer, buffer, and consumer Lnt processes for the producer-consumer example                | 16 |

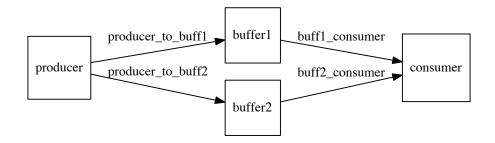

| 2.5  | Block diagram for the modified producer-consumer example                                      | 17 |

| 2.6  | Producer Lnt process with nondeterministic choice                                             | 17 |

| 2.7  | Consumer Lnt process with nondeterministic choice                                             | 18 |

| 2.8  | Top-level Lnt process with nondeterministic choice for the modified producer-consumer example | 18 |

| 2.9  | Producer Lnt process with internal nondeterministic choice                                    | 19 |

| 2.10 | Producer Lnt process with the case behavior                                                   | 20 |

| 2.11 | Producer Lnt process with repetition behaviors                                                | 21 |

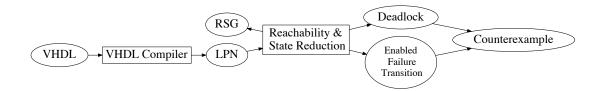

| 2.12 | Lema tool flow                                                                                | 22 |

| 2.13 | Top-level Vhdl entity for the producer-consume example                                        | 23 |

| 2.14 | Producer Vhdl entity for the producer-consume example                                         | 24 |

| 2.15 | Buffer Vhdl entity for the producer-consume example                                           | 25 |

| 2.16 | Consumer VHDL entity for the producer-consume example                                         | 25 |

| 2.17 | Producer Vhdl entity for the producer-consumer example with nondeterministic choice           | 27 |

| 2.18 | Consumer VHDL entity for the producer-consumer example with nondeterministic choice           | 28 |

| 2.19 | Top-level Vhdl entity for the producer-consumer example with nondeterministic choice          | 29 |

| 2.20 | Producer Vhdl entity for the producer-consumer example with internal non-deterministic choice | 30 |

| 2.21 | Producer Vhdl entity with a case statement                                                    | 31 |

| 2.22 | Producer Vhdl entity with a breakable infinite loop statement                                 | 32 |

| 2.23 | Producer Vhdl entity with a while-loop statement                                              | 33 |

| 2.24 | LPN for a simple producer-consumer model                                                      | 37 |

| 2.25 | LPN examples with failure and disabling failure transitions                                   | 38 |

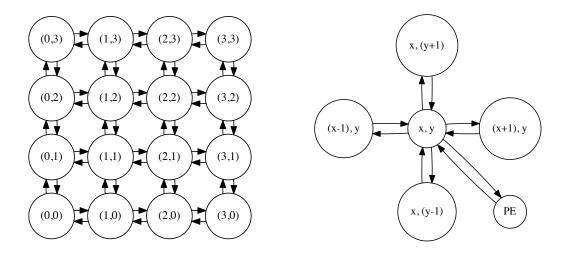

| 3.1  | A 4-by-4 2D mesh network with 16 nodes                                            | 43  |

|------|-----------------------------------------------------------------------------------|-----|

| 3.2  | A special case for negative edges in the Glass/Ni algorithm                       | 44  |

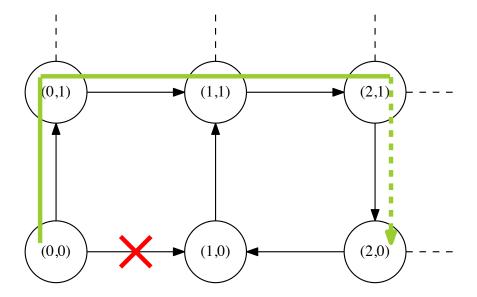

| 3.3  | Deadlock caused by a link fault                                                   | 45  |

| 3.4  | A fault lookahead mechanism                                                       | 46  |

| 3.5  | Packet is dropped by node 21 to break deadlock                                    | 47  |

| 3.6  | One-away fault handling example                                                   | 48  |

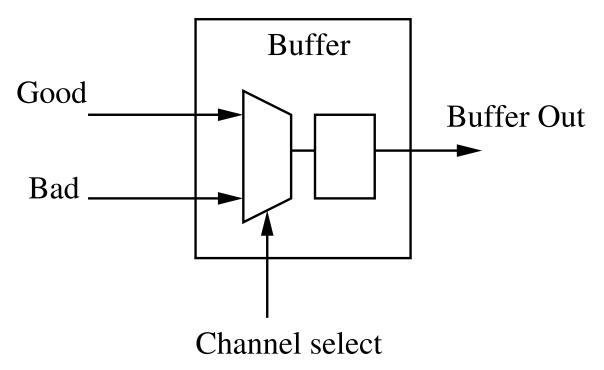

| 3.7  | Link buffer with tunable probability of failure                                   | 49  |

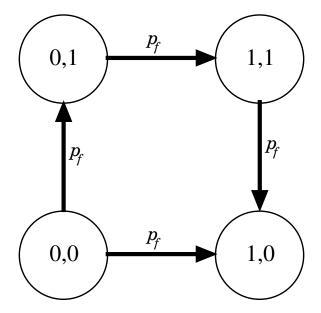

| 3.8  | A 2-by-2 mesh network with fault probability of $p_f$ on each link                | 51  |

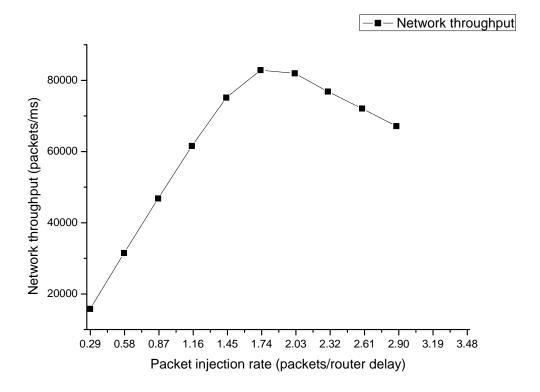

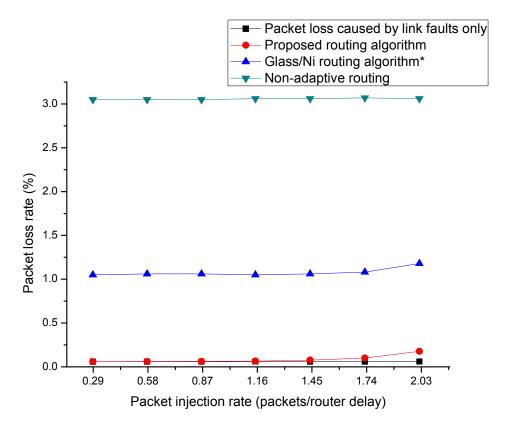

| 3.9  | Network throughput vs. packet injection rate                                      | 52  |

| 3.10 | Packet loss rates for different routing algorithms                                | 53  |

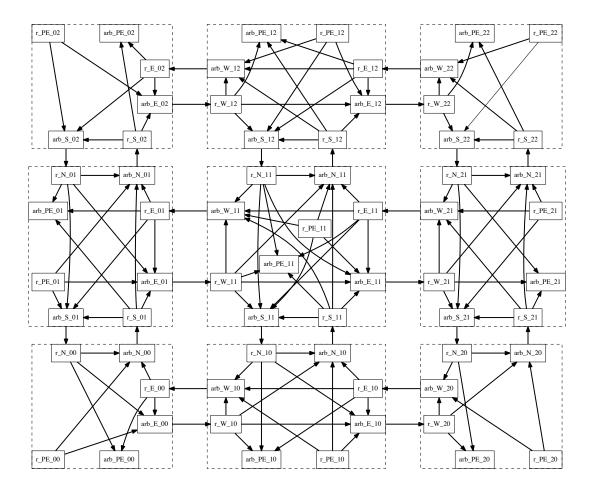

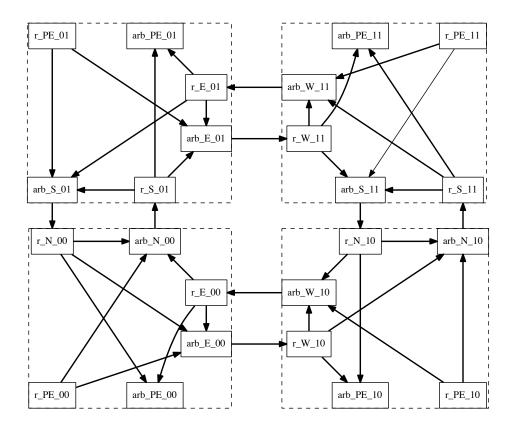

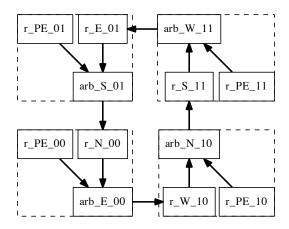

| 3.11 | Architecture of the nine routing nodes in a three-by-three mesh                   | 55  |

| 3.12 | Illustration of a deadlock caused by a cyclic communication dependency            | 56  |

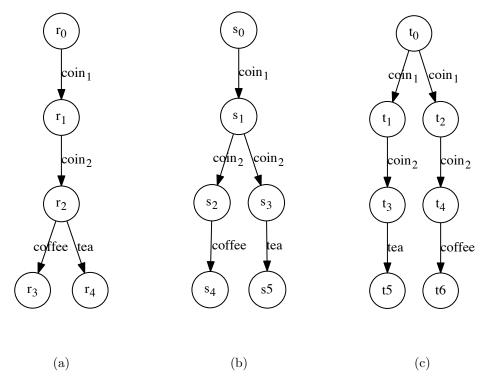

| 4.1  | Three vending machines                                                            | 60  |

| 4.2  | Weak bisimulation equivalence                                                     | 61  |

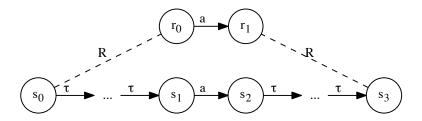

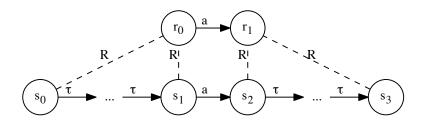

| 4.3  | Differences between weak and branching bisimulation                               | 62  |

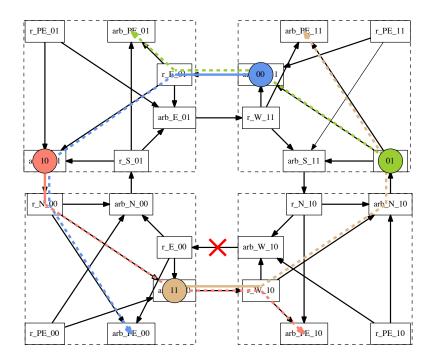

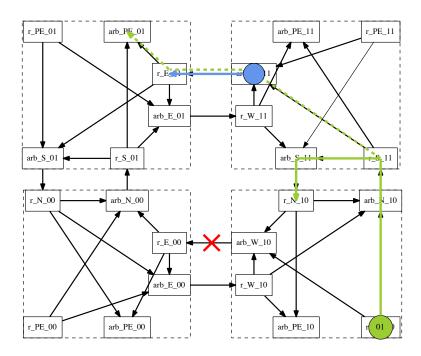

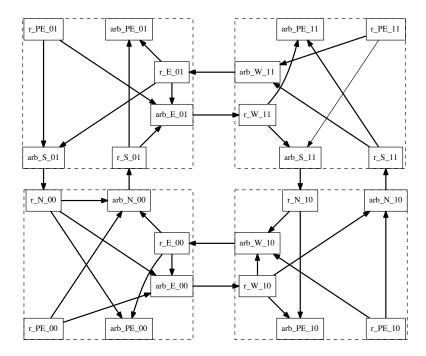

| 4.4  | Architecture of the two-by-two mesh                                               | 64  |

| 4.5  | A counterclockwise routing model                                                  | 65  |

| 4.6  | The Lnt processes for arb_W_11 and r_S_11                                         | 66  |

| 4.7  | The Lnt process for the RI2 router                                                | 70  |

| 4.8  | The Lnt process for the arbiter corresponding to RI2                              | 71  |

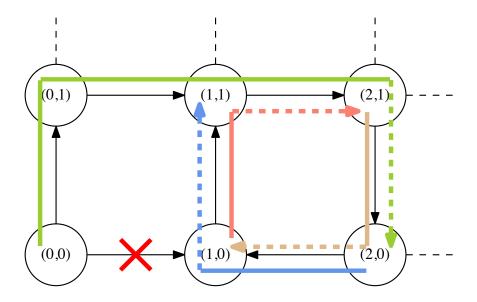

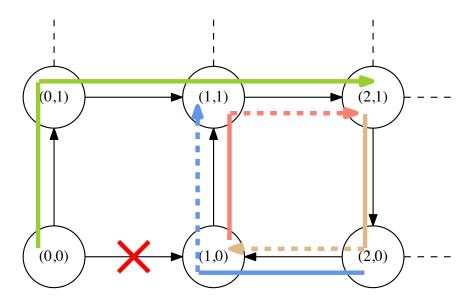

| 4.9  | Illustration of the problem with the abstract model                               | 72  |

| 4.10 | The original and modified Lnt process for abstract r_N_10                         | 74  |

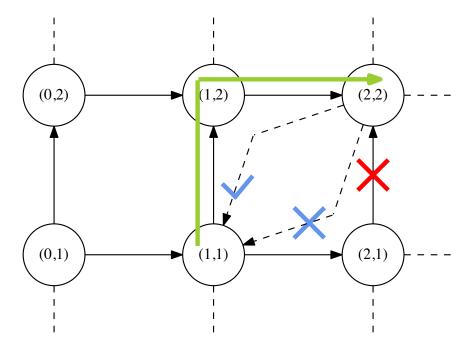

| 4.11 | Illustration of the two circular paths and a livelock loop                        | 76  |

| 4.12 | The new Lnt process for r_N_10                                                    | 77  |

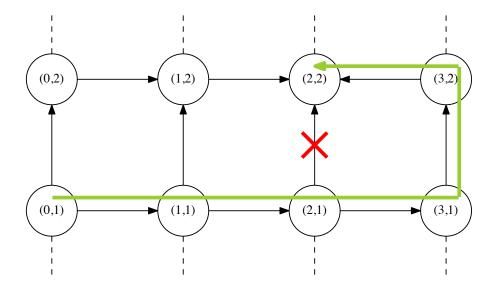

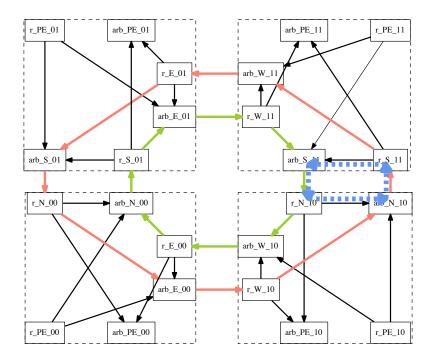

| 4.13 | Improved two-by-two NoC architecture with livelock removal                        | 78  |

| 4.14 | Pseudo-code of the routing protocol                                               | 80  |

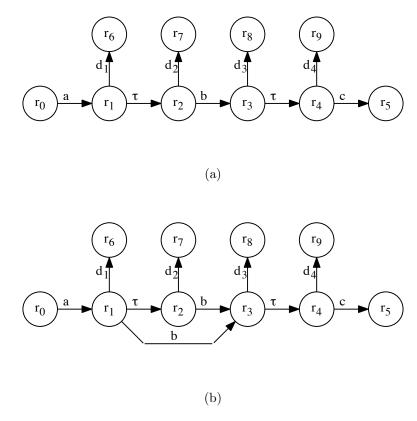

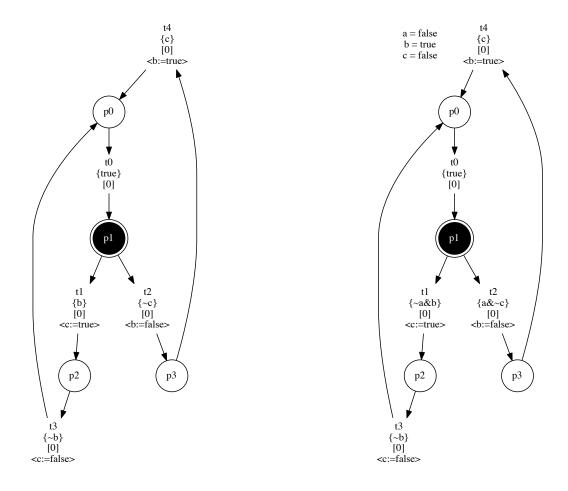

| 5.1  | Examples of refinements                                                           | 92  |

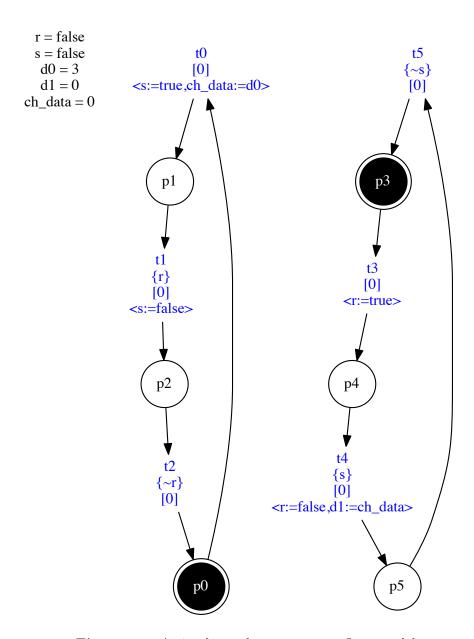

| 5.2  | A simple producer-consumer LPN model                                              | 96  |

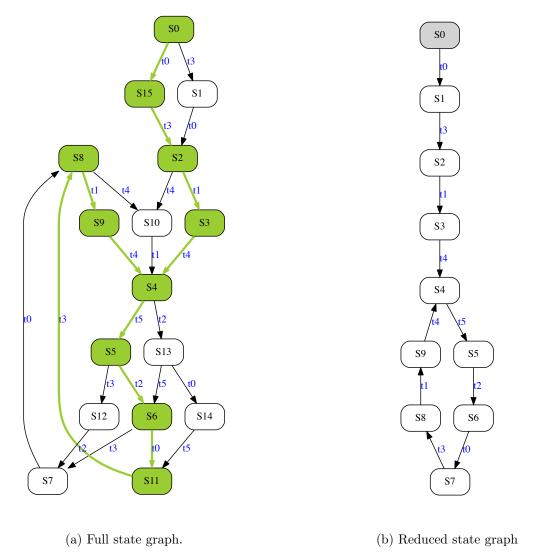

| 5.3  | Full and reduced state graphs for the producer-consumer LPN model                 | 97  |

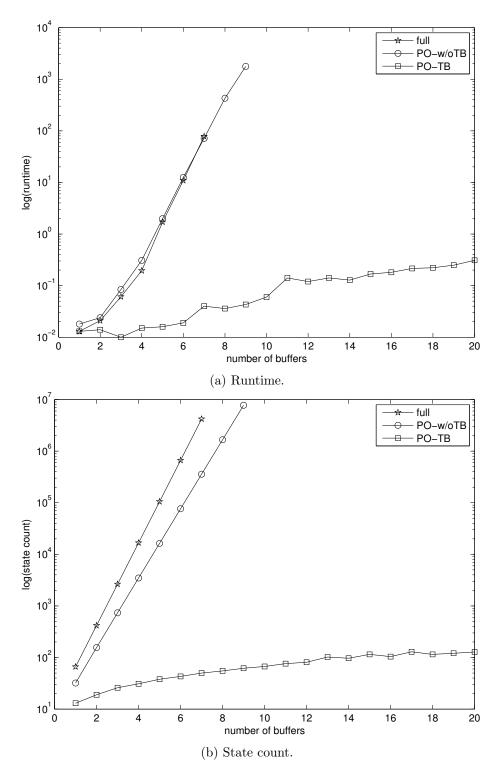

| 5.4  | Runtime and state count for the buffer examples with 1 to 20 buffers              | 100 |

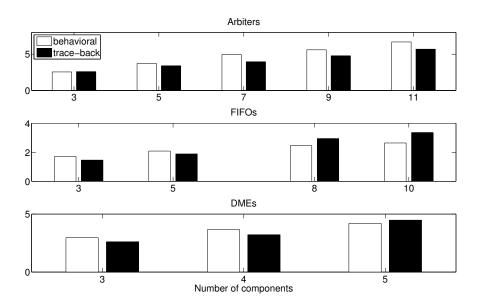

| 5.5  | State count comparison between trace-back and behavioral analysis                 | 102 |

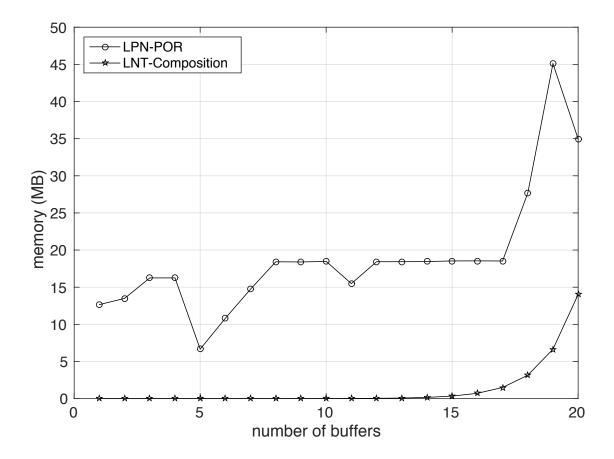

| 5.6  | State counts and runtimes comparisons of the buffer examples with 1 to 20 buffers | 103 |

| 5.7  | Memory comparison of the buffer examples with 1 to 20 buffers                     | 104 |

| 5.8  | VHDL entity for the arbiter with two inputs                                       | 106 |

| 5.9  | Partial Vhdl entity for the two-input arbiter with negative acknowledgement. | 107 |

|------|------------------------------------------------------------------------------|-----|

| 5.10 | Vhdl entity for the NoC PE router of node 10                                 | 108 |

| 5.11 | Vhdl entity for the west router of node 10                                   | 110 |

# LIST OF TABLES

| 4.1 | LTSs of the two-by-two NoCs generated for the verification of deadlock freedom and one-fault tolerance                          | 81  |

|-----|---------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.2 | Labels of the LTS's corresponding to two-by-two NoCs generated for the verification of deadlock freedom and one-fault tolerance | 83  |

| 5.1 | Results for several asynchronous circuits models                                                                                | 101 |

# LIST OF ALGORITHMS

| 5.1 | Ample set $ample(s)$ computation                 | 90 |

|-----|--------------------------------------------------|----|

| 5.2 | Dependent set $dependent(s, t, d)$ computation   | 93 |

| 5.3 | Necessary set $necessary(s, t_i, d)$ computation | 94 |

#### ACKNOWLEDGMENTS

I would like to thank my PhD advisor, Chris Myers. Chris introduced me to the world of formal verification after I joined his research group, and has been patiently guiding me to explore new knowledge in this field throughout my Ph.D. His guidance has significantly helped me to acquire necessary skills to become a fine scholar. He taught me many things, including academic paper writing, research presentation, and conducting paper reviews. Most importantly, he taught me practical principles of analyzing a given complex engineering problem: always start with a small and simplified version, and gradually build up the understanding of the whole problem. I will forever be grateful to him for assisting me in achieving my PhD.

I would not be the person I am today if it were not for my family. My wonderful parents, Ling Zhu and Chunning Zhang, have been a great source of unconditional and continuous love and support throughout my life. I will be forever indebted to their great effort in providing me the best education opportunities.

I would also like to thank my lab mates, Curtis Madsen, Nicholas Roehner, Andrew Fisher, Leandro Watanabe, and Tramy Nguyen. They each helped me to really become part of the group. Curtis and Nic generously invited me to dinner parties on major American holidays, provided an outlet to discuss frustrations, and hosted many fun board game nights. Curtis was also a great companion for discussions on my research work. Nic shared many of his thoughts with me on diverse topics from philosophy, music, and science fiction. Andrew taught me numerous topics on mathematical foundations related to my own work and helped me to get my thoughts straight. Leandro and Tramy provided discussions on topics of good software practice for my Synthetic Biology Open Language Java library project. In addition, I would like to thank the rest of my lab mates, Dhanashree Kulkarni, Robert Thacker, Satish Batchu, and Kevin Jones for their help on the Lema tool; and Xiaojun Sun, Jinpeng Lv, and Tim Pruss for conversations on computer algebra.

I would like to thank my committee, Wendelin Serwe, Hao Zheng, Ken Stevens, and Priyank Kalla. Wendelin taught me process algebra and has been a source of inspiration on many intellectually challenging problems. Hao exposed to me many verification techniques that also inspired my own research work. Ken and Priyank provided valuable feedback on my thesis and ideas for some future work.

Finally, I would like to thank all the past members of the lab who contributed to Lema. Without their work, this work would not be possible. In particular, I would like to thank Satish Batchu, Kevin Jones, Dhanashree Kulkarni, Robert Thacker, Scott Little, and David Walter for their contributions to Lema.

This material is based upon work supported by the National Science Foundation under grants CNS-0930510 and CNS-0930225. Any opinions, findings, and conclusions or recommendations expressed in this material are those of the author(s) and do not necessarily reflect the views of the National Science Foundation. Part of this work was performed during my visit at the Inria Grenoble-Rhône-Alpes research centre.

### CHAPTER 1

### INTRODUCTION

A cyber-physical system (CPS) is characterized by the tight interaction between a digital computing component (the cyber part) and a continuous-time dynamical system (the physical part). A CPS uses networked embedded computers to monitor the physical processes through feedback loops and issues adjustment control signals to them accordingly [1]. CPSs nowadays have ubiquitous applications in many areas, such as avionics, advanced automotive systems, robust medical devices, etc. One active area of CPS application is in the automotive industry. Modern vehicles can have up to 80 electronic control units (ECUS) that control and operate everything from the engine and brakes to door locks and electric windows. Currently, each ECU is statically tied to its specific sensors and actuators. This means that processing power between different ECUs cannot be shared, which may degrade the performance of the chip due to imbalanced workload on each ECU. More importantly, this structure is susceptible to faults as if an ECU fails, it causes a malfunction in the corresponding sensor/actuator. With the advances in semiconductor technology, it is now possible to have multiple cores on a single chip which communicate using a Network-on-Chip (NoC) paradigm. A NoC approach allows flexible mapping between ECUs and sensors/actuators, which makes it possible for Ecus to share processing power and tolerate faults by having spare units. Designing a fully functional NoC system is challenging. Specifically, the routing algorithm implemented on the NoC structure has to be fault-tolerant and guarantee deadlock freedom. Adding fault-tolerance adaptivity to a routing algorithm increases its design complexity and makes it prone to deadlock and other problems if improperly implemented.

## 1.1 Model Checking

To guarantee functional correctness of a complex NoC routing algorithm, formal verification techniques are needed to reason about its concurrent behavior. *Model checking* is an automated technique for the verification of finite-state systems. It involves three tasks [2]: modeling, specification, and verification. A mathematical model of the system of interest is constructed using some formalism, such as *labeled transition systems*, *Petri nets*,

Büchi automata, etc. Model construction can be automated as a compilation task from a high-level language to the language specified by the formalism. The next step is to specify properties that the system must satisfy. Temporal logic has been widely used as a formalism for this purpose, due to its ability to specify the system behavior over time. The last step is to automatically build the state space of the system model, which means exhaustively enumerating all states that are reachable by the model and all transitions in which the system evolves from one state to another. The properties can be checked during or after the state space construction of a model. If a violation of a property is identified, the model checker usually terminates and reports a counterexample to the user. A counterexample is an error trace consisting of a sequence of states and transitions that start from the initial state to the state with the property violation. Many model checkers are capable of providing accurate and shortest error traces to the user for debugging purposes. One advantage of model checking is that it automates many verification tasks and does not rely much on user's special skills. The only places where human assistance is needed are specifying the properties and analyzing the verification results. Also, many different kinds of properties can be verified from the constructed state space of the system model [2, 3].

Model checking has been successfully applied to the verification of a variety of hardware and software systems over the past few decades. It, however, suffers from the fundamental difficulty of the state explosion problem for large-scale designs. This problem occurs when the generated states during model checking become too large to fit into the computer memory. Roughly speaking, the size of a state space grows exponentially with the number of processes and variables in a system [2]. For example, for a system with n concurrent processes, each of them having  $\alpha$  states, then the state space for that system can be as large as  $\alpha^n$ . Many techniques have been developed in recent years to address the state explosion problem. Symbolic model checking [4, 5] has proven to be a powerful technique to deal with the state space problem. Specifically, symbolic state representation such as ordered binary decision diagrams (OBDDs) [6] has provided a compact form for Boolean formulas. Efficient algorithms [7] have been developed based on OBDDs to verify designs with extremely large state spaces. Bounded model checking (BMC) [8] is another flavor of symbolic model checking that is based on propositional decision procedures (SAT) [9]. The basic idea of BMC is to generate a propositional formula from a counterexample of a bounded length, and check the propositional formula with a SAT solver. A satisfiable formula reported by the SAT solver represents a concrete counterexample showing the property violation. Otherwise, the bound is increased and the process repeats. Complete extensions to BMC allow one to stop this process at some point, with the conclusion that the property cannot be violated, hopefully before the available resources are exhausted. Compositional verification techniques address the state explosion problem from a different perspective. They either avoid generating the global state space by performing local analysis on each component's state space, e.g. [10-12], or iteratively construct and minimize the local state space for a component and compose it with other components to gradually form the state space for the whole system, e.g. [13, 14]. Abstraction [15, 16] computes an overapproximation of the original model by building a small set of data values from the actual data values in the system based on a specified mapping, and the resultant smaller system is used to verify properties at an abstract level with less complexity [2]. Symmetry reduction [17–19] exploits the symmetry relation to construct equivalence class representatives in the model, and limits the state search to them in order to save memory and runtime. Partial order reduction (POR) [20-25], has been proven to successfully reduce the state space for systems with concurrency, such as most asynchronous systems. It exploits the commutativity of concurrently executed transitions, which reach the same state when executed in a different order. Only one such order is selected and executed, and thus the resultant state space is significantly smaller than that generated by exploring all possible orders. There has been research work on combining the said state reduction methods for better reductions. A combination of POR with symmetry reduction in [26] shows a much smaller reduced state space than that obtained from applying either method individually. Valmari [27] proposed a similar idea for deadlock detection for colored Petri-nets. Por techniques have also been applied to symbolic BDD-based invariant checking [28]. An approach that combines compositional analysis with Por [29] extracts dependency information from each component of a system and forms compositional rules for global dependency information. Offline Por has also been combined with BMC techniques to show that threshold-based distributed algorithms have a similar execution of bounded length [30, 31].

#### 1.2 Contributions

Formal verification techniques are therefore needed to verify its correctness. This dissertation proposes a link-fault-tolerant, multiflit wormhole routing algorithm, and its formal modeling and verification using two different methodologies.

Improving upon Glass and Ni's routing algorithm [32] that assumes node faults, this dissertation proposes a routing architecture extending that introduced by Wu et al. [33] to a multiflit wormhole setting. It loosens Glass and Ni's impractical assumption to achieve

link-fault tolerance, covering a wider range of link fault cases that Glass and Ni's algorithm fails to handle. Deadlock avoidance is implemented conservatively with adequate packet drops to break the cycle of dependencies. Simulation results indicate that this algorithm provides significant improvements in network reliability with minimal cost.

This link-fault routing algorithm is modeled in the process-algebraic language LNT [34]. With the help of the CADP verification tool box, formal analysis exposes design flaws leading to false behaviors such as a packet leakage path leading to unintended packet drop and deadlock caused by removing arbiter's buffering capacity. To combat the notorious state explosion problem, a data abstraction technique [35] is applied to map the destination coordinates of a packet to a Boolean value representing its diversion status. Mismatch between the abstract and concrete models leads to the discovery of a potential livelock problem due to redundant packet diversions. Elimination of these diversions leads to an improved algorithm that simplifies the routing architecture, enabling successful compositional verification. The routing algorithm is proven to have several desirable properties, including deadlock and livelock freedom, and tolerance to a single-link-fault [36].

As a comparison, the derived livelock-free routing protocol is modeled using the channel-level Vhdl that is automatically compiled to labeled Petri-nets (LPNs) [37, 38] for verification using the Lema tool. Algorithms are described for an ample set-based partial order reduction (POR) technique, which analyzes transition dependencies through a recursive trace-back search on LPNs. A set with the least number of enabled transitions that need interleaving is selected at each state. Cost and benefit of using trace-back are evaluated on several nontrivial asynchronous circuit models, and are compared to LNT models on a series of buffers that uses asynchronous communication. Although POR achieves significant state reduction on certain arbiter models, it is still outperformed by composition minimization of CADP on the corresponding LNT models. Root cause of the difference is analyzed by comparing the LNT and LPN specifications.

#### 1.3 Dissertation Outline

This dissertation is organized as follows. Syntax and semantics of the two modeling formalisms, namely LNT and LPN, are presented in Chapter 2. Examples of asynchronous channel models are presented in LNT first, and correspondingly, in the channel-level VHDL, which is then automatically compiled to LPNs. Common features and differences of these models are described in this chapter.

Chapter 3 describes Glass and Ni's fault-tolerant routing algorithm on a two-dimensional mesh network, and demonstrates, with examples, how this and other similar routing algo-

rithms fail to handle link-faults. This chapter then describes the proposed link-fault-tolerant routing algorithm and its architectural design. The deadlock avoidance mechanism is explained in detail with some illustrative examples.

The LNT specification of the link-fault model is presented in Chapter 4. Lessons learned during the design process are described, followed by a description of the data abstraction that enables verification of deadlock freedom and single-link-fault tolerance. This chapter then describes the discovery of a potential livelock problem. In the process of eliminating this problem, an improved routing architecture is derived. The improvement simplifies the routing architecture, enabling successful verification using the CADP verification toolbox. The routing algorithm is proven to have several desirable properties, including deadlock and livelock freedom, and tolerance to a single-link-fault.

Chapter 5 describes an alternative way of modeling and verification of the same link-fault-tolerant NoC routing protocol using the Lema tool. It presents in detail a partial order reduction method on Lpns with trace-back that optimally reduces unnecessary transition interleavings for state reachability analysis, avoiding exploring unimportant state-transition sequences. The cost and benefits of using trace-back are evaluated on a series of asynchronous circuits examples. Comparisons of state reduction and performances are drawn between Lnt and Lpn on a series of asynchronous buffer examples. Vhdl models for the representative routers and arbiters are described for the livelock-free link-fault-tolerant routing protocol that is presented in the pervious chapter. They are automatically compiled to Lpns which are used for state exploration by Lema. Although partial order reduction manages to achieve significant state reduction on certain arbiter models, it is still outperformed by composition minimization of Cadp on the corresponding Lnt models. Key observations are made on the comparison of the Lnt and Lpn specifications.

Finally, Chapter 6 concludes this dissertation by giving a summary of the work and by presenting future research directions.

#### CHAPTER 2

### MODELS OF CONCURRENT SYSTEMS

This chapter introduces the underlying model constructs for the behavioral modeling of the NoC routing architecture in subsequent chapters. It starts with a brief introduction of major process algebraic approaches in providing formal syntax and semantics of concurrent systems. The rest of the chapter focuses on describing key modeling constructs in terms of two approaches: the process algebraic language LNT, and the channel-level VHDL that can be automatically compiled to the LPN modeling formalism. Both modeling languages are introduced first with their respective verification environment, followed by a detailed description of communication channels, nondeterministic choice, parallel composition, and a subset of the control structures that are relevant to the modeling of NoC routing architectures.

### 2.1 A Brief Introduction to Process Algebra

Over the last forty years, process algebras have witnessed significant success in providing formal semantics of concurrent systems towards verification and validation. Process algebras are mathematical models of processes that are abstractions of components of a system that continuously interact with each other and with their common environment. A process algebra often provides process terms that are generated from its abstract syntax for specifying components of a system, and an operational semantics that associates each term with a *Labeled Transition System* (LTS) that consists of a set of states, a transition relation, and a set of transition labels. The three main approaches in providing semantics of syntactically correct process terms are operational, denotational, and algebraic semantics, with the operational semantics playing a central role in all process algebras. Moreover, a process algebra usually includes mechanisms for observing behavioral equivalences between two systems or between an abstract and a concrete one.

At its core, the abstract syntax of a process algebra defines operators in that language. It consists of combinations of elementary terms and operators, both of which are the ingredients for building basic process terms. Starting with a set of basic processes and actions, one can build new processes. Common operators in almost all known process algebras include

nondeterministic and parallel compositions of processes; the abstraction operation such as the hiding, restricting, and renaming operators that limit the interface of a process; and modeling infinite behaviors from finite operations.

An operational semantics provides an abstract machine-based view of computation by treating a program as a LTS. Based on structural induction offered by the Structural Operational Semantic (SOS) [39], each process term (or operator) is specified by a set of inference rules that describe its behavior through the behaviors of its composing components, each of which has its own process term that is specified by the corresponding set of inference rules. In fact, each process term can be considered as a component that can interact with other components or with its environment. Regarding its association with a LTS, process algebra terms are represented as states in their corresponding LTSs; actions are described by a transition relation going from a given state to its next possible one; and the visibility of each action is denoted by its corresponding transition label. With features from structural induction, the LTS of a complex system can be composed from its component LTSs. A denotational semantics establishes a mapping from a language to an abstract model so that the meaning of a program is determined by the meaning of each of its immediate subcomponents. Ideally, the abstract model should be able to describe the "essence" of programs in the language that is mapped to it. Semantic clauses for different operators can then be devised in order to specify semantic properties of a program that consists of these operators. An algebraic semantics is defined by a set of algebraic laws that are basic axioms of an equational system.

Behavioral equivalences are useful in proving whether two systems are equivalent or how one system approximates the other. Specifically, during an incremental process of constructing a system's LTS, one can replace a subcomponent by its behaviorally equivalent abstract counterpart without affecting the overall behavior of the system. Built in the definitions of different behavioral equivalences are aspects of behaviors that can or cannot be ignored. It is, therefore, necessary to know the properties that a behavioral equivalence preserves, as process equivalence is defined in terms of what equalities can be proved using them. Families of major behavioral equivalences are reviewed in Chapter 4.

The process algebra Calculus of Communicating Systems (CCS) [40, 41] was introduced by Robin Milner around 1980. Actions in CCS model atomic, two-way communications, i.e., nondivisible communications between exactly two participants, and common operators such as (binary) parallel composition, nondeterministic selection, restriction, and relabeling operations, etc. The basic semantics of CCS is operational where each CCS process term is

associated with a LTS. This allows the development of theories for its behavioral equivalences to be based on LTSS. A successor of CCS,  $\pi$ -calculus [42], was developed by Milner et al. to target the description of concurrent systems with dynamically changing configurations during the computation.

Another well-known process algebra is the Communicating Sequential Processes (CSP) invented by C.A.R. Hoare [43, 44]. It was designed with the goal of providing a notation and theory for the analysis of different components of a system interacting with each other through communication, and has served as a mechanism for understanding and applying concurrency theory extensively over the years. Unlike CCS whose original design was provided with operational semantics, CSP has been given a number of denotational semantics, mainly based on sets of behaviors such as traces, failures, and divergences, which are used for deciding process equivalence. The operational semantics of CSP, heavily influenced by the work on CCS, was historically developed to provide an alternative view in addition to its denotational semantics. Many tools that support CSP both for teaching and industrial applications have emerged over the years, and have contributed significantly to the formal description and (automated) analysis of industrial-sized problems. A comprehensive text on the fundamental theories and applications of CSP can be found in [45]. It is worth mentioning that the maturity of CSP in modeling communication and concurrency lent itself to many other domain-specific languages. For instance, the Communicating Hardware Processes (CHP) by Martin [46], and the Tangram language by van Berkel et al. [47], were adapted from CSP for modeling and designing asynchronous VLSI systems.

Taking from a more abstract and completely different viewpoint of process algebra, the Algebra of Communicating Processes (ACP) [48] provides a purely algebraic approach to concurrency theory. ACP takes process algebra as a mathematical structure, which consists of a set of processes and a set of operators such as sequential, nondeterministic, or parallel composition, communication, etc. All operations satisfy conditions governed by a set of axioms that are usually presented as a set of formal equations. Operational semantics and behavioral equivalences are possible models over which the algebra can be defined and the axioms can be applied.

The Language Of Temporal Ordering Specification (LOTOS) is yet another process algebra that was developed and standardized within International Standards Organization for specifying and verifying communication protocols during the years 1981-1988 [49]. The goal was to provide an unambiguous, precise, and complete formal description language with a well-defined basis for the verification and validation of the Open Systems Interconnection

(OSI) telecommunication standards. Borrowing features from both CSP and CCS, LOTOS handles process behaviors that are common to both process algebras. It uses gates that correspond to CSP channels for specifying communication, and extends this feature to do multiway synchronization that is not in either CCS or CSP; and the nondeterministic choice in LOTOS follows the CCS style with an internal event, but its parallel composition follows the CSP approach [50]. Additionally, it is able to describe data structures and value expressions using abstract data type technique ACT-ONE [51].

### 2.2 Behavioral Modeling and Verification in Cadp

The Construction and Analysis of Distributed Processes<sup>1</sup> (CADP) toolbox has been employed in many industrial projects for the design and analysis of asynchronous concurrent systems. More than 150 case-studies have been published, covering a wide range of applications, such as shared-memory mutual exclusion protocols [52], mobile ad hoc networks [53], dynamic management protocol for cloud applications [54], and logical regulatory modules for intercellular networks in Biology [55]. The modeling formalism is the LNT language, a process algebraic formal specification language that has been developed and implemented in the CADP toolbox since 2005. The LNT language has its roots in the LOTOS language. The LOTOS language, however, has limited data types that do not meet the users' needs and cannot handle real-time constraints. Extensions with significant improvements to the LOTOS language have been made and included in the LNT language, such as fully imperative syntax and semantics, the Rich Term Syntax notations, etc. The Rich Term Syntax notations allow complicated data types to be expressed naturally in LNT, compared to the LOTOS abstract data types. One example is the limited range of integers, i.e., integers between 0 and 9, in the LOTOS NATURAL library. To express numbers greater than 9, one has to use Succ. For instance, the natural number 12 in LNT is expressed as Succ( Succ( Succ (9))) in LOTOS. The Rich Term Syntax also provides standard notations for literal constants (e.g., lists, sets, strings) in LNT. Combining features from process calculi, and both functional and imperative languages, the concise and expressive power of the LNT language gives it many advantages in formally specifying complex concurrent systems.

Figure 2.1 shows a subset of tools from the CADP toolbox for model checking of a LNT model. The input LNT model is translated into a LOTOS specification in two steps: the LPP tool first expands the Rich Term Syntax notations in the LNT model into lower-level algebraic terms that are compatible with the LOTOS syntax, after which the LNT2LOTOS

<sup>1</sup>http://cadp.inria.fr

Figure 2.1: CADP tool flow.

tool translates the preprocessed LNT specification into a complete LOTOS specification. It is then compiled by the abstract data type compiler Cæsar. Add, which translates the data part of the Lotos specification into C types and functions. They are used by the Cæsar tool to compile the behavioral part of the Lotos specification into either a C program or a Labeled Transition System (Lts). The C program can be executed and simulated, as well as embedded in real applications to allow rapid prototyping. The Lts can be used for equivalence checking and/or model checking with temporal logic properties. Stored as the Binary Coded Graph (BCG) format, a Lts can be minimized by the BCG\_MIN tool according to strong, branching, or divergence-sensitive branching bisimulation relations. To model check a temporal logic property expressed as Model Checking Language (MCL) formulas, the EVALUATOR4 tool performs on-the-fly verification on the given Lts, and produces the verification results (true or false). A false result may optionally be accompanied by a counterexample in the form of a transition sequence or an Lts. Cadp features the Script Verification Language (SVL) [56], which automates invocations of all aforementioned tools.

#### 2.2.1 Lnt Module

A module in the LNT language is the basic building block for specifying models of a system. It is formally defined as

```

Int\_file ::= module M[(M_0, ..., M_m)]

[with predefined\_function_0, ..., predefined\_function_n] is

module\_pragma_1 ... module\_pragma_p

definition_0 ... definition_q

end module

```

where  $(M_0, ..., M_m)$  is a set of imported module identifiers. All definitions in the imported modules are visible to module M and can be used by definitions in this module. Predefined functions defined by the LNT\_V1.lib library provide data operations over both the six basic types, i.e., Booleans, natural numbers (Nat), integers (Int), real numbers (Real), characters (Char), and strings (String), as well as nonbasic types, e.g., list, sorted list, set. Details of these functions are described in Chapter 5 and Appendix C of [34]. Module pragmas can modify the default ranges of the three predefined types: natural numbers, integers, and strings. For example, "!nat\_bits 3" limits the number of bits to 3 for all variables of type Nat, and "!string\_card 5" limits the maximal cardinality of String to 5.

Each definition in a module defines one of the four entities: type, function, channel, or process. The type and function definitions allow specifications of customized data types and their operations, and the channel definition allows one to specify a set of gate profiles with custom gate types. These entities are described here informally with examples, and their grammar and semantics are defined in [34]. The process definition is given detailed explanations in the following sections.

In the following example, a data type NodeRange is defined as a closed range [0,4] of natural numbers, and Coordinates is defined as a pair of natural numbers, each of type NodeRange. The Coordinates type declares predefined functions get to retrieve its x and y values, and the infix function "!=" to do inequality check based on structural equivalence between two values of type Coordinates. The infix function "+" defines the addition operation of two values typed NodeRange as being added as natural numbers, and returns the result in NodeRange type.

```

module datatypes is

type NodeRange is

range 0 .. 4 of Nat

end type

type Coordinates is

Coordinates(x: NodeRange, y: NodeRange)

with "get", "!="

end type

function _+_ (x, y: NodeRange) : NodeRange is

return NodeRange (Nat (x) + Nat (y))

end function end module

```

A channel is defined as a set of gate profiles, each of which defines a list of gate types. Consider the type T and channel C, defined as follows:

```

type T is

Request, Response

end type

channel C is (T) end channel

```

The channel C includes two gates, namely "Request" and "Response". Two gates are considered as having compatible type, if and only if both are polymorphic or are declared with the same channel identifier. A channel is similar to the VHDL port declaration described in Section 2.3.1.

#### 2.2.2 Lnt Process

A system's behavior can be described using LNT processes, formally defined as follows:

```

process\_definition ::= \mathbf{process} \ \Pi \ [ \ [ gate\_declaration_0, ..., gate\_declaration_m ] \ ] \ [ \ ( formal\_parameters_1, ..., formal\_parameters_n ) \ ] \ [ \ \mathbf{raises} \ exception\_declaration_0, ..., exception\_declaration_k \ ] \ \mathbf{is} \ process\_pragma_1...process\_pragma_l \ B \ \mathbf{end} \ \mathbf{process}

```

where the process has a unique identifier  $\Pi$ , and can optionally be parameterized by a list of formal gates, a list of formal variables, and a list of formal exceptions. The optional list of process pragmas provides instructions for translating LNT source code to LOTOS and C. The process body B describes the behavior.

Gate declarations specify all communicating gates that are visible to other processes. Formal gate parameters must declare their types, which can be either a channel  $\Gamma$  or a polymorphic type using the **any** keyword:

$$gate\_declaration ::= G_0, ..., G_n : \Gamma$$

$$\mid G_0, ..., G_n : \mathbf{any}$$

Each of the formal parameters in the process definition can be declared with one of the three modes: the default mode in denotes a constant parameter whose value can be changed locally by a process and the change remains invisible to other processes; the out mode requires a parameter to be assigned to a value locally, and the value is visible outside the process after its execution terminates; and the inout mode describes a modifiable parameter, which has an initial value that may be modified by a process locally and is visible after the process termination. For the behavior description B, this chapter highlights behaviors related to the modeling of communication, concurrency, and certain control structures. The complete description of behaviors is shown in Chapter 7 of [34].

#### 2.2.3 Channel-Level Communication in LNT

The LNT language uses multiway gate rendezvous with data exchange to model communications between different processes. Two-way gate rendezvous can be used for modeling the channel-level communication. The behavior expression "G [  $(O_0, ..., O_n)$  ] [where V ]" specifies a potential rendezvous on gate G. Data exchange at a gate rendezvous is described as a list of offers  $O_0, ..., O_n$ . The optional condition expression V has to evaluate to **true** for the gate rendezvous to take place, and this expression uses values received by the offers  $O_0, ..., O_n$ . An offer is either output or input, defined as:

$$O ::= [X \Rightarrow] [!]V$$

$$|[X \Rightarrow]?P$$

where an output offer, "[!]V", describes an emission of value expression V and an input offer, "?P", corresponds to the reception of a value matching pattern P. There are two effects of the pattern matching of a value V with a pattern P: it returns a **true** if V has the same structure as P, otherwise it returns a **false**; if V matches P, the variables used by P are initialized with the values extracted from V. Detailed grammar of patterns and their corresponding matching effects are provided in Chapter 6 of [34].

The semantics of gate rendezvous is that the communication is blocked by values in the offers on both sending and receiving ends waiting for the rendezvous, and the corresponding process executions are suspended until the rendezvous takes place. In general, LNT does not differentiate the sender and the receiver, and it is possible to have both sending and receiving offers on one gate.

In order to specify the connections among multiple processes, the parallel composition construct can be used. The grammar for the parallel composition has the following form:

Each gate specified by the optional global synchronization gate set " $\{G_0, ..., G_n\}$ " requires that it appears in the gate declaration in every behavior that participates in the parallel composition. A global synchronization gate communication occurs if and only if all behaviors " $B_0, ..., B_m$ " can make this communication simultaneously. Omission of the global synchronization gate set means no such gate exists in the parallel composition. Each behavior  $B_i(\forall i \in [0, m])$  has an optional synchronization interface consisting of the set of gates  $\{G_{(i,0)}, ..., G_{(i,n_0)}\}$ . A gate communication in a behavior's synchronization interface can happen if and only if all behaviors specifying this gate in their respective communication interfaces can make this communication simultaneously. Omission of a synchronization interface of behavior  $B_i$  means that its synchronization is empty. The global synchronization gate set is a shorthand notation for gates that appear in every behavior's synchronization interface. Any behavior in the parallel composition can instantiate a process with the form:

$$\Pi \ [ \ [\mathit{actual\_gates}] \ ] \ [ \ (\mathit{actual\_parameter}_1, \ldots, \mathit{actual\_parameter}_n) \ ]$$

where process  $\Pi$  is instantiated with its gates and optional parameters substituted by  $actual\_gates$  and a list of actual parameters.

A producer-consumer example is shown in Figure 2.2. The top-level Lnt module,

Figure 2.2: Block diagram for the producer-consumer example.

"producer consumer", specified in Figure 2.3, implements this block diagram by instantiating one producer, two buffer, and one consumer processes, which are specified in Figure 2.4. It connects these instantiated processes through actual gates listed in their respective synchronization interfaces. Note that one of the modules in a model specification must be the principle module where the root process is included. The root process is a process with no value parameters and is named main. Each of the producer, the buffer, and the consumer processes has a *loop* construct that makes the process repeat infinitely without exiting. The producer process first declares an internal variable data, and then initializes it with a nondeterministic assignment that returns a value of type Nat ranging from 0 to 3. It then emits this value as an offer on the p\_to\_b gate. Connected to this gate is the input gate buf in of the buffer process. Both gates are replaced by the actual gate producer to buf1 when their processes are instantiated in the producer consumer module. Both processes have to simultaneously agree on a rendezvous on this gate. The input offer in a gate rendezvous uses pattern matching, which only admits offers that match its specified pattern. If the buffer process expected a Boolean input value instead, such as buf in (?any Bool), the gate rendezvous could never take place due to matching failure. A successful pattern matching assigns values of the sender's offers to variables used by the receiver's pattern. In this example, a rendezvous on gate producer to buf1 assigns the value stored in the producer's local variable data to the first buffer's local variable data. On receiving the value from the producer, this buffer is ready to relay it to the second buffer by doing a gate rendezvous between its output gate buf out and the second buffer's input gate buf in. In a similar fashion, the value is finally passed to the consumer. Note that in the buffer process, a sequential composition of two rendezvous gates, i.e., "buf in(?data); buf out(data)", implies that buf in (?data) is executed first, and if it terminates normally, then buf out(data) is executed with the variable value updated by buf in (?data). This ensures that the correct value is passed from the input to the output of a buffer.

Another feature of the parallel composition construct is that all behaviors " $B_0, ..., B_m$ " placed in parallel run concurrently. For example, a gate rendezvous on producer\_to\_buff1 occurs between producer and the first buffer, and simultaneously the second buffer and consumer may communicate on gate buff2\_to\_consumer.

#### 2.2.4 Nondeterministic Choice in LNT

The nondeterministic choice among a finite number of behaviors  $B_1$ , ...,  $B_n$  is expressed as **select**  $B_1$  [] ... []  $B_n$  **end select** in LNT. It first executes all choices of behaviors

```

module top(producer, consumer, buffer) is

process main [producer to buf1, buf1 to buf2, buf2 to consumer : any] is

producer to buf1 ->

producer [producer to buf1]

producer to buf1, buf1 to buf2->

buffer [producer to buf1, buf1 to buf2]

buf1 to buf2, buf2 to consumer ->

buffer [buf1 to buf2, buf2 to consumer]

buf2\_to consumer ->

consumer [buf2 to consumer]

end par

end process

end module

```

Figure 2.3: Top-level LNT process for the producer-consumer example.

```

module producer is

process producer [p_to_b : any] is

loop

var data : Nat in

data := any Nat where (data <= 3);

p to b(data)

end var

end loop

end process

end module

module buffer is

process buffer [buf in, buf out : any] is

loop

var data : Nat in

buf in (?data);

buf out (data)

end var

end loop

end process

end module

module consumer is

process consumer [b to c: any] is

b to c(?any Nat)

end loop

end process

end module

```

**Figure 2.4**: Producer, buffer, and consumer LNT processes for the producer-consumer example.

Figure 2.5: Block diagram for the modified producer-consumer example.

$B_1$ , ...,  $B_n$ , and the first action (i.e., gate rendezvous, internal action, or termination) executed by one of the behaviors determines the result of the choice.

As an example, the producer-consumer example is modified to give both the producer and consumer a choice to send to or receive from two data buffers. The block diagram is shown in Figure 2.5. The LNT specification is presented in Figures 2.6 to 2.8. The producer process now repeatedly selects to communicate with one buffer: the data are sent only to a buffer whose input gate is ready for synchronization; if both input gates of the two buffers are ready, the choice is nondeterministic; if neither gate is ready, then the producer process blocks until one buffer's input gate becomes ready. Note that the choice is nondeterministic only when both buffer's inputs are simultaneously ready to communicate with the producer. It is, however, deterministic when only one buffer's input is ready.

If one wants to model a choice that is independent of the gate rendezvous availability, an internal action i can be inserted as the first action for each choice behavior. In the producer process, both internal actions are always ready to execute without needing to wait

**Figure 2.6**: Producer LNT process with nondeterministic choice.

```

module consumer is

process consumer [b1_to_c, b2_to_c: any] is

loop

select

b1_to_c(?any Nat)

[]

b2_to_c(?any Nat)

end select

end loop

end process

end module

```

Figure 2.7: Consumer LNT process with nondeterministic choice.

```

module top(producer, consumer, buffer) is

process main [producer to buf1, producer to buf2,

buf1 to consumer, buf2 to consumer : any | is

producer_to_buf1 , producer_to_buf2 ->

producer[producer_to_buf1, producer_to_buf2]

producer_to_buf1 , buf1_to_consumer ->

buffer [producer to buf1, buf1 to consumer]

producer to buf2, buf2 to consumer ->

buffer [producer to buf2, buf2 to consumer]

buf1 to consumer, buf2 to consumer ->

consumer [buf1 to consumer, buf2 to consumer]

end par

end process

end module

```

Figure 2.8: Top-level Lnt process with nondeterministic choice for the modified producer-consumer example.

to synchronize with other gates. This is shown in Figure 2.9. Once an internal action is executed to resolve the choice, the producer only waits on communicating with one buffer, even though the other one might already be ready to synchronize.

#### 2.2.5 Conditional Behaviors and Repetition in LNT

Conditional behaviors are usually used to model systems with conditional flow controls. The most common conditional behaviors in LNT are the *if* and *case* constructs. The *if* construct has the following grammar:

Figure 2.9: Producer LNT process with internal nondeterministic choice.

```

[only]if V_0 then B_0

[ elsif V_1 then B_1

...

elsif V_n then B_n ]

[ else B_{n+1} ]

end if

```

where each of the expressions  $V_0, ..., V_n$  must evaluate to Boolean type. Another conditional behavior is the *case* construct. It is equipped with the pattern-matching feature like most functional languages. The *case* behavior has the following form:

```

case V in  [ \mathbf{var} \ var\_declaration_0, ..., var\_declaration_n \ \mathbf{in} \ ]   match\_clause_0 \ -> \ B_0   | \ ...   | \ match\_clause_m \ -> \ B_m  end case

```

where the first behavior whose matching clause evaluates to **true** is executed. A match clause has either a specific or generic pattern. The generic pattern is identified by the keyword **any**:

```

match\_clause ::= P_0 [ where V_0 ] | ... | P_n [ where V_n ] | any [ where V ]

```

Figure 2.10: Producer LNT process with the case behavior.

An expression matches "P where V" if it first matches the pattern P, and the evaluation of V in the context of variables bound by the matching returns the Boolean value  $\mathbf{true}$ .

Figure 2.10 shows a producer process with the case behavior. The process starts by assigning an initial value of 3 to variable data. It then repeatedly executes the case behavior to perform pattern matching on the value of data. The function Succ takes a natural number and returns its successor number. It is an example of a constant pattern. Pattern-matching of a value V with a constant pattern  $F(P_0, ..., P_n)$  returns a Boolean value **true** if it is equal to the value, or false otherwise. To make it clear to explain, let us rename the argument of this function to data' for the moment. For the value of data to match this constant pattern, it has to be equal to the value returned by this function, i.e., data = Succ(data'). It is obvious that data' has to be the predecessor of data to satisfy this condition. The case pattern Succ(data) then binds the value of variable data to that of data', effectively reassigning data the value of its own predecessor. Since the behavior is a repeated loop, this value is reused for the next iteration of the case behavior. Matching of the "Succ(data)" pattern keeps occurring in each iteration, which decrements the value of "data" by 1 until it becomes 0. After its value reaches 0, the next iteration of the case behavior fails to match this pattern since no natural number's successor is 0. Matching of the generic pattern occurs instead and the value is reset to 3. The behavior of this producer is that it repeatedly does the following sequence of steps: it first sends values 2, 1, 0 on gate "p to b1", and then sends value 0 on gate "p to b2".

The LNT language supports several repetition behaviors. The previous examples have shown the forever loop, i.e. "loop  $B_0$  end loop". This behavior is useful especially for modeling hardware processes, which usually execute their instructions forever. On the

Figure 2.11: Producer LNT process with repetition behaviors.

other hand, a breakable loop "loop L in  $B_0$  end loop" can exit on a loop break behavior "break L". Conditional loops include while and for loops, and their definitions and semantics are detailed in [34]. Figure 2.11 shows a breakable loop L nested inside a forever loop for a producer process. It exits when the value of "data" decrements to 0. This producer repeatedly sends value 2 on gate "p to b1", and then sends value 1 on gate "p to b2".

### 2.3 Behavioral Modeling and Verification in Lema

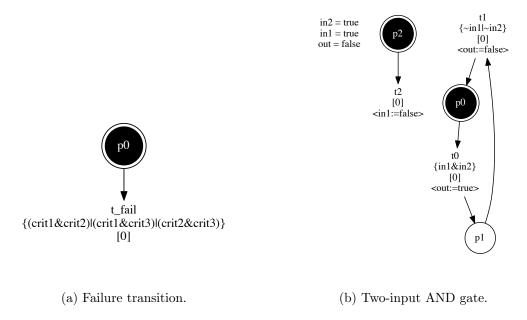

The LPN Embedded Mixed-signal Analyzer (LEMA) tool has been developed for the formal modeling and verification of speed-independent asynchronous circuits [57], timed circuits [58–60], analog-and-mixed-signal circuits [61, 62], assembly language software [37, 63], and genetic circuits [64, 65]. This tool supports, among many others, models described in the channel-level VHDL [66]. Drawing inspirations from CSP, the channel model added the notion of the probe operations [67]. VHDL stands for VHSIC (Very High Speed Integrated Circuits) Hardware Description Language. It was originally developed by the U.S. Department of Defence as a means to document the behavior of integrated circuits in the mid-1980s. It has become one of the industry's standard languages for describing digital systems. It has built-in parallelism to assist concurrency modeling of hardware systems. Taking a high-level VHDL model description, the LEMA tool compiles it into LPNs [68, 69] that are used for model checking as shown in Figure 2.12. State reachability analysis is performed on the set of LPNs, with the option of applying on-the-fly state reduction techniques such as automatic abstraction [37], partial order reduction, and compositional minimization [57]. If a deadlock, or a violation of a safety property is found, a counterexample consisting of a state-transition

Figure 2.12: Lema tool flow.

sequence that leads to the failure state is returned. Deadlock is reported when a state without any outgoing transitions is found. The safety property that can be checked during the reachability analysis is encoded by a *failure transition*, and it is the enabling of such a transition that causes a safety property violation. Alternatively, a *Reduced State-transition Graph* (RSG) is generated from the reachability analysis.

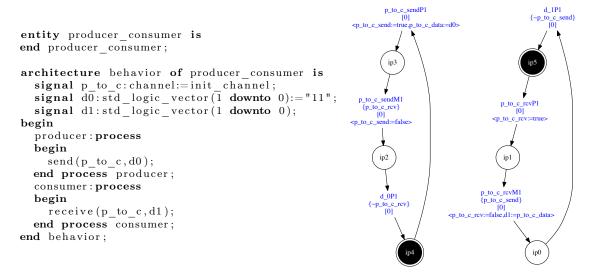

#### 2.3.1 Channel-Level Communication in VHDL

The channel-level communication in Vhdl describes point-to-point communication involving data exchange between two concurrently operating processes. A channel provides a means for two-way communication: it allows both participants to perform synchronization operations for passing data from one end to the other. Figures 2.13 to 2.16 show the Vhdl description for the same producer-consumer LNT example in Figures 2.3 and 2.4, whose block diagram is shown in Figure 2.2. The first three lines of comments in Figure 2.13 indicate the name of the file.<sup>2</sup> The next line indicates that the standard IEEE library is used, and it is followed by a line defining the standard logic data type. The next two lines include the nondeterminism and the channel packages which are described in Appendix A of [66]. The nondeterminism package defines functions for producing random delays or selections for simulations. The channel package defines data types and operations on channels.

The remaining part of this VHDL file describes a design *entity* that consists of an *entity* declaration and an architecture body. The entity declaration is used to describe the interface of a design. In this example, it is simply empty because the entire system does not have any inputs or outputs. The architecture body describes the entity in one of the following ways: behavioral, structural, or a combination of both. It consists of a declaration section and a concurrent statement section. The declaration section can include definitions of signals, constants, etc., as well as components that declare other lower-level entities that can be

<sup>&</sup>lt;sup>2</sup>In VHDL, comments start with "-" and extend to the end of the line.

```

-top-level\ entity\ -

library ieee;

use ieee.std logic 1164.all;

use work.nondeterminism.all;

use work.channel.all;

entity top is

end top;

architecture structure of top is

component producer

port(p to b : inout channel);

end component;

component buf

port (buf_in

: inout channel;

buf out : inout channel);

end component;

component consumer

port(b to c : inout channel);

end component:

signal producer to buf1 : channel := init channel;

signal buf1 to buf2 : channel := init channel;

signal buf2_to_consumer : channel := init_channel;

begin

THE PRODUCER: producer

\mathbf{port}\ \mathbf{map}(\mathtt{p\_to\_b} \Rightarrow \mathtt{producer\_to\_buf1});

BUF1 : buf

port map(buf_in => producer_to_buf1,

buf out \Rightarrow buf1 to buf2);

BUF2 : buf

port map(buf in \Rightarrow buf1 to buf2,

buf_out => buf2_to_consumer);

THE CONSUMER : consumer

port map(b_to_c => buf2_to_consumer);

end structure:

```

Figure 2.13: Top-level VHDL entity for the producer-consume example.

instantiated. Like the LNT language, hierarchical modeling support in VHDL allows entities to be instantiated and composed by a top-level structural entity. Three components, namely "producer", "buf", and "consumer", are declared by this top-level entity "top". The entity declaration for the producer specifies its interface by declaring its port "p\_to\_b1". The component declaration is followed by signal declarations of the three channels that are shared between the producer and the first buffer, the first buffer and the second buffer, and the second buffer and the consumer, respectively, which correspond to the labels on the block diagram shown in Figure 2.2. The concurrent statement part makes instantiations of one producer, two buffers, and one consumer. An instantiation begins with the instance name followed by a component name. For example, the first buffer is named "BUF1" and is an instance of the buf component. The next part is the port map, which associates ports in each instantiated component with the signals declared in the top-level entity. The "buf\_in" port of the "BUF1" instance is connected to "producer\_to\_buf1", which also connects the

```

library ieee;

use ieee.std_logic_1164.all;

use work.nondeterminism.all;

use work.channel.all;

entity producer is

port(p_to_b : inout channel := init_channel);

end producer;

architecture behavior of producer is

signal data : std_logic_vector(1 downto 0) := "11";

begin

producer : process

\mathtt{data} \mathrel{<=} \mathtt{selection} \, (\, 4 \, , 2 \, ) \, ;

wait for delay (5,10);

send(p_to_b, data);

end process producer;

end behavior;

```

Figure 2.14: Producer VHDL entity for the producer-consume example.

the "p\_to\_b" port of the producer instance named "THE\_PRODUCER". The rest of the instantiations for other entities are similar.

The VHDL description for the producer is shown in Figure 2.14. The entity declaration section for the producer specifies its interface by declaring its port:  $p\_to\_b$ . A port declaration defines its data flow direction, i.e. in for an input, out for an output, and inout for either an input or an output. In this example, every channel is set to inout to allow signals to flow in both directions. Bidirectional flow is necessary because although data always flows in one direction, the handshake communication signals on each channel flow in both directions. The next part of the port declaration is the port types. The port for the "producer" entity has a channel type, and is initialized by the function call init channel. Port initialization here is optional. Similar port declarations are specified in the entity declarations for the consumer and buffer entities, respectively. The architecture body begins with a signal definition, "data", that stores the value that is passed between communicating blocks. It is of type  $std\_logic\_vector$  which is an array of  $std\_logic$  signals. The std logic type has nine values, including the binary values 0 and 1, unknown value X, the uninitialized value U, the "don't care" value "-", the high impedance value Z, and symbols indicating weak strength signals (e.g., L for weak 0, H for weak 1, and W for weak unknown). The std logic type is defined in the  $std\_logic\_1164$  package of the IEEE library. The value for each of the signals is encoded by a 2-bit-wide std logic vector. The value stored in "data" is sent out by the producer, and is initialized to "00".

The concurrent statement section, started with "begin" and ended with "end behavior", describes the behavior of each entity in this example with a process statement. A process

```

library ieee;