# ABSTRACTIONS AND STRATEGIES FOR ADAPTIVE PROGRAMMING

$\mathbf{b}\mathbf{y}$

Saurav Muralidharan

A dissertation submitted to the faculty of The University of Utah in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

$\mathrm{in}$

Computer Science

School of Computing

The University of Utah

December 2016

Copyright © Saurav Muralidharan 2016

All Rights Reserved

# The University of Utah Graduate School

## STATEMENT OF DISSERTATION APPROVAL

| The dissertation of                            | Saurav Muralidha   | ran                         |

|------------------------------------------------|--------------------|-----------------------------|

| has been approved by the following supervisory | committee members: |                             |

| Mary W. Hall                                   | , Chair            | 05/16/2016<br>Date Approved |

| Ganesh Gopalakrishnan                          | , Member           | 05/16/2016                  |

|                                                |                    | Date Approved               |

| Matt Flatt                                     | , Member           | 05/16/2016<br>Date Approved |

| Matthew Brendon Might                          | , Member           | 05/16/2016<br>Date Approved |

| Michael Garland                                | , Member           | 05/19/2016                  |

|                                                |                    |                             |

| and by Ross T. White                           | aker               | _ , Chair/Dean of           |

| the Department/College/School of               | Computing          |                             |

| and by David B. Kieda, Dean of The Graduate S  | School.            |                             |

### ABSTRACT

Emerging trends such as growing architectural diversity and increased emphasis on energy and power efficiency motivate the need for code that adapts to its execution context (input dataset and target architecture). Unfortunately, writing such code remains difficult, and is typically attempted only by a small group of motivated expert programmers who are highly knowledgeable about the relationship between software and its hardware mapping. In this dissertation, we introduce novel abstractions and techniques based on automatic performance tuning that enable both experts and nonexperts (application developers) to produce adaptive code.

We present two new frameworks for adaptive programming: Nitro and Surge. Nitro enables expert programmers to specify code variants, or alternative implementations of the same computation, together with meta-information for selecting among them. It then utilizes supervised classification to select an optimal code variant at runtime based on characteristics of the execution context. Surge, on the other hand, provides a high-level nested dataparallel programming interface for application developers to specify computations. It then using Nitro. The resulting code performs on par with or better than handcrafted reference implementations on both CPUs and GPUs.

In addition to abstractions for expressing code variants, this dissertation also presents novel strategies for adaptively tuning them. First, we introduce a technique for dynamically selecting an optimal code variant at runtime based on characteristics of the input dataset. On five high-performance GPU applications, variants tuned using this strategy achieve over 93% of the performance of variants selected through exhaustive search. Next, we present a novel approach based on multitask learning to develop a code variant selection model on a target architecture from training on different source architectures. We evaluate this approach on a set of six benchmark applications and a collection of six NVIDIA GPUs from three distinct architecture generations. Finally, we implement support for combined code variant and frequency selection based on multiple objectives, including power and energy efficiency. Using this strategy, we construct a GPU sorting implementation that provides improved energy and power efficiency with less than a proportional drop in sorting throughput.

To my parents and wife.

## CONTENTS

| AB  | STRACT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | iii                                                                                                                                      |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| LIS | T OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ix                                                                                                                                       |

| LIS | T OF TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | xi                                                                                                                                       |

| AC  | KNOWLEDGEMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | xiii                                                                                                                                     |

| CH  | APTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                          |

| 1.  | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1                                                                                                                                        |

|     | <ul> <li>1.1 Abstractions for Adaptive Programming</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | $     \begin{array}{c}       1 \\       2 \\       2 \\       2 \\       3 \\       4 \\       5 \\       6 \\       7     \end{array} $ |

| 2.  | INPUT-ADAPTIVE TUNING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 8                                                                                                                                        |

|     | 2.1 Automating Code Variant Selection         2.1.1 Nitro System Overview         2.1.2 Nitro Library Constructs.         2.1.3 Nitro Autotuner Interface         2.1.4 Nitro Autotuner Interface         2.1.5 Nitro Autotuner         2.1.6 Nitro Autotuner         2.1.7 The Nitro Autotuner         2.2.8 The Nitro Autotuner         2.2.1 Building a Model for Variant Selection         2.2.2 Incremental Tuning to Reduce Training Inputs         2.2.3 Optimizing Feature and Constraint Evaluation         2.3 Benchmarks         2.3.1 Sparse Matrix-Vector Multiplication (SpMV)         2.3.2 Linear Solvers and Preconditioners         2.3.3 Breadth-First Search (BFS)         2.3.4 Histogram         2.3.5 Sort         2.4 Results         2.4.1 Variant Selection         2.4.2 Training Time Reduction         2.4.3 Feature Evaluation Overhead         2.5 Summary | $\begin{array}{c} 8\\ 10\\ 10\\ 15\\ 17\\ 17\\ 17\\ 17\\ 18\\ 18\\ 19\\ 20\\ 20\\ 20\\ 20\\ 21\\ 21\\ 22\\ 24\\ 25\\ 26\end{array}$      |

| 3. | ARCHITECTURE-ADAPTIVE TUNING                                           | <b>27</b>            |

|----|------------------------------------------------------------------------|----------------------|

|    | 3.1 System Overview                                                    | 27                   |

|    | 3.2 Tuning Process                                                     | 30                   |

|    | 3.2.1 Model Construction Using MTL                                     | 31                   |

|    | 3.2.2 Utilizing the Full Set of Device Features                        | 31                   |

|    | 3.2.3 Profile Device Feature Selection (P-DFS)                         | 32                   |

|    | 3.2.4 Cross-Validation Device Feature Selection (CV-DFS)               | 34                   |

|    | 3.3 Implementation                                                     | 36                   |

|    | 3.4 Benchmarks                                                         | 37                   |

|    | 3.4.1 Histogram                                                        | 37                   |

|    | 3.4.2 Sparse Matrix-Vector Multiplication (SpMV)                       | 37                   |

|    | 3.4.3 Sort                                                             | 39                   |

|    | 3.4.4 Breadth-First Search (BFS)                                       | 39                   |

|    | 3.4.5 Linear Solvers and Preconditioners                               | 39                   |

|    | 3.4.6 Matrix Transposition                                             | 40                   |

|    | 3.5 Results                                                            | $     40 \\     40 $ |

|    | 3.5.1Architecture Sensitivity of Benchmarks3.5.2Prediction Performance | 40<br>44             |

|    | 3.5.3 Device Feature Selection Overhead                                | 44<br>47             |

|    | 3.5.4 Results Summary                                                  | 47<br>47             |

|    | 3.6 Summary                                                            | 47                   |

|    | 5.0 Summary                                                            | -11                  |

| 4. | TUNING FOR ENERGY AND POWER EFFICIENCY                                 | 49                   |

|    | 4.1 Multiobjective Tuning in Nitro                                     | 49                   |

|    | 4.1.1 Extensions to Autotuning Interface                               | 50                   |

|    | 4.1.2 Combining Code Variant and Frequency Selection                   | 50                   |

|    | 4.2 Energy and Power-Efficient GPU Sorting                             | 51                   |

|    | 4.2.1 Aggregated Metrics for Sorting                                   | 51                   |

|    | 4.3 Experimental Methodology                                           | 52                   |

|    | 4.3.1 Target Architectures                                             | 52                   |

|    | 4.3.2 Input Data                                                       | 53                   |

|    | 4.4 Experimental Results                                               | 53                   |

|    | 4.5 Summary                                                            | 55                   |

| 5. | A TUNABLE PROGRAMMING SYSTEM                                           | 60                   |

|    | 5.1 Programming Interface                                              | 61                   |

|    | 5.2 Code Generation and Autotuning                                     | 63                   |

|    | 5.2.1 Computation Analysis                                             | 63                   |

|    | 5.2.2 Schedule Enumeration                                             | 64                   |

|    | 5.2.3 Policy Enumeration                                               | 67                   |

|    | 5.2.4 Autotuning                                                       | 68                   |

|    | 5.3 Translation to Target-Specific Code                                | 70                   |

|    | 5.3.1 Targeting New Architectures                                      | 71                   |

|    | 5.3.2 Operator Fusion                                                  | 72                   |

|    | 5.4 Benchmarks                                                         | 72                   |

|    | 5.4.1 Reduction and Scan                                               | 72                   |

|    | 5.4.2 Sparse Matrix-Vector Multiplication (SpMV)                       | 73                   |

|    | 5.4.3 K-Means Clustering                                               | 74                   |

|    | 5.4.4 Co-design Molecular Dynamics Proxy (CoMD)                        | 75                   |

| 5.5 Evaluation                                   | <br> |     | 77 |

|--------------------------------------------------|------|-----|----|

| 5.5.1 Methodology and Hardware Platforms         | <br> |     | 77 |

| 5.5.2 Performance Results                        | <br> |     | 78 |

| 5.5.3 Productivity Gains                         | <br> |     | 81 |

| 5.6 Summary                                      |      |     | 81 |

| 6. RELATED WORK                                  | <br> |     | 82 |

| 6.1 Autotuning for Adaptive Programming          | <br> |     | 82 |

| 6.1.1 Parameter and Domain-Specific Autotuning   | <br> |     | 82 |

| 6.1.2 Code Variant Tuning                        | <br> |     | 83 |

| 6.1.3 Architecture-Adaptive Tuning               | <br> |     | 83 |

| 6.1.4 Energy and Power Efficiency Tuning on GPUs | <br> |     | 84 |

| 6.2 High-Level Parallel Programming Systems      | <br> |     | 84 |

| 6.2.1 Nested Data-Parallelism                    | <br> |     | 84 |

| 6.2.2 Decoupling Computation and Implementation  |      |     | 85 |

| 6.2.3 Programming Models Supporting Autotuning   | <br> |     | 86 |

| 6.3 Summary                                      | <br> | • • | 86 |

| 7. CONCLUSIONS AND FUTURE RESEARCH               | <br> |     | 87 |

| 7.1 Contributions                                | <br> |     | 87 |

| 7.2 Future Work                                  |      |     | 88 |

| 7.2.1 Support for Tunable Parameters             | <br> |     | 88 |

| 7.2.2 Tuning Approximate Computations            |      |     | 90 |

| 7.2.3 Extensions to Surge                        |      |     | 90 |

| 7.3 Summary                                      |      |     | 91 |

| REFERENCES                                       | <br> |     | 92 |

## LIST OF FIGURES

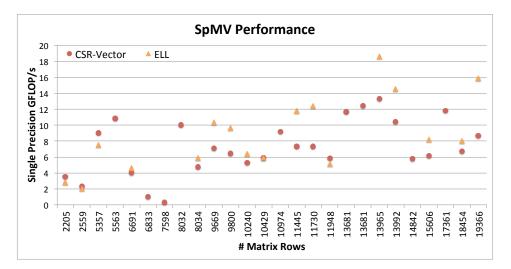

| 1.1 | Performance of SpMV code variants on the NVIDIA GeForce GTX 480 GPU.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

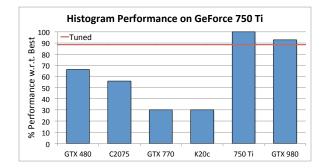

| 1.2 | Histogram performance on the GeForce 750 Ti when trained on other archi-<br>tectures. The tuned line shows the performance of our strategy when trained<br>using data from all architectures other than 750 Ti                                                                                                                                                                                                                                                                                                                                                                                                       | 5  |

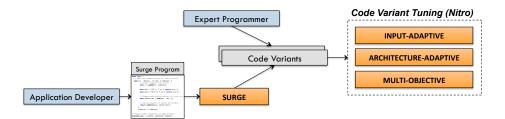

| 1.3 | Overview of the contributions of this dissertation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 6  |

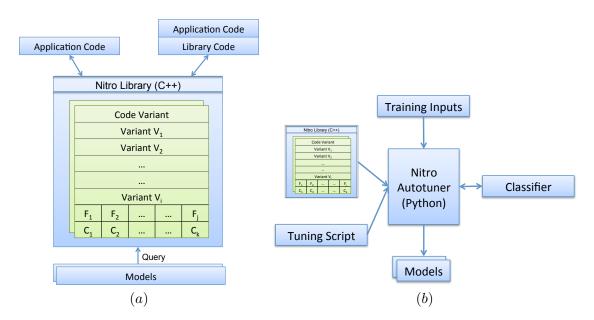

| 2.1 | Overview of the Nitro system. (a) The production version of the library/appli-<br>cation. The C++ library is used to define variants, features, and constraints.<br>Calling the variant evaluates the input features at runtime and queries the<br>accompanying model to select the right variant to execute for a given input.<br>(b) The offline autotuning process. User provides a tuning script and training<br>inputs. The autotuner runs the application/library for each training input and<br>collects training data. The classifier is then consulted with the training data<br>to construct the model(s). | 11 |

| 2.2 | Example Nitro Library interface for SpMV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 13 |

| 2.3 | Example Nitro Autotuner interface for SpMV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 16 |

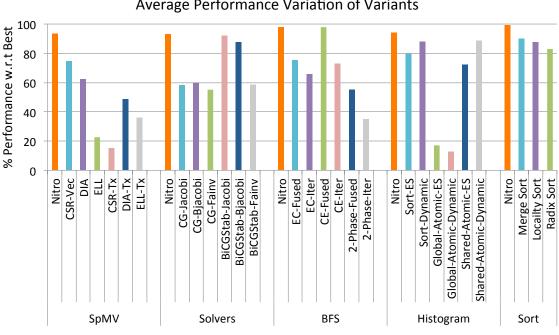

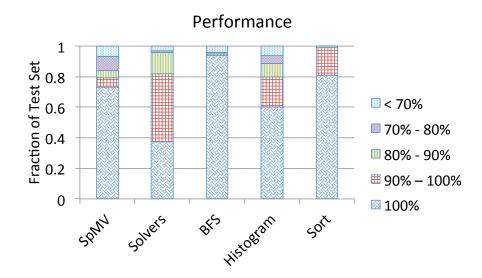

| 2.4 | Performance variation among variants.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 22 |

| 2.5 | Performance comparison across all test inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 23 |

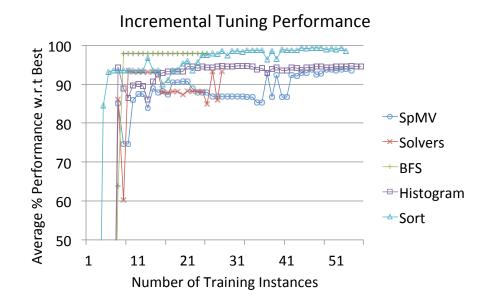

| 2.6 | Convergence for active learning training heuristic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 25 |

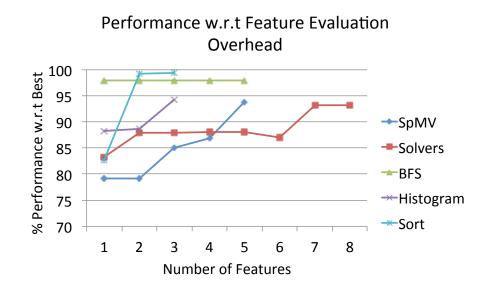

| 2.7 | Performance variation as features with higher evaluation overhead are added incrementally                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 26 |

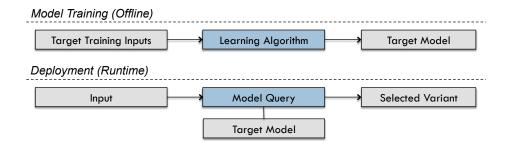

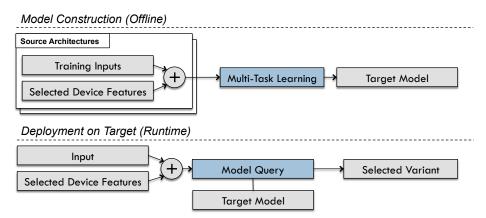

| 3.1 | Comparison of input-adaptive tuning in Nitro with architecture-adaptive tun-<br>ing. When tuning across architectures, values of the device features selected<br>through DFS are obtained on both the source (during model construction) and<br>target (during deployment). These are then concatenated with feature values<br>of the relevant input data point ('+' operator in the figure)                                                                                                                                                                                                                         | 28 |

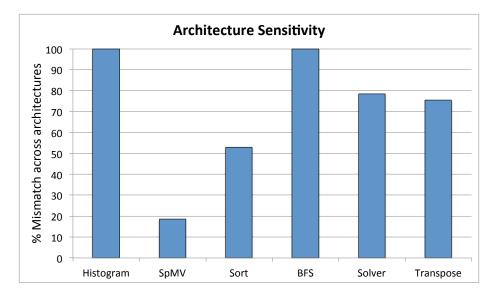

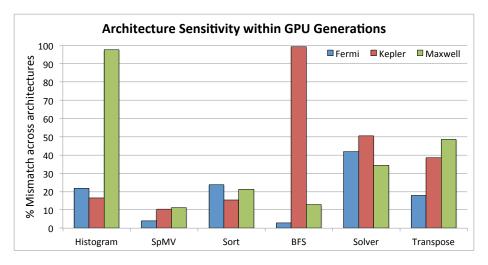

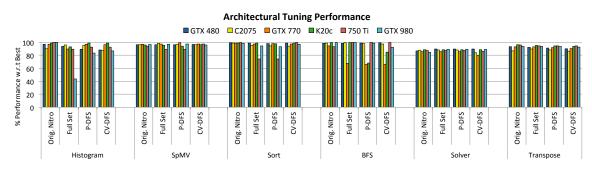

| 3.2 | Architecture-sensitivity of each benchmark. The y-axis represents the percent-<br>age of test inputs for which at least one architecture selects a different best<br>variant than the others                                                                                                                                                                                                                                                                                                                                                                                                                         | 41 |

| 3.3 | Architecture-sensitivity within GPUs of the same generation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 41 |

| 3.4 | Device feature selection performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 44 |

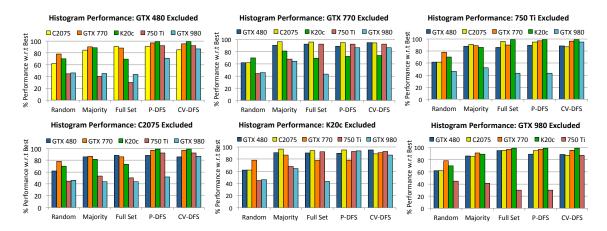

| 3.5 | Device feature selection performance for Histogram on a restricted set of ar-<br>chitectures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 46 |

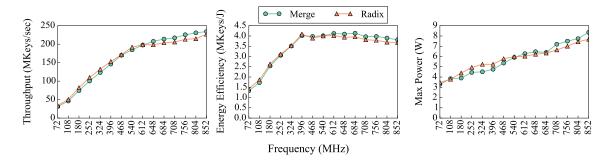

| 4.1 | Variation in throughput (keys sorted per second), energy efficiency (keys sorted per Joule), and maximum power draw of code variants as frequency increases. Results are for an input sequence of 10M elements, long datatype and uniform distribution on the Jetson TK1 | 54 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

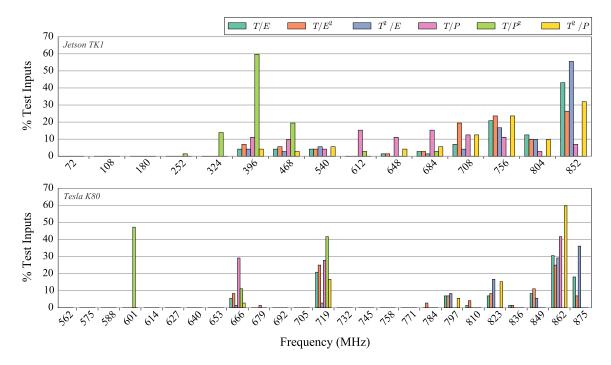

| 4.2 | Distribution of frequencies selected via exhaustive search on the Jetson TK1 (top) and Tesla K80 (bottom) for various optimization objectives                                                                                                                            | 54 |

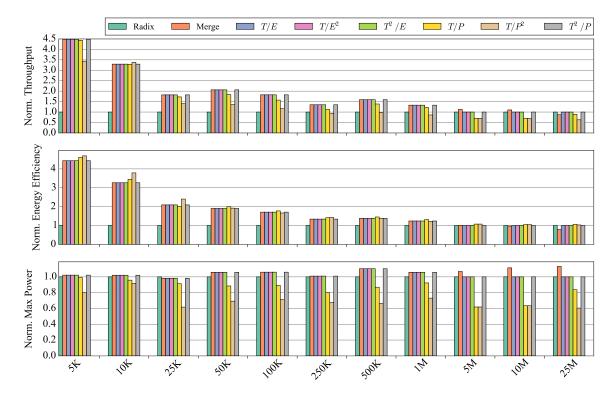

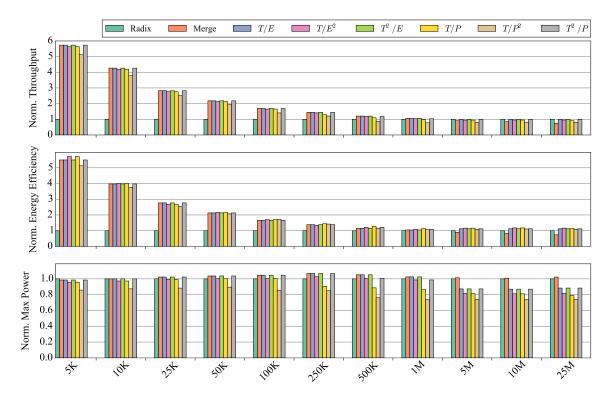

| 4.3 | Throughput (top), energy efficiency (middle), and maximum power (bottom) on the Jetson TK1 for radix and merge sort, and for variants selected for each optimization objective. Values are normalized with respect to radix sort. Inputs are of type (int, uniform)      | 56 |

| 4.4 | Throughput (top), energy efficiency (middle), and maximum power (bottom) on the Tesla K80 for radix and merge sort, and for variants selected for each optimization objective. Values are normalized with respect to radix sort. Inputs are of type (int, uniform)       | 57 |

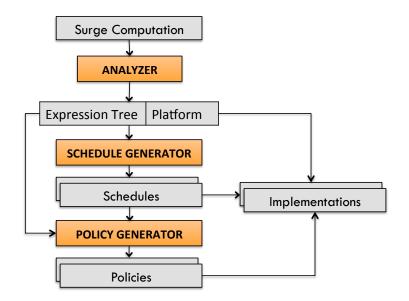

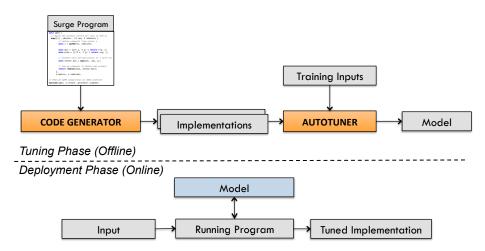

| 5.1 | Overview of the Surge code generator.                                                                                                                                                                                                                                    | 64 |

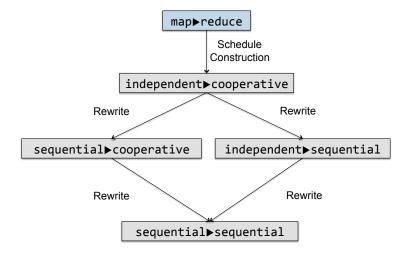

| 5.2 | SpMV schedule construction and rewriting                                                                                                                                                                                                                                 | 66 |

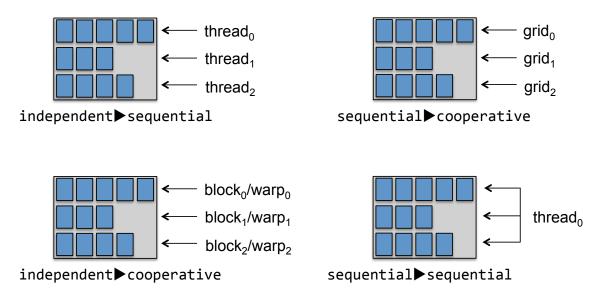

| 5.3 | How various SpMV schedules may be implemented in CUDA. In this example, the input matrix (gray boxes) has 12 nonzeros (blue boxes) and 3 rows                                                                                                                            | 66 |

| 5.4 | Overview of the Surge framework and its interaction with Nitro                                                                                                                                                                                                           | 70 |

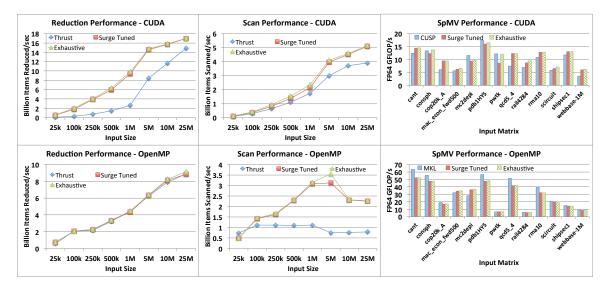

| 5.5 | Reduction, Scan and SpMV Performance on CUDA and OpenMP                                                                                                                                                                                                                  | 78 |

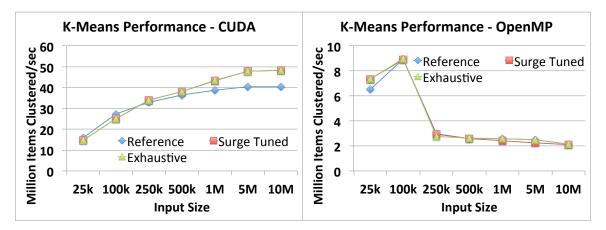

| 5.6 | K-Means Performance on CUDA and OpenMP.                                                                                                                                                                                                                                  | 79 |

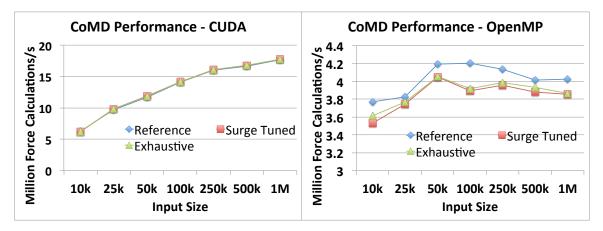

| 5.7 | CoMD Performance on CUDA and OpenMP.                                                                                                                                                                                                                                     | 79 |

## LIST OF TABLES

| 2.1 | List of functions provided by Nitro for variant, feature, and constraint man-<br>agement                                                                                                                                                            | 12 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Configuration options in the Nitro Autotuner interface.                                                                                                                                                                                             | 16 |

| 2.3 | A brief description of variants and list of features used for each benchmark.<br>The last column lists the sizes of training and testing sets                                                                                                       | 19 |

| 3.1 | Values of GPU device features for 6 architectures.                                                                                                                                                                                                  | 29 |

| 3.2 | Cosine similarity between architectures for Histogram $(H)$ and SpMV $(S)$ . Values closer to +1 indicate similarity, while values closer to -1 indicate dissimilarity.                                                                             | 30 |

| 3.3 | GPU application proxies with corresponding profiling metrics and device features.                                                                                                                                                                   | 33 |

| 3.4 | Variants and features used for each benchmark. The last column lists the sizes of training and testing sets.                                                                                                                                        | 38 |

| 3.5 | Variant selection histograms across different benchmarks and architectures.<br>Each subtable represents the distribution of variant selections across test data<br>for a particular benchmark.                                                      | 42 |

| 3.6 | Best device features for each benchmark, proxies predicted by P-DFS, and the best features chosen by CV-DFS.                                                                                                                                        | 43 |

| 3.7 | Device feature selection overhead (time in seconds)                                                                                                                                                                                                 | 47 |

| 4.1 | Throughput (T), energy efficiency (E) and maximum power draw (P) for the variants and frequencies selected by the constructed models with respect to fixed radix and merge sort (at highest frequencies). Values are averaged over all test inputs. | 58 |

| 5.1 | Current data-parallel operators in Surge. Parameters in square brackets are optional                                                                                                                                                                | 62 |

| 5.2 | List of Surge schedules.                                                                                                                                                                                                                            | 65 |

| 5.3 | Schedule lookup table for Surge operators.                                                                                                                                                                                                          | 66 |

| 5.4 | List of tunable parameters.                                                                                                                                                                                                                         | 67 |

| 5.5 | Inferred parameters for each SpMV schedule. The subscripts denote nesting depths.                                                                                                                                                                   | 69 |

| 5.6 | List of benchmarks with description, their core computation(s) and details about reference implementations.                                                                                                                                         | 72 |

| 5.7 | Features used, number of training and test inputs, size of search space, and number of variants for each benchmark.                                                                                                                                 | 78 |

| 5.8 | Average speedups over GPU and CPU reference implementations, and source   |    |

|-----|---------------------------------------------------------------------------|----|

|     | lines of code (SLOC) required for Surge, and GPU and CPU reference imple- |    |

|     | mentations.                                                               | 80 |

### ACKNOWLEDGEMENTS

I would first like to thank my advisor, Prof. Mary Hall, for her support and guidance throughout the course of my Ph.D. She has taught me most of what I know about research and technical writing, and I am confident that the skills I have learned from her will serve me well throughout my career.

I am thankful to my Ph.D. committee members, Prof. Ganesh Gopalakrishnan, Prof. Matthew Flatt, Prof. Matthew Might, and Dr. Michael Garland for their guidance and the many productive discussions we've had. I'd like to especially thank Michael for supervising a number of my research projects over the span of four years; I have benefited immensely from his feedback and guidance. I would also like to thank Prof. Hari Sundar for his help with the multiobjective tuning project.

My current and past labmates in the CTOP group, Anand, Protonu, Axel, Suchit, Manu, Amit, Tharindu, Khalid, Huihui, and Tuowen, have been good friends and collaborators. I would like to thank Manu and Amit in particular for their immense help with preparing my publications.

I spent two wonderful summers at NVIDIA Research, and would like to thank the various colleagues and friends I had there, including Bryan, Albert and Duane for their mentorship and help with the Surge project.

I'd like to thank the many friends I made in Salt Lake City, especially Arijit, Suchit, Anand, Nil, Nikhil, Prasanna, Sriram, Shreyas, Sharath, Manju, Meghana, Anusua, and Piyush for making my Ph.D. years fun and memorable.

I am grateful to Ann, Karen, and the School of Computing front desk staff for helping me out with various administrative tasks related to my Ph.D. and international student status; they have always been ready to help whenever I needed them.

Finally, I would like to thank my parents and wife for their unconditional support, love, and patience. They have made a number of sacrifices to help me get through my Ph.D. years smoothly, and I will be forever grateful to them.

This work was funded by Defense Advanced Research Projects Agency (DARPA) contract HR0011-13-3-0001.

### CHAPTER 1

### INTRODUCTION

With parallel architectures becoming increasingly complex and diverse, and energy and power efficiency also gaining importance, programmers are forced to continuously rewrite and reoptimize code as architectures and optimization objectives change. Unfortunately, this manual approach is time consuming, demands considerable knowledge of low-level architectural details, and is likely not portable. Instead, we believe that code targeting current and future parallel architectures must have the ability to intelligently and automatically adapt to changing *execution contexts* (input dataset and target architecture); additionally, it must meet multiple, possibly conflicting, higher level optimization objectives such as performance and energy/power efficiency.

A number of approaches for writing adaptive code, targeting various programmer expertise levels, have been proposed in the literature. High-level domain-specific programming systems such as Halide [1] and Elixir [2] decouple the specification of computations from their low-level implementations. This enables optimized implementations to be generated automatically, letting users focus on the computation itself. At the other end of the spectrum, there are new techniques and frameworks for automatic performance tuning (*autotuning*, for short) targeting expert programmers [3]–[6]. Such systems lift some of the burden off expert programmers, who can now focus on writing high-performance implementations, as opposed to spending effort on making the code adaptive.

In this dissertation, we present a cohesive framework for writing adaptive code that provides suitable abstractions for both experts and application developers, and incorporates a host of novel techniques for handling input adaptivity, architecture adaptivity, and multiobjectivity.

### 1.1 Abstractions for Adaptive Programming

Adaptive programming is the process of writing code that intelligently adapts to changing execution contexts and optimization objectives. A commonly employed mechanism in adaptive programming is the *code variant*, which represents a unique implementation of a computation, among many, that has the same interface and is functionally equivalent to the other variants but may employ fundamentally different algorithms or implementation strategies. Given a computation and a set of code variants implementing it, one way of achieving adaptivity is to select the optimal variant for a given execution context and optimization objective. However, the question of expressing code variants still remains; in other words, what is the right level of abstraction for specifying code variants given a programmer's expertise? In this section, we study this issue in more detail and outline the contributions that this dissertation makes to address it.

#### 1.1.1 Supporting Expert Programmers

This class of users demand very high levels of performance, and are highly knowledgeable about the relationship between software and its hardware mapping. They typically prefer to write high-performance code variants by hand, and are seeking mechanisms to make their code adaptive. To support such users, this dissertation introduces Nitro, a new programmer-directed code variant tuning system. In addition to code variants, Nitro lets programmers express metainformation for variant selection, such as how to calculate *features* or characteristics of the input datasets and target architecture, and representative training input datasets. Nitro also includes a tuning interface to optionally customize the tuning process.

#### 1.1.2 Supporting Application Developers

In contrast to expert programmers, application developers prioritize clean, maintainable code over raw performance. Consequently, low-level abstractions for code variant expression and tuning are unlikely to be adopted by this group. This dissertation presents Surge, a nested data-parallel programming system that decouples the high-level specification of computations from their implementation details. This enables Surge to automatically generate a search space of code variants, which are subsequently tuned using Nitro.

### 1.2 Adaptive Code Variant Selection.

Once code variants are specified, optimal ones among them must be automatically selected depending on factors of the execution context. The fact that some of this information, such as characteristics of the input dataset, is not known until runtime makes this problem harder. Additionally, the selected variants must meet high-level, possibly conflicting, optimization objectives such as performance and energy efficiency. In this section, we define input-adaptive, architecture-adaptive, and multiobjective tuning; we also briefly outline the contributions that this dissertation makes in these areas.

### 1.2.1 Input Adaptivity

Given a set of code variants implementing a computation, input-adaptive tuning finds the optimal one corresponding to a given input dataset. While some autotuning systems such as Sequoia [7] and PetaBricks [8] support input-adaptive code variant tuning, what is missing from these frameworks is more general metainformation that can be used to select variants, beyond input dataset size. This presents a particular problem for *irregular applications*, such as sparse numerical methods and graph algorithms, and any other applications (e.g., sorting) where characteristics of the input dataset may significantly impact selection of the best code variant, and is not known until runtime. As a motivating example, consider two GPU sparse matrix-vector multiplication (SpMV) variants from the CUSP library: ELL and CSR-Vector [9]. Their performance on the NVIDIA GeForce GTX 480 GPU is shown in Figure 1.1. Here, the x-axis represents number of matrix rows and the y-axis shows performance in GFLOP/s. As the figure shows, none of the variants is uniformly the best across all inputs; instead, the best variant changes with input.

One approach to input-adaptive code variant selection is to build a statistical *Model* that maps characteristics of the input dataset to the appropriate variant. In this work, we use supervised learning in an offline training phase to infer a model that maps from features of the input dataset to variants. The model is then used to select optimized code variants for new, unseen inputs. We also implement an incremental tuning mode based on active

Figure 1.1: Performance of SpMV code variants on the NVIDIA GeForce GTX 480 GPU.

learning [10] for reducing the number of inputs required for training the model.

### 1.2.2 Architecture Adaptivity

As described above, we rely on a model-based strategy for input-adaptive code variant selection. These models, however, require retraining every time the software is installed on a new architecture or if the underlying hardware is upgraded. This training process is typically very time consuming and heavy on system resources; we are required to evaluate each variant for each input when collecting the training data. This work evaluates the following question: Can we develop a methodology to reuse results of training on two or more source architectures to create a variant selection model for a different target architecture without training on the target architecture? In other words, can we come up with an input- and architecture-adaptive code variant selection strategy?

As a motivating example, consider the Histogram operation: it counts the number of observations that fall into one of a set of disjoint bins. Consider six code variants for Histogram in the high-performance GPU CUB library [11]. There are two variants that do not use atomic operations, two that use global memory atomics, and two that use shared memory atomics. The best variant is therefore *architecture-sensitive*, based on the relative performance of atomic operations, and also *input-sensitive*, e.g., affected by input size and mean sample distribution.

Figure 1.2 shows performance for Histogram on the GeForce 750 Ti GPU (Maxwell generation), when using a variant selection model trained on six different GPU architectures. The x-axis captures results when trained on the corresponding GPU. The y-axis represents percentage performance achieved by the variant selected by a model with respect to the best performing variant (exhaustive search), averaged across all inputs in a test dataset. From the figure, it is clear that while variant selection models trained and tested on the same architecture perform well (above 95% of exhaustive search), this is not the case when models trained on architecture X are deployed on architecture Y (X  $\neq$  Y), with performance dropping to as low as 30% of exhaustive in some cases.

While an architecture-specific model yields high performance, the time-consuming training phase must be repeated for each application and target architecture. In this work, we instead develop a strategy to automatically construct code variant selection model(s) on a target architecture using only training data from a set of source architectures specified by the programmer, together with information that characterizes each architecture. On the target, no variants are executed during the model construction process, since no training data from the target are required. Our strategy thus enables the construction of performance-portable

Figure 1.2: Histogram performance on the GeForce 750 Ti when trained on other architectures. The tuned line shows the performance of our strategy when trained using data from all architectures other than 750 Ti.

software that quickly and automatically adapts to both changing inputs and new hardware architectures. In Figure 1.2, the line labeled 'Tuned' shows performance achieved by our strategy trained on data from every architecture except the 750 Ti.

#### 1.2.3 Multiobjective Tuning

Higher power consumption and associated heat dissipation in HPC systems is forcing a corresponding increase in operating costs. On the other end of the spectrum, battery life is increasingly becoming a concern on smaller embedded devices. Optimizing code variants for power and energy efficiency, while also ensuring minimal degradation in performance, is thus becoming critically important. One way of achieving this goal is through multi-objective optimization, which aims to find a set of solutions (in this case, code variants) that satisfy a set of (possibly conflicting) optimization criteria. Dynamic voltage and frequency scaling (DVFS) is another approach that has proven effective for reducing energy and power consumption, especially on GPUs [12], [13]. Given an execution context, the ability to predict the optimal frequency, in addition to code variant, would thus be useful.

In this work, we present a mechanism for users to define custom aggregated optimization metrics. This enables code variant selection based on multiple objectives, such as performance, energy consumption, etc. Further, we describe techniques for combined (code variant, frequency) selection, enabling the use of DVFS to further reduce energy and power consumption of code variants with minimal performance loss.

Figure 1.3: Overview of the contributions of this dissertation.

### **1.3** Contributions

The contributions of this dissertation are outlined below, and summarized in Figure 1.3.

- A framework for code variant tuning: We describe Nitro, a programmer-directed code variant tuning framework targeted at expert users. Nitro allows code variants to be conveniently specified, together with metainformation to aid in selecting among them. As shown in Figure 1.3, it acts as a substrate for implementing all code variant tuning strategies described in this dissertation.

- 2. Input-adaptive tuning: We introduce a strategy for input-adaptive code variant selection based on supervised classification. Further, we demonstrate an incremental tuning mode based on active learning that achieves substantial reduction in the training set size. On five high-performance GPU applications, tuned variants achieve over 93% of the performance of variants selected through exhaustive search, averaged over the testing inputs.

- 3. Architecture-adaptive tuning: We present a novel approach based on multitask learning to develop a code variant selection model on a target architecture from training on different source architectures. Additionally, we introduce two techniques for pruning features that characterize each architecture and demonstrate their importance. Finally, we present performance results on a set of six benchmark applications and a collection of six NVIDIA GPUs from three distinct architecture generations.

- 4. Multiobjective tuning: We implement support for combined (code variant, core clock frequency) selection based on multiple objectives, including power and energy efficiency. In particular, we demonstrate how to build a sorting implementation for the NVIDIA Jetson TK1 and Tesla K80 GPUs that provides improved energy and power efficiency with less than a proportional drop in sorting throughput.

- 5. A tunable programming system: We introduce Surge, a nested data-parallel programming system that decouples the high-level specification of computations from their

low-level hardware implementations using two first-class language constructs named *schedules* and *policies*. Surge is then able to automatically generate code variants from these specifications and tune them using Nitro, as shown in Figure 1.3. For five real-world benchmarks expressed in Surge, we demonstrate performance that is on-par or better than handcrafted reference implementations on both CPUs and GPUs.

## 1.4 Dissertation Roadmap

The remainder of this dissertation is organized as follows: we first introduce Nitro and describe techniques for code variant tuning with respect to input adaptivity in Chapter 2. In Chapters 3 and 4, we describe strategies for architecture-adaptive and multiobjective tuning, respectively. Next, in Chapter 5, we describe Surge, including its programming interface, and code generation and tuning infrastructure. Finally, Chapter 6 discusses relevant prior research on autotuning techniques and high-level parallel programming systems, and Chapter 7 concludes.

## CHAPTER 2

### **INPUT-ADAPTIVE TUNING**

One approach to input-adaptive code variant selection is to build a statistical *model* that maps characteristics of the input dataset to the appropriate variant. Such a model can be queried to perform variant selection at runtime once properties of the input dataset are available. In previous work on the *algorithm selection problem* [14], statistical learning techniques are used to select among a set of different algorithms [15]–[17]. To date, however, no general-purpose framework enables users to specify and tune arbitrary code variants and also customize the tuning process.

This chapter describes a new programmer-directed autotuning system called Nitro. It focuses on (1) how code variants and metainformation for variant selection are expressed in Nitro, and (2) underlying system support that selects the most appropriate variant for a given input dataset. Nitro targets two classes of users: expert programmers who specify the variants and their meta-information, and end users who invoke Nitro-enabled software without using any Nitro-specific constructs. Code variants are created and added to the system with library calls. In addition to expressing code variants, expert programmers specify how to calculate features or characteristics of the input data sets for each variant and representative training input data sets. The underlying Nitro system uses supervised learning in an off-line training phase to infer a model that maps from features of the input data set to variants. The model is then used by end users to select optimized code variants for new, unseen inputs. Nitro also includes an interface to optionally customize the tuning process, which then invokes optimizations and heuristics to reduce training time of the model and amortize feature evaluation costs.

### 2.1 Automating Code Variant Selection

Before describing the Nitro system, we first motivate our approach with an example, a sparse matrix-vector multiply (SpMV). In SpMV implementations, the driving principle is to avoid representing and computing zero-valued elements of the sparse matrix, thus saving both space and computation. A common sparse matrix representation is the Coordinate representation, where for each nonzero element in matrix A, the corresponding row and column are recorded and used in the computation in the following way:

for(i = 0; i < nnz; i++)

y[row[i]] += A[i]\*x[col[i]];</pre>

While general, the representation and associated computation can be improved if structural properties of the matrix, such as the distribution of row lengths, are known. In fact, most SpMV libraries incorporate a variety of matrix representations and associated code for this reason [18]–[22]. Unfortunately, the structure of the matrix is usually not known until runtime, requiring the programmer to select the most appropriate variant directly, or some preprocessing of the input by the system to determine which version to use.

SpMV libraries usually incorporate multiple formats and sometimes multiple variants per format. For example, the CUSP library [22] for NVIDIA GPUs exposes the different variants and representations as part of the interface, and users select the appropriate variant to execute.

The way in which CUSP supports the end user in making these variant selections (and similar aspects of other libraries) inspired the approach taken in Nitro. Internally, CUSP examines properties of the input dataset at runtime to determine if a specific matrix representation selected by the user is likely to be efficient for that input. By encapsulating these properties along with a few others into features, a training phase can learn a model to guide the selection of the variant corresponding to the best matrix representation and among variants representing different parallelization strategies for a single representation. At runtime, the variant selection can then be performed automatically.

This automatic support of variant selection in Nitro benefits the expert programmers designing software to be used by others in a variety of contexts. Such expert programmers often have an understanding of what variants are appropriate for a class of target architectures and some intuition about how the input data set properties affect variant selection. However, managing the details of collecting properties and determining cutoff values for variant selection requires extensive and costly trial-and-error experimentation. Therefore, it is realistic for expert programmers to provide a collection of variants and features, which are used as metainformation for variant selection. This support in Nitro not only increases the productivity of expert programmers by eliminating the manual encoding of variant selection, but also improves the useability of the software for its end users. In the remainder of this section, we illustrate how the Nitro system can be used to automate variant selection for SpMV.

#### 2.1.1 Nitro System Overview

Figure 2.1 provides a high-level overview of the Nitro system, which consists of two parts: the Nitro Library, implemented using C++ Templates (Figure 2.1a), and the Nitro Autotuner, written in Python (Figure 2.1b). The Nitro Library is invoked within an application/library to define a set of variants,  $V = \{V_1, V_2, ..., V_i\}$ . The programmer also expresses meta-information for selecting variants: functions to compute features  $F = \{F_1, F_2, ..., F_j\}$ and optional constraints for each variant, shown as  $\{C_1, C_2, ..., C_k\}$  in the figure. Constraints are used to rule out certain variants that are either inappropriate or incorrect to use for a particular input.

The Nitro Autotuner is invoked with an external Python tuning script that allows programmers to specify the Training Inputs, how to perform feature evaluation, and other tuning properties for specific variants and the entire application/library. This decoupling between the library and the autotuner ensures that the main application code only contains algorithm-specific details such as variants and features, and allows programmers convenient experimentation with different tuning options and porting to different architectures. To communicate with the library, the Python-based autotuner generates a C++ header file and encapsulates the tuning properties within tuning policies for each variant.

The Nitro Autotuner builds a statistical *Model* (Figure 2.1b) that maps a set of features represented by a *feature vector*  $[x_1, x_2, ..., x_n]$  to the label corresponding to the optimal variant for the corresponding input. By default, Nitro employs for this purpose *Support Vector Machines (SVMs)* [23], a widely used machine learning algorithm to build the model from an offline training phase on the *Training Input* so that it can be consulted at runtime given the feature vector of a new input. We use the publicly available *libSVM* [24] for this purpose.

#### 2.1.2 Nitro Library Constructs

Table 2.1 provides a summary of the constructs available in Nitro for expressing variants and their associated features and constraints. Figure 2.2 provides Nitro code for SpMV to illustrate these constructs, as described in the following paragraphs.

Figure 2.1: Overview of the Nitro system. (a) The production version of the library/application. The C++ library is used to define variants, features, and constraints. Calling the variant evaluates the input features at runtime and queries the accompanying model to select the right variant to execute for a given input. (b) The offline autotuning process. User provides a tuning script and training inputs. The autotuner runs the application/library for each training input and collects training data. The classifier is then consulted with the training data to construct the model(s).

$\label{eq:table 2.1: List of functions provided by Nitro for variant, feature, and constraint management$

| Function                            | Parameters                   | Description                    |  |

|-------------------------------------|------------------------------|--------------------------------|--|

| <pre>code_variant Constructor</pre> | Template parameters:         | Creates code_variant object    |  |

|                                     | $tuning_policies$ $object$ , |                                |  |

|                                     | Tuple of argument types.     |                                |  |

|                                     | Arguments: Pointer to        |                                |  |

|                                     | context object               |                                |  |

| add_variant                         | Pointer to Variant Function  | Adds a variant to the          |  |

|                                     | Object                       | code_variant object's          |  |

|                                     |                              | internal variant table         |  |

| set_default                         | Pointer to Variant Function  | Used to set default variant to |  |

|                                     | Object                       | execute                        |  |

| add_input_feature                   | Pointer to Feature Function  | Adds the specified function    |  |

|                                     | Object                       | to the list of feature func-   |  |

|                                     |                              | tions                          |  |

| add_constraint                      | Pointer to Variant Func-     | Adds a constraint function     |  |

|                                     | tion Object, Pointer to Con- | to execute before evaluating   |  |

|                                     | straint Function Object      | given variant.                 |  |

| <pre>fix_inputs()</pre>             | Argument(s) to Variant       | Fixes inputs to variant.       |  |

|                                     |                              | Used for asynchronous          |  |

|                                     |                              | feature evaluation.            |  |

| operator()()                        | Argument(s) to Vari-         | Executes the correct under-    |  |

|                                     | ant (empty with              | lying variant.                 |  |

|                                     | async_feature_eval)          |                                |  |

```

namespace MySparse {

void SparseMatVec(HostMatrix *matrix)

ł

using namespace nitro;

typedef thrust::tuple<HostMatrix *> ArgTuple;

// Create Nitro Tuning Context

context cx;

// Create code_variant object

code_variant<tuning_policies::spmv,</pre>

ArgTuple> spmv(cx);

// Declare and Add Variants

csr_vector_type<HostMatrix> __csr_vector;

dia type<HostMatrix> dia;

. . .

spmv.add_variant(&__csr_vector);

spmv.add_variant(&__dia);

. . .

// Set Default Variant

spmv.set_default(&__csr_vector);

// Declare and Add Features...

nnz type<HostMatrix> nnz;

num_rows_type<HostMatrix> __num_rows;

. . .

spmv.add_input_feature(&__nnz);

spmv.add_input_feature(&__num_rows);

. . .

// ...and Constraints

dia_cutoff_type __dia_cutoff;

spmv.add_constraint(&_dia, &_dia_cutoff);

. . .

// Variant Call

spmv(matrix);

}

// Define CSR Vector Variant

template <typename HostMatrix>

struct csr_vector_type :

nitro::variant_type<HostMatrix *> {

double operator()(HostMatrix *matrix) {

. . .

}

};

} // end namespace MySparse

```

Figure 2.2: Example Nitro Library interface for SpMV.

#### 2.1.2.1 Defining and Adding Code Variants

Nitro represents a function that has code variants using the code\_variant class. Each variant is expected to be functionally equivalent and must use the same interface. During instantiation, a tuple of the function's argument types, and its tuning policy must be specified as template arguments. The tuning policy for each such function is generated by the tuning script in a separate header file, as discussed in the next section. A function to be tuned by Nitro can thus be any general-purpose C++ function. Also during instantiation of the code\_variant class, a pointer to a context object that maintains global state among all the variants in the program must be included as a constructor argument. In Figure 2.2, we define a function SparseMatVec within the MySparse library, which provides a tuned SpMV implementation using Nitro. The details of the tuning process are thus abstracted away from the end user, who can use the MySparse library without ever needing to know about Nitro.

Each variant must be defined as a C++ function object deriving from the variant\_type class. An example variant definition is provided in the bottom of Figure 2.2. Variants are added to the code\_variant object using the add\_variant function, which accepts a pointer to the function object for that variant. All variants of a function must have the same argument type(s). Users may explicitly specify a default variant using the set\_default function. Default variants are assumed to work correctly for all inputs and are used when one or more user-defined constraints fail. If no default is specified, the system selects the first variant as the default.

In Figure 2.2, we add two different variants for SpMV, corresponding to different formats for the sparse matrix: csr\_vector\_type for *Compressed Sparse Row*, and dia\_type for *Diagonal* [22].

The code for the variant must be specified in the **operator()** function, which is used by Nitro to invoke the desired variant. Nitro variants are required to return a double precision value, which by default denotes the time taken by the variant. However, by returning the appropriate value, Nitro can also be used to predict variants according to other optimization criteria, for example, energy usage, or to find the variant that provides the approximate result with the smallest margin of error.

#### 2.1.2.2 Defining Input Features

Input features are described in Nitro through *feature functions*. These have the same argument types as the variant, but always return a **double**, which represents the value of the

calculated feature for an input. In Nitro, feature functions must be wrapped in a function object derived from input\_feature\_type.

The add\_input\_feature function accepts a pointer to a feature function object and adds it to the internal feature function table. All values from the feature functions automatically get evaluated before the code for the variant starts executing. For example, in Figure 2.2, input features include \_\_nnz, and \_\_num\_rows, the number of nonzeroes, and the number of rows, respectively. To hide the runtime overhead of feature evaluation, an optimization discussed in Section 2.2.3 is asynchronous feature evaluation; asynchronous feature evaluation is enabled by calling the fix\_inputs function before calling operator().

#### 2.1.2.3 Defining Constraints

For certain inputs, it is possible that a variant produces wrong results, or takes unacceptably long to execute. Nitro provides support for handling such cases using user-defined *constraints*. Constraint functions can be added to code variants using the add\_constraint function, which accepts a constraint function and the specific variant for which it is valid. Constraints are automatically evaluated by the library and either force the variant to return an  $\infty$  value during the offline training phase (thus ensuring that variant is not selected), or revert back to the default variant during the online deployment phase. In the example of Figure 2.2, the constraint \_\_\_dia\_cutoff ensures that the \_\_\_dia variant does not get executed if the constraint evaluates to false.

#### 2.1.3 Nitro Autotuner Interface

The Nitro Autotuner uses an external Python interface to allow users to precisely control various aspects of the autotuner and the tuning process for each variant. The interface exposes the autotuner and code\_variant classes, which can be used to configure tuning options globally, and for each code variant, respectively. Table 2.2 shows the various configuration options available. Most of these options have a default value, and the only essential information that must be provided is the training input dataset and the functions to be tuned. The remaining functionality allows the expert user to optionally control the tuning process as desired.

Figure 2.3 shows a tuning script for the SpMV example. A single code\_variant object is created (named 'spmv') and both global and variant-specific tuning properties are set. The call to the tune method starts the autotuning process.

Tuning options specified using this interface are written out to a header file so that the autotuner can communicate with the C++ part of the system. Generating a static header

| Option                                        | Description                                                |  |  |

|-----------------------------------------------|------------------------------------------------------------|--|--|

| classifier                                    | Classifier Object to Use (Default:                         |  |  |

|                                               | classifier_svm)                                            |  |  |

| parallel_feature_evaluation                   | Enable/Disable Parallel Feature Evaluation                 |  |  |

| parallel_constraint_evaluation                | Enable/Disable Parallel Constraint Evalua-                 |  |  |

|                                               | tion                                                       |  |  |

| constraints                                   | Enable/Disable Constraints                                 |  |  |

| async_feature_eval                            | Enable/Disable Asynchronous Feature Evalu-                 |  |  |

| async_reature_evat                            | ation                                                      |  |  |

| feature_selection                             | Enable/Disable Feature Selection                           |  |  |

| Tuning Algorithm Description                  |                                                            |  |  |

| tune Default, trains on entire training input |                                                            |  |  |

| itune                                         | Incremental tuning, optional <i>iter</i> or <i>acc</i> pa- |  |  |

|                                               | rameters                                                   |  |  |

Table 2.2: Configuration options in the Nitro Autotuner interface.

```

from nitro.autotuner import *

from nitro.code_variant import *

import glob

# Set tuning properties for spmv

spmv = code_variant("spmv", 6)

spmv.classifier = svm_classifier()

spmv.constraints = False

spmv.parallel_feature_evaluation = False

spmv.constraints = True

spmv.async_feature_eval = False

tuner = autotuner("spmv")

# Set global tuning properties

matrices = glob.glob("inputs/training/*.mtx")

tuner.set training args(matrices)

tuner.set build command("make")

tuner.set clean command("make clean")

# Tune

tuner.tune([spmv])

```

Figure 2.3: Example Nitro Autotuner interface for SpMV.

file also enables us to use the C++ template mechanism to selectively generate relevant code.

### 2.2 The Nitro Autotuner

This section elaborates on the functionality of the Nitro Autotuner. We describe how it builds a model for variant selection and its optimizations and heuristics to reduce the overhead of training and feature evaluation.

#### 2.2.1 Building a Model for Variant Selection

As mentioned in the previous section, the Nitro Autotuner automatically constructs a model for variant selection using SVMs, a form of supervised classification. Supervised classification utilizes a set of labeled training examples to infer a function that maps new, unseen input instances to their correct labels. A set of training examples of the form  $\langle \mathbf{x}_i, y_i \rangle$ is provided, where each  $\mathbf{x}_i$  refers to a feature vector and  $y_i$  refers to the corresponding label for  $\mathbf{x}_i$ . In our case, the label set is integers in the range  $\{0, 1, ... | V | -1\}$ , where V is the set of variants. During the training phase, for each training input *i* with corresponding feature vector  $\mathbf{x}_i$ , the Nitro Autotuner performs exhaustive search over the code variants and assigns to label  $y_i$  the integer designating the variant that leads to the best performance. The result of the training phase is a classification model that predicts the appropriate label for a new, unseen feature vector.

Nitro uses the Radial-Basis Function (RBF) [25] kernel to perform classification by default. The features are scaled to the range [-1, 1], and subsequently a cross-validation-based parameter search is performed to find the kernel parameters.

#### 2.2.2 Incremental Tuning to Reduce Training Inputs

The execution time of code variants is difficult to predict in general, and can often be very high for certain inputs. Coupled with the fact that programmers may provide a large number of redundant training instances, the training phase can often become unacceptably time consuming. To reduce the number of training inputs required for the training phase, the Nitro Autotuner supports *incremental tuning*, which enables Nitro to perform exhaustive search of variants on only a subset of the training inputs.

A key observation is that the execution time required to derive feature vectors is typically far lower than the cost of actually executing variants. Therefore, we compute feature vectors for all the given inputs, and compute output labels using exhaustive search (which requires running all variants for that input) for only a small subset of the inputs and then select additional inputs to add to the training set to improve the model.