# ACHIEVING BACKEND ROBUSTNESS FOR TIMED ASYNCHRONOUS CIRCUITS

by

William Lee

A dissertation submitted to the faculty of The University of Utah in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Department of Electrical and Computer Engineering

The University of Utah

December 2016

Copyright  $\bigodot$  William Lee 2016

All Rights Reserved

# The University of Utah Graduate School

## STATEMENT OF DISSERTATION APPROVAL

| The dissertation | n of                        | William Lee               |                                       |

|------------------|-----------------------------|---------------------------|---------------------------------------|

| has been appro   | ved by the following superv | visory committee members: |                                       |

|                  | Kenneth S. Stevens          | , Chair                   | 3/23/2016<br>Date Approved            |

|                  | Alan Davis                  | , Member                  | 3/23/2016                             |

|                  | Pryank Kalla                | , Member                  | Date Approved 3/23/2016 Date Approved |

|                  | Erik L. Brunvand            | , Member                  | 3/23/2016                             |

|                  | Marly Roncken               | , Member                  | Date Approved 3/23/2016 Date Approved |

| and by           | Gianlu                      | ca Lazzi                  | , Chair/Dean of                       |

| the Department   | College/School of           | Electrical and Compute    | r Engineering                         |

|                  |                             |                           |                                       |

and by David B. Kieda, Dean of The Graduate School.

## ABSTRACT

The design of integrated circuit (IC) requires an exhaustive verification and a thorough test mechanism to ensure the functionality and robustness of the circuit.

This dissertation employs the theory of relative timing that has the advantage of enabling designers to create designs that have significant power and performance over traditional clocked designs. Research has been carried out to enable the relative timing approach to be supported by commercial electronic design automation (EDA) tools. This allows asynchronous and sequential designs to be designed using commercial cad tools. However, two very significant holes in the flow exist: the lack of support for timing verification and manufacturing test.

Relative timing (RT) utilizes circuit delay to enforce and measure event sequencing on circuit design. Asynchronous circuits can optimize power-performance product by adjusting the circuit timing. A thorough analysis on the timing characteristic of each and every timing path is required to ensure the robustness and correctness of RT designs. All timing paths have to conform to the circuit timing constraints.

This dissertation addresses back-end design robustness by validating full cyclical path timing verification with static timing analysis and implementing design for testability (DFT).

Circuit reliability and correctness are necessary aspects for the technology to become commercially ready. In this study, scan-chain, a commercial DFT implementation, is applied to burst-mode RT designs. In addition, a novel testing approach is developed along with scan-chain to over achieve 90% fault coverage on two fault models: stuck-at fault model and delay fault model. This work evaluates the cost of DFT and its coverage trade-off then determines the best implementation.

Designs such as a 64-point fast Fourier transform (FFT) design, an  $I^2C$  design, and a mixed-signal design are built to demonstrate power, area, performance advantages of the relative timing methodology and are used as a platform for developing the backend robustness. Results are verified by performing post-silicon timing validation and test. This work strengthens overall relative timed circuit flow, reliability, and testability. This dissertation is dedicated to my wife and my parents.

"If I have seen further it is by standing on the shoulders of giants."

– Isaac Newton

## CONTENTS

| AE  | BSTRACT                                                                                                                                                                                                              | iii                                    |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| LIS | ST OF FIGURES                                                                                                                                                                                                        | ix                                     |

| LIS | ST OF TABLES                                                                                                                                                                                                         | xii                                    |

| AC  | CKNOWLEDGMENTS                                                                                                                                                                                                       | xiv                                    |

| CH  | IAPTERS                                                                                                                                                                                                              |                                        |

| 1.  | INTRODUCTION                                                                                                                                                                                                         | 1                                      |

|     | 1.1 Background1.1.1 Asynchronous Method1.1.2 Relative Timing1.1.3 Relative Timing Tool Flow1.1.4 Timing Validation1.1.5 Design for Testability (DFT)1.1.6 Contribution of this Dissertation1.1.7 Thesis Organization | $2 \\ 2 \\ 3 \\ 3 \\ 4 \\ 6 \\ 8 \\ 9$ |

| 2.  | TIMING PATH-DRIVEN CYCLE CUTTING FOR SEQUENTIAL<br>CONTROLLERS                                                                                                                                                       | 10                                     |

|     | 2.1 Related Work                                                                                                                                                                                                     | $12 \\ 13$                             |

|     | 2.2 Dackground                                                                                                                                                                                                       | $13 \\ 13$                             |

|     | 2.2.2 Greatest Common Path Between Timing Endpoints                                                                                                                                                                  | 15                                     |

|     | 2.2.3 Path Identification from Timing Endpoints                                                                                                                                                                      | 15                                     |

|     | 2.2.4 Cutting the Timing Graph                                                                                                                                                                                       | 15                                     |

|     | 2.2.5 True and False Path Specification                                                                                                                                                                              | 16                                     |

|     | 2.2.6 Classification of Cycles                                                                                                                                                                                       | 17                                     |

|     | <ul><li>2.3 Key Contributions</li></ul>                                                                                                                                                                              | $\frac{19}{19}$                        |

|     | 2.5 Preliminary Results                                                                                                                                                                                              | $\frac{13}{21}$                        |

|     | 2.5.1 Benefits of Correct Cycle Cutting                                                                                                                                                                              | 21                                     |

|     | 2.5.2 Generality of Approach                                                                                                                                                                                         | 22                                     |

|     | 2.6 Rules for Timing Path Driven Cycle Cutting                                                                                                                                                                       | 23                                     |

|     | 2.6.1 Specifying True Paths and Ensuring Timing Arc Fidelity                                                                                                                                                         | 24                                     |

|     | 2.6.2 False Path and External Cycle Removal                                                                                                                                                                          | 24                                     |

|     | 2.6.3 Creating an Acyclic Timing Graph                                                                                                                                                                               | 25<br>26                               |

|     | 2.6.4 Additional Information                                                                                                                                                                                         | $\frac{26}{26}$                        |

|     | 2.0.4.1 Fun Design Module Optimization                                                                                                                                                                               | 20                                     |

|    | 2.6.4.2 Consistency and Rule Correctness                               | 26                                      |

|----|------------------------------------------------------------------------|-----------------------------------------|

|    | 2.6.4.3 Providing Correct Endpoint Sets                                | 26                                      |

|    | 2.7 Developed Cycle Cutting Algorithm                                  |                                         |

|    | 2.7.1 Finding All the Cycles Present in the Circuit                    | 28                                      |

|    | 2.7.2 Timing Paths with False Path Removal Using GCP                   | 29                                      |

|    | 2.7.3 Generating Cycle Cuts                                            | 29                                      |

|    | 2.8 Results                                                            | 33                                      |

|    | 2.8.1 Four-Cycle Handshake Controllers                                 | 33                                      |

|    | 2.8.2 Benchmark Circuits                                               |                                         |

|    | 2.9 Summary                                                            | 40                                      |

| 3. | PATH-BASED TIMING VALIDATION FOR TIMED<br>ASYNCHRONOUS DESIGN          | 43                                      |

|    | 3.1 Background                                                         | 44                                      |

|    | 3.1.1 Asynchronous Designs                                             |                                         |

|    | 3.1.2 Controller Indexing for Mapping Timing Constraints               |                                         |

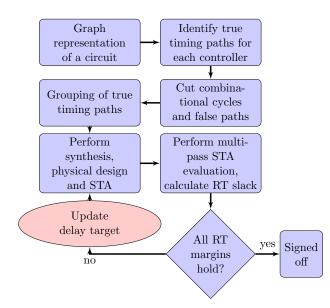

|    | 3.2 Relative Timing Verification                                       |                                         |

|    | 3.2.1 Graph Representation of a Circuit                                | 47                                      |

|    | 3.2.2 Identify Timing Paths for Each Controller                        | 47                                      |

|    | 3.2.3 True Timing Path Driven Cycle Cutting                            |                                         |

|    | 3.2.4 Graph Coloring Algorithm                                         |                                         |

|    | 3.2.5 Perform Static Timing Analysis                                   |                                         |

|    | 3.2.6 Evaluate RT Slack for Every Timing Path                          |                                         |

|    | 3.3 Results                                                            |                                         |

|    | 3.4 Summary                                                            | 53                                      |

| 4. | FAULT COVERAGE FOR RELATIVE TIMED ASYNCHRONOUS                         |                                         |

|    | DESIGN                                                                 | <b>58</b>                               |

|    | 4.1 Fault Coverage on the Control Channels                             |                                         |

|    | 4.1 Performing Stuck-At Fault Simulation                               |                                         |

|    | 4.1.1.1 Single Controller Sequential Test Pattern                      |                                         |

|    | 4.1.1.2 Sequential Test Patterns                                       |                                         |

|    | 4.1.1.3 Fault Analysis of Linear Controllers                           |                                         |

|    | 4.1.1.4 Fault Coverage of FFT Designs                                  |                                         |

|    | 4.2 Fault Coverage on the Data Path                                    | 62                                      |

|    | 4.3 Summary                                                            |                                         |

| 5. | MACRO-BASED TIMING CONSTRAINT MAPPING TO TIMED<br>ASYNCHRONOUS SYSTEMS | 64                                      |

|    |                                                                        |                                         |

|    | 5.1 Related Work                                                       | 65<br>65                                |

|    | 5.2 RT Constraint Template                                             | 65<br>65                                |

|    | 5.2.1 End Point Specification Format                                   | $\begin{array}{c} 65 \\ 66 \end{array}$ |

|    | 5.2.2 Timing Path Constraint                                           | 67                                      |

|    | 5.2.3 Finning Graph Specification                                      | 68                                      |

|    | 5.2.5 Symbolic Pins and Keywords                                       | 68                                      |

|    | 5.2.5 Symbolic Fins and Reywords                                       | 68                                      |

|    | 5.3 Constraint Mapper                                                  | 68                                      |

|    | 5.3.1 Path Reporting and Parsing                                       | 68                                      |

|    | • 0 0                                                                  |                                         |

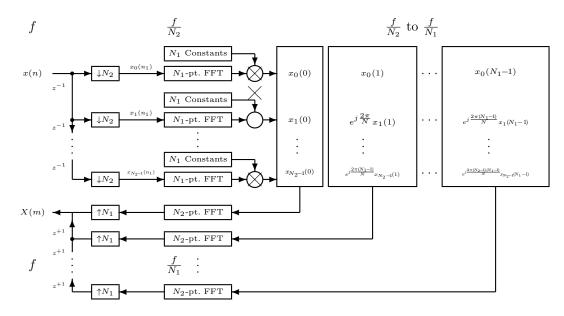

|    | 5.3.2 Mapping         5.4 Experiments         5.4.1 64-Point Multirate FFT         5.5 Summary | 69<br>70<br>70<br>71 |

|----|------------------------------------------------------------------------------------------------|----------------------|

| 6. | CASE STUDIES                                                                                   | 72                   |

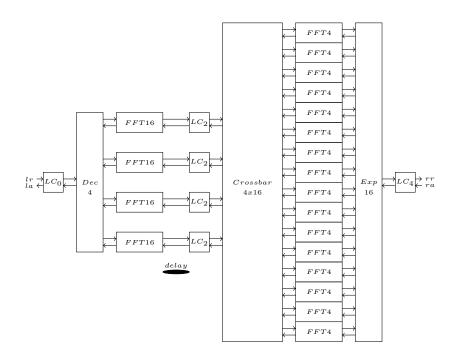

|    | 6.1 Synchronous and Asynchronous 64-Point FFT Design                                           | 72                   |

|    | 6.1.1 Key Contribution                                                                         | 72                   |

|    | 6.1.2 FFT Architecture                                                                         | 73                   |

|    | 6.1.3 FFT Design                                                                               | 74                   |

|    | 6.1.4 Synchronous Design                                                                       | 75                   |

|    | 6.1.5 Asynchronous Design                                                                      | 76                   |

|    | 6.1.6 Results                                                                                  | 80                   |

|    | 6.1.7 Summary                                                                                  | 84                   |

|    | 6.2 Relative Timed Clocking                                                                    | 85                   |

|    | 6.2.1 RT Clocking Method                                                                       | 86                   |

|    | 6.2.2 RT Clocking Types                                                                        | 86                   |

|    | 6.2.3 Verilog Conversion                                                                       | 87                   |

|    | 6.2.4 Direct RT Clocking                                                                       | 88                   |

|    | 6.2.4.1 Additional Setup and Hold Time                                                         | 89                   |

|    | 6.2.5 Indirect RT Clocking                                                                     | 90                   |

|    | 6.2.6 Cycle Accuracy                                                                           | 90                   |

|    | 6.2.7 Design Examples                                                                          | 91                   |

|    | 6.2.7.1 I <sup>2</sup> C with RT Clock Gating $\ldots$                                         | 91                   |

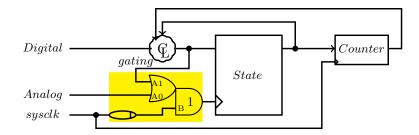

|    | 6.2.7.2 Mixed-Signal Design                                                                    | 92                   |

|    | 6.2.8 Summary                                                                                  | 94                   |

| 7. | CONCLUSION AND FUTURE WORK                                                                     | 95                   |

|    | 7.1 Conclusion                                                                                 | 95                   |

|    | 7.2 Future Work                                                                                | 96                   |

| RE | FERENCES                                                                                       | 98                   |

# LIST OF FIGURES

| 1.1  | 4-Phase Handshake Signals                                                                                                                                                                                                              | 2  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | Simplified Relative Timing Design Flow                                                                                                                                                                                                 | 4  |

| 1.3  | Timing Validation Flow                                                                                                                                                                                                                 | 5  |

| 1.4  | Pulse Clocking Schemes                                                                                                                                                                                                                 | 7  |

| 2.1  | LC Circuit Implementation                                                                                                                                                                                                              | 14 |

| 2.2  | LC Circuit with the Eight Local Cycles Highlighted                                                                                                                                                                                     | 18 |

| 2.3  | External Cycles                                                                                                                                                                                                                        | 18 |

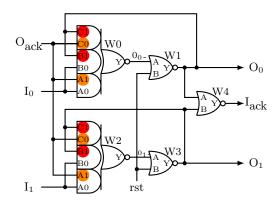

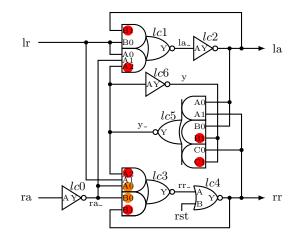

| 2.4  | WCHB Circuit, W0 and W2 are C-Element Implementations. Red and Orange Circles Denote Locally and Externally Cut Timing Arcs.                                                                                                           | 23 |

| 2.5  | Handshake Controller L222 $^{\circ}$ R2242 Synthesized with Petrify                                                                                                                                                                    | 25 |

| 2.6  | Handshake Controller L400 $\circ$ R0000 Synthesized with Petrify                                                                                                                                                                       | 27 |

| 2.7  | Graph Representation for LC circuit                                                                                                                                                                                                    | 28 |

| 2.8  | Covering Table of the Local Cycles for the Linear Controller                                                                                                                                                                           | 30 |

| 2.9  | The sdc Constraints Generated to Remove All Cycles                                                                                                                                                                                     | 31 |

| 2.10 | LC Circuit Implementation Showing Local (Red) and External (Orange) Tim-<br>ing Arc Cuts Through the Marked Gates                                                                                                                      | 32 |

| 2.11 | Covering Table for Set $\phi$                                                                                                                                                                                                          | 33 |

| 2.12 | The sdc Constraints to Remove Timing Paths                                                                                                                                                                                             | 33 |

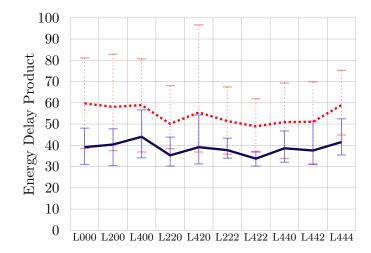

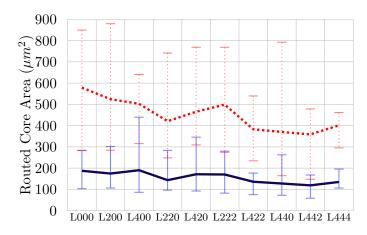

| 2.13 | $e\tau$ Ratio Averaged Across Left Cuts. Interval Shows Largest and Smallest Values for the Cut, Line Passes Through the Mean. Dotted Line Depicts Using Commercial CAD Tools While Solid Line Depicts Using Our Algorithm             | 36 |

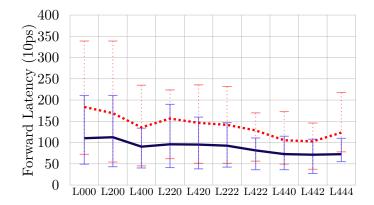

| 2.14 | Forward Latency Averaged Across Left Cuts. Interval Shows Largest and<br>Smallest Values for the Cut, Line Passes Through the Mean. Dotted Line<br>Depicts Using Commercial CAD Tools While Solid Line Depicts Using Our<br>Algorithm  | 36 |

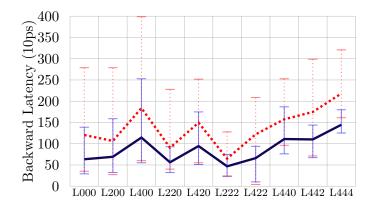

| 2.15 | Backward Latency Averaged Across Left Cuts. Interval Shows Largest and<br>Smallest Values for the Cut, Line Passes Through the Mean. Dotted Line<br>Depicts Using Commercial CAD Tools While Solid Line Depicts Using Our<br>Algorithm | 37 |

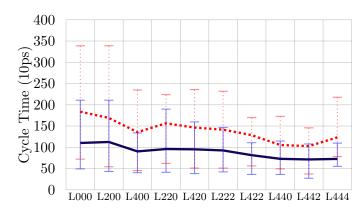

| 2.16 | Cycle Time (Post APR) (10 <i>ps</i> ) Averaged Across Left Cuts. Interval Shows<br>Largest and Smallest Values for the Cut, Line Passes Through the Mean.<br>Dotted Line Depicts Using Commercial CAD Tools While Solid Line Depicts<br>Using Our Algorithm          | 37 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.17 | Core Area Averaged Across Left Cuts. Interval Shows Largest and Smallest Values for the Cut, Line Passes Through the Mean. Dotted Line Depicts Using Commercial CAD Tools While Solid Line Depicts Using Our Algorithm                                               | 37 |

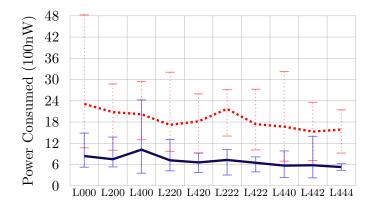

| 2.18 | Power Comsumption Averaged Across Left Cuts. Interval Shows Largest and<br>Smallest Values for the Cut, Line Passes Through the Mean. Dotted Line<br>Depicts Using Commercial CAD Tools While Solid Line Depicts Using Our<br>Algorithm                              | 38 |

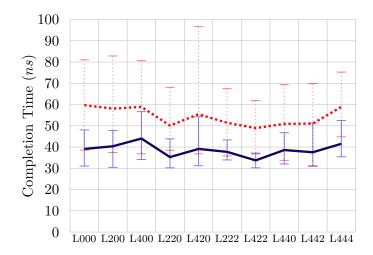

| 2.19 | Computation Time Averaged Across Left Cuts. Interval Shows Largest and<br>Smallest Values for the Cut, Line Passes Through the Mean. Dotted Line<br>Depicts Using Commercial CAD Tools While Solid Line Depicts Using Our<br>Algorithm                               | 38 |

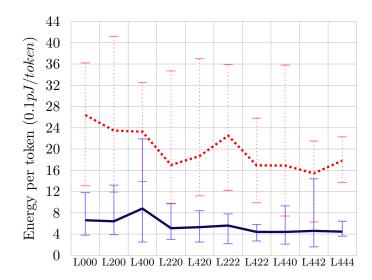

| 2.20 | Averaged Energy Averaged Across Left Cuts. Interval Shows Largest and<br>Smallest Values for the Cut, Line Passes Through the Mean. Dotted Line<br>Depicts Using Commercial CAD Tools While Solid Line Depicts Using Our<br>Algorithm                                | 39 |

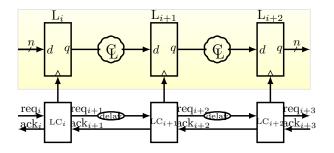

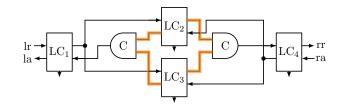

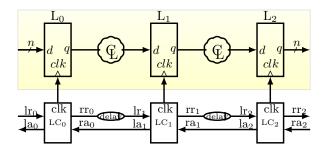

| 3.1  | Timed (Bundled Data) Handshake Design. Each $req_i \uparrow$ Handshake on $LC_i$<br>Indicates New Data are Presented to Pin $d$ of $L_i$ . Delay Sized by Relative<br>Timing Constraint $req_i \uparrow \mapsto L_{i+1}/d + margin \prec L_{i+1}/clk \uparrow \dots$ | 45 |

| 3.2  | Relative Timing Verification Flowchart.                                                                                                                                                                                                                              | 46 |

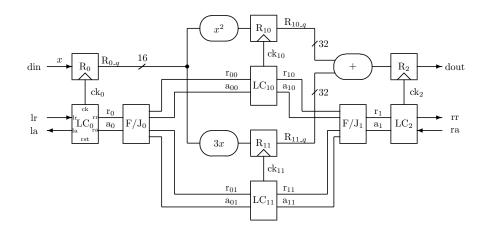

| 3.3  | Example Design: a Simple ASIC Mathematical Pipeline Segment Computing<br>dout $= x^2 + 3x$                                                                                                                                                                           | 46 |

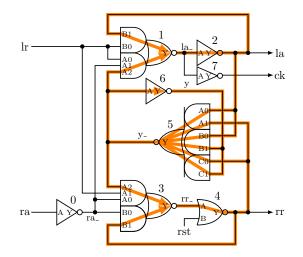

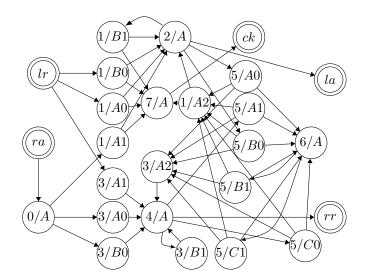

| 3.4  | Circuit Implementation of a Burst-Mode Linear Controller. The Cycles in the Design Have Been Highlighted.                                                                                                                                                            | 48 |

| 3.5  | Graph Representation for the Linear Controller in Figure 3.4                                                                                                                                                                                                         | 48 |

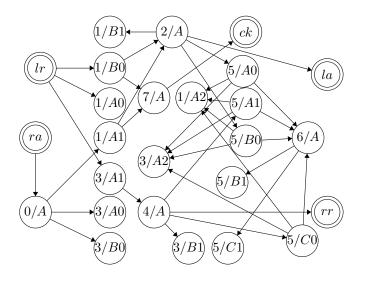

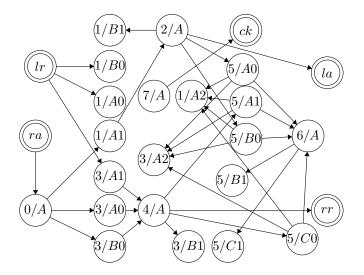

| 3.6  | Local Cycles Have Been Cut and Handshake Channel Cycles are Removed<br>with Forward Cycle Cutting (FCC) by Cutting All Timing Paths Between $ra$<br>and $rr$                                                                                                         | 50 |

| 3.7  | Local Cycles Have Been Cut and Handshake Channel Cycles are Removed<br>with Backward Cycle Cutting (BCC) by Cutting All Timing Paths Between<br><i>lr</i> and <i>la</i>                                                                                              | 51 |

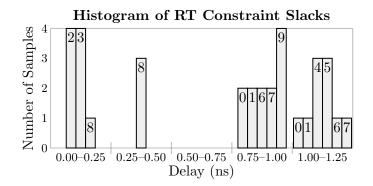

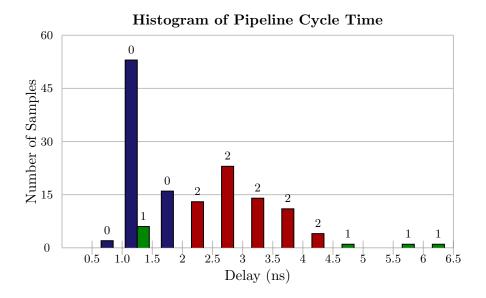

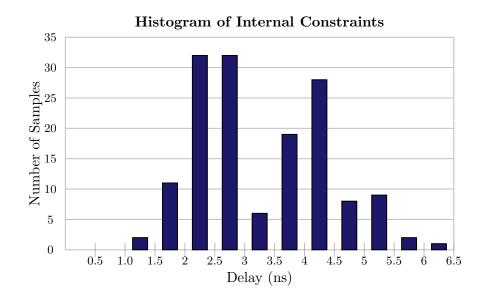

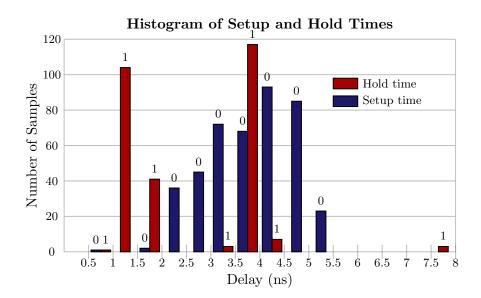

| 3.8  | Slack Distribution for Table 3.1 Constraints Applied to Figure 3.3 Design                                                                                                                                                                                            | 53 |

| 3.9  | Cycle Time Distribution                                                                                                                                                                                                                                              | 55 |

| 3.10 | Distribution of Internal Slack                                                                                                                                                                                                                                       | 55 |

| 3.11 | Slack for External RT Constraints                                                                                                                                                                                                                                    | 56 |

| 4.1  | A 3-Deep Pipeline Contains a Broadcast Fork and a Join Element                                                                                                                                                                                                       | 61 |

| 4.2  | Circuit Implementation of a C Element. The Undetected Faults Have Been Highlighted in Red (SA1) and Orange (SA0).                                                                                                                                                    | 61 |

| 5.1  | Three Stage Pipeline Design                    | 65 |

|------|------------------------------------------------|----|

| 5.2  | LC Circuit Implementation                      | 70 |

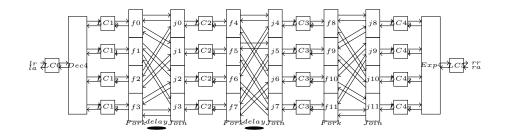

| 6.1  | Multirate FFT Architecture                     | 73 |

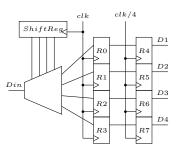

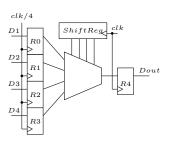

| 6.2  | Synchronous Decimator                          | 75 |

| 6.3  | Synchronous Expander                           | 75 |

| 6.4  | Fork/Join Template                             | 76 |

| 6.5  | Asynchronous Decimator                         | 77 |

| 6.6  | Asynchronous Expander                          | 77 |

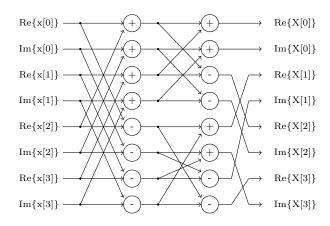

| 6.7  | Data Flow Graph of 4-Point FFT Calculation     | 78 |

| 6.8  | 4-Point FFT Design                             | 78 |

| 6.9  | RTL of FFT Design                              | 79 |

| 6.10 | 64-Point FFT Design                            | 80 |

| 6.11 | Direct RT Clocking                             | 86 |

| 6.12 | Indirect RT Clocking                           | 87 |

| 6.13 | Code Snap of Typical Register                  | 88 |

| 6.14 | Code Snap of RT Clocking Register              | 89 |

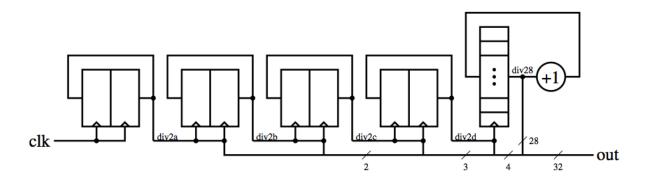

| 6.15 | Direct RT Clocking 32-Bit Counter              | 89 |

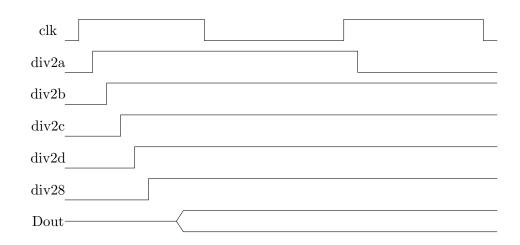

| 6.16 | Waveform of Direct RT Clocking                 | 90 |

| 6.17 | Direct RT Clocking with Data                   | 91 |

| 6.18 | Waveform of Indirect RT Clocking that Glitches | 91 |

| 6.19 | Glitch-Free Waveform of Indirect RT Clocking   | 91 |

| 6.20 | Digital Compute Unit                           | 93 |

# LIST OF TABLES

| 1.1 | ASIC Design Comparison Between Clocked and Relative Timed Designs                                                  | 2  |

|-----|--------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | SDC Constraint Translated from RT Constraint                                                                       | 3  |

| 2.1 | Comparison of Performance Metrics Using Timing Path Cycle Cutting (TPCC)<br>Versus a Commercial EDA Tool Algorithm | 22 |

| 2.2 | Comparison Using Timing Path Cycle Cutting (TPCC) Versus the Algorithm<br>in a Commercial CAD Tool for WCHB        | 24 |

| 2.3 | Full Paths to GCPs Conversion                                                                                      | 28 |

| 2.4 | Internal Cycles                                                                                                    | 28 |

| 2.5 | The Set of GCPs for $\Theta$                                                                                       | 29 |

| 2.6 | The Timing Endpoints Specified in Set $\Phi$                                                                       | 32 |

| 2.7 | Total Cycles Found / Cycles Left $\mathrm{Uncut}_{false\ path}$ / Orphans for the V1 Algorithm                     | 34 |

| 2.8 | The Parameters for the Aggregate Set of Controllers                                                                | 35 |

| 2.9 | Results Comparison for Benchmark Circuits                                                                          | 41 |

| 3.1 | Relative Timing Constraints and True Paths Representation of Figure 3.4 $\ldots$                                   | 49 |

| 3.2 | Relative Timing Graph Nodes as Timing Paths                                                                        | 52 |

| 3.3 | RT Slack Evaluation for the Multiplier Design                                                                      | 54 |

| 4.1 | The Sequential Test Pattern for a Linear Controller                                                                | 60 |

| 4.2 | Fault Coverage of FIFOs                                                                                            | 61 |

| 4.3 | Fault Coverage of Control Channels                                                                                 | 62 |

| 4.4 | Fault Coverage of Complete Asynchronous Designs                                                                    | 63 |

| 4.5 | Results Comparison                                                                                                 | 63 |

| 5.1 | A Subset of the RT Constraints Template for the LC Circuit (Figure $5.2$ )                                         | 67 |

| 5.2 | Connectivity Between $LC_0$ - $LC_2$                                                                               | 69 |

| 5.3 | A Subset of RT Constraints for a 16-Point FFT Design                                                               | 71 |

| 6.1 | The 16-Point FFT Comparison Result (* Constant Field Scaled to 65 nm Technology)                                   | 82 |

| 6.2 | The 64-Point FFT Comparison Result (* Constant Field Scaled to 65 nm<br>Technology, + Nominal Process Voltage)     | 83 |

| 6.3 | Design Comparisons (+ Nominal Process Voltage)                                                                     | 84 |

|     |                                                                                                                    |    |

| 6.4 | I <sup>2</sup> C Design Comparison | 92 |

|-----|------------------------------------|----|

| 6.5 | Mixed Signal Design Comparison     | 93 |

## ACKNOWLEDGMENTS

Firstly, I would like to express my sincere gratitude to my advisor Professor Stevens for the continuous support of my Ph.D study and related research, for his patience, motivation, and immense knowledge. He guided me during research and writing of this dissertation. I could not have imagined having a better advisor and mentor for my Ph.D study.

In addition to my advisor, I would like to thank the rest of my thesis committee: Professor Davis, Professor Brunvand, Professor Kalla, and Professor Roncken, for their insightful comments and encouragement, but also for the hard question which incented me to widen my research from various perspectives.

I thank my fellow lab mates, Vikas Vij, Jotham Manoranjan, Mac Wibbels, and Tannu Sharma for the stimulating discussions, the sleepless nights we were working together before deadlines, and for all the fun we have had in the last four years.

Last but not least, I would like to thank my family: my wife and my parents for supporting me spiritually throughout writing this dissertation and my life in general.

### CHAPTER 1

### INTRODUCTION

Scaling has enabled the transistor revolution, allowing the industry to embed as many as 4 billion transistors on a single chip. This increase in capabilities in semiconductor manufacturing has enabled the design of large, concurrent integrated circuits and systems. Computer-aided design (CAD) algorithms and tools enhance productivity and reliability of complex circuits. However, design methodology has not kept up with improvements in manufacturing. The clocked design flow is largely unchanged over the last 35 years and is targeted toward designs that operate at a single frequency.

Multiple frequency designs offer additional opportunities for optimization on power and performance avenues. Relative Timing (RT) is an asynchronous design methodology that empowers multiple frequency designs [1]. RT designs commonly demonstrate significant energy reduction and performance enhancement. Previous studies have show that several RT designs achieve  $3 \times$  energy reduction [2]–[11]. Some representative designs are listed in Table 1.1. Clocked design forms the baseline. Numbers larger than 1.00 are improvements for all metrics. Pentium front end results are comparing the fabricated designs. The area reported for the 2-phase link design does not include transistor area. The mixed signal design will be described in Section 6.2.7.2. The 64-point FFT design will be discussed in Section 6.1.

RT design enforces circuit timing by constraining a circuit design with a set of timing constraints. The circuit is functional if, and only if, all the constraints are hold. This method for handling circuit timing requires more in-depth algorithmic support to validate the correctness of the circuit operation during the design phase. Postmanufacturing testing is one other essential step in the process needed to validate and observe the correctness of the designs. Reliability and correctness are two main qualities that must be assured if the technology is to be considered commercially ready. This dissertation develops the backend support for RT designs. Backend robustness is achieved by validating event sequencing of the design and implementing design for testability (DFT).

| Design               | Energy | Area | Freq. | Latency | Aggregate       |

|----------------------|--------|------|-------|---------|-----------------|

| Pentium F.E. [3]     | 2.05   | 0.85 | 2.92  | 2.38    | $12.11 \times$  |

| 10-bit FIFO $[4]$    | 2.37   | 1.61 | 1.06  | 2.91    | $11.77 \times$  |

| 2-phase Link [5]     | 1.11   | 0.92 | 0.98  | 1.77    | $1.77 \times$   |

| SAS [5],[6]          | 2.54   | 1.36 | 1.00  | 9.54    | $32.95 \times$  |

| Mixed Signal         | 3.25   | 1.02 | 1.00  | 1.00    | $3.32 \times$   |

| NoC - Aeth/Orion [7] | 4.85   | 6.54 | 2.10  | 1.84    | $122.56 \times$ |

| NoC - COSI [8]       | 1.87   | 5.72 | 1.19  | 2.25    | 28.18           |

| 64-pt FFT [9]        | 2.43   | 2.42 | 1.97  | 3.17    | $36.72 \times$  |

| UART [10]            | 3.99   | 0.92 | 1.00  | 1.00    | $3.67 \times$   |

| OCP Socket [11]      | 4.65   | 1.36 | 2.75  | —       | $17.39 \times$  |

Table 1.1. ASIC Design Comparison Between Clocked and Relative Timed Designs

### 1.1 Background

#### 1.1.1 Asynchronous Method

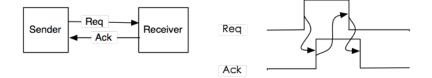

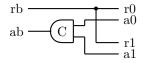

Asynchronous designs use handshake protocols to communicate between modules. There are two common types of handshake protocols: 2-phase and 4-phase. For this study, the 4-phase handshake protocol, which is shown in Figure 1.1, has been selected. Communication between modules starts with the sender raising the request signal. The receiver responds with an acknowledgment of the received signal. The sender then releases the request and the receiver returns to the initial state. Signal transitions are used for communication in the 2-phase handshake protocol. Circuit applies the 4-phase protocol generally have less overhead and are smaller than the one uses the 2-phase protocol [12], [13].

There are two common design styles for asynchronous circuits; bundled-data and delayinsensitive (DI) [14],[15]. The bundled-data style combines a standard combinational data path with a handshake mechanism to control data flow. The DI style encodes the handshake signals with the data to form 1-of-N encoding for communication [16]. In this study, bundleddata is the style chosen for asynchronous circuit design because of its superior power and performance over DI style, and due to the fact that timing verification is more complicated.

Figure 1.1. 4-Phase handshake signals

#### 1.1.2 Relative Timing

Timing in circuit design is where the proverbial rubber hits the road. The effect of time on a system is to order and sequence events. Timing is where asynchronous designs differ from clocked designs.

This creates problems and challenges for circuit optimization and validation because commercial electronic design automation (EDA) tools only support clocked design. However, asynchronous design is still of high interest because it can provide significant power and performance benefits.

Circuit timing in asynchronous circuits can be modeled and observed by applying the relative timing methodology. Relative timing is a method of expressing the signal ordering property of time with the logical expression is shown in Eqn. 1.1. The relative timing constraints have a common timing reference point called the point of divergence (pod). The timing paths between the two points of convergence ( $poc_0$  and  $poc_1$ ) with respect to pod are constrained relative to each other to ensure signal ordering is guaranteed.

The maximum delay of the path from the pod to  $poc_0$  must be less than the minimum delay of the path from the pod to  $poc_1$  for signal ordering to hold. The margin m is added to provide for a more robust event separation.

$$\mathsf{pod} \mapsto \mathsf{poc}_0 + m \prec \mathsf{poc}_1$$

(1.1)

Relative timing constraint paths can be directly translated into a set of synopsys delay constarint (SDC) set\_max\_delay and set\_min\_delay commands, as shown in Table 1.2. Note that the keyword magin below is a supportive command that refers to m in Eqn. 1.1.

#### 1.1.3 Relative Timing Tool Flow [2]

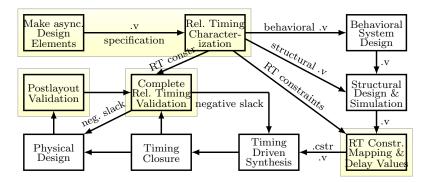

Extending the application of relative timing to the entire end-to-end design and synthesis flow is addressed. There are four main phases of the basic design flow where additional steps are added to the traditional clocked flow.

1. The design and characterization of the relative timed design elements.

| Table 1.2.         SDC Constraint Tran | islated from RT Constraint |

|----------------------------------------|----------------------------|

|----------------------------------------|----------------------------|

set\_max\_delay \$dpoc0 -from pod -to poc0

set\_min\_delay \$dpoc1 -from pod -to poc1

#margin m -from pod -to poc0 -from pod -to poc1

- 2. Mapping of the RT constraints and timing values onto the physical architecture.

- 3. Performing timing closure on the timing targets supplied in the previous step.

- 4. Performing complete postlayout validation of the relative timing constraints.

Figure 1.2 shows the flow including necessary steps to seamlessly integrate with current commercial clocked CAD tools. The highlighted portions in Figure 1.2 are additions to the traditional clocked flow. This study directly addresses (iv) and addresses area (iv) by expanding it to include DFT with RT designs.

#### 1.1.4 Timing Validation

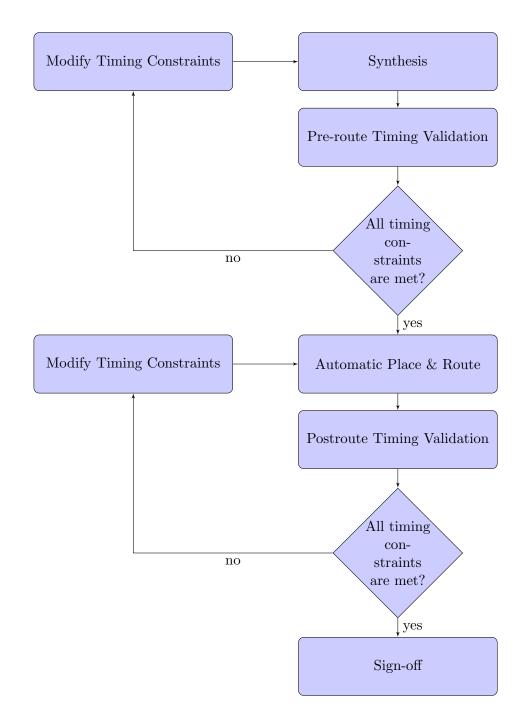

Circuits will only perform correctly when all timing constraints are met. The purpose of timing validation for circuits is to guarantee the correctness of the circuit after the circuit. The typical approach for performing timing validation for physical design is implement-thenverify [17]. This approach requires multiple iterations of time-consuming tasks, including circuit synthesis followed by place and route. The validation flow consists of two inner iterations as shown in Figure 1.3. Automation of the timing validation is needed to optimize the circuit designs and reducing overall nonrecurring engineering cost on the iterations.

Commercial tools and flows use well-developed algorithms to automate timing validation for clocked systems. However, these algorithms only work with circuits that can be represented as a direct acyclic graph (DAG). Asynchronous circuits are naturally cyclic, thus, they are not supported by commercial tools. Although there is a handful of timing validation methods for asynchronous circuits that use timed protocol or time separation of events, such approaches require additional custom tools and modifications on the circuit representation [18],[19].

Figure 1.2. Simplified Relative Timing Design Flow

Figure 1.3. Timing Validation Flow

Timing validation with clocked designs uses static timing analysis (STA) to compute the critical path delays. The setup and hold time of register banks are verified using those critical path delays to compare against global clock signal [20]. Static timing analysis is capable of quickly reporting path delays in a system without feedback. Circuit behavior is not evaluated by using static timing analysis because it reports only the longest or shortest path delay between two timing endpoints. The false paths have to be excluded when applying static timing analysis [21].

An approach to validate timing of asynchronous blocks using STA has been reported for scalable delay-insensitive circuits [22]. A custom timing verification tool is built using STA algorithms. A statistical static timing analysis is reported to analyze asynchronous circuits models [23]. This approach requires custom timing models for each asynchronous component. A tool set to automates the generation of bundled data implementation has been developed [24]. The design methodology uses a desynchronization approach [25]. The tool set includes the use of primetime to analyze path delays. However, the tool only evaluates three specific timing constraints including setup time, hold time, and branch constraints. The tool is not capable of handling timing paths with cycles.

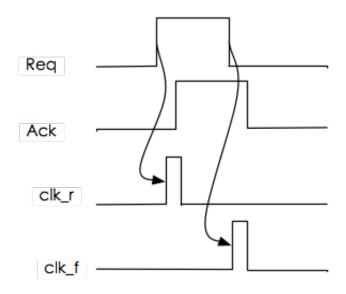

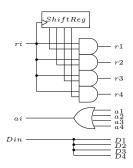

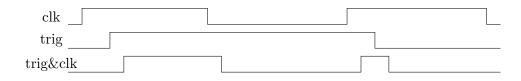

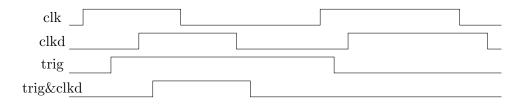

The timing validation for asynchronous circuits requires analyzing delays through cyclic paths. In addition, the tools and flows need to be general and support the richness of asynchronous designs. There are 137 protocols for the family of controllers that implement a 4-phase handshake with data valid on the rising edge of the request. There is also a myriad of different clocking schemes for each of the 137 protocols, including timing intense pulsed clock approaches as well as robust delay insensitive schemes [26].

Finally, there are also various data validity schemes that cooperate with 4-phase handshake protocols, including a scheme where the data is valid on the falling edge of the request signal. The protocol family where the data is valid on the rising edge of the request as well as on the falling edge of the request, along with a pulse clocked scheme for each is shown in Figure 1.4. A flexible and efficient RT validation mechanism, that utilized the commercial tools, is presented in this dissertation.

#### 1.1.5 Design for Testability (DFT)

Manufacturing failures exists due to impurities or imperfect silicon crystalline structure, dust particles, nonplanarity of the wafer, etc [27]. DFT is necessary for developing and producing any IC in the market since it helps identify chips with manufacturing defects postfabrication and ensures the defective chips are discarded, or that workarounds are

Figure 1.4. Pulse Clocking Schemes

devised to account for the defects. DFT enables circuit manufacturers to have the ability to test the IC by supplying a known state and to determine if the result is correct.

DFT also helps detect and diagnose the faulty ICs and save on overall chip cost and improve yield [28]. Finally, DFT is an essential component for better understanding the characteristic of manufactured ICs and providing a way to analyze and improve the product [29]. Including test structure in an IC allows designers and manufacturers to determine the reliability of the chip as well as debug the design after fabrication. Functional fault test and delay fault test are both required in this case since the relative timing methodology uses local clocks rather than a global clock signal. Typical clock systems can slow down the global clock to account for small delay variations caused by process variation. The RT circuit produces an invalid result if timing failures occur within any of the pipe stages. Namely, incorrect data will be stored if the data arrives later than the local clock signal.

There are several DFT approaches using scan design for various asynchronous circuits, including DI circuits, micropipelined, and self-timed circuits [30]–[34]. However, the approaches presented use in-house tools and require drastic modification in order to cooperate with other design approaches.

Similarly, automatic test pattern generation (ATPG) for asynchronous circuits has been implemented, but only applies to macro level asynchronous designs [35]. This ATPG approach did not scale to larger circuits or circuits with multiple asynchronous controllers.

MOUSETRAP, an asynchronous pipeline deisng, uses a D-latch as its state holding

element [36]. Thus, DFT can be performed on the control path by modifying the D-latch. However, the modification of D-Latch introduces  $2.36 \times$  area and  $3.45 \times$  power overhead. The addition of DFT to any designs will result in designs that consume more power and are larger and slower.

One approach is to attach additional fault detector circuitry onto the handshake control channels [37].

However, delay faults could not be detected with this approach. Another approach for detecting delay faults is developed [38]. A latch and muxes are inserted into the handshake control channels in order to control the handshake protocol.

This work targets DFT using scan design for the RT-based bundled-data circuits. These designs have a data path structure similar to those found in a clocked system so that commercial tools can be used to insert scan chains. The control network of the RT design remains unchanged and a functional test is applied. The control network achieves over 90% fault coverage with sequential test patterns.

#### 1.1.6 Contribution of this Dissertation

This dissertation enables the ability to optimize and manufacture timed asynchronous circuit. Algorithms are developed and implemented to automate the analysis for circuit reliability and testability. Major contributions of this work are as follows:

- A methodology is presented that removes combinational cycles in the timing graph of an asynchronous design. This enables the ability to perform timing-driven synthesis and place and route using commercial EDA tools. The methodology includes a formal verification and a cycle cutting algorithm to correctly characterize asynchronous designs.

- Algorithms are developed to perform timing validation for asynchronous designs. The timing validation is capable of analyzing cyclic timing paths using static timing analysis from the commercial tools.

- A flow for design for testability (DFT) of asynchronous designs is presented. The overall test coverage of the asynchronous design is investigated using such flow.

- An algorithm specifies timing constraints for asynchronous designs to incorporate with commercial EDA tools is presented. Specifying design constraints on asynchronous designs is necessary for circuit correctness and performance and this is a manual step. The algorithm addresses these issues.

- Synchronous 16-point and 64-point fast Fourier transform (FFT) designs are implemented to compare with the asynchronous implementations. The asynchronous design is also used as the testbench for the timing validation and DFT flow.

- A clock gating technique for synchronous design is introduced that adopted relative timing methodology. A mixed-signal design and a digital design are implemented using this technique and show power saving benefit.

#### 1.1.7 Thesis Organization

The thesis is organized as follows. Chapter 2 presents a method using a generic cycle cutting algorithm with true timing path to from a directed acyclic graph (DAG) that optimize timing driven synthesis and place and route. The DAGs generated are used for timing validation of true paths in Chapter 3. Chapter 4 presents the design for testing on the asynchronous circuits, including data path and control network. The automatic timing constraints mapping algorithm is introduced in Chapter 5. Chapter 6 shows several design applications that was used as test cases for Chapter 3, 4, and 5. In addition, a new design method for synchronous design is discussed in Chapter 6. Finally, a conclusion is drawn and future research works are discussed.

### CHAPTER 2

# TIMING PATH-DRIVEN CYCLE CUTTING FOR SEQUENTIAL CONTROLLERS<sup>1</sup>

Asynchronous handshake protocols and their associated controllers are used to implement the timing and sequencing of the design. The development of a complex asynchronous design can be simplified due to the modularity and composability of these controllers. All asynchronous circuits have cycles in their communication and timing graphs. Cycles in these graphs come from three primary sources. First, the handshake controllers themselves are often sequential controllers. The state memories in these sequential controllers are commonly implemented using combinational gates with feedback. Second, the basic nature of asynchronous handshake protocols produces cyclical feedback loops; the acknowledge signal creates a circuit cycle that responds to the request. This cyclical ring of request acknowledge logic gates produces an oscillator that dictates the operational frequency of each asynchronous pipeline stage. Thirdly, cycles are created in system level architectures where data is fed back to previous pipeline stages.

Many asynchronous design approaches leverage commercial electronic design automation (EDA) tools to optimize and validate power, performance, and timing correctness, and to perform timing driven optimizations for synthesis and place and route [40]–[45]. The timing driven algorithms in commercial EDA tools employ fast static timing analysis (STA) algorithms which require circuit models to be represented as directed acyclic graphs (DAGs). Unfortunately the sequential nature of asynchronous controllers and design approaches results in numerous topological feedback paths, presenting a fundamental challenge in employing commercial EDA tools.

<sup>&</sup>lt;sup>1</sup>This section has been published in TODAES , 2016 [39]. © 2016 ACM, Inc. http://doi.acm.org/10.1145/2893473. Reprinted, with permission, from William Lee, Vikas Vij, Kenneth S. Stevens, "Timing Path-Driving Cycle Cutting for Sequential Controllers," in ACM Transactions on Design Automation of Electronic Systems Volume 21, Issue 4, Article No. 64, June 2016

Sequential asynchronous circuits must be modeled with acyclic timing graphs to employ commercial EDA tools. This can be achieved with two fundamental elements which are directly supported by the commercial EDA flows in the Synopsys design constraints (sdc) format. First, circuit timing can be defined with a set of path-based timing constraints and their delay targets. Second, a set of timing cuts can be defined that model the native cyclic timing graph of the design as an acyclic graph without cutting the path-based timing constraints.

Following are three key observations for supporting cyclical circuits in the DAG-based commercial tools with the above two constraint sets.

- If a cyclic circuit is given directly to a commercial EDA tool, a DAG representation will automatically be created without respect to timing paths. If a timing path is cut, it will not be employed in the timing driven algorithms of the commercial EDA tools. This is true for both optimization and validation. The cut timing paths are considered to be vacuously true and are not reported as failures since they can not be evaluated.

- 2. A DAG representation of a sequential circuit can not directly model all of the necessary timing of a sequential circuit. For instance, a handshake cycle in an asynchronous design can be implemented with a controllable ring oscillator that has a target frequency based on the function of the pipeline stage. A DAG-based model will cut the ring, and thus, one can not give a frequency based delay target to optimize the design or validate its performance. Thus, sequential timing constraints of an asynchronous design require two or more timing runs to validate full cyclical timing paths.

- 3. All design approaches that map sequential asynchronous designs to commercial EDA tools will require an additional methodology for cycle cutting, timing validation, and performance verification. The methodology and CAD tool reported here for creating DAGs are developed in such a way that it should be applicable to nearly all high level methodologies that address system level timing for asynchronous designs.

Providing a DAG that supports a timing model of a sequential circuit to commercial EDA tools results in several benefits. In some design approaches, such as bundled data design, a nonfunctional design results if timing constraints do not hold. This can occur if timing constraints are cut in creating the DAG. Likewise, commercial EDA can not be employed to evaluate circuit timing unless the graph is represented as a DAG and the timing paths used for evaluation are not cut. Providing a DAG with associated timing constraints enables the

commercial EDA tools to better optimize designs, resulting in significant improvement in the power, area, and performance of such designs.

The fundamental problem is addressed of creating a DAG timing model for sequential controllers and systems that does not cut the set of timing paths used for design synthesis, optimization, and validation. This is the first published work to do so. path-based timing constraints are identified by timing endpoints, just as is done using sdc constraints in the commercial EDA tools. This approach thus simplifies the translation of the timing directives to the commercial EDA tools. An algorithm is implemented that creates cycle cuts that preserve the path-based timing constraints. This work also introduces the concept of identifying paths that must be cut in a design in order to remove cycles formed by netlist connectivity external to the controller, along with its associated algorithm. This algorithm is also used to remove false paths in the design. The tool uses vectorless graph traversal algorithms similar to commercial static timing analysis approaches. It assumes that the design has been technology mapped to specific gate implementations, and inputs the Verilog used in the design. The CAD algorithm is intended to be applied to single asynchronous sequential controllers making them the focal point for timing paths and system level cycle cuts. The combination of vectorless algorithms and controller-based focus makes this CAD tool applicable to most if not all asynchronous design methodologies and styles. The tool writes out sdc constraints that are directly supported by the commercial EDA tools. The tool reports coverage and the quality of the results of the cycle cutting algorithm.

A timed burst-mode protocol along with its circuit realization is employed as an example for this paper. The CAD algorithms in this paper are applied to several examples and compared against the commercial EDA tool. Results for applying the algorithm to 131 separate asynchronous sequential control circuits and to eight benchmark designs are reported. The comparison of these designs is made with respect to forward latency, backward latency, cycle time, area, power and energy per token. The results are also analyzed for quality by ensuring that the cycle cuts produce a DAG, false paths have all been cut, and the number of gates that have no timing path passing through them. Having at least one timing path passing through each gate in a design results in the gates being power and performance optimized based on the timing path constraints.

### 2.1 Related Work

Combinational cycles are generally associated with sequential circuit designs like asynchronous circuits. Cycles can also be present in combinational logic, and some cyclic combinational circuits have been shown to substantially reduce area [46]. Since algorithms in EDA tools require acyclic timing graphs, the problem of finding cycles and analyzing the combinational nature of circuits with cycles has been investigated [47]. Algorithms that generate an equivalent acyclic combinational circuit which reproduces all the combinational behavior of the original cyclic circuit have been developed [48]–[50]. These approaches can not be applied to sequential circuits because they change the sequential behavior when state-holding feedback of a circuit are removed. In order to support general sequential circuits built as combinational logic with feedback, the cyclic circuit must be represented as a DAG without modifying its structure or behavior.

The work that is most closely related applies cycle cutting to the testing of digital circuits with feedback [51]. This is formulated as a covering problem where the sets of paths form the cycles, the solution is to find the minimal number of paths that cut all the cycles. The drawback of this approach is similar to the algorithms in current commercial CAD tools which also cut cycles. A set of cycle cuts, even if they are minimal, will create a DAG, but timing driven optimizations can not be performed because timing paths are cut.

A core function of the algorithms in this work is to identify cycles and paths in a circuit graph. Reconvergent paths and circuit cycles are particularly problematic. Indeed, it has been shown that a circuit can have an exponential number of paths based on the number of gates. This path explosion has proven to be particularly challenging for the delay fault testing community. While path explosion is problematic in some domains, it has not been demonstrated to be a problem in this application. The sequential modules being evaluated have normally been designed to minimize hazards that can often be a byproduct of reconvergent paths. Our algorithms are applied to single sequential controllers which contain fewer than 100 gates. We have applied our tool to the largest published sequential controller designs which tax the limits of what can be synthesized. For all but one circuit, the run times are less than one second in the exhaustive search mode. Pipeline controllers used in nearly all commercial and academic design are more closely represented by the 131 controller set used in our example set.

#### 2.2 Background

#### 2.2.1 Circuit Representation

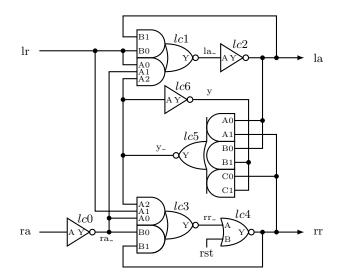

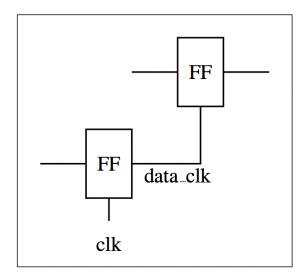

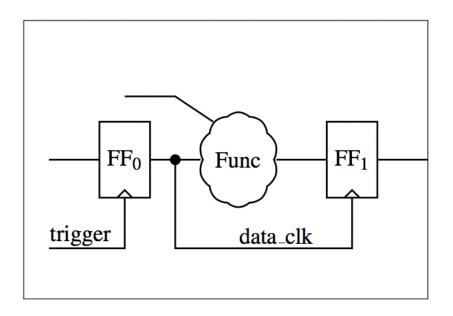

The circuit is represented as a directed graph G = (V, E) where each gate, primary input, and primary output  $v_i \in V$  is a vertex (node) of the graph, and edges  $e_i = (v_x, v_y) \in E$ map primary inputs and gate outputs to primary outputs and gate inputs of the design. We represent a path as a sequence of vertices (nodes) that are connected by edges in G. A cycle is a path that starts and ends with the same vertex.

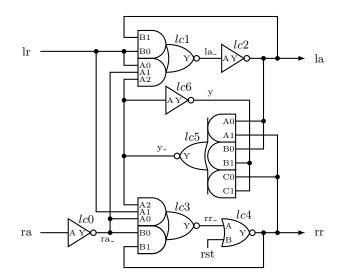

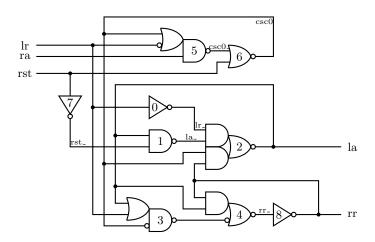

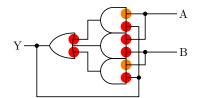

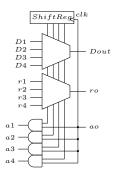

The path [lc1, lc2, lc1] is a cycle in the Figure 2.1 circuit. All noncyclic paths employed in this work are simple paths where repetitions of vertices and edges are not allowed. Each edge in the path can be directly derived; this cycle contains the edge set  $\{(lc1, lc2), (lc2, lc1)\}$ .

Four inputs are provided to this tool. A sequential circuit specified in structural Verilog that has been technology mapped to a set of library gates, a data structure that defines the input and output pins for each gate in the library, a set of *timing endpoints*  $p_i = (v_x, v_y) \in \Theta$ which preserve the greatest common path (or GCP) uncut between  $v_x$  and  $v_y$ , and a set of timing endpoints  $t_i = (v_x, v_y) \in \Phi$  that cuts all paths between  $v_x$  and  $v_y$  that are not GCP paths defined by  $\Theta$ . In this paper we represent timing endpoints in  $\Theta$  and  $\Phi$  as a pair of nodes (A, B) or the relationship pair  $(A \rightarrow B)$ . The set  $\Theta$  defines timing paths that must be preserved, and the set  $\Phi$  defines the *cut paths*.

Each primitive gate in the cell library will have one or more input and one or more output. Each input for gate  $v_y$  will be associated with one or more edge  $(v_x, v_y) \in E$ ; each output for gate  $v_x$  will be associated to one or more edge  $(v_x, v_y) \in E$ .

The algorithms that perform timing driven optimization in the EDA tools employ vectorless static timing analysis (STA). This is accomplished by employing the structural netlist, largely ignoring the functional behavior of the circuit. The simple directed graph G is sufficient to represent the timing graph of a circuit for such purposes. The algorithms developed in this thesis also use only the structural netlist, identifying paths using graph

Figure 2.1. LC Circuit Implementation

traversal algorithms.

#### 2.2.2 Greatest Common Path Between Timing Endpoints

A GCP is a minimal structural path between a pair of timing endpoints. If the node sequence in a shorter path is contained in a longer path between the same endpoints, then the longer path is not a GCP. For example, there are two simple paths that do not contain cycles which connect the timing endpoint lr and rr in Figure 2.1: [lr, lc1, lc2, lc5, lc3, lc4, rr] and [lr, lc3, lc4, rr]. The longer path is not a GCP because it is not minimal; it contains the shorter path. Note that paths that contain cycles will not be GCPs.

#### 2.2.3 Path Identification from Timing Endpoints

Our specification approach does not identify or enumerate individual paths through a circuit; rather we employ timing endpoints to correctly identify both the true and false paths in a circuit. The specification employed in this tool identifies all shortest unique paths (GCPs) between timing endpoints in  $\Theta$ . These are identified as true paths in the design. Conversely, all simple structural paths between the timing endpoints are identified by the timing endpoints in  $\Phi$ . This set is used to identify false paths.

#### 2.2.4 Cutting the Timing Graph

The liberty timing file that is used by the commercial EDA tools defines the path delay from the inputs to outputs of the primitive gates. For example, the NOR gate in Figure 2.1 has a timing path from pin A to pin Y and from pin B to pin Y. These liberty gate level timing paths can be cut with the sdc command set\_disable\_timing. This is the mechanism we employ for cutting timing paths and cycles in a circuit, and the tool outputs the results in the sdc format.

Assume we want to cut the Figure 2.1 cycle [lc3, lc4, lc3]. This can be accomplished by cutting either of the two edges (lc3, lc4) or (lc4, lc3). Removing edge (lc3, lc4) is implemented by disabling the liberty timing edge (A, Y) in gate lc4. We write this out as the sdc constraint set\_disable\_timing -from A -to Y for the lc4 gate in the design. Using this mechanism, our tool can create a timing graph DAG that is supported by commercial EDA.

Edge (lc4, lc3) is the preferable arc to cut in the above example to remove the cycle from the timing graph. If edge (lc3, lc4) is cut, the circuit has no timing path from the primary inputs lr and ra to the primary output rr.

#### 2.2.5 True and False Path Specification

Many structural paths in a design will be false paths that are not behaviorally sensitizable. True paths are the result of the logical sequential behavior of the circuit and how it responds to changes in the primary inputs and internal state. Since both STA and the algorithms employed in this tool are structural, a mechanism must be employed to specify the true and false paths in a design. True paths must be preserved, and false paths in a circuit must be cut. Otherwise timing results will be incorrect and the quality of the timing optimizations performed by the commercial EDA tools will be significantly degraded.

True paths in a design are identified by the timing endpoints in  $\Theta$ . False paths are identified by the timing endpoints in  $\Phi$ .

Often the true timing paths can be directly identified as a GCP. Assume we need to specify that the timing path between lr and rr is to remain uncut because a timing path passes through those nodes. Two simple paths exist between these vertices in Figure 2.1: [lr, lc1, lc2, lc5, lc3, lc4, rr] and [lr, lc3, lc4, rr]. In this case, the GCP identifies the shorter true path, thus placing the timing endpoints (lr, rr) into  $\Theta$  correctly identifies the true paths of the circuit. (The longer path is false because it can not behaviorally occur in this design. Lowering rr is only sensitized by ra. For rr to rise,  $ra_{-}$  and  $y_{-}$  must be asserted and lr must rise. For the longer path to occur,  $y_{-}$  would need to rise, which only occurs when la falls.)

A GCP can identify multiple paths. For instance, timing endpoints (lr, lc5) identify two paths as part of the GCP: [lc1, lc2, lc5] and [lc3, lc4, lc5]. In this case, both of these paths are true paths through the circuit.

In some designs, the true path is not identified as a GCP. Assume that the longer path from lr to rr through the circuit, [lr, lc1, lc2, lc5, lc3, lc4, rr], is the true path which we want to identify. The two timing endpoints  $(lr \rightarrow rr)$  will not correctly identify this path since its GCP will cut the longer path and preserve the shorter path [lr, lc3, lc4, rr]. Non-GCP paths can be identified as true paths by creating sets of timing endpoints whose transitive closure covers the full true path. By selecting lc2 as an intermediate timing endpoint, two sets of timing endpoints  $\{(lr \rightarrow lc2), (lc2 \rightarrow rr)\}$  are created to identify the longer true path and ensure it remains uncut. The GCP for (lr, lc2) is [lr, lc1, lc2] and the GCP for (lc2, rr) is [lc2, lc5, lc3, lc4, rr]. Together these two paths ensure that the longer true path from  $lr \rightarrow lc2$ is identified as true.

Simply identifying true paths through a design is not sufficient to ensure correct timing evaluation of the design. The false paths must also be identified and then cut. Assume that both simple paths between timing endpoints lr and rr remain uncut. Also assume for a moment that the delay of each gate is roughly identical. When a minimum delay analysis is performed on these endpoints, the shorter path will be selected since the latency will be two gate delays. When a maximum delay analysis is performed, the longer path will be employed since it has five gate delays. If the longer (shorter) path is false, it must be cut to ensure correct timing evaluation of the design. Thus, every simple path between timing endpoints that is not a true path of a design must be cut.

When the true path is modeled as a GCP, it will be identified by placing the timing endpoints into set  $\Theta$ . All false paths are identified by placing the same timing endpoints into set  $\Phi$  iff the GCPs identified in  $\Theta$  are not cut by paths identified in  $\Phi$ . If the true timing path requires multiple GCPs to be identified, then each of these pairs will be placed in  $\Theta$ . However, only the single pair that is the timing endpoints of the transitive closure of these paths is included in  $\Phi$  to identify false paths. Thus, if the true path of  $lr \rightarrow rr$  is the longer path, the set  $\{(lr, lc2)(lc2, rr)\}$  will be added to  $\Theta$  but only the single pair (lr, rr)will be added to  $\Phi$ . The GCPs in  $\Theta$  will ensure the longer path remains uncut, but the shorter path will be cut as it is a path identified in  $\Phi$ .

The set of timing endpoints that correctly identify the true and false timing paths through the circuit is provided as an input to this algorithm because this tool is intended to support many circuit families and design methodologies. The generation of the timing paths is dependent on the circuit family and high level timing methodology employed.

#### 2.2.6 Classification of Cycles

Handshake controllers and asynchronous sequential state machines are the primary source and convergence locations of combinational cycles in asynchronous architectures. Thus, high-level timing and optimization methodologies can eliminate most, if not all, cycles by pruning paths in the controllers. This work refers to two classes of combinational cycles based on their relationships to the controller under analysis, expressed below. This work supports cutting both classes of cycles.

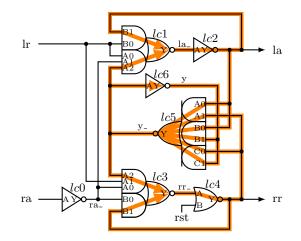

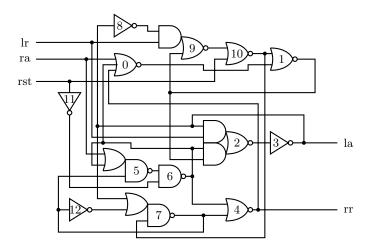

- Local Cycles: Cycles which can be identified by examining the structural netlist of the controller under analysis. Two of the eight local cycles of this circuit are [lc1, lc2, lc1] and [lc3, lc4, lc3], as shown in Figure 2.2.

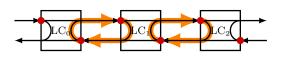

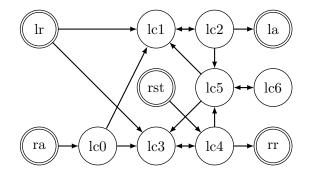

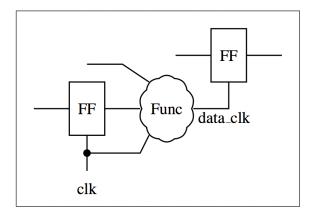

- External Cycles: Cycles which pass through the controller, but can not be identified from the structural netlist of the controller. The leftmost external cycle in Figure 2.3 is [LC<sub>0</sub>/rr, LC<sub>1</sub>/lr, LC<sub>1</sub>/la, LC<sub>0</sub>/ra, LC<sub>0</sub>/rr].

Figure 2.2. LC Circuit with the Eight Local Cycles Highlighted

**Figure 2.3**. External Cycles Formed from Handshake Channels are Highlighted. Additional Unmarked Cycles Exist, such as  $[LC_0/rr, LC_2/lr, LC_2/la, LC_0/ra, LC_0/rr]$ .

Figure 2.2 highlights the eight local cycles to the burst-mode controller. As drawn, three cycles converge pass through lc1, three through lc3, and two cycles through lc6. Figure 2.3 highlights external cycles that are formed when a handshake controller is connected in a linear pipeline. A common set of paths, based on the design and timing methodology, can be identified which will remove the cycles created from the handshake channels. Cutting all paths between the  $(ra \rightarrow rr)$  endpoints will cut the handshake channel cycle. Such an approach allows a single cut path constraint local to the pipeline controller to remove all handshake channel cycles in a design<sup>2</sup>.

Therefore, this algorithm will accept timing endpoints to a controller that will cut external cycles. These cuts are identified by placing the timing endpoints into the set  $\Phi$ .

Three observations can be made based on cycles external to the controllers being evaluated. First, placing a path that should be cut due to an external cycle into  $\Phi$  does not guarantee the path will be cut. If there exists a path between the timing endpoints that is fully covered by GCPs in  $\Theta$ , the path will not be fully cut. This will result in combinational cycles which remain in the timing graph of an architecture. Specifically, this condition will be reported as an error.

<sup>&</sup>lt;sup>2</sup>The location and expression of these cycles are dependent on the high level design methodology employed.

Second, each handshake controller will have its cycle cut values generated independently. Therefore, if multiple different controllers are used in a single design, and they employ a different handshake cut methodology, then cycles can remain in an architecture. (For instance, assume one controller cuts the handshake cycle with the (lr, la) endpoints and another with the (ra, rr) timing endpoints. If both are used in a design, the system can have cycles left uncut.) Thus, the application of this work is dependent on correctly conforming to the system-level methodology employed, and ensuring that it is applied uniformly to the control modules.

Finally, while this work helps support different circuit and timing validation methodologies, it remains dependent on the high level models employed. External cycles created by data path feedback may not be directly supported by adding a cut path in  $\Phi$  for all timed asynchronous circuit and timing methodologies.

### 2.3 Key Contributions

A tool which performs cycle cutting that preserves timing paths was introduced and implemented [2]. The implemented tool is capable of producing a DAG of a circuit once a set of GCPs is provided. The primary contribution of this section is forming an algorithm that integrates with the implemented cycle cutting tool. First, all true paths within the sequential module are identified. Second, the false paths are generated with respect to the true paths. Then, both the true paths and false paths are integrated with the developed cycle cutting tool. The provided true path information guides timing driven synthesis and place and route on circuit optimization. In addition, all false timing paths are removed from the timing graph to improve timing correctness and runtime of the commercial tools. A comparison of implemented tool with and without the true and false timing paths approach is studied.

### 2.4 Evaluation Approach