# PIEZOELECTRIC MICRORESONATORS ON SI FOR INDUCTOR FREE EMBEDDED (ON-CHIP) POWER CONVERTERS IN PV POWERED AUTONOMOUS MICROSYSTEMS

by

Abu Saleh Mohammad Imtiaz

A dissertation submitted to the faculty of

The University of Utah

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Department of Electrical and Computer Engineering

The University of Utah

December 2014

Copyright © Abu Saleh Mohammad Imtiaz 2014

All Rights Reserved

# The University of Utah Graduate School

# STATEMENT OF DISSERTATION APPROVAL

| The dissertation of                    | Abu Saleh Mohammad Imtiaz    |                          |  |

|----------------------------------------|------------------------------|--------------------------|--|

| has been approved by the following sup | pervisory committee members: |                          |  |

| Faisal Khan                            | , Chair                      | 8/13/2014 Date Approved  |  |

| Marc Bodson                            | , Member                     | 8/13/2014  Date Approved |  |

| Hanseup Kim                            | , Member                     | 8/13/2014  Date Approved |  |

| Michael Scarpulla                      | , Member                     | 8/13/2014  Date Approved |  |

| Jeffrey Walling                        | , Member                     | 8/13/2014                |  |

| Shad Roundy                            | , Member                     | 8/13/2014  Date Approved |  |

|                                        |                              |                          |  |

| and by Gian                            | nluca Lazzi                  | _ , Chair/Dean of        |  |

| the Department/College/School of       | Electrical and Computer      | Engineering              |  |

| and by David B. Kieda, Dean of The G   | raduate School.              |                          |  |

### **ABSTRACT**

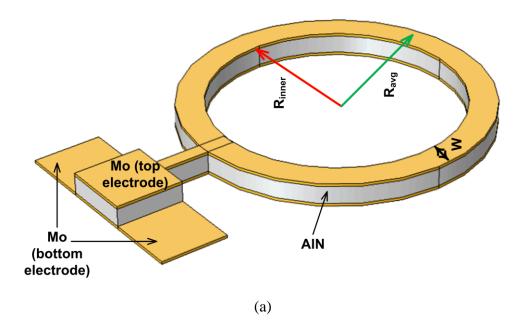

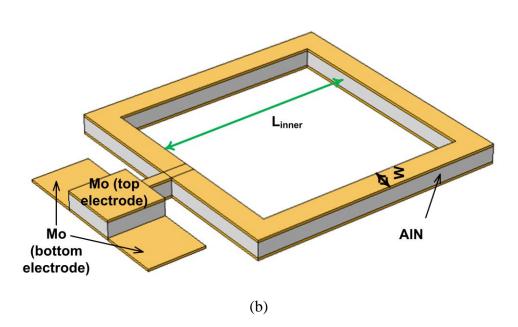

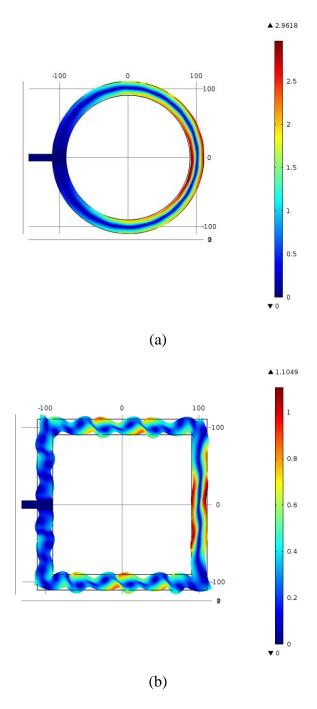

Microelectromechanical systems (MEMS) resonators on Si have the potential to replace the discrete passive components in a power converter. The main intention of this dissertation is to present a ring-shaped aluminum nitride (AlN) piezoelectric microresonator that can be used as an energy-transferring device to replace inductors/capacitors in low power resonant converters for biomedical applications in Autonomous Microsystems. The zero voltage switching (ZVS) condition for a series resonant converter incorporating the proposed MEMS resonator has been presented analytically and verified through experiment. This ZVS condition can be found in terms of the equivalent circuit parameters of the resonator. To the best of my knowledge, a ZVS model for thin film devices has not yet been reported in the literature. A CMOScompatible fabrication process has been proposed and implemented. In addition, the fabricated devices have been characterized, and experimental results are included. The first contour mode AlN MEMS resonator with moderately low resonant frequency and motional resistance is reported in this dissertation with measured resonant frequency and motional resistance of 87.28 MHz and 36.728  $\Omega$ , respectively. The first part of this dissertation discusses the feasibility of a PV powered autonomous microsystem. The reliability, efficiency, and controllability of PV power systems can be increased by embedding the components of a typical power converter on the same Si substrate of a PV cell.

In order to achieve more insight of the macro or surface electronics, a novel fabrication process along with experimental results has been presented in this dissertation demonstrating the integration of PV cells and major components needed to build a power converter on the same substrate/wafer. Because of the cell level power conversion, PV panels constructed from these cells are likely to be immune to partial shading and hot-spot effects. The effect of light exposure on converter switches has been analyzed to understand the converter behavior at various illumination levels. Simulation and experimental results have been provided to support this analysis. In addition to the process-related challenges and issues, this work explains the justification of this integration by achieving higher reliability, portability, and complete modular construction for PV based energy harvesting units for autonomous microsystems.

# TABLE OF CONTENTS

| ΑF  | BSTRACT                                                                                                                          | iii      |

|-----|----------------------------------------------------------------------------------------------------------------------------------|----------|

| LIS | ST OF TABLES                                                                                                                     | viii     |

| ΑC  | CKNOWLEDGEMENTS                                                                                                                  | ix       |

| Ch  | napters                                                                                                                          |          |

| 1.  | INTRODUCTION                                                                                                                     | 1        |

|     | 1.1 Recent Trend in Power Supply Design 1.2 Piezoelectric MEMS Resonator.                                                        | 3<br>5   |

|     | 1.3 Outline of Thesis                                                                                                            | 8        |

| 2.  | MONOLITHICALLY EMBEDDED POWER CONVERTERS FOR PV POWER GENERATION.                                                                | 12       |

|     | 2.1 Existing Microfabrication Processing for On-Chip Components: A Literature Review                                             | 14       |

|     | 2.1.1 Silicon Processing for PV Fabrication                                                                                      | 14       |

|     | <ul><li>2.1.2 Silicon Processing for Circuit Components Fabrication.</li><li>2.1.3 Si or SiC/GaN: Choice of Materials.</li></ul> | 15<br>17 |

|     | 2.1.4 Existing Monolithic Power Converter Solutions                                                                              | 19       |

|     | 2.2 Fabrication.                                                                                                                 | 19       |

|     | <ul><li>2.3 Justification of the Proposed Device Architecture.</li><li>2.4 Simulation Results.</li></ul>                         | 20<br>22 |

|     | 2.5 References.                                                                                                                  | 22       |

| 3.  | FEATURES AND CHALLENGES IN MONOLITHICALLY EMBEDDED POWER CONVERTERS FOR PV POWER GENERATION                                      | 31       |

|     | 3.1 Recent High Reliable, High Efficiency Designs for PV Power Generation                                                        | 32       |

|     | 3.2 Features of the Proposed Integration.                                                                                        | 35       |

|     | 3.2.1 Cost Reduction.                                                                                                            | 35       |

|     | 3.2.2 Partial Shedding                                                                                                           | 37       |

|    | 3.2.3 Enhanced Reliability                                           | 38   |

|----|----------------------------------------------------------------------|------|

|    | 3.3 Challenges of the Proposed Integration                           | 41   |

|    | 3.4 References.                                                      | 43   |

|    |                                                                      |      |

| 4. | CHARACTERIZATION OF MONOLITHICALLY EMBEDDED POWER                    |      |

|    | CONVERTERS FOR PV POWER GENERATION                                   | 49   |

|    |                                                                      |      |

|    | 4.1 Device Fabrication and Characterization.                         | 50   |

|    | 4.2 Embedded Power Converter                                         | 52   |

|    | 4.3 Analysis of Light Generated Effects on the Power Switches        |      |

|    | (Simulation Results)                                                 | 53   |

|    | 4.4 Analysis of Light Generated Effects on the Power Switches        | ۔ ۔  |

|    | (Experimental Results)                                               | 56   |

|    | 4.5 References                                                       | 56   |

| _  | DIEZOEI ECTRIC MEMC DECONATOR IN DOWER CONVERCION                    | 60   |

| Э. | PIEZOELECTRIC MEMS RESONATOR IN POWER CONVERSION                     | 69   |

|    | 5.1 Characteristics of MEMS Resonator                                | 71   |

|    | 5.2 Basic Principles of Contour Mode Piezoelectric Resonator         | 73   |

|    | 5.3 Piezoelectric Devices in Power Conversion.                       | 76   |

|    | 5.4 Merits of Utilization of MEMS Piezoelectric Devices in Power     | 70   |

|    | Converters                                                           | 78   |

|    | 5.5 References                                                       | 79   |

|    |                                                                      |      |

| 6. | FABRICATION AND CHARACTERIZATION OF CONTOUR MODE                     |      |

|    | PIEZOELECTRIC AIN MEMS RESONATOR                                     | 93   |

|    |                                                                      |      |

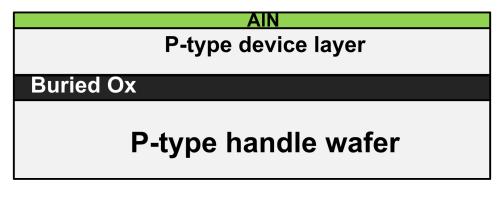

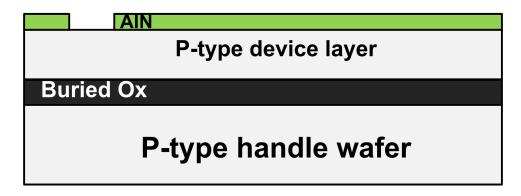

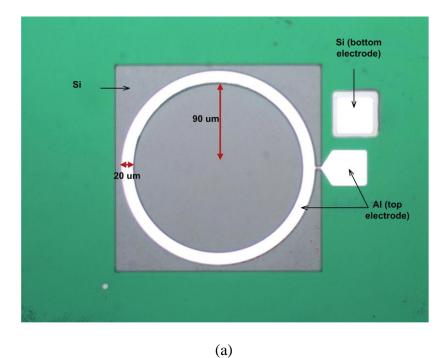

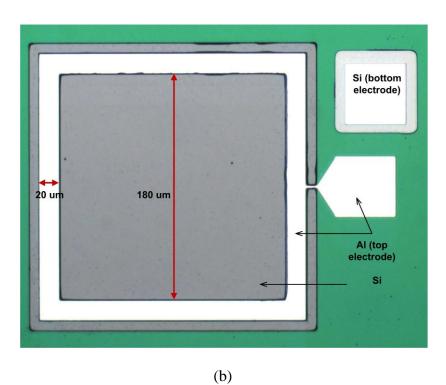

|    | 6.1 Fabrication Process on SOI Wafer                                 | 94   |

|    | 6.2 Fabrication Process on Si Wafer                                  | 96   |

|    | 6.3 Device Characterization.                                         | 98   |

|    | 6.4 Appendix                                                         | 104  |

|    | 6.5 References                                                       | 105  |

| 7  |                                                                      |      |

| 1. | FEASIBILITY ANALYSIS OF USING MEMS RESONATOR IN SERIES               | 100  |

|    | RESONANT CONVERTERS.                                                 | 123  |

|    | 7.1 Inductorless ZVS Condition of MEMS Resonator Based Converter     | 124  |

|    | 7.1 Inductoriess 2 v 5 Condition of WEWS Resonator Based Converter   | 133  |

|    | 7.3 Efficiency Analysis of MEMS Resonator Based Converter            | 134  |

|    | 7.4 Performance Analysis of the Fabricated Device in Series Resonant | 1.07 |

|    | Converter                                                            | 136  |

|    | 7.5 References                                                       | 138  |

|    |                                                                      |      |

| Q  | CONCLUSIONS                                                          | 156  |

# LIST OF TABLES

| 2.1 | Processing steps to integrate CMOS devices with PV cells                                                                                             | 25           |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| 3.1 | Cost breakdown of a typical PV power generating system                                                                                               | 46           |

| 3.2 | Cost breakdown of a typical AC module                                                                                                                | 46           |

| 3.3 | Cost breakdown of the proposed system.                                                                                                               | 46           |

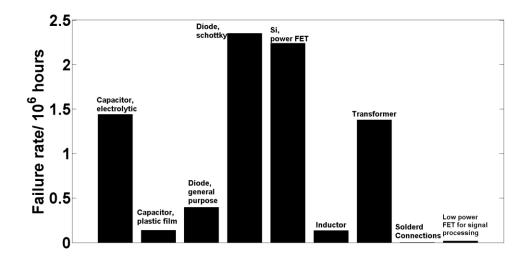

| 3.4 | Failure rate of different components used in power converters                                                                                        | 47           |

| 3.5 | MTBF calculation of proposed embedded converter                                                                                                      | 48           |

| 3.6 | MTBF calculation of the converter constructed from discrete components                                                                               | 48           |

| 5.1 | Estimated comparison of the state of the art devices to MEMS resonator                                                                               | 92           |

| 6.1 | Comparison of the electromechanical properties of three piezoelectric materials                                                                      | 107          |

| 6.2 | Materials coefficient of AlN thin film.                                                                                                              | 107          |

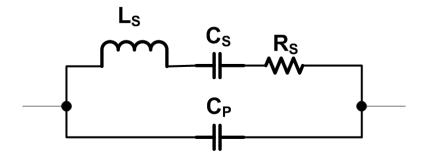

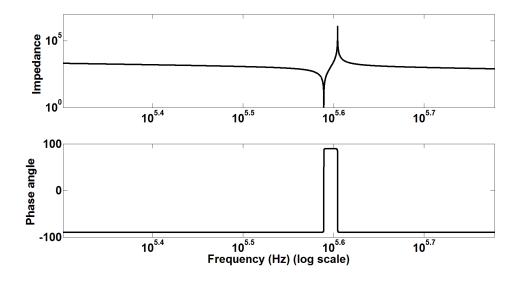

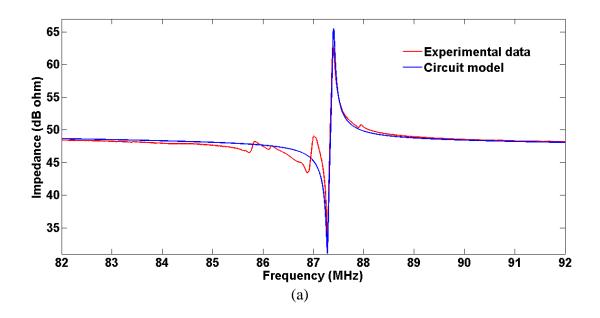

| 6.3 | Equivalent electrical circuit model parameters of the fabricated resonator corresponding to Fig. 5.1 in Chapter 5 using the data shown in Fig. 6.9a  | 108          |

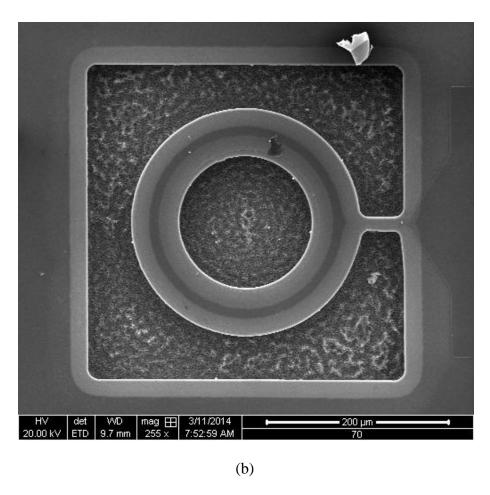

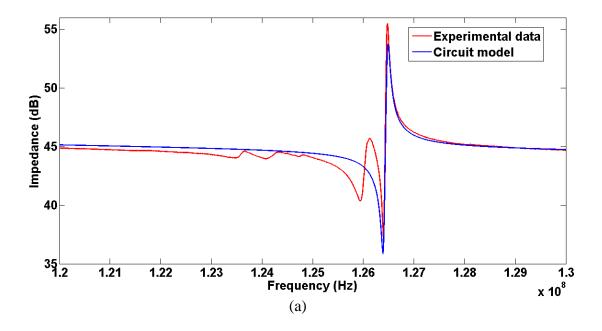

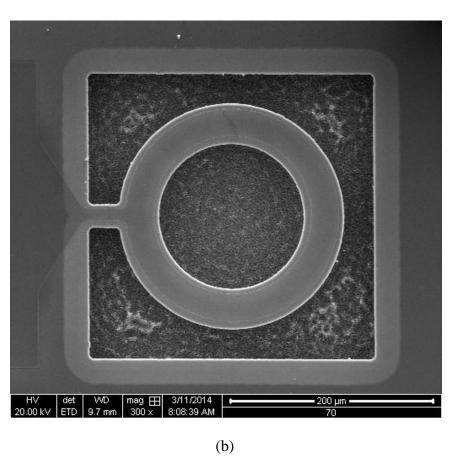

| 6.4 | Equivalent electrical circuit model parameters of the fabricated resonator corresponding to Fig. 5.1 in Chapter 5 using the data shown in Fig. 6.10a | 108          |

| 7.1 | Equivalent electrical circuit model parameters of the piezoceramic resonator corresponding to Fig. 5.1.                                              | 154          |

| 7.2 | Comparison of the PT based converters with the microresonator based convert terms of efficiency and size of the piezoelectric device                 |              |

| 7.3 | Comparison of the presented piezoelectric resonator-based converter with recereported microinductor based converters                                 | ently<br>155 |

### **ACKNOWLEDGEMENTS**

Through more than 25 years of schooling, I came across excellent mentors, colleagues, and friends. This journey would have been impossible without their help, suggestions, and guidance. I am grateful to all of them with all my heart.

Beginning graduate school in a completely different culture and environment was the most challenging task, and completing this task has only been possible due to the guidance of my advisor Professor Faisal Khan. His advice on both research as well as other aspects of my life has been priceless. The suggestions and encouragement that I received from him over the last 5 years have helped me to complete this dissertation. I would like to thank Professor Jeffrey Walling not just for being on my committee but also for the support and help he rendered to me during the last 2 years at the University of Utah. Many thanks to Professor Marc Bodson, Professor Hanseup Kim, Professor Mike Scarpulla, and Professor Shad Roundy for being on my committee and for offering valuable suggestions.

I would like to acknowledge the Electrical Power Research Institute (EPRI) and the University of Utah Nanofab Lab for their financial and technical support towards the research that I conducted in my dissertation. My deepest gratitude to Brian Baker at the University of Utah's Nanofab lab. My initial understanding of microfabrication process development came from him. I want to thank all the members of the power engineering and automation research lab for their help and support in various aspects.

Finally, I would like to acknowledge the continuous inspiration from my mother Habiba Begum and my father Md. Abdur Razzaque Bhuiya. Had it not been so, I would not have made it this far. Thank you so much for being an integral part of my journey so far.

### CHAPTER 1

### INTRODUCTION

The demand for miniaturized autonomous microsystems is increasing for different sensing and monitoring applications. In many applications it is necessary to measure sensor values and then control the actuators accordingly and to interact between (sense/decide/act/communicate) different systems [1]. Hence, autonomous Microsystems are active topics for research. Microbatteries are the conventional way of providing energy to these systems. Contemporary batteries can only supply little total energy (~1–3 J/mm<sup>3</sup>) until they run out in 1–3 years. The fabrication of thin film microbatteries requires nonstandard materials and processes [2]. Furthermore, the replacement of these batteries after a certain period becomes another issue. Therefore, the topic of power harvesting is increasingly considered as a key point to the development of autonomous Microsystems [3]. Continuously operated electronic circuits were reported to draw power less than 1µW/mm<sup>2</sup>, which can be lowered by running at a low duty cycle. Autonomous devices that are self-powered over their full lifetime by extracting energy from the ambient are crucial for applications such as intelligence, active security, or health monitoring purposes [4]. There are few technological challenges for the implementation of autonomous Microsystems. The biggest one is to harvest energy and increase the total efficiency of the system.

This efficiency is divided into the efficiency of the source itself limited by the physical principles and power electronic circuits' efficiency. These Microsystems incorporate energy sources and energy storage as well as energy management, sensing, and communications circuits. Solar energy harvesting is a potential energy source for autonomous Microsystems [5]. Energy management circuits are necessary to deliver maximum power to different loads in different lighting conditions. Integration of solar cell on a chip by "above-IC" complementary metal oxide semiconductor (CMOS) postprocessing has been reported in the literature [6], [7]. This integration should not compromise CMOS performance. However, extra processing steps are necessary. Interestingly, the fabrication process of a solar cell is mature and very much compatible with CMOS processes. Therefore, it is possible to integrate the power electronic circuit on the same die of a solar cell using the same fabrication process, and this can be used for powering the autonomous Microsystems.

In general, a switching power electronic converter/circuit contains power and control inputs and power output. The input raw power is processed according to the control input, and conditioned output power is produced. Efficiency is the key metric parameter while designing a power converter. Typical components of a power electronic converter include resistive elements, capacitive elements, magnetic devices (inductors and transformers), and semiconductor devices operated mainly in switched mode. Capacitors and magnetic devices are essential parts of a power converter because ideally they should not consume power. For the same reason, semiconductor devices are operated as switches—either ON with substantial current with a very small voltage drop or OFF with a substantial voltage drop but nearly zero current.

A periodic switching pattern creates rectangular voltage or current waveforms, which needed to be filtered to obtain a DC output. An RC filter is not an option due to losses, so an LC filter is used. One way to think about the roles of the passive reactive components is that they store energy on time scales similar to the switching period. Therefore, the energy that must be stored in the passive components is inversely proportional to frequency 0. Therefore, the increment of the switching frequency in order to reduce the size of passive components has played a key role in the advancement of power electronics.

### 1.1 Recent Trend in Power Supply Design

Consumers of electronic product have become accustomed to miniaturization and increased levels of functional integration in electronic devices. Cell phones are not simply a device with basic call capability with a monochrome display but a feature-rich computer with GPS, Internet connectivity, PDA functionality, cameras, music players, and high-resolution touch screens. The age old printed circuit board based power supply technology has been impacted by this continuous integration in recent times. A tremendous amount of research is going on to reduce the area and volume occupied by the power converters. Therefore, the converters can be designed for space-constrained and miniaturized applications. Integrating components may provide higher reliability. This can reduce assembly and inventory costs also.

Research advances in semiconductors, magnetics, capacitors, and packaging technologies are driving these integrated solutions of power converters. The following are the technology integration definitions by the Power Sources Manufacturers Association

### (PSMA) [9]:

- Power Supply in Package (PSiP) Separate ICs (switch drivers, controller) within the same package with external (off chip) inductors.

- Power IC: Switch drivers, switches, and control circuits on a single chip with external (off chip) inductors.

- Power Supply on a Chip (PwrSoC) Switch drivers, switches, and control circuits

on a single chip with integrated (on chip) inductors.

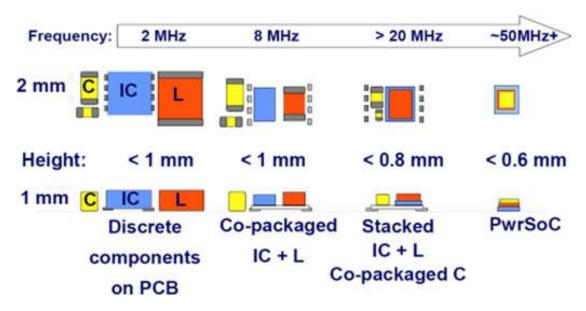

Fig. 1.1 shows the envisioned evolution of the power converter from discrete "power supply on printed circuit board (PCB)" solutions to the PwrSoC technology. PSiP and power ICs technologies are very similar technologies, where the later is suitable for only low power converters (<10 W). The integration of controllers and switch drivers is not feasible for high power converters because the chips are fabricated in different voltage processes (i.e., the controllers are fabricated on a low-voltage process, and the switch drivers are fabricated on a high voltage process). Therefore, PSiP is the suitable technology for higher power. Vicor manufactures many high power converters with PSiP technology.

Many companies such as Enpirion, Fuji, Micrel, National Semiconductor, and TI have been manufacturing products with PSiP and Power IC technology. Enpirion [10] and Micrel [11] copackaged the inductor in a plastic encapsulated package on the same lead frame as the adjacent PMIC. On the other hand, Fuji [12] and National Semiconductor [13] used ceramic ferrite inductor, which acts as a chip scale substrate on which the PMIC is mounted. 3-D stacked PSiP technology has been demonstrated by TI [14]. Few commercially available PSiP and power IC products are given [15]–[22].

Interestingly, there is no commercial product demonstrating the PwrSoC technology to date. This technology is still in the research phase. Only a few articles [23]–[29] have reported the true PwrSoC where the air core inductors are monolithically integrated with the power IC. The switching frequencies of these converters are greater than 50 MHz; thus the air core inductor is sufficient for the power conversion. Obviously, inductance density of air core is much lower than the conventional ferrite core transformer.

The main focus of research towards PwrSoC is on integrating the inductor. Many articles have been published on this integration and are well summarized in [30]–[31]. The performance of these inductors is analyzed in [32]–[33]. Different magnetic materials such as Co–Zr–Ta, Ni–Fe, etc., have been investigated for this purpose. In addition, a number of coil and winding geometries such as spiral, stripe, toroidal, solenoid, etc., have been investigated as well. In this regard, a completely different device such as a thin film piezoelectric resonator has been considered as a potential candidate in this dissertation as a replacement for on-chip inductors in power conversion applications.

### 1.2 Piezoelectric MEMS Resonator

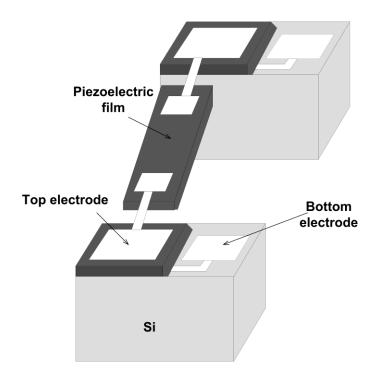

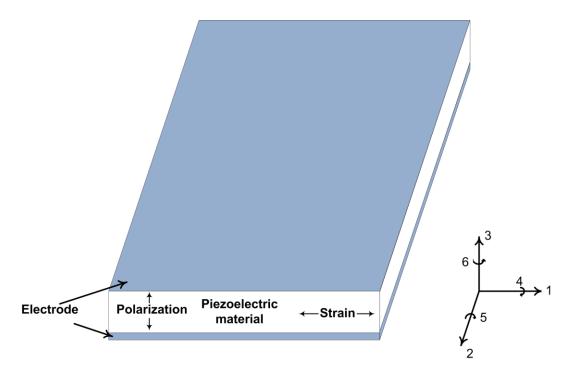

Advances in MEMS design and fabrication enabled growth of piezoelectric resonators span a frequency range from 10s to 100s of MHz on a single substrate. A mechanical motion is produced in the piezoelectric layer when a RF signal is applied across the device. The fundamental resonance is observed when the thickness of the film is equivalent to half the wavelength of the RF signal. Therefore,

$$v = \sqrt{\frac{E}{p}} \tag{1.1}$$

and

$$f = \frac{v}{2d} \tag{1.2}$$

where E, p, d, and v are the elastic constant, density, thickness, and acoustic velocity of the film, and f is the resonant frequency of the resonator [34]. The quality factor of the microresonator is significantly higher than the discrete L-C resonators and ceramic resonators [35].

These resonators are attractive as an on-chip resonator for different reasons:

- Compatibility of thin film devices with silicon and silicon processes.

- The acoustic and electrical properties of piezoelectric material (such as AlN and ZnO) are very attractive.

- The plate capacitor of the device ensures good performance against electrostatic discharge (ESD) and electromagnetic interference (EMI) compared to discrete L-C resonators.

### 1.3 Outline of Thesis

The dissertation is organized in the following chapters.

In Chapter 2, a literature review on macroelectronics or surface electronics is given at the beginning, followed by a literature review on integrating discrete components such as inductors, capacitors, field effect transistors (FET) etc., on-chip is given. A literature review on existing embedded power converters is also given in Chapter 2. The proposed CMOS compatible process to integrate MOS switches, capacitors, and diodes on the same die of a PV cell in the same process run is described next. With an embedded

power-conditioning circuit, PV powered autonomous Microsystems can be constructed using the proposed process. Simulation results of the proposed process are included in Chapter 2 also.

In Chapter 3, the advantages of the embedded power converter for PV power generation is discussed. Challenges to address for the proposed integration are also described in that chapter.

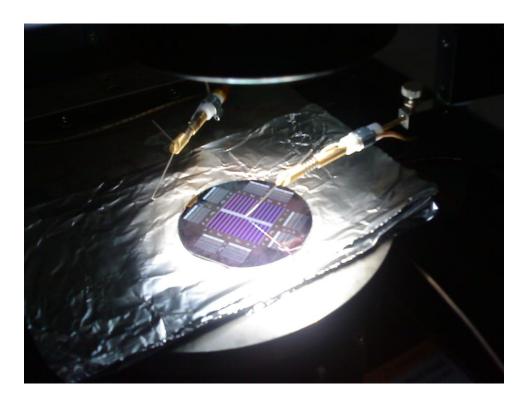

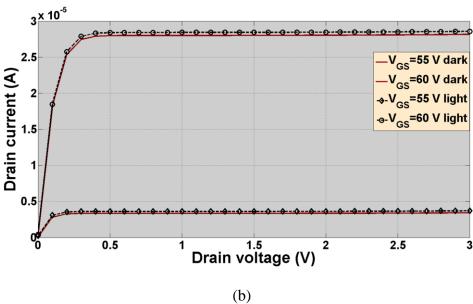

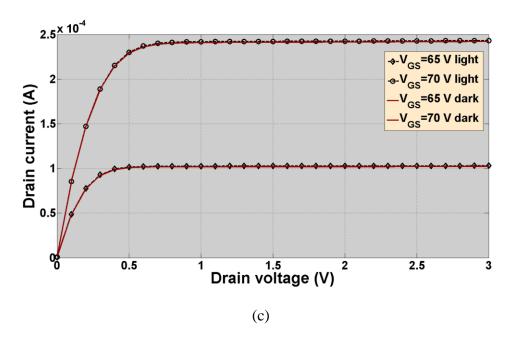

The proposed process is implemented and the experimental results are shown in Chapter 4. The characteristics of different components are depicted first followed by the performance of an embedded power converter for PV power generation. Light generated effects on the FETs are included at the end of Chapter 4.

As described earlier, inductive components are mandatory to achieve dynamic voltage scaling, and this dynamic voltage scaling is an essential feature for a renewable energy harvesting system. A piezoelectric microresonator on Si is proposed in Chapter 5 to replace the on-chip inductor for power converters. Brief discussions about the operating principles and characteristics of the proposed MEMS resonator vibrating in contour mode are provided. A literature review on utilization of piezoelectric devices such as bulk piezoelectric transformers in power conversion is described in Chapter 5 also.

The detailed fabrication process of the contour mode piezoelectric AlN MEMS resonator on Si is described in Chapter 6. The fabricated devices have been characterized and the experimental results are provided in this chapter also.

The feasibility of using this MEMS device in a series-resonant converter is discussed in Chapter 7. Inductorless zero voltage switching (ZVS) in a resonant converter can be

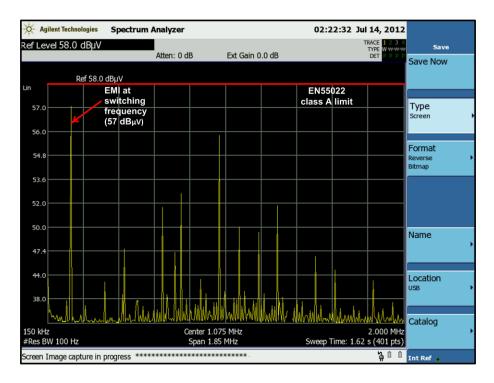

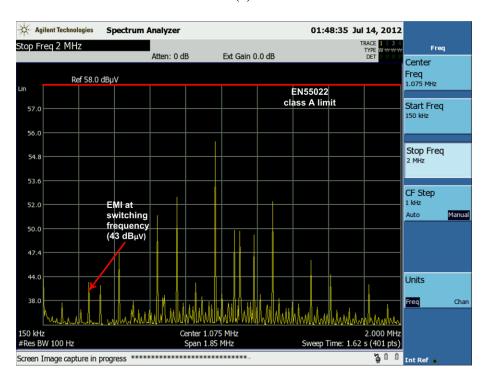

achieved using this device, and a state space model for this ZVS condition is provided in Chapter 7 also with experimental validation. An analysis of the efficiency of the device in the same converter is performed as well. Finally, the superior electromagnetic interference (EMI) performance of the device is proved through experimental results at the end of Chapter 7.

Finally, Chapter 8 summarizes the work presented in this dissertation. Future directions of the MEMS resonator based embedded power converter research are also provided in the final chapter

### 1.4 References

- [1] E. Mackensen *et al.*, "Smart wireless autonomous microsystems (SWAMs) for sensor actuator networks," in *Proc. ISA/IEEE Sensors for Industry*, 2004, pp. 72–78,.

- [2] W.C. West *et al.*, "Lithium microbattery development at the jet propulsion laboratory," *IEEE Aerosp. Electron. Syst. Mag.*, vol. 16, no. 8, pp. 31–33, Aug. 2001.

- [3] M. Ferrari *et al.*, "Modeling, fabrication and performance measurements of piezoelectric energy converter for power harvesting in autonomous microystems," *IEEE. Trans. Instrum. Meas.*, vol. 55, no. 6, pp. 2096–2101, Dec. 2006.

- [4] J. Penders *et al.*, "Human++: from technology to emerging health monitoring concepts," in *Symp. Medical Devices Biosensors*, 2008, pp. 94–98.

- [5] N. K. Pour *et al.*, "A reconfigurable micro power solar energy harvester for ultra-low power autonomous microsystems," in *IEEE Int. Symp. Circuits Systems*, 2013, pp. 33–36.

- [6] J. Lu *et al.*, "Above CMOS a-Si and CIGS solar cells for powering autonomous microsystems," in *IEEE Int. Electron Device Meeting*, 2010, pp. 31–34.

- [7] J. Lu *et al.*, "Integration of solar cells on top of CMOS chips part 1: a-Si solar cells" IEEE Tran. Elec. Devices, vol. 58, no. 7, pp. 2014–2021, Jul. 2011.

- [8] C. R. Sullivan, "Integrating magnetics for on-chip power: Challenges and opportunities," in *Proc. IEEE Custom Integrated Circuits Conf.*, Sep. 2009, pp. 291– 298.

- [9] F. Waldron *et al.* "Technology roadmapping for power supply in package (PSiP) and power supply on chip (PwrSoC)," *IEEE Tran. Power Electron.*, Vol. 28, no. 9, pp. 4137–4145, Sept. 2013.

- [10] Altera. (2014). *Enpirion product*, *EN5322Q* [Online]. Available: http://www.altera.com.

- [11] Micrel. (2014). *Micrel product*, *MIC3385* [Online]. Available: http://www.micrel.com.

- [12] Fuji. (2014). *Fuji product, FB6831* [Online]. Available: http://www.fujielectric.com.

- [13] Texas Instruments. (2014). *National Semiconductor Product, LM3218* [Online]. Available: http://www.ti.com.

- [14] Texas Instruments. (2014). *TI product, TPS82671* [Online]. Available: http://www.ti.com.

- [15] Vishay. (2014). *Vishay product, FX5545G108* [Online]. Available: http://www.vishay.com.

- [16] Bel Power. (2014). *Bel Power product, SRAH-12Fxx0* [Online]. Available: http://www.pwrsoc.com.

- [17] Delta Electronics. (2014). *Delta Electronics product, IPM04S0A0S10FA* [Online]. Available: http://www.digikey.com.

- [18] Linear Technology. (2014). *Linear Tech product, LTM4608* [Online]. Available: http://www.linear.com.

- [19] Murata. (2014). *Murata product, MPD6S022 S* [Online]. Available: http://www.power.murata.com.

- [20] Intersil. (2014). *Intersil product, ISL8201M* [Online]. Available: http://www.intersil.com.

- [21] ROHM. (2014) *ROHM product*, *BP5275* [Online]. Available: http://www.rohm.com.

- [22] Lineage Power. (2014) *Lineage Power product, PicoTLYnx* [Online]. Available: http://www.lineagepower.com.

- [23] J. Wibben and R. Harjani, "A high-efficiency DC–DC converter using 2 nH integrated inductors," *IEEE J. Solid-State Circuits*, vol. 43, no. 4, pp. 844–854, Apr. 2008.

- [24] M.Wens and M. S. J. Steyaert, "A fully integrated CMOS 800-mW fourphase semiconstant ON/OFF time step-down converter," *IEEE Trans. Power Electron.*, vol. 26, no. 2, pp. 326–333, Feb. 2011.

- [25] J. T. DiBene *et al.*, "A 400 Amp fully integrated silicon voltage regulator with indie magnetically coupled embedded inductors," in *Proc. Applied Power Electronics Conf.*, 2010, pp. 1381–1390.

- [26] H. Nakazawa *et al.*, "Micro-DC/DC converter that integrates planar inductor on power IC," *IEEE Trans. Magn.*, vol. 36, no. 5, pp. 3518–3520, Sep. 2000.

- [27] M. Alimadadi *et al*, "A fully integrated 660 MHz low-swing energyrecycling DC–DC converter," *IEEE Trans. Power Electron.*, vol. 42, no. 6, pp. 1475–1485, Jun. 2009.

- [28] J. Ni et al., "Improved on-chip components for integrated DC–DC converters in 0.13 μm CMOS," in Proc. 35th European Solid-State Circuits Conf., 2009, pp. 448– 451.

- [29] S. Musunuri and P. L. Chapman, "Design of low power monolithic DC–DC buck converter with integrated inductor," in *Proc. IEEE Power Electron Specialists Conference*, 2005, pp. 1773–1779.

- [30] D. S. Gardner *et al.*, "Review of on chip inductor structures with magnetic films," IEEE Trans. Magn., vol. 45, no. 10, pp. 4760–4766, Oct. 2009.

- [31] C. O. Mathuna *et al.*, "Review of integrated magnetic for power supply on chip (PwrSoC)," *IEEE Tran. Power Electron.*, vol. 27, no. 11, pp. 4799–4816, Nov. 2012.

- [32] R. Meere *et al.*, "Size and performance tradeoffs in micro-inductors for high frequency DC-DC conversion," *IEEE Tran. Power Electron.*, vol. 45, no. 10, pp. 4234–4237, Oct. 2009.

- [33] R. Meere *et al.* "Magnetic-core and air-core inductors on silicon: A performance comparison upto 100 MHz," *IEEE Trans. Magn.*, vol. 47, no. 10, pp. 4429–4432, Oct. 2011.

- [34] P. Osbond *et al.* "The influence of ZnO and elelctrode thickness on the performance of thin film bulkacoustic resonators," in *Proc. IEEE Ultrasonics*, 1999, pp. 911–914.

- [35] R. Ruby, "A decade of FBAR success and what is needed for another successful decade," in *Symp. Piezoelectricity, Acoustic Waves Device Application (SPAWDA)*, 2011, pp. 365–369.

Fig. 1.1: Vision for evolution of PwrSoC technology (Courtesy of Mathuna et al. © 2012 IEEE) [31]

### CHAPTER 2

# MONOLITHICALLY EMBEDDED POWER CONVERTERS FOR PV POWER GENERATION

The use of large area electronics or macroelectronics is a relatively recent idea. However, significant work has been done to integrate the display driver circuitry on the same substrate with the display itself used in large screen TV monitors. Therefore, there exist many success stories in the literature in this regard [1]. On the other hand, electronic components such as power semiconductor switches, resistors, capacitors, inductors, and other passive elements have been used in the form of discrete components on printed circuit boards (PCB) for several decades. However, the amount of work to integrate these components on the wafer level using custom fabrication processes is insignificant. Therefore integration of components in this form can significantly reduce space and weight compared to standard printed circuit board approaches.

Conventional discrete electronic circuits may not be the most suitable for spreading the components over a large area in order to monitor and address the partial shading problems in a PV system. In addition, surface electronics could be used to address several major failures such as the partial shading, formation of hotspots, bypass diode failure, module cracking, and arcing. Poor interconnection is a key reason for many of these failures.

Other than power electronics, several other research areas such as X ray imaging, solid state lighting with integrated driver circuitry, intelligent smart grid, medical application such as "sensitive skins" [2], etc., require the use of planar electronics. Fabrication challenges in these areas have not been properly addressed using traditional Si CMOS microelectronics. Several other reports have been found on the Department of Defense's (DOD) project of macroelectronics to improve the mission capability of unmanned aerial vehicles (UAVs). To address additional communication in UAV avionics, it needs to incorporate flexible plastics antennas with flexible active circuitry such as low-noise amplifiers (LNAs), RF switches, and digital control circuits.

Some of the macroelectronics projects of NASA include solar sails (kilometer wide light membrane of solar cells) with integrated sensors for health monitoring and reshaping the sail. Therefore it is beneficial to integrate sensors and control circuits with the membrane in order to reduce weight and achieve additional features. The idea of macroelectronics can be used with renewable energy sources by integrating the power converter circuit on the same wafer/substrate used to build the solar energy harvesting devices. Unfortunately, no previous work has been found in the literature on this application of macroelectronics. The concept of an on-die power conversion unit is becoming more prevalent in microprocessors. Although DC-DC converters have been monolithically fabricated for low-power applications, no attempts have been made to use them in the embedded fashion for PV power generation in critical applications such as in battlefield or scientific expedition. Recently, PV cells have been widely utilized to power wireless sensor network (WSNs) and autonomous microsystems for biomedical applications [3], [4]. Embedding PV cells in the substrate could be an efficient way for

generating power on chip. The limited power generated by the embedded PV cell could be sufficient for circuits designed especially for low-power operation leading to autonomous microsystem.

### 2.1 Existing Microfabrication Processing for On-Chip

### Components: A Literature Review

### 2.1.1 Silicon Processing for PV Fabrication

Today's PV production is dominated by Crystalline silicon (c-Si) based technologies [6]. Single crystal (SC-Si) technologies have several advantages such as i) an established technology base, ii) superior material quality, and iii) improved efficiency and stability over the two other conventional solutions (thin film and polycrystalline). For integration purposes, SC-Si technologies must be explored first. The individual components of grid tied inverters (MOSFETs, diodes, inductors, and capacitors) have already been fabricated on the c-Si wafer to implement power processing units inside microprocessors. Moreover, the efficiency of cells made from SC-Si is higher than that of all multicrystalline and thin film solar cells (those have been developed so far) [6] by a significant amount, and solar cells with efficiency of 20%–26% on commercialized Czochralski (Cz) wafers have been reported.

The main disadvantage of SC-Si is the higher fabrication cost compared to multicrystalline and thin film solar cells [6], and this additional cost can be justified if the combination of the cell and the power processing unit could achieve an extended lifespan. Moreover, SC-Si based solar cells require the smallest footprint for a certain power level, and this is advantageous over other PV technologies when space issue is prevalent, such

as in a battlefield.

### 2.1.2 Silicon Processing for Circuit Components Fabrication

In general, a typical power converter may have six different kinds of active and passive components. These components are 1) capacitor, 2) power switch, 3) inductor, 4) diode, 5) resistor, and 6) any integrated circuits for gate driving and control. The following paragraphs explain how these components could be accommodated on Si using the same process.

### 2.1.2.1 Capacitors

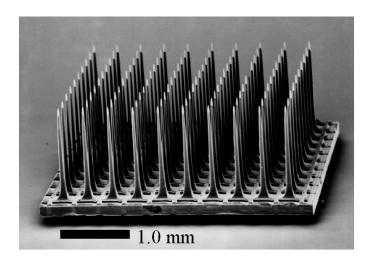

There are many known techniques to form capacitance on Si. The electrolytic capacitor used at the DC bus of the inverter can be replaced by a metal-silicon capacitance with an internal SiO<sub>2</sub> layer. Using a conventional 0.35 μm CMOS foundry process, it is possible to grow polydiffusion capacitance of about 5 nF/mm<sup>2</sup> with an oxide thickness of 5–10 nm [7]. Making high aspect ratio pores in Si by deep reactive ion etching (DRIE), 30 nF/mm<sup>2</sup> capacitance can be realized with standard insulator (SiO<sub>2</sub>/Si<sub>3</sub>N<sub>4</sub>) [8]. Moreover, insulators with high a dielectric constant (Al<sub>2</sub>O<sub>3</sub>) can produce very high capacitance (440 nF/ mm<sup>2</sup>) while fabricating higher aspect ratio pores [9]. MIM (metal- insulator-metal) capacitance is promising to give the highest capacitance for the integration purposes (5–40 nF/ mm<sup>2</sup>) [10], [11].

### 2.1.2.2 MOSFET

Commercially available power MOSFETs are trench MOSFETs. A detailed literature study reveals various techniques for trench MOSFET fabrication [12]–[14]. Reference [14] shows good process steps that can be easily integrated with the power diode.

### 2.1.2.3 Inductor

The idea of "power supply on chip" or "system on chip" for high power conversion is a relatively recent idea. However, no single on-chip power converter has been reported in literature yet offering high efficiency and adjustable conversion ratio [15] at the same time. Switched capacitor integrated voltage regulators (IVR) can provide high efficiencies at reasonable current densities; however, achieving dynamic conversion ratio is very challenging with switched capacitor IVRs [15], [16]. Switched inductors converters (such as a buck converter) can provide high efficiency and high current density, as well as offer a continuous range of conversion. The bottleneck of this switched inductor IVR is the integration of power inductors [17], [18] on silicon.

Very recently, on chip inductors having spiral geometry and fabricated without magnetic materials exhibit inductances ranging from 1–10 nH. The densities of these inductors are lower than 100 nH/mm<sup>2</sup>, occupying a large substrate area. To fabricate a magnetic film that is compatible with standard CMOS processing technology is a challenging task. The magnetic material should have high temperature stability, a good deposition and etching technique, and compatibility with Si technology. Moreover, increasing inductance typically involves increasing the magnetic film thickness, which in turn results in increased eddy currents; therefore, the peak quality factor is reduced.

The high quality factor inductors seem to have lower inductance density too. Therefore, significant research is still in place to design on-chip inductors with a high quality factor and small footprint. Different magnetic materials such as Co–Zr–Ta, Ni–Fe, etc., have been investigated for this purpose. In addition, a number of coil and winding geometries such as spiral, stripe, toroidal, solenoid, etc., have been investigated as well.

### 2.1.3 Si or SiC/GaN: Choice of Materials

Some of the favorable features of the wide band gap materials such as GaN and SiC are order of magnitude higher electrical field and three to five times higher thermal conductivity, higher breakdown voltage, higher doping density, and carrier lifetime. These properties contribute to the following reasoning: high Si–C bond strength facilitates towards higher breakdown voltage; due to high bandgap, higher temperature is needed to transfer carriers from valance to conduction band giving high-temperature withstanding capability. In addition, reduced carrier lifetime leads to faster switching capability [21].

However, the mass development of these devices is still limited by difficulties in crystal growth and material properties. The SiC wafers suffer from major impurities known as micropipes. A significant amount of research was conducted to reduce the density of these defects from hundreds per cm<sup>2</sup> to only a few per cm<sup>2</sup> or even a few per wafer depending on the cost. SiC power diodes are available from Cree, Infineon for a decade.

For low to medium voltage operation, devices with high breakdown voltage may not

add a significant value. A slight increase in efficiency may not be attractive if the cost is very high. However, reliability at high temperatures can be the decisive factor only if the SiC/GaN devices can overcome the prevalent cost issues [22]. SiC/GaN devices seem to be more suitable in renewable energy sectors or in harsh environments, like in space, given that the slight increase in efficiency and high temperature operation can be justified as cost increases.

Other than a slight increase in efficiency and power density, SiC/GaN cannot offer any other favorable features compared to those of Si devices. However, for high power/voltage DC-DC converters such as in accelerators or pulsed power converters for medical systems where a high output voltage is required, SiC/GaN devices can offer a big improvement. In addition, the recent adoption of micro-/nanogrid would be highly unrealistic without the high voltage, high temperature, and low footprint capability offered by the SiC/GaN devices. Therefore, it is apparent that SiC/GaN can go a long way for high power and high voltage operation even considering the higher cost.

In the embedded PV research, the converters are supposed to handle low power as well as low voltage. For low voltage applications, the higher cost incurred by the SiC or GaN devices may not be justified, although other advantages are present. Moreover, the technology to fabricate defect free SiC/GaN is still not mature and therefore, it is a natural choice to investigate the integration capability of Si devices as they use a very mature technology.

### 2.1.4 Existing Monolithic Power Converter Solutions

The concept of an on-die power conversion unit is becoming more prevalent in microprocessors. However, the power-handling capability of these converters is relatively small, and the same concept could be used in order to design larger converters for photovoltaic applications. Although DC-DC converters have been monolithically fabricated for low-power applications, no attempts have been made to use them in the embedded fashion for PV power generation. In the CMOS process, a linear regulator (LR) could be considered as an excellent candidate because of magnetic-element-free operation. However, linear regulators suffer from an inferior efficiency profile, and these designs do not achieve dynamic voltage regulation. In order to overcome this limited efficiency barrier, switched-capacitor (SC) DC-DC converters have been proposed in the literature [23], [24]. The major limitation of many SC converters is the inability to produce the necessary variable conversion ratio (CR). Reference [25] presents an improved SC DC-DC converter with controllable CR, which was implemented using multiple pumping capacitors.

### 2.2 Fabrication

Power converter circuits either use capacitors or inductors to transfer energy. Due to the fabrication complexity involved with inductors [7] and substantial development of on-die Si-capacitors [7]–[9], SC circuits are considered to be the most suitable candidate for embedded PV power converters. Switched capacitor converters are also being used in the PV converters [26], [27] in recent days. The feasibility of maximum power point tracking (MPPT) using switched capacitor converter is described in [26], and a low

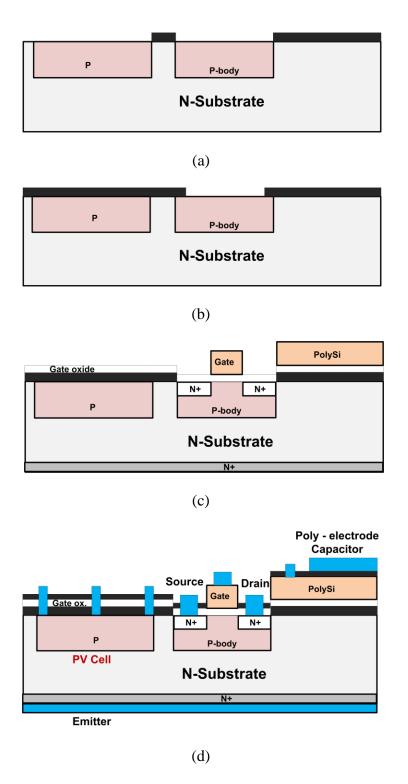

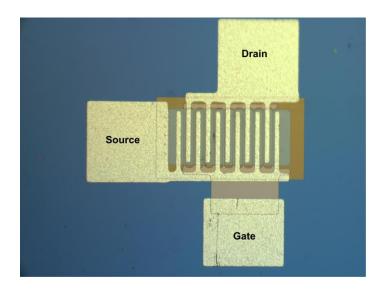

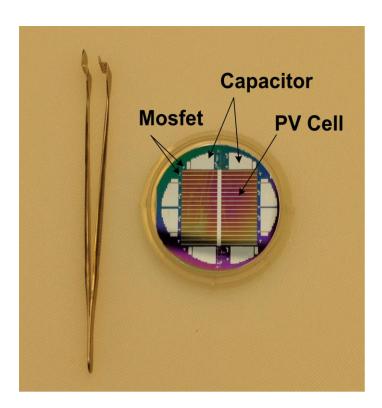

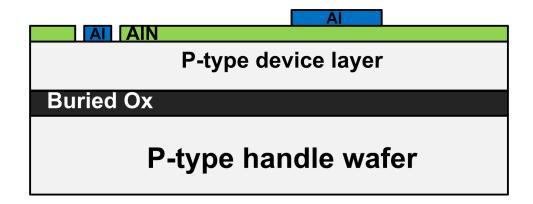

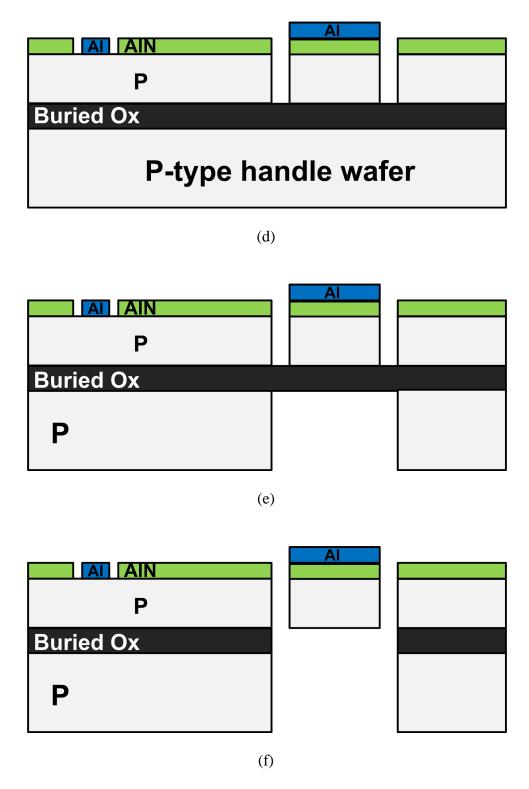

power SC DC-DC converter is used to charge a battery is presented in [27]. In this regard, a CMOS compatible process was proposed by the authors to fabricate converter components along with the PV cells on the same die (Table 2.1). The process steps are depicted in Fig. 2.1. If the converter is integrated only for a few cells, converters constructed from CMOS switches could easily withstand the low voltage and current stress. Moreover, fabrication of several low power converters will not be an issue as the process is compatible with standard CMOS process, and the feasibility of the implementation of these low power converters can be found in [28].

### 2.3 Justification of the Proposed Device Architecture

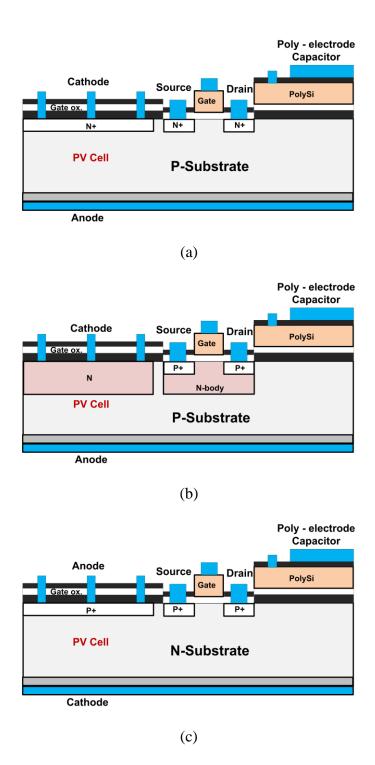

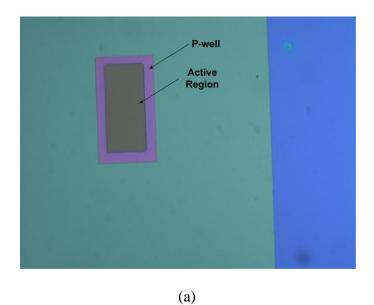

In the standard CMOS process, there are four possible structures of an MOS switch. An NMOS fabricated on the *p*-substrate is shown in Fig. 2.2a. The *P* side (anode) of a *p-n* junction PV cell typically has a higher biasing voltage than the *n* side (cathode). In CMOS circuits, the *p-n* junction between the source/drain and substrate is reverse-biased; therefore, no current flows through the substrate. If the device structure of Fig. 2.2a is chosen, source/drain of NMOS always needs to have a higher voltage compared to the *p*-substrate (anode of PV cell), which is not feasible because two sources needed to be connected to the cathode of the PV cells to form an H-bridge. Also, a higher threshold voltage will be necessary because the substrate (anode of the PV cell) voltage is not set to zero.

PMOS on the p-substrate structure is shown in Fig. 2.2b. The same issue discussed in the previous paragraph exists here as well; the n-well/body needs to be at higher potential than the substrate. This can be achieved by connecting the n-well/body to the high

voltage bus of the chip. However, *p*-type transistors are not optimum for power converter circuits due to lower mobility issues.

The third structure is PMOS on the *n*-substrate (Fig. 2.2c). As the *n*-substrate is the cathode of the PV cell, it will be the ground (GND) terminal of each segments of the multilevel inverter. Therefore, negative voltage will be necessary to turn on these switches, which is not trivial for integrated circuits.

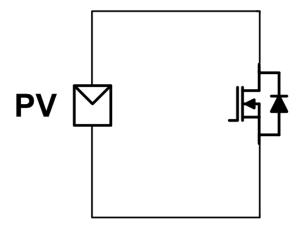

Based on the above phenomenon, NMOS on *n*-substrate was the best option for the embedded power converter for the AC solar cell (Fig. 2.2d). In this structure, the body terminal is not connected with the source, meaning the NMOS has four terminals—gate, drain, source and body unlike conventional three terminal devices. *P* well or body terminal can be tied with the *n*-substrate or the cathode (GND) of PV cells, in order to make sure this diode will not conduct. Therefore, the drains and sources can be connected to various other devices without any apparent issues.

In addition, simplified gate drivers could be used by virtue of the four terminal structure. The gate pulse applied to the device will be referenced to the GND of one segments of the multilevel inverter. Because the body or the well of each of these devices is connected to this GND (*n*-substrate), NMOS will function properly without the need of any complex gate drive circuits, making power processing simpler. The drawback of this structure is that commercial CMOS foundries like MOSIS or X-FAB do not offer this structure; however, Fig. 2.2a and Fig. 2.2b are available commercially because these structures can be used to make complex circuits with only two supply voltages (5 V and 0 V). Therefore, by designing a new fabrication process, Fig. 2.2d can be considered as the most suitable structure for the proposed embedded power converters.

### 2.4 Simulation Results

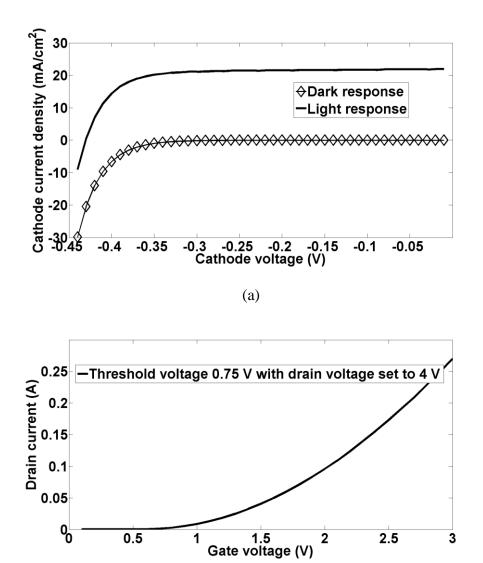

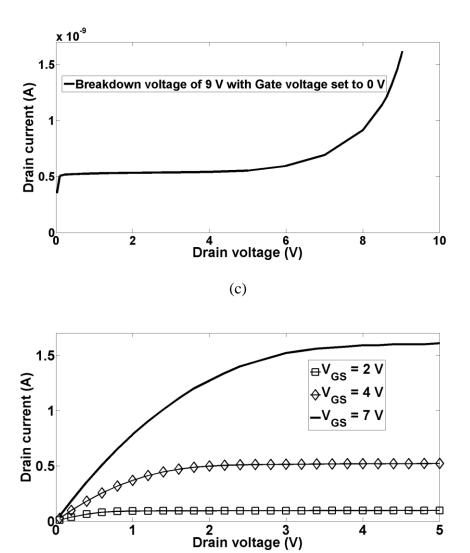

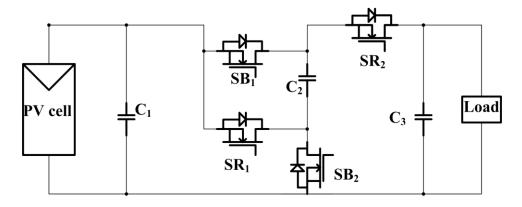

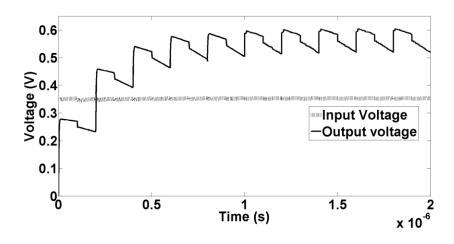

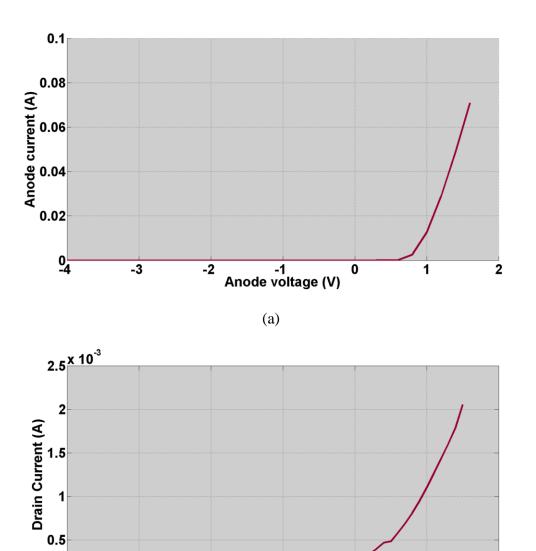

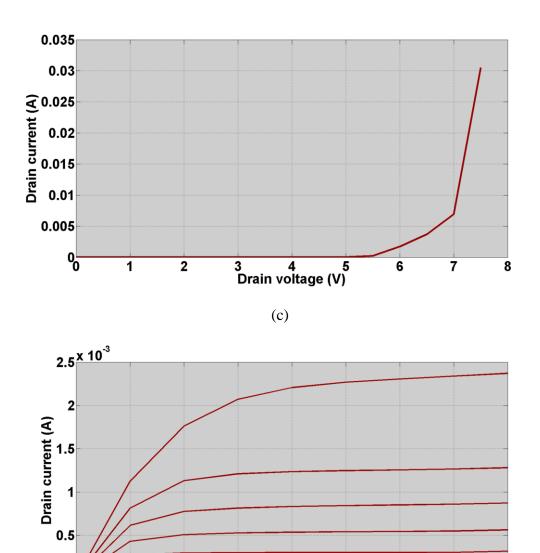

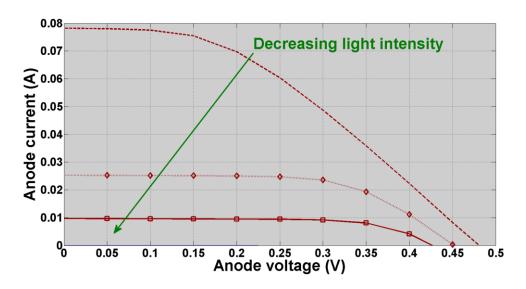

The simplified process described in the previous section has been implemented in the ATHENA [29] process simulator, and the fabricated device characteristics have been obtained using the ATLAS [30] device simulator. These characteristics have been shown in Fig. 2.3. The integrated PV cell has a fill factor of 76%, and the efficiency is found to be 14%. The Atlas software takes a significant amount of time to generate simulation results due to the complexity of the device. In order to reduce simulation time, the Si substrate was considered only 12 µm thick, which is very thin to absorb light properly. Therefore, the open circuit voltage, current density, and efficiency are found to be lower than usual (Fig. 2.3a). The simulated value of the metal polycapacitor was 4 nF/mm², and the MOSFET's threshold voltage and breakdown voltage were achieved as 0.75 V and 9 V, respectively (Fig. 2.3b & 2.3c).

The boosting operation of the embedded MMCCC power converter is illustrated in Fig. 2.4—the input was a PV cell with constant illumination and output load was 25  $\Omega$ . This entire converter was fabricated in the ATHENA process simulator and simulated in Smart Spice of Silvaco, and the simulation results are shown in Fig. 2.5

### 2.5 References

- [1] T. Afentakis *et al.*, "High performance poly-silicon thin film transistor circuits on flexible stainless steel foils," in *Symp. Material Research Society*, 2003, pp. 212–228.

- [2] V. Lumelsky et al., "Sensitive skin," *IEEE Sensors J.*, vol. 1, no. 1, pp. 41–51, Jun. 2001.

- [3] O. Bulteel *et al.*, "High efficiency solar cell embedded in SOI substrate for ULP autonomous circuits," in *Proc. IEEE International SOI Conf.*, 2009, pp. 1–2.

- [4] B. A. Warneke et al., "An autonomus 16 mm solar powered node for distributed

- wireless sensor networks," in *Proc. IEEE Senors*, 2002, pp. 1510–1515.

- [5] C. Chen *et al.*, "SOI cicuits powered by embedded solar cells," in *Proc. IEEE International SOI Conf.*, 2011, pp. 211–214.

- [6] D. D. Malinoskova, "Photovoltaic and photoactive paterials properties, technology and applications," *NATO Sci. Ser., II*, vol. 80, pp. 11–48, Sep. 2001.

- [7] S. C. O Mathuna, *et al.*, "Magnetics on silicon: an enabling technology for power supply on chip," *IEEE Trans. Power Electron.*, vol. 20, no. 3, pp. 585–592, March 2003.

- [8] F. Roozeboom, "High-density, low-loss MOS capacitors for integrated RF decoupling," *Int. Symp. Microelectronics*, 2001, pp. 477–483.

- [9] J. H. Klootwijk *et al.*, "Ultrahigh capacitance density for multiple ALD-grown MIM Capacitor Stacks in 3-D silicon," *IEEE Electron Device Lett.*, vol. 29, no. 7, pp. 740–742, July 2007.

- [10] M. Gros-Jean *et al.*, "High linear Ta2O5 MIM capacitor embedded in Alinterconnected BICMOS technology," in *Proc. WODIM Conf.*, 2002, pp. 73–76.

- [11] E. Fribourg-Blanc *et al.*, "PMNT films for integrated capacitors," in *Proc. WODIM Conference*, 2002, pp. 89–92

- [12] S. M. Sze, *Physics of Semiconductor Devices*, 2nd ed., New York: John Wiley, 1981.

- [13] V. A. K. Temple *et al.*, "A 600-V MOSFET designed for low on-resistance," *IEEE Trans. Electron Devices*, vol. 27, no. 2, pp. 343–348, Feb. 1980.

- [14] K. Shenai, "Optimally scaled low-voltage vertical power DMOSFET's for high-frequency power switching applications," *IEEE Trans. Electron Devices*, vol. 37, no. 4, pp, 1141–1153, Apr. 1990.

- [15] C. O. Mathuna *et al.*, "Review of integratred magnetics for power supply on chip (PwrSoC)," *IEEE Trans. Power Electron.*, vol. 27, no. 11, pp. 4799–4816 Nov. 2012.

- [16] L. Chang *et al.*, "A fully integrated switched capacitor 2.1 voltage converter with regulation capability and 90% efficiency at 2.3A/mm<sup>2</sup>," in *IEEE Symp. VLSI Circuits*, 2010, pp. 55–56.

- [17] H. Le *et al.*, "A 32 nm fully integrated reconfigurable switched capacitor DC–DC converter delivering 0.55 W/mm<sup>2</sup> at 81% efficiency," in *Proc. IEEE Int. Solid-State Circuits Conf.*, 2010. pp. 210–211,

- [18] J. T. DiBene *et al.*, "A 400 amp fully integrated silicon voltage regulator with indie magnetically coupled embedded inductors," in *Proc. IEEE Applied Power*

- Electronics Conf., 2010, pp. 212–219.

- [19] G. Schrom *et al.*, "A 60MHz 50W fine grain package integrated VR powering a CPU from 3.3V," in *Proc. IEEE Applied Power Electronics Conf.*, 2010, pp. 121–129.

- [20] D. Gardner *et al.*,"Review of on-chip inductor structures with magnetic films," *IEEE Trans. Magn.*, vol. 45 no. 10, pp. 4760–4766, Oct. 2010.

- [21] J. A. Carr and D. Hotz, "Assessing the impact of SiC MOSFETs on converter interfaces for distributed energy resources," in *Proc. IEEE Industrial Applications Conf.*, 2007, pp. 336–341.

- [22] J. Biela *et al.*, "Sic vs. Si evaluation potentials for performance improvement of inverter and DC–DC converter systems by SiC power semiconductor," *IEEE Trans. Ind. Electron*, vol. 58, no. 7, pp. 2872–2882, Sept. 2010.

- [23] S. Al-Kuran *et al.*, "GaAs switched capacitor DC-to-DC converter," *IEEE J. Solid-State Circuits*, vol. 35, no. 8, pp. 1121–1127, Aug. 2000.

- [24] D. Ma *et al.*, "Integrated interleaving SC power converters with analog and digital control schemes for energy-efficient microsystems," *J. Analog Integr. Circuits Signal Process.*, Vol. 62, no. 3, pp. 361–372, Mar. 2010.

- [25] I. Chowdhury and D. Ma, "Design of reconfigurable and robust integrated SC power converter for self-powered energy-efficient devices," *IEEE Trans. Ind. Electron.*, vol. 56, no. 10, pp. 4018–4025, Oct. 2000.

- [26] J. J. Cooley and S. B. Leeb, "Per panel photovoltaic energy extraction with multilevel output DC-DC switched capacitor converters," in *Proc. IEEE Applied Power Electronics Conf.*, 2011, pp. 419–428.

- [27] P. K. Peter and V. Agarwal, "A compact switched capacitor DC–DC converter based global peak power point tracker for partially shaded PV arrays of portable equipment," in *Proc IEEE Photovoltaics Specialists Conf.*, 2011, pp. 194–199.

- [28] B. Johnson *et al.*, "Photovoltaic AC module composed of a very large number of interleaved inverters," in *Proc. IEEE Applied Power Electronics Conf.*, 2011, pp. 976–981.

- [29] Silvaco. (2014). [Online]. Available: http://www.silvaco.com/products/tcad/process\_simulation/athena.html.

- [30] Silvaco. (2014). [Online]. Available: http://www.silvaco.com/products/tacd/device\_simulation/atlas.html.

Table 2.1: Processing steps to integrate CMOS devices with PV cells

| through ion implantation (120 keV) is carried out to create a 0.8 µm deep p-type body region (p-well) as well as an anode region for PV (Fig. 2.1a).  2. The second oxide mask blocked the region for the PV cell and opened up the area for the active region (Fig. 2.1b)  3. 10 nm of gate oxide are grown thermally. 1000 nm of polysilicon is deposited by the low pressure chemical vapor deposition (LPCVD) process. This polysilicon layer was patterned to open areas for source and drain (third mask). The remaining polysilicon layer acts as a gate as well as one electrode of the capacitor (Fig. 2.1c)  4. Ion implantation is carried out to form n+ source region and n+ drain region of the MOSFET (Phosphorus doping of 1x10 <sup>20</sup> cm <sup>-3</sup> , 80 keV) (Fig. 2.1c). The polysilicon layer also gets doped to reduce its resistivity.  5. A 500 nm thick intermetal oxide layer is deposited by the LPCVD process. The fourth mask is used to open windows in the inter-metal dielectric film for contacts. A Ti/Al layer (0.4–0.8 µm) is deposited by the sputtering process. Patterning of Al (fifth lithographic step) is done to separate gate, capacitor's upper and lower electrodes, source, drain, and emitter (of solar cell).  6. The next mask opens up the area for bond pads, and the final mask is used to pattern them. In this way, six pads are created for six terminals—gate, capacitor's upper and lower electrodes, source, drain, and emitter | 1. | Using an Oxide mask, Boron diffusion (doping density about 2x10 <sup>17</sup> cm <sup>-3</sup> ) |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--------------------------------------------------------------------------------------------------|

| <ol> <li>The second oxide mask blocked the region for the PV cell and opened up the area for the active region (Fig. 2.1b)</li> <li>10 nm of gate oxide are grown thermally. 1000 nm of polysilicon is deposited by the low pressure chemical vapor deposition (LPCVD) process. This polysilicon layer was patterned to open areas for source and drain (third mask). The remaining polysilicon layer acts as a gate as well as one electrode of the capacitor (Fig. 2.1c)</li> <li>Ion implantation is carried out to form n+ source region and n+ drain region of the MOSFET (Phosphorus doping of 1x10<sup>20</sup> cm<sup>-3</sup>, 80 keV) (Fig. 2.1c). The polysilicon layer also gets doped to reduce its resistivity.</li> <li>A 500 nm thick intermetal oxide layer is deposited by the LPCVD process. The fourth mask is used to open windows in the inter-metal dielectric film for contacts. A Ti/Al layer (0.4–0.8 µm) is deposited by the sputtering process. Patterning of Al (fifth lithographic step) is done to separate gate, capacitor's upper and lower electrodes, source, drain, and emitter (of solar cell).</li> <li>The next mask opens up the area for bond pads, and the final mask is used to pattern them. In this way, six pads are created for six terminals—gate, capacitor's upper and lower electrodes, source, drain, and emitter</li> </ol>                                                                                                                     |    | through ion implantation (120 keV) is carried out to create a 0.8 µm deep                        |

| the area for the active region (Fig. 2.1b)  3. 10 nm of gate oxide are grown thermally. 1000 nm of polysilicon is deposited by the low pressure chemical vapor deposition (LPCVD) process. This polysilicon layer was patterned to open areas for source and drain (third mask). The remaining polysilicon layer acts as a gate as well as one electrode of the capacitor (Fig. 2.1c)  4. Ion implantation is carried out to form n+ source region and n+ drain region of the MOSFET (Phosphorus doping of 1x10 <sup>20</sup> cm <sup>-3</sup> , 80 keV) (Fig. 2.1c). The polysilicon layer also gets doped to reduce its resistivity.  5. A 500 nm thick intermetal oxide layer is deposited by the LPCVD process. The fourth mask is used to open windows in the inter-metal dielectric film for contacts. A Ti/Al layer (0.4–0.8 µm) is deposited by the sputtering process. Patterning of Al (fifth lithographic step) is done to separate gate, capacitor's upper and lower electrodes, source, drain, and emitter (of solar cell).  6. The next mask opens up the area for bond pads, and the final mask is used to pattern them. In this way, six pads are created for six terminals—gate, capacitor's upper and lower electrodes, source, drain, and emitter                                                                                                                                                                                                                                 |    | p-type body region (p-well) as well as an anode region for PV (Fig. 2.1a).                       |

| <ol> <li>3. 10 nm of gate oxide are grown thermally. 1000 nm of polysilicon is deposited by the low pressure chemical vapor deposition (LPCVD) process. This polysilicon layer was patterned to open areas for source and drain (third mask). The remaining polysilicon layer acts as a gate as well as one electrode of the capacitor (Fig. 2.1c)</li> <li>4. Ion implantation is carried out to form n+ source region and n+ drain region of the MOSFET (Phosphorus doping of 1x10<sup>20</sup> cm<sup>-3</sup>, 80 keV) (Fig. 2.1c). The polysilicon layer also gets doped to reduce its resistivity.</li> <li>5. A 500 nm thick intermetal oxide layer is deposited by the LPCVD process. The fourth mask is used to open windows in the inter-metal dielectric film for contacts. A Ti/Al layer (0.4–0.8 μm) is deposited by the sputtering process. Patterning of Al (fifth lithographic step) is done to separate gate, capacitor's upper and lower electrodes, source, drain, and emitter (of solar cell).</li> <li>6. The next mask opens up the area for bond pads, and the final mask is used to pattern them. In this way, six pads are created for six terminals—gate, capacitor's upper and lower electrodes, source, drain, and emitter</li> </ol>                                                                                                                                                                                                                                    | 2. | The second oxide mask blocked the region for the PV cell and opened up                           |

| <ul> <li>deposited by the low pressure chemical vapor deposition (LPCVD) process. This polysilicon layer was patterned to open areas for source and drain (third mask). The remaining polysilicon layer acts as a gate as well as one electrode of the capacitor (Fig. 2.1c)</li> <li>4. Ion implantation is carried out to form n+ source region and n+ drain region of the MOSFET (Phosphorus doping of 1x10<sup>20</sup> cm<sup>-3</sup>, 80 keV) (Fig. 2.1c). The polysilicon layer also gets doped to reduce its resistivity.</li> <li>5. A 500 nm thick intermetal oxide layer is deposited by the LPCVD process. The fourth mask is used to open windows in the inter-metal dielectric film for contacts. A Ti/Al layer (0.4–0.8 μm) is deposited by the sputtering process. Patterning of Al (fifth lithographic step) is done to separate gate, capacitor's upper and lower electrodes, source, drain, and emitter (of solar cell).</li> <li>6. The next mask opens up the area for bond pads, and the final mask is used to pattern them. In this way, six pads are created for six terminals—gate, capacitor's upper and lower electrodes, source, drain, and emitter</li> </ul>                                                                                                                                                                                                                                                                                                          |    | the area for the active region (Fig. 2.1b)                                                       |

| <ul> <li>process. This polysilicon layer was patterned to open areas for source and drain (third mask). The remaining polysilicon layer acts as a gate as well as one electrode of the capacitor (Fig. 2.1c)</li> <li>4. Ion implantation is carried out to form n+ source region and n+ drain region of the MOSFET (Phosphorus doping of 1x10<sup>20</sup> cm<sup>-3</sup>, 80 keV) (Fig. 2.1c). The polysilicon layer also gets doped to reduce its resistivity.</li> <li>5. A 500 nm thick intermetal oxide layer is deposited by the LPCVD process. The fourth mask is used to open windows in the inter-metal dielectric film for contacts. A Ti/Al layer (0.4–0.8 μm) is deposited by the sputtering process. Patterning of Al (fifth lithographic step) is done to separate gate, capacitor's upper and lower electrodes, source, drain, and emitter (of solar cell).</li> <li>6. The next mask opens up the area for bond pads, and the final mask is used to pattern them. In this way, six pads are created for six terminals—gate, capacitor's upper and lower electrodes, source, drain, and emitter</li> </ul>                                                                                                                                                                                                                                                                                                                                                                          | 3. | 10 nm of gate oxide are grown thermally. 1000 nm of polysilicon is                               |

| <ul> <li>drain (third mask). The remaining polysilicon layer acts as a gate as well as one electrode of the capacitor (Fig. 2.1c)</li> <li>4. Ion implantation is carried out to form n+ source region and n+ drain region of the MOSFET (Phosphorus doping of 1x10<sup>20</sup> cm<sup>-3</sup>, 80 keV) (Fig. 2.1c). The polysilicon layer also gets doped to reduce its resistivity.</li> <li>5. A 500 nm thick intermetal oxide layer is deposited by the LPCVD process. The fourth mask is used to open windows in the inter-metal dielectric film for contacts. A Ti/Al layer (0.4–0.8 μm) is deposited by the sputtering process. Patterning of Al (fifth lithographic step) is done to separate gate, capacitor's upper and lower electrodes, source, drain, and emitter (of solar cell).</li> <li>6. The next mask opens up the area for bond pads, and the final mask is used to pattern them. In this way, six pads are created for six terminals—gate, capacitor's upper and lower electrodes, source, drain, and emitter</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    | deposited by the low pressure chemical vapor deposition (LPCVD)                                  |

| <ul> <li>as one electrode of the capacitor (Fig. 2.1c)</li> <li>4. Ion implantation is carried out to form n+ source region and n+ drain region of the MOSFET (Phosphorus doping of 1x10<sup>20</sup> cm<sup>-3</sup>, 80 keV) (Fig. 2.1c). The polysilicon layer also gets doped to reduce its resistivity.</li> <li>5. A 500 nm thick intermetal oxide layer is deposited by the LPCVD process. The fourth mask is used to open windows in the inter-metal dielectric film for contacts. A Ti/Al layer (0.4–0.8 μm) is deposited by the sputtering process. Patterning of Al (fifth lithographic step) is done to separate gate, capacitor's upper and lower electrodes, source, drain, and emitter (of solar cell).</li> <li>6. The next mask opens up the area for bond pads, and the final mask is used to pattern them. In this way, six pads are created for six terminals—gate, capacitor's upper and lower electrodes, source, drain, and emitter</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    | process. This polysilicon layer was patterned to open areas for source and                       |

| <ul> <li>4. Ion implantation is carried out to form n+ source region and n+ drain region of the MOSFET (Phosphorus doping of 1x10<sup>20</sup> cm<sup>-3</sup>, 80 keV) (Fig. 2.1c). The polysilicon layer also gets doped to reduce its resistivity.</li> <li>5. A 500 nm thick intermetal oxide layer is deposited by the LPCVD process. The fourth mask is used to open windows in the inter-metal dielectric film for contacts. A Ti/Al layer (0.4–0.8 μm) is deposited by the sputtering process. Patterning of Al (fifth lithographic step) is done to separate gate, capacitor's upper and lower electrodes, source, drain, and emitter (of solar cell).</li> <li>6. The next mask opens up the area for bond pads, and the final mask is used to pattern them. In this way, six pads are created for six terminals—gate, capacitor's upper and lower electrodes, source, drain, and emitter</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    | drain (third mask). The remaining polysilicon layer acts as a gate as well                       |

| <ul> <li>region of the MOSFET (Phosphorus doping of 1x10<sup>20</sup> cm<sup>-3</sup>, 80 keV) (Fig. 2.1c). The polysilicon layer also gets doped to reduce its resistivity.</li> <li>5. A 500 nm thick intermetal oxide layer is deposited by the LPCVD process. The fourth mask is used to open windows in the inter-metal dielectric film for contacts. A Ti/Al layer (0.4–0.8 μm) is deposited by the sputtering process. Patterning of Al (fifth lithographic step) is done to separate gate, capacitor's upper and lower electrodes, source, drain, and emitter (of solar cell).</li> <li>6. The next mask opens up the area for bond pads, and the final mask is used to pattern them. In this way, six pads are created for six terminals—gate, capacitor's upper and lower electrodes, source, drain, and emitter</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    | as one electrode of the capacitor (Fig. 2.1c)                                                    |

| <ul> <li>2.1c). The polysilicon layer also gets doped to reduce its resistivity.</li> <li>5. A 500 nm thick intermetal oxide layer is deposited by the LPCVD process. The fourth mask is used to open windows in the inter-metal dielectric film for contacts. A Ti/Al layer (0.4–0.8 μm) is deposited by the sputtering process. Patterning of Al (fifth lithographic step) is done to separate gate, capacitor's upper and lower electrodes, source, drain, and emitter (of solar cell).</li> <li>6. The next mask opens up the area for bond pads, and the final mask is used to pattern them. In this way, six pads are created for six terminals—gate, capacitor's upper and lower electrodes, source, drain, and emitter</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4. | Ion implantation is carried out to form n+ source region and n+ drain                            |

| <ul> <li>5. A 500 nm thick intermetal oxide layer is deposited by the LPCVD process. The fourth mask is used to open windows in the inter-metal dielectric film for contacts. A Ti/Al layer (0.4–0.8 μm) is deposited by the sputtering process. Patterning of Al (fifth lithographic step) is done to separate gate, capacitor's upper and lower electrodes, source, drain, and emitter (of solar cell).</li> <li>6. The next mask opens up the area for bond pads, and the final mask is used to pattern them. In this way, six pads are created for six terminals—gate, capacitor's upper and lower electrodes, source, drain, and emitter</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    | region of the MOSFET (Phosphorus doping of 1x10 <sup>20</sup> cm <sup>-3</sup> , 80 keV) (Fig.   |

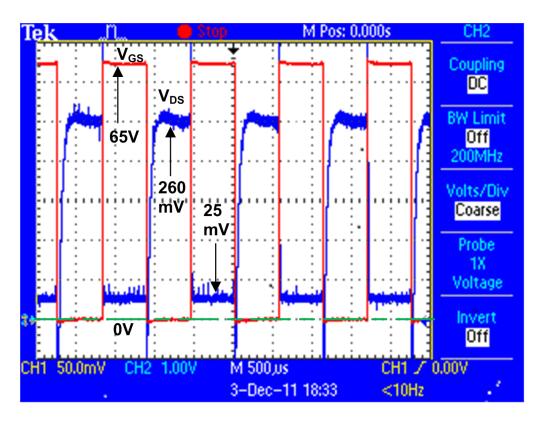

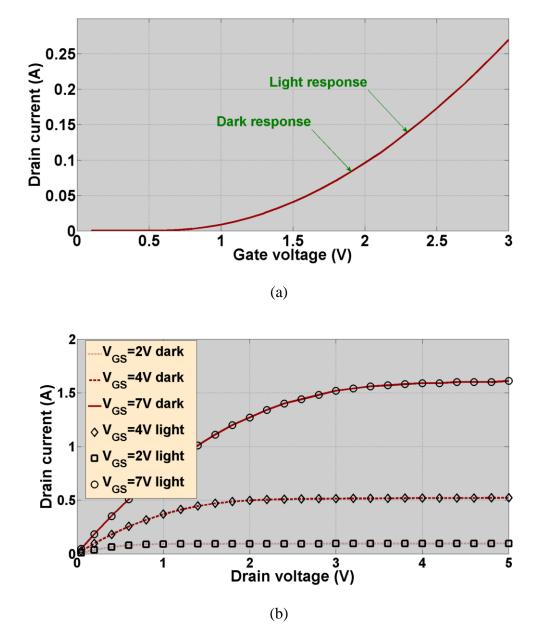

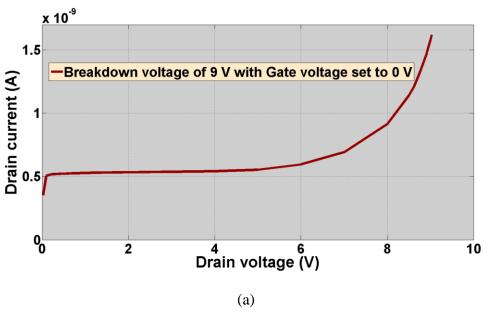

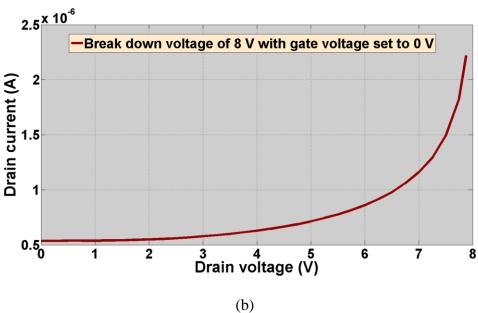

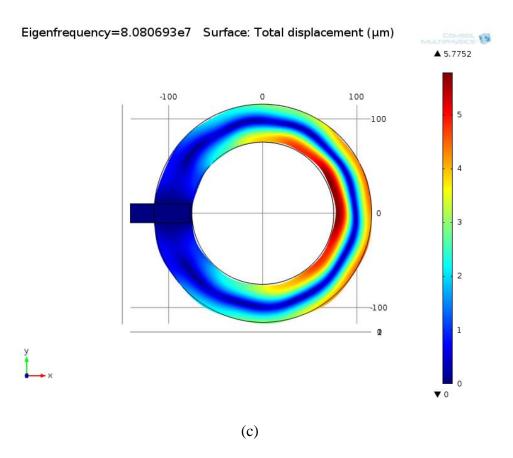

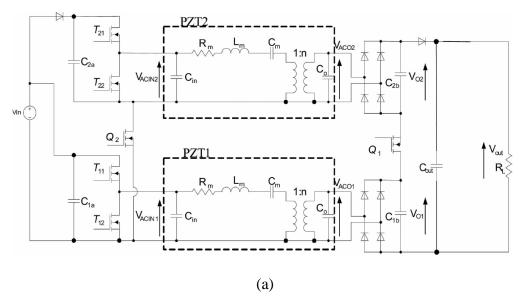

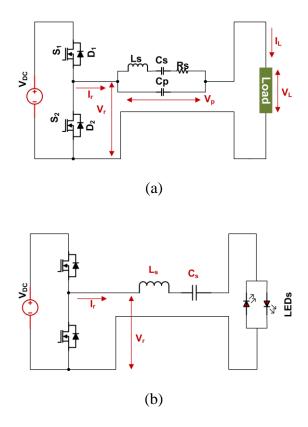

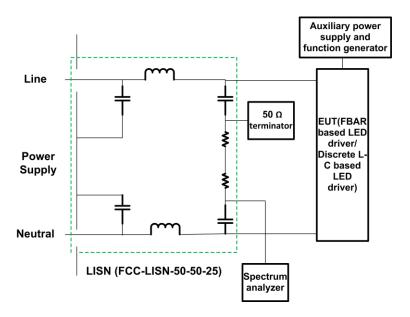

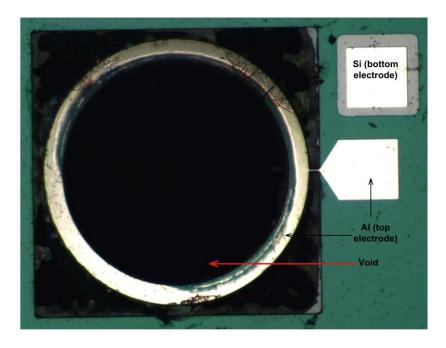

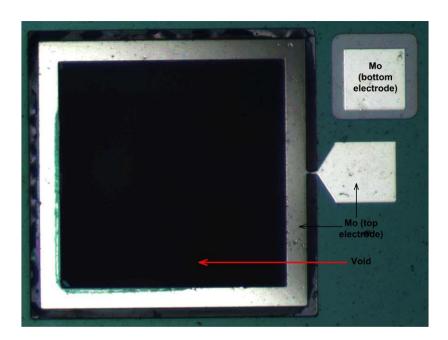

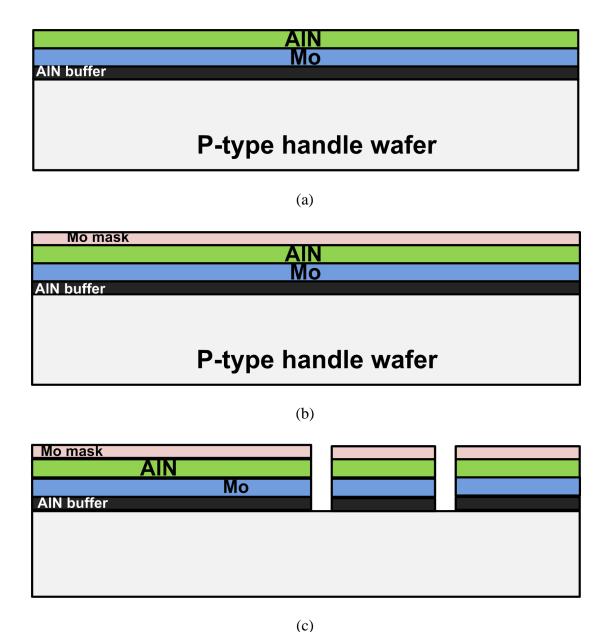

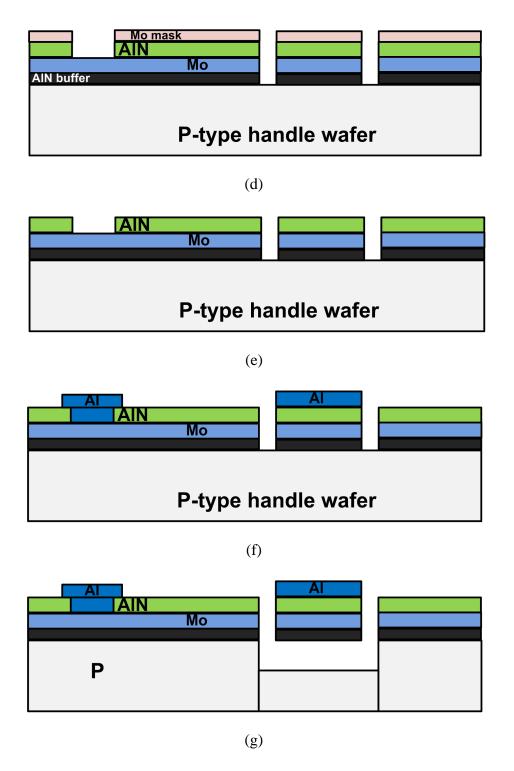

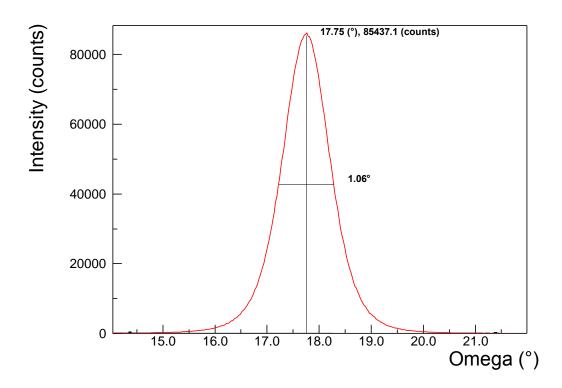

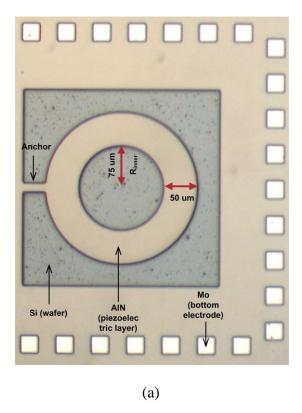

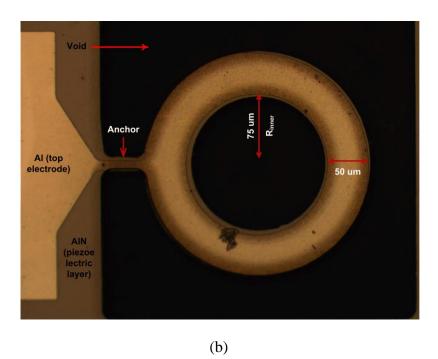

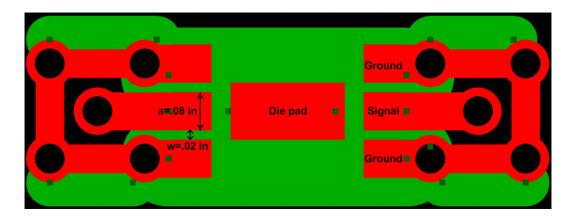

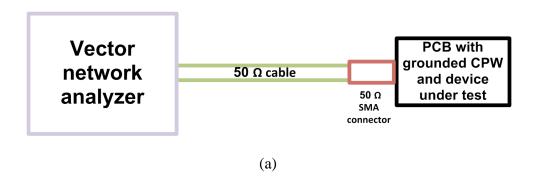

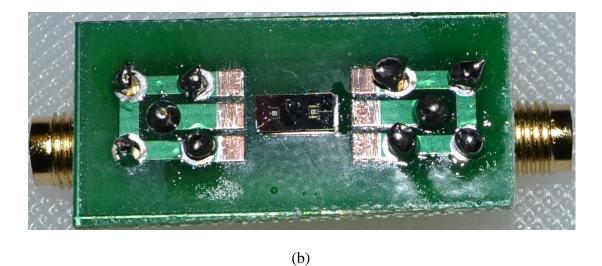

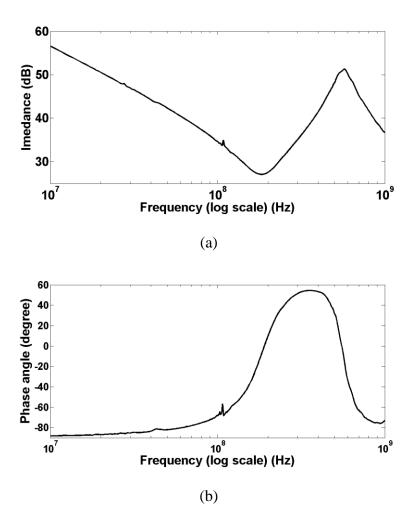

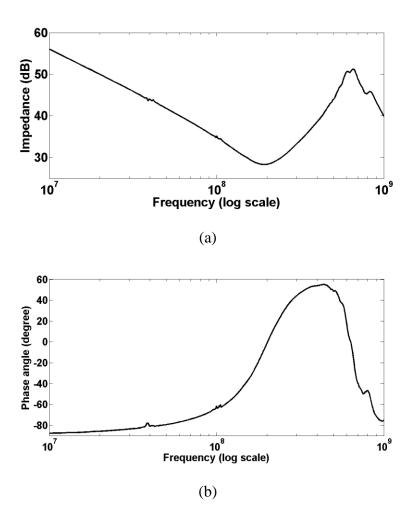

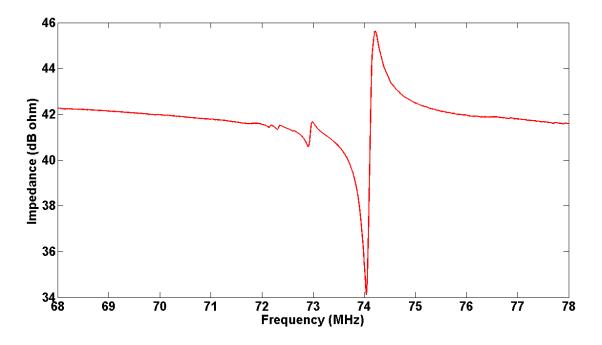

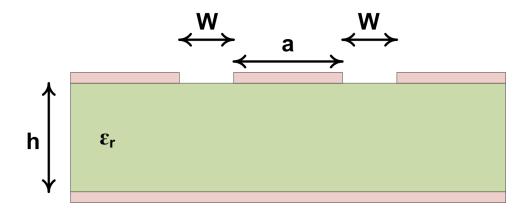

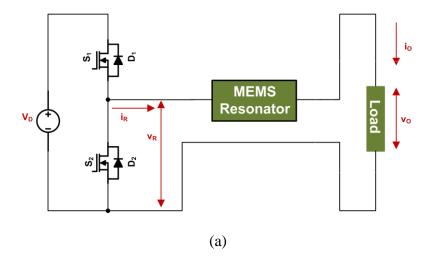

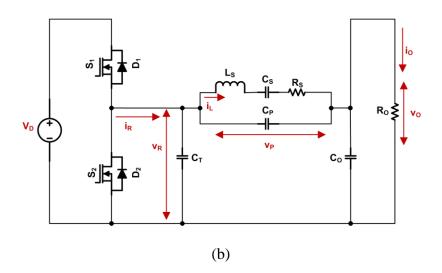

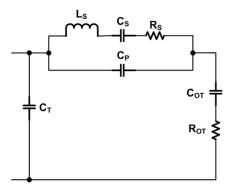

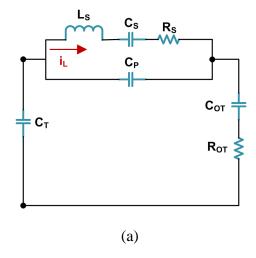

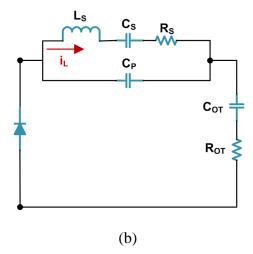

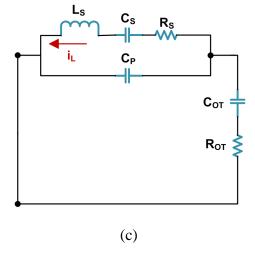

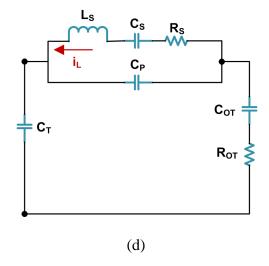

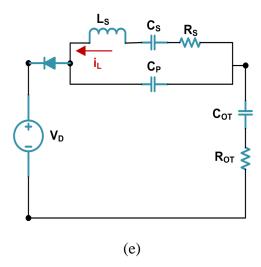

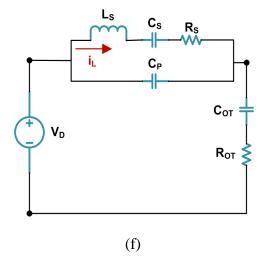

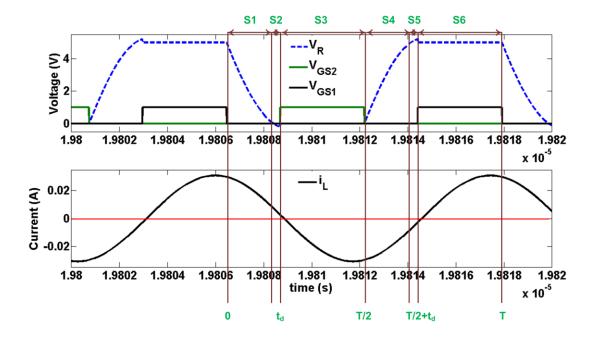

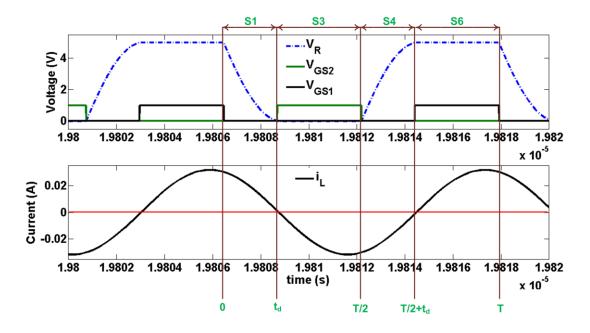

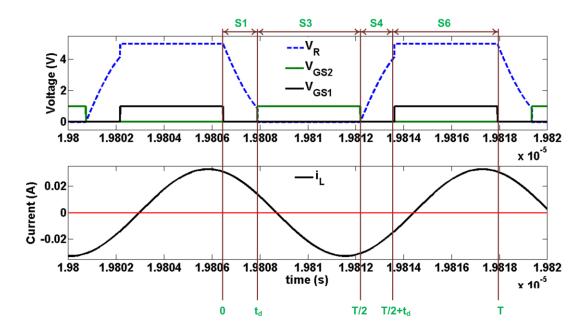

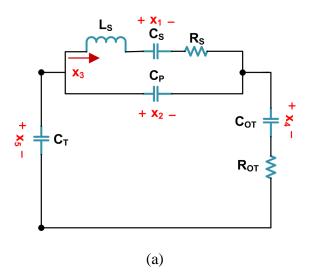

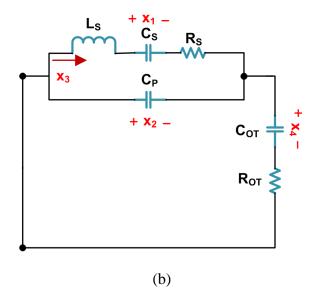

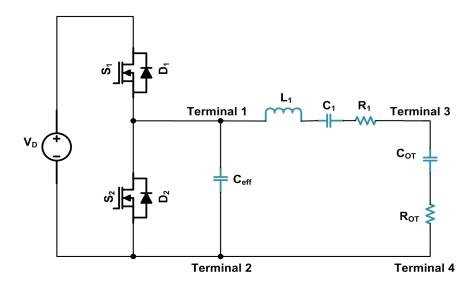

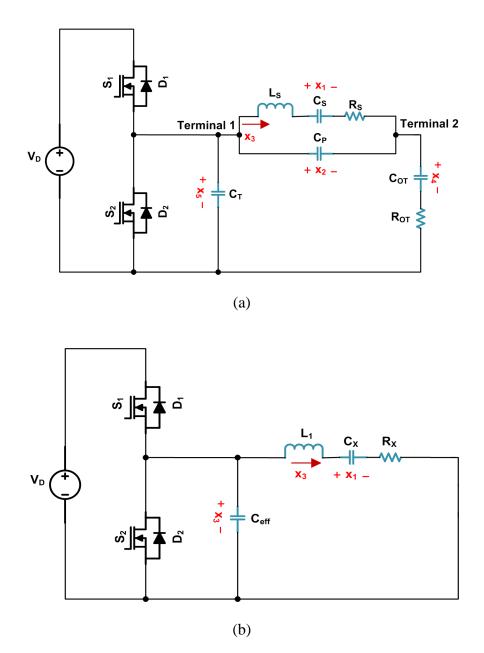

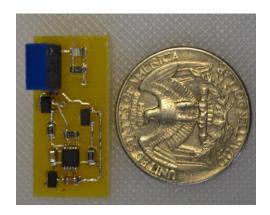

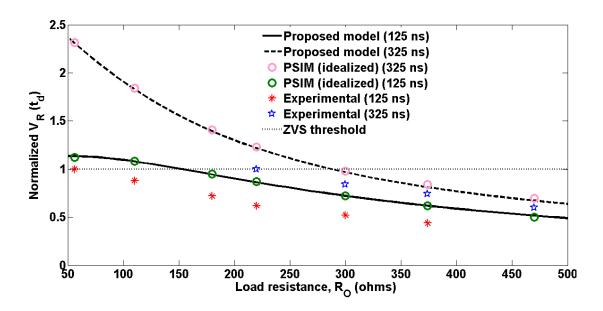

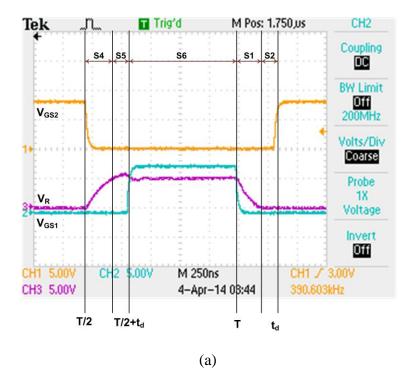

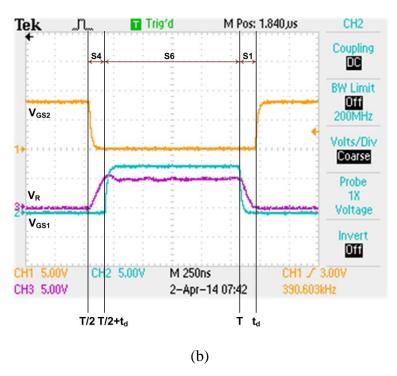

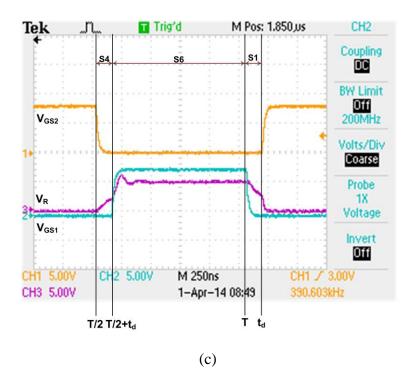

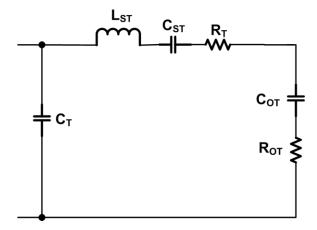

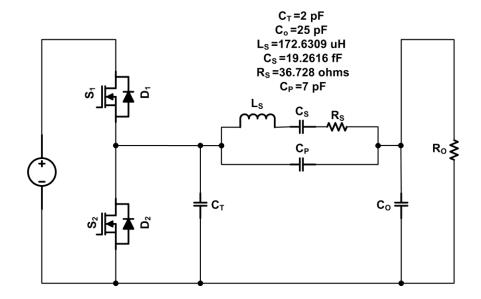

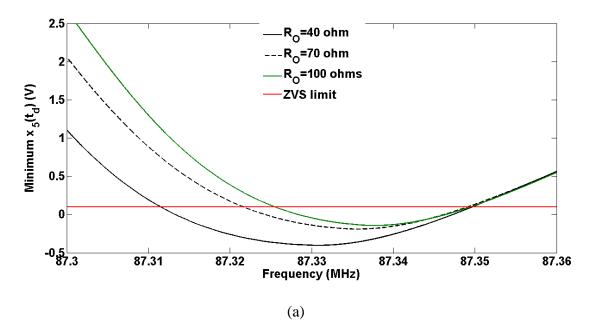

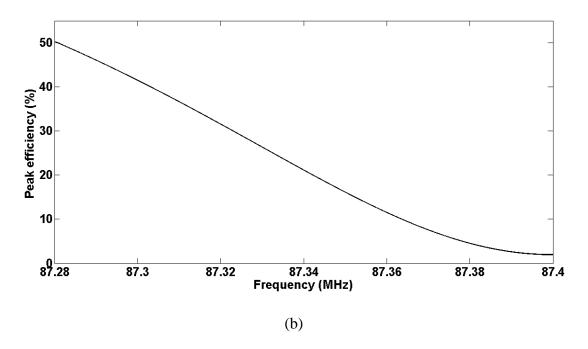

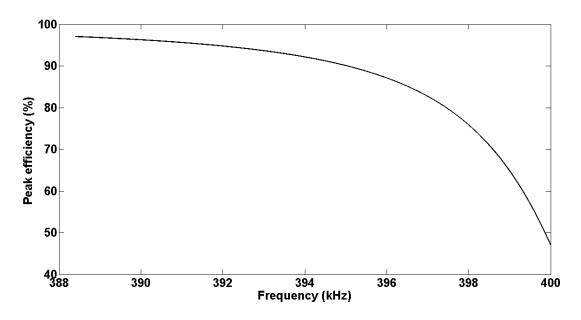

| <ul> <li>process. The fourth mask is used to open windows in the inter-metal dielectric film for contacts. A Ti/Al layer (0.4–0.8 μm) is deposited by the sputtering process. Patterning of Al (fifth lithographic step) is done to separate gate, capacitor's upper and lower electrodes, source, drain, and emitter (of solar cell).</li> <li>6. The next mask opens up the area for bond pads, and the final mask is used to pattern them. In this way, six pads are created for six terminals—gate, capacitor's upper and lower electrodes, source, drain, and emitter</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    | 2.1c). The polysilicon layer also gets doped to reduce its resistivity.                          |