# CUDA-CHILL: A PROGRAMMING LANGUAGE INTERFACE FOR GPGPU OPTIMIZATIONS AND CODE GENERATION

$\mathbf{b}\mathbf{y}$

Gabe Rudy

A thesis submitted to the faculty of The University of Utah in partial fulfillment of the requirements for the degree of

Master of Science

in

Computer Science

School of Computing

The University of Utah

August 2010

Copyright © Gabe Rudy 2010

All Rights Reserved

# The University of Utah Graduate School

# STATEMENT OF THESIS APPROVAL

| The thesis of                                                     | Gabe      |            |  |

|-------------------------------------------------------------------|-----------|------------|--|

| has been approved by the following supervisory committee members: |           |            |  |

| Hall                                                              | , Chair   | 5-28-2010  |  |

| Matthew                                                           | , Member  | 6-16-2010  |  |

| Matthew Flatt                                                     | , Member  | 5-28-2010  |  |

| and by the Department of                                          | School of | , Chair of |  |

and by Charles A. Wight, Dean of The Graduate School.

# ABSTRACT

The advent of the era of cheap and pervasive many-core and multicore parallel systems has highlighted the disparity of the performance achieved between novice and expert developers targeting parallel architectures. This disparity is most notifiable with software for running general purpose computations on grachics processing units (GPGPU programs). Current methods for implementing GPGPU programs require an expert level understanding of the memory hierarchy and execution model of the hardware to reach peak performance. Even for experts, rewriting a program to exploit these hardware features can be tedious and error prone. Compilers and their ability to make code transformations can assist in the implementation of GPGPU programs, handling many of the target specific details.

This thesis presents CUDA-CHiLL, a source to source compiler transformation and code generation framework for the parallelization and optimization of computations expressed in sequential loop nests for running on many-core GPUs. This system uniquely uses a complete scripting language to describe composable compiler transformations that can be written, shared and reused by nonexpert application and library developers.

CUDA-CHILL is built on the polyhedral program transformation and code generation framework CHILL, which is capable of robust composition of transformations while preserving the correctness of the program at each step. Through its use of powerful abstractions and a scripting interface, CUDA-CHILL allows for a developer to focus on optimization strategies and ignore the error prone details and low level constructs of GPGPU programming. The high level framework can be used inside an orthogonal auto-tuning system that can quickly evaluate the space of possible implementations. Although specific to CUDA at the moment, many of the abstractions would hold for any GPGPU framework, particularly OpenCL.

The contributions of this thesis include a programming language approach to providing transformation abstraction and composition, a unifying framework for general and GPU specific transformations, and demonstration of the framework on standard benchmarks that show it capable of matching or outperforming hand-tuned GPU kernels. To my loving wife

# CONTENTS

| AB  | BSTRACT                                                                                                                                                                                                                                                                                                                                                                                                                                  | iii                                                    |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| LIS | ST OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                            | vii                                                    |

| LIS | ST OF TABLES                                                                                                                                                                                                                                                                                                                                                                                                                             | viii                                                   |

| AC  | CKNOWLEDGMENTS                                                                                                                                                                                                                                                                                                                                                                                                                           | ix                                                     |

| СН  | IAPTERS                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                        |

| 1.  | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                             | 1                                                      |

|     | <ul> <li>1.1 Programmable Accelerators for<br/>Scientific Computing</li> <li>1.2 Using GPUs for General Purpose</li> </ul>                                                                                                                                                                                                                                                                                                               | 1                                                      |

|     | Computation       1.2.1 The Early Years         1.2.2 GPGPU Frameworks       1.3 Compiler Assisted Targeting of the GPU         1.4 Research Contributions of this Thesis       1.5 Organization of this Thesis                                                                                                                                                                                                                          | $     3 \\     3 \\     4 \\     5 \\     6 \\     6 $ |

| 2.  | THE GPU AS AN OPTIMIZATION TARGET                                                                                                                                                                                                                                                                                                                                                                                                        | 8                                                      |

|     | <ul> <li>2.1 GPU Architecture Features</li></ul>                                                                                                                                                                                                                                                                                                                                                                                         | 9<br>10<br>11<br>11<br>13                              |

| 3.  | TRANSFORMATION SCRIPTS TO DIRECT OPTIMIZATIONS                                                                                                                                                                                                                                                                                                                                                                                           | 14                                                     |

|     | <ul> <li>3.1 Capabilities of Transformation Recipes</li></ul>                                                                                                                                                                                                                                                                                                                                                                            | $15 \\ 15 \\ 15 \\ 17 \\ 17 \\ 17$                     |

|     | <ul> <li>3.2 A Programming Language Approach to<br/>Directing Optimizations</li> <li>3.2.1 Limitations of a Flat Sequential Transformation Recipe</li> <li>3.2.2 Scripting Language Foundation for Compiler Scripts</li> <li>3.3 CUDA-CHiLL: A Compiler Framework for Generating Optimized CUDA Code</li> <li>3.3.1 Basis on CHiLL</li> <li>3.3.2 Loop Variables as Semantic Handles</li> <li>3.4 Abstraction Layers with Lua</li> </ul> | 18<br>18<br>19<br>19<br>20<br>21                       |

|          | 3.4.1 High Level Description of Tiling3.4.2 High Level Description of Data Copy3.4.3 High Level Description of Unroll3.5 Summary                                                                                             | 21<br>24<br>26<br>27                                                 |  |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|--|

| 4.       | CUDA-CHILL TRANSFORMATIONS AND CODE GENERATION         4.1 The Two Phase Structure         4.1.1 Interpreting Transformation Scripts                                                                                         | 28<br>28<br>28                                                       |  |

|          | <ul> <li>4.1.2 Code Generation</li></ul>                                                                                                                                                                                     | 30<br>30<br>31<br>31<br>32<br>32<br>33<br>33<br>33<br>33<br>35<br>35 |  |

| 5.       | EVALUATION         5.1 Optimization Heuristics         5.2 BLAS Library Benchmarks         5.2.1 Matrix Vector Multiply         5.2.2 Transpose Matrix Vector Multiply         5.2.3 Matrix Multiply         5.3 Performance | 37<br>39<br>39<br>40<br>42<br>44                                     |  |

| 6.       | <b>RELATED WORK</b> 6.1Source Transformation Frameworks6.2Polyhedral Loop Transformations6.3Parallelization and CUDA Targeting                                                                                               | 48<br>48<br>49<br>49                                                 |  |

| 7.<br>RE | 7. CONCLUSION       50         REFERENCES       52                                                                                                                                                                           |                                                                      |  |

|          |                                                                                                                                                                                                                              |                                                                      |  |

# LIST OF FIGURES

| 1.1 | The Cray 1 at the Computer History Museum in Mountain View, CA.                                                                                                                                                                                                                                                | 2  |  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|

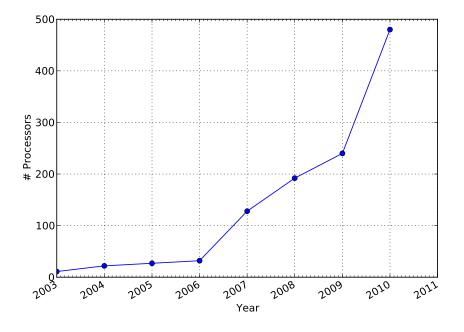

| 1.2 | # Execution Units (Texture/Vertex Pipelines $< 2007$ ) in NVIDA GPUs 5                                                                                                                                                                                                                                         |    |  |

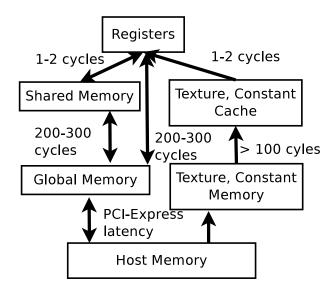

| 2.1 | The GPU memory hierarchy and latencies between each level                                                                                                                                                                                                                                                      |    |  |

| 2.2 | Example of tile transformations to deconstruct iteration space                                                                                                                                                                                                                                                 |    |  |

| 3.1 | Transformation recipe for LU with the CHiLL framework. Recipe syntax simplified for illustration purposes.                                                                                                                                                                                                     |    |  |

| 3.2 | A simplified example of tiled and CUDAized matrix-vector multiply                                                                                                                                                                                                                                              | 22 |  |

| 3.3 | Initial tiling for matrix multiply for GPU parallelism (CUBLAS 2)                                                                                                                                                                                                                                              | 24 |  |

| 3.4 | Data copy and unroll for matrix multiply for GPU memory hierarchy (CUBLAS 2)                                                                                                                                                                                                                                   | 25 |  |

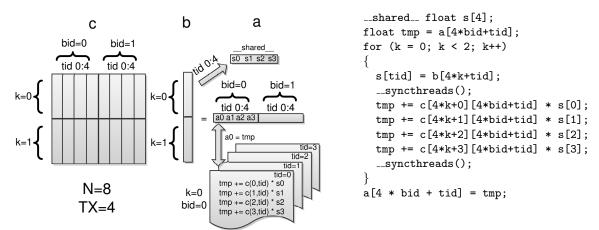

| 3.5 | Given an easy to depict, although trivially small problem size of N=8 for matrix-vector multiplication, the decomposition using a tile size of TX=4 is visually depicted with the global memory matrix, vectors and shared memory structures. The corresponding kernel code is also given                      | 26 |  |

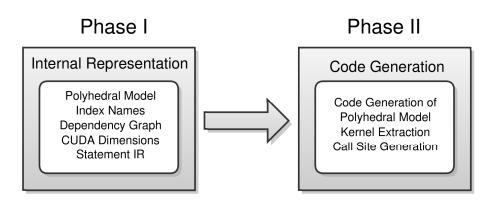

| 4.1 | CUDA-CHiLL System Diagram                                                                                                                                                                                                                                                                                      | 29 |  |

| 4.2 | Algorithm used by $tile_by_index$ where <i>FindLevel</i> finds the loop level of an index variable in the current internal representation and <i>BuildOrder</i> builds the snapshot of what the order should be between its current state and its final state given $n$ tile operations were already processed | 34 |  |

| 4.3 | Algorithm used by unroll_to_level                                                                                                                                                                                                                                                                              | 34 |  |

| 5.1 | MV transformation recipe and generated code                                                                                                                                                                                                                                                                    | 40 |  |

| 5.2 | Transformation recipe and generated code for TMV                                                                                                                                                                                                                                                               | 41 |  |

| 5.3 | Transformation recipe and generated code for MM                                                                                                                                                                                                                                                                | 43 |  |

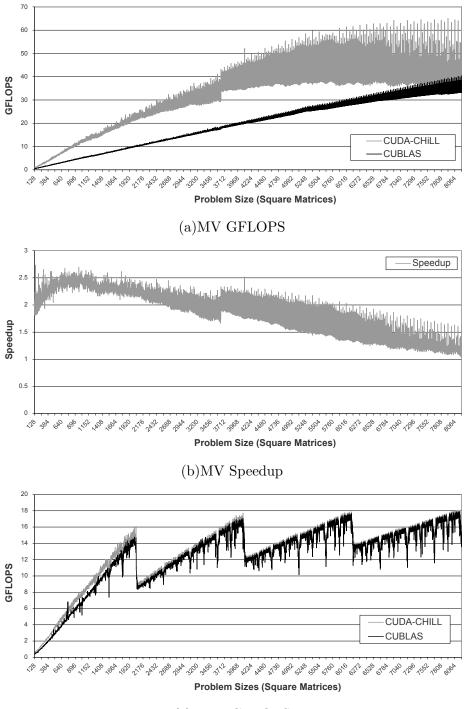

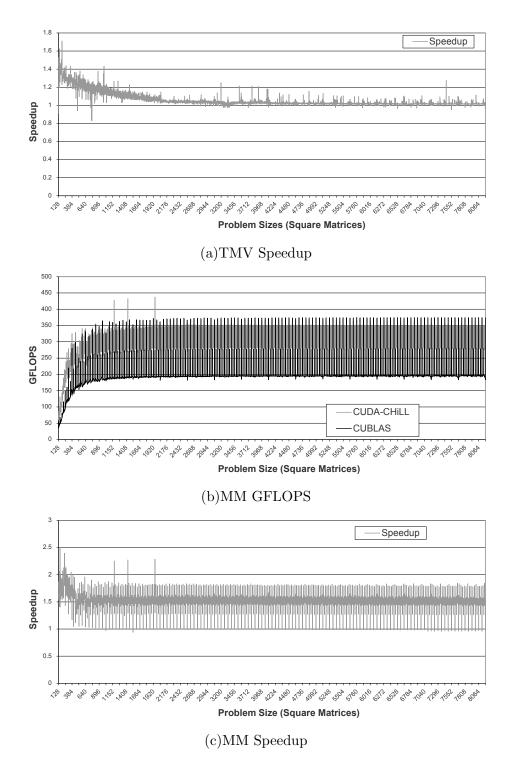

| 5.4 | Performance comparison of automatically generated code with CUBLAS 2.0 for matrix-vector (a,b), transposed-matrix-vector (c) multiplication kernels.                                                                                                                                                           | 45 |  |

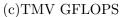

| 5.5 | Performance comparison of automatically generated code with CUBLAS 2.0 for transposed-matrix-vector (a) and matrix-matrix (b,c) multiplication kernels.                                                                                                                                                        | 46 |  |

# LIST OF TABLES

| 3.1 | Description of prominent commands in CUDA-CHiLL scripts | 23 |

|-----|---------------------------------------------------------|----|

| 4.1 | Description of CUDA-CHiLL querying commands             | 31 |

| 4.2 | Description of common CUDA-CHiLL commands               | 33 |

# ACKNOWLEDGMENTS

I would like to specially thank my adviser, Dr. Mary Hall, for her sage guidance, tireless editing and inspirational leadership of myself and her entire research team. This work would be a small pittance of what it became without her dedication to the research and encouraging nature. As a fellow researcher, and my number one user (really only user), I would like to thank Malik Murtaza Khan for running weeks and weeks of benchmarks on the system and collecting much of the results used in this thesis. Naturally, I would like to thank Chun Chen, who laid the groundwork for this thesis with his previous research and ongoing involvement as a research associate. I am fortunate to have Dr. Matt Might and Dr. Matthew Flatt as committee members and I appreciate their involvement and support.

Finally, as special thanks to my loving and supportive wife, who tirelessly read and listened about this work, helped me make schedules and more importantly, helped me keep them.

## CHAPTER 1

## INTRODUCTION

In the history of microprocessors, the Central Processing Unit (CPU) processor has been the focus of the industry for its powerful ability to run general purpose sequential programs. While hugely successful in meeting the majority of computing needs, there has also been a legacy of programmable accelerators to improve performance for specific domains of applications. In the embedded world, Digital Signal Processors (DSPs) are used to encode and decode audio. In High Performance Computing (HPC), there have been many examples of coprocessors going back to the 1970s designed for floating point calculations or other specific tasks. In consumer computing, discrete video processors have long been included to meet specialized needs of rendering images at the demanding rate of stutter-free video.

Under the pressures of the consumer gaming and professional workstation market, Graphical Processing Units (GPUs) have evolved to deliver ever-increasing amounts of computational performance. Reacting from the market demand to provide more direct means of accessing this potential performance, hardware manufacturers starting providing developer SDKs to treat the GPU as a programmable stream processor, instead of a specialized device only accessible through graphics oriented fixed-function APIs. This opened to door for GPUs to be used for massively parallel computations on nongraphics data. Scientific computing has had a long history of using coprocessors and programmable accelerators to serve its seemingly unbounded need for computational performance. In fact, modern high end super computers often include a hybrid of traditional processors and stream processors in the form of GPUs [56].

# 1.1 Programmable Accelerators for Scientific Computing

When hardware accelerators of various forms are designed, there is always a trade-off between how general versus function-specific to make the programming model. DSPs, for example, are specialized to handle streams of audio or video data but usually are designed to be programmable to support different and changing encoding standards.

This trade-off can also be seen in the field of Vector Computers such as the Cray 1 in Figure 1.1. The potential speed of the machine was really only unlocked by the use of special vector instructions for doing floating point operations. This required the creation of nonportable programs, but the potential speedup of six to ten times often outweighed the cost.

Other vector computer manufactures added language extensions to high level languages like FORTRAN to make developing for the platform more attractive. The Control Data Cyber 205, for example, made its vector instructions accessible by FORTRAN with notations like a(1;n) + b(2;n), which would add n elements of vector a starting at position 1 with vector b starting at 2.

Eventually, vectorizing compilers that could compile loops to platform specific vector instructions matured to the point that they were good enough for general programming purposes. However, highly tuned libraries were often still written in assembly language to take advantage of the nuanced behavior of the vector instructions. Soon, commercially successful compilers provided feedback and diagnostics to the programmer when a loop was not able to be vectorized. This feedback directed the programmer with specific information as to what was blocking the vectorization process. With these tools, programmers were then able to write in a portable, high-level language and be certain to have the benefits of vectorized code across hardware vendors.

Figure 1.1. The Cray 1 at the Computer History Museum in Mountain View, CA.

When Intel added the SSE instructions extensions to the x86 family in 1999, there was a similar situation with the vector-based SIMD instructions. At first, manual work was required from programmers to gain access to the potential performance. Eventually, compilers used the existing body of knowledge on vectorizing compilers to generate SSE instructions, when possible, automatically. Again, for programmers seeking this performance, it was key to have some feedback from the compiler on when vectorization was not possible and for what reason.

With GPUs today, we find a lot of similarities to vector computers and SIMD instructions in their requirements on programmers. Platform-specific program changes are required to take advantage of the hardware. Also similarly, although the set of programs that can be adapted with these changes is significant, it will never be universal. In a historical progression, you might expect the next step would be a compiler focused solution that auto-parallizes loops to GPU optimized programs. For various reasons discussed below, the programming of GPUs does not lend itself to this type of automatic and opaque solution.

# 1.2 Using GPUs for General Purpose Computation

#### 1.2.1 The Early Years

The use of computer graphics hardware for general-purpose computation has been an area of active research for many years. The Ikonas system in 1978 [17], a programmable raster display system for cockpit visualization, allowed the microprogrammable coprocessor to not just handle image processing but flight simulation, ray tracing and solid modeling. The Pixel-Planes group designed a heterogeneous multiprocessor for graphic rendering and "nonscreen" oriented calculations in 1989 [18]. With its independent scheduling of rendering units and message-passing interface between host and device, this general purpose architecture may have been the inspiration for the latest generation of GPUs designed for heterogeneous uses.

Graphics applications themselves have a history of using graphics hardware for procedural texturing and shading [42, 51]. In the early 90s, OpenGL was standardized across platforms and hardware as a way of using GPU resources. Thus, OpenGL was used by researchers as an intermediate language in their abstractions that provided general procedural programming [43, 46]. Clearly, there were still a lot of limitations and unnecessary complexity in using a purely graphics-centric API to gain access to the underlying SIMD capabilities of the hardware. This need was acknowledged by both the API developers and the hardware manufacturers, leading to different but ultimately converging solutions.

#### **1.2.2 GPGPU Frameworks**

The two primary hardware vendors in the discrete GPU market, NVIDIA and ATI (now part of AMD), felt the pressure to provide more programmable access to their processors. Clearly, a market was emerging for general purpose computations on non-graphics data on the GPUs. Leading the way with a General Purpose GPU solution (GPGPU), NVIDIA introduced CUDA (Compute Unified Device Architecture) in 2007. AMD also released a similar, but less popular SDK for targeting their GPUs called ATI Stream Technology, based on their own Brook+ compiler and runtime.

With the advent of CUDA, there was an increased use of GPGPU in various research efforts, but consumer providers were reluctant to develop libraries and code based on the proprietary SDKs of a single vendor. In response, a couple of frameworks have emerged to provide a vendor-neutral solution.

Originally developed by Apple and later submitted to the industry consortium that handled the OpenGL specification, Open Computing Language (OpenCL) is a framework for writing programs that can execute on a heterogeneous platform. This framework supports running programs on both GPUs and CPUs, and potentially other accelerator hardware. AMD soon decided to adopt OpenCL as their primary GPGPU framework in favor of their previous Brook+ based system. By 2009, NVIDA had also added support for running OpenCL programs in its updated GPU drivers.

Although OpenCL is gaining more interest for its potential cross platform support, it currently does not run well outside the Mac operating system. Also, by trying to target heterogeneous parallel processing models, OpenCL programs give up some GPU specific optimizations. Currently, an OpenCL program generally performs poorly when compared to a hand-tuned CUDA equivalent.

Microsoft has also developed its own high-level general purpose computing API called DirectCompute, part of DirectX 11 APIs released in 2009. DirectCompute provides a comfortable interface for current Direct3D programmers and abstracts away the vendorspecific hardware. However, its requirement on the DirectX 11 capable GPU has kept it from wide adoption in an industry that tries to target widely adopted technologies.

### **1.3** Compiler Assisted Targeting of the GPU

It is not hard to see why the GPU is an attractive target for general purpose computing. Figure 1.2 shows that the number of execution units on modern GPUs has grown substantially in the past few years. But unlike earlier targets of vectorizing compilers, GPUs offer a number of challenges to fully exploit their resources.

First, GPUs have two levels of parallelism. At the first level, there is MIMD parallelism across multiple independent streaming multiprocessors (SM). Within each SM, there are multiple thread units that provide SIMD parallelism. Any program that needs to synchronize data between running threads must take into account on which level of parallelism it is operating. While there are built-in methods for synchronizing across SIMD threads, custom and often slow methods are required to synchronize between SMs on the GPU.

Secondly, GPUs have a deep memory hierarchy. Although *global* memory is most commonly used, there is a relatively high latency cost for fetches and stores to global memory. Certain parts of global memory have special performance characteristics such as *constant* and *texture memory*. Outside of global memory, each SM has a certain amount of shared memory locally available. Also, the register file for each SM is large enough to be

Figure 1.2. # Execution Units (Texture/Vertex Pipelines < 2007) in NVIDA GPUs

considered a memory target for scaler variables in computations.

To target the complex nature of the GPU architecture, programs often have to go through profound transformations. A decomposition of the computational space may be required to match the levels of parallelism on the GPU. Then, to hide the latency of global memory fetches, some data may need to be copied to shared memory or registers. The optimal optimization strategy may not be the obvious one, so various different versions of a GPGPU program may need to be tested and evaluated.

Although it is clear that this process may not be fully automated by a compiler, it is also potentially labor intensive and error prone if unassisted. This thesis proposes that a compiler-assisted solution may be the best for iteratively exploring optimization strategies for the GPU.

## **1.4** Research Contributions of this Thesis

The contributions of this thesis follow:

- A programming language approach to describing code transformations which provides library and application developers high level abstractions for code generation and compiler transformation capabilities.

- Adding novel transformations and code generations to a unified framework alongside standard compiler transformations in an integrated and composable manner. This framework is capable of generating code targeting GPUs from sequential loop nests by composing these data and computation space partitioning transformations to achieve kernels that match or surpass the performance of hand-tuned equivalents.

- Demonstration of this approach on standard BLAS library routines and some common benchmark kernels yielding results comparable to hand-tuned versions in some cases, outperforming hand-tuned in other cases.

## 1.5 Organization of this Thesis

This thesis is organized into six chapters. The first two chapters provide background and details of the problem space of optimizing GPGPU programs for today's modern GPU architectures. In Chapter 3, we introduce a programming language approach to directing compiler assistance for this problem space. Chapter 4 provides the details of the system in its underlying technologies and novel components. Then, in Chapter 5, we present benchmarks of the techniques discussed. Finally, we present related work and conclusions in Chapter 6 and 7.

## CHAPTER 2

# THE GPU AS AN OPTIMIZATION TARGET

As we have seen in the previous chapter, the GPU has progressed to a powerful and programmable parallel architecture, with its multiple streaming multiprocessors with potentially hundreds of cores. Currently, the CUDA framework is the most widely used method of accessing this attractive architecture for general purpose computations. Our goal is to automate many of the difficult programming tasks in generating high-performing, equivalent CUDA code from a sequential computation. The approach presented in this thesis is motivated by the following observations:

- There is a standard and well-defined protocol for GPU kernel computations that involves allocating memory for GPU input and output, copying data to and from the GPU, and performing block and thread decomposition. Given appropriate parameters for computation and data decomposition, these tasks can be automated in a compiler.

- Known compiler transformations can be adapted and applied both in the decomposition and mapping process, and in subsequently optimizing the kernel code to manage the memory hierarchy and parallelism tradeoffs.

- Since there is significant performance variation on GPUs for very subtle differences in code, we would like our system to explore a space of different implementations, and different values of parameters associated with the mapping.

- A programming tool should support both automated compiler optimization as well as programmer-guided optimization, and not get in the programmer's way in achieving high performance.

In the remainder of this chapter, we will describe the salient features of the architecture, the ways in which CUDA accesses these features, and elements of a transformation process

Figure 2.1. The GPU memory hierarchy and latencies between each level.

from a sequential loop nest to a optimized CUDA program.

### 2.1 GPU Architecture Features

The target GPU architecture for this thesis is an NVIDIA GeForce GTX 280, which is representative of the current generation of GPU offerings from NVIDIA. The GTX 280 is organized into 30 streaming multiprocessors (SM), each of which has an 8-core SIMD unit; the device, therefore, has 240 cores, each clocked at nearly 1.3GHz. Using all cores, a single chip can perform an impressive 933 GFLOPS for single-precision computations, and 78 GFLOPS for double precision. Synchronization between threads in an SM is supported by a barrier; synchronization between threads mapped to different SMs typically relies on atomic operations.

The GTX 280 also has a heterogeneous, and mostly software-controlled, memory hierarchy, consisting of 16K registers and a 16 KByte shared memory *per SM*, and a 1GByte global memory shared among SMs. As seen in Figure 2.1, read-only constant and texture data in global memory are cached for low-latency average access time – but the bulk of global memory accesses are typically not cached, with latencies on the order of hundreds of cycles. To improve bandwidth to global memory, the memory controller will *coalesce* accesses to multiple data into a single memory transfer if the accessed data has spatial reuse within the size of a memory transfer [58].

### 2.2 Properties of High-Performance CUDA Code

CUDA, introduced in the previous chapter, includes a computing engine, language and compiler tools for running general purpose applications on NVIDIA GPUs [1]. The programming model involves some extensions to the C programming language. These extensions delineate a kernel function to be executed on a GPU, attach memory attributes to variables and provide special syntax to invoke kernel calls. A PathScale Open64 compiler is used to convert the CUDA C program to the NVIDIA GPU native instructions.

A CUDA program describes a computation decomposition into a one- or two-dimensional space of thread blocks called a *grid*, where a block is indivisibly mapped to one of the 30 SMs. Each thread block defines a multidimensional space with up to three dimensions and a maximum of 512 threads. A *kernel* code is executed for each point in the grid, providing a two-level parallelism hierarchy represented by this five-dimensional space. Threads within a block run concurrently on the same SM in batches, called *warps*, under a SIMT<sup>1</sup> execution model.

With so many parallel threads simultaneously accessing memory, effective utilization of the memory hierarchy has significant impact on performance. The programmer or compiler can *reduce memory latency* through *locality optimizations* that copy data into lower-latency portions of the memory hierarchy as compared to global memory on data that has *temporal or spatial reuse*. Whenever possible, registers provide the most ready low-latency access and the large size of the register file (16K registers per SM) permits code to exploit significant reuse within a thread. Shared memory has latency comparable to registers (as long as there are no memory bank conflicts) for data that can be shared by all threads in a block. To *maximize memory bandwidth*, the programmer/compiler can order data accesses across neighboring threads (a half-warp) so that global memory accesses are coalesced whenever possible, and shared memory accesses avoid bank conflicts.

While the large body of prior work on locality optimization for conventional architectures sheds some light on compiler optimizations for this and similar GPUs, new challenges arise due to the significant differences between the two levels of parallelism (blocks and threads), and how they synchronize and share data. As mentioned earlier, a low-cost barrier implemented with a CUDA function call permits synchronization between threads.

<sup>&</sup>lt;sup>1</sup>Single-instruction, multiple-thread (SIMT) is the name given to the NVIDIA execution model where multiple threads in a SM execute concurrently in a lock-step manner.

Synchronization across blocks is not supported directly in hardware, and is therefore costly and usually avoided.

## 2.3 Translating Sequential Loop Nests to CUDA

As most computations that are candidates for being run on the GPU start out as nested loops, we look at the process of translating these computations to efficient CUDA code. As we have observed earlier, there is a body of knowledge for compiler transformations that should provide the basis for compiler assistance in this translation process.

As a contemporary example of this translation process, in [70], Wolfe writes about tuning a simple single-precision matrix multiplication kernel on an NVIDIA GeForce GTX 280. Wolfe presents several versions of the matmul code obtained by using code transformations such as loop permutation, loop strip mine and loop unroll, and caching data in local memory. Performance ranges from 1.7 to 208 GFLOPs depending on the number of threads per block, the loop(s) unrolled and unroll sizes, and the amount of data cached in local memory. Summarizing the article, Wolfe writes "Matmul is just one simple example here, three loops, three matrices, lots of parallelism, and yet I put in several days of work to get this seven line loop optimized for GPU."

All seven versions of matmul in [70] can be derived with a combination of loop permutation, strip mine and unroll, and data copy optimization. In the following chapter, we discuss how these standard transformations can be expressed as an optimization strategy in the form of a transformation recipe. Next, we explore in more detail the two fundamental types of transformations made when translating a loop nest to an optimized CUDA program.

#### 2.3.1 Computation Decomposition

Programs written for CUDA must be explicitly aware of the two levels of parallelism of the GPU represented by the two grid dimensions and three block dimensions. It is often the case that the original nested loop computation does not embody the iteration space partitioning to match the GPU index space dimensions. Subdividing the iteration space of a loop into blocks or *tiles* with a fixed maximum size has been widely used when constructing parallel computations [68, 31]. The shape and size of the tile can be chosen to take advantage of the target parallel hardware and memory architecture, maximizing reuse while maintaining a data footprint that meets memory capacity constraints. Sometimes referred to as *loop blocking, tiling* involves deconstructing an iteration space into a control loop and tile loop. Given an iteration space of size N and a tile size of TX, the tile loop will iterate over a maximum space defined by the tile size (TX), while the constructed control loop then has N/TX steps (when TX divides N evenly). If tiling is used properly, the end result should be a loop nest where some loop levels match the iteration space of the GPU block and thread dimensions for a CUDA kernel. The constraints of loops representing threads and blocks are that they have a stride of 1 and can have their bounds coerced to the fixed iteration space of a GPU grid or block dimension.

In Figure 2.2, we show an example of using tile transformations to do an example deconstruction of the iteration space of a matrix vector multiplication source code shown in Figure 2.2 (a). In Figure 2.2 (b), two tile transformations are done on the first statement of the source code in (a), referenced as statement 0. Both transformations use the tile size of 16 and place the control loop at their default position of being right above the original loop. The tile on line 3 uses the *counted* method, which makes the control loop of stride 1, while the tile on line 5 uses the *strided* method, which results in a control loop with a stride of the tile size. The results given N=1024 and TX=16 can be seen in Figure 2.2 (c), where the outermost *ii* loop is the *counted* control loop and the *jj* loop at level 3 demonstrates a *strided* control loop. The *counted* tile method is used when the objective is to build loops to match the iteration space of GPU thread dimensions.

```

for (i = 0; i < N; i++)

for (j = 0; j < N; j++)

a[i] = a[i] + c[j][i] * b[j];</pre>

```

(a) Matrix vector source code (BLAS)

```

for(ii = 0; ii < 64; ii++)

for(i = 16 * ii; i < 16 * ii + 16; i++)

for(jj = 0; jj < 1009; jj += 16)

for(j = jj; j < jj + 16; j++)

a[i] = a[i] + c[j][i] * b[j];</pre>

```

(c) Result of tile command from (b) on input from (a) where N=1024

```

1 TX=16

2 l1 = find_cur_level(0,"i")

3 tile(0,l1,TX,l1,"i","ii",counted)

4 l2 = find_cur_level(0,"j")

5 tile(0,l2,TX,l2,"j","jj",strided)

```

(b) Tile transformations as commands

Figure 2.2. Example of tile transformations to deconstruct iteration space

#### 2.3.2 Targeting the GPU Memory Hierarchy

Other than computation space partitioning, to get optimal performance on a GPU architecture, transformations need to be made to target the deep memory hierarchy. With the high latency associated with a global memory fetch or store discussed earlier, *locality optimizations* should be used to copy data into lower-latency portions of the memory hierarchy.

Similar to how a *tile* operation helps with the computation space decomposition, a *datacopy* operation helps with targeting specific portions of the memory hierarchy. A *datacopy* transformation will introduce a new, smaller dimensional data structure from the array access pattern of statements in a given loop nest. The new data structure can be placed in shared memory and benefit from reuse and low-latency accesses from concurrently running threads.

Various data copy strategies can be used to utilize the shared memory structure accessible to all threads running concurrently on a streaming multiprocessor (SM). Although not an explicitly controlled memory structure, the large register file can be exploited by copying data into fixed sized thread-local arrays and scalars. A variant of *datacopy* variant, which we refer to as *datacopy\_privatized*, targets registers by only copying local data touched within a loop nest with respect to a subset of parallelized loops inside the loop nest.

In both cases of targeting shared memory or the register file, it may be necessary to employ a variety of different optimization strategies and empirically test to determine their relative merits. It is therefore extremely useful to have high level constructs that quickly allow for the generation of bug-free implementations of these strategies. In general, the advantage of these operations being done by the compiler are clear. For example, the compiler can ensure correctness by understanding the data dependences between loop statements and handling edge cases of unevenly divisible loop bounds.

In conclusion, although it is somewhat straightforward to convert a loop nest computation to a correct CUDA variant using compiler technology, generating high-performance code requires a sophisticated compiler tool to integrate complex loop transformations for parallelism and flexible data movement to fully utilize all the GPU architecture features that impact performance.

## CHAPTER 3

# TRANSFORMATION SCRIPTS TO DIRECT OPTIMIZATIONS

The compiler research community has developed a significant body of work in code transformation techniques that improve performance by optimizing for specific architectural features, especially by increasing parallelism or better managing the memory hierarchy [69, 64, 65, 54, 57, 12, 40, 34, 52, 47, 5, 37, 38, 28]. However, the prevailing interface for code optimization on production compilers remains compile-time flags, which limits the utilization of the transformation capabilities of the compiler to optimizations using static analysis. Furthermore, with the complex run-time behavior and hardware interplay of modern processor architectures, it is more effective to evaluate an optimization strategy in a representative execution context. Because of these limitations, application developers are often left with writing optimized code by hand, which is not only difficult and time consuming but results in low-level architecture-specific code that is difficult to port and maintain.

As an alternative to the compile-time flags paradigm, our compilation system exposes its code transformation and code generation capabilities through a *transformation recipe* interface [16, 23]. A transformation recipe expresses an optimization strategy as a sequence of composable transformations. In this form, recipes bring the benefits of separating algorithm writing and architecture specific optimization to application and library developers.

In this chapter, we discuss the use of transformation recipes as a powerful solution to leverage compiler optimization capabilities and achieve very high performance code. We describe the development of transformation recipes in the research community and their limitations in their current form. Finally, we present a more powerful language-based foundation for building layers of abstraction of transformations and provide examples from the CUDA-CHiLL framework.

## 3.1 Capabilities of Transformation Recipes

### 3.1.1 Composition of Transformations

In the domain of complex nested loop optimizations, which are quite relevant to scientific and HPC applications, there is a large body of research on loop transformations employed in the optimization process [11, 2, 19]. A key challenge to loop nest optimization is that it is difficult to express and compose a sequence of loop transformations. The ability to express and handle composition is an important feature of an optimization framework because multiple carefully combined program transformations can be necessary to improve performance in many-core architecture with deep memory hierarchies.

For example, after a permutation of the loop order of a loop nest, which is a common transformation to improve memory access patterns, a subsequent transformation must be aware of the difference in the new loop order to perform correctly. Other transformations that manipulate the iteration space may dramatically change the structure of the program. For these reasons, a purely syntactic transformation framework [16, 71, 48] will have difficulties with handling long and complex compositions of transformations in a flexible manner.

More powerful transformation frameworks are based on a polyhedral model of representing a statement's iteration space. Transformations with this model allow for the exploration of alternative iteration spaces while abstracting away many of the implementation artifacts of the syntactic representations. Figure 3.1 (b) shows an example of a transformation recipe using the CHiLL polyhedral framework that performs a long compositions of standard transformations on LU input code in Figure 3.1 (a). The result of applying this recipe is the automatically generated code in Figure 3.1 (c).

Alternative interesting methods of manipulating polyhedral models have been proposed. For example, a purely matrix-operation-based approach was proposed by Cohen et al. [14]. While limiting transformations to those expressible in a purely mathematical manipulation of the polyhedral model, this approach does not resolve the issue of referencing intermediate and newly created semantic constructs.

#### 3.1.2 Auto-Tuning

A well-recognized challenge in code optimizations for modern architectures is making trade-offs between different strategies, or identifying optimal values of optimization parameters such as unroll factors or loop tile sizes. Without sufficient knowledge of the execution environment, which is extremely difficult to model statically, compilers often make suboptimal choices, sometimes even degrading performance. The choice between trade-offs DO K=1,N-1 DO T2=2,N,64 DO I=K+1,N DO I=K+1,N DO J=K+1,N A(I,J)=A(I,J)-A(I,K)\*A(K,J)(a) Original code permute([L1, L2, L3])tile(S1,L3,TJ,L1) $\operatorname{split}(S1,L2,[L2 \leq L1 - 2])$ permute(S2,[L1,L2,L4,L3])permute(S1, [L1, L3, L4, L2]) $\operatorname{split}(S1,L2,[L2 \ge L1-1])$  $tile(S3,L2,TI_1,L3)$  $\operatorname{split}(S3,L3,[L5 \leq L2-1])$  $tile(S3,L5,TK_1,L3)$  $tile(S3,L5,TJ_1,L4)$ datacopy(S3,L4,[D1],1)datacopy(S3, L5, [D2]) $unroll(S3,L5,UI_1)$  $unroll(S3,L6,UJ_1)$ datacopy(S4,L3,[D1],1) $tile(S1,L4,TK_2,L2)$  $tile(S1,L3,TI_2,L3)$  $tile(S1,L5,TJ_2,L4)$ datacopy(S1,L4,[D1],1)datacopy(S1, L5, [D2]) $unroll(S1,L5,UI_2)$  $unroll(S1,L6,UJ_2)$ (b) Recipe

DO T4=2,T2-64,256 A(I,K)=A(I,K)/A(K,K) DO T6=1,T4-1,256 DO T8=T6,MIN(T4-1,T6+255) DO T10=T4,MIN(T2-2,T4+255) P1(T8-T6+1,T10-T4+1)=A(T10,T8) DO T8=T2,MIN(T2+56,N),8 DO T10=T8,MIN(N,T8+7) DO T12=T6,MIN(T6+255,T4-1) P2(T12-T6+1,T10-T8+1)=A(T12,T10) DO T10=T4,MIN(T2-2,T4+255) DO T12=T8,MIN(N,T8+7) DO T14=T6,MIN(T6+255,T4-1) A(T10,T12)=A(T10,T12)-P1(T14-T6+1,T10-T4+1) \*P2(T14-T6+1,T12-T8+1) DO T6=T4,MIN(T4+254,T2-3) DO T8=T6+1,MIN(T4+255,T2-2) P3(T6-T4+1,T8-(T4+1)+1)=A(T8,T6)DO T6=T4+1,MIN(T4+255,T2-2) DO T8=T2, MIN(N, T2+63) DO T10=T4,T6-1 A(T6,T8)=A(T6,T8)-P3(T10-T4+1,T6-T4+2)\*A(T10,T8)DO T4=1,T2-65,256 DO T6=T2-1,N,256 DO T8=T4,MIN(T4+255,T2-2) DO T10=T6,MIN(T6+255,N) P4(T8-T4+1,T10-T6+1)=A(T10,T8) DO T8=T2,MIN(T2+56,N),8 DO T10=T8,MIN(N,T8+7) DO T12=T4,MIN(T4+255,T2-2) P5(T12-T4+1,T10-T8+1)=A(T12,T10) DO T10=T6,MIN(T6+255,N) DO T12=T8,MIN(N,T8+7) DO T14=T4,MIN(T2-2,T4+255) A(T10,T12) = A(T10,T12) - P4(T14 - T4 + 1,T10 - T6 + 1)\*P5(T14-T4+1,T12-T8+1) DO T4=T2-1,MIN(N-1,T2+62) DO T8=T4+1,N A(T8,T4) = A(T8,T4) / A(T4,T4)DO T6=T4+1,MIN(N,T2+63) DO T8=T4+1,N A(T8,T6) = A(T8,T6) - A(T8,T4) \* A(T4,T6)

(c) Generated code from (b) with bound parameters

Figure 3.1. Transformation recipe for LU with the CHiLL framework. Recipe syntax simplified for illustration purposes.

can to be made by a developer, a compiler decision algorithm with empirical feedback or a collaboration of the two. A recent body of work on *auto-tuning* uses empirical techniques to execute code segments in representative execution environments to determine the best-performing optimization sequence and parameter values [32, 33, 61, 39, 49, 44, 45, 50, 25].

When parameterized and machine-generated, transformation recipes can form the core foundation of an auto-tuning compiler. Not limited to just simple changes in parameters, auto-tuning compilers can propose multiple code variants representing different optimization strategies that can be compared empirically. A desirable hybrid model involves allowing the developer to guide and interact with the auto-tuning framework, sometimes called *collaborative auto-tuning*.

#### 3.1.3 Remain Architecture and Compiler Agnostic

Transformation recipes allow application and library developers to interact directly with optimization and code generation constructs to transform their code, including expressing parallelism. As proven time and again, hand-coding these changes will result in the undesirable effect of creating a machine-specific program that is difficult to port.

The recipes themselves can be fine-tuned by other developers or modified for different architectures, while the original machine-independent code is maintained with the program. Additionally, using such a system, a developer can now focus on the performance impact of transformations on the target code, instead of the nitty-gritty implementation details of writing correct GPU code.

#### **3.1.4** Interface to Multiple Compilers

The structure of today's compilers makes it difficult to migrate new ideas into practice; retargeting optimizations and decision algorithms for a new compiler infrastructure is often simply infeasible. Every commonly-used compiler infrastructure has strengths and weaknesses, as well as years of development, that are costly to repeat. Converging on one or a small subset of compiler infrastructures is therefore unrealistic.

Composing compiler tools from the collective capabilities of independent systems by ensuring tool interoperability allows for the strengths of each system to be utilized. Transformation recipes can remain compiler and sometimes source language agnostic to be a bridging tool in this interoperable tool chain. A single recipe may even be able to use multiple compiler back-ends to perform the complex set of transformation and code-generation steps.

## 3.2 A Programming Language Approach to Directing Optimizations

#### 3.2.1 Limitations of a Flat Sequential Transformation Recipe

What have so far been referred to as transformation recipes are flat sequences of transformation commands and parameters. When building a framework that targets a specific architecture, it is necessary to provide layers of abstraction that can automatically handle a variety of input scenarios. Abstraction layers allow the optimization strategy to work at a level of detail more general than the ultimate target architecture.

To build such a rich and effective abstraction layer, the following traits are desirable.

- **Parameters as variables** Mutable variables allow for parameters to be set by the *auto-tuning* framework or by other methods.

- Queryable program state Queries capture the side-effects, results of commands and other code state.

- **Control flow** Branches and iteration constructs react to captured or parameterized information.

- Encapsulation Group together commands that are context insensitive to previous commands.

- **Readability** Reference semantic constructs in a way that carries over to the final generated program.

With these goals, it becomes immediately apparent that we are thinking of transformation recipes as programs written in a very limited language. Function outputs, logical branching and the ability to build layers of abstraction and reusable, generic components are easily obtained by using a more fully featured language. In doing so, we no longer refer to these objects as *transformation recipes*, but *transformation scripts*.

#### 3.2.2 Scripting Language Foundation for Compiler Scripts

Although there may be a few promising candidates when selecting a language on which to base a compiler framework for expressing code transformations, the Lua [27] programming language should certainly be on the short list.

Lua is a lightweight, embeddable scripting language with extensible semantics and easy

integration with a host program. With its small set of general features, it can be extended to fit a variety of different problem types. In fact, Lua has been described as "multiparadigm" with features that allow for functional, imperative and object-oriented programming styles.

Lua syntax is also very familiar. Transformation recipes of existing frameworks should be convertible to a script of Lua functions with very minimal syntax changes. Moving to a standard and easily embeddable language also allows for scripts to be potentially universal to more than just a single compiler framework if the compiler community were to establish a standard API for common transformation commands.

# 3.3 CUDA-CHiLL: A Compiler Framework for Generating Optimized CUDA Code

In this section, we introduce CUDA-CHiLL, a unified framework for novel transformations and code generation targeting CUDA code. The CUDA-CHiLL framework is capable of transforming sequential loop nests with standardized loop transformations and data movement commands. The commands are issued by a Lua script and can include complex compositions and use of abstraction layers. When the script execution is finished, CUDA-CHiLL outputs the resulting CUDA source program.

#### 3.3.1 Basis on CHiLL

CUDA-CHILL expands upon the standardized loop transformation commands of CHILL [2]. A polyhedral transformation framework, CHILL provides a powerful collection of polyhedral transformations for handling computation partitioning targeting parallelism on multicore architectures and data copy and layout operations that target deep memory hierarchies. CHILL uses a modified version of the Omega Library [29] for polyhedral manipulation and scanning.

The following is a summary of some of the additional functionality that CUDA-CHiLL provides compared to CHiLL.

- Lua scripting bindings CHiLL uses a sequentially executed custom recipe language to provide its transformation and code generation constructs to the script writer.

- Use of loop variables as semantic handles CHiLL commands use a statement group and loop level to reference specific loop constructs. As each statement modifies the shape and order of the polyhedral space, each command's addressing must reflect

the current state of the program. By adding loop index variables to CUDA-CHiLL, more context-free groups of transformations and abstraction layers can be written.

- New introspective functions To allow for scripts to handle a variety of input code and parameters, a number of functions were added to query the framework's internal representation of the polyhedral model, index variables and CUDA mappings.

- CUDA-specific functions and code generation New commands were needed to generate CUDA-specific constructs and allow the code generation to output valid CUDA programs. These include directing the mapping of loops to grid indices and data transfers between the host and GPU. Also, support was added for thread synchronization calls and special variable attributes like shared memory data structures.

#### 3.3.2 Loop Variables as Semantic Handles

The ability to reference newly created semantic constructs is important to support composition of multiple transformations and also to encapsulate groups of transformations in a context-independent manner. CHiLL's current method of addressing constructs in its polyhedral model uses a statements group number and a loop level. A *tile* command, for example, will produce a new loop level. Subsequent transformation commands must take into account this change in the internal representation of the polyhedral model when they make references using statement numbers and loop levels. The result of this addressing method can be hard to follow recipes such as the LU transformation recipe in Figure 3.1 (b). For example, L4, L5 and L6 refer to loops created by tile and split commands. Although powerful in its ability to compose multiple transformations, it is almost necessary to print out generated code at each line in the recipe in order to see what constructs are being referenced in the next command.

We make the observation that a loop index variable uniquely identifies a nested loop for a given statement. Thus, instead of specifying loop levels, the index variable for that level can be used. But as a loop *level* may reference different semantic constructs with each change to the polyhedral model, a loop *index* is a sticky handle that stays valid as new loop levels are introduced or others removed. As an additional advantage, having to specify a fresh index variable for newly created loops provides both a handle for referencing the loop in later operations and a more readable output from code generation.

For example, Figure 3.2 shows a transformation script applied to matrix vector multiply

that introduces two new control loops to be used as CUDA block and thread indices, ii and jj. In Figure 3.2 (b), these new loops are used as handles for the CUDA mapping operation at line 7 and they can be seen as the loop indices of the first two loop levels of the intermediate code shown in (c).

### **3.4** Abstraction Layers with Lua

Another feature of the underlying scripting language of CUDA-CHiLL that allows for shorter, more powerful and easily readable transformation scripts is the ability to write usable abstraction layers. Although every script can use the functions provided by CUDA-CHiLL directly to express the optimization strategies, building a domain-specific abstraction layer allows for shorter scripts and the reuse of common patterns.

Such abstraction layers themselves may collect the best strategies for targeting a specific architecture, which may change over time as better optimization techniques arise. By being specific to an architecture, simplifying assumptions can be made that allow the script writer a proper level of detail for constructing their optimization strategies.

In CUDA-CHiLL, the high-level functions described in the next section are written in Lua and built using the functions provided by CUDA-CHiLL. At the top of a transformation script, a Lua command dofile(hlcuda.lua) is used to import these functions into the current script namespace.

#### 3.4.1 High Level Description of Tiling

With the CUDA-CHiLL hlcuda.lua abstraction layer, the function tile\_by\_index provides a powerful and quick way to direct the computation space decomposition of the original nested loop. As shown in usage in Figure 3.3 (c), tile\_by\_index can express a group of tile operations and loop permutations through a high level Lua function. The original code is shown in Figure 3.3 (a) and the generated code in (d). Table 3.1 provides descriptions of each parameter of the tile\_by\_index command.

An algorithm discussed in Chapter 4 is employed to determine the tile operations and loop order permutations required to achieve an end result that matches the list of index variables given as the final parameter to tile\_by\_index. As shown when comparing the original CHiLL tile commands in Figure 3.3 (b) to the CUDA-CHiLL equivalent in Figure 3.3 (c), tile\_by\_index is often performing more than one tile transformation per function call.

```

void seqMV(float c[N][N], float a[N],

float b[N])

{

int i, j;

for (i = 0; i < N; i++)

for (j = 0; j < N; j++)

a[i] = a[i] + c[j][i] * b[j];

}

```

(a) The matrix-vector sequential source code.

```

dim3 dimGrid(64, 1);

dim3 dimBlock(64, 1);

1 init("seqMV.suif", 0, 0)

gpuMV<<<dimGrid,dimBlock>>>(dev01Ptr,

2 dofile(hlcuda.lua)

devI1Ptr, devI2Ptr);

3 N=1024

cudaMemcpy(a, devO1Ptr, 1024 * 4,

4 TI=16

cudaMemcpyDeviceToHost);

5 tile_by_index({"i","j"}, {TI,TI},

cudaFree(dev01Ptr);

{l1_control="ii", l2_control="jj"},

cudaFree(devI1Ptr);

{"ii", "jj", "i", "j"})

cudaFree(devI2Ptr);

6

print_code()

}

7

cudaize("gpuMV", {a=N, b=N, c=N*N},

{block={"ii"}, thread={"jj"}})

(d) The resulting CUDA scaffolding in the

original host-executed function.

(b) A very simple transformation recipe.

__global__ void gpuMV(float *a, float **c,

for (ii = 0; ii < 64; ii++)

float *b)

for (jj = 0; jj < 64; jj++)

ł

for (i = 16 * ii; i < 16 * ii + 16; i++)

int bx = blockIdx.x; int tx = threadIdx.x;

for (j = 16 * jj; j < 16 * jj + 16; j++)

for (i = 16 * bx; i < 16 * bx + 16; i++)

a[i] = a[i] + c[j][i] * b[j];

for (j = 16 * tx; j < 16 * tx + 16; j++)

a[i] = a[i] + c[j][i] * b[j];

(c) The results of output at line 6 from (b).

}

```

{

(e) The resulting CUDA kernel

void seqMV(float \*\*c, float \*a, float \*b)

float \*devO1Ptr, \*devI1Ptr, \*devI2Ptr;

cudaMalloc(&devO1Ptr, 1024 \* 4);

cudaMemcpy(devO1Ptr, a, 1024 \* 4,

cudaMemcpyHostToDevice);

cudaMemcpyHostToDevice);

cudaMalloc(&devI2Ptr, 1024 \* 4);

cudaMemcpy(devI2Ptr, b, 1024 \* 4, cudaMemcpyHostToDevice);

cudaMalloc(&devI1Ptr, 1048576 \* 4);

cudaMemcpy(devI1Ptr, c, 1048576 \* 4,

Figure 3.2. A simplified example of tiled and CUDAized matrix-vector multiply

| Command            | Example Parameter           | Description                                           |  |

|--------------------|-----------------------------|-------------------------------------------------------|--|

|                    | {"i","j"}                   | The index variables of the loops that will be tiled   |  |

| tile by inder      | {TI,TJ}                     | The respective tile sizes for each index variable     |  |

| tile_by_index      | {l1_control="ii",           | A mapping that specifies control loop variable        |  |

|                    | <pre>l2_control="jj"}</pre> | names and optionally renames tile loop index vari-    |  |

|                    |                             | ables.                                                |  |

|                    | {"ii", "jj", "i", "j"}      | Final order of nested loops with update loop index    |  |

|                    |                             | names                                                 |  |

|                    | "gpuMV"                     | The name of the kernel function                       |  |

| cudaize            | $\{a=N, b=N, c=N*N\}$       | The data sizes of the arrays if not statically deter- |  |

|                    |                             | minable                                               |  |

|                    | {block={"ii"},              | Block and thread indices for mapping. The             |  |

|                    | thread={"jj"}}              | bounds for these loops are used to define the grid    |  |

|                    |                             | dimensions.                                           |  |

| copy_to_registers  | "kk"                        | The loop level, given as an index variable, that is   |  |

| copy_co_registers  |                             | the target of register structure                      |  |

|                    | "c"                         | The name of the array variable to be copied           |  |

|                    | "tx"                        | The loop level, given as an index variable, that is   |  |

| $copy\_to\_shared$ |                             | the target of the copied data                         |  |

|                    | "b"                         | The name of the array variable to be copied           |  |

|                    | -16                         | Ensure the dimensions of the temporary array are      |  |

|                    |                             | coprime with 16                                       |  |

| unroll_to_level    | 1                           | Unrolls all statements up to one level from in-       |  |

|                    |                             | nermost loops outwards. This construct will stop      |  |

|                    |                             | unrolling if it encounters a CUDA thread mapped       |  |

|                    |                             | index.                                                |  |

${\bf Table \ 3.1.} \ {\rm Description \ of \ prominent \ commands \ in \ CUDA-CHiLL \ scripts.}$

### 3.4.2 High Level Description of Data Copy

The hlcuda.lua abstraction layer also provides functions for *locality optimizations* that target shared memory and registers. These functions, copy\_to\_shared and

copy\_to\_registers, are based on CUDA-CHiLL's *datacopy* and *datacopy\_privatized* operations, discussed more in Chapter 4, but utilize other features of CUDA-CHiLL to meet their objectives.

For example, copy\_to\_shared must ensure that the resulting extracted loops match one of the defined CUDA dimensions and that stores to the shared memory are properly synchronized. For targeting registers, the CUDA C compiler will predictably place local array accesses into registers providing the index expressions are simply determinable. Thus, copy\_to\_registers unrolls loops introduced by datacopy\_privatized to remove variables from the array index expressions.

```

1 original()

2 tile(0,1,TI,1,counted)

for (i = 0; i < n; i++)

3 tile(0,3,TJ,2,counted)

for (j = 0; j < n; j++)

4 tile(0,5,TK,3,strided)

for (k = 0; k < n; k++)

5 tile(0,4,TK,4,counted)

c[j][i] = c[j][i] + a[k][i] * b[j][k]

6 tile(0,5,1,5,counted)

7 tile(0,5,1,4,counted)

(a) Matrix multiply source code (BLAS)

(b) CHiLL tile commands

1 tile_by_index({"i","j"}, {TI,TJ}, {l1_control="ii", l2_control="jj"},

{"ii", "jj", "i", "j"})

2 tile_by_index({"k"}, {TK}, {l1_control="kk"}, {"ii", "jj", "kk","i", "j","k"},

strided)

3 tile_by_index({"i"}, {TJ}, {l1_control="tt",l1_tile="t"},

{"ii", "jj", "kk","t","tt","j","k"})

(c) CUDA-CHiLL tile_by_index equivalent

for (ii = 0; ii < 16; ii++)</pre>

for (jj = 0; jj < 64; jj++)

for (kk = 0; kk < 1009; kk += 16)

for (t = 0; t < 16; t++)

for (tt = 0; tt < 4; tt++)

for (j = 16 * jj; j < 16 * jj + 16; j++)

for (k = kk; k < kk + 16; k++)

c[j][64 * ii + 16 * tt + t] = c[j][64 * ii + 16 * tt + t] +

a[k][64 * ii + 16 * tt + t] * b[j][k];

```

(d) Generated code after tile commands

Figure 3.3. Initial tiling for matrix multiply for GPU parallelism (CUBLAS 2)

As seen in Figure 3.4, the resulting use of these high level functions to target the deep memory hierarchy of a GPU is much shorter and expressive than the CHiLL equivalent. The commands used in Figure 3.4 (b) have their parameters explained in Table 3.1. Note that the CHiLL recipe shown in Figure 3.4 (a) does not handle CUDA-specific constructs such as designating shared memory and inserting synchronization barriers but is otherwise comparable in the resulting transformations.

Figure 3.5 depicts how the computation of a small N=8 matrix-vector multiply (MV) problem shown in Figure 2.2 (a) can be optimized with these high level data copy commands. A *copy\_to\_shared* command is used to copy sections of the *b* vector into shared memory using multiple threads. A *copy\_to\_registers* is used to copy individual values picked by the thread and block index (*tid* and *bid*, respectively, in the figure) from the *a* result vector to a *tmp* variable where it is used in the computation and then copied back to the result vector. Although minimal in its problem size and tile size for example purposes, this is the same

```

1 --register copy

2 datacopy_privatized(0, 3, "c", 4, 5, false, -1, 1, 1)

3 --shared memory copy

4 datacopy(0, 4, "b", false, 0, 1, -16)

5 --thread parallelism for shared memory copy

6 tile(3,4,(TJ*TJ)/TI,4,counted)

7 tile(3,6,1,4,counted)

8 --unroll register copy loops

9 unroll(1,5,0)

10 unroll(2,5,0)

11 --fully unroll shared copy loop

12 unroll(3,6,0)

13 -- finally unroll main computation

14 unroll(0,8,0)

15 unroll(0,9,0)

16 --unroll additional cleanup loops

17 unroll(8,6,0)

18 unroll(4,5,0)

19 unroll(6,5,0)

(a) CHiLL commands

1 copy_to_registers("kk", "c")

2 copy_to_shared("tx", "b", -16)

3 unroll_to_depth(2)

```

(b) CUDA-CHiLL equivalent where "kk" and "tx" are index variables

Figure 3.4. Data copy and unroll for matrix multiply for GPU memory hierarchy (CUBLAS 2)

**Figure 3.5**. Given an easy to depict, although trivially small problem size of N=8 for matrix-vector multiplication, the decomposition using a tile size of TX=4 is visually depicted with the global memory matrix, vectors and shared memory structures. The corresponding kernel code is also given.

strategy used in the MV script discussed in Chapter 5 for running benchmarks.

### 3.4.3 High Level Description of Unroll

Part of a CUDA optimization strategy is sufficient granularity that the performance benefits of running on the GPU outweigh the overhead of data transfer and thread execution. This often means leaving some loop levels inside the kernel. Unrolling these loops in the GPU kernel provides the same performance benefits that unroll provides on conventional processors, except because of some GPU attributes discussed below, these benefits may be even more notable on the GPU.

Because hardware vendors try to provide as many execution units as possible in a GPU processor, the complexity of each execution unit is fairly simple. Without much silicon devoted to branch prediction, and with the lock-step manner in which threads are executed inside a SM, unrolling sometimes improves performance purely by removal of loop iteration overhead. Also, the compiler may be able to reuse data in registers and improve instruction scheduling when compiling statements from unrolled fixed-size loops.

The unroll\_to\_level command unrolls the innermost loops of compute statements. It may unroll up to a specified number of levels, but never unrolls a loop mapped to a thread or block. Also inherent in this CUDA-specific abstraction is the careful treatment of extra clean-up statements often created by the unroll transformation. These statements may not be created for every combination of data set size and tile dimensions. But, when generating library code for all potential problem sizes, various dimensions will result in different sets

of clean up statements. In this case, unroll\_to\_level makes certain to have the iteration spaces of the clean-up statements also mapped to CUDA thread dimensions for optimal performance.

Because unroll\_to\_level can query to detect side effects, this approach dramatically simplified generating optimized code for every potential matrix size of the matmul case study discussed in Chapter 5. Earlier research iterations required individually handling the sequence of unroll operations required for the different variations of clean-up loops generated by the various problem sizes.

# 3.5 Summary

With the high level abstraction interface and its specialization in building optimized GPU code, CUDA-CHiLL exemplifies the utility of using scripting languages as the interface to compiler transformations and code generation. Applicable transformations such as tiling and loop unrolling can be made available at a level of detail suited to a developer composing an optimization strategy. Next, we discuss the details of CUDA-CHiLL behind the abstraction interface.

# CHAPTER 4

# CUDA-CHILL TRANSFORMATIONS AND CODE GENERATION

In this chapter, we present how the organization of our compiler system falls into two phases. Phase I builds an internal representation of the source program and performs transformations and queries on that representation. Phase II of the compiler generates optimized code for the CUDA platform for various problem sizes and optimization techniques.

### 4.1 The Two Phase Structure

To allow for the most flexible and powerful model of code transformations and targetspecific optimizations, CUDA-CHiLL's compiler framework is partitioned into two phases of operation, as shown in Figure 4.1. Phase I is governed by the running of a Lua transformation script. The start of the script loads and initializes the internal representation of CUDA-CHiLL based on an input source file. Each API call of the script performs a transformation or query on this internal representation.

When the script finishes its execution, the framework enters Phase II. With the newly transformed and updated internal representation, a code generation library is given groups of statements and constraints and attempts to generate as output the cleanest sequential code representation for the statements. This intermediate generated code is then specialized for the CUDA architecture with the details of the CUDA grid space and data movement gathered from running the transformation script. Finally, the output is ready to be translated to compilable CUDA C that should be functionally equivalent to the input source program.

#### 4.1.1 Interpreting Transformation Scripts

Executing transformation scripts in CUDA-CHiLL involves creating, updating and querying an internal representation of the source program. When initialized at the beginning of a script, CUDA-CHiLL is given a source file that is preprocessed into a high-level source

Figure 4.1. CUDA-CHiLL System Diagram

intermediate representation (IR) based on SUIF [62]. Along with the SUIF source file, a specific procedure and loop are given as the target of the transformation script.

At initialization, the input IR for the specified loop is transformed into a set of groups of statements where each group shares the same index space. The internal representation of CUDA-CHiLL then consists of the following items.