# HYBRID SCHEDULING FOR GRAPH-BASED ALGORITHM DECOMPOSITION IN HIGH-PERFORMANCE COMPUTING ENVIRONMENTS

by

Braden Devin Robison

A thesis submitted to the faculty of The University of Utah in partial fulfillment of the requirements for the degree of

Master of Science

$\mathrm{in}$

Computational Engineering and Science

School of Computing

The University of Utah

May 2014

UMI Number: 1553595

All rights reserved

INFORMATION TO ALL USERS The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

UMI 1553595

Published by ProQuest LLC (2014). Copyright in the Dissertation held by the Author.

Microform Edition © ProQuest LLC. All rights reserved. This work is protected against unauthorized copying under Title 17, United States Code

ProQuest LLC. 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106 - 1346 Copyright © Braden Devin Robison 2014

All Rights Reserved

## The University of Utah Graduate School

## STATEMENT OF THESIS APPROVAL

| The thesis of  | Brad                               | len Devin Robison  |                            |

|----------------|------------------------------------|--------------------|----------------------------|

| has been appro | ved by the following supervisory c | committee members: |                            |

|                | James Sutherland                   | , Chair            | 4/2/2013<br>Date Approved  |

|                | Mary Hall                          | , Member           | 3/25/2013<br>Date Approved |

|                | Adam Bargteil                      | , Member           | 3/20/2013<br>Date Approved |

| and by         | Martin Berzins                     |                    | _ , Chair/Dean of          |

| the Departmen  | t/College/School of                | Computer Scienc    | e                          |

|                |                                    |                    |                            |

and by David B. Kieda, Dean of The Graduate School.

## ABSTRACT

At the beginning of the 21st century, it became apparent that the performance gains associated with continual die shrinks and the resulting increases in core central processing unit (CPU) speeds were beginning to flatten. This realization has gradually shifted the focus of CPU design away from single core speed increases and toward the idea of obtaining performance through increased concurrency. The resulting design paradigm has given us multi- and many-core CPUs, vector processing units, and more recently, programmable, massively parallel hardware coprocessors, such as graphics processing units from nVidia and Advanced Micro Devices, along with more recent general purpose devices such as Intel's "Knights Corner." One of the most significant resulting challenges in high-performance computing is to provide a framework in which the software development process is platform agnostic to its end users, while at the same time being capable of scaling efficiently on diverse hardware configurations. This thesis will present an improved approach for the analysis and scheduling of computational tasks within a heterogeneous hardware environment, while removing implementation details from end users. This will be presented within the context of the "Expression" framework, a component within a computational fluid dynamics solver, known as "Wasatch," developed at the University of Utah.

## CONTENTS

| ABSTRACT iii |                                                                                                           |                 |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------|-----------------|--|--|

| LIS          | ST OF FIGURES                                                                                             | $\mathbf{vi}$   |  |  |

| AC           | KNOWLEDGMENTS                                                                                             | viii            |  |  |

| СН           | IAPTERS                                                                                                   |                 |  |  |

| 1.           | INTRODUCTION                                                                                              | 1               |  |  |

|              | 1.1 Overview                                                                                              | 1               |  |  |

|              | 1.1.1 Advantages                                                                                          | 1               |  |  |

|              | 1.1.2 Challenges                                                                                          | 2               |  |  |

|              | 1.2 Distributed and Heterogeneous Hardware                                                                | 3               |  |  |

|              | 1.2.1 Grid-Based Computing                                                                                | 3               |  |  |

|              | 1.2.2 Transition from Single to Multicore Architectures1.2.3 Coprocessors and Massively Parallel Hardware | $\frac{4}{4}$   |  |  |

|              | 1.3 Approaches to Computational Software                                                                  | 4<br>5          |  |  |

|              | 1.3.1 Mastery of Everything                                                                               | $\frac{5}{5}$   |  |  |

|              | 1.3.2 Our Goal - Separating Form and Functionality                                                        | 6               |  |  |

|              | 1.4 The Wasatch Framework                                                                                 | 6               |  |  |

| 2.           | GRAPH THEORY AND APPLICATIONS                                                                             | 7               |  |  |

|              | 2.1 Overview                                                                                              | 7               |  |  |

|              | 2.1.1 Terminology                                                                                         | 7               |  |  |

|              | 2.1.2 Algorithms                                                                                          | 8               |  |  |

|              | 2.2 DAGs as Computational Models                                                                          | 9               |  |  |

|              | 2.2.1 Motivation                                                                                          | 9               |  |  |

|              | 2.2.2 Related Work                                                                                        | 9               |  |  |

|              | 2.2.3 The Expressions Context                                                                             | 11              |  |  |

|              | 2.2.4 The Dependency Graph                                                                                | 12              |  |  |

|              | 2.2.5 The Task Graph                                                                                      | $\frac{12}{12}$ |  |  |

|              | 2.3 Extracting Information      2.3.1 Task Granularity                                                    | 12 $12$         |  |  |

|              | 2.3.1 Task Granuarity                                                                                     | $12 \\ 12$      |  |  |

|              | 2.3.2       Graph infospection         2.3.3       Bounds on Execution Time                               | 12 $13$         |  |  |

|              | 2.3.4       Parallelization                                                                               | $13 \\ 13$      |  |  |

| 3.           | FRAMEWORK EXTENSIONS                                                                                      | 15              |  |  |

|              |                                                                                                           |                 |  |  |

|              | 3.1 The Expressions Library         3.1.1 Overview                                                        | $15 \\ 15$      |  |  |

|              | 3.1.1 Overview       3.1.2 Concepts and Terminology                                                       | $\frac{15}{15}$ |  |  |

|              |                                                                                                           |                 |  |  |

| 3.1.3 Implementing an Expression                           | 17 |

|------------------------------------------------------------|----|

| 3.1.4 Constructing the Task Graph                          | 19 |

| 3.1.5 Design Goals                                         | 20 |

| 3.1.6 A Flexible Scheduling Model                          | 21 |

| 3.1.7 The Priority Task Scheduler                          | 22 |

| 3.1.8 Graph-Based Execution                                | 22 |

| 3.1.9 Task Dispatch Model                                  | 23 |

| 3.1.10 Improving Resource Utilization                      | 25 |

| 3.1.11 Memory Resources                                    | 25 |

| 3.1.12 Threading Resources                                 | 29 |

| 3.1.13 The "Hybrid" Task Scheduler                         | 31 |

| 3.1.14 Device Assignment                                   | 33 |

| 3.1.15 Path Coalescing "Clustering"                        | 35 |

| 3.1.16 Reducing Edge Latency                               | 35 |

| 3.2 The Spatial Fields Library                             | 37 |

| 3.2.1 Overview                                             | 37 |

| 3.2.2 Concepts and Terminology                             | 37 |

| 3.2.3 Operator Selection                                   | 38 |

| 3.2.4 External Consumers                                   | 38 |

| 4. RESULTS AND EVALUATION                                  | 40 |

| 4.1 Test Cases                                             | 40 |

| 4.1.1 Scheduler Performance - Task Threaded Operator       | 10 |

| Interaction                                                | 40 |

| 4.1.2 Scheduler Performance - Task Threaded MPI-Process    | 10 |

| Interaction                                                | 43 |

| 4.1.3 Scheduler Performance - Task Threaded MPI-Scaling:   |    |

| Multinode                                                  | 49 |

| 4.1.4 Hybrid Scheduler Feasibility - Stencil 2 Performance | 49 |

| 4.2 Conclusion                                             | 54 |

| 4.2.1 Work Summary                                         | 54 |

| 4.2.2 Future Work                                          | 55 |

| 4.2.3 Final Thoughts                                       | 56 |

| APPENDIX: SCHEDULER CODE                                   | 57 |

| REFERENCES                                                 | 71 |

|                                                            |    |

## LIST OF FIGURES

| 3.1  | Framework component diagram.                                                                                   | 16          |

|------|----------------------------------------------------------------------------------------------------------------|-------------|

| 3.2  | Example of a basic expression.                                                                                 | 16          |

| 3.3  | Constructing the task graph from individual expressions                                                        | 18          |

| 3.4  | Advertise dependents implementation                                                                            | 19          |

| 3.5  | Bind operators implementation                                                                                  | 19          |

| 3.6  | Bind fields implementation.                                                                                    | 19          |

| 3.7  | Evaluate method implementation                                                                                 | 19          |

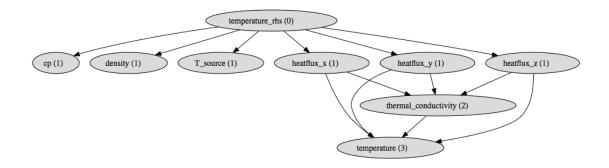

| 3.8  | Visualization of a potential task graph for the heat equation                                                  | 21          |

| 3.9  | Simplified communication memory model, multicore CPU                                                           | 23          |

| 3.10 | Priority Task Dispatch Model                                                                                   | 24          |

| 3.11 | Dependency graph illustrating the deallocation of a fully consumed expression.                                 | 26          |

| 3.12 | Initial field manager implementation.                                                                          | 27          |

| 3.13 | Updated field manager implementation                                                                           | 28          |

| 3.14 | Idealized multilevel parallelism                                                                               | 30          |

| 3.15 | Example task graph analysis to determine thread allocation. Note: execution times are all normalized to 1      | 31          |

| 3.16 | Expanded communication memory model                                                                            | 32          |

| 3.17 | Scheduling with mixed hardware and edge transfer cost                                                          | 34          |

| 3.18 | Multiconsumer field problem.                                                                                   | 35          |

| 3.19 | Illustration of consumer prefetching                                                                           | 36          |

| 3.20 | Illustration of consumer prefetching                                                                           | 37          |

| 4.1  | Example scalability graph, eight equation, no source coupling                                                  | 42          |

| 4.2  | Example scalability graph, eight equation, source coupling                                                     | 44          |

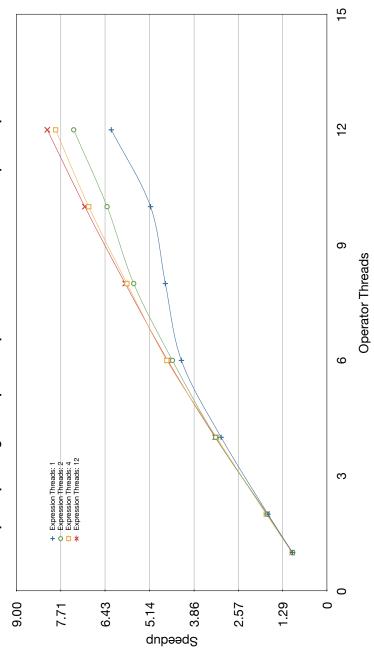

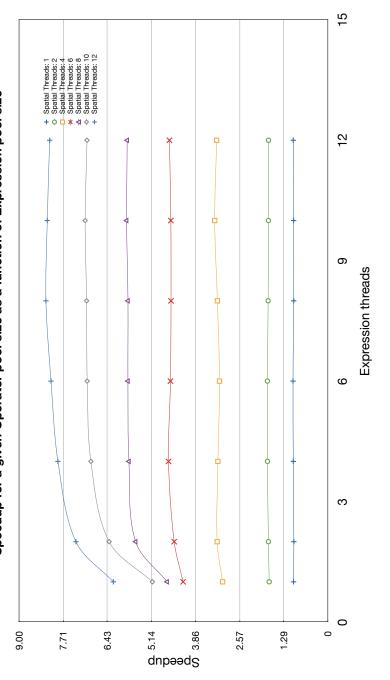

| 4.3  | Scalability test, ember 2012, plotted as a function of operator threads - 256x128x12<br>16 variables           | $28, \\ 45$ |

| 4.4  | Scalability test, ember 2012, plotted as a function of expression threads - 256x128x128, 16 variables          | 46          |

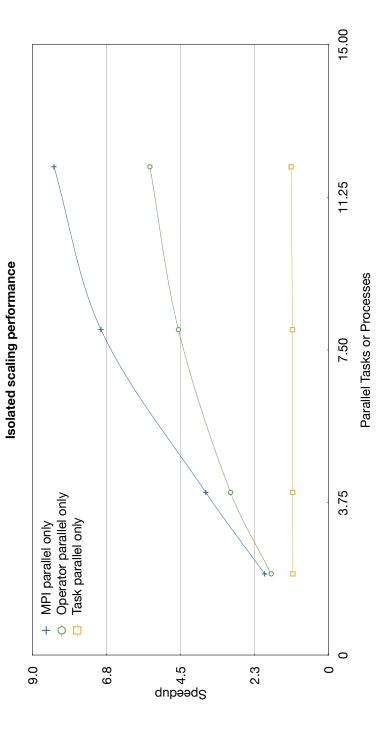

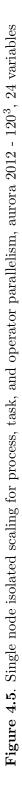

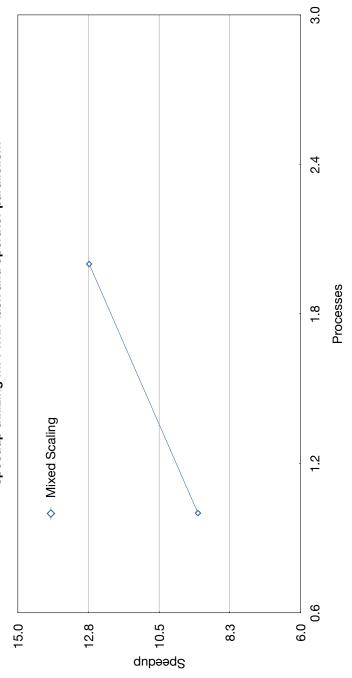

| 4.5  | Single node isolated scaling for process, task, and operator parallelism, aurora $2012 - 120^3$ , 24 variables | 47          |

| 4.6  | Single node MPI scaling with 12 task and 12 operator threads, aurora 2012 -     | 40 |

|------|---------------------------------------------------------------------------------|----|

|      | $120^3$ , 24 variables                                                          | 48 |

| 4.7  | Scalability test 2012 - $256^3$ , 16 variables                                  | 50 |

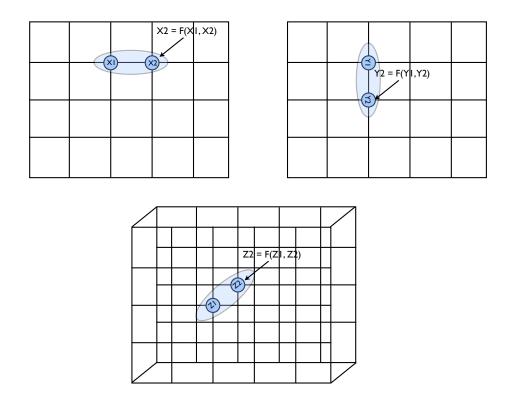

| 4.8  | Example stencil-2 computation, 2012                                             | 51 |

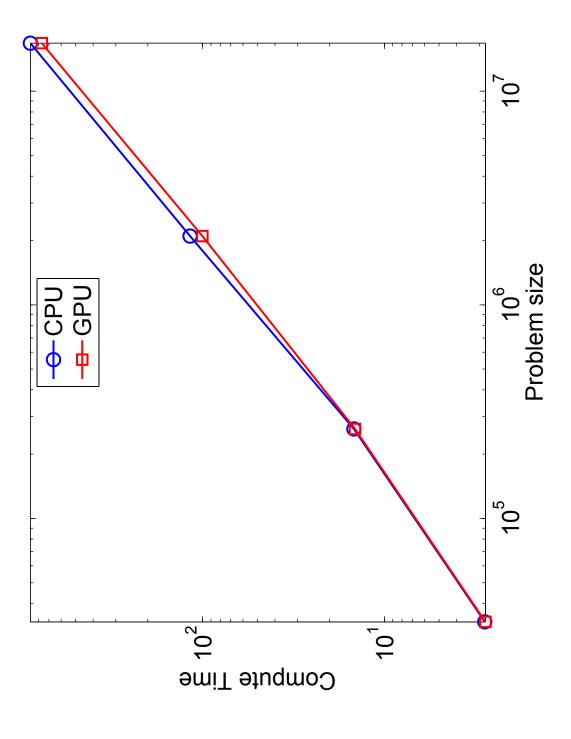

| 4.9  | CPU vs GPU scaling for gradient spatial operator - total graph time, $2012$     | 52 |

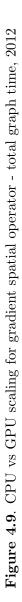

| 4.10 | CPU vs GPU scaling for gradient spatial operator - single operator time, $2012$ | 53 |

| 4.11 | Highly parallel task graph structure with punctuated serialization              | 56 |

## ACKNOWLEDGMENTS

I would like to acknowledge my graduate advisor, Professor James Sutherland, for all his enthusiasm, patience, and excellent advice. I learned a great deal from him and was exposed to a world of ideas that I might never have had an opportunity to experience anywhere else. I would also like to thank Dr. Tony Saad for being a wonderful friend and collegue over the last few years. He is an amazing person and will someday change the field of mass transport!

## CHAPTER 1

### INTRODUCTION

### 1.1 Overview

While the idea of predetermining the outcome or behavior of some physical system is much older than the computer itself, the ability to perform detailed simulation of large, complex problems was out of reach until the latter half of the 20th century. Even then, the tools and expertise required for such simulation were not available to anyone outside of government or large research institutions for much of that time. However, as the availability and cost associated with high-performance computing hardware has dropped, the capabilities of off-the-shelf and commodity hardware has reached a point where conducting accurate simulations has become feasible to a broad audience. Today, the average consumer smart phone is able to provide thousands of times more computing power than warehouse sized machines of the 1960s at a small fraction of the cost.

Along with the rapid improvements in hardware and its availability, there have also been significant improvements in the general accessibility of software tools for utilizing computational resources. With the standardization of large-scale message passing standards, such as the message passing interface (MPI), along with the rise in availability of time-shared super computers and clouds, the idea of using simulation to drive research and development has become more ubiquitous. This can be observed across a diverse range of applications, from the pharmaceutical industry, which attempts to model drug interactions [3], to hardware manufacturers who put new architectures through rigorous, transistor level simulations before ever taping out a physical product [15].

#### 1.1.1 Advantages

A major component of any development process is testing and verification, to ensure that a product or process functions in the desired fashion, and poses no overt danger to an end user when used properly. These testing processes can present significant hazards; complex chemical reactions with toxic or flammable components, explosives testing, or other high-energy interactions all have inherent risks associated with them. Utilizing the proper simulation tools, many of these systems can be examined in a safe environment, before ever being tested in the lab.

As an example, vehicle manufacturers can model thousands of arbitrary impact scenarios, while obtaining detailed information with respect to forces experienced by a passenger and vehicle components, without being forced to sacrifice valuable materials and testing equipment. This increase safety, reduces material costs, and in the event that a problem is detected during the testing process, a fix can be implemented and retested with significantly less effort than would have been possible in a more conventional testing lab.

Another issue which is important to consider is information completeness. In any real system, we are limited in the amount of data we can collect due to constraints on sensor density, and physical characteristics of the experiment itself. If we wish to examine some type of large-scale explosion or high-energy behavior, then it is entirely infeasible to experimentally capture the complete behavior of the explosive material and the resulting forces through the entire life cycle of the process. However, in simulating such a scenario, we can theoretically capture a complete data profile at all resolved scales of the simulation (so long as we have sufficient data storage capacity).

#### 1.1.2 Challenges

The advantages listed above are not without cost; there are numerous challenges which must be overcome in terms of the science, software, and processing capability required to generate accurate and verifiable results. The process of simulating interesting "real-world" problems consists of a number of nontrivial components. The physical processes governing the problem or system must be identified and, ideally, be well understood. These processes must then be properly stated in a mathematical form, often as a series of governing equations, which can then be solved, either directly or via discretization methods, to yield the desired piece of information. Finally, the described process must be implemented in software, which is then executed on a set of test bed machinery. Once the system is properly described and implemented, then the resulting information can be validated through analysis and visualization.

The final step is of particular interest from a computational science perspective. Translating a series of mathematical expressions into a form which can be accurately solved by a computer is a complex and challenging task. For a given type of problem, there are a variety of numerical methods which can be applied, each of which has trade offs in terms of performance and accuracy. This is important, as in almost any "real-world" situation, we will require a simulation to not only run and produce accurate results, but to do so in a "reasonable" amount of time. The problem of balancing these constraints, while still producing an effective solution, is quite challenging and will often require the collaborative efforts of engineers, physical and computer scientists, and mathematicians.

### **1.2** Distributed and Heterogeneous Hardware

To illustrate some of the additional challenges which have become more prominent during the 21st century, it is worthwhile to examine some of the significant changes in the philosophy of hardware and communication architectures over the last few decades, leading to grid-based computing.

#### 1.2.1 Grid-Based Computing

As previously mentioned, the idea of high-performance computing was, for much of the last century, unavailable to the vast majority of scientists, researchers, and businesses. One of the major driving factors of this problem was that almost all initial super computers were monolithic analog processing systems, which would take up entire warehouses, vast amounts of power, and require a full technical staff to operate [10]. This began to change, to some extent, with the introduction of the digital transistor, an amazing device which allowed for electronics to shrink drastically in size and power consumption; however, the notion of a single monolithic machine persisted until the early 1990s.

Initial attempts to develop faster commodity computing infrastructures began to take advantage of the increasing availability of x86-based personal computers (PCs) and the fact that they could be networked together. The idea was fairly straightforward, a single task would be broken into smaller pieces which could each be solved independently, and then each of those task would be "pushed," or assigned, to a networked device. Each device would work on its portion of the larger problem, and then notify the grid's controlling software when it had finished. In this fashion, it became possible to construct extensible computing infrastructures, using consumer-grade PCs, with only a modest initial investment. As networking capabilities and throughput capacity began to improve, this concept of "grid-computing" began to emerge as a popular and accessible method for researchers to benefit from large-scale simulation and modeling.

Grid computing ushered in a new design paradigm, in which discrete distributed resources were connected through a generic medium, such as Ethernet or fiber optics, rather than being hard wired to a central bus of a single large piece of hardware. While making largescale computing more accessible, this change in design significantly increased the cost of communication and synchronization between nodes, often by an order of magnitude or more. During the 1980s, numerous message passing environ/ments were designed to deal these problems, and around 1992, the best pieces of each were coalesced into the MPI standard, which has become the primary standard for modern, grid-based, high-performance and scientific computing [3].

#### **1.2.2** Transition from Single to Multicore Architectures

Core clock rates for central processing units (CPUs) grew drastically from 1990-2000, starting in the tens of MegaHertz and ending in the giga hertz range by the end of the century. However, as design processes continued to shrink and CPU clock rates pushed higher, it became apparent that manufacturers were rapidly approaching a performance limit with traditional designs. Problems related to current leakage and heat generation began to scale more rapidly than any associated performance gains, and CPU manufacturers such as Intel and Advanced Micro Devices began to look elsewhere for ways to improve performance.

As the speed of individual chips essentially plateaued, Moore's Law, an idea stating that the overall number of transistors on chip would double every 18 to 24 months, continued to hold [18]. Faced with ever-increasing on-chip real estate, CPU manufacturers began to fabricate chips with multiple processors or "cores" on a single die. The idea was that if it was not possible to improve the speed of serial computations, it was certainly still possible to increase the amount of concurrent work which could be performed on a single device.

#### 1.2.3 Coprocessors and Massively Parallel Hardware

Unlike CPU cores, which have been traditionally designed to maximize serial performance, utilizing complicated circuitry for out of order execution, and doing everything possible to avoid pipeline delays, there has long been the notion of "vector-based" processors. Vector processing is the idea of having hardware which is capable of operating on many pieces of data simultaneously, often executing a single instruction in parallel across each data element, a process known as single instruction multiple data (SIMD). However, with the exception of some multimedia extensions, such as streaming SIMD extensions (SSE), found within x86 processors, general purpose vector-based processors have not traditionally been readily available to consumers. This has changed with the advent of discrete programmable graphics hardware, known as graphics processing units (GPUs). Originally designed to accelerate tasks relating to computer graphics, such as geometry translation and coloring, which are often "embarrassingly" parallel, it was shown by various researchers [24] that GPUs had the potential for much more general computation.

Realizing the potential of generic, programmable, vector hardware, which was capable of operating on massive amounts of data concurrently, GPU vendors such as nVidia began to develop and expose application programming interfaces (APIs) allowing software developers to more easily exploit the functionality of their hardware [7]. This has, in turn, created a significant need to reexamine software design practices related to high-performance computing, as in certain cases, specific computations may run one or even two orders of magnitude faster on GPU than would be possible on CPU. With this understanding, the ability of software to properly distribute workloads across a variety of hardware, keeping task on the device which offers the best performance, has become extremely important.

### **1.3** Approaches to Computational Software

This trend, requiring added concurrency from software algorithms, has introduced significant complications into the process of architecting quality, high-performance, simulation software. There are now (multi/many)-core CPUs, massively parallel coprocessor like devices such as general purpose GPUs (GPGPUs), and more exotic coprocessors coming, all of which have their own memory, communication costs, and programing paradigms. Each of these devices offer additional benefits and trade-offs such as running multiple distinct processes vs multiple threads per process in the case of multicore CPUs, and in the case of GPGPUs, extremely fast vector processing in cases where data reuse is high and access patterns are regular. As a result, the choice of when and how to use available computing resources is often not straightforward.

### 1.3.1 Mastery of Everything

For an end user or domain scientist wishing to take advantage of the numerous computing options available today, the situation can seem quite daunting. It is no longer enough to know a general purpose programming language and then express ones computational model as a self-contained program. Care must be taken with respect to taking advantage of the features available from underlying systems hardware, and designing a program to not only run, but scale effectively on a large computing grid (often consisting of thousands if not hundreds of thousands of nodes). Additionally, as is the case with various GPGPU computing elements, more care must be taken with respect to algorithm correctness, as numeric rounding and floating point representations may not be entirely consistent between devices. In practice, we would very much like this not to be the case. Scientists and model developers should, ideally, be insulated from what would traditionally be considered engineering or computer science problems, and instead be allowed to focus upon their domain of specialization. Of course, this cannot always be the case, particularly given the pace of modern hardware development; however, there exists significant room for improving the state of existing simulation frameworks and design philosophies.

#### 1.3.2 Our Goal - Separating Form and Functionality

While these rapid increases in the power, data throughput, and flexibility of modern hardware are undoubtedly a step forward, they have come at a significant cost. These costs can be measured both in terms of the learning curve associated with being able to designed software effectively and the increased volume of code required to support a set of heterogeneous devices. As a result, many end users, often including engineers and domain scientists, are unnecessarily burdened by banal and pedantic implementation details, effectively wasting time on concerns which are orthogonal to their needs and goals. This significant problem provides a strong motivator for the development of computational frameworks which are able to abstract the design process of an end user, allowing them to focus on the accuracy and correctness of their work, while the framework itself is able optimize the underlying operations based on specific hardware details.

### 1.4 The Wasatch Framework

As stated previously, the goal of this thesis will be to extend a component, know as the "Expressions framework," of a computational fluid dynamics solver "Wasatch," to take advantage of a more diverse set of hardware targets, while obfuscating the implementation details and related considerations from end users. The Wasatch framework itself can be thought of as consisting of a variety of components, each of which exists at a different level. For the purposes of this discussion, the upper level component of this framework is responsible for providing MPI-based domain decomposition of a particular space we are simulating, an intermediate, "Expressions" layer, which is responsible for problem setup and solution within each MPI process, and a lower level "Spatial Operations" layer, which implements details related to specific mathematical operators.

## CHAPTER 2

### GRAPH THEORY AND APPLICATIONS

### 2.1 Overview

This chapter will be primarily concerned with introducing the required background material for discussion of the approach taken to algorithm decomposition and task scheduling in Chapter 3. This will begin by describing the ideas and machinery related to graph construction, and provide a generic description of the relevant algorithms used. Next, a more specific graph structure will be discussed, which will provide a basis for mapping between generic computational models and our graph construct. From there, we will discuss how the application of this structure to a problem set can provide valuable information, to include general model characteristics, such as identifying serialization points in our algorithm, and improving run-time scheduling behavior and resource management.

#### 2.1.1 Terminology

- Graph A graph is a set of elements, often written as G(V, E), where V is a set of vertices or nodes, and E is a set of edges, each of which connects two nodes. Edges themselves can be either directed, meaning that they are defined as having specific source and destination vertices, or undirected, in which case the edge indicates only that two nodes are connected. We say that an edge, e is 'incident' on a vertex pair,  $v_1$  and  $v_2$  if  $v_1$  and  $v_2$  are connected by e. For the purpose of this discussion, all graphs will be assumed to be directed; as such, we will write a given edge as  $e_{v_1,v_2}$ , where e is said to be an "out edge" of v1 and an "in edge" j of v2.

- Path A path through the graph is defined to be an ordered set of vertices and edges, which connect a specified source and sink, and written as p(source, sink).

- Cycle A cycle is a path within the graph such that the starting and ending vertices are equal. More specifically, if a cycle exists, then it indicates that for a given graph, G(V, E), there exists a path,  $p_i(source, sink)$ , where source = sink.

• Directed Acyclic Graph (DAG) - A DAG is a graph utilizing directed edges and containing no cycles.

#### 2.1.2 Algorithms

- Topological Sort Given a graph, G(V, E), the vertices are said to be topologically sorted if for every edge  $e_{v_i,v_j}$ ,  $v_i$  comes before  $v_j$  in the final ordering; the result is that we have a set of objects which can be processed without breaking any dependency relationships. The algorithm is run as follows:

- Let  $T_s$  be a first in first out (FIFO) queue representing our sorted list of objects, and  $T_u$  be a list of vertices with no incoming edges.

- Push all nodes with no incoming edges onto  $T_u$ .

- Pop a vertex,  $v_i$ , from  $T_u$  and push it onto  $T_s$

- For each out edge,  $e_{v_i,v_j}$ , color the edge as being processed. If  $v_j$  has no incoming edges which are unprocessed, push it to  $T_u$ .

- Repeat until there are no more vertices in  $T_u$ .

- $-T_S$  will now contain a topologically sorted list of vertices.

- Breadth First Search (BFS) Given a set of root, or starting nodes, which are each colored to indicate that they have been seen, and placed into a FIFO queue, the algorithm is run as follows:

- Pop a vertex,  $v_i$ , from the top of the queue.

- Perform any necessary work on  $v_i$

- For each out edge,  $e_{v_i,v_j}$ , check to see if  $v_j$  has been colored; if not, color it and push it to the queue.

- Repeat until the queue is empty.

- Depth First Search (DFS) Given a set of root, or starting nodes, which are each colored to indicate that they have been seen, and placed into a queue, the algorithm is run as follows:

- Pop a vertex,  $v_i$ , from the top of the queue.

- Perform any necessary work on  $v_i$

- For each out edge,  $e_{v_i,v_j}$ , check to see if  $v_j$  has been colored; if not, color it and call DFS on  $v_j$ .

- Repeat until the queue is empty.

## 2.2 DAGs as Computational Models 2.2.1 Motivation

DAGs have been studied extensively in their application to parallel computing problems, including: hardware task scheduling [11], [2], distributed computation [22], parallel compilers [23], [12], [20], numerical linear algebra [16], and even graphical programming tools [4]. As a result, the benefits of being able to represent a problem as a series of tasks and their dependencies within a DAG are significant. Such a representation can often provide a more intuitive understanding of the underlying structure of a computation or algorithm and is entirely open to automated inspection.

#### 2.2.2 Related Work

The process of utilizing software to decompose a computation's form into a representative DAG, and in turn generate an ordering of the problem's component tasks, is an idea that has been utilized in a number of different environments. One approach that shares similarities with the goals and application of work described in this paper, in that it is intended to facilitate development within the context of high-performance computing (HPC), is that of the Parallel Linear Algebra for Scalable Multicore Architectures (PLASMA) project. A collaborative effort between the University of Tennessee, the University of California Berkeley, and the University of Denver Colorado. It is targeted, specifically, at producing a framework that allows programmers to efficiently generate high-performance and portable code for computational linear algebra applications.

The PLASMA library was created in response to perceived limitations within existing linear algebra solvers, such as the linear algebra package (LAPACK) and its set of base linear algebra subprograms (BLAS) [9] on multicore architectures [1]. These libraries exhibit a number of undesirable implementation characteristics on modern systems, such as overuse of "fork" and "large stride" memory access patterns [14], which lead to poor scaling performance on current hardware. As one approach to overcoming these problems, PLASMA makes use of a tiling algorithms concept [5] for QR decomposition operations. This approach provides guidelines for a variety of algorithm requirements, but of particular interest to us is its notion of utilizing a DAG to order and execute tasks. In work done by Chan et al. [6], it was shown that one of the bottlenecks within the QR decomposition process can be reformulated to exhibit additional parallelism; this is achieved by reducing one of the intermediate matrix computations into a number of smaller block computations. The structure of the resulting computation can be well represented as a DAG and exposes a number of tasks which can be executed asynchronously and out of order. In [5], it is stated that this idea of dynamic scheduling with out-of-order execution was then applied as the basis for obtaining a fine-grained algorithm for QR factorization.

In the tiled algorithm approach developed for PLASMA, a multicore blocking algorithm is decomposed into a DAG describing the dependency structure between each block operation. Using this graph representation, it is possible to directly determine execution/scheduling dependencies of all component tasks, and identify elements forming the critical path of the computation. The result is a framework in which component tasks can be scheduled asynchronously using a simple priority scheduling policy, based on the type of task and its location along the critical path. This, in turn, results in an algorithm where idle time is almost completely eliminated and which adapts, in a basic way, to available computing resources [5].

The process of setting up a program to be able to utilize this tasking framework requires some programmer assistance. First, functions must be converted such that all arguments are removed from the function signature and redeclared as local variables; these variables are then accessed later through an unpacking macro. Next, function calls are replaced by calls to "insert\_task()," which must provide a pointer to the function being called, the parameters being passed, their size, and a type identifier the specifies a usage context; usage contexts are specifically defined as "VALUE," "INPUT," "OUTPUT," and "INOUT." At run time, tasks are inserted into the scheduler in preparation for execution, and individual tasks are removed from the queue and executed by worker threads based on their priority and declared INPUT values; for a more detailed treatment, see [16].

Unlike more traditional uses for task scheduling involving DAGs, such as hardware task scheduling [11], the tile-based QR algorithm only stores a windowed subset of the original DAG at any given time. The authors assert that this is due to the extremely fine granularity of individual tasks, which results in graph structures that grow rapidly with problem size.

In contrast to this extremely fine-grained behavior, other frameworks, such as "Uintah," a multiphysics HPC framework written at the University of Utah [8], utilize DAG-based scheduling to facilitate execution of asynchronous MPI-based tasks. In this context, it is possible that each task may be an entire subroutine which must be run on a "physical" piece of a decomposed domain; in such a framework, MPI tasks themselves may consist of finer grained DAG-based computations.

The expressions framework targets a space that is not focused on either the highly targeted use cases of a library like PLASMA, or the multinode monolithic task scheduling of a library like Uintah. Rather, the expressions library is focused more on creating a development environment in which individual tasks are run on a single node, may differ substantially in terms of computational requirements and resource usage, and which utilize graph structures that can be self-assembling, rather than explicitly directed. In this case, while graph structures can become quite large within the expressions context, they do not exhibit the exponential node growth corresponding to extremely fine task scheduling problems faced by PLASMA. The complete structure of the task graph may be kept in memory during the course of an execution; as a result, there is a great deal more flexibility with respect to analysis of the DAG and more care can be taken with respect to the scheduling of tasks.

#### 2.2.3 The Expressions Context

While significant work exists discussing the variations of this type of process scheduling model and its application to known task sets, [13], little work has been done with respect to the creation of such task sets from an underlying algorithm or model description. In [19], the authors introduce a novel method for the application of the graph-based methodology, described above, to the decomposition of problems found in multiphysics HPC, and in turn building consistent solution algorithms. In the outlined framework, the physical models are reduced to a set of individual tasks, each of which declares its data dependencies to sister tasks; from these task declarations, a DAG is built representing the overall structure of the computation. By processing the resulting graph, it is possible to develop a variety of consistent algorithms for a given model.

To illustrate the general principal, suppose that we have a model describing some physical process. At a basic level, this abstraction will consist of some number of variables or objects, and a series of operations which will act on these objects to produce some type of result. In the simplest case, we can imagine a function which computes the sum of two objects, F(A, B) = A + B. This system will consist of three data objects: A, B, and their sum S = A + B, as well as a function F, which requires A and B and produces S. If we generalize this notion to include any number of functions and objects, then we can, for a consistent model, generate an ordering to any valid set of operations such that their data requirements are satisfied and we obtain the desired solution(s).

#### 2.2.4 The Dependency Graph

In general, there are two distinct methods which are commonly used to represent a task set as a graph. The first, is to construct what is known as a dependency graph, which as its name suggests, describes the dependencies of each task using edges. What this means, is that the root nodes at the "top" of the dependency graph will be the last set of tasks which will be able to run. This is due to the fact that each edge,  $e_{v_i,v_j}$  in the dependency graph will indicate that  $v_i$  is a consumer of  $v_j$ , and therefore, the only root nodes in the graph will be those who have no consumers. The dependency graph represents our intuitive understanding of how a series of operations forming an algorithm are connected and will serve as an initial step in the process of translating a real model description into its graph representation.

#### 2.2.5 The Task Graph

The second method, which is often better suited to the idea of the graph as the basis for implementing the model, is know as the "task graph." The task graph differs from the dependency graph in that each edge,  $e_{v_i,v_j}$ , of the task graph has been reversed from its equivalent edge,  $e_{v_j,v_i}$ , in the dependency graph. In this representation, the root nodes of the graph will be those which have no incoming edges, and in turn have no initial prerequisites for execution. The task graph represents the effective "flow" of an algorithm and its direction of execution; it will be used extensively when we discuss ideas related to the scheduling of individual tasks in Section 3.

## 2.3 Extracting Information 2.3.1 Task Granularity

Here, it is worth pointing out that the notion of what constitutes a task has purposefully been left fairly generic. Within the context of a software implementation, a task itself may range from a single assembly instruction, all the way to the execution scope of an entire model, although, in almost all cases, either extreme would not be very useful. In general, we can package as many tasks as required into a single super task, adjusting the size of the resulting graph and the amount of work done for a given vertex.

#### 2.3.2 Graph Introspection

In addition to the direct benefit of using a graph-based approach for generating algorithms to solve a specific model, the structure of the graph itself can provide us insight into a number of the theoretic structural properties of a model. Specifically, after a bit of relatively straightforward analysis, it will allow us to estimate properties such as the percentage of the model which can be parallelized and the minimum total execution time. These will be given without proof; for a more detailed treatment, see Sinnen [22].

#### 2.3.3 Bounds on Execution Time

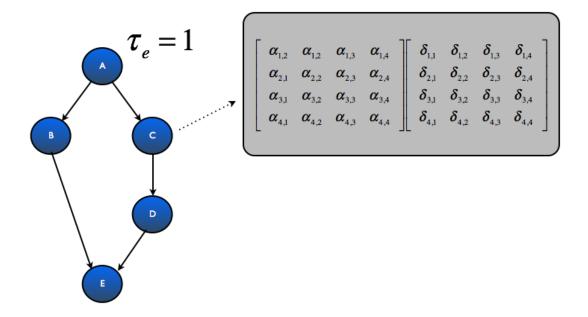

The minimum execution time for a graph, given a fixed set of hardware, can be obtained through examination of all sequential computations within a graph and then isolating the longest. To see why this is correct, we define the following:

- Schedule A schedule is a set vertex execution ordering. We will call a schedule "consistent" if it obeys all dependency relationships of a graph

- Path Cost For a given DAG, G(V, E), and a path p(source, sink), the total cost of executing p is given as:

$$\sum_{e_i \in p} t_e(e_i) + \sum_{v_i \in p} t_e(v_i) \tag{2.1}$$

where  $e_i$  and  $v_i$  are the edge and vertex components of the path.

• Critical Path - For all paths within the graph, the node(s) which have the maximum path cost is known as the critical path.

From our definition of a critical path, we can make two valuable observations. First, any critical path within a graph will begin at a root node and terminate at a leaf node. Intuitively, this property seems reasonable; however, it is not entirely obvious. The truth of this statement can be obtained by supposing that you have a critical path whose source node is not a root and from there proceeding to a contradiction. The second observation is that the critical path provides a lower bound on the time required to execute any feasible graph schedule. This property follows from the principal that in a task graph, edges signify a dependency relationship, and therefore, computation along a path must be sequential. If this is the case, then a critical path will represent the greatest set of sequential, or serialized tasks.

#### 2.3.4 Parallelization

While the above discussion yields insight regarding absolute execution times of our graph, it does not tell us anything about the requirements for approaching this minimum bound. In an extreme case, we could potentially have an entirely serial graph, such as a single chain of of n tasks, where the task  $1 < k \leq n$  depends on task k - 1. In such a case, it would be detrimental to allocate any additional resources for task execution, or attempt to perform any detailed introspection of the graph's properties. In less extreme situations, it may be the case that we could expect to see no benefit from scheduling on more than two or three processors. It turns out that we can again utilize the structure of the graph to produce a theoretic bound on potential gains, given additional processing resources. Under the assumption of minimal communication costs, we define the following properties:

- Single Processor Time  $\tau_1$  This is the total time required to execute a graph, given a single processor.  $\tau_1 = \sum_{i=1}^N \tau_e(n_i)$

- Infinite Processor Time  $\tau_{\infty}$  This is the total time required to execute a graph, given unlimited processing resources. This value is equal to the maximum finishing time of all nodes.

- Speedup  $S_n$  This is the reduction in the time taken to execute a graph when utilizing n processors, given as  $\frac{\tau_1}{\tau_n}$ . Of particular interest is the speedup value for  $n = \infty$ , or  $S_{\infty} = \frac{\tau_1}{\tau_{\infty}}$ .

The value  $S_{\infty}$  represents the maximum theoretic speedup we can obtain by allocating an infinite number of resources toward the execution of our graph. Using this value, we can compute an "Amdhal score,"  $P(G) = \frac{1-\frac{1}{S_{\infty}}}{1-\frac{1}{N}}$ , which represents the percentage of the graph which is parallelizable. This score provides a theoretical limit to the performance improvements we can expect from a given graph and provides us with a hard limit as to the number of resources which can be legitimately allocated toward a specific problem.

## CHAPTER 3

## FRAMEWORK EXTENSIONS

## 3.1 The Expressions Library 3.1.1 Overview

The expressions library is a framework designed to elevate the development level of an end user to the point where they are able to write their code with a structure similar to that a high-level interpreted language, such as Matlab, while at the same time being able to obtain scaling performance required by traditional high-performance computing applications. This is accomplished through a high-level Domain Specific Language called NEBO (not covered in this work), and a design paradigm which allows an end user to describe processes in terms of generic operators and their data dependencies. Once an end user has used this system to described their computation, the expressions framework takes the abstraction and automatically constructs an appropriate algorithm based on available resources.

In the usage context for this work, the expressions library serves as an intermediate layer between the Uintah/Wasatch component described in (1.4), responsible for domain decomposition and MPI message passing, and the spatial operator component, responsible for the abstraction of data fields and the implementation of mathematical operators (Figure 3.1).

#### 3.1.2 Concepts and Terminology

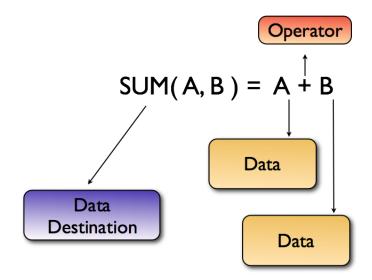

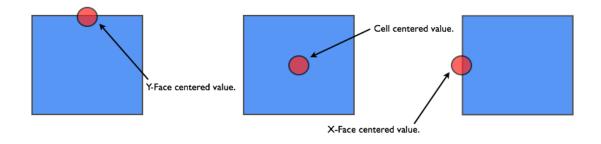

- Expression An expression is a abstract representation of a mathematical operation. Expressions expose their purpose and requirements through a set of interface methods given below. The basic concept of an expression is illustrated in Figure 3.2.

- advertise\_dependents() Returns a list of all other expressions which are required for this expression to be successfully computed; this allows us to determine ordering requirements of the model before execution.

- bind\_fields() Retrieves objects representing base fields which are consumed and computed within the evaluate(); this connects the logical operation with

Figure 3.1. Framework component diagram.

Figure 3.2. Example of a basic expression.

the physical resources it requires and allows resources for each expression to be allocated and bound independently.

- bind\_operators() Obtains objects representing various mathematical operations (ex. Div, Grad, etc.) used by the expression.

- evaluate() Executes user-defined operations forming the core work of the ex-

pression; note that the internal contents can be as fine or coarse as desired.

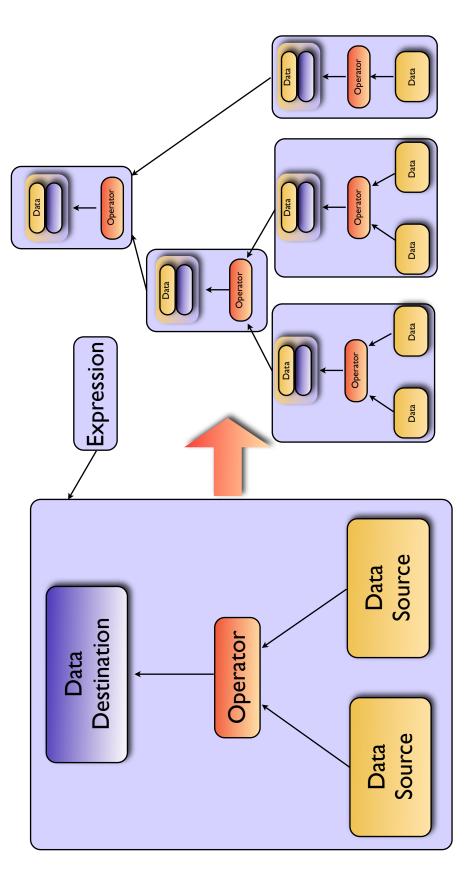

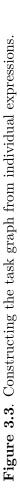

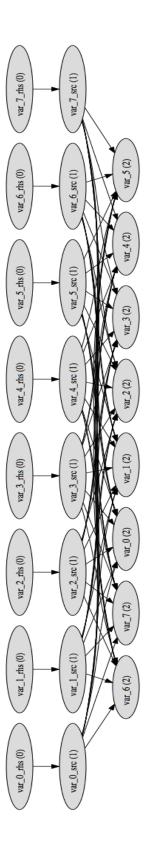

- Expression Tree A class object responsible for analyzing collections of individual expressions, exposing the overall structure of the computation, and ensuring that the structure is logically consistent. The expression tree is used to construct a dependency graph, described in Section 3.2; in this representation, graph nodes represent the expressions themselves, and directed edges express the data dependencies between expressions (Figure 3.3).

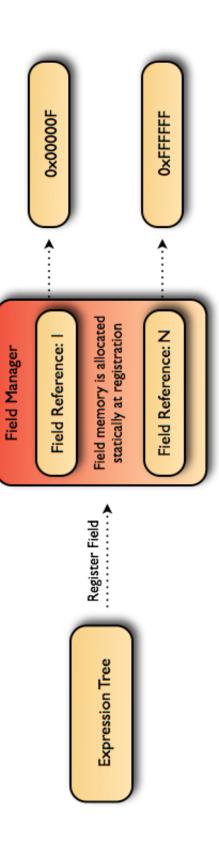

- Field Manager A class object responsible for managing field memory for the Expression Tree. This class provides interface methods to register, allocate, migrate, and deallocate all memory resources associated with a specific field.

- Task Scheduler A class object responsible for determining execution behavior based on a dependency graph; in general, this includes creation of either a static or dynamic schedule for each task, which preserves dependency requirements, and developing a variety of performance metrics for the overall computation.

#### 3.1.3 Implementing an Expression

The process of defining a task, or "expression," simply requires an end user to inherit and implement the interface contract described above. As an example, suppose we are computing the Heat Equation, (Equation 3.1).

$$\partial \delta T \delta t = -\frac{1}{\rho c_p} \partial \cdot q + \frac{1}{\rho c_p} S_T \tag{3.1}$$

$$q = -\lambda \nabla T \tag{3.2}$$

One of the operations required is to compute the gradient of the temperature, an operation which requires a scalar field representing the temperature, "T," and a gradient operator. To implement the required interface methods, we can first create an expression that will compute the gradient of "T," in this case, called "GradTExpr," and set it to require another expression which represents a temperature field (Figure 3.4). This will allow the expression tree to build a list of dependencies for this operator and ensure that all required fields, in this case "tempT.," are available before attempting to evaluate this expression.

Note here that our expression for temperature, "tempT\_," will not possess any dependencies or perform any computation. The element is an explicitly defined source term, which must be supplied by the caller, and will in turn have an initial condition and be

```

template < typename GradOp >

void GradTExpr <GradOp >::

advertise_dependents(Expr::ExprDeps& exprDeps){

exprDeps.requires_expression(tempT_);

}

```

1

2

3

4

5

4

#### Figure 3.4. Advertise dependents implementation.

updated during successive problem iterations; these terms will become the root nodes of our execution graph

Next, we implement the bind operator method (Figure 3.5) and bind fields (Figure 3.6) functions, which will fetch the required gradient operator and obtain a reference to the source field, "tempT\_," for this expression. Finally, we can implement the evaluate method, which will apply the gradient operator to our temperature field and place the result into the value field of our expression (Figure 3.7). In this fashion, we are able to completely describe the desired operations and their data dependencies, without any specialized knowledge of available hardware resources, threading model, or implementation details.

#### Constructing the Task Graph 3.1.4

After specifying the behavior of each expression for a given model, the expressions are passed as a collection to an expression tree. The expression tree will then parse the expression set and construct a task graph, as a "Boost Graph" structure [21], where individual

```

template < typename GradOp >

1

void GradTExpr<GradOp>::

bind_operators(const SpatialOps::OperatorDatabase& opDB){

2

3

4

gradOp_ = opDB.retreive_operator<GradOp>());

5

}

```

#### Figure 3.5. Bind operators implementation

```

template < typename GradOp >

2

void GradTExpr <GradOp >::

3

bind_fields(const Expr::FieldManagerList& fml){

temp_ = &fml.template field_manager<ScalarField>().field_ref(tempT\_);

5

}

```

Figure 3.6. Bind fields implementation.

```

template < typename GradOp >

1

void GradTExpr <GradOp >::

2

3

evaluate(){

4

gradOp_->apply_to_field(*temp_, this->value());

5

}

```

Figure 3.7. Evaluate method implementation.

vertex objects hold a reference to the base expression and related meta information, and edges represent the data dependencies between expressions. This can be done through explicit dependency specification, or by having the expressions themselves advertise their dependents and have them dynamically inserted into the expression tree. The second case, with dynamic insertion, yields a very useful method for automatic algorithm construction, in that the compute ordering is not need to be specified explicitly, but rather can be deduced by the expression tree at run time [19].

Once all expressions have been accounted for, the expression tree will perform error checking to ensure that the model does not contain circular dependencies, and register all required fields with an appropriate field manager; as a useful side-effect of this construction process, we are able to determine the problem's memory requirements before execution. At this point, the solution algorithm and computational resources required for the problem specification will have been determined, and the graph is ready for execution.

Using the example of the heat equation, one possible implementation will yield the directed graph seen in (Figure 3.8). Once assembled, the dependency graph contains all information required to represent the structure of the desired computation. After being handed to the task scheduler, this structure will form the basis for constructing an algorithm whose output is the solution to the heat equation.

#### 3.1.5 Design Goals

The primary focus of the work described by this thesis has been to extend the functionality of the Expressions Library to utilize both existing and future acceleration technologies, without requiring an end user to have hardware specific knowledge. To support this larger aim has required significant modification to a variety of framework systems, which can be summarized a follows:

- Implementation of a flexible task scheduling system, capable of utilizing a variety of scheduling algorithms, ranging form simple to complex, depending on available hardware and software resources. To facilitate the necessary flexibility, a task scheduler should be able to exert a high-level of control over the execution process and associated resources, to include:

- To reallocate threading resources between task and operator level execution.

- To determine scheduling priorities for individual expressions based on available hardware and graph meta information.

- To assign tasks to arbitrary hardware targets dynamically.

Figure 3.8. Visualization of a potential task graph for the heat equation.

- To ensure data availability between expressions which are computed on different hardware devices.

- Modification of existing field managers to allow for delayed memory allocation, additional allocation targets based on available hardware, and support for migration of fields between devices.

- Extension of the Spatial Field library to support field consumption from a variety of devices, and transparent operator selection based on the device on which the operation will be computed (Section 4.2).

#### 3.1.6 A Flexible Scheduling Model

To support an execution model where we may wish to utilize a variety of scheduling algorithms, each with potentially widely varying behavior, the scheduler itself is treated as a component of the execution framework, rather than a static implementation. Using a standard contract model [17], where base functionality is defined and inherited by specific scheduler implementations, we are able to test and change schedulers easily without refactoring core components. During the construction phase of an expression tree, the scheduler is built and then handed the dependency graph for the simulation model; later, when the "execute\_tree" method of the expression tree is called, it will notify the scheduler to perform any requiring preprocessing, and finally to run the algorithm.

The scheduler itself is now left with all available information about the operations and constraints required to reproduce the desired model. From the most basic perspective, it could simply sort the task set topologically and execute them in order. However, in most cases of interest, this will be insufficient, and we will want to develop an implementation that optimizes for speed, resource utilization, or some combination of both. By providing a simple interface contract to the scheduler used by the expression tree, while at the same time exposing as much control and information as possible to the scheduler's internals, we allow for new scheduling models to be rapidly prototyped as new components become available. Using this approach, we can integrate existing hardware accelerators, such as GPUs, seamlessly into the framework, while at the same time providing a foundation capable of supporting new devices as needed.

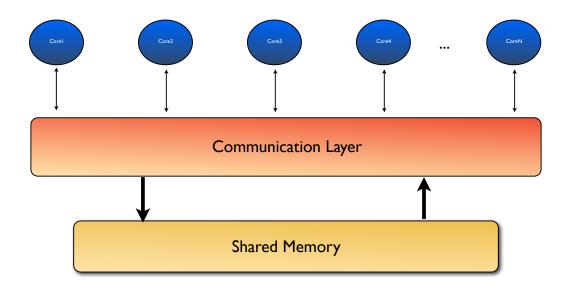

#### 3.1.7 The Priority Task Scheduler

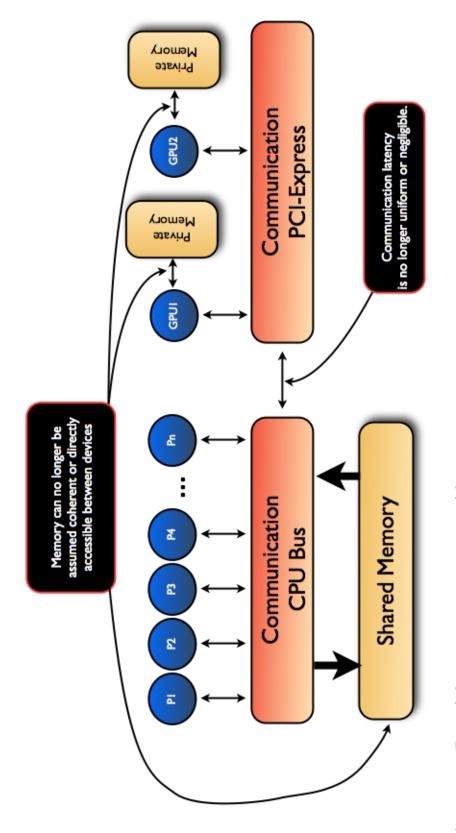

One of the most straightforward scheduler implementations is used when executing on a target system in which we assume a uniform, shared memory architecture with full communication interconnects. More specifically, this means that all processing devices are homogeneous, the cost of assigning a specific task to a hardware device is equal for all devices, and that communication between devices is negligible (Figure 3.9). These assumptions are reasonable in the context of our expression level process, running on a single computing node, where we leave the task of binding threads to processor cores to the operating system, and neglect latency relate to contention of the memory bus. Under this restricted model, we are left with the responsibility of ensuring that individual expressions are scheduled for execution in a near optimal fashion, based on execution times and graph layout.

#### 3.1.8 Graph-Based Execution

As one of our requirements for the priority task scheduler, we have said that it should be able to generate task priorities based on both executing timings and the general structure of the graph. This implies that the scheduler needs to be able to examine and reason about the task graph and be able to maintain/update information stored on its vertices. To support this behavior, the scheduler assigns priorities to each node in the graph and during its setup phase, based on its depth in the graph and the total number of other tasks which consume it (Figure 3.9). Later, during execution, each task will be timed and have the result added to a moving average, providing an estimate for its likely execution time on successive iterations.

After successive iterations of the task graph, the scheduler is able to improve on its initial priority estimate, by using the measured execution times to increase priority values for heavier weight tasks. For simulations where the graph may be executed thousands, or hundreds of thousands of times, this design has the effect of heavily prioritizing tasks

Figure 3.9. Simplified communication memory model, multicore CPU.

located near root nodes, and those which form serialization points within the graph.

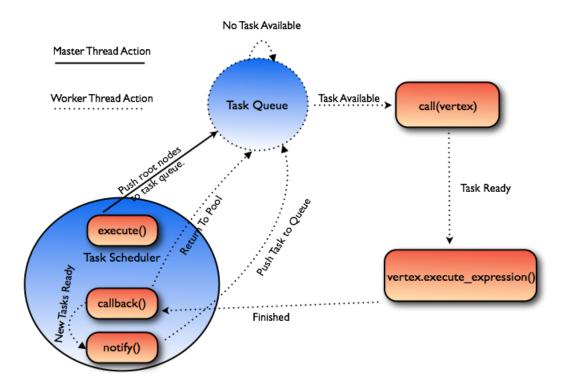

### 3.1.9 Task Dispatch Model

Execution of a task graph is initiated in a fairly direct manner. We first push all root node vertices, defined to be those with no "out" edges (dependencies), to the task queue for execution. The perthread process of acquiring and dispatching additional tasks occurs using the following execution callback model (Figure 3.10):

- A worker thread will select a vertex from the task queue and call through the task scheduler to prepare for the vertex's expression execution.

- The expression is executed.

- The worker thread will call back to the scheduler and inform it that the expression is done.

- The scheduler will notify all consumers of the finished expression that one of their dependencies has become available.

- If any of the dependency counters on the notified vertices reaches zero, they will indicate to the scheduler that they are in a ready state and will be added to the task queue.

Figure 3.10. Priority Task Dispatch Model.

• The process repeats until all vertices have been exhausted.

Ignoring function call overhead, the total time required for a worker thread to execute an expression is bounded by (Equation 3.3).

$$t_{V_i} + (t_l + t_e) \cdot |V_{V_i}| \tag{3.3}$$

$$t_{V_i} \gg (t_l + t_e) \cdot |V_{V_i}| \tag{3.4}$$

where  $V_{V_i}$  is the set of all dependent vertices of the  $i^{th}$  vertex, and  $t_{V_i}$ ,  $t_l$ , and  $t_e$  are the times required to execute the expression, look up a dependency target, and update the target, respectively. For situations where task granularity is not too fine, meaning that work done by each expression is much greater than the time required to examine its incident edges (Equation 3.4), this method of scheduling has been shown to produce negligible overhead (Chapter 4).

In situations where expression granularity is extremely fine and exhibits a high degree of dependency coupling, this scheduling method may not be suitable. In such situations, where executing "on top" of the graph itself produces unacceptable overhead, a better solution may be to preallocate all necessary fields, build a topologically sorted list from the task graph, and execute from a FIFO type queue structure.

#### 3.1.10 Improving Resource Utilization

Assuming the basic homogeneous scheduling model described above, we can begin to examine how to better exploit available information to improve performance, and look to extending the scheduler's functionality to support additional hardware targets. Within the context of the larger framework, this may include reallocation of available threading resources based on the task graph's structure, improved memory utilization, or other intelligent decision making related to consumer availability and hardware assignment.

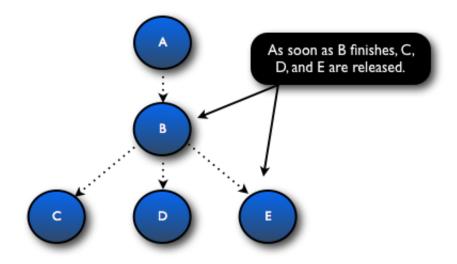

#### 3.1.11 Memory Resources

One immediate advantage of having execution take place on the task graph is that we are presented with a direct method for determining when the resources associated with an expression will no longer be used. As the edges of our graph represent data dependencies, then we know that for any given vertex, its resources may be released when each vertex on one of its out edges has been executed. As a result, we can refer to any vertex node  $V_c$ , for which another vertex  $V_d$  is a dependency, as a consumer of  $V_d$ ; by keeping track of how many consumers a given vertex has, and decrementing that counter each time one of those consumers finishes execution, we are able to free a dependency's resources as soon as they have been fully consumed. This is very useful property, as we are only required to keep an exact working set in memory at any given time (Figure 3.11).

While the graph-based approach itself provides a direct method for determining which vertices no longer require resources, early field manager implementations did not provide a method for deallocating a field without removing its registry entry (Figure 3.12). As a core component involved in registering, allocating, and retrieving memory resources related to all fields, this inflexibility would prove to be too restrictive, not only in the context of field persistence, but also with respect to field allocations on external devices. As a result, the existing field managers were modified to store a structural interface to an underlying field, allowing for a variety of logical states, and an extensible list of allocation targets.

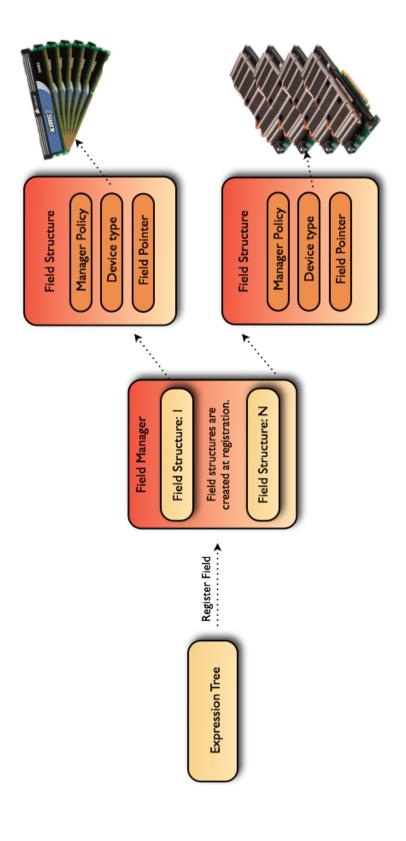

The rearchitected field manager system assigns a field structure to each registered field, which will exist throughout the lifetime of the field manager. The field structure itself maintains a variety of meta information related to the field, and methods for interacting with it. Meta information includes the logical state of the field, including whether or not it is currently allocated, if it contains coherent information, the type of memory management scheme associated with the field, and the type of device it resides on. Additionally, the field structures support methods for referencing, freeing, and modifying the behavior of their underlying fields. This modified behavior is exhibited in Figure 3.13.

Figure 3.11. Dependency graph illustrating the deallocation of a fully consumed expression.

In the modified system, the specifics of field allocation are changed significantly. Unless a field is specifically tagged to be "static," meaning that it is required to exist and be available at all times during the life of the field manager, fields themselves are not allocated until their first access. Additionally, nonstatic fields are allocated from a central memory pool, and new memory is allocated only when the pool itself cannot provide the requested field type. Later, when a dynamic field is released back to the system, rather than being freed, it is simply returned as a resource to the memory pool. In this manner, not only is it possible to reduce memory consumption through "just in time allocation" and maintaining a minimal working set, but system call overhead associated with memory allocation is entirely removed in at most one execution of the graph.

In conjunction with the much improved usage behavior described above, the modified field manager architecture also offers the flexibility to modify management behavior automatically. This includes basic modification of the persistence flags associated with a field to full reassignment of the field to an alternate manager policy. This can be useful in cases where an end user may wish to "lock" some intermediate field after a number of iterations to sample, or spot check the model's behavior; in such a case, the user would set a persistence flag through the expression tree which would then be propagated to the task scheduler and down to the field managers. On the next model iteration the field of interest could be sampled, verified, and unlocked.

Figure 3.12. Initial field manager implementation.

Similarly, the scheduler itself may decide that an expression would be better suited to execute on some type of coprocessing device, such as a GPU, and in turn notify the field manager to update the memory policy associated with fields computed by the given expression. The field manager would then automatically ensure that any data associated with the field was automatically propagated to the proper GPU device, and the previously allocated fields would be returned to the memory controller. On the following call to execute the expression, the expression's operators will be remapped based on the updated hardware and execution will continue.

The complexity associated with introducing the described memory saving operations into our priority scheduler is equivalent in both time and space requirements as to what is required to support "on graph" execution. Each graph vertex is required to maintain a list of consumer vertices, when the vertex itself finishes, each consumer vertex will be notified, and when their consumer counts reach zero, they will have their field resources released.

#### 3.1.12 Threading Resources

Just as the expression library is capable of exploiting task level parallelism, by decomposing a model specification and examining the related execution dependencies, it is also possible to expose inherent parallelism within mathematical operators or over their given domain. As a simple example, we can imagine an operator performing some number of direct pointwise computations on an NxN field; such an operator could, in many cases, compute many of these pointwise values for each computation simultaneously or perhaps compute the different operations in parallel.

Although not fully described here, this type of memory-based operator decomposition is a significant part of the spatial ops/NEBO framework, which has complete discretion in how an operator is implemented and as a result exploits various types of parallelism inherent to it. Given this notion, the spatial operators have their own threading resources in the form of a FIFO thread pool. As the internals of the operator thread pool are fully accessible by the task scheduler, this provides us with an additional degree of freedom in our ability to address potential computation bottlenecks.

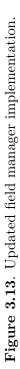

Of course, regardless of logical differences, both libraries share the same underlying resources; therefore, at the thread level, if the total threads allocated between the operator and expression thread pools exceed the available hardware resources, workers from each thread pool will be competing for processor time. To avoid such situations, we would like the task scheduler to, at a minimum, allocate a number of total worker threads such that we force as few context switches as possible. Accomplishing this is simple, as we can supply information regarding the total number of available processing resources to the scheduler, and it can determine a static ratio for how they should be allocated to each thread pool. If we imagine an idealized a situation, in which we have three total threads and three available tasks, each completely parallel at either the task or operator level, this trade off can be observed in Figure 3.14. However, this is rarely the case, and instead we see direct benefits to allocating threads in less extreme ratios. Once we have this notion of the task scheduler acting as a managing entity for multiple levels of parallelism, it affords us additional possibilities for performance improvement.

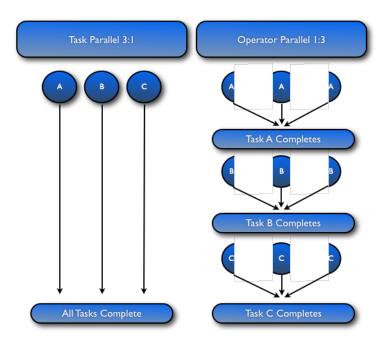

Suppose we wish to do better than static pool sizing, but rather, we would like the task scheduler to adjust the total number of workers assigned to each pool based on analysis of the task graph and real-time feedback during execution. In this case, our graph-based algorithm formulation will again prove to be extremely useful. Recalling the notion of parallelization scoring related to Ahmdal's Law, from (Section 3.2.2), we know that given a reasonable estimation of execution times for each vertex within our task graph, we can provide a good approximation for the maximum potential speedup and task level parallelism. This implies that as we progress through successive graph iterations, we can reasonably estimate the benefit of migrating threading resources between thread pools.

Figure 3.14. Idealized multilevel parallelism.

As an example, suppose that we are executing the task graph shown in Figure 3.15, and that each node of our system contains 8 processor cores. From section 3.2.2, we can compute the single and infinite processor case timings as  $\tau_{one} = 5$ ,  $\tau_{inf} = 4$ , which yields a maximum theoretic speedup of 1.25. Therefore, in this case, it would not be worthwhile to allocate more than 2 threads toward the execution of our task graph; however, if we imagine that the underlying tasks each to be large matrix matrix multiplies, then we could potentially obtain a 6 or 7 times speedup by pushing all our threading resources into the operator thread pool.

## 3.1.13 The "Hybrid" Task Scheduler

Given the general priority scheduler, along with the selection of framework tools described above, our next task is to develop a scheduler that its capable of reasoning not only about task ordering, but also with respect to the assignment of tasks to devices other than the CPU. This process introduces a good deal of complexity into both the process of graph analysis and the execution time responsibilities of the task scheduler. Not only does it break our simplified memory model (Figure 3.16), used to construct the priority task scheduler, but it injects ambiguity into the process of assigning execution timings, generating parallelization scores, and the notion of a field residing in a single location. The following is a basic outline of the major complications involved in allowing for individual

Figure 3.15. Example task graph analysis to determine thread allocation. Note: execution times are all normalized to 1.

tasks to be allocated across heterogeneous hardware.

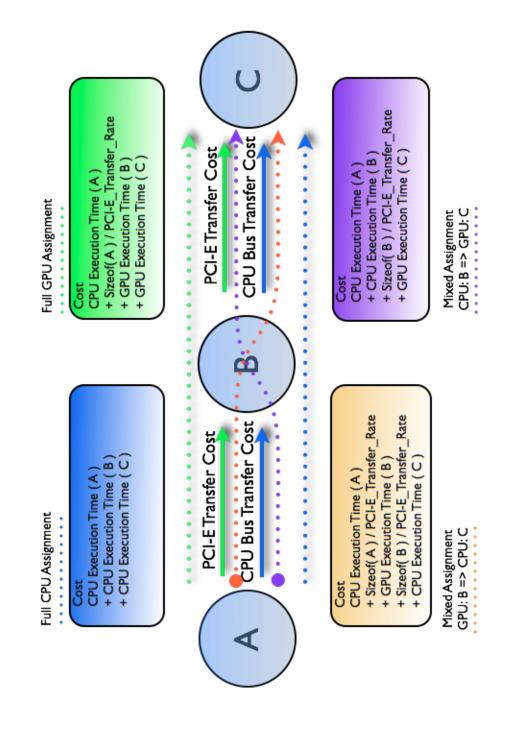

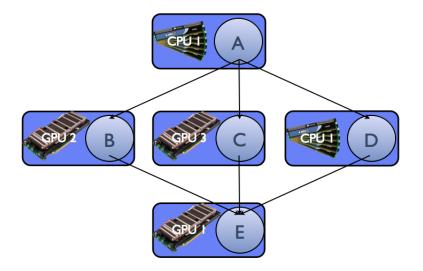

Scheduling of a task to a hardware device can no longer be considered to have a uniform cost. This is because there are tangible differences between the data transfer costs associated with differing communication layers. This issue is further compounded by the fact that in many cases of interest, the cost associated with a data allocation is not necessarily unidirectional; in a general sense, an expression will consume N data fields and produce M data fields, resulting in a total data transfer to and from a nonlocal computation equal to  $(N + M) * field\_size/transfer\_rate$ . This additional timing parameter can be thought of as applying an "edge scheduling" cost, meaning that we are, in effect, faced with a problem of scheduling paths in the graph, rather than simply tasks (Figure 3.17).

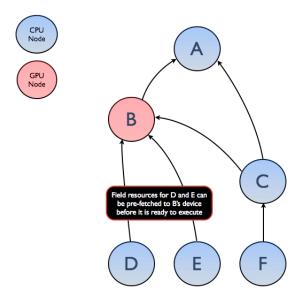

Acquiring representative timings for the execution of individual tasks requires us to make a determination as to which device a given task will execute on, including the transfer times described above. This implies that given a variety of coprocessor devices, we will need to maintain device specific timings for each individual task, along with a generic transfer timing parameter. Furthermore, without prior knowledge or hints as to task execution timings, we will need to execute each task at least once on every device in order to build its timing profile.