# LOW OVERHEAD DATA RACE DETECTION TECHNIQUES FOR LARGE OPENMP APPLICATIONS

by Simone Atzeni

A dissertation submitted to the faculty of The University of Utah in partial fulfillment of the requirements for the degree of

Doctor of Philosophy in Computer Science

School of Computing

The University of Utah

December 2017

Copyright © Simone Atzeni 2017 All Rights Reserved

### The University of Utah Graduate School

#### STATEMENT OF DISSERTATION APPROVAL

The dissertation of <u>Simone Atzeni</u>

has been approved by the following supervisory committee members:

| Ganesh Gopalakrishnan , | Chair(s)   | 08/10/2017  Date Approved |

|-------------------------|------------|---------------------------|

| Zvonimir Rakamarić,     | Co-Advisor | 08/15/2017  Date Approved |

| Dong H. Ahn ,           | Member     | 08/07/2017  Date Approved |

| Hari Sundar ,           | Member     | 08/10/2017  Date Approved |

| Ryan Stutsman ,         | Member     | 08/10/2017  Date Approved |

by <u>Ross Whitaker</u>, Chair/Dean of the Department/College/School of <u>Computer Science</u> and by <u>David B. Kieda</u>, Dean of The Graduate School.

#### **ABSTRACT**

High Performance Computing (HPC) on-node parallelism is of extreme importance to guarantee and maintain scalability across large clusters of hundreds of thousands of multicore nodes. HPC programming is dominated by the hybrid model "MPI + X", with MPI to exploit the parallelism across the nodes, and "X" as some shared memory parallel programming model to accomplish multicore parallelism across CPUs or GPUs. OpenMP has become the "X" standard de-facto in HPC to exploit the multicore architectures of modern CPUs. Data races are one of the most common and insidious of concurrent errors in shared memory programming models and OpenMP programs are not immune to them. The OpenMP-provided ease of use to parallelizing programs can often make it error-prone to data races which become hard to find in large applications with thousands lines of code. Unfortunately, prior tools are unable to impact practice owing to their poor coverage or poor scalability.

In this work, we develop several new approaches for low overhead data race detection. Our approaches aim to guarantee high precision and accuracy of race checking while maintaining a low runtime and memory overhead. We present two race checkers for C/C++ OpenMP programs that target two different classes of programs. The first, ARCHER, is fast but requires large amount of memory, so it ideally targets applications that require only a small portion of the available on-node memory. On the other hand, SWORD strikes a balance between fast zero memory overhead data collection followed by offline analysis that can take a long time, but it often report most races quickly. Given that race checking was impossible for large OpenMP applications, our contributions are the best available advances in what is known to be a difficult NP-complete problem.

We performed an extensive evaluation of the tools on existing OpenMP programs and HPC benchmarks. Results show that both tools guarantee to identify all the races of a program in a given run without reporting any false alarms. The tools are user-friendly, hence serve as an important instrument for the daily work of programmers to help them

identify data races early during development and production testing. Furthermore, our demonstrated success on real-world applications puts these tools on the top list of debugging tools for scientists at large.

# **CONTENTS**

| AB  | STRACT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | iii                                                                       |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| LIS | ST OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | viii                                                                      |

| LIS | ST OF TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ix                                                                        |

| AC  | CKNOWLEDGMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | X                                                                         |

| СН  | IAPTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                           |

| 1.  | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1                                                                         |

|     | <ul> <li>1.1 Thesis Statement</li> <li>1.2 Background</li> <li>1.3 Contributions of the Dissertation</li> <li>1.4 Organization of the Dissertation</li> </ul>                                                                                                                                                                                                                                                                                                                                | 2<br>4                                                                    |

| 2.  | EFFECTIVELY SPOTTING DATA RACES IN LARGE OPENMP                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                           |

|     | APPLICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6                                                                         |

|     | <ul> <li>2.1 Introduction</li> <li>2.2 Approach</li> <li>2.2.1 Static Analysis Phase</li> <li>2.2.2 Dynamic Analysis Phase</li> <li>2.3 Evaluation</li> <li>2.3.1 OmpSCR Benchmark Suite</li> <li>2.3.2 AMG2013 Case Study</li> <li>2.3.3 ARCHER Resolves Real-World Races</li> <li>2.4 Related Work</li> <li>2.5 Discussion</li> <li>2.5.1 Latest OpenMP Specifications</li> <li>2.5.2 Compiler Optimization Flags</li> <li>2.6 Conclusions and Future Work</li> <li>2.7 Summary</li> </ul> | 9<br>10<br>11<br>12<br>13<br>18<br>19<br>20<br>21<br>22<br>22<br>23<br>23 |

| 3.  | AN OPERATIONAL SEMANTIC BASIS FOR OPENMP RACE ANALYSIS                                                                                                                                                                                                                                                                                                                                                                                                                                       | 25                                                                        |

|     | 3.1 Introduction 3.2 Background 3.3 Operational Semantics 3.3.1 Predicates and Conventions 3.3.2 Offset-Span Labels 3.3.3 System State 3.3.4 Helper Functions and Predicates 3.3.5 Operational Semantics Rules                                                                                                                                                                                                                                                                               | 27<br>29<br>33<br>33<br>34<br>36                                          |

|     | 3.3.6 Operational Semantics Example 3.3.7 Lowering OpenMP Constructs 3.4 Implementation 3.5 Conclusions 3.6 Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 42<br>44<br>45                                                                         |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| 4.  | SWORD: A BOUNDED MEMORY-OVERHEAD DETECTOR OF OPENMP DATA RACES IN PRODUCTION RUNS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 47                                                                                     |

|     | 4.1 Introduction 4.1.1 Memory Overhead 4.1.2 Shadow-Cell Eviction 4.1.3 Race Masking 4.2 Background 4.2.1 Operational Semantics for OpenMP Race Checking 4.2.2 Offset-Span Labels 4.3 SWORD Technique and Implementation 4.3.1 Dynamic Analysis 4.3.1.1 Compiler Instrumentation 4.3.1.2 Log Collection 4.3.1.3 Bounded Dynamic Analysis Overhead 4.3.2 Offline Analysis 4.3.2.1 Interval Tree Example 4.3.3 Limitations 4.4 Experimental Results 4.4.1 DataRaceBench Microbenchmarks 4.4.2 OmpSCR Microbenchmarks 4.4.3 HPC Benchmarks 4.5 Related Work 4.6 Conclusions | 50<br>51<br>52<br>53<br>54<br>54<br>54<br>55<br>55<br>58<br>59<br>60<br>60<br>63<br>66 |

|     | 4.7 Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                        |

| 5.  | CONCLUSIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 69                                                                                     |

| REI | FERENCES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <b>71</b>                                                                              |

# LIST OF FIGURES

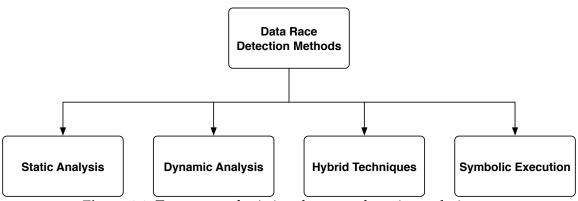

| 1.1 | Taxonomy of existing data race detection techniques                                                                                                                                                                                            | 3  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

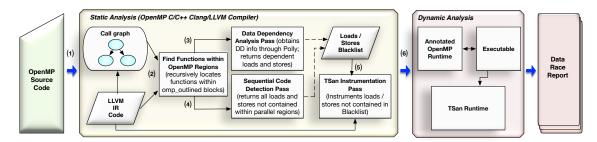

| 2.1 | Archer tool flow                                                                                                                                                                                                                               | 9  |

| 2.2 | Targeted instrumentation on a sample OpenMP program                                                                                                                                                                                            | 11 |

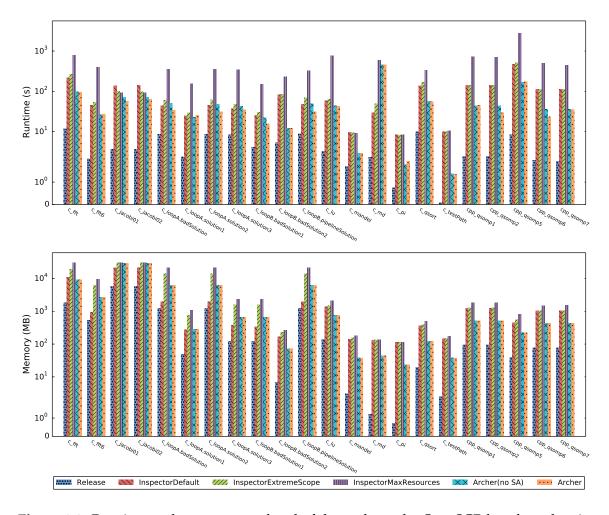

| 2.3 | Runtime and memory overhead of the tools on the OmpSCR benchmark suite executed with 16 threads.                                                                                                                                               | 16 |

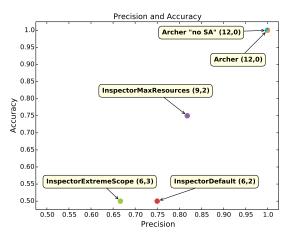

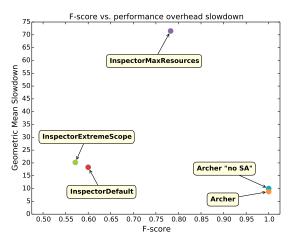

| 2.4 | Different metrics of comparison for the tools                                                                                                                                                                                                  | 17 |

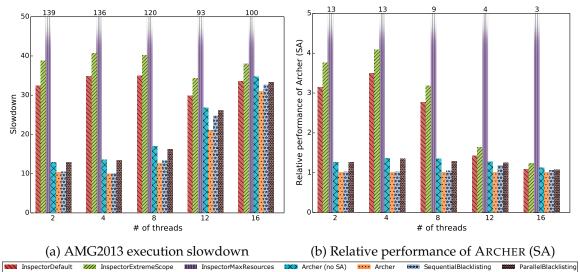

| 2.5 | AMG2013 execution slowdown factor introduced by the tools (a) and the relative performance factor of ARCHER (SA) against the other tools (b)                                                                                                   | 19 |

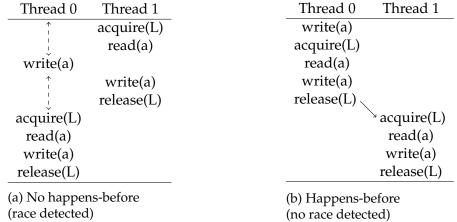

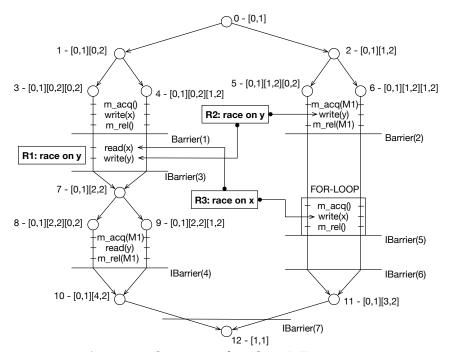

| 3.1 | Possible interleavings for program in Listings 3.1. The dashed line indicates the write operation of Thread 0 can happen simultaneously with the operations of Thread 1. The solid line indicates the happens-before edge between the threads. | 28 |

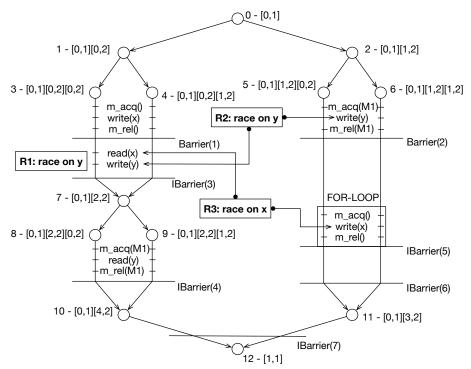

| 3.2 | Structure of the OpenMP program in Listing 3.2                                                                                                                                                                                                 | 30 |

| 3.3 | OpenMP concurrency operational semantics                                                                                                                                                                                                       | 38 |

| 3.4 | Structure of the OpenMP program in Listing 3.1                                                                                                                                                                                                 | 41 |

| 4.1 | Different interleavings generated by the same program. Dashed lines indicate that the write operations of Thread 0 can occur simultaneously with the operations of Thread 1. Solid lines indicate happens-before edges between the threads.    | 50 |

| 4.2 | Structure of an OpenMP program                                                                                                                                                                                                                 | 52 |

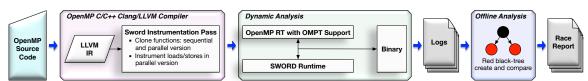

| 4.3 | SWORD tool flow                                                                                                                                                                                                                                | 54 |

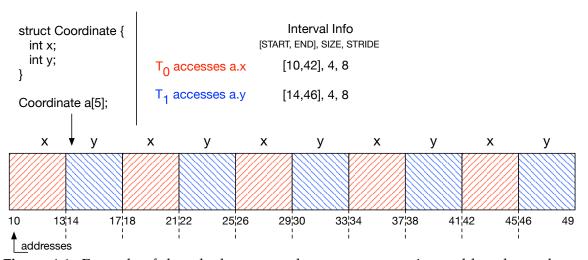

| 4.4 | Example of threads that access the same memory interval but do not have common addresses                                                                                                                                                       | 57 |

| 4.5 | Example interval trees. The red/underlined nodes are the two overlapping intervals that identify the race. The node's fields represent, respectively, begin, end of the interval, count, type of operation, access size, and program counter   | 58 |

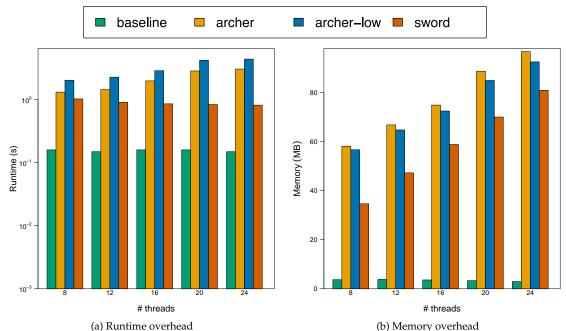

| 4.6 | Geometric mean of runtime and memory overhead for OmpSCR suite; the number of threads varies from 8 to 24                                                                                                                                      | 61 |

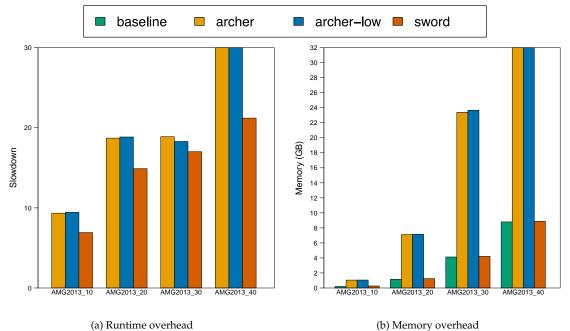

| 4.7 | Relative slowdown and memory overhead compared to the baseline for HPC benchmarks                                                                                                                                                              | 64 |

| 4.8 | Runtime and memory overhead on AMG2013 with varying problem size executed with 24 threads.                                                                                                                                                     | 65 |

# LIST OF TABLES

| 2.1 | Execution slowdown factor for various tool configurations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 14 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1 | State machine transitions for the example in Listing 3.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 41 |

| 4.1 | Example of thread's metadata file. Each line corresponds to one barrier interval. Column <b>pid</b> is parallel region ID, <b>ppid</b> is parent parallel region ID, <b>bid</b> is barrier ID, <b>offset</b> and <b>span</b> define offset-span label, <b>level</b> is level of parallelism, <b>data begin</b> is offset (in bytes) in the log file of the beginning of the respective data chunk, <b>size</b> is its size                                                                                                                                                                                                                                                                                         | 55 |

| 4.2 | Data races reported in OmpSCR suite                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 61 |

| 4.3 | Overheads on the OmpSCR suite executed with 24 threads, including the execution time of the parallel offline analysis. Column <b>baseline</b> is the baseline runtime; <b>archer</b> is the ARCHER runtime; <b>archer-low</b> is the low memory overhead ARCHER configuration runtime; <b>DA</b> is the total dynamic analysis runtime including logging; <b>OA</b> is the offline analysis runtime when executed sequentially; <b>MT</b> (Max Time) is the longest offline analysis runtime for any parallel region indicating how long parallel analysis runs; <b>#PR</b> is the number of independent parallel regions to analyze; <b>LS</b> is the amount of storage required to store the generated log files | 62 |

| 4.4 | Data races reported in HPC benchmarks. OOM indicates that a tool ran out of memory during the analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 63 |

| 4.5 | Overheads on the HPC benchmarks executed with 24 threads, including the execution time of the parallel offline analysis. See Table 4.3 for explanation of columns. OOM indicates that the tool ran out of memory during the analysis.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 65 |

#### ACKNOWLEDGMENTS

My PhD journey has come to an end. Although it has been full of challenges, it has also been intellectually fulfilling and a rewarding experience. In this page, I would like to acknowledge those people who have been part of this journey and have helped me in many ways during my 4 years here at Utah.

First and foremost, I would like to thank my advisor Prof. Ganesh Gopalakrishnan who has been essential during my whole PhD experience. I cannot thank him enough for his constant support during my research experience, which includes not only financial support and research advice, but also emotional support every time my PhD life put me in front of new challenges. Second, I would like to thank my coadvisor Zvonimir Rakamarić who has been more a second advisor rather than a coadvisor. Zvonimir's research advice and emotional support have been instrumental in shaping my whole PhD experience. Third, I would like to truly thank Dong H. Ahn from Lawrence Livermore National Laboratory (LLNL) for his financial support, research advice, and for giving me the opportunity to work in one of the largest computing facilities in the United States. Dong has been for me a third advisor during my PhD experience, he has given me the opportunity to spend two summers at LLNL where I could apply my research in real-world scenarios and collaborate with some of the greatest scientists in the world. Finally, I would like to sincerely thank the rest of my committee members Hari Sundar and Ryan Stutsman, who provided me great guidance and always find the time to help me whenever I was in need.

Thanks to all my friends in the Gauss and Soarlab research groups for their great support. In particular I would like to thank Marko Dimjašević and Mohammed Al-Mahfoudh, who have shared this experience with me since the beginning and together we have faced many of the PhD challenges, classes, but also fun and emotional moments. Thanks to Sriram Aananthakrishnan, Mark Baranowski, Geof Sawaya, Montgomery Carter, Charlie Jacobsen, Ian Briggs, and Shaobo He for all the technical discussions, coding advice, political talks, and pub nights out. All of you made these 4 years easier, fun, and memorable.

I would also like to thank two friends in particular that I have met here at Utah. Thanks to my friend Murry Mullenax, from the Steiner's Master Swimming group, for his advice on technical writing, for helping me out by proofreading this dissertation, and for our endless conversations. I would also like to thank Maurizio Bocca, an Italian fellow that I met at the beginning of my PhD who has become a great friend and gave me great advice for successfully complete my PhD

This dissertation would not have been possible without the support of my family. Thank you, mom Lucia, dad Tonio, and Alessia for the video calls during my lunch breaks, your texts, and your encouragement and emotional support during these 4 years. I missed you all, and I look forward to being able to come visit all of you more often now that my PhD has come to an end.

During my PhD I met the love of my life, Nicole. She and her family have welcomed me in their home, given me emotional support and encouragement every time I needed it the most. Thanks to Nicole's parents, Cherie and Lee, for helping me by proofreading this dissertation, and becoming my second family while being far away from home. Thanks to Nicole's siblings Chris, Bobbi, Carrie, and Gabe for the fun family dinners and for being always there to enjoy with me the holidays and breaks. I feel very lucky to have Nicole in my life, and now that this PhD journey has come to an end we look forward to starting our life together.

#### **CHAPTER 1**

#### INTRODUCTION

Multithreaded programming has become widespread in use, given the need to employ multicore CPUs to gain higher performance at a given energy budget. In the High Performance Computing (HPC) world, this has led to an increased adoption of on–node parallelism in large software applications. The work in progress at national research facilities [1, 2, 3] confirms this trend.

Multithreaded programming is achieved through different programming models (e.g. Pthreads); however, the predominant paradigm of choice in HPC is OpenMP [4], which guarantees portability and ease of use. At the Lawrence Livermore National Laboratory (LLNL), one of the world's largest computing facilities, one of the main ongoing tasks for computational scientists is the porting of critical multiphysics applications [5] to OpenMP. In this community, OpenMP is of paramount importance to enable shared memory parallel programming; yet, porting large HPC applications to OpenMP is error-prone. The correctness of these applications is crucial to the reliability of critical simulations pertaining to real world phenomena of fundamental importance such as modeling of nuclear explosions, weather simulations, hydrodynamics modeling, and so forth. One of the most common error types in OpenMP applications is the data race [6]. Data race detection is hard to achieve with traditional debugging methods, and it is also known to be a NP-complete problem [7]. Fast and precise checking tools to detect data races are needed now more than ever. While data race is a well-known problem and Pthreads data race detection tools have been proposed over the past 20 years, none or just a few of them are actually able to analyze OpenMP programs. This dissertation targets this critical need.

Data race detection research has focused both on static and dynamic analysis techniques. Static analysis techniques allow for exploration of all the inputs of the program and the interleavings of the threads. In addition, they are scalable and fast since they

do not incur any runtime overhead. However, the lack of information that exists only at runtime makes these techniques imprecise; in fact, they often miss races and generate false positives. Runtime techniques are precise, as they do not report any false positives, and only report races in the branches of programs that are actually executed. On the other hand, dynamic analysis for data race detection is known to generate a high runtime and memory overhead due to the operations it needs to perform and the state it needs to maintain during the execution.

The runtime overhead of even the best of dynamic tools, such as the ThreadSanitizer (Tsan) and Intel®Inspector XE, can cause between  $5\times-20\times$  slowdown, and the memory overhead can be between  $2\times-10\times$  of the memory used by the normal execution of the programs. For large programs, such as HPC applications, the runtime and memory overheads can be even larger. The high runtime slowdown and memory usage make such tools useless from the point of view of actual developers, who probably would not be keen on waiting a long time to check their programs *or they may not even have enough machine resources to run the tools*. We definitely need better techniques – static, dynamic, or combinations – to detect data races in large OpenMP applications.

#### 1.1 Thesis Statement

The goal of this dissertation is to provide new approaches for data race detection with low runtime and memory overheads while maintaining high precision and accuracy. With that said, our thesis statement is the following:

Combining the best of existing static and dynamic analysis techniques, and tailoring the implementation to the actual concurrency structure of structured parallel languages such as OpenMP, we can make data race checking of HPC applications practical.

# 1.2 Background

The problem of data race detection has been tackled by several researchers [8, 9, 10, 11, 12, 13, 14], through different techniques. Existing data race detection methods can be classified in four different categories as shown in Figure 1.1. Methods based on static analysis, dynamic analysis, hybrid techniques, and symbolic execution present strengths and limitations that raise the need for developing new techniques to enable or improve

Figure 1.1: Taxonomy of existing data race detection techniques.

the analysis of large OpenMP HPC applications. We explain the pros and cons of existing techniques that belong to the categories we identified:

- *Static Analysis:* Static analysis techniques utilize methods such as dependency analysis [15], alias analysis [16], type systems [17], interprocedural analysis [18], and so forth. While static analyses are able to consider all possible program behaviors without actually executing the program, they may report false positives due to dynamic behaviors that can not be actually modeled (e.g., pointers and aliases). Thus, static analysis is often not effective and can report false alarms or miss races.

- *Dynamic Analysis:* Dynamic techniques rely on compiler or binary instrumentation to gather information at runtime about memory accesses, synchronization operations, thread identifiers, and so forth. Dynamic approaches base their analysis on techniques such as happens-before [11, 9] or lockset analysis [10]. These techniques are more accurate; however, they depend on the current execution of the program, and in the case where a date race does not exhibit itself for a specific run, they miss the race. In addition, the overhead is often prohibitively high, which makes them inappropriate to analyze large scale applications.

- Hybrid Techniques: Hybrid techniques combine static and dynamic approaches. Static

analyses are often used to collect information that can be used by the dynamic analyses to increase the precision or reduce the overhead [14].

- *Symbolic Execution:* Symbolic execution [19] methods try to explore all possible program paths through symbolic values. The execution is then encoded into first-order

logic formulas and followed by Satisfiability Module Theories (SMT) based solving. To obtain scalable analysis [20, 21] the encoding must be well designed and optimized based on domain knowledge of the program.

#### 1.3 Contributions of the Dissertation

In this dissertation we present different contributions to overcome the limitations of the aforementioned methods. First, we combine existing techniques such as static and dynamic analyses, to bring together the best of the two approaches which are respectively low overhead and high precision and accuracy. Secondly, we formally define the concurrency of the OpenMP programming model through an operational semantics that exploits the OpenMP concurrency structure for race detection. Finally, starting from the operational semantics definition, we implement a novel OpenMP data race detection technique which guarantees zero memory overhead, soundness, and completeness of the data race detection analysis for a given input. These contributions result in two different data race detection tools for OpenMP programs that we present in detail in the chapters that follow.

The first tool, ARCHER (see Chapter 2), applies static analysis techniques to identify race free regions of code and remove them from the runtime analysis. On the other hand, the dynamic analysis checks the rest of the program for data races by applying an happens-before based technique. The results of our work show high precision and accuracy while maintaining a low runtime overhead. However, ARCHER suffers from high memory overhead ( $6\times$ ) memory overhead, which makes it unsuitable for large applications that require more than 16% of the available memory.

The high memory overhead issue inspired us to research and implement a new technique to reduce the memory overhead. Therefore we created SWORD, another OpenMP data race checker (Chapter 4) based on a formal operational semantics definition that we explain in Chapter 3. SWORD implements a fast logging technique to save information about the program memory accesses into files. This approach keeps the memory overhead to almost zero. We then implemented an offline analysis technique of the logs to identify the races. The offline analysis is highly parallelizable both across a multicore architecture and across a cluster. Results show that the logging techniques plus offline race detection algorithm reduce the memory overhead, enabling the analysis of large HPC applications

that were not possible with the existing tools.

The new approaches are novel contributions to effective and efficient data race detection for OpenMP programs. The two tools, subjects of this dissertation, are complementary in order to cover different classes of OpenMP programs. ARCHER is fast and detects most of the data races; however, because of its high memory overhead, it can only analyze a class of applications that requires a small amount of memory to complete the data race detection process. On the other hand, SWORD provides a technique that is able to analyze programs that necessitate of large amount of memory where other tools would fail, and thus *guaranteeing better coverage for a given run*.

# 1.4 Organization of the Dissertation

This dissertation is organized as follows: In Chapter 2, we present the first tool ARCHER with details about its data race detection approach and an extensive evaluation on well-know benchmarks and real-world applications; Chapter 3, illustrates an operational semantics to enable precise and accurate data race analysis exploiting the structured concurrency model of OpenMP; with Chapter 4, we present our implementation of the operational semantics in a tool called SWORD, with experimental results that demonstrate the effectiveness and efficiency of the approach; finally in the Chapter 5, we summarize all the contributions and conclude the dissertation.

#### **CHAPTER 2**

# EFFECTIVELY SPOTTING DATA RACES IN LARGE OPENMP APPLICATIONS

This chapter is based on work published at the Workshop on the LLVM Compiler Infrastructure in HPC [22] and at the IEEE International Parallel & Distributed Processing Symposium 2016 [23]<sup>1</sup>.

In this chapter we present ARCHER, the first of the two data race detection tools subject of this dissertation. We illustrate the details of ARCHER's techniques and an extensive evaluation of the tool in term of effectiveness and efficiency.

#### 2.1 Introduction

High performance computing (HPC) is undergoing an explosion in raw computing capabilities as evidenced by recent announcements of next-generation computing system projects [1, 2, 3]. To meet the stipulated performance and power budgets, many key software components in these projects are being transitioned to adopt on-node parallelism to a greater degree. The predominant programming model of choice in this transition is OpenMP—due in large part to its portability and ease of use. In fact, the main task for computational scientists at Lawrence Livermore National Laboratory (LLNL), one of the world's largest computing facilities, is the porting of mission-critical multiphysics applications [5] to exploit OpenMP.

We find, however, that efficient and scalable development tools for OpenMP are still quite scarce, making development efforts hard. In particular, none of the preexisting OpenMP data race checkers is capable of handling the code sizes involved, or provides effective debugging support for concurrency bugs. Meanwhile, libraries such as Hypre [24],

¹©2016 IEEE. Adapted, with permission, from Atzeni S., Gopalakrishnan G., Rakamarić Z., Ahn D. H., Laguna I. Schulz, M, Lee G., Protze J., Müller M. S., Archer: Effectively Spotting Data Races in Large OpenMP Applications, June 2016

which underlie many critical applications, have run into data races during this transition. In one LLNL application, because of this lack of debugging tools, developers who faced these races even took the draconian approach of reverting back to sequential code.

This work describes ARCHER, our new OpenMP data race detector, its unique capabilities in terms of scalability and precision, its use of a proposed standard, and our philosophy of building on well-engineered open-source software. While the core concept of a data race has been known for decades (uncoordinated, i.e., not separated by a happens-before edge, accesses on a memory location by two threads, with one access being a write), transitioning this idea into HPC practice required adherence to four key tenets.

- 1. Scalable Happens-Before Tracking Methods: Checking for races in production OpenMP programs requires the ability to track a huge number of memory references and their happens-before ordering. A significant amount of ARCHER's scalability stems from its exploitation of a preexisting tool—namely ThreadSanitizer (TSan) [12]. TSan's unique architecture enables it to implement the idea of vector-clock-based race checking far more efficiently than comparable tools do. Embracing TSan and its LLVM-based tooling approach enables us to write custom LLVM passes, and in general take advantage of the growing popularity of LLVM in HPC [22]. Previous OpenMP data race checking tools were never released for public evaluation, were based on binary instrumentation through PIN [25], or employed symbolic methods [20]. These approaches are neither scalable nor widely portable. ARCHER has been publicly released under the BSD License [26]. (Note: TSan was originally designed for PThread and Go programs, and cannot be directly applied to OpenMP programs as will soon be described.)

- 2. Static/Dynamic Analysis of Structured Parallelism: In Archer, we capitalize on OpenMP's structured parallelism to support two key features never before exploited in an OpenMP race checker. First, we exploit OpenMP's structured parallelism to easily write LLVM passes that identify guaranteed sequential regions within OpenMP. Such analysis would be difficult to conduct in the context of unstructured parallelism (e.g., PThreads). Second, we identify and suppress parallel loops from race checking. Archer achieves this by black-listing accesses within parallelizable loops with the help of a static

analysis.

- 3. Modular Interfacing with OpenMP Runtimes: While structured parallelism has been exploited in the context of Java-like languages (e.g., Habanero Java [27]), such exploitation in the context of OpenMP and Archer required a combination of innovations. Unlike in languages such as Habanero Java where the language and the runtime are designed together, in OpenMP vendors provide their own custom runtimes. Tools, such as TSan, must be suitably modified to ignore OpenMP internal actions, which may otherwise be falsely assumed to be data races [22]. Archer's approach is architected based on the OMPT standard [28] so that our solutions may modularly be incorporated with multiple OpenMP runtimes.

- 4. Collaboration with Active Projects: ARCHER has already made significant impact within LLNL. As one example, HYDRA [29] is a large multiphysics application developed at LLNL, which is used for simulations at the National Ignition Facility (NIF) [30] and other high energy density physics facilities. It comprises many physics packages (e.g., radiation transfer, atomic physics, and hydrodynamics), and although all of them use MPI, a subset of them use thread-level parallelism (OpenMP and PThreads) in addition to MPI. It has over one million lines of code and a development lifetime that exceeds 20 years. In the summer of 2013, developers began porting HYDRA to Sequoia [31], the over 1.5 million core IBM Blue Gene/Q-based system that had just been brought online at that time. Although the efforts included incorporating more threading for performance, the developers got significantly impeded when they could not resolve a non-deterministic crash on an OpenMP-threaded version of Hypre [24] (used by one of HYDRA's scientific packages). The developers found it very difficult to debug this error that occurred intermittently after varying numbers of time steps, only at large scales (at or above 8192 MPI processes), and only under compiler optimizations. After spending considerable amounts of time, the team suspected the presence of a data race within Hypre, but the difficulties in debugging and time pressure forced them to work around the issue by selectively disabling OpenMP in Hypre. When ARCHER was brought onto the scene, it located "benign races" involving two threads racing to write the same value to the same location—a practice

known to be dangerous in the presence of compiler optimizations [32]. Removing these benign races fixed the bug. This episode—detailed in Section 2.3.3—clearly shows that effective data race checkers specifically tailored to high-end computing environments are invaluable during critical projects.

## 2.2 Approach

Figure 2.1 illustrates how ARCHER implements our tenets by combining well-layered modular static and dynamic analysis stages. In more detail, our static analysis passes [33, 34, 35] help classify the given OpenMP code regions into two categories: *guaranteed race-free* and *potentially racy*. Our dynamic analysis then applies state-of-the-art data race detection algorithms [12, 9] to check only the potentially racy OpenMP regions of code. The static/dynamic analysis combination is central to the scalability (while maintaining analysis precision) of ARCHER, as evidenced by its ability to handle real-world examples that existing tools cannot handle with the same levels of precision and scalability (see Section 2.3.2).

As described earlier, we implemented ARCHER using the LLVM/Clang tool infrastructure [36, 37] and the TSan dynamic race checker [12]. On the static analysis side, ARCHER uses Polly [35] to perform data dependency and loop-carried data dependency analysis (together called *data dependency analysis* from now on). This results in a *Parallel Blacklist*. ARCHER also extends some of the static analysis passes already present in LLVM. Specifically, our extension builds a call graph and traverses it to identify memory accesses that do not come from within an OpenMP construct (i.e., sequential code regions). This results in a *Sequential Blacklist*. These blacklists are combined and used to limit the instrumentation in TSan.

On the dynamic analysis side, ARCHER uses our customized version of TSan to detect

**Figure 2.1**: ARCHER tool flow.

data races at runtime. To prevent TSan from being confused by OpenMP runtime internal actions (and falsely report them as OpenMP-level races), ARCHER employs TSan's Annotation API to highlight these synchronization points within LLVM OpenMP Runtime (the runtime presently associated with ARCHER in our studies). As we have already pointed out, our efforts are being migrated to adhere to the OMPT standard.<sup>2</sup>

#### 2.2.1 Static Analysis Phase

We now detail some of the finer details of our static analysis, including feeding the blacklist information to the TSan runtime. TSan carries out its dynamic data race detection by first instrumenting all the load and store actions of a program at compile time, and using this instrumentation to help track happens-before. TSan also provides a feature that allows users to blacklist functions [38] (by their name) that should not be instrumented and that are thus to be ignored at runtime. Unfortunately, this granularity of instrumentation is insufficiently refined to handle our sequential and parallel blacklists that express the intent to blacklist individual accesses (that are, in almost all cases, not demarcated by function boundaries). Thus, in order to communicate our blacklists to TSan, we extended its blacklisting capabilities to enable a finer-grained selection at the level of source lines. This allows the modified TSan used by ARCHER to exploit our sequential and parallel blacklists, thus guaranteeing a high degree of analysis precision and scalability.

In more detail, after the LLVM intermediate representation (IR) and call graph are generated, our analysis transforms OpenMP pragmas in the LLVM IR code as outlined functions named *omp\_outlined.NUM*, where *NUM* is an identifier for each parallel region present in the code. Our first pass visits the call graph, and for each *omp\_outlined* function finds all the functions called within it. For each of these functions, the analysis is recursively applied. Thereafter, data dependency analysis and sequential code detection are applied (step (3) in Figure 2.1). For the former, an existing tool in the LLVM/Clang suite called Polly [35] is used. In the example given in Figure 2.2, the first for-loop (lines 7–9) is data parallel (i.e., data independent) and is blacklisted, while the second one (lines 12–14) is not (exhibits a loop-carried dependence) and hence is not blacklisted.

<sup>&</sup>lt;sup>2</sup>Some of us are associated with the OMPT efforts, thus facilitating our collaboration further to benefit a wide variety of OpenMP runtimes.

```

1 main() {

// Serial code blacklisted

3

setup();

4

sort(); ←

Used in serial and parallel code

5

6

#pragma omp parallel for

7

for(int i = 0; i < N; ++i) {

No data-dependent

8

a[i] = a[i] + 1;

code blacklisted

9

10

11

#pragma omp parallel for

for(int i = 0; i < N; ++i) {

12

Potentially racy

a[i] = a[i + 1];

13

code instrumented

14

}

15

16

#pragma omp parallel

17

18

sort();

19

20

21

// Serial code

printResults();

Serial code blacklisted

22

23 }

```

**Figure 2.2**: Targeted instrumentation on a sample OpenMP program.

ARCHER also identifies sequential code sections (step (4)). In Figure 2.2, lines 3 and 22 are sequential instructions and are hence blacklisted. However, function sort(), invoked at lines 4 and 18, cannot be blacklisted, as it is invoked both from a sequential and parallel context. The payoff due to such sequential code detection is potentially very high in real-world projects where only some of the loops are parallelized with OpenMP (based on the benefits, the number of cores available, etc.). As already pointed out, these analyses are greatly facilitated by OpenMP's structured parallelism.

#### 2.2.2 Dynamic Analysis Phase

Our use of TSan for OpenMP race checking hinges on the fact that OpenMP parallelism is typically realized through a PThread-based runtime library. As already mentioned, unmodified TSan cannot be meaningfully used for OpenMP due to the large number of false positives ("false alarms") it reports [22].

The OpenMP standard specifies several high-level synchronization points. Explicit synchronization points include barrier, critical, atomic, and taskwait. Implicit syn-

chronization includes single, task, and the OpenMP reduction clause. As semantically intended and realized in the runtime, the threads can enter a critical section only in a serialized manner, thus avoiding a data race. However, TSan lacks any knowledge about these synchronization points. We use the Annotation API of TSan to mark these synchronization points within the OpenMP runtime to avoid such false positives. This technique was successful in eliminating all false positives in our benchmarks. Finally, the combination of the Archer's static analysis and new TSan instrumentation that exploits the blacklist information produces a selectively instrumented binary (step (6) in Figure 2.1).

#### 2.3 Evaluation

We evaluate ARCHER in three stages through: (1) a collection of smaller benchmarks called the OmpSCR benchmark suite [39] (an OpenMP source code collection); (2) AMG2013, a non-trivial application from the HPC CORAL benchmark suite [40]; and (3) the HYDRA case study. Our evaluation is in terms of the effectiveness, performance, and scalability of ARCHER compared to Intel®Inspector XE. We also compare ARCHER against an unmodified version of TSan applied to the same benchmarks.<sup>3</sup> When using TSan and ARCHER, we compile our benchmarks using Clang/LLVM, and when using Intel®Inspector XE, we compile them using the Intel Compiler. When running our benchmarks under ARCHER, we link them against our annotated LLVM OpenMP Runtime [41, 22]. When running them under Intel®Inspector XE as well as TSan, we employ the uninstrumented version of the same runtime. We studied the following configuration selections:

- ARCHER: We employ four configurations: (1) the basic configuration of ARCHER that applies both static and dynamic analysis to reduce runtime and memory overhead;

(2) ARCHER run without static analysis support (only dynamic race checking using the enhanced runtime to avoid false positives is used); (3) apply just the Sequential Blacklist; and (4) apply just the Parallel Blacklist.

- 2. **TSan:** When running the unmodified version of TSan, we employ its default parameters.

<sup>&</sup>lt;sup>3</sup>Despite this exercise yielding numerous false positives, it provides a good performance baseline.

3. Intel®Inspector XE: Intel®Inspector XE provides many "knobs" for controlling performance and analysis quality tradeoffs. Of these, we exercise three configurations: (1) a *default* mode that checks memory accesses at the coarse-grain granularity of four bytes; (2) the *extreme-scope* configuration that sets memory access granularity at a single byte (incidentally, this is the same granularity as what TSan employs), which obtains higher precision at higher cost; (3) the *use-maximum-resources* configuration that allows Intel®Inspector XE to detect more data races, but at the cost of increased memory consumption and greater runtime overhead.

We perform our evaluation on the Cab cluster at LLNL. Each Cab node has two 8-core, 2.6 GHz Intel Xeon E5-2670 processors and 32GB of RAM. It runs the TOSS Linux distribution (kernel version 2.6), which is a customized distribution specifically targeting engineering and scientific applications. Runtimes and memory overhead of all benchmarks were averaged across 10 executions, each time running with a variable number of threads (ranging from 2 to 16). In the experimental results, *Release* denotes the original benchmark characteristics. *SequentialBlacklisting* and *ParallelBlacklisting* denote that just those blacklisting strategies are exploited, ARCHER denotes that both are used, while ARCHER "no SA" denotes that none are used.

#### 2.3.1 OmpSCR Benchmark Suite

We chose the OmpSCR benchmark suite (see Table 2.1) primarily because it harbors a few known races, as reported in prior work [25]. We, however, found several additional races not previously reported. With respect to each tool and configuration, we now describe the overall analysis quality followed by the runtime overheads. Then, we summarize the overall merit of these tools by plotting their analysis quality vs. performance scores.

Our evaluation shows that ARCHER detects all of the documented races in all configurations. In particular, it discovered six such races in the following benchmarks: c\_md, c\_loopA.badSolution, c\_loopB.badSolution1, c\_loopB.badSolution2, c\_testPath, and c\_jacobi3. In addition, ARCHER reported six previously undocumented races in the following C++ benchmarks: cpp\_qsomp1, cpp\_qsomp2, cpp\_qsomp3, cpp\_qsomp4, cpp\_qsomp5, and cpp\_qsomp6. (We manually verify that all the reported races are real.) In contrast,

**Table 2.1**: Execution slowdown factor for various tool configurations.

|                          |             | Hne        | enescope       | so de | SA.     |

|--------------------------|-------------|------------|----------------|-------------------------------------------|---------|

| Benchmark                | Lidoodsu, 1 | Inspectors | the themes ope | ARTHUR AND OWNERS                         | 4800 Am |

| c_fft                    | 18.2        | 22.1       | 66.8           | 8.1                                       | 7.9     |

| c_fft6                   | 21.0        | 25.3       | 188.8          | 12.2                                      | 12.7    |

| c_jacobi01               | 38.2        | 27.5       | 25.2           | 19.2                                      | 15.6    |

| c_jacobi02               | 38.7        | 26.7       | 25.6           | 19.6                                      | 17.8    |

| c_loopA.badSolution      | 5.1         | 7.0        | 41.1           | 5.9                                       | 3.9     |

| c_loopA.solution1        | 10.2        | 12.2       | 64.9           | 9.4                                       | 10.5    |

| c_loopA.solution2        | 5.1         | 7.1        | 41.2           | 5.5                                       | 3.6     |

| c_loopA.solution3        | 4.5         | 5.8        | 42.1           | 5.1                                       | 4.2     |

| c_loopB.badSolution1     | 6.2         | 7.5        | 36.8           | 5.5                                       | 3.8     |

| c_loopB.badSolution2     | 15.6        | 16.2       | 43.7           | 2.3                                       | 2.3     |

| c_loopB.pipelineSolution | 5.4         | 7.8        | 36.7           | 5.6                                       | 3.6     |

| c_lu                     | 18.0        | 19.6       | 240.7          | 13.8                                      | 13.0    |

| c_mandel                 | 5.6         | 5.4        | 5.3            | 1.7                                       | 1.7     |

| c_md                     | 12.7        | 21.1       | 253.4          | 197.3                                     | 197.1   |

| c_pi                     | 11.1        | 10.7       | 11.1           | 2.3                                       | 2.6     |

| c_qsort                  | 14.2        | 16.9       | 34.1           | 5.8                                       | 5.7     |

| c_testPath               | 133.0       | 133.6      | 138.3          | 18.3                                      | 17.9    |

| cpp_qsomp1               | 57.5        | 57.4       | 289.5          | 18.0                                      | 18.1    |

| cpp_qsomp2               | 57.8        | 57.6       | 286.6          | 17.9                                      | 11.9    |

| cpp_qsomp5               | 56.8        | 62.5       | 338.2          | 20.4                                      | 20.8    |

| cpp_qsomp6               | 57.5        | 57.9       | 253.5          | 18.2                                      | 11.9    |

| cpp_qsomp7               | 57.8        | 57.8       | 229.3          | 18.8                                      | 18.3    |

| Mean                     | 29.5        | 30.3       | 122.4          | 19.6                                      | 18.4    |

| Median                   | 16.8        | 20.3       | 54.3           | 10.8                                      | 11.2    |

| Geometric Mean           | 18.3        | 20.2       | 71.5           | 10.0                                      | 8.8     |

Intel®Inspector XE incurs varying degrees of accuracy and precision loss in all three configurations.

In term of accuracy (the number of correctly detected races divided by the number of true races that should have been detected), Intel®Inspector XE, in its default and extreme-scope configurations, misses races in benchmarks c\_loopB.badSolution1, cpp\_qsomp1, cpp\_qsomp2, cpp\_qsomp5, and cpp\_qsomp6. On the other hand, Intel®Inspector XE under the max-resources configuration detects most of these races, though it still misses the races in cpp\_qsomp5 and c\_loopB.badSolution1.

In terms of precision (the number of correctly detected races divided by the number of all the races detected, including false positives—i.e., "false alarms"), ARCHER in both configurations<sup>4</sup> incurs no false positives, while Intel®Inspector XE does. For example, in benchmark c\_md, Intel®Inspector XE reports an additional race that is clearly a false positive, as documented in related work [42]. In addition, in cpp\_qsomp7—which uses the tasking construct as per OpenMP 3.1—Intel®Inspector XE reports two false positives, which ARCHER in both configurations correctly avoids reporting as races. These results clearly demonstrate that ARCHER accurately understands the OpenMP task synchronization semantics.

We now discuss in detail performance results in terms of runtime and memory overheads. We only present the results for 16 threads because the tools incur similar overheads as we vary the number of threads.<sup>5</sup> Figure 2.3 details runtime and memory overheads for benchmarks in the OmpSCR benchmark suite. In a nutshell, ARCHER outperforms Intel®Inspector XE across all of its configurations on most of the benchmarks. Intel®Inspector XE incurs the least overhead in its default configuration, but this comes at the expense of degraded analysis quality. The *extreme-scope* configuration of Intel®Inspector XE, which is closer to the ARCHER's analysis granularity, incurs much higher overhead than ARCHER with a few exceptions. The *max-resources* configuration results in a very high resource consumption and its overheads are always higher than that of ARCHER.

ARCHER performs slightly better with static analysis support than without, catching all the data races in both cases. This can be mainly attributed to the fact that the OmpSCR benchmarks are small (in terms of the lines of code), and hence static analysis finds very few blacklisting opportunities. Still, ARCHER with static analysis support is overall 15% faster on the average. In Section 2.3.2, we show that on real-world HPC application static analysis reduces much more the runtime overhead, thus underscoring its importance in practice.

<sup>&</sup>lt;sup>4</sup>We omit the evaluation of Archer in the Sequential and Parallel Blacklisting configurations for the OmpSCR benchmark suite since the results for those configurations match the results of Archer without static analysis.

<sup>&</sup>lt;sup>5</sup>We omit three OmpSCR benchmarks in our performance results. The data race in c\_jacobi3 highly influences the execution time of the benchmark, varying it by a factor of 1000 from run to run. The other two are cpp\_qsomp3 and cpp\_qsomp4, where data races cause them to crash.

**Figure 2.3**: Runtime and memory overhead of the tools on the OmpSCR benchmark suite executed with 16 threads.

We assess the merits of the tools by plotting their analysis quality against performance. Table 2.1 shows the execution slowdown for each of the OmpSCR benchmarks under each of the tool configurations. We give the mean, median, and geometric mean in the last three rows. For space reasons, we omitted our other statistical measurements. However, using a confidence level of 0.05, we compared the slowdown distributions of each configuration (i.e., how our 10 measurements varied for each target benchmark) and verified that the distributions of Archer and Archer "no SA" do not overlap for a majority of cases. This indicates that the difference in performance between Archer and Archer "no SA" is statistically significant. In addition, Figure 2.4a gives the precision and accuracy of the tools, displayed with their true and false positives counts. The plot show that Archer provides the best analysis quality with respect to other state-of-the-art race detectors in-

- (a) Precision and accuracy; in parentheses we report the number of reported races and false positives.

- (b) Overall merit expressed as analysis quality vs. performance.

Figure 2.4: Different metrics of comparison for the tools.

cluding Intel®Inspector XE.

In Figure 2.4b, we use an F-score (F1 score) [43] to capture the overall quality of analysis. The F-score is a measure of analysis quality that accounts for both accuracy and precision (as defined previously) and is given by:

$$F_1 = 2 \cdot \frac{\text{precision} \cdot \text{accuracy}}{\text{precision} + \text{accuracy}}.$$

Thus, the F-score reaches its best value at 1 and worst at 0. In Figure 2.4b we plot each tool onto a two-dimensional space defined by the F-score and slowdown geometric mean. We use the geometric mean as our performance metric because the mean and median are significantly skewed by outliers. Indeed, the slowdown values run the gamut from 253.4x to 1.7x (mainly because of the very different charateristics and running times of the OmpSCR benchmarks), and this biases the arithmetic mean and median, while the geometric mean is designed to compute a figure of merit under such circumstances. The plot shows the general attributes of each tool in terms of accuracy and runtime overheads, and our design goal is to create a tool that lies as close as possible to the lower right corner. It is clear from the plot that ARCHER best meets this goal, as compared to other state-of-the-art tools: both versions of ARCHER (with and without static analysis) do much better than Intel®Inspector XE in all its configurations.

#### 2.3.2 AMG2013 Case Study

To complement our OmpSCR study with a larger code base, we perform an evaluation on AMG2013, which contains approximately 75,000 lines of code. AMG2013 [44] is a parallel algebraic multigrid solver for linear systems and is based on Hypre [24, 45], a large linear solver library developed at LLNL. Our experiments with ARCHER discovered three races within AMG2013, which were previously unreported. Thus, this application was useful to quantify both the performance and analysis quality of the tools. In the following, we compare the precision and performance of unmodified TSan, each ARCHER configuration, and Intel®Inspector XE in three different configurations.

The unmodified TSan, after reporting about 150 false positives, crashes and never finishes its analysis. Intel®Inspector XE reports all three data races when it is configured with *use-maximum resources*. When using the *extreme-scope* configuration, it reports all three of the races, but only when running with 16 threads. Finally, when using the *default* configuration, Intel®Inspector XE always misses one particular race of the three.

We now compare the performance of these tools in all of the different configurations. Figure 2.5 shows the AMG2013 execution slowdown factor introduced by the tools a and the relative performance factor of ARCHER (SA) against the other tools b. Both ARCHER and Intel®Inspector XE are dynamic checkers, and hence they introduce a large runtime overhead with respect to the application execution under no tool control (see Figure 2.5a). However, it is clear that ARCHER has significant performance advantages relative to other tools. In fact, Figure 2.5b shows the relative performance of ARCHER (with and without static analysis) against all of the three configurations of Intel®Inspector XE. ARCHER is generally 2–15x faster than Intel®Inspector XE depending on the number of threads. When compared to itself, ARCHER without static analysis support improves the performance by a factor between 1.2 and 1.5 depending on the number of threads.

ARCHER also reduces the memory overhead relative to Intel®Inspector XE in comparable configurations (modes other than default). However, its memory footprint still appears unnecessarily large. We surmise that this is because of TSan's runtime shadow memory allocation policy, which ARCHER inherits unmodified. In particular, when an array is initialized, all of its elements are accessed, and this causes TSan to allocate shadow memory corresponding to the entire array during initialization. Thereafter, TSan does

**Figure 2.5**: AMG2013 execution slowdown factor introduced by the tools (a) and the relative performance factor of ARCHER (SA) against the other tools (b).

not selectively deallocate this shadow memory, for instance, based on whether the array locations are live beyond a certain point. In our future work, we plan to confirm this, and then achieve selective deallocation—a possibility suggested by OpenMP's structured parallelism model.

The overall gains due to static analysis depend on the proportion of sequential regions (for Sequential Blacklisting) and data independent loops (for Parallel Blacklisting). Our future work will focus on characterizing these gains across many more large case studies.

#### 2.3.3 ARCHER Resolves Real-World Races

We now present how ARCHER aided LLNL scientists in resolving the intermittent crashes in HYDRA mentioned in Section 2.1. This investigation was spurred into action when our AMG2013 experiment discovered the three races mentioned earlier. Of the three data races flagged by ARCHER, two<sup>6</sup> were found in a fairly complex OpenMP region spanning over 400 source lines with tens of reaching variables. The fact that these flagged sites were contained within a deeply nested control-statement level further complicated manual analysis; thus, we contacted the developer for further validation.

In response, the developer confirmed that both were indeed true races. Specifically,

$<sup>^6</sup>$ Specifically, one between the memory accesses at lines 1183 and 1248 and the other at lines 1184 and 1249 within par\_interp.c

one thread accesses the first element of a portion of an array defined by P\_diag\_i and P\_offd\_i (belonging to the next thread), while the second thread subtracts a number from this element. However, because the number being subtracted for this particular element was zero, this condition was never detected during testing. While programmers often consider this type of races (i.e., multiple threads writing the same value to the same memory location) benign, the developer did recognize that the containing function, hypre\_BoomerAMGInterpTruncation, was one of the routines that they had to disable OpenMP parallelization on for reliable use within HYDRA.

Encouraged by our findings, the application's team resumed their debugging of this issue. They applied a fix to these benign data races to the latest Hypre release (2.10.0b) and reran the simulation. This time, however, the simulation failed in a different way: a crash occurred very quickly and much more deterministically. Next, we applied ARCHER to this Hypre release using a representative test code provided by the developer, and ARCHER reported several additional benign data races; tqhe races were detected between lines 2313 and 2315 of par\_coarsen.c where threads write the constant 0 to the same element in an array: CF\_marker[j] = 0.

The developer was initially skeptical that these races were the root cause because threads write the same numerical constant: 0 in the coarsening and 1 in par\_lr\_interp.c. However, when we fixed all of these races, for example by synchronizing the respective assignments with OpenMP critical, the crashes no longer appeared. We theorize that the compiler (IBM XL) used on this platform, which would assume race-free code for optimization, transformed the code in such a way that those benign races turned into harmful ones, a pitfall described previously by Boehm [32].

While the developer is currently trying to find a way to resolve the races in a more performant manner, it was made clear that data race checkers like ARCHER, which are tailored to large HPC applications, are crucial to avoid a programmer productivity loss on such elusive bugs.

#### 2.4 Related Work

Data race detection in general is one of the most widely studied problems in concurrent program design and has been shown to be NP-hard [7]; a complete survey is beyond the scope of this section and so we focus on closely related approaches for correctness checking.

According to Erickson et al. [46], data races must be taken as "the smoking gun" for any number of root causes: insufficient atomicity (as per intended code behavior), an unreliable communication idiom, unintended sharing [13], or a misunderstanding of how generated code behaves vis-a-vis the higher level program view (including possible miscompilation [32]). Static race detection methods provide high checking efficiency, but are known to generate false positives (e.g. [47, 8]); each false positive can be a month of wasted reconfirmation time [48]. Polynomial-time race checking can often be achieved under structured concurrency [27]. Predictive methods attempt to find many more "implied" races based on an initial execution through the program (e.g., [49]).

ARCHER derives much of its efficiency by avoiding the instrumentation of independent loop iterations as well as sequential code regions. These approaches to achieve parsimonious instrumentation have recently been shown effective in the context of TSan and PThread programs through a technique called section-based program analysis [50]. The idea of specializing race checking has also taken root in the context of GPU programs where symbolic methods coupled with the idea of using a two-thread abstraction scheme have become popular [21, 51, 52]. This approach is also, in principle, applicable to OpenMP data race checking [20].

#### 2.5 Discussion

Despite OpenMP being around for over two decades, there are no practical data race detectors for OpenMP programs that an HPC practitioner can use in the field today; ARCHER is the first such race checker and its approach is both timely and necessary to provide the widening field of OpenMP programming with this critical correctness tool capability. In fact, the main developer of TSan has taken active interest in our work, and even the LLVM community has helped us by supporting TSan on the PowerPC platform [53].

While ARCHER has proven to be useful at debugging real-world races in OpenMP applications, we now discuss the practical implications of our approach with respect to (1) features in the latest OpenMP specifications and (2) the use of compiler optimization flags.

#### 2.5.1 Latest OpenMP Specifications

The OpenMP Architecture Review Board released the latest OpenMP specification (Version 4.0) in July 2013. We expect that it will take major compilers a few years to come to full compliance with this specification. At the point of writing, there exists no compiler that can fully support OpenMP 4—including its device construct. The OpenMP branch of Clang/LLVM, under which we demonstrate our approach, supports only OpenMP 3.1. While this practical limitation only allowed us to explore the problem space in OpenMP 3.1, we recognize that OpenMP 4, when implemented by compilers and thus adopted by our applications, will present a new set of challenges to our approach.

In particular, with the device construct, OpenMP threads will be run not only on CPUs but also on accelerators, such as GPUs, which could also be subject to the harmful effects of data races. Unfortunately, tooling in this area is not as comprehensive as designers may like. For example, the CUDA Memcheck tool [54] is limited in that it can only detect data races that occur in the thread-block level shared memory space; yet, in practice, races also occur in the global memory scope [52]. Given the current trends to provide coherent memory between CPUs and GPUs [2], it is clear that the community will need more comprehensive race detection techniques. In addition, because of the higher numbers of OpenMP threads that can run on GPUs, techniques to further enhance scalability (e.g., by exploiting thread symmetry relationships) must be researched and developed.

#### 2.5.2 Compiler Optimization Flags

Recent work [32] suggests that it is critical to pinpoint and fix data races that many programmers consider benign. In particular, the presence of any data race can lead a compiler to turn a benign race into a harmful one, even when code transformations that are considered safe are used. In this regard, ARCHER can best detect data races at the source level with no compiler optimization (-O0). This is because an optimization can hide the presence of a race through transformations. Further, there could be data races introduced through an illegal transformation. This is a problem within the compiler and ARCHER does not pursue this class of errors.

#### 2.6 Conclusions and Future Work

In this work we presented ARCHER, an OpenMP data race checker that embodies the design principles needed to cope with and exploit the characteristics of large HPC applications and their perennial development lifecyle. ARCHER seamlessly combines the best from static and dynamic techniques to deliver on these principles. Our evaluation results strongly suggest that ARCHER meets the design objectives by incurring low runtime overheads while offering very high accuracy and precision. Further, our interaction with scientists shows that it has already proven to be effective on highly elusive, real-world errors, which can significantly waste scientists' productivity.