# Detecting and Surviving Intrusions: Exploring New Host-Based Intrusion Detection, Recovery, and Response Approaches

Ronny Chevalier

# ► To cite this version:

Ronny Chevalier. Detecting and Surviving Intrusions: Exploring New Host-Based Intrusion Detection, Recovery, and Response Approaches. Cryptography and Security [cs.CR]. CentraleSupélec, 2019. English. tel-02417644

# HAL Id: tel-02417644 https://hal.inria.fr/tel-02417644

Submitted on 18 Dec 2019

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE DE DOCTORAT DE

CENTRALESUPELEC, RENNES COMUE UNIVERSITÉ BRETAGNE LOIRE

ÉCOLE DOCTORALE N° 601 Mathématiques et Sciences et Technologies de l'Information et de la Communication Spécialité : Informatique

# Par Ronny Chevalier

# **Detecting and Surviving Intrusions**

Exploring New Host-Based Intrusion Detection, Recovery, and Response Approaches

Thèse présentée et soutenue à Rennes, le 17 décembre 2019 Unité de recherche : IRISA Thèse N° : 2019CSUP0003

### Rapporteurs avant soutenance :

Joaquin Garcia-Alfaro Professeur, Telecom SudParis Herbert Bos Full Professor, Vrije Universiteit Amsterdam

# **Composition du Jury :**

| Examinateurs :  | Joaquin Garcia-Alfaro | Professeur, Telecom SudParis                            |

|-----------------|-----------------------|---------------------------------------------------------|

|                 | Herbert Bos           | Full Professor, Vrije Universiteit Amsterdam            |

|                 | Karine Heydemann      | Maître de conférences, Université Pierre et Marie Curie |

|                 | Guillaume Hiet        | Maître de conférences, CentraleSupélec Rennes           |

|                 | Laurence Pierre       | Professeur, Université Grenoble Alpes                   |

|                 | David Plaquin         | Senior Research Scientist, HP                           |

| Dir. de thèse : | Ludovic Mé            | Advanced Research Position, Inria                       |

#### ABSTRACT

Computing platforms, such as embedded systems or laptops, are built with layers of preventive security mechanisms to help reduce the likelihood of attackers successfully compromising them. Nevertheless, given time and despite decades of improvements in preventive security, intrusions still happen. Therefore, systems should expect intrusions to occur, thus they should be built to detect and to survive them.

Systems are monitored with intrusion detection solutions, but their ability to survive them is limited. State-of-the-art approaches from industry or academia either involve manual procedures, loss of availability, coarse-grained responses, or non-negligible performance overhead. Moreover, low-level components, such as the BIOS, are increasingly targeted by sophisticated attackers to implant stealthy and resilient malware. State-of-the-art solutions, however, mainly focus on boot time security, leaving the most privileged part of the BIOS—known as the System Management Mode (SMM)—a prime target.

The introduction of new solutions raises various challenges such as the security of the monitor, its ability to gather information about its target, the detection models, responding to intrusions and maintaining the availability of the system despite the presence of an adversary.

Our contribution is two-fold:

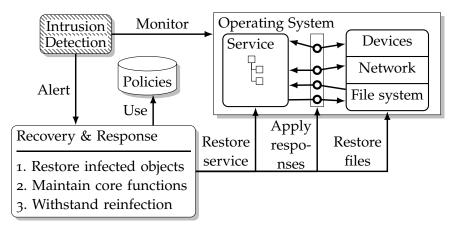

- At the OS-level, we introduce an intrusion survivability approach aimed at commodity OSs. We combine intrusion recovery and fine-grained cost-sensitive intrusion response to leverage a safe degraded mode when an intrusion is detected. Such a degraded mode prevents attackers to reinfect the system or to achieve their goals if they managed to reinfect it. It maintains the availability of core functions while waiting for patches to be deployed.

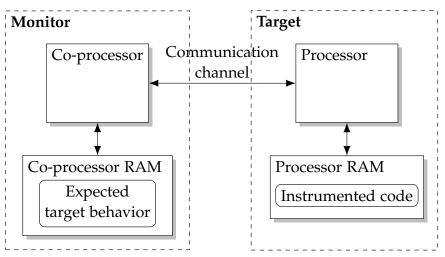

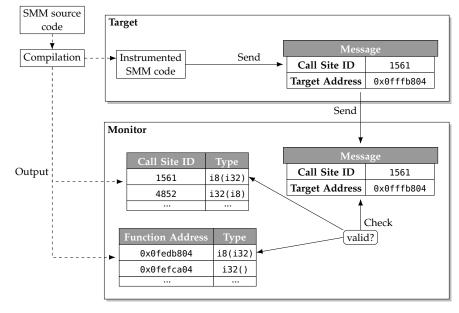

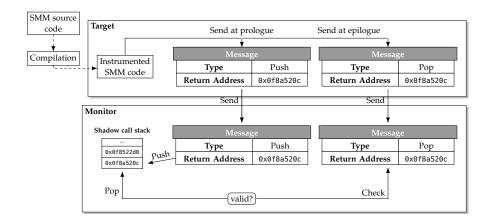

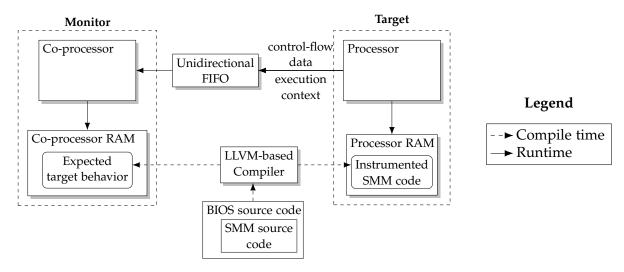

- At the BIOS level, we introduce an event-based and co-processorbased behavior monitoring approach to detect intrusions targeting the SMM on x86 platforms. We isolate the monitor using a co-processor to ensure its security and we bridge the semantic gap resulting from it by using a dedicated communication channel. This channel is used to send relevant information about the SMM code behavior that we compare with the model of its expected behavior—using invariants of its control-flow and relevant CPU registers.

**Keywords:** Information Security, Intrusion Detection, Intrusion Response, Intrusion Recovery, Intrusion Survivability

The initial idea behind this contribution was presented as a short-paper at RESSI'18 then the final work was published at ACSAC'19.

This contribution has been published at ACSAC'17.

# PUBLICATIONS

This thesis is based on previously published papers written jointly with several collaborators:

### INTERNATIONAL CONFERENCE PAPERS

- Ronny Chevalier, David Plaquin, Chris Dalton, and Guillaume Hiet. "Survivor: A Fine-Grained Intrusion Response and Recovery Approach for Commodity Operating Systems". In: *Proceedings of the 35th Annual Computer Security Applications Conference*. ACSAC'19. ACM, Dec. 2019. DOI: 10.1145/3359789.3359792.

- Ronny Chevalier, Maugan Villatel, David Plaquin, and Guillaume Hiet. "Coprocessor-based Behavior Monitoring: Application to the Detection of Attacks Against the System Management Mode". In: Proceedings of the 33rd Annual Computer Security Applications Conference. ACSAC'17. ACM, Dec. 2017, pp. 399– 411. DOI: 10.1145/3134600.3134622.

#### NATIONAL CONFERENCE PAPERS

Ronny Chevalier, David Plaquin, and Guillaume Hiet. "Intrusion Survivability for Commodity Operating Systems and Services: A Work in Progress". In: Rendez-vous de la Recherche et de l'Enseignement de la Sécurité des Systèmes d'Information. RESSI'18. May 2018.

In addition, during the three years of this Ph.D. I was employed by HP, patent applications related to the work, ideas, or solutions presented in this document were filed:

#### PATENT APPLICATIONS

- Ronny Chevalier, David Plaquin, Guillaume Hiet, and Adrian Baldwin. "Mitigating Actions". Pat. req. Hewlett-Packard Development Company, L.P. May 2018.

- Ronny Chevalier, David Plaquin, Maugan Villatel, and Guillaume Hiet. "Intrusion Detection Systems". Pat. req. Hewlett-Packard Development Company, L.P. June 2017.

• Ronny Chevalier, David Plaquin, Maugan Villatel, and Guillaume Hiet. "Monitoring Control-Flow Integrity". Pat. req. Hewlett-Packard Development Company, L.P. June 2017.

Finally, during these years I also contributed to another related area, but the following publication is not discussed in this thesis:

#### INTERNATIONAL CONFERENCE PAPER

Ronny Chevalier, Stefano Cristalli, Christophe Hauser, Yan Shoshitaishvili, Ruoyu Wang, Christopher Kruegel, Giovanni Vigna, Danilo Bruschi, and Andrea Lanzi. "BootKeeper: Validating Software Integrity Properties on Boot Firmware Images". In: Proceedings of the 9th ACM Conference on Data and Application Security and Privacy. CODASPY'19. ACM, Mar. 2019, pp. 315–325. DOI: 10.1145/3292006. 3300026. No one does everything alone. Many people contributed—sometimes even without knowing it—to this research and dissertation either intellectually, financially, logistically, or personally. This is my attempt at acknowledging their help, interest, and contributions over the years.

First and foremost, I would like to thank Herbert Bos, Joaquin Garcia-Alfaro, Karine Heydemann, and Laurence Pierre for taking an interest in my work and for accepting to be members of the jury. Especially Herbert and Joaquin for their detailed review of this manuscript.

I was fortunate to be advised by Boris Balacheff, Guillaume Hiet, Ludovic Mé, and David Plaquin. They all shared different responsibilities and duties during this work, but they all provided me with their expertise, helpful criticism, and time. I want to thank in particular Guillaume and David whose advice, comments, and discussions helped shape this dissertation and my research in many respects.

During these three years I was also part of two teams: the CIDRE team at Centrale-Supélec and the Security Lab at HP. I want to thank them for giving me an academic and industry perspective on research. I would like to thank the members of CIDRE for the scientific and technical discussions that I had with them over the years, but also all the "team building" we had at lUnchTime with the PhD students and interns. So thanks to all of them, especially to David Lanoë with his unrelenting force when hitting the cue ball, Pierre Graux with his nice collection of little orange men, Cédric Herzog with his love for Germany, Benoît Fournier who likes to keep a log of what we say, and Aïmad Berady le malicieux.

I also want to thank HP and especially the Security Lab at Bristol. Working with them gave me an insight at what it is like to work with a competent industry research lab. In particular, I would like to thank Philippa Bayley and Boris who worked hard to make sure that I could work at HP for my PhD. I would also like to acknowledge the expertise and time that Chris Dalton and Maugan Villatel provided me over the years; I was fortunate to have them as co-authors on some of my papers. I would also like to thank Vali Ali, Pierre Belgarric, Rick Bramley, Carey Huscroft, Jeff Jeansonne, and Thalia Laing for their feedback and technical discussions on my work. I am also grateful to Daniel Ellam, Jonathan Griffin, and Stuart Lees for their help in setting up and running some experiments in their malware lab, and Josh Schiffman for giving me opportunities to present my work at HP.

I would also like to thank François Bourdon and Laurent Jeanpierre. They were teachers of mine respectively in operating system and computer architecture during the first two years of my higher education. Both motivated me—probably without knowing it—to think about pursuing a career in research. François is also the reason why I went to Rennes for my studies. He told me that there was a research team in Rennes working on computer security, and he pointed me towards someone called Ludovic Mé. Unaware at the time that four years later I would be doing a PhD in this team and with Ludovic as my doctoral advisor.

I would also like to thank Jérémy and Martin who went from classmates, to friends, to best men at my wedding, and who also happened to follow a similar career path as PhD students.

Je vais terminer par remercier, en français, ma famille. En particulier, mes parents, qui m'ont toujours soutenu même s'ils ne réalisaient probablement pas que tout ce temps passé sur un ordinateur à l'époque allait être utile un jour. Puis, Léni, sans qui je ne me serais problablement jamais intéressé à l'informatique à l'origine. Enfin, Agathe, qui a relu le résumé français de ce manuscrit, et qui a surtout accepté de faire partie de ma vie.

### CONTENTS

| ΑŦ | BSTRA | ACT.    |                                                        | iii |

|----|-------|---------|--------------------------------------------------------|-----|

|    |       | ATION   | 8                                                      | V   |

|    |       |         | MENTS - REMERCIEMENTS                                  | vii |

|    |       |         | MEN15 - REMERCIEMEN15                                  |     |

| AC | CRON  | YM5     |                                                        | XV  |

| I  | PRO   | LOGUE   |                                                        |     |

| 1  | INT   | RODUC   | ΓΙΟΝ                                                   | 3   |

|    | 1.1   | Proble  | m Statement                                            | 3   |

|    |       | 1.1.1   | Preventive Security is not Sufficient                  | 4   |

|    |       | 1.1.2   | Commodity OSs Can Detect but Cannot Survive Intrusions | 5   |

|    |       | 1.1.3   | Low-Level Components Increasingly Targeted             | 6   |

|    | 1.2   | Thesis  |                                                        | 7   |

|    | 1.3   | Evalua  | tion Approach                                          | 8   |

|    | 1.4   | Outlin  | e                                                      | 8   |

| 2  | BAC   | KGROU   | nd: from x86 power-on to login prompt                  | 9   |

|    | 2.1   | BIOS a  | nd UEFI-Compliant Boot Firmware                        | 9   |

|    |       | 2.1.1   | Platform Initialization                                | 9   |

|    |       | 2.1.2   | Boot Time Security Mechanisms                          | 12  |

|    |       | 2.1.3   | Runtime Services                                       | 13  |

|    |       | 2.1.4   | System Management Mode                                 | 14  |

|    |       | 2.1.5   | Attacks Against the SMM                                | 16  |

|    | 2.2   | Operat  | ting Systems                                           | 19  |

|    |       | 2.2.1   | Kernel                                                 | 19  |

|    |       | 2.2.2   | User Space Initialization, Service Manager, Login      | 21  |

|    |       | 2.2.3   | Isolation Primitives: The Case of the Linux Kernel     | 21  |

|    |       | 2.2.4   | Limitations of OS Security Principles                  | 23  |

|    | 2.3   | Conclu  | ision                                                  | 24  |

| 3  | STAT  | ге об т | HE ART: DETECTION AND SURVIVABILITY                    | 25  |

| 5  | 3.1   | Terms   | and Concepts                                           | 25  |

|    |       | 3.1.1   | Common Terms                                           | 25  |

|    |       | 3.1.2   | Intrusion Detection                                    | 26  |

|    |       | 3.1.3   | Intrusion Survivability and Related Concepts           | 28  |

|    | 3.2   | Intrusi | on Detection for Low-Level Components                  | 29  |

|    | -     | 3.2.1   | Isolation of the Monitor                               | 30  |

|    |       | 3.2.2   | Hardware-Based Monitoring                              | 32  |

|    |       | 3.2.3   | Detection Method                                       | 35  |

|    |       | 3.2.4   | Summary                                                | 41  |

# X CONTENTS

|   | 3.3 | Intrus | sion Survivability for Commodity Operating Systems | 42 |

|---|-----|--------|----------------------------------------------------|----|

|   |     | 3.3.1  | Isolation                                          | 42 |

|   |     | 3.3.2  | Intrusion Recovery                                 | 44 |

|   |     | 3.3.3  | Intrusion Response Systems                         | 48 |

|   |     | 3.3.4  | Summary                                            | 54 |

|   | 3.4 | Concl  | usion                                              | 55 |

| п | SUR | VIVIN  | G INTRUSIONS AT THE OS LEVEL                       |    |

| 4 | INT | RODUC  | CING AN INTRUSION SURVIVABILITY APPROACH           | 59 |

|   | 4.1 | Motiv  | ration and Contributions                           | 59 |

|   | 4.2 |        |                                                    | 61 |

|   | 4·3 |        |                                                    | 62 |

|   | 4.4 |        | -                                                  | 63 |

| 5 | cos |        |                                                    | 65 |

| 5 | 5.1 | Mode   |                                                    | 65 |

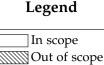

|   |     | 5.1.1  |                                                    | 65 |

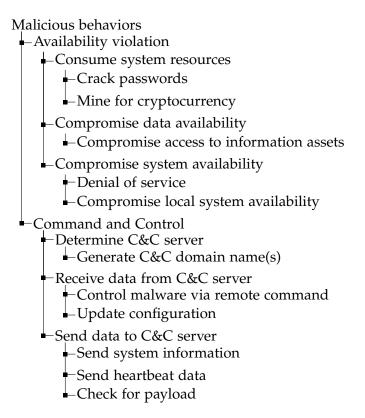

|   |     | 5.1.2  | -                                                  | 67 |

|   |     | 5.1.3  |                                                    | 69 |

|   |     | 5.1.4  | Risk Matrix                                        | 70 |

|   |     | 5.1.5  | Policy Definition and Inputs                       | 71 |

|   | 5.2 | Optim  | nal Response Selection                             | 71 |

|   | -   | 5.2.1  | Overview                                           | 71 |

|   |     | 5.2.2  | Pareto-Optimal Set                                 | 72 |

|   |     | 5.2.3  | Response Selection                                 | 72 |

| 6 | ARC | HITEC  | TURE AND IMPLEMENTATION                            | 75 |

|   | 6.1 | Archi  | tecture and Requirements                           | 75 |

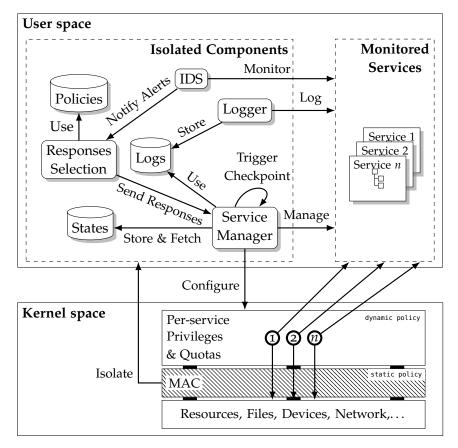

|   |     | 6.1.1  | Overview                                           | 76 |

|   |     | 6.1.2  | Last Known Safe State                              | 76 |

|   |     | 6.1.3  | Isolation of the Components                        | 76 |

|   |     | 6.1.4  | Intrusion Detection System                         | 77 |

|   |     | 6.1.5  | Service Manager                                    | 77 |

|   | 6.2 | Linux  | -based Prototype Implementation                    | 78 |

|   |     | 6.2.1  | Checkpoint and Restore                             | 79 |

|   |     | 6.2.2  | Responses                                          | 80 |

|   |     | 6.2.3  | Monitoring Modified Files                          | 81 |

|   |     | 6.2.4  | Bugs and Patches                                   | 81 |

| 7 | EVA | LUATI  | ON AND RESULTS                                     | 83 |

|   | 7.1 | Exper  | imental Setup                                      | 83 |

|   | 7.2 | Securi | ity Evaluation                                     | 84 |

|   |     | 7.2.1  | Responses Effectiveness                            | 84 |

|   |     | 7.2.2  | Cost-Sensitive Response Selection                  | 85 |

|     | 7.3  | Performance Evaluation                        | 87  |

|-----|------|-----------------------------------------------|-----|

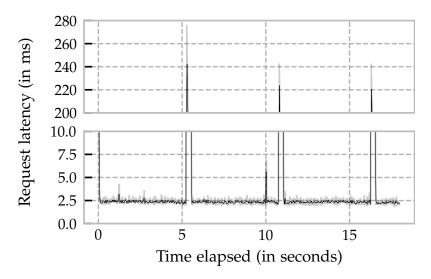

|     |      | 7.3.1 Availability Cost                       | 87  |

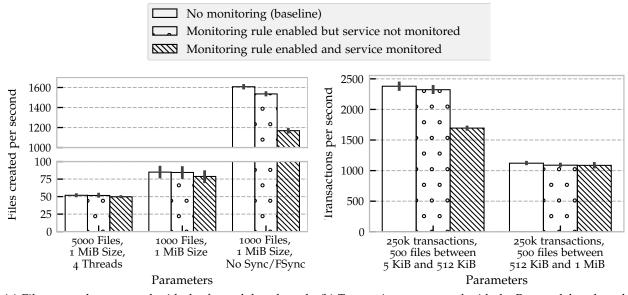

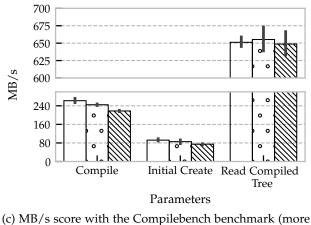

|     |      | 7.3.2 Monitoring Cost                         | 89  |

|     |      | 7.3.3 Storage Space Overhead                  | 93  |

|     | 7.4  |                                               | 93  |

|     | 7.5  | Summary                                       | 93  |

| 8   | CON  |                                               | 95  |

|     | 8.1  |                                               | 95  |

|     | 8.2  | -                                             | 97  |

|     | 8.3  | Conclusion and Future Work                    | 98  |

| III | DET  | ECTING INTRUSIONS AT THE FIRMWARE LEVEL       |     |

| 9   | INT  | RODUCING A SMM BEHAVIOR MONITORING APPROACH 1 | 03  |

| -   | 9.1  |                                               | .03 |

|     | 9.2  | Contributions                                 | .04 |

|     | 9.3  | Approach Overview and Requirements            | .06 |

|     |      | 9.3.1 Co-Processor                            | .06 |

|     |      | 9.3.2 Communication with the Monitor          | 07  |

|     |      | 9.3.3 Instrumentation of the Target           | .08 |

|     | 9.4  | Threat Model and Assumptions                  | .08 |

| 10  | DET  | ECTION METHODS AND MODELS 1                   | 11  |

|     | 10.1 | Type-Based Control Flow Integrity             | 11  |

|     |      | 10.1.1 Overview and Motivation                | 11  |

|     |      | 10.1.2 Illustrating Examples                  | 12  |

|     |      | 5                                             | 14  |

|     |      |                                               | 15  |

|     |      | 0,1                                           | 16  |

|     | 10.3 | Isolation of the Models                       | 17  |

| 11  |      |                                               | 19  |

|     |      |                                               | 19  |

|     |      | Communication Channel                         | 20  |

|     |      | 0                                             | 20  |

|     |      |                                               | 21  |

|     | 0    |                                               | 23  |

| 12  |      |                                               | 25  |

|     | 12.1 |                                               | 25  |

|     |      |                                               | 25  |

|     |      | 5                                             | .26 |

|     |      | 5                                             | 26  |

|     |      | •                                             | 27  |

|     | 12.3 | Performance Evaluation                        | 29  |

| 12.3.1 Runtime Overhead                                   |     |

|-----------------------------------------------------------|-----|

| 12.3.2 Co-Processor Performance                           | 130 |

| 12.3.3 Firmware Size                                      | 131 |

| 12.4 Summary                                              | 132 |

| 13 CONCLUDING REMARKS                                     | 133 |

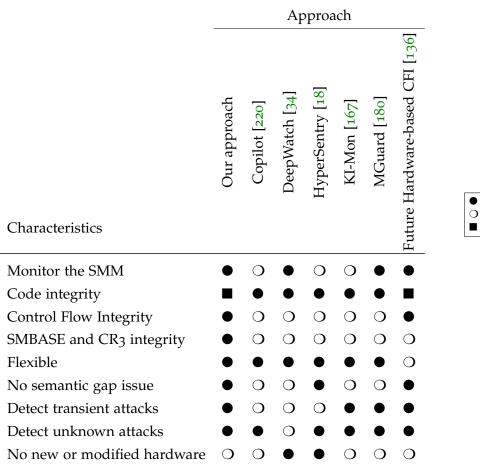

| 13.1 Discussion and Limitations                           | 133 |

| 13.2 Comparison with Related Work                         | 134 |

| 13.3 Conclusion and Future Work                           | 136 |

| IV EPILOGUE                                               |     |

| 14 CONCLUSION                                             | 139 |

| ' 14.1 Summary of the Contributions Supporting Our Claims |     |

| 14.2 Perspectives                                         |     |

| 14.2.1 Extend the Approaches and their Evaluation         |     |

| 14.2.2 Surviving and Adapting Intrusions                  |     |

| APPENDICES                                                |     |

| A MALWARE SAMPLES                                         | 145 |

| B GEM5 PARAMETERS                                         | 10  |

| U SEMJIARAMETERS                                          | 147 |

| RÉSUMÉ SUBSTANTIEL EN FRANÇAIS                            | 149 |

| BIBLIOGRAPHY                                              | 157 |

| COPYRIGHT PERMISSIONS                                     | 183 |

|                                                           | - ) |

# LIST OF FIGURES

| Figure 1.1  | The Maginot Line during WWII                                      | 4   |

|-------------|-------------------------------------------------------------------|-----|

| Figure 1.2  | Computer abstraction layers                                       | 6   |

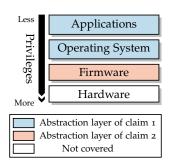

| Figure 1.3  | Computer abstraction layers covered in this dissertation          | 7   |

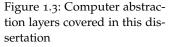

| Figure 2.1  | Simplified diagram of a recent Intel x86 architecture             | 10  |

| Figure 2.2  | UEFI PI phases and the UEFI interfaces exposed during the boot    |     |

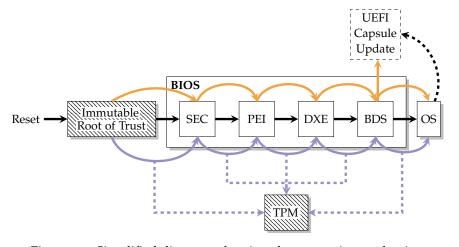

|             | sequence to the OS                                                | 12  |

| Figure 2.3  | Simplified diagram of various boot security mechanisms            | 13  |

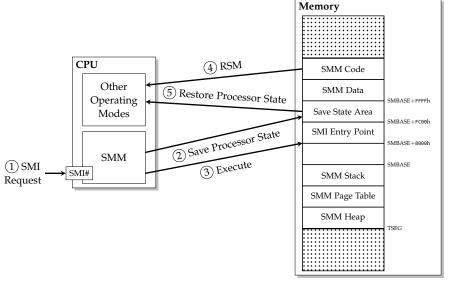

| Figure 2.4  | SMM execution flow and SMRAM memory layout                        | 15  |

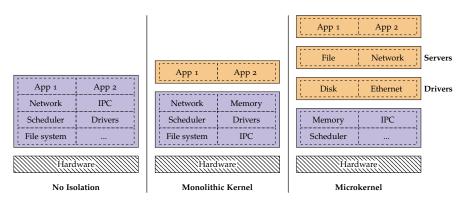

| Figure 2.5  | Difference of isolation between main kernel types                 | 20  |

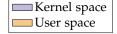

| Figure 3.1  | Timeline of a transient attack                                    | 33  |

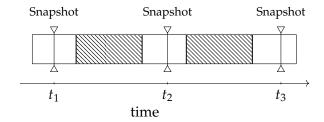

| Figure 3.2  | A prover attests its integrity via a challenge-response protocol. | 36  |

| Figure 4.1  | High-level overview of our intrusion survivability approach       | 61  |

| Figure 5.1  | Example of a non-exhaustive malicious behavior hierarchy          | 66  |

| Figure 5.2  | Example of a non-exhaustive per-service response hierarchy        | 67  |

| Figure 6.1  | Overview of the architecture of our intrusion survivability ap-   |     |

|             | proach                                                            | 75  |

| Figure 7.1  | Impact of checkpoints on the latency of HTTP requests made to     |     |

|             | an nginx server                                                   | 89  |

| Figure 7.2  | Results of synthetic benchmarks to measure the overhead of the    |     |

|             | monitoring                                                        | 91  |

| Figure 7.3  | Results of real-world workload benchmarks to measure the over-    |     |

|             | head of the monitoring                                            | 92  |

| Figure 9.1  | High-level overview of our co-processor-based monitoring ap-      |     |

|             | proach                                                            | 106 |

| Figure 10.1 | Simplified view of the stack frame of the function before the     |     |

|             | attacker overwrites functions[0]                                  | 112 |

| Figure 10.2 | Example of the mappings that the source code analysis outputs     | 114 |

| Figure 10.3 | How the monitor detects illegitimate indirect calls               | 115 |

| Figure 10.4 | How the monitor detects illegitimate returns using a shadow       |     |

|             | call stack                                                        | 116 |

| Figure 11.1 | High-level overview of our architecture that monitors the SMM     | 119 |

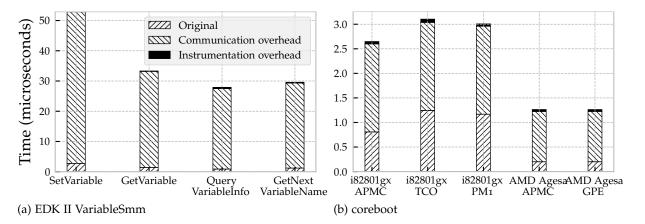

| Figure 12.1 | Time to execute SMI handlers divided between the communica-       |     |

|             | tion and the instrumentation overhead                             | 129 |

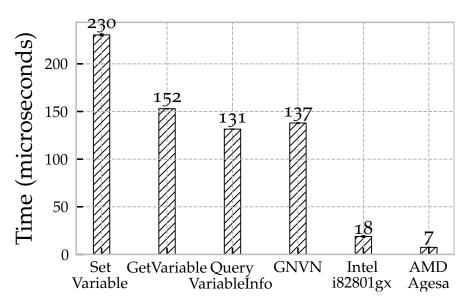

| Figure 12.2 | Time to process all the messages sent by one execution of each    |     |

| -           | SMI handler for the co-processor                                  | 131 |

|             | -                                                                 |     |

# LIST OF TABLES

| Table 2.1  | Summary of the main attacks targeting and vulnerabilities af-           | 0 |

|------------|-------------------------------------------------------------------------|---|

|            | 0                                                                       | 8 |

| Table 5.1  | Example of a $5 \times 5$ risk matrix that follows the requirements for |   |

|            | our risk assessment                                                     | 0 |

| Table 6.1  | Projects modified for the implementation of our intrusion sur-          |   |

|            | vivability approach                                                     | 9 |

| Table 7.1  | Summary of the experiments that evaluate the effectiveness of           |   |

|            | the responses against various malicious behaviors 8                     | 5 |

| Table 7.2  | Responses to withstand ransomware reinfection with their asso-          |   |

|            | ciated cost and performance for Gitea                                   | 6 |

| Table 7.3  | Time to perform the checkpoint operations of a service 8                | 8 |

| Table 7.4  | Time to perform the restore operations of a service 9                   | 0 |

| Table 8.1  | Summary of the comparison between our intrusion survivability           |   |

|            | approach and the related work                                           | 7 |

| Table 12.1 | Effectiveness of our approach against state-of-the-art attacks 12       | 8 |

| Table 12.2 | Number of packets sent during the execution of one SMI handler 13       | 0 |

| Table 13.1 | Summary of the comparison between our SMM behavior moni-                |   |

|            | toring approach and the related work                                    | 5 |

| Table A.1  | Malware used in our experiments with the SHA-256 hash of the            |   |

|            | samples                                                                 | 5 |

| Table B.1  | Parameters used with gem5 for the x86 and the ARM simulation 14         | 7 |

# LIST OF CODE SNIPPETS

| Listing 10.1 | Example of a simulated non-SMM vulnerable code                 | 113 |

|--------------|----------------------------------------------------------------|-----|

| Listing 10.2 | Example of a vulnerable function from a real SMI handler based |     |

|              | on decompiled code                                             | 113 |

### ACRONYMS

| AL                                               | After Life. 11, 12                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AP                                               | Application Processor. 11                                                                                                                                                                                                                                                                                                                                                                                              |

| ATRA                                             | Address Translation Redirection Attack. 34                                                                                                                                                                                                                                                                                                                                                                             |

|                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                        |

| BAR                                              | Base Address Register. 18                                                                                                                                                                                                                                                                                                                                                                                              |

| BDS                                              | Boot Device Selection. 11–13                                                                                                                                                                                                                                                                                                                                                                                           |

| BIOS                                             | Basic Input/Output System. iii, 6, 7, 9–19, 24, 32, 45,                                                                                                                                                                                                                                                                                                                                                                |

|                                                  | 55, 103, 104, 109, 112, 123, 125, 136, 151, 152, 154, 155                                                                                                                                                                                                                                                                                                                                                              |

| BITS                                             | BIOS Test Suite. 16, 120                                                                                                                                                                                                                                                                                                                                                                                               |

| BSP                                              | Bootstrap Processor. 9                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                        |

| C&C                                              | Command and Control. 64–66, 84, 85                                                                                                                                                                                                                                                                                                                                                                                     |

| CFG                                              | Control-Flow Graph. 38–40, 111, 128, 132, 154                                                                                                                                                                                                                                                                                                                                                                          |

| CFI                                              | Control-Flow Integrity. 34, 38–41, 105, 106, 111–113,                                                                                                                                                                                                                                                                                                                                                                  |

|                                                  | 115, 116, 118, 123, 128, 133–136                                                                                                                                                                                                                                                                                                                                                                                       |

| COW                                              | Copy-On-Write. 79                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                        |

| DAC                                              | Discretionary Access Control. 22                                                                                                                                                                                                                                                                                                                                                                                       |

| DAC<br>DDoS                                      | Discretionary Access Control. 22<br>Distributed Denial-of-Service. 64, 84                                                                                                                                                                                                                                                                                                                                              |

|                                                  | -                                                                                                                                                                                                                                                                                                                                                                                                                      |

| DDoS                                             | Distributed Denial-of-Service. 64, 84                                                                                                                                                                                                                                                                                                                                                                                  |

| DDoS<br>DKOM                                     | Distributed Denial-of-Service. 64, 84<br>Direct Kernel Object Manipulation. 37                                                                                                                                                                                                                                                                                                                                         |

| DD₀S<br>DKOM<br>DMA                              | Distributed Denial-of-Service. 64, 84<br>Direct Kernel Object Manipulation. 37<br>Direct Memory Access. 15, 32, 33, 37                                                                                                                                                                                                                                                                                                 |

| DDoS<br>DKOM<br>DMA<br>DNC                       | Distributed Denial-of-Service. 64, 84<br>Direct Kernel Object Manipulation. 37<br>Direct Memory Access. 15, 32, 33, 37<br>Democratic National Committee. 6                                                                                                                                                                                                                                                             |

| DDoS<br>DKOM<br>DMA<br>DNC<br>DOS                | Distributed Denial-of-Service. 64, 84<br>Direct Kernel Object Manipulation. 37<br>Direct Memory Access. 15, 32, 33, 37<br>Democratic National Committee. 6<br>Denial Of Service. 121                                                                                                                                                                                                                                   |

| DDoS<br>DKOM<br>DMA<br>DNC<br>DOS                | Distributed Denial-of-Service. 64, 84<br>Direct Kernel Object Manipulation. 37<br>Direct Memory Access. 15, 32, 33, 37<br>Democratic National Committee. 6<br>Denial Of Service. 121                                                                                                                                                                                                                                   |

| DDoS<br>DKOM<br>DMA<br>DNC<br>DOS<br>DXE         | Distributed Denial-of-Service. 64, 84<br>Direct Kernel Object Manipulation. 37<br>Direct Memory Access. 15, 32, 33, 37<br>Democratic National Committee. 6<br>Denial Of Service. 121<br>Driver Execution Environment. 11–13, 15, 117, 123                                                                                                                                                                              |

| DDoS<br>DKOM<br>DMA<br>DNC<br>DOS<br>DXE         | Distributed Denial-of-Service. 64, 84<br>Direct Kernel Object Manipulation. 37<br>Direct Memory Access. 15, 32, 33, 37<br>Democratic National Committee. 6<br>Denial Of Service. 121<br>Driver Execution Environment. 11–13, 15, 117, 123                                                                                                                                                                              |

| DDoS<br>DKOM<br>DMA<br>DNC<br>DOS<br>DXE<br>FIFO | Distributed Denial-of-Service. 64, 84<br>Direct Kernel Object Manipulation. 37<br>Direct Memory Access. 15, 32, 33, 37<br>Democratic National Committee. 6<br>Denial Of Service. 121<br>Driver Execution Environment. 11–13, 15, 117, 123<br>First In First Out. 121, 122, 125, 126, 129, 135, 155                                                                                                                     |

| DDoS<br>DKOM<br>DMA<br>DNC<br>DOS<br>DXE<br>FIFO | Distributed Denial-of-Service. 64, 84<br>Direct Kernel Object Manipulation. 37<br>Direct Memory Access. 15, 32, 33, 37<br>Democratic National Committee. 6<br>Denial Of Service. 121<br>Driver Execution Environment. 11–13, 15, 117, 123<br>First In First Out. 121, 122, 125, 126, 129, 135, 155<br>Intrusion Detection System. 5, 27–31, 33, 35, 41–43,                                                             |

| DDoS<br>DKOM<br>DMA<br>DNC<br>DOS<br>DXE<br>FIFO | Distributed Denial-of-Service. 64, 84<br>Direct Kernel Object Manipulation. 37<br>Direct Memory Access. 15, 32, 33, 37<br>Democratic National Committee. 6<br>Denial Of Service. 121<br>Driver Execution Environment. 11–13, 15, 117, 123<br>First In First Out. 121, 122, 125, 126, 129, 135, 155<br>Intrusion Detection System. 5, 27–31, 33, 35, 41–43, 45, 46, 50, 53, 61, 64, 66, 70, 71, 76, 77, 86, 87, 95, 98, |

| IPC<br>IR                                                    | Inter-Process Communication. 20, 22, 77<br>Intermediate Representation. 123                                                                                                                                                                                                                                                                                                             |

|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JOP                                                          | Jump-Oriented Programming. 38                                                                                                                                                                                                                                                                                                                                                           |

| КОН                                                          | Kernel Object Hooking. 37                                                                                                                                                                                                                                                                                                                                                               |

| MAC                                                          | Mandatory Access Control. 22, 76–78                                                                                                                                                                                                                                                                                                                                                     |

| MAEC                                                         | Malware Attribute Enumeration and Characteriza-                                                                                                                                                                                                                                                                                                                                         |

|                                                              | tion. 65, 67, 77, 153                                                                                                                                                                                                                                                                                                                                                                   |

| MBR                                                          | Master Boot Record. 11                                                                                                                                                                                                                                                                                                                                                                  |

| MMU                                                          | Memory Management Unit. 9, 22, 23, 35, 36, 41, 135                                                                                                                                                                                                                                                                                                                                      |

| MOO                                                          | Multi-Objective Optimization. 71, 72                                                                                                                                                                                                                                                                                                                                                    |

| NIST                                                         | National Institute of Standards and Technology. 28                                                                                                                                                                                                                                                                                                                                      |

| Or-BAC                                                       | Organization-Based Access Control. 53                                                                                                                                                                                                                                                                                                                                                   |

| OS                                                           | Operating System. iii, xiii, 3–9, 11–16, 18–25, 29, 31,                                                                                                                                                                                                                                                                                                                                 |

|                                                              | 34, 36, 42, 45, 46, 49, 50, 54, 55, 59, 61, 62, 66, 71,                                                                                                                                                                                                                                                                                                                                 |

|                                                              | 76–78, 98, 103, 104, 109, 139, 141, 142, 150–152                                                                                                                                                                                                                                                                                                                                        |

| P2P                                                          | 76–78, 98, 103, 104, 109, 139, 141, 142, 150–152<br>Peer-to-peer. 84                                                                                                                                                                                                                                                                                                                    |

| P₂P<br>PCH                                                   |                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                              | Peer-to-peer. 84                                                                                                                                                                                                                                                                                                                                                                        |

| РСН                                                          | Peer-to-peer. 84<br>Platform Controller Hub. 9–11                                                                                                                                                                                                                                                                                                                                       |

| PCH<br>PCI                                                   | Peer-to-peer. 84<br>Platform Controller Hub. 9–11<br>Peripheral Component Interconnect. 11, 18, 32, 33                                                                                                                                                                                                                                                                                  |

| PCH<br>PCI<br>PEI                                            | Peer-to-peer. 84<br>Platform Controller Hub. 9–11<br>Peripheral Component Interconnect. 11, 18, 32, 33<br>Pre-EFI Initialization. 11–13                                                                                                                                                                                                                                                 |

| PCH<br>PCI<br>PEI<br>PI                                      | Peer-to-peer. 84<br>Platform Controller Hub. 9–11<br>Peripheral Component Interconnect. 11, 18, 32, 33<br>Pre-EFI Initialization. 11–13<br>Platform Initialization. xiii, 11, 12                                                                                                                                                                                                        |

| PCH<br>PCI<br>PEI<br>PI<br>PID                               | Peer-to-peer. 84<br>Platform Controller Hub. 9–11<br>Peripheral Component Interconnect. 11, 18, 32, 33<br>Pre-EFI Initialization. 11–13<br>Platform Initialization. xiii, 11, 12<br>Process IDentifier. 21                                                                                                                                                                              |

| PCH<br>PCI<br>PEI<br>PI<br>PID<br>POSIX                      | Peer-to-peer. 84<br>Platform Controller Hub. 9–11<br>Peripheral Component Interconnect. 11, 18, 32, 33<br>Pre-EFI Initialization. 11–13<br>Platform Initialization. xiii, 11, 12<br>Process IDentifier. 21<br>Portable Operating System Interface. 22                                                                                                                                   |

| PCH<br>PCI<br>PEI<br>PI<br>PID<br>POSIX<br>PSP               | Peer-to-peer. 84<br>Platform Controller Hub. 9–11<br>Peripheral Component Interconnect. 11, 18, 32, 33<br>Pre-EFI Initialization. 11–13<br>Platform Initialization. xiii, 11, 12<br>Process IDentifier. 21<br>Portable Operating System Interface. 22<br>Platform Security Processor. 119–121                                                                                           |

| PCH<br>PCI<br>PEI<br>PID<br>POSIX<br>PSP<br>QPI              | Peer-to-peer. 84<br>Platform Controller Hub. 9–11<br>Peripheral Component Interconnect. 11, 18, 32, 33<br>Pre-EFI Initialization. 11–13<br>Platform Initialization. xiii, 11, 12<br>Process IDentifier. 21<br>Portable Operating System Interface. 22<br>Platform Security Processor. 119–121<br>QuickPath Interconnect. 121, 125, 126, 155                                             |

| PCH<br>PCI<br>PEI<br>PI<br>PID<br>POSIX<br>PSP<br>QPI<br>ROP | Peer-to-peer. 84<br>Platform Controller Hub. 9–11<br>Peripheral Component Interconnect. 11, 18, 32, 33<br>Pre-EFI Initialization. 11–13<br>Platform Initialization. xiii, 11, 12<br>Process IDentifier. 21<br>Portable Operating System Interface. 22<br>Platform Security Processor. 119–121<br>QuickPath Interconnect. 121, 125, 126, 155<br>Return-Oriented Programming. 38, 113–115 |

| SCRTM     | Static Core Root of Trust for Measurement. 13                                                                                 |

|-----------|-------------------------------------------------------------------------------------------------------------------------------|

| SEC       | Security. 11–13                                                                                                               |

| SEP       | Secure Enclave Processor. 119–121                                                                                             |

| SMI       | System Management Interrupt. xiii, xiv, 15–18, 31, 108, 109, 112–114, 116, 117, 120–122, 125–127, 129–133, 140, 142, 154, 155 |

| SMM       | System Management Mode. iii, xiii, xiv, 14–19, 24,                                                                            |

|           | 25, 30–34, 36, 37, 39–41, 55, 103–106, 108, 109, 111,                                                                         |

|           | 112, 114, 116, 117, 119–123, 125–136, 140–142, 151,                                                                           |

| SMRAM     | 153–156<br>Swetern Management BAM wiii de da an daa daa                                                                       |

| SIVINAIVI | System Management RAM. xiii, 15–19, 32, 109, 114, 115, 117, 126–128, 154                                                      |

| SMRAMC    | System Management RAM Control. 15, 16                                                                                         |

| SMRR      | System Management Range Register. 17, 18                                                                                      |

| SOO       | Single-Objective Optimization. 72                                                                                             |

| STIX      | Structured Threat Information eXpression. 69, 77                                                                              |

| STM       | SMI Transfer Monitor. 31, 142                                                                                                 |

| 01101     | 5111 Hulblet Wollton, 51, 142                                                                                                 |

| ТСВ       | Trusted Computing Base. 43                                                                                                    |

| TEE       | Trusted Execution Environment. 14                                                                                             |

| TLS       | Transient System Load. 11, 12                                                                                                 |

| TPM       | Trusted Platform Module. 13, 36, 127                                                                                          |

|           |                                                                                                                               |

| UEFI      | Unified Extensible Firmware Interface. xiii, 11–15,                                                                           |

|           | 44, 104, 125, 127, 154                                                                                                        |

|           |                                                                                                                               |

| VLAN      | Virtual Local Area Network. 83                                                                                                |

| VM        | Virtual Machine. 43, 45, 83                                                                                                   |

Part I

PROLOGUE

#### INTRODUCTION

I am convinced that there are only two types of companies: those that have been hacked and those that will be. And even they are converging into one category: companies that have been hacked and will be hacked again.

# — Robert Mueller

Director of the FBI from 2001 to 2013

Organized crime, corporate espionage, opportunistic attacks, statesponsored attacks, or activism, are all part of the threat landscape [188] that organizations and individuals have to take into account for the security of their computing platforms (e.g., laptops, servers, or smartphones). Decades of research in information security provided us with a large number of preventive security mechanisms—such as cryptography, access controls, and network security—that reduce the likelihood of these actors to successfully compromise such platforms.

Why, despite such mechanisms, do intrusions still happen? Why are we still not able to build secure systems by design? Multiple factors come into play that need to be explained to answer these questions. Before exposing the thesis behind this dissertation, we discuss these factors and the different problems that current systems face.

#### **1.1 PROBLEM STATEMENT**

Preventive security mechanisms generally aim to prevent an attacker from violating the following security properties during the execution of any system or application on those platforms:

- CONFIDENTIALITY Information must not be disclosed to unauthorized parties.<sup>1</sup> For example, some cryptography primitives enforce this property. By encrypting the content of a document, only the parties in possession of the decryption key can read it—an attacker cannot.

- **INTEGRITY** Information must not be tampered by unauthorized parties or without being detected. For example, access control mechanisms enforce this property when ensuring that only administrators can modify the configuration of a system.

- AVAILABILITY Information must be available to authorized parties when requested. For example, on modern Operating Systems

<sup>1</sup> The word party is used in the general sense and applies to entities, processes, systems, or individuals.

(OSs), unprivileged processes cannot kill core components of the OS. Otherwise, an attacker could make the system unavailable to its users.

#### 1.1.1 Preventive Security is not Sufficient

Figure 1.1: The Maginot Line during WWII

<sup>2</sup> Their strategy was to push the battles inside Belgium to avoid a front in French soil.

"Security isn't a matter of absolutes; it's a matter of picking the best set of strategies given assorted constraints and objectives." — Steven Bellovin, Thinking Security

"Real world attackers are of course not physically stopped by mathematical proofs." — Cormac Herley and P.C. van Oorschot, "SoK: Science, Security and the Elusive Goal of Security as a Scientific Pursuit"

<sup>3</sup> See the work of Fonseca et al. [112] that studied formally verified systems and found several violations of assumptions leading to various bugs. The mechanisms that we use to enforce the aforementioned properties, however, are not flawless. Indeed, much like the strong fortifications of the Maginot Line from World War II (WWII) that the Germans went around—by going through the Netherlands, Belgium, and Luxembourg—determined attackers will find a way to bypass defenses. One could easily think that France just had to expand the line to the coast, thus preventing any invasion from the Germans if they were to go through Belgium (which they did). France anticipated such an attack, but while it was straightforward to spot such weaknesses, expanding the line was not. Due to politics (Belgium was an ally when the construction started), wrong assumptions (they thought the German would not go through the Ardennes forest), time and budget constraints (hundreds of kilometers to cover with costly fortifications), only weak fortifications were eventually built along that border.<sup>2</sup>

Information security is similar in that regard. While many systems are designed with preventive security mechanisms (strong fortifications), the people designing and building these systems can make mistakes and are also constrained by time, money, or internal politics within their organization. These issues mean that information systems can only prevent the violation of security properties to a certain extent.

Furthermore, in contrast to troops on the battlefield, most threat actors do not have to take unnecessary risks, since they can attack information systems from a distance. Either via Ethernet, Wi-Fi, Bluetooth, or the cellular network, devices are exposed and can be attacked continuously, until compromised, without any attacker physically present. Thus, for example, it reduces the entry barrier for malicious individuals since it is perceived as a less risky endeavor than traditional crime.

Even formally verified secure systems will not keep determined attackers from compromising a system. While they can eliminate classes of attacks, formal proofs rely on assumptions that can turn out to be wrong—much like the Ardennes forest that France assumed that the Germans will not cross. Such wrong assumptions can then be exploited by attackers to violate security properties.<sup>3</sup>

More technically speaking, we consider that intrusions—attacks that successfully compromise a system—may happen due to the combination of two sources: technical and economic reasons. Technical reasons—such as a misconfiguration, a wrong assumption, a system not updated, or an unknown vulnerability—render a system vulnerable. Attackers, or threat actors, can exploit a vulnerability to violate the security policy of the system to achieve their goals (e.g., steal confidential information). It is common to think that by only considering technical measures (e.g., by deploying firewalls and two-factor authentication) intrusions will be stopped. Economic reasons, however, are also in play.<sup>4</sup> They are the different incentives that drive the decisions that organizations and individuals make—attackers or defenders. For example, do the benefits of an intrusion for attackers outweigh their costs in terms of time and money? (cost-benefit principle)<sup>5</sup>

Given these factors, we arrive at the conclusion that when building systems with security in mind, one must always remember that *given time*, *an intrusion will occur*. It means that we should not only build systems to prevent intrusions, but also to *detect* and *survive* them.

#### 1.1.2 Commodity OSs Can Detect but Cannot Survive Intrusions

The idea of Intrusion Detection Systems (IDSs)—systems that automatically detect intrusions—dates back to the 1980s.<sup>6</sup> Since then, more intrusion detection approaches were introduced, refined, and transferred from academia to industry. Most of today's commodity OSs are deployed with some kind of IDS—a well-known example would be anti-virus software which share many aspects of host-based IDSs.<sup>7</sup> Likewise, we find IDSs not only at the host level, but also at the network level [217]. However, as the name suggests, an IDS only focus on the detection and do not provide the ability to survive or withstand an intrusion once it has been detected.

Systems that aim at automatically withstanding intrusions exist. They are associated with various close and overlapping concepts from the literature such as intrusion tolerance, intrusion survivability, self-protecting systems, intrusion recovery, intrusion response, and intrusion resiliency. For example, the concept of intrusion tolerant systems—systems that can maintain their security properties even when some of their components are compromised—also dates back to the 1980s [116].

Most of the research on intrusion response, intrusion recovery, or intrusion survivability focuses on critical infrastructure, distributed systems, and networks [105, 157, 239, 294]. The ability of commodity OSs to withstand intrusions, however, is less studied. For example, nowadays when a system is compromised administrators have two choices while waiting for patches to fix the vulnerabilities. First, they can stop the compromised system. It would ensure the integrity and confidentiality properties, but they would lose availability. Unfortunately, the cumulative time to analyze the system to find the vulnerability, to either wait for a patch from the vendor or to develop the patch, to test the patch, and to finally deploy the patch, can be long (e.g., several days) depending on the organization. Hence, the system can be offline for a long time until it is patched. Second, administrators <sup>4</sup> See the seminal work by Anderson [8] and Anderson and Moore [9] that studies information security with an economic perspective.

<sup>5</sup> Contrary to popular belief, the Maginot Line was successful in a way—it worked as a deterrent—since the German army considered that the cost of invading France through the north-east border was too high—avoiding a cross-border assault.

<sup>6</sup> See the work of Anderson [7] and Denning [90].

<sup>7</sup> See the work of Morin and Mé [203] that studied the link between IDSs and anti-virus software.

#### 6 INTRODUCTION

can restore the system to a previous safe state. It would lose some availability (some information might be lost due to the restoration), but the system would be online. However, it would remain vulnerable and nothing would stop attackers from reinfecting the system again.

While there are solutions to help OSs to either recover from an intrusion [122, 286] or limit the impact of the intrusion on the system [20], these solutions have various limitations that hamper their deployment. For example, these solutions can incur a loss of availability by forcing a reboot of the system or an application. They can also apply coarse-grained responses that affect the rest of the system or the whole application in order to thwart one specific intrusion. Finally, they do not necessarily prevent the system from being reinfected or do not stop the attackers from achieving their goals if they manage to reinfect the system. We arrive at the conclusion that while commodity OSs can detect intrusions, current state-of-the-art solutions either from academia or industry do not allow these systems to survive intrusions once they have been detected.

#### 1.1.3 Low-Level Components Increasingly Targeted

We argued that preventive security mechanisms are not sufficient and that while today's OSs can detect some intrusions, they cannot automatically withstand them without various limitations. The state of security of applications and OSs, however, improved nonetheless since the 1980s or 1990s for example. These improvements mean that it becomes more difficult for attackers to compromise systems at the application and OS abstraction layers, or at least to do it stealthily. It results in an increased focus by sophisticated and well-resourced attackers on lower abstraction layers [118, 176, 181, 226].

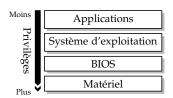

Firmware—software developed by device manufacturers—is one of such lower abstraction layers, as illustrated in Figure 1.2. It can be found in motherboards with the flash containing the Basic Input/Output System (BIOS), storage devices, network cards, graphic cards, or many other components that computers rely on. Firmware is present in all kind of platforms whether it is servers, laptops, or industrial systems.

Due to its direct access to the hardware and its often-early execution, such a low-level piece of software is highly privileged. Hence, any alteration to its expected behavior, malicious or not, can have dramatic consequences for the confidentiality, integrity, or availability of the system. We need to ensure that firmware, such as the BIOS, has not been compromised. Otherwise, attackers can control any upper layer software components, such as the OS, and can render moot any security solution present.

For example, in 2018, the malicious threat actor known as APT28, Fancy Bear, or Sednit,<sup>8</sup> used attacks against the BIOS to compromise

Figure 1.2: Computer abstraction layers

<sup>8</sup> They are believed to be responsible for the attacks on the Democratic National Committee (DNC) [3] and the French television network TV5 Monde [273]. some of its targets [226]. These attacks allowed them to have a stealthy malware implant in the BIOS that survived even if you reinstalled the OS or removed the storage devices.

While solutions exist to ensure firmware integrity (with detection and recovery) at boot time, runtime firmware code—that executes when the OS is running—has not gotten the same level of attention. Runtime firmware code security relies mainly on preventive security mechanisms (e.g., memory protections [289]). However, as concluded previously, such mechanisms are not sufficient. Without intrusion detection mechanisms, the most privileged components of our computing platforms remain unmonitored and a prime target for sophisticated attackers.

Unfortunately, low-level components introduce challenges for any intrusion detection solution. Such components must respect hard constraints in terms of resource usage to not degrade the user experience, and they are the most privileged on the platform. Hence, any modification might increase their resource usage and attackers with the same privileges might impede any monitoring.

#### 1.2 THESIS

This dissertation shows that computing platforms can be designed to detect intrusions at the firmware level and withstand intrusions at the OS level without significantly impacting the quality of service to users. First, by demonstrating that intrusion survivability is a viable approach for commodity OSs. Second, by developing a hardwarebased approach that detects attacks at the firmware level.

More precisely, in this dissertation, we introduce and validate the two following claims:

**Claim 1.** OSs can survive intrusions by restoring the infected services to a previous state and by temporarily leveraging a degraded mode with fine-grained cost-sensitive responses while waiting for more long-term fixes.

**Claim 2.** Attacks targeting highly-privileged low-level components at runtime, such as the BIOS, can be detected by using an event-based and co-processor-based behavior monitoring approach without degrading the user experience of the platform.

Each claim focuses on different abstraction layers. As illustrated in Figure 1.3, the former focuses on the OS and applications layers, while the latter focuses on detecting intrusions at the firmware layer.

#### **1.3** EVALUATION APPROACH

In this work, we proposed new approaches and architectures to tackle the aforementioned challenges. We took into account real-world constraints, and we relied on realistic use cases to drive our design choices.

In addition, we evaluated our solutions and validated our claims by developing proof-of-concept and prototype implementations that required significant development efforts. This work has thus a strong experimental focus.

For each claim, we evaluated both the security of the solution against real-world attacks and its performance (e.g., runtime overhead or storage space overhead) using real-world and synthetic benchmarks. Each time, we described our experimental setup, how we measured the performance overhead, and how we validated that our solution was successful.

Finally, we also discussed some limitations (or threats to validity) that our implementations and evaluations have, and how we addressed them. It allows us to reason about the level of confidence we have in the results and how they can be generalized.

#### 1.4 OUTLINE

This dissertation contains four parts: a prologue, two independent main parts with our contributions, and an epilogue. Part I, the prologue, contains this introduction, Chapter 2, which provides an overview and general background on the various components involved in the boot process with a security perspective, and Chapter 3, a chapter on state-of-the-art intrusion detection, intrusion recovery, and intrusion response, focusing on our use cases (i.e., host-based approaches, low-level components, and commodity OSs). As mentioned previously, the two claims, introduced in this dissertation, target different abstraction layers. Hence, we split the rest of the dissertation in two main independent parts. Part II describes our first main contribution that about how to design an OS able to survive intrusions.<sup>9</sup> Part III describes our second main contribution about how to detect intrusions in runtime firmware.<sup>10</sup> Finally, Part IV, the epilogue, summarizes our contributions and provides some perspectives for future work.

<sup>10</sup> This work was published and presented at ACSAC'17 [60].

<sup>&</sup>lt;sup>9</sup> The initial idea was presented at RESSI'18 [59], then the final work was published and presented at ACSAC'19 [58].

### BACKGROUND: FROM X86 POWER-ON TO LOGIN PROMPT

In this chapter, we describe with a security perspective what happens from the moment you press the power up button of your computer until the OS can launch basic services—such as a login prompt. We do not describe necessarily in detail these steps, but we provide the required background to understand the subsequent parts of this dissertation. While our focus is on x86 platforms, the general ideas are similar to other platforms—such as ARM.

The rest of this chapter is structured as follows. First, we provide the various steps of the initialization of the platform performed by the BIOS, why such steps are required, their complexity, and most importantly how we can and why we must guarantee security properties from the start (Section 2.1). We also mention various attacks and vulnerabilities against some runtime BIOS code. Such a background is important to understand the context and the models we use in the work described in Part III, and the reasoning behind our contributions. Second, we describe the key components of an OS and the various isolation primitives that one can use to enforce security policies on services or applications (Section 2.2). This section is important to understand Part II.

#### 2.1 BIOS AND UEFI-COMPLIANT BOOT FIRMWARE