THESIS FOR THE DEGREE OF LICENTIATE OF ENGINEERING

# Correct-by-Construction Tactical Planners for Automated Cars

JONAS KROOK

Department of Electrical Engineering Chalmers University of Technology Göteborg, Sweden, 2019

#### Correct-by-Construction Tactical Planners for Automated Cars

Jonas Krook

Copyright © 2019 JONAS KROOK All rights reserved.

ISSN 1403-266X This thesis has been prepared using LATEX.

Department of Electrical Engineering Chalmers University of Technology SE-412 96 Göteborg, Sweden Phone: +46 (0)31 772 1000 www.chalmers.se

Printed by Chalmers Reproservice Göteborg, Sweden, December 2019

### Abstract

One goal of developing automated cars is to completely free people from driving tasks. Automated cars that require no human driver need to handle all traffic situations that a human driver is expected to handle, and possibly more. Although human drivers cause a lot of traffic accidents, they still have a very low accident and failure rate that automated systems must match.

Tactical planners are responsible for making discrete decisions during the coming seconds or minute. As with all subsystems in an automated car, these planners need to be supported with a credible and convincing argument of their correctness. The planners' decisions affect the environment and the planners need to interact with other road users in a feedback loop, so the correctness of the planners depend on their behavior in relation to other drivers and the environment over time. One possibility to ascertain their correctness is to deploy the planners in real traffic. To be sufficiently certain that a tactical planner is safe by that methods, it needs to be tested on 255 million miles without having an accident.

Formal methods can, in contrast to testing, mathematically prove that the requirements are fulfilled. Hence, they are a promising alternative for making credible arguments of tactical planners' correctness. The topic of this thesis is how formal methods can be used in the automotive industry to design safe tactical planners. What is interesting is both how automotive systems should be modeled in formal frameworks, and how formal methods can be used practically within the automotive development process.

The main findings of this thesis are that it is natural to express desired properties of tactical planners in formal languages and use formal methods to prove their correctness. Model Checking, Reactive Synthesis, and Supervisory Control Theory have been used in the design and development process of tactical planners, and all three methods have their benefits, depending on the application.

Formal synthesis is an especially interesting class of formal methods because they can automatically generate a planner based on requirements and models. Formal synthesis removes the need to manually develop and implement the planner, so the development efforts can be directed to formalizing good requirements on the planner and good assumptions on the environment. However, formal synthesis has two limitations: the resulting planner is a black box that is difficult to inspect, and it is difficult to find a level of abstraction that allows detailed requirements and generic planners.

**Keywords:** Formal methods, automated cars, tactical planning, formal verification, formal synthesis, Model Checking, Reactive Synthesis, Supervisory Control Theory.

# List of Publications

This thesis is based on the following publications:

- Paper A Jonas Krook, Anton Zita, Roozbeh Kianfar, Sahar Mohajerani, and Martin Fabian. "Modeling and Synthesis of the Lane Change Function of an Autonomous Vehicle", IFAC-PapersOnLine, 14th IFAC Workshop on Discrete Event Systems (WODES), 2018.

- Paper B Jonas Krook, Lars Svensson, Yuchao Li, Lei Feng, and Martin Fabian. "Design and Formal Verification of a Safe Stop Supervisor for an Automated Vehicle", 2019 International Conference on Robotics and Automation (ICRA), 2019.

- Paper C Zahra Ramezani, Jonas Krook, Zhennan Fei, Martin Fabian, and Knut Åkesson. "Comparative Case Studies of Reactive Synthesis and Supervisory Control", 2019 18th European Control Conference (ECC), 2019.

- Paper D Jonas Krook, Roozbeh Kianfar, and Martin Fabian. "Formal Synthesis of Safe Stop Tactical Planners for an Automated Vehicle", Submitted to Workshop on Discrete Event Systems (WODES), 2020.

### Acknowledgments

I would like to thank Mattias Bengtsson for encouraging me to pursue a Ph.D. I had my doubts back then, but since I started my Ph.D. studies I have never felt that I made a bad choice; not even when I was writing this thesis.

Thanks also to Martin Fabian and Roozbeh Kianfar who have supported me with feedback, good discussions, and direction, without which I would have been completely lost.

Thank you very much Emilia for being so loyal and for supporting me at all times. I would never have gotten this far without you.

Jonas Krook Göteborg, December 2019

This work was partially supported by the Wallenberg AI, Autonomous Systems and Software Program (WASP) funded by the Knut and Alice Wallenberg Foundation.

# Acronyms

| AD:    | Automated Driving                  |  |

|--------|------------------------------------|--|

| ADAS:  | Advanced Driver Assistance Systems |  |

| ASIL:  | Automotive Safety Integrity Level  |  |

| BDD:   | Binary Decision Diagram            |  |

| DES:   | Discrete Event System              |  |

| DL:    | Deep Learning                      |  |

| E/E:   | Electronics or Electrical          |  |

| EFSM:  | Extended Finite State Machine      |  |

| FSM:   | Finite State Machine               |  |

| GR(1): | General Reactivity of Rank 1       |  |

| LSM:   | Lateral State Manager              |  |

| LTL:   | Linear Temporal Logic              |  |

| MC:    | Model Checking                     |  |

| ML:    | Machine Learning                   |  |

| RS:    | Reactive Synthesis                 |  |

| SCT:   | Supervisory Control Theory         |  |

|        |                                    |  |

# Contents

| Al | ostrac |                                                                                                                    | i |

|----|--------|--------------------------------------------------------------------------------------------------------------------|---|

| Li | st of  | Papers ii                                                                                                          | i |

| Ac | cknow  | edgements                                                                                                          | v |

| Ac | crony  | is v                                                                                                               | i |

| I  | 0      | erview 1                                                                                                           | L |

| 1  | Intro  | duction                                                                                                            | 3 |

|    | 1.1    | Hypothesis                                                                                                         | 3 |

|    | 1.2    | Research questions                                                                                                 | 3 |

|    | 1.3    | Contributions                                                                                                      | 3 |

|    | 1.4    | Method                                                                                                             | ) |

|    | 1.5    | Outline                                                                                                            | ) |

| 2  | Ном    | safe? 11                                                                                                           | L |

|    | 2.1    | Driving Around the World                                                                                           | 1 |

|    | 2.2    | ISO26262                                                                                                           | 2 |

|    | 2.3    | Saving Some Time 14                                                                                                | 1 |

| 3  | Forr   | al Methods 15                                                                                                      | 5 |

|    | 3.1    | Automata                                                                                                           | 5 |

|    | 3.2    | $LTL \dots $ | 3 |

|    | 3.3    | Terminology                                                                                                        | 7 |

|    | $3.4 \\ 3.5 \\ 3.6$                     | Model Checking .       18         Reactive Synthesis       19         Supervisory Control Theory       21                                  | 9           |

|----|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 4  | <b>Corr</b><br>4.1<br>4.2<br>4.3<br>4.4 | ect-by-Construction Tactical Planners21Inspection of Results20Verification vs. Synthesis21Abstraction of States30Modeling Considerations31 | 6<br>8<br>0 |

| 5  | <b>Con</b><br>5.1                       | clusions     3       Future Works     38                                                                                                   |             |

| 6  | Sum                                     | mary of Included Papers 39                                                                                                                 | 9           |

| Re | feren                                   | ces 4                                                                                                                                      | 1           |

| 11 | Pa                                      | pers 47                                                                                                                                    | 7           |

| Α  | Мос                                     | leling and Synthesis of a Lane Change Function A                                                                                           | 1           |

|    | 1                                       | Introduction                                                                                                                               | 3           |

|    | 2                                       | Preliminaries                                                                                                                              | 5           |

|    |                                         | 2.1 Extended Finite-State Machines                                                                                                         | -           |

|    |                                         | 2.2 Controllability A'                                                                                                                     |             |

|    |                                         | 2.3 BDD-based Synthesis A'                                                                                                                 |             |

|    | 0                                       | 2.4 Compositional Synthesis                                                                                                                |             |

|    | 3                                       | System Description and Modeling                                                                                                            |             |

|    | 4<br>5                                  | Specification                                                                                                                              |             |

|    | 5<br>6                                  | Conclusion                                                                                                                                 |             |

|    |                                         | rences                                                                                                                                     |             |

|    |                                         |                                                                                                                                            | Ŭ           |

| В  |                                         | nal Verification of a Safe Stop Planner B:                                                                                                 |             |

|    | 1                                       | Introduction                                                                                                                               | -           |

|    | 2                                       | System architecture                                                                                                                        | -           |

|    | 3                                       | Supervisor DesignB'3.1Formal requirementsFormal requirements                                                                               |             |

|    |                                         | 3.1       Formal requirements       Bit         3.2       Modeling in Stateflow       Bit                                                  |             |

|    |                                         | 3.3       Model checking       B1                                                                                                          |             |

|    | 4                                       | Results and Discussion                                                                                                                     |             |

|    |                                         | 4.1 Formal Verification                                                                                                                    |             |

|    |                                         | 4.2 RCV Experiment                                                                                                                         |             |

|    |                                         |                                                                                                                                            |             |

|   | 5        | Conch   | usion and Future Work                                                                 |

|---|----------|---------|---------------------------------------------------------------------------------------|

|   | Refe     | rences  | B16                                                                                   |

| с | Com      | parativ | ve case studies of RS and SCT C1                                                      |

|   | 1        | -       | uction                                                                                |

|   | 2        | Prelim  | ninaries                                                                              |

|   |          | 2.1     | Reactive Synthesis                                                                    |

|   |          | 2.2     | Supervisory Control Theory                                                            |

|   | 3        | Stick-l | Picking Game                                                                          |

|   |          | 3.1     | TuLiP                                                                                 |

|   |          | 3.2     | Supremica                                                                             |

|   | 4        | Auton   | omous Driving                                                                         |

|   |          | 4.1     | TuLiP                                                                                 |

|   |          | 4.2     | Supremica                                                                             |

|   | <b>5</b> | Comp    | arison                                                                                |

|   | 6        | Conclu  | usion                                                                                 |

|   | Refe     | rences  |                                                                                       |

| D | Forn     | nal Svn | thesis of Safe Stop Planners D1                                                       |

| - | 1        | •       | uction                                                                                |

|   | 2        |         | $\mathbf{D}_{\mathbf{D}}$                                                             |

|   | _        | 2.1     | Supervisory Control Theory                                                            |

|   |          | 2.2     | Reactive Synthesis                                                                    |

|   | 3        | Scenai  | rio                                                                                   |

|   |          | 3.1     | Transport mission                                                                     |

|   |          | 3.2     | Safe stop                                                                             |

|   |          | 3.3     | Architecture                                                                          |

|   |          | 3.4     | Requirements                                                                          |

|   | 4        | Result  | s                                                                                     |

|   |          | 4.1     | Vehicle, trajectory planner, and controller                                           |

|   |          | 4.2     | Requirements                                                                          |

|   |          | 4.3     | Synthesis Result                                                                      |

|   | 5        | Conclu  | usion $\dots$ |

|   |          |         |                                                                                       |

# Part I Overview

# CHAPTER 1

### Introduction

One goal of developing automated cars is to completely free people from driving tasks, and the introduction of such cars is thought to bring several benefits and new application areas. For instance, as many people spend a sizable part of their time commuting to and from work in their own cars, one major benefit is to let people spend that commuting time on more fun things than driving on congested urban roads. Another example is that automated cars would allow people who currently cannot or should not drive to get access to better personal mobility, for instance elderly people or people with visual impairments [1]-[4].

Automated cars that require no human driver are technologically very advanced machines, and they need to handle all traffic situations that a human driver is expected to handle, and possibly more. However, this level of automation is difficult to achieve [5], so automated cars that still partly rely on an active human driver might be an important step to making traffic safer [6]. Such cars with less advanced automation can be beneficial for drivers in other ways as well, for instance, cars that keep themselves at a certain speed and in lane with driver supervision might be considered a benefit to some drivers.

The amount of human involvement in the driving tasks is the main factor that affects the difficulty to implement an automated vehicle, so there is a classification system which categorizes vehicles into one of 6 levels depending on required driver involvement (see Table 1.1) [7]:

Level 0 The car does not help with driving, so the driver performs all tasks related to controlling speed, steering, etc.

Level 1 The car steers or controls speed; adaptive cruise control is an example.

- Level 2 The car steers and controls speed, but the driver needs to continuously monitor it; cars that stay in lane or parks themselves are examples.

- Level 3 The car steers and controls speed, but the driver might need to take over control in difficult situations; cars in this level might for instance overtake on their own.

- Level 4 The car completely manages the driving tasks within certain operational conditions; a car that can only drive on dry highways without human intervention would be in this level.

- Level 5 The car completely manages the driving tasks; there need not be anyone in the car.

Related to the automation levels are Advanced Driver Assistance Systems (ADAS) and Automated Driving (AD) systems. In this thesis, ADAS refer to functionality that help the driver with the driving tasks in Level 0 to 2, and AD systems refer to functionality that perform the driving task in Level 3 to 5.

| SAE Level | Name                   | Monitoring agent |                         |

|-----------|------------------------|------------------|-------------------------|

| Level 0   | No automation          | Driver           |                         |

| Level 1   | Driver assistance      | Driver           | Hands on                |

| Level 2   | Partial automation     | Driver           | Hands off               |

| Level 3   | Conditional automation | System           | Eyes off                |

| Level 4   | High automation        | System           | Mind off                |

| Level 5   | Full automation        | System           | Steering wheel optional |

Table 1.1: SAE automation levels [7].

Reasons for both ADAS and AD are to relieve the driver from driving tasks and to increase traffic safety. Some ADAS, like adaptive cruise control, are supposed to free the driver from controlling speed and distance, and instead let the driver focus on planning ahead, and in that way facilitate safer driving. Other ADAS correct for errors, of which autonomous emergency braking is an example; it overrides the driver's commands and automatically brakes the vehicle if the system believes that the driver cannot avoid a collision. The AD systems are supposed to increase traffic safety by removing the driver altogether.

Although human drivers cause a lot of traffic accidents, they still have a very low accident and failure rate [8]. This low rate poses difficulties when both ADAS and AD systems are developed; if these systems shall increase traffic safety, then their introduction cannot cause higher risk of accidents than what is expected without them. Hence, the low accident rate of human drivers effectively puts requirements on how fault tolerant the ADAS and AD systems need to be. However, this does not mean that all ADAS and AD systems have the same requirements on fault tolerance. Systems in higher SAE levels generally require higher fault tolerance. For instance, a collision warning system in Level 0 can easily be ignored by the driver and a high false warning rate can therefore be tolerated since it does not affect the safety significantly. The occurrence of erroneous and excessive braking in a Level 3 system, on the other hand, must be rare lest the vehicle runs an undue risk of being rear-ended. A more detailed motivation for this is given later in Section 2.2.

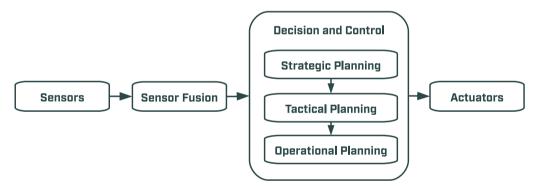

When human driving tasks are taken over by automation it is done so by several electronics or electrical (E/E) subsystems, each with a specific sub-task. For the purpose of this thesis the automated car's E/E subsystems are broken up into four categories according to the overview shown in Figure 1.1. Starting from the left, the sensors perceive the vehicle's surroundings and turn that into sensor-specific semantic information. For instance a camera can find other vehicles in an image. The information from each separate sensor is then passed on to the sensor fusion subsystem. It takes in information from all the sensors and merges it to produce a more accurate estimation of the environment. Based on the fused sensor information, decision and control decides which actions to take and how. Decision and control passes on its decisions to the actuators in form of, e.g., paths and acceleration commands. The actuators convert the decisions to, e.g., steering torque and brake torques.

Figure 1.1: System overview.

All four subsystems can be further divided, but here it is only interesting to consider decision and control which can be divided into strategic, tactical, and operational planning [9], as can be seen in Figure 1.1. Strategic planning refers to planning for long time horizons, such as route planning. Tactical planning refers to planning during the coming seconds or minute, which would include discrete decisions such as when to do lane changes or whether to stop at an intersection. The operational planning is performed on the scale of milliseconds up to a second, and examples can be speed control and sudden avoidance maneuvers.

All four subsystems in Figure 1.1 need to be supported by a credible and convincing

argument of their correctness [10]. Since the subsystems have different tasks and solve them with widely different algorithms their correctness are also ascertained with different methods. The actuators and the operational planning subsystems are analyzed and verified with methods from control theory, which provides tools for asserting stability, and determining maximal tracking error, etc. This is a field with mature analytical methods developed from the 1930's and onward. The sensors and sensor fusion subsystems can use a statistical approach to verify its correctness in open-loop simulations. Given a recorded input an accuracy of the estimates compared to ground-truth data can be calculated. The main issue for AD systems is that a lot of data is needed [8], and that reliable ground-truth data or annotations can be laborious to attain.

Many of the analytical tools from control theory are not suitable for discrete decisions made by the tactical planners that are the main concern of this thesis. For example, analytical proofs of stability and reachability for continuous or discrete time systems with continuous states cannot be used on discrete state systems. The open-loop simulations that are useful for the sensing parts can also not be used to the same extent for the tactical planning subsystem. This so since the planner's decisions affect the environment and the planner needs to interact with other road users in a feedback loop. A recording of a traffic scenario will therefore only be a valid basis for a convincing correctness argument if the planners take the exact same decisions as the vehicle did during the recording; an implausible feat for the millions of miles needed as indicated by Kalra and Paddock [8]. Instead of simulations, the tactical planners can be verified as part of the complete vehicle during real driving. However, this does not scale well since failures during the verification will add millions of kilometers to the needed total mileage [10]. This thesis explores ways to limit the needed verification effort of tactical planners, and tries to focus on the correctness of their construction to achieve fault tolerant planners.

The above gives some indication on how much effort that is needed to verify that a functionality is safe enough from a complete vehicle level. However, needed safety effort must be known already during the development of the E/E subsystems. It can be difficult to reason about and argue for how fault tolerant these individual ADAS or AD E/E subsystems need to be, so the automotive industry has developed the functional safety standard ISO26262 [11] to establish best practices to deal with the risks introduced by safety-critical functionality. In broad strokes, the standard defines a systematic process to judge the safety criticality of different end effects that can be caused by different E/E system faults. The safety criticality measure has 5 different levels and is called Automotive Safety Integrity Level (ASIL). Based on the ASIL for an end effect, the standard then recommends best practice methods to use to ensure a sufficient level of safety when designing, implementing, verifying, and validating parts of the E/E-system that can cause that end effect if they experience a failure. For instance, one possible end effect of a fault could be that the vehicle does not accelerate when the driver presses the accelerator pedal, and the fault might be a sensor that fails to measure the position of the accelerator pedal correctly. A vehicle that cannot accelerate has a problem, but maybe not a safety critical one, and in that case the ASIL would be low. A low ASIL would in turn mean that the accelerator pedal sensor could be developed with less safety effort and still keep the risk of harm at a sufficiently low level.

ISO26262 recommends two verification methods: *reviews* and *testing*. Reviews are qualitative and requires staff to go through and inspect work products. Testing is quantitative and measures the effect when systems are exposed to certain inputs. Both these verification methods can be applied to large parts of the development process [11], but neither of them can provide proofs of correctness; they can only find faults, not an absence of them [12]. Also, when the design or implementation of a part is changed the review and testing has to be performed again, and with higher ASIL the reviews and testing are recommended to be more thorough. This might be a bottleneck if more advanced ADAS and AD systems are to be developed. More advanced could mean several things, but two examples could be more capabilities or less driver involvement. Both these advances incur more work spent on reviews and testing, which is discussed more in Section 2.2.

The ISO26262 standard mentions one class of methods and tools that can alleviate some burdens of reviews and testing. These are called *formal methods* [12], [13], and can, in contrast to reviews and testing, mathematically prove that the requirements are fulfilled. (A caveat being that this statement holds for a model of the system, so any modeling errors void the correctness proof.) At their core, formal methods have a formal language that has well defined and unambiguous semantics. The formal language is used to formalize the requirements. After the requirements are formalized there are mainly two subclasses of formal methods from which to choose to continue the process; formal verification and formal synthesis.

Formal verification needs a formal model of the implementation and possibly the environment with which it interacts [12]. This model can be the actual software code, a simplified abstraction thereof, or a very simple model of the intended functionality of the item; it depends on which requirements are being verified against. When the formal requirements and the formal model are available the formal verification tool can search for counterexamples. If none are found, then the model fulfills the requirements. Because formal verification comes with a proof or a counterexample, less effort needs to be spent on reviews and tests.

Formal synthesis, on the other hand, does not have a model of the implementation included in the formal model, but it requires a model of the environment [13], [14]. Based on the formal requirements and the formal model, formal synthesis automatically creates a correct-by-construction implementation. This has the advantage over formal verification that the implementation does not need to be performed manually; an error prone and time consuming process. Also, changes in the requirements does not necessarily incur any manual reimplementation.

Formal methods, especially formal verification, have been used successfully in industrial applications [15]–[17]. They have a clear potential also in the automotive industry to

increase the quality of the safety work, as well as decrease development time and cost. However, except in the case of software verification, it is not established in any large extent as to what parts of the automotive development process that can benefit from formal methods. Potential pitfalls and limitations are also not well explored.

The topic of this thesis is how formal methods can be used in the automotive industry to design safe tactical planners. What is interesting is both how automotive systems should be modeled in formal frameworks, and how formal methods can be used practically within the automotive development process.

### 1.1 Hypothesis

The hypothesis of this thesis starts in the belief that formal methods, and especially formal synthesis, can be applied in automotive development processes to generate useful and meaningful correct-by-construction tactical planners. Such formal methods should be beneficial because they alleviate drawbacks of other methods that cannot provide correctness proofs, specifically the processes of reviews and testing. However, since formal methods, and especially formal synthesis, does not seem to be widely adopted for generation of tactical planners for automated cars there probably are limitations or obstacles that hinder the adoption. These potential limitations and obstacles are investigated in this thesis.

Furthermore, with discrete systems operating in continuous domains there must be a mapping, or abstraction, from continuous states to discrete states. This abstraction affects how a tactical planner can operate, and selecting the wrong level of abstraction could cause synthesis to generate useless or trivial planners, or fail to generate planners at all. This thesis investigates whether and how the abstraction of the continuous domain affects the usefulness of the tactical planners.

### 1.2 Research questions

Based on the hypothesis, this thesis aims to answer the following research questions:

- What are the current limitations of formal synthesis that currently hinders industrial adoption for automotive systems?

- What level of abstraction is possible to use for automotive systems, and will that level facilitate meaningful and non-trivial planners?

- To what problems can synthesis and verification be applied?

### 1.3 Contributions

The main contributions of this thesis are:

- It identifies the difficulty to inspect the result of synthesis as an obstacle to adoption of formal synthesis.

- It identifies a conflict between the desire to express detailed requirements and to generate generic tactical planners.

- It provides insights into how verification and synthesis models differ when it comes to separation of environment, requirements, and planner.

- It determines that the differing syntax and semantics of the modeling paradigms have little effect on the synthesized planners. However, a few characteristics of the synthesis results of the different paradigms are important to consider when formal synthesis is applied to a problem.

# 1.4 Method

The work of this thesis has been carried out in the form of several case studies connected to tactical planners for automated cars. Realistic requirements and scenarios have been formulated in each case, and formal methods have been used to design correct-byconstruction tactical planners. These planners have then been evaluated by simulations, experiments, and visual inspections. The evaluations and comparisons have mainly been qualitative.

# 1.5 Outline

This thesis is divided into two parts. Part I gives an introduction to safety of automated cars, explains fundamentals of formal methods, and puts the appended papers into context. Part II contains the appended papers that form the basis of this thesis.

Part I consists of the following chapters: Chapter 2 presents the problem of credibly arguing for the safety of automated cars. Chapter 3 goes through the fundamental concepts of formal methods that are used in later chapters. The appended papers are discussed and put into perspective in Chapter 4. Chapter 5 concludes the findings in this thesis and presents future challenges. Finally, Chapter 6 gives short summaries of the appended papers.

# CHAPTER 2

#### How safe?

In order to deploy AD systems on public roads, the automotive industry needs to present compelling arguments that the cars are sufficiently safe [10]. One way of providing such arguments, as mentioned in Chapter 1, is to follow the process recommended by ISO standard 26262 [11]. This in practice means that for certain safety requirements the probability of failure should be less than  $10^{-9}$ . Achieving such level of integrity and correctness makes any approach only based on simulation, field testing and statistical data inadequate and unrealistic. As noted by [8], if a fleet of 100 autonomous vehicles drives 24 hours/day, 365 days/year, at an average speed of 25 mph, it takes 400 years to demonstrate with 95% confidence that their failure rate is 20% better than the human driver failure rate of 1.09 fatalities per 100 million miles (US, 2013). Furthermore, if there is a failure during this verification, the amount of required field testing is increased [10].

This chapter gives an overview of how many miles have been driven by some automated car systems and an introduction to the functional-safety standard ISO 26262.

#### 2.1 Driving Around the World

Several companies working with automated cars are publishing safety reports that detail their efforts to ascertain safety [18]–[21]. They are also publishing how long they have driven with their field test vehicles (or customer vehicles in the case of Tesla): Waymo 10 million miles [22]; Tesla 1 billion miles [23]; Yandex 1 million miles [24]; Uber at least 2 million miles [25], [26]. All of these companies, except Tesla, are field testing SAE Level 4 or 5 cars. Tesla's system is available for consumers and relies on the driver as a fall-back, so it is at most a SAE Level 3 system (cf. Table 1.1).

Is this amount of driving enough to credibly argue that the systems are safer than a human driver? To be 95% sure that an automated car's systems are at least as safe as a human driver (in the U.S.) the systems need to drive 255 million miles with no fatalities [10]. As can be seen above, most automated-car companies fall short on this target with at least one order of magnitude. Tesla seems to fare well since they have tested on 4 times as many miles as required. However, fatalities increase the required number of miles; 402 million miles required for one fatality and 535 million miles for a second fatality, etc [10]. And there have been fatalities where, for instance, Tesla and Uber cars have been involved [27], [28]. An independent report also argues that Tesla cars with active AutoPilot are less safe than when AutoPilot is inactive [29].

The numbers above also assumes that the systems have a single occupant [10]. When the cars are put into use one has to consider the expected number of occupants and increase the number of miles driven accordingly.

A further caveat is that the statistical argument of number of miles driven without fatalities must be based on one and the same version of the system, a prerequisite which is clearly void for Tesla [30], but it is also unlikely that the other actors have been driving millions of miles for several years without updating their systems.

With these mileages in mind, it seems infeasible to base a correctness argument solely on the amount of miles driven by an ADAS or AD system. The question is then: what is the alternative?

### 2.2 ISO26262

As mentioned above and in Chapter 1, it can be difficult to reason about and argue for how fault tolerant individual subsystems of ADAS or AD systems need to be, so the automotive industry has developed the functional safety standard ISO26262 to establish best practices to deal with the risks introduced by safety-critical functionality [11]. Simply put, the process of the standard starts with a definition of the functionality to be developed (called the 'item' in the standard), and then a hazard analysis is performed for the item. During the hazard analysis potential malfunctions of the item are considered, and if they are possible sources of harm they are considered hazards. Each hazard is considered in all the operational situations of the item, and the combination of the hazard and an operational situation is called a hazardous event. The purpose of the standard is to provide best practice recommendations on how to reduce the risk of all hazardous events to an acceptable level<sup>1</sup>.

For each hazardous event it is judged how severe the consequences of that event can be (severity), how often the vehicle is in the operational situation of the hazardous event (exposure), and how difficult it is for an agent other than the safety-critical functionality

$<sup>^1 \</sup>rm Note that there is still a non-zero risk for the occurrence of the hazardous event; there is no such thing as 100 % safe.$

to detect and counteract the hazardous event (controllability). For instance, one identified possible hazard could be the omission of braking when approaching a stationary vehicle. The severity is decided by the collision speed, and the exposure is decided by the probability of a stationary vehicle on a road where such speed is held. The controllability is based on how likely the driver is to brake, which, among other things, is influenced by the automation level.

The purpose of the standard is to prevent the hazardous events, and the means with which to prevent them are specified in safety goals. To prevent fatal collisions with pedestrians, for instance, a safety goal might be to limit the top speed of the vehicle to 30 km/h. For every identified hazardous event, the estimated severity, exposure, and controllability are combined to form an automotive safety integrity level (ASIL). The ASIL is transfered to the safety goals that are attached to a hazardous event, and the ASIL will guide what safety efforts that are needed during development to ascertain the fulfillment of each safety goal.

When all safety goals have been formulated, the standard follows a V-model: an architecture with subsystems is developed for the item, and the safety goals are broken down into functional safety requirements, allocated to the subsystems. The subsystems are further split into hardware and software components by hardware and software architectures. Correspondingly, the functional safety requirements are further refined into lower level safety requirements allocated to the hardware and software components. All the architectural components (subsystems, hardware and software components) are then implemented, verified, and validated in accordance with the safety requirements. Here, the ASIL of the safety goal has a direct effect on the effort as the standard prescribes recommended implementation, verification, and validation activities based on the ASIL, and, in general, the ASIL of a safety goal is inherited to all the lower level requirements that refines it.

From a functional safety point of view, ADAS and AD systems are increasingly difficult to develop because of three mechanisms. Firstly, as desired operational situations and capabilities of the systems are expanded, so is the complexity of the technical solutions. Even if the ASIL of a specific component is the same, the increased complexity means more safety effort, and this typically does not scale linearly. Secondly, expansion of operational situations means more hazardous events with higher severity and exposure. These increases lead to higher ASIL, and thus greater safety effort. Thirdly, the goal is to remove the driver, or at least reduce the driver's involvement in the driving tasks. This removal or reduction causes lower controllability [31], which also means higher ASIL.

The ASIL is rightfully high as an effect of these three mechanisms since it is difficult to refine requirements that are complete with respect to the safety goal, and it is difficult to implement fault free code. High ASIL makes sure that requirement refinement, implementation, verification, and validation are all performed according to strict processes that minimize the risk of faults. However, these processes cause long and costly development. For instance, implementation and verification of high-ASIL software requires, among other things, extensive design reviews of the code and testing of almost every input-output combination to assure that the software requirements are fulfilled to high enough level. But these tasks are cumbersome and require involvement from many people, will still miss faults, and have to be repeated when requirements change [12].

# 2.3 Saving Some Time

Evidently, the approach of ensuring safety solely by driving many million miles is expensive and time consuming. Hence, there are incentives to limit the amount of miles required to assure a high confidence of correctness. For instance, limiting updates and failures of a system after field tests have started by ensuring that the system is correct from the start saves both time and lives. ISO 26262 provides a processes that can support that aim by judging risks in different situations, and how to mitigate them to acceptable levels. Part of the process is to break down the safety-critical requirements to individual components. The breakdown can be beneficial in the development work since the efforts to ensure safety can start before all components can be integrated into one system and tested as a whole in a field test. However, the extensive reviews and testing needed for components with the highest ASIL are imperfect and expensive in time and money. This is a limiting factor for SAE levels 4 and 5, as there is likely several components with the highest ASIL.

What can be done to construct systems that are correct from the start and limit the efforts put into review and testing? The ISO 26262 standard mentions formal methods as one class of methods that can be used to ascertain correctness of the developed systems. However, the standard does not instruct how formal methods can be applied, so before such methods can be applied within the development process of tactical planners it must be known what problems the formal methods can solve and how to apply them to the applicable problems. This thesis attempts to evaluate how problems in the development of tactical planners in automated cars can be solved by formal methods and how some formal methods compare in terms of benefits and drawbacks. A central question is whether there are any obstacles to adopting formal methods, and especially formal synthesis, as a tool to develop provably correct tactical planners for automated cars.

# CHAPTER 3

### Formal Methods

Formal methods are a class of methods that make it possible to reason about correctness of systems. A key property of these methods is that requirements and models are expressed in semantics that are very precise and unambiguous.

There are several formal semantic systems. Here we are interested in systems that can express temporal properties since we want to be able to reason about a vehicle's behavior over time. Examples of other systems are systems that reason about the correctness of a program's output only given the current input.

### 3.1 Automata

Temporal properties can be expressed in formal languages. A formal language is a set of strings constructed from letters of an alphabet according to well-formed and unambiguous rules. Connected to formal languages are finite state automata that can be used to model formal languages.

Finite state automata consists of states and transitions between them. The transitions between the states are labeled with letters from the alphabet and defines which inputs a certain state can consume and how the state changes with that input.

**Definition 1:** A finite state automaton is a tuple

$$A = \langle Q, \Sigma, \delta, q_0, F \rangle,$$

where Q is a finite set of states,  $\Sigma$  is a finite set of symbols, the alphabet,  $q_0 \in Q$  is the initial state, and  $F \subseteq Q$  is the accepting states.  $\delta : Q \times \Sigma \to Q$  is the transition function, a partial function defining which states are connected and which inputs causes these transitions.

In connection with the accepting states F, a finite state automaton has an acceptance condition that states which strings are accepted by the automaton. A string is generated by starting with an empty string in the initial state  $q_0$  and then concatenating  $\sigma \in \Sigma$ for every new transition taken. The subset of strings generated this way that fulfills the acceptance condition is the formal language defined by a specific automaton.

# 3.2 LTL

Linear Temporal Logic (LTL) is a formal logic capable of expressing temporal properties. In addition to atomic propositions in the set AP and standard propositional logic operators, LTL includes temporal operators [32]. The temporal operators ' (next),  $\Box$  (always), and  $\Diamond$  (eventually) are used in this thesis. These temporal operators can be used to express, for instance as done in Paper B, that if one of a vehicle's subsystems fails, then eventually the vehicle shall stop safely at the side of the road.

An LTL formula can be converted into a Büchi automaton that accepts the language expressed by the LTL formula [33], [34]. A Büchi automaton is an automaton that accepts all strings that visit the accepting states an infinite number of times. A Büchi automaton that represents an LTL formula has  $2^{AP}$  as its alphabet — the set of all sets of atomic propositions. Hence, the formal language of an LTL formula is a set of infinite strings, where each letter is a set of the atomic propositions that are true in that particular state.

If LTL formulae are interpreted over infinite runs of a program they can be used to check properties that hold for that program. For this purpose a program is translated into a transition system, of which Kripke structures are one subclass.

**Definition 2:** A Kripke Structure is a tuple

$$M = \langle S, I, R, AP, L \rangle,$$

where S is a set of states,  $I \subseteq S$  is a set of initial states,  $R \subseteq S \times S$  is a transition relation, AP is a set of atomic propositions, and  $L: S \to 2^{AP}$  is a labeling function that defines the atomic propositions that are true in each state.

LTL formulae can be evaluated over infinite runs on a Kripke structure. A run  $\pi$  of a Kripke structure M is an infinite sequence of states  $\{\pi_0, \pi_1, \ldots\}$ , where  $\pi_0 \in I$  and  $(\pi_i, \pi_{i+1}) \in R$ . Let  $\pi[i]$  represent the infinite run starting from state  $\pi_i$ . Let  $\tau$  and  $\theta$  be LTL formulae, and  $\psi$  be an atomic proposition. The definition of when a run  $\pi$  satisfies a formula is given inductively:

- $\pi \vDash \tau$  iff  $\pi[0] \vDash \tau$

- $\pi[i] \vDash \psi$  iff  $\psi \in L(\pi_i)$

- $\pi[i] \vDash \neg \tau$  iff  $\pi[i] \nvDash \tau$

- $\pi[i] \vDash \tau \lor \theta$  iff  $\pi[i] \vDash \tau$  or  $\pi[i] \vDash \theta$

- $\pi[i] \vDash \tau'$  iff  $\pi[i+1] \vDash \tau$

- $\pi[i] \vDash \Box \tau$  iff  $\pi[k] \vDash \tau$  for all  $k \ge i$

- $\pi[i] \vDash \Diamond \tau$  iff  $\pi[k] \vDash \tau$  for some  $k \ge i$

The Kripke Structure M satisfies a formula  $\tau$  if every possible run  $\pi$  satisfies the formula.

Two classes of interesting properties of LTL are safety and liveness properties, where the simplest examples are  $\Box p$  and  $\Box \Diamond p$ , respectively. Safety properties can be disproved with finite prefixes of the strings of the formal language, which in principle means that safety properties states what shall never happen. Liveness properties cannot be disproved with finite strings of the language, which means that liveness properties specify conditions that shall be fulfilled infinitely many times.

### 3.3 Terminology

Foundations for *Model Checking* (MC), *Reactive Synthesis* (RS) and *Supervisory Control Theory* (SCT) are presented in the next sections. The terminologies of Model Checking, Reactive Synthesis, and Supervisory Control Theory are both overlapping and conflicting, as Paper C points out when the formal synthesis tools TuLiP [35] and Supremica [36] are compared, so before they are presented, a note on the terminology used in these fields is needed.

To explain the different parts that go into the different formal methods there are a few terms that need to be defined. What is important for this thesis are mainly three things: *the planner, the environment,* and *the requirements.* The planner refers to the (artificial) product that is being designed — usually the tactical planner in the case of this thesis. For a given planning problem, the planner is exactly the parts of a system that are allowed to be changed or designed. The environment is the outside world with which the planner interacts. Within automotive applications this is typically the dynamics of the car, the roads, and other road users. However, the environment also includes other systems and subsystems of the car that cannot or must not be changed during the design of the planner. Examples of this can be brake systems or sensor systems. Lastly, the requirements are the desired behaviors of the system as it interacts with its environment. The requirements define desired and undesired behaviors of the system.

Model Checking starts from a planner, possibly interacting with an environment, and its requirements. However, MC lumps together the planner and its environment and calls them together the *system*. As the name Model Checking implies, MC is the process of checking properties of a model<sup>1</sup> of the planner and, when applicable, the environment. A model is a formal characterization of the planner and environment that captures the behaviors that are interesting for the verification. Depending on the goal of the project the

<sup>&</sup>lt;sup>1</sup>Also called the system model.

model can be a small piece of code, or an abstraction of an entire car and its surroundings. The formal properties that the Model Checker checks are the formalization of the requirements on the system; the requirements expressed in a formal language [12]. In this thesis the formalization of the requirements will mainly be called the *formal specification*.

In RS, at least in the case of TuLiP, the names have a bit different meaning compared to MC. RS use the concept of environment and system as names for the environment and planner, where the system is constructed such that it guarantees the fulfillment of the requirements as long as the environment model is correct. Also in RS terminology, the system *controls* the environment. Since RS aims to synthesize a controller, or a *reactive module*, there is never a model of the planner in RS. In RS terminology there is neither an environment model, but an environment specification that states the assumed behaviors of the environment. Paper C explains these concepts of RS with some examples. To be consistent through the thesis, the assumed behavior of the environment will be called the environment model for RS.

Supremica, and SCT in general, can be used for both formal verification and synthesis. Regardless, the formalization of the environment, planner, and requirements are divided into plants and specifications. In general, the plants are the models of the environment and/or planner, whichever is applicable. The specifications are the formalizations of the requirements. However, the plants can also have markings on states, which is a formalization of a certain type of requirements that express the possibility to reach those states. Some examples of this are also given in Paper C.

### 3.4 Model Checking

Model Checking is used to prove formal properties of a formal model of the system. The system can consist of hardware or software, but it is software applications that are considered here. Verification of software with MC starts with the formal specification, which is composed of the formal properties, and the formal model. The intended result of model checking is either a proof that the model exhibits the formal property, or a counterexample that demonstrates why the property does not hold in the model. The benefit of performing model checking over reviewing and testing is that model checking is exhaustive and can prove that no faults are present. However, a caveat is that this holds only when the model captures the relevant behaviors of the system. The model checker (the program that performs the Model Checking) can also run out of time or memory because of the state explosion problem. Then model checking can only be used to find faults, just like testing.

In LTL Model Checking the formal properties are expressed in LTL and the software program is modeled as a transition system.

**Definition 3:** Let  $K = \langle S, I, R, AP, L \rangle$  be a transition system and  $B = \langle Q, Q_i, \delta, AP, F \rangle$

be a Büchi automaton. Then the product  $K \times B$  is the following tuple

$$T = \langle S \times Q, N_i, \to, AP, N_a \rangle,$$

where

$$(s,q) \rightarrow (s',q') \quad iff \ (s,s') \in R \ and \ (q,L(s'),q') \in \delta$$

$$N_i = \{(s_i,q) \mid s_i \in I \ and \ \exists q_i \in Q_i : (q_i,L(s_i),q) \in \delta\}$$

$$N_a = \{(s,q) \mid q \in F\}$$

Let the transition system K be a Kripke structure that models a software program, and  $\varphi$  an LTL formula that expresses a desired formal property of K. To prove whether K satisfies  $\varphi$  the following steps are performed [12]:

- (i) Construct a Büchi automaton B for the LTL formula  $\neg \varphi$ .

- (ii) Construct the product  $K \times B$ .

- (iii) Analyze whether  $K \times B$  has a run  $\pi$  visiting accepting states infinitely often.

- (iv) If such a  $\pi$  is found, then  $\varphi$  is not satisfied by K, and  $\pi$  is a counterexample. If no such  $\pi$  is found, then K satisfies  $\varphi$ .

The construction of transition systems and Büchi automata can be quite involved, so there are software tools that let the user define the transition system in a formal format that is more suitable for humans, and the properties in LTL. These are then automatically translated into a transition system and Büchi automata, and then turned into a product tuple, which in turn is searched for the existence of  $\pi$ . One such model checker is Spin [37], which allows the user to specify the system model in the language Promela, and the desired properties in LTL.

#### 3.5 Reactive Synthesis

Reactive Synthesis (RS) [14] aims to automatically synthesize a reactive module that satisfies the desired guarantees  $\phi_s$ , under the assumptions of the environment  $\phi_e$ . In other words, the reactive module satisfies the formula  $\phi_e \rightarrow \phi_s$  [38]. A reactive module evolves in computation cycles and engages in an ongoing interaction with its environment. The reactive module alternately reads inputs from the environment and assigns values to its outputs, possibly affecting the environment. For a comprehensive introduction to RS, refer to [41].

One way to model the RS problem is to consider the reactive module to be synthesized and the environment as adversaries that play a finite-state game and take turns to provide input to each other [42]. Then, an iterative process can be adopted to find a fix-point of a subset of states and transitions that solves the RS problem. The states, transitions, inputs, and outputs can be modeled by a Kripke structure.

In RS, the set of atomic propositions AP is divided into two disjoint subsets  $AP_e$ and  $AP_s$ , representing the propositions of the environment and the reactive module, respectively. The atomic propositions in  $AP_e$  are seen as the inputs to the reactive module, while  $AP_s$  are its outputs. The atomic propositions in AP can be composed of relational operators on functions of discrete finite domain variables so they can be considered either true or false, given a certain valuation in a certain state.

A subset of LTL formulae that is particularly interesting is called *General Reactivity* of Rank 1 (GR(1)) [43]. This set of formulae is useful because it is possible to perform reactive synthesis of the GR(1) fragment in polynomial-time. Given an LTL formulae  $\varphi$ defining the environment model and the formal specification, GR(1) synthesis constructs a reactive module such that the total system satisfies  $\varphi$ , if such a reactive module exists. The LTL fragment GR(1) has the following form [43]:

$$\varphi \triangleq \left( \left( \psi_{init}^e \land \Box \psi_{safe}^e \land \bigwedge_{0 < i \le J} \Box \Diamond \psi_{live,i}^e \right) \to \left( \psi_{init}^s \land \Box \psi_{safe}^s \land \bigwedge_{0 < i \le N} \Box \Diamond \psi_{live,i}^s \right) \right), \quad (3.1)$$

where  $\psi_{init}^e$  and  $\psi_{init}^s$  contain all the initial conditions of the environment and the reactive module, respectively.  $\psi_{safe}^e$  and  $\psi_{live,i}^e$  (*J* number of sub-specifications) are the *safety* and *liveness* assumptions on the environment.  $\psi_{safe}^s$  and  $\psi_{live,i}^s$  (*N* number of sub-specifications) are the desired safety and liveness properties of the reactive module.

Note that the implication in (3.1) shall be interpreted as a *strict realizability* implication [44]. Strict realizability means that the reactive module must not 'cheat' by falsifying the environment assumptions. If a normal logical implication would be used, the reactive module could be synthesized such that it violates the formal specification to force the environment to violate the assumptions. If any of the formulae on the left of the implication in (3.1) is false, then the implication is trivially true if it is not interpreted as a strict realizability implication.

Klein and Pnueli give the following counterexample with two boolean variables p and q, where p is an environment variable and q is a reactive module variable:

$$\Box \neg p' \land \Box \Diamond (p \leftrightarrow q) \to \Box (p' \leftrightarrow q') \land \Box \Diamond q.$$

(3.2)

If the implication in (3.2) is treated as the standard logical implication, a reactive module could satisfy the formula by letting q be True in all states. The environment then cannot fulfill both its assumptions, and thus the implication is satisfied regardless of whether the reactive module fulfills its specifications or not.

The strict realizability implication details that the reactive module must not be the first player to violate the safety properties. Formula (3.2) cannot be satisfied if the implication is strictly realizable. If the environment fulfills the safety assumptions then p is False all the time, and hence the reactive module must let q be False all the time, otherwise breaking the specification  $\Box(p' \leftrightarrow q')$ . The liveness assumption  $\Box \Diamond (p \leftrightarrow q)$  is satisfied, but the reactive module cannot then fulfill the liveness specification  $\Box \Diamond q$ .

### 3.6 Supervisory Control Theory

The Supervisory Control Theory (SCT) [13], [45] is a model-based approach for control of Discrete Event System (DES). A DES is a category of automata whose transitions are triggered by occurrences of *events*; the labels on the transitions are not interpreted as inputs but observations of events. Given a DES to be controlled, the *plant*, and a *specification* describing the desired behavior, a control entity, called a *supervisor*, can be automatically synthesized to dynamically restrict the behavior of the plant, such that the closed-loop system satisfies the specification.

Finite state machines (FSM) are defined the same as automata (1), but is given here again to stress that the alphabet consists of events.

**Definition 4:** An FSM is a tuple

$$A = \langle \Sigma, Q, \to, Q^{\circ}, Q^{\omega} \rangle,$$

where  $\Sigma$  is a set of events, the alphabet; Q is a finite set of states;  $\rightarrow \subseteq Q \times \Sigma \times Q$ is the transition relation;  $Q^{\circ} \subseteq Q$  is the set of initial states; and  $Q^{\omega} \subseteq Q$  is the set of marked states.

In SCT, the accepting states are termed the marked states, so  $Q^{\omega}$  are equal to F in (1). The accepting condition of an FSM accepts all *finite* strings that are a prefix to a string ending in a marked state [13]<sup>2</sup>.

Given a plant G and a specification K of the desired controlled behavior, the SCT makes it possible to automatically synthesize a supervisor S that controls the plant such that the specification is satisfied.

The supervisor and the plant form an asymmetric *closed-loop* system where the supervisor restricts the event generation of the plant. As the plant generates events enabled by the supervisor, the supervisor observes the generated sequences of events and determines, at each state, which of the currently possible events that should be enabled. Some of the events cannot be disabled by the supervisor. These events are *uncontrollable*. The supervisor is required to be *controllable*, i.e. it must never try to disable an uncontrollable event. By disabling controllable events, the supervisor can confine the plant to a subset of its possible states so that the closed-loop system only visits states that are considered "good" by the specification. At the same time, the supervisor guarantees that from any closed-loop state, the system can always continue to a desired marked state, it is *non-blocking*. Finally, the supervisor disables as few events as possible, it is *maximally permissive*.

For a plant with controllable and uncontrollable events, the alphabet  $\Sigma$  consists of the two disjoint sets  $\Sigma_c$  and  $\Sigma_u$  consisting of the controllable and uncontrollable events, respectively.

**Definition 5:** Given two FSM  $G_1 = \langle \Sigma_1, Q_1, \rightarrow_1, Q_1^{\circ}, Q_1^{\omega} \rangle$  and  $G_2 = \langle \Sigma_2, Q_2, \rightarrow_2, Q_2^{\circ}, Q_2^{\omega} \rangle$ , the full synchronous composition of  $G_1$  and  $G_2$  is  $G_1 \parallel G_2 = \langle \Sigma_1 \cup \Sigma_2, Q_1 \times Q_2, \rightarrow, Q_2^{\omega} \rangle$ .

<sup>&</sup>lt;sup>2</sup>There are also SCT variants with accepting conditions that only accepts infinite strings [46]. Then the accepting condition is the same as for Büchi automata.

$Q_1^{\circ} \times Q_2^{\circ}, Q_1^{\omega} \times Q_2^{\omega} \rangle$ , where:

(

$$\begin{array}{ll} (x_1, x_2) \xrightarrow{\sigma} (y_1, y_2) & \textit{if } \sigma \in \Sigma_1 \cap \Sigma_2, \ x_1 \xrightarrow{\sigma}_1 y_1, \\ & and \ x_2 \xrightarrow{\sigma}_2 y_2 \ ; \\ (x_1, x_2) \xrightarrow{\sigma} (y_1, x_2) & \textit{if } \sigma \in \Sigma_1 \setminus \Sigma_2 \ and \ x_1 \xrightarrow{\sigma}_1 y_1 \ ; \\ (x_1, x_2) \xrightarrow{\sigma} (x_1, y_2) & \textit{if } \sigma \in \Sigma_2 \setminus \Sigma_1 \ and \ x_2 \xrightarrow{\sigma}_2 y_2 \ . \end{array}$$

Basically, supervisor synthesis is an iterative removal of states and/or transitions of an initially calculated supervisor "candidate". Practically, this candidate is calculated from G||K where || denotes the full synchronous composition operator [13]. The iterative algorithm removes from G||K the states that break the controllability and/or the nonblocking properties. Iteration is necessary since enforcing one property may break the other. The iteration will eventually reach a fix-point, and what then is obtained is the maximally permissive, controllable, and non-blocking supervisor.

Extended finite-state machines (EFSM) are similar to FSM, but augmented with updates associated to the transitions [47], [48]; formulas constructed from variables, integer constants, the Boolean literals true  $(\mathbf{T})$  and false  $(\mathbf{F})$ , propositional logic connectives, and discrete arithmetic operators.

A variable v is an entity associated with a bounded discrete domain dom(v) and an initial value  $v^{\circ} \in \text{dom}(v)$ . Let  $V = \{v_0, \ldots, v_n\}$  be the set of variables with domain  $\operatorname{dom}(V) = \operatorname{dom}(v_0) \times \cdots \times \operatorname{dom}(v_n)$ . An element of  $\operatorname{dom}(V)$  is called a valuation and is denoted by  $\hat{v} = (\hat{v}_0, \dots, \hat{v}_n)$  with  $\hat{v}_i \in \operatorname{dom}(v_i)$ , and the value associated to variable  $v_i \in V$  is denoted  $\hat{v}[v_i] = \hat{v}_i$ . The *initial valuation* is  $v^\circ = (v_0^\circ, \dots, v_n^\circ)$ .

A second set of variables, called *next-state variables*, denoted by  $V' = \{v' \mid v \in V\}$ with  $\operatorname{dom}(V') = \operatorname{dom}(V)$ , is used to describe the values of the variables after execution of a transition. Variables in V are referred to as *current-state variables* to differentiate them from the next-state variables in V'. The set of all update formulas using variables in V and V' is denoted by  $\Pi_V$ .

For an update  $p \in \Pi_V$ , the terms vars(p) and vars'(p) denote the sets of all variables, and all next-state variables, respectively, that occur in p. For example, if  $p \equiv x' = y + 1$ then  $\operatorname{vars}(p) = \{x, y\}$  and  $\operatorname{vars}'(p) = \{x\}$ . Here and in the following, the relation  $\equiv$ denotes syntactic identity of updates to avoid ambiguity when an update contains the equality symbol =.

With slight abuse of notation, updates  $p \in \Pi_V$  are also interpreted as predicates over their variables, and they evaluate to **T** or **F**, i.e.,  $p: \operatorname{dom}(V) \times \operatorname{dom}(V') \to \{\mathbf{T}, \mathbf{F}\}$ . For example, if  $V = \{x\}$  with dom $(x) = \{0, 1\}$ , then the update  $p \equiv x' = x + 1$  means that the value of the variable x in the next state will be increased by 1 over its current-state value. Its predicate p(x, x') evaluates as  $p(0, 1) = \mathbf{T}$  and  $p(1, 1) = p(0, 0) = p(1, 0) = \mathbf{F}$ .

**Definition 6:** An extended finite-state machine (EFSM) is a tuple

$$E = \langle \Sigma, Q, \to, Q^{\circ}, Q^{\omega} \rangle,$$

where  $\Sigma$  is a set of events, the alphabet; Q is a finite set of locations;  $\rightarrow \subseteq Q \times \Sigma \times \Pi_V \times Q$ is the conditional transition relation;  $Q^{\circ} \subseteq Q$  is the set of initial locations; and  $Q^{\omega} \subseteq Q$ is the set of marked locations.

The expression  $q_0 \stackrel{\sigma:p}{\to} q_1$  denotes the presence of a transition in E, from location  $q_0$  to location  $q_1$  with event  $\sigma$  and update p. Such a transition can occur if the EFSM is in location  $q_0$  and the update p evaluates to  $\mathbf{T}$ , and when the transition occurs, the EFSM changes its location from  $q_0$  to  $q_1$  while updating the variables in vars'(p) in accordance with p; variables not contained in vars'(p) are unchanged.

Given an EFSM  $E = \langle \Sigma, Q, \rightarrow, Q^{\circ}, Q^{\omega} \rangle$ , its variable set is

$$\operatorname{vars}(E) = \bigcup_{(q_0,\sigma,p,q_1)\in \to} \operatorname{vars}(p),$$

which contains all variables that appear on some transitions of E.

**Definition 7:** Given two EFSMs  $E_1 = \langle \Sigma_1, Q_1, \rightarrow_1, Q_1^{\circ}, Q_1^{\omega} \rangle$  and  $E_2 = \langle \Sigma_2, Q_2, \rightarrow_2, Q_2^{\circ}, Q_2^{\omega} \rangle$ , the synchronous composition of  $E_1$  and  $E_2$  is  $E_1 \parallel E_2 = \langle \Sigma_1 \cup \Sigma_2, Q_1 \times Q_2, \rightarrow, Q_1^{\circ} \times Q_2^{\circ}, Q_1^{\omega} \times Q_2^{\omega} \rangle$ , where:

$$\begin{array}{cccc} (x_1, x_2) \xrightarrow{\sigma:p_1 \wedge p_2} (y_1, y_2) & \text{if } \sigma \in \Sigma_1 \cap \Sigma_2, \ x_1 \xrightarrow{\sigma:p_1} y_1, \\ & and \ x_2 \xrightarrow{\sigma:p_2} y_2 \ ; \\ (x_1, x_2) \xrightarrow{\sigma:p_1} (y_1, x_2) & \text{if } \sigma \in \Sigma_1 \setminus \Sigma_2 \ and \ x_1 \xrightarrow{\sigma:p_1} y_1 \ ; \\ (x_1, x_2) \xrightarrow{\sigma:p_2} (x_1, y_2) & \text{if } \sigma \in \Sigma_2 \setminus \Sigma_1 \ and \ x_2 \xrightarrow{\sigma:p_2} y_2 \ . \end{array}$$

In an EFSM, the current state of the system is given by the current location together with the current values of all the variables. Since the variables are discrete and bounded, the EFSM can be *flattened*, which introduces states for the combinations of locations and variable values [12].

**Definition 8:** Let  $E = \langle \Sigma, Q, \to, Q^{\circ}, Q^{\omega} \rangle$  be an EFSM with variable set vars(E) = V. The monolithic flattening of E is  $U(E) = \langle \Sigma, Q_U, \to_U, Q_U^{\circ}, Q_U^{\omega} \rangle$  where

•  $Q_U = Q \times \operatorname{dom}(V);$

•

$$(x, \hat{v}) \stackrel{\sigma}{\to}_U (y, \hat{w})$$

if E contains a transition  $x \stackrel{\sigma:p}{\to} y$  such that  $p(\hat{v}, \hat{w}) = \mathbf{T}$ ,

- $Q_U^\circ = Q^\circ \times \{v^\circ\};$

- $Q_U^{\omega} = Q^{\omega} \times \operatorname{dom}(V).$

U(E) is the DES representation of the EFSM, where all the variables have been removed and their values  $\hat{v}$  embedded into the state set  $Q_U$ . This ensures the correct sequencing of transitions in the DES.

With the introduction of updates to FSMs it is possible to restrict the plants' behaviors by adding updates to the plants. In that case the synthesis algorithm does not need to generate a supervisor as separate automata. For the purpose of adding updates to plants, *Binary Decision Diagram* (BDDs) [49] can be used in the synthesis algorithm. A BDD is a data structure that can efficiently store huge state-spaces and transition sets encoded as Boolean functions. The computational complexity of synthesis using BDDs does not depend on the number of states or transitions, but on the number of nodes in the BDD, as the computations are performed symbolically rather than explicitly; synthesis is performed on sets of states and transitions rather than single such elements. So even though the BDD-based synthesis works on a monolithic model, it can handle systems of considerable sizes. The approach presented in [50] uses partitioning techniques to further stretch the ability of the synthesis procedure.

The BDD-based synthesis works directly on the EFSM model, encoding the transition relation and the updates as Boolean expressions. The synthesis then results in a partitioning of the state-space into *allowed* and *forbidden* states, and then guarantees that only controllable events take the system from the allowed into the forbidden states. From this is then generated updates that represent the control actions of the supervisor. These updates are Boolean expressions over values of variables and state labels, that define when the particular event is enabled.

# CHAPTER 4

## Correct-by-Construction Tactical Planners

In theory, formal methods are a promising approach for the development of correct tactical planners, and case studies have been performed to demonstrate the real usefulness of formal methods applied to practical problems [51]–[53]. Tactical planners are special because of three characteristics;

- they take discrete decisions in environments where they interact with other road users;

- the car's position continuously changes and therefore they are moving while taking decisions; and

- they need to be agnostic of absolute position since they should operate in large parts of the world's road network.

These three characteristics mean special consideration because temporal specifications are needed to describe the desired interactions, and the states need to have a careful abstraction.

This chapter describes how the characteristics affect the modeling of the planner and the environment, and the formalization of the requirements. Especially, different modeling formalisms are compared to expose benefits and drawbacks of using one formalism over the another.

#### 4.1 Inspection of Results

One of the key findings of obstacles to using formal synthesis in larger scale industrial applications is the importance of inspection of the results. When the number of states of the supervisor or reactive module exceeds about 20 and when the states are highly interconnected, it becomes very difficult to inspect and understand their resulting properties. Obviously, the supervisor or reactive module adheres to the stated requirements that all have very precise and formal syntax and semantics, but with several interacting requirements it is increasingly difficult to anticipate all effects of the interactions. An objection would be that the supervisor or reactive module could be calculated by hand to get an understanding of the results, but that defeats the purpose of applying automatic methods to reduce the efforts of manual labor.

Interestingly, this obstacle of interpreting the results are also an issue within machine learning (ML), and specifically within deep learning (DL) [54], [55]. On a high level the work processes of ML and formal synthesis are very similar. A model of the environment is one input (data in the case of ML and a formal model in the case of formal synthesis), the requirements is the second input (reward function for ML and formal specification for formal synthesis), and a black box model is the output (a trained agent in ML and an automaton in formal synthesis). The goal in both fields is to find a black box output that fulfills the requirements, adhering to the rules of the environment.