## University of Windsor Scholarship at UWindsor

**Electronic Theses and Dissertations**

Theses, Dissertations, and Major Papers

2008

# A Compact Camera with a Reconfigurable Real-time Embedded Image Processor for Pharmaceutical Capsule Inspections

Anthony Karloff University of Windsor

Follow this and additional works at: https://scholar.uwindsor.ca/etd

#### **Recommended Citation**

Karloff, Anthony, "A Compact Camera with a Reconfigurable Real-time Embedded Image Processor for Pharmaceutical Capsule Inspections" (2008). *Electronic Theses and Dissertations*. 8030. https://scholar.uwindsor.ca/etd/8030

This online database contains the full-text of PhD dissertations and Masters' theses of University of Windsor students from 1954 forward. These documents are made available for personal study and research purposes only, in accordance with the Canadian Copyright Act and the Creative Commons license—CC BY-NC-ND (Attribution, Non-Commercial, No Derivative Works). Under this license, works must always be attributed to the copyright holder (original author), cannot be used for any commercial purposes, and may not be altered. Any other use would require the permission of the copyright holder. Students may inquire about withdrawing their dissertation and/or thesis from this database. For additional inquiries, please contact the repository administrator via email (scholarship@uwindsor.ca) or by telephone at 519-253-3000ext. 3208.

# A Compact Camera with a Reconfigurable Real-time Embedded Image Processor for Pharmaceutical Capsule Inspections

by

**Anthony Karloff**

A Thesis

Submitted to the Faculty of Graduate Studies through Electrical and Computer Engineering in Partial Fulfillment of the Requirements for the Degree of Master of Applied Science at the University of Windsor

Windsor, Ontario, Canada 2008

#### Library and Archives Canada

Published Heritage Branch

395 Wellington Street Ottawa ON K1A 0N4 Canada

#### Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 978-0-494-47052-7 Our file Notre référence ISBN: 978-0-494-47052-7

### NOTICE:

The author has granted a nonexclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or noncommercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis. Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

### O 2008 Anthony Karloff

All Rights Reserved. No Part of this document may be reproduced, stored or otherwise retained in a retreival system or transmitted in any form, on any medium by any means without prior written permission of the author.

# Declaration of Co-Authorship/Previous Publication

#### I. Co-Authorship Declaration

This thesis also incorporates the outcome of a joint research undertaken in collaboration with Neil Scott and Mohammad Islam under the supervision of Dr. Roberto Muscedere and Dr. Majid Ahmadi. The collaboration is covered in Chapter 2 of the thesis. In all cases, the key ideas, primary contributions, experimental designs, data analysis and interpretation, were performed by the author.

I am aware of the University of Windsor Senate Policy on Authorship and I certify that I have properly acknowledged the contribution of other researchers to my thesis, and have obtained written permission from each of the co-author(s) to include the above material(s) in my thesis.

I certify that, with the above qualification, this thesis, and the research to which it refers, is the product of my own work.

#### **II.** Declaration of Previous Publication

This thesis includes one original paper that has been previously published in a peer reviewed journal, as follows:

| Thesis Chapter | Full Citation                                        | Status    |

|----------------|------------------------------------------------------|-----------|

| Chapter 2      | A. Karloff, N. Scott, and R. Muscedere. A flexible   | Published |

|                | design for a cost effective, high-throughput inspec- |           |

|                | tion system for pharmaceutical capsules. In Proc.    |           |

|                | IEEE International Conference on Industrial Technol- |           |

|                | ogy, April 2008                                      |           |

I certify that I have obtained a written permission from the copyright owner(s) to include the above published material(s) in my thesis. I certify that the above material describes work completed during my registration as graduate student at the University of Windsor.

I declare that, to the best of my knowledge, my thesis does not infringe upon anyones copyright nor violate any proprietary rights and that any ideas, techniques, quotations, or any other material from the work of other people included in my thesis, published or otherwise, are fully acknowledged in accordance with the standard referencing practices. Furthermore, to the extent that I have included copyrighted material that surpasses the bounds of fair dealing within the meaning of the Canada Copyright Act, I certify that I have obtained a written permission from the copyright owner(s) to include such material(s) in my thesis.

I declare that this is a true copy of my thesis, including any final revisions, as approved by my thesis committee and the Graduate Studies office, and that this thesis has not been submitted for a higher degree to any other University of Institution.

v

# Abstract

The following thesis presents the system requirements, design methodology, final hardware design and system integration of a custom digital camera for high-speed pharmaceutical capsule inspections.

The primary goals of the camera design were to minimize the cost of the device and to have a flexible design that could be easily upgraded in the future. For this application, a 3.1 mega pixel CMOS image sensor was used with a USB 2.0 interface. In addition, the custom camera can pre-process image data in an embedded, reconfigurable real-time image processor implemented in a FPGA. All data processing in the camera occurs with only buffering four rows of an image, eliminating the need for RAM on the device and lowering the overall cost.

The final design was manufactured and implemented into a complete inspection system which used 16 of these cameras to inspect up to 60 000 capsules per second. To my family and friends for their endless support and encouragement. This work would not have been possible without you.

# **Acknowledgments**

There are several people who deserve to be acknowledged for their generous contributions to this project. I would first like to express my sincere gratitude and appreciation to Dr. Roberto Muscedere, my supervisor, for his invaluable guidance and involvement throughout the course of this thesis. I would also like to extend a very special thanks to Dr. Majid Ahmadi and Dr. Maher Sid-Ahmed for their expert guidance, encouragement and constant support throughout my studies.

# Contents

| D  | eclara | ation o | of Co-Authorship/Previous Publication   | iv   |

|----|--------|---------|-----------------------------------------|------|

| A  | bstra  | ct      |                                         | vi   |

| D  | edica  | tion    |                                         | vii  |

| A  | cknov  | wledgn  | nents                                   | viii |

| Li | st of  | Figure  | es                                      | xiii |

| Li | st of  | Table   | S                                       | xv   |

| Li | st of  | Abbre   | eviations                               | xvii |

| 1  | Intr   | oducti  | ion                                     | 1    |

|    | 1.1    | Projec  | et Overview                             | 2    |

|    | 1.2    | Qualit  | cy Control of Two Part Gelatin Capsules | 2    |

|    | 1.3    | Metho   | ods of Defect Detection                 | 3    |

|    |        | 1.3.1   | Current Inspection Methods              | 3    |

|    |        | 1.3.2   | Introduction to Machine Vision          | 5    |

|    |        | 1.3.3   | Commercial Systems                      | 6    |

|    | 1.4    | Propo   | sed Solution                            | 7    |

|    |        |         |                                         |      |

#### CONTENTS

|          | 1.5  | Thesis Organization                       | 7  |

|----------|------|-------------------------------------------|----|

| <b>2</b> | Syst | em Overview                               | 9  |

|          | 2.1  | Introduction to the Optisorter            | 9  |

|          |      | 2.1.1 Background Information              | 9  |

|          |      | 2.1.2 Summary of Operation                | 0  |

|          | 2.2  | System Timing                             | .1 |

|          | 2.3  | Imaging Environment                       | .3 |

|          | 2.4  | Objectives for Modification               | .3 |

|          |      | 2.4.1 Selecting a Camera                  | 4  |

|          |      | 2.4.2 Modifying the Imaging Environment   | .6 |

|          | 2.5  | Proposed Design                           | .8 |

| 3        | Can  | era Design Methodology 2                  | 1  |

|          | 3.1  | Camera Design Flow                        | 21 |

|          | 3.2  | Design Specifications                     | 23 |

|          | 3.3  | Major Design Methods                      | 23 |

|          |      | 3.3.1 Reconfigurable Hardware Programming | 24 |

|          |      | 3.3.2 Simulation Tools                    | 24 |

|          |      | 3.3.3 Prototyping Hardware                | 25 |

|          | 3.4  | Testing                                   | 25 |

| 4        | Har  | dware Design 2                            | 26 |

|          | 4.1  | Component Selection                       | 26 |

|          |      | 4.1.1 Imaging Sensors                     | 27 |

|          |      | 4.1.2 Reconfigurable Devices              | 28 |

|          |      | 4.1.3 Communication Interface             | 31 |

|          |      | 4.1.4 Component Summary                   | 32 |

#### CONTENTS

|   | 4.2 | Circuit            | t Schemat             | tics                            | 32        |

|---|-----|--------------------|-----------------------|---------------------------------|-----------|

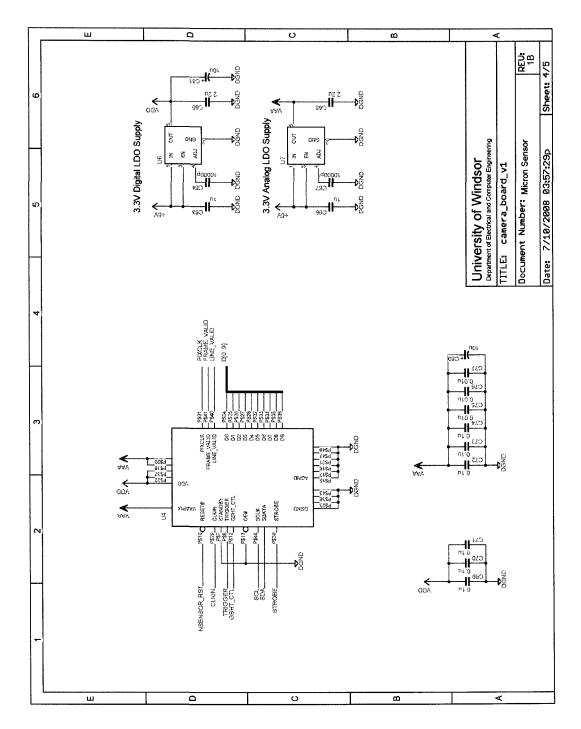

|   |     | 4.2.1              | Micron I              | MT9T001 CMOS Imaging Sensor     | 32        |

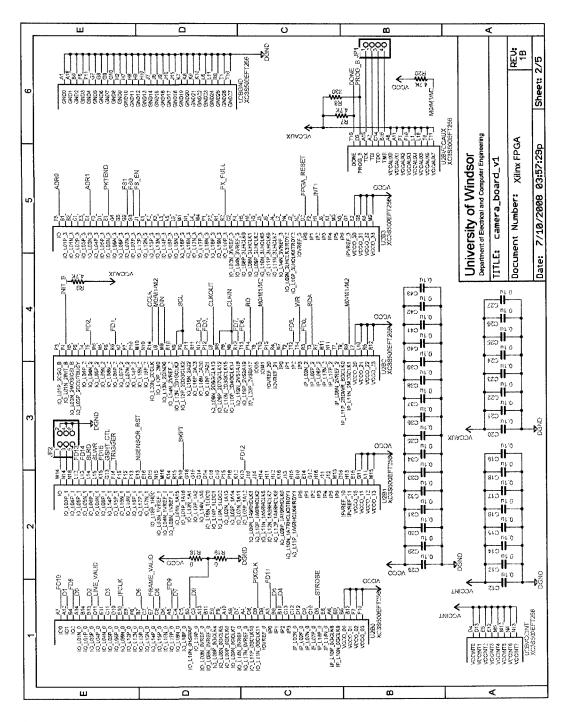

|   |     | 4.2.2              | Xilinx S              | partan-3E500 FPGA               | 33        |

|   |     |                    | 4.2.2.1               | I/O Connections                 | 33        |

|   |     |                    | 4.2.2.2               | Clock Connections               | 34        |

|   |     |                    | 4.2.2.3               | Power Connections               | 34        |

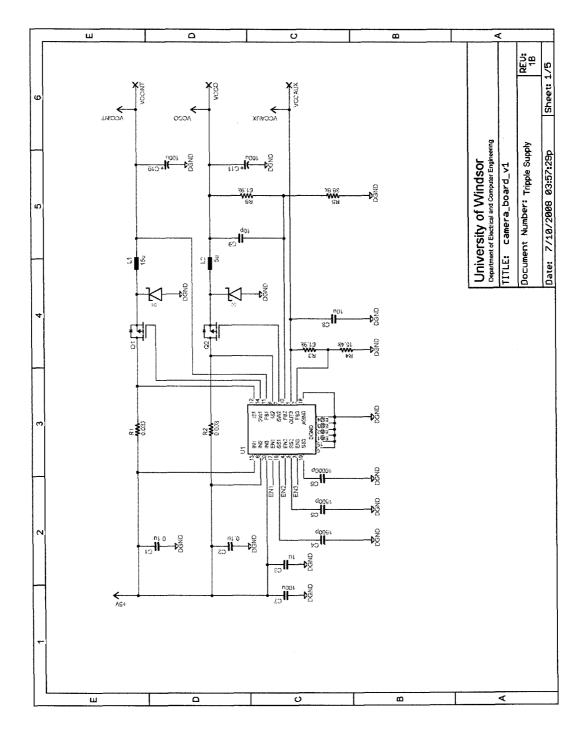

|   |     | 4.2.3              | TPS Tri               | ple Supply                      | 35        |

|   |     |                    | 4.2.3.1               | Limiting Buck Converter Current | 36        |

|   |     |                    | 4.2.3.2               | Setting VCCO                    | 37        |

|   |     |                    | 4.2.3.3               | Sizing Soft Start Capacitors    | 37        |

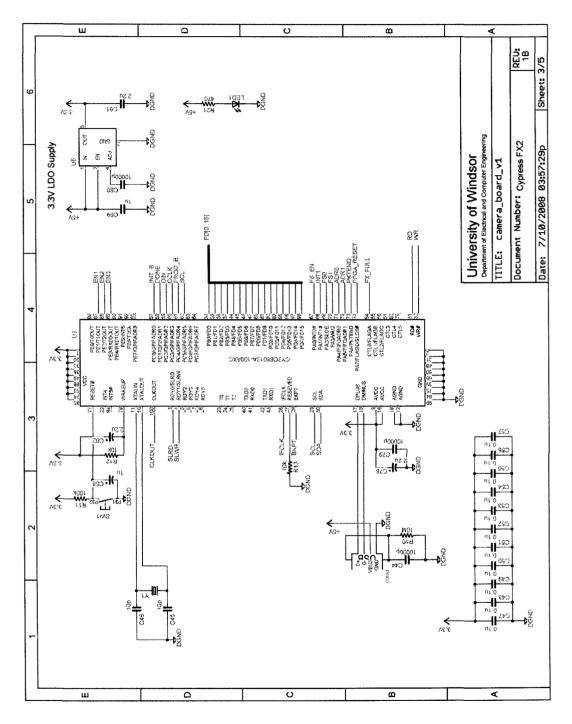

|   |     | 4.2.4              | Cypress               | FX2 USB Microcontroller         | 38        |

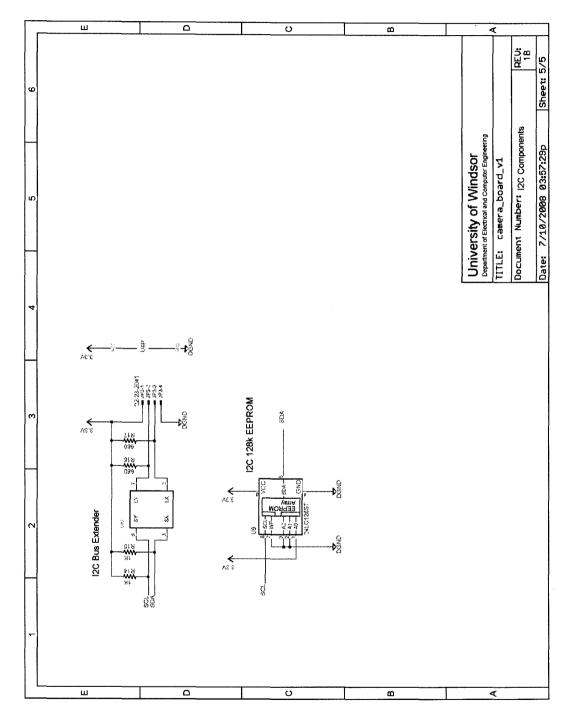

|   |     | 4.2.5              | I <sup>2</sup> C Con  | nmunication Bus                 | 39        |

|   | 4.3 | PCB I              | Layout .              |                                 | 40        |

|   |     | 4.3.1              | PCB sp                | ecifications                    | 41        |

|   |     | 4.3.2              | Compon                | ent Placement                   | 43        |

|   |     | 4.3.3              | Power a               | nd Grounding                    | 46        |

|   |     | 4.3.4              | Bypass                | capacitors                      | 47        |

|   |     | 4.3.5              | Routing               |                                 | 51        |

|   |     | 4.3.6              | Manufao               | cturing Files                   | 52        |

| 5 | HD  | L Bloc             | ks and l              | Programming                     | <b>54</b> |

|   | 5.1 | FPGA               | A Program             | nming Overview                  | 54        |

|   | 5.2 | Frame              | e Timing a            | and Data Synchronization        | 55        |

|   | 5.3 | I <sup>2</sup> C W | Vrite Slave           | 9                               | 57        |

|   |     | 5.3.1              | I <sup>2</sup> C Bus  | Overview                        | 58        |

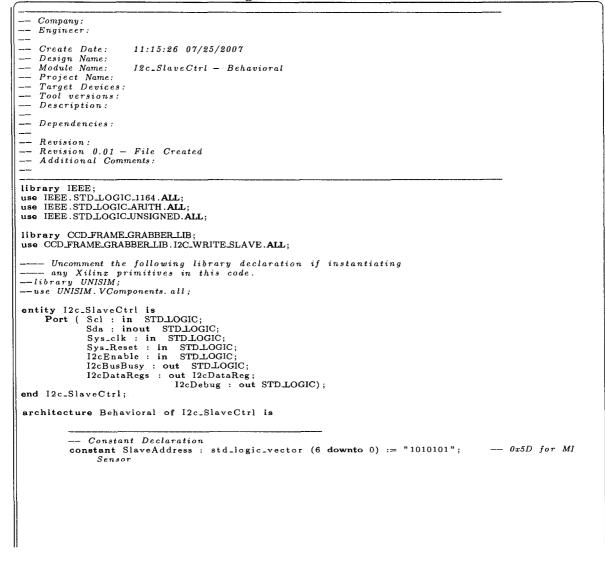

|   |     | 5.3.2              | I <sup>2</sup> C Slav | ve VHDL implementation          | 59        |

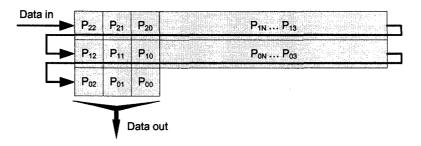

|   | 5.4 | Async              | hronous l             | FIFO                            | 61        |

|   |     |                    |                       |                                 |           |

### CONTENTS

|              | 5.5                    | Output Controller                             | 62  |

|--------------|------------------------|-----------------------------------------------|-----|

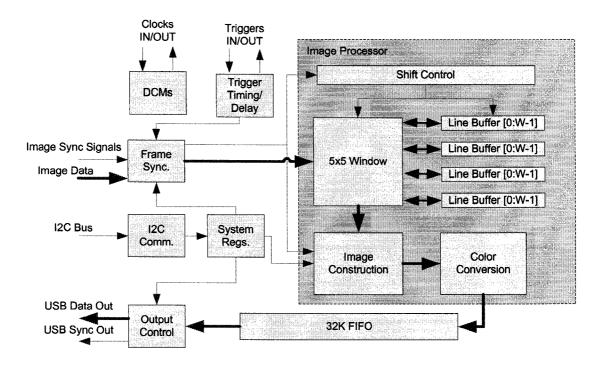

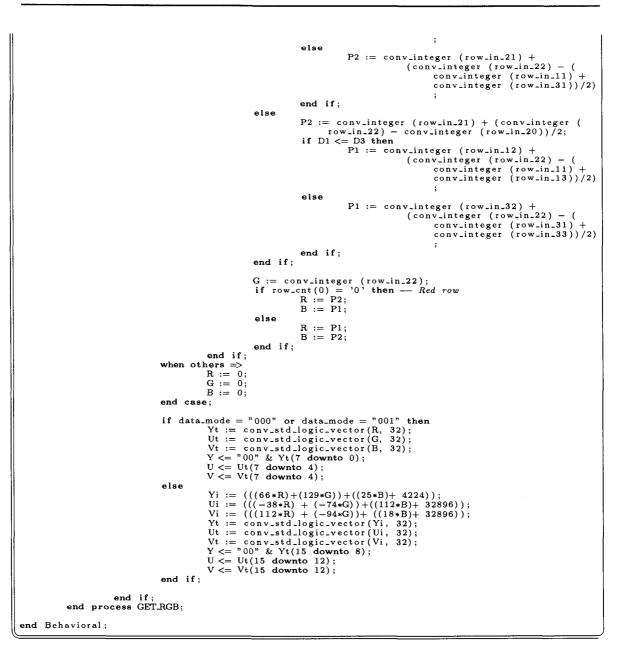

|              | 5.6                    | Image Processing Block                        | 64  |

|              | 5.7                    | Trigger Delay                                 | 65  |

|              | 5.8                    | Synthesis Constraints and Results             | 65  |

| 6            | Ima                    | ge Processing                                 | 68  |

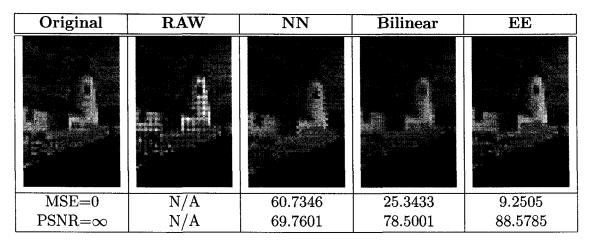

|              | 6.1                    | Demosaicking                                  | 68  |

|              | 6.2                    | Hardware Implementations                      | 71  |

|              | 6.3                    | Edge-Enhanced Real-Time Hardware Demosaicking | 73  |

|              | 6.4                    | Implementation and Results                    | 77  |

| 7            | Con                    | clusion                                       | 79  |

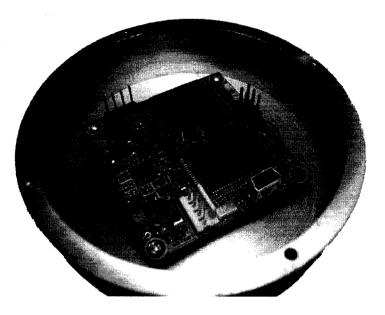

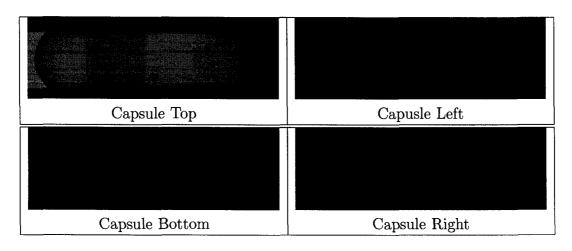

|              | 7.1                    | System Integration                            | 79  |

|              | 7.2                    | Summary                                       | 82  |

|              | 7.3                    | Future Work                                   | 84  |

| Re           | efere                  | nces                                          | 86  |

| A            | $\mathbf{Syst}$        | tem Requirements                              | 88  |

| в            | Can                    | nera Board Schematics                         | 92  |

| $\mathbf{C}$ | $\mathbf{V}\mathbf{H}$ | DL Code                                       | 99  |

| D            | MA                     | TLAB Code                                     | 124 |

| VI           | TA                     | AUCTORIS                                      | 129 |

# List of Figures

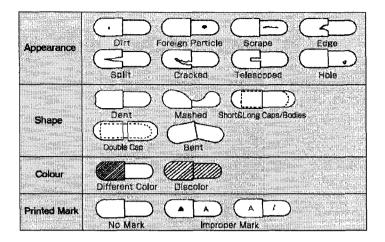

| 1.1 | Typical Defects in Gelatin Capsules              | 4  |

|-----|--------------------------------------------------|----|

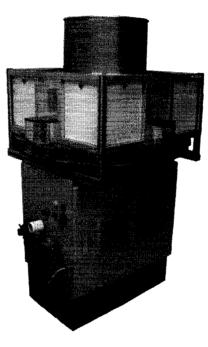

| 2.1 | Optisorter External View                         | 10 |

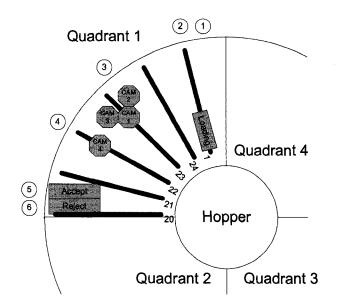

| 2.2 | Quadrant 1 Detailed                              | 12 |

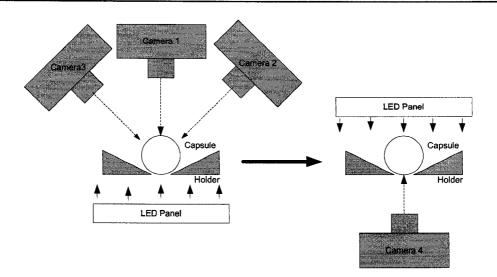

| 2.3 | Camera Configuration                             | 14 |

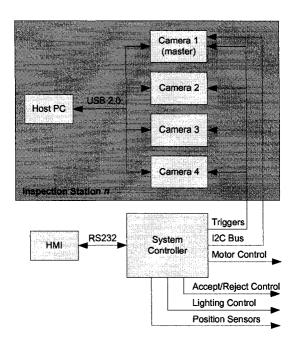

| 2.4 | System Block Diagram                             | 18 |

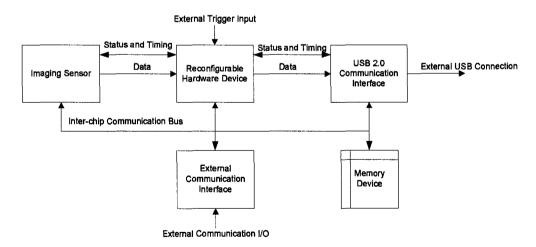

| 2.5 | Camera Block Diagram                             | 19 |

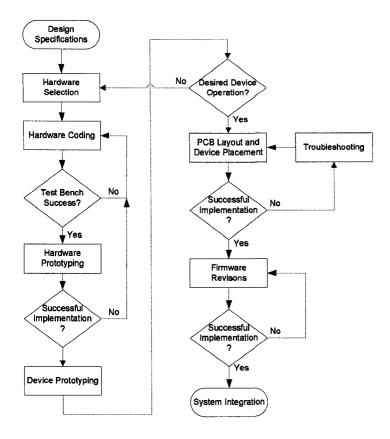

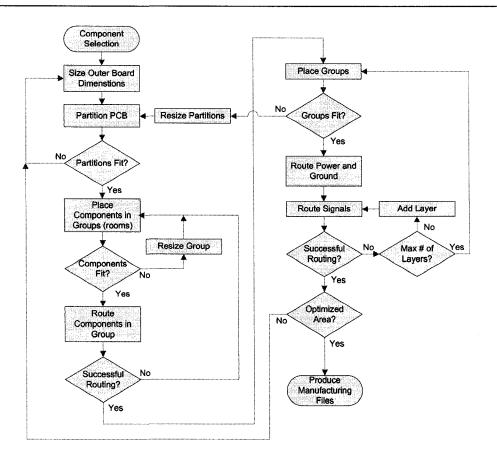

| 3.1 | Hardware Design Flow                             | 22 |

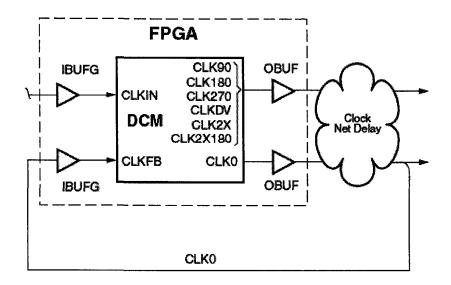

| 4.1 | DCM with Off-Chip Delay Feedback                 | 35 |

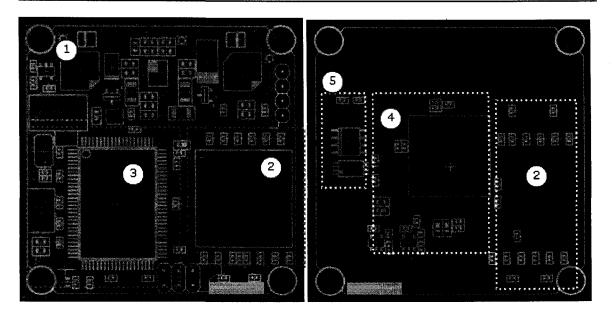

| 4.2 | PCB Design Flow                                  | 41 |

| 4.3 | PCB Partitions and Final Layout                  | 44 |

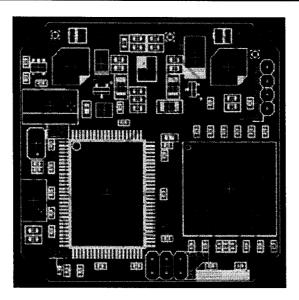

| 4.4 | PCB Power Plane Layout                           | 47 |

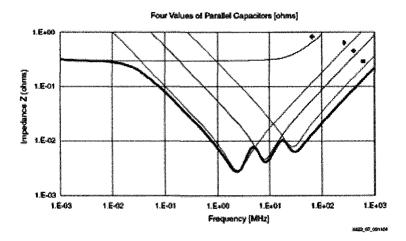

| 4.5 | Bypass Capacitor Values                          | 48 |

| 4.6 | Bypass Capacitor Impedance Profile [1]           | 48 |

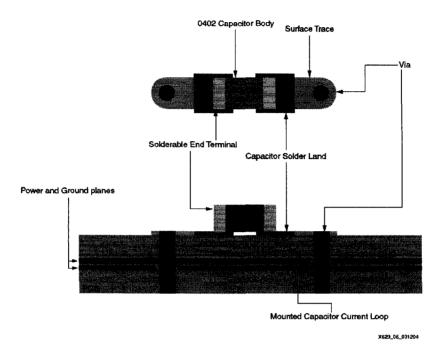

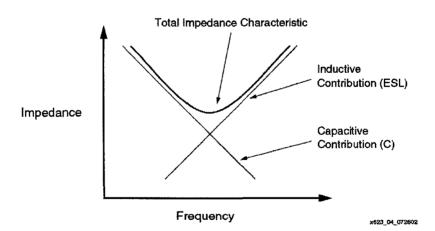

| 4.7 | Capacitor Placement Inductive Loop[1]            | 50 |

| 4.8 | Capacitor Impedance and Resonant Frequency $[1]$ | 50 |

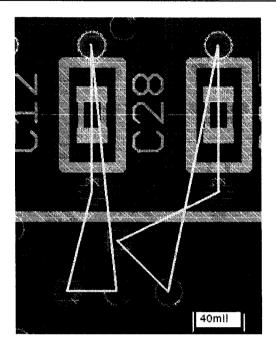

| 4.9 | Bypass Capacitor Critical Current Path           | 51 |

| 5.1 | FPGA VHDL Modules and Data Flow                  | 55 |

#### LIST OF FIGURES

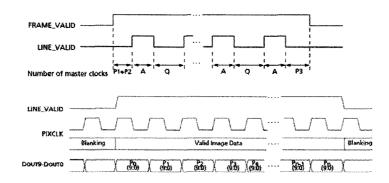

| 5.2 | MT9T001-3100 Timing [10]                   | 56 |

|-----|--------------------------------------------|----|

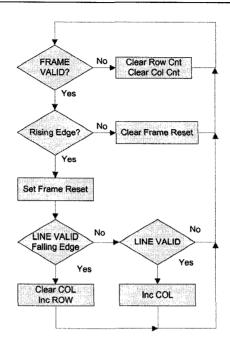

| 5.3 | MT9T001-3100 Synchronization Flow          | 57 |

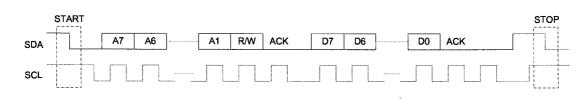

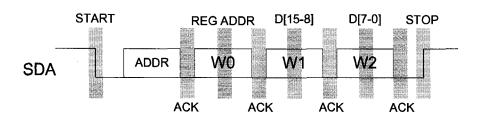

| 5.4 | I <sup>2</sup> C Bus Communication         | 59 |

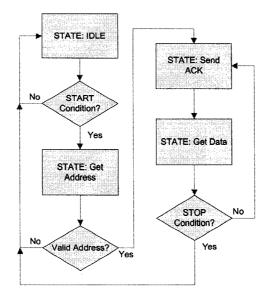

| 5.5 | $I^2C FSM \dots$                           | 60 |

| 5.6 | I <sup>2</sup> C write in FPGA             | 61 |

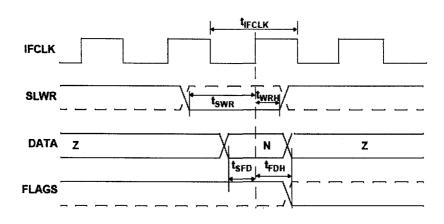

| 5.7 | Timing for Cypress FX2 Slave FIFO          | 63 |

| 6.1 | Bayer Pattern CFA on a CMOS Image Sensor   | 69 |

| 6.2 | 3x3 Data Window for Bilinear Interpolation | 71 |

| 6.3 | 5x5 Data Window for Edge Weight Function   | 73 |

| 7.1 | Camera PCB in an Enclosure                 | 80 |

| 7.2 | Final Capsule Images                       | 81 |

| B.1 | TPS Triple Supply Schematic                | 94 |

| B.2 | Spartan-3E FPGA                            | 95 |

| B.3 | Cypress FX2 USB Microcontroller            | 96 |

| B.4 | Micron Sensor Schematic                    | 97 |

| B.5 | I2C Component Schematic                    | 98 |

# List of Tables

| 1.1 | Current MV Capsule Inspection Systems and Proposed Model 6 |

|-----|------------------------------------------------------------|

| 1.2 | Proposed MV Components                                     |

| 3.1 | Design Specification Summary                               |

| 4.1 | Spartan FPGA Summary[19]                                   |

| 4.2 | Component Summary                                          |

| 4.3 | Spartan-3E Supply Voltage Ramp Rate[21]                    |

| 4.4 | I <sup>2</sup> C Devices: Loading Capacitance              |

| 5.1 | Write Controller Cases                                     |

| 5.2 | FPGA Utilization with Edge Enhanced Demosaicking           |

| 5.3 | FPGA Utilization without Edge Enhanced Demosaicking 67     |

| 6.1 | Bilinear Output                                            |

| 6.2 | Demosaicking Results                                       |

| A.1 | Defect List and Tolerances[5]                              |

| A.2 | High Level Business Requirements[5]                        |

| A.3 | High Level Performance Requirements[5]    90               |

| A.4 | Business Scenarios[5]                                      |

LIST OF TABLES

| B.1 Bill of Materials | B.1 | Bill of Materials |  |  |  |  | • |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  | Ģ | 92 |

|-----------------------|-----|-------------------|--|--|--|--|---|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|---|----|

|-----------------------|-----|-------------------|--|--|--|--|---|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|---|----|

# List of Abbreviations

| CFA                  | Color Filter Array                     |

|----------------------|----------------------------------------|

| $\mathrm{DCM}$       | Digital Clock Manager                  |

| DSP                  | Digital Signal Processing (Processor)  |

| EEPROM               | Electrically Erasable PROM             |

| FIFO                 | First In First Out                     |

| FPGA                 | Field Programmable Gate Array          |

| $\mathbf{FSM}$       | Finite State Machine                   |

| HMI                  | Human Machine Interface                |

| I/O                  | Input/Output                           |

| $I^2C$               | Inter Integrated-circuit Communication |

| IC                   | Integrated Circuit                     |

| $\operatorname{LED}$ | Light-emiting Diode                    |

| $\operatorname{LUT}$ | Look Up Table                          |

| MV                   | Machine Vision                         |

| $\operatorname{PAL}$ | Phase Alternating Line                 |

| PCB                  | Printed Circuit Board                  |

| PLC                  | Programmable Logic Controller          |

| PROM                 | Programmable ROM                       |

| RAM                  | Random Access Memory                   |

| ROM                  | Read Only Memory                       |

| VHDL                 | VHSIC Hardware Description Language    |

| VHSIC                | Very High Speed Integrated Circuit     |

|                      |                                        |

# Chapter 1

# Introduction

As technology advances, there is an ever increasing demand for faster, smaller and more affordable technology in all corners of industry. The field of machine vision is no exception. Advances in imaging devices and computing power has allowed machine vision based inspection systems to increasingly appear in a variety of industrial and manufacturing settings. The manufacturing of pharmaceutical gelatin capsules is an extremely high volume and high throughput manufacturing environment which has a strong need for quality control inspections to take place. However the intricacies of performing such inspections make both an effective and affordable solution a challenge to develop.

### **1.1 Project Overview**

The objective of this project was to work in collaboration with a local pharmaceutical capsule manufacturer, Pharmaphil Inc., with funding from the Ontario Centres of Excellence (OCE), to develop a cost effective prototype inspection system for two-part gelatin capsules.

The development of this system entailed upgrading and retrofitting an existing capsule sorting device, the Optisorter, to perform detailed, high-throughput visual inspection of these capsules at a low cost. The overall project was divided into three major parts to be developed by individual students. These included: development of control hardware and a PC interface, development of image processing software, and finally, the development of custom digital cameras for image acquisition, construction and processing. The final contribution listed above is the focus of this thesis along with contributions to co-ordinating system timing and modifying the imaging environment.

### **1.2 Quality Control of Two Part Gelatin Capsules**

The manufacturing of pharmaceutical two part gelatin capsules is a highly sensitive process to both environmental and process variations which lead to undesired flaws in some of the product. Currently there are limited methods of quality control that provide a flexible, accurate and cost-effective solution. As a single capsule is essentially valueless, neither time nor expense can be afforded to the quality assurance of the product [8], yet each capsule must be fully inspected for potential defects so that the manufacturer can provide a marketable quality guarantee for their product. The ability to ensure that the capsules are within certain manufacturing specifications and free of defects, without adding substantial cost the process, can give the manufacture an edge in sales and increase profit in this highly competitive market.

The two-part telescoping gelatin capsule was patented in London in 1847 by James Murdock [14]. They are made in two parts by dipping metal rods in a liquid gelatin. The two ends are trimmed, and supplied as partially closed units to various pharmaceutical companies who then separate, fill and close the two halves.

Typical defects found in these two part gelatin capsules include, but are not limited to: holes, dents, bubbles, missing halves, incorrect dimensions, and foreign product (such as a different colour or sized capsule). A complete list of defects required for detection is provided in Table A.1 and some examples of these defects can be seen in Fig. 1.1. The cost of discarding a defective capsule is negligible especially when compared to the potential cost that could be incurred by its accidental distribution. Defective capsules can disrupt the filling process performed by drug companies that purchase the product, leak contents into packaging, or in the case of a foreign capsule (such as a red pill appearing in a batch of blue pills) promote a lack of confidence in the drug distributor or even pose legal issues. Hence, there is a strong desire for quality assurance in the manufacturing of these capsules. The following sections detail current methods of defect detection, state of the art solutions on the market and the advantages of a custom Machine Vision (MV) solution.

### **1.3** Methods of Defect Detection

### **1.3.1** Current Inspection Methods

There are currently two primary methods being used to inspect two part gelatin capsules for quality assurance. The simplest method is manual inspection, whereby an individual attempts to identify defective capsules as they pass through an inspection station. This usually involves a large quantity of capsules moving over a conveyor belt

Figure 1.1: Typical Defects in Gelatin Capsules

that is illuminated from the bottom. Although this is effective for processing very large quantities at a very fast rate, the accuracy in which the capsules are inspected is greatly compromised. This is because not every capsule can be fully inspected by the individual and the integrity of the inspection fluctuates greatly due to human error, fatigue, and focus. Also, the capsules are susceptible to areas of occlusion where they may overlap or touch one another, making it impossible for every capsule to be fully inspected. Generally, if an excessive number of defective capsules are identified, the entire manufactured batch is discarded, adding greatly to the overall manufacturing cost. The benefits of such a manual system are the reduced equipment and maintenance cost, especially where labour is relatively inexpensive.

The second predominate method of capsule inspection involves the use of machine vision systems to attempt to identify defective capsules. While the benefits of such systems include improved accuracy and consistency in the inspection of each capsule, they are typically very expensive to setup, may suffer reduced inspection rates depending on the hardware and demand on the system and generally lack flexibility and the ability to upgrade.

### **1.3.2** Introduction to Machine Vision

A Machine Vision (MV) System is the application of computer vision to industry and manufacturing. A typical machine vision system consists of several of the following nine components[16]:

- 1. One or more digital or analog cameras (black-and-white or colour) with suitable optics for acquiring images.

- 2. Camera interface for digitizing images (widely known as a "Frame grabber").

- 3. A processor, often a PC or embedded processor, such as a DSP. In some cases, all of the above are combined within a single device, called a "Smart Camera."

- Input/Output hardware (e.g. digital I/O) or communication links (e.g., network connection or RS-232) to report results.

- 5. Lenses to focus the desired field of view onto the image sensor.

- Suitable, often very specialized, light sources (LED illuminators, fluorescent or halogen lamps, etc.).

- 7. A program to process images and detect relevant features.

- 8. A synchronizing sensor for part detection (often an optical or magnetic sensor) to trigger image acquisition and processing.

- 9. Some form of actuators used to sort or reject defective parts. Each of the following must be carefully considered and customized for a specific application.

In this thesis, the complete specifications of the MV system used for this application will not be discussed in extensive detail, as the focus of this document is on the imaging sensor.

### **1.3.3** Commercial Systems

There are currently a variety of MV systems on the market targeted at defect detection of pharmaceutical gelatin capsules and tablets. These range in price from \$4,200 USD to over \$600,000 USD. Table 1.1 outlines a few current systems as well as the specifications for the proposed system. The approach these systems use to acquire and process images varies greatly. Almost all the systems listed rely on line scan cameras that process visual information as it is acquired. This benefits the system by working extremely fast, but it limits the variety and accuracy of inspections that can take place because only a single line of the image is available to process. In addition, storing images of defective capsules is difficult unless image buffering occurs in the system. Table 1.1 shows that regardless of the type of camera used, generally an inspection rate of at least 60,000 capsules per hour is attained by these systems.

Some current systems such as the CVIS-SXX-E consist of a very elaborate mechanical system which adds significantly to the cost of the overall system. This seems typical for most of the systems, as fixturing the capsules proves to be a difficult task. Finally, while an average of 100 micron resolution is maintained, each system does vary to some degree in detail and resolution.

| System Model  | Cost      | Caps/h  | Camera Type     | Processing  | Resolution         |

|---------------|-----------|---------|-----------------|-------------|--------------------|

| CTI-1         | \$4,200   | 50,000  | Unknown         | Unknown     | 0.1mm              |

| InspeCaps 150 | Unknown   | 120,000 | 3x Linescan CCD | Visicard 4  | 0.1mm              |

| CVIS-SXX-E    | \$600,000 | 100,000 | 8x Linescan CCD | Analog Sig. | $0.1 \mathrm{mm}$  |

| MVT           | \$350,000 | 60,000  | Unknown         | Unknown     | $0.2 \mathrm{mm}$  |

| Proposed      | <\$35,000 | 60,000  | 12x  CMOS       | Digital PC  | $0.01 \mathrm{mm}$ |

Table 1.1: Current MV Capsule Inspection Systems and Proposed Model

## 1.4 Proposed Solution

The proposed system maintains the competitive throughput requirements of competing systems with an inspection rate of 60,000 capsules per hour, while showing greatly reduced cost and an increase in inspection accuracy. This is achieved by taking a completely customized approach to the hardware of the system and combining it with an affordable existing mechanical design. The additional benefits of such an approach lay in both the flexibility and the ability to upgrade the proposed system. Table 1.2 outlines the general MV components used in the proposed system and the advantages of using these components over existing MV systems.

| Component        | Typical       | Proposed             | Advantage          |

|------------------|---------------|----------------------|--------------------|

| Camera           | CCD Linescan  | CMOS                 | Full digital image |

| Interface        | Frame Grabber | USB 2.0              | Cost effective     |

| Processor        | DSP           | PC                   | Easy to upgrade    |

| Lens             | Standard      | Standard             | None               |

| Lights           | Red LED       | White LED            | Full colour images |

| IP Program       | Custom        | Custom               | Flexible to change |

| Sync. Sensors    | Unknown       | Inductive proximity. | Easy to interface  |

| Reject Mechanism | Mechanical    | Air actuator.        | Touchless          |

Table 1.2: Proposed MV Components

### 1.5 Thesis Organization

This thesis discusses the design, build and testing of a custom digital camera used as part of a MV system for quality control in the manufacturing of two part gelatin capsules. Chapter 2 begins by giving an overview of the proposed MV system including the current mechanical setup, imaging environment and system timing constraints. Following this, Chapter 3 discusses the design methodology for the development of the camera component of the MV system. This includes the design specifications for the camera, the design flow methodology used for high level device design and finally introduces the development tools and equipment used for programming, simulating and testing the design. Chapter 4 discusses the actual hardware design of the camera including detailed schematic designs as well as physical component layout and PCB design consideration for the final camera. Chapter 5 will detail the VHDL code developed for the FPGA on the camera and will discuss the various blocks and their role on the camera. Chapter 6 introduces the image processing elements of the camera, specifically discussing Colour Filter Array (CFA) imaging sensor data and the use of "demosaicking" techniques to perform image reconstruction. This chapter will also cover the software simulation and hardware implementation of several demosaicking methods including a novel real-time edge enhancement method proposed in this thesis. Finally, Chapter 7 will discuss the integration of the camera with the MV system as well as conclude the work and provide a discussion for future development of the system.

# Chapter 2

# System Overview

### 2.1 Introduction to the Optisorter

### 2.1.1 Background Information

The Optisorter, seen in Fig. 2.1, was a German engineered MV system built in the early 1990s. A number of these systems were acquired by Pharmaphil Inc. to be implemented as an affordable quality control method for the manufacturing of their size #00-#5 two part gelatin capsules. Although the Optisorter has a solid mechanical foundation for an MV system, the hardware was essentially obsolete. The exact functionality of the Optisorter is still unknown, however the hardware contained therein gives a good indication of what functions this system may have performed.

With only analog PAL cameras and analog processors, the existing machine was most likely only able to identify foreign capsules and measure basic geometric tolerances such as the length and width of the capsule.

Figure 2.1: Optisorter External View

### 2.1.2 Summary of Operation

The system original system is comprised of four identical inspection stations designed to operate in parallel to provide the desired system throughput. Capsules are initially loaded into a large hopper seated on top of the machine. This hopper feeds a series of 24 radial arms that rotate counter clockwise within the system. As an arm enters a quadrant, the holder is first cleared of any stray contents such as a double loaded capsule from the previous station. Next, a loading mechanism allows a single capsule to descend down the arm into a holder that seats the capsule. The arm continues to spin until the capsule passes beneath a series of four cameras which are triggered by proximity sensors that track the arm positions. The four photographs are inspected using simple analog circuits and an accept or reject decision is made as the capsule passes over an air valve actuator responsible for ejecting the capsule into the appropriate bin.

## 2.2 System Timing

To understand the most important factors in system timing, let an *event* represent an operation that will be occurring in the system when an arm arrives at a certain location and a *cycle* represent the time it takes for a new arm to arrive at an event, in other words, the time between arms. Major events will include:

- 1. Clearing the holder.

- 2. Loading the holder.

- 3. Imaging the top of the capsule.

- 4. Imaging the bottom of the capsule.

- 5. Accepting the capsule.

- 6. Rejecting the capsule.

Fig. 2.2 shows the details of quadrant one with six of the 24 arms that will appear in the quadrant at a single cycle. The general location of the enumerated events above are show as circled numbers.

It is important to note that because each event is performed for a new arm on every cycle, the amount of time allocated for an event is dependent on the cycle time and not on the amount of time between events. This means greater time allocation for critical events can only be gained by increasing the time allocated to a cycle, not by increasing the physical spacing between events. Since cycle time is the product of the physical spacing between arms and the rotational speed of the system, the system timing is directly proportional to the rotational speed. This ultimately defines the total system throughput. To achieve the desired inspection rate of 60,000 capsules per hour, the 24 radial arms must be spinning at 10.411 revolutions per minute.

Figure 2.2: Quadrant 1 Detailed

This was found by determining the number of capsule a single arm would have to inspect in this time and then computing how fast this arm would have to move in order to accomplish this task. Equation 2.1 shows this computation.

$$\frac{1000 \ caps/min}{(24 \ arms/rev \times 4 \ caps/arm)} = 10.4167 \ rev/min \tag{2.1}$$

Since a cycle represents 1/24 of a revolution, the maximum time allocated to any event can be computed as shown equation 2.2.

$$\frac{60 \ sec/min}{10.4167 \ rev/min} \times (1/24) \ rev = 0.24 \ sec \tag{2.2}$$

Therefore, the most critical event of the system (arguably the transfer and processing of image data) must occur in < 240 ms. Both equations 2.1 and 2.2 are simply theoretical calculations based on the operation of the the system as described above.

## 2.3 Imaging Environment

The current Optisorter system uses four cameras to capture the full 360 degree surface of the capsule. The capsule is seated in an opaque holder with a slot down the middle which allows both the top and back surfaces of the capsule to be visible. The capsules are illuminated with back lighting to cast the outline of the capsule and any defects in shadow while illuminating the background and flawless portions of the body for the capsule. Three cameras are positioned to examine the top surface of the capsule while a single camera is positioned from the reverse angle to examine the bottom of the capsule. The cameras are angled to image as much of the surface as possible, however, the solid metal holder occludes a small portion where the capsule makes contact with the holder. In an ideal imaging environment, the back lighting would remain perpendicular to the camera in order to reduce any uneven illumination that results from reflected light. It would appear that due to space constraints, a single panel of LEDs was used for back lighting the three top images while a separate panel of LEDs was used to back light the bottom of the image. Fig. 2.3 shows the details of the camera and lighting setup.

### 2.4 Objectives for Modification

As the project objectives state, the ultimate goal is to retrofit the existing Optisorter system with upgraded hardware to perform faster, more comprehensive inspections of the capsules. The following modifications were proposed as part of the final system upgrade. These modifications were to be developed as three separate parts by individual students.

1. New hardware to perform motor control, monitor proximity sensors, control accept and reject air actuators, trigger cameras, and interface with the HMI.

Figure 2.3: Camera Configuration

- 2. Develop a PC based computer vision system to perform image processing and analysis.

- 3. Develop new low cost digital cameras to acquire and transfer images.

The third modification listed above is the focus of this thesis where the first two items were developed my Neil Scott and Mohammad Islam respectively. More specific technical details regarding the requirements of these cameras will be discussed in subsequent section. For more information regarding the other project objectives, refer to thesis of Neil Scott and Mohammad Islam.

### 2.4.1 Selecting a Camera

After determining the overall system requirements, it was necessary to select the hardware for capturing images and transferring them to PCs. The first and foremost consideration was the potential cost of a camera, as 16 cameras were required for a complete system (four cameras for each of the four quadrants). There were three possible approaches, each with inherent advantages and disadvantages.

1. Frame Grabber

The first possible approach would be to purchase very inexpensive image sensors that could be connected via a Frame Grabber card to a PC. This would result in extremely fast implementation, but the high cost of a frame grabber made this solution very undesirable, especially if the final system were to be mass produced.

2. Firewire PC Interface

The second consideration was to create custom cameras with a high speed Firewire interface. Producing custom cameras would cost effective compared to the cost of a frame grabber. It would also allow the hardware to be reasonably upgraded. However the design of such cameras would require longer development time. This was still advantageous over the high cost of the frame grabber interface, however developing hardware and PC drivers for the Firewire interface would have been quite difficult due to the interface complexity and lack of commercial hardware and software support.

3. USB PC Interface

The final option was to continue with the idea of custom cameras, only with a slightly slower speed USB interface. The advantages of USB lay not only in the cost effectiveness, but in ease of development since many USB ready micro controllers and open sourced software were readily available. This was determined to be the optimal approach, as long as the USB transfer rates could keep up with required data throughput.

Since the most desirable data interface was USB 2.0, a quick calculation was made to verify that the USB transfer speeds could keep up with the system timing demands. Assuming a simple 1024x768 image window at 8 bits per pixel, a single image would consist of 786432 bytes of data. USB 2.0 has a theoretical maximum transfer rate of 60 MB/s but this is unattainable due to packet communication overhead. Bulk transfer rates of up to 40 MB/s are possible with a realistic observable transfer rate of around 30 MB/s [3]. Preliminary USB 2.0 transfer test conducted by Neil Scott (a partner in this collaborative project) found a sustained bulk transfer rate of 31145280 bytes per sec or equivalently 30 MB/s. At this rate, it would take 0.1 seconds to transfer 4 full images to the PC. As 240 ms is the maximum cycle time available in order to achieve the desired system throughput, the USB interface would be sufficient and still leave up to 140 ms to be allocated for image processing to occur within the PC.

The preliminary system timing consideration outlined above showed that a USB 2.0 interface would be sufficient, and two demo boards were obtained to perform initial hardware feasibility tests.

### 2.4.2 Modifying the Imaging Environment

Although the current imaging setup may be sufficient, a number of improvements were proposed to provide improved images for processing. These included:

- 1. Improved lighting

- 2. Transparent holders

- 3. Three camera setup

- 4. Reflected front lighting

- 5. Reduced stray reflections

Each item listed above was identified as a potential area of improvement not only for the quality of images, but in the case of a three camera setup, reduced system load and cost. Of these items, only the first was implemented in the final system. Instead of using red LEDs, the diffused back lighting of the current system was upgraded to high intensity white LEDs. The higher intensity light allowed for a shorter exposure time while taking an image of the capsule, resulting in less blur introduced due to the movement of the capsule. The white light allowed for full color spectrum exposure of the color CMOS image sensors used in the final custom cameras.

The use of transparent holders for fixturing the capsules during imaging was tested, however, due to difficulties manufacturing perfectly clear holders free of scratches, the existing opaque holders were used. The use of clear holders should be considered as an area of future development.

A three camera setup was also tested, however without perfect clear holders, there are areas of the capsule that are occluded using three cameras and opaque holders. Again, the use of a three camera setup should be further investigate along with the use of clear holders.

The idea of reflected front lighting was proposed as a way of illuminating the front of an opaque capsule without needing an additional front light. The idea was to place a reflective surface over the front of the camera (around the lens) so that stray light from the back lighting of the capsule would be reflected and illuminate the surface of the capsule. This would provide the visibility required to identify color and surface defects. This item was tested and verified, however, was not implemented since the prototype was only desired to inspect clear capsules due to lack of project time.

Finally, as another point to consider, it was found that under certain circumstances, light from an inspection was reflecting off the various shiny metallic surfaces withing the system, causing bright areas on the capsule surface to appear. This type of reflection could be reduced by ensuring all surfaces within the system had a dark matte finish as to reduce the reflection of light within the system. This was not implemented into the final system, but could be considered as an area for improvement in the future development of the inspection system.

### 2.5 Proposed Design

Using the understood operating principles of the existing mechanical system along with the desired areas of improvement, a basic proposed system overview was composed. This can be seen in Fig. 2.4.

Figure 2.4: System Block Diagram

The design maintains the principal concept of having four identical stations work in parallel to accomplish the desired inspection throughput. These four inspection stations are connected via a custom control board that is responsible for co-ordinating the entire system. The control board acts as an interface between the mechanical systems and the computer vision stations, triggering the stations to capture an image of the capsules at the appropriate time and using the inspection results from the station to mechanically accept and reject the appropriate capsules.

The proposed custom digital cameras reeive triggers from the control board and

send image data via a UBS 2.0 interface to a PC that is responsible for performing the necessary inspections. The results of the inspections are relayed through the master camera, back to the control board. Thus the proposed custom cameras must provide the following functionality:

- 1. Maintain the desired inspection rate.

- 2. Communicate image data to PC via USB 2.0.

- 3. Receive external triggers.

- 4. Output inspection results.

- 5. Remain competitive in cost compared to commercial systems.

- 6. Satisfy size constraints of existing imaging fixtures.

At this point, a proposed camera architecture was developed. Fig. 2.5 shows the most basic required functional blocks.

Figure 2.5: Camera Block Diagram

In this design, a suitable imaging sensor provides image data to a reconfigurable hardware device. This device acts as the camera controller, initially processing the image data and preparing the image data output. The image data is then be sent to a USB 2.0 capable microcontroller, which is responsible for the data communication to the PC for image processing. To satisfy the external communication requirements, an I<sup>2</sup>C bus extender was used along with simple 3.3 V inputs for receiving triggers. A small EEPROM is also added to the design, in order to store basic configuration information such as the device identification for the USB enumeration as well as a master camera setting.

A unique feature to this proposed architecture is that there will be no frame buffering taking place within the camera. Data is processed and transferred in realtime. This will greatly reduce the unit cost, as well as assist in maintaining the desired inspection rates for the system.

# Chapter 3

# Camera Design Methodology

## 3.1 Camera Design Flow

After identifying the objectives for the custom digital camera and how it was to operate as part of the larger system, a design procedure was developed. The major steps involved in the camera design methodology include:

- 1. Deriving device specifications

- 2. Simulating hardware operation

- 3. Prototyping functional groups

- 4. Testing hardware functions

- 5. Building complete device

- 6. Testing device operation

- 7. System integration

- 8. System testing

Fig. 3.1 shows the general bottom-up design flow for the proposed custom camera. With our camera specifications, performance requirements, desired operation and basic overview in mind, this design procedure was developed to assist in the realization of the custom camera.

Figure 3.1: Hardware Design Flow

## **3.2** Design Specifications

The system design specifications were based on inspection requirements outlined by Pharmaphil Inc. The details of both the business and defect detection requirements can be found in Appendix A. Table A.1 outlines the inspection requirements used to derive the required resolution of the system. Table A.2 outlines the desired operation and is used to determine the required operating speed of the system as well as the test parameters. Finally, Table A.3 describes the desired features and functionality that must be incorporated into the modified design. Since the focus of this thesis is on the Camera Design with some insight into the imaging environment, Table 3.1 summarizes the pertinent specifications and the area of the system design to which they apply to.

| Requirement         | Specification   | Applies to              |

|---------------------|-----------------|-------------------------|

| Defect size         | 0.2mm or larger | Imaging sensor          |

|                     |                 | Imaging Environment     |

| Capsule Colour      | RGB/YUV         | Imaging sensor          |

|                     |                 | Imaging Environment     |

|                     |                 | Reconfigurable Hardware |

| Speed of Inspection | 1000  caps/min  | Imaging Sensor          |

|                     |                 | Data Interface          |

|                     |                 | Memory/Buffering        |

| Products Inspected  | All             | Reconfigurable Hardware |

Table 3.1: Design Specification Summary

# 3.3 Major Design Methods

The following sections summarize the procedures used while developing the camera. These cover the actual software and hardware tools used and their function in the design process.

## 3.3.1 Reconfigurable Hardware Programming

One of the largest portions of this design project involved developing hardware code for the reconfigurable device used on the camera. All coding was done in VHDL because of its modularity and easy readability (though Verilog coding would have been a viable substitute). The development environment used was Xilinx ISE 10.1 where the final VHDL code was synthesised.

The required VHDL coding was broken down into various behavioural blocks. Each block was behaviourally verified using an appropriate test bench when required, also coded in VHDL.

The top level VHDL block was assigned timing constraints with respect to the system clocks that would be provided to the system and final timing and resource utilization reports were generated. More specific information pertaining to the actual design results can be found in Chapter 6.

#### 3.3.2 Simulation Tools

Some aspects of development for the system, such as the development of a demosaicking (image reconstruction) algorithm required rapid logical implementation for verification before realization in hardware as part of the final design. For these purposes, Matlab was used. Algorithms were implemented as functions in ".m" files and called from either the Matlab command line or by a series of tests coded in additional ".m" file. Although Matlab is a relatively slow simulation tool, it was selected because of the wide range of library support in image processing as well as its ability to easily interface with external data sources. More detail about the specific functions implemented in Matlab, as well as the corresponding code, can be found in Chapter 6 and Appendix D.

## 3.3.3 Prototyping Hardware

Only limited hardware prototyping took place concerning the camera design. This was primarily due to the nature of the components, specifically their unique footprints that could not easily be mounted to a breadboard. Essentially, hardware prototyping took place by modifying demo boards. Ideally, multiple revisions of the final PCB would have been developed allowing for measurement of circuit noise and further adjustments. Details on the camera demo board used are outlined in the component selection section of the following chapter.

## 3.4 Testing

Testing the design occurred on two levels. The first testing occurred independently of the inspection environment, ensuring that the resulting camera was capable of generating the required hardware. The second form of testing occurred with the camera integrated into the system, increasing the operating speed and analyzing the resulting quality of image until failure in either the device or in the transferred data. The test results were used to verify that the final design met the system requirements. The details of these test are outlined in the conclusion of this thesis.

# Chapter 4

# Hardware Design

## 4.1 Component Selection

After the design specifications for the camera were determined, the next step was to select specific components capable of satisfying these requirements. Fig. 2.5 showed the major components that were to be included in the design. These include:

- 1. Imaging sensor

- 2. Reconfigurable device

- 3. USB 2.0 compatible microcontroller

- 4. External communication interface

- 5. Small memory device

The following sections detail the selection of these devices and justifies their use in the design with respect to the system specifications.

### 4.1.1 Imaging Sensors

Two of the most heavily weighted factors in selecting hardware were: cost and availability. Under these constraints, a variety of imaging sensors were compared for suitability. One critical decision was on whether to use a CMOS sensor or a CCD sensor as both have specific advantages and disadvantages.

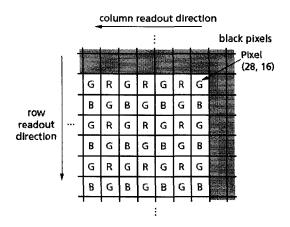

Although they are faster and often cheaper than CMOS sensors, Charge Coupled Device (CCD) sensors only output an analog signal representing the charge resulting from a pixel being exposed to light. This analog value must be amplified and converted to a digital value by additional components and circuitry. On the other hand, a CMOS image sensor has an internal CCD with supporting digital circuitry integrated into the sensor itself. The sensor data output from a CMOS is in digital format and accompanied by associated timing signals for tracking the row and column of the current pixel being read out. In addition, CMOS sensors allow for windowing an area of the sensor's pixel array so that the entire image frame does not need to be outputted from the device. This provides greater control over both the exposure time of the sensor as well as the frame readout time. Micron, one of the primary suppliers of CMOS image sensors, provided a variety of demo boards with USB support. The sensors, though slightly more expensive than typical CCD sensors, were readily available in large quantities and would not require as much additional hardware (i.e. a controller to integrate into the design) providing overall savings in development costs.

The Micron MT9T001 3.1 mega pixel sensor was selected as it was readily available with a demo board featuring a chip memory, Virtex II FPGA and a Cypress FX2 USB microcontroller. This demo board provided a solid backbone to the camera design, even though it possessed expensive components and unnecessary features for the requirements of our design, especially in terms of memory and logic capacity of the FPGA. Nonetheless, the demo board acted as the basis for the custom camera's hardware selection in the first iteration of the design flow.

## 4.1.2 Reconfigurable Devices

The reconfigurable device on the camera plays a vital part in synchronizing the various hardware components as well as managing and processing image data. The reconfigurable device acts as the camera's memory for all necessary image data buffering as well as a communication interface to the imaging sensor. Selecting a suitable device for such a dynamic role involved many considerations and making a number of trade offs. The decision parameters for selecting the appropriate device were as follows in order of priority.

- 1. Memory

- 2. Cost

- 3. Device Capacity

- 4. Development Time

- 5. Footprint

- 6. I/O Capacity

Initial firmware development was done on a Xilinx Virtex II series device (XC2V2500) as it was part of the Micron Demo board (MI3100 sensor head with DEMO2 FPGA base) which was used as a basis for the final design. Since expandability of the initial design was part of the camera design specifications, a reconfigurable device was required.

There were two predominate reconfigurable devices considered for this design. They were the FPGA and CPLD. FPGAs are "fine-grain" devices, meaning they contain many tiny blocks of logic made up of flip-flops. CPLDs are "coarse-grain" devices with relatively few larger blocks of logic made up with flip-flops. FPGAs are RAM based and need to be configured each time they are powered up. CPLDs are EEPROM based and retain their memory after being programmed. CPLDs have faster input-to-output timing than FPGAs because FPGAs have a coarse-grain architecture where a single logic block can implement a more complex function. However, FPGAs have special routing resources to implement efficiently binary counters and arithmetic functions (adders, comparators, etc.) and RAM, where CPLDs do not. In general, FPGAs can contain very large digital designs, while CPLDs can contain small designs only [11]. In order to satisfy the more sophisticated operations required by the reconfigurable device, an FPGA was selected as the more suitable device for this role.

Next, an appropriate FPGA was selected. As Xilinx ISE development software was readily licensed by the university with full access to support and CoreGEN designs, Xilinx FPGAs were favored over competing FPGAs such as Altera. This decision to use a Xilinx device was simply due to the availability of licensed development software as well as compatibility of code being developed on the demo board with a Xilinx FPGA.

As demo board firmware was already being developed for this application using the Xilinx Virtex II device, Virtex was the first family investigated as a suitable Xilinx FPGA for the final camera design. However, the cost for the Virtex family far exceeded the cost parameters outlined, so the lower cost Spartan family was investigated. Table 4.1 shows the Spartan series descriptions used in selecting the appropriate device. Comparing the Spartan summary to our decision metrics, it was quite clear that the Spartan-3E series was most suitable for our application due to the high logic density, low I/O count and overall low cost.

4. HARDWARE DESIGN

| Series         | Domain           | Description                                                                                                                                                       | Cost(CAD)      |

|----------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Spartan-3A DSP | DSP optimized    | For applications where in-<br>tegrated DSP MACs and<br>expanded memory are re-<br>quired.                                                                         | \$140 to \$215 |

| Spartan-3AN    | Non-Volatile     | For applications where non-<br>volatile, system integration,<br>security and large user flash<br>are required.                                                    | \$13 to \$80   |

| Spartan-3A     | I/O optimized    | Ideal for bridging, differ-<br>ential signaling and mem-<br>ory interfacing applications,<br>requiring wide or multiple<br>interfaces and modest pro-<br>cessing. | \$63 to \$88   |

| Spartan-3E     | Logic optimized  | Ideal for logic integration,<br>DSP co-processing and em-<br>bedded control, requiring<br>significant processing and<br>narrow or few interfaces.                 | \$11 to \$75   |

| Spartan-3      | I/O + Logic Opt. | Ideal for highly-integrated data-processing applica-<br>tions.                                                                                                    | \$10 to \$130  |

Table 4.1: Spartan FPGA Summary[19]

The final step was to select a specific device from the Spartan-3E series FPGAs. As per the reconfigurable device requirements listed at the start of the section, the specific Spartan-3E device was not only selected based on its internal specifications, but also based on a common footprint that would allow for future upgrades. The Spartan-3E500 was selected as a balance of cost and logic capacity in the series of devices that shared the FT256 footprint. This footprint was selected not only for its compact nature, but also so that the more powerful Spartan-3E1200, or cheaper Spartan-3E250 could replace the selected FPGA without having to modify the physical layout and placement of these devices in the final camera design. A final point on the FPGA selection relates to the powering of the device. Unlike the more expensive Virtex II devices, the Spartan series has some specific power requirements. In order to supply the correct voltages to the device with the proper power on start-up conditions, a separate component was chosen to perform this role. The TPS7500 Triple supply by Texas Instruments was chosen based on a recommendation in the device data sheet [21].

### 4.1.3 Communication Interface

There were two main components selected to act as communication interfaces for the camera. The primary device responsible for transferring image data to the PC is the Cypress CYCFX2. This specific device was selected by the developer of the USB 2.0 communication drivers so the details of this device are not covered in detail as part of this thesis.

One benefit of using this device is its ability to act as a data slave device. A 16bit data bus allows an external device to write data to a 4 KB FIFO within the Cypress controller that is automatically packeted and sent according to USB 2.0 communication specifications. The device also supports an I<sup>2</sup>C interface which is utilized on the camera as part of the external communication interface. Finally, the device is relatively cheap which is an extremely important factor in component selection.

The second major device is the selection of an  $I^2C$  bus extender. This allows the local  $I^2C$  bus on the camera to be connected to the control board for relaying the accept and reject singles from the PC. The NXP P82B715TD-T device was simply selected because of its low cost, availability and ability to provide the required range of communication dictated by the physical system.

## 4.1.4 Component Summary

Table 4.2 summarizes the major components selected for the device design noting how they will be referenced for the remainder of the thesis. For a complete list of components used in the device design, a bill of materials can be found in appendix C.

| Device        | Manufacturer     | Part Number        | Referenced As |

|---------------|------------------|--------------------|---------------|

| Image Sensor  | Micron           | MT9T001P12STC      | MT9T001       |

| FPGA          | Xilinx           | XC3S500E-4FTG256C  | Spartan-3E    |

| USB MCU       | Cypress          | CY7C68013A-100TAXC | FX2           |

| Bus Extender  | NXP              | P82B715TD-T        | $I^2C BE$     |

| Memory        | Microchip        | 24LC128-I/ST       | 128kB EEPROM  |

| Triple Supply | Texas Intruments | TPS75003RHLT       | TPS supply    |

Table 4.2: Component Summary

## 4.2 Circuit Schematics

After having selected the specific devices to use in the camera design, the device connections must be carefully made to ensure their desired and correct operation. Some of the major considerations entail: powering the devices, terminating I/O, routing I/O and external connectors, sizing filtering capacitors, providing clocks, building reset circuits, designing power supplies and even placing test points on critical nets.

## 4.2.1 Micron MT9T001 CMOS Imaging Sensor

The MT9T001 CMOS imaging sensor is one of the most critical devices in the camera design. This device is responsible for acquiring image data and thus any error introduced at this point will propagate throughout the remaining components. There were some particular considerations that had to be made when designing the schematics for this device as it required separate analog and digital power supplies. The purpose of these separate supplies is to isolate the very noisy digital circuitry from the analog portion of the IC, which is highly susceptible to noise in the power supply.

To improve the sensor's operation, separate analog and digital low drop-out linear regulators were used to power this device. However, the ground pins share the same grounding net. The appropriate placement of grounding points in the PCB layout of this device made this possible, reducing the effect any ground noise may have on the analog ground of the device by providing a direct path for the current to flow, preventing potential current leaks towards the other ground pins.

The power saving features of the chip have been grounded to simplify the PCB routing. The remaining data bus, timing signals and reset and status signals have been connected to pins on the FPGA for flexible control over this device. Fig. B.4 in Appendix B shows the final schematic drawing for the Micron MT9T001 sensor.

## 4.2.2 Xilinx Spartan-3E500 FPGA

#### 4.2.2.1 I/O Connections

Since the FPGA acts as the main controller for the custom camera, almost every device in one way or another is connected to the FPGA. The I/O connections for the FPGA to the neighbouring devices were placed on pins whose functions did not change between the three different Spartan-3E devices that share the FT256 footprint. This provided greater flexibility for future upgrades. All I/O on the device were configured as 3.3 V Low Voltage CMOS (LVCMOS33) capable of syncing or sourcing up to 16 mA of current [21].

#### 4.2.2.2 Clock Connections

Special considerations were also made when connecting clock signals to the FPGA. Although the FPGA can internally route any I/O to any cell, the Spartan-3E device has dedicated Digital Clock Managers (DCMs) with specific pins associated with them. Any part of the design where an output clock was supplied to another device, such as the clock for controlling exposure rate of the MT9T001 sensor, a neighbouring I/0 pin was shorted to the DCM output in order to provide DLL feedback for the clock manager. The configuration of such a scenario can be seen in Fig. 4.1. For the specific case of the camera schematic net CLKIN (provided to the MT9T001 sensor from the FPGA), the net IFCLK enters the FPGA at IBUFG feeding CLKIN of the DCM (which is optionally shifted within the DCM). This is outputed from the FPGA at OBUF as the net CLKIN which is then connected to the MT9T001 sensor. The net CLKIN also re-enters the FPGA at the IBUFG feeding the *CLKFB* of the DCM to regulate the clock output. This configuration is essential to removing any clock skew that can occur through the FPGA device. This is critical, especially when the clock net is shared by multiple devices and routed through the FPGA. A similar configuration was used on the clock net (SCL) of the I<sup>2</sup>C communication bus.

#### 4.2.2.3 Power Connections

Unlike most other components, the FPGA requires three different supply voltages: 1.2 V for the core, 2.5 V for auxiliary features and 3.3 V for the I/O. These voltages required specific power-on conditions in order to properly power the Spartan device. The exact voltage specifications are described in the following section. For the schematics of the power connections, the most critical point was that each power pin had to be assigned at least one bypass capacitor. The sizing and placement of

Figure 4.1: DCM with Off-Chip Delay Feedback

these capacitors is discussed in greater detail in a later section of this thesis.

## 4.2.3 TPS Triple Supply

The TPS7500 Triple Supply was selected as an ideal component to supply the FPGA with the required voltage levels for operation. This integrated circuit uses two non-synchronous buck converters to supply up to 3 A on the 3.3 V and 1.2 V lines. In addition, it has an integrated low-dropout linear regulator for the 2.5 V supply. Each supply has an adjustable "soft start" that allows the desired voltages to be increased at a controlled rate during power-on. This feature is used to satisfy the power on requirements of the Spartan-3E series FPGAs. The specifications for these voltages can be found in [21] and the voltage ramp rates are summarized in Table 4.3.

In order to configure the device correctly, the following design considerations needed to be made when drawing the TPS7500 schematic (seen in Fig. B.1 of Appendix B). These included: sizing soft start capacitors, selecting appropriate sized

| Symbol              | Description                                           | Min | Max | Units     |

|---------------------|-------------------------------------------------------|-----|-----|-----------|

| V <sub>CCINTR</sub> | Ramp rate from GND to valid $V_{CCINT}$ supply level. | 0.2 | 50  | ms        |

| V <sub>CCAUXR</sub> | Ramp rate from GND to valid $V_{CCAUX}$ supply level. | 0.2 | 50  | ${ m ms}$ |

| $V_{CCO2R}$         | Ramp rate from GND to valid $V_{CCO}$ supply level.   | 0.2 | 50  | ${ m ms}$ |

Table 4.3: Spartan-3E Supply Voltage Ramp Rate[21]

components for the non-synchronous buck converters, selecting appropriate sized filtering capacitors and providing a reverse current path on the drain of the power transistors via Schottky diodes.

To suit the upgradable nature of the design, the supporting components were sized for a maximum current draw of 3 A. This is the maximum the TPS device can source. Even though the maximum current supplied from the USB controllers is limited to 500 mA, the cameras can handle external supplies capable of supplying greater currents for potential off-line application (such as additional testing and prototyping).

#### 4.2.3.1 Limiting Buck Converter Current

The two non-synchronous buck converters that supply voltage to the VCCO and VC-CINT lines of the FPGA are both capable for sourcing up to 3 A (internally limited) unless externally limited by sizing  $R_1$  and  $R_2$ , as seen in Fig. B.1 of Appendix B. Unlimited current allows the converters to operate in a continuous mode, preventing "ringing" from occurring in the junction of the PMOS transistors and inductors. For this reason,  $R_1$  and  $R_2$  were sized as to not limit current through these devices to any less than 3 A and at the same time, be capable of dissipating the maximum power. As power is a function of  $I^2$ R with I at 3 A, R must be reduced as much as possible to minimize power dissipation.  $R_1$  and  $R_2$  were sized at 330 m $\Omega$  according to suggested values in [15] resulting in a maximum power of 0.297 mW. Thus 1/2 W, 330 m $\Omega$  resistors were chosen for this application.

#### 4.2.3.2 Setting VCCO

The non-synchronous buck converts are designed to sustain a 1.22 V output with a unity feedback. In order to set the voltage output of one of the buck converters greater than 1.22 V, the feedback to the converter must be appropriately scaled down (i.e., through a voltage divider circuit) so that the resulting output voltage is regulated at a desired level. Since the camera design operates on 3.3 V I/O, as specified in both the Cypress FX2 device as well as the MT9T001 image sensor, a single VCCO of 3.3 V was required and was generated using Buck2. The feedback output voltage for Buck2 can be written as:

$$V_{OUT} = V_{FB} \left(\frac{R_6}{R_5} + 1\right) \tag{4.1}$$

Since  $V_{FB} = 1.22$  V and  $V_{OUT} = 3.3$  V then  $R_6/R_5 = 1.705$ . Based on recommendations from [15],  $R_6$  and  $R_5$  were chosen as 61.9 k $\Omega$  and 36.9 k $\Omega$  respectively.

#### 4.2.3.3 Sizing Soft Start Capacitors

One of the most substantial benefits of using the TPS7500 supply is the soft start capability of the device. This controls the voltage ramp rate of the output supplies by appropriately sizing soft start capacitors  $C_4$ ,  $C_5$  and  $C_6$  in Fig. B.1 of Appendix B. The voltage ramp rate is a complex function of many variables. It is recommended that the soft start capacitors are appropriately sized by using a test bench setup and monitoring the power-on conditions outlined in Table 4.3, adjusting the soft start capacitor values until the desired power on conditions are met. This design used recommended values supplied by [15] and [20] in the sizing of these capacitors, and the resulting voltage ramps were verified on the first hardware revision of the board.

## 4.2.4 Cypress FX2 USB Microcontroller

The schematics seen in B.3 for the Cypress FX2 microcontroller were essentially replicated from the Cypress CY3684/3674 EZ-USB Advanced Development Board. Slight modifications were made, such as connecting the reset pin directly to power through an RC circuit designed to delay the power on transient. As in the demo board, the analog power was shared with the digital power. The data bus pins for the slave FIFO were connected to the FPGA which was used to drive data to the device.

The FX2 required an external clock. For this, a 24 MHz crystal was supplied. This clock was internally divided to produce a 48 MHz clock for IFCLK (used to synchronize the incoming FIFO data) as well as provide an external system clock CLKOUT. The CLKOUT net was supplied directly to the FPGA and was internally referenced as USBCLK, which can be scaled using a DCM of the FPGA and sent to the MT9T device to control exposure time.

The FX2 was also connected to the FPGA in a configuration that allowed it to program the FPGA in serial slave mode. With this setup, FPGA code could be loaded to the device through the USB port, eliminating the need for an additional program memory device or external programming connection. This also allowed the USB device drivers to supply the latest FPGA code whenever the device was plugged in, ensuring that the FPGA was always loaded with the most recent code. This also ensures that all cameras in a system will operate with the same code, without the need to update each FPGA of each camera separately.

The final consideration for the FX2 schematics was the connection of a bypass capacitor to each power pin to ground. The sizing and placement of these capacitors is described in more detail in a section to follow. B.3 in Appendix B shows the final schematics for this device.

## 4.2.5 I<sup>2</sup>C Communication Bus

The I<sup>2</sup>C components were connected so that the data net (SDA) was shared between all I<sup>2</sup>C devices, as was done with the clock net (SCL). Special considerations had to be made to size the pull-up resistors on both the local side of the I<sup>2</sup>C bus as well as the external side of the I<sup>2</sup>C bus extender.