Avances en Energías Renovables y Medio Ambiente Vol. 10, 2006. Impreso en la Argentina. ISSN 0329-5184

# PRIMERAS EXPERIENCIAS DE DISEÑO, FABRICACIÓN Y CARACTERIZACIÓN DE DIODOS DE PASO PARA CELDAS SOLARES DE USO ESPACIAL\*

M. Altamirano<sup>1</sup>, C.A. Cadena<sup>1,3</sup>, M.G. Martínez Bogado<sup>2,3</sup>, S.E. Rodríguez<sup>2</sup>, M.J.L. Tamasi<sup>2,3</sup>

<sup>1</sup>Facultad de Ciencias Exactas - Universidad Nacional de Salta

<sup>2</sup>Grupo Energía Solar - Departamento de Física – Centro Atómico Constituyentes – CNEA

<sup>3</sup>Consejo Nacional de Investigaciones Científicas y Técnicas

Av. General Paz 1499 (1650) San Martín, Pcia. de Buenos Aires, Argentina. Tel. (011) 6772-7837

martinaltamirano@gmail.com, tamasi@tandar.cnea.gov.ar

**RESUMEN:** Se presentan los primeros desarrollos en la elaboración y caracterización eléctrica de diodos de paso de silicio para uso espacial. Se elaboraron diodos con dos tipos de juntura: n<sup>+</sup>p y n<sup>+</sup>pp<sup>+</sup>. Se detalla el proceso de fabricación de este dispositivo, que requiere el uso de técnicas similares a las empleadas en la elaboración de celdas fotovoltaicas: oxidación, difusión de dopantes, fotolitografía y deposición de contactos metálicos. Si bien ésta tecnología es bien conocida y se puede encontrar en los libros de texto, éstos dispositivos son los primeros que se fabrican íntegramente en el país. Se caracterizaron eléctricamente mediante la medición de la curva corriente-tensión (I-V) sin control de temperatura. Asimismo, para estudiar el funcionamiento del dispositivo, tanto desde el punto de vista eléctrico como electrónico, se presentan simulaciones teóricas con los programas PC1D5 y Simusol.

Palabras clave: diodos de paso, silicio, juntura p-n, usos espaciales

#### INTRODUCCIÓN120

El objetivo de este trabajo es el desarrollo tecnológico de diodos de paso para celdas solares de uso espacial con el fin de evaluar la factibilidad de reemplazar los adquiridos comercialmente por los fabricados en nuestro laboratorio. El desarrollo de esta tecnología y la fabricación de estos dispositivos en el país reduciría costos importantes en la fabricación del panel solar. Este trabajo se encuentra enmarcado dentro del convenio CNEA-CONAE para el desarrollo, integración y ensayo de paneles solares para misiones satelitales (Bolzi et al., 2005).

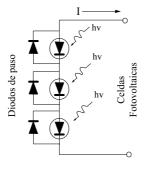

Un panel solar para aplicaciones espaciales, en general, está formado por celdas fotovoltaicas interconectadas en serie y en paralelo según el requerimiento de potencia del satélite. Dado que los módulos solares son la fuente principal de energía del satélite, cualquier inconveniente en ellos puede hacer que la misión fracase. Si una porción del panel entra en sombra puede provocar que las celdas inactivas funcionen con polaridad inversa, bloqueando el paso de corriente en el circuito y provocando que la celda sombreada disipe energía. Esta disipación de potencia puede conducir tanto a la ruptura de la juntura p-n en regiones localizadas de la celda, como a daños en el vidrio protector o en la soldadura de los interconectores.

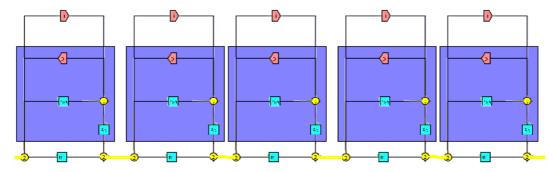

Cada una de las celdas que conforman los paneles solares poseen un diodo de paso conectado en paralelo a cada una de ellas (Figura 1). Este diodo permite el paso de la corriente si la celda entrara en sombra y limita la potencia a disipar evitando así los denominados puntos calientes.

Figura 1: Esquema de interconexión de celdas y diodos de paso en un panel de uso espacial.

Los principales efectos que influyen en el comportamiento del dispositivo como son: la resistencia serie (Rs) y la resistencia paralelo (Rp). La resistencia paralelo como producto de las fugas de corriente proporcionales a la tensión, tiene mayor

<sup>\*</sup> Trabajo financiado fundamentalmente por la CNEA y la CONAE. Cuenta también con aportes de la Agencia Nacional de Promoción Científica y Tecnología (PICT 2003 N° 10-14327).

influencia en la región de bajas tensiones cercanas al cero. Su origen puede deberse a pérdidas en los bordes del dispositivos, defectos en la juntura y a cortocircuitos en los contactos metálicos. La resistencia serie se debe fundamentalmente a la resistencia de contacto entre el metal y el semiconductor, a la resistencia ofrecida por el emisor y por los contactos metálicos. Teniendo en cuenta estos efectos, la ecuación I-V del diodo se puede escribir de la siguiente manera:

$$I = I_0 \left( \exp\left(\frac{q(V + IR_S)}{AkT}\right) - 1 \right) + \frac{V + IR_S}{R_P}$$

(1)

donde  $I_o$  es la corriente de saturación en inversa, q es la carga del electrón y A es el factor de idealidad del diodo, que puede variar entre 1 y 2.

#### SIMULACIONES NUMÉRICAS

Análisis de la curva I-V del diodo utilizando el programa PC1D5

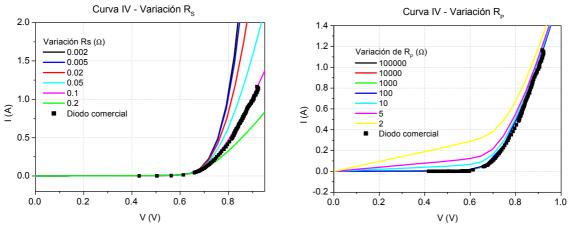

Se realizaron simulaciones del dispositivo usando el programa PC1D5 (Clugstone y Basore, 1997) variando los valores de Rs y Rp. Al variar otras características tales como: profundidad de juntura, recombinación superficial y resistividad de la base, no se observaron cambios significativos.

Los parámetros utilizados en estas simulaciones son:

Espesor de la oblea de silicio: 300µm

Área efectiva: 16mm<sup>2</sup>

Resistividad de la base: 1  $\Omega$ .cm

Tiempo de vida media de la base: 10 μs, longitud de difusión: 163μm

Emisor n<sup>+</sup>: concentración de dopaje de fósforo (P) superficial: 8 x 10<sup>19</sup> at/cm<sup>3</sup>

Profundidad de juntura: 0,4µm

Velocidad de recombinación superficial frontal: 1000 cm/s

En la Figura 2 se muestran las simulaciones obtenidas variando la Rs y se puede apreciar que al disminuir el valor de la misma, disminuyen las pérdidas de corriente que se ve reflejado en la región de tensiones altas. En la misma figura se muestra la curva del diodo comercial medida experimentalmente.

Las simulaciones realizadas variando la Rp se presentan también en la Figura 2. Como es de esperar al aumentar Rp hay menor pérdida de corriente a través del diodo.

Figura 2: Curvas I-V simuladas con variación de la Rs (izquierda) y Rp (derecha).

Simulación del circuito del diodo conectado a la celda con el programa SIMUSOL

Se utilizó el programa SIMUSOL (Saravia et al.2000) para mostrar el funcionamiento del diodo de paso en una cadena de cinco celdas interconectadas en serie. Si bien no es un estudio completo representa los primeros pasos, utilizando este programa, para la simulación del comportamiento en interconexión de celdas con diodos. Tampoco se consideró aún el acoplamiento eléctrico y térmico de las celdas (Gea et al, 2006) pues el objetivo principal fue modelar una cadena de celdas y evaluar el comportamiento del diodo de paso.

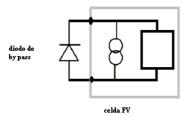

En la Figura 3 se observa el modelo de un circuito equivalente de una celda triple juntura InGaP/GaAs/Ge con un diodo de paso conectado en paralelo, la ecuación característica del diodo, y la curva I-V del mismo. Para el modelo de cada celda utilizado en el SIMUSOL se supuso un generador de fotocorriente, conectado a una "caja negra". Cabe aclarar que la celda, a los efectos del modelo, no se caracteriza por una ecuación sino por una tabla de valores I-V medidos experimentalmente.

Figura 3: Esquema de una celda triple juntura con diodo de paso de Si en paralelo.

Se plantea a modo de ejemplo el caso de una cadena de cinco celdas de triple juntura conectadas en serie con sus respectivos diodos en paralelo, tal como se observa en la Figura 4. En este caso, por simplicidad se tomaron todas las celdas idénticas repitiéndola cinco veces.

Figura 4: Modelo equivalente en SIMUSOL de una cadena de cinco celdas.

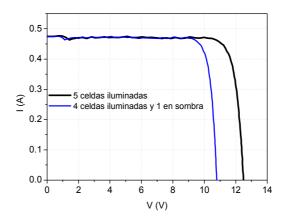

El programa para esta situación funciona de manera muy simple: se traza la curva I-V de la cadena en serie en condiciones normales de funcionamiento y paso siguiente se traza la curva simulando la existencia de una celda dañada o en oscuridad (en condiciones de circuito abierto), funcionando entonces el diodo como un *by-pass*. El resultado obtenido, se muestra en la Figura 5, donde se observa que para este último caso, existe una disminución en la tensión de la cadena pero no así en la corriente total.

Figura 5:Curva I-V de 5 celdas triple juntura conectadas en serie (negro) y las mismas celdas con una de ellas en sombra (azul).

### DISEÑO DE LOS DIODOS DE PASO

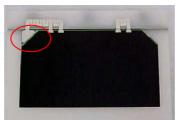

Los diodos de paso comerciales para uso espacial, utilizados hasta el momento, tienen una forma triangular y se ubican en una de las esquinas recortadas de la celda de triple juntura para optimizar el espacio, como se puede observar en la Figura 6.

Figura 6: Imagen de la celda de triple juntura con el diodo de paso integrado (circulo rojo).

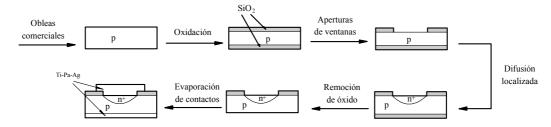

El proceso de elaboración de diodos de silicio es similar a la elaboración de dispositivos fotovoltaicos. El mismo involucra limpiezas, oxidación, difusión de la juntura y utilización de técnicas fotolitográficas para deposición de contactos. Se fabricaron diodos con dos tipos de junturas distintas: con difusión de fósforo en la cara frontal  $(n^+p)$  y con difusión de fósforo frontal y de aluminio en la cara posterior (tipo  $n^+pp^+$ ).

Como primer paso y para conocer el punto de partida con los procesos que se realizan en el laboratorio (Tamasi, 2003), se elaboraron diodos sin pasivación, es decir, sin máscara de óxido que define el área difundida. Esto se realizó mediante la difusión completa de una oblea y posterior corte de los diodos del tamaño adecuado.

Para un control geométrico preciso del área del emisor, o sea del área difundida, es necesario realizar técnicas de difusiones localizadas que uniformizan el tamaño de los dispositivos. Para ello se crear una máscara de SiO<sub>2</sub> sobre la oblea de Si por oxidación térmica. Esta máscara con el espesor adecuado (Ghandhi, 1983) permite difundir el fósforo sólo en aquellas regiones donde el óxido es removido.

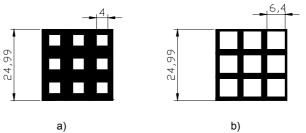

Para la apertura de ventanas en el  $SiO_2$ , así como para la confección de los contactos metálicos, se diseñaron y confeccionaron máscaras fotolitográficas, de tal manera que los diodos puedan cortarse en la dirección de los planos cristalográficos, simplemente, con un lápiz con punta de diamante. El emisor del diodo elaborado posee un área equivalente a la de los diodos comerciales (16 mm<sup>2</sup>).

El diseño de las máscaras se muestra en la Figura 7. El patrón se transfiere a un dibujo de mayor tamaño el cual puede ser fotografiado y así obtener los negativos fotográficos que son usados como máscaras durante el proceso de fotolitografía.

Figura 7: a) Esquema de la máscara para la difusión localizada, b) esquema de la máscara para la evaporación de los contactos de la cara frontal.

### ELABORACIÓN DE LOS DIODOS DE PASO

#### Diodos n<sup>+</sup>p

Para la elaboración de los diodos de paso se utilizaron obleas de silicio monocristalino comerciales dopadas con boro (tipo P) de resistividad 2 Ωcm y 300 μm de espesor. A las mismas se les realizó una limpieza que incluye pulido químico y limpiezas MOS, eliminando así posibles daños producidos en el proceso de corte y la presencia de suciedades orgánicas e inorgánicas que puedan encontrarse sobre la superficie.

Como se mencionó en la sección anterior, se elaboraron dos tipos de diodos: con o sin máscara de SiO<sub>2</sub> (con pasivación y sin pasivación respectivamente).

Para la elaboración de los diodos con pasivación se partió de obleas de Si comerciales las cuales fueron oxidadas en el horno a alta temperatura. La oxidación realizada en ambiente de oxígeno (pureza 99,998%) y nitrógeno a una temperatura de 1200°C durante 2 horas. Este tiempo se fijó de acuerdo a la bibliografía (Ghandhi, 1983), de tal manera que el SiO<sub>2</sub> actúe de barrera en las regiones deseadas en el proceso posterior de difusión de P.

Con este proceso se logró una capa de óxido de 1900 Å de espesor, el cual se determinó mediante la medición de la reflectancia espectral medida con una esfera integradora.

Para realizar la difusión localizada de fósforo, se abrió una ventana en la capa de óxido utilizando técnicas de fotolitografía con las mascaras antes mencionadas.

En los diodos sin pasivación no se realizó la etapa de oxidación y se difundió sobre toda la superficie frontal de la oblea. La difusión realizada en todos los casos fue la misma y se denomina difusión en un paso (Basore et al,1994) a 870°C.

Una vez completo el proceso de difusión se removió la capa posterior de SiO<sub>2</sub> y el óxido formado en la difusión. Se evaporaron los contactos de Ti-Pd-Ag en cámara de alto vacío, de forma completa en la cara posterior y localizados, usando técnicas de fotolitografía, en la cara frontal, para así evitar posibles cortocircuitos. Dichos contactos fueron engrosados electroquímicamente con plata; de esta manera, al soldarlos, disminuye la pérdida óhmica. En la Figura 8 se esquematiza el proceso completo de elaboración de los diodos con pasivación.

Figura 8: Esquema del proceso de elaboración de los diodos n<sup>+</sup>p.

Como último paso de la elaboración, los diodos son sometidos a un recocido a 400°C en ambiente de *forming gas* (4% de hidrógeno y 96% nitrógeno). Este proceso se realiza para mejorar el sinterizado de los metales y obtener el buen contacto óhmico entre el metal y el semiconductor.

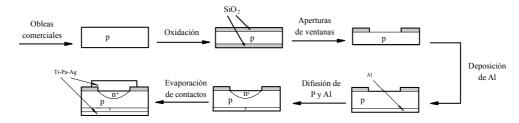

#### Diodos n<sup>+</sup>pp<sup>+</sup>

El proceso de elaboración de estos diodos difiere de la anterior únicamente en el etapa de dopado. Para la formación del emisor p<sup>+</sup> en la cara opuesta a la juntura n<sup>+</sup>p, se evaporó aluminio de las obleas previamente. Una vez en el horno se realizó la misma difusión en un paso detallada anteriormente. En la Figura 9 se muestra el esquema del proceso de elaboración de estos diodos con pasivación.

Figura 9: Esquema del proceso de elaboración de los diodos n<sup>+</sup>pp<sup>+</sup>.

#### CARACTERIZACIÓN ELÉCTRICA Y ANÁLISIS PRELIMINAR

Para poder implementar modificaciones para producir un dispositivo con las características deseadas, se tomó, como punto de partida, el proceso de difusión en un paso (Basore et al,1994). Dicha difusión es la utilizada actualmente en el laboratorio para la fabricación de celdas solares y sensores de radiación (Barrera et al, 2004). Este proceso forma junturas n<sup>+</sup>pp<sup>+</sup> y con obleas recortadas de un tamaño adecuado se elaboraron una serie de diodos sin pasivación.

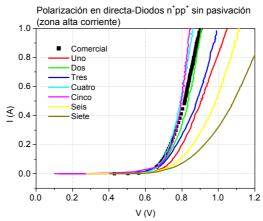

La caracterización eléctrica se realizó mediante la medición de la curva I-V de los diodos en polarización directa e inversa sin control de temperatura. Los resultados se compararon en todos los casos con un diodo de paso de Si para aplicaciones espaciales, adquirido comercialmente. En la Figura 10 se muestran las primeras curvas de los diodos fabricados y la del diodo comercial.

Figura 10: Curvas I-V (zona de alta corriente) de diodos sin pasivación y del diodo comercial.

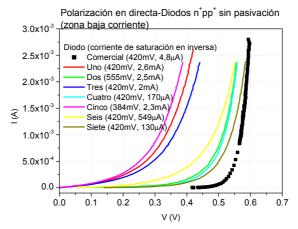

Se midieron además las curvas I-V en la zona de bajas corrientes para analizar el comportamiento en esta región. En la Figura 11 se muestran estas curvas junto con el valor de la corriente en inversa.

Figura 11: Curvas I-V (zona de baja corriente) de diodos sin pasivación y del diodo comercial.

Puede verse en la tabla del gráfico de la Figura 11 que los valores de corriente en inversa de los diodos elaborados están tres órdenes de magnitud por encima de los valores para el diodo comercial. La importancia de esta característica eléctrica radica en el hecho que si esta corriente es muy alta provoca una pérdida de potencia adicional. Existe, además, una dispersión en las curvas de los diodos fabricados debido principalmente a la falta de pasivación en los bordes de las obleas y a que los diodos no presentan las mismas áreas efectivas al ser cortados manualmente.

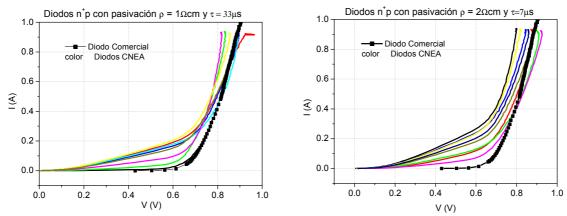

La caracterización eléctrica de los diodos con pasivación también se realizó mediante las mediciones de curvas I-V sin control de temperatura. En el segundo conjunto elaborado se definieron dos tipos de estructuras:  $n^+p$  y  $n^+pp^+$ . Los diodos  $n^+p$  fueron realizados con dos obleas de Si de distintas características: resistividad de  $1\Omega$ cm y de  $2\Omega$ cm, tiempo de vida media  $33\mu$ s y  $7\mu$ s, respectivamente. Los resultados obtenidos se muestran en la Figura 12.

Figura 12: Curvas I-V de diodos n<sup>+</sup>p con pasivación elaborados a partir de obleas de distintas características.

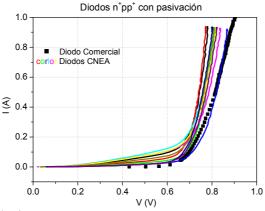

Los diodos n<sup>+</sup>pp<sup>+</sup> a partir de obleas de Si de 2 Ω.cm y las respectivas curvas I-V se presentan en la Figura 13.

Figura 13: Curvas I-V de diodos n<sup>+</sup>pp<sup>+</sup> con pasivación.

En la Tabla 1 se muestran los valores mínimos y máximos obtenidos de la corriente en inversa a 2,3V (tensión de operación) de los diodos con pasivación.

| Diodos    | Características de las obleas                         | Corriente medida a 2,3V |

|-----------|-------------------------------------------------------|-------------------------|

| $n^+p$    | $\rho = 1 \Omega \text{ cm} - \tau = 33 \mu \text{s}$ | 0,6-1,4 mA              |

| $n^+p$    | $\rho = 2 \Omega \text{ cm} - \tau = 7 \mu \text{s}$  | 4-6 mA                  |

| $n^+pp^+$ | $\rho = 2 \Omega \text{ cm} - \tau = 7 \mu \text{s}$  | 0,2-2 mA                |

Tabla 1: Intervalos de corriente de saturación en inversa de los diodos elaborados con pasivación.

En los casos con pasivación las curvas obtenidas resultaron menos dispersas que la de los dispositivos sin pasivación.. Además la corriente en inversa de estos diodos resultó mucho menor.

Analizando las pendientes de las curvas de las Figuras 12 y 13 para zonas de alta corriente (mayores a 0,3 A) se puede ver que la resistencia serie para los diodos  $n^+p$  con pasivación varía entre 0,2  $\Omega$  y 0,3  $\Omega$  y para los diodos  $n^+pp^+$  se mantiene cercana a 0,1  $\Omega$ , mientras que el diodo comercial tiene una Rs aproximada de 0,2  $\Omega$ .

A pesar de que las curvas son menos dispersas entre sí, aún existe una resistencia paralelo baja en todos los casos. En el caso del diodo comercial, la Rp es de aproximadamente  $2 \text{ k}\Omega$ , mientras que en los diodos elaborados es del orden de los  $10\Omega$ .

#### **CONCLUSIONES**

En estas primeras experiencias se evaluaron las características eléctricas de los diodos de paso para posteriormente ajustar los parámetros y cumplir así con los requisitos de calificación de dispositivos de uso espacial. Como se afirma en el análisis preliminar realizado a partir de los gráficos, los diodos elaborados aún poseen una resistencia paralelo que no se ajusta a los requerimientos. Para mejorar esta característica se deben realizar modificaciones en el proceso de fabricación de los mismos, en particular se utilizarán obleas más delgadas y dado que, en estos diodos la longitud de difusión es menor que el espesor del dispositivo, la utilización de obleas con una mayor vida media de portadores minoritarios permitiría reducir la Rs. Asimismo deberá evaluarse la disminución del área efectiva del emisor.

Para mejorar el alineamiento de las máscaras es necesario equipamiento especial que todavía no se dispone en el laboratorio, ya que este alineamiento permitiría mejorar efectos de borde.

Para disminuir la dispersión en las curvas de los diodos fabricados, será necesario mejorar la pasivación en los bordes de las obleas y contar con diodos de áreas efectivas iguales. Esto último no es posible por el momento dado que nuestro laboratorio no cuenta con una máquina de corte de obleas.

Si bien la tecnología de fabricación de diodos de silicio es muy bien conocida el objetivo final es el desarrollo tecnológico de estos diodos de paso en el país con el fin de evaluar la factibilidad de reemplazar los adquiridos comercialmente por los desarrollados en el laboratorio. Este trabajo presenta los primeros pasos en la investigación y el desarrollo de diodos de paso de uso espacial aprovechando la experiencia del Grupo Energía Solar de la CNEA en la elaboración de celdas solares de silicio.

## **AGRADECIMIENTOS**

Los autores agradecen a Cristián J. Bruno y a Javier Fernández Vázquez por la ayuda brindada en la medición e interpretación de resultados.

#### REFERENCIAS

- M. Barrera, C. G. Bolzi, D. Corvalán, M. G. Martínez Bogado, J Plá, M. J. L. Tamasi (2004). Últimos desarrollos en celdas solares de silicio en CNEA. Avances en Energías Renovables y Medio Ambiente, Vol. 8, pp. 4.19.

- P. Basore, M.J. Gee, M.E. Buck, W.K. Schubert y D.S. Ruby. (1994) Simplified High-Efficiency Silicon Cells. Solar Energy Materials and Solar Cells. 91.

- C.G. Bolzi, C.J. Bruno, P. Cabot, E. Carella, J.C. Durán, J. Fernández Vázquez, E.M. Godfrin, V. Goldbeck, M.G. Martínez Bogado, A. Moglioni, J. Plá, S.E. Rodríguez., M.J.L. Tamasi, M. Alurralde, F. Antonuccio, M. Barrera, J. Di Santo, A. Filevich, C.D. Franciulli, A. Iglesias, E. Mezzabolta, S.L. Nigro, I. Prario, M.C. Raffo Calderón, y A. Vertanessian. Desarrollo, fabricación y ensayo de paneles solares para uso espacial en la CNEA. V Congreso Regional de Ensayos no Destructivos y Estructurales, del 2 al 4 de noviembre de 2005, Ciudad de Neuquén.

- D. Clugstone y P. Basore. (1997) PC1D version 5:32-bit solar cell modeling on personal computers. Proceeding of the 26th IEEE Photovoltaic Specialist Conference, Anaheim, EE.UU.

- M. Gea, M. T. Montero, C. Cadena (2006), Simulación eléctrica y térmica de paneles fotovoltaicos, presentado para su publicación en Avances en Energías Renovables y Medio Ambiente, Vol. 10.

- S. Ghandhi (1983). VLSI Fabrication Principles. Silicon and Gallium Arsenide. 386-394. Wiley Interscience, New York.

- Saravia L. y Saravia D. (2000) "Simulación de sistemas solares térmicos con un programa de cálculo de circuitos eléctricos de libre disponibilidad". Avances en Energías Renovables, Vol. 4, pp. 8.17.

- M J. L. Tamasi (2003). Tesis de doctorado: Celdas Solares para Uso Espacial: Optimizacion de Procesos y Caracterización. Universidad Nacional de General San Martín, Comisión Nacional de Energía Atómica, Instituto de Tecnología "Prof. Jorge A. Sábato".

## ABSTRACT

This paper presents our early developments on the elaboration and electric characterization of silicon bypass diode for space uses. Two different types of junction diode were manufactured:  $n^+p$  and  $n^+pp^+$ . The elaboration's processes of those devices which requires similar techniques to those utilized in the manufacture of photovoltaic cells is detailed: oxidation, phosphorus diffusion, photolithography and metallic contact deposition.

Current-Voltage curves with no temperature control were measured and theoretical simulations using PC1D5 and Simusol programs were presented.

Keywords: bypass diode, silicon, p-n junction, space applications