Graduate Theses, Dissertations, and Problem Reports

2019

## Low-Power Reconfigurable Sensing Circuitry for the Internet-of-Things Paradigm

Alexander DiLello West Virginia University, adilello@mix.wvu.edu

Follow this and additional works at: https://researchrepository.wvu.edu/etd

Part of the Electrical and Electronics Commons

### **Recommended Citation**

DiLello, Alexander, "Low-Power Reconfigurable Sensing Circuitry for the Internet-of-Things Paradigm" (2019). Graduate Theses, Dissertations, and Problem Reports. 7386. https://researchrepository.wvu.edu/etd/7386

This Dissertation is protected by copyright and/or related rights. It has been brought to you by the The Research Repository @ WVU with permission from the rights-holder(s). You are free to use this Dissertation in any way that is permitted by the copyright and related rights legislation that applies to your use. For other uses you must obtain permission from the rights-holder(s) directly, unless additional rights are indicated by a Creative Commons license in the record and/ or on the work itself. This Dissertation has been accepted for inclusion in WVU Graduate Theses, Dissertations, and Problem Reports collection by an authorized administrator of The Research Repository @ WVU. For more information, please contact researchrepository@mail.wvu.edu.

# Low-Power Reconfigurable Sensing Circuitry for the Internet-of-Things Paradigm

### Alexander Todd DiLello

Dissertation submitted to the Benjamin M. Statler College of Engineering and Mineral Resources at West Virginia University in partial fulfillment of the requirements for the degree of

Doctor of Philosophy in Electrical Engineering

David W. Graham, Ph.D., Chair Roy S. Nutter, Jr., Ph.D. Daryl S. Reynolds, Ph.D. Jeremy Dawson, Ph.D. Edward M. Sabolsky, Ph.D.

Lane Department of Computer Science and Electrical Engineering

Morgantown, West Virginia 2019

Copyright 2019 Alexander Todd DiLello

### Abstract

Low-Power Reconfigurable Sensing Circuitry for the Internet-of-Things Paradigm

### Alexander Todd DiLello

With ubiquitous wireless communication via Wi-Fi and nascent 5th Generation mobile communications, more devices – both smart and traditionally "dumb" – will be interconnected than ever before. This burgeoning trend is referred to as the Internet-of-Things. These new sensing opportunities place a larger burden on the underlying circuitry that must operate on finite battery power and/or within energy-constrained environments. New developments of low-power reconfigurable analog sensing platforms like field-programmable analog arrays (FPAAs) present an attractive sensing solution by processing data in the analog domain while staying flexible in design. This work addresses some of the contemporary challenges of low-power wireless sensing via traditional application-specific sensing and with FPAAs. A large emphasis is placed on furthering the development of FPAAs by making them more accessible to designers without a strong integrated-circuit background – much like FPGAs have done for digital designers.

# Acknowledgments

This material is based upon the generous support by the National Science Foundation under Award No. CNS-1148815, Department of Energy's National Energy Technology Laboratory under Federal Grant DE-FE0012383, and West Virginia University's Provost Fellowship.

## Contents

| $\mathbf{A}$  | Abstract         |                                                                      |        |

|---------------|------------------|----------------------------------------------------------------------|--------|

| A             | ckno             | wledgments                                                           | iii    |

| $\mathbf{Li}$ | $\mathbf{st}$ of | Figures                                                              | vii    |

| 1             |                  | roduction                                                            | 1      |

|               | 1.1<br>1.2       | Power Consumption with a Battery Supply                              | 3<br>6 |

| 2             |                  | art Refractory Sensor Systems for Wireless Monitoring of Temperature |        |

|               |                  | Slagging Gasifiers                                                   | 7      |

|               | 2.1              | "Smart" Foundry Bricks                                               | 7      |

|               | 2.2              | Resistive Sensor                                                     | 8      |

|               | 2.3              | Resistive Sensing Circuit                                            | 11     |

|               | 2.4              | Circuit Implementation                                               | 13     |

|               |                  | 2.4.1 Voltage Regulator and Battery                                  | 13     |

|               | ~ ~              | 2.4.2 Brick Characterization and Circuit Components                  | 14     |

|               | 2.5              | Conclusion                                                           | 16     |

| 3             | Hig              | h-Side Switch                                                        | 20     |

|               | 3.1              | High-Side Switches                                                   | 20     |

|               | 3.2              | Power management and energy-harvesting systems                       | 22     |

|               | 3.3              | High-Side Switch                                                     | 24     |

|               | 3.4              | Circuit Implementation                                               | 27     |

|               | 3.5              | Results                                                              | 30     |

|               | 3.6              | Conclusion                                                           | 34     |

| 4             | Ten              | nperature Compensation of Floating-Gate Transistors in Field-Program | mable  |

|               | Ana              | alog Arrays                                                          | 36     |

|               | 4.1              | Floating-Gate Temperature Dependence                                 | 36     |

|               | 4.2              | Floating-Gate Devices                                                | 37     |

|               | 4.3              | FG Temperature Compensation                                          | 41     |

|               |                  | 4.3.1 System Architecture                                            | 41     |

|               |                  | 4.3.2 System Programming                                             | 42     |

|               | 4.4              | System Performance                                                   | 43     |

CONTENTS v

|   | 4.5  | Conclusion                                                                | 44    |

|---|------|---------------------------------------------------------------------------|-------|

| 5 | Floa | ating-Gate Device Introduction                                            | 49    |

|   | 5.1  | Floating-Gate Development and Background                                  | 49    |

|   | 5.2  | Floating-Gate Device Overview                                             | 51    |

|   | 5.3  | Floating-Gate Device Structure and Operation                              | 53    |

|   |      | 5.3.1 Floating-Gate Operation                                             | 54    |

|   | 5.4  | FG charge modification                                                    | 57    |

|   |      | 5.4.1 FG Tunneling and Electron Removal                                   | 57    |

|   |      | 5.4.2 Hot-Electron Injection and the Addition of Electrons                | 59    |

|   | 5.5  | Conclusion                                                                | 62    |

| 6 | Floa | ating-Gate Injection Programming                                          | 64    |

|   | 6.1  | Floating-Gate Injection                                                   | 64    |

|   | 6.2  | Pulsed Programming                                                        | 66    |

|   | 6.3  | Continuous-Time Programming                                               | 67    |

|   | 0.0  | 6.3.1 Programming Target Convergence Structure                            | 70    |

|   | 6.4  | $V_{sd}$ Voltage for Injection                                            | 73    |

|   | 0.1  | 6.4.1 Above-Ground Injection Voltage and Associated Programming Circuitry | 73    |

|   |      | Above-Ground FG Cell Operational Modes                                    | 77    |

|   |      | 6.4.2 Below-Ground Injection Voltage                                      | 77    |

|   |      | FG Selection and Isolation for Below-Ground Injection Programming         | 78    |

|   | 6.5  | Programming Accuracy                                                      | 80    |

|   | 6.6  | Conclusion                                                                | 85    |

|   | 0.0  | Conclusion                                                                | 06    |

| 7 |      | configurable Analog Preprocessing for Efficient Asynchronous Analog-      |       |

|   | to-I | Digital Conversion                                                        | 92    |

|   | 7.1  | Introduction                                                              | 92    |

|   | 7.2  | Asynchronous Quantization                                                 | 94    |

|   | 7.3  | System Overview                                                           | 96    |

|   |      | 7.3.1 Reconfigurable Analog Mixed-Signal Platform                         | 96    |

|   |      | 7.3.2 Asynchronous Data Converter Design                                  | 97    |

|   |      | Successive-Approximation Register                                         | 98    |

|   |      | Comparator                                                                | 99    |

|   |      |                                                                           | 101   |

|   | 7.4  |                                                                           | 103   |

|   |      | · · · · · · · · · · · · · · · · · · ·                                     | 103   |

|   |      | 1 0                                                                       | 105   |

|   | 7.5  | 00 0 1                                                                    | 107   |

|   |      |                                                                           | 109   |

|   |      |                                                                           | 110   |

|   |      |                                                                           | 111   |

|   |      | , O 1 ,                                                                   | 112   |

|   | 7.6  | 8                                                                         | 114   |

|   | 1.0  | Conclusions                                                               | · T 4 |

| CONTENTS | vi |

|----------|----|

|          |    |

| 8            | Reconfigurable Analog Mixed-Signal Processor8.1 Software Infrastructure8.2 RAMP Version 1.1 Enhancements8.3 Conclusion | 120               |

|--------------|------------------------------------------------------------------------------------------------------------------------|-------------------|

| 9            | Conclusions and Future Work 9.1 Future Work                                                                            | <b>124</b><br>126 |

| Re           | eferences                                                                                                              | 128               |

| $\mathbf{A}$ | Wheatstone Bridge Resistive Sensing Circuit                                                                            | 135               |

# List of Figures

| 2.1 | (a) Cross-sectional diagram of the smart brick furnace and (b) a photo of the proposed testing furnace with superimposed circles designating the proposed                       |    |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | smart brick positions.                                                                                                                                                          | Ö  |

| 2.2 | Experimental measurements of a thermistor characterization                                                                                                                      | 10 |

| 2.3 | Thermistor sensing circuit that utilizes two operational amplifiers and Wheatstone bridge                                                                                       | 12 |

| 2.4 | Six smart brick characterizations.                                                                                                                                              | 15 |

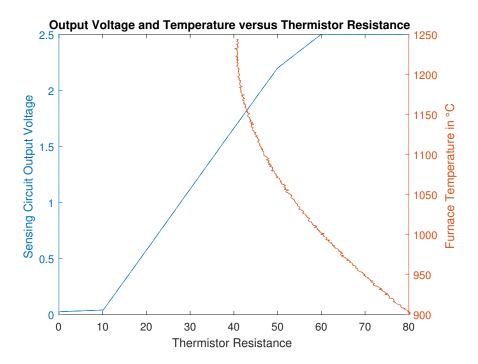

| 2.5 | Left y-axis shows the sensing circuit output versus thermistor resistance.<br>Right y-axis shows the hot-junction furnace temperature versus resistance.                        |    |

|     | The figure is used to map output voltage to temperature                                                                                                                         | 17 |

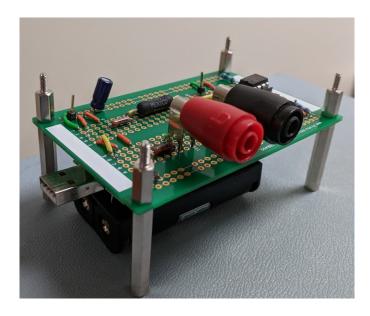

| 2.6 | Physical design of the sensing circuit consists of battery, wireless mote, and                                                                                                  |    |

|     | Wheatstone bridge circuit stack from bottom to top                                                                                                                              | 18 |

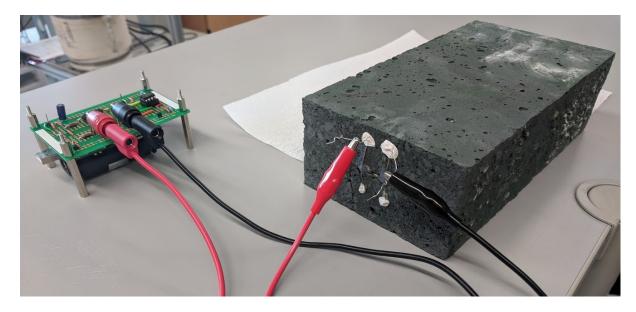

| 2.7 | The sensing circuit interfaced with a smart brick. This a staged picture to simply demonstrate how the interface connection would look like in a real                           |    |

|     | deployment.                                                                                                                                                                     | 18 |

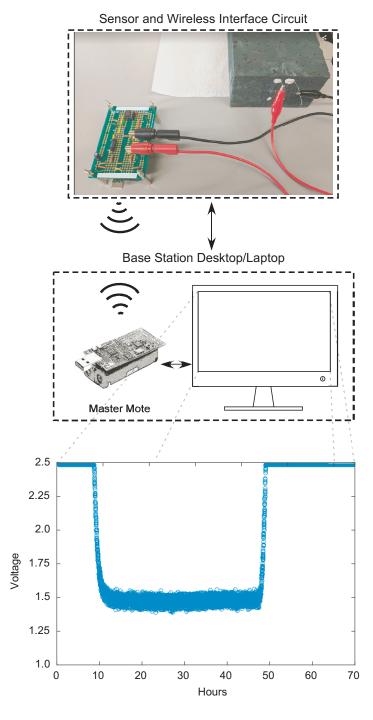

| 2.8 | Demonstration of the wireless sensing node and its fit within the smart brick sensing system                                                                                    | 19 |

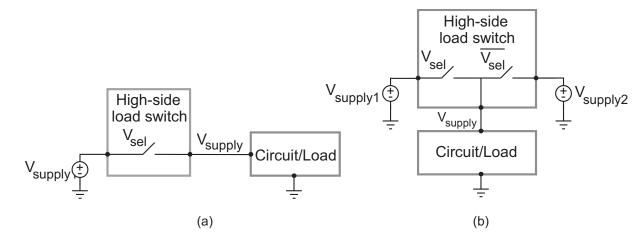

| 3.1 | (a) Block diagram of a conventional high-side load switch and (b) a multiplexing high-side load switch                                                                          | 21 |

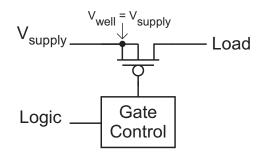

| 3.2 | Block diagram of a conventional high-side load switch                                                                                                                           | 26 |

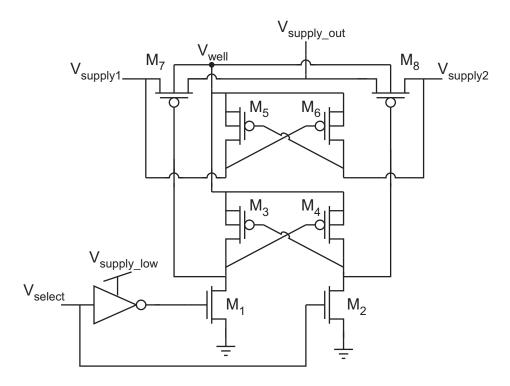

| 3.3 | Schematic of the multiplexing high-side load switch using adaptive well biasing.                                                                                                | 28 |

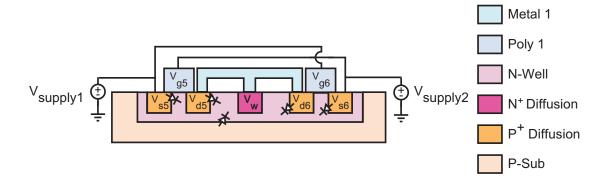

| 3.4 | Physical cross-section of the well-selection transistor pair with schematically overlaid parasitic pn-junctions                                                                 | 29 |

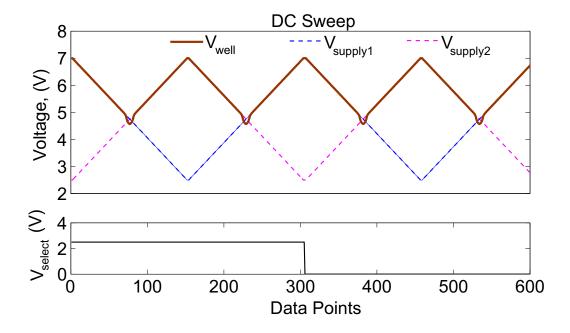

| 3.5 | DC measured results showing $V_{well}$ (brown) floats consistently for every com-                                                                                               |    |

|     | bination of $V_{select}$ (blue) $V_{supply1,2}$ (blue, pink) when $V_{supply1,2}$ are within a                                                                                  |    |

|     | 200mV of each other                                                                                                                                                             | 29 |

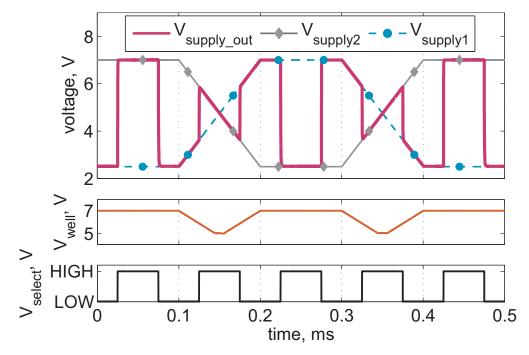

| 3.6 | Measured transient results showing the (top) input/output behaviour, (mid-                                                                                                      |    |

|     | dle) well potential, and (bottom) selection signal. Logic HIGH = $V_{supply\_low}$                                                                                              |    |

|     | and logic LOW = $0V$                                                                                                                                                            | 30 |

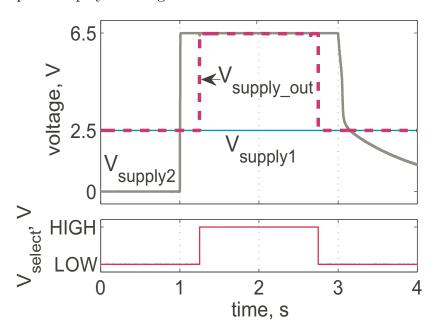

| 3.7 | Floating-gate programming demonstration using the high-side load switch and charge pump where $V_{supply1}$ , $V_{supply2}$ , and $V_{supply\_out}$ is shown in teal, gray, and |    |

|     | dashed red. respectively                                                                                                                                                        | 31 |

LIST OF FIGURES viii

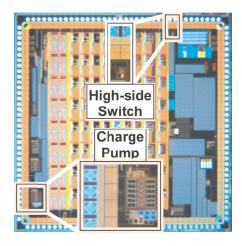

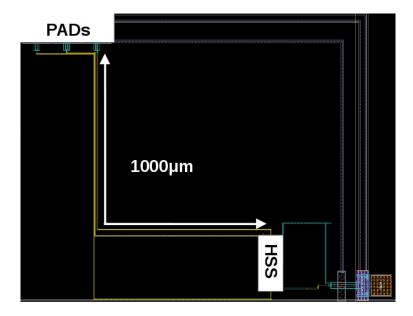

| 3.8        | Die photo of chip with insets showing the detail of the charge pump and high-side switch.                                                                                                                                                                                                                   |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

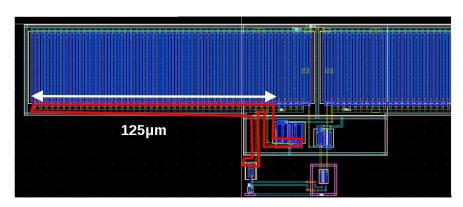

| 3.9        | Physical layout of a $2\Omega$ HSS. Outlined in red is a single connection or node,                                                                                                                                                                                                                         |

| 3.10       | which is $125\mu m$ long                                                                                                                                                                                                                                                                                    |

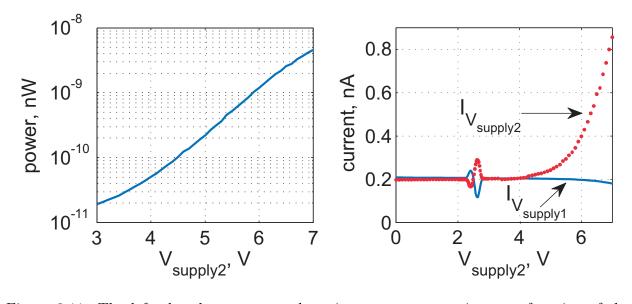

| 3.11       | resistance                                                                                                                                                                                                                                                                                                  |

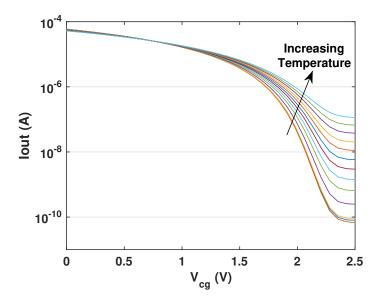

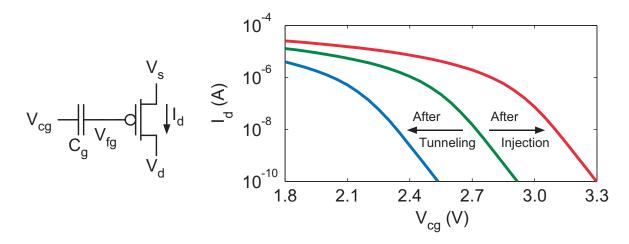

| 4.1        | Temperature dependence of an FG transistor. The plateaued currents for $V_{cg} > 2.25V$ are artifacts of many junction connections to a single global connection where the current reading was taken. As a consequence, their collective leakage current becomes non-negligible. The current in a single FG |

| 4.9        | transistor continues below these values                                                                                                                                                                                                                                                                     |

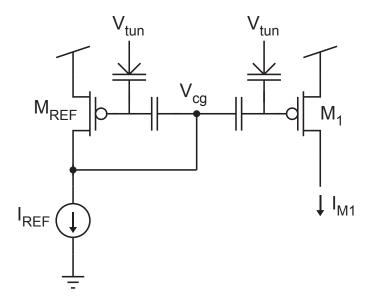

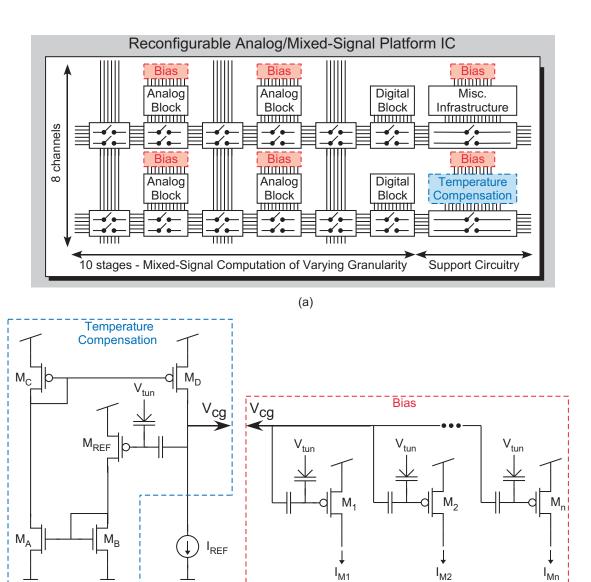

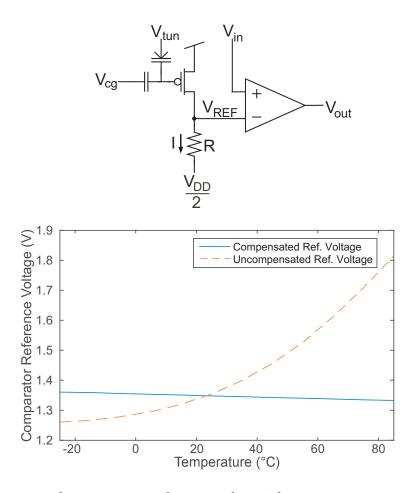

| 4.2<br>4.3 | Floating-gate current mirror configuration                                                                                                                                                                                                                                                                  |

| 4.0        | houses the FG temperature compensation structure. (b) Floating-gate temperature compensation structure showing connection to global $V_{cg}$ . Currents                                                                                                                                                     |

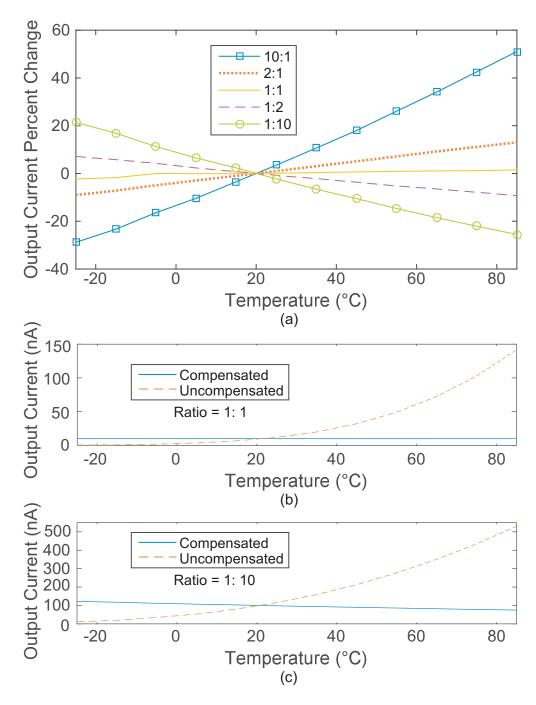

| 4.4        | source to an nFET current mirror before connecting to the CAB circuits (a) Percent change in output current of an FG with temperature compensation normalized to room temperature. (b) and (c) show the effects of compensation                                                                             |

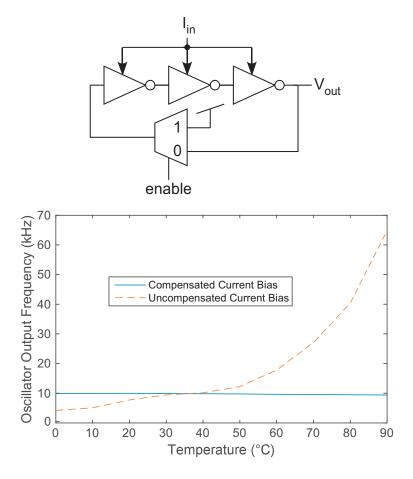

| 4.5        | compared to an uncompensated case for a ratio of 1:1 and 1:10 respectively. Ring oscillator frequency output with respect to temperature for a compensated and uncompensated FG current bias                                                                                                                |

| 4.6        | Programmed comparator reference value with respect to temperature for a compensated and uncompensated FG current bias                                                                                                                                                                                       |

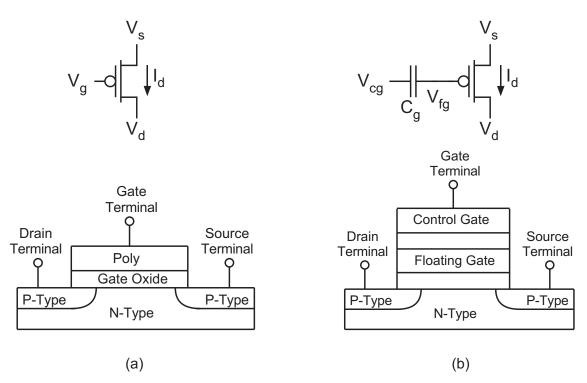

| 5.1        | Schematic representation and physical cross-section of (a) a pFET transistor and (b) a FG transistor, respectively                                                                                                                                                                                          |

| 5.2        | Floating-gate transistors allow for programmable threshold shifts from the perspective of the control gate. Injection programming adds electrons to the                                                                                                                                                     |

| - 0        | floating-gate, while tunneling removes electrons from the floating-gate                                                                                                                                                                                                                                     |

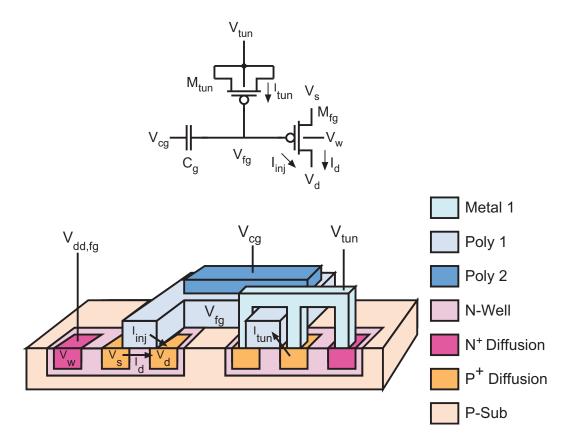

| 5.3        | Physical cross-sectional layout of a FC transistor                                                                                                                                                                                                                                                          |

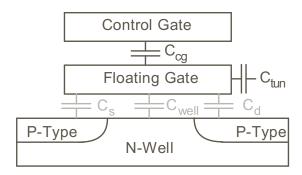

| 5.4        | Physical cross-sectional layout of a FG transistor showing all capacitors coupled to the FG including parasitics (in gray color)                                                                                                                                                                            |

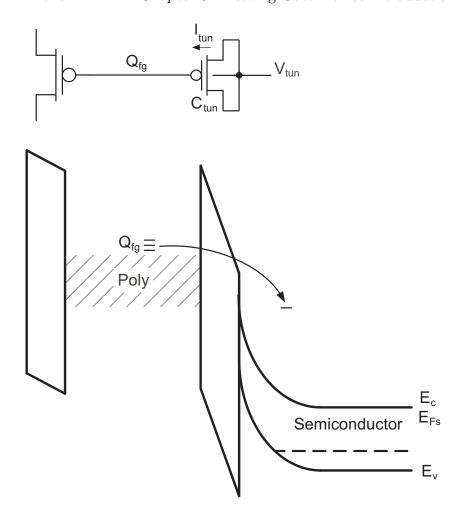

| 5.5        | Qualitative demonstration of Fowler-Nordheim tunneling in the FG band di-                                                                                                                                                                                                                                   |

|            | agram. The control gate has been omitted in the schematic for clarity                                                                                                                                                                                                                                       |

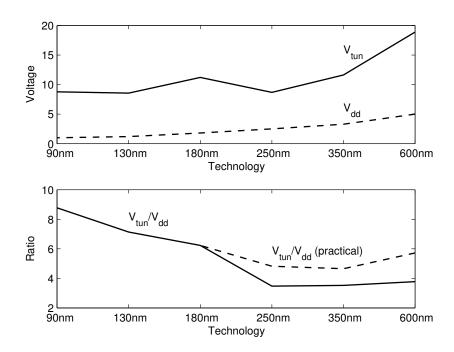

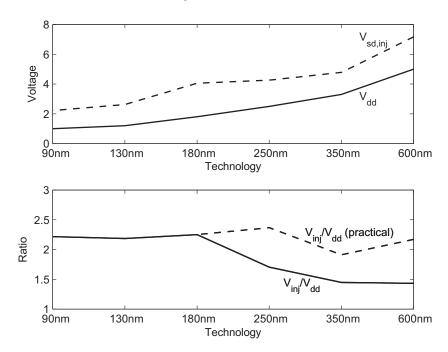

| 5.6        | Comparison of the required $V_{tun}$ voltage for scaling CMOS technologies. Top plot shows that the $V_{dd}$ has scaled for the technologies, but $V_{tun}$ plateaus at 250nm due to FGs needing to be realized in less leaky I/O devices. Bottom                                                           |

|            | plot shows the ratio of $V_{tun}$ to $V_{dd}$ . Above 250nm, the ratio is relatively constant. 250nm and below, the ratio increases because $V_{dd}$ continues to scale                                                                                                                                     |

|            | as $V_{tun}$ stays relatively constant [1]                                                                                                                                                                                                                                                                  |

LIST OF FIGURES ix

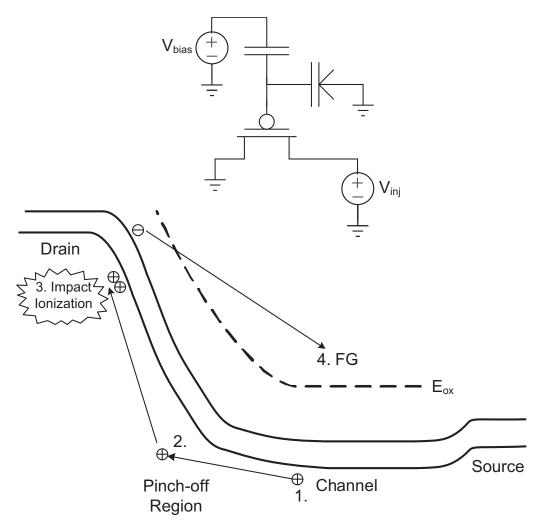

| 5.7 | Demonstration of hot electron injection in the FG band diagram. The band diagram is not to scale.                                                                                                                                                                                                                                                                                                                                                                                                                                           | 60       |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 5.8 | Comparison of the required $V_{inj}$ voltage for scaling CMOS technologies. Top plot shows that $V_{dd}$ and $V_{inj}$ scale similarly over the downsizing of technologies. Bottom plot shows the ratio of $V_{inj}$ to $V_{dd}$ . In practice, the supply $V_{dd}$ should be kept lower than standard $V_{dd}$ to prevent unwanted HEI. Taking this into consideration, the ratio stays around 2 over all technologies [2]                                                                                                                 | 61       |

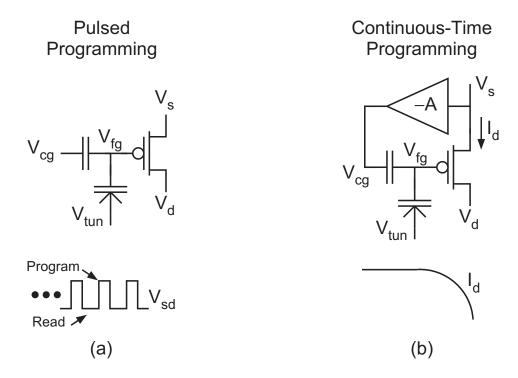

| 6.1 | (a) Pulsed programming sequentially cycles program/read modes until desired programming target is achieved. (b) Continuous programming employs                                                                                                                                                                                                                                                                                                                                                                                              | a=       |

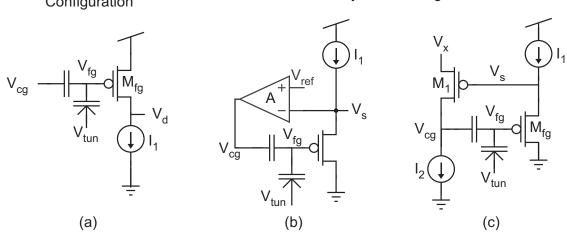

| 6.2 | negative feedback to converge upon programming target                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 65       |

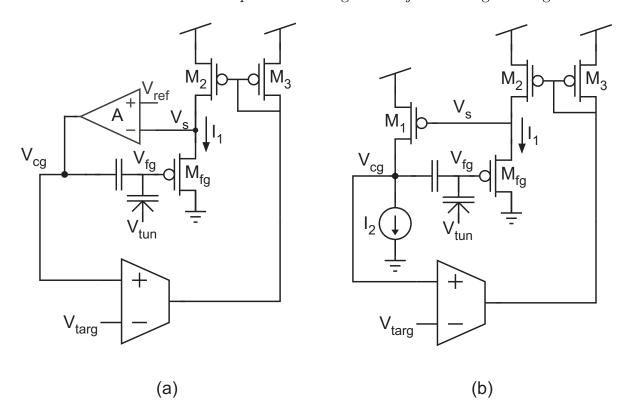

| 6.3 | feedback through $V_x$ and $I_2$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 68<br>70 |

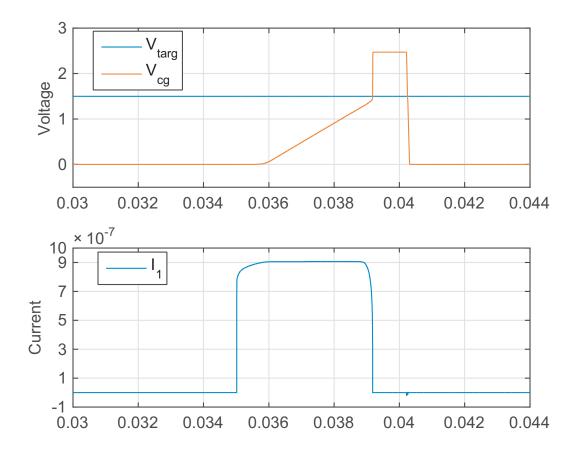

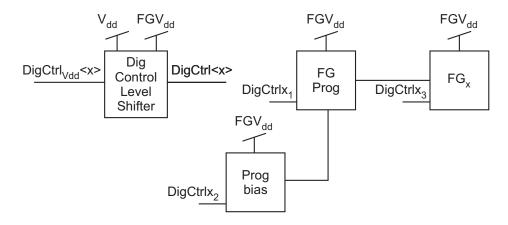

| 6.4 | Transient simulation of the injection process utilizing the continuous-time linear injection programmer with target converging circuitry of Fig. 6.3(b). The plots demonstrate that during injection, FG drain current $I_1$ is saturated to an appropriate current conducive to injecting electrons. In the above case $I_1 = 900$ nA. Once $V_{cg}$ reaches $V_{targ}$ , FG drain current $I_1$ drops precipitously to end the injection programming process.                                                                             | 70       |

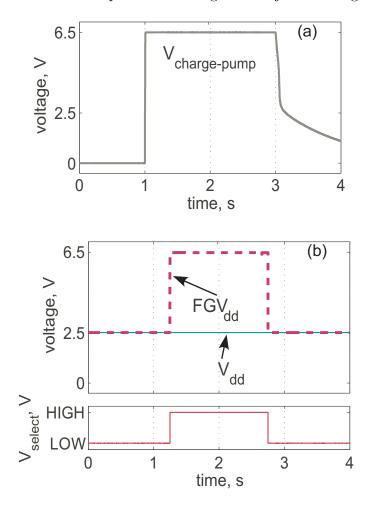

| 6.5 | Functionality of a supply-voltage selecting circuit. (a) Typical charge-pump signal used for programming FGs. The ramp-up time is on the order of microseconds and the discharge time is on the order of milliseconds to seconds. (b) Shows the functionality of a voltage supply selecting circuit. The dashed maroon signal $FGV_{dd}$ selects and outputs higher voltages when programming (i.e. charge-pump is enabled). While run-mode, it is outputting the nominal supply voltage $V_{dd}$ regardless of $V_{charge-pump}$ 's state. | 75       |

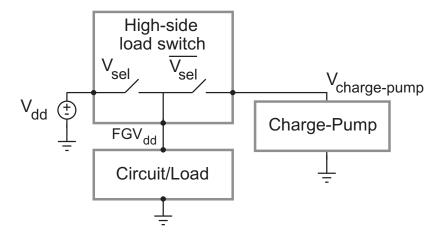

| 6.6 | High-side switch block diagram. This circuit is capable of choosing one of two supplies by a signal control signal. It's design is unique in that it can select a supply voltage larger than its nominal supply voltage without a secondary                                                                                                                                                                                                                                                                                                 | 76       |

| 6.7 | charge-pump                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 76<br>76 |

|     | side ioud switten und then relation among caen outer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 10       |

LIST OF FIGURES x

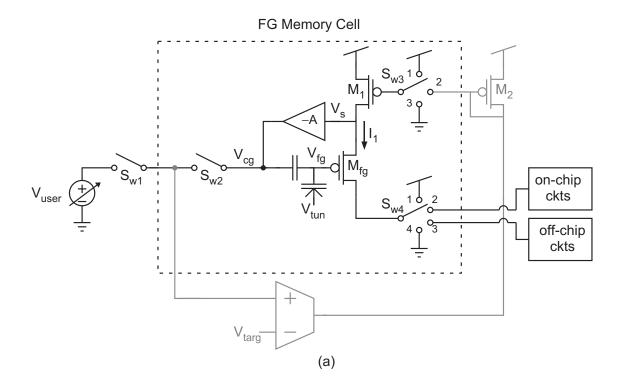

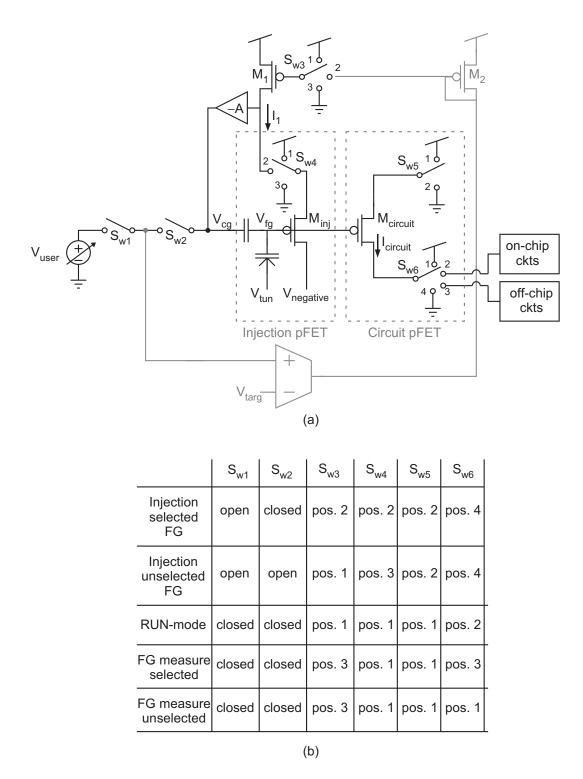

| 6.8  | Above-ground FG memory cell various operational modes and their respective connections. In (b) the first two rows refer to programming modes in which the selected FG is connected to the programmer, while all other FGs of the array are disconnected. RUN-mode refers to a configuration in which programmed FGs are connected to internal circuits. FG measure selected/unselected refers                                                                             |          |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 6.9  | to a configuration in which a single FG from the array is connected off-chip. Below-ground programming FG circuit configurations for injection and circuit modes (i.e. RUN-mode and FG measure). Both memory cells allow for FG selection/deselection in an arrayed FG configuration such that only the desired FG is programmed. Both configurations allow for circuit-mode operations                                                                                   | 87<br>88 |

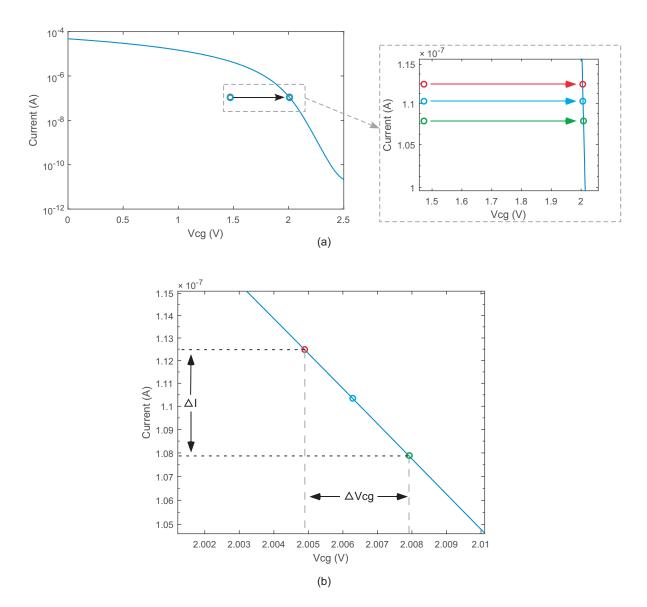

| 6.10 | (a) Programming experiments are mapped to a reference IV-curve to allow for one-to-one comparisons among different programming experiments. (b) Once the $n$ number of trails have been mapped – in the above case 3 –, the data can be projected onto the x-axis and y-axis statistically calculate the accuracy of                                                                                                                                                      | 00       |

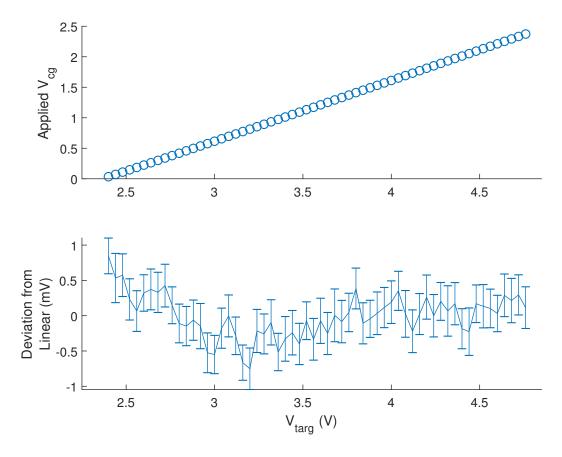

| 6.11 | to $V_{targ}$ voltages in linear steps. After programming to each $V_{targ}$ , the control voltage is modulated until the desired current is measured — in this case $10nA$ . The continuous-time programmer operates in a closed-loop configuration and forces the linearization of programming. The bottom plot shows the deviation of $V_{targ}$ from the linear regression line and the candlesticks shows the standard deviation for the 100 programming experiments | 90       |

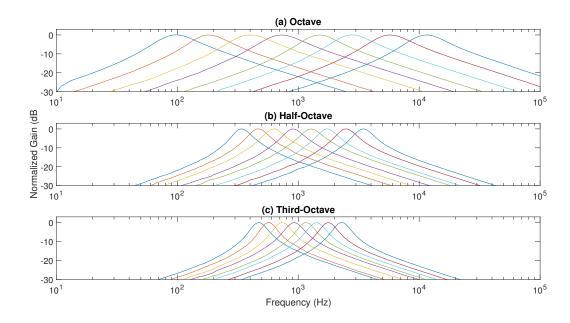

| 0.12 | Programmed C4 bandpass filters at full, half, and quarter octaves                                                                                                                                                                                                                                                                                                                                                                                                         | 91       |

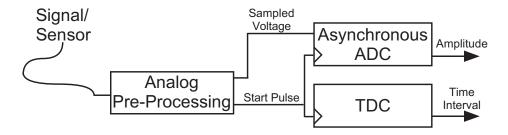

| 7.1  | Asynchronous analog-to-digital conversion system. A reconfigurable analog front-end reduces information to only the relevant data points and also triggers the subsequent blocks, which produce digital words for the corresponding voltages and time intervals                                                                                                                                                                                                           | 93       |

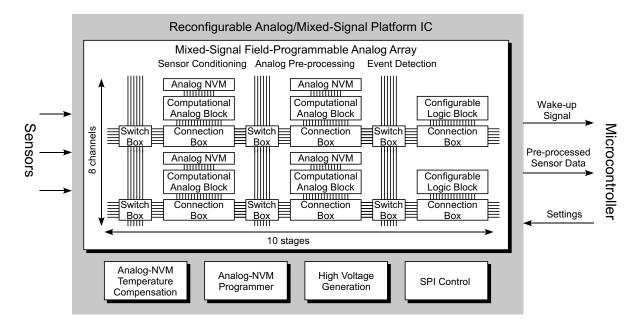

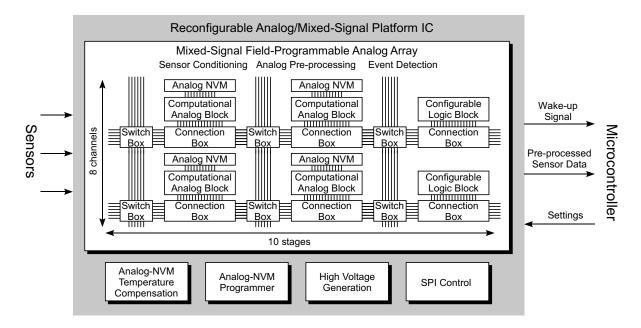

| 7.2  | Architecture of the reconfigurable analog/mixed-signal platform (RAMP) integrated circuit                                                                                                                                                                                                                                                                                                                                                                                 | 97       |

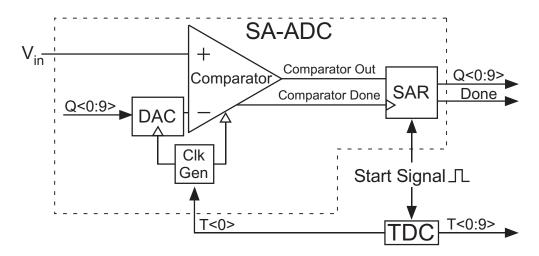

| 7.3  | System diagram of the successive-approximation ADC (SA-ADC)/time-to-digital converter (TDC). A trigger from the RAMP analog preprocessing stage acts as the 'Start Signal' to initiate conversion and record the time                                                                                                                                                                                                                                                     | 98       |

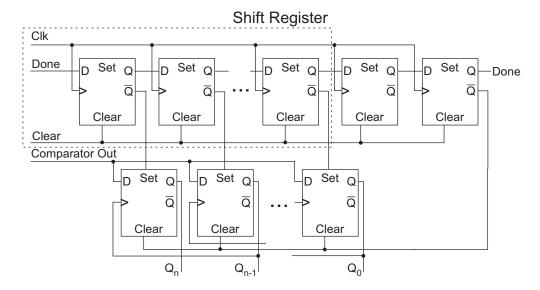

| 7.4  | A schematic of the successive approximation register. The boxed area acts as a shift register. The lower set of D flip-flops is where the bits are actually                                                                                                                                                                                                                                                                                                               |          |

| 7 5  | applied to the rest of the system and stored appropriately                                                                                                                                                                                                                                                                                                                                                                                                                | 99       |

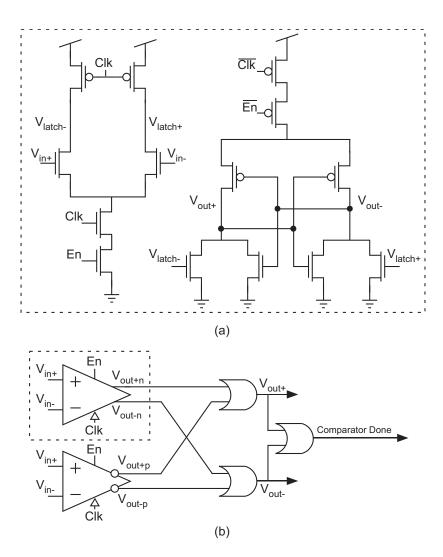

| 7.5  | (a) Comparator schematic of the nFET-based comparator. A complementary pFET-based comparator is also used in parallel. (b) Complete comparator schematic showing both the nFET-based (dashed box) and pFET-based comparators operating together. The MSB selects which version to use to                                                                                                                                                                                  |          |

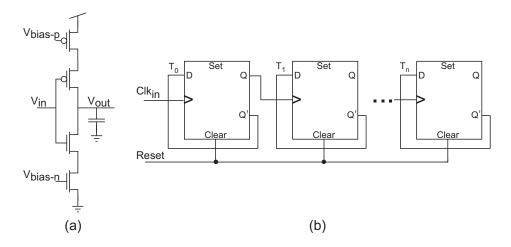

| 7.6  | maximize the input range of the complete comparator circuit                                                                                                                                                                                                                                                                                                                                                                                                               | 100      |

|      | which ensures that it begins in the same state after every reset                                                                                                                                                                                                                                                                                                                                                                                                          | 102      |

LIST OF FIGURES xi

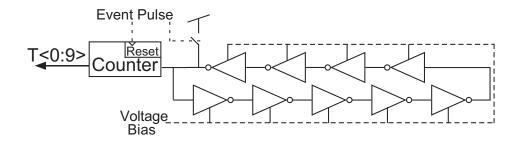

| 7.7  | (a) A simple delay unit using a current-starved inverter. The delay is proportional to the size of the capacitor and inversely proportional to the current flowing through the inverter. (b) A simple binary counter. The D flip-flops                                                                                              |     |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | are sequentially linked and output successive binary numbers                                                                                                                                                                                                                                                                        | 102 |

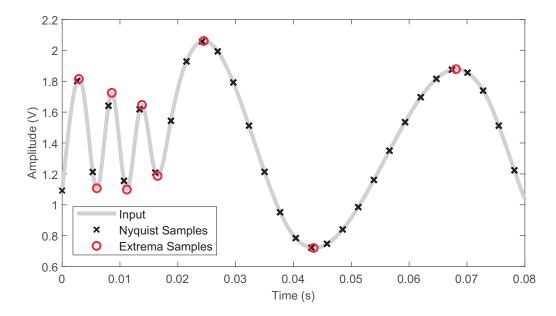

| 7.8  | Comparison of constant-rate Nyquist sampling versus an adaptive-sampling                                                                                                                                                                                                                                                            |     |

|      | method using extrema sampling.                                                                                                                                                                                                                                                                                                      | 104 |

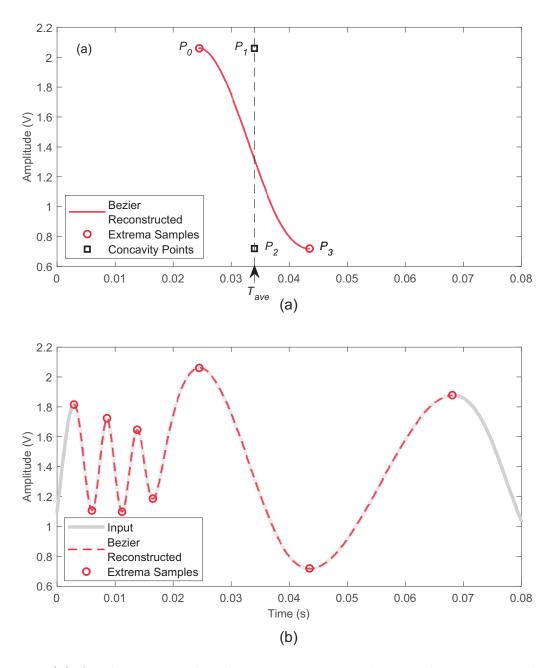

| 7.9  | (a) A Bézier interpolated segment constructed via endpoints $P_0$ and $P_3$ with concavity points $P_1$ and $P_2$ defining the directional path. $T_{ave}$ is the center point between endpoints $P_0$ and $P_3$ . (b) A continuous piecewise Bézier reconstruction that was generated from local maxima/minima and overlaid on the |     |

|      | input signal                                                                                                                                                                                                                                                                                                                        | 106 |

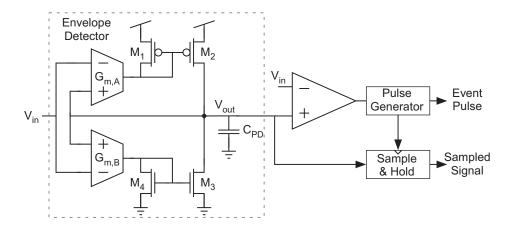

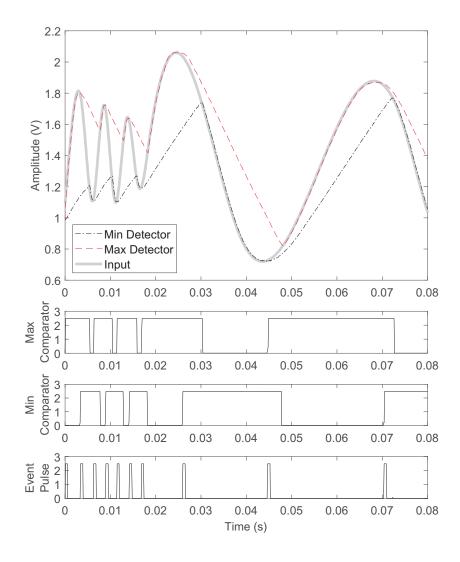

| 7.10 | The maxima detector circuit, which makes up one half of the analog front-<br>end synthesized in the RAMP system. The minima detector circuit is the                                                                                                                                                                                 |     |

|      | symmetric equivalent                                                                                                                                                                                                                                                                                                                | 107 |

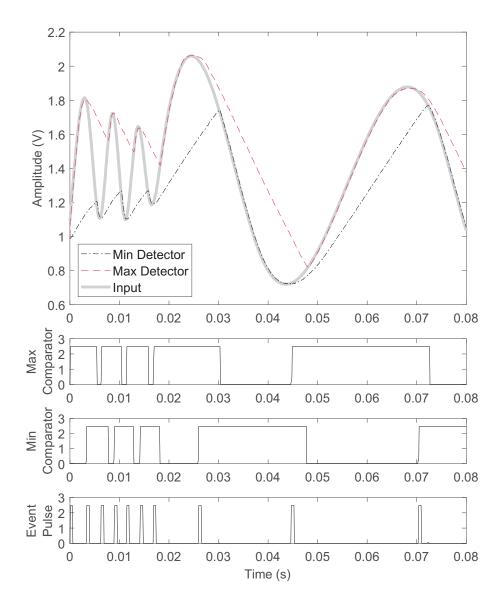

| 7.11 | v 1                                                                                                                                                                                                                                                                                                                                 |     |

|      | agrams indicate when an event (local maximum/minimum) has been detected.                                                                                                                                                                                                                                                            | 108 |

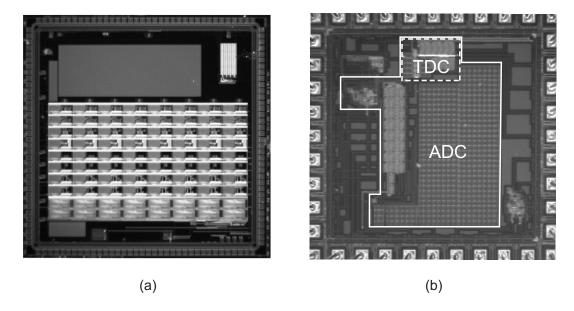

| 7.12 | (a) Die photograph of the reconfigurable analog/mixed-signal platform (RAMP)                                                                                                                                                                                                                                                        | 100 |

|      | fabricated in a 0.35 $\mu$ m standard CMOS process. (b) Die photograph of the                                                                                                                                                                                                                                                       | 109 |

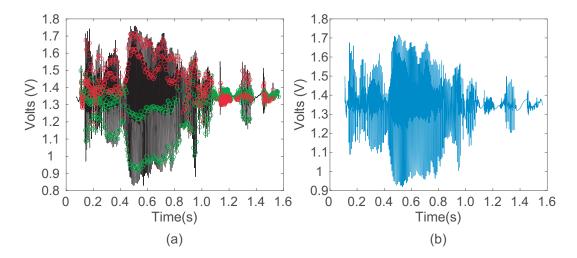

| 7 12 | asynchronous ADC/TDC fabricated in a 0.5 $\mu$ m standard CMOS process. Results of a vocal signal extrema capture and quantization                                                                                                                                                                                                  | 111 |

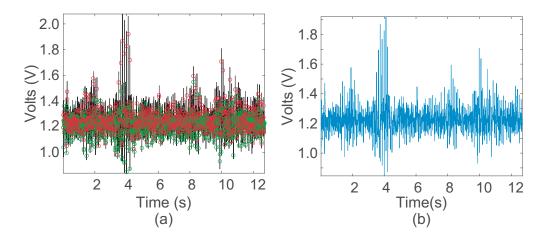

|      | Results of an EMG extrema capture and quantization                                                                                                                                                                                                                                                                                  | 111 |

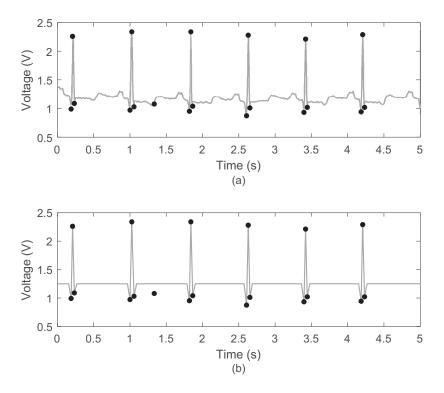

|      | Results of an electrocardiogram (ECG) extrema capture and quantization                                                                                                                                                                                                                                                              | 113 |

| 8.1  | Architecture of the reconfigurable analog/mixed-signal platform (RAMP) in-                                                                                                                                                                                                                                                          | 110 |

| 0.0  | tegrated circuit.                                                                                                                                                                                                                                                                                                                   | 116 |

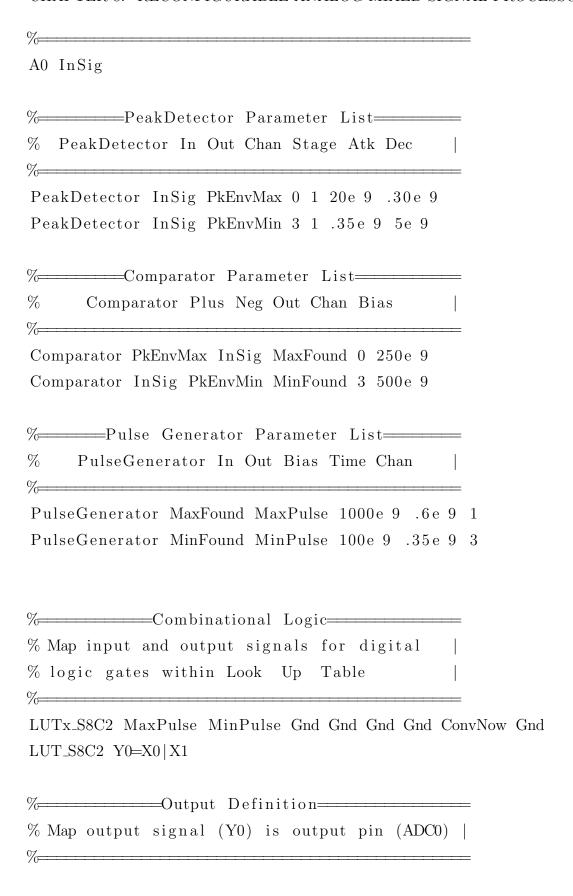

| 8.2  | The maxima and minima locator circuits find local extrema by comparing<br>the output of an envelope detector with the input signal. Each output signal                                                                                                                                                                              |     |

|      | shown corresponds to an output of a synthesized RAMP component (e.g.                                                                                                                                                                                                                                                                |     |

|      | pulse generator) that flows into another component or the final output                                                                                                                                                                                                                                                              | 119 |

| A.1  | Thermistor sensing circuit that utilizes two operational amplifiers and Wheat-<br>stone bridge. This designs is also capable of operating on a single supply rail                                                                                                                                                                   |     |

|      | like a battery source.                                                                                                                                                                                                                                                                                                              | 136 |

## Chapter 1

## Introduction

Wireless communication is becoming more ubiquitous with the deployment of Wi-Fi and nascent 5th Generation mobile communications. Furthermore, the bandwidth capacity has never been larger. This bounty of wireless communication has created an opportunity to connect together "dumb" devices – that is devices that were not traditionally networked and communicating with other devices – and make them "smart." This burgeoning trend is referred to as the Internet of Things (IoT) and is most visibly manifested to the common consumer in smart-home technology (e.g. thermostats, speakers, refrigerators) and smart-car technology.

In connecting many devices, there is an exchange of information stemming from the devices' sensors or their remote control of actuators. In some application spaces like the smart-home realm, there is the accessibility of a constant power source to accomplish this type of computing. But for other applications areas that exist in energy-constrained environments like agricultural sensing, the power consumption of the device is a large component in what determines its viability. Energy-constrained environments rely on a battery of finite energy. For these remote sensing applications, there is a need for energy-conscious designs to complement the developments made in wireless communication.

The objective of this work is to addresses the sensing circuitry challenges for the Internet of Things paradigm. It will advocate for a general-purpose, low-power, reconfigurable analog circuitry solution. Beyond the immediate benefits for the aforementioned sensing applications, developments in this field could have large impacts on integrated analog design because of the possibility of integrated analog designs done post-fabrication. Longer-term implications for this work would be a contribution to the democratization of analog inte-

grated circuit design akin to what FPGAs have done to integrated digital design. Further background and context is expanded upon below.

The conventional development of low-power sensing circuity has come from two different sources — a digital solution and an analog solution. The former has reduced power consumption by downscaling its feature sizes which have allowed its voltage supply rail to shrink down to 0.75V in a nascent 7nm process [3]. Furthermore, the power savings have been compounded with supply voltage reduction because it's characterized by a quadratic relationship in  $P = CV^2f$ . However, downscaling has not been following Moore's law within the past five years and it is showing diminishing returns due to semiconductor processing complications at sub 100nm feature sizes. For example, from 2006-2011, Intel had been following a schedule for downscaling the process about every two years (i.e. "tick-tock" development cycle) from 65nm to 22nm for their popular desktop CPUs. However, from 2011 to early 2019 (at the time of this writing), there has only been one downscale from 22nm to 14nm process. While there are optimizations in design to save power, the supply rail is not likely to drop as precipitously as it did from 5V to 0.75V in the next decade.

Low-power sensing in the analog domain has also benefited from downscaling, but the most dominant component of power-reduction has come from keeping computation in its original domain to save power. It's natural to try to keep most of the sensing in the analog realm as long as possible because the world that is being sensed is inherently analog. At some point in the communication chain, the analog values need to be converted to their digital equivalency for a microprocessor. However, being the conversion process is power-hungry, there are opportunities for power savings by employing analog front-ends to give discretion on what data to convert. An example application for this analog-digital interface to be applied is speech sensing. One power-savings opportunity would be to convert only speech data but not silence and non-speech audio. This could be accomplished with an analog front-end speech detector that listens for speech events while the digital circuitry stays in a low-power sleep mode when speech is not occurring. When speech is detected, the digital portions can then perform the digital conversion and transmission.

Like the speech detection example, the most power savings can be achieved by minimizing the use of a general-purpose microprocessor and offloading a portion of the microprocessor computation to the analog domain. The traditional method of accomplishing this is choosing an application-specific integrated circuit (ASIC) once the application space has been determined. ASICs focus on one specific task and do it very efficiently. However, if at any point during the design phase that the priorities change or the sensing fundamentally changes (e.g. changing a resistive-type temperature sensor switching a voltage-based sensor), the ASIC may not be able to accommodate the change. For battery-powered sensing in the IoT realm, there is a need for efficient sensing like that of ASICs, but there lacks a solution in design flexibility like that of field-programmable gate arrays (FPGAs) in the digital realm.

FPGAs provide application-specific integrated design, as well as flexibility in its reporgrammability. In the past, there have not been many platforms that have this ability to reconfigure integrated analog circuity. However, recent developments of field-programmable analog arrays (FPAAs) has brought this closer to a reality [4, 5, 6, 7]. FPAAs provide reconfigurability of integrated analog components (active and passive) at an ultra-low power consumption (typical applications in low 10's of  $\mu$ W) [8] – a great option to be used as analog front-ends for IoT wireless sensing applications. Furthermore, if the wireless aspect of these potential sensing devices is leveraged, the FPAAs can be reconfigured in the field.

FPAAs fulfill this need for ultra low power sensing for wireless devices. Its reconfigurability and low-power operation can be attributed to large sets of floating-gate FG transistors. For analog applications, FGs are used as programmable current sources for a variety of different circuit applications. With all the benefits, FGs do not come without their challenges. Currently, the low-power operation of FGs has an exponential relationship with temperature change, which becomes more of a challenge on an FG-dense FPAA platform. Similar issues arise in creating repeatable and accurate programming of FGs within an array of FGs. For both temperature and programming, reducing overhead and obviating external components equipment becomes a goal for an FPAA platform to succeed as an in-the-field circuit solution for wireless sensing. In the rest of this work, I set out to address these issues and contribute to improving wireless sensing for energy-constrained applications.

## 1.1 Power Consumption with a Battery Supply

Throughout this work, "low-power" is frequently listed as a design goal in battery-operated circuitry, and it would remiss if it was not given a contextual definition. "Low-power" in this work refers to circuitry that utilizes sub-threshold-level current biases which are largely below  $1\mu$ A currents. In battery-powered sensing applications, a net sub- $100\mu$ A current draw is a good rule-of-thumb benchmark for low-power circuits; however, this is highly dependent upon the complexity of circuits being used and application-space.

This work focuses on the sensing circuitry aspect of the wireless sensing nodes and does not focus on design improvements of the wireless microcontroller units (MCUs). However, MCUs can be the largest component of the power budget when not in a lower-power sleep-state mode. For example, current wireless COTS MCUs Particle Xenon and TelosB motes can consume up to 20mA and 24.8mA, respectively — not including any current draw from notification LEDs — with the RF transceiver active and the microprocessor at full capabilities [9, 10]. But, both boast sleep-states (i.e. transcievers off and microprocessor in a low-power, inhibited stated) with respective power consumptions on the order of  $\mu$ A draw (unmeasured by Particle at the time of writing) and  $6.1\mu$ A for the TelosB platform. Therefore, it's advantageous for a paradigm change from how microcontrollers are traditionally employed to conserve a finite battery supply.

The paradigm change methodology is to (1) keep the wireless microcontroller in a sleep-state for as long as possible and (2) offload computation to an always-on, low-power front-end. The motivation is that most, if not, all computation can be done at a lower power consumption by the front-end circuitry than by an active wireless MCU. The MCU can be woken-up for certain digital computations and information transmissions. The amount of time the MCU stays in sleep-state is ultimately dictated on a per-application basis.

The front-end circuitry can be fulfilled by employing ASICs or by the aforementioned FPAA. It's useful to put into context the theoretical battery life for both circuits in an application example like thermistor temperature sensing application. The following example is for a hypothetical agricultural application for in-the-field frost warning system. Let's assume both types of sensing circuits leverage the same MCU and its sleep state time; this negates any advantage with respect to the choice of microcontroller. A thermistor's output of resistance is converted to voltage when a current is dropped across the sensor like that of a Wheatstone bridge circuit — See Figure 2.3 and Appendix A. Since there are millivolt changes (i.e. relatively small) at DC-like frequencies, instrumentation amplifiers like the Microchip MCP6N16 are a good candidate for small-signal changes, and the MCP6N16, in particular, can operate on a single supply voltage under 5V.

The MCP6N16 draws a quiescent current of 1.1mA, while a sensing circuit of Figure 2.3 can be completely biased at less than 500nA. When accounting for additional overheads of the FPAA, the net current draw for FPAA synthesized circuit like that of Figure 2.3 would most conservatively be  $5\mu$ A. Furthermore, accounting for the resistive network power consumption, we can arbitrarily design for branch current of  $50\mu$ A total when utilizing a Panasonic ERT-

500nA

State: 59 Sec/Min  $10\mu A$

$\mu Proc.$  $\mu Proc.$ ASIC Average Battery Battery Operational Current w/ Current w/ Size(mAh) Efficiency Current Current Days Radio Off Radio On Active 1.15 mA1.8 mA24.5 mA8.63 mAState: 1 4000 80% 360 Sec/Min Sleep

Table 1.1: Operational lifetime using the ASIC front-end and on a single 4000mAh battery.

Table 1.2: Operational lifetime using the FPAA front-end and on a single 4000mAh battery.

$10.3\mu A$

$10\mu A$

|                               | FPAA<br>Current   | μProc. Current w/ Radio Off | μProc. Current w/ Radio On | Average<br>Current  | Battery<br>Size(mAh) | Battery<br>Efficiency | Operational Days |

|-------------------------------|-------------------|-----------------------------|----------------------------|---------------------|----------------------|-----------------------|------------------|

| Active State: 1 Sec/Min       | $55\mu\mathrm{A}$ | 1.8mA                       | 24.5mA                     | 7.53mA              | 4000                 | 80%                   | 409              |

| Sleep<br>State: 59<br>Sec/Min | 500nA             | $10\mu\mathrm{A}$           | $10\mu\mathrm{A}$          | $10.5\mu\mathrm{A}$ |                      |                       |                  |

J1VV154H  $220k\Omega$  thermistor. We can then compute the total ideal operational time if a battery's Ampere Hour rating is known. The tables 1.1 and 1.2 show the differences in operational lifetime using the ASIC and FPAA circuits on a single 4000mAh battery.

These calculations were based on a couple of assumptions. First, the MCUs will toggle the supply to the resistive network for the ASIC and the FPAA to sample the voltage divider. This reduces the parasitic current draw from the resistive network. The second assumption was that the ASIC and FPAA contain a comparator that would pulse HIGH if the temperature met some temperature threshold that was representative of a frost warning (while ignoring the dew point for this demonstrative example). This HIGH pulse would initiate the MCU to transmit a warning message. An additional assumption was this condition would occur 1/4 time of the year, which is represented by the metrics of the third column. The rest of the year would operate in the second column state with the radio off. The FPAA-based circuit would net 49 additional operational days compared to the ASIC circuit.

The 49 additional operational days can be attributed to an order of magnitude less current draw compared to ASIC front-end. Ultimately, there could have been a more extensive separation between the two designs if there was not a parasitic resistive network at the front-end and it was allowed to run 100% of the time. Chapter 7 demonstrates application examples where the MCU is asynchronously woken up. The result is a net magnitude of current difference from traditional periodic methods that can have an even larger effect on battery life compared to the demonstrative example of this chapter.

### 1.2 Outline of Work

The remainder of this document is devoted to elaborating on the various topics that have been previously enumerated in this introduction. Chapter 2 exhibits a complete wireless sensing system from its application, design, and deployment. In Chapter 3, I describe a high-side load switch used for FG programming that could also be employed for energy-harvesting circuits. Following in Chapter 4, I present an FG temperature compensation scheme for FPAAs. Chapter 5 gives a floating-gate transistor overview and analysis including their operation and programming which will be indispensable for the following chapters. Chapter 6 describes an FG below-ground programming array presented as a lower overhead alternative to many traditional works that utilize above-ground programming. The penultimate chapter exhibits a complete analog front-end for use with an ADC along with its use in a diverse set of end-use applications. The final chapter will serve as my conclusion and remarks on future work.

## Chapter 2

# Smart Refractory Sensor Systems for Wireless Monitoring of Temperature in Slagging Gasifiers

This chapter establishes the motivational basis for this dissertation work. A complete wireless sensor network is introduced to demonstrate the various components and their functional relationships. Furthermore, the end-use application of temperature sensing is a common sensing mode for IoT. The work completed in this chapter illustrates some of the hindrances of developing application-specific circuity which ultimately becomes the motivation for reconfigurable circuitry. This work was funded by the Department of Energy's National Energy Technology Laboratory Grant no. DE-FE0012383.

## 2.1 "Smart" Foundry Bricks

The premise for this Department of Energy (DOE) project was to develop "smart bricks" for a coal gasifier furnace to monitor the internal furnace conditions. The internal furnace environment experiences temperatures up to 1450°C and pressure up to 1000 psi for a duration over months. These extreme conditions make it a barrier to monitor internal furnace conditions which makes it difficult to determine it's operation. Currently, the furnace is treated like a black box where it is operated until the structural integrity is compromised such that it is unsafe to operate. The structure is then completely dismantled and rebuilt which is a lengthy expensive process.

However, if conditions within the furnace could be monitored, this information could be fed-back to operators (computers or human) so that they could modulate operational settings to moderate the internal conditions. The scope of the project would be to place a number of these "smart bricks" throughout the whole furnace structure to create a three-dimensional model for it's state of health. Presently, a single compromised brick is what ultimately leads to the catastrophic failure of the whole furnace. The three-dimensional model allows operators to find "hot spots" — harsh conditions in the furnace that could indicate impending brick failure at that particular point — and moderate furnace operation accordingly.

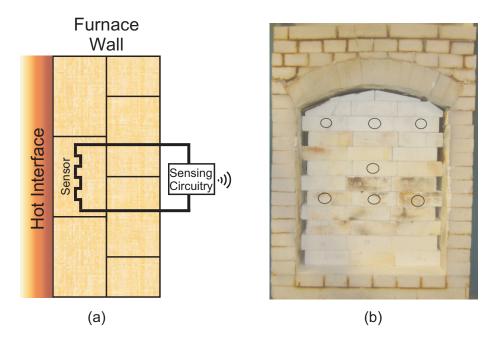

The "smart bricks" compose of the same refractory material that make-up the construction of the furnace, but have a lab-designed sensors embedded in them at the time of the brick casting. The terminals of the sensor exit the brick from the opposing side that will be exposed to the internal furnace. The sensor can then be interfaced with electronics to sense the internal conditions. The sensors that were developed by mechanical and chemical engineering team, and used to sense temperature, stress/strain and the internal furnace liner health. A cross-section of the furnace wall with a smart brick is shown in Fig. 2.1a. Fig. 2.1b shows the proposed testing furnace with the tentative sensor positions. The critical temperatures to be sensed by the circuit should be  $1100^{\circ} - 1400^{\circ}$ C as defined by the project proposal.

The sensing circuitry will be wireless and will run off battery power because there will be a number of sensors that could potentially be set in hard-to-access places on the furnace. The the test setup of Fig. 2.1b is for demonstration of the concept, but one can imagine the wireless sensing nodes encompassing the whole furnace. All the measured data at the sensor is transmitted to a centralized base-station node that listens for the data. The received data can then be processed and reviewed by an operator in real time.

### 2.2 Resistive Sensor

The two modes of temperature sensing that were explored in this project were voltage and resistance. The focus of this section is to examine the resistive sensors and its associated electronics. While the project explored both modes, the resistive sensors ultimately became the project's preferred avenue for temperature sensing.

A thermistor was chosen as the resistive temperature sensor and was designed by the

Figure 2.1: (a) Cross-sectional diagram of the smart brick furnace and (b) a photo of the proposed testing furnace with superimposed circles designating the proposed smart brick positions.

material sciences group. A thermistor is a resistor whose resistance is a function of temperature. There are two different types of thermistors: negative temperature coefficient (NTC) and positive temperature coefficient (PTC). An NTC thermistor's resistance decreases with an increase temperature, while the PTC resistance has the opposite behavior with an increase in resistance. The thermistors for this project are of NTC type due to their chemical composition.

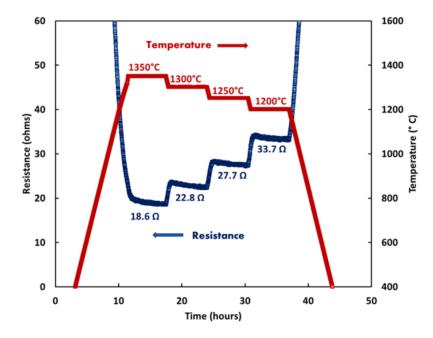

An example thermistor used in this project is pictured in Fig. 2.2. The figure is a characterization plot of the measured thermistor resistance versus the temperature that the sensor experiences in the furnace. This characterization experiment is function of time since the furnace instantaneously heat-up or cool-down to the target temperature. Additionally the sensor is embedded in the furnace brick since this is how the sensor will be deployed in actual application. The first ten hours of the experiment has the furnace heating up to its highest temperature of 1350°C; this is shown as the red line utilizing the right y-axis. Within that time frame, we see the measured resistance (in blue utilizing the left y-axis) conversely decreasing in resistance during the same time period. This confirms the sensor is an NTC thermistor. The experiment holds the temperature of the furnace for a few hours before plateauing at lower successive temperatures. This is shown from 10 hours to 40 hours

Figure 2.2: Experimental measurements of a thermistor characterization.

during the experiment, followed by a ramping down of temperature.

Designing a circuit for the thermistor in Fig. 2.2, we must account for the range of resistances the thermistor can take on while balancing sensitivity of the sensing circuit. The critical temperatures we want to be able to sense are temperatures above 1150°C. However, the range of resistances that correspond to the desired temperatures must be set within reasonable range to be useful. Using Fig. 2.2 as an example, the sensing electronics could be configured to sense a resistance between 15 $\Omega$  and 115 $\Omega$ . However, referring back to Fig. 2.2, if the temperature changed from 1200°C to 1300°C, and consequently the thermistor resistance would change from 33.7 $\Omega$  to 22.8 $\Omega$ , the sensing circuitry's output would only change about 10%. This example demonstrates that for the desired temperature range, there is relatively little change (only about 10%) in the output. On the other hand, every fabricated sensor will have mismatch among their resistance readings at the same corresponding temperature. As a result, the design must accommodate these 10-15% tolerances in their respective resistances due to non-idealities in the fabrication process.

### 2.3 Resistive Sensing Circuit

As described in the introductory section, the sensing circuitry needs to be battery-powered. Therefore, it needs to be energy efficient so that the batteries do not need to be replaced often – at least on the scale of months. The specific battery circumstances of this design will be three AA batteries as this supply will be shared with more than just the sensing circuitry. This constraint is set by the wireless microcontroller that will transmit the data and will be described in a following section. Furthermore, battery operation also means the circuitry needs to work on a single supply voltage.

Since the constraints are known and the solution needs to be low-power, the number of active components should be minimized. Furthermore, looking back at Fig. 2.2, we will need the circuitry capable of sensing a very small resistance whose change over the desired temperature range is in tens of Ohms. Measuring a resistance of this magnitude by means of Ohm's law (i.e.  $V = I \times R$ ) will require either a robust voltage or current relative to the demands of low-power sensing. Since this design is operating off of a battery supply, we are limited to a supply voltage of 2.5V – this voltage is dictated by the microcontroller [11]. This supply voltage constraint means that the current will need to be in the milliampere range given the sensor change is in tens of Ohms resistance.0

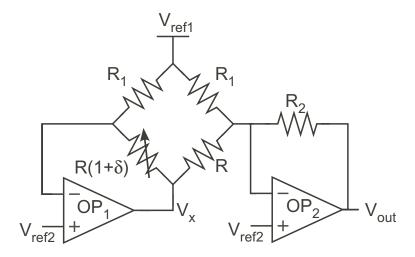

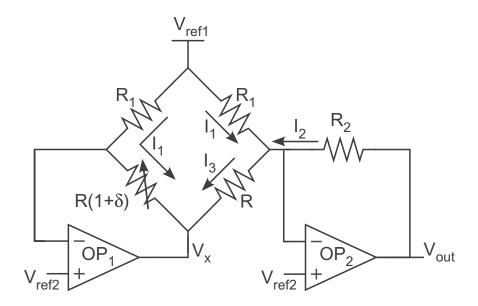

Given that the overall constraints are known, we employed a resistive sensing circuit pictured in Fig. 2.3 [12], [13]. This design utilizes a traditional Wheatstone bridge circuit and only two operational amplifiers (op-amps). In its essence, this circuit senses a change in resistance, and in response, outputs a corresponding voltage. This output voltage can then measured by the wireless mote's analog-to-digital converter (ADC). The ADC's conversion represents this data as a codeword that can transmitted back to the base-station mote.

This design has a number of advantages for battery-powered sensing. The first is that only two op-amps are being used as opposed to an instrumentation amplifier, which in their most conventional forms, utilize three op-amps. The second is that this design can be easily designed for at the board level and integrated level. Third, this circuit can operate from a single supply rail if the operational amplifiers are chosen/designed correctly.

The qualitative operation can be understood and help in the analysis of the output voltage expression. Ignoring the second op-amp  $(OP_2)$  circuit for the time being leaves the Wheatstone bridge and op-amp one  $(OP_1)$ .  $R_1$  and R of the Wheatstone bridge are static resistors, while  $R(1 + \delta)$  is the thermistor. The thermistor is placed in a negative feedback

Figure 2.3: Thermistor sensing circuit that utilizes two operational amplifiers and Wheat-stone bridge.

configuration of  $OP_1$ . Ignoring the right branch of the Wheatstone bridge simply yields a voltage divider down from  $V_{ref1}$ . This configuration permits a current to flow down from  $V_{ref1}$  to  $V_x$ , and the negative feedback configuration will attempt to maintain a consistent voltage drop across the thermistor such that its inverting input is the same value as its non-inverting input  $V_{ref2}$ . Stated another way,  $OP_1$  will modulate  $V_x$  such that the same current is always flowing through the left branch of the Wheatstone bridge.  $OP_1$  will only module  $V_x$  in response to a changing  $R(1 + \delta)$  resistance, which in our application will be when furnace temperature changes.

This leaves the right branch of the Wheatstone bridge and the inverting configuration of  $OP_2$ . The right branch of the Wheatstone bridge is simply a voltage divider with static resistances  $R_1$  and R. When the thermistor changes, and consequently  $V_x$ , the current through the right branch will change. Simply looking at the right branch and ignoring the  $OP_2$  inverting amplifier, the net effect is that the voltage division seen at the node of  $R_1$  and R will be  $V_{ref2}$  when  $\delta \neq 0$ . This voltage can be leveraged to produce an linearized output voltage with the help of  $OP_2$ 's feedback configuration.

Taking the closed-loop  $OP_2$  amplifier configuration into consideration,  $OP_2$  will respond to the voltage difference between its two input terminals. If there is too much current running through the right branch (i.e. the voltage at the top of R is too high),  $OP_2$  will lower  $V_{out}$  to draw some current out of the branch to maintain  $V_{ref2}$  at the non-inverting terminal. If there is too little current flowing through the right branch,  $OP_2$  it will attempt to source the

current difference by increasing  $V_{out}$ .

Using Ohm's Law and the ideal op-amp characteristics, the output voltage of the Wheatstone bridge sensing circuit can be expressed as the following equation. The full derivation is shown in Appendix A.

$$V_{out} = V_{ref2} + \frac{R_2}{R_1} \delta(V_{ref1} - V_{ref2})$$

(2.1)

$\delta$  is the change in the sensing resistor (specifically, a thermistor). Also note that the output is not dependent upon the sensing resistance R (i.e. the resistance without any subscript), but is a function of its change. However, when designing and selecting an appropriate value for R in the right leg of the Wheatstone bridge, you must know the top and bottom range of  $R(1 + \delta)$ . Ultimately, R is selected to be the middle value of the  $R(1 + \delta)$  range.

After R has been determined, one can select  $R_1$  to determine an appropriate amount of current through the Wheatstone bridge legs. This would be dependent upon R. For example, if R is in tens or low-hundreds of ohms, the current through the Wheatstone bridge legs should be in the low milliampere range to create a large enough voltage drop across  $R(1+\delta)$  for  $OP_1$ . This would also depend upon  $V_{ref1}$  and  $V_{ref2}$ . For our designs,  $V_{ref1}$  and  $V_{ref2}$  have been chosen to be  $V_{dd}$  and mid-rail, respectively. And finally,  $R_2$  is selected to gain up the change in resistance to correspond the  $R(1+\delta)$  range to an output voltage between 0V and  $V_{dd}$ .

### 2.4 Circuit Implementation

### 2.4.1 Voltage Regulator and Battery

The focus of this work has been to design a low-power sensing circuit for a wireless microcontroller, which implicitly means the power source is battery. A voltage regulator is needed to generate a stable and known voltage from an ever-changing battery output. Without regulation, the effective supply voltage would lower (non-linearly) over time. More specifically, the output voltage expression of relies on assumption of stable voltage references of  $V_{ref1}$  and  $V_{ref2}$ , which need to be held constant as the batteries' output voltage lowers over time. While it has not been explicitly stated or shown in the schematics up to this point, a voltage regulator is called for in this design.

The dynamic between the battery supply and the voltage regulator is for the battery to supply a larger than needed voltage and for the regulator to regulate the supplied battery voltage down to a desired value. Voltage regulators are able accomplish this functionality through a negative feedback configuration. For the case of this work, the main specification of the voltage regulator is to maintain a regulated 2.5V as the reference voltage and power supply of the sensing circuit. The output of three AA batteries is typically measured to about 4V, which gives plenty of headroom for the voltage dropout.

The voltage dropout specification is main reason for not choosing two AA batteries in series as the supply. The difference in measured output voltage of a two, full-capacity AA battery supply and the regulated voltage is on the order of 250mV. This is close to the minimum dropout voltage required for regulators of this application. If the two AA battery supply was employed, it would only be a matter of hours to draw down the capacity below the minimum dropout voltage. The issue is resolved by simply adding a third AA cell in series with the aforementioned two AA cell. This design choice does not affect any space and weight requirements of the project, and has the additional benefit of extended operation time. Ultimately, we chose a commercially available off-the-shelf component MCP 1700 as our voltage regulator [14].

### 2.4.2 Brick Characterization and Circuit Components

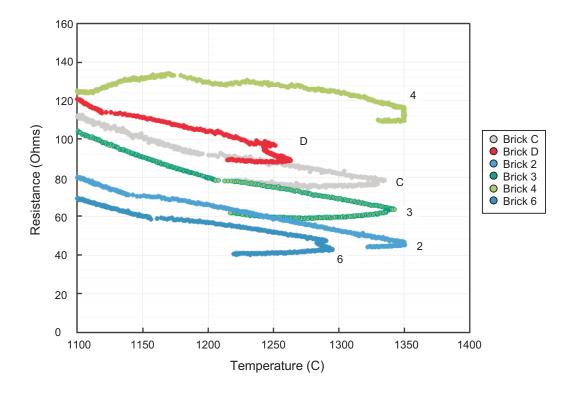

The smart bricks that were cast have been characterized and are shown in Fig. 2.4. This figure is a slightly different viewpoint from Figure 2.2 in that time has been removed from the figure, but ultimately conveys the same information. There is some variance among the smart bricks in that for the same furnace temperature, each respective thermistor does not map to the same measured resistance. As discussed in the previous section, the sensing range of  $R(1+\delta)$  should encompass the top-end of the highest resistive sensor and the bottom-end of the lowest resistive sensor in the desired temperature range. Furthermore, only four of the bricks are being deployed for the final demo: Brick D, Brick C, Brick 3, and Brick 2. This means that the expected  $R(1+\delta)$  sensing range to design the circuit around is  $35\Omega$  and  $115\Omega$ .

Knowing the data from Fig. 2.2 and considering the aforementioned design process of the circuit, the following values were selected for the various reference voltages and resistors of the Wheatstone bridge circuit in Table 2.1.

Figure 2.4: Six smart brick characterizations.

Fig. 2.5 allows one to map the output voltage of the sensing circuit to a specific temperature. The data of the figure is from two separate experiments layered over each other. The sensing circuit was physically measured with  $R(1+\delta)$  changing in  $10\Omega$  increments, and the resistance measurement of the smart brick was measured during a characterization run. It is evident that the chosen sensor material has a nonlinear dependence on temperature, but the sensing circuit output is linear with the exception of when the op-amp does not operate in it's linear region at the supply-rail extremes. The nonlinear temperature dependence was expected for the sensor in this type of high-temperature, high-pressure furnace environment.

The wireless sensing circuit that will be used in proof-of-concept demonstration is shown in Fig. 2.6. It consists of a vertical stack of battery-pack, wireless mote, and sensing circuit from bottom to top. The sensing circuit contains two standard banana adapters to directly interface with the smart brick. Fig. 2.7 demonstrates how the wireless sensing circuit would be interfaced at a foundry furnace wall. The mechanical design of the wireless sensing circuit allows them to be vertically stacked. The top metal spacer can be screwed into the bottom of the taller spacer of another wireless sensing circuit.

The data shown Fig. 2.8 is the wireless sensor mote's data received at the master mote

| $V_{ref1}$ | 2.5V           |

|------------|----------------|

| $V_{ref2}$ | 1.25V          |

| $R_1$      | $680\Omega$    |

| $R_2$      | $1.133k\Omega$ |

| R          | $75\Omega$     |

Table 2.1: Designed values for Wheatstone bridge resistive sensing circuit.

node. This figure demonstrates how one of the wireless sensing nodes fits within the whole system. The chain of events begins at the sensor. The sensing circuit amplifies and conditions the sensor signal for the mote ADC to measure. The mote takes the ADC measurement, encodes it into a code-word, and wirelessly transmits the measurement to the master mote. The master mote is the central location where all the measured data is aggregated and provides the human interface to the system. The master mote can then decode the codeword and plot the data.