## **Old Dominion University**

## **ODU Digital Commons**

Electrical & Computer Engineering Theses & **Dissertations**

**Electrical & Computer Engineering**

Spring 1989

# Performance Modeling and Enhancement for the ATAMM Data Flow Architecture

Sukhamoy Som Old Dominion University

Follow this and additional works at: https://digitalcommons.odu.edu/ece\_etds

Part of the Computer Sciences Commons, and the Electrical and Computer Engineering Commons

#### **Recommended Citation**

Som, Sukhamoy. "Performance Modeling and Enhancement for the ATAMM Data Flow Architecture" (1989). Doctor of Philosophy (PhD), Dissertation, Electrical & Computer Engineering, Old Dominion University, DOI: 10.25777/r62w-cq14

https://digitalcommons.odu.edu/ece\_etds/196

This Dissertation is brought to you for free and open access by the Electrical & Computer Engineering at ODU Digital Commons. It has been accepted for inclusion in Electrical & Computer Engineering Theses & Dissertations by an authorized administrator of ODU Digital Commons. For more information, please contact digitalcommons@odu.edu.

# PERFORMANCE MODELING AND ENHANCEMENT FOR THE ATAMM DATA FLOW ARCHITECTURE

by

Sukhamoy Som B.Tech. July 1980, Indian Institute of Technology, Kharagpur M.E. August 1984, Old Dominion University

A Dissertation Submitted to the Faculty of Old Dominion University in Partial Fulfillment of the Requirements for the Degree of

DOCTOR OF PHILOSOPHY in ENGINEERING

OLD DOMINION UNIVERSITY May 1989

| Approve | d by:        |             |

|---------|--------------|-------------|

|         | <u> </u>     | <u></u>     |

| John W. | Stoughton    | (Director)  |

|         |              | <del></del> |

|         |              |             |

|         |              | -           |

|         | <del>-</del> |             |

#### ABSTRACT

"PERFORMANCE MODELING AND ENHANCEMENT FOR THE ATAMM DATA FLOW ARCHITECTURE"

Sukhamoy Som Cld Dominion University, 1989 Director: Dr. John W. Stoughton

Algorithm To Architecture Mapping Model (ATAMM) is a new marked graph model from which the rules for data and control flow in a homogeneous, multicomputer, data flow architecture may be defined. This research is concerned with performance modeling and performance enhancement for periodic execution of large-grain, decision-free algorithms in such an ATAMM defined architecture. Performance measures and bounds are established. Algorithm transformation techniques are identified for performance enhancement and reduction of computing element requirements. Operating strategies are developed for optimum time performance and for sub-optimum time performance under limited availability of computing elements. An ATAMM simulator is used to test and validate these operating strategies. Experiments on a three computing element testbed provide verification of performance modeling and transformation methods.

## DEDICATION

This is dedicated to my parents and my wife for their love and support.

#### **ACKNOWLEDGMENTS**

I am grateful to Dr. J. W. Stoughton for his guidance, consultations for this research and help in bringing this manuscript to its present form. I am indebted to Dr. R. R. Mielke for many discussions regarding this research and reviewing this dissertation. I wish to thank Dr. D. Livingston and Dr. L. Wilson for reviewing this dissertation.

I also wish to thank R. Obando and W. R. Tymchyshyn for their help whenever needed. I am grateful to the Information Processing Technology Branch of NASA Langley Research Center for supporting this work.

Finally, my sincerest thanks are reserved for my wife, Sreelata M. Som, who has helped and encouraged me all along.

## TABLE OF CONTENTS

|       |       | PAGE                                                  |

|-------|-------|-------------------------------------------------------|

| LIST  | OF TA | BIFS vi                                               |

| LIST  | OF FI | GURES vii                                             |

| LIST  | OF SY | MBOIS xi                                              |

| CHAP. | IER   |                                                       |

| 1.    | INTR  | ODUCTION                                              |

|       | 1.0   | Preface 1                                             |

|       | 1.1   | Background                                            |

|       | 1.2   | Problem Representation by the ATAMM model 5           |

|       | 1.3   | Objectives and Organization of Dissertation 13        |

| 2.    | PERF  | ORMANCE MODEL                                         |

|       | 2.0   | Introduction                                          |

|       | 2.1   | Performance Measures                                  |

|       | 2.2   | Marked Graph Characteristics                          |

|       | 2.3   | Graph Theoretic Performance Bounds                    |

|       | 2.4   | Resource Requirements                                 |

|       | 2.5   | Summary 53                                            |

| 3.    | ALGO  | RITHM TRANSFORMATION                                  |

|       | 3.0   | Introduction                                          |

|       | 3.1   | Algorithm Transformation Guidelines 55                |

|       | 3.2   | Performance Improvements by Transformation 62         |

|       | 3.3   | Implementation of Periodicity by Transformation 72    |

|       | 3.4   | Structural Changes in Algorithm by Transformation. 80 |

|         | 3.5   | Summary                            | 93  |

|---------|-------|------------------------------------|-----|

| 4.      | ATAM  | M OPERATING POINT DESIGN           | 95  |

|         | 4.0   | Introduction                       | 95  |

|         | 4.1   | Characteristics of Operating Point | 95  |

|         | 4.2   | Operating Point Design             | 101 |

|         | 4.3   | Test Results                       | 111 |

|         | 4.4   | Summary                            | 146 |

| 5.      | CONC  | LUSION                             | 147 |

| LIST    | OF RE | FERENCES                           | 153 |

| 3 TYPEN | DTM   |                                    |     |

## LIST OF TABLES

| TABLE |                                  | PAGE |

|-------|----------------------------------|------|

| 4.1   | Comparison of Results for Test 1 | 119  |

| 4.2   | Comparison of Results for Test 2 | 127  |

## LIST OF FIGURES

| FIGURE |                                                                                   | PAGE |

|--------|-----------------------------------------------------------------------------------|------|

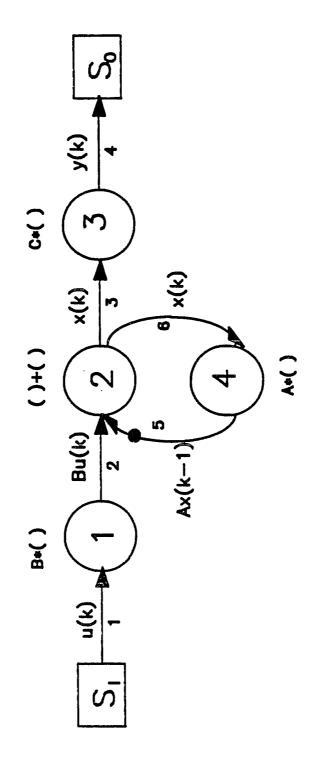

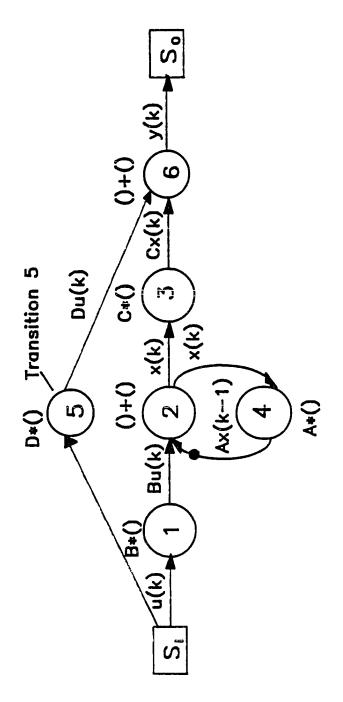

| 1.1    | Algorithm marked graph for discrete system equation                               | 9    |

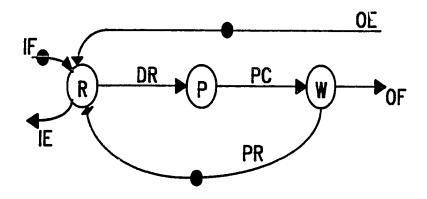

| 1.2    | ATAMM node marked graph model                                                     | 12   |

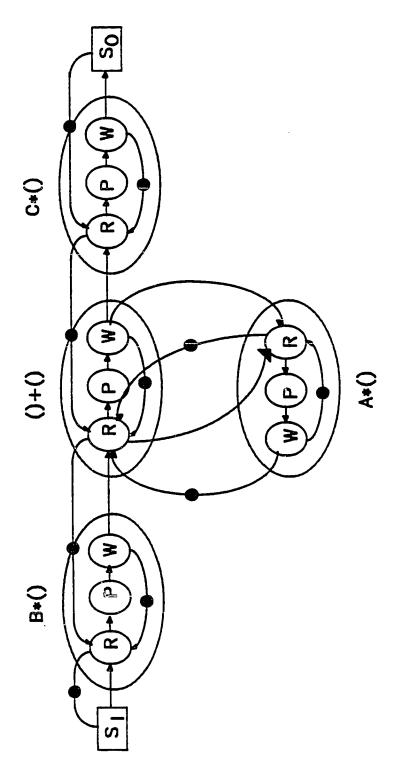

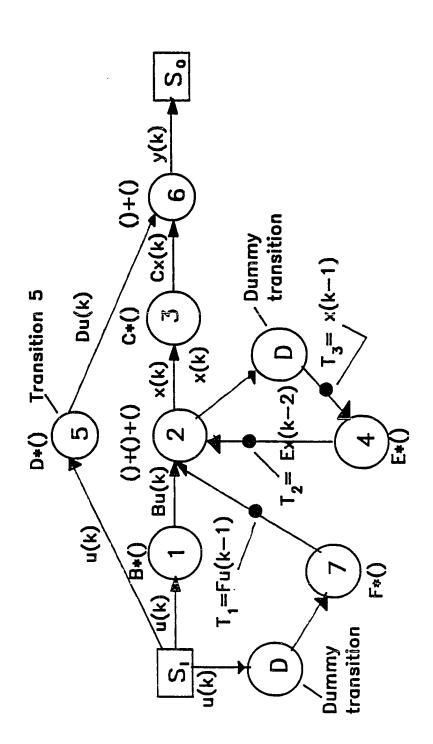

| 1.3    | ATAMM computational marked graph model for discrete system equation               | 14   |

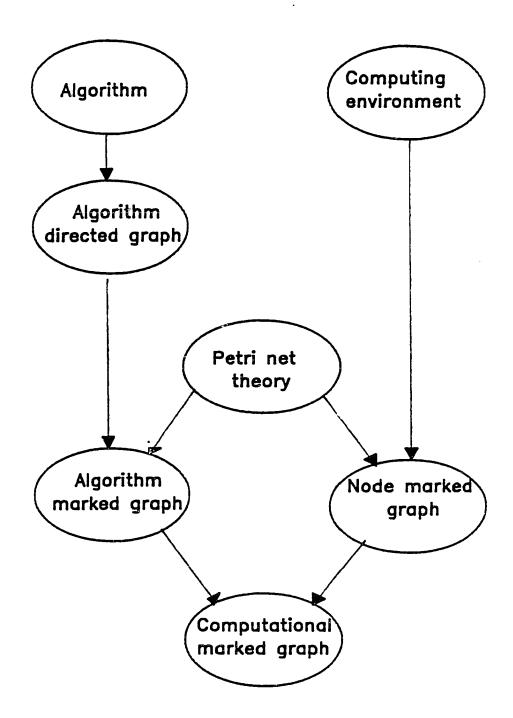

| 1.4    | ATAMM model components                                                            | 15   |

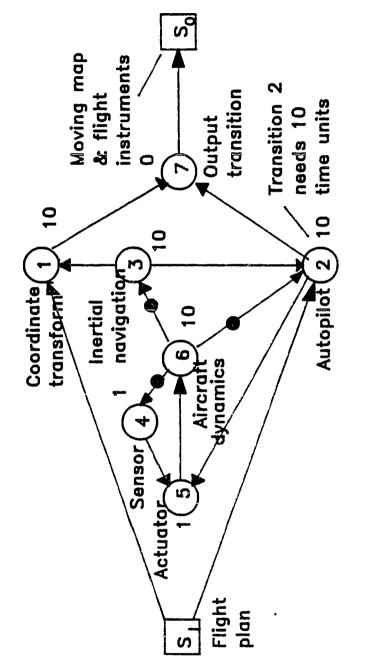

| 2.1    | An algorithm for flight simulation plan                                           | 21   |

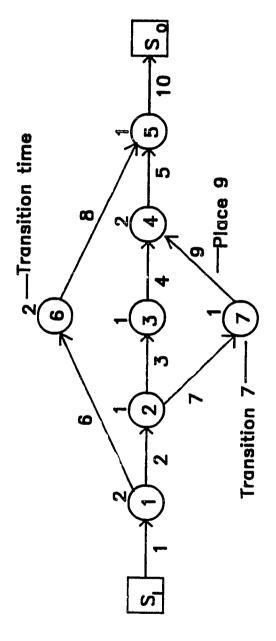

| 2.2    | Example algorithm marked graph                                                    | 23   |

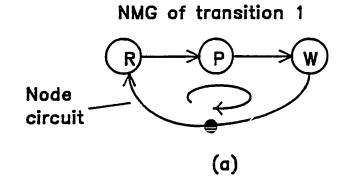

| 2.3    | Example of node and process circuits                                              | 26   |

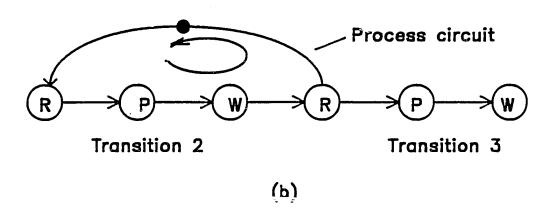

| 2.4    | Computational marked graph for the AMG                                            | 28   |

| 2.5    | Example of recursion and parallel path circuits                                   | 29   |

| 2.6    | Modified algorithm marked graph for Figure 1.1                                    | 32   |

| 2.7    | Algorithm marked graph for illustration of GPST AND REST                          | 42   |

| 2.8    | GPST and REST                                                                     | 43   |

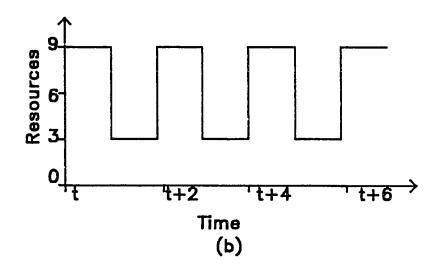

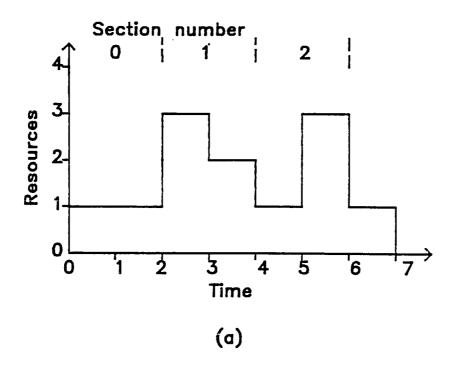

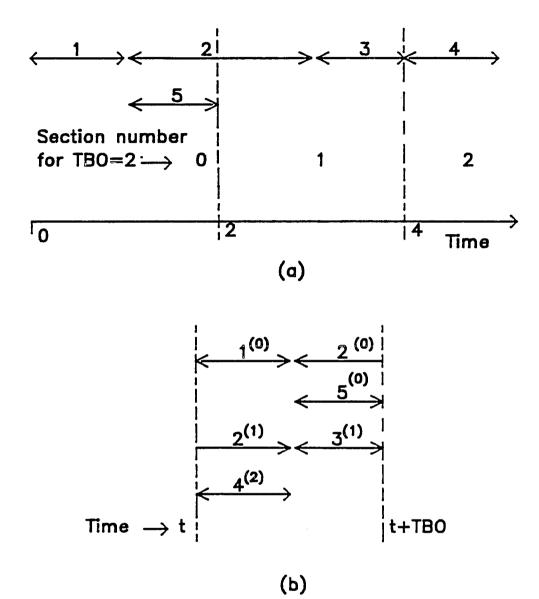

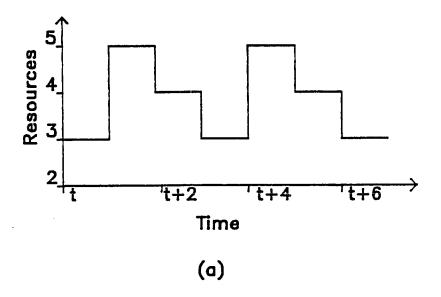

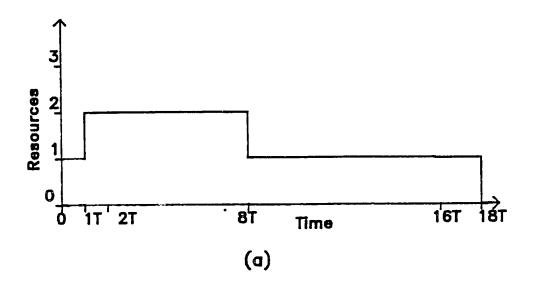

| 2.9    | Total graph play and total resource envelope for TBO = 2                          | 50   |

| 2.10   | Resource envelope for a single task input and total resource envelope for TBO = 3 | 52   |

| 3.1    | Transformed algorithm marked graph in Application 1                               | 60   |

| 3.2    | Computational marked graph for the transformed AMG                                | 61   |

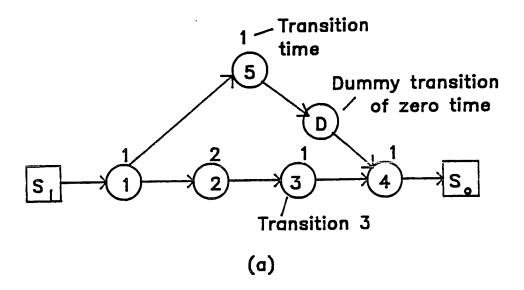

| 3.3    | AMG for illustration of Application 2                                             | 68   |

| 3.4    | REST and TRE for TBO = 2                                                          | 69   |

| 3.5    | Transformed AMG for Figure 3.3                                                     | 70  |

|--------|------------------------------------------------------------------------------------|-----|

| 3.6    | For the AMG transformed by control place<br>1, REST and TRE for TBO = 2            | 71  |

| 3.7    | For the transformed AMG with all control places, REST and TRE for TBO = 2          | 73  |

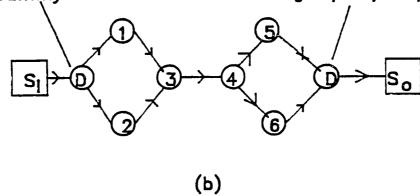

| 3.8    | Injection control by Application 3                                                 | 75  |

| 3.9    | Example AMG for illustration of Application 4                                      | 78  |

| 3.10   | GPST and TGP for TBO = 2                                                           | 79  |

| 3.11   | Transformed AMG and total graph play for TBO = 3                                   | 81  |

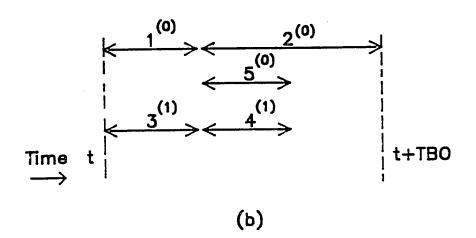

| 3.12   | AMG $A_1$ and transformed AMG $A_2$                                                | 83  |

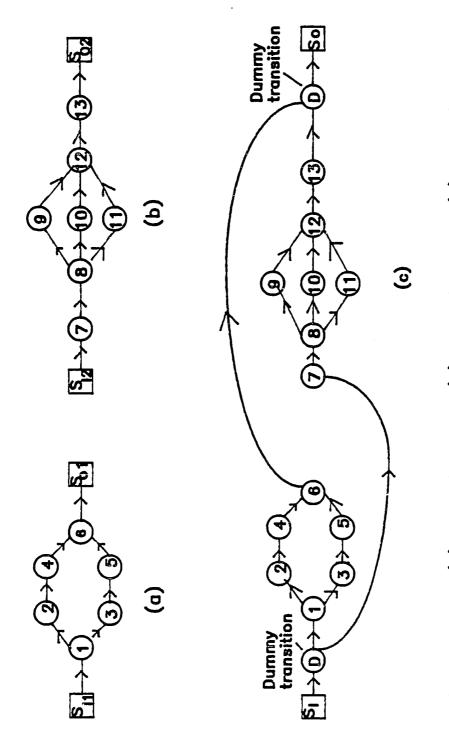

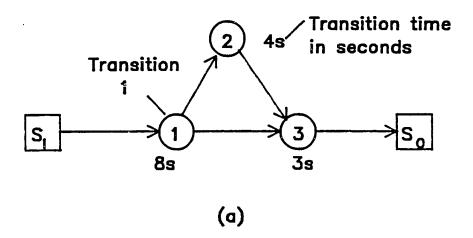

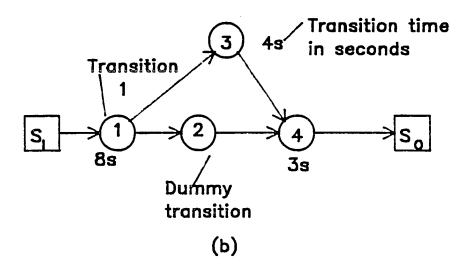

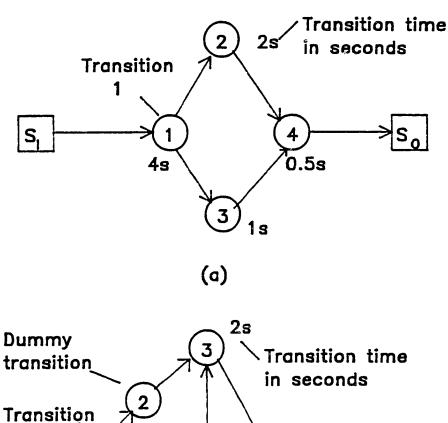

| 3.13   | Algorithm 1, Algorithm 2, and Algorithms 1 and 2 are combined by dummy transitions | 84  |

| 3.14   | AMG for the linear time invariant system                                           | 85  |

| 3.15   | Transformed AMG for the linear time invariant system                               | 88  |

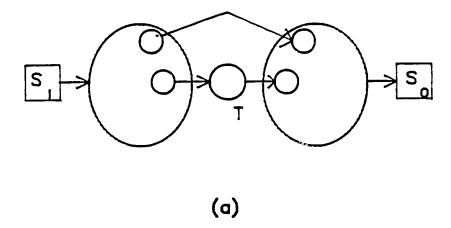

| 3.16   | An AMG with a large transition T and T is decomposed in N parallel transitions     | 91  |

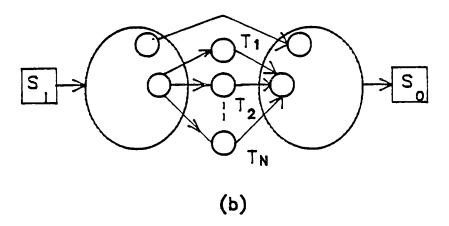

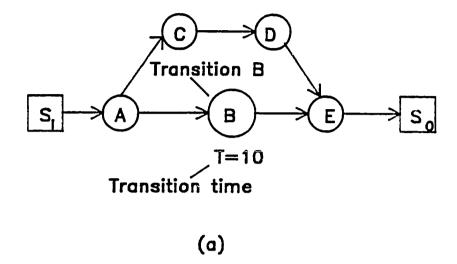

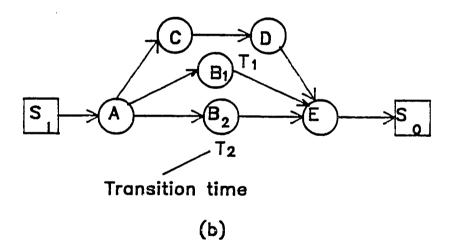

| 3.17   | AMG before decomposition of B and B is decomposed                                  | 94  |

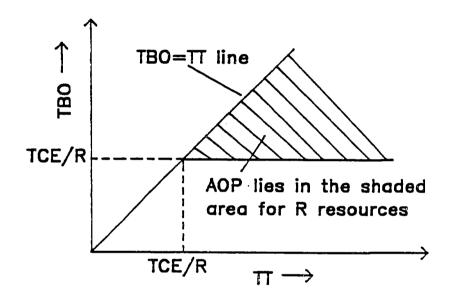

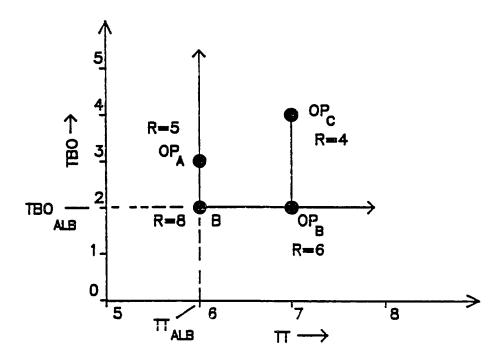

| 4.1    | ATAMM operating point characteristics                                              | 98  |

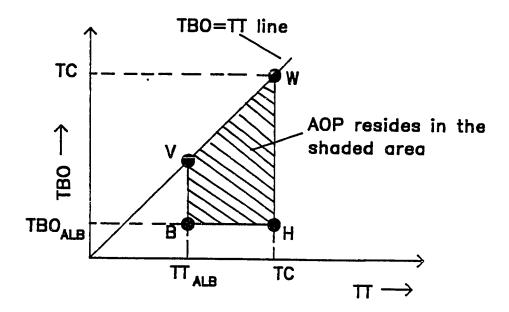

| 4.2(a) | AOP characteristics under specific transformations                                 | 102 |

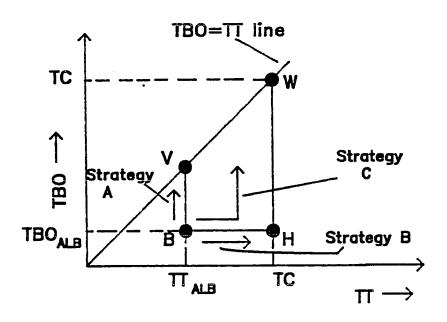

| 4.2(b) | The strategies for AOP design under resource constraints                           | 106 |

| 4.3    | GPST and TGP for TBO = 2                                                           | 107 |

| 4.4    | TRE for TBO = 3 in Step 4 and TRE for TBO = 4 in Step 6                            | 109 |

| 4.5    | GPST and TGP for TBO = 2                                                           | 110 |

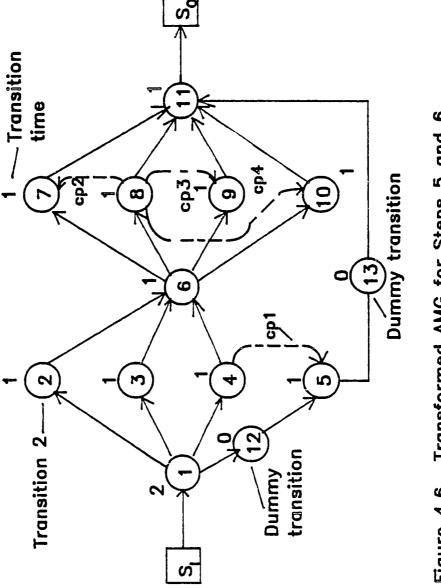

| 4.6    | Transformed AMG for Steps 5 and 6                                                  | 112 |

| 4.7    | ATAMM operating points for the example algorithm marked graph                      | 113 |

| 4.8  | The testbed ATAMM data flow architecture               | 115 |

|------|--------------------------------------------------------|-----|

| 4.9  | AMG for Test 1 and transformed AMG for Test 1          | 117 |

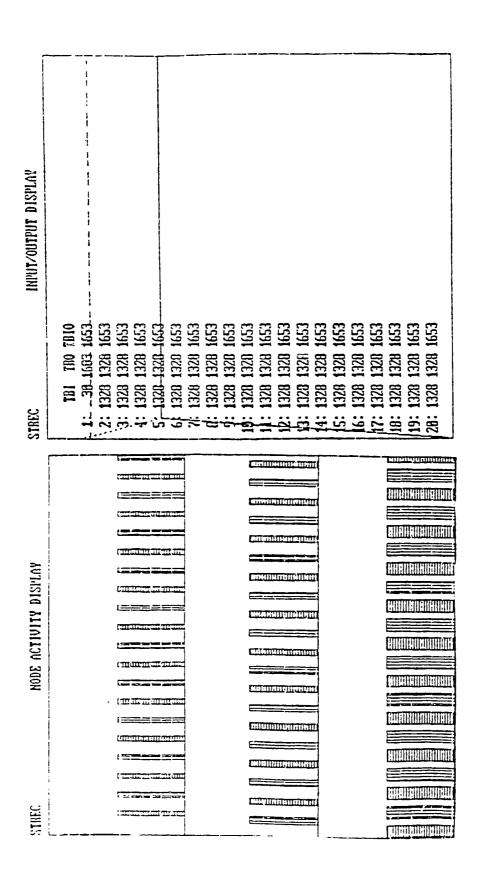

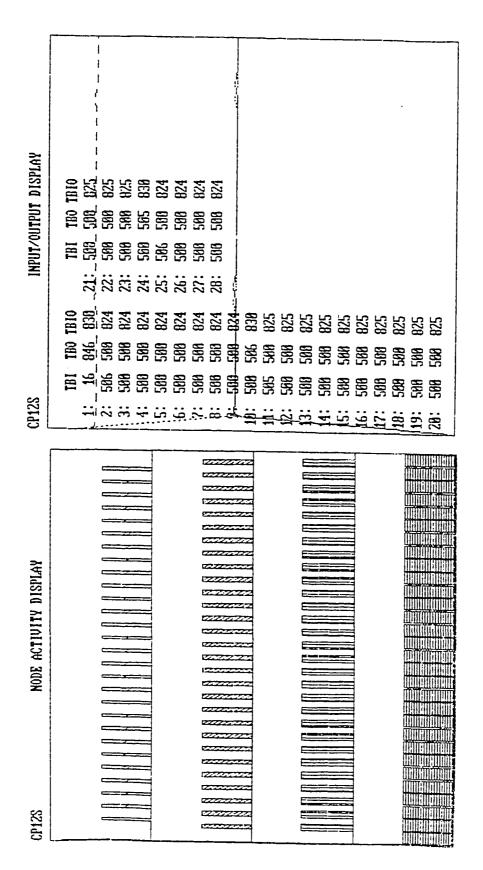

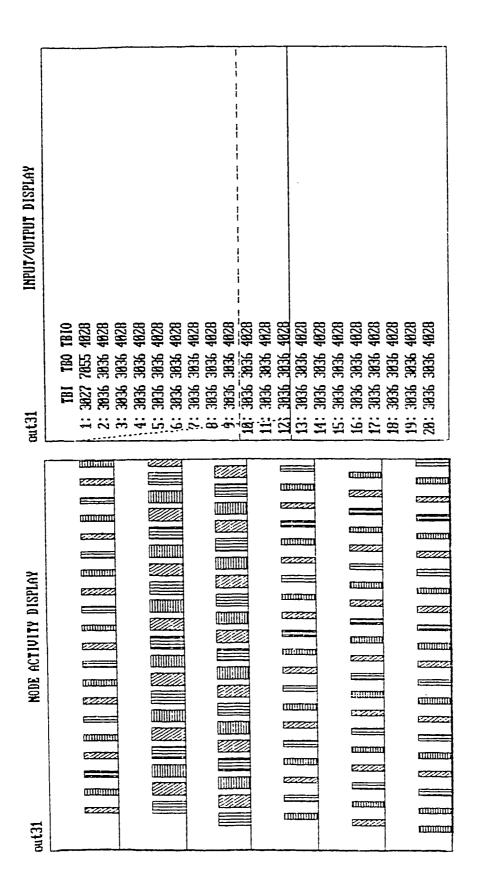

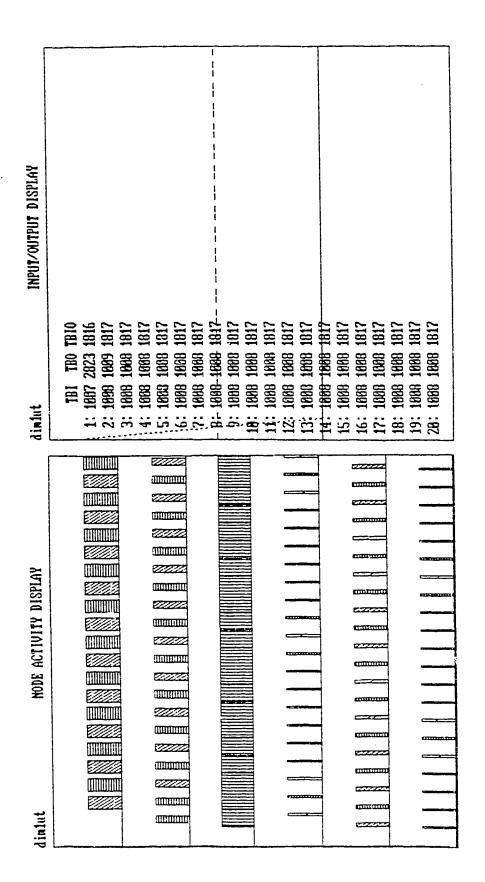

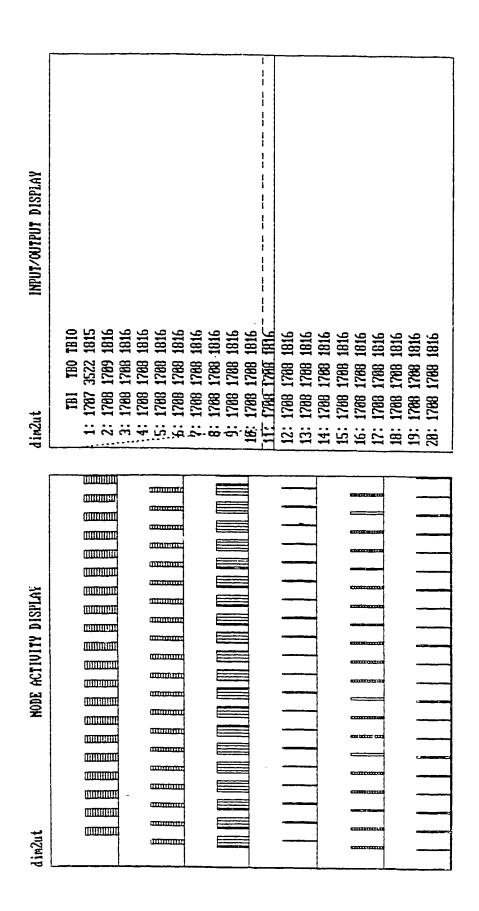

| 4.10 | Simulation results for the AMG in Test 1               | 120 |

| 4.11 | Simulation results for the transformed AMG in Test 1   | 121 |

| 4.12 | Experimental results for the AMG in Test 1             | 122 |

| 4.13 | Experimental results for the transformed AMG in Test 1 | 123 |

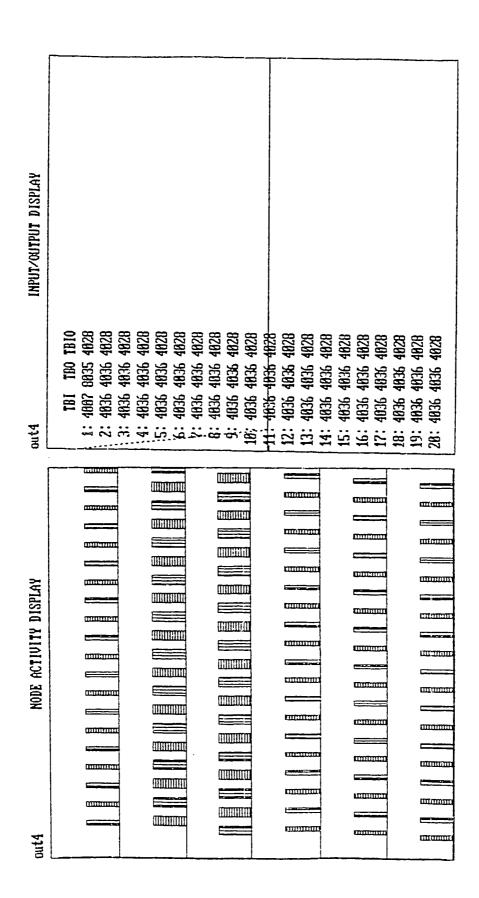

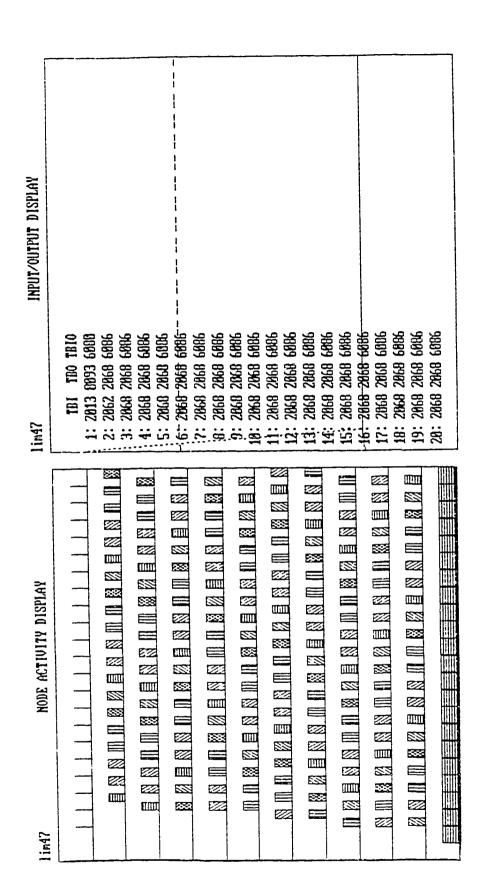

| 4.14 | AMG for Test 2 and transformed AMG for Test 2          | 125 |

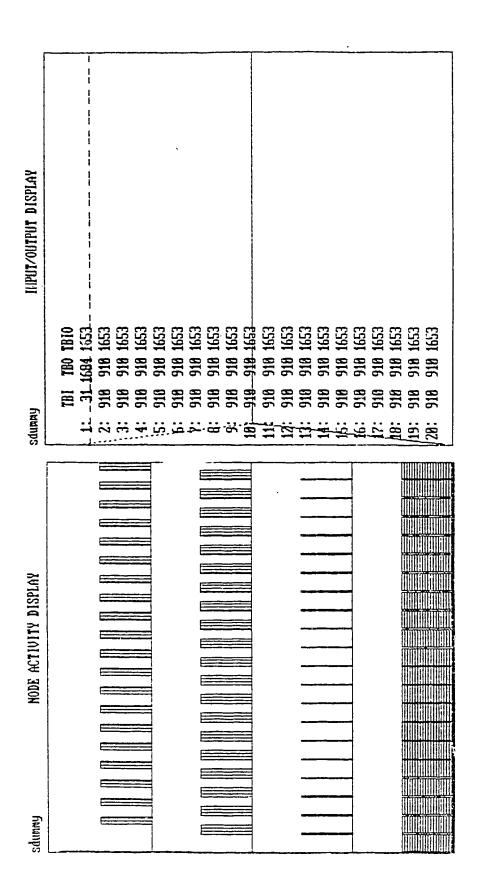

| 4.15 | Simulation results for the AMG in Test 2               | 128 |

| 4.16 | Simulation results for the transformed AMG in Test 2   | 129 |

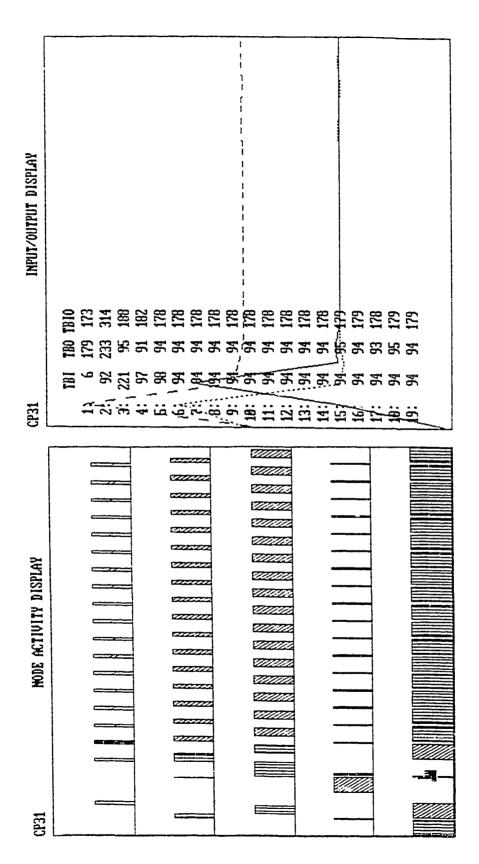

| 4.17 | Experimental results for the AMG in Test 2             | 130 |

| 4.18 | Experimental results for the transformed AMG in Test 2 | 131 |

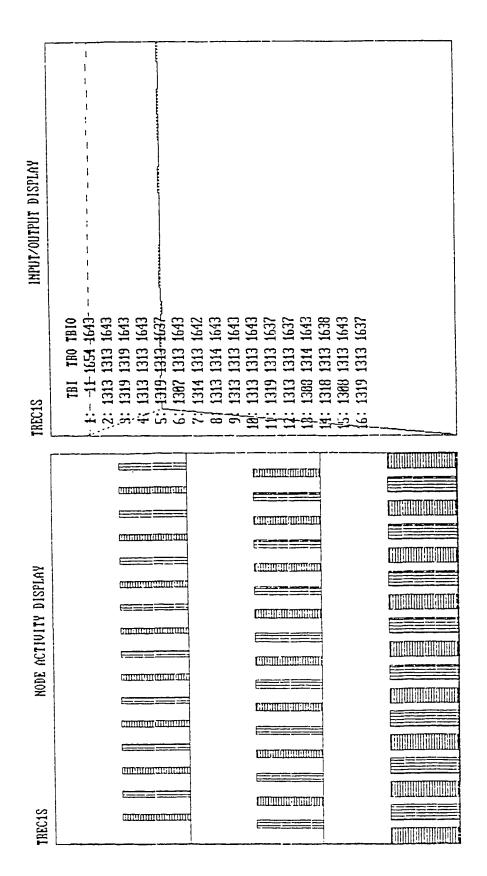

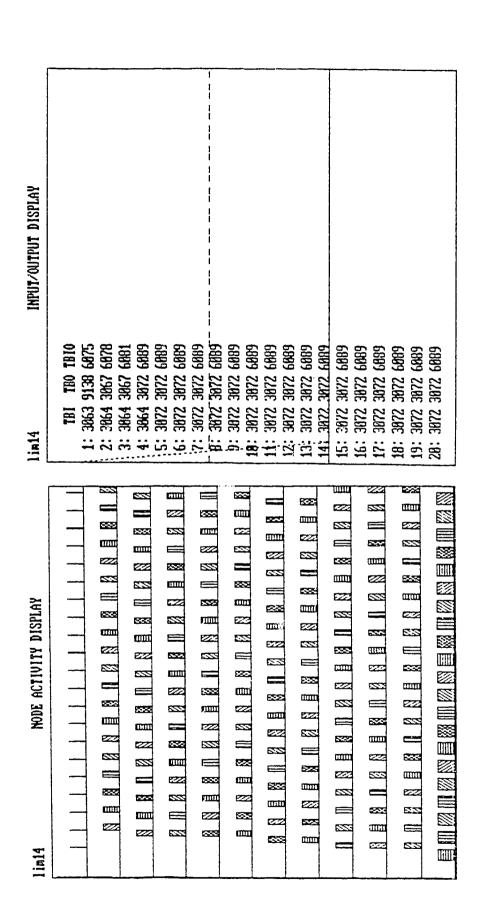

| 4.19 | For Test 3, AMG and REST                               | 132 |

| 4.20 | Simulation results for AOP of Step 3 in Test 3         | 134 |

| 4.21 | Simulation results for AOP of Strategy A in Test 3     | 135 |

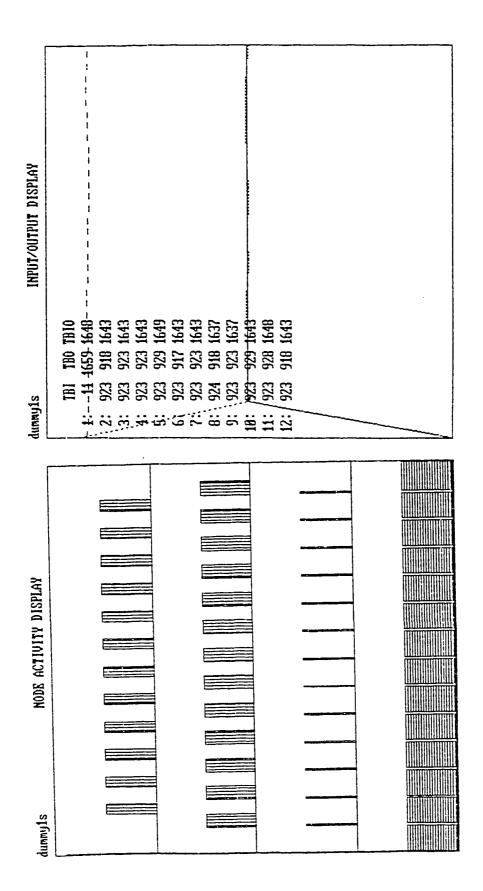

| 4.22 | AMG for Test 4 and REST for the AMG of Test 4          | 136 |

| 4.23 | For the transformed AMG, REST and GPST                 | 138 |

| 4.24 | TGP for transformed AMG                                | 139 |

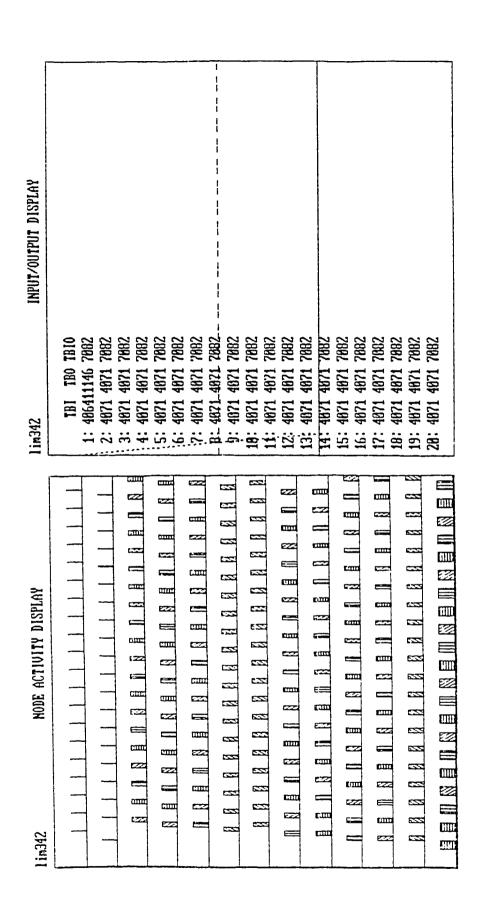

| 4.25 | Simulation results for AOP of Step 3 in Test 4         | 140 |

| 4.26 | Simulation results for AOP of Strategy A in Test 4     | 141 |

| 4.27 | Simulation results for AOP of Step 3 in Test 5         | 142 |

| 4.28 | Simulation results for A Strategy A in Test 5 | AOP of | 143 |

|------|-----------------------------------------------|--------|-----|

| 1.29 | Simulation results for A Strategy B in Test 5 | AOP of | 144 |

| 4.30 | Simulation results for A                      | AOP of | 145 |

#### LIST OF SYMBOLS

SYMBOL

DESCRIPTION

AOP

ATAMM Operating Point

AMG

Algorithm Marked Graph

ATAMM

Algorithm To Architecture Mapping Model

b

Section number of GPST and data packet number

$C_i$

ith directed circuit

CMG

Computational Marked Graph

CC

Computing Capacity

Œ

Computing Effort

DR

Data Ready

FUN

Functional Unit

G

An algorithm marked graph

$G_{\mathbb{C}}$

A computational marked graph

$G_{M}$

Modified algorithm marked graph for G

GLM

Global Memory

GPST

Graph Play for a Single Task Input

GM

Graph Manager

ΙE

Input Buffer Empty

IF

Input Buffer Full

MAMG

Modified Algorithm Marked Graph

$M(C_i)$

Number of tokens in circuit i

NMG

Node Marked Graph

OE Output Buffer Empty

OF Output Buffer Full

pj Place j

P<sub>i</sub> i<sup>th</sup> directed path

PC Process Complete

PR Process Ready

REST Resource Envelope for a Single Task Input

RU Resource Utilization

t<sub>j</sub> Transition j

$T(C_i)$  Total transition times in  $C_i$

$T(P_i)$  Total transition times in  $P_i$

TBI Input data injection interval

TBO Time Between Outputs

${\it TBO}_{\it OD}$   ${\it TBO}$  at the operating point

TBO<sub>ALB</sub> Absolute lower bound for TBO

TBOTR Lower bound for TBO

TBIO Time Between Input and Output

${\rm TBIO}_{{\rm ATR}}$  Absolute lower bound for TBIO

${

m TBIO}_{

m IR}$  Lower bound for TBIO

TGP Total Graph Play

TRE Total Resource Envelope

TBC Total Backward Computation

TC Total Computation

TCE Total Computing Effort

TFC Total Forward Computation

TFCE Total Forward Computing Effort

TT Task Time

${

m TT}_{

m ALB}$  Absolute lower bound for TT

$\mathrm{TT}_{\mathrm{LB}}$  Lower bound for  $\mathrm{TT}$

#### CHAPTER ONE

#### INTRODUCTION

#### 1.0 Preface

Algorithm To Architecture Mapping Model (ATAMM) is a new graph theoretic model from which the rules for data and control flow in a homogeneous, multicomputer, data flow architectures may be defined [1, 2]. The subject of this dissertation is the investigation of concurrent processing in such an ATAMM defined architecture for large-grain, decision-free algorithms. Performance modeling, performance enhancement, and the development of operating strategies for periodic execution of such algorithms are the key research objectives. Chapter One is an introduction of ATAMM and a discussion of the motivation behind the research. Background for the ATAMM model and this research is presented in Section 1.1. The computational problem representation by the ATAMM model is presented in Section 1.2. The objectives and organization of this dissertation are described in Section 1.3.

#### 1.1 Background

The principles of computer architecture design historically have been based upon von Neumann organization [3]. These principles have lead to architectures consisting of a single computer in which low level machine language instructions perform simple operations on elementary operands, and centralized, sequential control of

computation is employed. Despite the fact that electronic components are becoming increasingly faster, the desired computer performance has always been much more than that which is obtainable with von Neumann organization. Advances in the solid state technology alone are not expected to be enough to produce computers to meet the computational needs of the future. There is a growing agreement that the next (fifth) generation of computers will be based upon non-von Neumann structures.

Recently, a number of new computer architectures have been proposed from which a number of computer systems have been built [3]. A few examples are Texas Instruments Distributed Data Processor (USA), Cellular Tree Machine of the University of North Carolina-Chapel Hill (USA), and Manchester Data Flow Computer (England) [3]. This work has been motivated mainly by three objectives. First, there is the desire to increase computer performance through the use of concurrency. Second, there is the desire to more fully exploit very large scale integration (VISI) in the design of computers. Third, there is interest in new programming methods which facilitate the mapping of algorithms onto architectures. These ideas suggest a decentralized computer architecture in which a number of independent computers are to work together. These independent computers, each having a capability for processing, communication, and memory, can be as large as a geographically distributed mainframe computer or as small as microcomputers on a single VISI chip. Unfortunately, strategies for interconnecting and programming such architectures based upon von Neumann principles have not evolved. It appears that von Neumann organization principles are not adequate to address the complex issues of scheduling, coordination, and communication.

Strategies for control of computations on decentralized computer architectures can be classified broadly as control flow, demand driven, and data driven. In control flow computers, explicit flows of control cause the execution of instructions. In demand driven architectures, the execution of operations are triggered by the requirements of outputs or results. In data driven architectures (also known as data flow computers), the availability of operands trigger the execution of operations. Data flow architectures are the primary interest of this research because of their suitability for concurrent processing of complex algorithms.

A useful mathematical tool for modeling execution of complex algorithms on a data flow decentralized architecture is the Petri net. Petri nets were first developed in 1962 by Carl Petri [4], and later were identified as a useful analysis tool in the work of Holt and Commoner [5]. A comprehensive treatment of Petri nets is presented in [6]. One problem with the Petri net model is that it tends to be too complicated to analyze. An important subclass of Petri net is the marked graph where each place has exactly one incoming and one outgoing arc. Marked graphs can be used to model the processing of decision-free algorithms [7]. Properties such as liveness, safeness, and reachability can be achieved for marked graph models [6]. Procedures also exist for expanding and reducing marked graphs while preserving these properties [8]. These graph features are suitable for modeling the succession of single events such as data and status conditions. In this dissertation, the marked graph is used as a modeling tool for data driven computations.

The data flow concept has already attracted the attention of a great many researchers. Starting with the work on data flow at MIT by

Jack Dennis, a number of data flow computers have been built [9]. The best strategy for executing an algorithm in these data flow computers is machine dependent. However, only a few researchers have tried to develop a theoretical model for evaluating computation in a data driven architecture [10]. These models do not appear to be adequate to address the complex issues of scheduling, coordination, and communication.

There is a need for a simple, but effective, model for data driven computations in order to investigate the relative merits of different algorithm decompositions and implementation strategies in a hardware independent context. Ongoing research effort at Old Dominion University has lead to the development of a new marked graph model for describing data and control flow associated with the execution of algorithms in data flow architectures [2]. The model is identified by the acronym ATAMM which represents Algorithm To Architecture Mapping Model [11]. Specifications derived from the model lead directly to the description of a data flow architecture and will be called the ATAMM data flow architecture henceforth. The availability of the ATAMM model is important for at least three reasons. First, it provides a context in which to investigate algorithm decomposition strategies without the need to specify a specific ATAMM data flow architecture. Second, the model identifies the data flow and control dialogue required of any ATAMM data flow architecture which implements the algorithm. Third, the model provides a basis for analytically calculating performance bounds and developing a methodology for improvement in performance.

The problem domain addressed by the ATAMM data flow architecture and this research consists of decision-free, large-grain, complex algorithms which are assumed to be executed periodically in a multicomputer environment. The algorithms are assumed to require large computations which would include such computations as matrix addition, multiplication, etc. The anticipated multicomputer environment is assumed to consist of two to twenty identical computers or functional units each having a capability of processing, communication and memory. The primary reason for such assumptions is the objective of implementing control and signal processing algorithms in fifth generation multicomputer architectures for real time applications on board the proposed Space Station. The granularity level of the algorithm decomposition is kept high to avoid communication bottlenecks as observed in many fine-grain data flow architectures [12]. The range of functional units is suggested due to the large-grained aspect of the algorithm decomposition. Of interest is the definition of a performance model so that the performance of the algorithms can be evaluated and improved. Also an operating procedure is needed for obtaining predictable performance with respect to available computing elements.

### 1.2 Problem Representation by the ATAMM Model

The ATAMM model consists of a set of Petri net marked graphs which incorporate general specifications of communication and processing associated with each computational event in a data flow architecture. In this section, the computational problem is represented by the ATAMM model. First of all a detailed description

of the problem context is stated. This is followed by the definition of the ATAMM model consisting of the algorithm marked graph, the node marked graph, and the computational marked graph. Some familiarity with Petri nets [6] and marked graphs [13] is assumed.

A problem description normally results in the definition of a function given by the triple (X, Y, F), where X represents the set of admissible inputs, Y the set of admissible outputs, and F: X -> Y the rule of correspondence which unambiguously assigns exactly one element from Y to each element of X. Associated with a computational problem is one or more algorithms. An algorithm is an explicit mathematical statement, expressed as an ordered set of primitive operations, which explains how to implement the rule of correspondence F. A primitive operation is a complex computation. Matrix multiplication and addition are examples of primitive operations. In general, a given problem can be decomposed by several different primitive operator sets. Also, for a given primitive operator set, there are often different ordering of primitive operations which can be specified to carry out the problem. Of special interest are algorithm decompositions in which two or more primitive operations can be performed concurrently. For such decompositions, the potential exists for decreasing the computational time required to solve the problem by increasing the computational resources which implement the primitive operations.

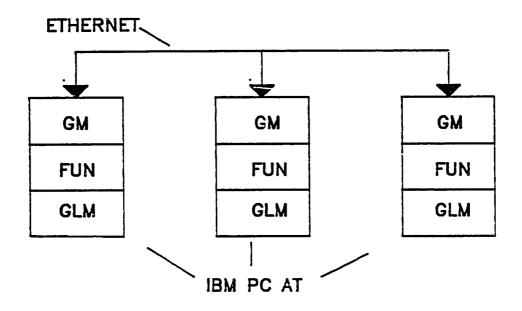

The hardware environment for executing the decomposed algorithms is assumed to consist of R identical computers or functional units (FUN's), where R has a value in the range of two to twenty. These computers or functional units are also denoted by the terms

"computing element" or "resource". Each functional unit is a processor having local memory for program storage and temporary input and output data containers. Each functional unit can execute any algorithm primitive operation. The functional units share a common global memory (GIM), which may be either centralized or distributed. The coordination of functional units in relation to data and control flow is directed by the graph manager (GM). The graph manager also may be centralized or distributed. Output created by the completion of a primitive operation is placed into global memory only after the output data containers have been emptied. That is, outputs must be consumed as inputs to successor primitive operations before allowing new data to fill the output locations. Assignment of a functional unit to a specific algorithm primitive operation is made by the graph manager only when all inputs required by the operation are available in global memory and a functional unit is available.

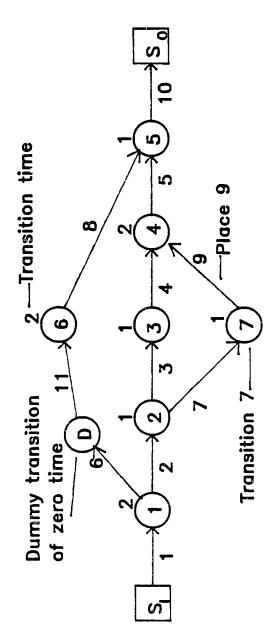

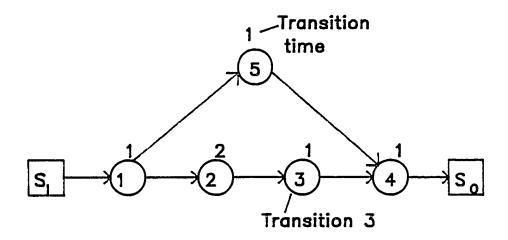

An algorithm marked graph (AMG) is a marked graph which represents a specific algorithm decomposition. Transitions and places are represented as vertices and directed edges respectively. Vertices of the algorithm marked graph are in a one-to-one correspondence with each occurrence of a primitive operation. The transition times represent the computation times of the respective primitive operations. The algorithm marked graph contains an edge (i, j) directed from vertex i to vertex j if the output of vertex i is an input for vertex j. Edge (i, j) is marked with a token if an output from vertex i is available as an input to vertex j. By the rules of the marked graph, the computation of a vertex can only be done when all the incoming edges have a token on them. When constructing an

algorithm marked graph, vertices (transitions) are displayed as circles, and edges (places) are displayed as directed line segments connecting appropriate vertices. The presence of a token on an edge is indicated by a solid dot placed on the edge. Source transitions and sink transitions for input and output signals are represented as squares. Sources for constants are not usually included in the algorithm marked graph; however, triangles are used for this purpose when necessary.

To illustrate the construction of an algorithm marked graph, consider the problem of computing the output of a discrete linear, time invariant system given a sequence of inputs to the system. Let the system be described by the state equation

$$x(k) = Ax(k-1) + Bu(k)$$

and the output equation

$$y(k) = Cx(k)$$

,

where x is a p-vector, u is an m-vector, and y is an r-vector. The primitive operations are defined as matrix multiplication and vector addition, and the natural algorithm decomposition resulting from the state equation description is selected. The algorithm marked graph for this decomposed algorithm is shown in Figure 1.1. The initial marking indicates that initial condition data are available.

The algorithm marked graph is a useful tool for representing decomposed algorithms and for displaying data flow within an

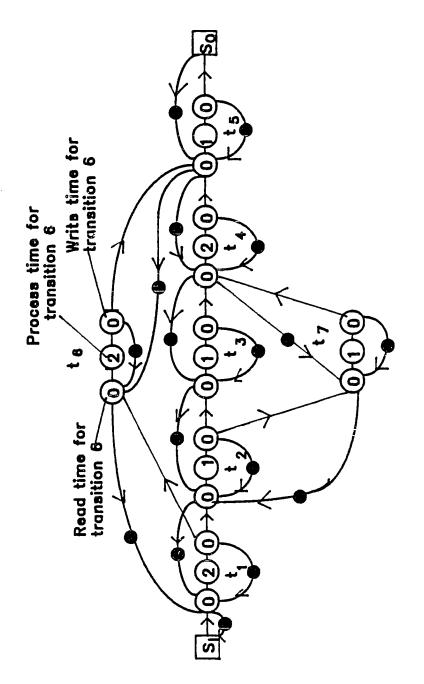

Figure 1.1. Algorithm marked graph for discrete system equation.

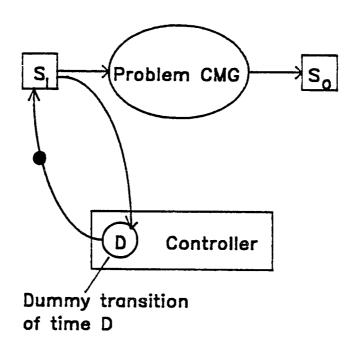

algorithm. However, the algorithm marked graph does not display procedures that a computing structure must manifest in order to perform the computing task. In addition, the issues of control, time performance, and resource management are not apparent in this graph. These important aspects of concurrent processing are included in the ATAMM model through the definition of two additional graphs. The node marked graph (NMG) is defined to model the execution of a primitive operation. The computational marked graph (CMG), obtained from the AMG and the NMG by a set of construction rules, integrates both the algorithm requirements and the computing environment requirements into a comprehensive graph model. These additional marked graphs are defined below.

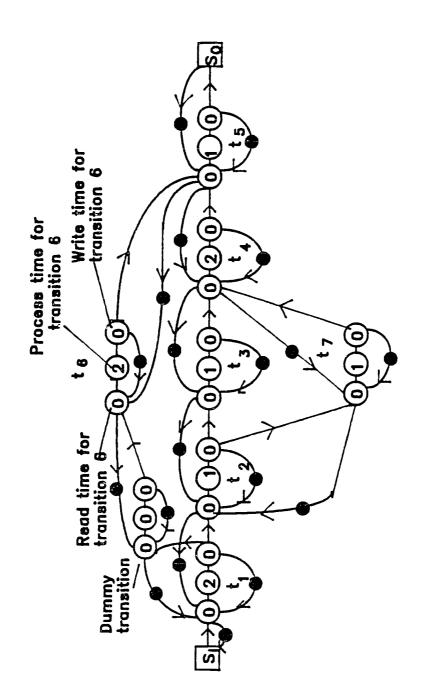

The node marked graph (NMG) is a Petri net representation of the performance of a primitive operation by a functional unit. Three primary activities: reading of input data from global memory, processing of input data to compute output data, and writing of output data to global memory, are represented as transitions (vertices) in the NMG. Data and control flow paths are represented as places (edges), and the presence of signals is notated by tokens marking appropriate edges. The conditions for firing the process and write transitions of the NMG are as defined for a general Petri net, while the read transition has one additional condition for firing. In addition to having a token present on each incoming signal edge, a functional unit must be available for assignment to the primitive operation before the read node can fire. Once assigned, the functional unit is used to implement the read, process, and write operations before being returned to a queue of available functional

units. The initial marking for an NMG consists of a single token in the Process Ready place. The NMG model in shown in Figure 1.2.

A computational marked graph (CMG) is constructed from the AMG and the NMG by the following rules:

- Source and sink nodes in the algorithm marked graph are represented by source and sink nodes in the CMG.

- 2) Nodes corresponding to primitive operations in the algorithm marked graph are represented by NMG's in the CMG.

- 3) Edges in the algorithm marked graph are represented by edge pairs, one forward directed for data flow and one backward directed for control flow, in the CMG.

The forward directed edge goes from predecessor write transition to successor read or sink transition. This forward edge is also shown as part of the NMG where it is the OF and IF edge of the predecessor and successor respectively. The backward directed edge goes from successor read transition to predecessor read or source transition. This backward edge is also shown as part of the NMG where it is OE and IE edge of predecessor and successor respectively. The initial marking for the edge pair consists of a single token in the forward directed place if data are available, or a single token in the backward directed place if data are not available.

The play of the CMG proceeds according to the following graph rules:

A node is enabled when all incoming edges are marked with a token. An enabled node fires by encumbering one token from each incoming edge, delaying for some specified transition time, and then depositing one token on each outgoing edge.

# NMG EDGE LABELS

- IF Input Buffer Full

- IE Input Buffer Empty

- DR Data Read

- PC Process Complete

- PR Process Ready

- OE Output Buffer Empty

- OF Output Buffer Full

Figure 1.2. ATAMM node marked graph model.

- A source node and a sink node fire when enabled without regard for the availability of a functional unit.

- 3) A primitive operation is initiated when the read node of an NMG is enabled and a functional unit is available for assignment to the NMG. A functional unit remains assigned to an NMG until completion of the firing of the write node of the NMG.

In order to illustrate the construction of a computational marked graph, the CMG corresponding to the algorithm marked graph of Figure 1.1 is shown in Figure 1.3. The computational marked graph is useful because it clearly displays the data and control flow which must occur in any hardware implementation of the algorithm, and because it provides a hardware independent context in which to evaluate algorithm performance.

The complete ATAMM model consists of the algorithm marked graph, the node marked graph, and the computational marked graph. A pictorial display of this model is shown in Figure 1.4. ATAMM model characteristics are described in detail in the Appendix.

1.3 Objectives and Organization of Dissertation.

The behavior and performance for periodic execution of complex algorithms in the ATAMM data flow architecture is investigated in this dissertation. The problem domain consists of large-grain, decision-free algorithms. The major research objectives are threefold. First, a performance model is established. Second, rules for transformation of algorithms for performance enhancement and reduction of computing element requirements are identified. Third,

Figure 1.3. ATAMM computational marked graph model for discrete system equation.

Figure 1.4. ATAMM model components.

operating strategies are developed for optimum time performance and for sub-optimum time performance under limited availability of computing elements.

The dissertation is organized in five chapters and an appendix. In the Appendix ATAMM model characteristics, some of which are used in this dissertation, are described in detail. Definitions of the computing environment, performance measures, and evaluation of performance bounds and resource requirements are presented in Chapter Two. In Chapter Three, algorithm transformations for improving performance, and methods for enforcing desired resource envelope and inducing structural changes in algorithm marked graph are described. Definition, characteristics, and design procedure of operating point along with simulation and experimental results are presented in Chapter Four. Finally conclusions from this research and future research topics are presented in Chapter Five.

#### CHAPTER TWO

#### PERFORMANCE MODEL

#### 2.0 Introduction

A performance model for the ATAMM (Algorithm To Architecture Mapping Model) data flow architecture is described in this chapter. The objective is to determine computing speed, throughput capacity and resource (computing element) need for implementing decision-free large-grain algorithms on the ATAMM data flow architecture. The computing environment and performance measures are defined in Section 2.1. In Section 2.2, characteristics of marked graphs, which are needed to establish the performance model, are described. Graph theoretic lower bounds for the time performance of algorithm marked graphs operated in the ATAMM data flow architecture are established in Section 2.3. Resource needs are predicted and performance bounds in the presence of resource limitations are evaluated in Section 2.4. A summary of the chapter is presented in Section 2.5.

#### 2.1 Performance Measures

The importance of the ATAMM model is that it provides a hardware independent context in which to investigate the performance of decomposed algorithms as long as the architecture obeys the rules of CMG. It is assumed that a decomposed algorithm is implemented in a ATAMM data flow architecture containing R identical resources or

functional units. Each functional unit is capable of performing any of the primitive operations whose sequence defines the decomposition. The tokens on the CMG indicate the data and control flow that must occur in any hardware implementation of the algorithm. A task is a sequence of computations as described by the AMG. The computational task is applied on all input data from the source node. Task output occurs when a corresponding output data token is deposited at the output sink node. A task is completed when all computing associated with the task is completed. It should be noted that task output and task completion do not always coincide. In many iterative signal processing algorithms, computing to generate initial conditions for the next iteration often occurs after the output has been calculated. Task completion is usually indicated in the AMG or the CMG by the return of the graph to some steady state initial marking. To use the output of an algorithm for control and signal processing applications, it is assumed that the task is repeated periodically with new input data sets (data packets). New data sets are injected as input tokens from the input source node at a finite interval of time so that computing time and resource needs are identical for all data sets. Included in this problem class are iterative algorithms where the present task requires input data from previous task calculations.

Computational concurrency occurs in two ways. First, several transitions of the task on individual data set may be performed simultaneously. We have referred to this type of concurrency as parallel concurrency because it is the result of inherent parallelism in the algorithm. Parallel concurrency has a direct effect on task computing speed. It is limited by the number of transitions that can

be performed simultaneously for the given task and by the number of functional units available to perform the transitions. Second, transitions of the task belonging to different data sets can be performed simultaneously in the computing system. This type of concurrency is referred to by us as pipeline concurrency because the task is repeated for successive data sets, like a pipeline. This type of concurrency has a direct effect on throughput capacity. It is limited by the capacity of the graph to accommodate additional data sets and by the number of functional units available to implement the algorithm periodically.

Three performance measures, TBIO, TT, and TBO, are now defined for concurrent processing of complex algorithms in ATAMM data flow architectures. TBIO and TT are indicators of computing speed for a task and thus reflect the degree of parallel concurrency. TBO is a measure of time interval between task outputs. The inverse of TBO indicates throughput, and thus reflects the degree of pipeline concurrency.

<u>Definition 2.1: TBIO.</u> The performance measure TBIO (time between input and output) is the elapsed computing time between a task input and the corresponding task output.

<u>Definition 2.2: TT</u>. The performance measure TT (task time) is the elapsed computing time between a task input and the completion of all computation associated with that task input.

<u>Definition 2.3: TBO.</u> The performance measure TBO (time between outputs) is the elapsed computing time between successive task outputs when the graph is operating periodically at steady state.

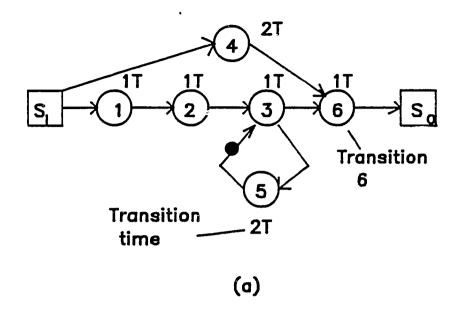

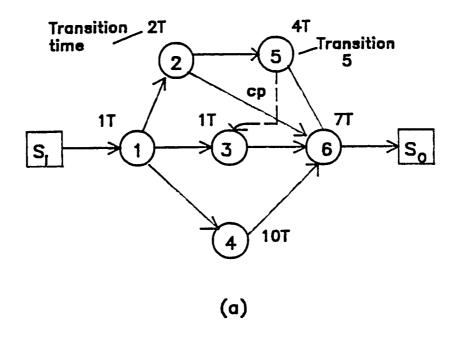

To illustrate, an algorithm marked graph for an aircraft flight simulation is shown in Figure 2.1.  $S_{

m I}$  is the input source

representing flight plan data.  $S_{O}$  is the output sink representing moving map and flight instruments data. Transitions of the graph represent activities. Places represent data dependency or precedence relation. Tokens on places are initial tokens representing initial condition data. As an example, transition 3 represents inertial navigation computation and requires ten time units for processing. Time units associated with transitions are relative and are measured with respect to a reference. Transition 7 (zero processing time) is used to combine outputs of the coordinate transform computation (moving map) and the auto-pilot computation (control for flight instruments). TBIO is the time to produce the outputs in  $S_{\overline{O}}$  for a flight plan data. TT is the time to finish all processing for a task input. TBIO and TT need not be the same for all problems although they are related. TBO is the time between arrival of successive output tokens in the output data sink when the algorithm is executed periodically at steady state.

#### 2.2 Marked Graph Characteristics

Marked graphs, a class of Petri nets, are used as a device for expressing the ATAMM. A marked graph is viewed as a directed graph where the vertices are the transitions and the edges are directed places. In this section, concept of path and circuit for the marked graph is developed. Only directed paths and circuits are of interest to this dissertation. If not mentioned, a path or a circuit of a marked graph should always be understood to be a directed path or a directed circuit respectively. Some properties of the marked graph

Figure 2.1. An algorithm for flight simulation plan.

which are needed to establish a performance model are stated. Also, circuits of the CMG are classified. Let  $t_i$  and  $p_i$  denote transition i and place i respectively.

<u>Definition 2.4: Directed Path.</u> A directed path in a marked graph is a finite alternating sequence of distinct transitions and distinct directed places with the following property. The sequence begins and ends with transitions and every place originates from the immediate predecessor transition and ends on the immediate successor transition in that sequence.

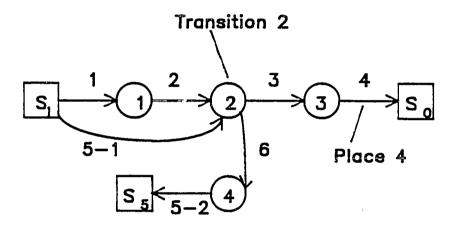

To illustrate, the sequence  $S_1$ ,  $p_1$ ,  $t_1$ ,  $p_2$ ,  $t_2$ ,  $p_3$ ,  $t_3$ ,  $p_4$ , and  $S_0$  is a directed path in Figure 1.1. But the sequence  $t_1$ ,  $p_2$ ,  $t_2$ ,  $p_6$ ,  $t_4$ ,  $p_5$ ,  $t_2$ ,  $p_3$ , and  $t_3$  is not a directed path in Figure 1.1 as transition 2 is repeated twice in that sequence.

<u>Definition 2.5: Directed Circuit</u>. A directed circuit in a marked graph is the same as a directed path except that beginning and end transitions are the same in a directed circuit.

To illustrate, the sequence  $t_2$ ,  $p_6$ ,  $t_4$ ,  $p_5$  and  $t_2$  is a directed circuit in Figure 1.1.

<u>Definition 2.6: Parallel Paths.</u> Parallel paths are directed paths which have identical beginning and ending transitions; however, all other transitions and places on all directed paths are distinct.

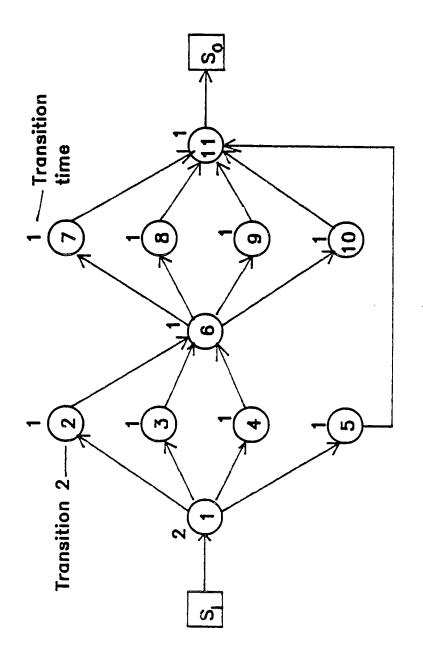

In Figure 2.2 the sequence  $t_1$ ,  $p_2$ ,  $t_2$ ,  $p_3$ ,  $t_3$ ,  $p_4$ ,  $t_4$ ,  $p_5$ , and  $t_5$  and the sequence  $t_1$ ,  $p_6$ ,  $t_6$ ,  $p_8$ , and  $t_5$  are parallel paths.

Definition 2.7: Group Of Paths. Group of paths are a finite number of directed paths from a marked graph.

To illustrate, the sequences  $t_2$ ,  $p_7$ ,  $t_7$ ,  $p_9$ ,  $t_4$  and  $t_1$ ,  $p_6$ ,  $t_6$ ,  $p_8$ ,  $t_5$  form a group of paths in Figure 2.2.

Figure 2.2. Example algorithm marked graph.

<u>Definition 2.8: Path Length</u>. The length of a directed path in a marked graph is defined to be the summation of all the times for transitions in that directed path.

<u>Definition 2.9: Circuit Length</u>. The length of a directed circuit in a marked graph is defined to be the summation of all the times for transitions in that directed circuit.

<u>Definition 2.10: Critical Path.</u> The critical path among a group of paths is the one which has the highest path length.

This definition of critical path is identical to the one used in task scheduling [14, 15] and project management [16, 17].

To illustrate, let T(i) stand for the time of the  $i^{th}$  transition. In Figure 1.1, let T(1) = 4, T(2) = 1, T(3) = 5 and T(4) = 6,  $T(S_I) = 0$  and  $T(S_0) = 0$ . Then, the directed circuit  $t_2$ ,  $p_6$ ,  $t_4$ ,  $p_5$ , and  $t_2$  has length 7. The directed path used to illustrate Definition 2.4 has length 10. The directed path  $S_I$ ,  $p_1$ ,  $t_1$ ,  $p_2$ ,  $t_2$ ,  $p_6$ , and  $t_4$  has length 11. These two directed paths form a group of paths. In that group of paths, the directed path from  $S_I$  to  $t_4$  is the critical path. It is to be noted that there can be more than one critical path in a group of paths.

<u>Property 2.1</u>. The critical path length of a group of paths is the lowest possible time to move tokens from the input of the beginning transition to the output of the end transition on all directed paths of that group.

This is a property of the critical path known from critical-path scheduling [14] and project management [17]. In the context of a marked graph, as the token has to move through all the transitions of the directed path in order to reach the output of the end transition

from the input of the beginning transition, the minimum time required is the length of the directed path. Considering all the directed paths of the group, the lowest possible time to move tokens on all directed paths from the input of the beginning transition to the output of the end transition is the critical path length.

<u>Property 2.2.</u> With unlimited resources, tokens always take time equal to critical path length to complete the move from the input of the beginning transition to the output of the end transition on all directed paths of the group.

This is another property of the critical path known from task scheduling [14] and project management [17]. In the context of the marked graph, with unlimited resources, a transition can always be fired as soon as it is enabled by input data. Therefore, the lowest possible time can actually be achieved. Hence, the critical path length is the time to move all tokens from the input of the beginning transition to the output of the end transition.

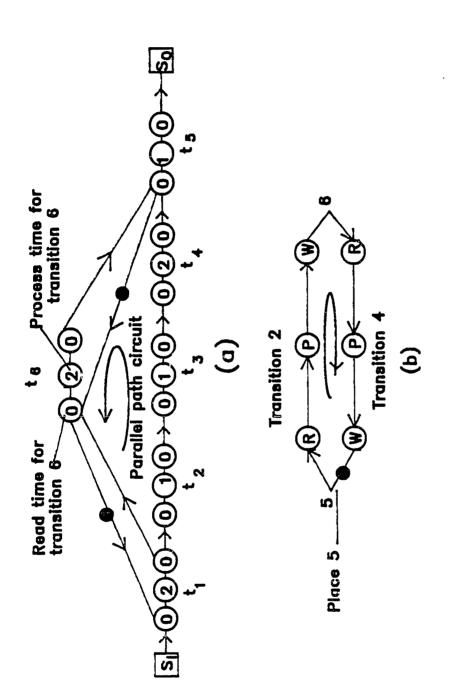

Directed circuits are created in the computational marked graph in four different ways. They are node, process, recursion and parallel path circuits. Formal definitions of each kind of directed circuit are presented below along with examples.

<u>Definition 2.11: Node Circuit</u>. This is a directed circuit in the CMG which is the only internal directed circuit of an NMG.

To illustrate, the sequence  $t_R$ ,  $p_{DR}$ ,  $t_P$ ,  $p_{PC}$ ,  $t_W$ ,  $p_{PR}$ , and  $t_R$  is a node circuit in the ATAMM node marked graph model of Figure 1.2. One such node circuit in the CMG of Figure 1.3 is shown in Figure 2.3(a). This is the node circuit of transition 1 in the AMG of Figure 1.1. Node circuits always have one token, as described in the Appendix.

Figure 2.3. Example of node and process circuits.

Definition 2.12: Process Circuit. This is a directed circuit in the CMG which is formed each time an NMG or source is linked to another NMG or sink. The backward directed place from successor read or sink transition to predecessor read or source transition, along with forward directed places from predecessor to successor create the process circuit.

A process circuit of Figure 1.3 is shown in Figure 2.3(b). This process circuit is formed when node marked graphs of transition 2 and 3 are linked. Process circuits always have one token as described in the Appendix.

<u>Definition 2.13: Parallel Path Circuit</u>. This is a directed circuit in the CMG which is created by any two parallel paths in the AMG. The circuit is formed by the forward directed places through the NMG'S of one directed path and backward directed places from the successor read to the predecessor read transition from the NMG's of the other directed path.

To illustrate, the CMG of Figure 2.2 is shown in Figure 2.4. The parallel paths of the AMG form parallel path circuits in the CMG. One such parallel path circuit is shown in Figure 2.5(a). This circuit is created by two parallel paths in the Figure 2.2 between transition 1 and transition 5.

<u>Definition 2.14: Recursion Circuit</u>. This is a circuit in the CMG which is created due to a directed circuit in the algorithm marked graph.

To illustrate, the recursion circuit of Figure 1.3 is shown in Figure 2.5(b). The directed circuit  $t_2$ ,  $p_6$ ,  $t_4$ ,  $p_5$ , and  $t_2$  in Figure 1.1 translates itself into a recursion circuit in the CMG of

Figure 2.4. Computational marked graph for the AMG.

A parallel path circuit from the CMG of Figure 2.4. A recursion circuit from Figure 1.3. Example of recursion and parallel path circuits. <u>D</u> Figure 2.5.

Figure 1.3. Directed circuits are created in the AMG mainly due to a recursion in computation and hence the corresponding circuits in the CMG are called recursion circuits.

# 2.3 Graph Theoretic Performance Bounds

The process of algorithm decomposition imposes bounds on the amount of parallel concurrency and pipeline concurrency possible in a given problem. If sufficient computing resources are available, operation at these bounds can be achieved. In this section, graph theoretic lower bounds on three performance measures are established for decomposed algorithms to be operated in ATAMM data flow architectures. These lower bounds are only a function of the algorithm marked graph and the node marked graph. Therefore, performance cannot be improved beyond these bounds by increasing the number of resources. The remainder of this section is devoted to developing lower bounds for these performance measures.

Let G denote an algorithm marked graph representing a decomposed algorithm. The lower bound for TBIO is the shortest time required for a data token from the data input source to propagate through the graph to the data output sink. Similarly the lower bound for TT is the shortest time required to complete all computing activity initiated by the injection of a data from the input source. These shortest times are the actual performance times when only a single data set is present in the graph during any time interval (no pipeline concurrency), and as many computing resources as are required are available (maximum parallel concurrency). Under these operating conditions, lower bounds for TBIO and TT are calculated by identifying

certain longest paths in a graph obtained from the algorithm marked graph. This new graph, called the modified algorithm marked graph  $G_{M}$ , is defined and then used to determine lower bounds for TBIO and TT.

<u>Definition 2.15: Modified Algorithm Marked Graph.</u> Let  $p_i$  be a place of G, directed from transition  $t_r$  to transition  $t_s$ , which contains a token of the initial marking. The modified algorithm marked graph  $G_M$  is obtained from the graph G by the following construction rules:

- 1) Place p; is deleted from G.

- 2) A new place,  $p_{i1}$ , directed from the data input source to transition  $t_s$ , is added to G.

- 3) A new output sink S<sub>i</sub> different from all other output sinks, and a new place p<sub>i2</sub>, directed from transition t<sub>r</sub> to S<sub>i</sub>, are both added to G.

- 4) The above rules are repeated for each place of G containing a token of the initial marking.

Example: The recursion problem of Figure 1.1 is used to generate a modified algorithm marked graph as shown in Figure 2.6. Only place 5 from transition 4 to 2 has an initial token in the algorithm marked graph of Figure 1.1. According to rule 1, place 5 is deleted. A new place 5-1 is inserted from data input source to transition 2 by rule 2. Rule 3 is then used to generate a new output sink  $(S_5)$  and a new place 5-2 as shown in Figure 2.6. As there are no more places with initial tokens, this completes the procedure to generate a modified algorithm marked graph.

Figure 2.6. Modified algorithm marked graph for Figure 1.1.

Theorem 2.1: Graph Theoretic Lower Bound for TBIO. Let  $P_i$  be the  $i^{th}$  directed path in  $G_M$  from the data input source to the data output sink, and let  $T(P_i)$  denote the sum of transition times for transitions contained in  $P_i$ . Then,

$$TBIO_{LB} = Max \{T(P_i)\},\$$

where the maximum is taken over all paths  $P_i$  between the data input source and the data output sink in graph  $G_M$ .

Proof.  $T(P_i)$  is the length of path  $P_i$ ; therefore, Max  $\{T(P_i)\}$  is the length of the critical path from the data input source to the data output sink. From the properties of the critical path [14, 17],  $TBIO_{IB} = Max \{T(P_i)\}$ . This completes the proof.

Theorem 2.2: Lower Bound for TT. Let  $P_i$  be the  $i^{th}$  directed path in  $G_M$  from the data input source to any output sink, and let  $T(P_i)$  denote the sum of transition times of transitions contained in  $P_i$ . Then,

$$TT_{LB} = Max \{T(P_i)\},\$$

where the maximum is taken over all paths  $P_i$  in graph  $G_M$ . Proof. By the construction rules for graph  $G_M$ , a task is initiated with an input from the data input source, and is completed when all output sinks have accepted tokens. Therefore, TT is the time which elapses from injection of input tokens to the arrival of a token at the last fired output sink. Let  $T(P_j) = Max \ \{T(P_i)\}$ , among all  $P_i$  in  $G_M$ .  $P_j$  is the longest path among all paths from the

data input source  $S_I$  to any output sink. Therefore,  $P_j$  is the critical path among all paths from the data input source to any output sink. Hence, by the properties of the critical path [14, 17],  $TT_{IB} = T(P_j) = Max(T(P_i))$ , where the maximum is over all paths  $P_i$  in  $G_M$ . This completes the proof.

To illustrate the application of Theorem 2.1 and Theorem 2.2, TBIO $_{LB}$  and  $TT_{LB}$  are computed for the algorithm marked graph shown in Figure 1.1. For this example, the following transition times are assumed: T(1) = 4, T(2) = 1, T(3) = 5, and T(4) = 6. The modified algorithm marked graph corresponding to Figure 1.1 is shown in Figure 2.6. The modified algorithm marked graph contains two paths directed from the data input source  $S_{I}$  to the data output sink  $S_{O}$ . Path  $P_{1}$  is the sequence  $t_{1}$ ,  $p_{2}$ ,  $t_{2}$ ,  $p_{3}$ , and  $t_{3}$  with  $T(P_{1}) = 10$ . Path  $P_{2}$  is the sequence  $t_{2}$ ,  $p_{3}$ , and  $t_{3}$  with  $T(P_{2}) = 6$ . Since  $T(P_{1}) > T(P_{2})$ , path  $P_{1}$  determines the lower bound for TBIO and  $TBIO_{LB} = 10$ . The modified algorithm marked graph contains two additional directed paths from the data input source  $S_{I}$  to the output sink  $S_{5}$ . Path  $P_{3}$  is the sequence  $t_{1}$ ,  $p_{2}$ ,  $t_{2}$ ,  $p_{6}$ , and  $t_{4}$  with  $T(P_{3}) = 11$ . Path  $P_{4}$  is the sequence  $t_{2}$ ,  $p_{6}$ , and  $t_{4}$  with  $T(P_{4}) = 7$ . Since  $T(P_{3})$  is the highest, path  $P_{3}$  determines the lower bound for TT and  $TT_{LB} = 11$ .

Next a lower bound for the performance measure TBO may be determined. Let G be an algorithm marked graph representing a decomposed algorithm. It is assumed that the operating conditions for G are set to maximize pipeline concurrency. That is, data tokens are continuously available at the data input source, and as many computing resources as needed can be called to perform primitive operations. The graph G is executed periodically and TBO<sub>LB</sub> is the shortest time possible between successive outputs.

Theorem 2.3: Graph Theoretic Lower Bound for TBO. Let  $G_C$  be a computational marked graph and let  $C_i$  be the  $i^{th}$  directed circuit in  $G_C$ . The notation  $T(C_i)$  denotes the sum of transition times of transitions contained in  $C_i$ , and  $M(C_i)$  denotes the number of tokens contained in  $C_i$ . Then,

$$TBO_{LB} = Max \{T(C_i) / M(C_i)\},$$

where the maximum is taken over all directed circuits in G. The circuits which determine  $TBO_{\mbox{\footnotesize{IB}}}$  will be called critical circuits of the CMG.

Proof. Without loss of generality, let  $t_f$  be the output transition in  $G_C$  so that an output is produced each time  $t_f$  completes firing.  $TBO_{LB}$  is then the minimum firing period of transition  $t_f$ . By consistency property of the Appendix,  $G_C$  is consistent so that all transitions of  $G_C$  fire periodically with minimum period  $TBO_{LB}$ . It is shown in [18] (pp. 58-60) that the minimum firing period of each transition of a marked graph is given by Max  $\{T(C_i)/M(C_i)_i\}$ , where the maximum is taken over all directed circuits  $C_i$  in G. Therefore, the theorem follows.

The algorithm marked graph shown in Figure 1.3 is used to illustrate Theorem 2.3. The CMG contains many directed circuits. However, the recursion circuit which contains all NMG nodes of transitions 2 and 4 has only one token and maximizes the ratio  $T(C_i)/M(C_i)$ . Therefore, the shortest time possible between successive outputs in this graph is  $TBO_{LB}=7$ .

# 2.4 Resource Requirements

The performance bounds of the last section assume availability of a resource for each transition to fire when enabled. Therefore, graph theoretic performance bounds are absolute bounds provided sufficient resources are available to meet the firing requirements. However, for insufficient resources, performance cannot reach the graph-theoretic bounds. The number of resources (R) of an ATAMM data flow architecture imposes bounds on performance of an algorithm marked graph. In this section, characteristics of resource usage, maximum resource requirement, and resource imposed performance bounds are investigated. Formal definitions of computation, graph execution, and resource requirements are stated. Definitions and results are illustrated with examples.

<u>Definition 2.16: TC.</u> Total Computation (TC) is the sum of all transition times of an algorithm marked graph.

<u>Definition 2.17: TFC.</u> Total Forward Computation (TFC) is the sum of all transition times that appear in the forward paths from the data input source to the data output sink of the modified algorithm marked graph.

<u>Definition 2.18: TBC.</u> Total Backward Computation (TBC) is the sum of all transition times that do not appear in the forward paths from the data input source to the data output sink of the modified algorithm marked graph.

Lemma 2.1. TC is the sum of TFC and TBC of an algorithm marked graph. Proof. With the notation of Definitions 2.16, 2.17, and 2.18, transitions which constitute TFC and TBC are mutually exclusive and collectively exhaustive of all transitions of the algorithm marked

graph. Hence, the sum of all transition times of the algorithm marked graph equals the sum of transition times for both transitions on the forward paths and not on the forward paths from the data input source to the data output sink of the modified algorithm marked graph. Therefore, TC equals the sum of TFC and TBC. This completes the proof.

<u>Definition 2.19: Computer Time</u>. A unit of Computer Time is defined to indicate one functional unit available over one unit of time.

To illustrate, if two functional units are used for three units of time, six units of computer time are used.

<u>Definition 2.20: Computing Capacity (T)</u>. Computing Capacity (CC) is the total available units of computer time over an interval of time T.

To illustrate, for a time interval of T, the computing capacity of an ATAMM data flow architecture with R functional units is given by R \* T. Thus CC (T) = R \* T.

<u>Definition 2.21: Computing Effort (T)</u>. Computing Effort (CE) is the total used units of computer time over an interval of time T.

To illustrate, for a time interval of T and R functional units, let  $T_i$  be the number of time units the  $i^{th}$  functional unit is used. Then  $T_i * 1 = T_i$  units of computer time is the computing effort due to the  $i^{th}$  resource in interval T. Thus the computing effort due to R resources is given by

CE (T) =

$$\sum_{i=1}^{R} (T_i)$$

units of computer time.

Lemma 2.2. For any number of functional units and any interval of time, computing effort is always less than, or equal to, computing capacity.

Proof. With the notation of definitions 2.20 and 2.21,

$$CC(T) = R * T$$

CE (T) =

$$\sum_{i=1}^{R} (T_i)$$

,

where  $T_i$  is the number of time units the  $i^{th}$  functional unit was used in time interval T. So  $T_i$  cannot be more than T [15]. Hence,  $CE(T) \leq CC(T)$ . This completes the proof.

<u>Definition 2.22: Resource Utilization (T)</u>. The Resource Utilization (RU) of functional units over a time interval T is given by the ratio of computing effort to computing capacity over that time interval. Thus,

$$RU(T) = CE(T) / CC(T)$$

.

Lemma 2.3. Resource Utilization (RU) over a time interval T is always greater than, or equal to, zero but less than, or equal to, 1. Proof. By definition, resource utilization is a ratio of computing effort to capacity. With the notation of Definitions 2.20 and 2.21,  $T_{\dot{1}} \geq 0 \ , \ T > 0. \ \ \text{So CE}(T) \geq 0. \ \ \text{CC}(T) = R * T > 0 \ \text{as the ATAMM data}$  flow architectures must have at least one functional unit. So RU(T)  $\geq$  0. Also as CE (T)  $\leq$  CC (T), RU (T)  $\leq$  1. This completes the proof.

<u>Definition 2.23: Total Computing Effort (TCE)</u>. TCE is defined to be the computing effort required to execute once all transitions of an algorithm marked graph.

Lemma 2.4. TCE equals TC units of computer time.

Proof. With the notation of Definitions 2.16, 2.21, and 2.23,

$$TCE = CE(T) = \sum_{i=1}^{R} (T_i)$$

$$= TC$$

units of computer time as total computation to execute all transitions of the AMG once is TC. This completes the proof.

<u>Definition 2.24: Total Forward Computing Effort (TFCE)</u>. TFCE is defined to be the computing effort required to execute once all transitions on forward paths from the data input source to the data output sink of the modified algorithm marked graph.

<u>Lemma 2.5</u>. TFCE equals TFC units of computer time.

Proof. The proof is similar to that of Lemma 2.4.

With the above definitions and lemmas regarding computation of a task, it is now intended to establish resource imposed bounds on the computing time of a task. The following two theorems state the minimum possible value of TT and TBIO for an ATAMM data flow architecture of R resources.

Theorem 2.4: Minimum TT for R Resources. The minimum value of TT for an algorithm marked graph operated with R resources is always greater than, or equal to, TCE / R.

Proof. TT is the computing time to complete all computation associated with a task input. For a time interval of TT, the

computing capacity of R resources is R \* TT. The total computation for any task input is the execution of all transitions of the algorithm marked graph once and hence, equals TC. The corresponding computing effort is TCE. By Lemma 2.2, R \* TT  $\geq$  TCE, or TT  $\geq$  TCE / R [19]. This completes the proof.

Theorem 2.5: Minimum TBIO for R Resources. The minimum value of TBIO for an algorithm marked graph operated with R resources is always greater than, or equal to, TFCE / R.

Proof. TBIO is the computing time to generate data output for a task. For a time interval of TBIO, the computing capacity of R resources is given by R \* TBIO. In order to generate data output, all transitions on all the forward paths from the data input source to the data output sink in the modified algorithm marked graph must be executed once. The computation involved is TFC and the corresponding computing effort is TFCE. By Lemma 2.2, R \* TBIO  $\geq$  TFCE [19], or TBIO  $\geq$  TFCE / R. This completes the proof.

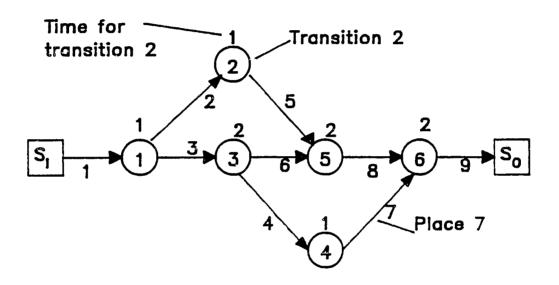

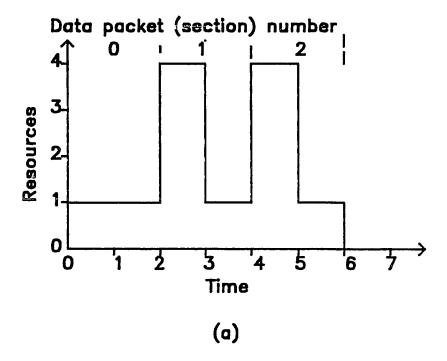

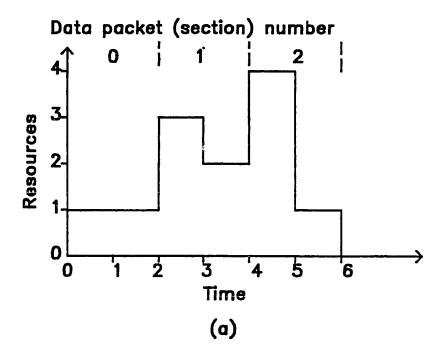

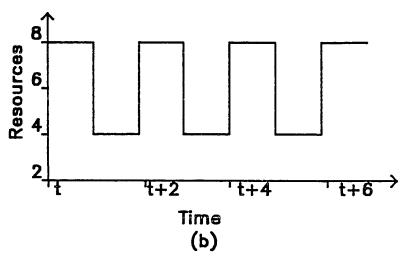

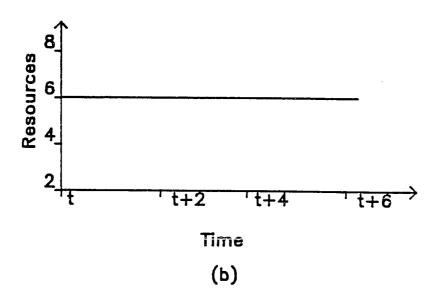

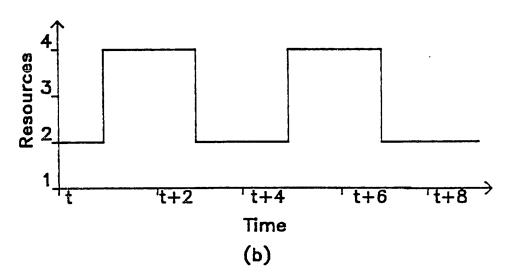

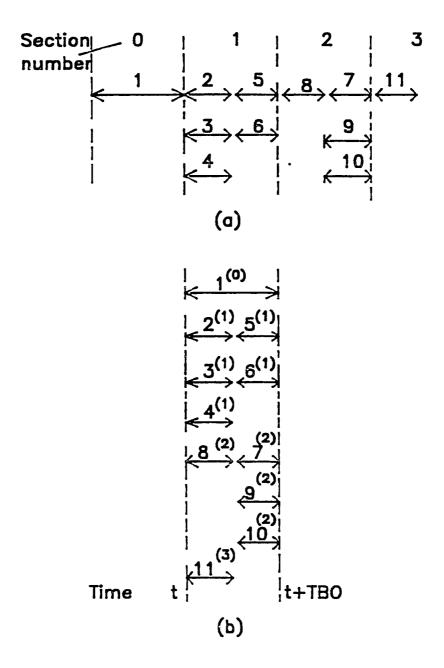

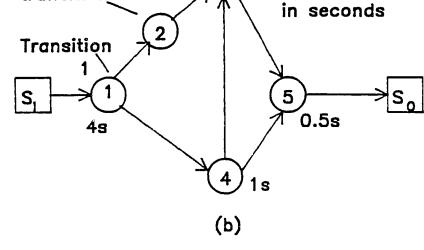

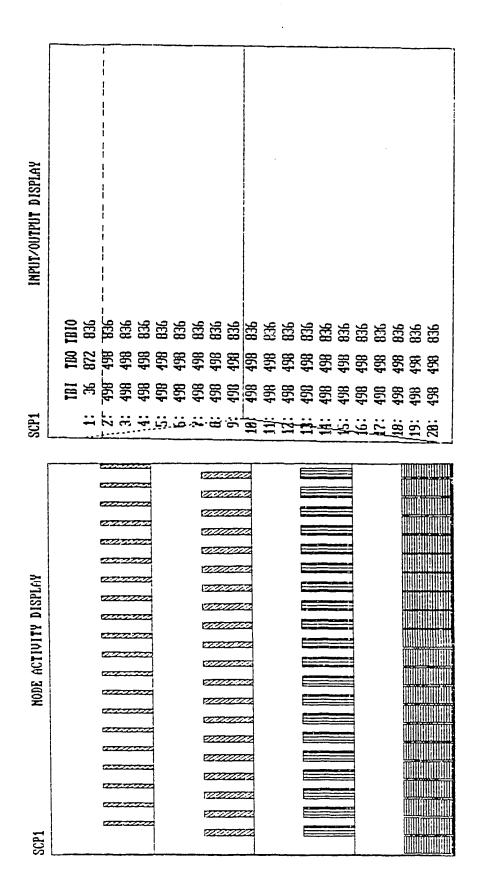

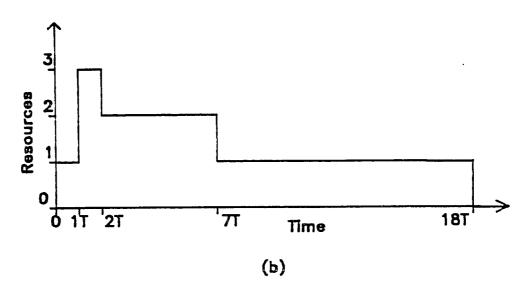

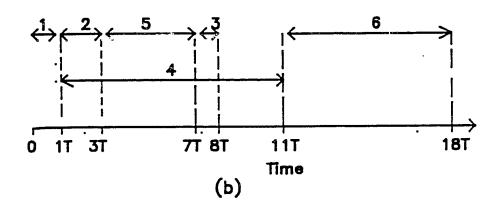

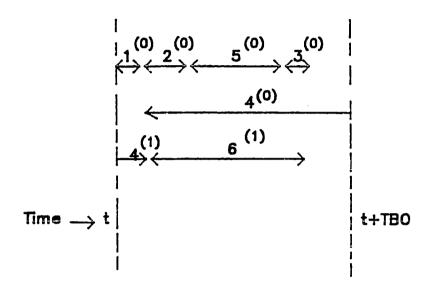

Two graph execution features (GPST and TGP) and two hardware usage measures (REST and TRE) are now defined for predicting resource requirements. GPST describes the execution of transitions of the algorithm marked graph for a single data packet. REST is the description of the resource usage to process one data packet. TGP and TRE are the graph execution description and resource usage envelope when the algorithm marked graph is executed repeatedly and periodically.

<u>Definition 2.25: GPST.</u> GPST (graph play for a single task input) is a drawing depicting beginning, duration, and end of execution for each transition of the task when operated for a single data packet.

<u>Definition 2.26: TGP.</u> TGP (total graph play) is a drawing depicting beginning, duration, and end of execution for each transition of each task input at steady state when the AMG is executed periodically with an input data injection interval of TBO.

<u>Definition 2.27: REST.</u> REST (resource envelope for a single task input) is an envelope of resource usage by a single data packet between the time of task input and the completion of all computation associated with that task.

<u>Definition 2.28: TRE.</u> TRE (total resource envelope) is an envelope of resource usage to execute the graph at steady state with input period TBO.

Definition 2.29: Construction of GPST and REST. GPST and REST are generated by firing every transition in the algorithm marked graph at the earliest possible moment assuming unlimited resources and a single task input. Graph play is generated by depicting execution of all transitions in every time interval. Symbols (<, >) are used to show the beginning and the end of execution for a transition respectively. The resource usage envelope is obtained by counting the number of computing resources used during each time interval.

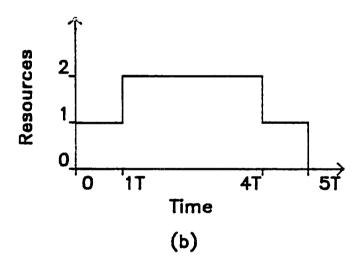

Example. Consider the algorithm marked graph of Figure 2.7.

Transitions 1, 2, and 4 have duration of one time unit. Transitions 3, 5, and 6 have duration of two time units. The graph is played according to Definition 2.29 and the GPST is shown in Figure 2.8(a). The need for resources is the same as the number of active transitions in each time interval. The REST is computed by counting the number of resources used in each time interval and is shown in Figure 2.8(b).

Figure 2.7. Algorithm marked graph for illustration of GPST and REST.

Figure 2.8. (a) GPST. (b) REST.

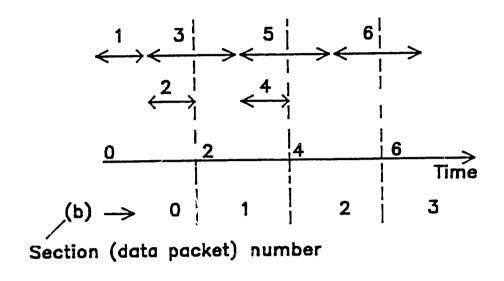

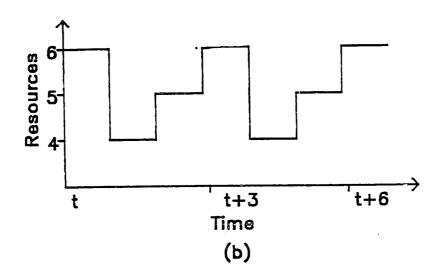

Now suppose the algorithm is executed periodically. Assume that the input data injection interval is long enough so that every data packet executes the graph as the GPST and needs resources over the task time as given by the REST. As a result, the algorithm is executed with a input period equal to output period TBO. The total resource envelope (TRE) is to be determined then by adding the resource needs of the concurrently processed data packets. The total graph play (TGP) is generated by drawing the execution of transitions from all the concurrently processed data packets. It is shown in the following two theorems that TRE and TGP are periodic with period TBO. If REST and GPST are divided from the beginning in sections of TBO time units, these sections are shown to be the contributions from the consecutive concurrent data packets towards a period of TRE and TGP. As an example, GPST and REST of Figure 2.8, are divided in sections of TBO = 2 time units. Section as well as data packet numbers are represented by the integer variable b. To illustrate, data packet 2 has been injected two time units before data packet 1. Moreover, transition 3, 2 for data packet 0, transition 5, 4 for data packet 2 and transition 6 for data packet 3 are executed concurrently at steady state requiring a total of five resources.

Theorem 2.6. When the algorithm marked graph is operated periodically for input period TBO with all data packets requiring resource envelopes identical to REST, the total resource envelope at steady state is periodic with period TBO and one period of TRE is generated by the summation of sections of REST of width TBO as follows.

Let REST (x) represent the resource envelope for a single task input where REST (x) = 0 for  $x \ge TT$ . Let the origin of time axis (t)

at steady state be the injection of a data packet. Let TRE (t) be the value of total resource requirement at time t. Let b represent the concurrently processed data packets at time t. A period of TRE(t) is then given by

TRE (t) =

$$\Sigma$$

REST (t + b \* TBO),

b

where

$$0 \le t < TBO$$

$0 \le b < [TT / TBO]$ .

Proof. By the rules of operation, data packets are injected and outputs are generated at the interval of TBO at steady state. Consider three consecutive data packets P, Q, and R injected at t = K \* TBO, (K+1) \* TBO and (K+2) \* TBO respectively, where K is a positive integer. Let d be a time unit in which the total resource requirement is desired. Let s denote the time between d and time for the last data packet injection. Suppose d is a time between the injection of data packets P and Q. Thus  $K * TBO \le t < (K+1) * TBO$ , and s = t - (K \* TBO). TRE(t) in this interval is made of REST's due to data packet P and previous data packets whose computations are completed after P has started. As all data packets have resource envelope identical to REST of duration TT, any data packet which is injected TT or more time before P has no effect on TRE in this interval. Consequently, the total number of concurrently processed data sets creating TRE(t) in this interval is given by [TT / TBO].

Hence, let the range of b be  $0 \le b < [TT / TBO]$ ; b is an integer. TRE(t) for time interval between P and Q is then the summation of the resource requirements for these concurrently processed data packets. Let b = 0 identify task input P whose contribution to TRE (t) is REST (s). The data packet which has started TBO time units before P will contribute REST (s + TBO) and is identified by b = 1. In general, a data packet which is injected b \* TBO time units before P is identified by the data packet number b and contributes REST (s + b \* TBO) to TRE (t). Therefore, summing REST (s + b \* TBO) over the entire range of b for the concurrently processed data packets will give the corresponding TRE (t). The data packet corresponding to the largest b may contribute to TRE(t) for only a partial interval. As REST (x) = 0 for  $x \ge TT$ , REST (s + b \* TBO) properly represents the contribution due to the data packet corresponding to the largest b. Therefore, TRE (t) at d between P and Q is given by the following equation,

TRE (t) =

$$\Sigma$$

REST (s + b \* TBO)

b =  $\Sigma$  REST (t - K \* TBO + b \* TBO) (2.4.1)

where

$$K * TBO \le t < (K + 1) * TBO$$

$0 \le b < [TT/TBO].$

Now let d be a time unit t + TBO from the origin. As d now is a time unit between data packet injection Q and R, s = (t+TBO) - (K+1)\*TBO.

By similar arguments as before,

TRE (t + TBO) =

$$\Sigma$$

REST (s + b \* TBO)

b

=  $\Sigma$  REST {(t+TBO) - (K+1)\*TBO + b \* TBO}

b

=  $\Sigma$  REST (t - K\*TBO + b\*TBO)

b

= TRE (t),

from equation (2.4.1). Thus, TRE(t) is periodic with period TBO. Hence, it is sufficient to specify TRE(t) for one period only; let s = t, or K = 0. Modifying equation (2.4.1) we get,

$$TRE(t) = \Sigma REST (t + b * TBO)$$

where

$$0 \le t < TBO$$

$0 \le b < [TT/TBO].$

Thus, one period of TRE(t) is generated by the summation of the sections of REST (x) of width TBO, starting from x=0. The sections are identified by the corresponding value of b. This completes the proof.

Theorem 2.7. When the algorithm marked graph is operated periodically for input period TBO with all data packets executing the AMG as GPST, total graph play at steady state is periodic with period TBO and one

period of TGP is generated by the overlapping of sections of GPST of width TBO as follows.

Let GPST (x) represent the graph play for a single task input where  $0 \le x < TT$ . Let the origin of time axis (t) at steady state be the injection of a data packet. Let TGP (t) be the total graph play at time t. Let b represent the concurrently processed data packets at time t. A period of TGP (t) is then given by,

$$TGP(t) = \Sigma GPST (t + b * TBO)$$

where

Proof. The proof is similar to Theorem 2.6 with one exception.

Unlike REST, sections of GPST of width TBO represent portions of graph play for successive data packets which overlap to form TGP at steady state. Hence, instead of adding sections of GPST, one period of TGP should be constructed by overlapping sections of GPST with each section being identified separately by the value of b. If two values of b are i and i+1, it means data packet i+1 is injected TBO time units before data packet i. This completes the proof.

Example. One period of TGP and TRE is constructed for the AMG of Figure 2.7 according to Theorem 2.6 and 2.7 with an input period TBO of two time units. GPST and REST of Figure 2.8 are divided in sections of width two time units as shown in Figure 2.8 by the dotted

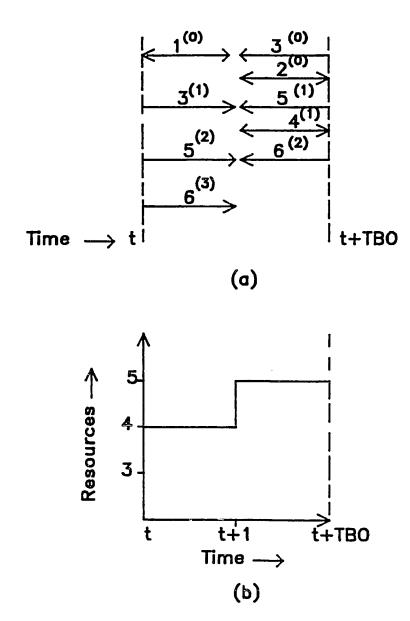

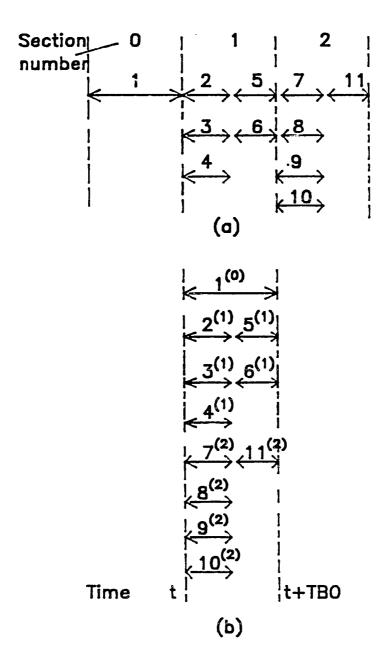

lines. Figure 2.9 shows the TGP and TRE for input period TBO of 2. Time t is any time when a new data packet is injected at steady state. In the TGP, the superscript of transitions indicate the value of b (data packet number). Data packet 1 is injected TBO time units before data packet 0.  $1^{(0)}$  and  $5^{(1)}$  represent the execution of transition 1 and 5 for the data packet 0 and 1 respectively in Figure 2.9(a). The TGP indicates that  $5^{(1)}$  begins after the completion of 1<sup>(0)</sup>. As in GPST, (<, >) arrow symbols indicate the beginning and end for execution of a transition respectively. In Figure 2.9(a), transitions  $3^{(0)}$ ,  $5^{(1)}$ , and  $6^{(2)}$  have started in this period but did not end. Similarly  $3^{(1)}$ ,  $5^{(2)}$ , and  $6^{(3)}$  have been completed in this period but did not start in it. The resource usage in the four sections of REST in order of increasing b are (1, 2), (1, 2), (1, 1), and (1, 0). One period of TRE is calculated by adding the four sections of REST. The total resource need in one period of TRE is (4, 5) as shown in Figure 2.9(b). It is to be noted that TRE could also have been calculated from TGP by counting the number of active transitions in each time interval.

Lemma 2.6. Computing effort in one period of TRE is TCE at steady state when the algorithm marked graph is operated periodically with an input period of TBO.

Proof. As the algorithm marked graph is operated periodically, computing effort in every period is the same. Computing effort in a period TBO of TRE will equal TCE as one task output is generated in every TBO time units. This completes the proof.

<u>Lemma 2.7.</u> Resource Utilization (RU) in one period (TBO) of TRE is given by  $\{TCE / (R * TBO)\}$ .

Figure 2.9. For TBO=2, (a) Total graph play. (b) Total resource envelope.

Proof. By Lemma 2.6, computing effort in one period (TBO) of TRE is TCE. Computing capacity in the TBO time interval is R \* TBO. By definition then, resource utilization is  $\{TCE / (R * TBO)\}$ . This completes the proof.

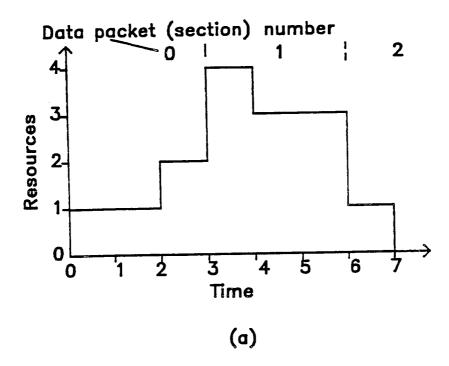

Example. Consider the REST as shown in Figure 2.10(a) with TT = 7, TC = 15 (ignore the dotted lines). The peak of REST is 4 which indicates that the ATAMM data flow architecture requires at least four functional units to process the task according to the REST in seven time units. Let TBO = 3. Tasks are initiated and outputs are generated at the interval of three time units with all having identical REST at steady state. TRE is calculated from Theorem 2.6. Dividing REST from the beginning in sections of width TBO, as in Figure 2.10(a), with the dotted lines, (1, 1, 2), (4, 3, 3), and (1, 0, 0) are the contributions of three overlapping task inputs to a period of TRE. Adding three sections of REST, a period of TRE is given by (6, 4, 5) and is shown in Figure 2.10(b). The computing effort in three time units of TRE is 15 as claimed by Lemma 2.6. Since the peak of TRE is 6, a minimum of six functional units is required to operate an algorithm marked graph with REST of Figure 2.10(a) and TBO = 3. By Lemma 2.7, resource utilization (RU) for six functional units is given by  $\{15 / (6 * 3)\} = .833$ .

With the help of above lemmas, the resource imposed bound on TBO is established in the following theorem.

Theorem 2.8: Minimum TBO for R Resources. The minimum value of TBO for an algorithm marked graph operated periodically with R resources is always greater than, or equal to, TCE / R.

Proof. By Theorem 2.6, the total resource envelope is periodic. By Lemma 2.6, the computing effort needed in period TBO is TCE. The

Figure 2.10. (a) Resource envelope for a single task input. (b) Total resource envelope for TBO=3.

computing capacity for time interval of TBO is R \* TBO. By Lemma 2.2, R \* TBO  $\geq$  TCE. Hence, TBO  $\geq$  TCE / R. This completes the proof.

Corollary 2.8.1. The minimum value of resource requirements (R) for a desired TBO is bounded by [TCE / TBO] when the graph is operating periodically at steady state.

Proof. As TBO  $\geq$  TCE / R, it follows that R  $\geq$  TCE / TBO. Since R is an integer, R  $\geq$  [TCE / TBO]. This completes the proof. Example. Consider the algorithm marked graph of Figure 1.1 and the corresponding modified algorithm marked graph of Figure 2.6. Let T(1) = 4, T(2) = 1, T(3) = 5, and T(4) = 6. The sum of all transition times are 16. Hence, TC = 16. TFC and TBC are calculated from the modified algorithm marked graph. Transitions 1, 2, and 3 appear in the forward paths from  $S_{\rm I}$  to  $S_{\rm O}$ . Therefore, TFC = T(1) + T(2) + T(3) = 10. As only transition 4 does not appear in any of the forward paths from data input source to data output sink, TBC = T(4) = 6. Also, TFC and TBC add up to TC. If only two functional units are available, the minimum values of TT, TBIO, and TBO are 8, 5, and 8 respectively. For a TBO of 7, the minimum R is [TCE / TBO] = 3.

### 2.5 Summary

The computing environment and performance measures in the ATAMM data flow architecture are established. Graph time performance is expressed by time between input and output (TBIO), task time (TT), and time between outputs (TBO). The modified algorithm marked graph is defined to compute lower bounds for TT and TBIO. Lower bounds for the performance measures are calculated analytically from the modified algorithm marked graph and the computational marked graph with the