### University of Tennessee, Knoxville TRACE: Tennessee Research and Creative Exchange

#### Masters Theses

**Graduate School**

12-2018

### Analysis and Design of a Hybrid Dickson Switched Capacitor Converter for Intermediate Bus Converter Applications

Maeve Elise Lawniczak University of Tennessee, mlawnicz@vols.utk.edu

Follow this and additional works at: https://trace.tennessee.edu/utk\_gradthes

#### **Recommended Citation**

Lawniczak, Maeve Elise, "Analysis and Design of a Hybrid Dickson Switched Capacitor Converter for Intermediate Bus Converter Applications. " Master's Thesis, University of Tennessee, 2018. https://trace.tennessee.edu/utk\_gradthes/5371

This Thesis is brought to you for free and open access by the Graduate School at TRACE: Tennessee Research and Creative Exchange. It has been accepted for inclusion in Masters Theses by an authorized administrator of TRACE: Tennessee Research and Creative Exchange. For more information, please contact trace@utk.edu.

To the Graduate Council:

I am submitting herewith a thesis written by Maeve Elise Lawniczak entitled "Analysis and Design of a Hybrid Dickson Switched Capacitor Converter for Intermediate Bus Converter Applications." I have examined the final electronic copy of this thesis for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Master of Science, with a major in Electrical Engineering.

Daniel Costinett, Major Professor

We have read this thesis and recommend its acceptance:

Benjamin J. Blalock, Syed K. Islam, Leon M. Tolbert

Accepted for the Council: <u>Dixie L. Thompson</u>

Vice Provost and Dean of the Graduate School

(Original signatures are on file with official student records.)

# Analysis and Design of a Hybrid Dickson Switched Capacitor Converter for Intermediate Bus Converter Applications

A Thesis Presented for the

Master of Science

Degree

The University of Tennessee, Knoxville

Maeve Elise Lawniczak

December 2018

© by Maeve Elise Lawniczak, 2018 All Rights Reserved.

## Acknowledgments

I would like to thank all of my undergraduate and graduate professors over the course of my time at the University of Tennessee. Especially, Dr. Costinett, my graduate advisor, for the opportunity to work in the Power Electronics Lab as an undergraduate and graduate student and his guidance throughout. Thank you for always keeping your office door open to discuss any ideas or roadblocks in my research and challenging me to think outside of the box. I would also like to thank Dr. Syed Islam, my undergraduate advisor, for his support and encouragement since my first day as an undergraduate student in the EECS department.

Additionally, I would like to thank Dr. Tolbert and Dr. Blalock who have helped me to become a better engineer through both their courses and friendship over the years. Thank you to my entire graduate thesis committee, Dr. Costinett, Dr. Islam, Dr. Tolbert and Dr. Blalock, for your guidance, review and feedback of my work.

Thank you to CURENT, the Center for Ultra-wide-area Resilient Electric Energy Transmission Networks, and the Department of Energy's Wide Bandgap Traineeship through the University of Tennessee for the academic and financial support which enabled me to continue my education in Electrical Engineering.

Finally, I would like to thank my family, Kolleen, Jon, Olivia and Zoe for your steadfast support and encouragement throughout.

### Abstract

By 2020 it is predicted that 1/3 of all data will pass through the cloud. With society's growing dependency on data, it is vital that data centers, the cloud's physical house of content, operate with optimal energy performance to reduce operating costs.

Unfortunately, today's data centers are inefficient, both economically and environmentally. This has led to an increase in demand for energy-efficient servers. One opportunity for improved efficiency is in the power delivery architecture which delivers power from the grid to the motherboard. In this dissertation, the main focus is the intermediate bus converter (IBC), used for the intermediate conversion, typically 48-12V/5V, in server power supplies. The IBC requires compact design so that it can be placed as close to the load as possible to enable more space for computing power and high efficiency to reduce the need for external cooling. Most commonly used converter topologies today include expensive bulky magnetics hindering the converter's power density. Furthermore, high output current of an IBC makes the efficiency very sensitive to any resistance, such as magnetic parasitic resistance or PCB trace resistance. In this work, analytical loss models are used to review the advantages and disadvantages of frequently used IBC topologies such as the phase-shifted full bridge and LLC. The Hybrid Dickson Switched Capacitor (HDSC) topology is also analyzed. The HDSC's high step-down conversion ratio and low dependence on magnetics due to the reduced applied volt-seconds, provides a new opportunity for applications such as the intermediate bus converter. The HDSC designs the on-time of devices in order to achieve soft-charging between flying capacitors. Other advantages of the HDSC include low switch stress, small magnetics and adjustable duty cycle for voltage regulation. Challenges, such as minimizing parasitic inductance and resistance between flying capacitors, are addressed and recommendations for PCB layout are provided. In this paper, a 4:1 24-5V and 8:1 48-5V, 100W GaN-based HDSC is designed and tested. The influences of capacitor mismatch and limitations placed on soft-charging operation for the HDSC is also modeled. This analysis can be used as a tool for designers when selecting flying capacitors.

## **Table of Contents**

| 1 | Intr | oduction                                                 | 1  |

|---|------|----------------------------------------------------------|----|

|   | 1.1  | Data Centers and the Global Economy                      | 1  |

|   | 1.2  | Market Trends for the Intermediate Bus Converter (IBC)   | 3  |

|   |      | 1.2.1 Centralized Power System                           | 4  |

|   |      | 1.2.2 Distributed Power Architecture                     | 5  |

|   |      | 1.2.3 Intermediate-Bus Architecture                      | 5  |

|   |      | 1.2.4 Other Architecture Designs                         | 6  |

| 2 | Тор  | ology Exploration for the IBC                            | 8  |

|   | 2.1  | Buck Converter                                           | 8  |

|   | 2.2  | Phase-Shifted Full Bridge Converter                      | 9  |

|   | 2.3  | LLC Converter                                            | 0  |

|   | 2.4  | Switched-Tank Converter                                  | 1  |

|   | 2.5  | Switched Capacitor Converters                            | 3  |

|   | 2.6  | Hybrid Dickson Switched Capacitor (HDSC)                 | 4  |

|   | 2.7  | Topology Design and Loss Analysis                        | 4  |

|   |      | 2.7.1 Buck Converter Design and Loss Analysis            | 4  |

|   |      | 2.7.2 Phase Shifted Full Bridge Design and Loss Analysis | 9  |

|   |      | 2.7.3 LLC Design and Loss Analysis                       | 25 |

|   |      | 2.7.4 Switched Tank Design and Loss Analysis             | 29 |

|   |      | 2.7.5 Topology Comparison and Summary                    | 33 |

| 3  | Swi    | tched Capacitor Converters                                                           | <b>34</b> |

|----|--------|--------------------------------------------------------------------------------------|-----------|

|    | 3.1    | Energy Density of Capacitors                                                         | 34        |

|    | 3.2    | Ideal Simplified Switched Capacitor Model                                            | 36        |

|    | 3.3    | Hard-Charging Loss                                                                   | 37        |

|    | 3.4    | Dickson Topology                                                                     | 40        |

|    | 3.5    | Reducing Hard-Charging Loss by Adding an Output Inductor                             | 43        |

|    | 3.6    | Complete Soft-Charging for the HDSC                                                  | 49        |

|    | 3.7    | Incorporating Output Voltage Regulation in the HDSC                                  | 57        |

|    | 3.8    | HDSC Design                                                                          | 60        |

|    |        | 3.8.1 Selecting the Conversion Ratio $(N)$ , Flying Capacitance $(C_{fly})$ , Induc- |           |

|    |        | tance $(L)$ , and Switching Frequency $(f_s)$                                        | 60        |

| 4  | Imp    | elementation and Testing                                                             | 68        |

|    | 4.1    | Flying Capacitor Selection                                                           | 68        |

|    | 4.2    | Device Selection                                                                     | 71        |

|    | 4.3    | Isolation Stage                                                                      | 73        |

|    | 4.4    | Power Stage Printed Circuit Board                                                    | 75        |

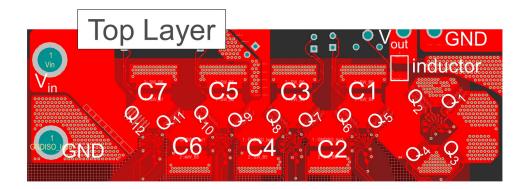

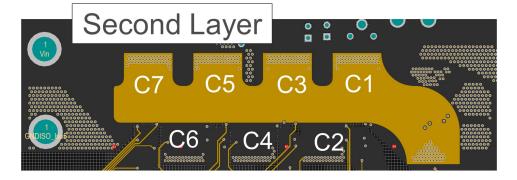

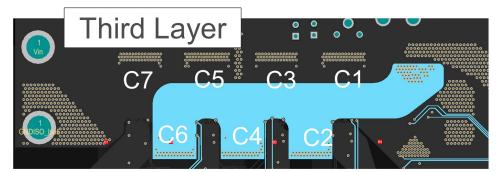

|    |        | 4.4.1 HDSC 4:1 PCB 1                                                                 | 75        |

|    |        | 4.4.2 HDSC 4:1 Printed Circuit Board 2                                               | 78        |

|    |        | 4.4.3 HDSC 4:1 Printed Circuit Board 3                                               | 83        |

|    |        | 4.4.4 Loss Model                                                                     | 91        |

|    |        | 4.4.5 HDSC 8:1 Printed Circuit Board 3                                               | 99        |

|    | 4.5    | Modeling Hard-Charging Loss for Varying $C_{fly}$                                    | 99        |

| 5  | Cor    | clusion and Future Work                                                              | 116       |

| Bi | ibliog | graphy                                                                               | 118       |

| Vi | ita    |                                                                                      | 129       |

## List of Tables

| 2.1  | IBC target design specifications.                                        | 13 |

|------|--------------------------------------------------------------------------|----|

| 2.2  | Buck Characteristics                                                     | 17 |

| 2.3  | Buck Simulation Parameters                                               | 18 |

| 2.4  | Values and components for buck design.                                   | 18 |

| 2.5  | Phase shifted full bridge characteristics                                | 21 |

| 2.6  | PSFB Simulation Parameters                                               | 23 |

| 2.7  | Components for Phase Shifted Full Bridge Design                          | 24 |

| 2.8  | Components for LLC Design                                                | 28 |

| 2.9  | LLC simulation parameters.                                               | 28 |

| 2.10 | STC Simulation Parameters                                                | 32 |

| 2.11 | Components for STC Design                                                | 32 |

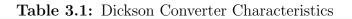

| 3.1  | Dickson Converter Characteristics                                        | 41 |

| 3.2  | 4:1 Dickson Capacitor Voltage Rating                                     | 43 |

| 3.3  | Comparison of circuit characteristics for the 4:1 and 8:1 HDSC           | 60 |

| 4.1  | Measured capacitance with DC bias voltage using the 4294A 40Hz-110MHz $$ |    |

|      | Precision Impedance Analyzer                                             | 70 |

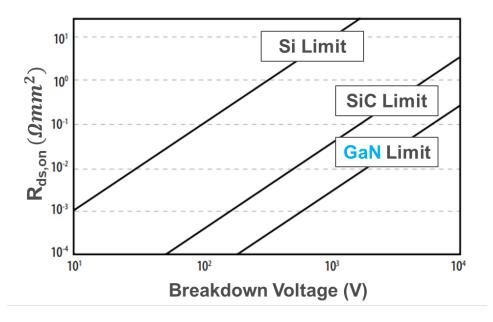

| 4.2  | Material Characteristic of GaN compared to Si and SiC                    | 71 |

| 4.3  | EPC2023C device characteristics [1]                                      | 74 |

| 4.4  | Q3D results for commutation loop during Phase 2a for PCB 1-3             | 86 |

| 4.5  | Q3D results for commutation loop during Phase 1a for PCB 1-3             | 86 |

| 4.6  | Trace Resistance Comparison between PCB 2 and PCB 3                      | 91 |

| 4.7  | Operating Conditions for 4:1 Loss Model and Testing                      | 92 |

| 4.8 | 8:1 Testing Parameters |  | 100 |

|-----|------------------------|--|-----|

|-----|------------------------|--|-----|

## List of Figures

| 1.1  | Intermediate bus location in the data center power supply system | 4  |

|------|------------------------------------------------------------------|----|

| 1.2  | Centralized power architecture [2]                               | 4  |

| 1.3  | Distributed power supply [2].                                    | 5  |

| 1.4  | Intermediate-bus architecture [2]                                | 6  |

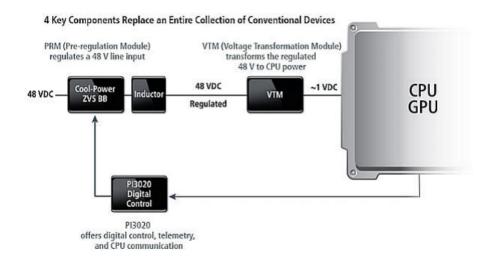

| 1.5  | Vicor's 48V direct to the CPU architecture [3]                   | 7  |

| 2.1  | Buck topology.                                                   | 9  |

| 2.2  | Phase-shifted full bridge topology.                              | 10 |

| 2.3  | LLC topology.                                                    | 11 |

| 2.4  | Switched-tank capacitor topology.                                | 12 |

| 2.5  | Efficiency summary at maximum currents                           | 12 |

| 2.6  | Buck schematic.                                                  | 15 |

| 2.7  | Buck circuit configurations.                                     | 16 |

| 2.8  | Buck operating waveforms.                                        | 16 |

| 2.9  | SPICE simulated buck waveforms                                   | 18 |

| 2.10 | Loss distribution of designed buck converter.                    | 19 |

| 2.11 | Phase shifted full bridge circuit.                               | 20 |

| 2.12 | Phase shifted full bridge waveforms                              | 21 |

| 2.13 | PSFB simulated waveforms.                                        | 24 |

| 2.14 | Simulated PSFB loss breakdown.                                   | 25 |

| 2.15 | LLC operating waveforms.                                         | 27 |

| 2.16 | LLC simulated waveforms.                                         | 29 |

| 2.17 | LLC loss distribution.                                           | 30 |

| 2.18 | Switched-tank converter subintervals and waveforms.                              | 31 |

|------|----------------------------------------------------------------------------------|----|

| 2.19 | STC simulated waveforms.                                                         | 32 |

| 2.20 | STC simulated waveforms.                                                         | 33 |

| 3.1  | Energy density comparison of ceramic capacitors and inductors [4]                | 35 |

| 3.2  | Basic Model for a switched capacitor converter.                                  | 36 |

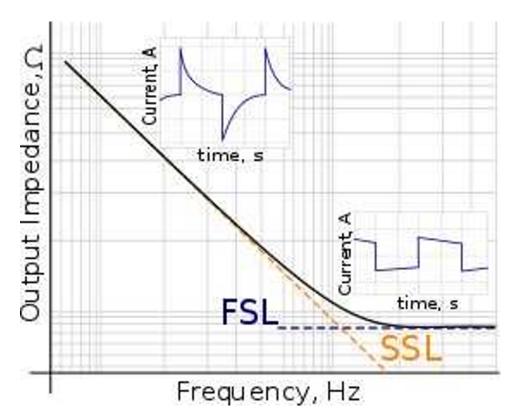

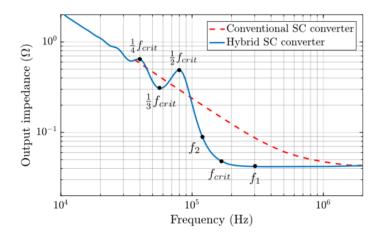

| 3.3  | Output impedance vs. switching frequency [5]                                     | 38 |

| 3.4  | Basic capacitor charging scenarios.                                              | 38 |

| 3.5  | Capacitor voltages and current waveforms in the charge redistribution process    |    |

|      | [6]                                                                              | 39 |

| 3.6  | 4:1 Dickson Topology                                                             | 41 |

| 3.7  | Gate signals for 4:1 Dickson Converter                                           | 41 |

| 3.8  | 4:1 Dickson topology for each phase of the switching period                      | 41 |

| 3.9  | Direct Energy Transfer                                                           | 44 |

| 3.10 | Indirect Energy Transfer                                                         | 44 |

| 3.11 | 4:1 Dickson with soft-charging capability                                        | 45 |

| 3.12 | Circuit configurations for the 4:1 Dickson.                                      | 46 |

| 3.13 | Capacitor discharged by a constant current load                                  | 46 |

| 3.14 | KVL 4:1 Dickson Modes of Operation                                               | 47 |

| 3.15 | Voltage mismatch between branches during phase transitions                       | 50 |

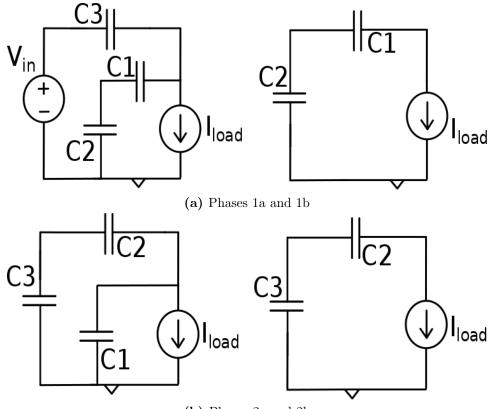

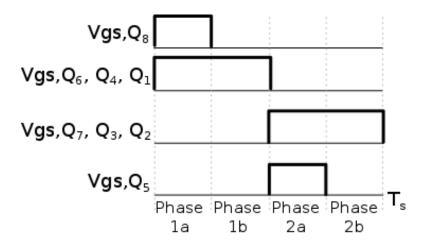

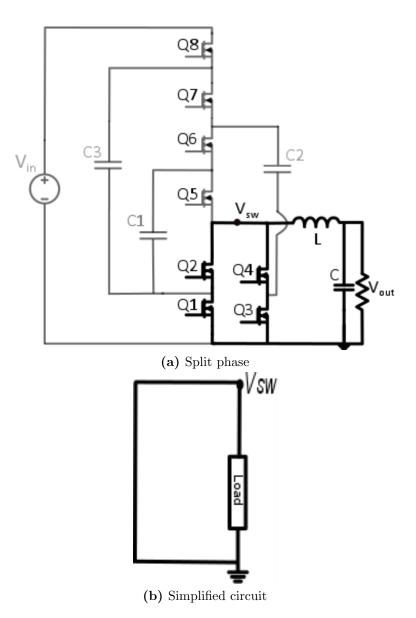

| 3.16 | 4:1 Dickson simplified circuit configurations for each interval within the       |    |

|      | switching period with additional split phases.                                   | 51 |

| 3.17 | 4:1 Dickson gate signals operating with added split phase intervals              | 51 |

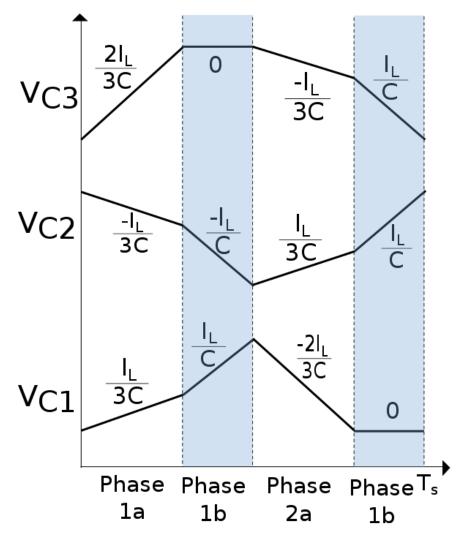

| 3.18 | Ideal capacitor voltage waveforms.                                               | 54 |

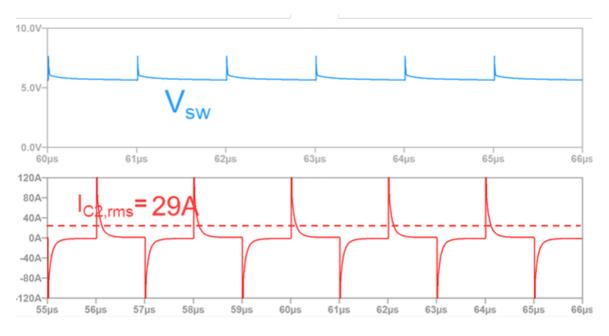

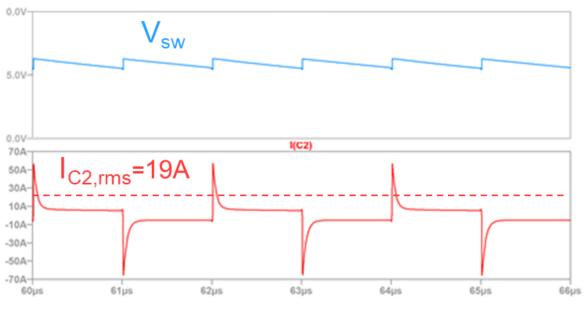

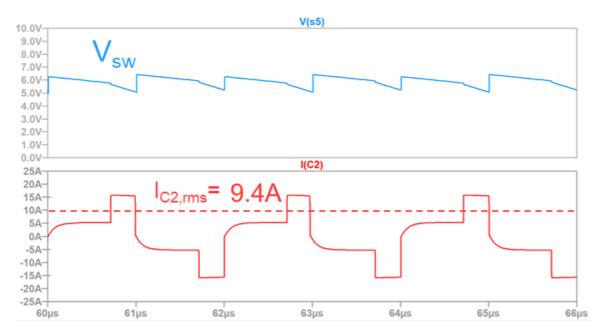

| 3.19 | Original Dickson, $V_{out}$ (blue), $I_{C2}$ (red)                               | 55 |

| 3.20 | Dickson with output inductor, $V_{sw}$ (blue), $I_{C2}$ (red)                    | 56 |

| 3.21 | Split-phase Dickson with output inductor, $V_{sw}$ (blue), $I_{C2}$ (red)        | 56 |

| 3.22 | Voltage regulation circuit.                                                      | 58 |

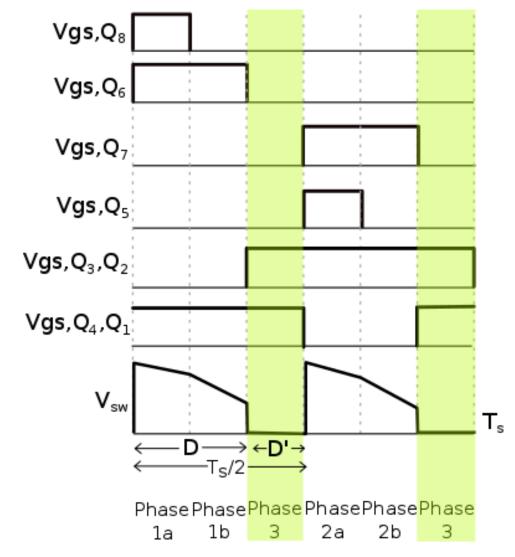

| 3.23 | Gate signals and the switch node voltage, $V_{sw}$ , for the regulated 4:1 HDSC. | 59 |

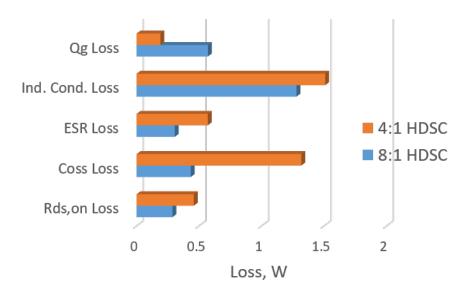

| 3.24 | Loss comparison for the 4:1 and 8:1 conversion ratio, $V_{in}$ =48V, $V_{out}$ =5V,                                                      |    |

|------|------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | $f_s = 500 \text{kHz} \dots \dots$ | 61 |

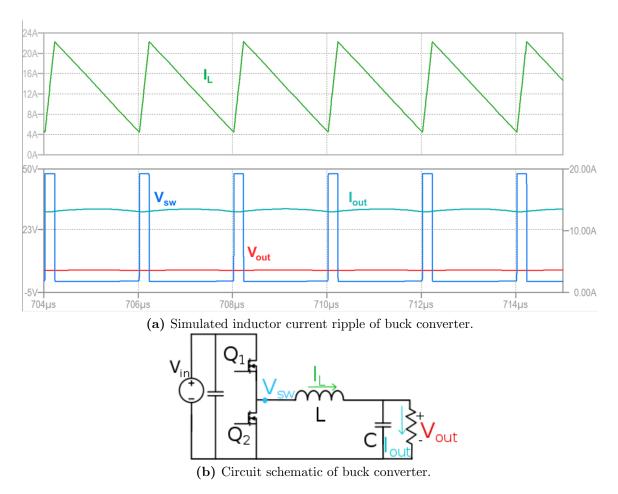

| 3.25 | Simulated inductor current ripple of buck converter and schematic.                                                                       | 63 |

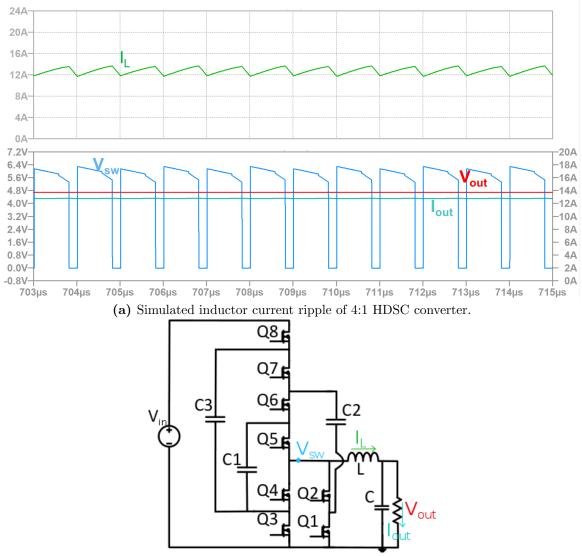

| 3.26 | Simulated inductor current ripple of 4:1 HDSC converter and circuit schematic.                                                           | 64 |

| 3.27 | Simulated output impedance vs. frequency [7]                                                                                             | 65 |

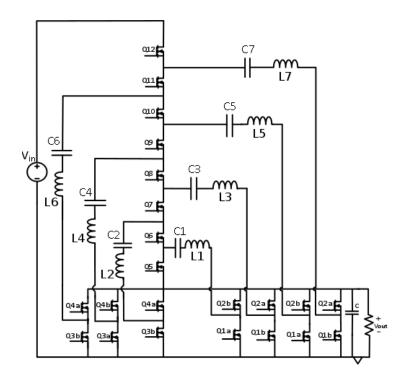

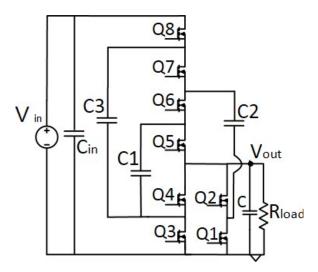

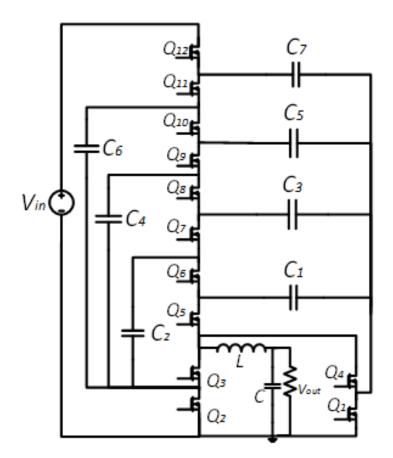

| 3.28 | 8:1 Hybrid Dickson Switched Capacitor Converter                                                                                          | 67 |

| 4.1  | Class 2 ceramic capacitors Code system.                                                                                                  | 69 |

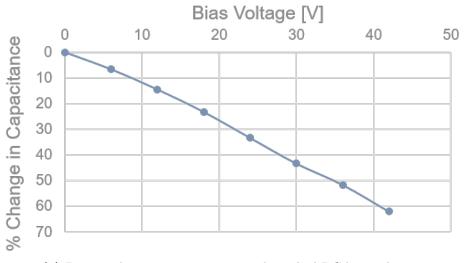

| 4.2  | Capacitance change vs. Voltage for (3) TDK CGA6M3X7S2A475K200AB in                                                                       |    |

|      | parallel                                                                                                                                 | 70 |

| 4.3  | Theoretical on-resistance vs. blocking voltage capability for silicon, silicon                                                           |    |

|      | carbide and gallium nitride [8].                                                                                                         | 72 |

| 4.4  | Top view of an eGaN FET EPC2023C [9]                                                                                                     | 72 |

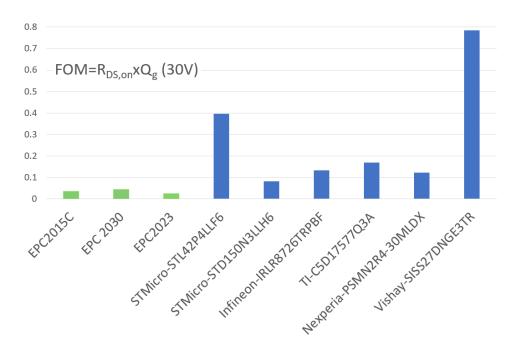

| 4.5  | $R_{on}Q_g$ product for 30V benchmark silicon compared to GaN                                                                            | 73 |

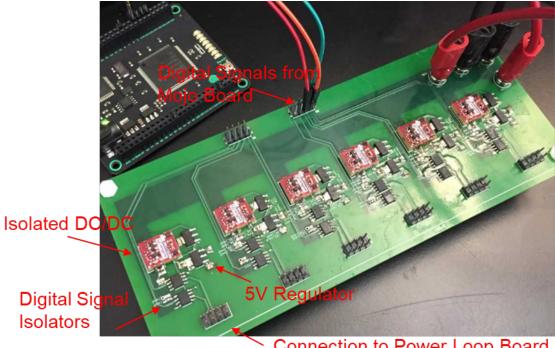

| 4.6  | Isolation board.                                                                                                                         | 74 |

| 4.7  | PCB 1                                                                                                                                    | 75 |

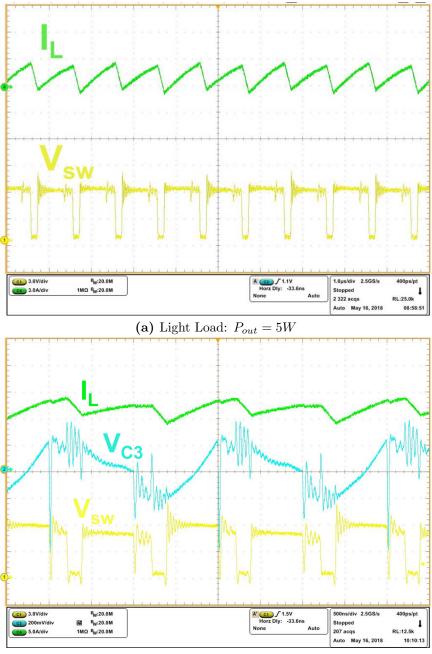

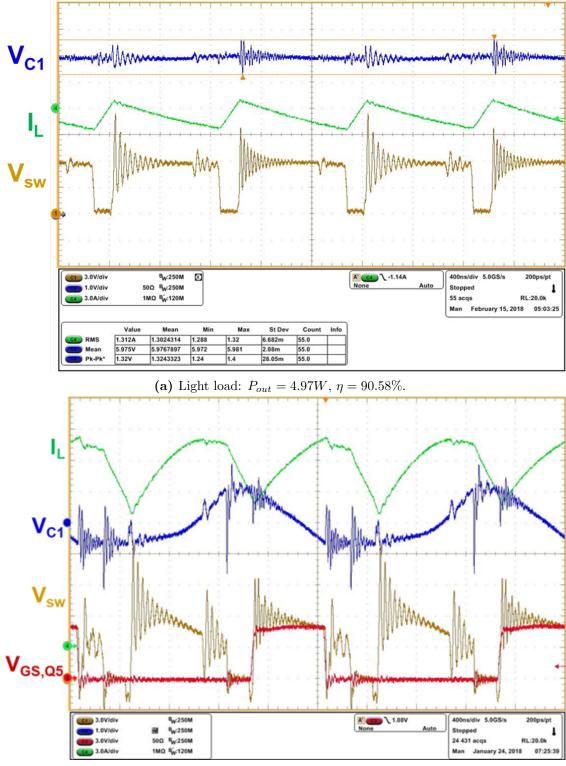

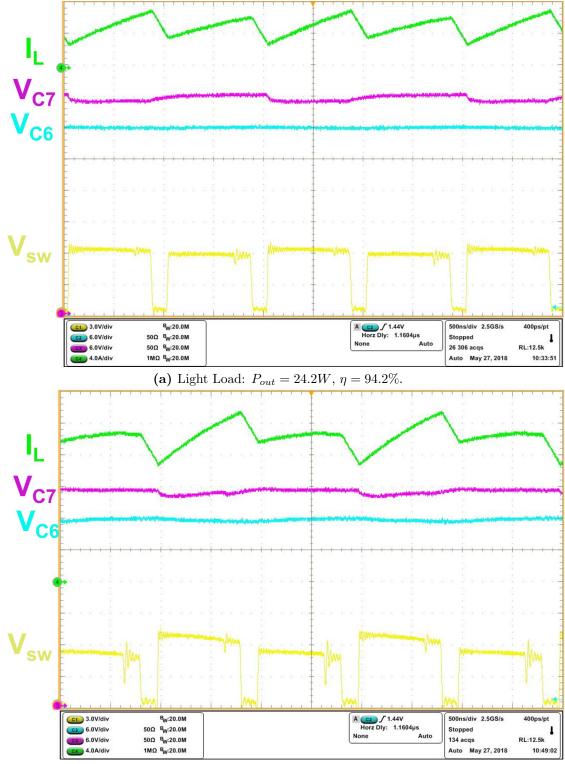

| 4.8  | PCB 1 4:1 waveforms: $V_{in} = 24V, f_s = 500kHz.$                                                                                       | 76 |

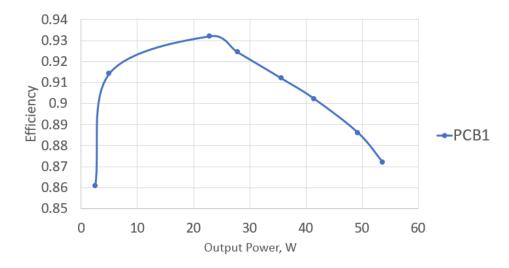

| 4.9  | PCB 1 experimental efficiency.                                                                                                           | 77 |

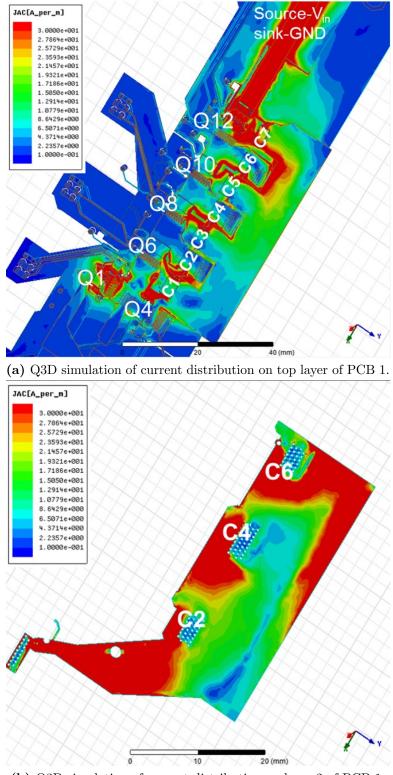

| 4.10 | Q3D simulations of current distribution for PCB 1                                                                                        | 79 |

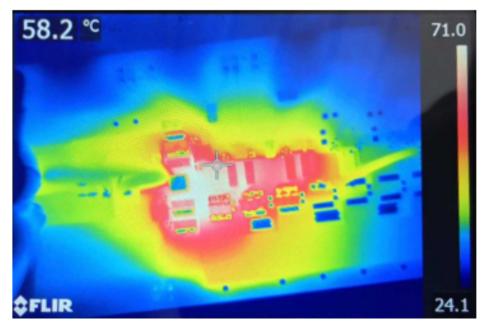

| 4.11 | Thermal image of PCB 1 taken with FLIR-T630sc camera                                                                                     | 80 |

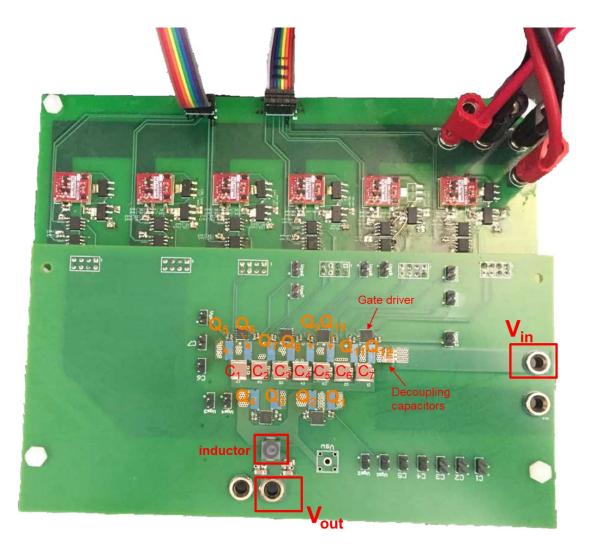

| 4.12 | Populated PCB 2 power stage connected to isolation board.                                                                                | 81 |

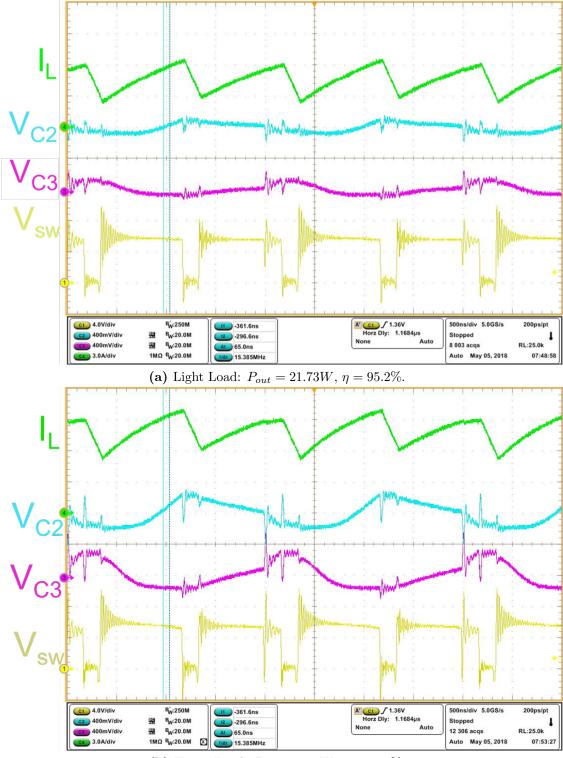

| 4.13 | PCB 2 4:1 waveforms: $V_{in} = 24V, f_s = 500kHz.$                                                                                       | 82 |

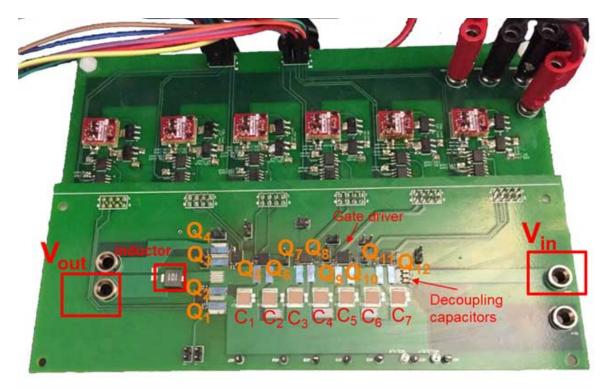

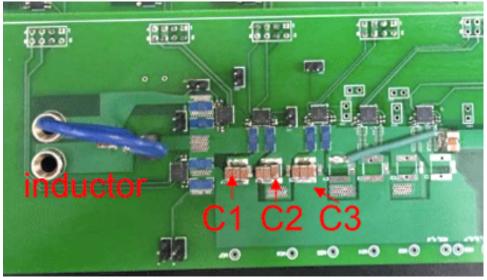

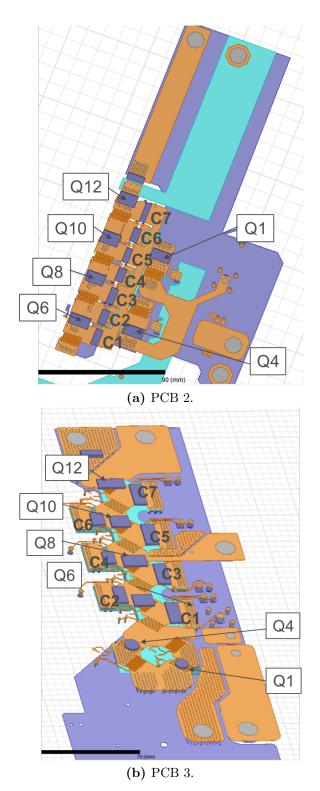

| 4.14 | PCB 3 populated for 4:1 testing.                                                                                                         | 84 |

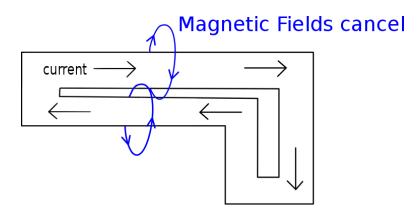

| 4.15 | Field cancellation of parallel conductors with currents flowing in opposite                                                              |    |

|      | directions.                                                                                                                              | 84 |

| 4.16 | PCB 3 Altium layers designed for field cancellation.                                                                                     | 85 |

| 4.17 | Circuit for measured loop inductance of Phase 1a with a constant load current.                                                           | 87 |

| 4.18 | Q3D simulation for Phase 1a parasitic loop inductance                                                                                    | 88 |

| 4.19 | PCB 3 4:1 waveforms: $V_{in} = 24V, f_s = 500kHz.$                                                                                       | 90 |

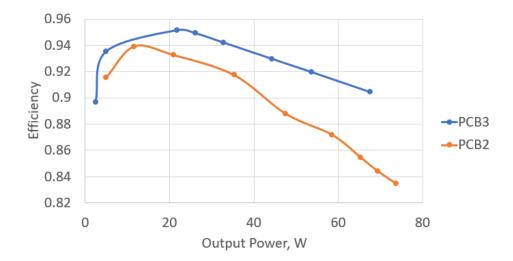

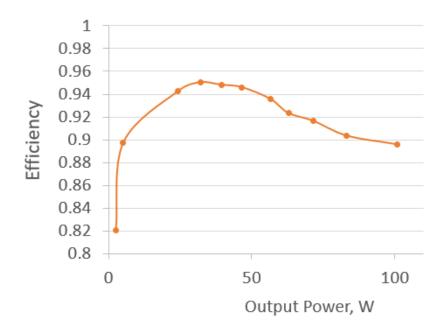

|      | Experimental efficiency comparison between PCB 2 and PCB 3                                                                               | 92 |

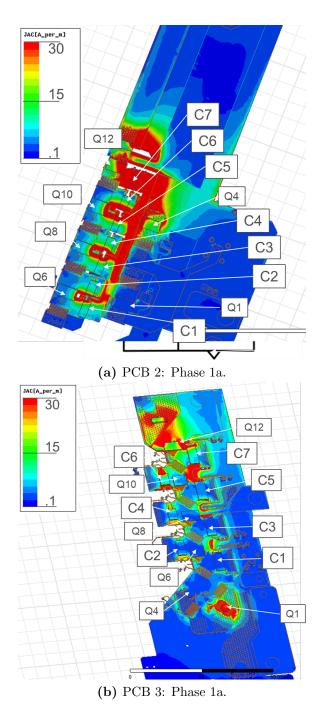

| 4.21 | Q3D simulation of current density for Phase 1a                                         | 93  |

|------|----------------------------------------------------------------------------------------|-----|

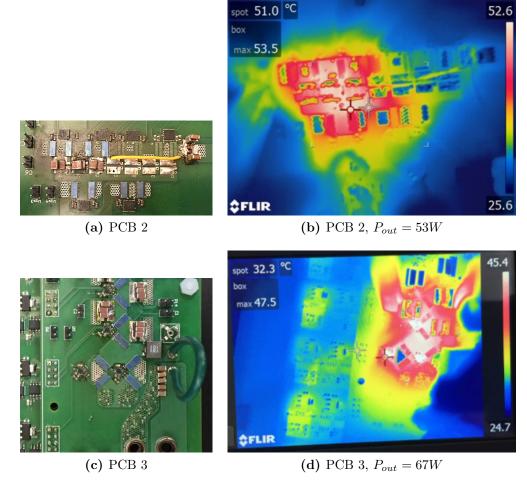

| 4.22 | Comparison of thermal images for PCB 2 and PCB 3 in the 4:1 configuration.             | 94  |

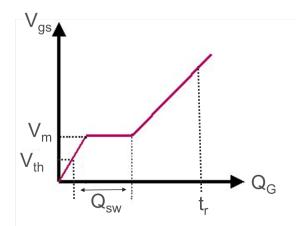

| 4.23 | Gate charge plot.                                                                      | 96  |

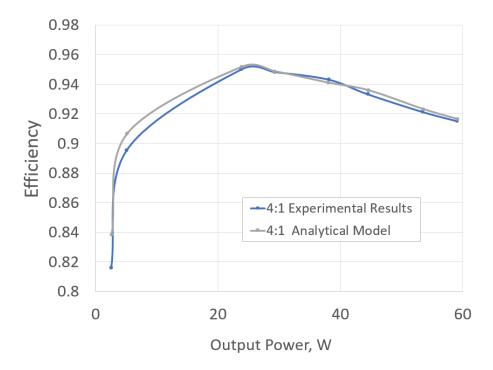

| 4.24 | Efficiency curve validation for the 4:1 HDSC                                           | 98  |

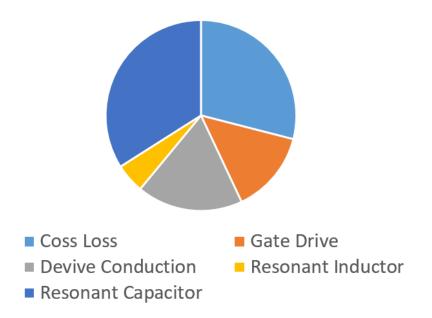

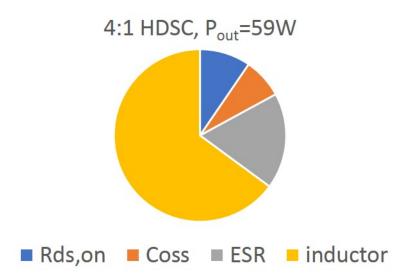

| 4.25 | 4:1 loss distribution at an output power of 59W, $\eta = 90.3\%$                       | 98  |

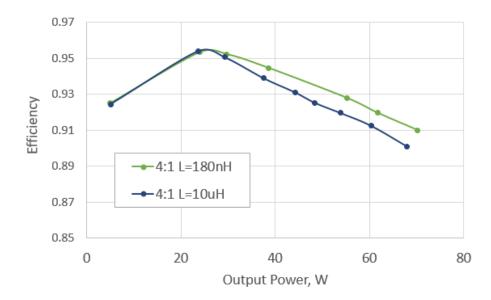

| 4.26 | Efficiency comparison for L=10uH and L=180nH                                           | 99  |

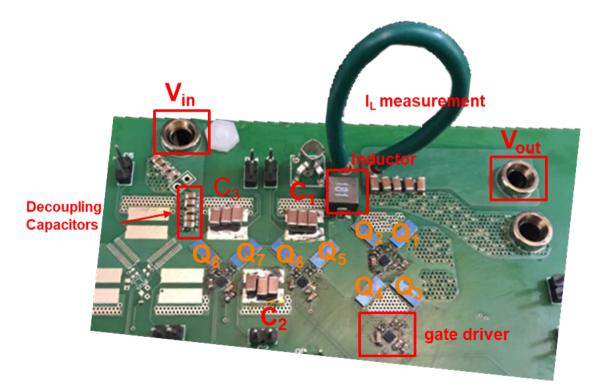

| 4.27 | PCB 3 populate for 8:1 conversion ratio.                                               | 100 |

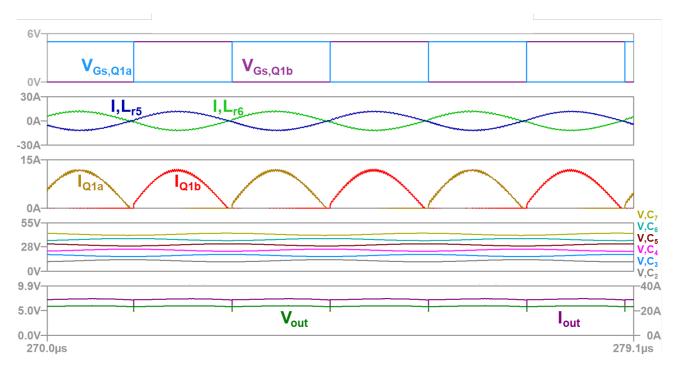

| 4.28 | PCB 3 8:1 waveforms $V_{in} = 48V$ , $f_s = 500kHz$                                    | 101 |

| 4.29 | 8:1 experimental efficiency                                                            | 102 |

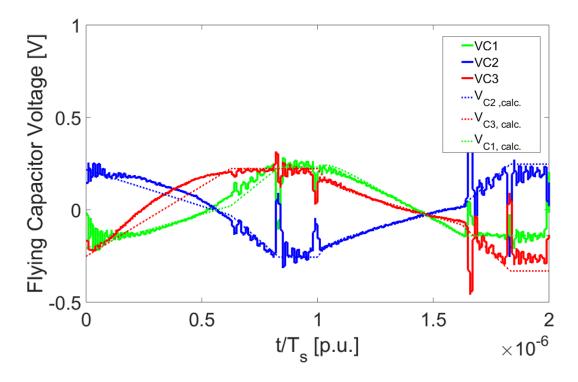

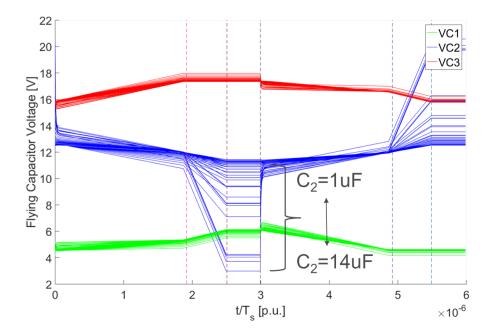

| 4.30 | Comparing experimental capacitor voltages to analytical models                         | 103 |

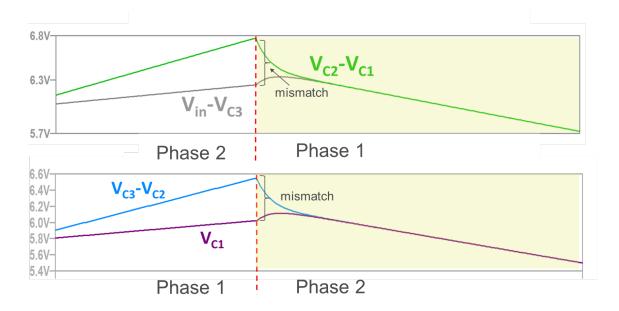

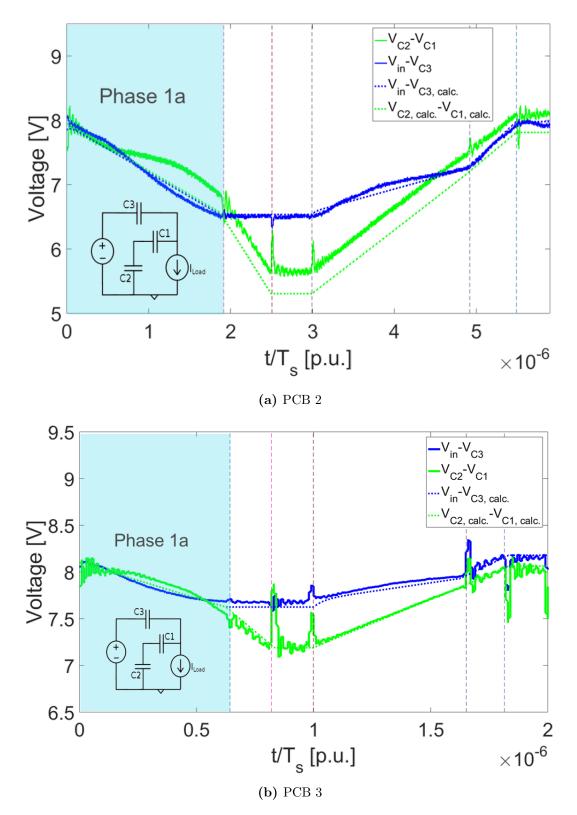

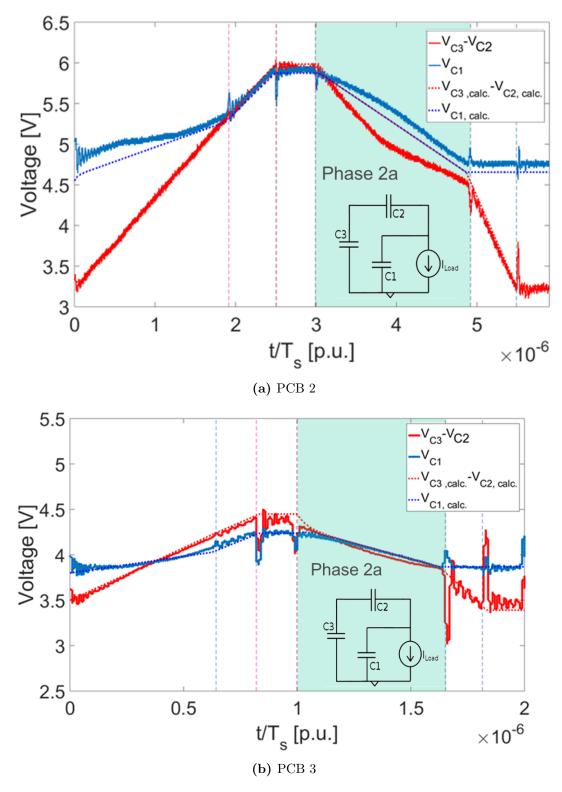

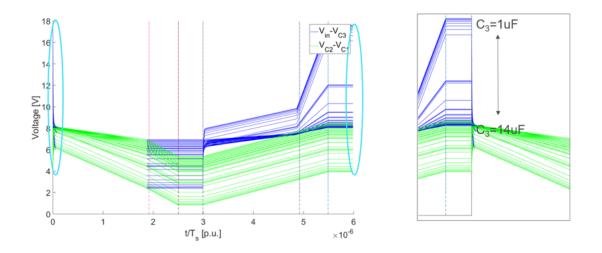

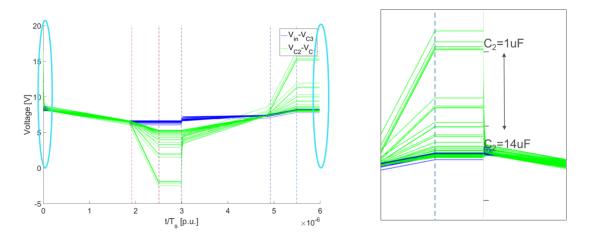

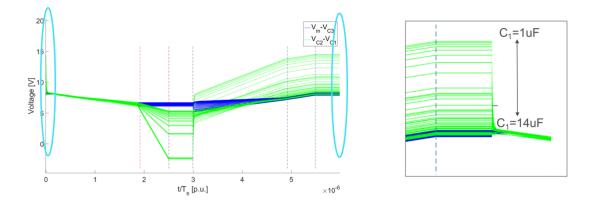

| 4.31 | Experimental and analytical waveforms of $(V_{in} - V_{C3})$ and $(V_{C2} - V_{C1})$ . | 104 |

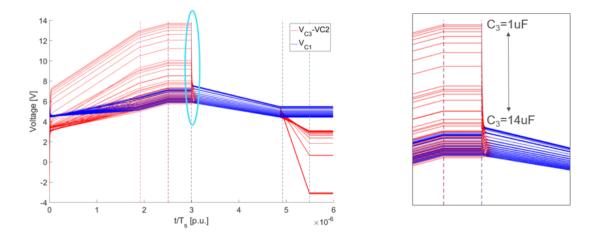

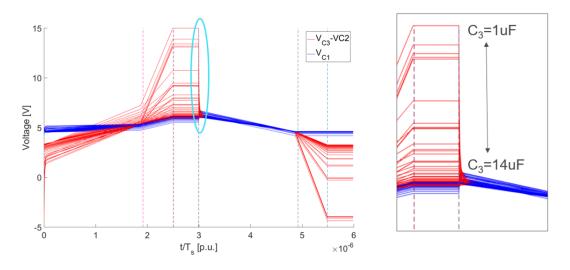

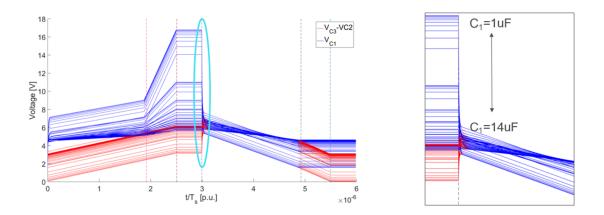

| 4.32 | Experimental and analytical waveforms of $(V_{C3} - V_{C2})$ and $(V_{C1})$ .          | 106 |

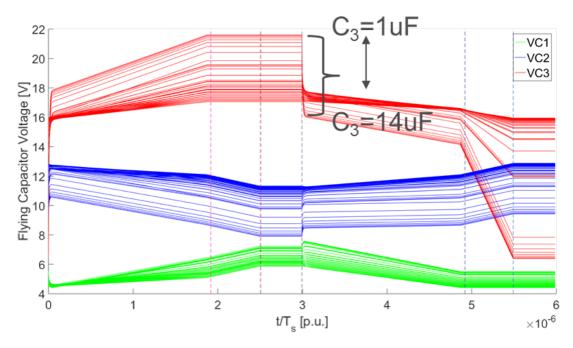

| 4.33 | Varying $C_3$ voltage waveform in steady state                                         | 107 |

| 4.34 | Hard-charging during transition to Phase 1a between inner leg and outer leg            |     |

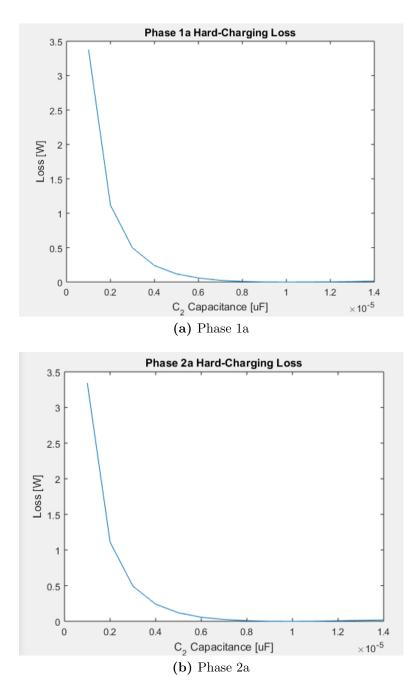

|      | of capacitors as $C_3$ iterates through a range of values                              | 107 |

| 4.35 | Hard-charging during transition to Phase 2a between inner leg and outer leg            |     |

|      | of capacitors as $C_2$ iterates through a range of values                              | 108 |

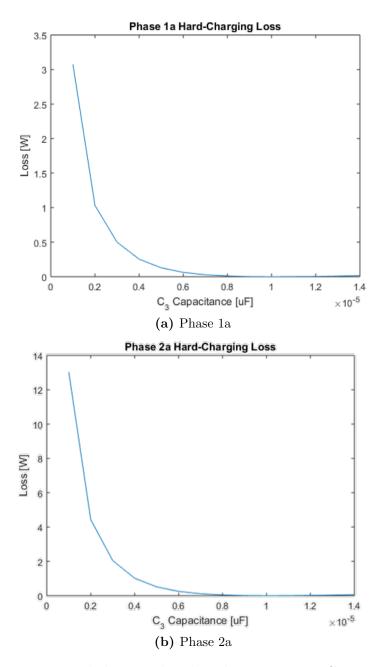

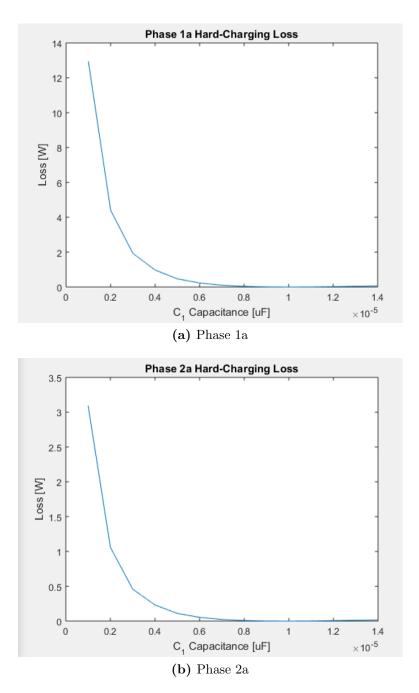

| 4.36 | Hard-charging loss based on a varying $C_3$ capacitance                                | 109 |

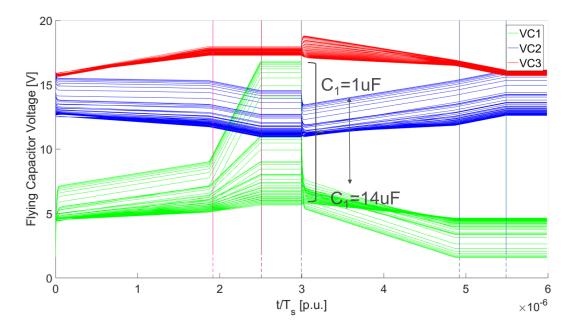

| 4.37 | Determining steady-state voltage waveforms for a varying $C_2$                         | 110 |

| 4.38 | Combined capacitor voltage branch equations to determine voltage mismatch              |     |

|      | between capacitors as $C_2$ varies                                                     | 111 |

| 4.39 | Hard-charging loss for varying $C_2$                                                   | 112 |

| 4.40 | Determining steady-state voltage waveforms for a varying $C_1$                         | 113 |

| 4.41 | Combined capacitor voltage branch equations to determine voltage mismatch              |     |

|      | between capacitors as $C_1$ varies                                                     | 114 |

| 4.42 | Hard-charging loss for varying $C_1$                                                   | 115 |

## Chapter 1

## Introduction

#### 1.1 Data Centers and the Global Economy

#### **Global Economy's Dependence on Data Centers**

In recent decades, data centers have become the backbone of the global economy. Without data centers, businesses could not operate, communications could not occur and online consumer services would not be possible. Furthermore, with new technologies such as driver-less vehicles and crypto-currency leveraging data centers as well, the global economy's dependency on data centers is undeniable and continuing to grow [10].

#### Massive Data Center Infrastructure

The data center infrastructure required to support the world's Internet users is massive. On an individual level, most Americans today have a significant digital presence. Emails, social media, banking transactions, streaming entertainment, etc., all require the Internet and are made possible by data centers. On a global scale, there are approximately 2.5 billion people who use the Internet, 70 percent of which use the Internet every day [11] [12]. Not surprisingly, the infrastructure to support this global system is extremely large. In fact, according to the International Data Corporation (IDC), in 2015 there were 8.55 million data centers in the world, with the largest called The Citadel, covering 7.2 million square feet in Tahoe Reno, Nevada [13].

#### **Data Center Energy Consumption**

As stated in [14], "Data centers are one of the most energy-intensive building types, consuming 10-50 times the energy per floor space of a typical commercial office building." Put into more personal terms, charging a single tablet or smart phone requires a negligible amount of energy. However, streaming an hour of video once a week on either of these devices requires more energy from the data centers than two new refrigerators use in one year [15]. According to a study on data center energy usage conducted by the United States Department of Energy in 2014, US data centers consumed about 70 billion kilowatt-hours of electricity, representing about 2 percent of the country's total energy. This is a 4 percent increase in the data center energy consumption from 2010 to 2014 [16]. On a global scale, data centers consume approximately 3 percent of the world's global power [?]. And while the rate of increase has slowed down in recent years, the integral nature of data centers and cloud computing in today's global economy is undeniable and will continue to be one of the single largest global energy consumers.

#### **Energy Consumption and Efficiency**

A data center's massive energy consumption is largely due to the inefficiency of the system. Not only is energy needed for direct computing power, but to avoid temperature and humidity rise, which may lead to condensation forming on machines, energy is also needed for massive cooling systems. Most of the energy loss for a server occurs at the power supply, which converts the AC voltage coming from a standard outlet to a set of low DC voltages used to power microprocessors, memory subsystems, mass storage, network devices and the analog and digital interfaces that complete the system [17] [18]. Considering the power delivered from the grid to the motherboard, typical overall delivery efficiencies are around 50% [19]. As for the power supply, because of multiple power conversions within a single architecture, efficiencies are typically range from 70% [20]-80% [3] [21].

#### Summary

In summary, the global economy's reliance on data centers is undeniable. The sheer size and energy consumption is massive and there is a lot of room for improvement for making data centers more efficient. In particular, substantial efficiency improvements are needed in the power delivery architecture. Increasing efficiency and power density of the power delivery architecture will enable the overall system to operate more efficiently and in turn decrease the energy consumption and operating costs of data centers.

## 1.2 Market Trends for the Intermediate Bus Converter (IBC)

As stated in the previous section, increasing the efficiency of the data center power supply can greatly impact a data center's operating costs. Over recent decades, the power distribution technology for data centers has transitioned through several architectures starting with the centralized-power architecture (CPA) and evolving to the intermediate bus architecture. Each advancement has been driven by factors such as new technologies, demand for wider input voltage ranges, higher power levels and better supply performance [22].

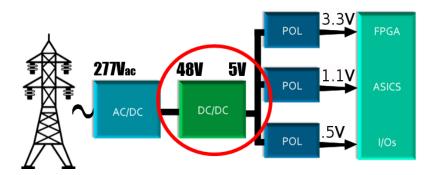

This thesis focuses on the design for the intermediate bus converter (IBC), which is part of the intermediate bus architecture (IBA) depicted in Fig. 1.1. The IBC is one of three conversions in the power supply architecture and high efficiency is paramount for the design. The IBC is what differentiates the distributed power architecture (DPA) from the IBA. In order for the IBA to be competitive to the DPA, the IBC must have the highest efficiency among the power conversion stages. The power density is also critical. In order to keep conduction loss from connectors between conversion stages low, the IBC needs to be placed close to the motherboard. The evolution of the power supply system architecture ending with the inclusion of the IBC is summarized in the following section.

Figure 1.1: Intermediate bus location in the data center power supply system.

#### 1.2.1 Centralized Power System

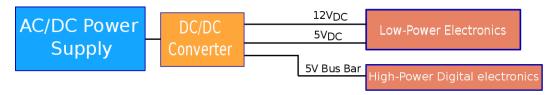

During the 1960's when semiconductor switches were becoming more accessible, a typical configuration for the centralized power system included an AC-DC rectifier/ charger that converted the AC input voltage to a 48V bus voltage. Then a DC/DC converter was used to step the voltage down from 48V to 5V or 12V. The centralized power supplies were typically located at the bottom of a server cabinet and connectors between conversion stages were long and made it difficult to deliver high power. The typical configuration is provided in Fig. 1.2. All of the voltages were generated at a central location and distributed to loads via buses. This particular design was used until the mid 1980's and was discontinued due to issues relating to long time to market, system failures occurring from a single component power failure, high cost for bulky bus bars and inability to accurately regulate the supply voltage [2].

Figure 1.2: Centralized power architecture [2].

#### 1.2.2 Distributed Power Architecture

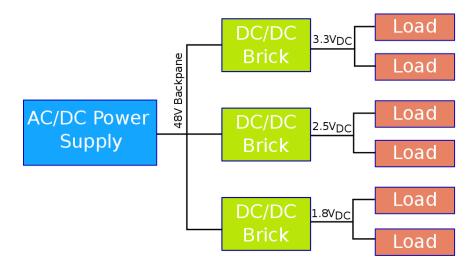

In the early 1990s, following the centralized power system, came the distributed power architecture (DPA). The distributed power architecture broke the power conversion into building blocks as pictured in Fig. 1.3. The centralized system was replaced with an AC/DC front-end power supply that provided a 48V output to each shelf and line card. This more modular architecture enabled the line cards to be replaced when component failures occurred and decreased failure downtime. Each line card included multiple 48V, isolated DC/DC modules that provided the required voltages for the line-card loads. A combination of the trends towards digital functional blocks with lower voltages, market introduction of modular-isolated DC/DC converters and a need for higher reliability contributed to the evolution from the centralized power system to the distributed power architecture [2].

Figure 1.3: Distributed power supply [2].

#### **1.2.3** Intermediate-Bus Architecture

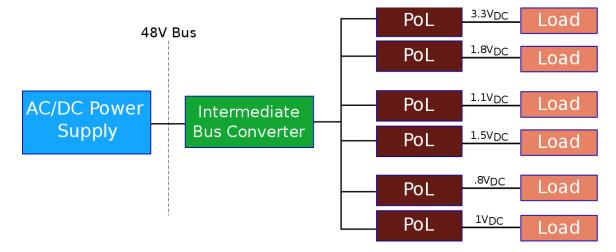

By the early 2000s, demand increased for on-board low-cost point of load regulators, ranging from .5-3.3V, for digital and analog chips. This meant more DC/DC bricks were needed which took up more space and increased the system cost. This led to the market adoption of the Intermediate Bus Architecture (IBA). The IBA includes a front end AC/DC power supply, with a typical output of 48V, an intermediate bus converter that provides isolation and steps the voltage down to a bus voltage, typically between 14V-5V and non-isolated point of loads (POLs) which provides high-quality voltages for a variety of digital and analog blocks. A diagram of this architecture is provided in Fig. 1.4. The IBA has been widely adopted and due to requiring only one isolated converter has enabled financial savings. The high quality voltage from the POLS has enabled higher efficiency and processing power for data center operations [23, 24, 25]. Other industries, such as space, are also taking a page from the data center world and are incorporating the intermediate bus architecture into their own technical designs [26].

Figure 1.4: Intermediate-bus architecture [2].

#### **1.2.4** Other Architecture Designs

With data centers upgrading IT equipment every 3-5 years [27], new architecture designs are looking for ways to lengthen system longevity while continuing to increase power density and efficiencies. Other approaches include the Factorized Power Architecture (FPA) developed by Vicor, claiming to provide better system performance, longevity and cost compared to the IBA [17]. This architecture eliminates the IBC and converts 48V to 1V as detailed in Fig.1.5. Google and Facebook have also recently collaborated to propose a similar architecture, boasting to reduce losses by 30% by delivering 48V directly to the server [3]. For this system, regulation occurs at the 277Vac-48V conversion, enabling the converter to be compact and placed closer to the load. While new architectures such as this may have proven to be efficient, they require large scale redesigns of data center server structuring and large initial infrastructure investments.

Figure 1.5: Vicor's 48V direct to the CPU architecture [3].

#### Summary

Over the past few decades the power supply architecture has evolved to the IBA. The IBA is cost effective and its modular structure enables high flexibility for modifications and updates. Adoption of the IBA is in part due to the IBC. IBCs need to have high efficiency for improved overall system efficiency as well as high power density. The IBC needs to be placed as close to the load as possible to reduce any  $I^2R$  loss that can be introduced by parasitics in the connectors between stages.

## Chapter 2

## **Topology Exploration for the IBC**

In the following section different topologies used in data center power supplies and for similar power levels are reviewed. Not all of the topologies include isolation though. Generally, the IBC is implemented using an isolated structure to protect the server components from power faults that could propagate from the front-end AC/DC converter. If a power surge occurs, the isolated IBC can shield the POL converters, which do not have isolation. Recently however, isolation for the IBC stage has not been required in some systems. Interestingly, the isolation characteristic was adopted from telecommunication systems which do require isolation. However, the power spike that warrants the isolation in telecommunication systems does not actually occur in data centers due to the isolation from the ac/dc conversion stage before the IBC. Therefore, isolation in the IBC stage, for particular systems, has been increasingly viewed as an over provisioned safety requirement [28].

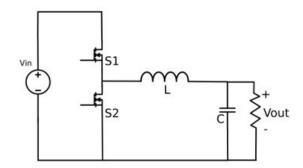

#### 2.1 Buck Converter

The buck converter is appealing for stepping down voltage due to its design simplicity and low cost. The buck, depicted in Fig. 2.1, is commonly used today for the Point-of-Load (POL) stage [? 29, 30]. With some data centers shifting to DC distribution systems due to the penetration of renewable energy sources in the distribution networks, the buck has been researched for other stages within the IBA, such as the 380V-48V conversion [31].

Figure 2.1: Buck topology.

One of the design limitations of the buck is the stress and loss created when operating with an extreme duty cycle. To extend a short duty cycle, designs such as [32] can divide the input voltage across stacked capacitors, increasing the duty cycle and decreasing the voltage stress across the high-side device. Other designs reduce the conduction loss at the output using a multi-phase design [33, 34, 35]. In [32] a multi-phase cascaded buck design is used for a 54V-1V conversion, the input voltage is stacked in series and the outputs are connected in parallel, however the overall power density becomes limited by the output inductors.

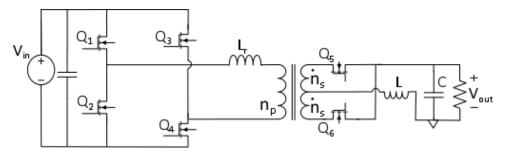

#### 2.2 Phase-Shifted Full Bridge Converter

For IBC designs that still require isolation between the input and output, a transformer is needed in the converter design. The Phase-Shifted Full Bridge (PSFB) provides isolation as well as lower stress on devices and higher efficiencies compared to the buck converter. The phase-shifted full bridge, depicted in Fig. 2.2, is typically used for medium power levels ranging from 200W-3kW and for applications such as data center power supplies, telecommunication, micro/mild hybrid vehicles, renewable energy systems and battery based storage systems. Efficiencies for PSFB used across these applications range from 85% to 93% [36, 37, 38, 39, 40]. Similar to the buck design, the phase shifted full bridge includes an inductor at the output which commonly causes high conduction loss. In [41], series-connected transformers were used, each acting as a transformer or inductor depending on the switching interval and could be used to replace the output inductor. Other factors that impact the performance of the PSFB are the turns ratio of the transformer, core loss, AC winding loss and non-zero current switching (ZCS) of the synchronous rectifier devices. This topology uses zero voltage switching (ZVS) for increased efficiency but it is not achievable across the full load range [42]. Efforts to extend the ZVS range include utilizing the adaptive energy stored in components of an auxiliary circuit [43].

Figure 2.2: Phase-shifted full bridge topology.

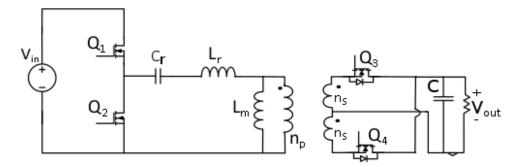

#### 2.3 LLC Converter

An additional option for an isolated IBC design is the LLC converter. The LLC converter, depicted in Fig. 2.3, is a popular topology used in DC-DC converters for data center server power supplies [40], telecommunication power supplies [44] and electric hybrid vehicle converters [45]. Compared to the PSFB, the LLC is capable of achieving ZVS over the full load range [46]. By greatly reducing switching loss, the LLC is able to operate at high frequencies to increase power density and reduce the size of the resonant components [47]. Transformer loss is typically the dominant loss mechanism in high-frequency LLC designs [48]. Planar transformers can be used for greater power density but they can introduce other issues such as termination loss that can hinder efficiency [49]. Typical LLC designs range in power levels from 400W to 5kW with efficiencies ranging from 92% to 98% [50] [51] [52] [53] [54].

Figure 2.3: LLC topology.

#### 2.4 Switched-Tank Converter

The switched-tank converter (STC), shown in Fig. 2.4 is also a resonant converter. Each of the inductors creates a resonant tank with the capacitors. Compared to the PSFB and LLC, the STC does not use a bulky transformer to step down the voltage. Instead, capacitors are used to step down the voltage. The STC design has been used for data center power supply applications due to its high efficiency, high power density and light-weight. One drawback to the design is it's inability to regulate the output voltage. Furthermore, while the topology component count can be high increasing overall converter costs, the efficiencies achieved are comparable to the LLC. The topology has achieved 98% efficiency for power levels up to 600W [55] [56] [57].

#### Summary

Fig. 2.5 shows a graphical summary of the articles reviewed in this chapter. The converter efficiencies are compared with their output current. The buck converter design had the lowest efficiency and current capability, followed by the PSFB. The LLC and STC are capable of achieving efficiencies close to 98% at output currents upwards of 50A. The resonant converters are limited by conduction loss of the resonant tank and in the case of the LLC, transformer loss. The design specifications for this IBC are provided in Table 2.1 and the target is included in the graphical summary.

Figure 2.4: Switched-tank capacitor topology.

Figure 2.5: Efficiency summary at maximum currents.

| Design Parameter      | Value     |

|-----------------------|-----------|

| DC Input Voltage      | 48V       |

| Output Power          | 500W      |

| DC Output Voltage     | 5V        |

| Output Current        | 100A      |

| Conversion Efficiency | 99%       |

| Size                  | 1/8 Brick |

Table 2.1: IBC target design specifications.

#### 2.5 Switched Capacitor Converters

High current applications have long been dominated by resonant converters such as the LLC and phase-shifted full bridge. While such converters are capable of achieving high efficiencies, further improvement of efficiency is strongly linked to specialized magnetic design and manufacturing. Searching for a topology that does not rely on magnetics for energy transfer naturally pushes the designer towards switched capacitor (SC) topologies. With high-power density becoming of greater importance for the power electronics designer, switched capacitor designs offer unique opportunities for increased power density. Conventional switched capacitor topologies include the Ladder, Fibonacci, Dickson, and Series-Parallel. From these traditional designs, other topologies have been introduced such as the multilevel modular capacitor-clamped converter (MMCCC) [58] and flying capacitor multilevel converter (FCMDC) [59].

Switched capacitor converters have been used in a wide range of applications such as low and high power integrated circuits [60, 61, 62], energy harvesting [63], interconnections of offshore wind farms to DC grids [64] and for self-powered signal processing [65, 66]. Limitations of the SC topologies include inherent loss due to voltage mismatch during energy transfer between capacitors that are shorted together and inability to regulate the output voltage.

#### 2.6 Hybrid Dickson Switched Capacitor (HDSC)

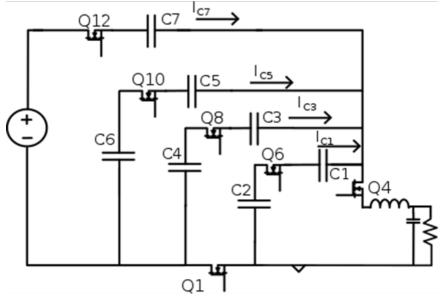

The Hybrid Dickson Switched Capacitor (HDSC) Converter is based on the original Dickson switched capacitor topology [61] which will be discussed in depth in Ch. 3. The HDSC is suitable for extreme conversion ratios, has low switch stress [67], reduced magnetic size, provides voltage regulation [68] and increased efficiency using soft-charging [69]. This topology is analyzed, designed and tested for the IBC application and discussed in Chapters 3 and 4.

#### 2.7 Topology Design and Loss Analysis

In this section, the four topologies introduced in Sections 2.1-2.4, the Buck, PSFB, LLC and STC are analyzed and simulated for a loss comparison to the HDSC. The characteristics of the selected passive elements and devices, such as  $R_{ds,on}$ ,  $C_{oss}$ , capacitor ESR and inductor DCR, are integrated into the simulation for accurate efficiency calculations. Magnetic loss due to core loss and ac winding loss are calculated separately and included in the loss distribution summary. The loss breakdown for each topology enables insight into the limitations of these converters and used for comparison to the HDSC. The topologies are compared for a 135W design and most of the designs are analyzed at a switching frequency,  $f_s=1$  MHz. In each analysis the power loss distribution and required component list are provided.

#### 2.7.1 Buck Converter Design and Loss Analysis

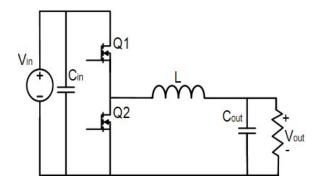

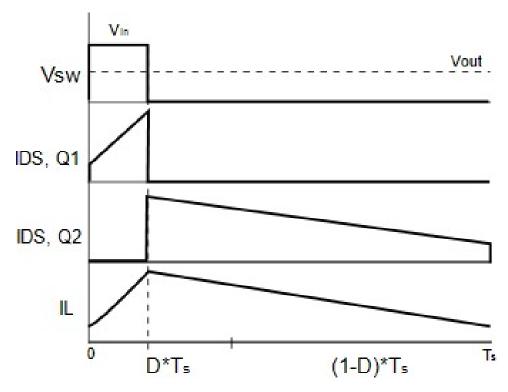

One of the advantages to the Buck topology is the simple design. It requires two switches, an output inductor, input capacitor and output capacitor. The basic operation and operating waveforms are depicted in Fig. 2.8 along with the operating characteristics in Table 2.2.

Each of the devices,  $Q_1$  and  $Q_2$ , are driven with complementary gate-to-source voltage signals. The length of time that  $Q_1$  is ON is related to the duty cycle, D, and conducts current for  $DT_s$ , where  $T_s$  represents the switching period.  $Q_2$  conducts for the remaining

Figure 2.6: Buck schematic.

period,  $(1 - D)T_s$ . The duty cycle is determined using the following equation,

$$D = \frac{V_{out}}{V_{in}} \tag{2.1}$$

One of the disadvantages to the buck converter is the high stress that occurs on the hi-side device,  $Q_1$ , when operating under a high voltage conversion ratio. This high stress is due to high voltage and peak current, resulting in increased switching loss, such as turn-off loss and overlap loss. Additionally, the high peak currents through the inductor will lead to increased RMS currents,  $I_{L,RMS}$ , and higher inductor conduction loss. From Eq. 2.1 and the design parameters listed in Table 2.3, the duty cycle is D=.104. This short duty cycle means that  $Q_1$ , must transfer the entire power flow of the converter during this short amount of time. The device not only has to block the input voltage but also withstand much higher current levels than the average current that goes through the device. From the simulated buck model, where  $L = 4.7 \mu H$ ,  $I_L = 27$  A, the average current through  $Q_1$  is 2.8 A. The RMS current through the device is over three times the average current,  $Q_{1,rms}=8.7$  A. This high rms current will result in high conduction loss. The simulated drain-to-source voltage,  $V_{ds}$ , waveforms for  $Q_1$  and  $Q_2$  are provided in Fig. 2.9. The list of components selected for the buck design are provided in Table 2.4. With regards to cost, when selecting devices, the cost of the device will increase depending on the voltage and current stresses that each device needs to withstand. The discrete device and passive characteristics were integrated into the simulation for an accurate efficiency approximation. The losses of this converter include, conduction loss due to the on-resistance of the devices,  $R_{ds,on}$ , switching loss due to device

(a) Buck schematic for subinterval 1,  $DT_s$ . (b) Buck schematic for Subinterval 2

(b) Buck schematic for Subinterval 2,  $(1-D)T_s$ .

Figure 2.7: Buck circuit configurations.

Figure 2.8: Buck operating waveforms.

| Operation Characteristics                  | Symbol                   |

|--------------------------------------------|--------------------------|

| Conversion Ratio, $\frac{V_{out}}{V_{in}}$ | D                        |

| Max. Switch Voltage                        | $V_{in}$                 |

| Max. rectifier voltage                     | $V_{in}$                 |

| Average Rectifier Current                  | $I_{out}D$               |

| Switch Utilization                         | $\frac{V_{out}}{V_{in}}$ |

Table 2.2: Buck Characteristics

output capacitance, conduction loss from the DCR of the output inductor, inductor core loss, inductor ac winding loss and gate charge loss, accounting for the charge required to turn the FET on and off. The conduction loss and output capacitance loss were calculated from the simulation, the core and winding loss were determined using Coilcraft's Power Inductor Analysis and Comparison Tool. The loss distribution is provided in Fig. 2.10. The overall efficiency of the converter was 87.2%. The leading loss is due to the inductor conduction loss from the inductor's parasitic resistance and core loss.

Table 2.3:

Buck Simulation Parameters

| $V_{in}$   | 48V  |

|------------|------|

| $V_{out}$  | 5V   |

| $I_{load}$ | 27A  |

| $f_s$      | 1MHz |

| D          | .104 |

Table 2.4: Values and components for buck design.

| Component | Name        | Rating           | Value                                                              |

|-----------|-------------|------------------|--------------------------------------------------------------------|

| $Q_1$     | EPC2001C    | 100V, 25A,       | $R_{ds,on} = 7 \mathrm{m}\Omega$                                   |

| $Q_2$     | EPC2023     | 30V, 60A         | $C_{oss}$ =450pF<br>$R_{dson}$ =1.3m $\Omega$<br>$C_{oss}$ =2400pF |

| inductor  | XAL1510-472 | $DCR=3.8m\Omega$ | 4.7μH                                                              |

Figure 2.9: SPICE simulated buck waveforms.

Figure 2.10: Loss distribution of designed buck converter.

#### **Buck Summary**

To improve the efficiency of this buck design, multiple devices could be used in parallel to reduce the conduction loss attributed to the device's on resistance and multiple inductors could be used in parallel to reduce the equivalent parasitic resistance of the output inductor. While adding devices in parallel will reduce the conduction loss it will increase the overall volume as well as increase switching losses such as turn-off loss, with every additional device added.

#### 2.7.2 Phase Shifted Full Bridge Design and Loss Analysis

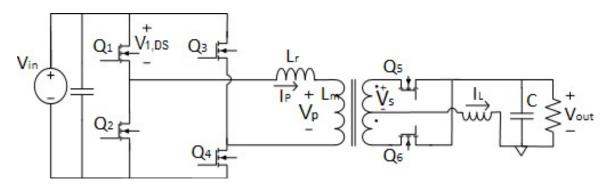

The PSFB design is more complex than the buck converter and requires more components leading to increased overall cost. The components required include four switches on the primary side, a transformer, and two diodes or synchronous switches on the secondary side. The phase shifted-full bridge circuit is provided in Fig. 2.11

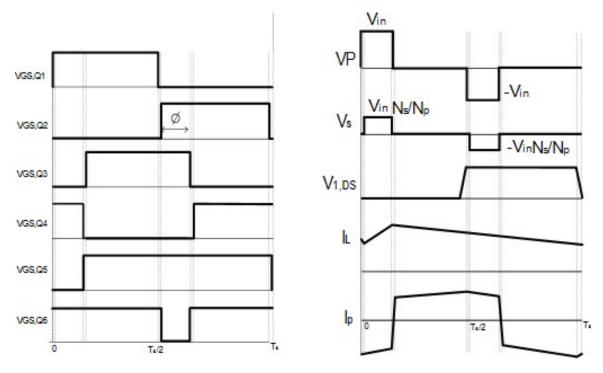

The phase shifted gate signals and operational waveforms are provided in Fig. 2.12. The basic operation entails,  $Q_1$  and  $Q_2$  switched at 50% duty cycles and 180° out of phase from

each other.  $Q_3$  and  $Q_4$  follow this same switching scheme and are phase shifted with respect to  $Q_1$  and  $Q_2$ . The amount of energy transferred depends on the phase-shift,  $\phi$ , or overlap between the diagonal switches of the  $Q_1/Q_2$  and the  $Q_3/Q_4$  leg. The leakage inductance,  $L_r$  resonates with the output capacitance of the devices and enables soft-switching. The synchronous devices on the secondary side act as a current rectifier followed by an output filter. The operating characteristics are provided in Table 2.5.

Figure 2.11: Phase shifted full bridge circuit.

Figure 2.12: Phase shifted full bridge waveforms.

Table 2.5: Phase shifted full bridge characteristics.

| PSFB Converter Operation Characteristics |                                                     |

|------------------------------------------|-----------------------------------------------------|

| Conversion Ratio                         | $\frac{N_s}{N_p} \frac{V_{out}}{V_{in}}$            |

| Pri. Side Max. Switch Voltage            | $V_{in}$                                            |

| Pri. Side Peak Switch Current            | $I_{out} \frac{N_s}{N_p}$                           |

| Max rectifier Voltage                    | $I_{out} \frac{N_s}{N_p} \\ V_{in} \frac{N_s}{N_p}$ |

| Average Rectifier Current                | $\frac{(I_{out})}{2}$                               |

When considering the PSFB design for a high output current application it is mandatory to replace the secondary side diode rectification with synchronous devices. This is due to the forward voltage drop,  $V_F$  of each diode. The losses caused by the forward voltage drop of the diode current rectification can greatly impact the overall efficiency. Loss due to the forward voltage drop of a diode rectifier can be calculated using Eq. 2.2.

$$P_{V_F} = V_F I_F \tag{2.2}$$

At high output currents, losses become detrimental to proper operation.

$$P_{synch.} = I^2 R_{ds,on} \tag{2.3}$$

In [?] the  $R_{ds,on}$  losses due to the synchronous rectifiers, calculated using Eq. 2.3 and switching losses of the synchronous FETs are shown to be less compared to loss from the forward voltage drop of the secondary rectifiers.

The leakage inductance of the transformer is leveraged to achieve zero voltage switching (ZVS) on all of the primary side devices by resonating with the output capacitance of the primary side devices. The resonant tank, consisting of the device output capacitance and transformer leakage inductance, is used to position zero volts across the switching device eliminating any loss due to simultaneous overlap of the switch current and voltage at each transition. It should be noted that ZVS is not achievable across the full load range, but is limited to the bounds of minimum output load and maximum input line voltage [42]. The duty cycle of the PSFB is determined by

$$D_{PSFB} = \frac{nV_{out}}{V_{in}} \tag{2.4}$$

Comparing Equation 2.4 to Equation 2.1 for the buck, the duty cycle is extended by the turns ratio, n. Assuming a phase shift of  $\phi = .4$ , the turns ratio of the transformer  $\frac{N_s}{N_p}$ , can be solved by

$$\frac{N_s}{N_p}\phi = \frac{V}{Vg} \tag{2.5}$$

From Equation 2.5 and the simulation parameters of Table 2.6 the turns ratio is approximately n=.25. Proper dead-time, dt, must be included in order for the converter to achieve ZVS this can be determine using the resonant frequency of the magnetizing inductance,  $L_m$ and output capacitance,  $C_{oss}$  of the primary side devices using the following equation,

$$f_r = \frac{1}{2\pi\sqrt{L_m 2C_{oss}}}\tag{2.6}$$

$$dt \ge \frac{\pi}{2}\sqrt{L_m(2C_{oss})} \tag{2.7}$$

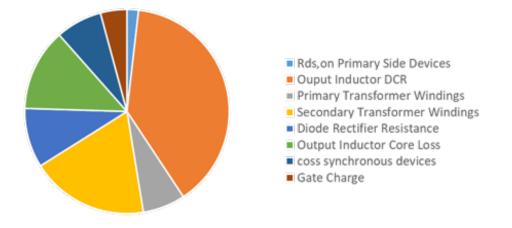

Using the parameters provided in Table 2.6 and the selected discrete components listed in Table 2.7, the design is verified in simulation. The results are provided in Fig. 2.13. The overall efficiency for the 135W design is 89.3%. The PSFB loss distribution is provided in Fig. 2.14.

Table 2.6:

PSFB Simulation Parameters

| $V_{in}$   | 48V              |

|------------|------------------|

| $V_{out}$  | 4.89V            |

| $I_{load}$ | 28.9A            |

| $f_s$      | $1 \mathrm{MHz}$ |

| D          | .365             |

| $C_r$      | 100 nF           |

| $N_s: N_p$ | 4:1              |

| Component       | Value                  | Rating           | Characteristics                                                                                                      |

|-----------------|------------------------|------------------|----------------------------------------------------------------------------------------------------------------------|

| Q1, Q2, Q3, Q4  | EPC2031                | 60V, 48A         | $\begin{array}{c} R_{ds,on} = 2.6 \mathrm{m}\Omega \\ C_{oss} = 940 \mathrm{pF} \\ Q_g = 16 \mathrm{nC} \end{array}$ |

| Q5, Q6          | EPC2023                | 30V, 60A         | $\begin{array}{c} R_{ds,on} = 1.3 \text{m}\Omega \\ C_{oss} = 2400 \text{pF} \\ Q_g = 19 \text{nC} \end{array}$      |

| Transformer     | coilcraft-RA7040       | 4:1              | $DCR_{pri} = 10.75 \text{m}\Omega$ $DCR_{sec} = 4.25 \text{m}\Omega$ $L_m = .55 \mu \text{H}$                        |

| Output inductor | coilcraft-SER2915L-222 | $2.2u\mathrm{H}$ | $DCR=2.5m\Omega$                                                                                                     |

Table 2.7: Components for Phase Shifted Full Bridge Design

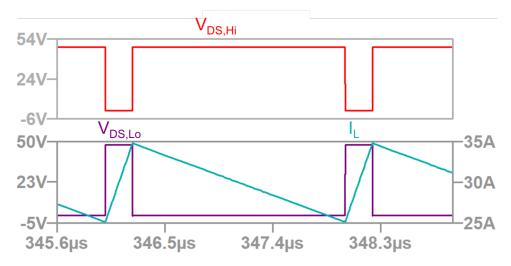

Figure 2.13: PSFB simulated waveforms.

Figure 2.14: Simulated PSFB loss breakdown.

### **PSFB Summary**

The loss distribution shows that over half of the losses are related to the output inductor and the transformer. Similar to the buck converter multiple inductors could be used in parallel to decrease conduction loss at the output, however power density will be reduced.

## 2.7.3 LLC Design and Loss Analysis

The LLC converter, illustrated in Fig. 2.15, is a widely used design that is capable of achieving high efficiencies for a wide load range. One advantage the LLC has in comparison to the PSFB is its ability to achieve soft-switching for all of the switching devices over the full load range where as the PSFB is limited in operation for maintaining ZVS. Due to the low switching losses of the LLC, the converter is able to operate at higher switching frequencies and can therefore use smaller passive components for increased power density. Additionally, in comparison to the PSFB which suffers from high-order harmonics on the secondary side currents requiring a large output inductor to reduce the current ripple, the LLC has the advantage of not needing an output inductor and can further increase its power density in comparison to the PSFB [70] [71].

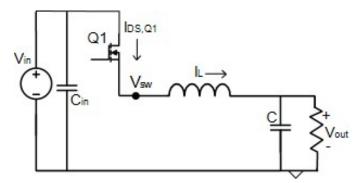

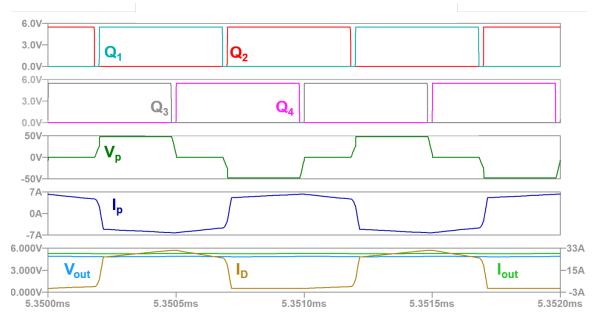

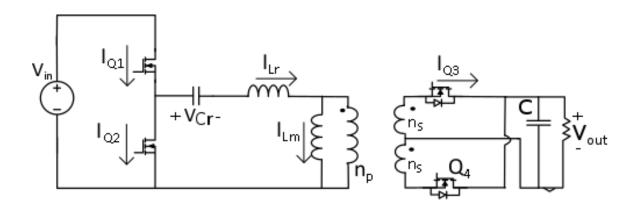

The LLC is a resonant converter, obtaining regulation through frequency modulation not pulse-width modulation. Compared to the PSFB the LLC requires the same amount of switches with the option to implement a half or full bridge on the primary or secondary. In this design a half bridge,  $Q_1$  and  $Q_2$ , is designed on the primary and synchronous switches,  $Q_3$  and  $Q_4$  are used on the secondary. As stated previously, each of the switches can achieve soft-switching enabling the LLC to operate at higher switching frequencies for increased power density. While the design of the converter is more complicated in comparison to the buck or PSFB, the basic operation shown in Fig. 2.15, is simple.  $Q_1$  and  $Q_2$  operate complimentary and generate a square wave voltage across the resonant tank. The reactive components,  $L_r$  and  $C_r$ , generate a sinusoidal current. The sinusoidal current is then rectified by the synchronous devices on the secondary side and sent through a low pass filter to the output. Zero-voltage switching is achievable on all devices and zero current switching (ZCS) is achievable on the secondary side devices. The resonant circuit is comprised of the primary side inductance,  $L_m$ , leakage inductance of the transformer,  $L_r$  and the device output capacitance,  $C_r$ . In order to reduce the size of the magnetics high frequency operation is needed. The disadvantage of operating at high frequencies however is this leads to increased AC loss in the magnetics. Other drawbacks of the transformer include core loss heating, large footprint and expensive implementation costs. For designs that include planar transformers, cost can by high due to multilayer PCBs and cutouts for transformer pieces. The loss breakdown of the LLC include the synchronous rectifier conduction loss, transformer loss, primary side conduction loss and resonant tank conduction loss.

The LLC was simulated using the characteristics for the selected devices listed in Table 2.8. The operating point and simulation parameters for the LLC design is provided in Table 2.9. The simulated waveforms are provided in Fig. 2.16. The overall efficiency for the 141W design was 95.6%.

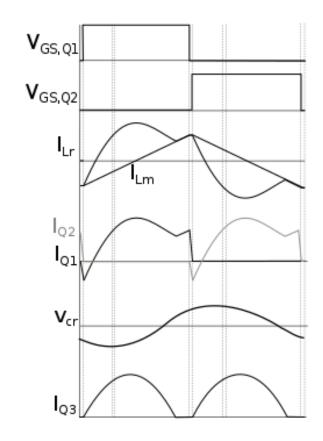

Figure 2.15: LLC operating waveforms.

| Component                                                       | Name                                                                                                                           | Rating                 | Characteristics                                                                                                       |

|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------|

| $Q_1, Q_2$                                                      | EPC2031                                                                                                                        | 60V, 48A               | $\begin{array}{c} R_{ds,on} = 2.6 \mathrm{m}\Omega \\ C_{oss} = 940 \mathrm{pF} \\ Q_g = 16 \mathrm{nC} \end{array}$  |

| $Q_3, Q_4$                                                      | EPC2023                                                                                                                        | 30V, 60A               | $\begin{array}{c} R_{ds,on} = 1.3 \mathrm{m}\Omega \\ C_{oss} = 2400 \mathrm{pF} \\ Q_g = 19 \mathrm{nC} \end{array}$ |

| $\begin{array}{c} C_r \\ L_r \\ \text{transformer} \end{array}$ | $\begin{array}{l} \text{Murata-}GCM21BR72A104KA37K\\ \text{coilcraft-}XEL6030-28ME\\ \text{coilcraft-}POE120PL-33 \end{array}$ | 100nF<br>280nH<br>24:5 | 100V, X7R, ESR= $30m\Omega$<br>DCR= $2.1m\Omega$<br>DCR= $5m\Omega$                                                   |

Table 2.8: Components for LLC Design

Table 2.9:

LLC simulation parameters.

| $V_{in}$   | 48V               |

|------------|-------------------|

| $V_{out}$  | 4.89V             |

| $I_{load}$ | 28.9A             |

| $f_s$      | 1MHz              |

| Lr         | $280 \mathrm{nH}$ |

| Cr         | 100 nF            |

| $N_s: N_p$ | 24:5              |

Figure 2.16: LLC simulated waveforms.

#### Summary of LLC

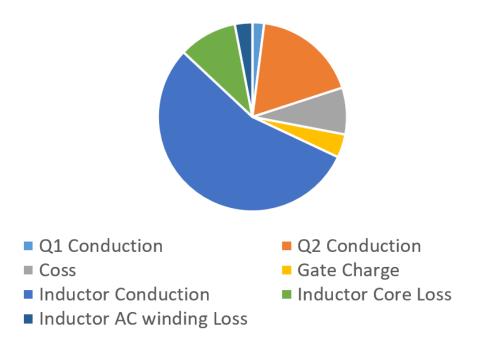

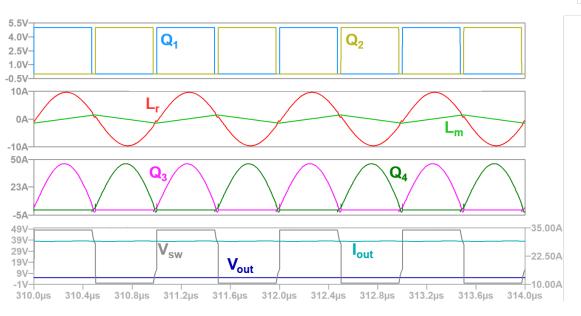

The simulated LLC loss breakdown in Fig. 2.17 shows that the transformer and the synchronous secondary devices are the largest contributors of loss. In [72] a matrix transformer is used with enhanced termination loop for the synchronous rectifier using a non uniform winding structure. AC losses such as proximity effect, skin effect and termination loss can be improved through magnetic manufacturing [73] [74] [75].

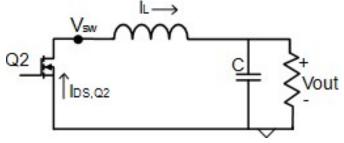

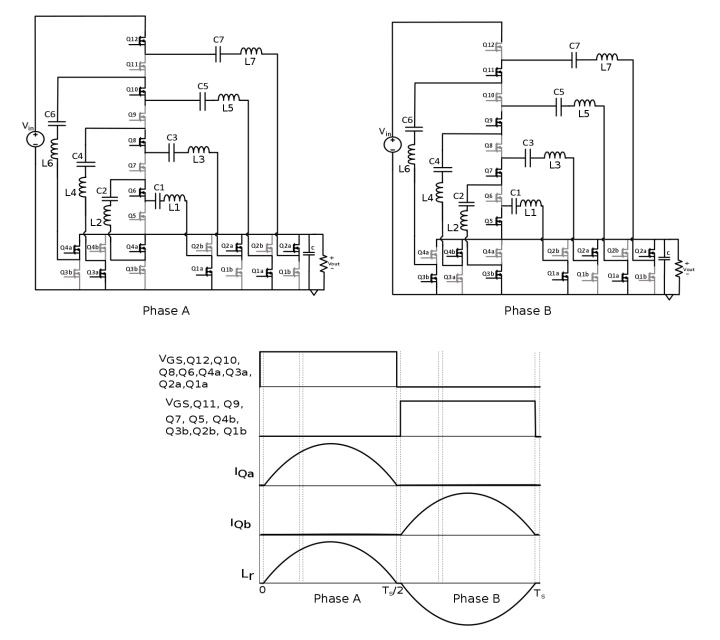

## 2.7.4 Switched Tank Design and Loss Analysis

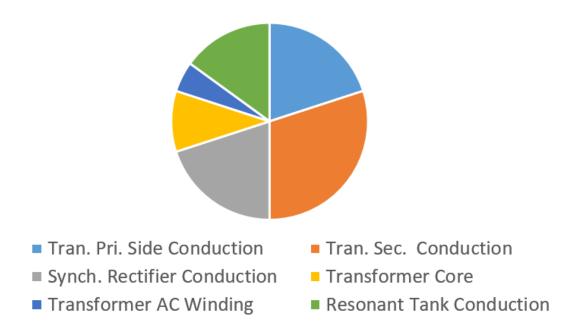

The advantage that the STC has over the previous topologies, is it does not require a large output inductor or bulky transformer. The disadvantage is that the STC requires many more switches than the previous designs. However, each device has low voltage stress helping to reduce switching loss. While no transformer is needed, small inductors are used to create resonant currents. The sinusoidal resonant currents enable zero-current switching. While many switches are needed the switching scheme is simple, each half-bridge operates with complimentary gate signals that are 180 deg out of phase. The circuit subintervals and corresponding waveforms are provided in Fig. 2.18.

Figure 2.17: LLC loss distribution.

The resonant frequency is determined using Equation 2.8. The resonance occurs between the capacitor and inductor in series in each branch.

$$f_r = \frac{1}{2\pi\sqrt{LC}}\tag{2.8}$$

Using the discrete devices used in Table 2.11, the STC topology was simulated and the corresponding waveforms are provided in Fig. 2.19 with a summary of the simulated waveforms given in Table 2.10. The overall efficiency for the 179W design is 93.6%.

#### STC Summary

The loss breakdown in Fig. 2.20 shows that the combined conduction loss of the resonant tank capacitors and devices are the dominant loss mechanism. This can be improved by paralleling more capacitors for a decreased equivalent ESR, but will require re-design of the resonant tank and switching frequency. Furthermore, added capacitors will decrease power density and increase the design cost.

Figure 2.18: Switched-tank converter subintervals and waveforms.

| Simulated Parameters |                    |

|----------------------|--------------------|

| $V_{in}$             | 48V                |

| $V_{out}$            | $5.87\mathrm{V}$   |

| $I_{load}$           | 28.7A              |

| $f_s$                | $328 \mathrm{kHz}$ |

| $I_{Q11,pk}$         | 11.9A              |

| $I_{Q11,rms}$        | 5.9A               |

Table 2.10:

STC Simulation Parameters

Table 2.11: Components for STC Design

| Component  | Value               | Rating            | Characteristics                    |

|------------|---------------------|-------------------|------------------------------------|

| GaN device | EPC2023             | 30V, 60A          | $R_{ds,on} = 1.3 \mathrm{m}\Omega$ |

|            |                     |                   | $C_{oss} = 2400 \text{pF}$         |

|            |                     |                   | $Q_g = 19 \text{nC}$               |

| $C_r$      | C3225X7S2A475K200AB | $4.7 \mu F, 100V$ | X7S, $ESR=5m\Omega$                |

| $L_r$      | LP02-500-1S         | 50nH, 50A         | $DCR=.22m\Omega$                   |

Figure 2.19: STC simulated waveforms.

Figure 2.20: STC simulated waveforms.

## 2.7.5 Topology Comparison and Summary

While the designed buck converter required the fewest number of devices, the efficiency was the lowest. For the buck design a large inductor was needed to reduce the inductor current ripple. Due to the large inductance the series resistance was high as well causing high conduction loss of the output inductor. While the PSFB has better efficiency the greatest loss is similarly attributed to the output inductor series resistance. The resonant converters eliminate the need for an output inductor and instead conduction losses for the resonant tank largely contribute to the overall power loss. For this high output current application, series resistance from magnetics, whether at the output or in the resonant tank are a common loss mechanism across each of the converters simulated.

# Chapter 3

# Switched Capacitor Converters

SC converters use capacitors to store and transfer energy instead of inductors. The energy storing capacitors, commonly called flying capacitors,  $C_{fly}$ , transfer power by alternately connecting the source to the load or another capacitor. The following sections cover the fundamentals of switched capacitor circuits and their inherent loss.

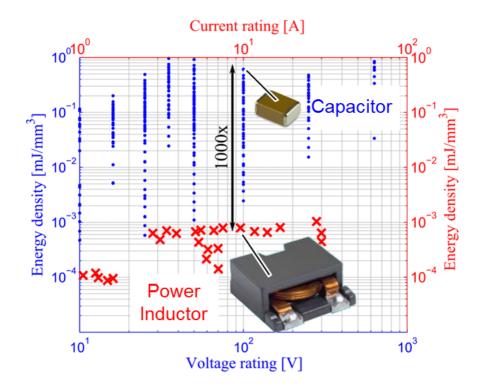

# 3.1 Energy Density of Capacitors

Today's capacitor dielectric materials allow capacitors to exceed the power density of inductors [76]. In [77], a detailed analysis of available surface mount discrete components was performed and the results show that capacitors have substantially higher energy and power density than inductors. For example, a  $1\mu$ F T-Y Ceramic capacitor was 149x more energy dense than the  $10\mu$ H Coilcraft SMT inductor it was compared to. Fig. 3.1 compares the energy density of shielded inductors and ceramic capacitors, confirming that capacitors can provide increased energy density [78].

Figure 3.1: Energy density comparison of ceramic capacitors and inductors [4].

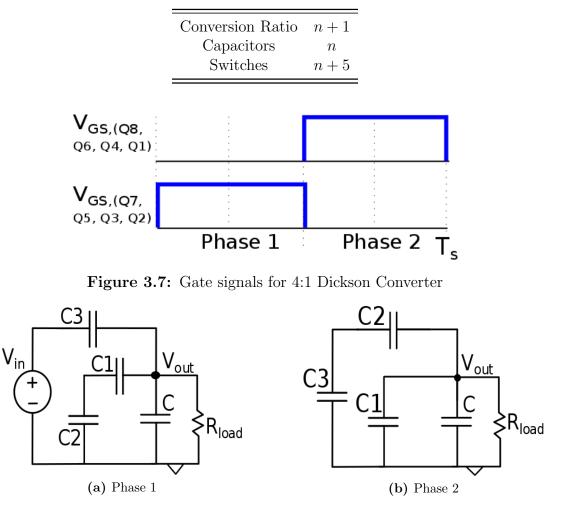

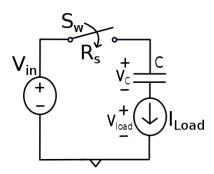

# 3.2 Ideal Simplified Switched Capacitor Model

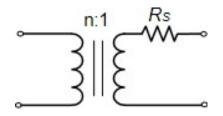

A simplified model for the switched capacitor converter is presented in Fig.3.2 [?]. The ideal SCC model uses a transformer to represent the voltage conversion and an output impedance representing the losses and output variation. For switched capacitor converters, the output impedance is a measure of performance and power loss.

Figure 3.2: Basic Model for a switched capacitor converter.

The transformer turns ratio represents the unloaded conversion ratio of the converter. When the ideal converter is connected to a load, there is a voltage drop across  $R_s$ , due to charge transfer and conduction loss.

There are two asymptotic limits to  $R_s$ , the slow switching limit, SSL and the fast switching limit, FSL. The ideal SSL and FSL output impedance asymptotes along with the corresponding capacitor current wave-shapes, are plotted in Fig. 3.3. For SSL, the capacitors are able to fully equilibrate during each switching cycle and the charge transfer is impulsive, resulting in high current spikes. When a SC converter is operating in the SSL region,  $R_s$  is determined by switching frequency and capacitance. For the FSL region of operation, when the switching frequency exceeds the critical frequency,  $f_{crit}$ , the output resistance becomes independent of frequency. The capacitor voltages remain constant due to the nature of high switching frequency and current flow is constant. When operating in FSL,  $R_s$  is determined by the device on-resistance,  $R_{ds,on}$ , capacitor ESR and other parasitic resistances in the charge transfer path [79]. The optimal design is at the intersection of the SSL and FSL. The analytical expressions for the output impedance for the two operating regions of a SCC are provided in Equations 3.1 and 3.2. The charge flow coefficient for each capacitor and switch,  $a_{r,i}$ , correspond to charge flows that occur immediately after the switches are closed to initiate each respective phase of the SC and are derived in [5].

$$R_{SSL} = \sum \frac{(a_{r,i})^2}{C_i f_{sw}} \tag{3.1}$$

$$R_{FSL} = 2\sum R_i ((a_{r,i})^2)$$

(3.2)

Charge sharing determines  $R_{SSL}$  so the next section will analyze the effects of charge-sharing and the losses that are inherent for operation in the SSL region.

## 3.3 Hard-Charging Loss

As stated in the previous section when operating in SSL, hard-charging losses are the dominant loss mechanism. In this section a basic capacitor charge sharing scenario and the inherent loss is described.

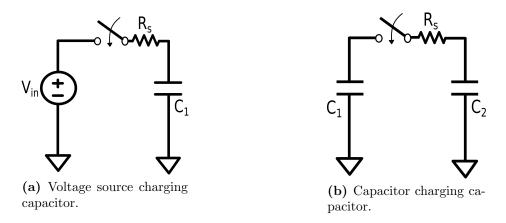

Hard charging loss, also known as charge sharing loss, occurs when two capacitors, or a voltage source and a capacitor, with a difference in voltage,  $\Delta V_{diff}$ , are shorted together. The basic capacitor charging scenarios are provided in Fig. 3.4.

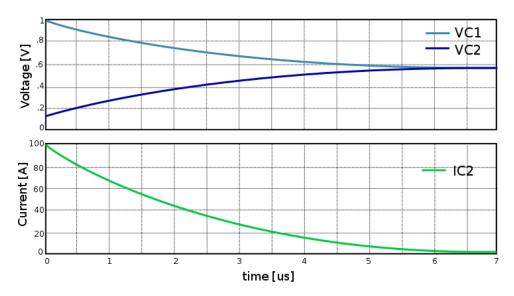

As stated in [6], after the switch is closed between the two capacitors in Fig. 3.14b, "The capacitor voltage can not change instantaneously and the mismatch of the initial capacitor voltage will be present across the series resistance,  $R_s$ , resulting in a large instantaneous current," as shown in Fig. 3.5. This can be described analytically in Equation 3.3. Where  $C_{eq}$  is the equivalent series and parallel capacitance seen at the output.

$$I_C = \frac{\Delta V_{diff}}{R_s} e^{\frac{-t}{R_s C_{eq}}} \tag{3.3}$$

Due to the voltage difference,  $\Delta V_{diff}$ , the rate of change in voltage across the capacitor is extremely high causing the current in the capacitor,  $I_c$  to be very high with a decay rate related to the time constant of the series resistance,  $R_s$  and capacitance,  $C_{eq}$ .

Assuming that the time constant,  $\tau = R_s C_{eq} \ll T_s$ , such that the converter is operating in the SSL region, the power loss for hard-charging for the scenarios of Fig. 3.4 can be related

Figure 3.3: Output impedance vs. switching frequency [5].

Figure 3.4: Basic capacitor charging scenarios.

Figure 3.5: Capacitor voltages and current waveforms in the charge redistribution process [6].

to the average current,  $I_{avg}$ . The average current can be calculated using Equations 3.4 to Equation 3.7.

$$\frac{d(Q)}{dt} = I_{avg} \tag{3.4}$$

$$I_{avg} = C_1 \frac{(V_{in} - V_1)}{T_s} = \frac{C_1 \Delta V}{T_s}$$

(3.5)

$$R_{eq} = \frac{\Delta V}{I_{avg}} = \frac{T_s}{C_1} = \frac{1}{f_s C_1} \tag{3.6}$$

$$P_{HC} = \frac{(\Delta V)^2}{R_{eq}} = f_s C_1 (\Delta V)^2$$

(3.7)

Notice that this inherent charge transfer loss does not depend on the series resistance,  $R_s$ . Therefore, a lower  $R_{ds,on}$  or decreased parasitic resistance will only result in an increased current spike over a shorter time, but the total power loss in each charge cycle will remain the same [80]. Instead the change in energy stored in the capacitors and the losses of the charging process are a function of the voltage mismatch,  $\Delta V_{diff}$ , and capacitance.

For a constant current load where  $I_{rms}=I_{avg}$ , the mismatch is related to how much charge each capacitor transfers in the previous subinterval of the switching period. The voltage mismatch is proportional to the load current or the charge drawn from the load and inversely proportional to the capacitor values. Using the relationship between voltage and current in a capacitor,

$$I_C = C \frac{dV}{dt} \tag{3.8}$$

equations 3.9 and 3.10, presented in [6] summarize the relationship between the capacitor voltage difference, switching frequency and capacitance. From Equation 3.10 we see that for a constant capacitor current, losses due to hard-charging can be decreased by increasing the switching frequency,  $f_s$  or the capacitance,  $C_{fly}$ . While a higher  $f_s$  would allow smaller passives to be used, drawbacks of increasing the switching frequency or capacitance include, increased switching loss, difficulty with control, achieving precise timing intervals, increased capacitor size and increased cost.

$$\Delta V \propto \frac{1}{f_s}, \frac{1}{C_{fly}} \tag{3.9}$$

$$P_{loss} \propto \frac{1}{f_s}, \frac{1}{C_{fly}} \tag{3.10}$$

Therefore, it is desirable to minimize the capacitor voltage mismatch,  $\Delta V$ , without increasing  $f_s$  or  $C_{fly}$  [6]. This is achieved with the ideal hybrid Dickson switched capacitor topology and will be addressed in a later section.

## 3.4 Dickson Topology

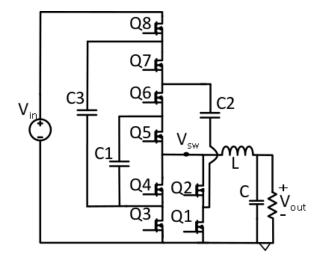

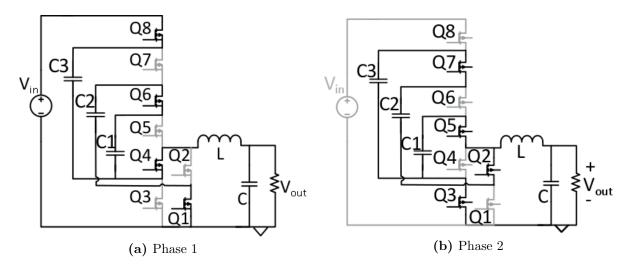

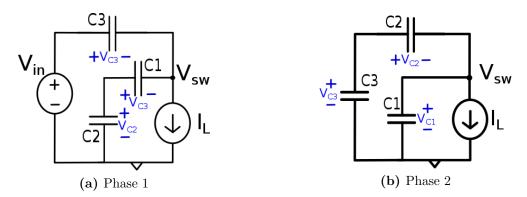

The hybrid Dickson switched capacitor circuit is derived from the original Dickson topology [61]. The 4:1 Dickson topology, provided in Fig. 3.6 has two switching intervals which will be referred to as phases. Each phase lasts half of the switching period. The corresponding gate signals for the circuit are provided in Fig. 3.7. The simplified circuits for subintervals 1 and 2, are provided in Fig. 3.8. The characteristics of the Dickson topology design are described in Table 3.1. The basic operation of the Dickson Converter is summarized below.

Figure 3.6: 4:1 Dickson Topology

Figure 3.8: 4:1 Dickson topology for each phase of the switching period.

#### Subinterval 1

$Q_1, Q_4, Q_6$  and  $Q_8$  turn-on and the input voltage,  $V_{in}$  charges  $C_3$ .  $C_2$  discharges into  $C_1$ . Each branch discharges to the load.

#### Subinterval 2

$Q_2$ ,  $Q_3$ ,  $Q_5$  and  $Q_7$  turn-on and the previously on switches turn-off.  $C_3$  is now connected in series to  $C_2$ .  $C_1$  is connected to the load, in parallel with the branch containing  $C_2$  and  $C_3$ .  $C_3$  which was just charged in the previous subinterval, discharges into  $C_2$  which discharges to the load. In a parallel branch  $C_1$  also discharges to the load.

#### Advantages and Limitations of the Dickson

One advantage of the Dickson switched capacitor converter is its low switch stress [81] [82]. The bottom switches,  $Q_1 - Q_4$ , are rated for  $V_{out}$  while the upper switches,  $Q_5 - Q_8$  are rated for  $2V_{out}$ . Admittedly, other switched capacitor circuits such as the ladder topology, also have similar switch utilization, but the ladder topology requires more flying capacitors and is therefore less appealing for the design [83]. Limitations to the Dickson include it's inability to regulate the output voltage [6] and low capacitor utilization [84]

. Regarding voltage regulation, instead of being able to regulate the output voltage, the conversion ratio is fixed, and is determined by the circuit topology. This results in loss as the load changes. Capacitor utilization [82] provides a way to quantify the capacitor's ability to effectively utilize energy. The constraint can be calculated as

$$E_{tot} = \sum_{i} \frac{1}{2} (V_{C,i(rated)})^2 (C_i)$$

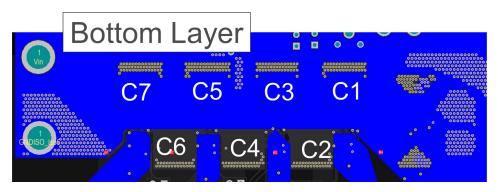

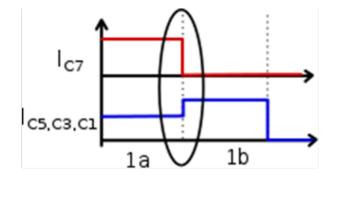

(3.11)

where  $C_i$  is the value of the capacitor and  $(V_{C,i(rated)})$  is the voltage rating of the capacitor. A capacitor's utilization, or energy storage capability, is related to the voltage rating which corresponds to the volume and price of the capacitor [82]. To decide whether switch utilization should take priority over capacitor utilization the cost of devices and capacitors can be considered. Since capacitors are less expensive than devices it was decided that switch utilization should be higher in order to reduce converter cost. Each of the flying capacitors in the Dickson converter requires a different voltage rating related to a fraction of the input voltage. The capacitor voltage ratings for the 4:1 are provided in Table 4.1. The capacitor DC bias is derived using the charge-flow voltage vector in a later section. In Section 3.3, the impact on efficiency due to hard-charging loss was

Table 3.2:

4:1 Dickson Capacitor Voltage Rating

| Component                                        | Rating                                                          |

|--------------------------------------------------|-----------------------------------------------------------------|

| $\begin{array}{c} C_3 \\ C_2 \\ C_1 \end{array}$ | $\frac{\frac{3V_{in}}{4}}{\frac{V_{in}}{2}}$ $\frac{V_{in}}{4}$ |

introduced. To determine whether a circuit can achieve soft-charging, where hard-charging losses are eliminated, KVL equations in each interval must be satisfied at all times [85] including during phase transitions. In the original Dickson, since the output capacitance does not allow instantaneous change in the output voltage, the KVL equations can not be satisfied for each phase. As a result, there is a mismatch in capacitor voltage during each phase transition. This mismatch causes high transient currents as demonstrated in Fig. 3.5. This is characteristic of a converter operating in the slow switching limit, where efficiency is dominated by voltage mismatch losses and result in low efficiency [86].

## Original Dickson Topology Summary

The Dickson converter has the advantage of low switch stress and the disadvantage of low capacitor utilization and hard-charging loss. The next section will discuss steps that can be taken in order to eliminate the hard-charging loss.

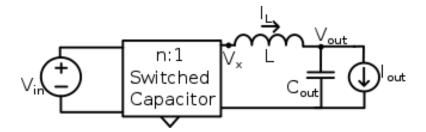

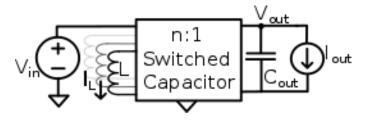

# 3.5 Reducing Hard-Charging Loss by Adding an Output Inductor