University of Tennessee, Knoxville Trace: Tennessee Research and Creative Exchange

# Masters Theses

Graduate School

5-2007

# Traceable Standard for Sub - 100nm Metrology

Sachin Jayant Deo University of Tennessee - Knoxville

#### **Recommended** Citation

Deo, Sachin Jayant, "Traceable Standard for Sub - 100nm Metrology." Master's Thesis, University of Tennessee, 2007. https://trace.tennessee.edu/utk\_gradthes/276

This Thesis is brought to you for free and open access by the Graduate School at Trace: Tennessee Research and Creative Exchange. It has been accepted for inclusion in Masters Theses by an authorized administrator of Trace: Tennessee Research and Creative Exchange. For more information, please contact trace@utk.edu.

To the Graduate Council:

I am submitting herewith a thesis written by Sachin Jayant Deo entitled "Traceable Standard for Sub - 100nm Metrology." I have examined the final electronic copy of this thesis for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Master of Science, with a major in Materials Science and Engineering.

David C. Joy, Major Professor

We have read this thesis and recommend its acceptance:

Philip D. Rack, Michael L. Simpson

Accepted for the Council: <u>Dixie L. Thompson</u>

Vice Provost and Dean of the Graduate School

(Original signatures are on file with official student records.)

To the Graduate Council:

I am submitting herewith a thesis written by Sachin Jayant Deo entitled "Traceable Standard for Sub - 100nm Metrology." I have examined the final electronic copy of this thesis for form and content and recommend that it be accepted in partial fulfillment of the requirements of the degree of Master of Science, with a major in Materials Science and Engineering.

David C Joy

Major Professor

We have read this thesis and recommend its acceptance:

Philip D Rack

Michael L Simpson

Accepted for the Council:

Linda Painter

Interim Dean of Graduate Studies

(Original signatures are on file with official student records)

# **TRACEABLE STANDARDS FOR Sub – 100 nm METROLOGY**

A THESIS PRESENTED FOR THE MASTER OF SCIENCE DEGREE THE UNIVERSITY OF TENNESSEE, KNOXVILLE

> SACHIN JAYANT DEO MAY 2007

This work is dedicated to my family, colleagues and friends

# Acknowledgement

The author would like to thank his thesis advisor Dr. David C. Joy for his guidance and support throughout the course of the research work.

The author would like to extend acknowledgement to Semiconductor Research Corporation (SRC), which supports this research work. SRC Task ID: 1281.001, Project Monitor: Dr. Daniel Herr.

Thanks to Dr. Mark Davidson for providing the "Measure" software, and Maggie Connaster for her help during the course of the research work.

The author would like to extend acknowledgement to the colleagues and members of the Electron Beam Facility at the University of Tennessee, Knoxville. Finally, the author would like to extend his gratitude to the University of Tennessee, Knoxville.

# Abstract

As we approach the 65nm technological node, transistor gates with dimensions of the order of 40nm are being manufactured. As the device performance is directly related to the dimensions of the gate, critical dimension (CD) control becomes an important part of the fabrication process. Characterization of these small feature size, generally referred to as *Metrology*, is an indispensable ingredient of the semiconductor manufacturing processes. *Metrology* relies not only on the precision, but also the accuracy of commercially used metrology tools like the CD-SEM. To facilitate the magnification calibration of the CD-SEM, an easy access to standard reference artifact traceable to international specifications is an added advantage. Considerable literature is available for CD-SEM, which relies on in-house artifacts or general test objects. The absence of commercially available artifacts hinders evaluation of different CD-SEM. To facilitate for the sub-100nm metrology, which can be made available in wafer form at low cost.

In this work, artifacts have been designed and fabricated for precise magnification calibration of the CD-SEM. The designing of the artifacts takes into account the *proximity effect*, a problem associated with the e-beam exposure, to produce dense grid type structure in the sub-100nm region. The structures are fabricated using the e-beam lithography tool, operated at 50KeV. The artifacts have been fabricated on a thin layer of negative resist HSQ spun on silicon substrate. Subsequent development in 0.26N TMAH gives a structure on silicon wafer, thereby eliminating contamination issues.

Furthermore, characterization of the artifacts for line pitch determination is carried out using "Measure" (Spectel Corp.), which provides an absolute calibration of the image pixel size that can then be used to measure other features. The low values for the line edge roughness (LER) further facilitate precise linewidth metrology.

| Chapter                                           | Page |

|---------------------------------------------------|------|

| 1. Introduction                                   |      |

| 1.1 Introduction                                  | 1    |

| 1.2 Overview of the lithography process           | 2    |

| 1.3 Scope of the Project.                         | 11   |

| 2. Literature Review                              |      |

| 2.1 Semiconductor Substrates                      | 13   |

| 2.1.1 Czochralski Growth                          | 13   |

| 2.1.2 Wafer Preparation and Specification         | 16   |

| 2.2 High Resolution Lithography System            | 18   |

| 2.2.1 Optical Lithography                         | 19   |

| 2.2.2 Next Generation Lithography (NGL)           | 21   |

| 2.2.2.1 X-Ray Lithography                         | 21   |

| 2.2.2.2 Ion-Beam Projection                       | 21   |

| 2.2.2.3 Extreme UV Lithography                    | 21   |

| 2.2.3 Electron Beam Lithography                   | 24   |

| 2.2.3.1 Principle of Electron Beam Lithography    | 24   |

| 2.2.3.2 JBX 6000 FS/E – Direct Write Lithography  | 27   |

| 2.3 Electro-Solid Interaction.                    |      |

| 2.4 Proximity Effect in Electron Beam Lithography |      |

| 2.5 Resist Technology                             | 40   |

| 2.5.1 Photoresists                                | 42   |

# **TABLE OF CONTENTS**

| 2.5.2 Electron Beam Resists                   |

|-----------------------------------------------|

| 2.5.2.1 Polymethyl Methacrylate (PMMA)49      |

| 2.5.2.2 Hydrogen Silsesquioxane (HSQ)52       |

| 2.6 Lithography process flow                  |

| 2.6.1 Cleaning of wafers                      |

| 2.6.2 Spinning resist on wafers               |

| 2.6.3 Baking of the resist                    |

| 2.6.4 Exposure of the resist                  |

| 2.6.5 Developing of the resist                |

| 2.6.6 Imaging and Metrology70                 |

| 2.6.6.1 Critical Dimension – SEM (CD- SEM)72  |

| 3. Experimental Procedures                    |

| 3.1 Selection and Designing of the artifact77 |

| 3.1.1 Selection of the artifact               |

| 3.1.2 Designing of the artifact               |

| 3.2 Fabrication of the artifact               |

| 3.2.1 Fabrication in positive resist – PMMA   |

| 3.2.2 Fabrication in negative resist – HSQ    |

| 4. Results and Discussion                     |

| 4.1 Results                                   |

| 4.2 Discussion                                |

| 5. Future Work                                |

| 5.1 Commercial Applications                   |

| 5.2 Future Work | 115 |

|-----------------|-----|

| References      | 116 |

| Vita            | 122 |

# LIST OF FIGURES

| Fig  | ure                                                                 | Page |

|------|---------------------------------------------------------------------|------|

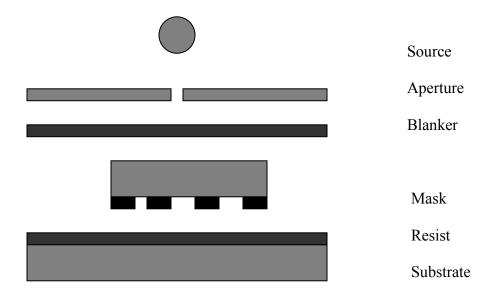

| 1.1  | Schematic representation of the lithography process                 | 3    |

| 1.2  | Minimum chip size and area versus time                              | 6    |

| 2.1  | Czochralski growth for silicon wafers                               | 15   |

| 2.2  | Wafer orientation indicated with primary and secondary flats        | 17   |

| 2.3  | Schematic of a simple optical lithography system                    | 20   |

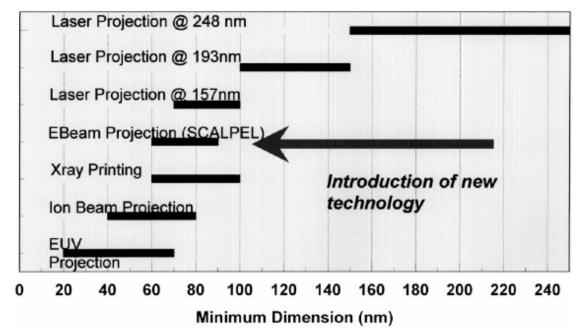

| 2.4  | Potential introduction of new resolution lithography tools          | 20   |

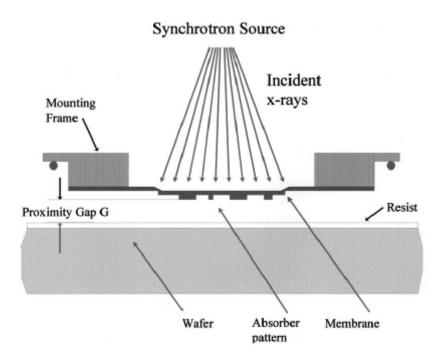

| 2.5  | Schematic view of X-Ray lithography                                 | 22   |

| 2.6  | Schematic of experiment X-Ray lithography                           | 23   |

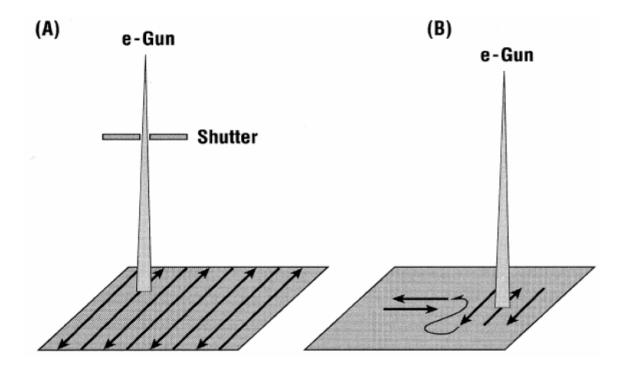

| 2.7  | Comparing of scanning methodologies (A) Raster Scan (B) Vector Scan | 26   |

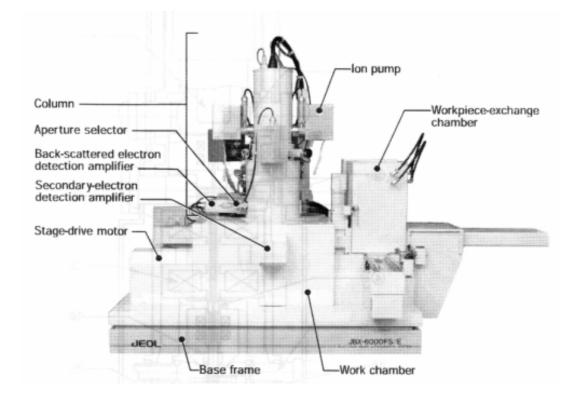

| 2.8  | Electron Beam Lithography tool – JBX 6000 FS/E (JEOL)               | 28   |

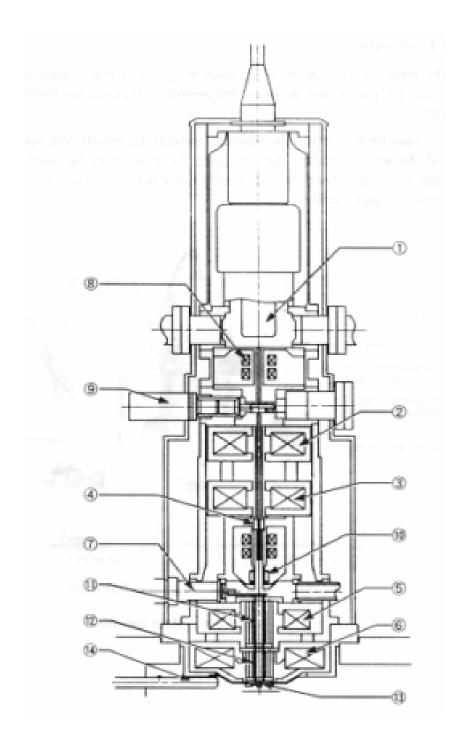

| 2.9  | Main Console for JBX 6000 FS/E                                      | 29   |

| 2.10 | Gun Column of JBX 6000 FS/E                                         | 30   |

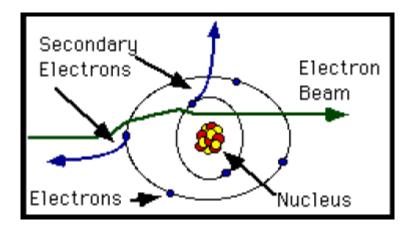

| 2.11 | Secondary electron scattering                                       | 35   |

| 2.12 | 2 Backscattered electron scattering                                 | 35   |

| 2.13 | 3 Monte Carlo simulation for 50 keV electron beam                   | 37   |

| 2.14 | Chemical structure for positive photoresist – DQN                   | 43   |

| 2.15 | 5 Chemical structure for negative photoresist – SU-8                | 45   |

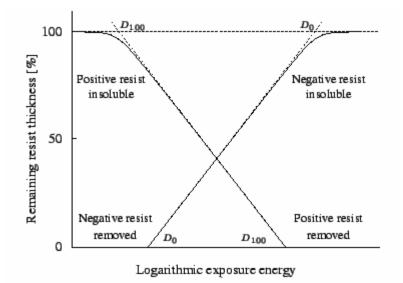

| 2.16 | 5 Schematic representation of basic resist mechanism                | 47   |

| 2.17 | 7 Positive resist and Negative resist profile                       | 48   |

| 2.18 | Chemical structure of PMMA: pre development and post development    | 50   |

| 2.19 | Chemical structures of HSQ (a) cage form (b) network form           | 53   |

| 2.20 Contrast curves for both positive and negative resists                             | 55                   |

|-----------------------------------------------------------------------------------------|----------------------|

| <b>2.21</b> Flow sheet for the lithography process                                      | 58                   |

| 2.22 Schematic representation of resist spinning                                        | 60                   |

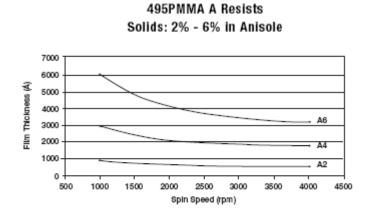

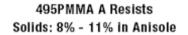

| 2.23 Spin curves for 495K PMMA formulated in Anisole                                    | 61                   |

| 2.24 Spin curves for 950K PMMA formulated in Anisole                                    | 62                   |

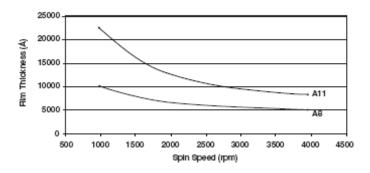

| 2.25 Baking of the resist spun on the wafer                                             | 64                   |

| <b>2.26</b> CEE 100CB for spinning and baking                                           | 64                   |

| 2.27 Schematic diagram showing development process for both positive and                | d negative           |

| resist                                                                                  | 69                   |

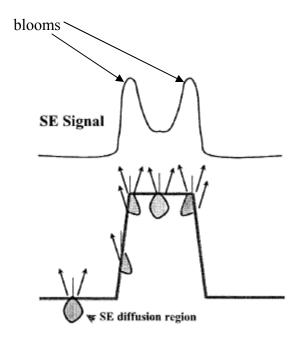

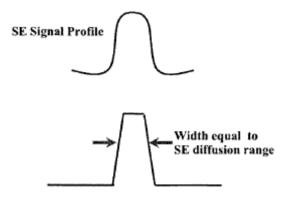

| 2.28 Schematic representation of signal intensity at the line edges                     | 75                   |

| <b>2.29</b> Schematic representation of the resolution of the CD-SEM                    | 75                   |

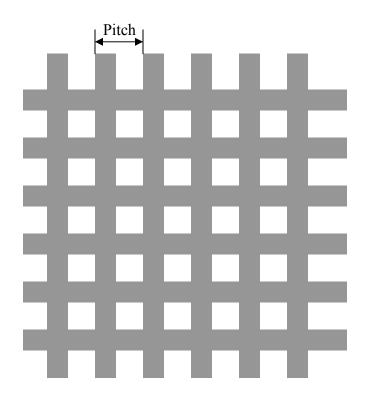

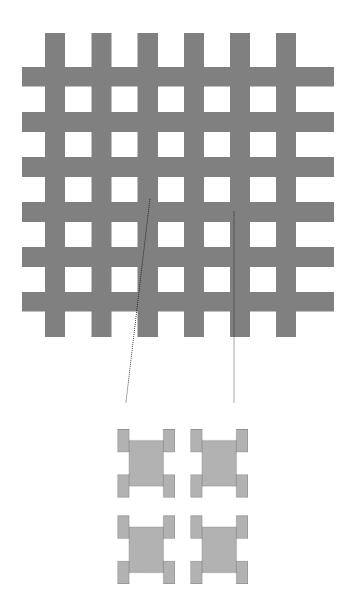

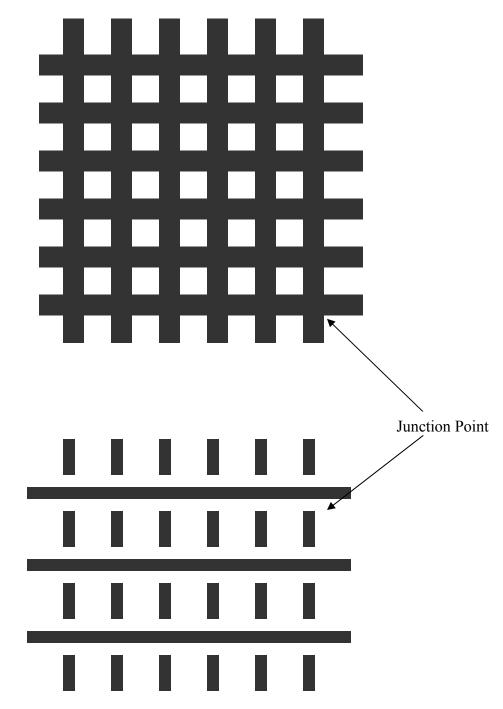

| <b>3.1</b> Schematic design of dense array of lines                                     | 79                   |

| <b>3.2</b> Proximity correction based on shape modulation                               | 81                   |

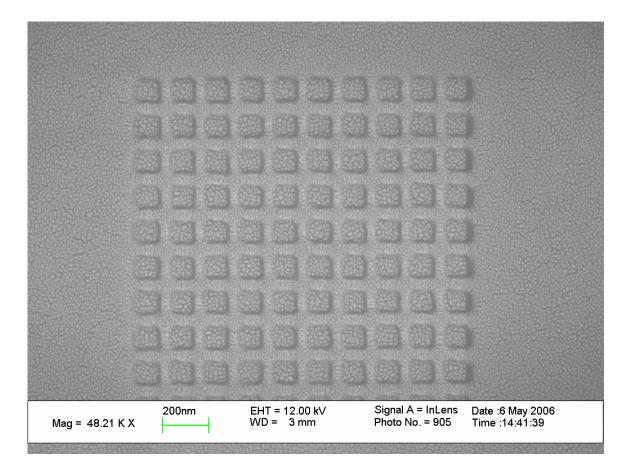

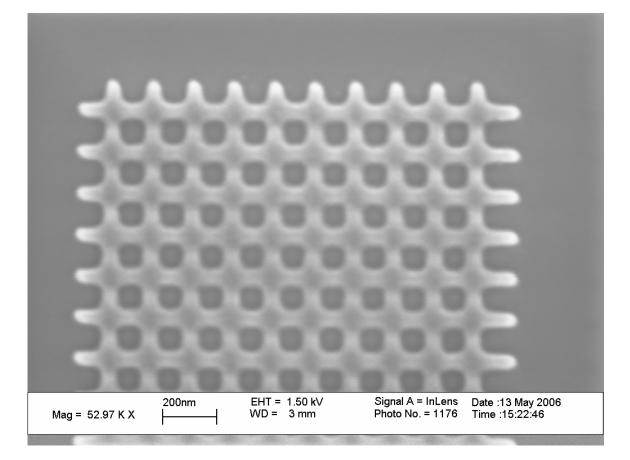

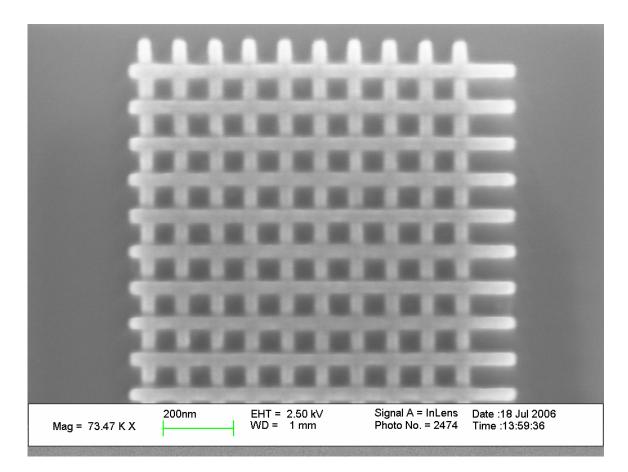

| <b>3.3</b> SEM micrograph of 500 nm pitch artifact in PMMA                              | 85                   |

| <b>3.4</b> LEO <sup>®</sup> 1525 FEG SEM, Carl Zeiss, Thornwood, NY                     | 87                   |

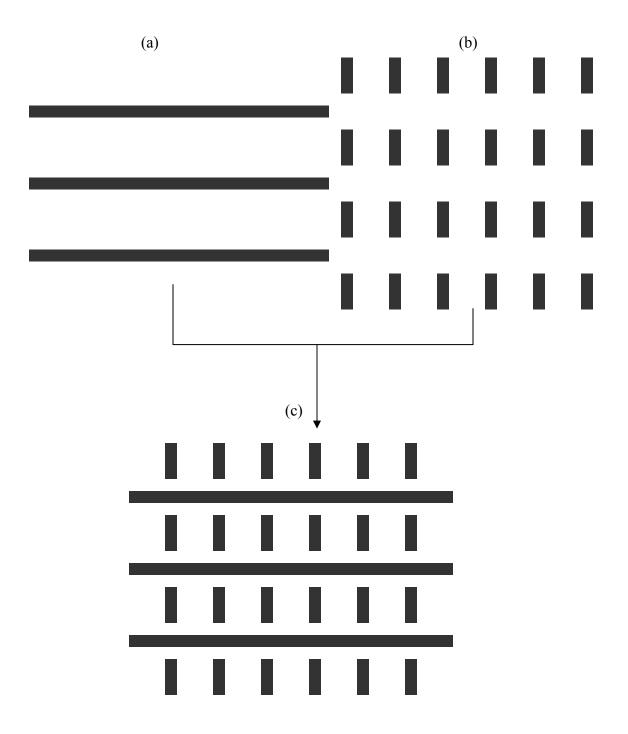

| <b>3.5</b> Schematic representation of shape modulation for proximity correction        | 89                   |

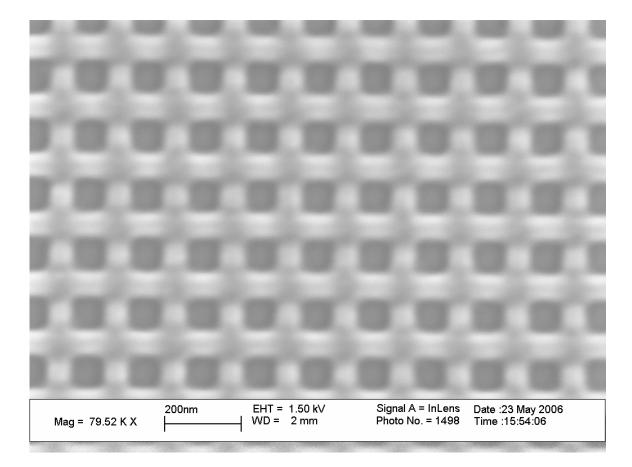

| <b>3.6</b> SEM micrograph of 150 nm pitch artifact in PMMA                              | 90                   |

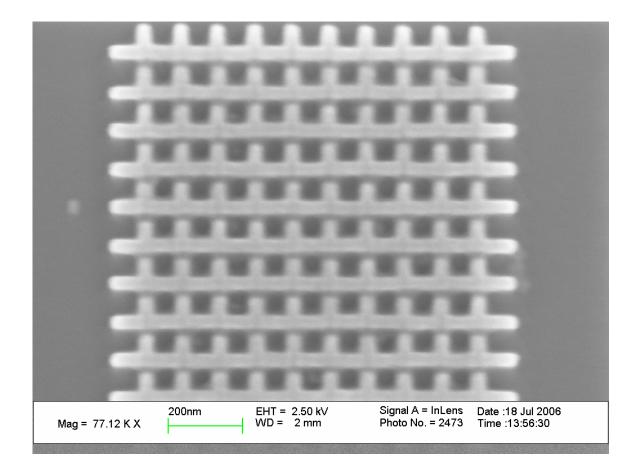

| <b>3.7</b> (A) SEM micrograph for 100nm pitch artifact (B) Sub-100nm artifact in PM     | 1MA92                |

| <b>3.8</b> Schematic representation incorporating the proximity correction into the de  | sign of the          |

| artifact                                                                                | 98                   |

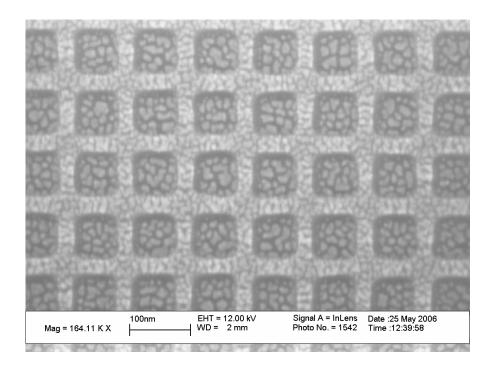

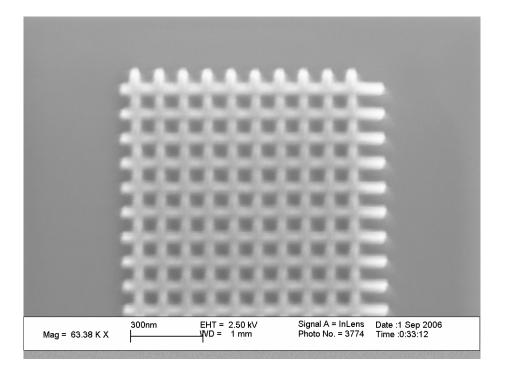

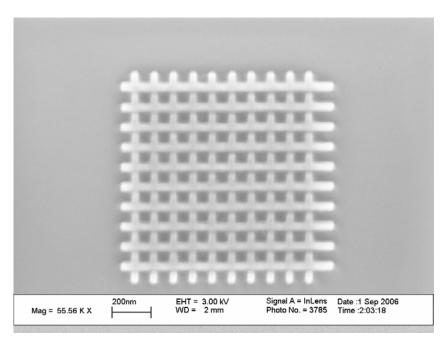

| <b>3.9</b> Calibration artifact with a pitch of 150 nm, and with dose in the range of 5 | 20µC/cm <sup>2</sup> |

| $-780\mu$ C/cm <sup>2</sup>                                                             |                      |

| <b>3.10</b> Calibration artifact with a pitch of 150 nm, and with dose in the range of $800\mu$ C/cm <sup>2</sup> |

|-------------------------------------------------------------------------------------------------------------------|

| $-1200\mu C/cm^{2}$                                                                                               |

| 3.11 Calibration artifact with a pitch of 100 nm, and with dose in the range of                                   |

| $1300\mu C/cm^2 - 1400\mu C/cm^2$                                                                                 |

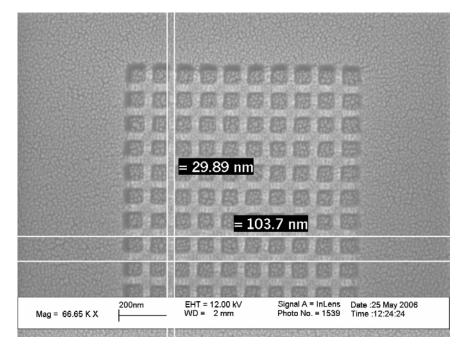

| <b>3.12</b> Calibration artifact with a pitch of 100 nm, and with dose of $1490\mu$ C/cm <sup>2</sup> 103         |

| <b>3.13</b> Schematic representation of (a) First unit with horizontal lines (b) Second unit with                 |

| vertical lines and (c) the units combined to form the design of the artifact105                                   |

| 3.14 Calibration artifact with pitch of 100 nm and with the dose different for the                                |

| horizontal and the vertical lines                                                                                 |

| <b>3.15</b> Calibration artifact with pitch of 100 nm and with different doses106                                 |

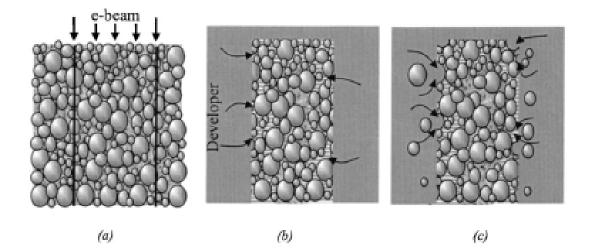

| <b>3.16</b> Schematic diagram of a development process of a negative tone resist including (a)                    |

| exposure, (b) development and (c) polymer aggregate extraction (PAB)108                                           |

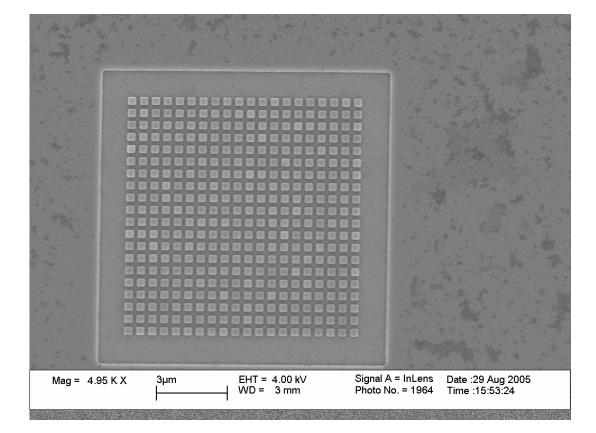

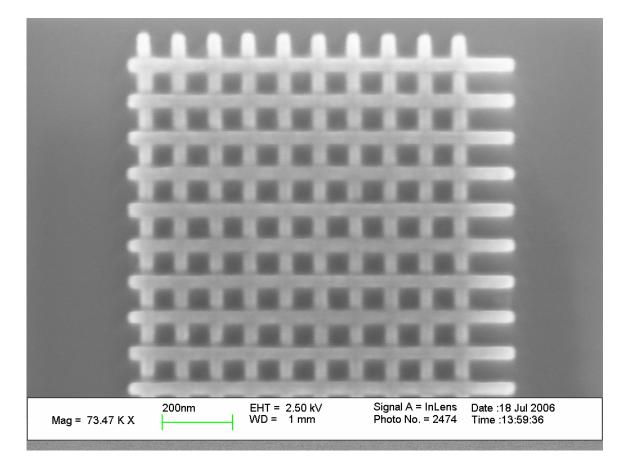

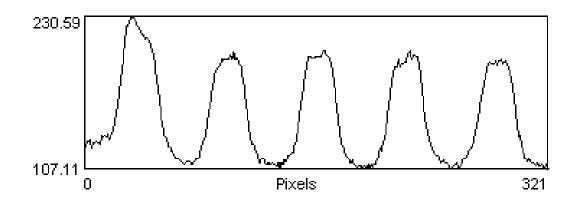

| <b>3.17</b> SEM micrograph used for "Measure" software, Spectel Research Corporation110                           |

| <b>3.18</b> Measurements done using "Measure" software, Spectel Research Corporation111                           |

# LIST OF TABLES

| Table                                                                  | Page |

|------------------------------------------------------------------------|------|

| 2.1 Specification of 2" silicon wafer                                  | 18   |

| <b>2.2</b> Field and sub-field for an electron beam lithography system | 32   |

| <b>2.3</b> Resist requirements for the near term years                 | 41   |

| <b>2.4</b> CD-SEM parameters and the factors which drive their choice  | 72   |

| <b>2.5</b> Some key parameters, and their possible solutions           | 73   |

| <b>3.1</b> Thickness variation of the resist with temperature          | 94   |

| <b>3.2</b> Line width and line edge roughness measurements             | 111  |

### **CHAPTER I**

# **INTRODUCTION**

# **1.1 Introduction**

From the birth of the electronic age to the present  $21^{st}$  century, computing power of the microprocessors has evolved rapidly. From the world's first commercial single chip microprocessor - Intel 4004, a 4 bit CPU released by Intel Corp. in 1971, with a computing power of 60000 cycles per second to Intel<sup>®</sup> Pentium<sup>®</sup> 4 processor at 2 gigahertz (GHz) – or two billion cycles per second [1], microprocessors computing power has come a long way and is still increasing as we speak. To cater to this need of the consumers to have a better and faster microprocessor, new technologies to sustain this growth have evolved.

Over these three decades, semiconductor industries have moved from micron level to sub-micron level. Circa 2005, we are entering a new frontier of technology, the sub 0.1 micron technology. This has lead to a complicated device fabrication involving small fine features, increased number of masks, variety of light sources and photoresists. Conventional photolithography is still widely used for mass production of microprocessors, but with emphases on the sub 0.1 micron era, new technologies like Extreme Ultra Violet (EUV) lithography, Immersion Lithography, Nanoimprint Lithography to name few, are seriously being considered as an alternative to the conventional photolithography. These new technologies still need to be perfected to use them in mass production, but with time these technologies might be a serious contender for the photolithography technique. To perfect these technologies, companies like Intel,

AMD, IBM are pouring billions of dollars to develop infrastructure supporting these technologies.

# 1.2 Overview of the lithography process

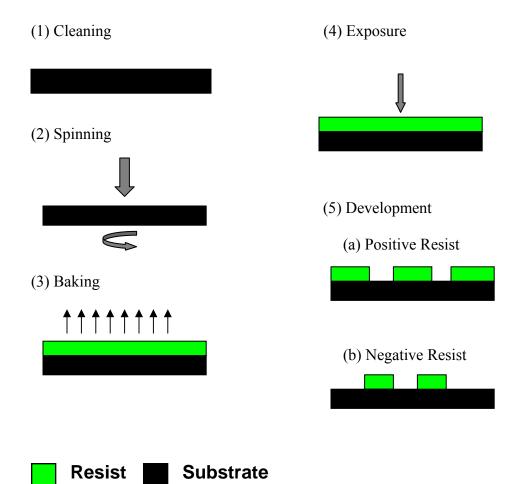

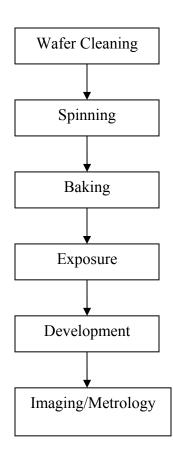

A brief introduction regarding the lithography process used for semiconductor manufacturing is being discussed (Figure 1.1).

(1) <u>Cleaning of the wafers</u>

Normally done to remove the contaminants from the wafer surface.

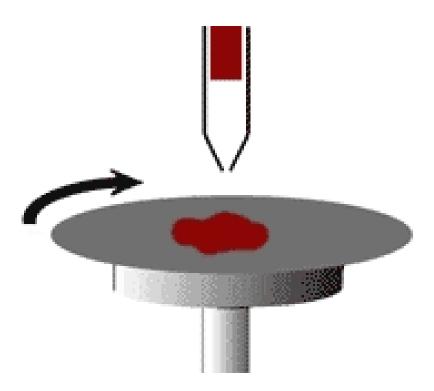

# (2) Spinning resist on the wafers

Used for applying resist on the wafer surface. The final rpm and the time for spinning play a role in determining the resist thickness.

#### (3) <u>Baking of the resist on the wafers</u>

The role of baking involves removing the extra solvent present on the wafer surface. It also helps in bond strengthening in the resist.

#### (4) Exposure of the wafers

Irradiation of the resist surface by either photolithography or electron beam lithography.

# (5) Development of the wafers:

After exposure, the wafers are immersed in a development solution to achieve the final pattern shape.

In case of positive resists, the exposed part is removed after development, while the unexposed part remains of the wafers. In case of negative resist, the exposed part remains on the wafer after development, while the unexposed part is removed from the wafer surface.

Figure 1.1: Schematic representation of the lithography process.

In 1965 Gordon Moore, one of the two founders of Intel made an observation that innovation in technology will allow the number of transistors on a wafer to double every two years. This observation is popularly known as "Moore's Law". Over the last few years, it was believed by many experts from the semiconductor industries that the Moore's Law will no longer be a benchmark for the industry, but a recent report by Semiconductor International Association (SIA) [2], indicates that the Moore's Law is to stay for the next decade or so. To ensure that the semiconductor industries go on the path as set by the Moore's Law, in 1999, the International Technology Roadmap for Semiconductors (ITRS) was setup by leading semiconductor companies of the world. The objective of ITRS is to identify the technological difficulties and need to be faced by the semiconductor industries in the next fifteen years [3].

The International Technology Roadmap for Semiconductors (ITRS) uses the node size to identify the technology era for the semiconductor industries. Presently, we are in the 90nm technology and are expected to reach 65nm technology in year 2007. It is projected that by year 2016, we would be in the 22nm technology [4]. To achieve these goals, semiconductor companies are trying to improve the current technology and in some cases incorporate new technology. The current technology employs photolithography based on the excimer laser. The 193 nm ArF source is predominantly used for the 90nm technology. But as we enter the 65nm technology expected in year 2007, new source of excimer lasers are being studied. Tools using the 157nm ArF<sub>2</sub> excimer laser are currently being developed by some companies and may help in a smooth transition from 90nm technology to the 65nm technology by year 2007.

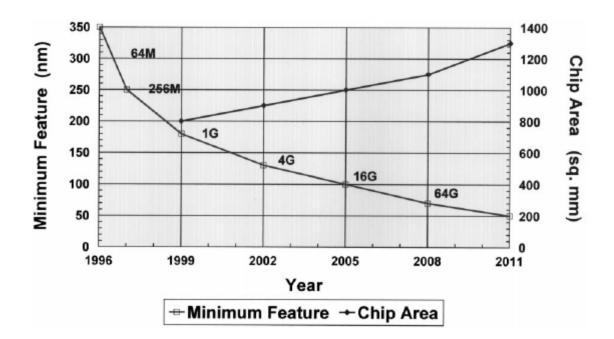

Moore's Law also states that with the exponential increase in the transistors, there should be decrease in the manufacturing cost for the transistors. To be inline with Moore's Law, semiconductor industries have made transition from the 200mm wafers to 300mm wafers. Intel has started using 300mm wafers in its Oregon and Arizona Fabs, while AMD in partnership with IBM has started using 300mm wafers at East Fishkill, NY facility of IBM. With the roadmap set by the ITRS, the next transition would be to 450mm wafers. Figure 1.2 gives the relation of chip size and area versus time. Photolithography is still the workhorse for the semiconductor industry, even with transition to 300mm wafers. Photolithography is one of the most critical operations involved in making microprocessors. It forms the base for the subsequent processes that would be carried on till the final product is obtained. Photolithography is also called as photomasking, masking and microlithography [5]. Photolithography employs two important goals. First, is to make and transfer the pattern on the silicon wafer, well within the design accuracy. This is also termed as the *resolution* of the patterns on the silicon wafer. Second, to align the different layers of patterns that would be stacked on top of the first layer. This is termed as *alignment* of the patterns on the wafers. Both the *resolution* and *alignment* play a critical role in the photolithography process. Any error in either of the two, will lead to stopping of the entire process and in turn the rejection of the product. With the increasing complexity of the devices, the feature size is becoming smaller as we speak, and the number of layers is also increasing. A lot of research is being carried out to ensure a good *resolution* of the images and a perfect *alignment* of the layers on the silicon wafers [5].

Figure 1.2: Minimum chip size and area versus time [15].

Photolithography is a multi step pattern transfer process. It involves transfer of pattern drawn on the photomask or the reitcle onto the silicon wafer by flashing a light source through the mask. This process is continued till all the layers are stacked in perfect alignment. First step for this process involves spinning light sensitive photoresists on the silicon wafer. This is carried out using industrial spinners which are automated to control the spinning and baking cycles, which in turn ensures correct thickness of the resist layers for all the wafers. Semiconductor companies first used the photoresists produced by Eastman Kodak and Shipley Company in the year 1950. Photoresists are of two types, positive photoresists and negative photoresists. Depending upon the requirement the photroresists are chosen for the photolithography process. Most photoresists are sensitive to the visible, ultraviolet and deep ultraviolet light source. With the advent of X-Ray Lithography and EUV Lithography, new photoresists, known as *Chemically Amplified* Photoresists are being manufactured. Commonly used photoresists are DNQ and DNQ-Novolac based resist. Each of these resists are sensitive to particular wavelength of light source and can be used only for that particular light source.

After the photoresist is spun on the wafer, light source illuminates the photomask with the pattern on it. Light passes through the transparent parts of the photomask and is deflected back by the opaque parts, thereby, forming the pattern image on the silicon wafers. Photomasks are normally made of quartz or borosilicate glass which have a good dimensional stability and transmission properties for the wavelength of the source. The mask is normally covered with a layer of chrome. Most advanced masks use layers of chrome, chromium oxide in the order the process parameters demand. Photomask or the reticles are generally produced using the Electron Beam Lithography. Electron beam lithography does not involve any use of masks or reticle, hence it is also called as direct write lithography. The process involves scanning of an electron beam across the silicon wafer. This scanning of the beam can be done in two ways, vector scan and raster scan. *Vector Scan* involves scanning of the electron beam only in the area which needs to be developed, in other words, area of interest. While Raster Scan involves scanning the entire wafer. Due to this, the time required by *raster scan* is more than that by the *vector* scan. Most of the modern lithography machine use vector scan technique. With advances in the electron beam lithography machine, theoretical it is possible to get feature sizes as small as 5nm-6nm. In reality it is difficult to get very small feature size due to proximity effect. As quoted by T. H. P. Chang, "Proximity effect is a well known phenomenon that an uniform exposure causes a non uniform distribution of actually received exposure" [6]. Since electron beam lithography is a direct write process, the chances of errors in the pattern design due to any kind of contamination is eliminated. A proper CAD design incorporating the proximity effect correction is fed into the lithography machine. The machine uses the vector scan technique to write the pattern. Electron beam lithography helps in getting very accurate pattern shape, but the disadvantage is the time for writing. Electron beam lithography takes more time compared to photolithography, hence not used for mass production.

After the exposure is completed the mask is developed to obtain the patterns which would be later on transferred onto the silicon wafer. A number of masks are placed in the stepper and are used in the order in which the layer of the patterns on the silicon wafers are required. Each exposure is followed by developing, metal deposition and etching technique before the next exposure can be started. Semiconductor companies employ processes which require a high degree of precision in imaging the pattern, alignment of the layers, the electrical properties of the wafers, film thickness measurement and few other parameters. Any mistake in either of these parameters can lead to a substantial loss of time and money. New techniques are employed to ensure thorough evaluation of the wafers in a fast, efficient and precise way. Device evaluation and characterization is required for production-line control and product stability. Most of the device evaluation is carried out along with the fabrication process (In line evaluation). Testing processes can be broadly classified as *Indirect Testing* and *Direct Testing* [5]. *Indirect Testing* is normally carried out on test wafers to prevent any damage on actual device wafer [5]. Most of the electrical measurement tests, ion implantation tests are carried on by *Indirect Testing*. *Direct testing* like linewidth measurement, film thickness measurement, and defect detection are carried on the actual device wafer [5].

With ever decreasing feature size, control and evaluation of these feature size is becoming more critical. Evaluation of the feature size is normally called as *Metrology of a linewidth*. This normally involves Critical Dimension(CD) and Overlay(OVL) measurement. Critical Dimension(CD) is normally measured using CD-SEM, CD-AFM and Scatterometry, while Overlay(OVL) is normally measured using bright field optical microscope [7]. Overlay measurement involves measuring the alignment of the various layers built to form the final product. Any error in this alignment of layers causes rejection of the product. This is an inline metrology process carried out during the fabrication process by registering the marks on the wafers and ensuring the position of these marks remain as precise as possible for each layer built in the microprocessor.

With increasing demand for faster, repeatable and accurate linewidth measurements, new techniques like scatterometry are being employed by the semiconductor industries to cut down the processing time and get accurate measurement as possible. Scatterometry is the analysis of light scattered or diffracted from the sample. In this technique, a scatter signature is obtained by varying the angle between the light source and the sample to be measured, and monitoring the power diffracted into the zeroth order. This signature contains the dimensional information about the scattering [8]. These reading are later on compared with an in built library and thus an accurate linewidth measurement can be done. Scatterometry evaluates a group of lines as compared with CD-SEM , which evaluates single line at one time.

Inspite of the new techniques for the metrology of linewidth, CD-SEM is still the most preferred by the semiconductor industries. CD-SEM is like any conventional SEM, modified with some special data processing capabilities for Critical Dimension Measurement. Charging and damage induced by the beam encountered in conventional SEM plays an important role in deciding key parameters like beam current, beam energy, beam size and scan speed. An optimum condition is required to ensure as minimum charging and damage due to beam as possible on the wafer [9]. As the number of the transistors on the wafers increases, the resolution offered by the CD-SEM becomes one of the most important criteria considered while buying a new CD-SEM. KLA-TENCOR, Hitachi High Technologies are some of the companies which are manufacturing the CD-SEM. The S-9380II CD-SEM manufactured by Hitachi High Technologies, Schaumburg, IL can handle 300mm wafers with a resolution of 2nm, precision of 0.8nm and throughput of 33 wafers per second [10].

# **1.3 Scope of the Project**

As discussed earlier, CD-SEM is still considered as the benchmark for Critical Dimension Metrology. Efforts are being made to improve the resolution and the efficiency of CD-SEM. All the CD-SEM's are calibrated before they can be used for Critical Dimension Metrology. This calibration is done by using the standards provided by the CD-SEM manufacturer. Companies like Hitachi, KLA-TENCOR provide their own standards to their consumers. Thereby restricting the use of the standards to their consumers only. Though there are companies like VLSI Standards and government organization like NIST working on developing metrology standards which can be used by anyone interested in doing metrology.

To facilitate the measurement of the CD-SEM performance, an easy access to standard reference artifact traceable to international specifications is an added advantage. Considerable literature is available for CD-SEM performance, which relies on in-house artifacts or general test objects. The absence of commercially available artifacts hinders performance evaluation of different CD-SEM. The objective of this abstract is to introduce the fabrication and characterization of artifacts for the sub-100nm metrology, which can be made available in wafer form at low cost.

In this research work, artifacts have been designed and fabricated for precise magnification calibration of the CD-SEM. The designing of the artifacts takes into account the *proximity effect*, a problem associated with the e-beam exposure, to produce dense grid type structure in the sub-100nm region. The structures are fabricated using the e-beam lithography tool, operated at 50KeV. The artifacts have been fabricated on a thin layer of negative resist HSQ spun on silicon substrate. Subsequent development in 0.26N

TMAH gives a structure on silicon wafer, thereby eliminating contamination issues. The artifacts have 100nm pitch, with linewidth of the order of 40nm.

Furthermore, characterization of the artifacts for line pitch determination is carried out using standard software such as "Measure", Spectel Research Corp. which provides an absolute calibration of the image pixel size that can then be used to measure other features. Line pitch determination carried out by the threshold method and the regression to baseline method gives out values close to 100nm, in accordance to designed values. The low values for the line edge roughness (LER) further facilitate precise linewidth metrology. Line pitch determination using optical metrology tools and the inbuilt laser interferometer in the electron beam lithography tool is being evaluated for precise measurements.

#### **CHAPTER 2**

# LITERATURE REVIEW

#### 2.1 Semiconductor Substrates

With the transition from 90nm technology to 65nm technology, the number of transistors on the silicon wafers is increasing. To accommodate this increase in the transistors, and also maintain the Moore's Law, the size of the silicon wafer has been increased. Currently the semiconductor industries are using the 300mm wafer. The next transition is expected to be at 450mm wafers, according to SIA Technology Roadmap. Though the size of the wafers has increased, the production methods have remained pretty much the same. This has lead to number of problems associated with weight of the cast, structural issues and electrical properties of the wafers.

Some of the manufacturing techniques for silicon wafer are Czochralski growth, float zone growth and Bridgman Growth. The latter is used more often for GaAs wafer production.

### 2.1.1 Czochralski Growth

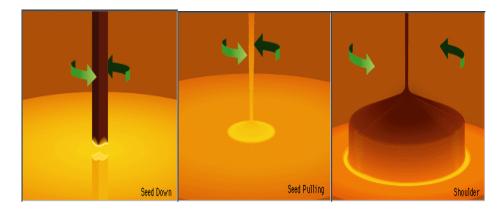

Czochralski growth technique is the most used manufacturing method for silicon wafers. It was developed by Jan Czochralski in 1916 while studying the crystallization rate for some metals. It involves drawing of thin metal rod from a melt of pure single crystal silicon, the process would be further explained in the following paragraph. The first wafers produced were 100mm in diameter, while the present day wafers have 300mm diameter. The wafers thus produced have around 600-700µm thickness with a purity level of almost 99.99999999 % [11]. The biggest producers of silicon wafers are MEMC, SEH, SUMCO, Wacker Siltronic and Komatsu.

Czochralski growth involves solidification of a crystal from the melt. In this technique a ultra high purity grade polycrystalline silicon (purity= 99.99999999%), is placed in a fused silica crucible. To eliminate any impurities during melting, the crucible is encased in an evacuated chamber with an inert gas flowing. A small single crystal silicon is introduced in the melt of polycrystalline silicon. The orientation of this crystal is very important, since it decides the orientation for the entire silicon melt [11]. This small crystal just touches the surface of the melt and is pulled up and simultaneously rotated by hydraulic shafts. The pressure and the composition of the melt and the single crystal are almost same, hence there is reduction in the temperature as the surface area increases. The larger crystal thus obtained by this technique is known as *Boule* [11]. Modern boules have a diameter of the order of 300mm. In this technique the pulling rate is very important, any increase or decrease in this pulling rate can cause severe problems in manufacturing of silicon wafers. The steps involved in czochralski growth for silicon substrates are shown in figure 2.1.

The diameter of the silicon wafer determines the process parameters required to maintain the quality of the silicon wafers. As the diameter of the crystal increases, the pulling rate is decreased to ensure a uniform cooling of the boule. During the cooling the crystal orientation of the seed propagates in the melt. Also, the dopant atoms get incorporated to form the N-type of the P-type silicon wafers [5]. Moreover, a very low pulling rate may cause introduction of point defects in the crystal. *Dislocation loops*, the most common defects found in the crystal, are formed by improper pulling rate of the melt.

Figure 2.1: Czochralski growth for silicon wafers [13].

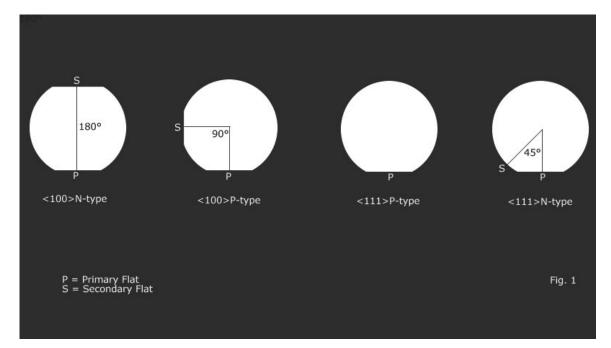

# 2.1.2 Wafer Preparation and Specifications

After the production of the boule is completed, the final step involves the preparation of the wafer. Grinding, slicing, etching, lapping, polishing and cleaning are some of the steps enroute to final wafer suitable for fabrication purposes. The boule is checked for electrical resistivity and crystal perfection, followed by grinding to the required diameter of the wafer. Every silicon wafer has a particular orientation which is indicated by providing a flat to the circular silicon wafer. The largest flat is known as *primary*, and oriented perpendicular to <110> direction. One or more minor flats may be given in some cases, while in large wafers with diameter more than 200mm, a notch is ground into the edge [11]. Figure 2.2 shows the different type of orientations for a silicon substrate. Table 2.1 gives the specification of silicon wafers.

Grinding to get a flat in the silicon wafer produces lot of residues, which are removed by etching the boule in a proprietary mixture. This is followed by slicing of the boule to obtain individual silicon wafers. Extreme care has to be enforced to prevent any breakage in the silicon wafers or damage to the boule. Slicing induces roughness in the edges of the silicon wafers, which is later on removed by lapping both sides of the wafers in alumina and glycerine slurry. Lapping reduces the stresses on the wafer edges, and also prevents pile up of liquid that is spun on the silicon wafer. Final polishing is achieved using Chemical Mechanical Polishing (CMP), which ensures a smooth mirror like finish on either one side or both sides of the wafers as per the requirement. Oxygen concentration, carbon concentration, wafer orientation, metal contaminants and resistivity are some of the specifications used to describe the quality and type of the wafer.

Figure 2.2: Wafer orientation indicated with primary and secondary flats [14].

| Diameter:    | 50.8 mm | Resitivity: | 1-20 Ohm-cm       |

|--------------|---------|-------------|-------------------|

| Туре:        | N/Phos  | Thickness:  | 250-300µm         |

| Orientation: | (100)   | Grade:      | Test              |

| Flats:       | 2<110>  | Surface:    | One side polished |

Table 2.1: Specification of 2" silicon wafer.

Courtesy: Wafer World Inc

Some of the specification for a test grade silicon wafer.

Variation in the resistivity can be achieved by changing the amount of dopant atoms in the silicon melt. To decide the amount of dopant required, the weight of the melt is calculated, followed by determining the amount of impurity atom required and adding the weight of the impurity as needed. A rough calculation of the dopant weight is done by using the segregation coefficient k, defined as

$$k = \frac{C_s}{C_l}$$

where  $C_s$  and  $C_l$  are the impurity concentrations at the solids and liquid sides of the solid/liquid interface [11]. Some of the specification for a test grade silicon wafer.

# 2.2 High Resolution Lithography System

The key technology that drives the semiconductor industries are the high resolution lithography systems used to fabricate fine feature size. With the semiconductor industries preparing themselves for the 65nm technology, efforts are being made to improve and increase the throughput of these systems. A brief introduction to Optical Lithography, Next Generation Lithography (NGL) and the Electron Beam Lithography is provided in an effort to emphasize the importance of these systems.

# 2.2.1 Optical Lithography

Optical lithography, right from its inception till the present day, has been the workhorse for the semiconductor industries. Since this technique uses a light source, it is also called as *photolithography*. In this technique, light passes through a mask with the design features onto a photoresist coated silicon wafer, thereby transferring the design features from the mask to the photoresist. The masks used in photolithography are generally chrome on quartz or borosilicate glass. They are manufactured using the electron beam lithography to ensure a precise dimension control. Extreme care has to be taken to avoid any defects or pinholes on the masks, since these masks are used to pattern thousands of wafers. The design of the feature on the mask is done taking into account optical proximity correction. A typical wafer fabrication will need 10-15 masks to form the final microprocessor. The improvements in the wavelength of light and the numerical aperture (NA) of the projection lens have helped in the growth of the optical lithography system.

Resolution,

$$R \approx \frac{Wavelength(\lambda)}{2NA}$$

The present day photolithography use Deep Ultra Violet (DUV) source of the order of 193nm excimer lasers and 157nm excimer lasers. With the 157nm excimer lasers, the major cause of concern is the availability of material transparent to 157nm lasers [15]. Schematic of a simple optical lithography system and the potential of introduction of new tools are shown in figure 2.3 and figure 2.4 respectively.

Thus to ensure advancement in technology, problems associated with the new technology need to be solved before the technology can be used for mass production.

Figure 2.3: Schematic of a simple optical lithography system

Figure 2.4: Potential introduction of new resolution lithography tools [15].

# 2.2.2 Next Generation Lithography (NGL)

With the Moore's Law still governing the future of the microprocessors, International SEMATECH through its Next Generation Lithography Task Force, has charted a roadmap till 2011 [15]. This will need the implementation of next generation lithography system like X-Ray Lithography, Extreme UV Lithography and Ion Beam Projection.

# 2.2.2.1 X-Ray Lithography

The concept of X-Ray Lithography was introduced in the early 1980s, and has been undergoing development since then. The major problems associated with this technique are the use of the mask and the x-ray source. Though the problem of the X-Ray source might be resolved with the introduction of X-Ray synchrotron source [16], there still remains the issue of manufacturing mask for this technique. The mask is thin membrane of patterned gold layer of the order of 500 nm, and is transparent to wavelength of 1 nm. The biggest limitation of this technique is the manufacturing of masks, which have the design dimensions same as the final pattern [15]. If this problem can be solved, X-Ray Lithography can be considered for mass production. Figure 2.5 and Figure 2.6 gives a schematic view of X-Ray Lithography.

#### 2.2.2.2 Ion Beam Projection

A stencil mask of few micrometers in thickness and 100 keV hydrogen or helium ion source constitutes the ion beam projection system.

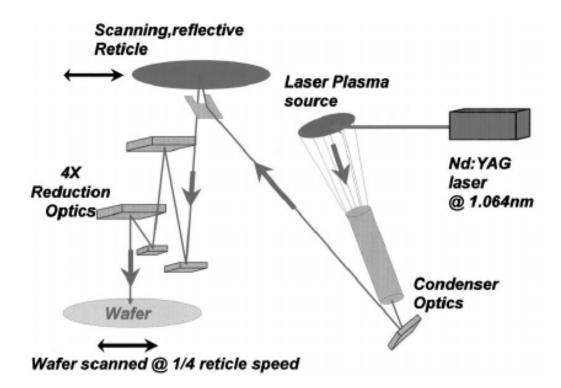

#### 2.2.3 Extreme UV Lithography

EUV Lithography is still in its early stage of development, with various companies in USA and Europe. It uses 13 nm wavelength photons emitted from the high powered Nd:YAG laser [15].

Figure 2.5: Schematic view of X-Ray Lithography [15]

Figure 2.6: Schematic of experimental X-Ray Lithography [15].

### 2.2.3 Electron Beam Lithography

Electron beam lithography has come a long way from the first EBL systems like the Bell Labs EBES [11]. The new state of the art lithography systems are expensive, costing more than \$ 2M per unit, and with a good resolution of the order of 5nm. Electron beam lithography is also called as direct write lithography, since it involves no mask for fabrication purpose. Inspite of the advantages offered by electron beam lithography, the use of this technique for mass production has been hampered by the slow throughput. Electron beam lithography is mainly used for fabrication of masks, which are later on used for photolithography.

### 2.2.3.1 Principle of Electron Beam Lithography

Most of the lithography system involves moving the electron beam across a wafer to expose the pattern on a pixel basis. The basic principle involves heating of the electrode gun, which produces an electron beam. The final size of the beam (around 5nm) is controlled by the electrostatic lens and a variety of apertures. There are three main types of electrode gun commonly used: *Thermionic emitter* and *field emission emitter*. *Thermionic emitter* is a tungsten (W) filament of about 100µm diameter, bent in a V-shape hairpin. Resistive heating of this tungsten filament gives thermionic emitters. The emitters is around 30 to 100 hours for temperature of 2700 K , vacuum of order of  $10^{-3}$  Pa and brightness of  $\beta=10^{-5}$  A/cm <sup>2</sup>sr. In thermionic emitters, the brightness typically increases with accelerating voltage. Energy spread, brightness, source size and lifetime are some of the factors which affect the performance of the thermionic emitters [17]. *Field emission emitters* are usually made from single-crystal tungsten in a form of a wire of a radius of about 100nm. Electrons are generated from

these emitters by field emission, thereby eliminating thermal drifts, evaporation of cathode material and low brightness. There is another set of field emission emitters, the *Schottky Emitters*, made from ZrO/W annealed in forming gas. These emitters have excellent emission stability, but larger demagnification is required, hence reducing current available [17].

The electron beam thus produced by the gun is further demagnified to the required size by using electrostatic lens and a variety of apertures. The final spot diameter on the silicon wafer is given by

$$d^{2} = d_{o}^{2} + d_{s}^{2} + d_{c}^{2}$$

where  $d_o$  is the perfect lens diameter,  $d_s$  is the spherical aberration and  $d_c$  is chromatic aberration. The final electron beam has a Gaussian shape, with intensity increasing with radius from the center.

In direct write lithography, scanning is achieved either by *raster scan* or by *vector scan* (figure 2.7). *Raster scan* was used in the first EBL systems including those manufactured by Bell Labs. In this type of scanning, the beam is deflected from one point to another in one direction, thereby scanning the entire wafer. The time required by raster scanning is quite high, thereby decreasing the throughput of the machine. While *vector scan* EBL systems have high throughput on account of the electron beam scanning only the area of interest. In such EBL systems, the co-ordinates of the area of interest is fed to the X and Y digital and analog converters (DACs), which directs the beam to the exact location. This ensures that the time required for writing patterns on wafers is less compared to the raster scanned EBL systems.

Figure 2.7: Comparing of scanning methodologies (A) Raster Scan (B) Vector Scan

## 2.2.3.2 JBX 6000 FS/E – Direct Write Lithography

## (Courtesy: JEOL JBX 6000 FS/E, JEOL, Peabody, MA)

The JBX 6000 FS/E is an electron beam lithography system designed for production of GaAs FETs as well as process development and prototype engineering for optical elements and silicon devices. It is best suited for research work involving very high precision pattern fabrication.

The system employs a high-brightness electron gun using a zirconium oxide coated tungsten thermal field emitter (ZrO/W TFE) and an in-lens detector. The system is capable of high speed pattern exposure on high resolution resists. The JBX 6000 FS/E (figure 2.8) uses a single-stage in-lens electrostatic deflector free from hysteresis, assuring high stability. It incorporates two different objective lenses as standard for fine and ultra fine pattern with a beam diameter range of 5nm to 200nm. The operation mode is roughly divided into 4<sup>th</sup> lens-mode and 5<sup>th</sup> lens-mode each having distinct features.

The 4<sup>th</sup> lens-mode is used for submicron electron beam lithography to write fine geometries on wafers. In addition to the primary application of direct submicron writing on the wafers, this mode is provided with the pattern writing functions for masks applied to small volume production.

The 5<sup>th</sup> lens-mode is used for ultra fine electron beam lithography to write ultra-fine geometries on wafers. It has been developed for conducting basic researches on very large scale integrated circuits or new physical phenomenon. In the 5<sup>th</sup> lens-mode, the beam diameter is around 5 nm, while for the 4<sup>th</sup> lens-mode the beam diameter is in the order of tens of nanometers (Figure 2.9 and Figure 2.10). The JBX 6000 FS/E is a vector scanning type electron beam lithography system which facilitates faster writing time.

Figure 2.8: Electron Beam Lithography tool - JBX 6000 FS/E (JEOL)

Figure 2.9: Main Console for JBX 6000 FS/E (Courtesy: JEOL- Peabody, MA)

Figure 2.10: Gun Column for JBX 6000 FS/E (Courtesy JEOL – Peabody, MA)

- (1) Electron Gun

- (2) 2<sup>nd</sup> Lens (2<sup>nd</sup> demagnification lens)

- (3) 3<sup>rd</sup> Lens (3<sup>rd</sup> demagnification lens)

- (4) Blanking Electrode

- (5) 4<sup>th</sup> Lens (Projector Lens)

- (6) 5<sup>th</sup> Lens (Projector Lens)

- (7) Aperture Selector

- (8) 1<sup>st</sup> Beam Alignment Coil

- (9) Astigmatism Correction Coil

- (10) 1<sup>st</sup> Deflector

- (11) 2<sup>nd</sup> Deflector

- (12) Backscattered Electron Detector

- (13) Secondary Electron Detector

The acceleration voltage provided to the system can be manually changed from 25 kV to 50 kV or vice versa. The workpiece stage movement is controlled by Laser Beam Control (LBC) to ensure high accuracies in the movement of the stage. The stage position is controlled in units of 0.62 nm, with a resolution of  $\lambda/1024$ .

To help in accurate writing conditions, the entire scanning method is based on scanning ranges which define the *field* and the *sub field*. The pattern to be written by the electron beam lithography system is divided into regions called *field*. To further ensure the accuracy in writing, decrease distortion in writing the field size is divided into small area called the *sub-field*.

Depending upon the type of the acceleration voltage used and the type of objective lens used, the field size varies. The following Table 2.2 gives an idea of the field and the sub-field size.

If the dimensions of the design are in the range of few hundreds of microns, it is advisable to use the combination of 4<sup>th</sup> objective lens and 50 kV accelerating voltage. With this combination the time required for writing a pattern decreases drastically. Moreover, the field size has to be taken into account while designing the pattern, else stitching becomes an issue during fabrication.

In the quest of higher precision and accuracy in the dimensions of the pattern, it is advisable to go for a combination of 5<sup>th</sup> objective lens, 50 kV accelerating voltage with 100pA current.

Table 2.2: Field and sub-field for an electron beam lithography system

| ( | <i>Courtesy:</i> | JEOL, | Peabody,                              | MA) |

|---|------------------|-------|---------------------------------------|-----|

|   |                  | )     | · · · · · · · · · · · · · · · · · · · |     |

| Sr.<br>No. | 8  |   | Field Size<br>(X and Y dir.)<br>(µm) | Sub-Field Size<br>(X and Y dir.)<br>(µm) |  |  |  |

|------------|----|---|--------------------------------------|------------------------------------------|--|--|--|

| 1          | 25 | 4 | 1600 X 1600                          | 100 X100                                 |  |  |  |

| 2          | 25 | 4 | 800 X 800                            | 50 X 50                                  |  |  |  |

| 3          | 50 | 5 | 160 X 160                            | 10 X 10                                  |  |  |  |

| 4          | 50 | 5 | 80 X 80                              | 5 X 5                                    |  |  |  |

### 2.3 Electron-Solid Interaction

When a beam of electrons is impinged onto a substrate, there is an interaction between the electrons and the atoms of the substrate. This electron-substrate interaction can be broadly classified as *Elastic Scattering* and *Inelastic Scattering*.

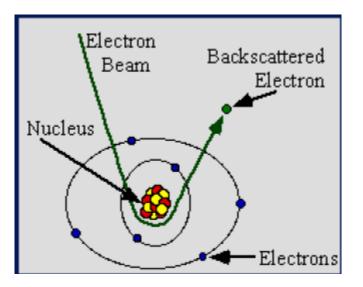

*Elastic Scattering* changes the path of the electrons within the specimen without affecting the kinetic energy of the electrons. This scattering event causes electron backscattering from the substrate and is the major imaging signal for scanning electron microscope. The amount of the backscattered electrons can be quantified by the backscattering coefficient  $\eta$ , defined as

$$\eta = \frac{n_{BSE}}{n_B} = \frac{i_{BSE}}{i_B}$$

Where,  $n_{\rm B}$  is the number of electrons incident on the specimen and  $n_{\rm BSE}$  is the number of backscattered electrons (BSE). The backscattering coefficient can also be expressed in terms of current [17]. The backscattering coefficient generally increases with the atomic number, thus forming the basis for *atomic number contrast*. Individual backscattering electrons involves angles less than 90°, but the cumulative effects of all the electrons together helps the BSE to escape the sample surface.

The backscattered electrons are the major cause of the proximity effect observed during the lithography. As a result of the proximity effect, the pattern design suffers from a high degree of deformation. This effect is dependent on beam voltage, resist material, substrate material, contrast characteristics and the development process used. Thus proximity correction is an important part of the lithography process. *Inelastic Scattering* events involve transfer of energy from beam electrons to the atoms of the substrate. This scattering events lead to the generation of secondary electrons, auger electrons, x-rays, phonons and plasmons. Secondary electrons produced by inelastic scattering have energy less than 50 ev, and form an important imaging signal. The secondary electrons are quantified by secondary electron coefficient  $\delta$ , defined as

$$\delta = \frac{n_{SE}}{n_B}$$

Where,  $n_{\rm B}$  is the number of electrons incident on the specimen and  $n_{\rm SE}$  is the number of secondary electrons (SE). Elastic scattering deviates the electrons from their original directions of travel, while the inelastic scattering progressively reduces the energy of the electrons as they travel through the substrate. This causes the formation of a region wherein the electrons interact and deposit their energy leading to the emission of secondary electrons, known as *interaction volume*.

The emission of the secondary electrons (SE) and the backscattered electrons (BSE) is schematically described in Figure 2.11 and Figure 2.12

During the electron beam lithography operation, the electrons penetrate through the resist, undergoing small angle scattering (forward scattering) and large angle scattering (backscattering) which greatly affects the feature design. *Forward scattering* causes broadening of the beam diameter at the base of the resist. This broadening effect can be minimized by using a very thin layer of the resist and highest possible accelerating voltage [18]. The broadening in the beam diameter can be empirically given as

$$d_f = 0.9(R_t/V_b)^{1.5}$$

where,  $R_t$  is the resist thickness and  $V_b$  is the beam voltage in KeV [18].

Fig 2.11 Secondary electron scattering

(Adapted from <a href="http://maic.mse.ufl.edu/Lecture-5.pdf">http://maic.mse.ufl.edu/Lecture-5.pdf</a>)

Fig 2.12 Backscattered electrons scattering

(Adapted from <a href="http://maic.mse.ufl.edu/Lecture-5.pdf">http://maic.mse.ufl.edu/Lecture-5.pdf</a>)

Forward scattering can be useful in getting a good undercut of the sidewall in a pattern, by ensuring an optimum development time of the resist [18]. As discussed earlier, backscattering causes the proximity effect in the resist, thereby distorting the design feature.

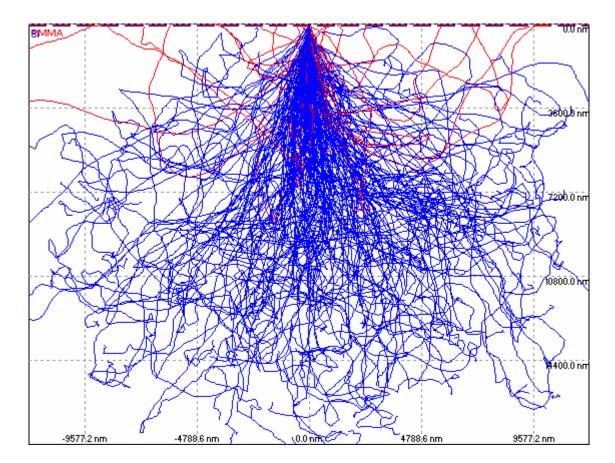

These electron scattering can be modeled accurately by using some simulation modeling software. The most common technique is the Monte Carlo simulation which is used by many commercial available software. The input parameters for this program are electron energy, beam diameter and film thickness, while the output is a plot of energy deposited in the resist as the function of distance. This distance is calculated from the center of the beam. The following figure gives a Monte Carlo model for electron scattering using 50 KeV accelerating voltage and PMMA resist thickness of the order of 50 nm. The software used for the simulation is CASINO v2.42, developed by Alexandre Real Couture and others. The program uses Joy and Luo (1989) physical model for the Monte Carlo simulation (figure 2.13).

### 2.4 Proximity Effect in Electron Beam Lithography

The resolution of the electron beam is good on account of small wavelength, hence small diffraction. This resolution is limited by the optical aberration and the electron scattering events in the resist and substrate, mostly referred to as the proximity effect.

Extensive research has been done on the causes and correction of the proximity effect. There are number of research papers on this topic, and new ways are being developed to overcome the proximity effect. As quoted by T.H.P Chang , "proximity effect is a well known phenomenon that a uniform exposure by the incident beam can give rise to a non

Figure 2.13: Monte Carlo simulation for 50 KeV electron beam

uniform distribution of actually received exposure in the pattern area." [19]. The backscattering electrons are the major cause for the proximity effect and depend on beam accelerating voltage, resist thickness, resist contrast and material, substrate and the development technique used.

Large feature size requires less development time compared to the small features, hence any attempt to develop the small features on the same wafer with large features leads to overdevelopment of the large features. This effect is defined as the *Intrashape proximity effect*. The most serious distortion of the patterns is shown by the *Intershape proximity effect*, wherein increasing packing density of features leads to overexposure of the feature size. This causes decrease in the spacing between the features and increase in the size of the feature size [20]. The degree of distortion due to proximity effect is different for the positive and the negative resists. As the feature size goes on decreasing with every technology node, the proximity effect is becoming more serious. In the sub 100 nm region, the proximity effect is extremely severe and is a major obstacle for transition to 45 nm node and the subsequent 32 nm node.

The type and the thickness of the resist used also govern the mathematical calculation used for proximity effect correction. Thicker the resist more would be the forward scattering, thereby increasing the final beam diameter. Since backscattered electrons travel through the substrate, the type of substrate used plays an important role in proximity effect. The severity in proximity effect increases with decrease in the linewidth and the gap width. The denser the patterns are on the substrate, the distortion in the linewidth increases rapidly. Over the years, it has been suggested that the scattering events are affected by the initial electron energy, but recent research carried out by Erik H. Anderson et al [21], suggests that initial electron source does not govern the scattering and resist exposure mechanism. They have used 50 kV and 100 kV electron source on the same wafer coated with a thin layer of HSQ resist. The proximity effect can be corrected by incorporating a unique mathematical solution, for a particular function and pattern. This mathematical solution takes into account the factors leading to the proximity effect in the pattern and provides solution for the problem. Traditionally, proximity effect correction has been carried out using three basic techniques. These are *dose modulation*, shape modification and background correction exposure. Different program and software are used for the proximity correction. Commercial program like PROXECCO, as a component of CATS are used for dose modulation calculation. Shape and dose modulation are also carried out using the PYRAMID approach as suggested by S.Y. Lee [22]. The unique function of the PYRAMID approach is the use of the DSP model for finding the energy each pixel in the pattern. This cuts down the time required to find the amount of correction required for each pixel to take care of the proximity effect. The use of the DSP model also gives an accurate estimation of the correction required.

The PYRAMID approach for the proximity correction is different than other commercially available softwares like PROXECCO. In absence of any dose modulation software, proximity correction can be done using the shape modulation. This involves changing the design of the artifact to accommodate the increase in the dimension of the artifact on account of proximity effect. Proximity effect is seen more on sharp edges or corners due to high dose concentration. On account of this high dose concentration, the edges or the corners tend to round off. To avoid this problem, shape modulation is used for dimensional control of the design.

### 2.5 Resist Technology

The lithography tools have come a long way from its development period to be the forte of the current and the future technology nodes. The popularity of these lithography tools can be attributed not only to changes in the optics, the light sources, materials technology but also to the resist technology. Drastic changes in the resist technology enabled the lithography tools to define sub-micrometer structures with high precision. Resists are polymeric material dissolved in liquid solvent with varying molecular weights and compositions. Normally a thin layer of the resist is used for pattern definition. In places where overlaying of the patterns is required, multiple resist thicknesses are used. To achieve the multiple layers of the resists, the process flow is repeated as many times required. The resists are generally spun on the substrate, followed by baking the resist to get the required thickness and also to strengthen the bonds of the polymeric material. After radiation from the lithography tools, the resist undergoes a chemical reaction to facilitate the formation. The transfer of pattern design on the silicon wafer or other substrates is carried out after development, followed by etching. The selection of a resist and development of the resist process is a detailed research in itself. Once a resist process flow has been developed, it is rarely changed, unless a change ensures a substantial difference in the output of resist process. The International Technology Roadmap for Semiconductors (ITRS) has predicted the development of the resist technology over the next few years. The resist requirement as given by ITRS is in Table 2.3

Depending on the type of radiation used to cause the chemical reaction, resists are classifieds as *Photoresists* or *Electron beam resists*.

## Table 2.3: Resist requirements for near-term years [3].

# (Adapted from http://public.itrs.net)

| Year of Production                                                                  | 2005    | 2006    | 2007    | 2008    | 2009   | 2010   | 2011   | 2012   | 2013   |

|-------------------------------------------------------------------------------------|---------|---------|---------|---------|--------|--------|--------|--------|--------|

| DRAM ½ pitch (nm) (contacted)                                                       | 80      | 70      | 65      | 57      | 50     | 45     | 40     | 36     | 32     |

| Flash ½ pitch (nm) (un-contacted poly)                                              | 76      | 64      | 57      | 51      | 45     | 40     | 36     | 32     | 28     |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm)(contacted)                                       | 90      | 78      | 68      | 59      | 52     | 45     | 40     | 36     | 32     |

| MPU physical gate length (nm) [after etch]                                          | 32      | 28      | 25      | 23      | 20     | 18     | 16     | 14     | 13     |

| MPU gate in resist length (nm)                                                      | 53      | 47      | 42      | 38      | 33     | 30     | 27     | 24     | 21     |

| Resist Characteristics *                                                            |         |         |         |         |        |        |        |        |        |

| Resist meets requirements for gate resolution and gate CD control (nm, 3 sigma) **† | 3.3     | 2.9     | 2.6     | 2.3     | 2.1    | 1.9    | 1.7    | 1.5    | 1.3    |

| Resist thickness (nm, single layer) ***                                             | 150-265 | 125-225 | 110-200 | 100-180 | 90-160 | 80-145 | 70-130 | 60-115 | 55-100 |

| PEB temperature sensitivity (nm/C)                                                  | 2       | 1.75    | 1.75    | 1.5     | 1.5    | 1.5    | 1.5    | 1.5    | 1      |

| Backside particle density (particles/cm <sup>2</sup> )                              | 0.57    | 0.57    | 0.28    | 0.28    | 0.28   | 0.28   | 0.28   | 0.28   | 0.28   |

| Back surface particle diameter: lithography and<br>measurement tools (nm)           | 160     | 120     | 120     | 120     | 100    | 100    | 100    | 100    | 75     |

| Defects in spin-coated resist films (#/cm $^2$ ) $\dagger$                          | 0.01    | 0.01    | 0.01    | 0.01    | 0.01   | 0.01   | 0.01   | 0.01   | 0.01   |

| Minimum defect size in spin-coated resist films (nm)                                | 50      | 45      | 40      | 35      | 30     | 30     | 20     | 20     | 20     |

| Defects in patterned resist films, gates, contacts, etc. $(\#/cm^2)$                | 0.05    | 0.04    | 0.04    | 0.03    | 0.03   | 0.03   | 0.02   | 0.02   | 0.02   |

| Minimum defect size in patterned resist (nm)                                        | 50      | 45      | 40      | 35      | 30     | 30     | 20     | 20     | 20     |

| Low frequency line width roughness:<br>(nm, 3 sigma) <8% of CD *****                | 4.2     | 3.8     | 3.4     | 3.0     | 2.7    | 2.4    | 2.1    | 1.9    | 1.7    |

\* Noted exception for RED in next three years: Solution NOT known, but does not prevent production manufacturing.

Manufacturable solutions exist, and are being optimized Manufacturable solutions are known Interim solutions are known

Manufacturable solutions are NOT known

### 2.5.1 Photoresists

The printing industry has been a user of the photoresist for quite a long time. In the 1950s the semiconductor industries used the photoresist for the wafer fabrication processes. In the late 1950s, Eastman Kodak and the Shipley Corporation (now Rohm and Hass), respectively, were the first to introduce the negative and the positive resists [5].

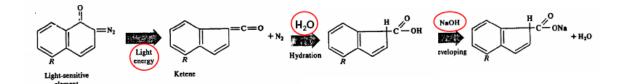

Photoresists are extensively used in the semiconductor industries for production of the sub micron level structures. The composition of the photoresist responds to a particular wavelength obtained from a set of defined exposure sources. The four most important ingredients of any photoresists are polymers, solvents, additives and sensitizes. The photoresist can be further characterized on the basis of its polarity. In a positive photoresists, the exposed part of the resist dissolve, while the unexposed part of the resist is unaffected by the developer reaction. While in the negative resist, the unexposed part dissolve in the developer, and the exposed part remains unaffected. As photolithography relies on the use of UV light source for fabrication, the resist used for pattern development changes as per the corresponding UV light source. The earlier UV sources had wavelength of the order of 405nm and 365nm, but with the further miniaturization of the features, 193nm ArF excimer laser is the current UV source for photolithography. The semiconductor industry would be making a transition to the 157nm light source in the near future. With this transition, a quest for new kind of resist which complies with the ITRS requirement is underway. The most common positive photoresist is the DQN resist, most suited for the i-line and g-line exposures (figure 2.14). As with every photoresist, DQN consists of a photoactive compound (DQ) and matrix material (N). The matrix material (Novolac) dissolves easily in aqueous solution. Though solvents are

Figure 2.14: Chemical structure for positive photoresist – DQN [23]

added to obtain the required viscosity, most of the solvent evaporates from the resist before the exposure. The photoactive compound – Diazoquinone (DQ) is insoluble in base solution, and changes to carboxylic group on exposure to UV source. The popularity of DQN photoresist is its good resolution capability, environmentally friendly and makes a good mask for plasma etching. With the ever increasing control over the critical dimensions of the features, there is a demand for resists which will satisfy the requirement of the semiconductor industries. One of the most common negative resist used for optical mask production is the SU-8 photoresist (figure 2.15). SU-8 works pretty well in the near UV range and can also be used as an e-beam resist. Features with very high aspect ratio with vertical sidewalls can be easily fabricated using SU-8 photoresist. Other advantages of SU-8 are its high sensitivity, fairly good adhesion properties, and easy processing conditions. Moreover the drying time for film thickness of 50µm is pretty less, thereby saving a lot of processing time.

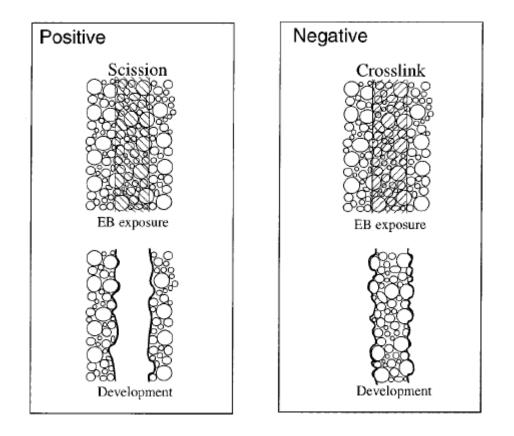

Both the negative and positive photoresist have almost the same process flow. The wafers are heated to remove any contaminants, followed by application of a adhesion promoter, hexamethyldisilazane (HMDS). The next step involves dispensing a predetermined amount of resist onto the wafer. After spinning, the wafer undergoes pre-bake or often called as soft bake. Pre-baking ensures that most of the solvent evaporates, leaving behind a uniform layer of resist. The temperature and time for pre-baking depends on many parameters which affect the final dimensions of the features. The wafers are later exposed to UV light source-photolithography to transfer the pattern design from the mask to wafers.

Figure 2.15: Chemical structure for negative photoresist - SU-8 [24]

### 2.5.2 Electron Beam Resists

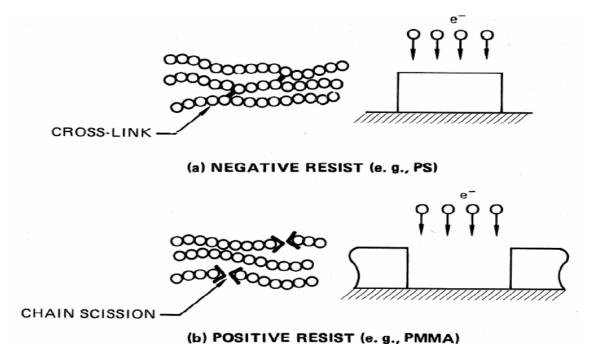

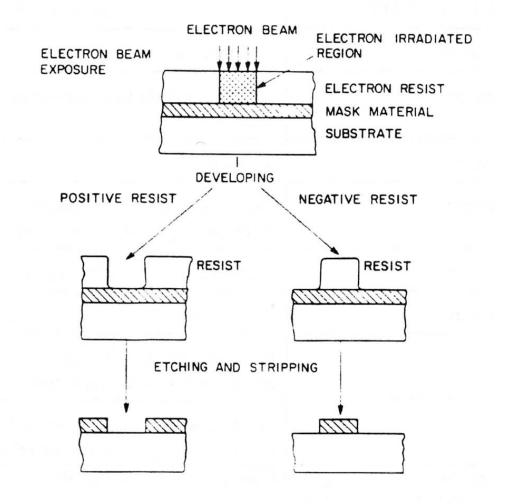

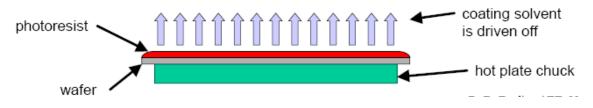

Unlike the photoresists which corresponds to a particular wavelength of the UV source, electron beam resists are exposed to a wide range of high intensity secondary electrons with different energies. Hence, there is a complexity in the chemical reactions involved in the bond formation or bond scission. Due to high energy of the electron beam, there is some damage to the substrate which further contributes to the complexity of the chemical reactions. The electron beam resists consist of long chain of carbon polymer, which on irradiation undergoes a process known as cross linking. Materials in which cross linking is a dormant reaction upon exposure are know as *positive resists*, while the materials in which cross linking is the dominant reaction on exposure are known as *negative resists* [11]. Most commonly used positive resist is polymethyl methacrylate (PMMA), which is extensively used for electron beam lithography. There are few other positive resists like EBR-9, PBS and ZEP which also offer good process control, though not as good as PMMA. Some of most commonly used negative resists are COP, Shipley SAL and HSQ. In recent years, hydrogen silsesquioxane (HSQ) has gained importance in terms of its use as an negative resist. Process integration issues associated with HSQ have been extensively studied. Most of the studies suggest the unique chemical structure of HSQ is the main driving force for its use as the electron beam resist. Electron beam resists are primarily used to get high resolution, with very good sensitivity. Features of the order of 10nm or less have been successfully been fabricated using electron beam resists-both positive and negative. The basic resist mechanism for the positive and negative is schematically illustrated in figure 2.16 and in figure 2.17.

Figure 2.16: Schematic representation of basic resist mechanism

Figure 2.17: Positive resist and Negative resist profile.

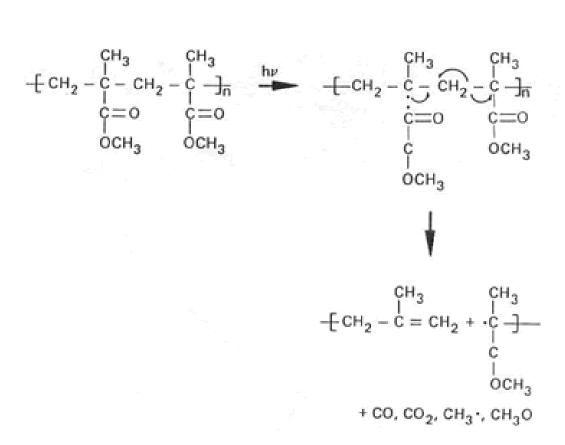

### 2.5.2.1 Polymethyl Methacrylate (PMMA)

One of the most common electron beam resist is polymethyl methacrylate (PMMA). It is considered to offer the highest resolution in any organic resist, hence PMMA is extensively used in the research and development of new lithography process. PMMA is normally not used for manufacturing process due to its low sensitivity [25]. It is generally used for short wavelength lithography: deep UV (220-250nm), extreme UV and electron beam lithography. Cross linking and fragmentation are the key to the formation of polymeric chains in polymethyl methacrylate (PMMA). The monomer of PMMA:

### -[CH<sub>2</sub>-CCH<sub>3</sub>(COO(CH<sub>3</sub>))]-

Unlike other hydrocarbon polymer, PMMA has very poor etch resistance which is one of the reason for using PMMA as a mask material. MicroChem Corp is one of the leading companies manufacturing positive electron beam resist PMMA. Normally, 495K and 950K molecular weights of PMMA are available formulated either in acetone or cholorobenzene. Unlike, the photoresists which require a photoactive compound (PAC) for sensitization by radiation, PMMA itself sensitizes upon radiation. It offers high resolution with good contrast and fair amount of sensitivity. The ultimate resolution of PMMA is affected by various parameters like the edge roughness, surface roughness, swelling of the resist and most important scattering of the electrons (proximity effect). Extensive research has been carried out to reduce the problems which are hindering the resolution of PMMA. Contrast, sensitivity, molecular weight are some of the other parameters which can influence the resolution of the positive resist. Moreover, the developing conditions also have effect on final resolution limit of the positive resist – PMMA (figure 2.18).

Figure 2.18: Chemical structure of PMMA : pre development and post development.

For electron beam resist, most of the development solutions consist of a strong solvent and a moderate non-solvent. The influence of these binary solutions on the developing conditions of any resist is complex reaction. One of the parameter which is affected by these binary solutions is the swelling, which in turn affects the resolution of the resists [26]. Molecular weight of a polymer determines the solubility of polymeric matrix after exposure. Plasticization and thermodynamic compatibility between the resist and the developer affects the solubilization rate [26]. The most common developer solution for PMMA is a mixture of Methyl Isobutyl Ketone (MIBK) and Isopropyl Alcohol (IPA) in varying proportion. MIBK:IPA (1:3) and MIBK:IPA (1:1) are some of commonly used development solution. The exposed part in the PMMA resist is removed, while the unexposed part of PMMA is unaffected when the development is carried out in MIBK: IPA. It is generally accepted that increasing the MIBK ratio, increases the sensitivity of the resist, but decreases the contrast value, thereby making it unsuitable for nanofabrication. S. Yasin et al have developed an alternative developer scheme for PMMA resist, which increases sensitivity (~40%), in contrast (~20%) compared to the MIBK:IPA 1:3 developer [26]. They used binary solution of Water:IPA (3:7) as a developer for PMMA to get best combination of sensitivity and contrast. When PMMA is developed in Water: IPA (3:7) solution, H<sub>2</sub>O molecule causes swelling of the exposed region, which is later on removed by IPA. Main chain scission occurs when the carboncarbon bond breaks into carbonyl carbon bond, causing volatile products as  $CO_{2}$ ,  $CH_3O$  and others [27]. This developer scheme ensures a low thickness loss for the unexposed region, thereby giving a good combination of contrast and sensitivity.

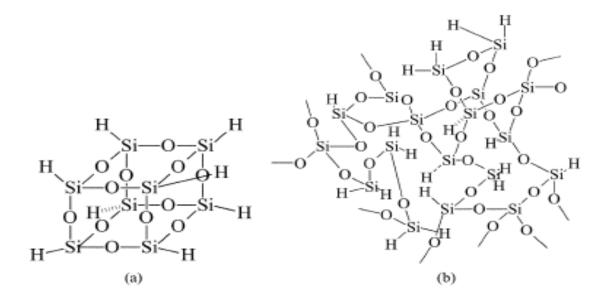

### 2.5.2.2 Hydrogen Silsesquioxane (HSQ)

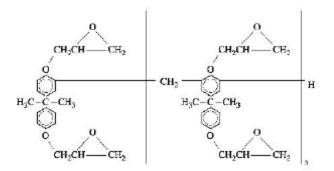

A low-k dielectric material, Hydrogen Silsesquioxane (HSQ) has long been used as an interlayer dielectric (ILD) in the semiconductor. Ultra high purity grade of HSQ is available from Dow Corning Corp., in form of Flowable Oxide<sup>®</sup> (FOx<sup>®</sup>) in different concentration grade. In recent years, lot of research has been focused on use of HSQ as a high resolution electron beam resist. HSQ has a negative tone, can be imaged directly in a SEM, and has high contrast and moderate sensitivity. HSQ is an inorganic resist with three dimensional structure which undergoes cross linking on exposure to electron beam. The cross linking in HSQ creates a structure on same lines of silicon dioxide [28]. Thermal treatment greatly affects the final structure of HSQ, which in turn can affect the ultimate resolution of the resist.

In generality, HSQ has a cage like structure which further changes to network like structure. There are two different schemes which define the chemical structure for HSQ. In the first case, HSQ is assumed to have a structure with silicon (Si) atom bound to three oxygen (O) and single hydrogen (H) atom (figure 2.19). During curing, a cross linking takes place with condensation of Si-OH group to Si-O-Si group, thereby forming a three dimensional structure [29].

In second case, HSQ is considered to have a caged oligomer structures with the general formula  $(HSiO_{3/2})_{2n}$ . The caged oligomer structure open up to form a network like structure. For electron beam exposure, the energy deposition is pretty high, hence bond scission and network forming is more pronounced during the exposure period, than the development period [29]. Being a negative resist, on development the unexposed part is dissolved while the exposed part is unaffected due to cross linking or network formation.

Figure 2.19: Chemical structures of HSQ (a) cage form (b) network form [30]

The development in tetramethyl ammonium hydroxide (TMAH) facilitates the bond scission in the unexposed part on the resist. The electron beam exposure gives rise to three dimensional network like structure, which decreases the dissolution rate in the exposed part of the resist during the development process in TMAH. Some of the factors like the exposure dose, baking time, baking temperature together with the developing conditions greatly affect the contrast and the sensitivity of the negative resist HSQ.