Masters Theses Graduate School

12-2003

## Silicon-on-Insulator Power Management Integrated Circuit for Thin-Film Solid-State Lithium-Ion Micro-Batteries

Jeremy Ross Jackson University of Tennessee - Knoxville

#### Recommended Citation

Jackson, Jeremy Ross, "Silicon-on-Insulator Power Management Integrated Circuit for Thin-Film Solid-State Lithium-Ion Micro-Batteries." Master's Thesis, University of Tennessee, 2003. https://trace.tennessee.edu/utk\_gradthes/2018

This Thesis is brought to you for free and open access by the Graduate School at Trace: Tennessee Research and Creative Exchange. It has been accepted for inclusion in Masters Theses by an authorized administrator of Trace: Tennessee Research and Creative Exchange. For more information, please contact trace@utk.edu.

#### To the Graduate Council:

I am submitting herewith a thesis written by Jeremy Ross Jackson entitled "Silicon-on-Insulator Power Management Integrated Circuit for Thin-Film Solid-State Lithium-Ion Micro-Batteries." I have examined the final electronic copy of this thesis for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Master of Science, with a major in Electrical Engineering.

Dr. Benjamin J. Blalock, Major Professor

We have read this thesis and recommend its acceptance:

Dr. Syed K. Islam, Dr. Donald W. Bouldin

Accepted for the Council: Carolyn R. Hodges

Vice Provost and Dean of the Graduate School

(Original signatures are on file with official student records.)

To the Graduate Council:

I am submitting herewith a thesis written by Jeremy Ross Jackson entitled "Silicon-on-Insulator Power Management Integrated Circuit for Thin-Film Solid-State Lithium-Ion Micro-Batteries." I have examined the final electronic copy of this thesis for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Master of Science, with a major in Electrical Engineering.

|                               | Dr. Benjamin J. Blalock   |

|-------------------------------|---------------------------|

|                               | Major Professor           |

|                               |                           |

|                               |                           |

| We have read this thesis      |                           |

| and recommend its acceptance: |                           |

| Dr. Syed K. Islam             |                           |

| Dr. Donald W. Bouldin         |                           |

|                               |                           |

|                               |                           |

|                               | Accepted for the Council: |

|                               | Anne Mayhew               |

|                               | Vice Provost and          |

|                               | Dean of Graduate Studies  |

(Original signatures are on file with official student records.)

# SILICON-ON-INSULATOR POWER MANAGEMENT INTEGRATED CIRCUIT FOR THIN-FILM SOLID-STATE LITHIUM-ION MICRO-BATTERIES

A Thesis Presented for the

Master of Science Degree

The University of Tennessee, Knoxville

Jeremy Ross Jackson December 2003

## **DEDICATION**

This thesis is dedicated to my grandfather, Roland B. Butterfield, II, who was always there to give a helping hand whenever I needed it most.

#### ACKNOWLEDGMENTS

I would like to thank all the professors at the University of Tennessee who have instructed me through my undergraduate and graduate studies. Professors T.V. Blalock and M.L. Simpson taught me how important the fundamentals of electronics are in order to build a strong foundation for future learning. I would also like to thank my graduate committee; Dr. B.J. Blalock, Dr. S.K. Islam, and Dr. D.W. Bouldin, for reviewing and directing the work for this thesis. Special thanks to Dr. B.J. Blalock for serving as head of my committee and providing excellent instruction in the field of analog circuit design.

I am grateful to the University of Tennessee for the graduate research assistantship that I received to work in the Integrated Circuits and Systems Laboratory under Dr. B.J. Blalock, which made this thesis possible. The work for this thesis also could not have been completed without the help of my fellow graduate research assistants. Special thanks to Stephen Terry for his never-ending help in all areas of electronics and to Suheng Chen for providing help with Cadence problems and layout.

I would also like to thank Analog Devices Inc. for providing me with the Analog Devices Fellowship that provided support for some of this work. This fellowship also facilitated a position for me as a summer intern at ADI's Greensboro, NC design center. There is no substitute for a hands-on learning experience.

Finally, I would like to thank my family and friends who have been very supportive while I completed my master's degree. I would especially like to thank my Aunt Judy and Uncle Gus who have always provided a home for me when I needed to take some time off.

This work was supported by the Jet Propulsion Laboratory (JPL), California Institute of Technology, under a contract with the National Aeronautics and Space Administration (NASA). Part of this work was done through collaboration with the University of Idaho, also under contract with JPL.

#### **ABSTRACT**

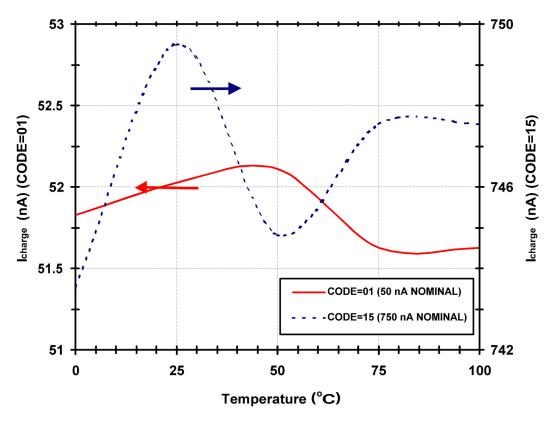

This thesis presents the design and implementation of a power management integrated circuit (IC) that is capable of both current and voltage charging thin-film, solid-state, lithium-ion micro-batteries. The power management system has been fabricated using a single-poly, 0.35-µm, partially-depleted, silicon-on-insulator process (PD-SOI). The system contains a temperature stable current charger (current generator and a 4-bit current-mode DAC), a regulated voltage supply (voltage amplifier), and a voltage monitoring circuit (2-bit flash ADC). Experimental results of the first version of the power management system show proper functionality was obtained. The current charger produced a 2% worst-case variation in output current over the temperature range 0–100°C. The regulated voltage output was measured to be 4.4 V and the digital outputs of the flash ADC transitioned at 3.45 and 4.76 V.

## TABLE OF CONTENTS

| Chap | oter                                                       | Page |

|------|------------------------------------------------------------|------|

| I.   | Introduction and Overview                                  | 1    |

|      | Introduction                                               | 1    |

|      | Overview                                                   | 3    |

| II.  | Micro-Battery Power Management System Concepts             | 4    |

|      | Micro-Battery Structure                                    |      |

|      | Current Source                                             | 5    |

|      | Voltage Source                                             | 11   |

|      | Low-Resolution ADC                                         | 13   |

| III. | Design of Micro-Battery Power Management System Components | 17   |

|      | Programmable Current Source                                | 17   |

|      | Current Generator                                          | 17   |

|      | Current Output DAC                                         | 22   |

|      | Regulated Voltage Source                                   |      |

|      | Micro-Battery Voltage Monitor                              | 37   |

| IV.  | Micro-Battery Power Management System – Measured Results   | 43   |

|      | Test Setup                                                 |      |

|      | Micro-Battery Current Charger                              | 45   |

|      | Micro-Battery Voltage Charger                              |      |

|      | Micro-Battery Voltage Monitor                              | 56   |

| V.   | Conclusion                                                 | 60   |

|      | Conclusion                                                 | 60   |

|      | Future Work                                                | 60   |

|      | Bandgap Voltage Reference                                  | 61   |

|      | Beta-Multiplier Current Reference                          |      |

|      | 4-Bit Flash ADC                                            | 68   |

| LIST | Γ OF REFERENCES                                            | 72   |

| APP  | ENDIX                                                      | 77   |

| VIT. | Α                                                          | 79   |

## LIST OF FIGURES

| Figure       | I                                                                               | Page |

|--------------|---------------------------------------------------------------------------------|------|

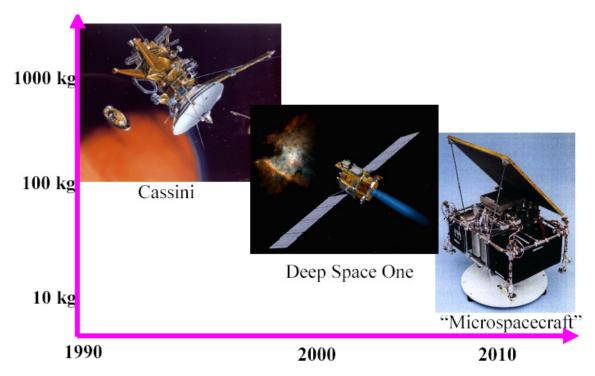

| Figure 1.1:  | Reduction in spacecraft mass and volume over time.                              | 2    |

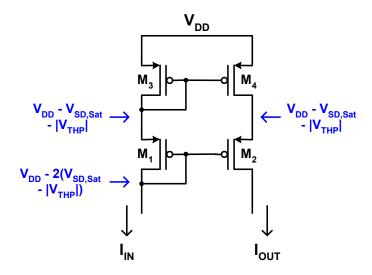

| Figure 2.1:  | Cascode current mirror.                                                         | 8    |

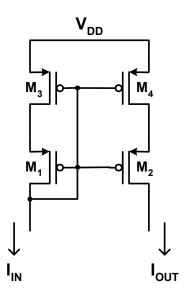

| Figure 2.2:  | Wide-swing, low-voltage cascode current mirror.                                 | 9    |

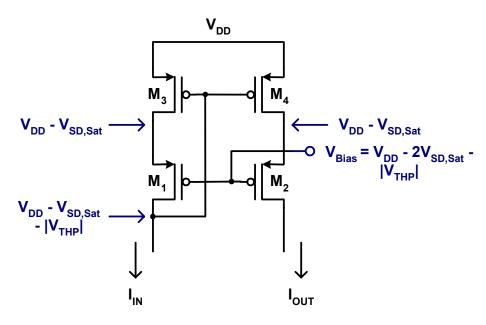

| Figure 2.3:  | Self-biased cascode current mirror                                              |      |

| Figure 2.4:  | Minch cascode current mirror.                                                   | 11   |

| Figure 2.5:  | Schematic of series voltage regulator                                           | 12   |

| Figure 2.6:  | Basic flash ADC architecture.                                                   |      |

| Figure 2.7:  | Single stage of pipelined converter.                                            | 15   |

| Figure 2.8:  | Successive-approximation (SAR) ADC architecture                                 |      |

| Figure 3.1:  | Beta-multiplier current reference topology.                                     |      |

| Figure 3.2:  | Drain current plotted from weak to strong inversion.                            |      |

| Figure 3.3:  | Hole mobility in bulk silicon vs. temperature.                                  |      |

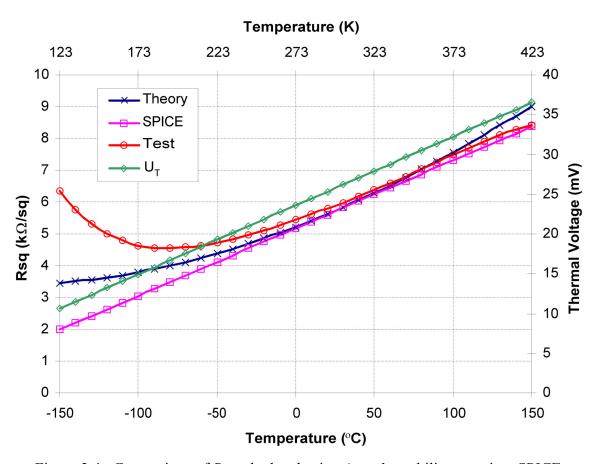

| Figure 3.4:  | Comparison of $R_{sq}$ calculated using Arora's mobility equation, SPICE        |      |

| C            | simulations, and measured results, all compared to thermal voltage $U_T$        | 23   |

| Figure 3.5:  | Current-mode DAC topology                                                       | 24   |

| Figure 3.6:  | Sample and hold circuit illustrating charge injection.                          | 25   |

| Figure 3.7:  | Input slew-rate control circuit applied to each of the DAC inputs               |      |

| Figure 3.8:  | Simulation of input slew-rate control circuit.                                  |      |

| Figure 3.9:  | Simulation results of start-up and active conditions of DAC output              | 28   |

| Figure 3.10: | V <sub>GS</sub> -multiplier biasing the LVCCM of the DAC output stage           |      |

| _            | $I_{DS}$ vs. $V_{DS}$ curve showing regions of operation of an nMOS transistor  |      |

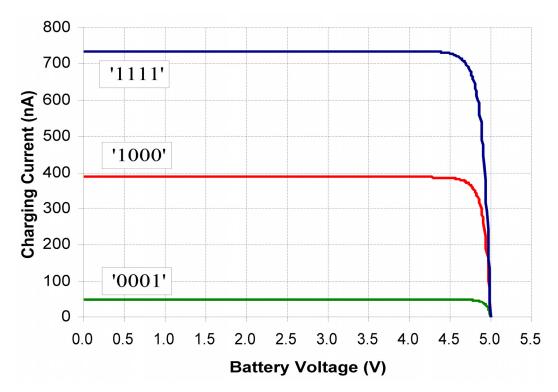

| _            | Simulated DC sweep of current charger output at room temperature for            |      |

| _            | selected input codes.                                                           | 33   |

| Figure 3.13: | Simulation of DAC mid-scale output plotted against temperature                  | 34   |

|              | Calculated $IC$ of $M_1$ and $M_2$ devices of beta-multiplier current reference |      |

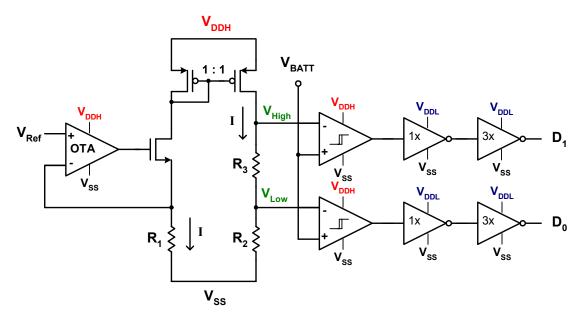

|              | Regulated voltage source using a voltage amplifier                              |      |

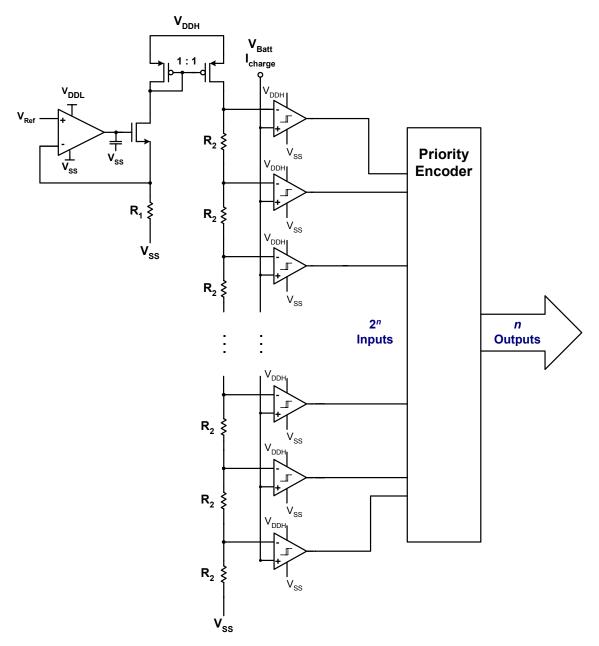

|              | Two-bit flash ADC architecture.                                                 |      |

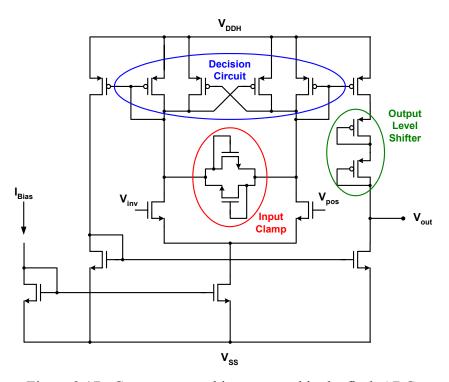

| Figure 3.17: | Comparator architecture used in the flash ADC.                                  | 39   |

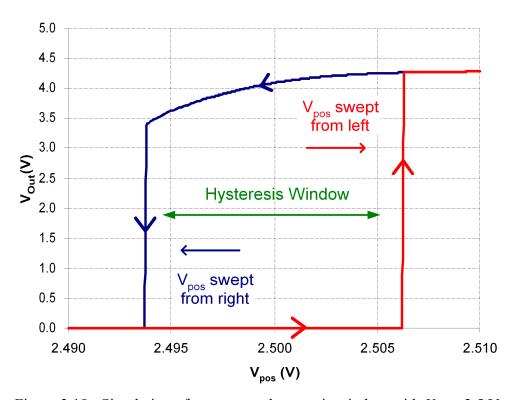

|              | Simulation of comparator hysteresis window with $V_{inv} = 2.5 \text{ V}.$      |      |

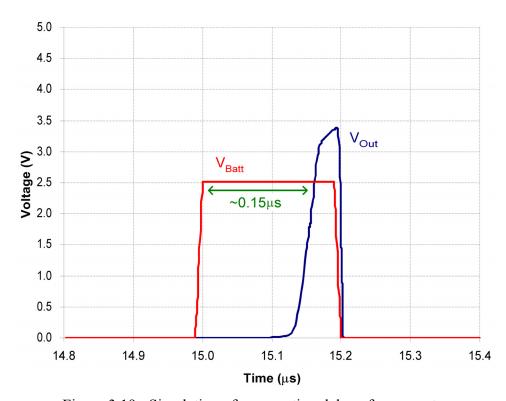

|              | Simulation of propagation delay of comparator                                   |      |

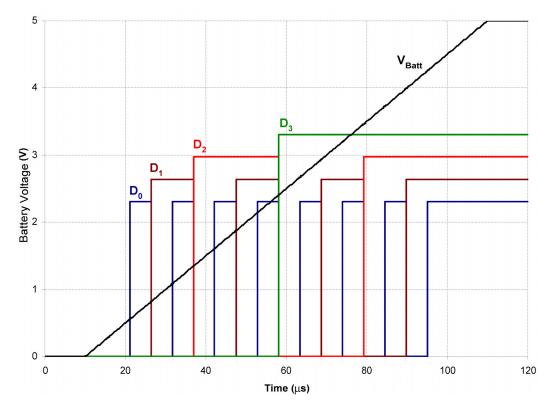

|              | Flash ADC simulation by sweeping $V_{Batt}$                                     |      |

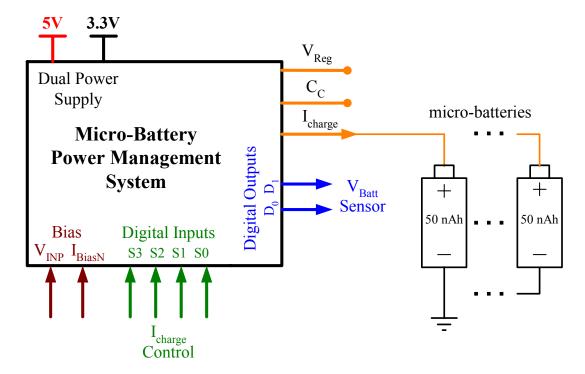

| Figure 4.1:  | System level diagram of micro-battery power management system                   | 43   |

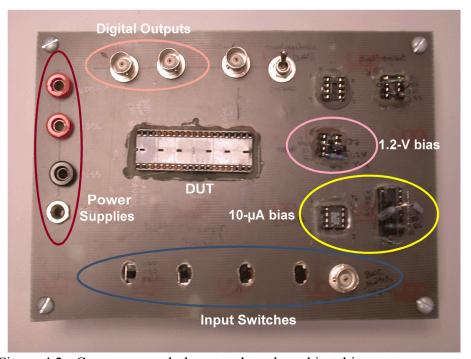

| Figure 4.2:  | Copper ground plane test board used in taking measurements.                     | 44   |

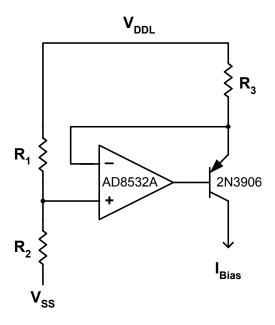

| Figure 4.3:  | Off-chip 10-µA bias current generator.                                          |      |

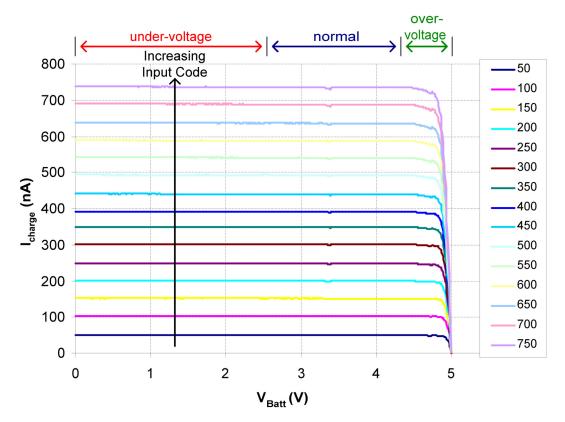

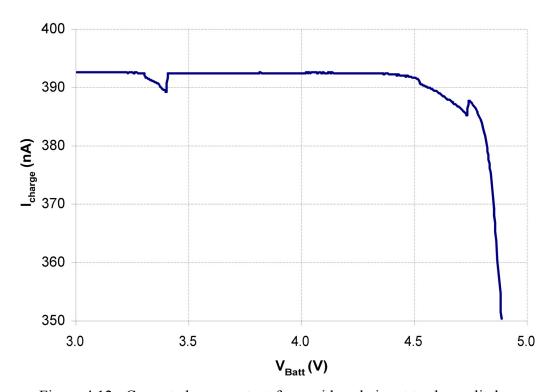

| Figure 4.4:  | Measured DC sweep of $V_{Batt}$ at room temperature for each DAC code           |      |

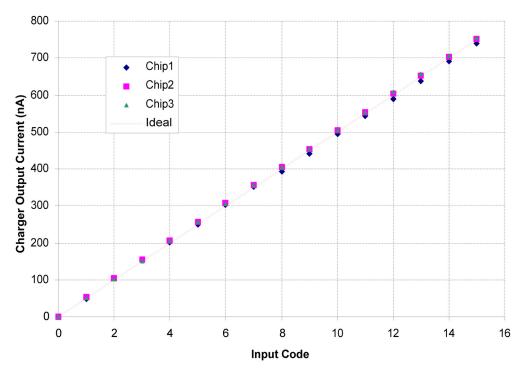

| Figure 4.5:  | Measured transfer cure of the programmable current charger.                     |      |

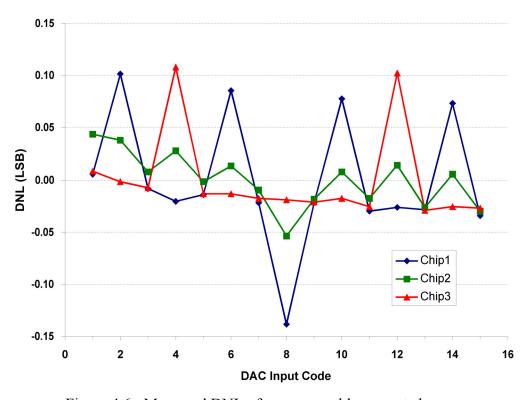

| Figure 4.6:  | Measured DNL of programmable current charger.                                   |      |

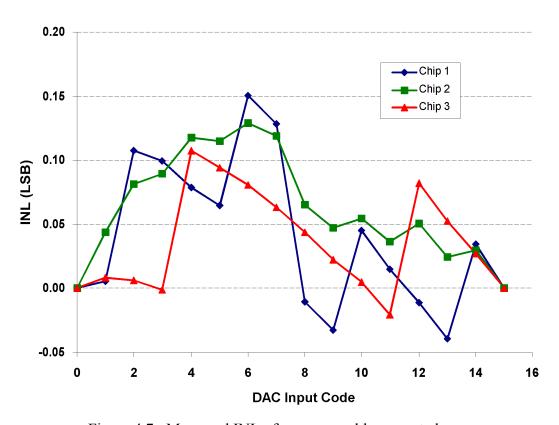

| Figure 4.7:  | Measured INL of programmable current charger                                    |      |

| Figure 4.8:  | Temperature comparison of 50 and 750-nA <i>I<sub>charge</sub></i> currents      |      |

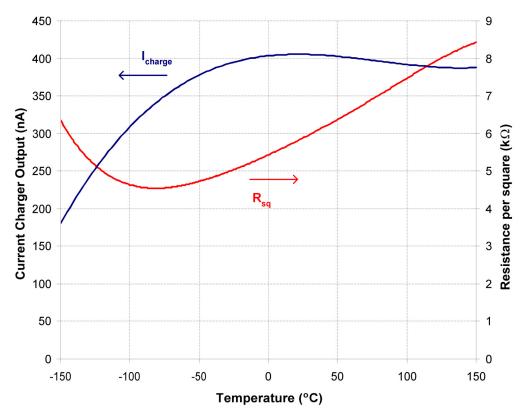

| Figure 4.9:  | Comparison of current charger output and p-well $R_{sq}$ .                      |      |

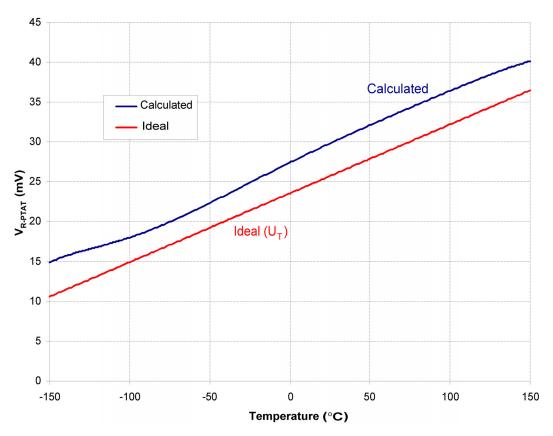

| Ideal and calculated PTAT voltage reference across temperature          | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

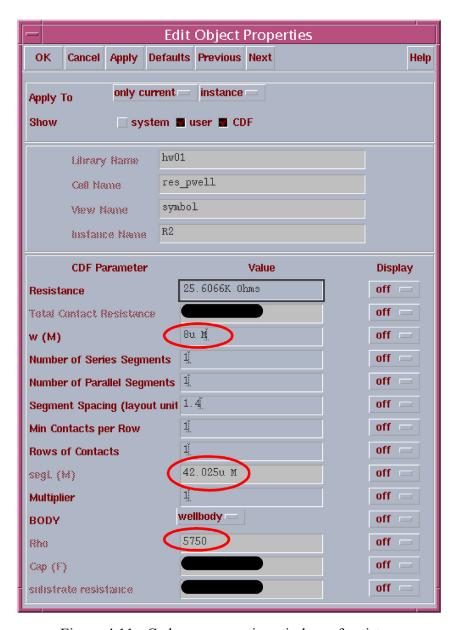

| Cadence properties window of resistor.                                  | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Current charger output for a mid-scale input to show glitches.          | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Simulation of overall gate capacitance of comparator input devices      | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

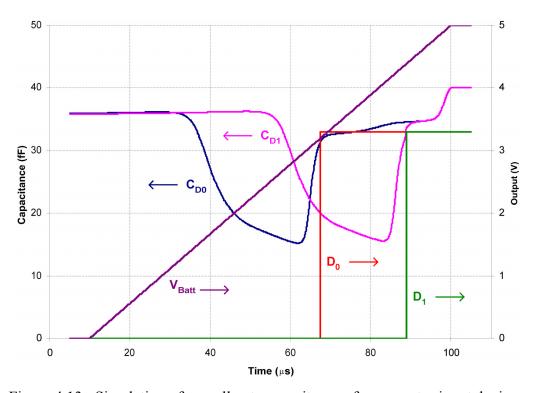

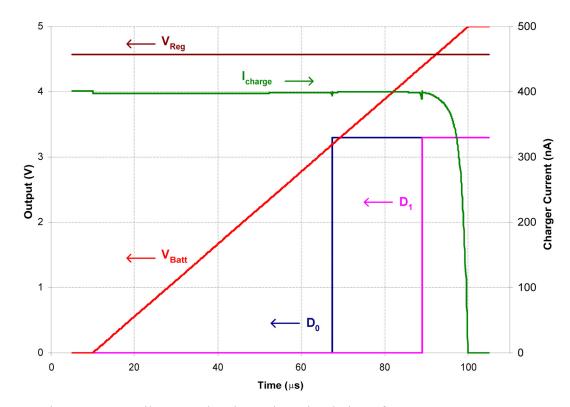

| Full system-level transient simulation of power management IC           | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

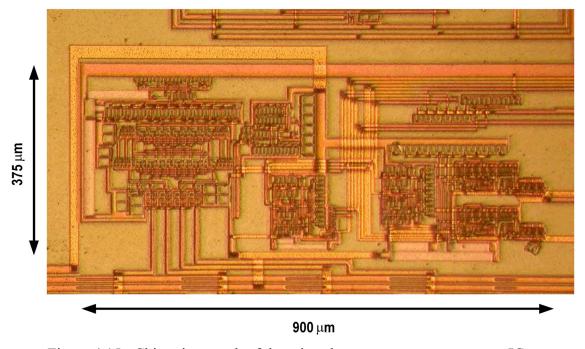

| Chip micrograph of the micro-battery power management IC.               | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

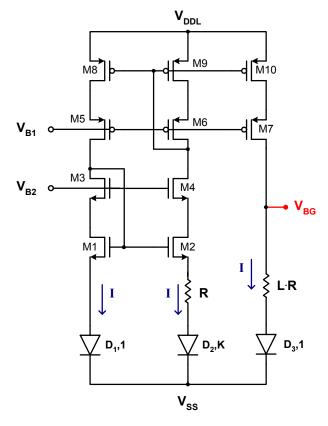

| Bandgap voltage reference circuit.                                      | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

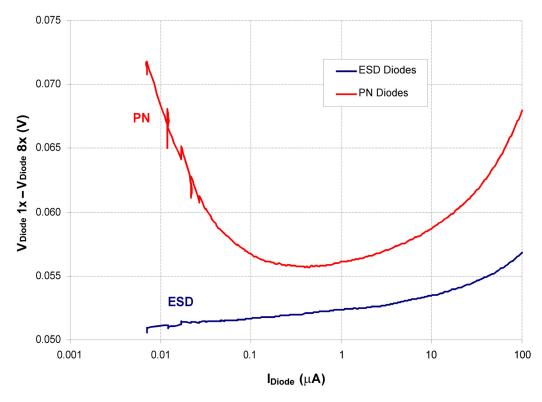

| Voltage difference of 1× and 8× diode sizing for ESD and PN diodes      | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

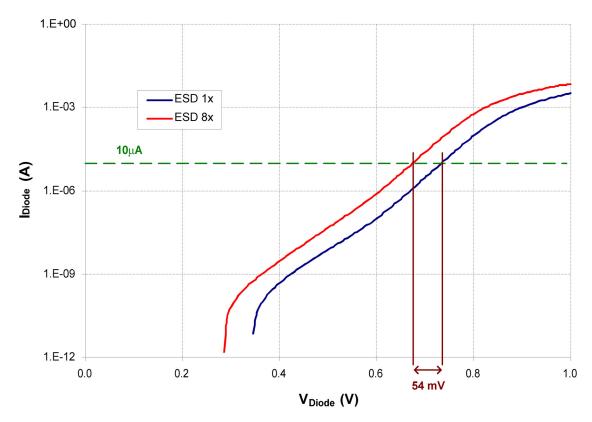

| Measured I–V characteristics of 1× and 8× ESD diodes                    | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

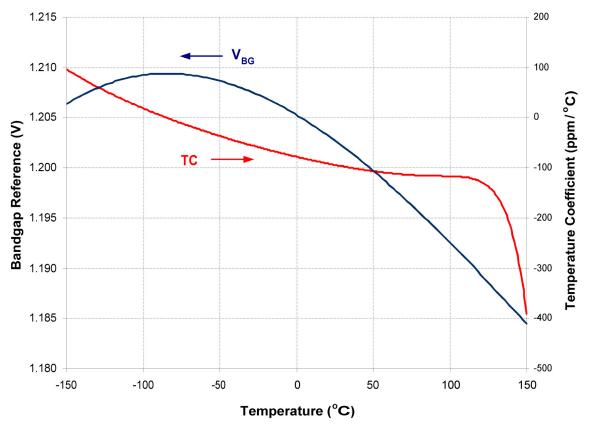

| Simulation of bandgap reference temperature performance.                | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

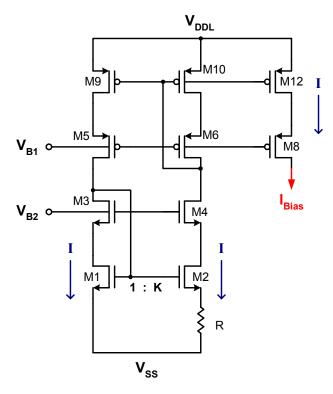

| Beta-multiplier self-biased current reference.                          | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4-bit flash ADC architecture with priority encoder                      | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Transient simulation of 4-bit flash ADC with priority encoder. (Digital |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| output levels scaled to show transitions—normally logic '1' = 3.3 V.)   | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

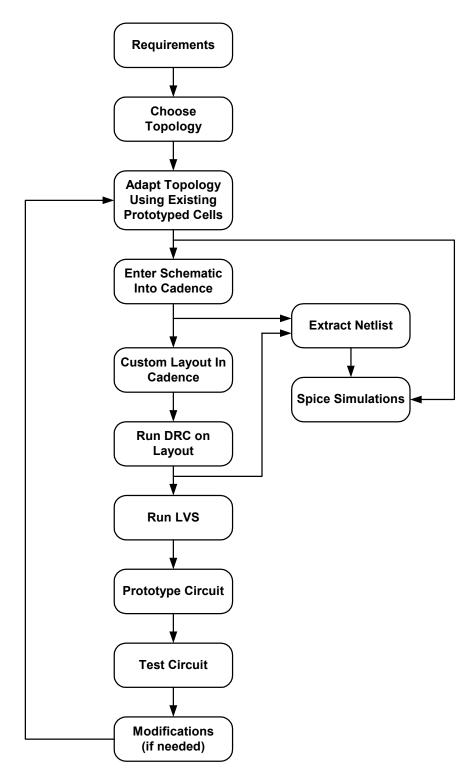

| Design flow process                                                     | 78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                         | Cadence properties window of resistor.  Current charger output for a mid-scale input to show glitches.  Simulation of overall gate capacitance of comparator input devices.  Full system-level transient simulation of power management IC.  Chip micrograph of the micro-battery power management IC.  Bandgap voltage reference circuit.  Voltage difference of 1× and 8× diode sizing for ESD and PN diodes.  Measured I–V characteristics of 1× and 8× ESD diodes.  Simulation of bandgap reference temperature performance.  Beta-multiplier self-biased current reference.  4-bit flash ADC architecture with priority encoder.  Transient simulation of 4-bit flash ADC with priority encoder. (Digital output levels scaled to show transitions—normally logic '1' = 3.3 V.) |

#### **CHAPTER 1**

#### INTRODUCTION AND OVERVIEW

#### Introduction

Recent successes in the effort to miniaturize spacecraft components using microelectromechanical systems (MEMS) technology, integrated passive components, and low power electronics have driven the need for very low power, low profile, low mass micro-power sources for micro/nanospacecraft applications [1]. The power sources chosen to combat this problem are rechargeable, thin-film and micro-scale batteries prepared using microelectronic fabrication techniques. A number of thin-film micro-batteries have been documented in literature and of these, rechargeable lithium (Li) batteries have shown the best performance of cycle life and shelf life [2]. These Li-Ion micro-batteries are proving themselves to be useful in more applications than expected.

Due to the complications and safety requirements needed to send a human into deep space, unmanned space flights aimed at exploring the far reaches of the universe are underway. However, the cost of launching a spacecraft into outer space is proportional to its mass, so efforts are being made to achieve the goal of "microspacecrafts" as shown in Figure 1.1. Power electronics generally contribute considerably to the mass and volume of the total avionics systems, which can be problematic for applications leveraging miniaturized components [1]. As power electronics miniaturize, the power sources must also decrease in size in order to meet this goal of microspacecrafts.

Micromachining manufacturing methods have made MEMS-based sensors and actuators a reality and there is a push for power sources small enough to fit on a microchip to power them [2]. Because of this, there is a growing interest in the development, fabrication, and volume manufacturing of these micro-power sources [3]. With the enhancement of power sources on the same microchip as MEMS, energy efficiency could be maintained due to low power transmission losses, cost would decrease due to reduced complexity of electrical connections and packaging, and the

Figure 1.1: Reduction in spacecraft mass and volume over time.

micro-power cells could be arrayed to achieve different combinations of operating voltages for an integrated circuit [2].

Circuit designers could also benefit from the use of micro-battery structures. One possibility in the case of low current applications is for a micro-battery to act as an on-chip power supply [4]. Something being investigated at JPL is the use of thin-film micro-batteries to act as momentary CMOS memory backup in the event of system power failure [1]. Analog circuit designers could also utilize micro-batteries as voltage shifters or as on-chip, low noise, reference voltages. This is a vast area that has yet to be explored fully for use in CMOS analog circuit design for system on a chip (SOAC) applications.

As one can see, the use of a micro-battery structure is only limited by the imagination of the user. The one thing missing from all the literature dealing with micro-power sources, however, is the design of a power management IC capable of recharging these micro-batteries.

#### **Overview**

This thesis provides a detailed overview of a power management IC designed for solid-state, Li-Ion micro-batteries using a standard 3.3-V/0.35-µm, single-poly, PD-SOI process. The power management design consists of a programmable current charger, a constant voltage charger, and a voltage monitoring circuit that reads the micro-battery's voltage during the current charging process. The programmable current charger is designed using a temperature stable, low-level current reference that feeds into a current-mode digital-to-analog converter (DAC), which uses a new technique to bias low-voltage cascode current mirrors (LVCCM). The voltage charger is designed using voltage amplifier techniques and the voltage monitoring circuit is designed using a low-resolution flash analog-to-digital converter (ADC) architecture.

Contained in this thesis are four main sections. Chapter 2 starts with a brief description of the micro-battery structures that are currently being developed by researchers at JPL. Also included in this chapter are descriptions of the different circuit designs that were considered when investigating the design of this micro-battery power management system.

Chapter 3 provides an in-depth analysis of the topologies chosen to implement this system including first-order theory and simulation results where applicable. A comparative discussion of alternate topologies is also presented.

Chapter 4 gives the measured results achieved from first-run silicon as well as presents the test setup used in taking these measurements. The measured results are compared against theoretical and simulated results obtained from the previous chapter.

Chapter 5 provides conclusions for this work and details the enhancements that were made for the first revision of this system. Figure A-1 contains the typical design flow used in designing each component of this power management IC.

#### CHAPTER 2

#### MICRO-BATTERY POWER MANAGEMENT SYSTEM CONCEPTS

#### **Micro-Battery Structure**

The batteries that are to be charged with this power management system are thin-film, solid-state, Li-Ion micro-batteries. Numerous papers have been written on processing procedures and characterization of these types of micro-batteries [1]–[8]. The power management IC presented in this thesis is targeted for use on the micro-batteries developed at JPL.

JPL researchers have been trying to develop a processing technique aimed at integration of micro-battery cells directly on-chip. The fabrication process used by JPL is based upon the Oak Ridge National Laboratory (ORNL) process. This process calls for annealing the sputtered films at 700°C in order to crystallize the cathode film [1]. This high temperature anneal makes it almost impossible to fabricate cells on temperature sensitive substrates (such as ICs), so JPL has pushed for developing a lower annealing temperature process on the order of 300°C, which is more compatible with CMOS technology. Using this lower annealing temperature, they have fabricated cells with slightly reduced capacity cathodes but maintained excellent cycle life.

Just recently, JPL has found an improved method of fabrication for micro-battery cathodes that requires less processing steps [7]. The energy storage capability of a micro-battery is limited by the amount of active material present [2]. The volume of active electrode material that can be deposited by sputtering is limited and the process is slow. The new method uses electrophoretic deposition (EPD), which is much faster and has shown to produce cells with a factor of ten increase in discharge capacities [7].

Micro-batteries that have been made available for this project have a reported capacity of 50 nAh. The full-rated voltage for a cell is 4.25 V with a normal operating condition between 3 and 4.25 V. A cell is overcharged if its voltage is above 4.4 V and in deep discharge for a voltage level below 2 V. The normal charge rate is 50 nA or 1 capacity (1 C) of the micro-battery with efficient charge rates as low as 0.1 C [5].

Two charging methods are needed when charging a Li-Ion micro-battery—current charging and voltage charging [5]. The necessity to charge micro-batteries at or below 50 nA requires the design of a low-level current reference. The voltage charger is given the task of maintaining a 4.25-V voltage bus to trickle charge a micro-battery to complete its charging cycle once it reaches full voltage capacity, or storing unused micro-batteries. Since a fully charged micro-battery is 4.25 V, this system has to operate with a 5-V supply, but recall that a  $3.3\text{-V}/0.35\text{-}\mu\text{m}$  technology is being used to fabricate this system. This requires the use of dual  $V_{DD}$  supply rails denoted by  $V_{DDH}$  and  $V_{DDL}$  for the 5 and 3.3-V supplies, respectively, and carefully designed circuit topologies.

The micro-battery's voltage state during the current charging process has to be monitored so that when the micro-battery reaches 4.25 V, it can be transitioned from current charging to voltage charging. A low-resolution ADC was chosen to create the digital output representation of a micro-battery's voltage state.

#### **Current Source**

Current references are one of the basic building blocks of analog circuitry. Requirements desired from most current references are high output impedance, low temperature sensitivity over a broad temperature range and good power supply rejection. CMOS current references that perform well over temperature or require small area to implement have been reported [9]–[14]. For this power management system, it is desired to have a low-level current reference that occupies a small area and is insensitive to temperature variations.

In MOS transistors, the temperature dependence of the drain current originates from various physical parameters such as threshold voltage ( $V_{TH}$ ), mobility ( $\mu$ ), and thermal voltage ( $U_T$ ). The mobility dependence of carriers in the conduction channel on temperature is given by

$$\mu(T) = \mu(T_0) \times \left(\frac{T}{T_0}\right)^{-1.5}$$

(2.1)

where T is the absolute temperature in Kelvin and  $T_0$  is 300K [15]. Some circuits reduce the effects of temperature on mobility by generating a proportional-to-absolute temperature (PTAT) voltage reference that can be used to produce an output current that is proportional to  $T^{0.5}$ , and therefore only slightly increases with temperature [10].

A common way to produce a PTAT voltage reference is to use bipolar transistors, but the only bipolar transistor available in a standard CMOS process is a parasitic vertical bipolar. These vertical bipolar transistors are poorly modeled, so an all CMOS topology seems better suited to design a current reference. Sansen *et al.* developed an 800-nA current reference based off a bipolar PTAT voltage source implemented using floating MOSFETs operating in weak inversion [10]. This circuit uses several weakly inverted MOSFETs to generate the PTAT source, which in turn requires a large aspect ratio for those devices, consuming a large amount of chip area. Measured results of this system show 3% temperature dependence between 0 and 80°C with a MOSFET acting as the current defining element.

To further reduce the temperature insensitivity of this type of design, Lee and Park [11] tried to completely cancel out the mobility dependence in the output current by multiplying a current that is proportional to mobility and a current that is inversely proportional to mobility with a CMOS square root circuit. The CMOS square root circuit uses four pMOS transistors operating in weak inversion, which again requires a large area. The result of this work is a 1.7% variation of output current (285 nA at 60°C) over a temperature range 0–75°C.

A well-known current reference proposed by Vittoz and Fallrath [9] is expanded upon by eliminating the need for a space-consuming resistor [12]. In lieu of a resistor, the new topology calls for a MOSFET operating in triode or linear mode of operation. This circuit topology uses weak inversion MOSFETs to set up a PTAT voltage source across the linear MOSFET. This circuit is capable of producing extremely low reference currents (5 nA with a 3-V supply at 20°C), but occupies a large area due to the aspect ratio of the linear MOSFETs needed to create a large resistance used in generating a low-level reference current.

Another possible method of generating an on-chip current reference is explored in [13] using a switched-capacitor network. The motivation for a switched-capacitor circuit is to avoid relying on physical parameters of MOS transistors and IC resistors to set an accurate reference current. In addition, capacitance per unit area can be substantially independent of temperature. The value of the reference current generated using Torelli's switched-capacitor circuit is given by [13]

$$I = \frac{C \times V_{Ref}}{f_{clk}}$$

(2.2)

where C is the value of the capacitance, and  $f_{clk}$  is the clock frequency in Hz. One of the problems associated with this method of current generation is a ripple in the output current at the switching frequency. This output current is also directly dependent on the reference voltage  $(V_{Ref})$  applied, but can be adjusted by varying the clock frequency.

Instead of trying to just obtain first-order temperature effect cancellation of a current reference, some designs try to compensate for second-order temperature effects as well [14]. The proposed circuit by Fiori and Crovetti uses only five MOSFETs operating in strong inversion saturation and two resistors to cancel second-order temperature effects. Simulated results of this circuit show that a 13.65- $\mu$ A reference current with less than 0.5% variation of current output over the temperature range from –30 to 100°C has been developed in a 0.35- $\mu$ m process. This circuit can be very compact because it requires only MOSFETs operating in strong inversion saturation to be used, which normally translates to transistors with small aspect ratios.

Once a low-level reference current topology has been chosen, the reference current can be scaled accordingly using weighted current mirrors. The application for this power management system dictates that it should be able to charge multiple microbatteries at one time. This can be achieved by designing a low-resolution current-mode DAC to scale the reference current. We set the limit for the number of micro-batteries to be charged at once to 15, which means the DAC needs to be capable of maintaining 4-bit accuracy if binary weighted current mirrors are used.

When charging either a single or multiple micro-batteries at a time, the current charging output must remain a high impedance node to efficiently deliver current to the micro-battery. Cascode current mirrors provide an improvement of output resistance over simple current mirrors. The small-signal output resistance ( $R_o$ ) of the cascode current source in Figure 2.1 is given by

$$R_o = r_{o2} (1 + g_{m2} r_{o4}) + r_{o4} \approx g_{m2} r_o^2$$

(2.3)

where  $r_o = r_{o2} = r_{o4}$  is the MOSFET small-signal output resistance and  $g_m$  is the MOSFET small-signal transconductance. If  $M_1$  and  $M_2$  were removed from Figure 2.1, a simple current mirror would be left whose small-signal output resistance would be equal to  $r_{o4}$ .

Although this cascode current mirror provides high output impedance, it does not allow for a high output voltage swing. The dynamic range of this cascode current mirror with respect to  $V_{DD}$  is limited to less than

$$V_{OUT} = V_{DD} - 2V_{SD,Sat} - |V_{THP}| \approx V_{DD} - 1.3V$$

(2.4)

where  $V_{SD,Sat}$  is the saturation voltage of a pMOS transistor and  $V_{THP}$  is the pMOS threshold voltage. Recall that the full voltage capacity of a micro-battery is 4.25 V. If the 5-V supply were used to bias this cascode current mirror, there would not be enough

Figure 2.1: Cascode current mirror.

Figure 2.2: Wide-swing, low-voltage cascode current mirror.

headroom to charge a micro-battery fully with this current mirror. Alternate schemes of biasing cascode current mirrors for wide-swing or low-voltage applications exist [16]–[20].

The typical wide-swing, low-voltage cascode current mirror is presented in Figure 2.2. For this wide-swing current mirror to work efficiently,  $V_{Bias}$  must be set at  $V_{DD}$  –  $2V_{SD,Sat} - |V_{THP}|$ , leaving a  $V_{SD,Sat}$  across mirror devices  $M_3$  and  $M_4$ . This is called a wide-swing current source because the minimum voltage across the current source for proper operation is  $2V_{SD,Sat}$  [16], which is one threshold voltage drop less than the regular cascode mirror shown in Figure 2.1. This current mirror is dependent on the voltage of  $V_{Bias}$  remaining constant and only works well for a small variation of input current. For a large change of the input current, additional circuitry is required to track the  $V_{SG}$  of the cascode devices  $M_1$  and  $M_2$ , so the current mirror's output characteristics do not vary [19].

One approach to increase the dynamic range of a current mirror without extra biasing voltages is the self-biased structure shown in Figure 2.3. Assuming that the threshold voltage of the devices are similar, [18] shows that the mirror devices  $M_3$  and  $M_4$

Figure 2.3: Self-biased cascode current mirror.

are in the triode or linear region and the cascode devices  $M_1$  and  $M_2$  are in saturation. This topology allows for simple implementation and high output voltage swing, but having the mirror devices biased in the linear region lead to some disadvantages [19]. Linear mode MOSFETs have a high susceptibility to transistor mismatch causing current gain errors and output impedance is reduced compared to a conventional cascode current mirror.

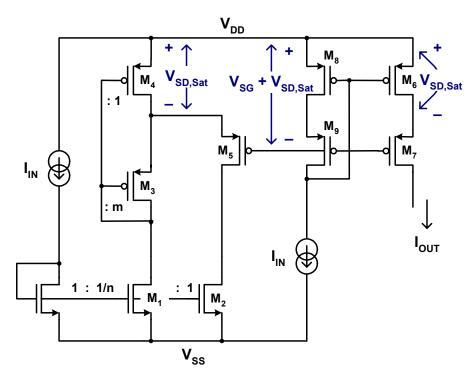

Minch developed a circuit that biases the mirror devices in a cascode current mirror right at the edge of saturation, thus optimizing its dynamic range [20]. A schematic of this circuit is shown in Figure 2.4. The values of the aspect ratios n and m are described in the paper. The circuit operates by using the input current and a ratio of the input current to set up an exact  $V_{SD,Sat}$  voltage drop across device  $M_4$ .  $M_5$  then acts as a level shifter, which creates a voltage of  $V_{DD} - V_{SG} - V_{SD,Sat}$  on the gate of  $M_5$ . The gate voltage on  $M_5$  is used to bias the gate voltages of the cascode devices  $M_7$  and  $M_9$  of the current mirror. The mirror devices  $M_6$  and  $M_8$  in the output of the current mirror now have the optimum headroom ( $V_{SD,Sat}$ ) to provide for the largest dynamic range possible from a cascode current mirror.

Figure 2.4: Minch cascode current mirror.

An advantage of this circuit is that a replica of the input current is being used to generate the  $V_{SD,Sat}$  voltage reference. This means that as the input current changes over a wide range, the  $V_{SD,Sat}$  voltage reference will adaptively bias itself to accommodate any level of inversion—weak, moderate, or strong. One disadvantage of this circuit is reduced output impedance of the current mirror compared to a normal cascode current mirror because the mirror devices are biased right at the edge of saturation. This will be explained in more detail in Chapter 3.

#### **Voltage Source**

Once a micro-battery has been current charged up to 4.25 V, it has to be transitioned to a voltage charger to complete its charging process. The voltage charger needs to output a constant voltage of 4.25 V and be able to trickle charge and/or store multiple micro-batteries attached to it at one time. The exact values for resistance and capacitance of these micro-batteries have not yet been established, but the resistance is

estimated to be as high as 1 G $\Omega$ . For this reason, extra caution needs to be taken in designing the voltage source to handle a large variation of capacitance and resistance.

An ideal voltage amplifier provides infinite input impedance, zero output impedance, and a steady output voltage regardless of loading conditions. If a voltage sample-voltage sum feedback amplifier is designed properly, the voltage gain is determined by the feedback network, the output resistance ( $R_o$ ) is decreased, the input resistance ( $R_i$ ) is increased, and the voltage gain remains constant for changes in circuit parameters [21]. This type of configuration is ideally suited for voltage amplifiers.

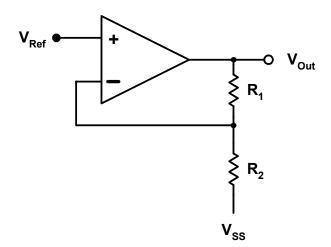

Voltage regulators are widely used components that accept a poorly specified DC input voltage and produce from it a constant, well-specified output voltage that can then be used as a supply voltage for other circuits [22]. The most common voltage regulator is the series regulator shown in Figure 2.5. The output of this voltage regulator is based off the ratio of the resistors and the reference voltage ( $V_{Ref}$ ) given by

$$V_{Out} = V_{Ref} \, \frac{R_1 + R_2}{R_2} \tag{2.5}$$

Low drift and offset are essential for the op-amp so that the output voltage  $(V_{Out})$  is as stable as possible. Very low output impedance will be produced at  $V_{Out}$ , which is a requirement for a good voltage source.

Figure 2.5: Schematic of series voltage regulator.

The voltage sources described above are generally used to drive low resistive loads with a large amount of current output. In contrast, for this application of voltage charging micro-batteries, a high output current availability is not needed from the voltage regulator. The micro-batteries would have been current charged at a rate of 50 nA before they are transitioned to the voltage charger. As long as the voltage charger node is at the same potential as the micro-batteries right before they are connected, each micro-battery should not draw more than 50 nA of current from the voltage charger node. The purpose of the voltage charger is to provide a decaying current supply to each micro-battery until their full capacity of 50 nAh is reached. In the worst-case scenario, the voltage charger would need to be able to provide 50 nA of current to each of the 15 micro-batteries at one time.

#### **Low-Resolution ADC**

To be able to monitor the micro-battery voltage while current charging, a low-resolution ADC is required. The accuracy of a digitized signal is dependent on the number of samples taken and the resolution, or number of quantization levels, of the converter [16]. The resolution required of an ADC is dependent on its application. The finer the range of interest, the more resolution required. The sampling rate of an ADC is defined by the Nyquist criterion, which states that the sampling rate must be at least two times the highest frequency of the analog signal for it to be reconstructed accurately in the digital domain. The analog signal that is of interest in this application is the slow, continuous ramping of the micro-battery voltage as it is being current charged. Current charging times for micro-batteries have been reported to be greater than 30 minutes [5].

Probably the four most popular architectures for ADC conversion are the flash, pipeline, successive approximation (SAR), and sigma-delta ( $\Sigma\Delta$ ) converters. Each of these ADC converters is intended for different applications, but all of them require one or more steps involving comparison of an input signal with a reference [17].

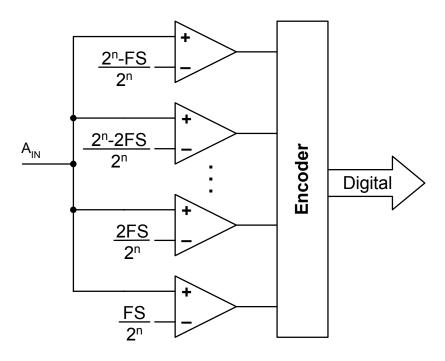

The flash converter is the most straightforward ADC architecture. It requires a set of  $2^n$  comparators to measure an analog signal to n-bit resolution. An example of a flash ADC architecture is shown in Figure 2.6, where FS is the full-scale input and  $A_{IN}$  is the

Figure 2.6: Basic flash ADC architecture.

analog input. For a 3-bit flash ADC, eight comparators would be needed, each of which is biased with a discrete voltage value spaced 1 LSB apart. The analog input signal is compared against the discrete voltage values to simultaneously generate  $2^n$  discrete digital output states. The digital output is in the form of thermometer code and is usually converted to binary form using an encoder. The benefit of the flash architecture is that the conversion only takes one ADC cycle. The disadvantage of this type of architecture is the large number of carefully matched and properly biased comparators needed to generate a high-resolution output.

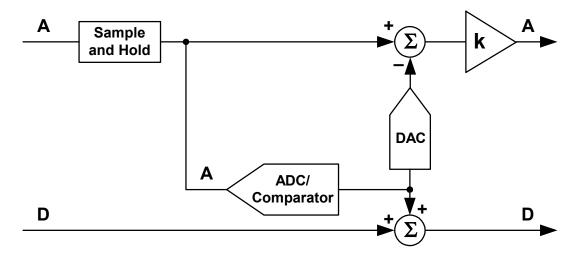

Pipelined or pipelined-flash converters divide the conversion process over several consecutive stages. Each stage normally consists of a sample-and-hold circuit, an m-bit ADC (flash converter), and an m-bit DAC. The m-bit flash converter converts the sampled signal from the sample-and-hold circuit to digital data. This digital output forms one of the significant bits of the digital output. The same digital output is fed back into the DAC whose output is subtracted from the original sampled signal. The residual analog signal is then amplified (k) and sent to the next stage in the pipeline to undergo the

Figure 2.7: Single stage of pipelined converter.

same process. This process continues until the desired resolution is acquired. An example of a single stage of a pipelined ADC is shown in Figure 2.7.

The pipelined converter with p pipeline stages, each with an m-bit flash converter, can produce a resolution of  $n = p \times m$  bits using  $p \times (2^m-1)$  comparators [17]. This corresponds to a higher resolution of pipelined converters compared to flash converters for the same number of comparators. The total conversion time increases though from one to p cycles for pipelined converters. However, since each stage samples and holds its input, p conversions can take place simultaneously so the total throughput of the pipelined converter can be equal to the flash converter, now with added p cycle latency.

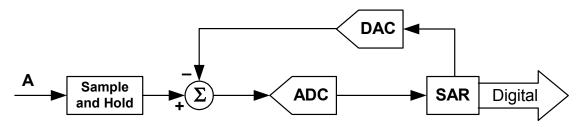

The SAR converter uses a single comparator over many cycles to generate its digital output. The SAR compares the unknown sampled voltage against a known voltage. If the sampled voltage is higher than the known voltage, the SAR will set the significant bit. If the sampled voltage is lower than the known voltage, the SAR does not set the significant bit. This process repeats by using successively smaller weights in binary progression until the desired resolution, n, is reached. An example of a SAR ADC is shown in Figure 2.8. The limitation of the SAR is that it takes n comparison cycles to generate n-bit resolution, compared to p cycles for the pipelined converter and one cycle for the flash converter.

Figure 2.8: Successive-approximation (SAR) ADC architecture.

The  $\Sigma\Delta$  converter is advantageous to use when a high resolution, on the order of 20+ bits, is needed. It is able to have such high resolution because of a process known as noise-shaping in which the low-frequency noise components are pushed to higher frequencies beyond the input signal bandwidth. The limitation of this type of converter is the latency associated with its digital output, which is significantly higher than the other architectures presented, and the digital filtering overhead required to produce a parallel-bit binary output word.

Now that some possible circuit topologies have been investigated, this information can be used in collaboration with our system requirements to design a power management IC for micro-batteries. The three main components of the design are a programmable low-level current charger, a constant voltage charger, and a voltage monitoring circuit.

#### **CHAPTER 3**

## DESIGN OF MICRO-BATTERY POWER MANAGEMENT SYSTEM COMPONENTS

#### **Programmable Current Source**

To be able to charge micro-batteries effectively, a low-level current source with a high output impedance across a wide range of output currents is desired. This output current also needs to have low temperature sensitivity so that it is able to function accurately in a variety of environments. For these reasons, the current source chosen for this project encompasses two different parts; a temperature stable, low-level current generator (400 nA) and a 4-bit current output DAC with a novel output stage, dubbed the " $V_{GS}$ -multiplier," which ensures a high output impedance over a large range of output current.

#### **Current Generator**

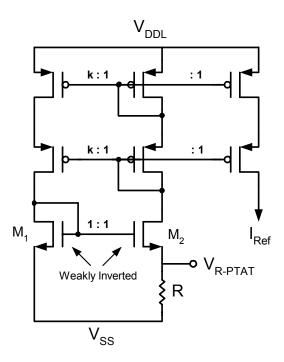

Different current reference circuits were discussed in the previous chapter, but one design stood out due to its low sensitivity to temperature variations when used for this application. Shown in Figure 3.1 is a beta-multiplier current reference with the nMOS devices  $M_1$  and  $M_2$  operating in weak inversion. This architecture of the beta-multiplier with weakly inverted devices functions as a PTAT voltage reference [9].

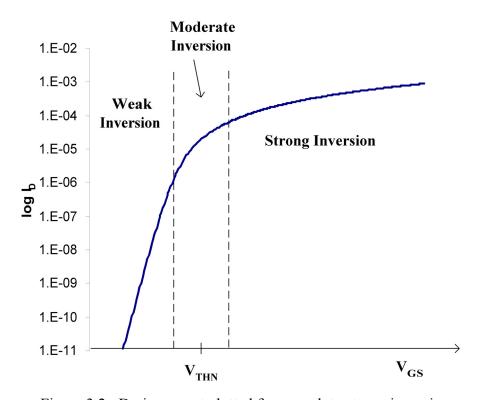

MOSFETs operating with a  $V_{GS}$  less than  $V_{T0}$  are said to be operating in weak inversion or sub-threshold mode as shown graphically in Figure 3.2. In this region of operation, diffusion current dominates and the drain current becomes an exponential function of the gate voltage. It is important to size  $M_1$  and  $M_2$  of Figure 3.1 such that for a given current level, the devices are guaranteed to remain in weak inversion in order for the PTAT reference to properly function.

To better illustrate analytically where the region of weak inversion exists, an inversion coefficient was first introduced by Vittoz [23] and then later expanded upon by Binkley *et al.* [24]. The simplified definition of inversion coefficient (*IC*) is

Figure 3.1: Beta-multiplier current reference topology.

Figure 3.2: Drain current plotted from weak to strong inversion.

$$IC = \frac{I_D}{I_o\left(\frac{W}{L}\right)}$$

(3.1)

where  $I_D$  is the drain current, W and L are the effective channel width and length respectively, and  $I_o$  is a process dependent current known as the technology current. The technology current is defined as the drain current for a device with an aspect ratio of unity, W/L = 1, which is biased at the center of moderate inversion where IC = 1. According to Vittoz's definition [23], a device is weakly inverted if its IC is less than 0.1, moderately inverted for an IC between 0.1 and 10, and strongly inverted for an IC greater than 10. For this design, an aspect ratio of 120 was used to ensure that both devices would remain in weak inversion for drain currents less than 1  $\mu$ A.

The equation for an n-channel MOSFET operating in weak inversion is given by [25]

$$I_{D,Weak} = 2n\mu_n C_{ox}' \frac{W}{L} \left(\frac{kT}{q}\right)^2 e^{\frac{q(V_{GS} - V_{THN})}{nkT}}$$

(3.2)

where  $\mu_n$  is the electron mobility,  $C_{ox}$  is the gate oxide capacitance per unit area, k is Boltzman's constant, T is the temperature in Kelvin, q is the electron charge,  $V_{THN}$  is the nMOS threshold voltage, and n is the process dependent sub-threshold slope factor. Summing the voltages around the bottom half of Figure 3.1 using Kirchoff's Voltage Law (KVL) yields

$$V_{GS1} = V_{GS2} + V_{R-PTAT} (3.3)$$

where

$$V_{R-PTAT} = I_{D2} \times R = I_{Ref} \times R$$

(3.4)

Solving for  $V_{GS}$  from (3.2) gives

$$V_{GS} = nU_T \ln \left( \frac{I_{D,Weak}}{I_{DO}} \right) + V_{THN}$$

(3.5)

where  $U_T$  is equal to the thermal voltage (kT/q) and  $I_{DO}=2n\mu_n C_{ox}^{'}W/L$ . Substituting (3.5) into (3.3) and solving for the PTAT reference voltage yields

$$V_{R-PTAT} = nU_T \ln \left( \frac{I_{D1}}{I_{D2}} \right) = nU_T \ln(k) = I_{Ref} \times R$$

(3.6)

The cascode pMOS current mirror in Figure 3.1 provides the k ratio of the currents so that  $M_1$  and  $M_2$  devices have different drain currents allowing for a systematic  $V_{GS}$  offset. By sizing these two devices the same, it is possible to symmetrically layout the MOSFETs allowing for better matching, which will cause less error associated with random  $V_{GS}$  mismatch of the nMOS pair. For this design, a current ratio of k = 2 was implemented in the pMOS current mirror in order to limit the size of the resistor needed to generate a low-level reference current ( $I_{Ref}$ ) of 400 nA.

P-well resistors with high sheet resistivity ( $\rho$ ) exist in the SOI process selected to fabricate this power management system. This allows a low-level current to be produced without the required resistor consuming a large chip area. In addition, the temperature coefficient associated with the p-well resistor tracks that of the generated PTAT reference voltage to provide temperature stable operation of the current reference. For a different technology without a high resistivity p-well option, the PTAT reference voltage generated by the weakly inverted MOSFETs can be reduced by connecting the body terminals of  $M_1$  and  $M_2$  together. The new equation for the PTAT reference voltage would then be given by [9]

$$V_{R-PTAT} = U_T \ln(k) = I_{Ref} \times R$$

(3.7)

The only difference between (3.6) and (3.7) is the absence of the sub-threshold slope factor in (3.7). This means that either an equivalent low-level reference current can be generated using a lower resistivity resistor option or a dimensionally smaller resistor can be implemented to generate the same  $I_{Ref.}$

Mobility of bulk silicon in a semiconductor is determined by various scattering mechanisms. The two most important mechanisms are lattice scattering and impurity scattering [26]. Lattice scattering results from thermal vibrations of the lattice atoms at

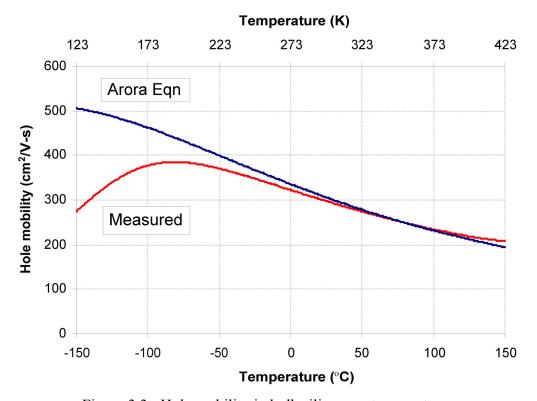

any temperature above absolute zero. At higher temperatures, lattice scattering dominates and the mobility decreases with increasing temperature. The hole mobility in p-type, bulk silicon is given by [27]

$$\mu_p = 54.3T_n^{-0.57} + \frac{1.36 \times 10^8 T^{-2.23}}{1 + \frac{N}{2.35 \times 10^{17} T_n^{2.4}} 0.88 T_n^{-0.146}}$$

(3.8)

where  $T_n$  is T/300 K and N is the impurity concentration. This equation was obtained by Arora *et al.* through experimental data over the temperature range 250 to 500K [27]. Due to the limitation of the temperature range in deriving (3.8), measured results of p-well resistors for this SOI process were obtained and compared against the derived equation as seen in Figure 3.3. Notice that the two curves track well within the 250 to 500K temperature range and then start to deviate at lower temperatures. This broad temperature range from -150 to  $150^{\circ}$ C was chosen for measurement purposes because of

Figure 3.3: Hole mobility in bulk silicon vs. temperature.

the possible extreme environments in which this system might operate.

Resistivity,  $\rho$ , of bulk silicon is dependent on its mobility and concentration of majority carriers, p [26]:

$$\rho = \frac{1}{q\mu_p p} \tag{3.9}$$

The resistance per square  $(R_{sq})$  for an IC resistor can be found by dividing its resistivity by the thickness of the silicon island. Once the  $R_{sq}$  is known, then an integrated circuit resistor of any value can be made by varying its aspect ratio.

$$R = R_{sq} \left( \frac{L}{W} \right) \tag{3.10}$$

Figure 3.4 shows a comparison plot of the resistance per square calculated using the mobility equation in (3.8), SPICE simulations with a process specific, first-order temperature coefficient term, and measured results across temperature. Also included in this figure is a plot of the thermal voltage across temperature. Recall from (3.6) that the only temperature dependent term in the PTAT reference is the thermal voltage,  $U_T$ . Notice how well the thermal voltage tracks the measured  $R_{sq}$  curve from 0 to 100°C, which in turn will provide the current reference generator with temperature stable operation over this temperature range. Simulation results of the current reference output show a 7% change in  $I_{Ref}$  from 0 to 100°C.

#### Current Output DAC

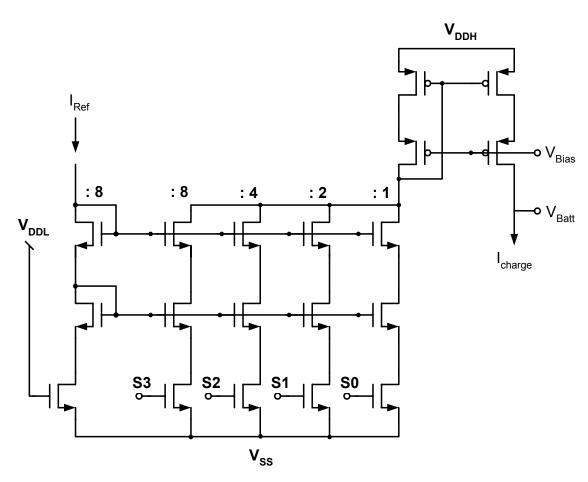

In order for the generated 400-nA reference current to be scaled to different levels to charge one to *N* micro-batteries in parallel, it is fed into a current-mode DAC. The 4-bit DAC consists of a series of binary-weighted current mirrors driven by MOSFET switches (*S*3–*S*0) and is shown in Figure 3.5. Using four bits, it is possible to produce 16 different continuous current output levels ranging from 0 to 750 nA in 50-nA steps. When charging micro-batteries at a normal rate of 1 C (50 nA), up to 15 micro-batteries can be charged simultaneously given a full-scale input to the DAC.

Figure 3.4: Comparison of  $R_{sq}$  calculated using Arora's mobility equation, SPICE simulations, and measured results, all compared to thermal voltage  $U_T$ .

Figure 3.5: Current-mode DAC topology.

Another key component to this design is the ability to interchange between continuous current charging and pulse-width modulated (PWM) current charging. By applying a PWM voltage input to the switches of the DAC, it is possible to charge microbatteries at an average rate lower than that made possible by the least significant bit (LSB) of the DAC (50 nA). For instance, a 10% duty cycle input can be applied to *S*0 of the DAC producing an overall effect of charging at 5 nA or a 0.1 C rate. Experimental results have shown that pulse-charging increases the cycle life of Li-Ion batteries due to improved replating of Lithium [28].

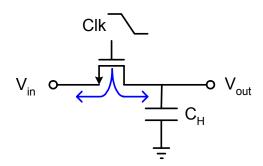

Most often charge injection issues do not arise unless dealing with a sample and hold topology where switched capacitors are utilized. For the sample and hold case, shown in Figure 3.6, the inversion layer charge is dumped into the holding capacitor when the switch is opened. The error associated with this type of setup is a positive voltage spike at the output as the hold capacitor ( $C_H$ ) is injected with a small surge of current. The problem then of course is how to minimize the inversion layer charge, which will in turn minimize errors associated with charge injection. Usually, the effect of charge injection when a switch is closed is not taken into consideration because the signal source is driving  $C_H$  through the MOS switch.

Wegmann *et al.* [29] show that a rapid variation of the gate voltage causes a variation of the MOSFET surface potential because the amount of mobile charges cannot change instantaneously. The surface potential induces an immediate variation of the depletion width, which compensates the excessive charge. Equilibrium corresponding to the new gate voltage is reached by the subsequent charge flow to drain and source. This

Figure 3.6: Sample and hold circuit illustrating charge injection.

is "charge injection." This undesirable effect had to be examined and minimized for this system since a low-level output current is desired and severe current output transients could damage micro-batteries.

The equation for charge injection is given by [30]

$$Q_{ch} = W \times L \times C_{ox} (V_{GS} - V_{TH})$$

(3.11)

where  $Q_{ch}$  is the total charge in the inversion layer. From this equation, it is clear that the physical size of the switch and the  $V_{GS}$  voltage are both factors that the designer can manipulate to minimize the charge in the inversion layer. What is not evident in this equation, however, is how the charge is shared between the source and drain of the device. In most cases, it is assumed that half the excess charge is shared equally between the source and drain. In reality, the fraction of charge that exits through the source and drain terminals is a relatively complex function of various parameters such as the impedance seen at each terminal to ground and the transition time of the clock [29].

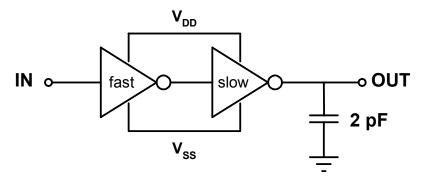

To help minimize the total charge in the inversion layer of the input switches in the DAC, the lower 3.3-V supply voltage,  $V_{DDL}$ , was used as the switching voltage instead of the higher 5-V supply voltage,  $V_{DDH}$ . In addition, all the switches were sized identically instead of sizing them with their respective binary-weighted value, like the cascode devices above them, thus reducing their effective area. Also, charge injection decreases when a slow transient is applied to the input of a switch compared to a fast transient [29]. For this reason, an input slew-rate control circuit consisting of an inverter buffer and a capacitor were added before each switch input as shown in Figure 3.7.

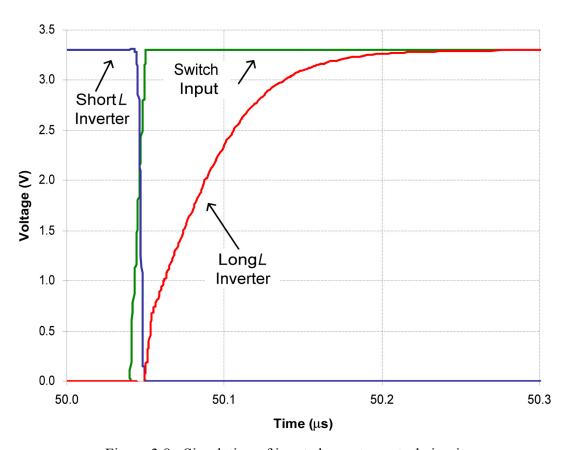

The inverter buffer consists of a short L inverter (fast) followed by a longer L inverter (slow). A capacitor is added to further slow the input transient response to the DAC. The purpose of the slew-rate control buffers is to ensure symmetrical inputs to each switch and slow the rise and fall time of the digital inputs, so the circuit has more time to dissipate each switch's inversion layer charge. A simulated response of the slew-rate control circuit is shown in Figure 3.8. As the switch input transitions high, the first inverter transitions low immediately followed by the second inverter which has to charge the capacitor at its output, slowing its rise time.

Figure 3.7: Input slew-rate control circuit applied to each of the DAC inputs.

Figure 3.8: Simulation of input slew-rate control circuit.

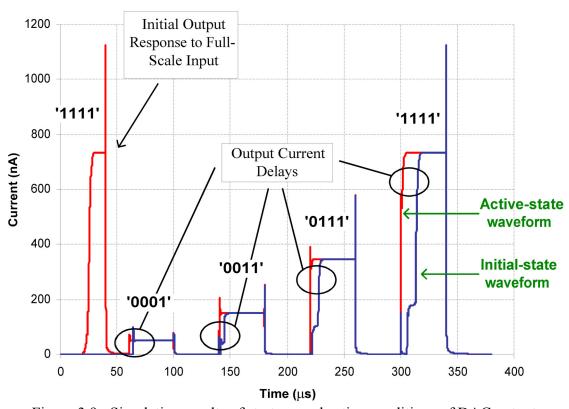

Two different situations arise in simulating the DAC design of Figure 3.5 when the switching voltages are applied to the inputs (S3-S0). When the DAC is in a steady-state or start-up condition where no initial voltage has been applied to a given switch, there is a delay in the output current response. This delay occurs on the rising edges of the output current pulses as seen in Figure 3.9 and is due to an initial charging of all capacitances associated with a given switch's cascode devices and any parasitics within the output current path.

The other condition seen in Figure 3.9 involves the DAC being in an active state where all the capacitances and cascode devices have been fully charged prior to the next switch cycle. The difference between the two states is the delay associated with capacitance charging that is no longer present in the active state. This situation was simulated by including an initial full-scale input pulse to the DAC ('1111') before individually pulsing the inputs to the switches.

Figure 3.9: Simulation results of start-up and active conditions of DAC output.

Figure 3.9 also shows how much charge injection affects the output current when a switch is open or closed. When the circuit is operating in the initial-state condition, an input switch closing does not affect the output current because its charge injection is just transferred to the uncharged capacitances that are inherently present in the system. For the active-state condition, the charge injection associated with a switch closing does affect the output current because the circuit's stray capacitances are already pre-charged by the initial pulse input. For both active and initial conditions, a switch opening contributes to an overshoot of output current due to charge injection. From Figure 3.9 it looks like the charge injection from a switch opening is proportional to the output current, but this is not the case. The large current spike occurring at the end of the simulation comes from the combination of all four input switches opening simultaneously, so all the switches' charge injection is being summed at the output (400-nA overshoot).

Despite the lengths taken to reduce charge injection into the system by including the input slew-rate control circuit, minimizing the sizing of the input switches, and using the lower supply voltage as the switching supply, the DAC still seems to produce considerable charge injection. However, without the input slew-rate control circuit applied to the input switches of the DAC, the output current overshoot is 1.85 µA. This equates to almost a factor of five reduction in the overshoot of output current with the addition of the input slew-rate control circuitry. The current overshoots in the output current would also not be so obvious if larger current levels were being output since channel charge is not dependent on the current level. If the DAC were providing a 10-µA output current, a 400-nA overshoot would only equate to a 4% change of the output current. The overshoot in the initial output response to a full-scale input and the final pulse in Figure 3.9 can be further reduced by opening the input switches in a controlled manner. Offsetting the switch openings in time would decrease the amount of overshoot of the output current that a micro-battery would have to sink at one time.

The output stage of the DAC consists of a LVCCM biased by  $V_{Bias}$  shown previously in Figure 3.5. A cascode current mirror provides for higher output impedance  $(R_o)$  of the current charger compared to a single output device. High output impedance is

important for the system because we want to mimic the operation of an ideal current source, which theoretically has infinite output impedance. The LVCCM scheme was used because a fully charged micro-battery has a voltage capacity of 4.25 V and the current source needs to provide adequate headroom to charge to this level. A regular cascode current mirror would only provide a charging capability up to  $V_{DDH} - |V_{THP}| - 2V_{SD,Sat}$ . For a standard 0.35- $\mu$ m SOI process, this would equate to approximately 1.3 V below the  $V_{DDH}$  supply voltage (3.7 V). For the case of the LVCCM used in this design, the micro-batteries can charge to approximately  $2V_{SD,Sat}$  (500 mV) below the  $V_{DDH}$  supply voltage or 4.5 V.

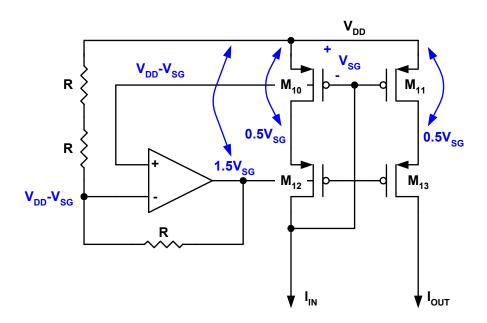

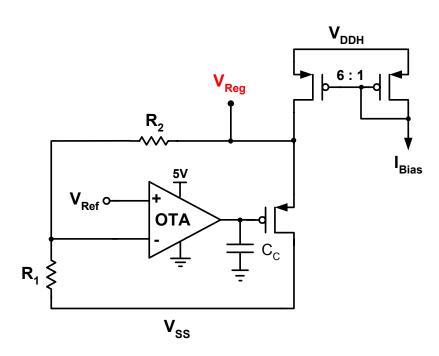

The bias voltage for the LVCCM is generated using the " $V_{GS}$ -multiplier" [31] shown biasing the output stage of the DAC in Figure 3.10. The op-amp senses the gate voltage of  $M_{10}$  and  $M_{11}$  with respect to  $V_{DD}$  ( $V_{SG}$ ) with its non-inverting input. Assuming an ideal op-amp with no error voltage between the two input terminals of the op-amp, the inverting input is at the same voltage as the non-inverting input,  $V_{SG}$  down from  $V_{DD}$ . This is an accurate assumption if the op-amp has a large open-loop gain and negligible offset. The resistor divider between the  $V_{DD}$  supply voltage and the inverting input sets

Figure 3.10:  $V_{GS}$ -multiplier biasing the LVCCM of the DAC output stage.

up a current that flows through the resistor between the inverting input and the output of the op-amp. If all the resistors are equally sized, then the output of the op-amp and the gates of  $M_{12}$  and  $M_{13}$  are forced to be  $1.5V_{SG}$  down from  $V_{DD}$ . This leaves the mirror devices  $M_{10}$  and  $M_{11}$  with  $0.5V_{SG}$ , which is greater than  $V_{SD,Sat}$ , for their voltage headroom  $(V_{SD})$  in the LVCCM.

The novelty of this circuit comes in its ability to provide adequate headroom for  $M_{10}$ – $M_{13}$  to remain in saturation from weak to strong inversion, over a wide range of input currents, and over a broad temperature range while still providing high output impedance. Some other LVCCM bias circuits have been developed [23], [20], [32], but none encompass all the benefits of the  $V_{GS}$ -multiplier. Minch describes a method that biases the current source devices of a LVCCM right at the edge of saturation where  $V_{SD}$  =  $V_{SD,Sat}$  [20]. This, however, does not deliver the highest output impedance possible from the current mirror.

The output resistance of the Minch current mirror shown in Figure 2.4 is

$$R_o = r_{o7} (1 + g_{m7} r_{o6}) + r_{o6}$$

(3.12)

where  $r_{o6}$  is the small-signal output resistance of the device biased at the edge of saturation. The V<sub>GS</sub>-multiplier does an opposite trade-off by biasing the current source device a little farther into the saturation region thus reducing the current mirror's overall output voltage swing, but provides higher output impedance. The output resistance of the V<sub>GS</sub>-multiplier shown in Figure 3.10 has the same form as (3.12)

$$R_o = r_{o13} (1 + g_{m13} r_{o11}) + r_{o11}$$

(3.13)

but  $r_{o11}$  is greater than  $r_{o6}$  of the Minch circuit since  $M_{11}$  is biased further into saturation than  $M_6$ .

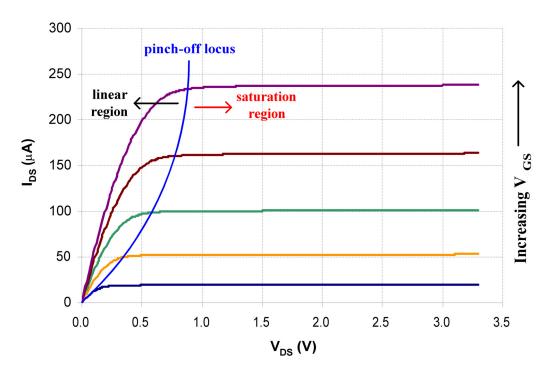

To help illustrate graphically where  $V_{DS,Sat}$  is located and how it pertains to output impedance, Figure 3.11 shows a typical  $I_{DS}$  vs.  $V_{DS}$  curve for an nMOS device. The area to the left of the pinch-off locus is known as the linear or triode region of operation in which a resistive channel directly connects the source and drain of the MOSFET. Once the channel has reached the pinch-off point for a given  $V_{GS}$ , the drain current becomes

Figure 3.11:  $I_{DS}$  vs.  $V_{DS}$  curve showing regions of operation of an *n*MOS transistor.

constant if short-channel effects are neglected [33]. This region of constant current is known as the saturation region of operation. The intersection of the pinch-off locus and a given  $V_{GS}$  curve defines a MOSFET's  $V_{DS,Sat}$  voltage [33]. A transistor's output impedance can by found by finding the slope of the curve at a given point. As the slope flattens out in the saturation region, the output impedance reaches its maximum; hence the reason for higher output impedance in the  $V_{GS}$ -multiplier over the Minch circuit.

The temperature stable beta-multiplier current reference, the DAC with input slew-rate control circuitry, and the  $V_{GS}$ -multiplier comprise the current charger in this design. Figure 3.12 shows a DC simulation of the current charger output at room temperature as the micro-battery voltage ( $V_{Batt}$ ) is swept from 0 to 5 V. The three curves in the figure represent the output current generated by a 1 LSB input, a mid-scale input, and a full-scale input into the DAC. The current charging profile associated with these inputs remains flat over the entire battery voltage range, 0–4.25 V, indicative of the current charger's high output impedance. Above 4.5 V, the cascode devices start to fall

Figure 3.12: Simulated DC sweep of current charger output at room temperature for selected input codes.

out of saturation as the battery voltage nears the upper supply voltage,  $V_{DDH}$ , turning off the output stage of the DAC.

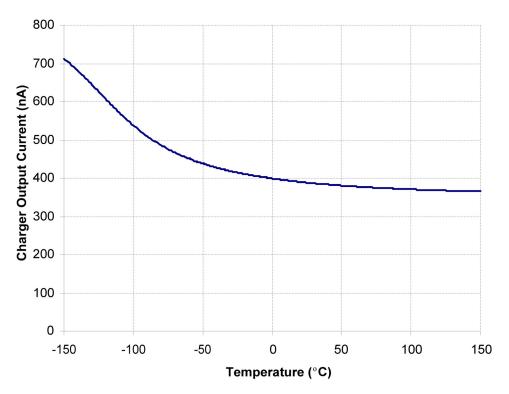

The charger output current as a function of temperature is dependent mainly on the beta-multiplier reference current. Figure 3.13 shows a simulation of how the charger output for a mid-scale input varies with temperature. Notice that at lower temperatures, the charger output current starts to increase because the reference current increases. This might not be an accurate representation of how the actual current reference will operate since the resistor parameters used in simulations were not modeled for low temperature situations.

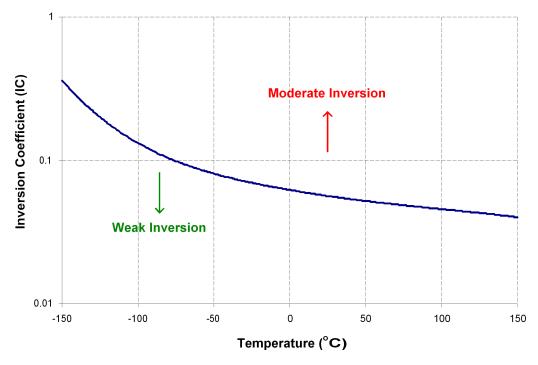

Recall from (3.1) that the IC is temperature dependent on  $I_o$ , which is described by

$$I_o = 2n\mu_o C_{ox}^{'} U_T^2$$

(3.14)

Figure 3.13: Simulation of DAC mid-scale output plotted against temperature.

Based off experimental resistance measurements, the hole mobility was determined (Figure 3.3) and used to find the technology current for this process. Calculations show that  $I_o$  is proportional to temperature, which corresponds to inverse temperature proportionality to IC, assuming a constant  $I_D$ . Therefore, as temperature decreases, devices are moved from weak inversion slightly into moderate inversion (Figure 3.14), which will cause a shift in the reference current. Note that as  $M_1$  and  $M_2$  of the current generator (Figure 3.1) move well into moderate inversion for temperatures below  $-100^{\circ}$ C, the generated reference voltage is no longer a PTAT voltage, thus temperature compensation against the p-well resistor is no longer achieved. For an extreme temperature case of  $-100^{\circ}$ C, the devices  $M_1$  and  $M_2$  are at the transition point between weak and moderate inversion (IC = 0.1) so the reference voltage can still be assumed PTAT.

The largest contributor to the shift in output current at low temperatures in Figure 3.13 is the temperature dependence of the p-well resistor used in the beta-multiplier

Figure 3.14: Calculated IC of  $M_1$  and  $M_2$  devices of beta-multiplier current reference.