Masters Theses Graduate School

8-2016

# Review and Characterization of Gallium Nitride Power Devices

Edward Andrew Jones *University of Tennessee, Knoxville*, ejones55@vols.utk.edu

#### Recommended Citation

Jones, Edward Andrew, "Review and Characterization of Gallium Nitride Power Devices." Master's Thesis, University of Tennessee, 2016.

https://trace.tennessee.edu/utk\_gradthes/4048

This Thesis is brought to you for free and open access by the Graduate School at Trace: Tennessee Research and Creative Exchange. It has been accepted for inclusion in Masters Theses by an authorized administrator of Trace: Tennessee Research and Creative Exchange. For more information, please contact trace@utk.edu.

#### To the Graduate Council:

I am submitting herewith a thesis written by Edward Andrew Jones entitled "Review and Characterization of Gallium Nitride Power Devices." I have examined the final electronic copy of this thesis for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Master of Science, with a major in Electrical Engineering.

Fred Wang, Major Professor

We have read this thesis and recommend its acceptance:

Leon Tolbert, Daniel Costinett

Accepted for the Council: <u>Dixie L. Thompson</u>

Vice Provost and Dean of the Graduate School

(Original signatures are on file with official student records.)

# **Review and Characterization of Gallium Nitride Power Devices**

A Thesis Presented for the

Master of Science

Degree

The University of Tennessee, Knoxville

Edward Andrew Jones August 2016 Copyright © 2016 by Edward A. Jones All rights reserved.

#### Acknowledgments

I would like to acknowledge the support and collaboration of my many peers and mentors at the University of Tennessee, Knoxville. Dr. Fred Wang provided many years of guidance and education as my advisor, and continues to do so in the pursuit of my Ph.D.. Drs. Leon Tolbert, Daniel Costinett, Benjamin Blalock, Syed K. Islam, Burak Ozpineci, and Lee Riedinger have also been valuable faculty advisors during my graduate career. The feedback and advice offered during group meetings and individual discussions have made this work possible.

The collaboration with other students at the University of Tennessee has been equally important. I have been guided and challenged by these peers as we all work together to learn and earn our degrees. I would especially like to thank Yalong Li, Dr. Zheyu Zhang, Dr. Ben Guo, Dr. Weimin Zhang, Cameron Riley, Bo Liu, Ren Ren, Rémi Perrin, Dr. Zhiqiang Wang, Chongwen Zhao, Dr. Yutian Cui, Dr. Zhuxian Xu, Dr. Jing Xue, and Fei Yang for working closely with me on my research over the past four years.

Outside of UTK, there are many others I would like to thank for their part in my graduate career so far. These include Dr. Eugene Solodovnik and Dr. Kamiar Karimi from The Boeing Company; Julian Styles, Di Chen, and Greg Klowak from GaN Systems; Eric Persson, Dr. Wenduo Liu, and Dr. Vickie Zhou from Infineon; Christina Dimarino, Xiucheng Huang, Bin Lu, and Zhengyang Liu from CPES at Virginia Tech; He Li at Ohio State University; Dr. Raghav Khanna at University of Toledo; Dr. Andrew Lemmon at University of Alabama; and Dr. Adam Barkley at Wolfspeed.

This work made use of facilities supported in part by the Engineering Research Center Program of the National Science Foundation and Department of Energy under NSF Award Number EEC-1041877 and the CURENT Industry Partnership Program. Financial support was also provided by the Bredesen Center for Interdisciplinary Research and Graduate Education.

#### Abstract

Gallium Nitride (GaN) power devices are an emerging technology that have only recently become available commercially. This new technology enables the design of converters at higher frequencies and efficiencies than those achievable with conventional Si devices. This thesis reviews the characteristics and commercial status of both vertical and lateral GaN power devices from the user perspective, providing the background necessary to understand the significance of these recent developments. Additionally, the challenges encountered in GaN-based converter design are considered, such as the consequences of faster switching on gate driver design and board layout. Other issues include the unique reverse conduction behavior, dynamic on-resistance, breakdown mechanisms, thermal design, device availability, and reliability qualification.

Static and dynamic characterization was then performed across the full current, voltage, and temperature range of this device to enable effective GaN-based converter design. Static testing was performed with a curve tracer and precision impedance analyzer. A double pulse test setup was constructed and used to measure switching loss and time at the fastest achievable switching speed, and the subsequent overvoltages due to the fast switching were characterized. The results were also analyzed to characterize the effects of cross-talk in the active and synchronous devices of a phase-leg topology with enhancement-mode GaN HFETs. Based on these results and analysis, an accurate loss model was developed for the device under test.

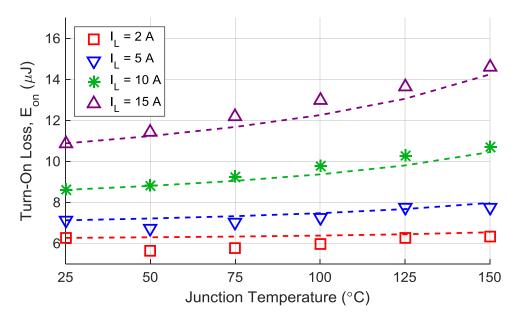

Based on analysis of these characterization results, a simplified model was developed to describe the overall switching behavior and some unique features of the device. The consequences of the Miller effect during the turn-on transient were studied to show that no Miller plateau occurs, but rather a decreased gate voltage slope, followed by a sharp drop. The significance of this distinction is derived and explained. GaN performance at elevated temperature was also studied, because turn-on time increases significantly with temperature, and turn-on losses increase as a

result. Based on this relationship, a temperature-dependent turn-on model and a linear scaling factor was proposed for estimating turn-on loss in e-mode GaN HFETs.

## **Table of Contents**

| Chapter 1 | Introdu | action                                     | 1  |

|-----------|---------|--------------------------------------------|----|

| 1.        | 1 Wid   | le Bandgap Semiconductors                  | 1  |

| 1.        | 2 Lite: | rature Review                              | 5  |

|           | 1.2.1   | Reviewing a Power Device                   | 5  |

|           | 1.2.2   | Device Characterization and Modeling       | 7  |

| 1.        | 3 Mot   | ivations and Objectives                    | 8  |

| 1.        | 4 The   | sis Organization                           | 9  |

| Chapter 2 | Review  | v of GaN Power Devices                     | 10 |

| 2.        | 1 Intro | oduction                                   | 10 |

| 2.        | 2 Vert  | tical GaN Devices                          |    |

|           | 2.2.1   | GaN-on-GaN Power Devices                   | 10 |

|           | 2.2.2   | GaN-on-Si Vertical Power Devices           | 12 |

|           | 2.2.3   | GaN Wafer Fabrication                      |    |

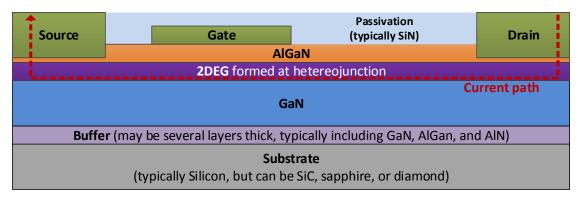

| 2.        | 3 The   | Lateral GaN HFET                           | 15 |

|           | 2.3.1   | Basic Device Structure                     | 16 |

|           | 2.3.2   | Cascode HFETs                              | 17 |

|           | 2.3.3   | Enhancement-Mode HFETs                     | 19 |

|           | 2.3.4   | Reverse Conduction Behavior                | 21 |

|           | 2.3.5   | Dynamic R <sub>ds-on</sub>                 | 24 |

|           | 2.3.6   | Breakdown Mechanisms                       | 26 |

| 2.        | 4 Reli  | ability Qualification                      | 27 |

| 2.        |         | rating Temperature and Thermal Design      |    |

| 2.        | 6 Swi   | tching Behavior                            | 29 |

| 2.        | 7 Dev   | ice Packaging and PCB Layout               | 30 |

| 2.        | 8 Con   | nmercial Device Availability               | 31 |

| 2.        | 9 Gate  | e Driver Considerations                    | 31 |

|           | 2.9.1   | Gate Voltage and Current                   | 31 |

|           | 2.9.2   | Common Mode Transient Immunity             | 33 |

|           | 2.9.3   | Cross-Talk                                 | 33 |

|           |         | ummary                                     |    |

| Chapter 3 |         | terization of an Enhancement-Mode GaN HFET |    |

| 3.        | 1 Intro | oduction                                   | 38 |

| 3.        | 2 Stati | ic Characterization                        | 39 |

|           | 3.2.1   | Curve Tracer Test Setup                    | 39 |

|           | 3.2.2   | On-Resistance                              |    |

|           | 3.2.3   | Self-Commutated Reverse Conduction (SCRC)  | 43 |

|           | 3.2.4   | Transfer characteristic                    | 44 |

|           | 3.2.5   | Steady-State Gate Current                  | 46 |

|           | 3.2.6   | Junction Capacitances                      | 47 |

| 3.        | 3 Dyn   | amic Characterization                      |    |

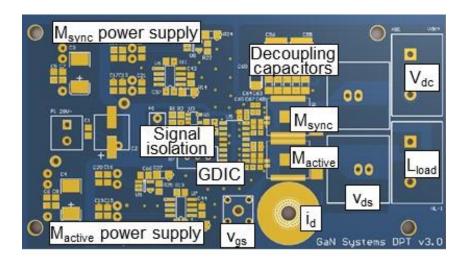

|           | 3.3.1   | Double Pulse Test Setup                    |    |

|           | 3.3.2   | Measurement System Setup                   | 51 |

|         |     | 3.3.3  | V-I Alignment and Deskew Technique                              | 53 |

|---------|-----|--------|-----------------------------------------------------------------|----|

|         |     | 3.3.4  | DPT Board Design                                                | 54 |

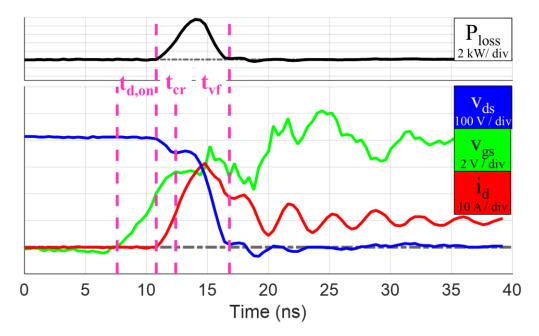

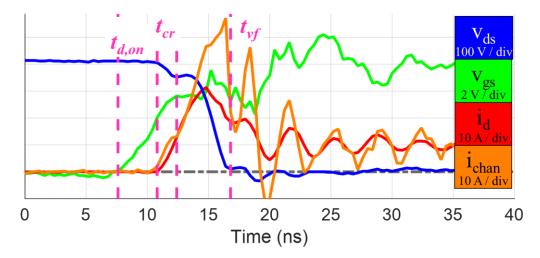

|         |     | 3.3.5  | Turn-On Transient Analysis                                      | 55 |

|         |     | 3.3.6  | Turn-Off Transient Analysis                                     | 59 |

|         |     | 3.3.7  | Switching Losses                                                | 62 |

|         |     | 3.3.8  | Peak dv/dt                                                      | 65 |

|         |     | 3.3.9  | Observed Device Failures                                        | 66 |

|         |     | 3.3.10 | Effects of Varying Gate Driver Voltage and Resistance           | 67 |

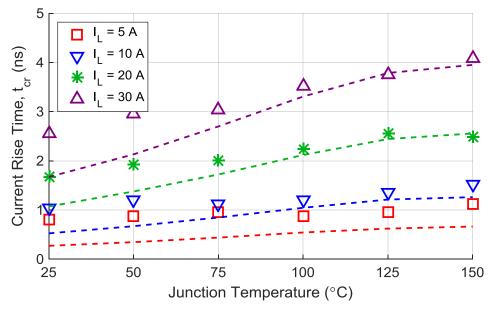

|         |     |        | Effects of Elevated Temperature                                 |    |

|         | 3.4 | Ana    | lysis of Cross-Talk                                             | 69 |

|         |     | 3.4.1  | Test Setup                                                      | 69 |

|         |     | 3.4.2  | Results for Active Device                                       |    |

|         |     | 3.4.3  | Results for Synchronous Device                                  |    |

|         | 3.5 | Sum    | mary                                                            |    |

| Chapter | 4   |        | Development                                                     |    |

| 1       | 4.1 |        | oduction                                                        |    |

|         | 4.2 | Subo   | circuit Model                                                   | 82 |

|         | 4.3 | Turr   | n-On Transient Behavior                                         | 83 |

|         | 4.4 | Turr   | n-Off Transient Behavior                                        | 90 |

|         | 4.5 |        | lysis of the Miller Effect During the GaN HFET Turn-On Transien |    |

|         |     |        | Introduction                                                    |    |

|         |     |        | Derivation of Turn-On Gate Voltage with Miller Effect           |    |

|         |     | 4.5.3  | Verification With Experimental Results and Simulation           |    |

|         | 4.6 | Ana    | lysis of the Temperature Dependency of the Turn-On Transient    |    |

|         |     | 4.6.1  | Introduction                                                    |    |

|         |     | 4.6.2  | Assumptions and Simplifications for the Model                   |    |

|         |     | 4.6.3  | Relationship Between Transconductance and Turn-On Loss          |    |

|         |     | 4.6.4  | Effect of Temperature on Transconductance                       |    |

|         |     | 4.6.5  | Consideration of Special Case at Elevated Temperature           |    |

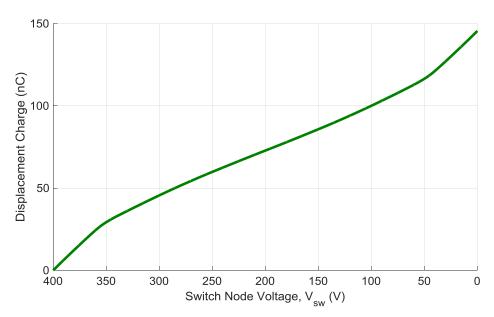

|         |     | 4.6.6  | Consideration of Nonlinear Coss                                 |    |

|         |     | 4.6.7  | Linear Approximation                                            |    |

|         |     | 4.6.8  | Experimental Verification                                       |    |

|         | 4.7 | Sum    | mary                                                            |    |

| Chapter |     |        | sion                                                            |    |

| 1       | 5.1 |        | tributions                                                      |    |

|         | 5.2 |        | re Work                                                         |    |

|         | 5.3 |        | ications                                                        |    |

| Referen |     |        |                                                                 |    |

|         |     |        |                                                                 |    |

## **List of Tables**

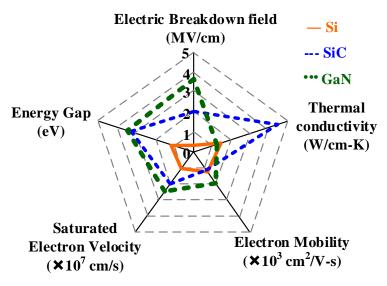

| Table 1.1. Properties of wide bandgap semiconductors [3],[4]                     | 2  |

|----------------------------------------------------------------------------------|----|

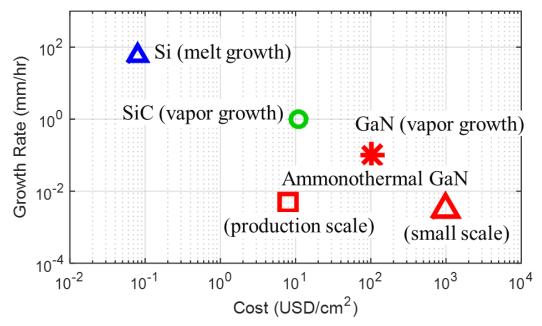

| Table 2.1. Comparison of GaN Wafer Fabrication Methods [59]                      |    |

| Table 2.2. Commercial Cascode Devices                                            | 18 |

| Table 2.3. Commercial Enhancement-Mode Devices                                   | 19 |

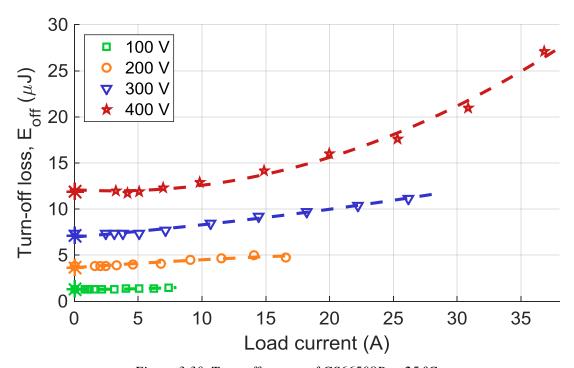

| Table 3.1. Eon Second Order Approximation Coefficients for GS66508P              | 64 |

| Table 3.2. E <sub>off</sub> Second Order Approximation Coefficients for GS66508P | 64 |

# **List of Figures**

| Figure 1.1 Comparison of Si, SiC, and GaN for power semiconductor applications [3],                  |      |

|------------------------------------------------------------------------------------------------------|------|

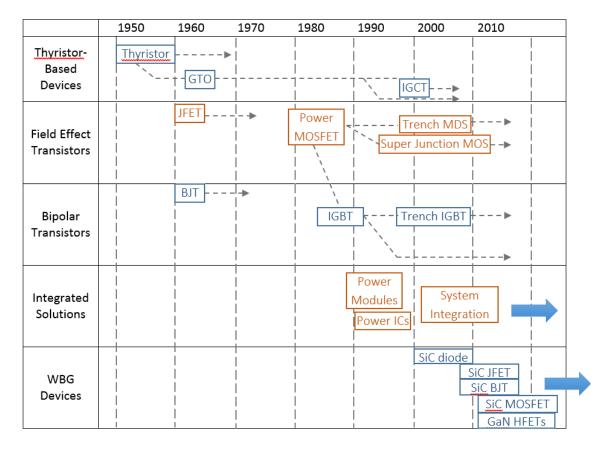

| Figure 1.2. Timeline of the development of power semiconductor devices [7]                           |      |

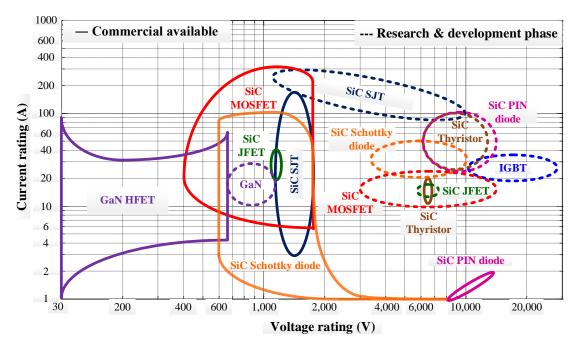

| Figure 1.3. Ratings of selected WBG power devices [9]                                                |      |

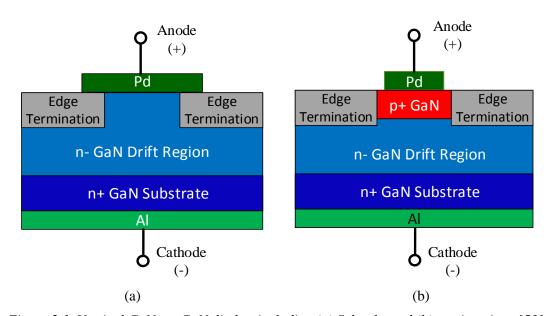

| Figure 2.1. Vertical GaN-on-GaN diodes, including (a) Schottky and (b) p-n junctions                 |      |

| [53]                                                                                                 |      |

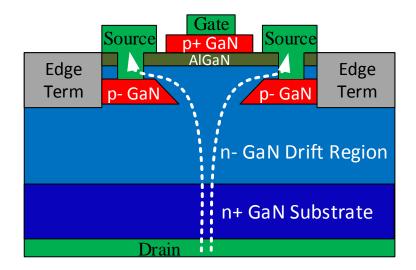

| Figure 2.2. Vertical GaN-on-GaN normally-off JFET [56]                                               |      |

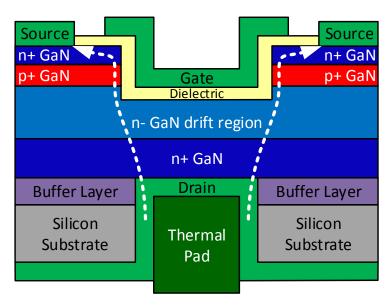

| Figure 2.3. Vertical GaN-on-Si MISFET [57]                                                           |      |

| Figure 2.4. Cost and growth rate comparison of wafers with different growth technique                |      |

| [59]                                                                                                 |      |

| Figure 2.5. Basic structure of depletion-mode lateral GaN HFET (not drawn to scale)                  |      |

| [49]                                                                                                 | 16   |

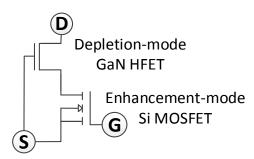

| Figure 2.6. Device structure for the normally-off GaN cascode                                        |      |

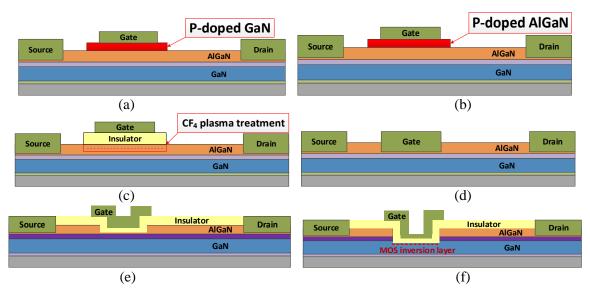

| Figure 2.7. Gate modification techniques for enhancement-mode GaN HFETs, (a) P-                      |      |

| doped GaN, (b) P-doped AlGaN, (c) Plasma treatment, (d) Recessed gate, (e)                           |      |

| Insulated recessed gate, (f) Hybrid MIS-HFET [23],[25],[67],[71],[74-77],[83]                        | 21   |

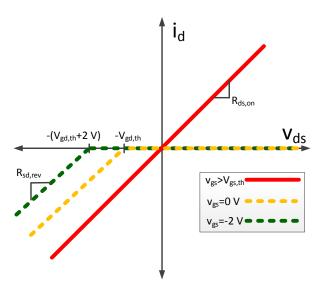

| Figure 2.8. Reverse conduction characteristic of an e-mode GaN HFET.                                 |      |

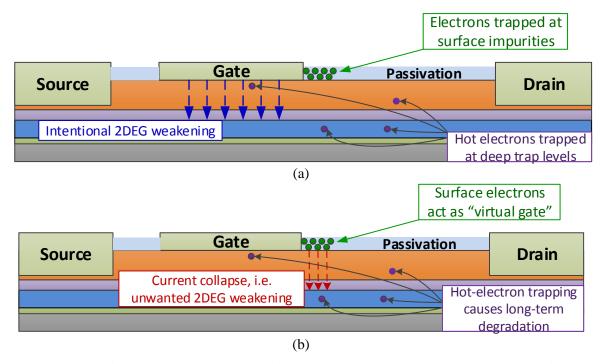

| Figure 2.9. Mechanisms causing dynamic Rds,on in lateral GaN HFETs: (a) Trapping                     |      |

| charges when blocking voltage in off-state, (b) Consequences of trapped charges                      |      |

| during following on-state.                                                                           |      |

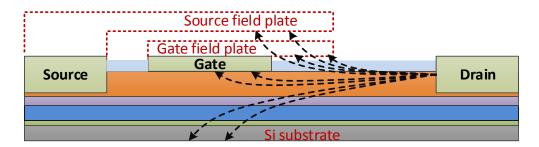

| Figure 2.10. Field plates reshaping the gate-drain electric field to mitigate current                |      |

| collapse.                                                                                            | 26   |

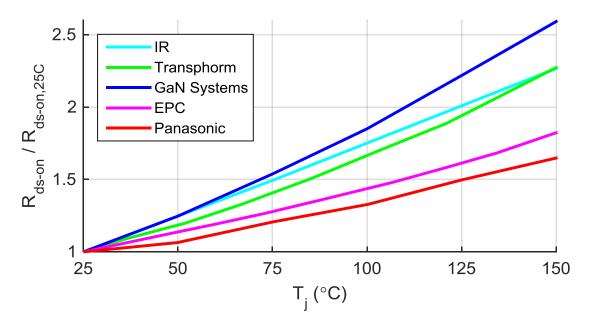

| Figure 2.11. Normalized on-resistance of commercial GaN HFETs                                        |      |

| [26],[60],[69],[72],[84]                                                                             | 28   |

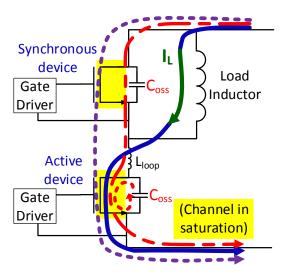

| Figure 2.12. Mechanism causing cross-talk in the synchronous device of a phase leg                   | 34   |

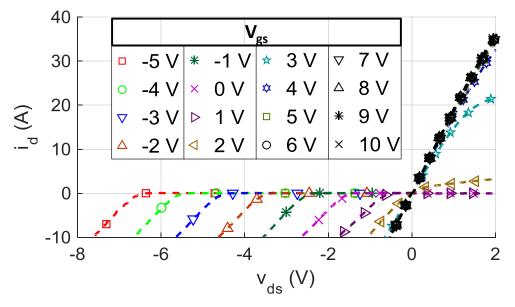

| Figure 3.1. Output characteristic at $Tj = 25$ °C.                                                   |      |

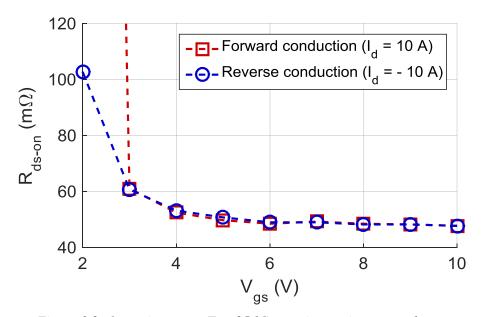

| Figure 3.2. On-resistance at $T_i = 25$ °C, over increasing gate voltage                             | 40   |

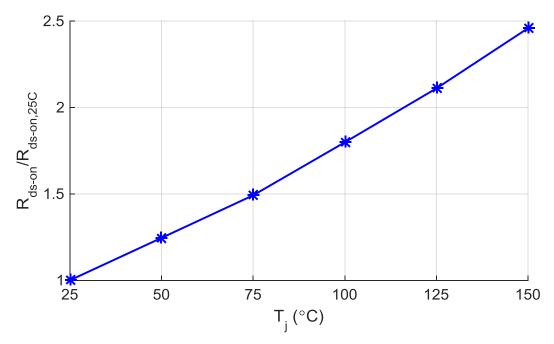

| Figure 3.3. On-resistance over increasing junction temperature.                                      | 41   |

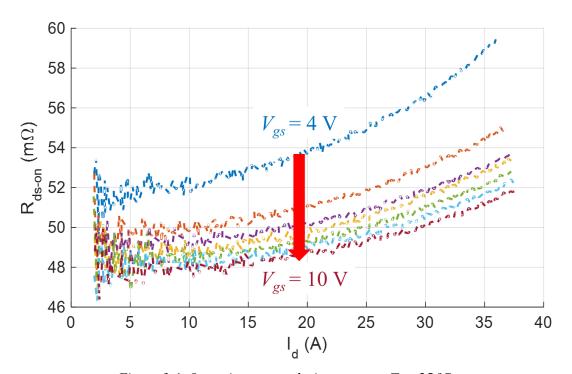

| Figure 3.4. On-resistance vs. drain current at $T_i = 25$ °C                                         |      |

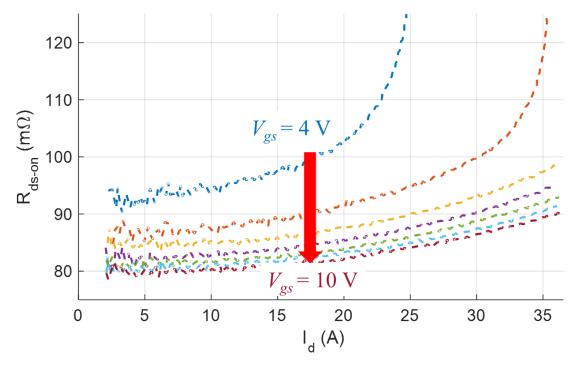

| Figure 3.5. On-resistance vs. drain current at $T_j = 125$ °C                                        | 43   |

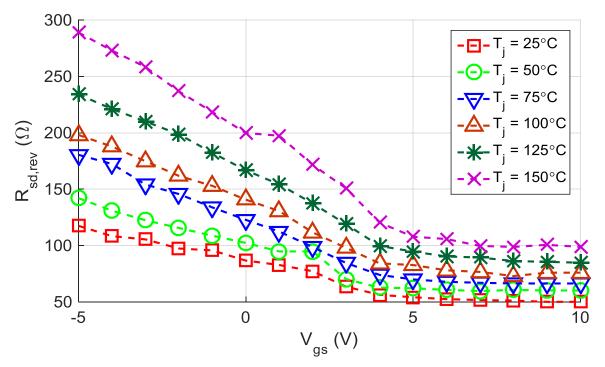

| Figure 3.6. Reverse conduction on-resistance at 10 A                                                 |      |

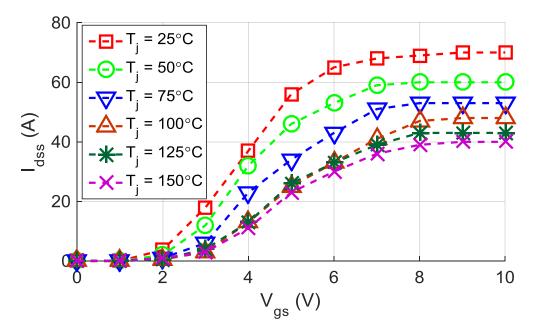

| Figure 3.7. Transfer characteristic over increasing junction temperature, $V_{ds} = 5 \text{ V}$     | 45   |

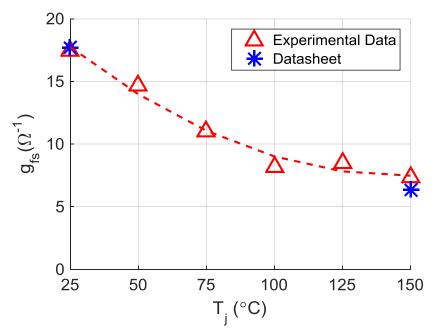

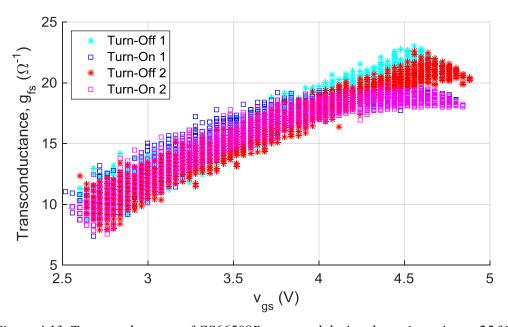

| Figure 3.8. Average transconductance of GS66508P, calculated based on static testing                 |      |

| and the transfer characteristics published in the datasheet.                                         | 45   |

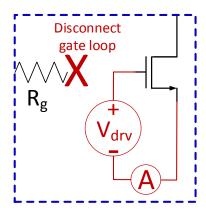

| Figure 3.9. Test setup for measuring steady-state gate (leakage) current                             | 46   |

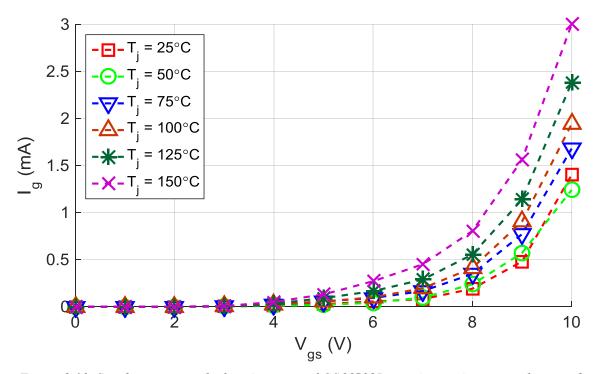

| Figure 3.10. Steady-state gate (leakage) current of GS66508P over increasing gate                    |      |

| voltage and junction temperature                                                                     | 47   |

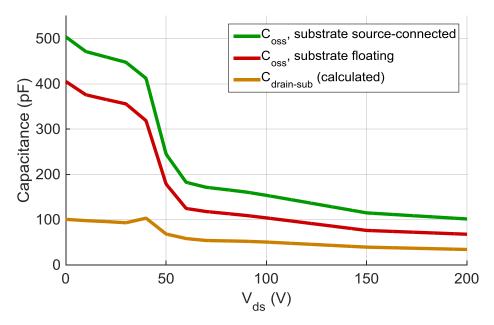

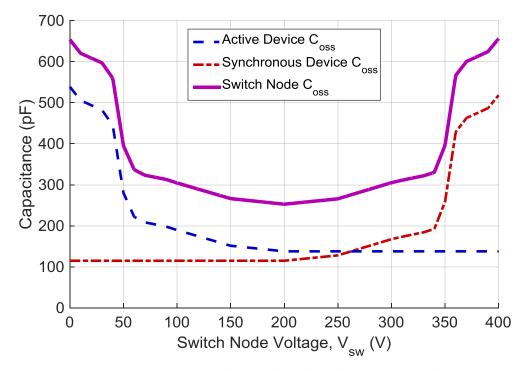

| Figure 3.11. Output capacitance of GS66508P measured on-board and off-board                          | . 49 |

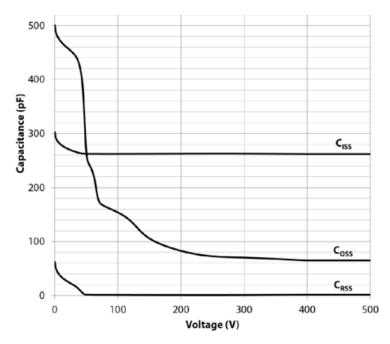

| Figure 3.12. Published junction capacitance curves from GS66508P datasheet [70]                      | 49   |

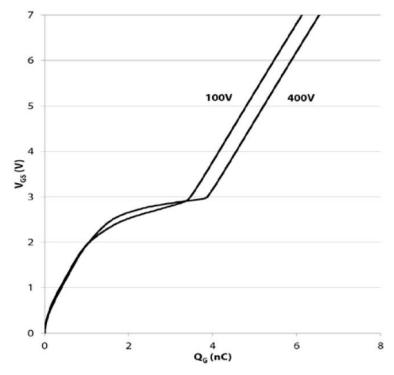

| Figure 3.13. Published gate charge characteristic from GS66508P datasheet [70]                       | 50   |

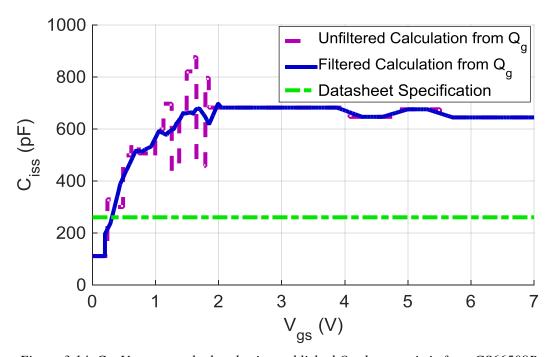

| Figure 3.14. $C_{iss}$ - $V_{gs}$ curve calculated using published $Q_g$ characteristic from GS66508 |      |

| datasheet [70]                                                                                       | 50   |

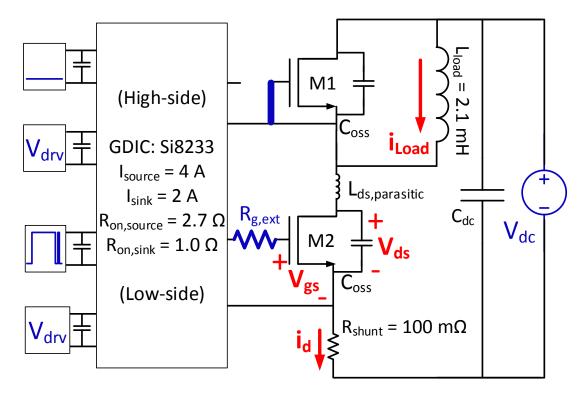

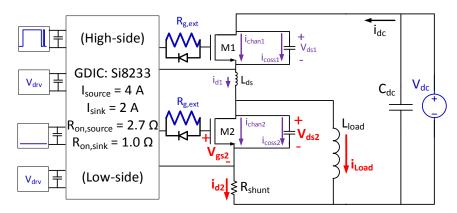

| Figure 3.15. Double pulse test circuit schematic.                                             | 52   |

|-----------------------------------------------------------------------------------------------|------|

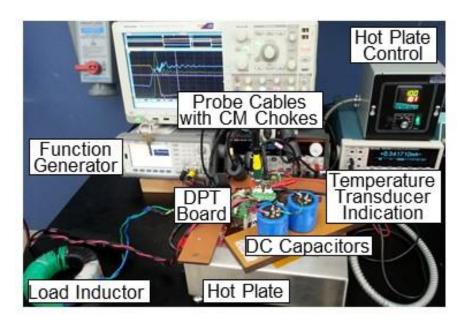

| Figure 3.16. Double pulse test bench setup.                                                   | 52   |

| Figure 3.17. I-V alignment waveforms, used to verify current channel deskew                   |      |

| Figure 3.18. DPT board layout.                                                                |      |

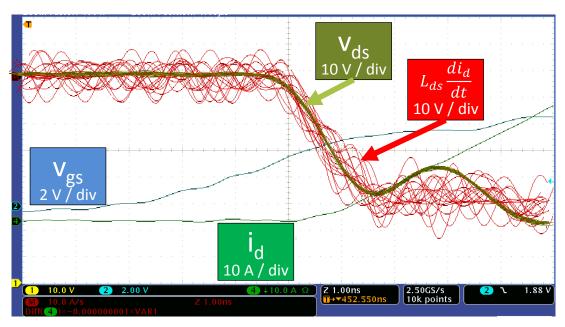

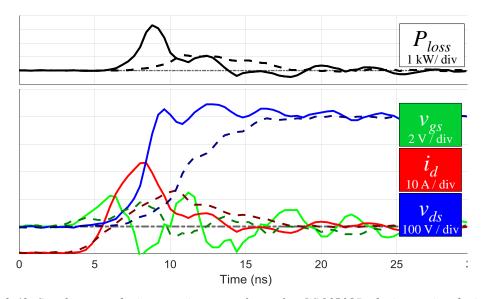

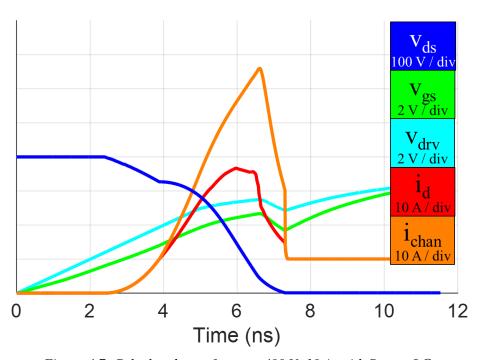

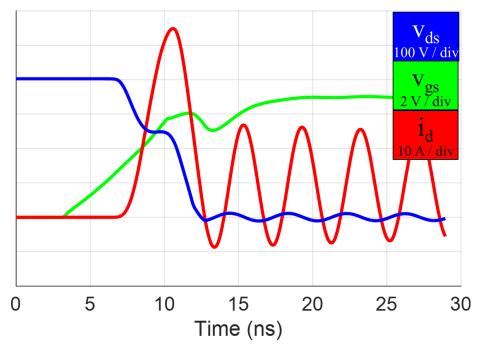

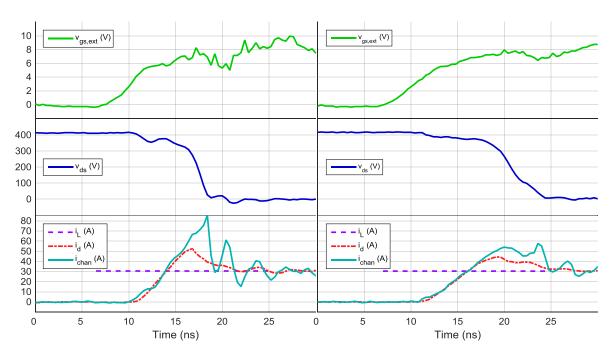

| Figure 3.19. Turn-on waveform of GS66508P at 400 V, 10 A, 25 °C                               | 56   |

| Figure 3.20. Turn-on waveform of GS66508P with calculated channel current at 400              |      |

| 10 A, 25 °C                                                                                   |      |

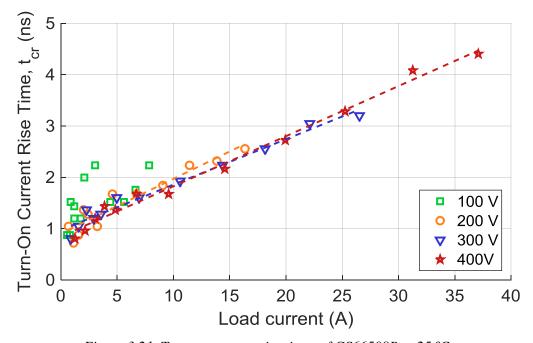

| Figure 3.21. Turn-on current rise times of GS66508P at 25 °C                                  |      |

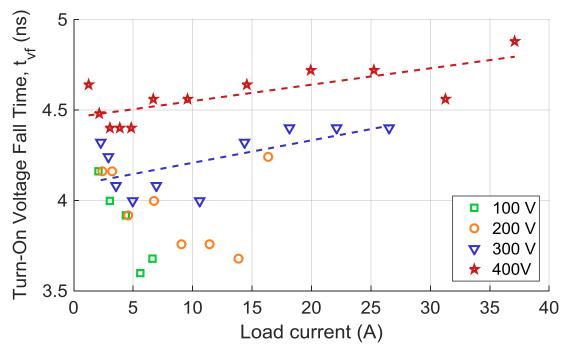

| Figure 3.22. Turn-on voltage fall times of GS66508P at 25 °C                                  |      |

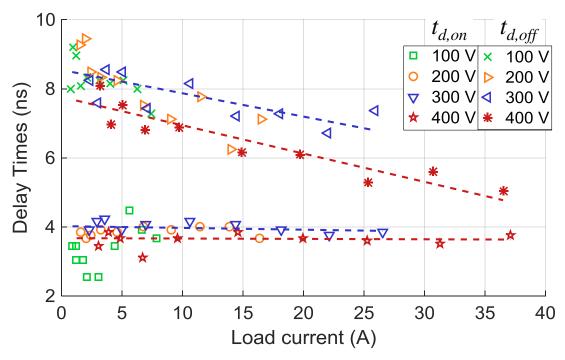

| Figure 3.23. Switching delay times of GS66508P at 25 °C.                                      |      |

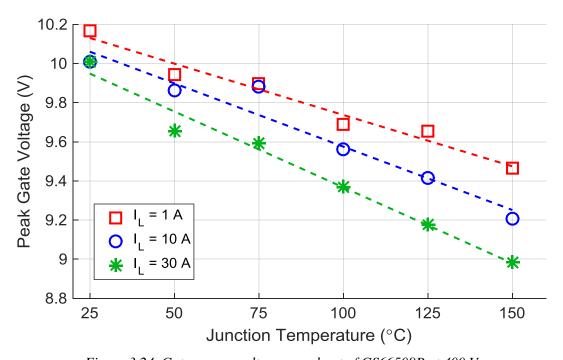

| Figure 3.24. Gate-source voltage overshoot of GS66508P at 400 V                               |      |

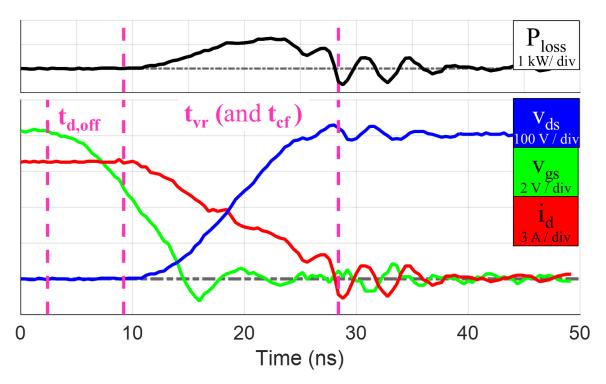

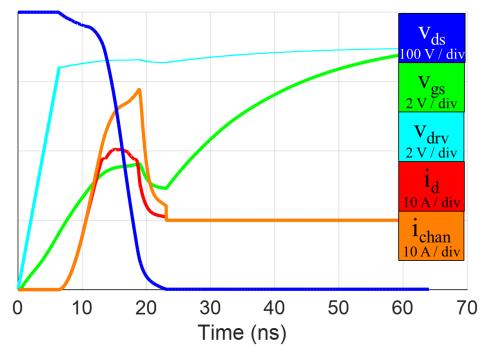

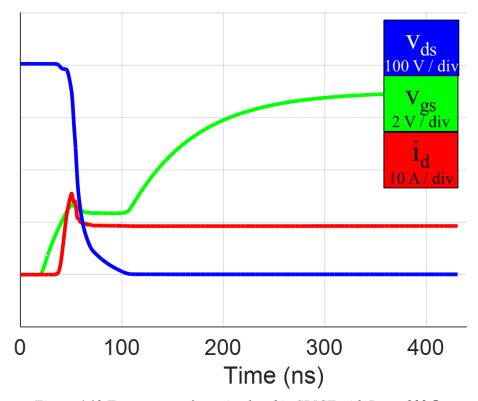

| Figure 3.25. Turn-off waveform of GS66508P at 400 V, 10 A, 25 °C                              |      |

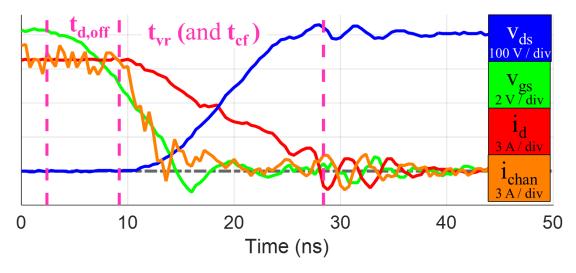

| Figure 3.26. Turn-off waveform of GS66508P with calculated channel current at 400             |      |

| 10 A, 25 °C                                                                                   |      |

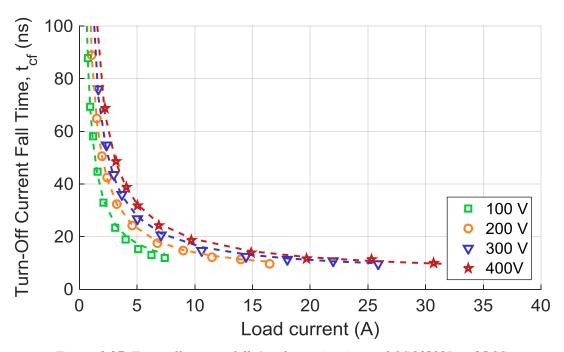

| Figure 3.27. Turn-off current fall & voltage rise times of GS66508P at 25 °C                  |      |

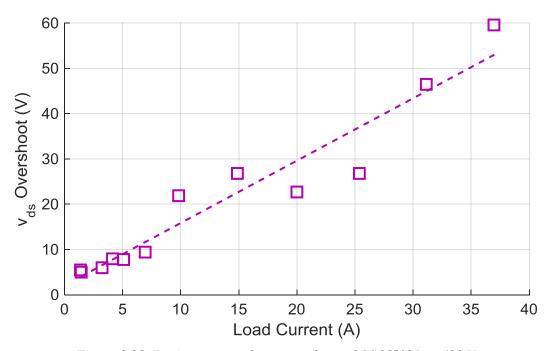

| Figure 3.28. Drain-source voltage overshoot of GS66508P at 400 V.                             |      |

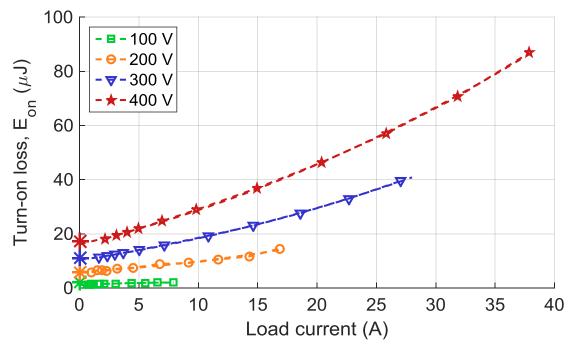

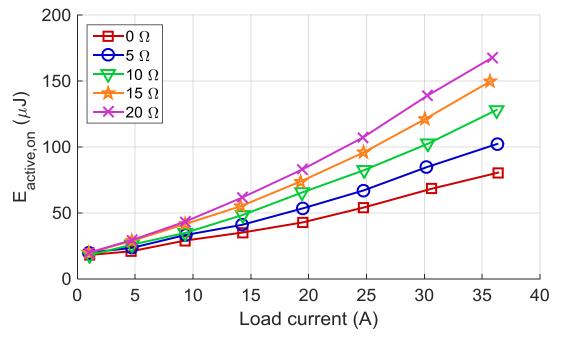

| Figure 3.29. Turn-on energy of GS66508P at 25 °C                                              |      |

| Figure 3.30. Turn-off energy of GS66508P at 25 °C.                                            |      |

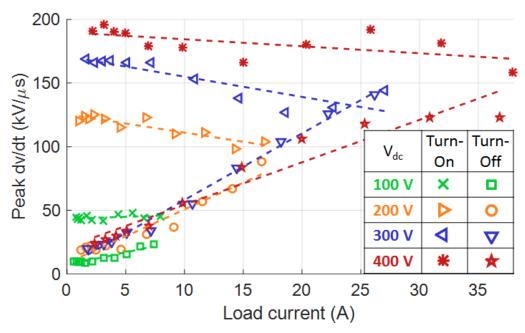

| Figure 3.31. Peak dv/dt of GS66508P during turn-on and turn-off at 25 °C.                     |      |

|                                                                                               |      |

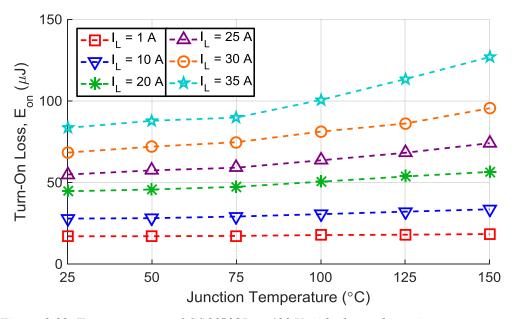

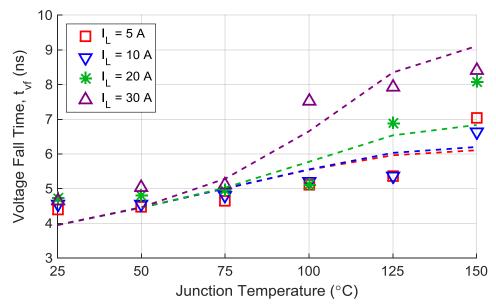

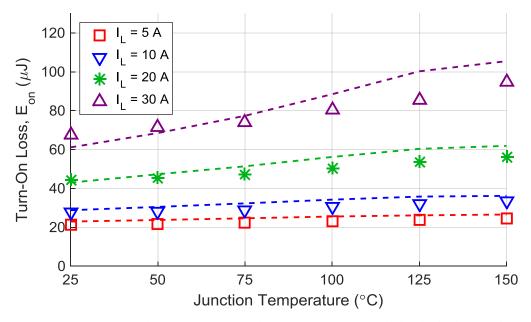

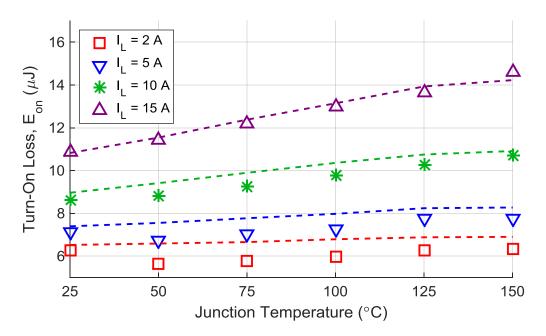

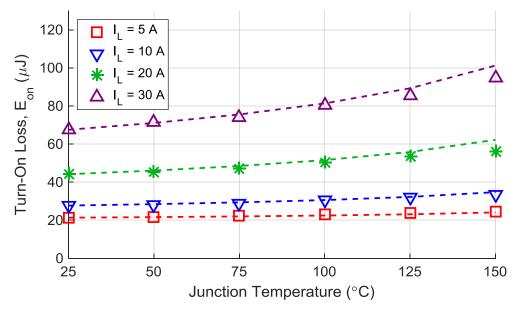

| Figure 3.32. Turn-on energy of GS66508P at 400 V with elevated junction temperatu             |      |

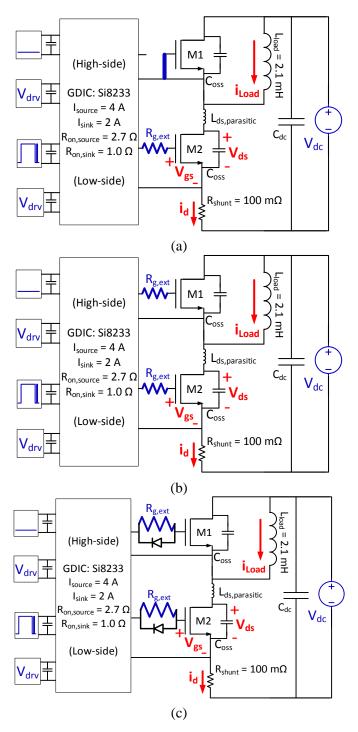

| Figure 3.33. Double pulse test circuit schematic. (a) with limited cross-talk, (b) with       | , 00 |

| worst-case cross-talk, (c) with asymmetric gate drive                                         | 71   |

|                                                                                               |      |

| Figure 3.34. Double pulse test circuit schematic to measure synchronous device, with          |      |

| asymmetric gate drive.                                                                        |      |

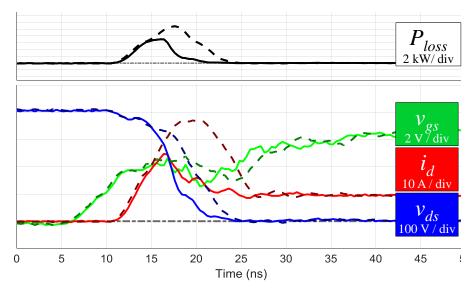

| Figure 3.35. Turn-on transient waveforms of GS66508P at 400 V and 10 A with R <sub>g,ex</sub> |      |

| $10 \Omega$ , showing the best case as a solid line and the worst case as a dashed line       |      |

| Figure 3.36. Turn-on transient waveforms of GS66508P at 400 V and 10 A with R <sub>g,ex</sub> |      |

| 10 $\Omega$ , showing the cross-talk best case as a solid line and the asymmetric drive c     |      |

| as a dashed line.                                                                             |      |

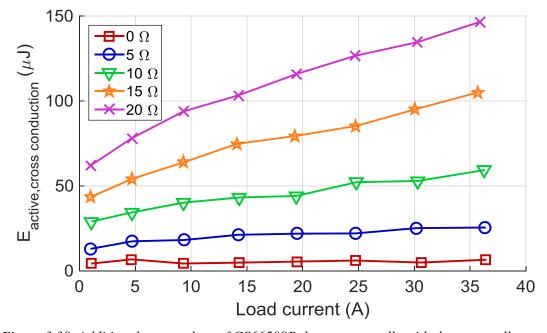

| Figure 3.37. Turn-on loss of GS66508P for an active device, with the cross-talk best of       |      |

| gate drive circuit.                                                                           |      |

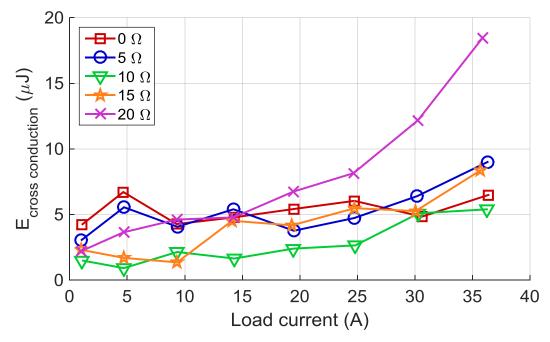

| Figure 3.38. Additional turn-on loss of GS66508P due to cross-talk, with the cross-talk       |      |

| worst case gate drive circuit.                                                                |      |

| Figure 3.39. Additional turn-on loss of GS66508P due to cross-talk, with the practical        |      |

| case using an asymmetric gate drive                                                           |      |

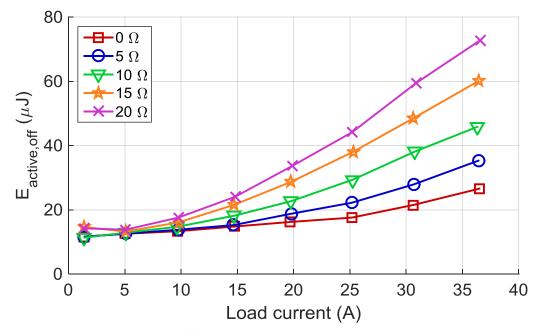

| Figure 3.40. Turn-off loss of GS66508P for an active device in the cross conduction by        |      |

| case                                                                                          |      |

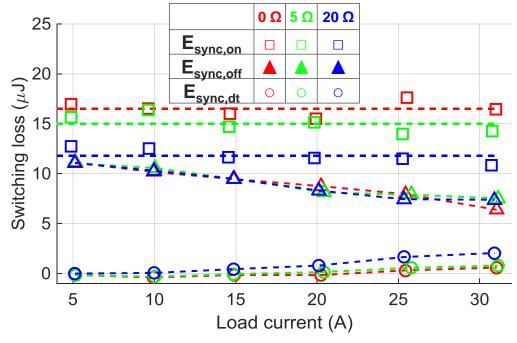

| Figure 3.41. Synchronous device energy with GS66508P, including energy lost during            |      |

| active device turn-on dv/dt, energy recovered during active device turn-off dv/dt             |      |

| and energy lost during dead time following active device turn-off                             | 78   |

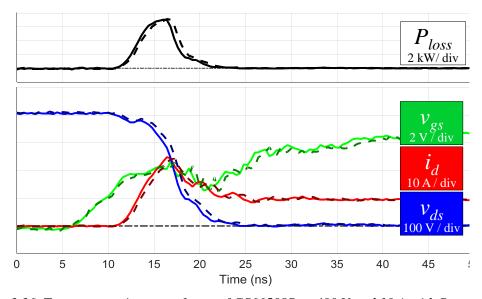

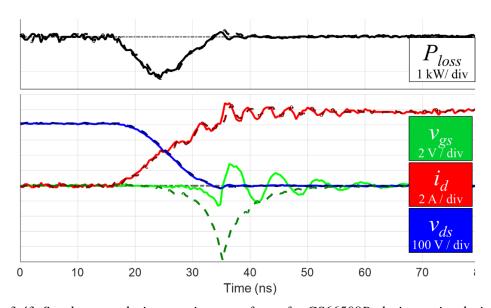

| Figure 3.42. Synchronous device transient waveforms for GS66508P, during active               |      |

| device turn-on at 400 V and 10 A with an asymmetric gate drive circuit, showing               | _    |

| $R_{g,ext} = 0 \Omega$ with a solid line and $R_{g,ext} = 20 \Omega$ with a dashed line       | 78   |

| Figure 3.43. Synchronous device transient waveforms for GS66508P, during active device turn-off at 400 V and 10 A with an asymmetric gate drive circuit, showing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| $R_{g,ext} = 0 \Omega$ with a solid line and $R_{g,ext} = 20 \Omega$ with a dashed line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 70             |

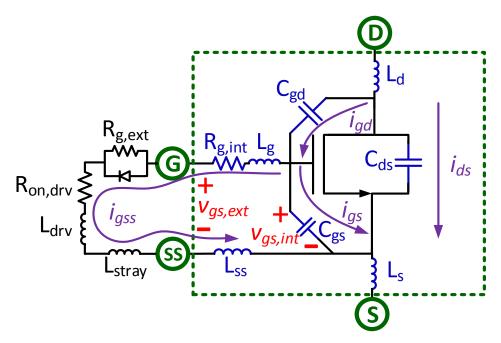

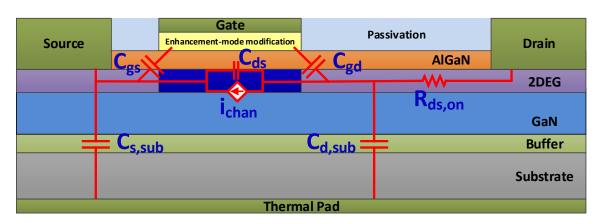

| Figure 4.1. Subcircuit model for an enhancement-mode GaN HFET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                |

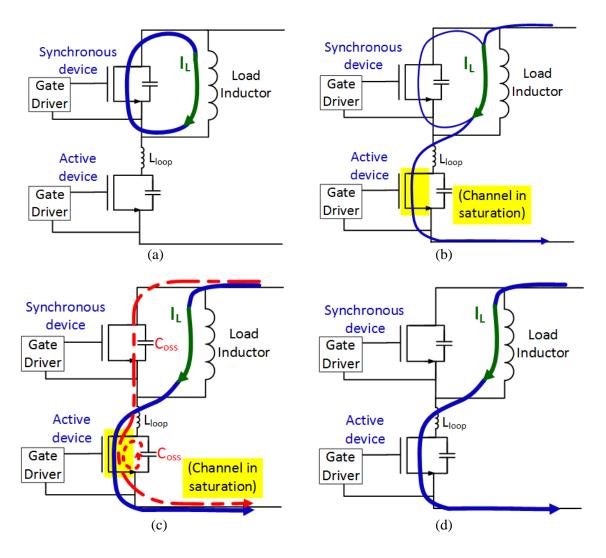

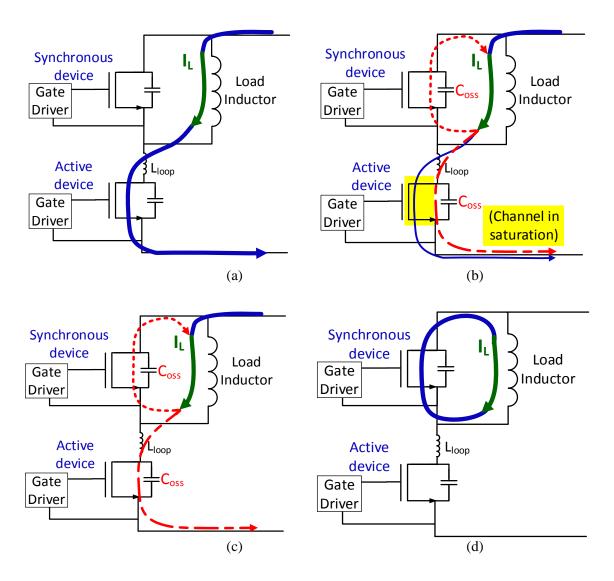

| Figure 4.2. Current in a phase leg during a hard turn-on transient with fast-switching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ))             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |

| devices. (a) Before turn-on transient and during turn-on delay time; (b) During                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |

| current rise time; (c) During voltage fall time; (d) After turn-on transient is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.4            |

| complete                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                |

| Figure 4.3. Impact of cross-talk on voltage fall time in a phase leg, showing the induced                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                |

| shoot-through current with a purple dashed line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5/             |

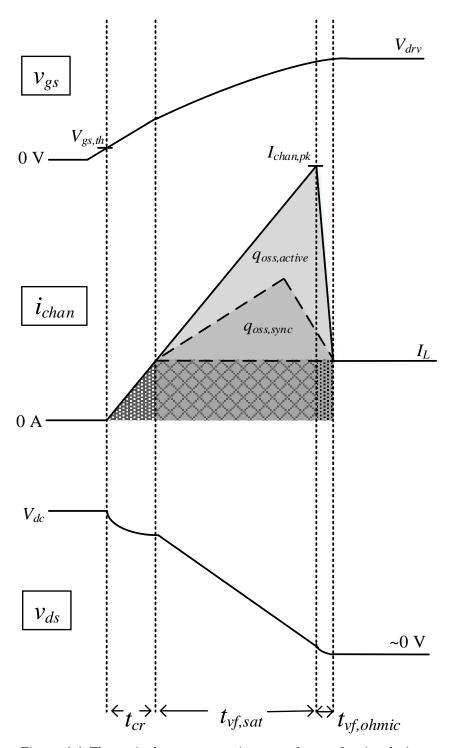

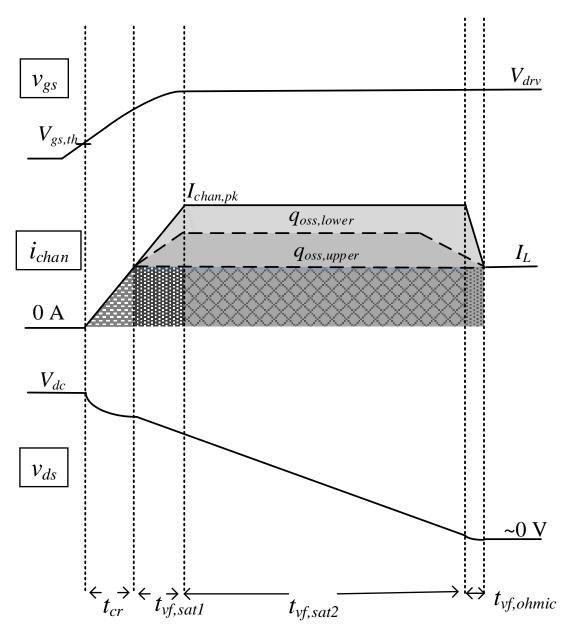

| Figure 4.4. Theoretical turn-on transient waveforms of active device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 39             |

| Figure 4.5. Current in a phase leg during a hard turn-off transient with fast-switching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                |

| devices. (a) Before turn-off transient and during turn-off delay time; (b) During                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                |

| current fall and voltage rise time, while channel is turning off; (c) During current fa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ı11            |

| and voltage rise time, after channel is fully off; (d) After turn-off transient is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                |

| complete9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <del>)</del> 2 |

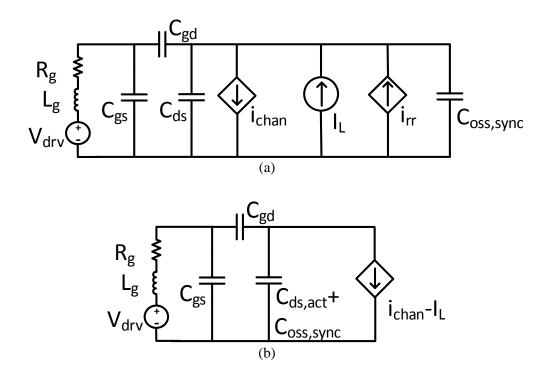

| Figure 4.6. Equivalent circuit of active device during turn-on voltage fall time, (a)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                |

| Detailed model including reverse recovery, (b) Simplified model with no reverse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |

| recovery9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | )5             |

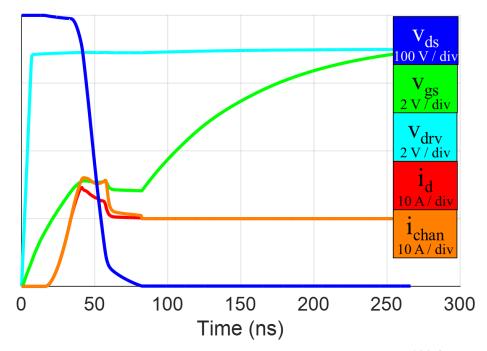

| Figure 4.7. Calculated waveforms at 400 V, 10 A, with $R_{g,ext} = 0 \Omega$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                |

| Figure 4.8. Calculated waveforms at 400 V, 10 A, with $R_{g,ext} = 20 \Omega$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                |

| Figure 4.9. Calculated waveforms at 400 V, 10 A, with $R_{g,ext} = 100 \Omega$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                |

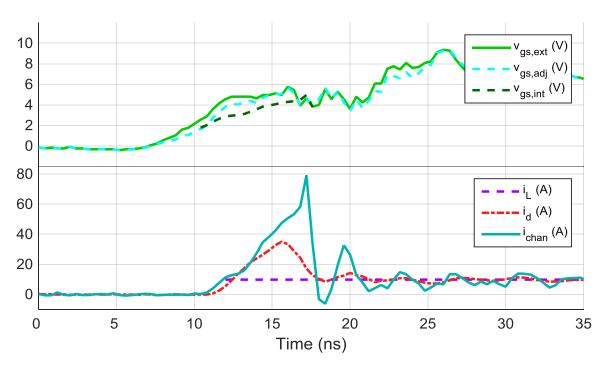

| Figure 4.10. Experimental waveforms manipulated to estimate internal gate voltage 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                |

| Figure 4.11. Turn-on waveform simulated in SPICE with $R_{g,ext}=0$ $\Omega$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                |

| Figure 4.12 Turn-on waveform simulated in SPICE with $R_{g,ext}$ =100 $\Omega$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                |