University of Tennessee, Knoxville Trace: Tennessee Research and Creative Exchange

### Masters Theses

Graduate School

12-2005

# "Design and Verification of a Reusable Self-Reconfigurable Gate Array Architecture

Gabriel Cozmin Chereches University of Tennessee - Knoxville

#### **Recommended** Citation

Chereches, Gabriel Cozmin, ""Design and Verification of a Reusable Self-Reconfigurable Gate Array Architecture. "Master's Thesis, University of Tennessee, 2005. https://trace.tennessee.edu/utk\_gradthes/1840

This Thesis is brought to you for free and open access by the Graduate School at Trace: Tennessee Research and Creative Exchange. It has been accepted for inclusion in Masters Theses by an authorized administrator of Trace: Tennessee Research and Creative Exchange. For more information, please contact trace@utk.edu.

To the Graduate Council:

I am submitting herewith a thesis written by Gabriel Cozmin Chereches entitled ""Design and Verification of a Reusable Self-Reconfigurable Gate Array Architecture." I have examined the final electronic copy of this thesis for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Master of Science, with a major in Electrical Engineering.

Dr. Don Bouldin, Major Professor

We have read this thesis and recommend its acceptance:

Dr. Gregory Peterson, Dr. Itamar Elhanany

Accepted for the Council: Carolyn R. Hodges

Vice Provost and Dean of the Graduate School

(Original signatures are on file with official student records.)

To the Graduate Council:

I am submitting herewith a thesis written by Gabriel Cozmin Chereches entitled 'Design and Verification of a Reusable Self-Reconfigurable Gate Array Architecture". I have examined the final electronic copy of this thesis for form and content and recommend that it be accepted in partial fulfillment of the requirement for the degree of Master of Science, with a major in Electrical Engineering.

Dr. Don Bouldin

Major Professor

We have read this thesis and recommend its acceptance:

Dr. Gregory Peterson

Dr. Itamar Elhanany

Accepted for the Council:

Anne Mayhew

Vice Chancellor and Dean of Graduate Studies

(Original signatures are on file with official student records.)

## Design and Verification of a Reusable Self-Reconfigurable

Gate Array Architecture

A Thesis Presented for the Master of Science Degree

University of Tennessee, Knoxville

Gabriel Cozmin Chereches

December 2005

to titu (my father) and to ron

## Acknowledgments

I would like to thank my academic and thesis advisor Dr. Donald W. Bouldin for his support and guidance throughout my graduate school and for taking an interest in me pursuing this research and providing me with the facilities in the Microelectronic System Research Lab at the University of Tennessee. I would like to thank Dr. Gregory D. Peterson and Dr. Itamar Elhanany for their interest in this work and for serving on my thesis committee.

I would like to acknowledge the University of Southern California and the University of Trento (Italy) for coming up with such an innovative Self-Reconfigurable device which caught our attention (Dr. Bouldin and I) – thanks to R. Sidhu, A. Mei, and V. Prasanna.

I would like to thank Dr. Roger Parsons, Director of the Engage Engineering Fundamentals Program at the University of Tennessee, for offering me the Graduate Teaching Assistant position and allowing me to be part of one of the nation's most innovative freshman engineering programs. I also would like to thank Dr. Fred Gilliam, the former Associate Dean of the College of Engineering, for his guidance throughout my education.

I would like to thank the Athletic Department at the University of Tennessee for supporting me while in graduate school by awarding me the Herman Hickman Memorial Scholarship. Dave, JT, Joe, and all my coaches, have made a difference and I would like to express my appreciation.

I would like to thank the Environmental Systems Corporation, especially Adam Engle, for offering me a great job while being tied up with my academic goals.

I am very thankful for having a great family – Magdalena (my mother), Anca (my sister), Lucian (my brother), and Jim Hoyle, thanks for believing in me.

I would like to thank the class of ECE 652 (spring 2003) for sharing their knowledge and support. And I would like to express my appreciation for those that have been there for me – and in no particular order: Lee Blask, Bree, Joel, Bird, M. Burton, Wei, Akila, Scott, Kay Shanahan, and Tyler Johnson.

## Abstract

This thesis presents the design and verification of a Self-Reconfigurable Gate Array architecture *(SRGA-UT)* created for reuse, and available with a step-by-step tutorial and comprehensive documentation.

The original SRGA [1], created at the University of Southern California, is an innovative architecture for a reconfigurable device that allows single cycle context switching and single cycle random access to a unified on-chip configuration/data memory. The key architecture that enables the above two features is the use of a mesh of trees based interconnect with logic cells and memory blocks at the leaf nodes and identical switches at the parent nodes.

The *SRGA-UT* was adapted by making necessary modifications to the original design, to be implemented using the available University of Tennessee electronic design automation tools. An 8x8 array of PEs (Processing Elements) was synthesized and routed targeting a standard cell library for a 0.18  $\mu$ m process. The synthesized design can store eight configuration contexts in each PE (this number can be modified by editing the Verilog files). The place and route generated a core-chip size of 5,413,300  $\mu$ m<sup>2</sup>, and contains 354,053 number of gates. The step-by-step tutorial demonstrates that the *SRGA-UT* design is capable to switch context and perform memory access operations in a single clock cycle.

ModelSim tools were used for verification and simulation at all levels, Design Compiler executed the synthesis and created the netlist design, and First Encounter SoC performed the place and route and created the delay constraints.

iv

## **Table of Contents**

| Chapter | 1 Introduction                  | 1  |

|---------|---------------------------------|----|

| 1.1     | Thesis Goals                    | 1  |

| 1.2     | Outline of Thesis               | 2  |

| Chapter | 2 Background                    | 4  |

| 2.1     | Reconfigurable Technology       | 4  |

| 2.2     | Design Reuse                    | 5  |

| 2.3     | SRGA-USC                        | 6  |

| Chapter | 3 Component Background          | 10 |

| 3.1     | Components Overview             | 10 |

| 3.2     | Registers                       | 10 |

| 3.3     | Configuration Word              | 13 |

| 3.4     | Logic Cell                      | 16 |

| 3.5     | Memory Cell                     | 20 |

| 3.6     | Switch Structure                | 23 |

| 3.7     | PE Structure                    | 25 |

| 3.8     | 2x2 Array                       | 27 |

| 3.9     | 8x8 Array                       | 27 |

| Chapter | 4 SRGA-UT Implementation        | 29 |

| 4.1     | SRGA-UT Overview                | 29 |

| 4.2     | EDA Tools                       | 29 |

| 4.3     | Setting up Files                | 31 |

| 4.4     | 8x8 Array Step-by-Step Tutorial | 32 |

|         | Array 8x8 Pre-Synthesis         | 36 |

|         | Array 8x8 Synthesis             | 40 |

|         | First Encounter Tools           | 43 |

|         | Step 1: Setting up the files    | 43 |

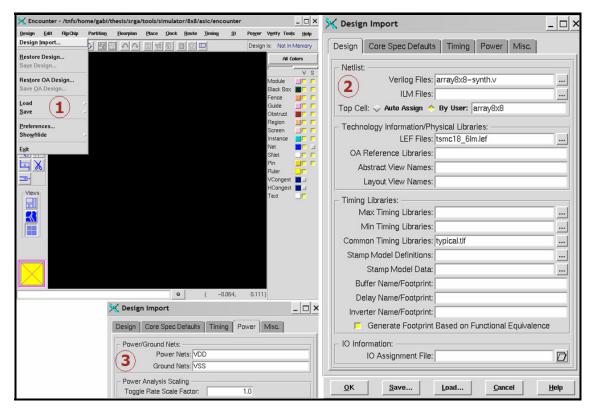

|        | Step 2: Import the Design                       | 43 |

|--------|-------------------------------------------------|----|

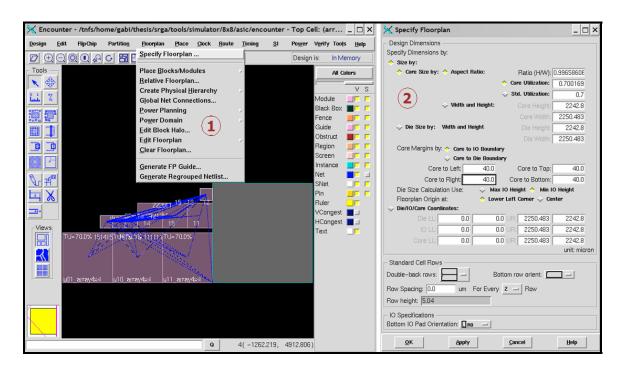

|        | Step 3: Specify the Chip Size                   |    |

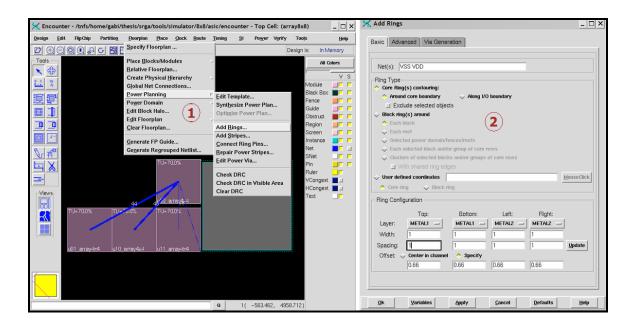

|        | Step 4: Power Planning                          |    |

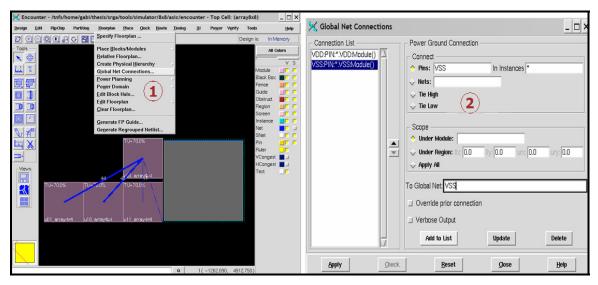

|        | Step 5: Global Net Connections                  |    |

|        | Step 6: Standard Cell Placement                 |    |

|        | Step 7: Add Filler Cells                        |    |

|        | Step 8: Route Power                             |    |

|        | Step 9: Final Route                             |    |

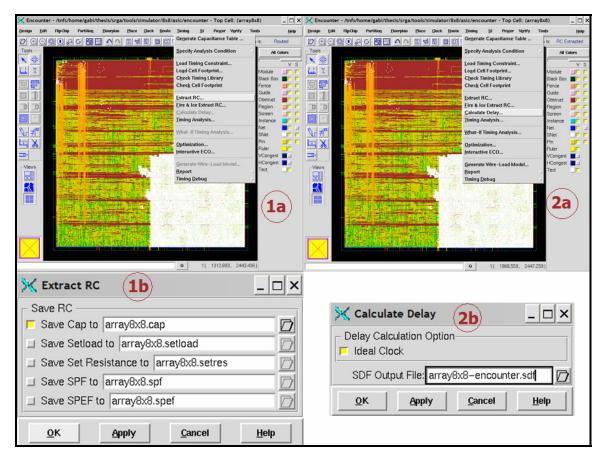

|        | Step 10: Extract RC                             | 50 |

|        | Step 11: Calculate Delay                        | 50 |

|        | Step 12: Results, Save, and Restore Design      |    |

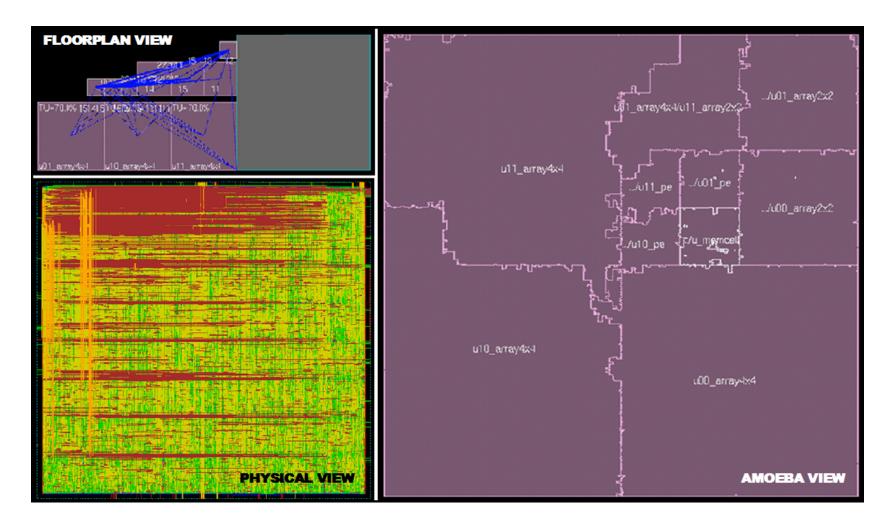

|        | Final Layouts                                   | 51 |

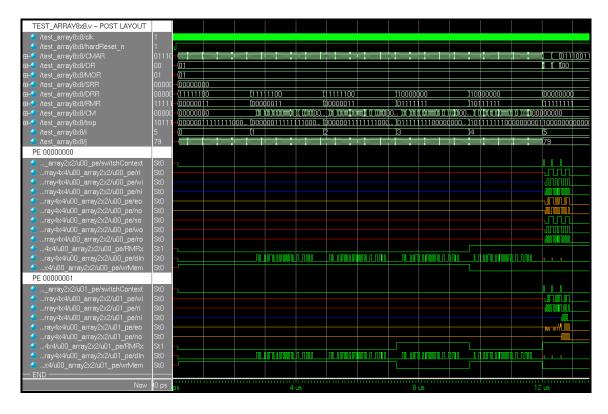

|        | Array 8x8 Post Layout Simulation                | 51 |

| Chapte | r 5 Implementing the <i>SRGA-UT</i> Sub-Designs |    |

| 5.1    | Logic Cell Implementation                       | 55 |

|        | Logic Cell Pre-Synthesis                        |    |

|        | Logic Cell Synthesis                            | 57 |

|        | Logic Cell Place and Route                      | 59 |

| 5.2    | Memory Cell Implementation                      |    |

| 5.3    | Switch Implementation                           |    |

| 5.4    | PE Implementation                               |    |

| 5.5    | 2x2 Array Implementation                        | 72 |

| Chapte | r 6 SRGA-UT Results, Conclusion and Future      |    |

|        | Possibilities                                   |    |

| 6.1    | Results                                         |    |

| 6.2    | Conclusion and Future Possibilities             |    |

| Refere | nce                                             | 79 |

|        |                                                 |    |

| VIIA   |                                                 |    |

## List of Figures

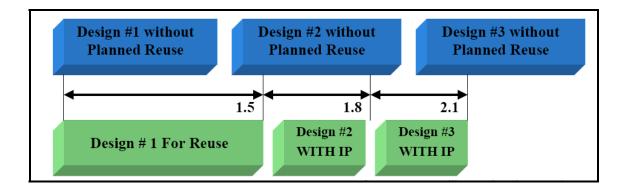

| Figure 2.2.1: | Design for Reuse Diagram [5]6                                  | 5 |

|---------------|----------------------------------------------------------------|---|

| Figure 2.3.1: | SRGA Architecture                                              | 7 |

| Figure 3.2.1: | OR and MOR Registers                                           | L |

| Figure 3.2.2: | Periphery Registers (a) N x N Array of PEs [1] (b) PE 12       | ) |

| Figure 3.3.1: | Configuration Word Format (a) Diagram and (b) From             |   |

| Configuration | File                                                           | ł |

| Figure 3.3.2: | Full Add Configuration (a) Truth Table (b) LUT 15              | 5 |

| Figure 3.3.3: | Full Subtract Configuration (a) Truth Table (b) LUT 15         | 5 |

| Figure 3.4.1: | (a) LUT Structure and (b) Flip-Flop Structure                  | 5 |

| Figure 3.4.2: | Logic cell Structure [1]                                       | 7 |

| Figure 3.4.3: | Internal Functions of the LUT 18                               | 3 |

| Figure 3.4.4: | Input and Output Set of Wires for the Logic Cell Muxes 19      | ) |

| Figure 3.5.1: | Memory Block Structure [1] 21                                  | L |

| Figure 3.5.2: | Defining the Size of the Memory Array 21                       | L |

| Figure 3.6.1: | Switch Structure                                               | ł |

| Figure 3.7.1: | PE Structure [1] 26                                            | 5 |

| Figure 3.8.1: | Structure of the 2x2 Array 28                                  | 3 |

|               | Structure of the 8x8 Array 28                                  |   |

| Figure 4.2.1: | SRGA-UT Design Flow 31                                         | L |

| Figure 4.4.1: | Configuration Word Format for the 8x8 Array                    | 3 |

| Figure 4.4.2: | Importing Configuration Word Section of <i>test_array8x8.v</i> | 5 |

| Figure 4.4.3: | Assigning Inputs to the 8x8 Array 35                           | 5 |

| Figure 4.4.4: | Array 8x8 Pre-Synthesis - Loading Memory Blocks                | 7 |

| Figure 4.4.5: | Array 8x8 Full Add Demo Schematic                              | 3 |

| Figure 4.4.6: | Array 8x8 Pre-Synthesis - Applications                         | ) |

| Figure 4.4.7: | Array 8x8 Pre Synthesis Workspace                              | ) |

| Figure 4.4.8:  | Array 8x8 Synthesis - Loading Memory Blocks              | 42 |

|----------------|----------------------------------------------------------|----|

| Figure 4.4.9:  | Array 8x8 Pre-Synthesis - Applications                   | 42 |

| Figure 4.4.11: | Encounter Tools - Importing Design                       | 44 |

| Figure 4.4.12: | Encounter Tools - Specify Chip Size                      | 45 |

| Figure 4.4.13: | Encounter Tools - Power Planning                         | 45 |

| Figure 4.4.14: | Encounter Tools - Global Net Connections                 | 46 |

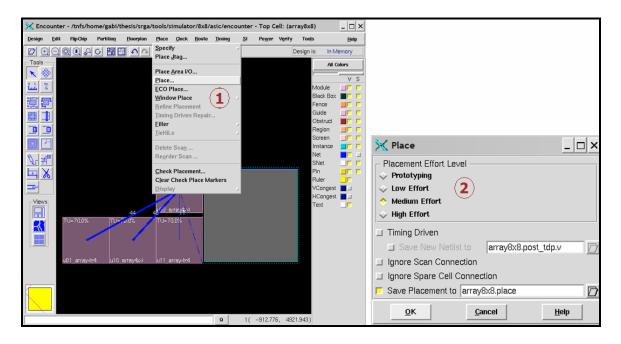

| Figure 4.4.15: | Encounter Tools - Standard Cell Placement                | 47 |

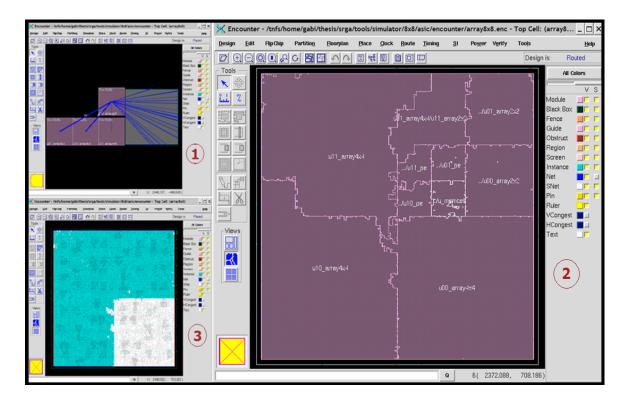

| Figure 4.4.16: | Encounter Tools - Cell Placement Views                   | 47 |

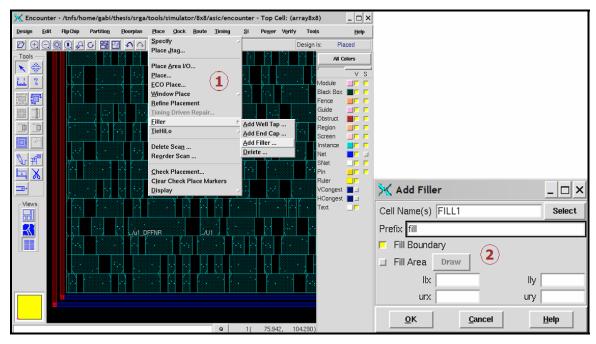

| Figure 4.4.17: | Encounter Tools - Add Filler Cells                       | 48 |

| Figure 4.4.18: | Encounter Tools - Route Power                            | 49 |

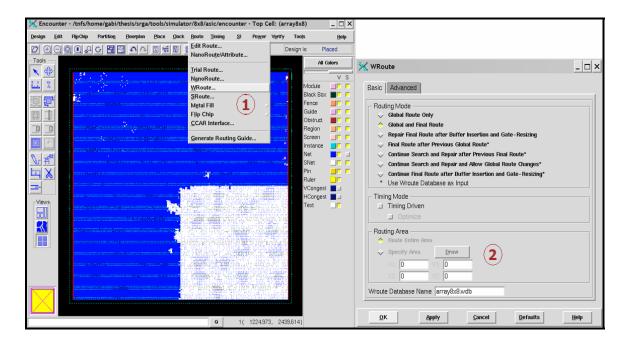

| Figure 4.4.19: | Encounter Tools - Final Route                            | 49 |

| Figure 4.4.20: | Encounter Tools - (1) Extract RC and (2) Calculate Delay | 50 |

| Figure 4.4.21: | Encounter Tools - Final Pace and Route of 8x8 Array      | 52 |

| Figure 4.4.22: | Array 8x8 Post Layout - Loading Memory Blocks            | 53 |

| Figure 4.4.23: | Array 8x8 Post Layout – Applications                     | 54 |

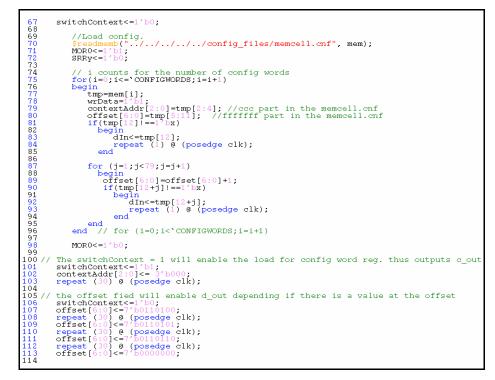

| Figure 5.1.1:  | Section of Test-bench for Logic Cell Block               | 56 |

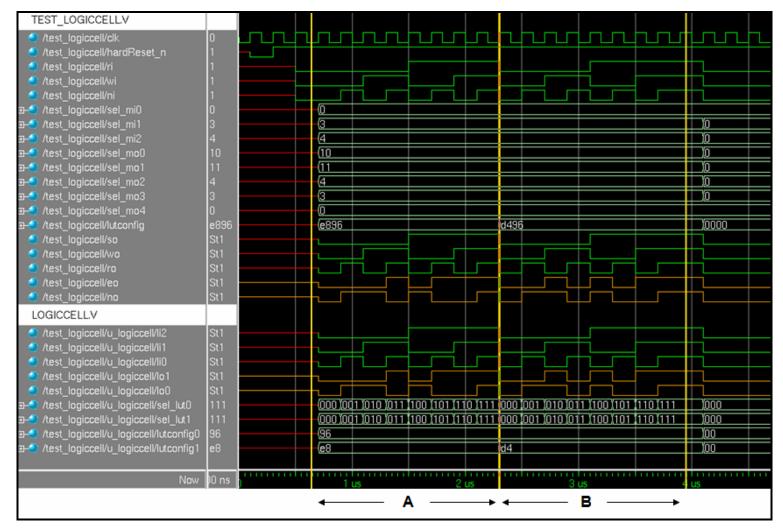

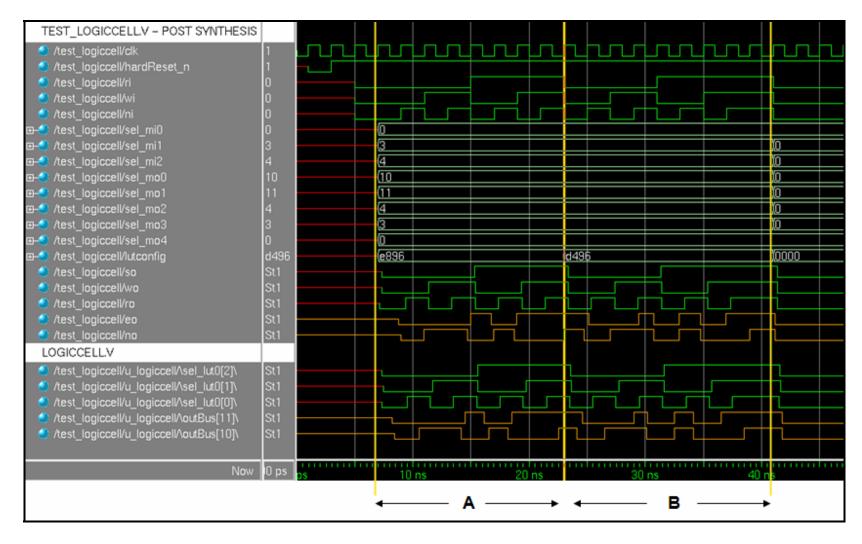

| Figure 5.1.2:  | Logic Cell - Pre-Synthesis Simulation                    | 58 |

| Figure 5.1.3:  | Logic Cell - Post-Synthesis Simulation                   | 60 |

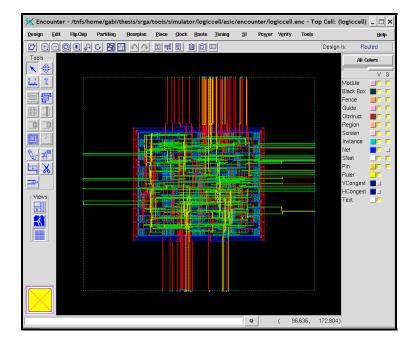

| Figure 5.1.4:  | Logic Cell Layout after WRoute                           | 61 |

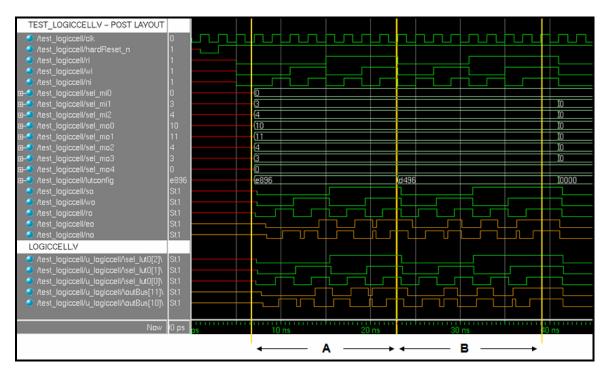

| Figure 5.1.5:  | Logic Cell - Post-Layout Simulation                      | 62 |

| Figure 5.2.1:  | Section of Test Bench for Memory Cell Block              | 64 |

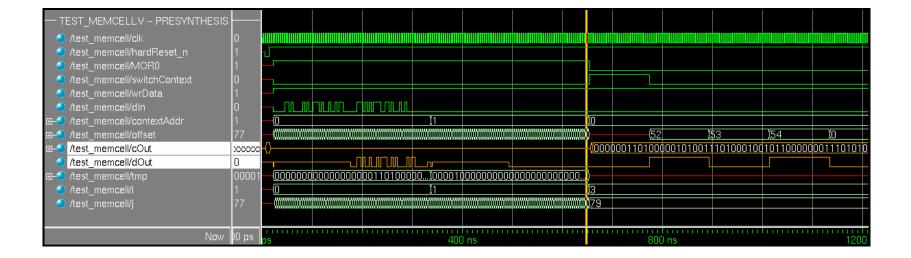

| Figure 5.2.2:  | Memory Cell Testing                                      | 65 |

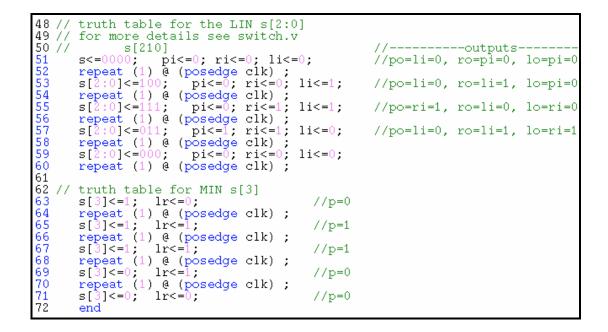

| Figure 5.3.1:  | Section of Test Bench for Switch Module                  | 67 |

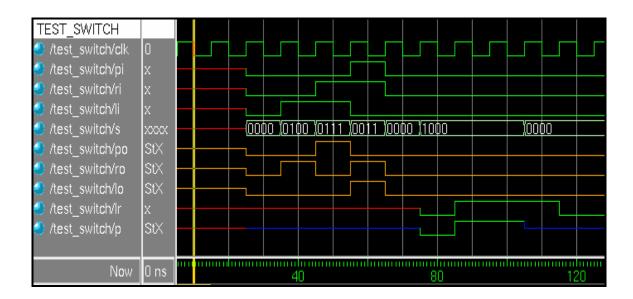

| Figure 5.3.2:  | Switch Testing                                           | 67 |

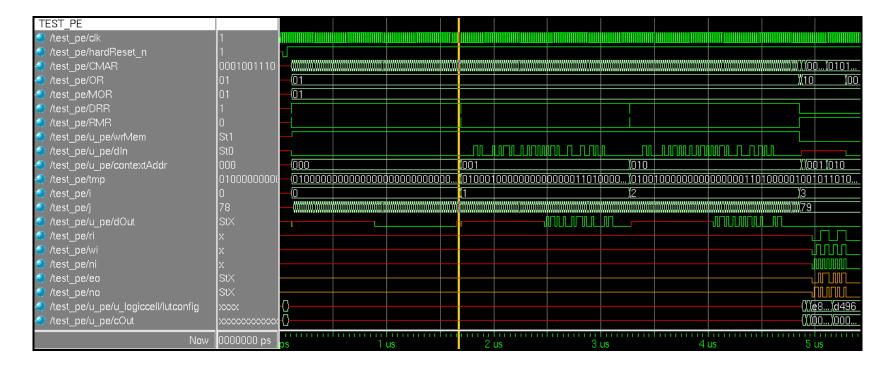

| Figure 5.4.1:  | PE Testing – Loading Configuration                       | 69 |

| Figure 5.4.2:  | PE Testing – Operations                                  | 70 |

| Figure 5.5.1:  | 2x2 Array Testing – Loading Configuration                | 73 |

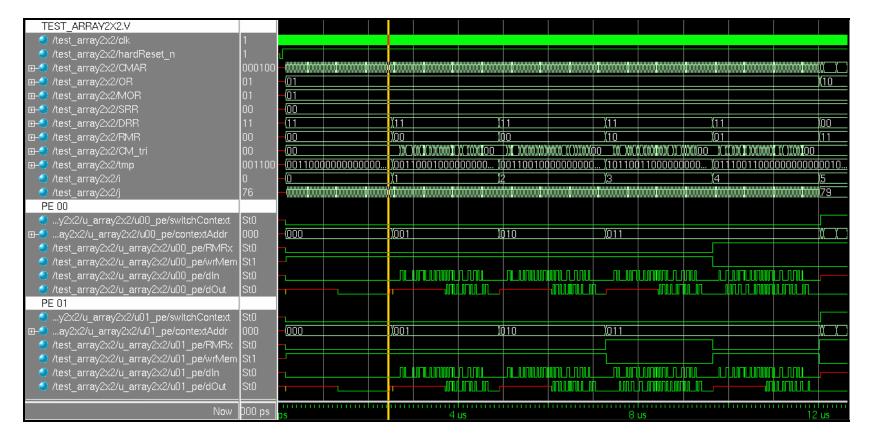

| Figure 5.5.2:  | 2x2 Array Testing – Operations                           | 74 |

| Figure 6.1.1:  | 8x8 SRGA-UT Results                                      | 77 |

## List of Acronyms

| CCR  | – Current Context Register                              |

|------|---------------------------------------------------------|

| CMAR | <ul> <li>Context and Memory Address Register</li> </ul> |

| CMR  | – Column Mask Register                                  |

| CSMR | <ul> <li>Context Switch Mask Register</li> </ul>        |

| DCR  | <ul> <li>Destination Column Register</li> </ul>         |

| DRMR | – Data Restore Mask Register                            |

| DRR  | <ul> <li>Destination Row Register</li> </ul>            |

| ECE  | <ul> <li>Electrical and Computer Engineering</li> </ul> |

| EDA  | <ul> <li>Electronic Design Automation</li> </ul>        |

| FF   | – Flip-Flop                                             |

| FPGA | <ul> <li>Field Programmable Gate Array</li> </ul>       |

| GDS  | – Graphic Design System                                 |

| HDL  | <ul> <li>Hardware Description Language</li> </ul>       |

| IC   | – Integrated Circuit                                    |

| IP   | <ul> <li>Intellectual Property</li> </ul>               |

| I/O  | – Input/Output                                          |

| LIN  | <ul> <li>Logic Interconnection Network</li> </ul>       |

| LUT  | – Lookup Table                                          |

| MIN  | <ul> <li>Memory Interconnection Network</li> </ul>      |

| MOR  | <ul> <li>Memory Operation Register</li> </ul>           |

| OR   | <ul> <li>Operation Register</li> </ul>                  |

| PE   | <ul> <li>Processing Element</li> </ul>                  |

| RAM  | <ul> <li>Random Access Memory</li> </ul>                |

| RMR  | – Row Mask Register                                     |

| RTL  | – Register Transfer Level                               |

| SCR  | – Source Column Register                                |

| SDF  | – Standard Delay Format                                 |

SoC – System on Chip

SRGA – Self-Reconfigurable Gate Array

SRGA-USC – Self-Reconfigurable Gate Array - University of Southern California

*SRGA-UT* – Self-Reconfigurable Gate Array - University of Tennessee

SRR – Source Row Register

## **Chapter 1: Introduction**

#### **1.1 Thesis Goals**

The objective of this thesis was to use the open code of the Self-Reconfigurable Gate Array (SRGA) architecture, created by the Department of EE-Systems at University of Southern California and the Department of Mathematics at the University of Trento (Italy), and make the minimum adjustments necessary to adapt and implement using the available EDA (electronic design automation) tools at the Department of ECE at the University of Tennessee. The outcome of this thesis was to end up with a *SRGA-UT* design for reuse, accessible with a step-by-step tutorial and comprehensive documentation.

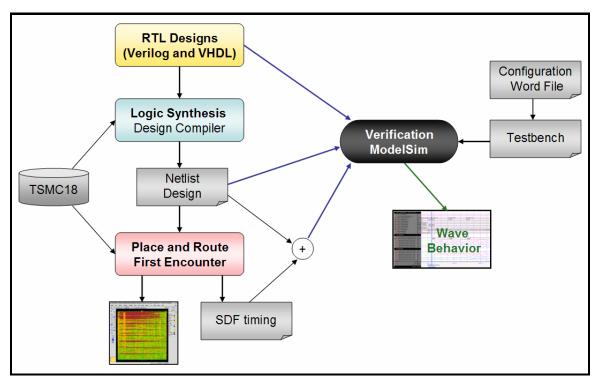

To achieve this goal, a great deal of knowledge of the *SRGA-USC* architecture was required. The first step was to examine the RTL (register transfer level) design, make the appropriate adjustments and pass the pre-synthesis verification stage. The second challenge was to synthesize the RTL design, create the netlist and pass the synthesis verification stage. And the last step was to generate the place and route from the netlist design, produce the timing delay files, and test the final design for proper functionality.

The EDA tools used to implement the SRGA were: ModelSim for verification and simulation at all stages, Design Compiler for synthesis and creating the netlist, and First Encounter for performing the place and route and creating the delay files.

### **1.2 Outline of Thesis**

The introduction states the thesis goals. An open self-reconfigurable design, *SRGA-USC*, developed at the University of Southern California was taken and implemented using the available EDA tools at the University of Tennessee. The intent was to make the minimum changes, while the focus was to develop a *SRGA-UT* design for reuse with complete documentation and a step-by-step implementation tutorial.

The second chapter will present a background of the IC (integrated circuit) technology – focusing on the reconfigurable devices such as the *SRGA-USC*, an innovative architecture for a self-reconfigurable device that allows single cycle context switching and single cycle random access to the on-chip configuration memory. This chapter also describes the importance of the design for reuse techniques which can greatly decrease the time-to-market by reducing the design cycle and the manufacturing cycle.

The third chapter illustrates the background of each component of the SRGA architecture including the changes made to the original *SRGA-USC* design to adapt and implement it at the University of Tennessee. The *SRGA-UT* design retains the overall original architecture but was mostly adjusted to be able to pass the verification stages of synthesis and place and route.

The fourth chapter provides a step-by-step tutorial of an 8x8 *SRGA-UT* array. The steps will confirm the pre-synthesis RTL verification (using ModelSim), the synthesis process (using Design Compiler) and verification of the netlist (using ModelSim), and the place and route process (using First Encounter) and verification of the delay constraints (using ModelSim).

2

The fifth chapter shows the implementation of the 8x8 array sub-blocks in the same manner as the tutorial. Some blocks were small enough to be proven just by verifying the pre-synthesis RTL step.

The sixth chapter will describe the results of the *SRGA-UT* implementation and followed by the conclusion remarks and suggestions for future possibilities. The overall thesis provides a detailed documentation for a reusable design.

## **Chapter 2: Background**

### 2.1 Reconfigurable Technology

Reconfigurability denotes the potential of a system to dynamically change its behavior usually in response to changes in its environment. In the computing world, the Field Programmable Gate Arrays (FPGAs) are the most popular means of accomplishing reconfigurability. An FPGA consists of an array of programmable logic elements and programmable interconnects. The logic elements can be logic gates (AND, OR, XOR, Invert), lookup tables (memory usually RAM), or flip-flops [2]. The interconnects allow the logic elements to be connected as needed by the design.

The logic elements and interconnects can be programmed by the customer so that the FPGA can perform a certain functionality. This functionality can be reconfigured to suit new application requirements desired by the customer by writing appropriate bits into the configuration memory. The challenges with most FPGAs however, whether they are reconfigured at compile time or runtime, is that they require an external source to execute the reconfiguration.

A device, that is capable to generate configuration bits at runtime and use them to modify its own configuration, exhibits self-reconfiguration. A selfreconfigurable device needs to be able to store multiple contexts of configuration information and context switch between them. The configured logic should be able to access any of the contexts of information stored and perform selfreconfiguration by modifying the contents of the information stored. When the configured logic has made the modifications to the configuration information, the device should be able to switch context to any of the contexts of configuration stored. For an efficient self-reconfiguration to occur, the device should be able to configure logic to perform: (1) fast context switching and (2) fast random access of the configuration information stored. The *SRGA-USC* [1] was designed to perform the fast context switching and fast random access of the configuration stored in one clock cycle. The *SRGA-USC* is capable of storing eight contexts of configuration information (this number is editable).

Another device that is capable of storing four contexts of configuration information on-chip and switch between them on a clock cycle basis is the Sanders CSRC [3]. This device can also load configurations while other contexts are active. Despite the fast switching and loading capabilities, it only provides serial configuration memory access which can take hundreds of clock cycles to access a particular location. The Berkeley HSRA [4] is capable of accessing the configuration information in a fast manner but it takes hundreds of clock cycles to switch context.

#### 2.2 Design Reuse

Time-to-market is a crucial aspect for the survival of many IC manufacturing companies in such a competitive environment. Time-to-market may be optimized by reducing the design cycle and by reducing manufacturing cycle. The design cycle may be greatly reduced and the quality of the designs may be increased by providing designs with reuse [5]. IP (intellectual property) blocks such as configurable I/O (input/output), power and ground grids, block RAMs (random access memories), and timing generators were some of the first blocks created for reuse as sub-designs in larger projects such as SoCs (system-on-chips). If a sub-design were to be developed from scratch, it would take a lot more time than to adapt the reusable block. Figure 2.2.1 shows that without planned design reuse, the total time for development is proportional to the

Figure 2.2.1: Design for Reuse Diagram [5]

number of sub-designs, given that each module has the same complexity. During development with planned design reuse, the designer will spend more time in creating a reusable block by providing comprehensive documentation and more adaptable interface.

The design for reuse techniques are closely studied in today's SoC development. A basic combination of such reusable features is known as a platform. The platform used to implement a SoC greatly impacts all of the issues and is the fundamental decision the hardware designers must make at the start of each new project. By 2010 the percentage of IP contained in a System-on-Chip application is predicted to grow to 95% [6].

One of the goals for this thesis is to end up with a *SRGA-UT* design for reuse, accessible with a step-by-step tutorial and comprehensive documentation.

## 2.3 SRGA-USC

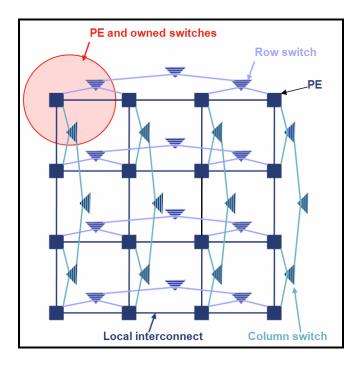

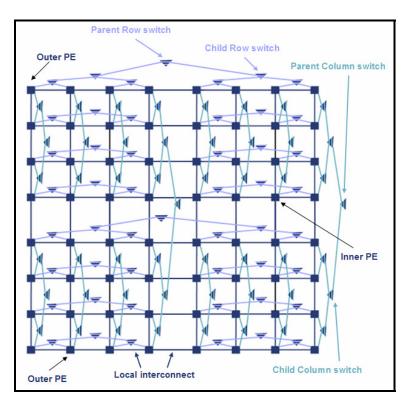

The original Self-Reconfigurable Gate Array Architecture [1] is an open core design implemented by the Department of EE-Systems at University of Southern California and the Department of Mathematics at the University of Trento (Italy). The reconfigurable device allows single cycle context switching and single cycle random access to the unified on-chip memory which stores the configuration data. Both features are necessary for efficient self-reconfiguration. The context switching feature permits arbitrary regions of the chip to selectively switch context. The memory access feature allows data transfer between logic cells and memory locations as well as between memory locations. A mesh of trees based interconnects with logic cells and memory blocks at the leaf nodes and identical switches at the other nodes make it possible to perform the above features. Figure 2.3.1 shows the basic SRGA architecture of a 4x4 array of PEs.

The architecture can be of any N x N array of PEs. The PE sits at the leaf node of the mesh of trees interconnects and is composed of a logic cell, memory block, and memory interface. Each switch is identical except that some switches are connected in a column mesh network and some are connected in a row mesh network. Each PE is connected to a row switch and a column switch.

Figure 2.3.1: SRGA Architecture

The connection between the PEs through the switches is configured using two methods. The first method serves the same purpose as the interconnection network in a typical FPGA, connecting together the logic cells as specified by the configuration bits controlling the network switches. The second method is used for performing data transfer during the memory access operations. For this method, only one wire that carries signals in either direction is used for each connection.

The logic cell of each PE can connect directly to the four neighbor's logic cells. Fore example, the south output of a PE will become the north input of the neighbor PE directly to the south of the original PE – and/or – the east output of a PE will become the west input of the neighbor PE directly to the east of the original PE.

The SRGA contains three global registers – their contents are broadcast to all PEs, and four periphery registers – located along the boundary of the N x N PE array. The purpose of the global registers is to specify – the operation to be initiated, the source and destination of the data, and the context to switch to or the memory address to be accessed. The purpose of the periphery registers is to control which rows or columns will be the source or destination during the different functionalities. See section 3.2 for a more detailed description of the registers.

The Memory block stores the different configuration words which are 77 bits long each. During a memory access operation, the contents of the configuration words can be transferred between rows or between columns. All memory access operations complete in a single clock cycle. The operation can be a memory read (memory to logic cells), memory write (logic cells to memory), or memory transfer (memory to memory) depending on the contents of the global registers. The memory interface generates the proper inputs to the memory block and to some extent to the logic cell by taking the register signals and combining them through basic logic gates to create the appropriate signals.

## **Chapter 3: Component Background**

#### 3.1 Components Overview

This chapter will describe in details the structure of each component of the *SRGA-UT*, which includes the changes made to the original *SRGA-USC* design. The changes, which will be pointed out throughout the next three chapters, were necessary for the design to be adapted and able to implement using the available EDA tools. The *SRGA-UT* design retains the overall original architecture but was mostly adjusted to be able to pass the verification stages of presynthesis, synthesis and place and route.

The *SRGA-UT* architecture consists of an array of N x N array of PEs. The PE sits at the leaf node of the mesh of trees interconnects and is composed of a logic cell, memory block, and memory interface (described later in this chapter). Each switch is identical except that some switches are connected in a column mesh network and some are connected in a row mesh network. Each PE is connected to a row switch and a column switch.

The N x N array of PEs is configured by inputting configuration contexts (described in section 3.3) into the memory array of each PE – which can store eight contexts of configuration. Once the memory is loaded, the *SRGA-UT* can switch context and perform memory operations in a single clock cycle. This is done through a number of global and periphery registers.

### 3.2 Registers

The *SRGA-USC* contains three global registers and four periphery registers. The memory interface module takes signals from the registers and creates the internal signals *wrMem*, *WrLog*, *switchContext*, *data\_In*, *Rmi*, and *Cmi*. These signals are used to perform context switching and memory operations.

The three global registers are the Operation Register (OR), the Memory Operation Register (MOR), and Context and Memory Address Register (CMAR). OR seen in figure 3.2.1 (a) is a 2-bit register that specifies what operation will be initiated in the next clock cycle. MOR seen in figure 3.2.1 (b) is a 2-bit register that specifies the source and destination of the data transfer for the next clock cycle when OR indicates memory access. Note: The order of the OR and MOR bits were changed in the figure bellow for consistency with the verilog code. CMAR, depending on the OR contents, specifies the context to switch to or the memory address to be accessed in the next clock cycle. CMAR consists of two fields: (1) the context field and (2) the offset field. The context field points to the memory column to be accessed. In testing this design, *nc* equals eight (8), the number of memory verilog files found in the /srga/tools/rtl/mem/ directory.

| OR[0] | OR[1]                      | Operation                   |     |  |  |  |  |  |  |  |  |

|-------|----------------------------|-----------------------------|-----|--|--|--|--|--|--|--|--|

| 0     | 0                          | No operation                |     |  |  |  |  |  |  |  |  |

| 0     | 1                          | Context switch              |     |  |  |  |  |  |  |  |  |

| 1     | 0                          | Row memory access           |     |  |  |  |  |  |  |  |  |

| 1     | 1 1 Column memory access   |                             |     |  |  |  |  |  |  |  |  |

|       |                            | (a)                         |     |  |  |  |  |  |  |  |  |

| MOR[  | 0][MO                      | R[1] Source and destination | m   |  |  |  |  |  |  |  |  |

| 0     | (                          | ) Memory to memory          |     |  |  |  |  |  |  |  |  |

| 0     | 1                          | I Memory to logic (real     | ud) |  |  |  |  |  |  |  |  |

| 1     | 1 0 Logic to memory (write |                             |     |  |  |  |  |  |  |  |  |

| 1     | 1                          | l Logic to logic            |     |  |  |  |  |  |  |  |  |

|       |                            | (b)                         |     |  |  |  |  |  |  |  |  |

Figure 3.2.1: OR and MOR Registers

The size of the context field can be calculated as:  $(2^{\chi} = nc)$  where X is the context field number of bits which equals to 3  $(2^3 = 8)$ . The offset field points to the memory row to be accessed. In the design, *cs* equals eighty (80), the number of output bits from the *Row Demux* (see memory cell section 3.5). The first seventy-seven (77) bits of *cs* are the number of rows for the memory array. *cs* can also be defined as the number of bits required to configure a logic cell and its two owned switches. Each memory array block consists of *nc* x *cs* bits.

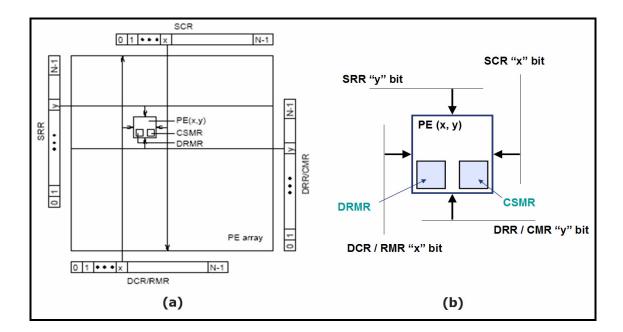

The four periphery registers are SCR, SRR, DCR/RMR, and DRR/CMR, shown in figure 3.2.2 (a) and (b). All the periphery registers are N bits long to match the size of the N x N array of PEs.

SCR (Source Column Register), a set bit implies that the corresponding PE column will be the source for the next column memory access.

SRR (Source Row Register), a set bit implies that the corresponding PE row will be the source for the next row memory access.

DCR/RMR (Destination Column Register)/(Row Mask Register), a set bit implies that the corresponding PE column will be the destination for the next memory access – or – during a row memory access, no data will be transferred for the corresponding column.

DRR/CMR (Destination Row Register)/(Column Mask Register), a set bit implies that the corresponding PE row will be the destination for the next memory access – or – during a column memory access, no data will be transferred for the corresponding row.

Each PE also contains two memory mapped registers CSMR and DRMR to give the design more flexibility. CSMR (Context Switch Mask Register), a set bit will not allow the corresponding PE to switch context even when a context switch operation occurs. DRMR (Data Restore Mask Register), a set bit prevents the corresponding flip-flop contents from being restored when a context switch operation occurs.

## 3.3 Configuration Word

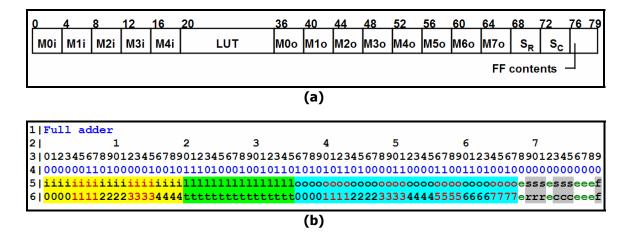

The configuration word that is loaded to the memory array is 80-bit long. Figure 3.3.1 (a) and (b) shows the format of the configuration word. The word is composed of: select 4-bit input for five input muxes (M0i to M4i), configuration 16-bit input for the LUT, select 4-bit input for eight output muxes (M0o to M7o), select 4-bit input for the row switch ( $S_R$ ), select 4-bit input for the column switch ( $S_C$ ), and four bit contents of the FF.

For testing, different configuration word files were created and stored in the /srga/config\_files/ directory, and called by the test-bench of each module.

Figure 3.3.1: Configuration Word Format (a) Diagram and (b) From Configuration File

Note: Only three bits  $S_R[69:71]$  and  $S_C[73:75]$  are used for the switches, and only one bit *FF*[79] is used for the flip-flop. Part (a) of the figure 3.3.1 was edited to be consistent with the configuration word format from the verilog code.

The four input muxes M0i to M3i generate the select bits for the LUT. For a detailed illustration of how the LUT works, refer to section 3.4. To test this design, 16-bit configuration words were created for a full adder and a full subtractor. The format of the LUT configuration is demonstrated in figure 3.3.2 and figure 3.3.3. It can be seen that the output of the truth table forms the configuration bits for the LUT.

The LUT can perform two boolean functions of three inputs and one output each and one boolean function of four inputs and one output. The truth tables are color coded to show how the configuration for the LUT must be applied. A binary and hexadecimal number format is shown which will be useful when generating the ModelSim simulations.

| Carry-In<br>bit | Input bit | Input bit | Carry-<br>Out bit | Sum bit |                      |                            |         |                |       |

|-----------------|-----------|-----------|-------------------|---------|----------------------|----------------------------|---------|----------------|-------|

| L2i             | L1i       | L0i       | L1o               | L0o     |                      |                            |         |                |       |

| 0               | 0         | 0         | 0                 | 0       |                      |                            |         |                |       |

| 0               | 0         | 1         | 0                 | 1       |                      | Carry-                     | Out bit | Sun            | n bit |

| 0               | 1         | 0         | 0                 | 1       |                      | -                          | 10      | L              | )o    |

| 0               | 1         | 1         | 1                 | 0       | Binary<br>Format     | 1110                       | 1000    | 1001           | 0110  |

| 1               | 0         | 0         | 0                 | 1       |                      |                            |         |                |       |

| 1               | 0         | 1         | 1                 | 0       | Hex Format           | е                          | 8       | 9              | 6     |

| 1               | 1         | 0         | 1                 | 0       | LUT<br>Configuration | lutconfig[15:8]            |         | lutconfig[7:0] |       |

| 1               | 1         | 1         | 1                 | 1       | word                 | lateornig[10.0] lateornig[ |         |                |       |

|                 |           | (a)       |                   |         |                      | (b)                        | )       |                |       |

Figure 3.3.2: Full Add Configuration (a) Truth Table (b) LUT

| Borrow-<br>In bit | Input bit | Input bit | Borrow-<br>Out bit | Difference<br>bit |    |                      |                 |       |        |                |  |  |

|-------------------|-----------|-----------|--------------------|-------------------|----|----------------------|-----------------|-------|--------|----------------|--|--|

| L2i               | L1i       | L0i       | L1o                | L0o               |    |                      |                 |       |        |                |  |  |

| 0                 | 0         | 0         | 0                  | 0                 |    |                      |                 |       |        |                |  |  |

| 0                 | 0         | 1         | 0                  | 1                 | 11 |                      | Borro           | w-Out | Diffe  | rence          |  |  |

| 0                 | 1         | 0         | 1                  | 1                 |    |                      | L1o             |       | L0o    |                |  |  |

| 0                 | 1         | 1         | 0                  | 0                 |    | Binary<br>Format     | 1101            | 0100  | 1001   | 0110           |  |  |

| 1                 | 0         | 0         | 1                  | 1                 |    |                      |                 |       |        |                |  |  |

| 1                 | 0         | 1         | 0                  | 0                 |    | Hex Format           | d               | 4     | 9      | 6              |  |  |

| 1                 | 1         | 0         | 1                  | 0                 |    | LUT<br>Configuration | lutconfig[15:8] |       | lutcon | lutconfig[7:0] |  |  |

| 1                 | 1         | 1         | 1                  | 1                 |    | word                 |                 |       |        |                |  |  |

|                   |           | (a)       |                    |                   | -  |                      | (b              | )     |        |                |  |  |

Figure 3.3.3: Full Subtract Configuration (a) Truth Table (b) LUT

## 3.4 Logic Cell

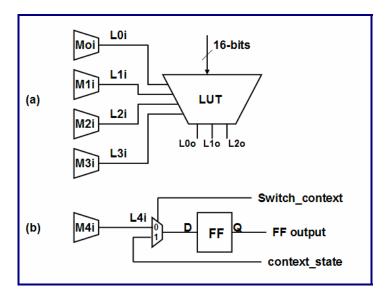

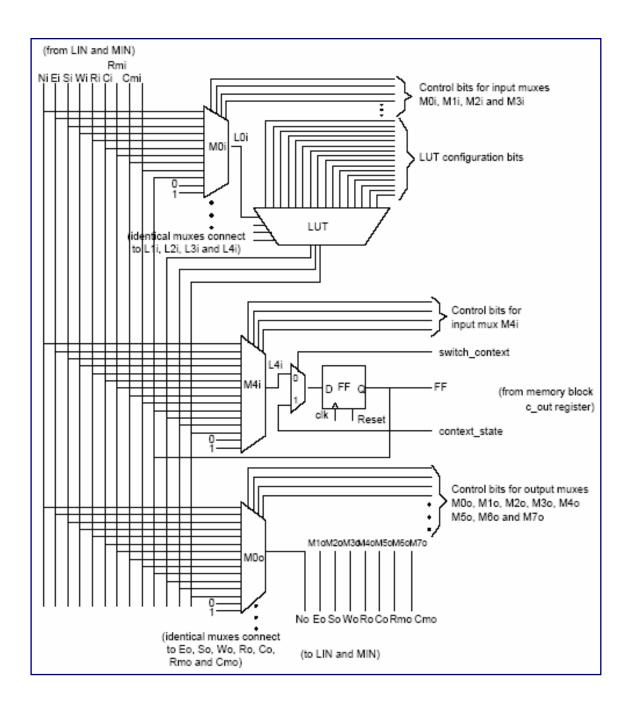

The logic cell block shown in figure 3.4.2 consists of a 16-bit LUT, a Flip-Flop (FF), five input muxes (M0i, M1i, M2i, M3i, and M4i), and eight output muxes (M0o, M1o, M2o, M3o, M4o, M5o, M6o, and M7o). The input muxes (M0i, M1i, M2i, and M3i) are used to generate the four control bits *(L0i, L1i, L2i, and L3i)* for the LUT. See also figure 3.4.1 (a). The input mux M4i generates the signal *(L4i)*, the input to the Flip-Flip when the Switch\_context signal is '0'. When the Switch\_context signal is '1', the context\_state is the input to the Flip-Flop. See also figure 3.4.1 (b).

The LUT can perform two boolean functions of three inputs and two outputs or one boolean function of four inputs and one output. As can be seen from the logiccell.v section in figure 3.4.3, the mux8  $u_lut0$  and  $u_lut1$  instances will perform the two boolean functions of three inputs and two outputs.

f(L0i, L1i, L2i) = L00f(L0i, L1i, L2i) = L10

Figure 3.4.1: (a) LUT Structure and (b) Flip-Flop Structure

Figure 3.4.2: Logic cell Structure [1]

```

assign sel lut0 = {li2,li1,li0};

assign sel_lut1 = {li2,li1,li0};

assign sel lut2 = li3;

assign lutconfig0 = lutconfig[7:0];

assign lutconfig1 = lutconfig[15:8];

mux8 u lut0 (.sel

(sel lut0),

.dataIn

(lutconfig0),

.dataOut (100));

mux8 u lut1 (.sel

(sel lut1),

(lutconfig1),

.dataIn

.dataOut (lo1));

mux2 u lut2 (.Y

(102),

. A

(100),

.B

(101),

. SO

(sel lut2));

```

Figure 3.4.3: Internal Functions of the LUT

The instance *u\_lut2* of mux2 takes the signals *L0o* and *L1o* and generates the output *L2o* depending on the state of *Li3*. This is the internal function of the LUT that performs the one boolean function of four inputs and one output.

f (L0i, L1i, L2i, L3i) = L2o

The signal *L0i* from figure 3.4.2 is equivalent to li0 from figure 3.4.3. The same applies to *L1i*, *L2i*, *L3i*, *L0o*, *L1o*, and *L2o*.

The inputs to the PE *(Ni, Ei, Si, Wi, Ri, Ci, Rmi, Cmi)* are grouped together in the *logiccell.v* module to form the 8-bits *inBus* set of wires. See figure 3.4.4. The 16-bits *inMuxBus* is the set of wires which groups together the *inBus, lo3* (the output Q from the Flip-Flop), and other strategically placed ones and zeros.

inMuxBus[15:0] = {1, 0, lo3, 0, 0, 0, 0, 0, inBus} inMuxBus[15:0] = {1, 0, lo3, 0, 0, 0, 0, 0, Cmi, Rmi, Ci, Ri, Wi, Si, Ei, N}

| <pre>assign inBus = {cmi, rmi, ci, ri, wi, si, ei, ni};<br/>assign inMuxBus = {1'b1, 1'b0, lo3, 5'b0, inBus};<br/>assign outBus = {lo2, lo1, lo0, 2'b0, inBus};<br/>assign outMuxBus ={1'b1, 1'b0, lo3, outBus};<br/>(a)</pre> |                                                             |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|

| Binary a<br>Decimal nu                                                                                                                                                                                                         |                                                             | 1111 | 1110 | 1101 | 1100 | 1011 | 1010 | 1001 | 1000 | 0111 | 0110 | 0101 | 0100 | 0011 | 0010 | 0001 | 0000 |

| for the cor<br>bits of each                                                                                                                                                                                                    | 13                                                          | 12   | 11   | 10   | 9    | 8    | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |      |      |      |

| inMuxBus[                                                                                                                                                                                                                      | inMuxBus[15:0] 1 0 lo3 0 0 0 0 0 Cmi Rmi Ci Ri Wi Si Ei I   |      |      |      |      |      |      |      |      | Ni   |      |      |      |      |      |      |      |

| outMuxBus                                                                                                                                                                                                                      | outMuxBus[15:0] 1 0 103 L20 L10 L00 0 0 Cmi Rmi Ci Ri Wi Si |      |      |      |      |      |      | Si   | Ei   | Ni   |      |      |      |      |      |      |      |

|                                                                                                                                                                                                                                |                                                             |      |      |      |      |      | (    | (b)  |      |      |      |      |      |      |      |      |      |

Figure 3.4.4: Input and Output Set of Wires for the Logic Cell Muxes

The *inMuxBus* is the input to each of the four input muxes M0i, M1i, M2i, and M3i. This architecture allows the flexibility to use any of the signals in the *inMuxBus* to become the control bits *L0i*, *L1i*, *L2i*, and *L3i* for the LUT. This is done by the control bits for the input muxes which come from the configuration words. For example, the input *Ni* can be the output for all the muxes (including output muxes discussed later in this section) if the control bits from the configuration word for each mux are set to '0000'.

The 13-bits *outBus* is the set of wires which groups together the *inBus*, the outputs from the LUT (*L0o*, *L1o*, and *L2o*), and other strategically placed zeros.

outBus[12:0] = {L20, L10, L00, 0, 0, inBus}

The 16-bits *outMuxBus* is the set of wires which groups together the *outBus*, *lo3* (the output Q from the Flip-Flop), and other strategically placed ones and zeros.

outMuxBus[15:0] = {1, 0, lo3, outBus} outMuxBus[15:0] = {1, 0, lo3, L2o, L1o, L0o, 0, 0, Cmi, Rmi, Ci, Ri, Wi, Si, Ei, Ni} The *outMuxBus* is the input to the input mux M4i and to the output muxes (M0o, M1o, M2o, M3o, M4o, M5o, M6o, and M7o). In this manner any of the signals in the *outMuxBus* can become the output for the muxes depending on the control bits from the configuration word.

The complete flexibility in configuring connections allows the LUT and Flip-Flop to be used while other signals are routed through the logic cell – to perform operations as inputs for other PEs.

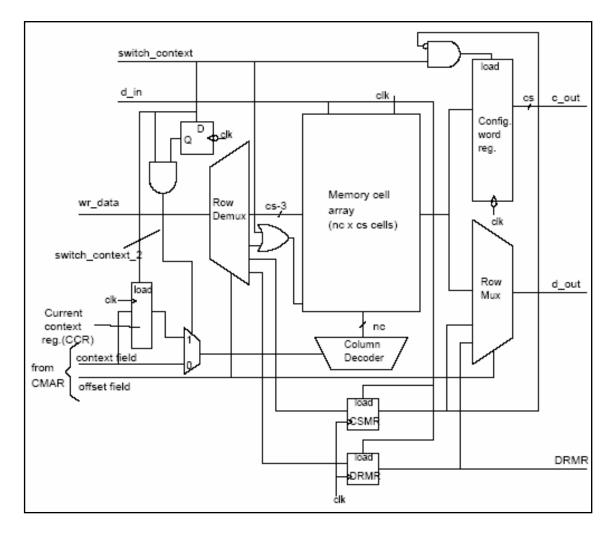

#### 3.5 Memory Cell

The memory block shown in figure 3.5.1 consists of a memory cell array, a row decoder, a column decoder, three current context registers (CCR) with three context field muxes, a configuration word register, and a data-out row mux. The memory cell array block *(memArray.vhd)* was redesigned to reduce the number of instances. The original memory array block *(memArray.v)* instantiated seventy-seven (77) sub-blocks of *storageCellRow*. The *storageCellRow* block then instantiated eight (8) *storageCell* sub-blocks which also contains other instances. When used with the 8x8 array of PEs, the large number of instances for the design would surpass the allocated amount of files allowed in a folder. This happens when running the synthesis of the 8x8 array. The new *memArray.vhd* block was created with one instance *memArray*, and also by using the mixed compile method, the design was successfully synthesized.

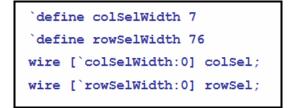

The memory cell array is internally arranged as a *nc* columns of *cs* storage cell rows. The *nc* and *cs* can be edited in the module *memArray.vhd* to become any memory array size as seen in figure 3.5.2. In this design the size of nc = 8 [*colSelWidth* to 0] and the size of *cs* = 77 [*rowSelWidth* to 0].

Figure 3.5.1: Memory Block Structure [1]

Figure 3.5.2: Defining the Size of the Memory Array

Each column can store a configuration word in this case 77-bits long, thus the memory array can store eight different configuration words. In testing the 8x8 array, only four (4) configuration contexts are used thus leaving the last four columns of memory vacant in each PE. By editing this in the future, the number of gates in each PE will be reduces by about one third.

The row decoder  $u_rowdecode$  is instantiated in the *memcell.v* and it selects the row to write the data to. The column decoder  $u_coldecode$  is instantiated in the *memcell.v* and it selects the column to write data to. The row decoder and column decoder together select a specific memory cell to be accessed.

The three CCRs, *u\_10EDFFTRX1*, *u\_11EDFFTRX1*, *u\_12EDFFTRX1*, and the three context field muxes *u31\_MX2X1*, *u32\_MX2X1*, *u33\_MX2X1*; are instantiated in the *memcell.v.* Their functionality is to perform a context switch operation in a single clock cycle. This is done as follows: At the positive edge which marks the beginning of the next clock cycle, the CMAR and OR contents are registered and broadcast to all the memory blocks. In each memory block, in the first half of the clock cycle, the new configuration is loaded into the configuration word register (for details refer to figure 3.5.1 above) when *switch\_context* is "1" and *switch\_context\_2* is "0" *(swith\_context\_2* is *switchContextHalf* in *memcell.v)*. In this manner, the context field of CMAR gets applied to the column decoder thus selecting the memory column to place the new configuration. At the negative edge of the clock cycle, the new configuration word gets loaded into the configuration word register and ready to be used.

The configuration word register *u\_reg\_77bnlr* is instantiated in the *memcell.v* and it loads and stores the configuration word from the memory array that is selected by the column decoder. This is done internally in the *memArray.vhd*.

When a switch context occurs, the load signal to the configuration word register will enable the new selected memory column to be loaded in a single clock cycle.

The output of the configuration word register sends the 16-bit configuration to the LUT, the control 4-bit configuration to each of the logic cell muxes, the configuration bits for the switches, and the signal to the Flip-Flop for the generation of the context state.

The data-out row mux *u\_mux80* is instantiated in *memcell.v* and it performs the bit transfers during memory operations. The offset field signal will select the memory bit (row) of the currently used configuration word (memory column). In this manner a single memory cell can be transmitted to another memory block to change its configuration. The signals CSMR and DRMR are inputs to the data-out row mux and can also be accessed through memory operations.

## 3.6 Switch Structure

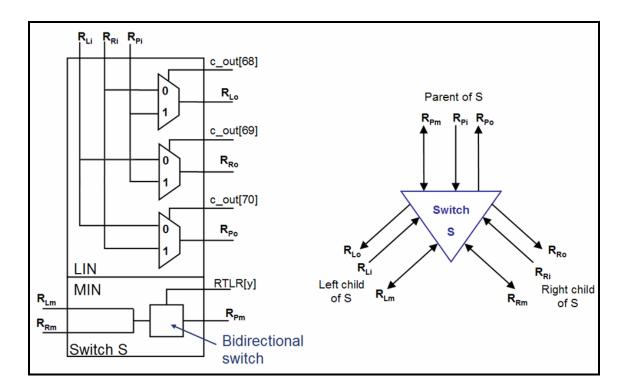

The switch is the most important part of the mesh of trees network because the switches together with connecting wires create the mesh network. Each PE is connected to one row and one column switch. The row and column switches are identical. Each switch is connected to two child nodes and a parent node where the child nodes can be other switches or PEs. The switch shown in figure 3.6.1 is composed of two parts: (1) the Logic Interconnection Network (LIN) and (2) the Memory Interconnection Network (MIN).

The LIN is composed of three muxes with select inputs ( $c_out[68]$ ,  $c_out[69]$ , and  $c_out[70]$  for the row switch, and  $c_out[72]$ ,  $c_out[73]$ , and  $c_out[74]$  for the column switch) coming from the configuration word.

Figure 3.6.1: Switch Structure

This setup allows any input to be connected to any output without restrictions except connecting an input to its output pair. This way a signal is not routed back where it came from.

The MIN part is composed of a bidirectional tri-state circuit where the wires connected to it can flow signals in both directions. In this manner, by opening all switches at a particular network level, a memory tree can be divided into multiple smaller trees. The wires from the child connections  $R_{Lm}$  and  $R_{Rm}$  are connected together thus any signal coming from any parent or child node will be transmitted to all nodes. The tri-state circuit will determine which way the signal flows.

Note: The schematic connections to the LIN muxes were changed in the schematic above (from the original) to be consistent with the verilog code.

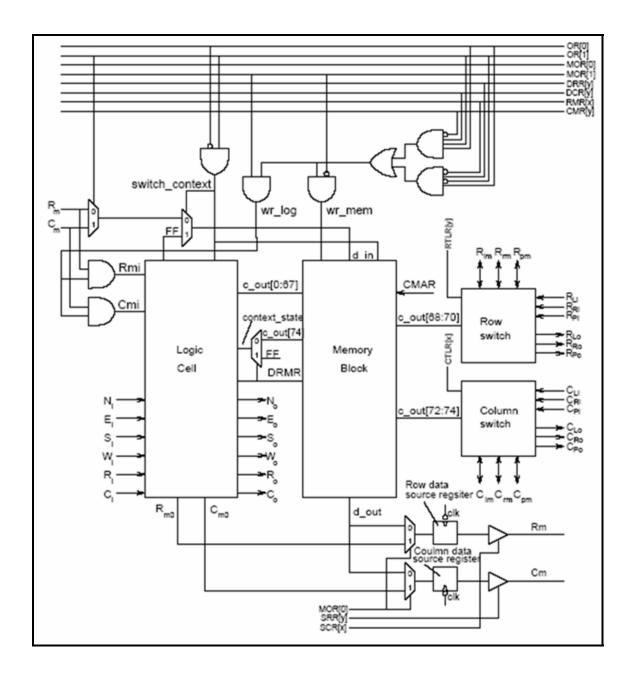

#### 3.7 PE Structure

The PE block shown in figure 3.7.1 consists of a logic cell, a memory cell, a memory interface, a row switch, and a column switch. At this level all the modules are connected together and all the inputs and outputs to all the modules, including registers will go through the PE. The register signals are processed by the memory interface which will create the internal signals *wrMem*, *WrLog, switchContext, data\_In, Rmi,* and *Cmi.* These signals are used to perform context switching and memory operations.

The logic cell connections through the PE are: The LIN nearest neighbors' connections (inputs *Ni, Ei, Si, Wi*, and outputs *No, Eo, So, Wo*). The mesh network connections (inputs *Ri, Ci, Rmi, Cmi*, and outputs *Ro, Co, Rmo, Cmo*).

Configuration bits from the memory cell (configuration word register) are connected through  $c_out$  (*cOut* in the RTL code) to the select bits for the logic cell's muxes and input to the LUT. Also, configuration bits are passed to the row and column switches.

The inputs and outputs *Cm* or *Rm* are connected together. This setup indicates the bidirectional connectivity with the MIN part of the switch. If the direction is input to PE, the *Cm* or *Rm* will be input signals shown on the upper left-hand side of figure 3.7.1. If the direction is output from PE, the *Cm* or *Rm* will be output signals shown on the lower right-hand side of figure 3.7.1. The test-bench inputs data for the configuration word file to the PE (logic cell and memory cell) through one of the inputs *Cm* or *Rm* depending whether a column or row operation is expected.

Figure 3.7.1: PE Structure [1]

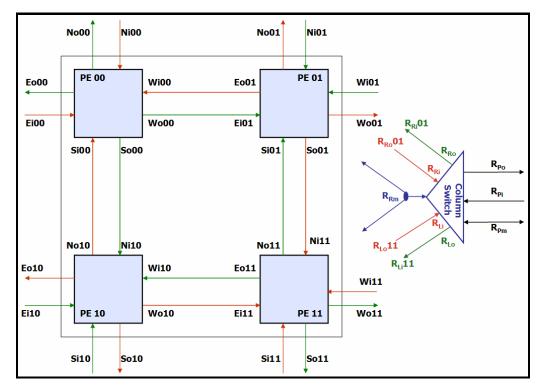

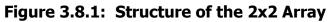

#### 3.8 2x2 Array

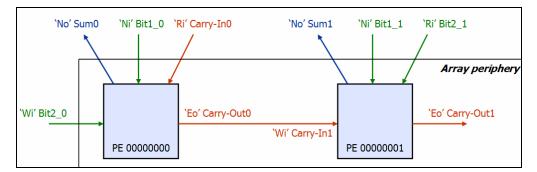

The 2x2 array module shown in figure 3.8.1 consists of four instances of the PE block. Note: Only one column switch is shown for a clearer diagram. The four instances are *u00\_pe*, *u01\_pe*, *u10\_pe*, and *u11\_pe*, which are joined together in the *array2x2.v* file. Each PE is connected to one row switch and one column switch. The external connections such as *No00*, *Wi01*, *Rpm*, will become the inputs and outputs to the 2x2 array while the internal interconnects such as *Wo00* will become *Ei01*. The other I/O to the design are the three global registers (OR, MOR, CMAR), and four periphery registers.

#### **3.9** 8x8 Array

The 8x8 array block shown in figure 3.9.1 consists of four instances of the 4x4 array. The four instances are *u00\_array4x4*, *u01\_array4x4*, *u10\_array4x4*, and *u11\_array4x4*, which are joined together in the *array8x8.v* file. The local interconnects for each of the 4x4 arrays are connected in the same manner that four PEs are connected together to form a 2x2 array. The same way that *Eo* for PE00 connects to the *Wi* for PE01 in a 2x2 array, *Eo* for PE00\_0101 connects to the *Wi* for PE01\_0000. For more details see the local interconnections in the *array8x8.v* file located in the /srga/tools/rtl/ directory. There are also eight row and eight column switches added to the design. In figure 3.9.1 only switches in rows one and five and columns four and eight are shown for a clearer schematic. These switches are the parent switches in the 8x8 array design. The inputs and outputs of the 8x8 array are connected to the outer PEs, parent switches, three global registers (OR, MOR, CMAR), and four periphery registers.

Figure 3.9.1: Structure of the 8x8 Array

# Chapter 4: SRGA-UT Implementation

### 4.1 SRGA-UT Overview

This chapter provides a step-by-step tutorial of an 8x8 *SRGA-UT* array. The steps will confirm the pre-synthesis RTL verification (using ModelSim), the synthesis process (using Design Compiler) and verification of the netlist (using ModelSim), and the place and route process (using First Encounter) and verification of the delay constraints (using ModelSim).

There are several new RTL designs that were created to simplify the testing of the design. The synchronous D Flip-Flip *dffsync.vhd* file, located in the /tools/rtl/logiccell/ directory, was created to replace the tsmc18 version to eliminate timing errors. The memory array *memArray.vhd* file, located in the /tools/rtl/mem/ directory, was created to replace the *memArray.v* to reduce the number of instances when synthesizing the memory cell.

In chapter 5 the implementation of the *SRGA-UT* sub-designs is described.

#### 4.2 EDA Tools

For the 8x8 array *SRGA-UT* design some of the EDA tools available at the ECE Department at University of Tennessee will be utilized to explore design alternative and enhance productivity. The EDA tools used are ModelSim from Mentor Graphics, Design Compiler from Synopsys, and First Encounter from Cadence.

The ModelSim tools were used for design testing and verification done at the pre-synthesis level (HDL designs), post-synthesis level (gate-level netlist), and post place and route level (SDF timing) [7].

The Design Compiler (dc\_shell) was used for logic synthesis, which is the process of converting a design description written in a hardware description language such as Verilog and VHDL into an optimized gate-level netlist targeting the tsmc18 libraries. The mixed compile method was used, where the top-down and bottom-up strategies are simultaneously applied [8]. The top-down compile is the most used strategy where the top-level design and all its sub-designs are compiled together. The bottom-up compile strategy compiles the sub-designs separately and then incorporates them in the top-level design. The top-level constraints are applied, and the design is checked for violations.

The Mixed compile or bottom-up methods must be used to synthesize the *SRGA-UT* design. This is because of the large number of instances present in the memory cell module. By running only the top-down approach for a design of 2x2 array and higher, the available number of files ( $\sim$ 32,000) that can be used in a folder or the amount of memory ( $\sim$ 4000M) allocated by the internal CPU for each user, will be surpassed and the synthesis will crash. The synthesis scripts can be found in the /synthesis/synopsys/ directory of each module.

First Encounter was used to generate the place and route steps, targeting the TSMC 0.18-micron technology, and extract the SDF file which contains net delays and cell delays [9]. This is done by going through a series of steps, described in section 4.4, where the netlist is transformed into the graphic design system (GDS) format for 2D layout display.

The design flow for implementing the *SRGA-UT* is shown in figure 4.2.1.

Figure 4.2.1: SRGA-UT Design Flow

# 4.3 Setting up Files

There are two files needed to setup the *SRGA-UT*: (1) the script *start-SRGA-UT* and (2) the zipped file *srga-ut.tar.gz*. The files can be obtained from Dr. Bouldin at the ECE department of the University of Tennessee. The first step is to copy the two files to the directory where the *SRGA-UT* is going to be initiated. The second step is to run the script *start-SRGA-UT*.

# » start-SRGA-UT

The script will unzip the *srga-ut.tar.gz* which will setup the folders and files in the following format.

| /srga/                   | main directory                      |

|--------------------------|-------------------------------------|

| /srga/documentation/USC/ | original project and files from USC |

/srga/documentation/UT/ /srga/config\_files/ /srga/tools/rtl/ /srga/tools/simulator/lib/ /srga/tools/simulator/logiccell/ /srga/tools/simulator/memcell/ /srga/tools/simulator/switch/ /srga/tools/simulator/PE/ /srga/tools/simulator/2x2/ /srga/tools/simulator/8x8/ SRGA-UT documentation and libraries configuration word files RTL designs (verilog and vhdl) tsmc18, synopsys, and encounter library files logic cell testing folders, scripts, and files memory cell testing folders, scripts, and files switch testing folders, scripts, and files PE testing folders, scripts, and files array 2x2 testing folders, scripts, and files array 8x8 testing folders, scripts, and files

## 4.4 8x8 Array Step-by-Step Tutorial

The file for testing the functionality of the 8x8 array block is the verilog file *test\_array8x8.v* which is located in the /srga/tools/simulator/8x8/ directory. A number of predefined configuration words are provided by the configuration file *8x8\_config\_words.cnf* located in the /srga/config\_files/ directory. Line number five in figure 4.4.1 is a configuration word taken from the configuration file and can be described as follows:

- x Eight bits from 0 to 7 are the horizontal periphery bit registers for the 8x8 array. A bit "1" selects the specific column.

- y Eight bits from 8 to 15 are the vertical periphery bit registers for the 8x8 array. A bit "1" selects the specific row.

- c Three bits from 17 to 19 are the context field from the CMAR register.

The context field selects the memory column to perform a memory access operation.

|            | 1                         | 2        | 3                       | 4          | 5                         | 6           | 7          | 8           | 9           | 10                                      |

|------------|---------------------------|----------|-------------------------|------------|---------------------------|-------------|------------|-------------|-------------|-----------------------------------------|

| 012345678  | 9012345678                | 90123456 | 5789012345              | 678901234  | 5678901234                | 5678901234  | 4567890123 | 4567890123  | 45678901234 | 15678901234567                          |

| xxxxxxxy   | ууууууу <mark>е</mark> сс | cefffff  | f <mark>00001111</mark> | 222233334  | 444 <mark>tttttt</mark> t | ttttttttt   | 0000111122 | 2233334444  | 55556666777 | 1 <mark>7</mark> errreccceeef           |

| Full adde: | r                         |          |                         |            |                           |             |            |             |             |                                         |

| 00000111   | 1111100000                | 1000000  | 000000011               | 010000010  | 0101110100                | 010010110   | 1010101101 | 0000110000  | 11001101001 | 000000000000000000000000000000000000000 |

| REGISTE    | R'S CONFIG                | URATION  | 11                      |            | N                         | EMORY ARRA  | AY CONFIGU | RATION      |             | I                                       |

|            |                           |          | <mark>iiiiiii</mark>    | liiiiiiii: | <mark>iii</mark> 1111111  | .111111111  |            | 00000000000 | 00000000000 | o <mark>e</mark> sssessseeef            |

|            |                           |          | 01234567                | 7890123456 | 7890123456                | 57890123450 | 5789012345 | 6789012345  | 67890123456 | 57890123456789                          |

|            |                           |          |                         | 1          | 2                         | 3           | 4          | 5           | 6           | 7                                       |

Figure 4.4.1: Configuration Word Format for the 8x8 Array

- e Indicates an extra bit.

- f Seven bits from 21 to 27 are the offset field from the CMAR register. The offset field selects the memory row to perform a memory access operation.

- i The five sets of four bits each from 28 to 47 are the select bits for the input muxes M0i to M4i. The first four sets of four bits from 28 to 43, select the four select bit inputs, L0i to L3i, to the LUT. The fifth set of four bits from 44 to 47, select the first input to the switch\_context mux.

- t Sixteen bits from 48 to 63 are the input bits for the LUT. In this case

"1110100010010110" in binary or "e896" in hex is the configuration for a full adder.

- o The eight sets of four bits each from 64 to 97 are the select bits for the output muxes M0o to M7o. The outputs from these muxes are No, Eo, So, Wo, Ro, Co, Rmo, and Cmo respectively. The No, Eo, So, and Wo are connected to the neighbor PEs while Ro, Co, Rmo, and Cmo are connected to the logic and memory interconnects of the owned switches.

- r Three bits from 97 to 99 are the configuration bits for the row owned switch.

- c Three bits from 101 to 103 are the configuration bits for the column owned switch.

- f One bit 107. Only bit 0 is used to configure the content of the Flip-Flop.

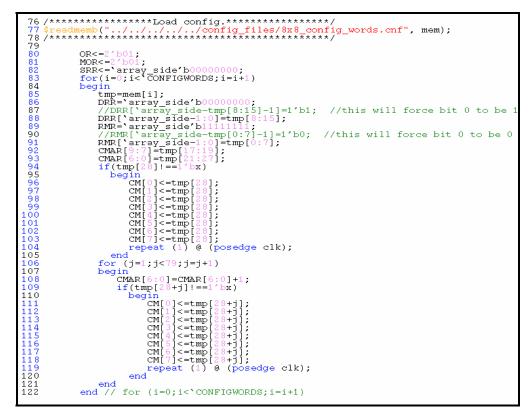

On line eight of the test-bench *test\_array8x8.v* the number of configuration words is defined (*`define CONFIGWORDS 5*). In this case, the number of *CONFIGWORDS* comes from the configuration file (*8x8\_config\_words.cnf*). Figure 4.4.2 is the section of the test-bench that takes the configuration words and distributes the different sections of each word to the 8x8 memory array and registers. Figure 4.4.3 shows the method of assigning the truth table inputs *ni*, *wi*, and *ri*, to perform the full addition and subtraction operations.

Figure 4.4.2: Importing Configuration Word Section of *test\_array8x8.v*

| 187 // |                                                                                                                                                                              |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 188 // | FULL SUBTRACTOR                                                                                                                                                              |

| 189    |                                                                                                                                                                              |

| 190    | CMAR[9:7]<=3'b010: // memory column "010" has LUT config for full adder                                                                                                      |

|        |                                                                                                                                                                              |

| 191    | repeat (1) @ (posedge clk);                                                                                                                                                  |

| 192    |                                                                                                                                                                              |

| 193    | <pre>force test_array8x8.u_array8x8.u00_array4x4.u00_array2x2.u00_pe.u_logiccell.ni=1'b0;</pre>                                                                              |

| 194    | force test array8x8.u array8x8.u00 array4x4.u00 array2x2.u00 pe.u logiccell.wi=1'b0;                                                                                         |

| 195    | force test array8x8.u array8x8.u00 array4x4.u00 array2x2.u00 pe.u logiccell.ri=1'b0;                                                                                         |

| 196    | repeat (1) @ (posedge clk);                                                                                                                                                  |

| 197    | force test array8x8.u array8x8.u00 array4x4.u00 array2x2.u00 pe.u logiccell.ni=1'b1;                                                                                         |

| 198    | force test_array8x8.u array8x8.u00_array4x4.u00_array2x2.u00 pe.u logiccell.wi=1 b);                                                                                         |

|        |                                                                                                                                                                              |

| 199    | <pre>force test_array8x8.u_array8x8.u00_array4x4.u00_array2x2.u00_pe.u_logiccell.ri=1'b0;</pre>                                                                              |

| 200    | repeat (1) @ (posedge clk);                                                                                                                                                  |

| 201    | <pre>force test_array8x8.u_array8x8.u00_array4x4.u00_array2x2.u00_pe.u_logiccell.ni=1'b0;</pre>                                                                              |

| 202    | force test array8x8.u array8x8.u00 array4x4.u00 array2x2.u00 pe.u logiccell.wi=1'b1;                                                                                         |

| 203    | force test array8x8.u array8x8.u00 array4x4.u00 array2x2.u00 pe.u logiccell.ri=1'b0;                                                                                         |

| 204    | repeat (1) @ (posedge clk):                                                                                                                                                  |

| 205    | force test array8x8.u array8x8.u00 array4x4.u00 array2x2.u00 pe.u logiccell.ni=1'b1;                                                                                         |

| 206    | force test array8x8.u array8x8.u00 array4x4.u00 array2x2.u00 pe.u logiccell.wi=1'b1;                                                                                         |

|        |                                                                                                                                                                              |

| 207    | <pre>force_test_array8x8.u_array8x8.u00_array4x4.u00_array2x2.u00_pe.u_logiccell.ri=1'b0;</pre>                                                                              |

| 208    | repeat (1) @ (posedge clk);                                                                                                                                                  |

| 209    | <pre>force test_array8x8.u_array8x8.u00_array4x4.u00_array2x2.u00_pe.u_logiccell.ni=1'b0;</pre>                                                                              |

| 210    | force test array8x8.u array8x8.u00 array4x4.u00 array2x2.u00 pe.u logiccell.wi=1'b0;                                                                                         |

| 211    | force test array8x8.u array8x8.u00 array4x4.u00 array2x2.u00 pe.u logiccell.ri=1'b1;                                                                                         |

| 212    | repeat (1) @ (posedge_clk);                                                                                                                                                  |

| 213    | force test array8x8.u array8x8.u00 array4x4.u00 array2x2.u00 pe.u logiccell.ni=1'b1;                                                                                         |

| 214    | force test array8x8.u array8x8.u00 array4x4.u00 array2x2.u00 pe.u logiccell.wi=1/b0;                                                                                         |

| 215    | force test_array8x8.u array8x8.u00_array4x4.u00_array2x2.u00 pe.u logiccell.wi=1 b);                                                                                         |

|        |                                                                                                                                                                              |

| 216    | repeat (1) @ (posedge clk);                                                                                                                                                  |

| 217    | <pre>force test_array8x8.u_array8x8.u00_array4x4.u00_array2x2.u00_pe.u_logiccell.ni=1'b0;</pre>                                                                              |

| 218    | force test array8x8.u array8x8.u00 array4x4.u00 array2x2.u00 pe.u logiccell.wi=1'b1;                                                                                         |

| 219    | force test array8x8.u array8x8.u00 array4x4.u00 array2x2.u00 pe.u logiccell.ri=1'b1;                                                                                         |

| 220    | repeat (1) @ (posedge clk);                                                                                                                                                  |

| 221    | force test array8x8.u array8x8.u00 array4x4.u00 array2x2.u00 pe.u logiccell.ni=1'b1:                                                                                         |

| 222    | force test array8x8.u array8x8.u00 array4x4.u00 array2x2.u00 pe.u logiccell.wi=1 bl;                                                                                         |

| 223    | force test array8x8.u array8x8.u00 array4x4.u00 array2x2.u00 pe.u logiccell.ri=1'bl;                                                                                         |

| 224    | Toree cest_arrayes.s.d_arrayes.uoo_arrayes.uoo_arrayes.uoo_pe.d_logicceff.fi=r_bf;                                                                                           |

|        |                                                                                                                                                                              |

| 225 // |                                                                                                                                                                              |

| 226 // | FULL ADDER - TESTING PE00000000 AND PE00000001                                                                                                                               |

| 227    |                                                                                                                                                                              |

| 228    | CMAR[9:7]<=3'b011; // memory column "011" has LUT config for full adder                                                                                                      |

| 229    | repeat (1) @ (posedge clk):                                                                                                                                                  |

| 230    |                                                                                                                                                                              |

| 231    | force test array8x8.u array8x8.u00 array4x4.u00 array2x2.u00 pe.u logiccell.ni=1'b0;                                                                                         |

| 232    | force test array8x8.u array8x8.u00 array4x4.u00 array2x2.u00 pe.u logiccell.wi=1'b0;                                                                                         |

| 233    | force test_array8x8.u array8x8.u00_array4x4.u00_array2x2.u00 pe.u logiccell.vi=1 b);                                                                                         |

| 233    | force test_arrayox0.u_arrayox0.u00_array4x4.u00_array2x2.u00_pe.u_logiccell.ri=1_b0;<br>force test_array0x8.u array0x8.u00_array4x4.u00_array2x2.u01_pe.u_logiccell.ri=1_b0; |

|        |                                                                                                                                                                              |

| 235    | force test_array8x8.u_array8x8.u00_array4x4.u00_array2x2.u01_pe.u_logiccell.ri=1'b0;                                                                                         |

| 236    | repeat (1) @ (posedge clk);                                                                                                                                                  |

|        |                                                                                                                                                                              |

Figure 4.4.3: Assigning Inputs to the 8x8 Array

Line seventy-seven stores the configuration words into a temporary system memory. The OR, MOR, and SRR registers are then setup to allow memory write. The FOR loop creates a counter for the number of configuration words and a counter for the amount of bits in a configuration word.

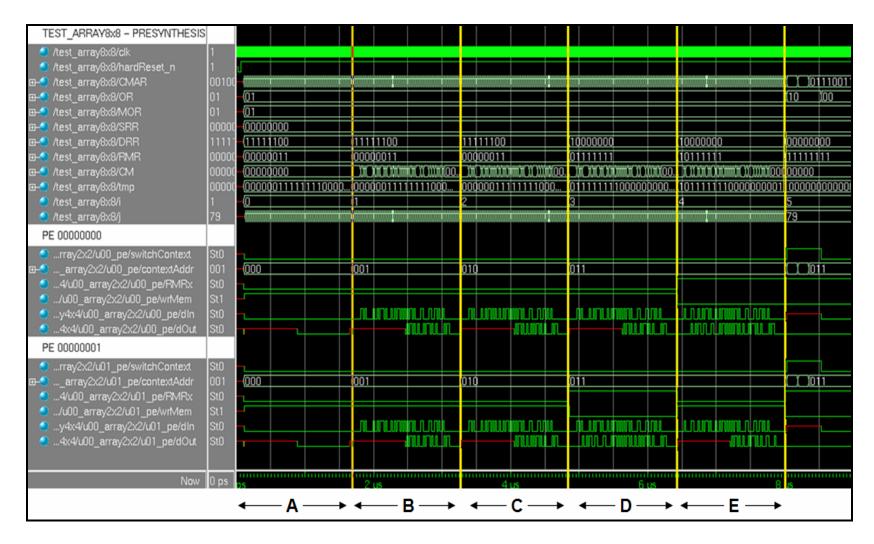

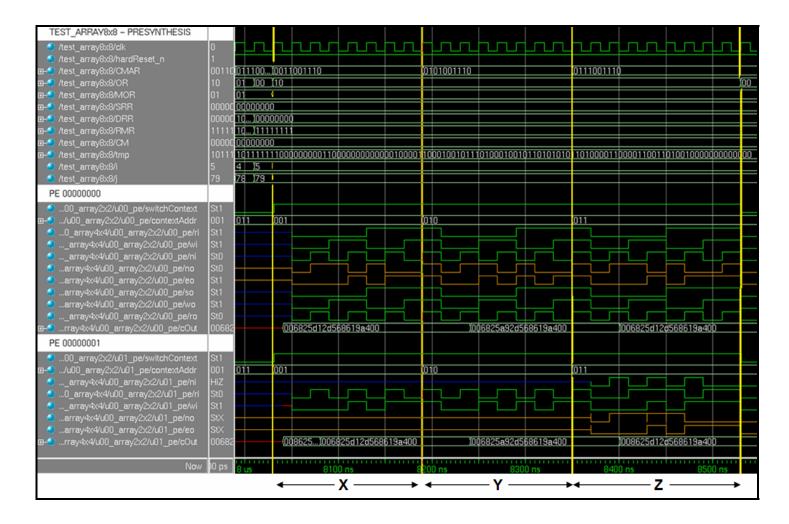

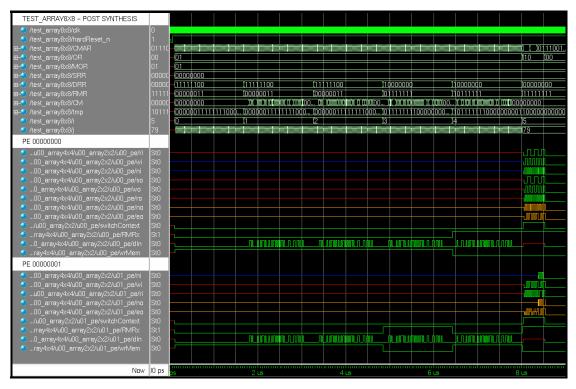

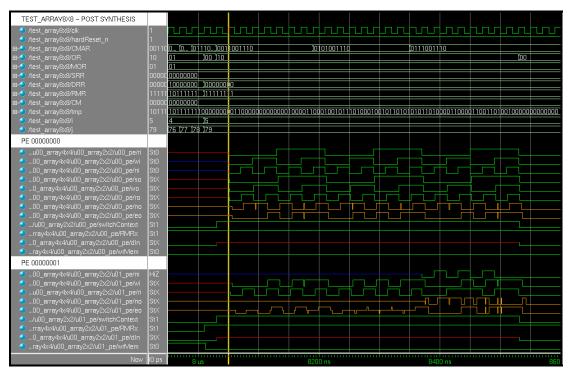

### **Array 8x8 Pre-Synthesis**

To test the RTL design using ModelSim simulation, run the script *1-presynth-8x8* by following the next steps:

- » cd /simulator/8x8/presynth/

- » 1-presynth-8x8

This will bring up the ModelSim main and wave windows. After reviewing the *test\_array8x8.v* signals in the wave window, other signals such as the *array8x8* signals can be added to the wave from the main window by highlighting the  $u_array8x8$  in the Workspace area, then right click and Add to Wave.

When the signals appear in the wave window, at the main window prompt type *restart*, then click Restart on the next window. To simulate all the signals, at the main window prompt type *run 15000000.* To load the signals from figure 4.4.4, open *presynthesis\_8x8\_load\_TB.do* from the ModelSim wave window, located in /8x8/presynth/modelsim/ directory.