# University of Tennessee, Knoxville TRACE: Tennessee Research and Creative Exchange

Masters Theses

**Graduate School**

8-2010

# Design and Implementation of Signal Processing Circuitry for Implantable Sensors

Anusha Atla aatla@utk.edu

Follow this and additional works at: https://trace.tennessee.edu/utk\_gradthes

Part of the Electrical and Computer Engineering Commons

#### **Recommended Citation**

Atla, Anusha, "Design and Implementation of Signal Processing Circuitry for Implantable Sensors." Master's Thesis, University of Tennessee, 2010. https://trace.tennessee.edu/utk\_gradthes/683

This Thesis is brought to you for free and open access by the Graduate School at TRACE: Tennessee Research and Creative Exchange. It has been accepted for inclusion in Masters Theses by an authorized administrator of TRACE: Tennessee Research and Creative Exchange. For more information, please contact trace@utk.edu.

To the Graduate Council:

I am submitting herewith a thesis written by Anusha Atla entitled "Design and Implementation of Signal Processing Circuitry for Implantable Sensors." I have examined the final electronic copy of this thesis for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Master of Science, with a major in Electrical Engineering.

Syed K Islam, Major Professor

We have read this thesis and recommend its acceptance:

Jeremy Holleman, Jayne Wu

Accepted for the Council: Carolyn R. Hodges

Vice Provost and Dean of the Graduate School

(Original signatures are on file with official student records.)

To the Graduate Council:

I am submitting herewith a thesis written by Anusha Atla entitled "Design and Implementation of Signal Processing Circuitry for Implantable Sensors." I have examined the final electronic copy of this thesis for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Master of Science, with a major in Electrical Engineering.

Syed K Islam, Major Professor

We have read this thesis

and recommend its acceptance:

Jeremy Holleman

Jayne Wu

Accepted for the Council:

Carolyn R. Hodges

Vice Provost and Dean of the Graduate School

(Original signatures are on file with official student records.)

# Design and Implementation of Signal Processing Circuitry for Implantable Sensors

A Thesis Presented for

the Master of Science

Degree

The University of Tennessee, Knoxville

Anusha Atla

August 2010

# Dedication

•

This thesis is dedicated to my parents.

### Acknowledgements

I would like to sincerely thank my advisor, Dr. Syed K. Islam for guiding me and helping me throughout my Masters program. I would like to thank my committee members Dr. Jeremy Holleman and Dr. Jayne Wu for their time and suggestions.

I would like to thank Mohammad R. Haider for his guidance and helpful advice. I would also like to thank the members of Analog VLSI and Devices Laboratory for their help in various aspects. A special thanks to Ashraf B. Islam, Kai Zhu, Melika Roknsharifi, and Salwa Mostafa for the valuable discussions I had with them.

I am thankful to my parents, Pradeep Reddy Atla and Kavitha Atla for their incessant support and unconditional love, my brother Anirudh, my grandparents, Prathap Reddy Atla and Lalitha Atla for believing in me and encouraging me.

I would like to thank all my teachers for they have helped me become a better person. It is from them that I have learnt what is right and what is wrong. I will always look up to them. I would like to thank my friends at UT, Harika and Neeharika for the wonderful time I got to spend with them, the fun trips we had, the banter we shared and much more. I will always cherish these wonderful memories. I would also like to thank my close friends Neha, my friend since middle school, Sowjanya, for making my under-graduate years so memorable and Vamshi annaya, for always being there. I would also like to thank Harshini, Shaima, Dhirender, Shambhu, Simi, Sirisha, Nithiya and all my other friends for being a part of my life.

# Abstract

Recent technological advancements in integrated circuits and medical technology have made real-time monitoring of physiological factors possible. One such important physiological factor to be measured is glucose. Continuous monitoring of glucose is extremely important for patients with diabetes as it helps make optimal treatment decisions. To enable continuous measurement, a chip containing the sensors and the electronic circuitry is implanted in the human body. This implanted chip provides for continuous measurement and helps reduce inconvenience caused to diabetic patients. A potentiostat forms an integral part of a sensor signal processing circuit. In this thesis the design and simulation of an on-chip potentiostat circuit has been presented. A potentiostat is needed to maintain a constant potential, so that the sensor can measure glucose. This design has been fabricated using a 0.35-µm bulk CMOS process available through MOSIS.

# **Table of Contents**

、

| 1 Introduction |        | 1                                           |    |

|----------------|--------|---------------------------------------------|----|

| 1.1            | Ov     | erview                                      | 1  |

| 1.2            | 2 Glu  | acose sensing implantable sensors           | 4  |

| 1.3            | B Im   | portance of continuous glucose monitoring   | 5  |

| 1.4            | l Te   | chniques for measuring blood glucose levels | 5  |

| 1              | 1.4.1  | Using invasive devices                      |    |

| ]              | 1.4.1  | Using minimally invasive devices            | 6  |

| 1              | 1.4.2  | Using non-invasive devices                  | 8  |

| 1.5            | 5 Ba   | sic Glucose-Sensor Concepts                 | 9  |

| 1              | 1.5.2  | Types of electrochemical sensors            | 11 |

| 1              | 1.5.1  | Oxidation of glucose                        | 11 |

| 1.6            | 5 Sco  | ope of the thesis                           | 12 |

| 1.7            | 7 Th   | esis organization                           | 13 |

| 2 8            | System | overview                                    | 14 |

| 2.1            | Int    | roduction                                   | 14 |

| 2.2            | 2 Ba   | nd gap Voltage Reference                    | 14 |

| 2.3            | B Po   | tentiostat                                  | 19 |

| 2.4            | l Sig  | nal Processing Block                        | 19 |

| 4              | 2.4.1  | Data Generator                              | 20 |

| 4              | 2.4.2  | Schmitt trigger                             | 22 |

| 2              | 2.4.3  | D latch                                     | 23 |

| 2              | 2.4.4  | Frequency Generator                         | 24 |

| 2.5 | 5     | Inductive link                                                  | 26 |

|-----|-------|-----------------------------------------------------------------|----|

| 3   | The   | Potentiostat                                                    | 28 |

| 3.1 | 1     | Introduction                                                    | 28 |

| 3.2 | 2     | Principle of a potentiostat                                     | 28 |

| 3.3 | 3     | Potentiostat using constant cathode potential                   | 29 |

| 3.4 | 1     | On-chip potentiostat with four op-amps                          | 31 |

| 3.5 | 5     | On chip potentiostat with a single op-amp                       | 33 |

| 3.6 | 5     | Design of the Class AB buffers                                  | 36 |

| 3.7 | 7     | Design and Simulation of the Rail to Rail Operational Amplifier | 38 |

|     | 3.7.  | Frequency Response                                              | 40 |

|     | 3.7.2 | 2 Slew Rate                                                     | 41 |

|     | 3.7.3 | Common Mode Rejection Ratio                                     | 42 |

|     | 3.7.4 | Settling Time                                                   | 43 |

| ,   | 3.7.5 | B   Rise Time                                                   | 43 |

| ,   | 3.7.0 | 5 Power Supply Rejection Ratio (PSRR)                           | 43 |

|     | 3.7.7 | Input Common Mode Range (ICMR)                                  | 44 |

| 4   | Sim   | ulation and Test Results                                        | 46 |

| 4.1 | 1     | Actual Schematics Used                                          | 46 |

| 2   | 4.1.  | Schematic of the Band gap reference circuit                     | 46 |

| 2   | 4.1.2 | 2 Schematic of Operational Amplifier                            | 47 |

| 2   | 4.1.3 | Schematic of Class AB Buffer                                    | 47 |

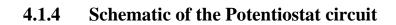

| 2   | 4.1.4 | Schematic of the Potentiostat circuit                           | 48 |

| 2   | 4.1.5 | Schematic of the data-generator circuit                         | 49 |

| 2   | 4.1.0 | Schematic of the frequency generator circuit                    | 49 |

`

| 4.2 Ac   | tual Layouts Used                                    | 50 |

|----------|------------------------------------------------------|----|

| 4.2.1    | Layout of the Band gap reference circuit             | 50 |

| 4.2.2    | Layout of Operational Amplifier                      | 51 |

| 4.2.3    | Layout of Class AB Buffer                            | 52 |

| 4.2.4    | Layout of the Potentiostat circuit                   | 53 |

| 4.3 Sin  | nulation results of schematics                       | 54 |

| 4.3.1    | Output of the potentiostat circuit                   | 54 |

| 4.3.2    | Output of the Band gap Reference Circuit             | 55 |

| 4.3.1    | Output of the Data Generator Circuit                 | 55 |

| 4.3.1    | Output of the Frequency Generator Circuit            | 56 |

| 4.4 Po   | st layout simulation results                         | 58 |

| 4.4.1    | Voltages at the reference and the working electrodes | 58 |

| 4.5 Sir  | nulation of the potentiostat with I/O pads           | 60 |

| 4.5.1    | Screenshot of the potentiostat and the pads          | 60 |

| 4.5.2    | Simulation of the potentiostat with the I/O pads     | 62 |

| 4.6 Po   | st Fabrication Test results                          | 64 |

| 4.6.1    | Microphotograph of the fabricated chip               | 64 |

| 4.6.2    | Test set-up                                          | 65 |

| 4.6.3    | Test Results                                         | 67 |

| 5 Conclu | ision                                                | 68 |

| 5.1 Th   | esis Summary                                         | 68 |

| 5.2 Fu   | ture Work                                            | 68 |

| 6 Refere | nces                                                 | 69 |

| 7 Vita   |                                                      | 72 |

、

# **Table of Figures**

`

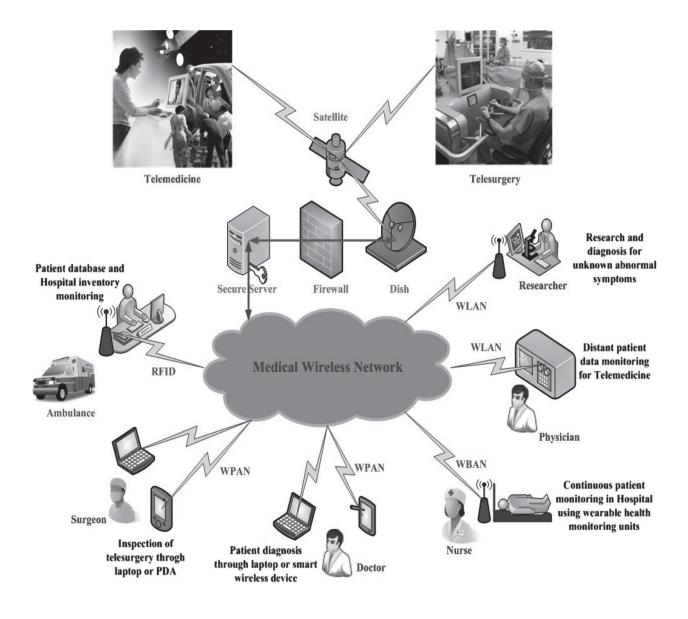

| Figure 1.1Applications of medical wireless networks [1]                                  | 3        |

|------------------------------------------------------------------------------------------|----------|

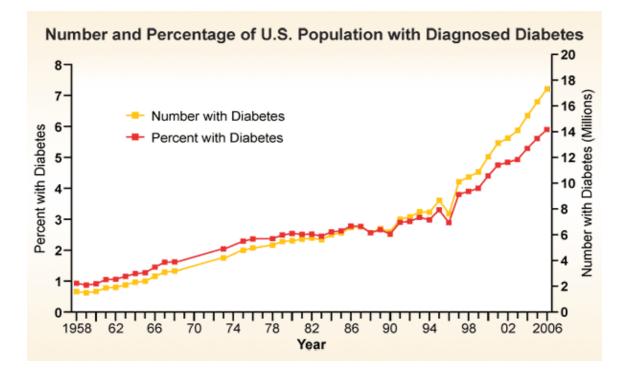

| Figure 1.2 Graph showing the percentage of people with diabetes against the year [3]     | 4        |

| Figure 1.3 Depiction of a blood glucose test using invasive devices [4]                  | 7        |

| Figure 1.4 A minimally invasive monitoring system                                        | 7        |

| Figure 1.5 A non-invasive gluco-monitoring system [6]                                    | 9        |

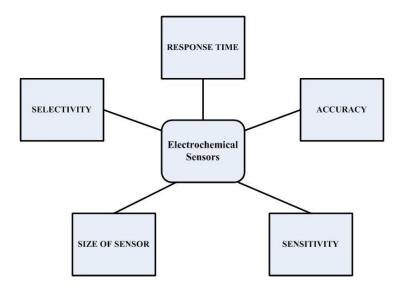

| Figure 1.6 Block diagram showing the factors affecting an electrochemical sensor         | 10       |

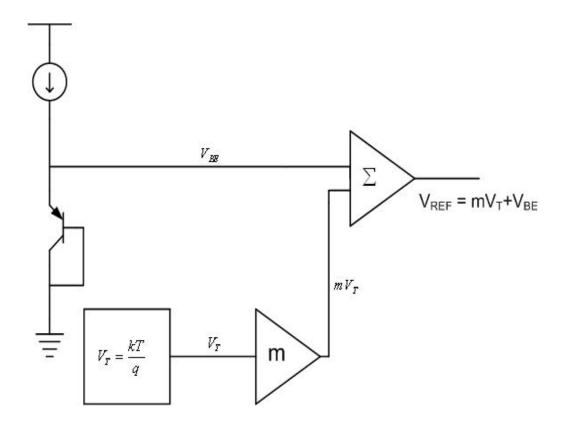

| Figure 2.1 Operating principle of the band gap reference circuit                         | 16       |

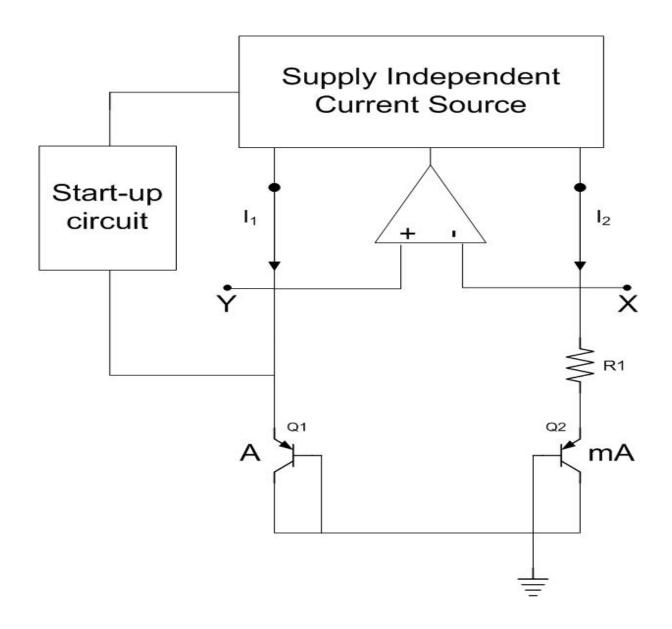

| Figure 2.2 Block diagram of a band gap reference circuit                                 | 17       |

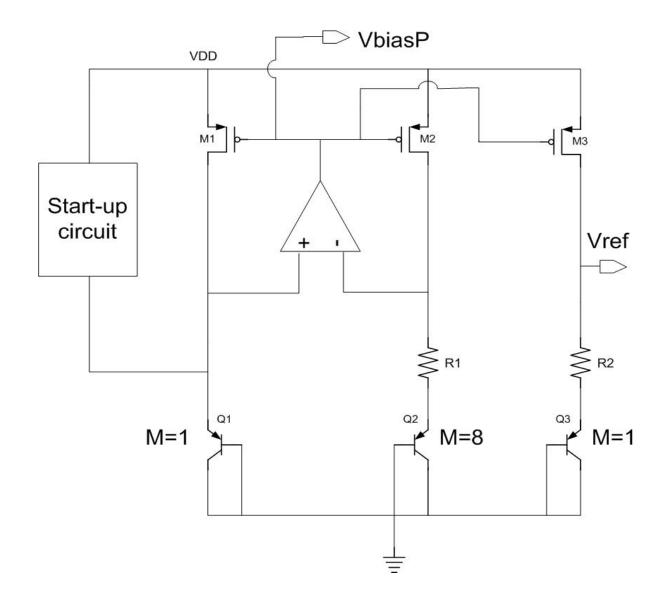

| Figure 2.3 Complete schematic of the band gap reference circuit [10]                     | 18       |

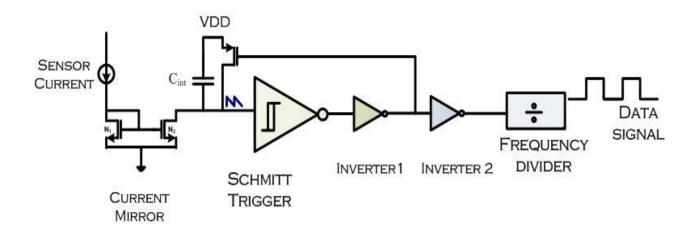

| Figure 2.4 Block diagram of a data generator                                             | 21       |

| Figure 2.5 Variation of frequency with respect to change in current obtained from the    | sensor   |

|                                                                                          | 21       |

| Figure 2.6 Schematic of a Schmitt trigger                                                | 22       |

| Figure 2.7 Block diagram of a frequency divider                                          | 24       |

| Figure 2.8 Block diagram of a frequency generator                                        |          |

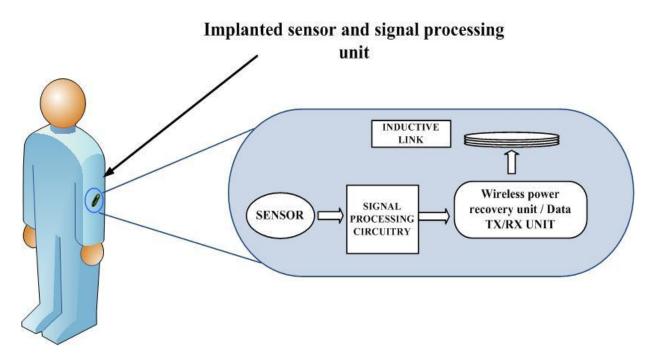

| Figure 2.9 Block diagram of an implanted sensor powered using inductive links            | 27       |

| Figure 3.1 Block diagram of a basic three electrode system                               | 30       |

| Figure 3.2 A potentiostat using a constant cathode potential                             | 31       |

| Figure 3.3 Block Diagram of the previously used potentiostat using four operational ampl | ifiers32 |

| Figure 3.4 Resistive divider used at the Band gap Reference circuit                      | 34       |

| Figure 3.5 Block diagram of the potentiostat                                             | 35       |

| Figure 3.6 Schematic of the Class AB buffer                                              | 37       |

| Figure 3.7 Rail to Rail CMOS Operational amplifier                                       | 39       |

| Figure 3.8 Schematic to measure the frequency response of an op-amp                      | 40       |

| Figure 3.9 Circuit configuration to measure Slew Rate                                    | 41       |

| Figure 3.10 Circuit configuration to measure CMRR                                        |          |

| Figure 3.11 Circuit configuration to determine PSRR                                      | 44       |

|                                                                                          |          |

| Figure 3.12 Circuit configuration to measure ICMR                                             | 45   |

|-----------------------------------------------------------------------------------------------|------|

| Figure 3.13 Simulation result showing the ICMR                                                | 45   |

| Figure 4.1 Schematic of the Band gap reference circuit                                        | 46   |

| Figure 4.2 Schematic of Operational Amplifier                                                 | 47   |

| Figure 4.3 Schematic of Class AB Buffer                                                       | 47   |

| Figure 4.4 Schematic of the Potentiostat circuit using a single op-amp                        | 48   |

| Figure 4.5 Schematic of the data-generator circuit                                            | 49   |

| Figure 4.6 Schematic of the frequency generator circuit                                       | 49   |

| Figure 4.7 Layout of the bangap reference circuit                                             | 50   |

| Figure 4.8 Layout of the operational amplifier                                                | 51   |

| Figure 4.9 Layout of the class AB buffer                                                      | 52   |

| Figure 4.10 Layout of the Potentiostat circuit                                                | 53   |

| Figure 4.11 Voltages at the Working electrode and the Reference electrode                     | 55   |

| Figure 4.12 Graph of difference in voltage across the electrodes versus the change in resista | ance |

|                                                                                               | 55   |

| Figure 4.13 Simulation result of the band gap reference circuit                               | 56   |

| Figure 4.14 Output of the Data Generator Circuit for a sensor current of 0.2µA                | 57   |

| Figure 4.15 Output of the data generator circuit for a sensor current of 2.33µA               | 57   |

| Figure 4.16 Output of the Frequency Generator Circuit                                         | 58   |

| Figure 4.17 Voltages at the Working electrode and the Reference electrode                     | 59   |

| Figure 4.18 Screenshot of the potentiostat circuit with pads                                  | 61   |

| Figure 4.19 Simulation result of the potentiostat along with the I/O pads                     | 62   |

| Figure 4.20 Graph representing the difference of voltages at the reference and the working    |      |

| electrodes with respect to the resistance of the solution                                     | 63   |

| Figure 4.21 Micro-photograph of the chip                                                      | 64   |

| Figure 4.22 Test setup of the circuit                                                         | 65   |

| Figure 4.23 Test setup of the circuit                                                         | 66   |

| Figure 4.24 Voltage at the Reference Electrode                                                | 67   |

`

# Chapter 1 Introduction

### 1.1 Overview

Technological advancements in healthcare monitoring systems and the down-scaling of CMOS technology have paved the way for many medical applications. These include continuous monitoring of physiological factors such as oxygen, glucose, lactose, pH level etc in a human body using implantable sensors, telemedicine, telesurgery etc.

This advancement in sensor electronics is highly beneficial for patients who need regular metabolic monitoring. Regular metabolic monitoring can be done using an implantable biosensor system. An implantable biosensor system converts a biologically or a chemically produced signal into an electrical signal, which is transmitted out of the body by suitable means and then monitored. Biosensors help treat the patient more effectively since any irregularities in the patient's system can be detected immediately. In addition to giving accurate data on a regular basis, these can also be particularly useful in the case of emergencies. These monitored parameters can be transmitted through a personal digital assistant (PDA) or a cell-phone to the hospital and the doctor can perform the necessary action as soon as the data is available.

The development of the concept of telemedicine along with the growth of improved and innovative wireless sensor networks has led to the application of sensor technology in the field of healthcare. Wireless sensors are creating a huge impact in the area of healthcare because of their ease of accessibility to patients and healthcare professionals. They help provide real-time response results as well as access to the laboratory results, the medical history of the patients as well as their insurance related information. It can also help the hospital management staffs to monitor a patient database. Wireless sensor applications also extend the concept of 'Telemedicine' where the patient can get treated at home via a remote access to the medical facilities or medical professionals. Different types of implantable sensors can be used to continuously monitor different physiological parameters. This could be particularly helpful in the case of emergencies as it saves valuable time.

Another area in the medical field where wireless sensors are finding their application is in the field of 'Telesurgery'. In this scheme, the doctor need not be physically present in the same room. The patient can be operated by robot manipulators. The doctor can remotely monitor the robot manipulators. Some of the sensor networks that can be used for health care applications are wireless body area network (WBAN), radio frequency identification (RFID), wireless personal area network (WPAN), general packet radio service (GPRS)/universal mobile telecommunications system (UMTS) and wireless LAN. Figure 1.1 illustrates the applications of wireless sensors in the medical field.

、

Figure 1.1Applications of medical wireless networks [1]

### **1.2** Glucose sensing implantable sensors

In this project, a biosensor system has been designed for monitoring blood-glucose levels of diabetic patients. Diabetes Mellitus or commonly known as diabetes is a condition in which a person has high levels of sugar in his blood. This may be due to the insufficient production of insulin (type 1 diabetes) or the ineffective use of insulin (type 2 diabetes). A person is said to have diabetes if his/her fasting plasma glucose level is at or above 7.0mmol/l. Diabetes is a fast-spreading disease world-wide. According to the WHO, more than 220 million people, worldwide [2] and nearly 24 million Americans have diabetes. Figure 1.2 shows the percentage of people with diabetes against the year.

Figure 1.2 Graph showing the percentage of people with diabetes against the year [3]

# **1.3** Importance of continuous glucose monitoring

Monitoring blood sugar levels is very important to patients since diabetes can lead to many complications such as kidney failure, blindness, nerve damage etc. Continuous monitoring of glucose is particularly useful for type 1 diabetic patients. It helps take optimal treatment decision for patients. Discrete measurements of glucose cannot predict future trends but continuous monitoring does have a predictive capability. An intermittent or discrete glucose monitoring system requires the user's effort whereas a continuous glucose monitor does not. In addition, continuous measurements of glucose provide information about the direction, magnitude, duration, frequency and causes of fluctuations of blood glucose levels. Therefore continuous monitoring is required as it provides a greater insight into the blood-glucose levels of a patient. A method of continuous monitoring of glucose combined with an insulin pump would require no effort from the patients and thereby will help improve their quality of life.

# **1.4** Techniques for measuring blood glucose levels

The three commonly used techniques for blood sugar monitoring are

- By means of invasive devices

- Using minimally invasive monitors

- By means of non-invasive sensors

#### **1.4.1** Using invasive devices

Invasive monitors analyze blood samples. Usually small lancets are used to prick the finger and obtain blood. The blood sample thus obtained is placed on a testing strip. The testing strip is then placed on a monitor that displays the blood sugar level. Figure 1.3 shows the measurement of blood glucose level using an invasive device.

#### **1.4.1** Using minimally invasive devices

Minimally invasive devices use needle-like electrodes, which are implantable subcutaneously. Minimally invasive monitors analyze interstitial fluid of the subcutaneous tissue. There are different methods to get a sample, like a laser induced puncture in the skin and vacuum collection of the trans-membrane fluid or with the aid of a low frequency ultra-sound, which causes the permeability of the skin to increase by 25 times. Minimally invasive monitors do not puncture any blood vessels. Figure 1.4 shows an implanted sensor unit.

•

Figure 1.3 Depiction of a blood glucose test using invasive devices [4]

Figure 1.4 A minimally invasive monitoring system

#### **1.4.2** Using non-invasive devices

Use of non-invasive devices, result in having no skin injury and are totally painless. The accuracy of these devices depends upon factors like body temperature, ambient temperature, body sweat etc. According to the Food and Drug Administration (FDA), the accuracy of non-invasive devices is 15%. Non-invasive methods fall into two classes: with an external factor and without any external factor. Electromagnetic radiation is a commonly used external factor. Near infrared (IR) radiation is used since the maximum transmission range in a bio-tissue is 800- 1200 nm. Blood glucose concentration can be measured without an external factor, by analyzing liquids secreted from the human body, such as tears, saliva or sweat. But, these methods do not provide continuous monitoring. Non-invasive techniques are rarely used due to their high percentage of measurement errors [5]. Figure 1.5 shows a non-invasive method of monitoring blood glucose. It is known as a gluco-watch. It uses low levels of electric current to extract glucose and move it into a transdermal pad. The glucose levels are estimated by an auto sensor.

Figure 1.5 A non-invasive gluco-monitoring system [6]

# **1.5 Basic Glucose-Sensor Concepts**

A minimally invasive biosensor is used to detect the level of blood glucose and convert the signal into an electrical signal. This electrical signal can be analyzed for any irregularities. A biosensor is a device used for the detection of a physiological change. It consists of three major components:

- 1. Biological recognition elements, which help differentiate the target analyte from various other molecules.

- 2. A transducer, which helps convert the reaction of the glucose molecules into a current.

- 3. The electronic circuitry needed to convert the signal into a userreadable form.

The commonly used transducers are electrochemical, optical, thermometric, piezoelectric and magnetic. For glucose sensing, electrochemical transducers are commonly used. They are preferred due to their better sensitivity, selectivity, lower power consumption and low cost. Figure 1.6 shows the factors affecting an electrochemical sensor.

•

Figure 1.6 Block diagram showing the factors affecting an electrochemical sensor

#### **1.5.2** Types of electrochemical sensors

There are three types of electrochemical sensors: potentiometric, amperometric and conductimetric.

- i. Potentiometric sensors: They measure the change in charge density at the surface of an electrode.

- ii. Amperometric sensors: Amperometric sensors monitor currents generated when an exchange of electrons takes place either directly or indirectly between an electrode and a biological system. These sensors have evolved along with the fabrication technology [7].

- iii. Conductimetric sensors: In such sensors, the measurement of solution resistance provides the concentration of charge. These sensors are therefore not species-selective. Conductimetric sensors are called so because they measure electrical conductance as their signal change.

#### **1.5.1** Oxidation of glucose

Usually, the measurement of glucose ( $C_6H_{12}O_6$ ) requires an enzyme. Different enzymes have different redox potentials, turn-over rates and selectivity for glucose. The common enzyme used for glucose measurement is glucose oxidase ( $GO_x$ ). It is preferred because it is easy to obtain, has a low cost, can withstand greater levels of pH and has a greater ionic strength. Glucose oxidase thus places relatively relaxed conditions for biosensor users. The oxidation reaction of glucose in the presence of glucose oxidase is given by,

Glucose +  $O_2 \xrightarrow{glucose \text{ oxidase}}$  Gluconic acid +  $H_2O_2$  (1.1)

Hydrogen peroxide  $(H_2O_2)$  is oxidized at a platinum electrode. The electrode recognizes the number of electron transfers. The number of electrons produced is proportional to the glucose molecules present in the analyte [8].

$$H_2O_2 \to 2H^+ + O_2 + 2e^-$$

(1.2)

### **1.6** Scope of the thesis

An implantable biosensor consists of a sensing system, a potentiostat and signal processing circuitry. A potentiostat helps in providing a proper bias between the electrodes of a sensor. In other words it enables the sensing system to measure a certain physiological element, as different physiological elements have different values of bias voltages. This thesis summarizes the design and testing of a potentiostat for implantable sensor applications. The power and area constraints are taken into account while designing this potentiostat.

The main concerns while designing an implantable biosensor are the size of the system, longterm bio-compatibility and minimal usage of power. The use of CMOS technology for signal processing in medical applications helps reduce the size of the sensor system drastically. A miniature sensor system is highly preferred since the sensor and the signal processing units are to be implanted in a human body. In addition, CMOS technology helps achieve low power consumption which is an essential requirement for implantable sensor electronics. Powering an implanted system is very critical. An implantable biosensor should be powered by means that are non-invasive, reliable, long lasting and effective. An inductive link is preferred, as it satisfies all the above requirements. It helps improve the lifetime of the system and also provides for a secure transmission of power and data transmission.

# 1.7 Thesis organization

•

Chapter 2 gives a detailed description of the various blocks involved in the construction of an implantable sensor for metabolic monitoring. The various blocks described are the band gap reference circuit, the potentiostat, the signal processing block and the inductive link.

Chapter 3 describes in detail the purpose and design of a potentiostat, which is used to provide a proper bias to the implanted sensor. It also describes in detail the various blocks that constitute a potentiostat. This improved potentiostat is designed taking the power and area constraints into consideration.

Chapter 4 consists of the presentation of simulation results and the test results.

Chapter 5 gives the conclusion and recommends future work that could be done to further improve the potentiostat design.

# **Chapter 2**

# System overview

# 2.1 Introduction

This chapter presents an overview of the different blocks constituting an implantable sensor system. An implantable sensor system generally constitutes the actual sensors implanted in the body and sensor electronics block consisting of - a signal processing block and a transmission system. The implantable sensor electronic system being considered here is for monitoring the level of glucose and/or other physiological parameters in the human body. The whole system runs on a voltage supply of 2.5V.

The various blocks that constitute an implantable sensor electronic system are as follows:

- Band gap voltage reference

- Potentiostat

- Signal processing block which consists of

- Data generator

- Frequency generator

- Inductive link

# 2.2 Band gap Voltage Reference

A voltage reference is needed to provide a constant and stable voltage which is insensitive to changes in temperature. Of the different voltage reference circuits, a band gap voltage reference

is the most widely used. Usually the output voltage of the band gap reference circuit is 1.25V. In order to generate a voltage reference that does not change with temperature, it is assumed that if two quantities that have opposite polarities of temperature co-efficient are added with proper weighting factors, then the resultant quantity would have a zero temperature co-efficient. The base-emitter voltage  $V_{BE}$  in a BJT has a negative temperature coefficient of -2.2 mV/°C and the thermal voltage  $V_t$  (=kT/q) has a positive temperature coefficient of +0.085 mV/°C. If the thermal voltage is multiplied by a constant *m* and then added to  $V_{BE}$ , we get,

$$\mathbf{V}_{\text{REF}} = \mathbf{V}_{\text{BE}} + m\mathbf{V}_{\text{t}} \tag{2.1}$$

Figure 2.1 shows the operating principle of a band gap reference circuit. Figure 2.2 shows the block diagram of a band-gap reference circuit. A supply independent current source produces a current  $I_1$ , which passes through  $Q_1$ . An equal amount of current  $I_2$  passes through  $Q_2$ , which has m BJT s connected in parallel. The voltage difference between  $V_{BE1}$  and  $V_{BE2}$  can be expressed as follows

$$\mathbf{V}_{\text{BE1}} - \mathbf{V}_{\text{BE2}} = \Delta \mathbf{V}_{\text{BE}} = \mathbf{V}_{\text{T}} \ln \left( \frac{I_1}{I_s} \right) - \mathbf{V}_{\text{T}} \ln \left( \frac{I_2}{mI_s} \right) = \mathbf{V}_{\text{T}} \ln \left( m \right) \quad (2.2)$$

From Figure 2.3, the output voltage at R2 is given by [9],

$$V_{ref} = V_{BE3} + \frac{V_T \ln(m)}{R_1} R_2 = V_{BE3} + IR_2$$

(2.3)

15

Where,

$$\mathbf{I}_{\text{Diode}} = \mathbf{I}_{\text{S}} e^{\left(\frac{V_{BE}}{V_T}\right)}$$

,  $\mathbf{I} = \mathbf{I}_1 = \mathbf{I}_2$  and  $\mathbf{I}_1 = \mathbf{I}_2 = \frac{V_T \ln(m)}{R_1}$

•

The band gap voltage reference circuit consists of an operational amplifier, two PMOS transistors, two large on-chip resistors, two bipolar junction transistors, and a start-up circuit.

Figure 2.1 Operating principle of the band gap reference circuit

Figure 2.2 Block diagram of a band gap reference circuit

•

Figure 2.3 Complete schematic of the band gap reference circuit [10]

## 2.3 Potentiostat

A potentiostat is required to provide the desired bias to an electrochemical sensor. The biosensor produces a current proportional to the concentration of glucose molecules, provided the voltage between the *Reference* electrode and the *Working* electrode is maintained at a constant value of 0.7V. This is done by using electronic circuitry comprising of an opamp and two class-AB buffers. The third electrode i.e. the *Collector* electrode collects the charges and produces a sensor current. The sensor current is further modified and made into a user-readable form. The circuit description and schematic of the potentiostat is discussed in detail in chapter 3.

# 2.4 Signal Processing Block

The purpose of the signal processing block is to convert the current received from the *Collector* electrode to an FSK signal that can be transmitted out of the human body. To transmit the data from the implantable sensor in the body, a modulation scheme is required. Amongst the various available modulation schemes, a frequency shift keying (FSK) mechanism is preferred because of its ease of implementation and low cost. FSK modulation scheme has been chosen due to its ease of implementation and immunity to noise. Since the power and the data are transmitted through the same set of coils, FSK modulation is used to avoid any power-amplifier non-linearity issues.

The signal processing circuitry consists of two blocks – the data generator and the frequency generator. The functions of these two blocks are explained in the following sections.

#### 2.4.1 Data Generator

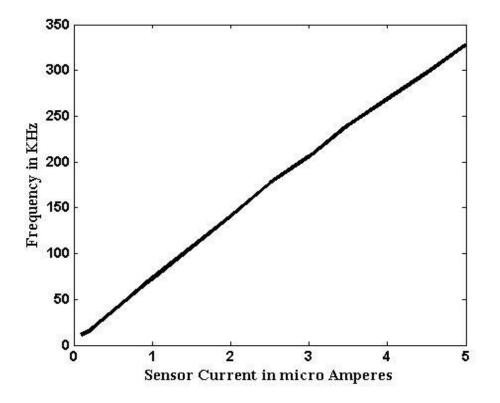

The function of the data generator block is to convert the input sensor current into a data signal. Figure 2.4 shows the block diagram of a data generator block. The input to the data generator block is the current generated from the electrochemical sensor. The current is fed to a current mirror (N1-N2). This mirrored current charges the integrating capacitor  $C_{int}$  to the supply voltage ( $V_{DD}$ ). As the capacitor gets charged up, the voltage at the input of the Schmitt trigger decreases. When the input of the Schmitt trigger goes below its lower threshold voltage, the output turns *low*. This output is connected to an inverter. Therefore the output of the inverter is *high*. This is connected to a PMOS transistor, which acts as a switch. When its input is high, it turns on, and thereby forming a shorted connection between  $V_{DD}$  and the input to the Schmitt trigger. This shorted path discharges the capacitor and hence starts a new cycle. The rate at which the capacitor charges, is dependent on the mirrored current, which depends on the sensor current. Therefore, the frequency of the data signal is directly proportional to the sensor current.

The second inverter is needed to minimize the effect of loading on the data signal. The output of the second inverter is finally connected to a D-latch, to make the duty cycle of the data signal to approximately 50% and also to provide a frequency separation of ten times between the data and the lowest carrier frequency[11]. The Schmitt trigger and the D latch are explained in the next sections.

`

Figure 2.4 Block diagram of a data generator

Figure 2.5 Variation of frequency with respect to change in current obtained from the sensor

# 2.4.2 Schmitt trigger

`

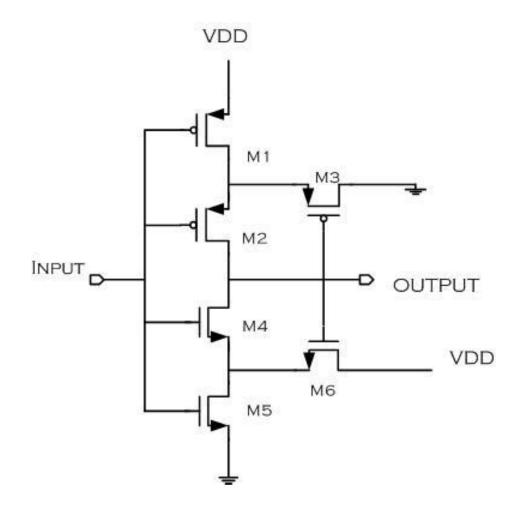

A Schmitt trigger is a type of comparator that gives the output as *low* if the input is below the lower threshold voltage and outputs *high* if the input is above the higher threshold voltage. The hysteresis makes the circuit immune to noise. Figure 2.6 shows the schematic of a Schmitt trigger.

Figure 2.6 Schematic of a Schmitt trigger

### 2.4.3 D latch

•

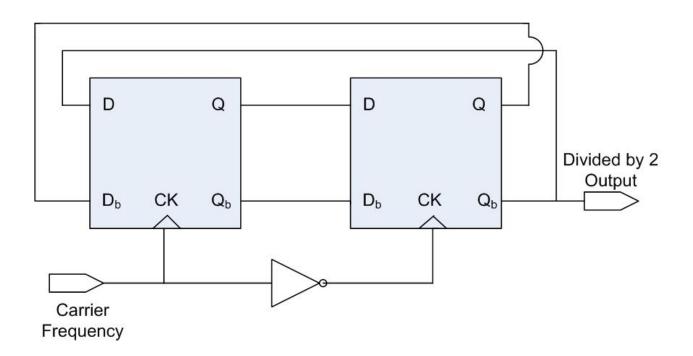

A D latch is a variation of the SR latch. It is constructed by connecting the inverted S input to the R input. The advantage of a D latch is that it cannot experience a "race" condition. One of the applications of a D latch is a frequency divider. Here, it is used for the same purpose. The output Qbar is connected to the D input. Figure 2.7 shows a frequency divider using a D latch. The truth table for a D latch is as shown in Table 2.1.

#### Table 2.1: Truth table of a D latch

| Clock | D | Q         | Qprevious |

|-------|---|-----------|-----------|

| 1     | 0 | 0         | Х         |

| 1     | 1 | 1         | Х         |

| 0     | 0 | Qprevious |           |

| 0     | 1 | Qprevious |           |

### 2.4.4 Frequency Generator

To transmit the data from the implantable sensor in the body, a modulation scheme is required. Usually an amplitude shift keying (ASK) or a frequency shift keying (FSK) mechanism is preferred because of their ease of implementation and low cost. Here, an FSK modulation scheme has been used. FSK modulation scheme has been chosen due to its ease of implementation and immunity to noise. Since the power and the data are transmitted through the same set of coils, FSK modulation is used to avoid any power-amplifier non-linearity issues.

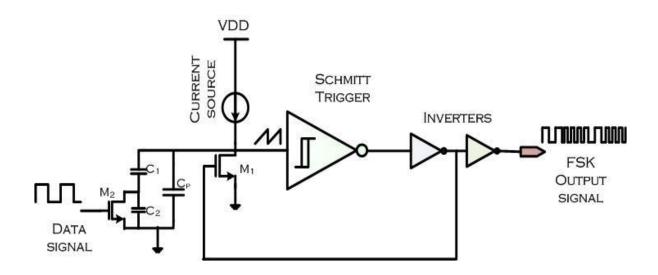

The frequency generator block comprises a Schmitt trigger, an inverter, a switched capacitor structure and an NMOS (M1) transistor. The NMOS transistor  $(M_1)$  is used to discharge the

capacitor. A beta multiplier is used to provide a constant current. This current charges the switched-capacitor structure towards the supply voltage  $V_{DD}$ . When the capacitor voltage reaches the upper threshold voltage of the Schmitt trigger, a negative pulse is generated by the Schmitt trigger. The Schmitt trigger is connected to an inverter and hence the output of the inverter is positive/high. This is fed to the NMOS transistor, which discharges the capacitor. The rate at which the capacitor discharges is dependent on the value of the capacitance and the on resistance of the NMOS, M1. To get a 50% duty cycle of the carrier frequency, the on resistance of M1 is optimized with equivalent capacitance of the switched-capacitor structure.

There are three capacitances involved in the switched-capacitor structure. They are  $C_1$ ,  $C_2$  and  $C_p$ . An NMOS transistor (M<sub>2</sub>) is connected in parallel with  $C_2$ . The data signal from the data generator is given as input to the gate of M<sub>2</sub>. When the data signal is low, the capacitance value can be expressed as

$$C_{eq,LOW} = C_p + \frac{C1 C2}{C1 + C2}$$

(2.4)

When the data signal is *high*, M<sub>2</sub> acts as a short and therefore the effective capacitance becomes,

$$C_{eq,HIGH} = C_p + C_1 \tag{2.5}$$

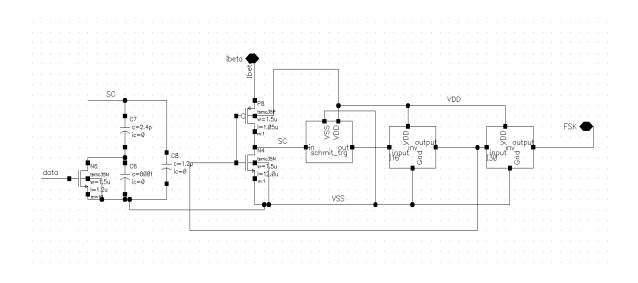

It can be observed that when the data signal is *low*, the equivalent capacitance is *low* and the output frequency is *high*. When the data signal is *high*, the equivalent capacitance is *high* and the output frequency is *low*. Thus the frequency generator produces two different frequencies based on the *high* or *low* value of the data signal. Figure 2.8 shows the schematic of the frequency generator. The values of the capacitors used are,  $C_p = 1.2pF$ ,  $C_1 = 2.4pF$  and  $C_2 = 800fF$ .

Figure 2.8 Block diagram of a frequency generator

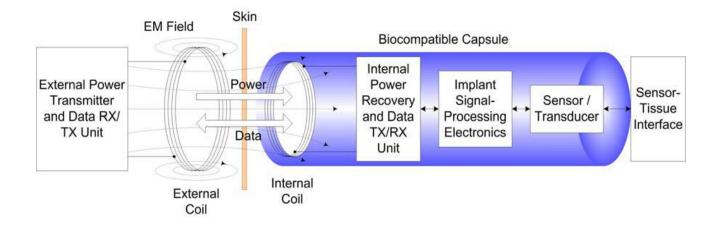

## 2.5 Inductive link

An inductive link is used in this system to transmit power to the implanted sensor unit and also to transmit the FSK modulated signal from the sensor to the external unit. The transmission of data between an implanted sensor and the outside world can be done using other methods i.e. through batteries, wire cables etc. Powering an implantable sensor using batteries is not usually preferred since a battery usually has a short life and therefore frequent replacement or recharging of the battery is required. Also, there are leakage problems involved and these may prove to be injurious to the patient. A battery also increases the size of the implanted system. An inductive link is a safe option since there is less risk of infection and it is durable for long term use. However an inductive link has disadvantages due to the size of the coils used and the attenuation of signal through the skin of the user.

An inductive link is formed by a loosely coupled transformer comprising of a pair of coils arranged co-axially. The primary coil is excited using an alternating current. This current creates an electro-magnetic field and the change in the flux linkage produces a voltage in the secondary coil. The overall performance of the inductive link coils depends on the coil dimensions, coupling factor, coil spacing and frequency of operation. The larger the dimension of the coil, greater is its efficiency. The mutual inductance is directly proportional to the coupling coefficient. Increase in the spacing between the coils causes a decrease in the efficiency. The operating frequency should be low enough to keep the tissue absorption at a minimum and high enough to allow a sufficient data transfer rate.

An FSK modulation scheme is one the preferred methods of transmission due to its high power efficiency, better noise performance and simple implementation. Figure 2.9 shows the block diagram of an implanted unit powered with inductive links.

Figure 2.9 Block diagram of an implanted sensor powered using inductive links

## Chapter 3 The Potentiostat

### 3.1 Introduction

Recently there has been much advancement in the field of implantable sensor technology. An implantable sensor is useful in situations when *in vivo* measurement of a substance in an analyte is required. Implantable sensors are mainly useful in medical applications when it is required to monitor physiological factors like the levels of glucose, lactate, pH, oxygen etc. The output from the sensor is usually a current and this current can be converted into a voltage signal and transmitted outside the human body for analysis and monitoring purposes. A potentiostat is an integral part in an implantable sensor. It is used to set a fixed potential for the proper operation of the sensor. The electrochemical sensor produces a current, proportional to the target analyte when the voltage between the reference and the working electrode is constant. Therefore the potentiostat has to maintain a constant voltage between the reference electrode and the working electrode. [12].

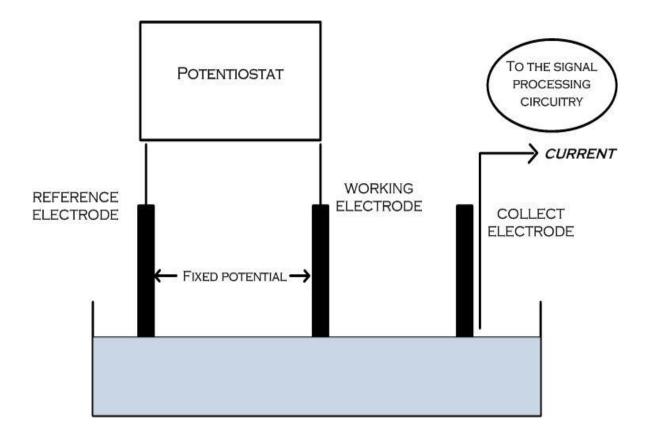

#### **3.2** Principle of a potentiostat

A potentiostat can be considered as a controlling and a measuring device. It is the electronic circuitry that is used to bias a sensor. It helps maintain a constant potential between the *Reference* and the *Working* electrode. The *Working* electrode is the sensing electrode. It is chemically inactive and the electrochemical reaction of the analyte occurs here. The *Collector*

electrode is used to collect the current present in the solution. The third electrode is known as a *Reference* electrode. The *Reference* electrode is needed to maintain a constant reference. Figure 3.1 shows the construction of a basic three electrode sensor and a potentiostat. The current resulting from the Faradaic reaction occurring at the *Working* electrode can be written as,

$$I_{\rm f} = k_{\rm f} A_{\rm w} C_{\rm o} \tag{3.1}$$

where  $A_w$  is the area of the working electrode,  $C_o$  is the concentration of the analyte, and  $k_f$  is the proportionality constant[13].

The constant value of voltage to be maintained between the *Reference* and the *Working* electrodes depends on the purpose the potentiostat is being used for. For example if it is a part of a glucose sensing system the value of the bias voltage is 0.7V, for a lactate sensing system, the bias voltage is 0.6V, for oxygen sensing the bias voltage should be -0.1V etc. For this project, the potentiostat has been designed to maintain a 0.7V difference between the *Reference* and the *Working* electrode. The resistance of the analyte i.e. blood is assumed to be in the order of kilo ohms.

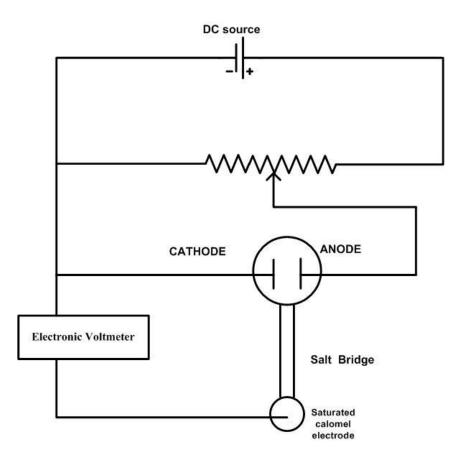

#### **3.3** Potentiostat using constant cathode potential

Earlier this type of potentiostat was used; however it is not suitable for implantable purposes. In such a device, the potential at the cathode is measured continuously with respect to a *Reference* electrode. This *Reference* electrode is in the form of a saturated calomel electrode. The total

potential applied to the cell is controlled with the aid of a voltage divider, such that the potential at the cathode is constant. Figure 3.2 shows the diagram of the device. The saturated calomel electrode, the salt bridge, the cathode and the anode are immersed in the solution being monitored.

Figure 3.1 Block diagram of a basic three electrode system

Figure 3.2 A potentiostat using a constant cathode potential

## 3.4 On-chip potentiostat with four op-amps

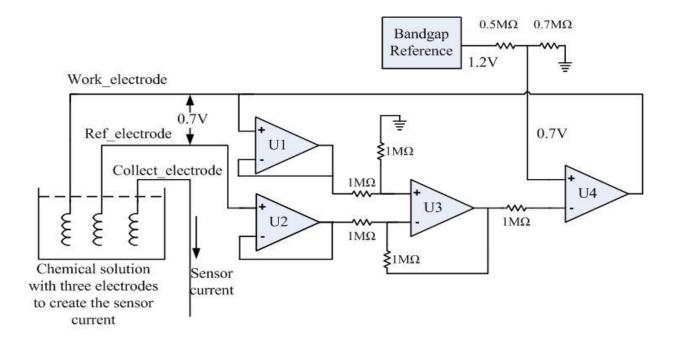

There are four operational amplifiers involved in this circuit. Figure 3.3 shows the block diagram of the potentiostat. They are U1, U2, U3 and U4. Op-amps U1 and U2 function as buffers, U3 functions as a unity gain differential amplifier and U4 acts as an error amplifier. The input at the non-inverting terminal of the error amplifier (U4) is fixed at 0.7V. This voltage is fixed with the aid of a resistive divider from the band gap reference, which provides a constant 1.2 V. The output of the error amplifier is fed back to the work electrode [14].

The feedback loop ensures that the voltage at the inverting and the non-inverting terminals of U4 remains the same. The voltage at the inverting terminal of U4 is equal to the output of U3, which is 0.7V. This is because there is no current flowing into the inverting terminal. The voltage of the non-inverting input of U3 is  $V_{work_el}/2$ , because of the resistive divider used. Using Kirchhoff s current law at the inverting input of the differential amplifier (U3), we get

$$V_{ref\_el} - \frac{V_{work\_el}}{2} = \frac{V_{work\_el}}{2} - 0.7$$

(3.2)

•

Therefore,

$$V_{work\_el} - V_{ref\_el} = 0.7$$

(3.3)

# Figure 3.3 Block Diagram of the previously used potentiostat using four operational amplifiers

#### **3.5** On chip potentiostat with a single op-amp

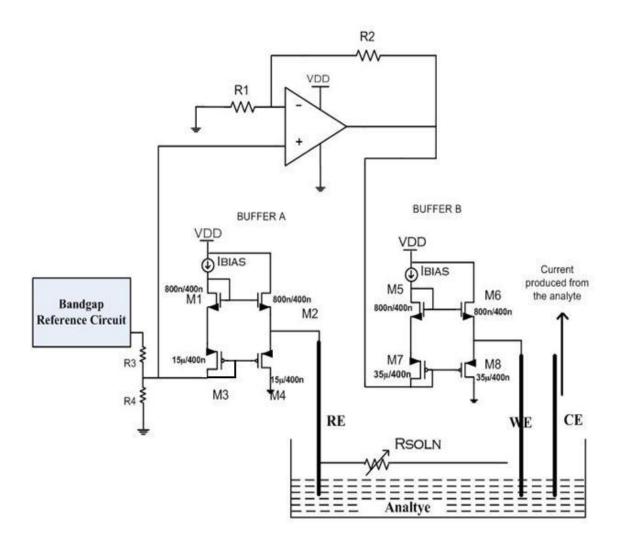

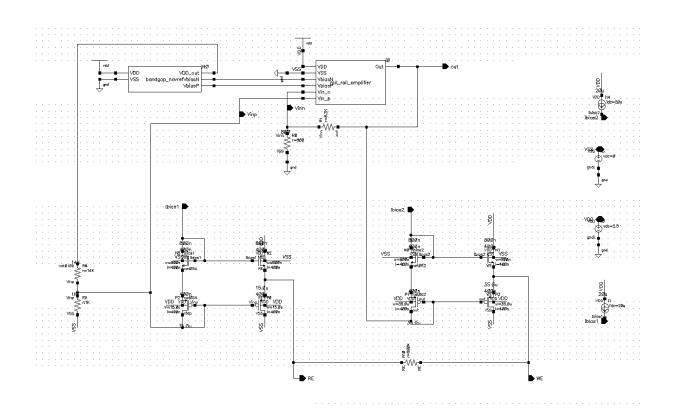

The above mentioned potentiostat uses four op-amps, thereby increasing the number of components and hence increasing the area on the chip. Here, the proposed design of the on-chip potentiostat uses a single op-amp. It maintains a constant value of 0.7V between the *Reference* electrode and the *Working* electrode. The circuit diagram of the potentiostat is shown in Figure 3.5. It consists of an op-amp in a non-inverting configuration and two class AB buffers. The positive terminal at the input and the output terminal of the op-amp are connected to class AB buffer circuits. The outputs of these buffer circuits are connected to electrodes, which are immersed in the analyte. The *Reference* electrode is connected to the buffer A, which is at the non-inverting (positive) input terminal and the *Working* electrode is connected to the buffer B, which is at the output of the op-amp.

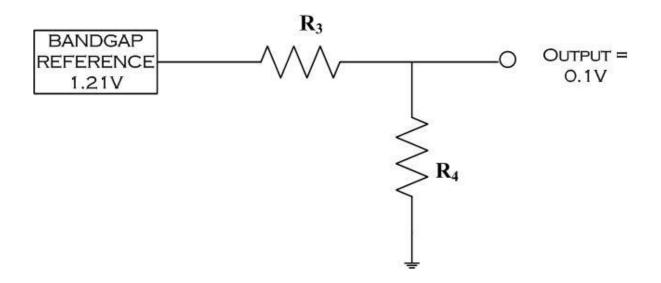

A band gap reference circuit is used to provide a stable reference voltage of 1.21V. The input at the positive terminal of the op-amp is 0.1V which is attained by using a resistive divider ( $R_3$  and  $R_4$ ) from the band gap reference circuit. The value of the resistors  $R_3$  and  $R_4$  are 1K  $\Omega$  and 11K  $\Omega$  respectively to give an output of 0.1V. Figure 3.4 shows the resistive divider. The resistors  $R_1$ and  $R_2$  (the input resistance and the feedback resistance), connected to the op-amp can be adjusted to give a value of 1 V at the output of the op-amp. The ratio of  $R_1$  and  $R_2$  can be found by,

$$V_{out} = V_{in} (1 + R_2 / R_1)$$

(3.4)

$R_2/R_1 = 9/1$

Here,  $R_2 = 18K\Omega$  and  $R_1 = 2K\Omega$

The buffers are used to minimize the loss of signal strength at the output due to loading. They also help maintain a constant voltage. The resistance of the solution is modeled with a 300K $\Omega$  resistor. Since the potential between the electrodes is 0.7V and the current from the sensor is around 2µA. Therefore the resistance is approximately 300K $\Omega$ . The parameters of the buffer circuits and the op-amp are designed to have minimal variation with change in resistance of the solution.

This resistance of the solution depends on the electrochemical reactions taking place in the analyte. The circuit is simulated assuming the resistance of the analyte to vary between  $300K\Omega$  to  $1M\Omega$ . The potentiostat maintains a fairly constant value with the above mentioned change in resistance. The operation of the class AB buffer and the operational amplifier are explained in the following sections.

Figure 3.4 Resistive divider used at the Band gap Reference circuit

Figure 3.5 Block diagram of the potentiostat

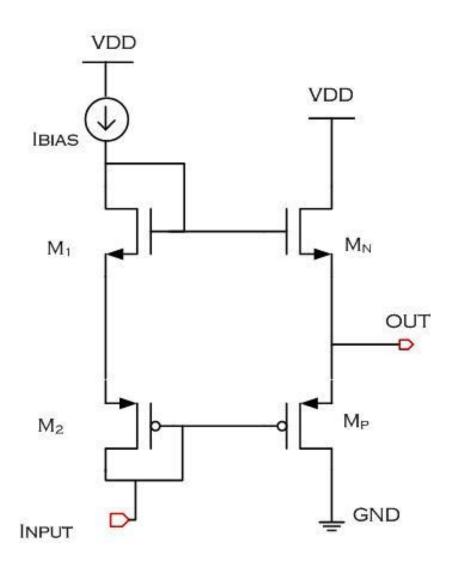

### 3.6 Design of the Class AB buffers

The class AB buffers are used to maintain constant voltages at their output terminals, since the electrodes are connected at these output terminals. A constant current ( $I_{BIAS}$ ), flows through  $M_1$  and  $M_2$ . This establishes a DC bias voltage  $V_{GG}$ , between the gates of  $M_N$  and  $M_P$ . If  $M_N$  and  $M_P$  are matched and  $M_1$  and  $M_2$  are matched, then

$$I_{\rm M} = I_{\rm BIAS} (W/L)_{\rm n} / (W/L)_{\rm 1}$$

(3.5)

also,

•

$$(V_{GS})_{M1} + (V_{GS})_{M2} = (V_{GS})_{MN} + (V_{GS})_{MP}$$

(3.6)

The diode connected MOSFETS  $M_1$  and  $M_2$  are used for biasing since they are always in saturation. Figure 3.6 shows a class AB buffer. Here, the buffers are biased with a current of 20  $\mu$ A. The bias current and the dimensions of the transistors are chosen to maintain a stable difference of 0.7V between the output terminals of both the buffers.

Figure 3.6 Schematic of the Class AB buffer

# **3.7** Design and Simulation of the Rail to Rail Operational Amplifier

•

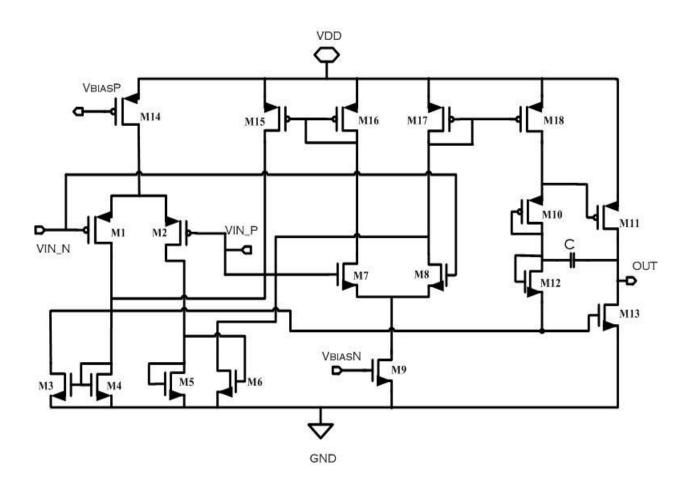

CMOS operational amplifiers or op-amps find their applications in various analog and digital circuits. Here, in the circuit of a potentiostat, a rail to rail op-amp is used in the non-inverting configuration is used. A rail to rail op-amp gets its name from the fact that its output can go near the power supply rails. The op-amp had been tested for various factors such as its frequency response, phase margin, settling time, slew rate, offset voltage, common-mode range, CMRR etc. The circuit diagram of the op-amp is as shown in Figure 3.7. The input stage of the op-amp amplifies the difference between the two inputs. The input stage consists of a PMOS differential pair and an NMOS differential pair. The PMOS input-pair can detect a signal even as low as a ground signal and an NMOS differential pair can detect a signal as high as  $V_{DD}$ .  $M_1$ ,  $M_2$ ,  $M_7$  and  $M_8$  form the differential pairs.  $M_{15}$ ,  $M_{16}$ ,  $M_{17}$  and  $M_{18}$  act as loads. VbiasP and VbiasN are used to bias the circuit.  $M_{11}$  and  $M_{13}$  form the output buffer.

Figure 3.7 Rail to Rail CMOS Operational amplifier

## 3.7.1 Frequency Response

•

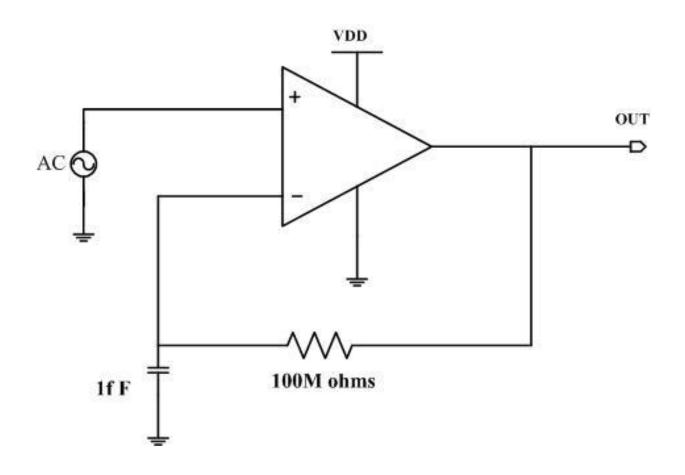

The frequency response of the amplifier is tested using the configuration shown in Figure 3.8. The DC gain of the amplifier is 72 dB. The phase margin is 59.5°. The unity gain frequency is found to be 835.56K Hz.

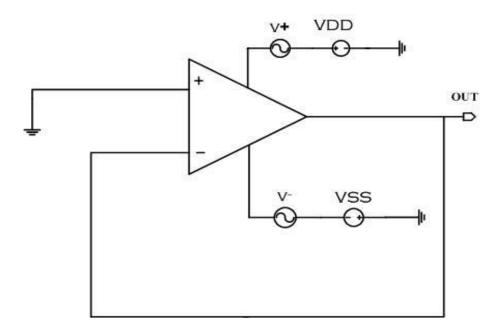

Figure 3.8 Schematic to measure the frequency response of an op-amp

## 3.7.2 Slew Rate

•

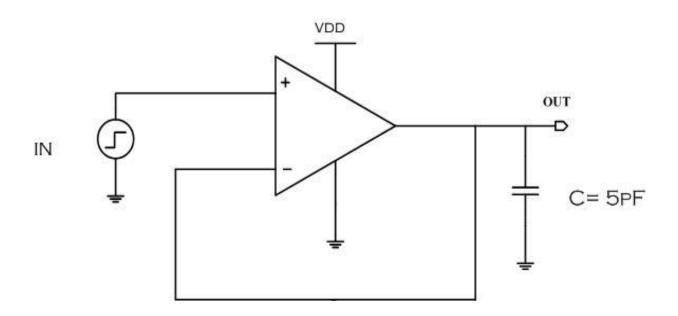

It is defined as the maximum rate of change of the output of the op-amp. The slew rate of the opamp is found by using the schematic shown in Figure 3.9. For simulation purposes, the load capacitor is assumed to be 5pF. The slew rate is found to be  $2.1e^6$  V/s. The slew rate is given by the following equation

$$SR = \frac{dV_{out}}{dt}\Big|_{MAX}$$

(3.7)

**Figure 3.9 Circuit configuration to measure Slew Rate**

#### 3.7.3 Common Mode Rejection Ratio

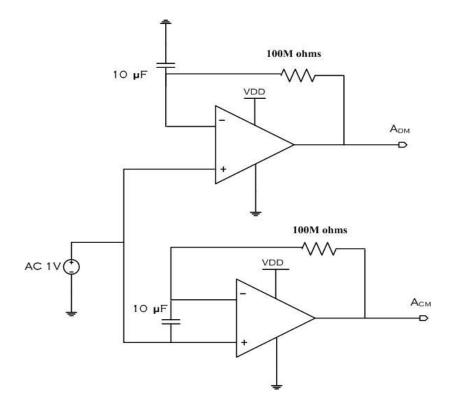

CMRR can be defined as the ratio of the voltage gain for a differential mode input signal to the voltage gain for a common mode signal. An ideal op-amp will not respond to a common-mode signal. Figure 3.10 shows the test configuration.

$CMRR = 20 \log (A_{DM} / A_{CM})$ (3.8)

The CMRR of this op-amp is 67.15 dB.

Figure 3.10 Circuit configuration to measure CMRR

#### 3.7.4 Settling Time

It is defined as the time needed for the output of the op-amp to reach a final value, when excited by a small signal. The circuit configuration used to determine the slew-rate is shown in Figure 3.9. The settling time was found to be 2.68µs.

#### 3.7.5 Rise Time

The time taken for the output signal to change from 10% to 90% of its final value when a step input is applied is known as rise time. The rise time is found to be 0.44µs.

#### **3.7.6 Power Supply Rejection Ratio (PSRR)**

It is defined as the product of the ratio of the change in supply voltage to the change in output voltage of the op-amp caused by the change in the power supply and the open-loop gain of the op-amp. Ideally, an op amp would have an infinite PSRR.

$$PSRR^{+} = V^{+} / V_{out}$$

(3.9)

$$PSRR^{-} = V^{-} / V_{out}$$

(3.10)

Figure 3.11 shows the circuit configuration used to find the PSRR. From the simulation, PSRR<sup>+</sup> is found to be 118.2dB and PSRR<sup>-</sup> is found to be 84.38dB.

Figure 3.11 Circuit configuration to determine PSRR

Figure 3.11 Circuit configuration to determine PSRR

#### **3.7.7** Input Common Mode Range (ICMR)

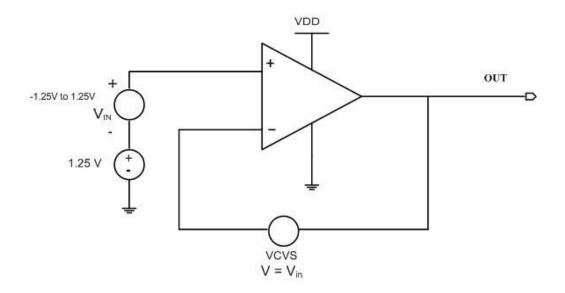

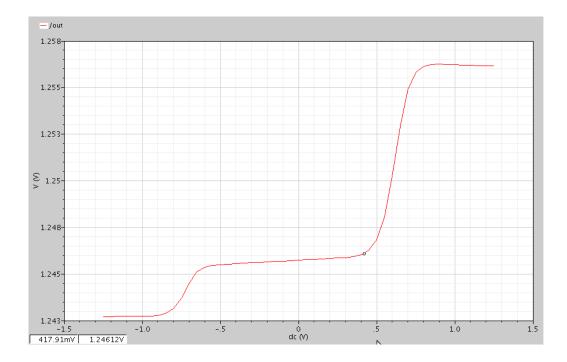

The common mode range is defined as the voltage range over which the input common mode signal can vary. Ideally, as the common-mode voltage varies, the output of the differential amplifier should remain constant. Figure 3.12 shows the circuit configuration used to measure the ICMR. The common mode range is found to be -1.25V to 1.25V.

Figure 3.13shows the simulation result. The three stable regions are due to the fact that it is a rail to rail op-amp.

Figure 3.12 Circuit configuration to measure ICMR

Figure 3.13 Simulation result showing the ICMR

## Chapter 4

## **Simulation and Test Results**

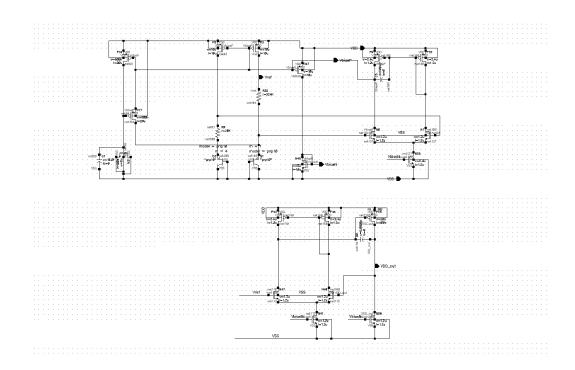

The schematic and layout have been created and simulated using CADENCE tools in a 0.35µm 4M-2P bulk CMOS process. DRC (design rule check) and LVS (layout versus schematic) matching have been used to verify the layout.

## 4.1 Actual Schematics Used

In this section, the actual schematics used to simulate the various circuits have been presented.

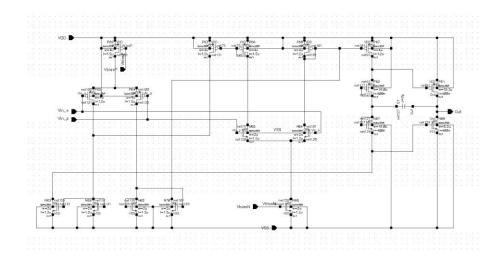

#### 4.1.1 Schematic of the Band gap reference circuit

Figure 4.1 Schematic of the Band gap reference circuit

## 4.1.2 Schematic of Operational Amplifier

**Figure 4.2 Schematic of Operational Amplifier**

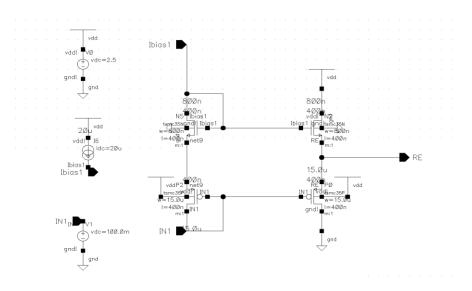

## 4.1.3 Schematic of Class AB Buffer

Figure 4.3 Schematic of Class AB Buffer

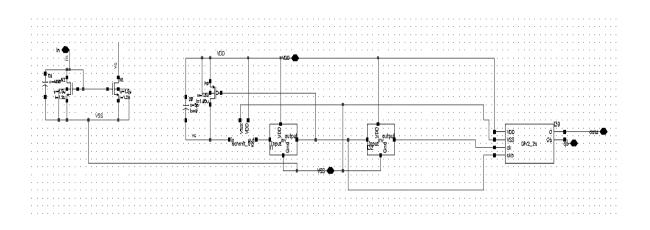

Figure 4.4 Schematic of the Potentiostat circuit using a single op-amp

## 4.1.5 Schematic of the data-generator circuit

Figure 4.5 Schematic of the data-generator circuit

## 4.1.6 Schematic of the frequency generator circuit

Figure 4.6 Schematic of the frequency generator circuit

## 4.2 Actual Layouts Used

•

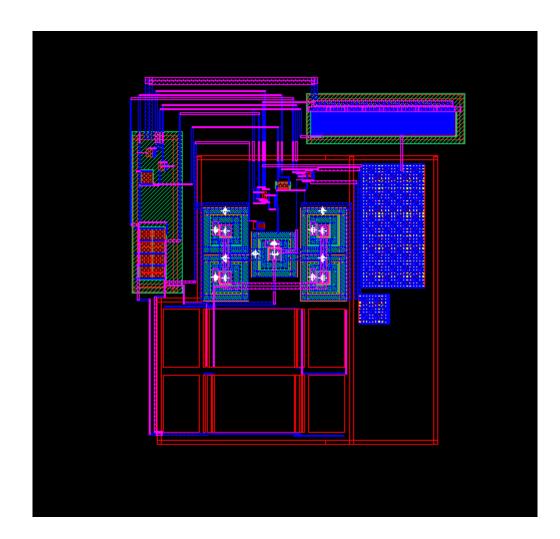

The actual layouts created in a 0.35  $\mu$ m bulk CMOS process using the CADENCE software are as follows:

## 4.2.1 Layout of the Band gap reference circuit

Figure 4.7 Layout of the bangap reference circuit

## 4.2.2 Layout of Operational Amplifier

Figure 4.8 Layout of the operational amplifier

## 4.2.3 Layout of Class AB Buffer

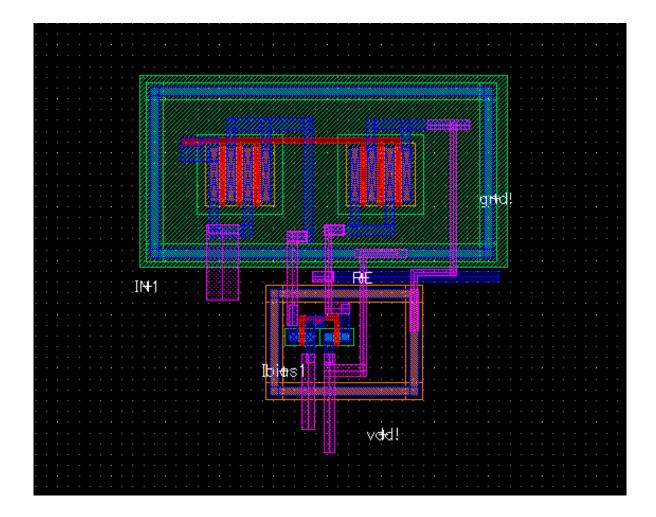

Figure 4.9 Layout of the class AB buffer

## 4.2.4 Layout of the Potentiostat circuit

、

Figure 4.10 Layout of the Potentiostat circuit

## 4.3 Simulation results of schematics

#### 4.3.1 Output of the potentiostat circuit

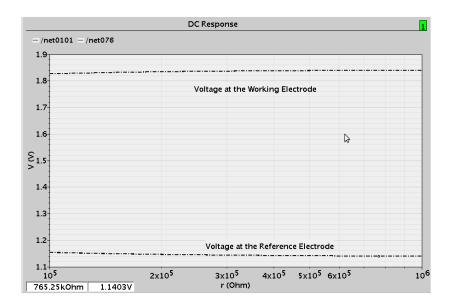

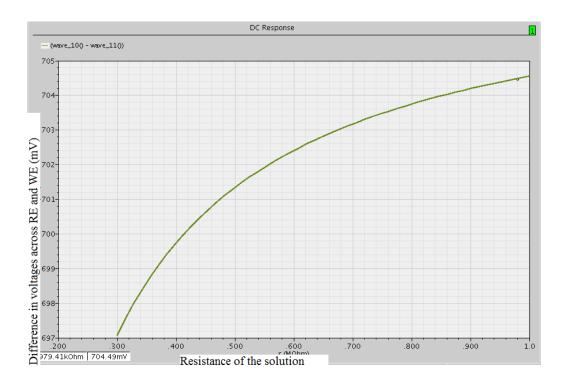

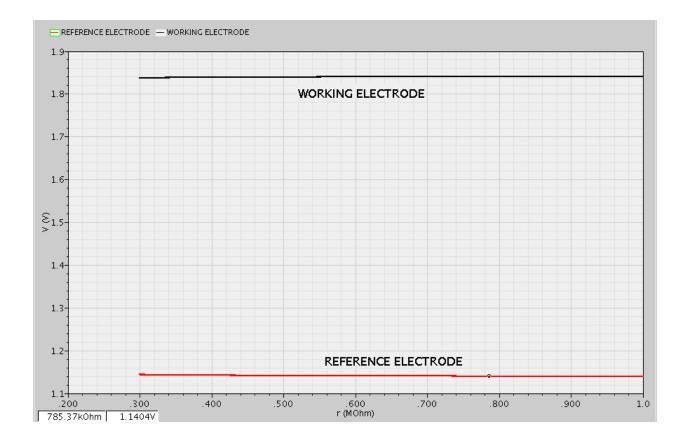

Figure 4.11 Voltages at the Working electrode and the Reference electrode Figure 4.11 shows the DC simulation of the schematic of the potentiostat. The difference between the Working electrode and the Reference electrode is almost a constant 0.7V for resistance varying from 100K $\Omega$  to 1M $\Omega$ . The resistance is used to indicate the solution resistance, in which the electrodes are immersed. The total current consumed by this circuit is 107.8µA and the total power consumed is 0.215mW. Figure 4.12 shows the difference in potentials across the electrodes with changing resistance. The x axis represents the resistance of the analyte changing from 300K $\Omega$  to 1M $\Omega$ . The y-axis represents the difference in voltages across the reference and the working electrodes.

Figure 4.12 Graph of difference in voltage across the electrodes versus the change in resistance

#### 4.3.2 Output of the Band gap Reference Circuit

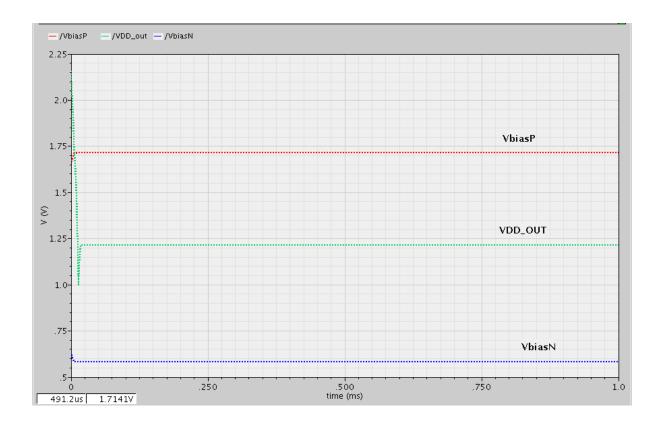

Figure 4.13 shows the simulation result of a band gap reference circuit. We can see that the output is a constant value of 1.21 V. VbiasP and VbiasN are used to bias the op-amp.

#### 4.3.1 Output of the Data Generator Circuit

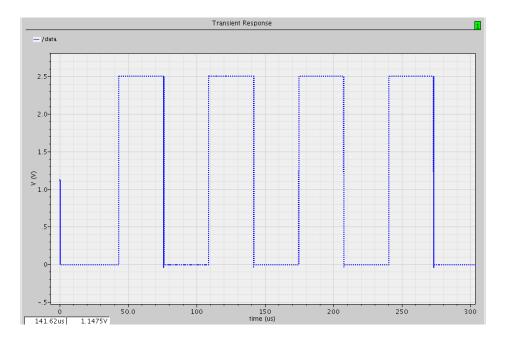

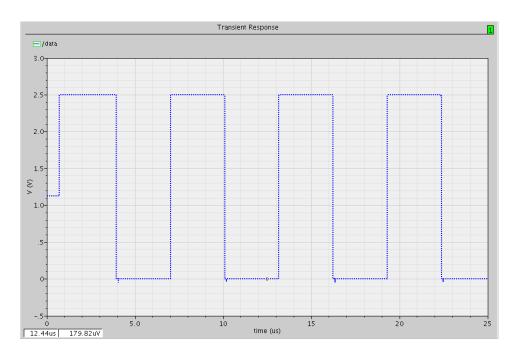

Figure 4.14 shows the output of the data generator circuit for a sensor current of  $0.2\mu A$  and Figure 4.15 shows the output of the data generator circuit for a sensor current of  $2.33\mu A$ . For a

0.2  $\mu$ A current, the frequency of the data signal is 15.15 KHz and for a 2.33  $\mu$ A current, the frequency of the data signal is 163.39 KHz.

## 4.3.1 Output of the Frequency Generator Circuit

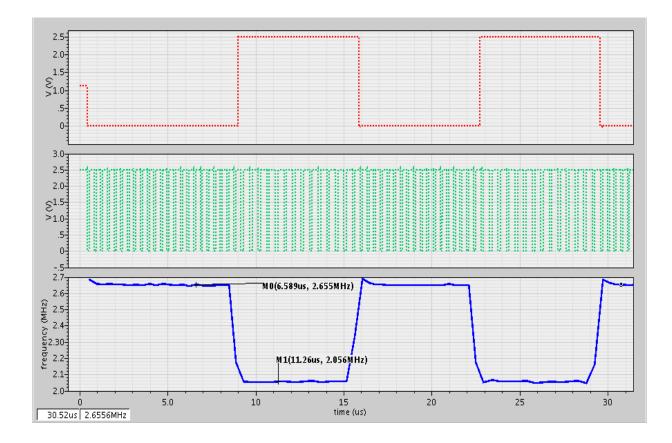

Figure 4.16 shows the output of the frequency generator circuit for a sensor current of  $2.33\mu$ A (i.e. a solution resistance of 300K $\Omega$ ). The upper trace shows the data signal, the middle trace shows the FSK modulated output and the bottom trace shows the frequency measurement of the second trace. The high frequency is 2.655 MHz and the low frequency is 2.056 MHz.

Figure 4.13 Simulation result of the band gap reference circuit

Figure 4.14 Output of the Data Generator Circuit for a sensor current of 0.2µA

Figure 4.15 Output of the data generator circuit for a sensor current of 2.33µA

Figure 4.16 Output of the Frequency Generator Circuit

## 4.4 Post layout simulation results

Simulating the layout is essential as it takes the parasitics into account.

#### 4.4.1 Voltages at the reference and the working electrodes

Figure 4.17 shows the results of simulating the layout of the potentiostat. It can be seen that when the resistance changes from  $100K\Omega$  to  $1M\Omega$ , the difference between the Working electrode and the Reference electrode is maintained at almost a 0.7V.

Figure 4.17 Voltages at the Working electrode and the Reference electrode

## 4.5 Simulation of the potentiostat with I/O pads

•

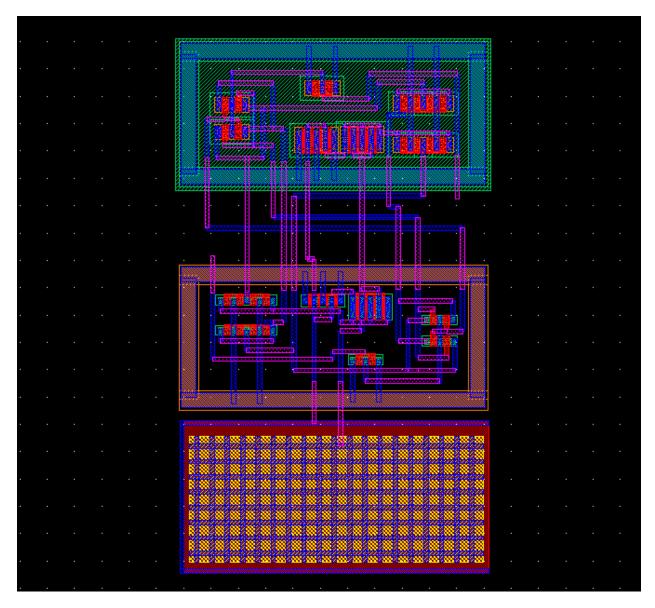

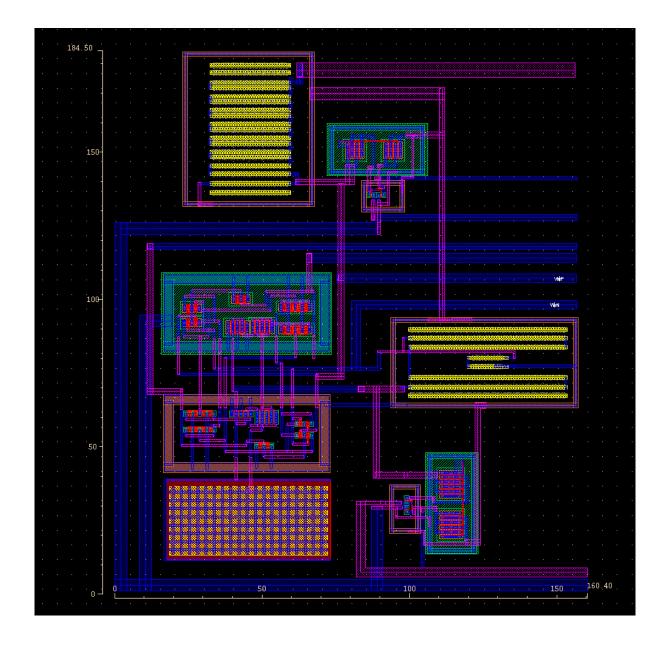

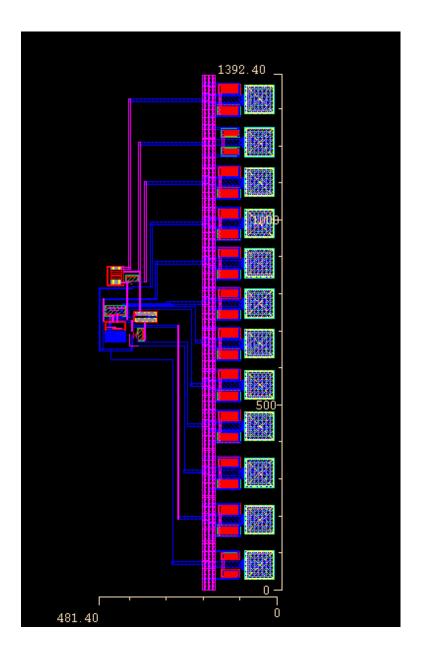

## 4.5.1 Screenshot of the potentiostat and the pads

The dimensions of the potentiostat circuit on chip are  $1392.4\mu m X 481.4\mu m$ . The area of the circuit with the pads is 0.67 mm<sup>2</sup>.

•

Figure 4.18 Screenshot of the potentiostat circuit with pads

### 4.5.2 Simulation of the potentiostat with the I/O pads

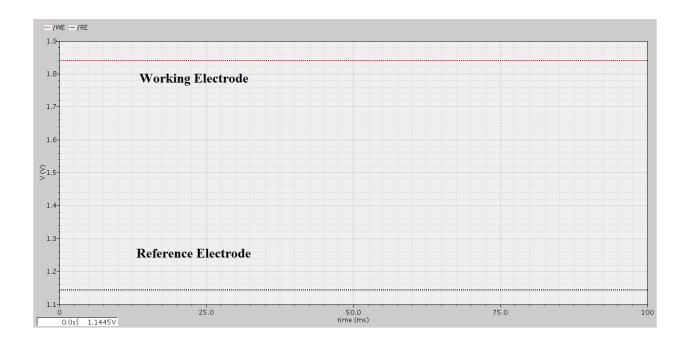

Figure 4.19 shows the voltages at the working and the reference electrode, when the layout of the circuit is simulated with the pads. The resistance is taken to be  $300K\Omega$ . The graph between resistance of the analyte and the difference of voltages at the working electrode and the reference electrode is shown in Figure 4.20. From this graph, the percentage change in the voltage across the electrodes with respect to the change in resistance of the solution is calculated to be 1.14%.

Figure 4.19 Simulation result of the potentiostat along with the I/O pads.

Figure 4.20 Graph representing the difference of voltages at the reference and the working electrodes with respect to the resistance of the solution

## 4.6 Post Fabrication Test results

•

## 4.6.1 Microphotograph of the fabricated chip

Figure 4.21 Micro-photograph of the chip

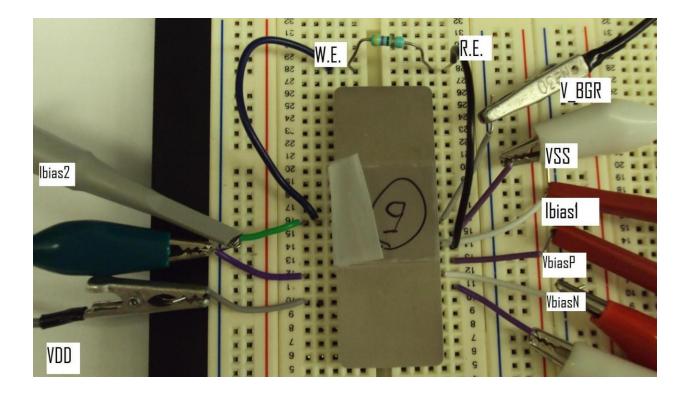

### 4.6.2 Test set-up

In this section, photographs of the prototype boards and associated test system are provided. Figures show the hardware components that make up the prototype design. Figure 4.22 and Figure 4.23 show the test setup of the circuit. Table 4.1 shows the values of the inputs given to the circuit.

Figure 4.22 Test setup of the circuit

### Table 4.1: Inputs to the circuit

•

| Parameter | Value   |

|-----------|---------|

| VDD       | 2.5 V   |

| V_BGR     | 1.215V  |

| VbiasP    | 1.714 V |

| VbiasN    | 0.581 V |

| Ibias1    | 20µA    |

| Ibias2    | 20µA    |

Figure 4.23 Test setup of the circuit

### 4.6.3 Test Results

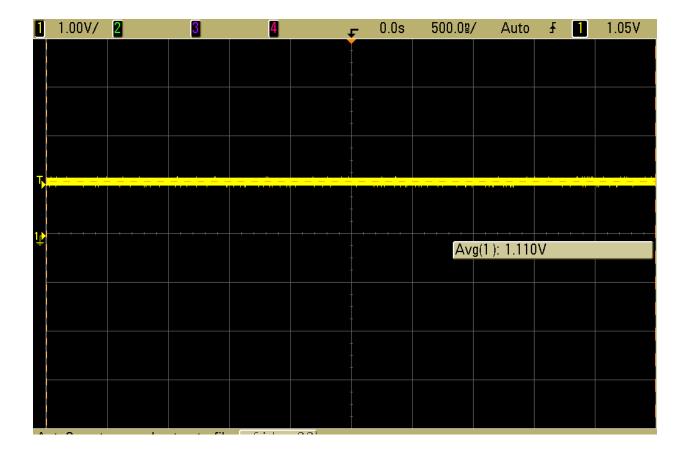

In this section the test results of the fabricated chip have been presented. Figure 4.24 shows the voltage at the Reference electrode, which is 1.1V. Unfortunately, the voltage at the *Working* electrode is not as expected. The working electrode is connected to the output of the second buffer. This buffer is in turn connected to the op-amp, so the variation maybe because either the second buffer or the operational amplifier is not fabricated properly. The output variation could also be due to improper bonding.

**Figure 4.24 Voltage at the Reference Electrode**

# Chapter 5 Conclusion

### 5.1 Thesis Summary

Potentiostats play an integral role in the functioning of any implantable sensor circuitry. The bias of the potentiostat depends on the application it is used for. This thesis has presented a potentiostat which can be used in an implantable system for detecting glucose concentration. This potentiostat consumes less area and less power, thus it is suitable for implantable biomedical applications. The pre layout and post layout simulation results were encouraging.

### 5.2 Future Work

Future work in this project would be to integrate the potentiostat with the remaining circuitry. The entire chip could be implanted and tested in real time with inductive powering. The current consumption of the entire circuit can be further reduced. This can be done by designing an opamp for low-power applications and by reducing the supply voltage from 2.5V to 1.5V. Another improvement could be to make a single potentiostat suitable for monitoring different physiological factors.

Another improvement that could be made to the entire system is to see that the entire system does not remain on all the time. It could be devised such that it gives the measurement of the target analytes every one hour and then goes into a power saving mode.

## References

`

[1] S.K. Islam M R Haider, Sensors and Low power signal processing. Springer, 2010, pp83.

[2] World Health Organization, Diabetes - factsheet no. 312, November 2009, Available online: http://www.who.int/mediacentre/factsheets/fs312/en/print.html

[3] http://www.cdc.gov/Features/dsDiabetesTrends/

[4] <u>http://www.cosmosmagazine.com/news/2590/nanoparticle-tattoo-allows-diabetics-</u>

monitor-blood-glucose

•

[5] N.A. Bazaev, S.V. Selishche, Noninvasive Methods for Blood Glucose Measurement.Biomedical Engineering, Vol. 41, No. 1, 2007, pp. 42\_50.

[6] Google image http://www.diabetesnet.com/images/meters/glucowatchhand.jpg

[7] Anthony P.F. Turner, Beining Chen, Sergey A. Piletsky, In Vitro Diagnostics in Diabetes: Meeting the Challenge. Clinical Chemistry, 45: 1596-1601, 1999.

[8] E.H. Yoo, S.Y. Lee, "Glucose Biosensors: An Overview of Use in Clinical Practice," Sensors 2010, 10, 4558-4576.

[9] Paul R. Gary, P.J.H., Stephen H. Lewis, Robert G. Meyer, ANALYSIS AND DESIGN OF ANALOG INTEGRATED CIRCUITS. Fourth Edition ed. 2001: WILEY.

[10] T. Oh," A LOW POWER INTEGRATED CIRCUIT FOR IMPLANTABLE BIOSENSOR INCORPORATING AN ON-CHIP FSK MODULATOR", M.S. Thesis, University of Tennessee, May 2007.

[11] M. R. Haider, S. Mostafa, and S. K. Islam, "A Low-Power Sensor Read-Out Circuit with FSK Telemetry for Inductively-Powered Implant System," 2008 Midwest Symposium on Circuits and Systems (MWSCAS), pp. 450-453, Knoxville, TN, Aug. 10-13, 2008.

[12] Carl H. Hamann, Andrew Hammet, Wolf Vielstich. Electrochemistry. Wiley-VCH, 1998

[13] Steven M. Martin, Timothy D. Strong, and Richard B. Brown. Design, Implementation, and Verification of a CMOS-Integrated Chemical Sensor System

•

[14] M. Zhang, M. R Haider, M. A Huque, M. A. Adeeb, S. Rahman, and S. K. Islam, "A low power sensor signal processing circuit for implantable biosensor applications," Smart Materials and Structures, 16, pp. 525-530, 2007.

## Vita

•

Anusha Atla was born on 25<sup>th</sup> January 1986 in Hyderabad, India. She completed her high school from St Ann's High School and her under-graduation from Jawaharlal Nehru Technological University, Hyderabad in Electronics and Communication Engineering. She joined the University of Tennessee, Knoxville in the Department of Electrical Engineering and Computer Science in Fall 2007. In the same semester, she joined the Analog VLSI and Devices Laboratory at UT. She has worked as a Teaching Assistant for the Electrical Circuits lab and the courses, Signals and Systems, Probability and Random variables and Electronic Circuits. She will be graduating in summer 2010. Her research focuses mainly on analog/mixed-signal IC design.