## University of Tennessee, Knoxville TRACE: Tennessee Research and Creative Exchange

#### Masters Theses

**Graduate School**

5-2006

# The Development of a Capacitance-Based Biotelemetry System for Implantable Applications

Calum John Johnson University of Tennessee - Knoxville

Follow this and additional works at: https://trace.tennessee.edu/utk\_gradthes

Part of the Electrical and Computer Engineering Commons

#### **Recommended Citation**

Johnson, Calum John, "The Development of a Capacitance-Based Biotelemetry System for Implantable Applications. " Master's Thesis, University of Tennessee, 2006. https://trace.tennessee.edu/utk\_gradthes/1705

This Thesis is brought to you for free and open access by the Graduate School at TRACE: Tennessee Research and Creative Exchange. It has been accepted for inclusion in Masters Theses by an authorized administrator of TRACE: Tennessee Research and Creative Exchange. For more information, please contact trace@utk.edu.

To the Graduate Council:

I am submitting herewith a thesis written by Calum John Johnson entitled "The Development of a Capacitance-Based Biotelemetry System for Implantable Applications." I have examined the final electronic copy of this thesis for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Master of Science, with a major in Electrical Engineering.

Benjamin J Blalock, Major Professor

We have read this thesis and recommend its acceptance:

Charles L. Britton, M. Nance Ericson

Accepted for the Council: Carolyn R. Hodges

Vice Provost and Dean of the Graduate School

(Original signatures are on file with official student records.)

To the Graduate Council:

I am submitting herewith a thesis written by Calum John Johnson entitled "The Development of a Capacitance-Based Biotelemetry System for Implantable Applications." I have examined the final electronic copy of this thesis for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Master of Science, with a major in Electrical Engineering.

Benjamin J. Blalock

Major Professor

We have read this thesis and recommend its acceptance:

Charles L Britton

M. Nance Ericson

Accepted for the Council:

Anne Mayhew

Vice Chancellor and Dean of Graduate Studies

(Original signatures are on file with official student records)

# The Development of a Capacitance-Based Biotelemetry System for Implantable Applications

A Thesis Presented for the

Master of Science Degree

The University of Tennessee, Knoxville

Calum John Johnson

May 2006

#### Acknowledgements

I would like to thank all the teachers, both academic and non-academic, who have influenced me throughout my studies. I am especially grateful for the education I received as an undergraduate at Tennessee Technological University because it is the foundation of my career. I am also grateful to the University of Tennessee for continuing my education at the graduate level and helping me expand my horizons. I would also like to thank Oak Ridge National Laboratory for the assistantship that made this work possible and for providing an environment in which I could learn and succeed.

I would like to all the members of my committee, Dr. B. J. Blalock, Dr. C. L. Britton, and Dr. M. N. Ericson, for their efforts and patience in helping me create this thesis. I would like to especially thank Dr. M. N. Ericson for taking such a personal role in my work.

I would like to thank my family for their support, encouragement, and understanding. I would like to especially thank Leah E. Watson for her love and support.

Finally I would like to thank God for making this and all things possible.

#### Abstract

Most modern biomedical implants implement some form of communications link between the implant and the outside world. This biotelemetry link has many requirements such as data bandwidth and power consumption. Designing an appropriate link that meets these requirements is one of the most significant engineering challenges associated with these implants. Communications methods that are currently used for this link include standard Radio Frequency (RF) approaches, inductively coupled approaches, and load modulation approaches. This thesis describes the development of a unique capacitance-based biotelemetry system for implantable applications. This system consists of two distinct parts: the implanted transmitter and the external body-mounted receiver. The prototype transmitter is based on a custom Application Specific Integrated Circuit (ASIC) fabricated using the AMI 1.5µ process. This ASIC encodes and transmits predetermined data packets by driving two electrodes in a slew-controlled manner, all contained within a biocompatible material. The receiver consists of charge-sensitive amplifier front end using a discriminator to distinguish individual bits. A Field Programmable Gate Array (FPGA) decodes the transmitted data and relays it to a PCbased LabVIEW interface. Test results using a saline-based human tissue model are presented.

iii

## **Table of Contents**

| Chapter 1 | Intr | oduction                                               | 1  |

|-----------|------|--------------------------------------------------------|----|

|           | 1.1  | Telemetry in Implantable Systems                       | 1  |

|           | 1.2  | Biological Interaction                                 | 2  |

|           |      | 1.2.1 Biological Effects on Communications             | 3  |

|           |      | 1.2.2 Communications Effects on Biology                | 3  |

|           | 1.3  | Current Wireless Implant Biotelemetry Methods          | 6  |

|           |      | 1.3.1 RF Approaches Based on Common Modulation         |    |

|           |      | Techniques                                             | 6  |

|           |      | 1.3.2 Inductively Coupled RF Power                     | 7  |

|           |      | 1.3.3 Passive Load-Modulation                          | 8  |

|           |      | 1.3.4 Direct-Sequence Spread Spectrum                  | 10 |

|           |      | 1.3.5 Directly Coupled Current Injection               | 11 |

|           | 1.4  | Communication Via Capacitive Coupling for Biotelemetry |    |

|           | А    | pplications                                            | 12 |

|           |      | 1.4.1 Previous Capacitive Coupling Work                | 12 |

|           |      | 1.4.2 Capacitance-Based Approach Compared to Other     |    |

|           |      | Techniques                                             | 14 |

|           | 1.5  | Justification for Research                             | 17 |

|           | 1.6  | Scope of Thesis                                        | 17 |

| Chapter 2 | Мос  | deling Capacitive Coupled Biotelemetry                 | 20 |

|           | 2.1  | Modeling Human Tissue                                  | 20 |

|           | 2.2  | Establishing an Equivalent Electrical Model            | 22 |

|           |      | 2.2.1 Time Domain Characterization Test Setup          | 23 |

|           |      | 2.2.2 Step Response                                    | 23 |

|           |      | iv                                                     |    |

|           |      | 2.2.3    | Equivalent Electrical Model25                           |

|-----------|------|----------|---------------------------------------------------------|

|           | 2.3  | Establ   | ishing a More Accurate Experimental Setup               |

|           |      | 2.3.1    | Summary of Test Results                                 |

|           |      | 2.3.2    | Test Results and Conclusions                            |

| Chapter 3 | Syst | tem Des  | sign and Implementation32                               |

|           | 3.1  | System   | n Summary - Overview                                    |

|           | 3.2  | Impla    | nt Transmitter                                          |

|           |      | 3.2.1    | Dummy Packet Generator                                  |

|           |      | 3.2.2    | Packet Format                                           |

|           |      | 3.2.3    | Bi-Phase Mark Encoding Scheme                           |

|           |      | 3.2.4    | Alternative Encoding Schemes                            |

|           |      | 3.2.5    | Analog Slew Control Circuits46                          |

|           | 3.3  | Exterr   | nal Receiver                                            |

|           |      | 3.3.1    | Charge-Sensitive Preamplifier with Discriminator Front- |

|           |      | End      | 61                                                      |

|           |      | 3.3.2    | UART-Style Decoder Block64                              |

|           |      | 3.3.3    | PC-based LabVIEW Graphical User Interface (GUI)66       |

|           | 3.4  | Impla    | nt Transmitter Implementation                           |

|           |      | 3.4.1    | CapTran1 Chip66                                         |

|           |      | 3.4.2    | Test Transmitter PCB69                                  |

|           | 3.5  | Receiv   | ver Implementation                                      |

|           |      | 3.5.1    | Gain and Discriminator Board75                          |

|           |      | 3.5.2    | FPGA Implementation76                                   |

|           |      | 3.5.3    | USB Communication Board77                               |

|           |      | 3.5.4    | LabVIEW GUI Implementation79                            |

| Chapter 4 | Ver  | ificatio | n and Characterization81                                |

|           | 4.1  | Testin   | g Overview                                              |

|            | 4.2 | Functionality Testing                               |                 |

|------------|-----|-----------------------------------------------------|-----------------|

|            |     | 4.2.1 Testing the Functionality of the CapTran1     |                 |

|            |     | Transmitter                                         |                 |

|            |     | 4.2.2 Power Consumption                             |                 |

|            | 4.3 | Telemetry Link Evaluation                           |                 |

|            |     | 4.3.1 Transmission in Free Air                      |                 |

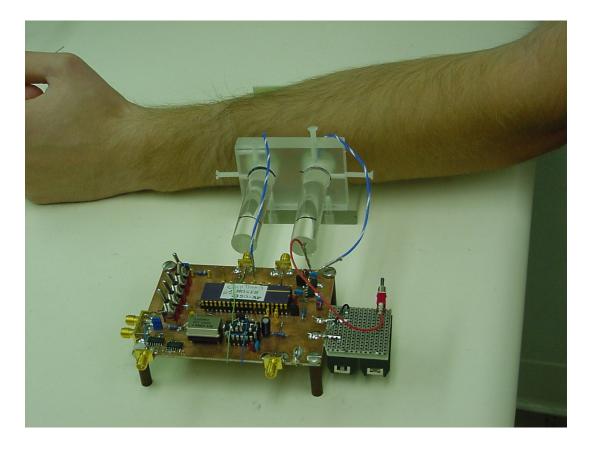

|            |     | 4.3.2 Transmission Through Tissue                   | 96              |

|            |     | 4.3.3 Partially Submerged Saline Bath               |                 |

|            |     | 4.3.4 Fully Encapsulated Tests                      |                 |

|            | 4.4 | Statistical Reliability Measurements                |                 |

|            | 4.5 | Additional Findings and Discussion of Limitation    | ıs111           |

|            |     | 4.5.1 Environmental Noise                           |                 |

|            |     | 4.5.2 Differential Drive Technique                  |                 |

|            |     | 4.5.3 Plate Orientation and Alignment               |                 |

|            |     | 4.5.4 Limitations for Implanted Applications        |                 |

| Chapter 5  | Con | clusion and Future Work                             |                 |

|            | 5.1 | Conclusion                                          |                 |

|            | 5.2 | Future Work                                         |                 |

|            |     | 5.2.1 Further Testing                               |                 |

|            |     | 5.2.2 System Improvement                            |                 |

| References |     |                                                     |                 |

| Appendices |     |                                                     |                 |

|            | Арр | endix 1 – Source Listing for Dummy Packet Gener     | ator127         |

|            | Арр | endix 2 – SPICE listing for Current Starved Inverte | er Amplifier138 |

|            | App | endix 3 – SPICE Listing for Slew Rate Limited An    | nplifier140     |

| Appendix 4 – Source Listing for FPGA-to-USB Interface144 |

|----------------------------------------------------------|

|                                                          |

Vita

## List of Tables

| Table 1.1: | Electromagnetic properties for high fluid content tissue         | 4   |

|------------|------------------------------------------------------------------|-----|

| Table 1.2: | Electromagnetic properties for low fluid content tissue          | 4   |

| Table 4.1: | Slew-rates for the tail-current controlled operational amplifier | .85 |

| Table 4.2: | Slew-rates for feedback controlled current-starved inverter      | .86 |

| Table 4.3: | Average power for various blocks                                 | .90 |

# List of Figures

| Figure 1.1: Basic model of an implanted capacitance coupled system                    | 13 |

|---------------------------------------------------------------------------------------|----|

| Figure 2.1: Schematic for time domain characterization test setup                     | 23 |

| Figure 2.2: Step response of the system                                               | 24 |

| Figure 2.3: Equivalent electrical model derived from the experimental setup           | 25 |

| Figure 2.4: One of the battery-powered oscillators used to simulate an implant        | 27 |

| Figure 2.5: Tank used in the improved experimental test setup                         | 28 |

| Figure 2.6: 1 <sup>st</sup> Order harmonic power versus distance and plate size       | 30 |

| Figure 3.1: Block diagram for complete system                                         | 33 |

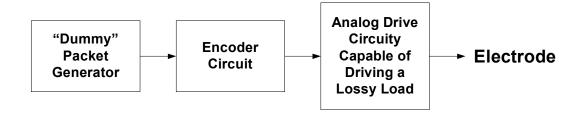

| Figure 3.2: Implant transmitter block diagram                                         | 35 |

| Figure 3.3: Layout of the dummy packet generator block                                | 37 |

| Figure 3.4: Simulated waveforms of "dummy" packets                                    | 38 |

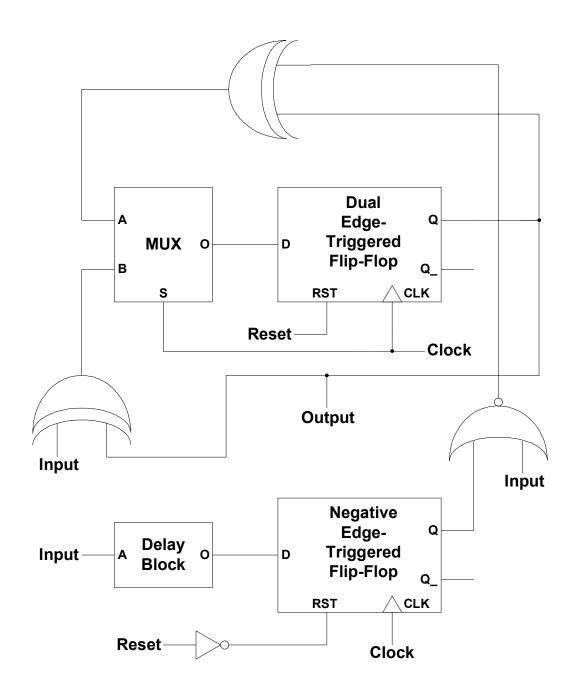

| Figure 3.5: Logic for the bi-phase mark encoder block                                 | 42 |

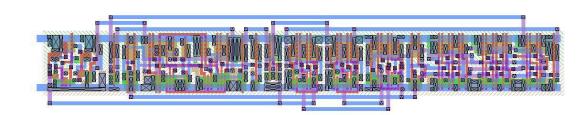

| Figure 3.6: ASIC layout of the bi-phase mark encoder block                            | 43 |

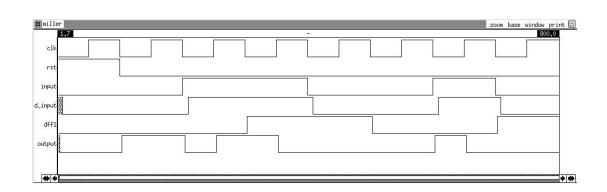

| Figure 3.7: Simulation of the bi-phase mark encoder block                             | 43 |

| Figure 3.8: Logic for the Manchester encoder block                                    | 44 |

| Figure 3.9: Simulation of the Manchester encoder block                                | 45 |

| Figure 3.10: Layout of the Manchester encoder block                                   | 45 |

| Figure 3.11: Logic for the Miller encoder block                                       | 47 |

| Figure 3.12: Layout of the Miller encoder block                                       | 48 |

| Figure 3.13: Simulation of the Miller encoder block                                   | 48 |

| Figure 3.14: Basic operational amplifier                                              | 50 |

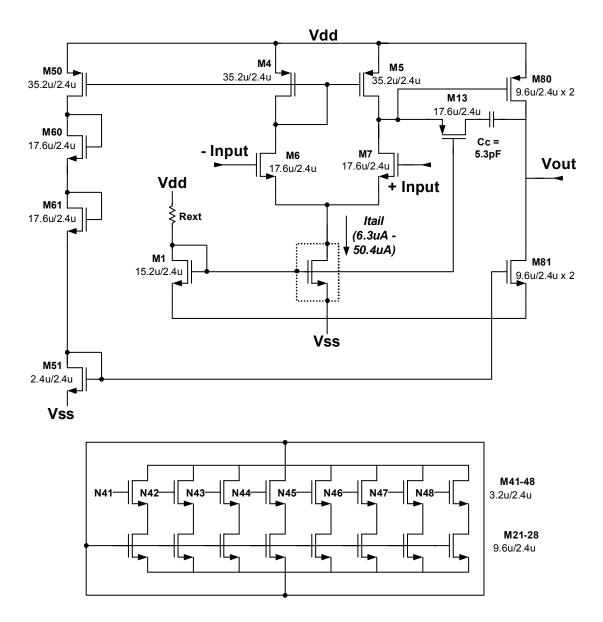

| Figure 3.15: Tail-current adjustable slew-rate controlled op-amp                      | 52 |

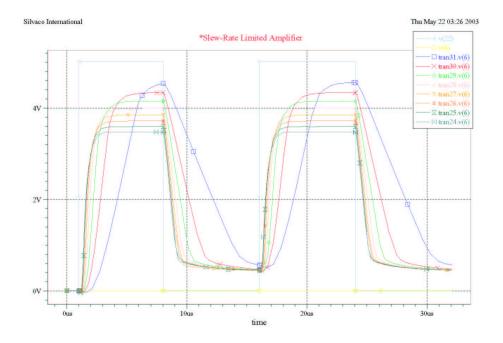

| Figure 3.16: Simulated slew range of tail-current limited amplifier (assuming a 100pl | F  |

| load capacitance)                                                                     | 53 |

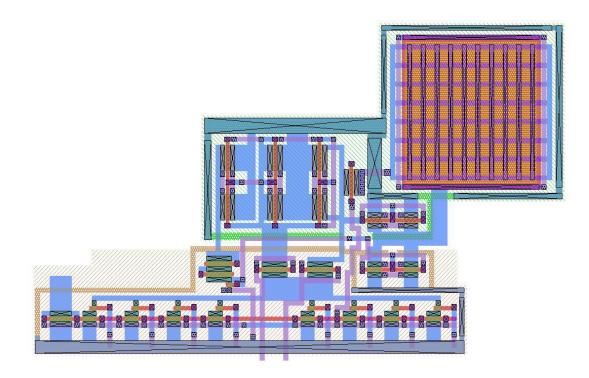

| Figure 3.17: Layout of the tail-current controlled adjustable slew-rate op-amp        | 54 |

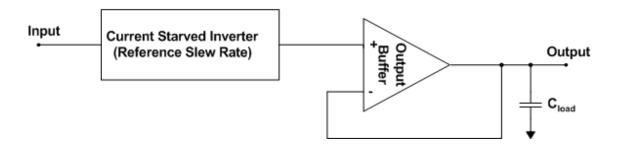

| Figure 3.18: Block diagram for a buffered current starved inverter                    | 55 |

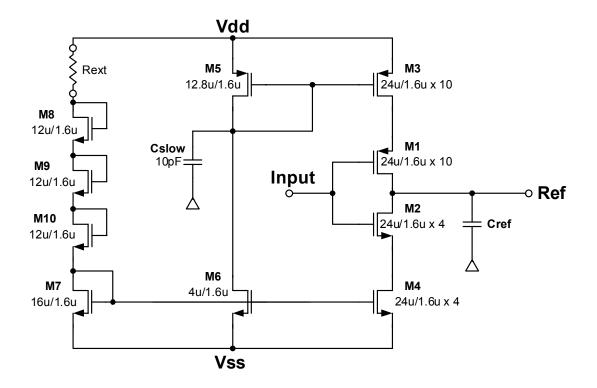

| Figure 3.19: Current-starved inverter reference slew-rate circuit                     | 57 |

|                                                                                       |    |

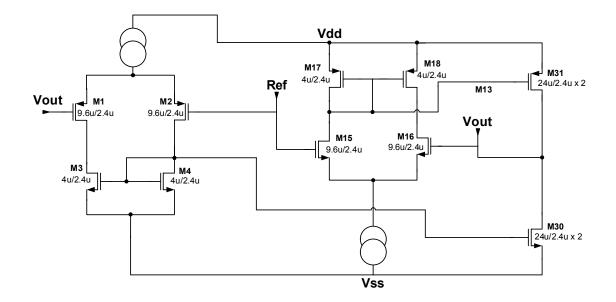

| Figure 3.20: Rail-to-rail output buffer                                                | 58   |

|----------------------------------------------------------------------------------------|------|

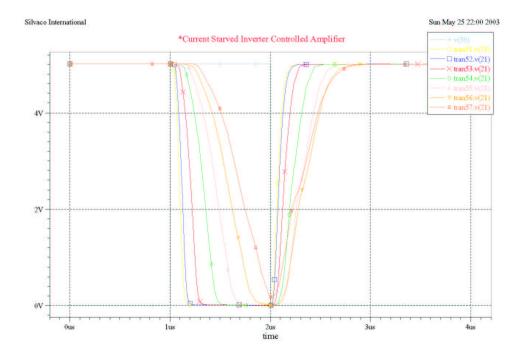

| Figure 3.21: Simulated slew range for a series of reference load capacitances and a bi | ias  |

| current of 7.25µA                                                                      | 59   |

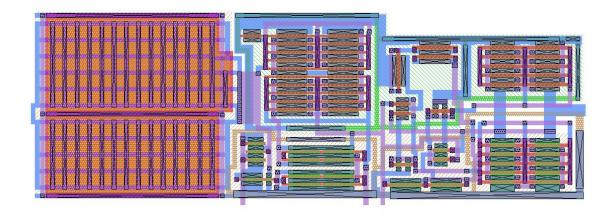

| Figure 3.22: Layout for buffered current-starved inverter                              | 60   |

| Figure 3.23: Block diagram of the external receiver                                    | 62   |

| Figure 3.24: The charge sensitive preamplifier used in the front-end                   | 63   |

| Figure 3.25: The process of decoding a bit                                             | 65   |

| Figure 3.26: The fabricated CapTran1 chip                                              | 67   |

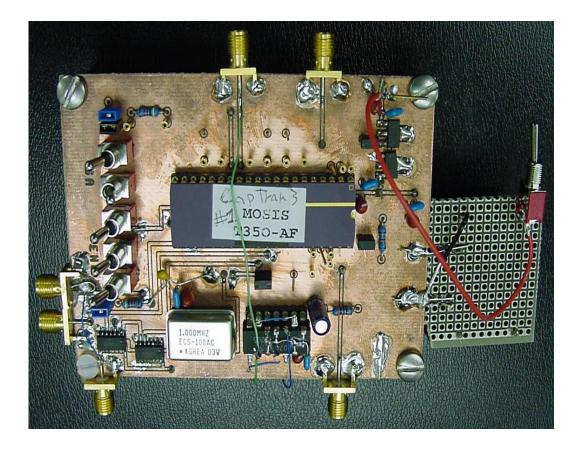

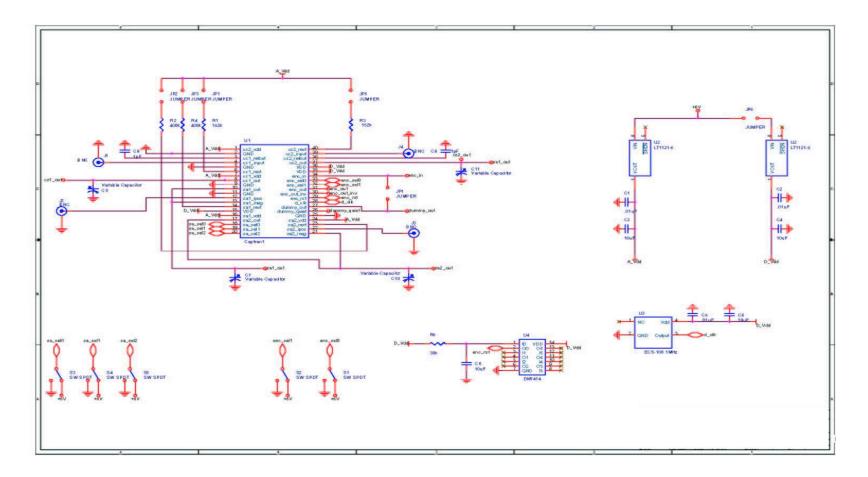

| Figure 3.27: The transmitter functionality test board                                  | 70   |

| Figure 3.28: Schematic of the transmitter functionality test board                     | 71   |

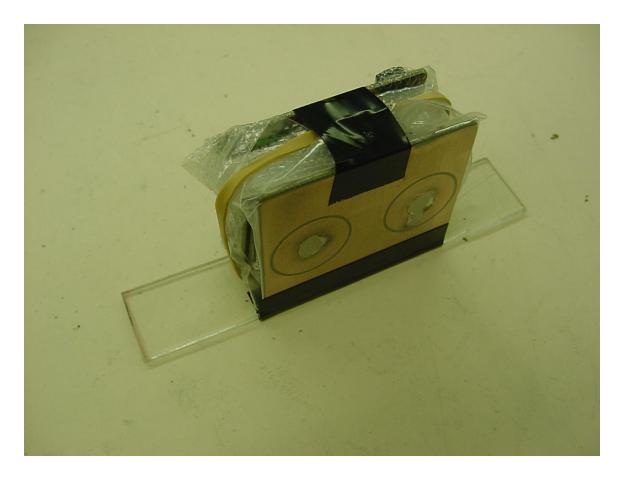

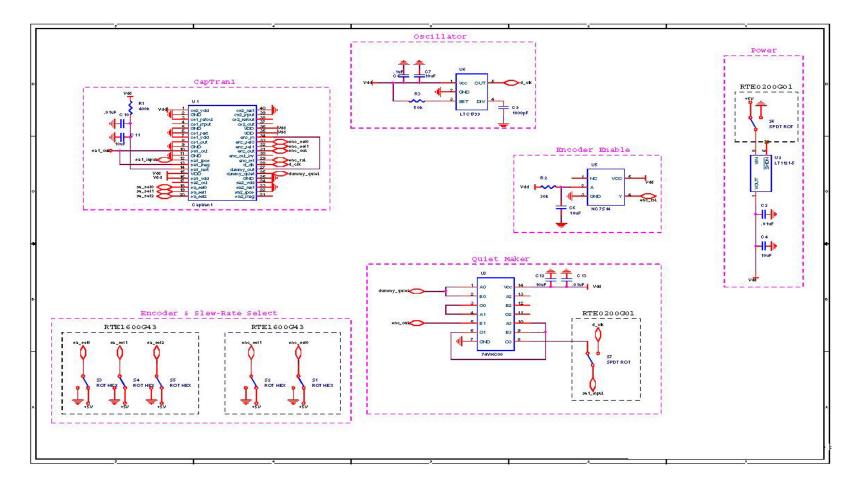

| Figure 3.29: The sealed mini-transmitter test unit                                     | 73   |

| Figure 3.30: Schematic of the mini-transmitter test board                              | 74   |

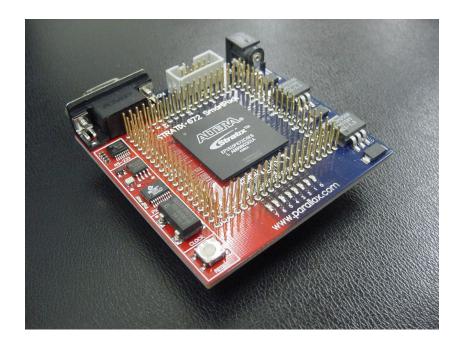

| Figure 3.31: The Stratix 672 SmartPack FPGA board used in the receiver                 | 76   |

| Figure 3.32: Parallel-to-USB interface board                                           | 78   |

| Figure 3.33: The LabVIEW program detecting an incorrect packet                         | 80   |

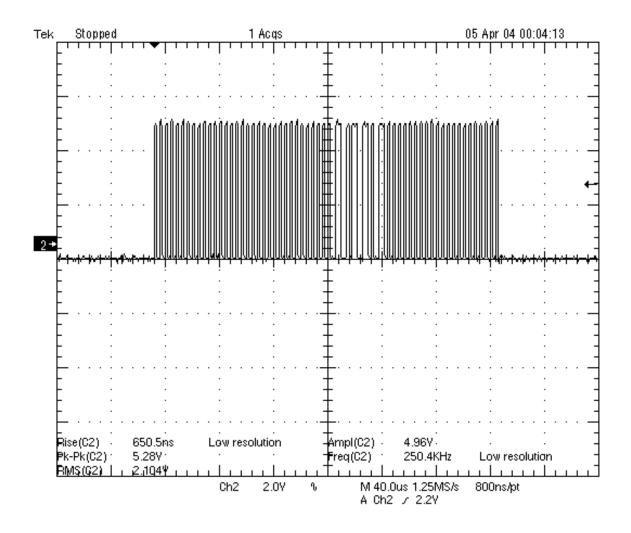

| Figure 4.1: An encoded packet generated by the "dummy" packet generator block          | 83   |

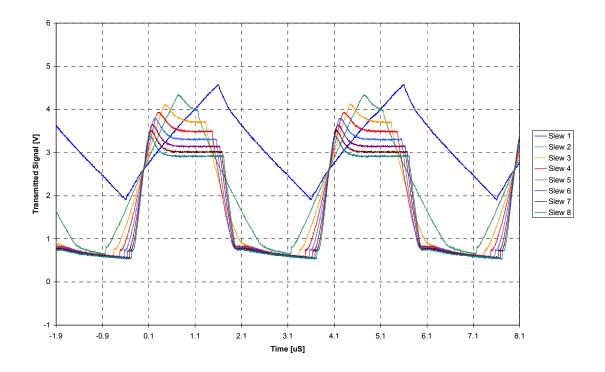

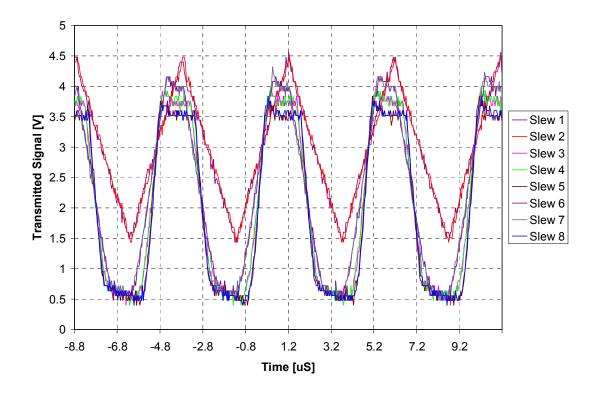

| Figure 4.2: Measured waveforms demonstrating the slew range of the feedback            |      |

| controlled current-starved inverter                                                    | 87   |

| Figure 4.3: Slew range of the tail-current controlled op-amp measured using a load     |      |

| capacitance of 100pF                                                                   | 89   |

| Figure 4.4: Free-air test setup                                                        | 93   |

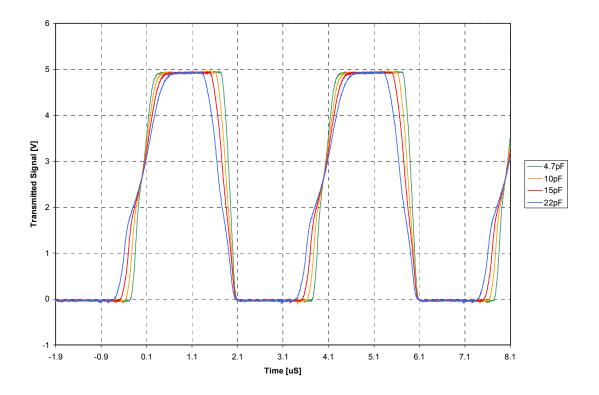

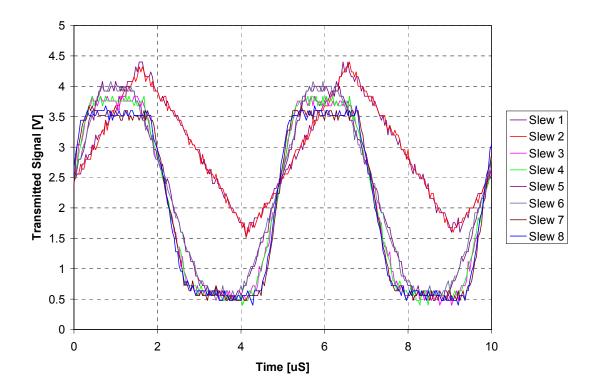

| Figure 4.5: Measured transmitter output waveforms showing adjustable slew range w      | /hen |

| loaded by free-air                                                                     | 94   |

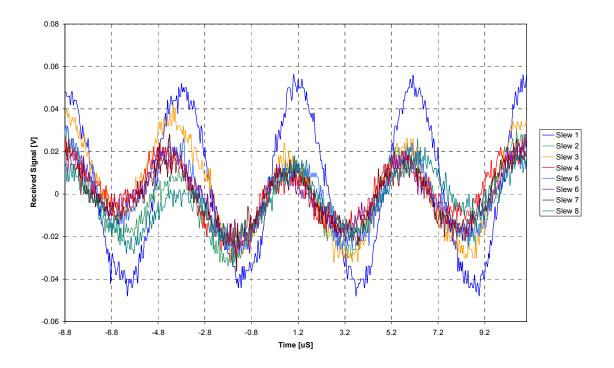

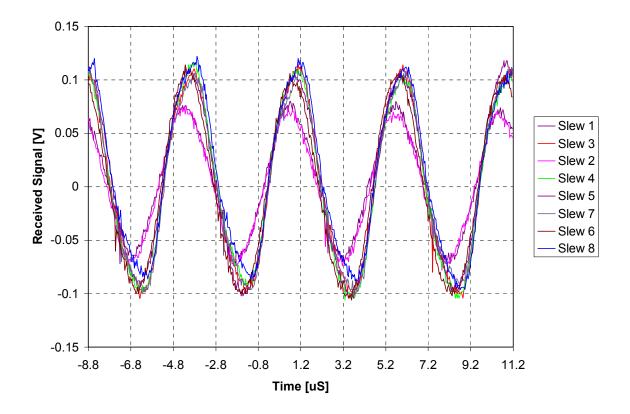

| Figure 4.6: Measured received waveforms for various slew-rates in free-air             | 95   |

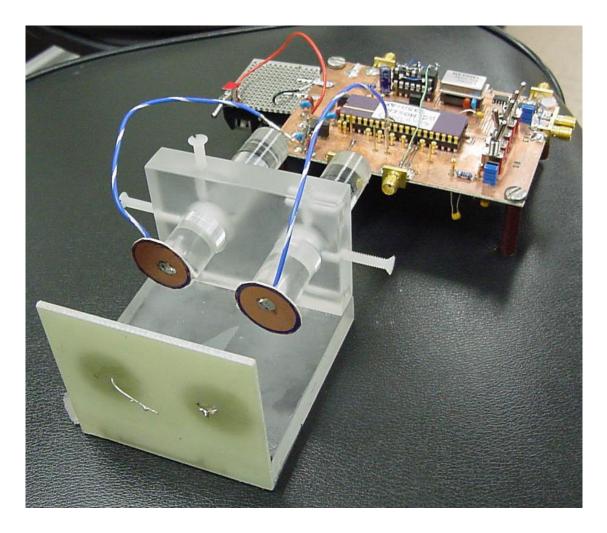

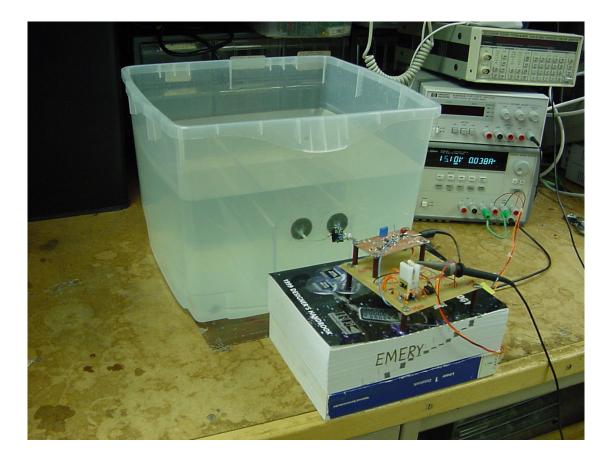

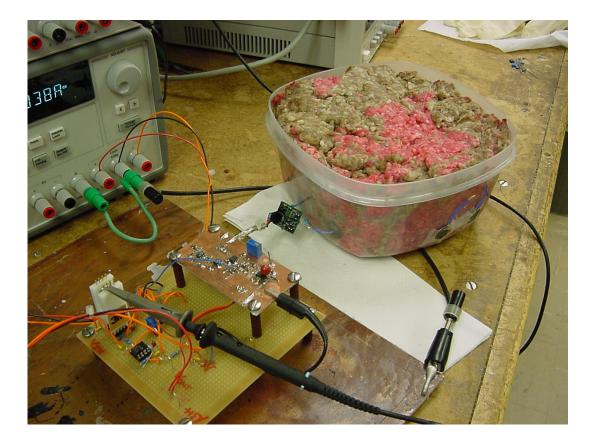

| Figure 4.7: Transmission through tissue test setup                                     | 97   |

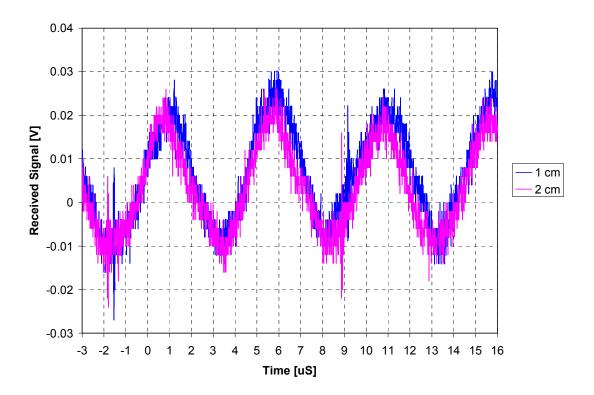

| Figure 4.8: Measured worst-case through-tissue received signals                        | 98   |

| Figure 4.9: Partially submerged saline bath test setup                                 | .100 |

| Figure 4.10: Measured transmitting waveforms demonstrating output slew range whe       | en   |

| loaded by saline                                                                       | .101 |

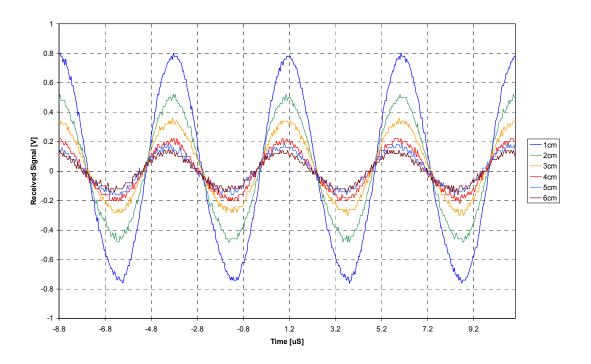

| Figure 4.11: | Received waveforms for various slew rates in partially submerged saline     |     |

|--------------|-----------------------------------------------------------------------------|-----|

| ba           | th                                                                          | 102 |

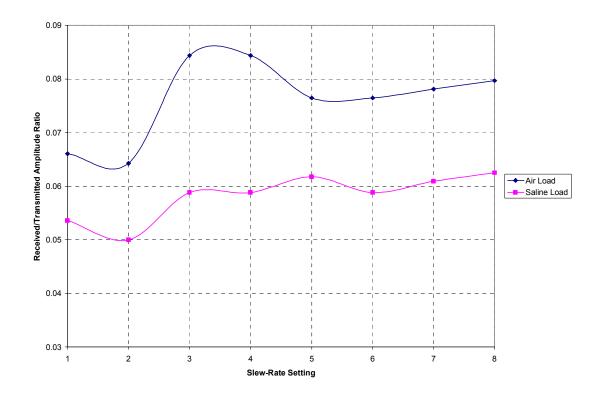

| Figure 4.12: | Ratio of received signal amplitude to transmitted signal amplitude for free | e-  |

| air          | load and saline load                                                        | 104 |

| Figure 4.13: | Saline encapsulation test setup                                             | 106 |

| Figure 4.14: | Tissue encapsulation test setup using ground beef                           | 107 |

| Figure 4.15: | Received waveforms for the fully encapsulated in tissue test setup          | 108 |

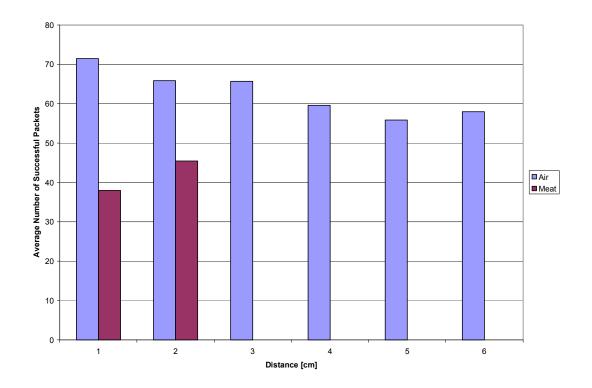

| Figure 4.16: | Average number of successful packets received for various distances, as     |     |

| tes          | sted in free-air and fully encapsulated in tissue                           | 110 |

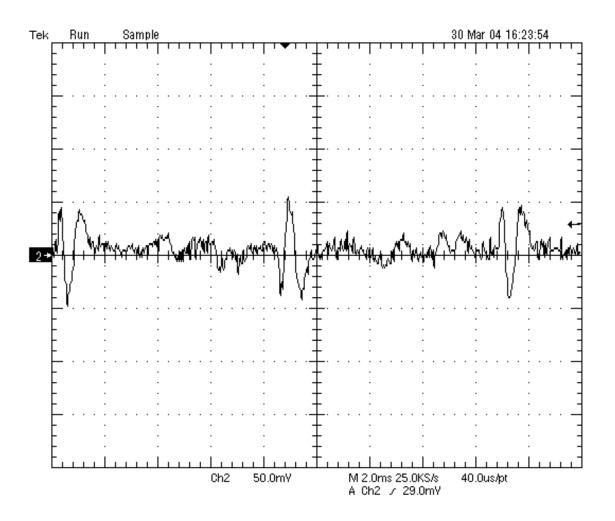

| Figure 4.17: | Common environmental noise as seen at the output of the receiver's gain     | 1   |

| sta          | age with no transmitted signal present                                      | 113 |

#### Chapter 1 INTRODUCTION

#### 1.1 Telemetry in Implantable Systems

Implanted sensors have been in use in some form for almost 50 years for measuring physiological parameters such as heart rate, electrocardiogram (ECG), electroencephalogram (EEG), temperature, pH, and various pressures [1]. Clinical applications of sensor-based implants are increasing rapidly as recent advances in Low Voltage, Low Power (LVLP) integrated circuits and sensing techniques are enabling new areas of monitoring including blood perfusion and neural activity [2, 3]. The earliest example of implantable controllable actuators is externally programmable pacemakers that became commercially available in the early 1980s [4]. Newer implant types include those for implantable drug delivery systems, urinary incontinence, pain management, movement disorders like Parkinson's disease, and retinal prostheses [5].

Wireless communication with implanted systems is preferred, as transcutaneous wires significantly increase the risk of infection and may cause a high level of patient discomfort. However, communicating wirelessly through the human body is a complex problem, the solution to which depends largely on the particular application. There is no universal communication system that is the optimum solution for every type of implant. Many limitations such as the implant's size, function, power consumption, implanted location, required telemetry distance, and patient environment play an important role in determining the optimum communication technique. Designing a communication system to meet all of these requirements is one of the most challenging aspects of implant design.

1

This chapter reviews many of the primary design challenges associated with data transmission through tissue and provides an overview of the primary wireless communication systems employed in modern implanted systems. An alternative technique based on capacitve coupling is introduced and compared to these more commonly employed methods.

#### **1.2 Biological Interaction**

For optimum results, any wireless system must be designed for an explicit transmission media. When designing a wireless system typically what is examined is how the transmission media influences the communication. The most common influence examined is how the media limits the transmission distance or in other words how far reliable communication can be achieved given a fixed amount of transmitting power. When designing a wireless system for communicating through tissue however, the problem is exacerbated: not only must the effects of how the tissue influences the communication be examined, but also how the communication affects the tissue. A wireless system that causes severe damage to surrounding tissue is not a valid solution for implant communication. The problem is made harder by the fact that the electrical properties of tissues are not uniform for all types of tissues. For example, the conductivity of fat for a given frequency can be twenty times or more than that of muscle.

The following subsections discuss the complicated two-way interaction of tissue and communications.

2

#### **1.2.1 Biological Effects on Communications**

Tissue can be separated into two general classes: tissues with high fluid content and tissues with low fluid content. The fluids contained in the tissue are composed of salt ions, polar protein molecules, and polar water molecules. Thus, the response of tissues to electromagnetic fields is largely dominated by ionic conduction, a phenomenon strongly coupled to fluid content. Conduction currents in the tissue are caused by the oscillations of free charges (ions) when a time-varying electromagnetic field is applied to the tissue. The rotation of the dipole molecules causes changes in the displacement currents. Ohmic losses and dielectric losses cause the power dissipation of the conduction and displacement currents respectively [5].

Tables 1.1 and 1.2 summarize the properties of high and low fluid content tissues, respectively. From these tables several trends can be established. The most important trend gathered from the tables is that for high fluid content tissues, such as those found in the abdomen, higher frequencies have a lower depth of penetration for a given transmitting power and are thus less efficient. These tables are meant as a general guide; more exact modeling can be accomplished through the use of detailed computer models of the human body [6].

#### **1.2.2** Communications Effects on Biology

The harmful effects of communication on the biological media can be broken down into three classes: interference, athermal biological effects, and thermal heating, and each of these poses certain limitations on the communication link.

| Englisher          | Wavelength    | Dielectric      | Conductivity | Wavelength            | Depth of    |

|--------------------|---------------|-----------------|--------------|-----------------------|-------------|

| Frequency<br>(MHz) | in Air        | Constant        | $ ho_{L}$    | in Tissue $\lambda_L$ | Penetration |

| (1/1112)           | ( <i>cm</i> ) | $\mathcal{E}_D$ | (mho/m)      | (cm)                  | (cm)        |

| 1                  | 30000         | 2000            | 0.400        | 436                   | <i>91.3</i> |

| 10                 | 3000          | 160             | 0.625        | 118                   | 21.6        |

| 1000               | 30            | 50              | 1.7          | 2.8                   | 2.4         |

| 10000              | 3             | 39.9            | 10.3         | 0.46                  | 0.34        |

Table 1.1: Electromagnetic properties for high fluid content tissue

Table 1.2: Electromagnetic properties for low fluid content tissue

| Frequen | Wavelength | Dielectric      | Conductivity | Wavelength            | Depth of    |

|---------|------------|-----------------|--------------|-----------------------|-------------|

| су      | in Air     | Constant        | $ ho_L$      | in Tissue $\lambda_L$ | Penetration |

| (MHz)   | (cm)       | $\mathcal{E}_D$ | (mho/m)      | (cm)                  | (cm)        |

| 1       | 30000      |                 |              |                       |             |

| 10      | 3000       |                 |              |                       |             |

| 100     | 300        | 7.45            | 19-76        | 106                   | 60.4        |

| 1000    | 30         | 5.6             | 71-171       | 8.4                   | 13.9        |

| 10000   | 3          | 4.5             | 324-549      | 1.4                   | 3.4         |

The first of these effects occurs when electrical signals are either directly interfering with a natural biological signal or when parts of the body misinterpret the electrical signal as a natural biological signal. However, because natural biological signals are generally in a very low frequency range (DC to approximately 3 KHz) this type of effect is easily preventable [7].

The second of these effects, athermal biological effects, is a general classification of non-thermal biological responses to electromagnetic fields. These effects include plasma membrane damage within cells, immune system changes, neurological effects, behavioral effects, interaction of certain drug and chemical compounds to electromagnetic fields, action potential disturbance, and effects on DNA [8]. While studies have shown that very high levels of electromagnetic fields can cause these effects [5], they have not shown conclusive evidence that low level exposure to electromagnetic fields is harmful.

The third and most common type of effect is thermal heating. The energy needed to produce thermal heating comes from the power dissipation of the electromagnetic wave in the tissue through both Ohmic and dielectric losses. The operation of Microwave ovens is dependent on this same principle. The quantity used to characterize the absorption of electromagnetic energy is known as the specific absorption rate (SAR), and is expressed in the units of watts per kilogram (W/kg).

Any dissipation of RF energy will cause some amount of thermal heating, but this heating is only harmful when the amount of heating becomes greater than that associated with the natural metabolic rate of the body, or approximately 1 Watt/kg. The FCC

mandated limit for RF exposure is 0.4 W/kg for the whole body under controlled conditions, and 8 W/kg for only partial of the body exposure [8]. Exceptions are made for certain body parts such as the ankles, wrists, hands, and feet which can have higher exposure rates, and the eyes and testes, which have lower exposure rates due to their relative lack of available blood flow to dissipate excessive heating.

#### **1.3 Current Wireless Implant Biotelemetry Methods**

The following subsections summarize current approaches for implant communications: standard Radio Frequency (RF) techniques based on Amplitude Modulation (AM), Frequency Modulation (FM), and other modulations, inductive RF approaches for data and power transfer, load or passive reflection modulation, spread spectrum approaches, and techniques based on current injection.

#### **1.3.1 RF Approaches Based on Common Modulation Techniques**

Narrow band RF data transmission is one of the most common techniques employed in biotelemetry. Of the modulation techniques used in narrow band transmissions, one of the most common in implanted systems is frequency modulation (FM). FM-based approaches are attractive because they are less sensitive to received signal strength than some other approaches, thus the movement of the internal and external antennae in relation to each other does not affect signal recovery. This is one reason why an FM-based approach was popular in early implants where analog data was directly transmitted [1]. The transmission of digital signals has seen the rise of several other modulation techniques employed in implanted systems, namely on-off keying (OOK) [9], amplitudeshift keying (ASK) [10,11], phase-shift keying (PSK) [12], and frequency-shift keying (FSK) [13]. Although ASK is the simplest to implement, the FSK and PSK offer increased robustness to noise, making them attractive for certain applications.

#### **1.3.2 Inductively Coupled RF Power**

Inductive data and power transfer works by the principle of a time-varying magnetic flux density producing electrical energy, as described by Faraday's law:

#### $\mathbf{V} = -\mathbf{N} \partial \Phi / \partial t$

Generally, a loop antenna (also known as the primary coil) is used to create the time-varying magnetic flux by having a time-varying current applied to it (Ampere's law). This in turn is coupled to another loop antenna (or the secondary coil) of N turns that converts the flux to a voltage.

The amount of flux that is successfully coupled depends on a number of different factors, the most important being the coil sizes and number of turns, coil separation distance, alignment of the coils, and the transmitted frequency. In an implanted system, each of these factors is limited by either the implant's physical requirements or by limitations imposed by the surrounding biological media. The limitation on the implant's size sets a maximum limit on the size of the secondary coil. However, tethering the secondary coil from the implant and positioning it on the surface can minimize the separation distance and improve alignment between the secondary coil and the primary coil placed on the skin. The transmitted frequency is a compromise: higher frequencies transfer more power because of the higher time derivative of the magnetic flux, but higher frequencies also have more loss in tissue, as described in section 1.2.1. Typically a transmitting frequency around 2MHz is used for power transfer [14].

Information from the external unit to the implant can be easily piggybacked on the transmitted power signal by modulating the signal. Information may be transmitted from the implant to the external unit through a variety of methods, but usually one of three methods is employed: an additional RF transmitter and antenna is used (see section 1.3.1), a passive load-modulation technique is used (see section 1.3.3), or a very short return pulse is sent using the secondary coil as the transmitting antenna [15]. In the last case the transmitting and receiving roles of the coils are reversed, although much less power is transmitted from the implant compared to the power transmitted from the external unit. Pulse position modulation (or varying the time when the return pulse is transmitted) is the most common modulation technique used when this method is employed.

#### **1.3.3 Passive Load-Modulation**

Load-modulation techniques control a change in reflected impedance between two coupled elements to transmit information passively to a receiver. In such a system, the receiver transmits a RF signal that is coupled in the near field to an implant whose load is modulated. Typically both the transmitter and receiver are inductively coupled coils. Shunting of the implanted coil to ground causes a change in reflected impedance seen by the receiver, enabling data communication. This technique is becoming more common in implant biotelemetry [5]. Application of this technique to implant biotelemetry was initially used in animal implants before becoming more common in human implants [16]. The foremost advantage this technique offers is the ability to providing power to the implant while using the backscattered RF signal for data communications. This technique is especially useful in simple, very low power implants such as RFID tags used for tracking and identification of individual animals [17]. The drawback is the same as any inductively coupled technique: reliable communication (and power transfer) can only occur if the coils are sufficiently coupled. This can be easily seen from the quadratic dependence of the coupling factor in the equation for the reflected load impedance,

### $Z_{ref} = (1-k^2)/j\omega C_P + (L_P/L_S) * R_{load}k^2$

Here *k* is the coupling factor,  $C_P$  is the primary capacitance,  $L_P$  is the primary inductance,  $L_S$  is the secondary inductance, and  $R_{load}$  is the secondary load [5]. The coupling factor has a large dependence on both the shape of the coil (where larger is better) and the distance between the two coils (where shorter is better). These factors together limit the implant to either shallow implantation depth or fairly large size.

One novel variation of this technique is in using thin-wire dipoles coupled to the electric field components of an external electromagnetic signal rather than using the standard inductively coupled coils [18]. This offers the advantage that the antenna dimensions are reduced to one dimension rather than two, but there is a drawback in that frequency choices become limited due to realistic limitations on antenna size. For some applications, however, a long, thin antenna could be appropriate. In order to make the antenna length reasonably short, a higher transmitting frequency (and thus shorter

wavelength) must be used. This is complicated by two factors. The first of these, as was shown earlier in this chapter, is that higher frequency signals have a lower depth of penetration in a high water content biological medium. The second complication, unlike inductive backscatter modulation techniques, is that the returned signal is actually a reflected second harmonic of the transmitted signal. This compounds the problem of balancing frequency and the resulting depth of penetration versus antenna length.

#### **1.3.4 Direct-Sequence Spread Spectrum**

Spread spectrum communication systems can be described by three basic parameters [19]:

- The transmitted signal is spread over bandwidth much greater than the bandwidth needed to transmit the information.

- The transmitted bandwidth is determined by some function that is independent of the information that is transmitted.

- The receiver uses the same function to recover the transmitted data, and does so in a synchronous manner with the transmitter.

In Direct-Sequence Spread Spectrum (DSSS) these parameters are met by first modulating the data by a pseudo-random code, otherwise known as a spreading code, operating at a much higher clock frequency than the data. The resulting data is then modulated to the desired frequency and transmitted.

The standard advantages of a spread spectrum to other applications also apply to implant applications: namely a much greater reduction in interference with other signals, especially narrow band signals. The opposite is also true; the transmitted spreadspectrum signals are themselves more resistant to interference caused by narrow band signals operating in the same frequency space. This could prove especially advantageous in situations where multiple implanted transmitters need to share the same frequency space and non-interference is imperative (such as a pacemaker coexisting with a pain management implant).

The use of DSSS in implant biotelemetry applications is currently limited. A search of current literature produced two examples. The first is an ingestible capsule used for real-time monitoring of the gastrointestinal tract that discusses a DSSS communication system for one-way data transmission from the implant [20]. However, although this work discussed a DSSS scheme, it did not actually implement this scheme but instead used a narrowband RF approach. The second example is research in progress involving real time transmission of data for an implanted tissue profusion monitor at Oak Ridge National Laboratory [21].

#### **1.3.5 Directly Coupled Current Injection**

One new interesting and significantly more esoteric implant biotelemetry approach is the technique of directly coupling currents to the tissue [22]. In this technique platinum electrodes are connected to the implant, with one electrode driven by a fixed amount of current and the other electrode serving as a ground. The injected current produces voltage differences when measured at the skin in multiple places by an electromyogram (EMG) amplifier. This technique directly takes advantage of the ionic conduction properties of the tissue. Unlike the approach proposed by this thesis, however, directly coupling current into the tissue has a much higher risk of biological stimulation. Indeed, in the previously cited work between 1 and 3 mA of current were injected into the tissue, which may impact the physiological measurements of interest. Likewise, the relatively high currents prevent this from being a useful low-power technique.

# 1.4 Communication Via Capacitive Coupling for Biotelemetry Applications

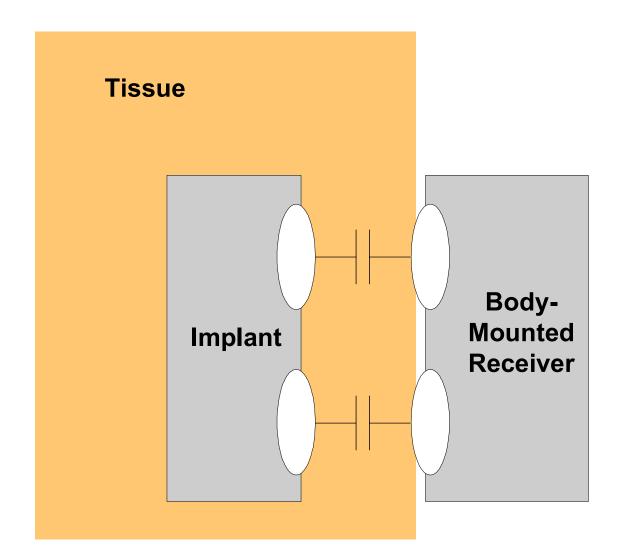

Unlike most of the previously described techniques, the work described in this thesis is not a modulated RF technique. Instead, an unmodulated baseband technique using a capacitive link between the implant and a body-mounted receiver was investigated. This technique treats the tissue as a lossy capacitor. The crux of this system is comprised of two transmitting plates capacitivley coupled to the tissue and two like-coupled body-mounted receiving plates, with the tissue in between these sets of plates acting as the dielectric for the capacitor. The basic model for this system is shown in Figure 1.1.

#### **1.4.1 Previous Capacitive Coupling Work**

While communication via capacitive coupling is certainly not novel, applying this approach to an implant is. Communicating via a capacitive link has been used in many applications, from very short-range high-speed links between microchips [23] to relatively long-range links for communication between rooms for audio/visual equipment [24].

Figure 1.1: Basic model of an implanted capacitance coupled system

The closest application of this type of link to an implantable type is in the work done by Thomas Zimmerman in developing personal area networks where the communications backbone is a capacitive link [25]. However, in this case the data is capacitivley coupled to the skin with one electrode, and the skin is used as a conductor for coupling to another skin-mounted electrode. The ground return for this system is through the air. In this thesis both the transmission and ground links are through the tissue. One set of plates is attached to the implant and the other set is in contact with the skin, attached to a body-mounted receiver.

#### 1.4.2 Capacitance-Based Approach Compared to Other Techniques

As compared to the other techniques, communication via capacitive coupling offers several distinct advantages and disadvantages. The following subsections briefly describe the advantages and disadvantages associated with this approach.

The first distinct advantage is the use of no off-chip passive components. Unlike RF systems, the only components this technique uses that are external to the chip are the plates used in the capacitive link. However, clever use of the implant package can assuage even this limitation.

The second distinct advantage is in the limited chip area needed to implement this approach. The reason for this comes primarily from the fact that this is an unmodulated baseband technique. All that is effectively needed to implement this approach is an encoder to encode the outgoing data and an analog drive circuit to shape the transmitted waveform. The logic needed for the encoder can be made relatively compact and the

analog drive circuitry is essentially just an op-amp, so the size of each of these can be made quite small.

The third distinct advantage to this approach is that it is relatively simple to implement compared to RF approaches. This also comes from the fact that it is an unmodulated baseband technique. The significantly lower complexity compared to RF techniques means that its implementation can be accomplished more quickly and with fewer components.

One of the goals in the design of this technique was to make the power consumption rival that of comparable battery powered RF techniques. Obviously this technique cannot rival the power consumption (or lack thereof) of inductively powered links. The state of the art power consumption for a battery powered RF link is approximately  $1\mu$ W [5]. One of the goals of this work was to evaluate if a comparable result could be achieved.

The primary limitation in terms of power consumption for a capacitive coupled link is in the slew-rate of the transmitted signal. The equation for the slew-rate of a purely capacitive system is defined as

#### dVc/dt = I/C

Here dVc/dt is the slew-rate, *I* is the current, and *C* is the capacitance. For lower current and thus lower power slew-rate must therefore be minimized. If the load was purely The practical limit of this is determined by the desired transmission rate of the system; a slower transmission rate minimizing the slew-rate allows for lower power

consumption. For this reason this technique is well suited for low-speed unmodulated baseband approaches.

Communication via capacitive coupling through tissue places two major limitations on implant design. The first of these is in the effective range of communication. Because of the nature of the link, the communication distance via capacitive coupling is limited to the distance from the implant to the skin. In other words, by its very nature the receiver must be mounted to the body. Also, depending on plate size and the size of the patient, the implant depth is limited. In the worst-case scenario of a morbidly obese person, the maximum implant depth could actually not extend to the desired organ.

The first of these range limitations can be overcome through the use of a bodymounted repeater using an RF link. In this case the body-mounted receiver would be nothing more than a relay station to some other station where any necessary data analysis and storage would take place. The second of these limitations can be overcome by adequate plate sizing for particularly large patients.

The second major limitation communicating via capacitive coupling places on implant design is on the size of the implant. The effective range for communicating via capacitive coupling is directly influenced by the plate size. As a function of this, the primary limitation the capacitive coupling technique places on implant size is the size of the plates used. Empirical testing results of plate sizes are presented in Chapter 2, but generally speaking implant depth for plates much smaller than 1cm diameter would be severely limited. Thus for a very small implant this technique is not a valid solution.

16

However, for a medium sized implant creative use of the implant casing can easily provide relatively large plate sizes.

#### 1.5 Justification for Research

As demonstrated, a number of different techniques have been reported. This thesis reports the first application of a capacitance based communication technique to implanted sensors. There is no universal communication system that works for every type of implant. A communication system designed for use by a relatively large battery powered implant would not be appropriate for a small externally powered implant. In presenting the work done for this thesis the intent is to provide another option to the implant designer when choosing a communication technique. This communication technique was designed for a medium sized (on the order of the size of a pacemaker or smaller), battery powered, and short-range implant. While other techniques may offer other advantages, what this technique offers is a low number of off-chip passive components, low on-chip silicon area requirements, and relatively simple implementation.

#### 1.6 Scope of Thesis

This thesis describes the development of a capacitance-based biotelemetry system for implantable applications. This system consists of two distinct parts: the implanted transmitter and the external receiver. The prototype transmitter is based on a custom ASIC fabricated using the AMI 1.5µ process available through MOSIS. This ASIC encodes and transmits predetermined data packets by driving two electrodes in a slew-controlled manner, all contained within a biocompatible material. The receiver consists of charge-sensitive front end using a discriminator to distinguish individual bits. A FPGA decodes the transmitted data and relays it to a PC-based LABVIEW interface.

In Chapter 1, a review of many of the primary design challenges associated with data transmission through tissue are presented. Also, an overview of the primary wireless communication systems employed in modern implanted systems is provided. Finally, an alternative technique based on capacitive coupling is introduced and compared to the previously discussed techniques.

Chapter 2 details the initial sensor design and evaluation. The first approach to characterize the medium is discussed. This includes simulation and experimental results from this method. A second method for simulating the medium is then developed. From this method, optimum electrode configurations are determined. A discussion of the various electrode configurations is presented along with experimental data to conclude why the particular electrode configuration was chosen.

Chapter 3 presents the system design and implementation. The chapter begins with an overview of the complete system. Next, each of the individual blocks in the transmitter and receiver are discussed in detail. This includes a justification for why a particular design for each block was chosen and in some cases presents alternate designs that were also implemented. The design, simulation, and implementation of the

18

transmitter as a custom ASIC is also presented. Finally, the design and implementation of the receiver is given.

Chapter 4 details the testing of the system. Three different test setups were created to test the system. Each of the three setups are first described, then the various test results such as successful data link range, slew-control results, and power consumption from each setup are explored.

Chapter 5 presents the conclusions of the testing and discusses improvements that could be made.

#### **Chapter 2** MODELING CAPACITIVE COUPLED BIOTELEMETRY

#### 2.1 Modeling Human Tissue

Successful design of any implantable communication system requires the use of a suitable model for the human body. These models are classified into two types: computer-based models and physical experimental models. One major problem with building accurate system models for either of these types comes not in the modeling of single tissue types, but in how to model complex structures composed of multiple tissues with significantly different electrical properties. Although solutions to this problem exist for both model types, they are not always appropriate for early prototyping.

For computer-based models, highly detailed human body models and simulator packages such as the XFDTD High Fidelity Body Mesh from Remcom are available. These packages have emerged primarily in response to the need for accurate prediction of the interaction of electromagnetic fields with biological tissues specifically for evaluating compliancy to federal FCC guidelines [26]. However, after evaluation, the Remcom package was not used directly in this research for two reasons. First, the XFDTD package was specifically designed for RF simulations with waveforms of 500 MHz or more, and not low frequency baseband signals as are employed in this research. Consequently, simulation times were extremely lengthy (on the order of a day or more) and frequently produced failed simulations. The second reason was that software with this level of detail is much more useful for fine-tuning working systems than for evaluating prototype systems. Advanced physical models suffer from the same complexity problem. Obviously the most accurate solution is to use either a live animal or a human corpse, but neither of these options is suitable for quick prototyping where repeated implantation over fairly long periods of time is desired. The common solution is to use a compound that fairly accurately imitates the electrical properties of tissue for a given frequency (otherwise known as a phantom tissue). Phantom tissues can be broken down into two different types: solid cast forms and liquids. The chemical composition for solids with the electrical characteristics of a variety of tissue types at various frequencies has been documented [26]. These can be layered to create a more detailed simulation. Very detailed body forms made up of these materials are commercially available [27]. Liquidbased phantom tissues are generally saline-based solutions of varying salt concentrations. Although it is inherently harder to layer liquid-based phantoms, they are easier to produce and being liquids naturally conform to the device under test.

For this research a single-concentration saline-based solution was used as the primary test setup. Although this only offers a first order approximation at best to modeling the human body, it is suitable for prototyping functionality rather than making subtle adjustments in performance. Saline was chosen under the assumption that blood dominated tissues will comprise most of the tissues surrounding the implant. Furthermore, it is assumed that these tissues provide the worst-case scenario for transmission, as they are the lossiest. Both saline and blood have dielectric properties that reflect their ionic conduction nature. Adjusting the salt concentration per mass in

21

saline to approximately 0.8% produces a relative conductivity for low frequencies that is the same as blood [26].

The next section describes the equivalent circuit model extracted from an initial experimental test setup. In the third section an improved experimental setup is presented. The experimental setup used addresses some of the issues not addressed by the first setup, and helps lay the foundation of the problems the custom ASIC will need to solve.

#### 2.2 Establishing an Equivalent Electrical Model

With saline chosen as the experimental medium one of the first steps that was performed was to establish an equivalent electrical model. However, what was desired was not a model based on the frequency response of the saline but on the time domain response. Characterization in the time domain rather than the frequency domain is natural when dealing with an unmodulated baseband communication scheme. This is because with an unmodulated baseband approach the designer is principally interested in is the step response of the system, not the frequency response. Thus the goal in this case was to establish an electrical model with a step response similar to that of the medium, not necessarily one with a similar frequency response.

The key assumption in building this model is that saline behaves like a capacitor with extreme dielectric absorption. Thus, the model chosen for the saline was the Dow model of a dielectric absorptive capacitor. The method chosen to verify this model was to first find the experimental step response of the system. Then, via numerical analysis, the parameters of a Dow model of a dielectric absorptive capacitor were fitted to produce a matching step response [28].

### **2.2.1** Time Domain Characterization Test Setup

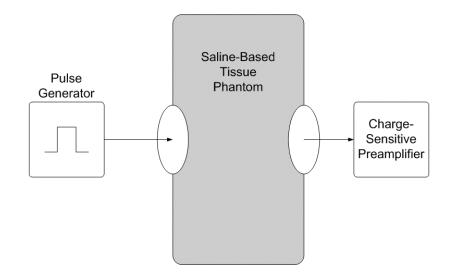

The initial test setup consisted of two copper electrodes pressed against a phosphate buffered saline-based tissue phantom as shown in Figure 2.1. Each electrode was 15mm in diameter and the separation distance was approximately 20mm. One electrode was connected to a pulse generator and the other to a charge-sensitive preamplifier.

## 2.2.2 Step Response

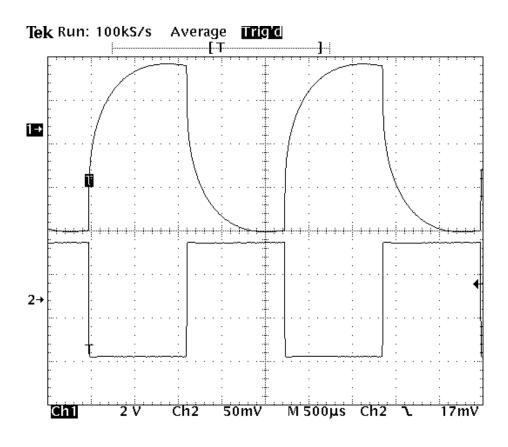

The step response for the experimental setup is shown in Figure 2.2, where the upper trace is the output of the charge sensitive preamplifier and the lower trace is the input from the pulse generator. As expected, this response is similar to that of a capacitor with a large amount of dielectric absorption.

Figure 2.1: Schematic for time domain characterization test setup

Figure 2.2: Step response of the system

## **2.2.3 Equivalent Electrical Model**

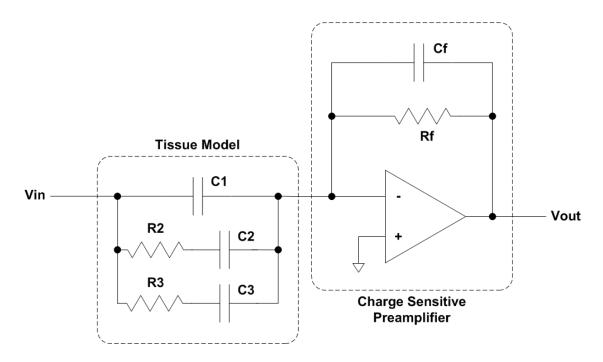

Based on the experimental step response, the electrical model given in Figure 2.3 was developed, where the saline is modeled as a third-order absorptive capacitor. The values for the feedback capacitor and resistor of the charge sensitive preamplifier are 2.3pF and 978.3M $\Omega$  respectively. Numerical analysis was performed to fit the values of C1, C2, C3, R2, and R3 to produce an approximately matching step response. These values were 0.208pF, 1.477pF, and 0.861pF for C1, C2, and C3. Approximate fits for R2 and R3 were 1.156M $\Omega$  and 95.6M $\Omega$ . Obviously, adjusting any parameters in the experimental test setup such as plate size or transmission distance would change the fitted values, but this does verify that indeed saline (and thus human tissue) can be modeled as a extremely dielectric absorptive capacitor.

Figure 2.3: Equivalent electrical model derived from the experimental setup

## 2.3 Establishing a More Accurate Experimental Setup

While the experimental test setup detailed in the previous section is useful for establishing an equivalent electrical model for saline, there are two issues it fails to address. The first of these is that with the first test setup there is an explicit hardwired return path between the pulse generator and the charge sensitive preamplifier. Ideally for a real-world implant there is no transcutaneous ground wire connecting the ground of the implant with that of the receiver. The second issue is that for an actual implant the tissue does not just act as a wall in front of the implant but completely surrounds the implant.

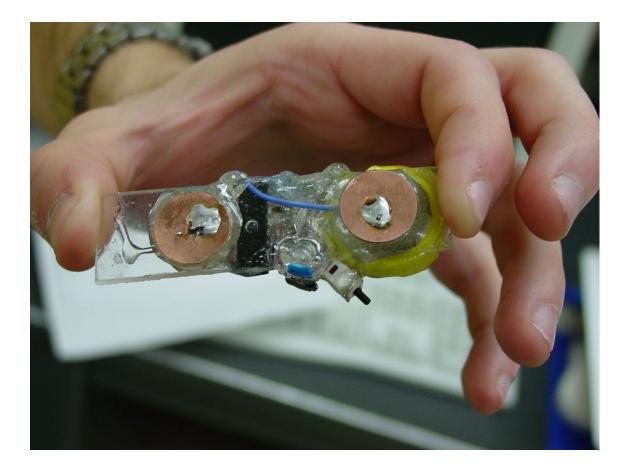

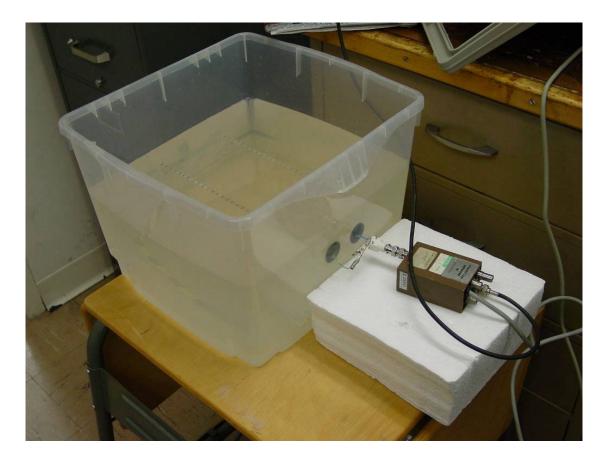

The second test setup addressed these points in two ways. First, a batterypowered oscillator replaced the pulse generator. To establish a return path a second electrode was added to both the oscillator and receiver. One of the test oscillators used is shown in Figure 2.4. Second, a tank was constructed to completely submerge the oscillator in phosphate buffered saline. This tank volume was substantially larger than the glove used in the previous experiment, measuring slightly over 1 ft<sup>3</sup>, to better approximate a human torso. Also, the oscillator could be positioned accurately at fixed distances from the receiving electrodes in the tank through the use of a marked track. This tank is shown in Figure 2.5.

### **2.3.1 Summary of Test Results**

Besides just offering a proof-of-concept, the new setup allowed for the testing of several new parameters establishing better empiric characterization of the transmission method.

Figure 2.4: One of the battery-powered oscillators used to simulate an implant

Figure 2.5: Tank used in the improved experimental test setup

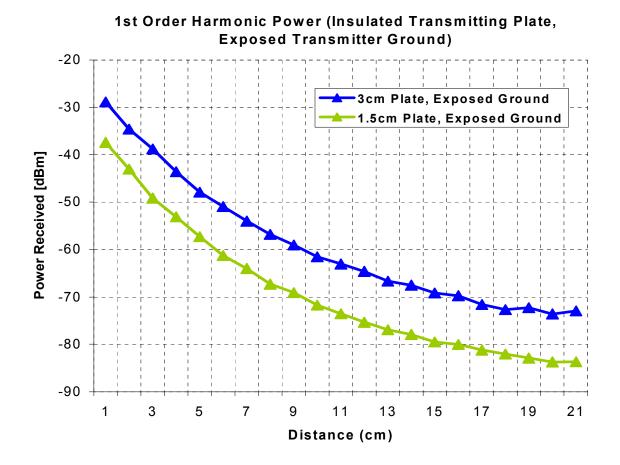

The first was the distance of the transmitting electrodes from the receiving electrodes. The second was the size of the transmitting and receiving electrodes. The third was the electrode isolation. To test these parameters the output of the charge sensitive preamplifier was connected to a spectrum analyzer. The received power at the fundamental harmonic was measured while each parameter was adjusted. As expected, both plate size and separation directly affects the received power. Figure 2.6 clearly shows the effects of each of these: First, doubling the receiving electrode plate diameter (or quadrupling the area) produces a 10 times increase in received signal power. Second, received signal power drops approximately with the square of the distance.

Changing the electrode isolation also revealed interesting results. Hypothetically each electrode can be either insulated from the saline or directly electrically connected to the saline. However, certain configurations are more desirable than others from a biological compatibility standpoint, namely those configurations where both implant electrodes are insulated. Also, certain configurations change the nature of the transmission. For instance, directly coupling the transmitting electrode to the saline is no longer communication via capacitive coupling but instead directly coupled current injection, as described briefly in Chapter 1. It was found that with the receiving ground electrode directly connected and the receiving electrode insulated, reliable transmission could be seen with both of the implants electrodes insulated. Exposing the transmitter's ground electrode increased the received power by 6dBm. Ideally all electrodes should be insulated, however, but in this configuration the received signal strength was found to be significantly lower than any other configuration.

Figure 2.6: 1<sup>st</sup> Order harmonic power versus distance and plate size

## **2.3.2 Test Results and Conclusions**

Although this test setup contributed valuable data, the key contribution came in the form of a better understanding of the test medium, not in exact measurements. The reason for this lies in the oscillators used. It was discovered that changing the type of oscillator changed both the shape and amplitude of the received waveform. The reason for this is twofold: First, the output stages of the oscillators are not designed to drive a capacitor with a large dielectric absorption. Second, the shape of the waveform each oscillator generates is different, especially with regard to ringing and slew-rate, and this causes a large change at the output of the charge sensitive preamplifier. These factors highlight the need for an output stage designed to both drive a capacitor with a high dielectric absorption and offer some degree of waveform shaping.

### **Chapter 3** System Design and Implementation

### 3.1 System Summary - Overview

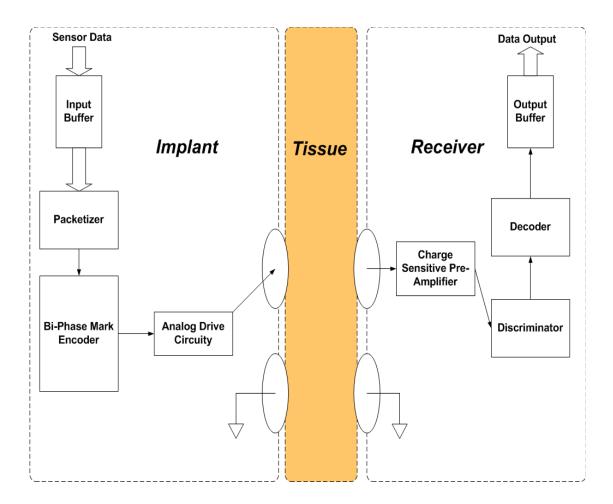

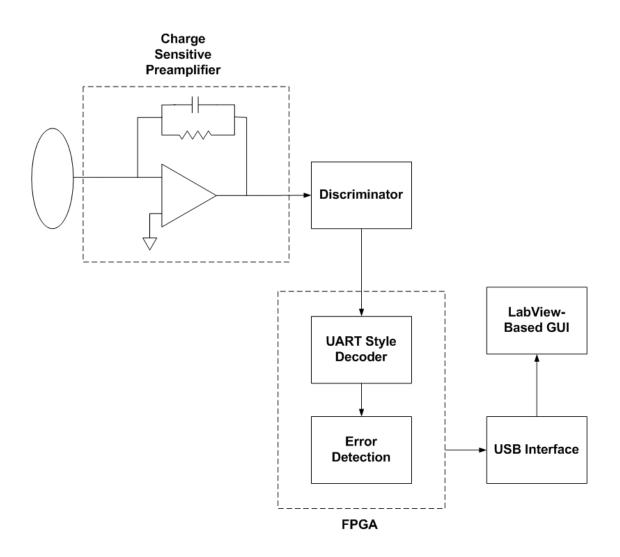

The capacitance-based telemetry system consists of two distinct parts: an implemented transmitter, and a body-mounted receiver (see Figure 3.1).

The transmitter has three basic functions: packetizing digital sensory data, encoding these packets using a DC-balanced method, and transmitting the data via an analog drive circuit incorporating pulse shaping to optimize transmission characteristics. This circuit drives a plate that is electrically insulated from the tissue, thus ensuring no direct DC coupling to the tissue. A ground-return electrode is also attached that is likewise insulated from the tissue.

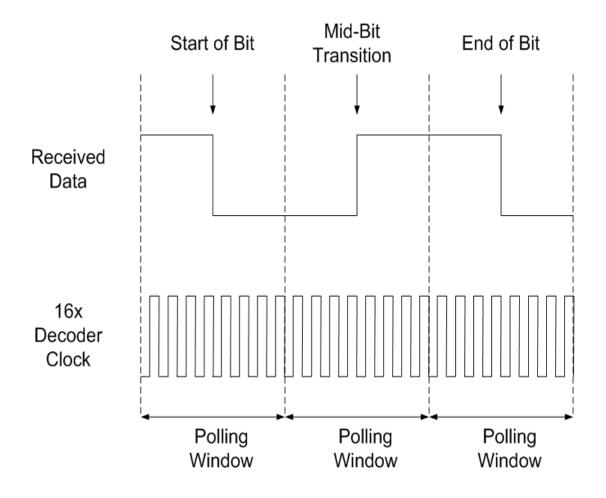

The receiver module also has three distinct blocks: a charge sensitive preamplifier front-end, discriminator, and packet decoder. The pre-amplifier is connected to an electrode that, like the transmitting electrode, is electrically insulated from the tissue. An insulated ground-return electrode is also present. The pre-amplifier produces a pulsetrain output of that is feed into a discriminator circuit that acts as a 1-bit A/D converter transforming the received analog waveforms into digital bits. The converted digital signal is then input to a packet decoder block. The decoding process involves several functions: basic packet detection, synchronization, error detection and correction, and removing the encapsulated data.

This chapter presents the design of each of the individual blocks within the transmitter and receiver.

Figure 3.1: Block diagram for complete system

Each function is presented in the order data is transmitted and received, following the data through the system as it would be transmitted from the implant to the external body-mounted receiver. The chapter concludes with a presentation of the physical implementation of the transmitter and receiver.

### **3.2 Implant Transmitter**

As was stated previously, the basic function of the transmitter is to take data from the implant, encapsulate it in packets, encode the packets in a scheme suitable for transmission through tissue, and transmit the encoded packets with each pulse shaped to maximize transmission efficiency. For testing purposes, to eliminate the need for incorporating a sensor and associated interfacing electronics, "dummy" data is generated on chip. This data is a non-random number pattern, allowing the test receiver to accurately determine when packets have been dropped or incorrectly transmitted. A basic block diagram of the transmitter is shown in Figure 3.2. The following subsections detail the block that generates the dummy data packets, and then describes the format chosen for the data packets. Example waveforms of the packets are also shown, showing in detail the structure of the packets and the generated packet train as a whole. The chosen encoding scheme and its design is detailed next, followed by a discussion of alternative encoding schemes and their implementations. Finally two different analog drive circuits are presented. The basic functionality of each is discussed, along with simulation results and associated integrated circuit layout details.

34

### Figure 3.2: Implant transmitter block diagram

## 3.2.1 Dummy Packet Generator

The dummy packet generator's function is to generate data encapsulated within packets as though it was coming from a real external sensor. However, unlike real data from an external sensor, this data must be both regular and periodic allowing straightforward verification of the data link. Thus for the purposes of the transmitter the dummy packet generator has three functions: generating a series of predictable data so that missed or erroneous packets can easily be detected, encapsulation of the data into packets of the chosen format, and periodic generation of these packets. The packet transmission interval must be sufficiently long enough to prevent accidental pileup of packets and short enough to enable straightforward observation with an oscilloscope or logic analyzer. The time between packets was chosen to be 224 cycles of the system clock, or roughly 788 packets per second. This low data rate was chosen to simplify testing, and does not represent a limitation of the system. Also, a "sleep" signal is generated during the dead-time to shutdown other sections of the chip.

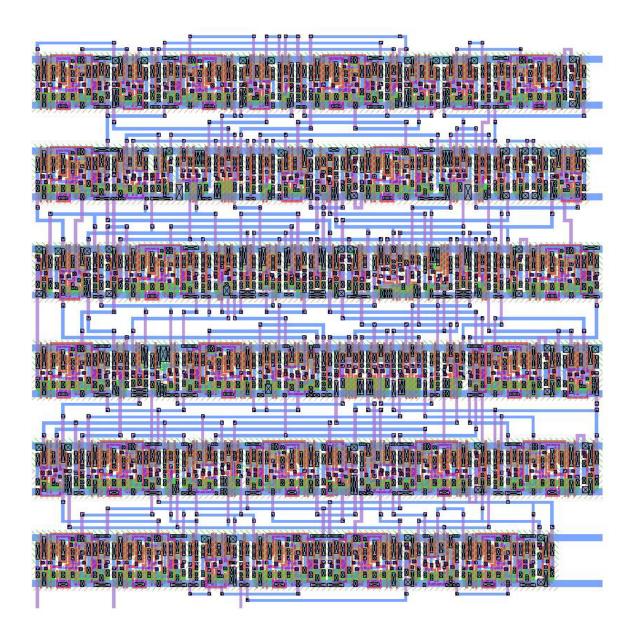

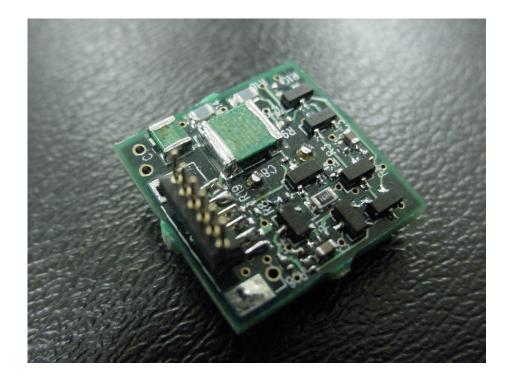

The dummy packet generator was designed in VHSIC Hardware Description Language (VHDL) using Altera's Quartus II software. Initial testing was done using an off-the-shelf test board incorporating an Altera Stratix FPGA. This test board was used in both the transmitter and receiver to minimize the required effort and to allow easier verification of both functional blocks. The dummy packet generator is a simple state machine consisting of four states. Each state represents a section of the packet currently being generated: header, footer, data block, and sleep (off state). Because each section has a fixed length, most of the activity is simply counting clock cycles until it is time to switch to the next state. The VHDL code for the dummy packet generator is given in Appendix 1. After verification of the design using the FPGA board, the VHDL based design was ported to an auto-place, auto-route software package (Timberwolf [30]) and an ASIC layout was produced using a library of standard CMOS primitives (this layout is shown in Figure 3.3).

### **3.2.2 Packet Format**

The packet format was designed first and foremost to enable ease of decoding. For this reason a large header and footer were used. The header is composed of thirtytwo "1" bits and the footer is composed of twenty-four "1" bits. A start bit and a stop bit were also used to separate the header and footer portions of the packet from the data. Both start and stop bits are 0s. The data block of the packet is composed of one 4-bit counter repeated twice, for a total of eight data bits. Figure 3.4 shows the Quartus II simulation results the of the dummy packet generator block. The first waveform is a single packet. The "position" vector in the waveform gives the current state of the state machine. The data vector is 4-bit counter that is repeated twice in the packet. The second waveform shows a close-up of the actual data in a packet.

Figure 3.3: Layout of the dummy packet generator block

|   | Name      | 15.72 us | 15.85 us | 15.98 us | 16.12 us | 16.25 us | 16.39 us | 16.52 us | 16.66 us | 16.79 us | 16.92 us | 17.06 u |  |

|---|-----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|---------|--|

| 0 | outout    |          |          |          |          |          |          |          | _        |          |          |         |  |

|   | clock     |          |          |          |          |          |          |          |          |          |          |         |  |

| 0 | quiet     |          |          |          |          |          |          |          |          |          |          |         |  |

|   | 115N (6)Y |          |          |          |          |          |          | χ0110    |          |          |          |         |  |

| Ð | 🗄 data    |          |          |          | 101      |          | X        |          |          |          |          |         |  |

# A) A single generated "dummy" packet

|   | Name     | 16.3 us | 16.32 us | 16.34 us | 16.35 us | 16.37 us | 16.39 us | 16.4 us | 16.42 us | 16.44 us | 16.45 us | 16.47 us |

|---|----------|---------|----------|----------|----------|----------|----------|---------|----------|----------|----------|----------|

| 0 | output   | -       |          |          |          |          |          |         |          |          |          | _        |

|   | clock    |         |          |          |          |          |          |         |          |          |          |          |

| ø | quiet    | _       |          |          |          |          |          |         |          |          |          |          |

| Ð | 🗄 data   |         |          |          | 0101     |          |          |         | χ        | 0110     |          |          |

| 0 | position | header  | χ        |          |          | middle   |          |         | χ        | footer   |          |          |

# B) A close-up view of the data contained within the packet

|   | Name     | 34.4 us | 35.48 us   | 36.55 us | 37.63 us | 38.7 us       | 39.78 us | 40.85 us | 41.93 us   | 43.0 us | 44.08 us | 45.16 us   |

|---|----------|---------|------------|----------|----------|---------------|----------|----------|------------|---------|----------|------------|

| 0 | output   |         |            |          |          |               |          |          |            |         |          |            |

| D | clock    |         |            |          |          |               |          |          |            |         |          |            |

| 0 | quiet    |         |            |          |          |               |          |          |            |         |          |            |

| ð | 🗄 data   | 101     | l1(        | 1        | 100      | X             | 1        | 101      | χ          | 1       | 110      |            |

| 1 | nosition | sleep   | XeadXIXotX | sle      | ep       | Xeadi/()/iot/ | sle      | ер       | )<br>(ead) | sle     | ер       | )<br>(ead) |

# C) Multiple packets being generated

Figure 3.4: Simulated waveforms of "dummy" packets

In this waveform the count value ("0101" in this case) can clearly be seen, repeated twice and surrounded by the '0' start and stop bits. The third waveform shows a series of packets being generated at regular intervals.

### **3.2.3 Bi-Phase Mark Encoding Scheme**

In choosing an encoding scheme three main criteria should be met [31]:

- For biocompatibility reasons the DC component of the bit stream should be approximately zero for all possible patterns.

- 2) For ease of decoding the encoding scheme should be self-clocking.

- 3) Due to the observed differential nature of the channel for certain transmitter plate arrangements, an event should cause a transition in the input signal to create a pulse at the output. At the output of the receiver the rising-edge of an input square wave causes a positive pulse and the falling-edge causes a negative pulse.

Of the popular encoding schemes, Manchester encoding, bi-phase mark encoding, and bi-phase space encoding were chosen due to their self-clocking nature and zero DC average level. Bi-phase space is identical to bi-phase mark except '0' is encoded as a mid-level bit rather than '1'.

Bi-phase level is encoded to represent a '1' as the first half-bit high and the second half-bit low. Conversely, a '0' is represented by the first half-bit low and the second halfbit high, guaranteeing a level change in the middle of each bit. For bi-phase mark there is always a level change on the beginning of each bit (i.e. the rising edge of the clock signal). A '1' is encoded as a level change in the middle of the bit (or on the falling edge of the clock) and a '0' is encoded by no level change. As stated earlier, bi-phase space is the inverse of this. For each of these schemes is NRZ style, that is a high is +V and a low is -V.

Each of these encoding methods meets the first two requirements. They each have one guaranteed level change within each bit allowing extraction of a clock signal, and the average DC level for each is zero. However, the bi-phase mark and bi-phase space schemes are more suitable for this application because of the third criterion. In a bi-phase level scheme a '1' is dependant on the first half of the bit being high and the second half being low, and vice-versa for a '0'. However bi-phase mark and bi-phase space are purely dependant on transitions only and not on the actual level, making either of them more suitable for this application.

One advantage to using either bi-phase mark or bi-phase space is that there is some inherent error detection without having to use additional bits. Because there must be a transition on the beginning of every bit, any bit sent without that transition is considered an error. Because the channel transmits rising edges as a positive pulse and falling edges as a negative pulse, for any encoding scheme with only two levels there can never be two consecutive positive pulses or two consecutive negative pulses. Thus any bit containing this pattern should be considered an error.

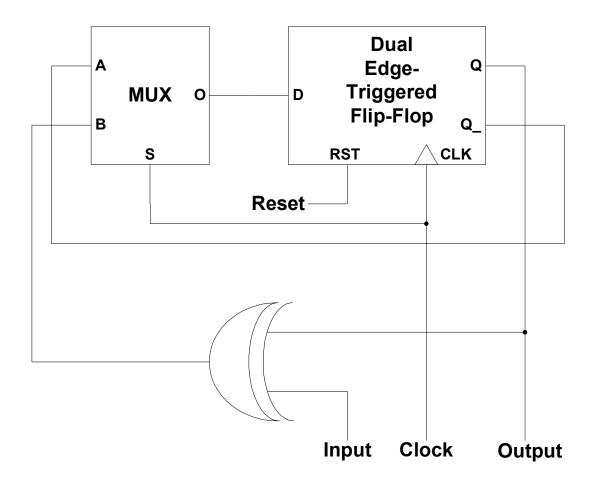

For these reasons bi-phase mark was chosen as the primary encoding scheme. Although a VHDL encoder block was developed at the same time as the dummy packet generator (as it was needed for verification of the functionality of the receiver), it was not used in the transmitter implementation. Instead the encoder blocks for use on the chip were designed and laid out manually using standard logic. The logic used for the biphase mark encoder block in shown in Figure 3.5.

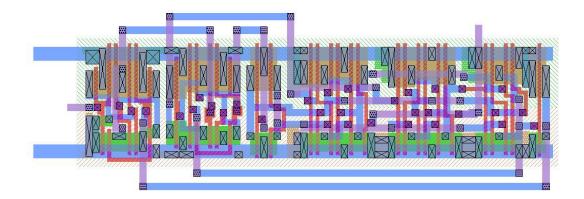

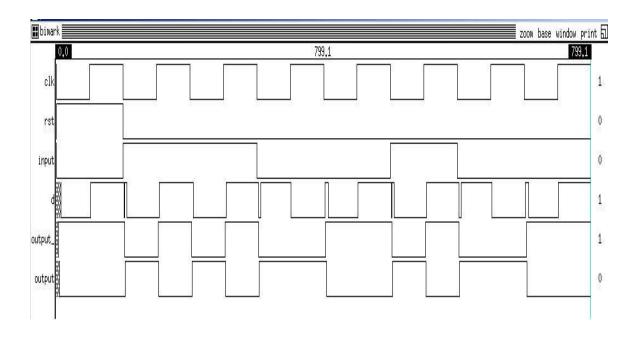

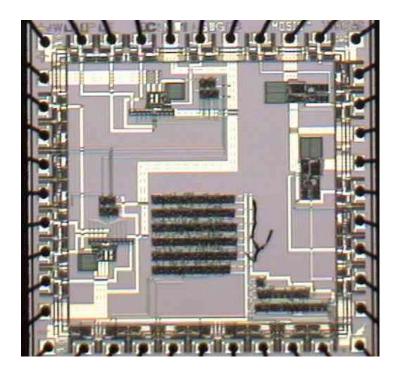

The layout for the bi-phase mark encoder block was designed in MAGIC using blocks from the MSU standard cell library, with the exception of the dual edge-triggered flip-flop, a previously designed ORNL custom cell. The bi-phase mark encoder block was extracted and simulated directly from the layout using IRSIM. The layout is shown in Figure 3.6 and the resulting simulation in Figure 3.7.

### **3.2.4** Alternative Encoding Schemes

Two other schemes were also designed and implemented in addition to the biphase mark approach: bi-phase level (Manchester encoding) and delay modulation (Miller encoding). Like the bi-phase mark implementation, the logic and layouts for both of these were implemented by hand design rather than via VHDL and an extracted layout.

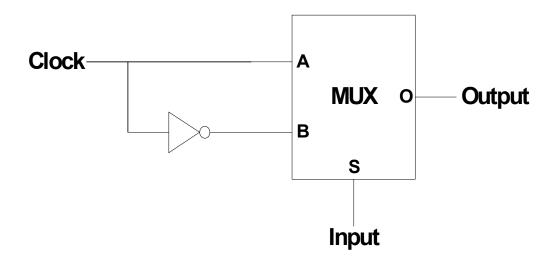

### **3.2.4.1** Manchester Encoding

Manchester encoding is straightforward compared to either bi-phase mark or Miller encoding. In Manchester encoding a '1' is encoded as a half-bit wide pulse in the first half of the bit and a '0' as a pulse in the second half of the bit. Because there is always a transition in the middle the clock can be easily extracted. The main advantage Manchester encoding has over bi-phase mark is the simplicity of implementation, and this is why it was included in the ASIC design. Even though the bi-phase mark encoder block met the system requirements and simulated correctly, including

Figure 3.5: Logic for the bi-phase mark encoder block

Figure 3.6: ASIC layout of the bi-phase mark encoder block

Figure 3.7: Simulation of the bi-phase mark encoder block

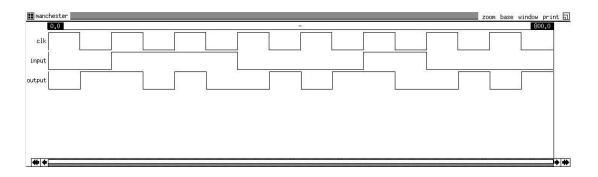

Manchester encoding was an easy way to add a redundant encoding type with a reasonably high level of assurance of functionality. Figure 3.8 shows the logic for Manchester encoding. Figure 3.9 shows the ASIC layout for the block. This approach can be implemented using few gates, as can be expected from the comparatively low complexity of the logic. Thus, the layout is the simplest of the encoding schemes included on the chip. Figure 3.10 shows the simulation results of this block.

### **3.2.4.2** Miller Encoding

Unlike Manchester encoding Miller encoding is a fairly complex encoding scheme. In this scheme a '1' is represented by a transition in the middle of the bit, and a '0' by no transition. However, if the next bit is a '0' and the current bit is also a '0' then a transition is made at the end of the current bit. The increased functional complexity results in more complex logic for implementation.

**Figure 3.8: Logic for the Manchester encoder block**

**Figure 3.9: Simulation of the Manchester encoder block**

Figure 3.10: Layout of the Manchester encoder block

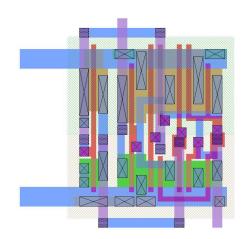

Figure 3.11 shows the logic used to implement the Miller encoding block. One technique was the use of a delay block to temporarily hold the previous state. Although this may not be the best choice for use in a robust block, it was used here because this block was intended for testing purposes and only as an extreme worst-case backup. Figure 3.12 shows the layout used for the Miller encoder block. Figure 3.13 shows the simulation results of this block.

### 3.2.5 Analog Slew Control Circuits

The main function of the drive circuitry is to drive a range of capacitive loads with the load having minimal affect on the shape of the driven waveform. Also, some degree of shaping of the waveform was desired to determine the optimum shape for maximum transmission distance. This shaping consists of entirely of slew-rate control. A tight slew-rate control is important due to the nature of the media. One result of early investigations was that there is a direct relation between the slew rate of the transmitted signal and the shape and level of the received signal. Therefore being able to set the slew-rate for optimum transmission is highly desired.

The center of virtually every slew-rate limiting circuit is controlling a fixed drive current into a capacitive load. Slew-rate is defined as the maximum change in voltage per amount of time, i.e. the maximum slope of the output signal for a given load. The current through a capacitor is defined as

$$Ic(t) = C dVc/dt.$$

**Figure 3.11:** Logic for the Miller encoder block

Figure 3.12: Layout of the Miller encoder block

Figure 3.13: Simulation of the Miller encoder block

Thus for a capacitive load, the slew-rate can be expressed as

$$dVc/dt = Ic(t) / C.$$

Two different analog drive circuits were designed and implemented for slew-rate control. Optimally, the drive circuitry should have the following characteristics: ability to drive a wide range of output loads, tallow precision adjustment of the slew-rate, drive the output from rail-to-rail, and have an output waveform with maximally linear transitions. Rather than trying to meet all of the design criteria in a single design, two approaches were implemented. These two designs differ on two points: the range of settable slew-rates and the total output range. The following sections detail these two approaches.

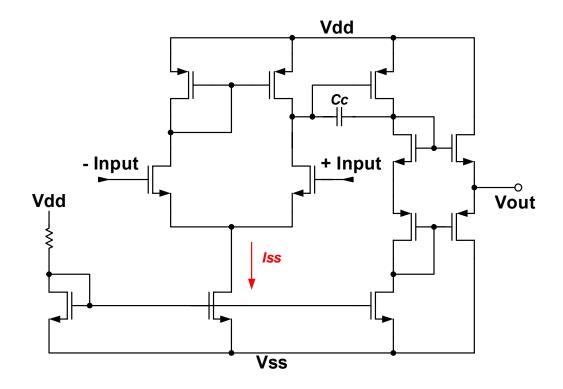

### **3.2.5.1 Op-Amp with a Tail-Current Controlled Slew-Rate**