University of Tennessee, Knoxville Trace: Tennessee Research and Creative Exchange

#### **Doctoral Dissertations**

Graduate School

5-2018

# Digitally Interfaced Analog Correlation Filter System for Object Tracking Applications

Mohsen Judy University of Tennessee, mjudy@vols.utk.edu

#### **Recommended** Citation

Judy, Mohsen, "Digitally Interfaced Analog Correlation Filter System for Object Tracking Applications. " PhD diss., University of Tennessee, 2018. https://trace.tennessee.edu/utk\_graddiss/4978

This Dissertation is brought to you for free and open access by the Graduate School at Trace: Tennessee Research and Creative Exchange. It has been accepted for inclusion in Doctoral Dissertations by an authorized administrator of Trace: Tennessee Research and Creative Exchange. For more information, please contact trace@utk.edu.

To the Graduate Council:

I am submitting herewith a dissertation written by Mohsen Judy entitled "Digitally Interfaced Analog Correlation Filter System for Object Tracking Applications." I have examined the final electronic copy of this dissertation for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Doctor of Philosophy, with a major in Electrical Engineering.

Jeremy H. Holleman III, Major Professor

We have read this dissertation and recommend its acceptance:

Benjamin J. Blalock, Syed K. Islam, Vasileios Maroulas

Accepted for the Council: <u>Dixie L. Thompson</u>

Vice Provost and Dean of the Graduate School

(Original signatures are on file with official student records.)

# Digitally Interfaced Analog Correlation Filter System for Object Tracking Applications

A Dissertation Presented for the

Doctor of Philosophy

Degree

The University of Tennessee, Knoxville

Mohsen Judy

May 2018

© by Mohsen Judy, 2018 All Rights Reserved.

# Acknowledgements

I would like to thank my advisor Dr. Jeremy Holleman for his valuable guidance and support during this research.

I am also thankful to my colleagues at the *Integrated Silicon Systems* laboratory from August 2013 to December 2017, especially Nicholas C. Poor, Peixing Liu, and Tan Yang, as well as, Dr. Charles Britton for their contributions in the design of some of the circuit blocks that have been used in this dissertation.

I would also like to thank Dr. Aravind Mikkilineni and Dr. David Blome from Electrical and Electronics Systems Research Division at the Oak Ridge National Laboratory for their valuable contribution in chip-to-computer interfacing as well as providing the test data and analyzing the results.

I am also grateful to Dr. Benjamin J. Blalock, Dr. Syed K. Islam, and Dr. Vasileios Maroulas for serving as my Ph.D. committee members. Their valuable feedback improved the readability and organization of this dissertation.

And last but not least, I would like to thank my family for patiently enduring the inevitable situation of living apart far away during all these years.

The arc of the moral universe is long, but it bends toward justice.

Martin Luther King, Jr.

# Abstract

Advanced correlation filters have been employed in a wide variety of image processing and pattern recognition applications such as automatic target recognition and biometric recognition. Among those, object recognition and tracking have received more attention recently due to their wide range of applications such as autonomous cars, automated surveillance, human-computer interaction, and vehicle navigation.

Although digital signal processing has long been used to realize such computational systems, they consume extensive silicon area and power. In fact, computational tasks that require low to moderate signal-to-noise ratios are more efficiently realized in analog than digital. However, analog signal processing has its own caveats. Mainly, noise and offset accumulation which degrades the accuracy, and lack of a scalable and standard input/output interface capable of managing a large number of analog data.

Two digitally-interfaced analog correlation filter systems are proposed. While digital interfacing provided a standard and scalable way of communication with preand post-processing blocks without undermining the energy efficiency of the system, the multiply-accumulate operations were performed in analog. Moreover, non-volatile floating-gate memories are utilized as storage for coefficients. The proposed systems incorporate techniques to reduce the effects of analog circuit imperfections.

The first system implements a  $24 \times 57$  Gilbert-multiplier-based correlation filter. The I/O interface is implemented with low-power D/A and A/D converters and a correlated double sampling technique is implemented to reduce offset and low-frequency noise at the output of analog array. The prototype chip occupies an area of  $3.23mm^2$  and demonstrates a 25.2pJ/MAC energy-efficiency at 11.3 kVec/s and 3.2% RMSE.

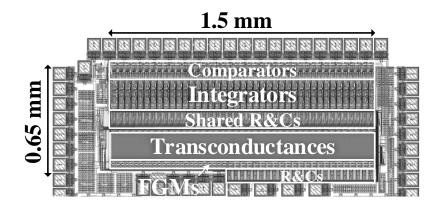

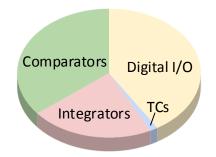

The second system realizes a  $24 \times 41$  PWM-based correlation filter. Benefiting from a time-domain approach to multiplication, this system eliminates the need for explicit D/A and A/D converters. Careful utilization of clock and available hardware resources in the digital I/O interface, along with application of power management techniques has significantly reduced the circuit complexity and energy consumption of the system. Additionally, programmable transconductance amplifiers are incorporated at the output of the analog array for offset and gain error calibration. The prototype system occupies an area of  $0.98mm^2$  and is expected to achieve an outstanding energy-efficiency of 3.6 pJ/MAC at 319 kVec/s with 0.28% RMSE.

# **Table of Contents**

| Chapt | er 1: Iı | ntroduction                                        | 1  |

|-------|----------|----------------------------------------------------|----|

| 1.1   | Correl   | lation Filter                                      | 1  |

| 1.2   | Analo    | g Versus Digital Implementation                    | 2  |

| 1.3   | Challe   | enges in Analog Implementations                    | 4  |

| 1.4   | Resear   | rch Goals                                          | 6  |

| 1.5   | Origin   | al Contributions                                   | 7  |

| 1.6   | Disser   | tation Organization                                | 8  |

| Chapt | er 2: A  | Gilbert-Multiplier-Based Correlation Filter System | 9  |

| 2.1   | Syster   | n Description                                      | 9  |

| 2.2   | The F    | ront-End Interface                                 | 11 |

|       | 2.2.1    | Digital-to-Analog Converter                        | 12 |

|       | 2.2.2    | Current-Mode Demultiplexer/SH                      | 13 |

| 2.3   | Analo    | g Multiplier Array                                 | 13 |

|       | 2.3.1    | Power and Speed Performance                        | 14 |

|       | 2.3.2    | Noise Performance                                  | 16 |

| 2.4   | Nonvo    | latile Floating-Gate Memories                      | 19 |

| 2.5   | The B    | Back-End Interface                                 | 21 |

|       | 2.5.1    | Current mirrors and I-V Converters                 | 21 |

|       | 2.5.2    | Analog Buffers                                     | 25 |

|       | 2.5.3    | Analog-to-Digital Converter                        | 26 |

| 2.6     | Experimental Results                                             | 26 |

|---------|------------------------------------------------------------------|----|

| 2.7     | Conclusion                                                       | 34 |

| Chapt   | er 3: A PWM-Based Correlation Filter System                      | 35 |

| 3.1     | PWM-Based Four-Quadrant Multiplication                           | 36 |

| 3.2     | System Description                                               | 38 |

| 3.3     | Digital I/O                                                      | 39 |

| 3.4     | Analog Processing and Offset Calibration                         | 42 |

| 3.5     | Energy-Efficient Dynamic Comparator with a Fast Convergence Rate | 44 |

|         | 3.5.1 Offset Calibration                                         | 45 |

|         | 3.5.2 Convergence Time                                           | 49 |

|         | 3.5.3 Simulation and Experimental Results                        | 50 |

| 3.6     | Experimental Results (First Prototype)                           | 53 |

| 3.7     | Revised Prototype                                                | 55 |

|         | 3.7.1 Asynchronous vs. Synchronous Counter                       | 55 |

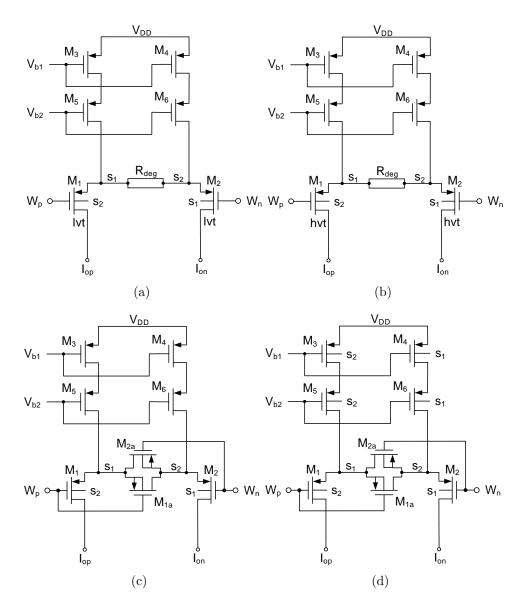

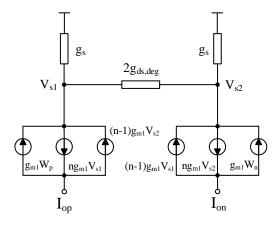

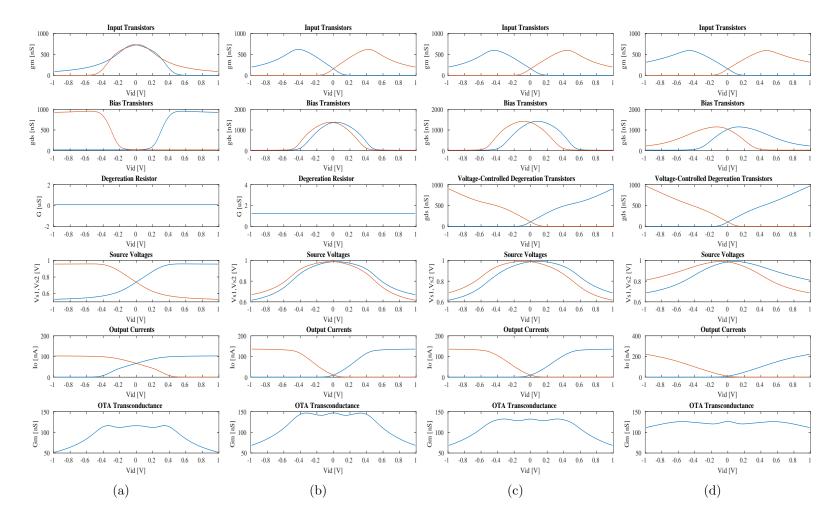

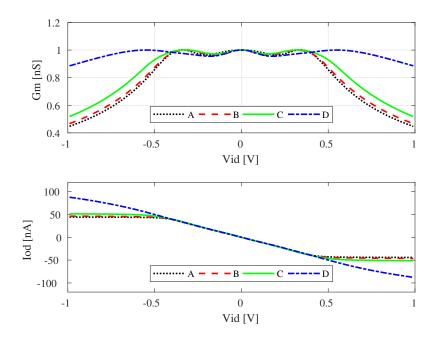

|         | 3.7.2 A Linearized Pseudo-differential OTA                       | 56 |

|         | 3.7.3 Voltage-Domain Subtraction                                 | 63 |

|         | 3.7.4 Gain Error Calibration                                     | 65 |

| 3.8     | Simulation Results (Revised Prototype)                           | 65 |

| 3.9     | Conclusion                                                       | 70 |

| Chapt   | er 4: Conclusions and Future Work                                | 72 |

| 4.1     | Conclusions                                                      | 72 |

| 4.2     | Future Work                                                      | 73 |

| Bibliog | graphy                                                           | 75 |

| Vita    |                                                                  | 82 |

# Chapter 1

# Introduction

## **1.1** Correlation Filter

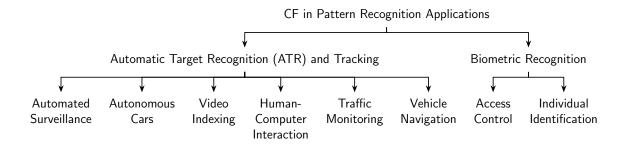

Advanced correlation filters (CFs) have been employed in a wide variety of image processing and pattern recognition applications such as automatic target recognition (ATR) and biometric recognition[24]. Among those, object recognition and tracking [9, 10, 28] have received more attention recently due to their wide range of applications such as autonomous cars, automated surveillance, video indexing, human-computer interaction, traffic monitoring, and vehicle navigation. Figure 1.1 summarizes the CF utilization in pattern recognition applications.

Advances in designing robust but simple CFs that show a better performance at discriminating object and background have paved the way for implementing efficient object tracking systems using fewer computational resources.

The object tracking is performed in two main steps:

- 1) Detection of the objects of the interest, and

- 2) Tracking of such objects from frame to frame.

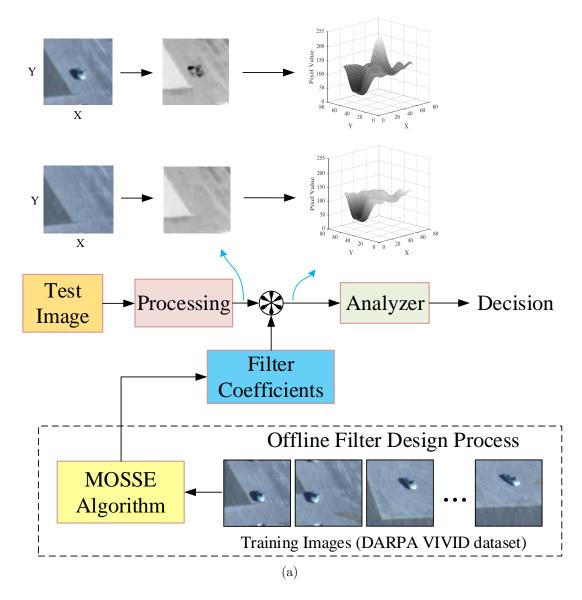

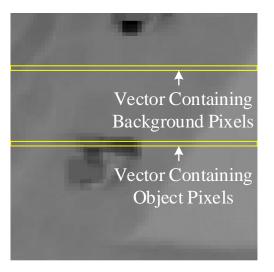

The focus of this work is implementing a CF system to carry out the first step. The object detection procedure using a CF is illustrated in Figure 1.2(a). First, in an off-line training process, the filter coefficients are designed. Images of the object

Figure 1.1: CF utilization in pattern recognition applications.

of interest at different backgrounds, orientations and, points of view are fed to an algorithm which trains the coefficients to generate a sharp peak at the output of the CF wherever a match is detected. In this work, training images are from DARPA VIVID dataset and the target object is a vehicle. The algorithm used here is minimum output sum of squared error (MOSSE) [9]. After obtaining filter coefficients for the target object, the system will respond to images containing the target object by generating a sharp peak at the output. It should be noted that images go through a preprocessing step beforehand in order to reduce shadows and intense lighting effects. Figure 1.2(a) shows simulated responses of the CF implemented in MATLAB to presence and absence of a vehicle on a road.

### 1.2 Analog Versus Digital Implementation

Digital signal processing (DSP) has long been used in a wide variety of application including audio and speech processing, image processing, telecommunications, control systems, etc. However, for some application e.g portable devices, the energy efficiency of the DSP systems is a point of concern. The fastest digital supercomputer to-date (Sunway TaihuLight - 2016) [7] has reached the computational power of a human brain, however, it dissipates a power equivalent to the output of a typical power

Figure 1.2: Object detection procedure using a CF. Filter coefficients are designed using the MSSOE algorithm and training images from the DARPA VIVID dataset. After obtaining the filter coefficient, the CF is ready to be tested. If a test image includes the same object, the correlation output exhibits a sharp peak, otherwise, the correlation output should not have any significant peak. Simulated responses of the CF implemented in MATLAB to presence and absence of a vehicle on a road is shown at the top of this figure.

station!<sup>1</sup> In fact, most of the energy efficiency of the brain comes from the fact that the biological systems are analog. Unlike the digital world, where each wire only

<sup>&</sup>lt;sup>1</sup>Sunway TaihuLight has a computational power of  $93 \times 10^{15}$  Ops./s at 15 MW power, while human brain has an estimated computational power of more than  $10^{15}$  Ops./s at less than 10 W.

| Realization | Addition        | Multiplication   |  |  |  |  |

|-------------|-----------------|------------------|--|--|--|--|

| Digital     | 240 Transistors | 3000 Transistors |  |  |  |  |

| Analog      | A wire (KCL)    | 4-8 Transistors  |  |  |  |  |

Table 1.1: Analog versus digital realization of multiplication and addition [39]

represents one bit of information, a wire in the analog world can represent multiple bits. On the other hand, analog implementation can exploit basic laws of physics in order to perform mathematical operations. For instance, addition can be easily implemented using the Kirchhoff's Current Law (KCL) for current-mode signals, and a pair of MOSFETs biased in the sub-threshold region can perform the multiplication, thanks to the semiconductor device physics. Table 1.1 compares estimated hardware resources for the realization of basic mathematical operations (multiplication and addition) for two 8-bit numbers in analog and digital domains[39]. As a matter of fact, it has been shown that computational tasks that require low to moderate Signalto-Noise Ratios (SNRs) are more efficiently realized in analog than digital in terms of area and power consumption [39].

### **1.3** Challenges in Analog Implementations

In spite of all the advantages mentioned above, the analog implementation of computational systems has certain issues. One of the most important problems with analog computing systems is the noise and offset accumulation which could result in a significant degradation of accuracy. A common way to compensate for the offset in such systems is to manually calibrate the biasing current of the analog memories [34, 11] or measure the offset for each output and store them in a separate array of analog memories and then subtract them from the output signals [5]. The former requires one analog memory per array element and the latter can only compensate for one of two inputs by fixing the other one. In both of these methods, the remaining offset depends on the programming accuracy.

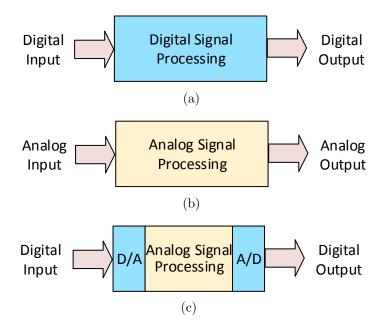

Figure 1.3: Signal processing methods: (a) Digital, (b) analog, and (c) analog with digital I/O interfacing.

Apart from the noise and offset-related issues, fully parallel implementation of analog processing operations requires input/output interface circuitry capable of supplying/acquiring a large number of analog data simultaneously to/from the computational block. Although implementing such interfaces is essentially a challenging task for any system, this becomes more of an issue when dealing with noise- and mismatch-sensitive analog signals. Therefore, it is a key to develop configurable digital interfaces that can easily scale with the number of inputs and efficiently communicate with other pre- and post-processing blocks.

The three signal processing methods discussed above are visualized in Figure 1.3. Figure 1.4 outlines the pros and cons of analog and digital implementation of I/O interfacing versus signal processing.

Several architectures implementing such hybrid/mixed-signal approaches have been reported in the literature. In [19] a bit-serial input/bit-parallel output architecture has been proposed that demands one flash ADC per output and needs further off-chip processing. Moreover, it utilizes DRAM memories which require

|         | I/O Interfacing                                                                                                                     | Signal Processing                                                                                  |

|---------|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| Digital | <ul> <li>✓ High-speed</li> <li>✓ Noise-tolerant</li> <li>✓ Easily scalable</li> <li>✓ Standard communication</li> </ul>             | <ul> <li>x Power hungry</li> <li>x Bulky design</li> <li>x Complex interconnection</li> </ul>      |

| Analog  | <ul> <li>x Low-speed</li> <li>x Noise-sensitive</li> <li>x Complicated scaling</li> <li>x Non-standard<br/>communication</li> </ul> | <ul> <li>✓ Energy-efficient</li> <li>✓ Area-efficient</li> <li>✓ Simple interconnection</li> </ul> |

Figure 1.4: Pros and cons of analog versus digital implementation of I/O interfacing and signal processing.

constant refreshing. The architecture proposed in [22] employs a large number of SRAM memories and other supporting digital logic circuits which add excessive power overhead to the system.

## 1.4 Research Goals

This dissertation investigates the implementation of a correlation filter system with analog signal processing and digital I/O interface. In summary, desired specifications of the system are:

• Energy and area efficiency.

An 8-bit digital multiply-accumulate (MAC) circuit in a 130 nm CMOS process operating at a data-rate of higher than 1MHz consumes  $\sim 5$  pJ energy and occupies an active area of  $80\mu m \times 80\mu m$ . Adding data registers, decoders and other digital blocks for I/O interfacing, clock buffers, etc. which are needed to build a system such as the correlation filter, and considering the leakage power will significantly add to the energy consumption per MAC. In fact, a post-layout evaluation of a  $24 \times 57$  fully-digital CF system operating at 1.5 V supply and 50-500 MHz data-rate shows an energy-efficiency of ~280 pJ/MAC. The total layout area was 6mm×4.75mm.

• High throughput to keep up with the 25-30 frames/sec produced by modern cameras (real-time processing requirement).

Processing an  $80 \times 80$  pixel frame with an 80-input CFS means running 137 vectors through the system. This means in order to have 30 frames/sec rate, the CFS should have a throughput of more than 4.11 kVector/s.

• Programmable analog non-volatile storage.

Analog non-volatile floating-gate memories are capable of storing values even without power in contrast to SRAM/DRAM. Additionally, floating-gate memories occupy less area compared to digital storage, making it an attractive solution for storage in analog signal processing systems.

- 8-bit digital interface to communicate with pre- and post-processing blocks that:

- Easily scales with the number of inputs and outputs.

- Does not add significant power overhead to the system. (The entire system should maintain its energy-efficiency.)

- 8-bit input linearity

- The collective RMS error < % 4

## **1.5** Original Contributions

In this work, two digitally-interfaced analog correlation filter systems for object tracking applications are proposed. The original contributions are summarized below:

- Proposed novel architecture and circuits to realize a Gilbert-multiplier-based correlation filter system with digital I/O interface, non-volatile storage, and techniques to reduce the offset and low-frequency noise of the analog array. The proposed system incorporates power management techniques to further increase the energy-efficiency of the system.

- Proposed novel architecture and circuits to realize a PWM-based correlation filter system with digital I/O interface, non-volatile storage, and techniques to reduce the offset and gain error of the analog array. The proposed system incorporates power management techniques to further increase the energyefficiency of the system.

- Proposed a fast convergent calibration technique for dynamic comparators.

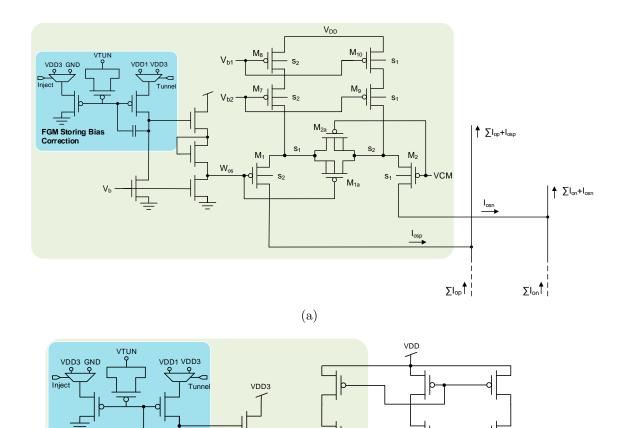

- Proposed a linearized pseudo-differential OTA with ±800 mV linearity range at 1 V power supply.

## **1.6** Dissertation Organization

The remaining chapters of this dissertation will cover the design of circuits and architectures to implement the CFS systems described above.

Chapter 2 describes the design and presents the experimental results of a Gilbertmultiplier-based CFS. In chapter 3 development of a PWM-based CFS is presented as an alternative architecture which addresses limitations of the Gilbert-multiplier-based CFS and achieves better performance in terms of energy-efficiency and operating speed. Chapter 4 concludes the dissertation and proposes potential future works.

# Chapter 2

# A Gilbert-Multiplier-Based Correlation Filter System

An energy-efficient digital I/O interface solution for an analog correlation operator for linear filtering is presented which maintains the power and area efficiency of the entire system and easily scales with the number of inputs. Furthermore, the proposed system utilizes non-volatile floating-gate memories as storage devices, eliminating the need for DRAM/SRAM memories. Also, a correlated double sampling (CDS) technique has been implemented to cancel offset and to reduce the low-frequency noise at the outputs of the array.

### 2.1 System Description

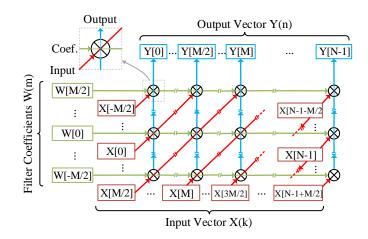

The correlation of two vectors w(m) and x(k) is defined as:

$$y(n) = \sum_{i=-M/2}^{M/2} w(i) \cdot x(n-i)$$

(2.1)

In this equation w(m) is the filter coefficient vector, where  $-M/2 \le m \le M/2$ , x(k) is the input vector, where  $-M/2 \le k \le N - 1 + M/2$  and y(n) is the output vector,

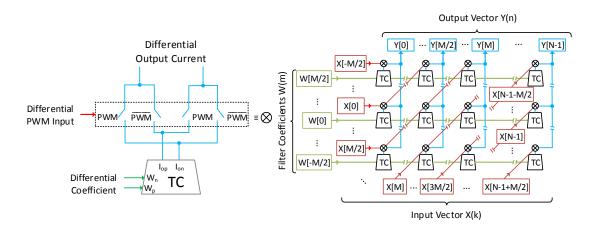

Figure 2.1: An  $M \times N$  fully parallel analog correlation filter realized with four-quadrant multipliers and floating-gate memories. The multipliers at each row share the same weight inputs (green lines) and diagonal multipliers share the same signal inputs (red lines). The multiplier outputs at each column are wire-summed to yield a single pixel (blue lines).

where  $0 \le n \le N - 1$ . It should be noted that in an array with M coefficients and N outputs, the input vector has M - 1 more elements than the outputs. Figure 2.1 illustrates a fully parallel implementation of a M×N correlation filter.

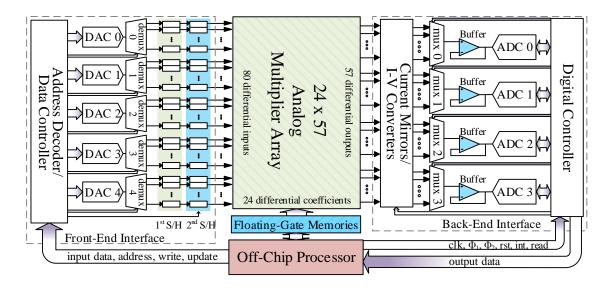

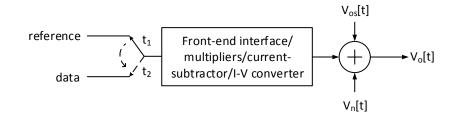

Figure 2.2: The proposed architecture for a  $24 \times 57$  fully parallel correlation filter system with digital I/O interface.

The proposed architecture for a digitally interfaced fully parallel analog correlation filter system (CFS) is shown in Figure 2.2. The filter coefficient vector is stored in an array of analog floating-gate memories (FGMs) which are connected to voltage inputs of multipliers in each row. In other words, the FGMs are shared across N multipliers. A front-end interface converts the digital input vector to analog current vector and delivers them to the multiplier array simultaneously. Thanks to the utilization of current-mode signals, the summation in (2.1) is performed by simply connecting the output of multipliers in each column together according to Kirchoff's current law (KCL). After computation, a back-end interface converts the output vector back to digital. In this paper, we present a prototype CFS with M = 24, N = 57, and 80 inputs.

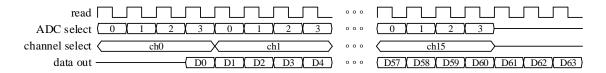

## 2.2 The Front-End Interface

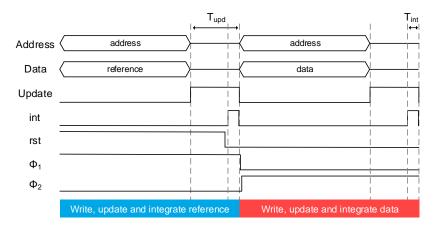

The front-end interface comprising five digital-to-analog converters (DACs) followed by eighty sample-and-hold (SH) circuits. Every 16-channels share one DAC using a time-domain multiplexing (TDM) scheme. It should be noted that an 8-bit address space is chosen for input data to account for future growth. The lower 4 bits choose the DAC and the upper 4 bits select the SH channel. Figure 2.3 shows the timing diagram of the front-end interface.

| write          |           |      |      |      |                     |           |      | <u> </u> | ட    | டா   | 000 |           |      |      |      |      | L |

|----------------|-----------|------|------|------|---------------------|-----------|------|----------|------|------|-----|-----------|------|------|------|------|---|

| address        | 0x00      | 0x01 | 0x02 | 0x03 | 0x04                | 0x10      | 0x11 | 0x12     | 0x13 | 0x14 | 000 | 0xF0      | 0xF1 | 0xF2 | 0xF3 | 0xF4 |   |

| data index     | 0x00      | 0x10 | 0x20 | 0x30 | 0x40                | 0x01      | 0x11 | 0x21     | 0x31 | 0x41 | 000 | 0x0F      | 0x1F | 0x2F | 0x3F | 0x4F |   |

| DAC select     | 0         | 1    | 2    | 3    | 4                   | 0         | 1    | 2        | 3    | 4    | 000 | 0         | 1    | 2    | 3    | 4    |   |

| channel select | $\subset$ |      | ch0  |      | $ \longrightarrow $ | $\square$ |      | ch1      |      |      | 000 | $\square$ |      | ch15 |      |      |   |

| update         |           |      |      |      |                     |           |      |          |      |      | 000 |           |      |      |      |      |   |

Figure 2.3: The front-end timing diagram: In the write phase 80 8-bit data samples are sent to the chip. The five DACs operating in TDM scheme convert digital data to analog and store them in the SHs.

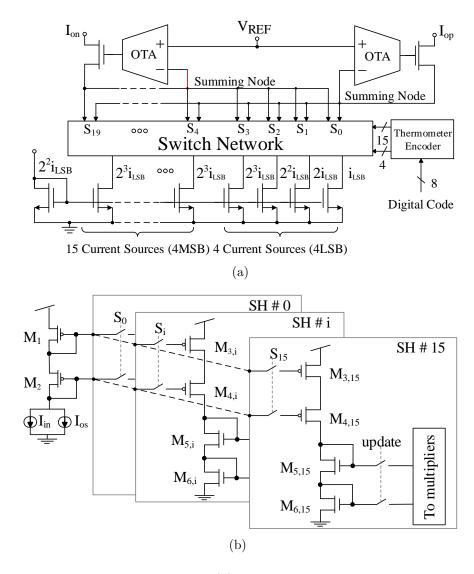

Figure 2.4: The front-end interface: (a) the segmented current-steering DAC with differential outputs, and (b) the current-mode demultiplexer/SHs. The switches  $S_{0}$ - $S_{15}$  are controlled by the channel select signal shown in the timing diagram of Figure 2.3.

### 2.2.1 Digital-to-Analog Converter

An 8-bit current-steering DAC was designed to convert the digital input signals to analog signals for the analog computation block. As shown in Figure 2.4(a), the DAC uses segmented topology: 4 MSBs are thermometer coded, and the 4 LSBs are binary weighted. The segmentation helps to reduce differential non-linearity (DNL) and integral non-linearity (INL). An operational transconductance amplifier (OTA) is used in a cascode current sink configuration to increase the output resistance. A detailed description of this design can be found in [33].

### 2.2.2 Current-Mode Demultiplexer/SH

Figure 2.4(b) shows the schematic of the current-mode demultiplexer/SH circuit. Transistors  $M_1$  and  $M_2$  are diode-connected and have a sink current directly from the DAC output  $(I_{in})$ . An externally-controlled DC offset current  $(I_{os})$  was added in order to decrease the time-constant of input stage especially for small input currents. The gate connections of  $M_1$  and  $M_2$  are shared with 16 SHs through switches controlled by  $S_i, i = 0, 1, ...15$ . When a set of switches is turned on, a current mirror is formed between transistors  $M_1 - M_2$  and the transistors on the other side of the given switch,  $M_{3,i} - M_{4,i}$ . The sampled voltages are held on the gate capacitance of  $M_{3,i} - M_{4,i}$ when their switches are turned off. The second SH is formed between  $M_{5,i} - M_{6,i}$ and the multiplier tail transistors. By activating *update* signal, input currents held in the first SHs are passed to the multiplier array to start the computation. In order to minimize the charge injection error dummy switches have been used whose gates are driven by inverted clock signals.

## 2.3 Analog Multiplier Array

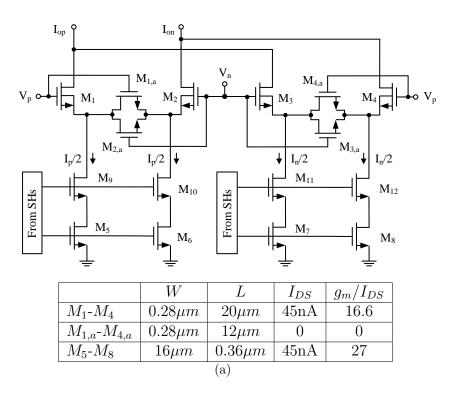

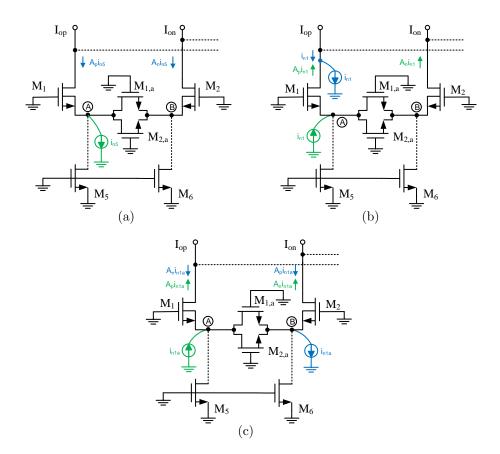

The four-quadrant Gilbert multiplier circuit is shown in Figure 2.5(a). The multiplier is formed with NMOS transistors operating in the sub-threshold region. The multiplier linear region was extended using voltage-controlled degeneration technique [23]. Using the equation provided in [45], the differential transconductance can be written as:

$$G_{m0} \approx \frac{I_{in}}{nU_T} \cdot \frac{2}{L+4} \tag{2.2}$$

where  $I_{in}$  is the input current, n is the sub-threshold slope factor,  $U_T$  is the thermal voltage, and L is the ratio of transconductance parameters of  $M_i$  and  $M_{i,a}$  i.e.  $\beta_i/\beta_{i,a}$ ,

Figure 2.5: The linearized four-quadrant multiplier circuit. Transistors W, L,  $I_{DS}$  and  $g_m/I_{DS}$  (for  $V_p = V_n$ ) are given in the table.

i = 1, 2, 3, 4. The linearity was found to be maximum for  $L \approx 2.5$ . Transistors  $M_i$  were chosen to be *triple-well* devices to eliminate the body effect and hence, to improve multiplier linearity with respect to the current input. Moreover, isolation from the substrate improves the noise performance. It should be noted that achieving an 8-bit dynamic range and tolerable mismatch-related errors come at the expense of using long-channel devices, with the result that each multiplier cell occupies an area of  $30\mu m \times 40\mu m$ . Nevertheless, this design is markedly smaller than a digital counterpart.

### 2.3.1 Power and Speed Performance

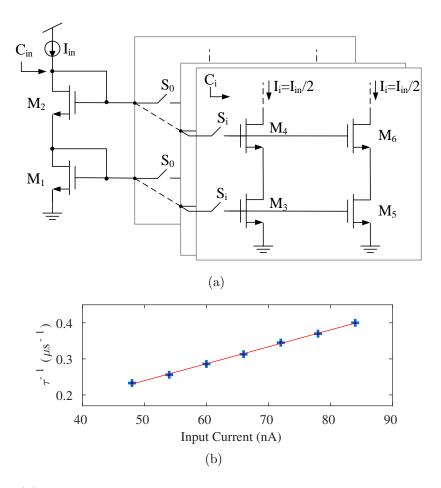

The input stage shown in Figure 2.6(a) dominates the frequency response of the CFS. From a small-signal analysis of the self-biased cascode current mirror, the

Figure 2.6: (a) The input stage of the multiplier array. The switches  $S_0$ - $S_i$  are controlled by the update signal. (b) The inverse of multiplier array time constant varies linearly with input current as predicted by (2.5).

dominant pole is:

$$P = \frac{-g_{m1}}{C_{in}} \tag{2.3}$$

where  $g_{m1}$  is the transconductance of the transistor  $M_1$  and

$$C_{in} = (j+1)C_i \tag{2.4}$$

and j is the number of multipliers connected to the input node and the worst case is when the input node is connected to multipliers in all of the rows (j = M). By substituting the sub-threshold equation for  $g_{m1}$ , the inverse time constant can be written as:

$$\tau^{-1} = \frac{I_{in}}{nU_T C_{in}}.\tag{2.5}$$

This equation shows that the inverse time constant linearly scales with the input current level and the number of rows in the array. Figure 2.6(b) plots the measured inverse time constant for a given input current level. Total power consumption of the  $N \times M$  multiplier array is:

$$P_{MA} = 2 N M I_{in} V_{dd}. \tag{2.6}$$

Assuming a settling time of  $5\tau$  for the array, the power-delay product is then:

$$P_{MA}(5\tau) \approx 10 N M^2 n U_T C_i V_{dd}.$$

(2.7)

This equation shows that the power-delay product for multiplier array is a linear function of N and a quadratic function of M. It is also independent of input current, suggesting that operating at higher speed by increasing the input current level does not reduce the energy efficiency. However, increasing the input current level increases the non-linearity because transistors start moving out of the sub-threshold region.

### 2.3.2 Noise Performance

In the multiplier circuit shown in Figure 2.5(a) the shot noise is the dominant noise source due to the large size of the devices. The noise spectral density of transistors in sub-threshold region is given by [38]:

$$i^2 = 2 q I_s (1 + \exp(-V_{DS}/U_T))$$

(2.8)

where  $I_s$  is the sub-threshold saturation current. Considering that transistors  $M_i(i = 1, 2, ..., 8)$  operate in the saturation region  $(V_{DS} >> U_T)$ , their noise spectral density

can be approximated by:

$$\overline{i_{M_i}^2} = 2qI_{s,i} = qI_{in}, \quad i = 1, 2, ..., 8$$

(2.9)

where  $I_{in}$  is the SH input current. Transistors  $M_{i,a}$ , on the other hand, operate in the triode region and according to (2.8) their noise contribution reach their maximum of  $4qI_{s_{i,a}}$  when  $V_{DS_{i,a}} = V_p - V_n = 0$ . However, because  $I_{s_{i,a}}/I_{s_i} = \beta_{i,a}/\beta_i = 0.4$  (i = 1, 2, 3, 4), therefore  $I_{s_{i,a}} = 0.2I_{in}$  and the noise spectral density of  $M_{i,a}$  can be written as:

$$\overline{i_{M_{i,a}}^2} = 4qI_{s_{i,a}} = 0.8qI_{in}, \quad i = 1, 2, 3, 4.$$

(2.10)

If we consider the current noise of the tail transistor  $M_5$ , as shown in Figure 2.7(a), the current gain from the node A to the positive and negative outputs can be written as:

$$A_p = \frac{L}{L+1} = 0.71, \qquad A_n = \frac{1}{L+1} = 0.29.$$

(2.11)

Therefore, the noise contribution of  $M_5$  to the output is:

$$(A_p - A_n)i_{n5} = 0.42i_{n5}. (2.12)$$

As depicted in Figure 2.7(b), the current noise of transistor  $M_1$  can split into two correlated noise sources with the same values, one at the drain of  $M_1$  and the other at the node A. Thus, the noise contribution of  $M_1$  to the output is:

$$(1 - A_p + A_n)i_{n1} = 0.58i_{n1}.$$

(2.13)

And finally, the current noise of transistor  $M_{1,a}$  can split into two noise sources at node A and node B as shown in Fig 2.7(c). Hence, the noise contribution of  $M_{1,a}$  to the output is:

$$2(A_n - A_p)i_{n1a} = 0.84i_{n1a}.$$

(2.14)

Figure 2.7: The simplified schematic of the multiplier circuit for noise analysis (the cascode transistors are not shown). The Noise contribution of (a)  $M_5$ , (b)  $M_1$ , and (c)  $M_{1,a}$ .

Consequently, the noise contribution of all the transistors to the output can be calculated as:

$$\overline{i_{out}^2} = (0.58)^2 \sum_{i=1}^4 \overline{i_{M_i}^2} + (0.42)^2 \sum_{i=5}^8 \overline{i_{M_i}^2} = 1.34 \overline{i_{M_i}^2} + 2.82 \overline{i_{M_{i,a}}^2} + 0.7 \overline{i_{M_i}^2}.$$

(2.15)

Hence, the total output noise is given by:

$$\overline{i_{out}^2} = (1.34\,\overline{i_{M_i}^2} + 2.82\,\overline{i_{M_{i,a}}^2} + 0.7\,\overline{i_{M_i}^2})\,\Delta f = 4.3\,qI_{in}\,\Delta f.$$

(2.16)

Figure 2.8: The floating-gate memory cell and digital control logic.

Substituting the equivalent noise bandwidth (ENB) of  $1/4\tau$  in the above equation we obtain:

$$\overline{i_{out}^2} \approx \frac{4.3 \, q I_{in}^2}{4n U_T \, (M+1)C_i}.$$

(2.17)

Thus, the RMS signal-to-noise ratio (SNR) can be written as:

$$SNR = \frac{I_{od}}{\overline{i_{out}}} = \frac{G_{m0} \cdot V_{id}}{\overline{i_{out}}} \approx \frac{4V_{id}}{\sqrt{4.3}(L+4)} \sqrt{\frac{(M+1)C_i}{n \, kT}}$$

(2.18)

where k is the Boltzmann constant and T is the absolute temperature. Based on this equation, increasing the input capacitance leads to higher SNR, which is indeed nothing but the well-known trade-off between the bandwidth and SNR. From (2.5) and Figure 2.6(b) the  $C_i$  is estimated to be 325 fF. With a  $V_{id} = 0.1$  V,  $kT = 4.11 \times 10^{-21}$ J, and n = 1.42 from simulation, expected SNR is 60.8 dB.

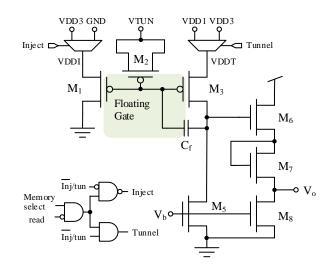

### 2.4 Nonvolatile Floating-Gate Memories

An array of floating-gate (FG) memories is employed to store the analog filter coefficients in a differential mode. The schematic of the FG analog memory cell is shown in Figure 2.8 [26]. The gate of  $M_1$ ,  $M_2$  and  $M_3$  and the top plate of capacitor

| Control Signal       | Injection | Tunneling | Read | VDDT | VDDI |  |  |  |  |

|----------------------|-----------|-----------|------|------|------|--|--|--|--|

| VTUN                 | L         | Н         | L    | 1    | 0    |  |  |  |  |

| $\overline{inj}/tun$ | L         | Н         | L    | 3    | 3    |  |  |  |  |

| read                 | L         | L         | Η    | 3    | 0    |  |  |  |  |

Table 2.1: Control Signals for Different Operation Modes

form the FG. The stored charge on the FG is modified by the injection process through  $M_1$  and the tunneling process through the transistor  $M_2$ . Tunneling removes electrons from the FG node while injection adds electrons. Both of these processes change the amount of charges stored in  $C_f$ , therefore, change the output voltage according to the equation:

$$V_{out} = \frac{\Delta Q}{C_f}.$$

(2.19)

In the tunneling mode, VTUN is connected to 7 V, and VDDT is switched from 3 V to 1 V to reduce the FG voltage and increase the gate oxide voltage,  $V_{ox}$ . The amount of charge added or removed from the FG is controlled by the pulse width of VDDI and VTUN signals, respectively. In the injection mode, VDDI is switched to 3 V from GND, VTUN is switched to GND and VDDT is switched back to 3 V to prevent tunneling. In the read mode, VTUN and VDDI are switched to 0 and VDDT is switched to 3 V to make sure no tunneling or injection is happening. Upon activation of 'read' signal, the output of the selected cell is connected to a pad and read by off-chip read-out circuitry. Because the programming process utilizes feedback based on  $V_o$ , non-linearities, finite-gain effects, etc. are accounted for. Table 2.1 summarizes the FGM operation modes and the control signals. In general, the programming time depends on the number of floating-gate memories and the target values. For this prototype, it takes about one minute in average to program all the floating gates. The RMS error between target and actual values for all of the floating-gate memories was less than 1mV. This was calculated based on the errors measured at the  $V_o$  node.

Figure 2.9: The back-end timing diagram: In the read phase 64 analog samples are converted to 8-bit digital data and sent out of the chip using four ADCs operating in TDM scheme.

## 2.5 The Back-End Interface

An array of 57 current mirrors performs differential to single-ended conversion. The difference currents are then integrated into the capacitors. The analog output voltages are multiplexed into four unity-gain buffers driving four 8-bit SAR ADCs. The timing diagram of Figure 2.9 illustrates the sequence in which ADCs perform the conversion and output digital data.

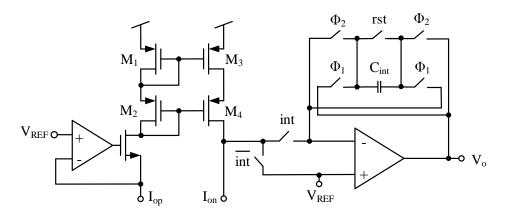

### 2.5.1 Current mirrors and I-V Converters

Figure 2.10 shows the schematic of current mirror followed by the I-V converter circuit. An OTA keeps the voltage on the  $I_{op}$  node at  $V_{REF}$  to improve the accuracy. Using (2.1) and (2.2) the output voltage of the integrator can be written as:

$$V_o(n) \approx \frac{2 T_{int}}{n U_T C_{int}(L+4)} \sum_{i=-M/2}^{M/2} V_{id}(i) \cdot I_{id}(n-i)$$

(2.20)

Where  $C_{int}$  is the integration capacitor and  $T_{int}$  is the integration time. The CDS technique was implemented on the CFS chip to cancel offset at the array outputs. The CDS is performed in two phases. In the first phase, the off-chip processor writes *reference* input, then updates the analog multipliers and integrates the output current. In the second phase, the processor repeats the same process, this time for *data* input. The data input is subtracted from reference input by switching plates of  $C_{int}$  between the two phases.

Figure 2.10: The current-mirror and the I-V converter.

A correlated double sampling (CDS) offset cancellation technique is implemented [17]. As shown in the Figure 2.11, offset voltage  $V_{os}$  and noise voltage  $V_n$  are added to the output of I-V converter at any sampling time t. If we apply reference input to the system at time  $t_1$ , the output signal can be written as:

$$V_o[t_1] = V_{o,ref}[t_1] + V_{os}[t_1] + V_n[t_1]$$

(2.21)

Then we apply *data* input to the system at sampling time  $t_2$ :

$$V_o[t_2] = V_{o,data}[t_2] + V_{os}[t_2] + V_n[t_2]$$

(2.22)

If we subtract these two output voltages and note that  $V_{o,ref}$  indeed is the output common-mode voltage with no signal component, we get:

$$V_{o,CDS} = V_o[t_2] - V_o[t_1]$$

=  $V_{o,data} + (V_n[t_2] - V_n[t_1])$  (2.23)

if we define  $f_s = \frac{1}{t2-t1}$ , we can write 2.23 in s-domain as:

Figure 2.11: Correlated double sampling technique

$$V_{o,CDS} = V_{o,data} - V_n(\frac{2s}{s+2f_s})$$

(2.24)

This equation shows that the remaining noise spectrum is shaped by a high-pass filter with a corner frequency at  $2f_s$ . Thus, CDS not only removes the DC offset voltages but also reduces the low-frequency noise.

Figure 2.12 shows how CDS is implemented in two phases on CF system. In the first phase, Microprocessor writes 'reference' input, then updates the analog multipliers and integrates the output current. This is indeed the first sampling and the resultant voltage is equal to  $V_o[t_1]$  from equation 2.21.

In the second phase, Microprocessor repeats the same process, this time for 'data' input (second sampling) and the resultant voltage is equal to  $V_o[t_2]$  from equation 2.22.

Figure 2.12: Timing diagram for CDS implementation on CFS.

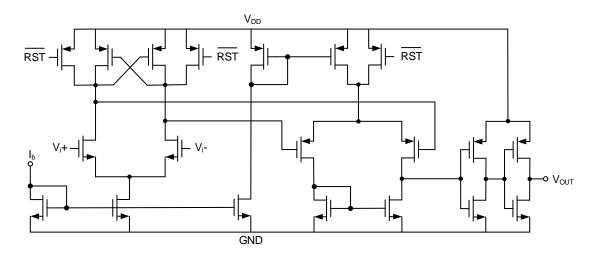

Figure 2.13: The complementary input two-stage class-AB op-amp circuit schematic

The subtraction in equation 2.23 is simply implemented by switching plates of  $C_{int}$ . Two non-overlapping signals  $\phi_1$  and  $\phi_2$  control switches  $S_{4-5}$  and  $S_{6-7}$  respectively. During the first phase,  $\phi_1$ , top plate of the  $C_{int}$  is connected to  $S_1$ , and the bottom plate is connected to the output. In the beginning of the second phase,  $\phi_2$ , the plates are switched such that the bottom plate is connected to  $S_1$ , and the top plate is connected to the output. This process conserves the charge stored in the capacitor and only changes its polarity.

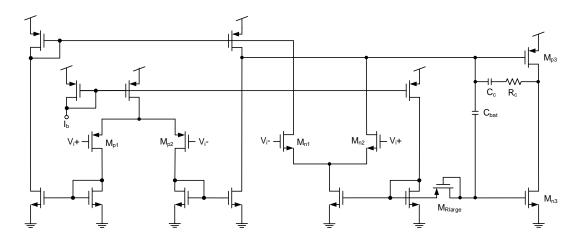

The operational amplifier (op-amp) used for I-V conversion (Figure 2.10) is a class-AB two-stage op-amp designed based on the circuit presented in [35]. The circuit schematic is shown in Figure 2.13.<sup>1</sup>. Compared to [35], the input stage was modified to a complementary stage to extend the input voltage range. The circuit is basically a conventional two-stage class-A op-amp with two additional elements:  $C_{bat}$ and  $M_{Rlarge}$ . During the quiescent conditions, the circuit operates as a conventional two-stage class-A op-amp because no DC current flows through  $M_{Rlarge}$ , however, during dynamic operation,  $C_{bat}$  operates as a floating battery and passes the voltage variations to the gate of  $M_{n3}$  and enables the class-AB operation with no additional static power dissipation.

<sup>&</sup>lt;sup>1</sup>Design credit goes to Dr. Tan Yang.

The 57 analog voltage outputs were multiplexed to four channels. Each channel was buffered and connected to an ADC. The buffered analog voltages were also connected to PADs through a second set of analog buffers for testing and characterization.

### 2.5.2 Analog Buffers

The circuit shown in Figure 2.13 has been used as a unity gain buffer to drive the ADC input capacitor array during the sampling phase which is as large as 1.66pF. The class-AB operation helps to reduce power consumption. Based on the simulation results, buffer requires  $1\mu A$  of biasing current to settle to half LSB during the ADC sampling time (312.5ns at 24MHz ADC clock frequency).

Figure 2.14: (a) SAR ADC architecture, and (b) Reference switch implemented using a charge pump circuit.

Figure 2.15: Comparator circuit schematic designed for the ADC.

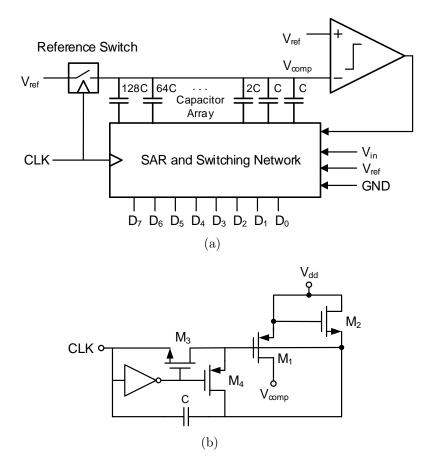

### 2.5.3 Analog-to-Digital Converter

The SAR ADC is a popular choice for medium resolution/speed applications because of its energy efficiency advantage. A conventional 8-bit SAR ADC was designed<sup>2</sup> to convert analog output vector to digital output vector (Figure 2.14(a)). The 6.5 fF unit capacitors were realized using VNCAP devices and were arranged as an array with a common-centroid configuration to decrease mismatch effects. A single-cycle charge pump circuit [41] was used to boost the gate voltage of the reference switch which made it possible to use the supply voltage as the reference voltage. The comparator circuit (Figure 2.15) comprises a regenerative circuit followed by a differential to single-ended amplifier stage.

## 2.6 Experimental Results

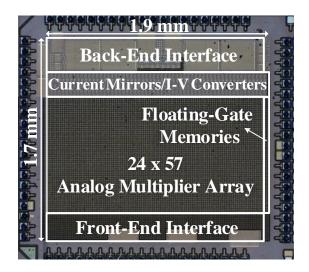

A prototype  $24 \times 57$  CFS was designed and fabricated in a 0.13  $\mu$ m CMOS process. The chip area is 1.7 mm×1.9 mm. Figure 2.16 depicts annotated chip micrograph. The CFS chip was evaluated using a custom test board interfaced to a PC via an FPGA board. The FPGA board controls the write, update, integrate and read timings

<sup>&</sup>lt;sup>2</sup>Design credit goes to Peixing Liu and Dr. Charles Britton.

Figure 2.16: The micrograph of the CFS chip fabricated in a 0.13  $\mu$ m CMOS process.

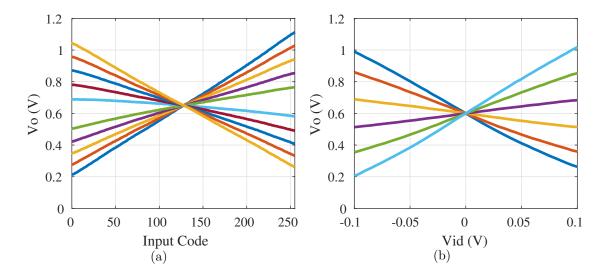

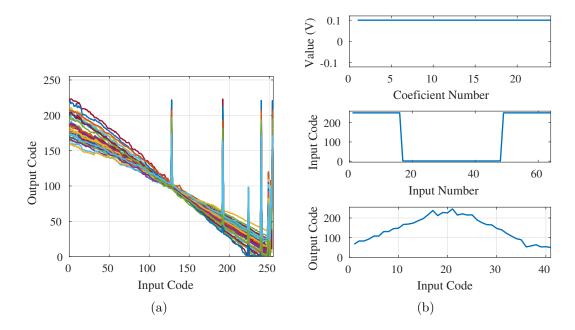

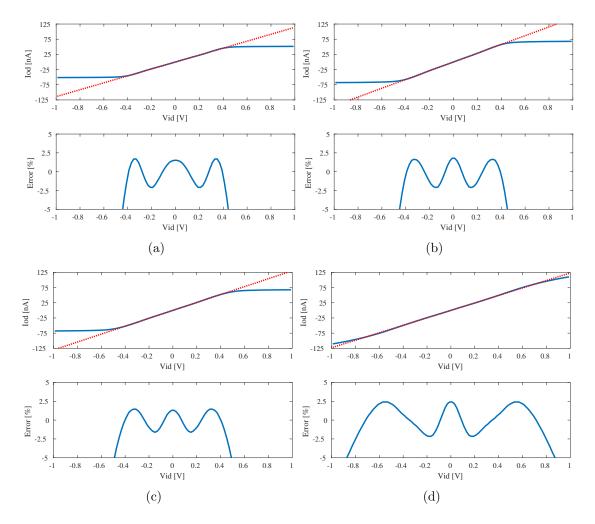

and communicates with the PC through a USB-UART interface. Figure 2.17 shows the input/output characteristics for a column of multipliers. The output is taken after the charge integrator, which converts the current output to a voltage. The measured worst-case INL and DNL for the inputs were +4.7/-5.2 and +1.8/-1 8-bit LSBs, respectively, whereas those of the weights were +1/-1.2 and +0.26/-0.27 6-bit LSBs, respectively.

Figure 2.17: The multiplier array characteristics: (a) The output voltage vs. input code for various programmed  $V_{id}$  values, and (b) the output voltage vs.  $V_{id}$  for various input codes.

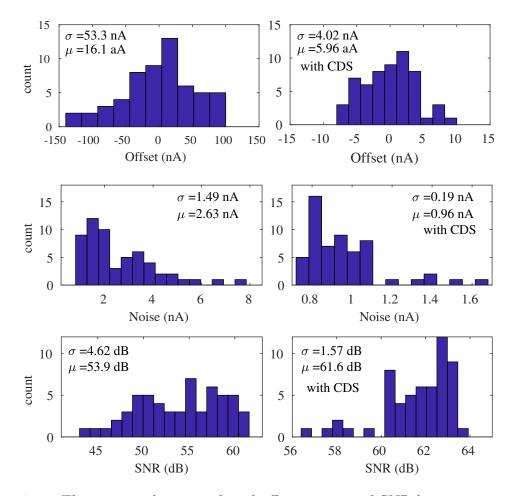

Figure 2.18: The measured input-referred offset, noise, and SNR histograms without and with the CDS.

The input-referred offset, current noise, and SNR with and without performing the CDS offset cancellation technique are depicted in Figure 2.18. Since the measured values are the sum of several independent random processes, a Gaussian distribution is assumed here for calculating the mean and the standard deviation. If the number of samples (i.e. outputs) were sufficiently large the Gaussian distribution would be more evident (the Kolmogorov-Smirnov test also supports the Gaussian assumption). Implementing the CDS technique reduced the offset from 53.3 nA to 4 nA (13.2X reduction). The SNR without the CDS is 53.9 dB with a standard deviation of 4.62 dB which is in agreement with the expected SNR of 60.8 dB. The CDS also

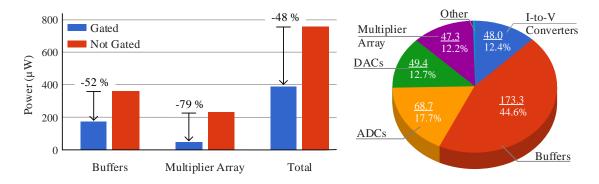

Figure 2.19: The saved power due to the power gating (left) and the power distribution of the CFS chip (right).

reduced low-frequency noise (by a factor of 2.7) and improved the average SNR from 53.9 dB to 61.6 dB.

Operating at the maximum sampling rate of 600kSps each ADC consumes an average of  $10.1\mu W$  of power. The INL and DNL of the ADCs were measured by applying a slow moving ramp signal to the positive input of all the I-V converters while keeping the rst switch on. The INL ranges from -2 to 2 LSBs and DNL ranges from -1 to 1.14 LSBs. The ADCs show an SFDR of 45dB and an effective number of bits (ENOB) of 6.5 bits.

The comparator was designed to work with 1.5V power supply and 150nA of bias current with a conversion time of 10ns and  $5.04\mu W$  power dissipation. However, a mismatch problem caused conversion failure at some input values. To fix that, the biasing current was increased to  $1.1\mu A$  and  $V_{dd}$  to 1.7V. This allows for conversion time of 2.8ns with the cost of increased power dissipation to  $7.55\mu W$ .

Table 2.2 summarizes the specifications of the system. Operating at 6 MHz write speed and 2.4 MHz read speed, the entire system achieves 25.2 pJ/MAC of energy efficiency at 11.3 kVec/sec throughput. The multiplier array and the unity-gain buffers were the most power-hungry blocks in the system and therefore they were turned off during the standby intervals. As a result, as shown in Figure 2.19, 48 percent of the power was saved. Table 2.3 compares key specifications of this work with similar systems. The 8-bit CFS chip presented in this paper uses non-volatile

|             | 1                 | 1                     |

|-------------|-------------------|-----------------------|

|             | Specification     | Value                 |

| Front-End   | Write Speed       | 6 MHz                 |

| Interface   | D/A INL/DNL       | -0.8/0.54 LSB         |

|             | Power Dissipation | $49.4 \ \mu W$        |

| Multipliers | Power Dissipation | $47.3 \ \mu W$        |

| Back-End    | Read Speed        | 2.4 MHz               |

| Interface   | A/D SFDR/ENOB     | 45  dB/6.5  bits      |

|             | Power Dissipation |                       |

|             | OTAs              | $1.35 \ \mu W$        |

|             | I-V Converters    | $48 \ \mu W$          |

|             | Buffers           | $173.3 \ \mu W$       |

|             | A/Ds              | $68.7 \ \mu W$        |

| System      | Power Supply      | 1.5 V                 |

|             | Throughput        | 11.3  kVec/sec        |

|             | SNR               | 61.6 dB               |

|             | Power Dissipation | $388.4~\mu\mathrm{W}$ |

|             |                   |                       |

Table 2.2: Summary of Specifications: Gilbert-Multiplier-Based CFS

floating-gate memories to store filter coefficients and achieves better total energy efficiency compared to other systems reported with similar functionality.

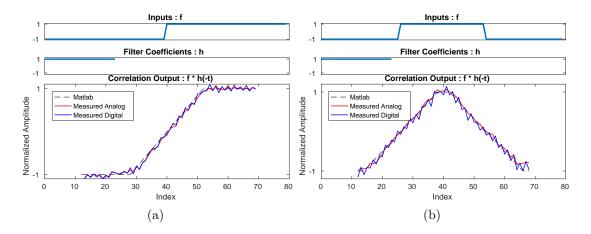

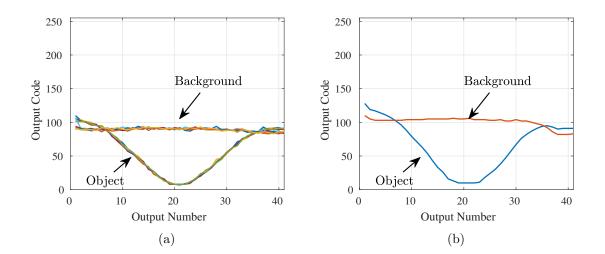

The CFS chip was tested by filter-input vector pairs and the resultant vector was compared to an ideal filtering performed in Matlab. Figure 2.20 shows the results of two experiments. Note that all the values are normalized to  $\pm 1$ . Top plot of Figure 2.20(a) shows the input vector which contains an abrupt transition from -1 to +1 in the middle. As shown in the second plot, the filter coefficients were

| Specification                         | This work      | TCAS II [19]     | VLSIC [22]     | CICC [12]       | VLSIT[34]       |

|---------------------------------------|----------------|------------------|----------------|-----------------|-----------------|

| Process $(\mu m)$                     | 0.13           | 0.5              | 0.35           | 0.5             | 0.35            |

| Purpose                               | CF             | VMM              | Image Filter   | VMM             | VMM             |

| I/O type                              | Digital        | Digital          | Digital        | Analog          | Analog          |

| No. of Bits                           | 8              | 1                | 6              | -               | -               |

| Memory Type                           | FG             | DRAM             | SRAM           | FG              | FG              |

| Array Size                            | $24 \times 57$ | $512 \times 128$ | $51 \times 80$ | $128 \times 32$ | $100 \times 10$ |

| Chip Size $(mm^2)$                    | 3.23           | 9                | 9.8            | 0.82            | 25              |

| Settling Time <sup>*</sup> ( $\mu$ s) | 12.5           | 10               | 1              | 0.08            | 13              |

| Core Energy <sup>*</sup> (pJ/MAC)     | 0.43           | 0.5              | 22             | 0.57            | 0.32            |

| Total Energy (pJ/MAC)                 | 25.2           | N/A              | 68.6           | -               | -               |

Table 2.3: Performance Comparison: Gilbert-Multiplier-Based CFS

\* Measured for the analog array.

Figure 2.20: Measurement results for correlation between two vectors, coefficients resemble a smoothing filter (a) input signal has one abrupt change (b) input signal has two abrupt changes.

programmed to +1 which resemble a 'smoothing filter' and expected to smooth out abrupt transitions. The digital output vector, as well as the analog output vector, are depicted in the bottom plot. The expected ideal output vector is also plotted for comparison. Figure 2.20(b) shows another experiment, where the input data has two abrupt changes: one from -1 to +1 and the another from +1 to -1. The outputs are again displayed in the bottom plot. The root-mean-square error (RMSE) for the analog output vector is 0.044 or 2.2%. The RMSE is increased to 0.065 corresponding to 3.2% after digitization (CFS output).

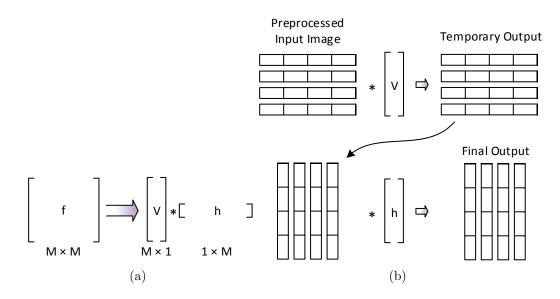

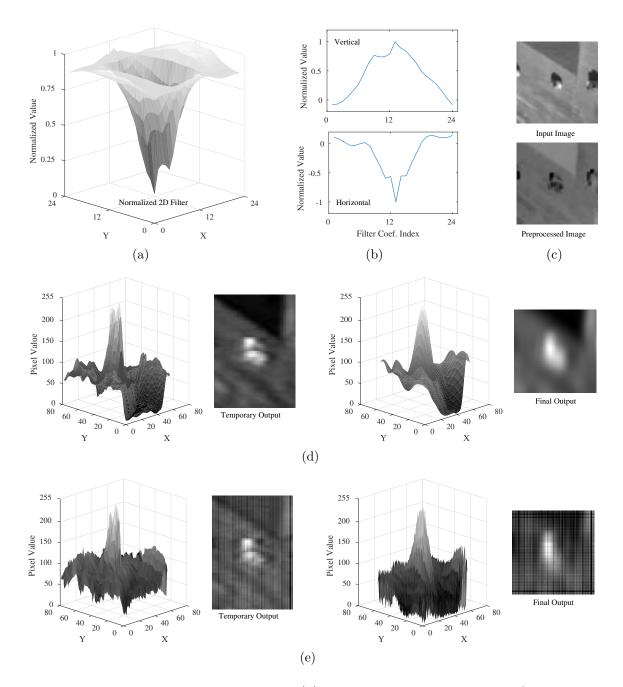

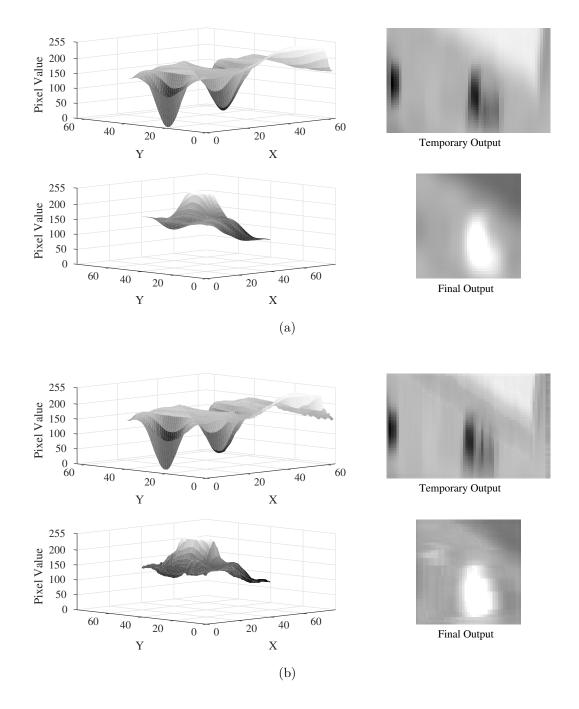

To demonstrate the effectiveness of the designed CFS in object tracking, a custom filter was designed to detect vehicles based on the MOSSE algorithm [9]. Figure 2.22 shows the designed filter kernel. As illustrated in Figure 2.21(a) this two-dimensional filter is then decomposed into a *vertical* and a *horizontal* filter (Figure 2.22(b)). The test image went through a few preprocessing steps to reduce shadow and intense lighting effects [10]. The test process is illustrated in Figure 2.21(b). The *preprocessed image* rows were scanned into the chip and correlated with the vertical filter to form a *temporary output*. Afterward, the columns of the temporary output were scanned into the chip and correlated with the horizontal filter to produce the *final output* which is expected to exhibit a sharp peak when there is an authentic match between the filter and the target in the input image. Figure 2.22(d) depicts the expected output from an ideal digital filter implemented in MATLAB for a test image from the DARPA VIVID dataset[14] and Figure 2.22(e) shows the measured results. The final outputs of the analog filter match closely with the simulated digital filter, indicating negligible degradation due to noise, mismatch, etc. The analog filtered image shows a strong peak at the target location which clearly discriminates the target from the background. It worth noting that this prototype only includes one set of floating gate memories; however, the future versions of the chip will include multiple kernels that can be selected at run-time, so that both the horizontal and vertical filters can be executed with no reprogramming. A similar solution could be implemented using two of the current chips, with one programmed for the horizontal filter and one for the vertical filter.

Figure 2.21: (a) A separable two-dimensional filter kernel (f) is decomposed to two vectors, called horizontal (h) and vertical (v) filters (b) Filtering with f is equivalent to filtering first with v and then filtering the result with h.

Figure 2.22: The vehicle detection test: (a) normalized two-dimensional filter kernel, (b) decomposed vertical and horizontal filters, (c) original and preprocessed input test image, (d) temporary and final outputs from an ideal digital filter implemented in MATLAB, and (e) temporary and final outputs from the chip.

# 2.7 Conclusion

A 24×57 correlation filter system has been p resented. The proposed system performs MAC operations in the analog domain and provides a standard and scalable digital I/O interface for data transfer. An array of non-volatile floating-gate memories are used to store filter coefficients. The CFS chip dissipates 388.4  $\mu$ W of power at a throughput of 11.3 kVec/s, achieving an energy efficiency of 25.2 pJ/MAC. The fabricated chip occupies 3.23 mm<sup>2</sup> of the silicon area in a 0.13  $\mu$ m CMOS process. A custom filter based on the MOSSE algorithm to detect vehicles was programmed into the CFS chip. The result of applying the filter on an image from DARPA VIVID dataset was presented, showing a strong peak at the location of the target.

# Chapter 3

# A PWM-Based Correlation Filter System

In the previous chapter, a Gilbert-multiplier-based architecture for CFS was presented and it was shown that the output of the system matches closely with the expected output. Nevertheless, here is a summary of limitations regarding the Gilbert-multiplier-based CFS:

• Operating Speed

The speed for the multiplier array is limited by the input stage and is directly proportional to input current amplitude and inversely proportional to the number of rows in the array. Input current amplitude is limited to a few hundred nanoamps because of the fact that the multiplier is linear only in the sub-threshold region. Adding auxiliary circuits, e.g. OTAs help reduce the input capacitance but at the cost of additional power and circuit complexity. In addition to the multiplier array, digital I/O interface can also limit the overall speed. The low power DACs and the S/H circuits operating in the sub-threshold region at the input interface can operate up to 6MHz and the output interface operates at a maximum speed of 2.4MHz.

• Power Consumption

Although the proposed Gilbert-multiplier-based CFS demonstrated a better energy-efficiency compared to similar works reported in the literature, it was clear that energy consumption of the system was dominated by the I/O interfaces. The input and output interfaces consume  $\sim 13\%$  and  $\sim 62\%$  of the power, respectively. The power consumption for the output interface was dominated by the analog buffers ( $\sim 45\%$ ) which are required to drive the A/D converters input capacitance.

• Input linearity range

The multiplier in the Gilbert-multiplier-based CFS was linearized by applying degeneration techniques. However, the linear range depends on the input current level. An optimum design that could cover the entire input current level results in a narrower linear range than a linearized differential pair operating at a certain bias current.

In this chapter, an alternative architecture is proposed to address the issues listed above. The proposed architecture is capable of operating at a higher speed and a lower power consumption.

## 3.1 PWM-Based Four-Quadrant Multiplication

The search for a better way of implementing multiplication lead to using the *time* as the second factor (the first factor being the voltage stored on floating-gate memories). In this method, the image pixel values are encoded into pulse-width modulated (PWM) signals. Figure 3.1 shows four-quadrant multiplier implementation using the PWM modulation technique. The transconductance amplifier (TC) block converts the filter coefficient (stored as voltage) to a differential current signal and the switch network controls the direction of current flow. By defining the clock period,  $T_u$ , as the time unit, the PWM signals for a M - bit multiplication can be written as:

Figure 3.1: Left: The PWM-based multiplication. The image pixels are encoded to PWM signals and the filter coefficients are converted to current signals. Right: A fully-parallel time-domain multiplier array. The wire-summed current at each column will be integrated to a capacitor, forming the product voltage.

$$PWM = d_{in}T_u$$

$$\overline{PWM} = (2^M - d_{in})T_u$$

(3.1)

where  $d_{in}$  is the 8-bit image pixel value. The output current is integrated into a capacitor  $C_{int}$  (Figure 3.5), resulting in a voltage that is proportional to the product of the image pixel and filter coefficient values:

$$V_o = \frac{g_m T_u}{C_{int}} (W_p - W_n) (d_{in} - 2^{M-1})$$

(3.2)

To convert the product back to digital, the voltage stored on the capacitor is discharged by a constant reference current source  $I_{dis}$  (Figure 3.5) and the time that  $V_o$  reaches  $V_{ref}$  is measured by a counter running at  $1/T_u$  clock frequency.

In PWM-based multiplication, the current switching happens at the output of the transconductance amplifier which has much lower parasitic capacitance compared to the input of the multiplier in previous architecture. Therefore, this system can potentially operate at much higher speeds than the Gilbert-multiplier-based CFS.

Figure 3.2: Simplified block diagram of the PWM-based CFS.

Furthermore, this architecture can be easily scaled without much decrease in operating speed. Increasing the array size means that the PWM signals need to drive extra minimum size switches and interconnects. This is in contrast with the Gilbert-multiplier-based CFS, where analog currents were driving non-minimum size (analog) devices plus interconnects. Therefore, this technique can be used for large arrays without a significant speed penalty.

# **3.2** System Description

Figure 3.2 shows block diagram of the proposed architecture. It is clear from this block diagram that, unlike the Gilbert-multiplier-based CFS, the I/O interface does not require any explicit D/A or A/D converters. Instead, this architecture utilizes digital-to-PWM (D/PWM) and PWM-to-digital (PWM/D) conversion all realized in digital (using a counter, a digital comparator, and a dynamic comparator). All-digital I/O interface is indeed an attractive feature for this type of systems especially moving

toward deep sub-micron CMOS technologies. As technology scales, the propagation delay of digital gates reduce, and therefore the I/O interface can operate at higher speeds. Operating at high frequencies reduces the leakage current contribution in total power dissipation, resulting in a better energy-efficiency. Additionally, digital circuits are capable of operating under low supply voltages, making them a suitable choice for I/O interfacing in modern technologies.

The active analog blocks in this architecture include transconductance amplifiers and integrators. These blocks perform the main processing task of multiplyaccumulation which, as discussed before, is costly in terms of area and power consumption if implemented in digital.

In summary, this architecture takes full advantage of all-digital design over analog or even mixed-signal design (A/D or D/A as in Gilbert-multiplier-based CFS) in I/O interfacing, and, on the other hand, benefits from the efficiency of analog design in signal processing.

The system building blocks are described in the following sections.

## 3.3 Digital I/O

In this architecture, the energy efficiency of digital I/o interface is increased by exploiting several techniques. Firstly, low-threshold devices are employed instead of regular devices. It should be noted that using low-threshold devices has a caveat: increased leakage power consumption of the digital blocks in low-frequencies.

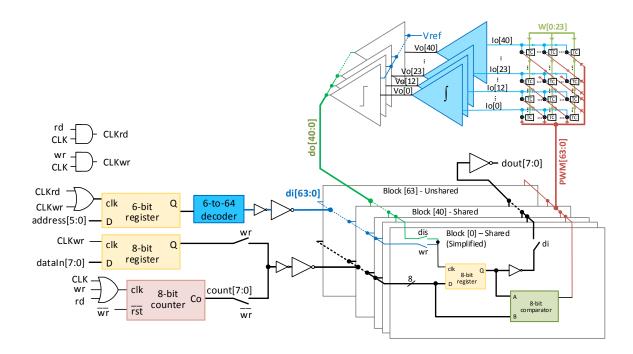

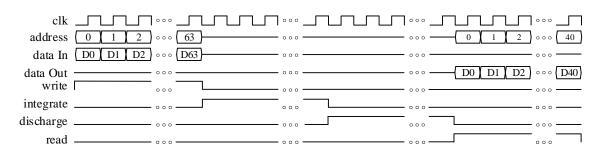

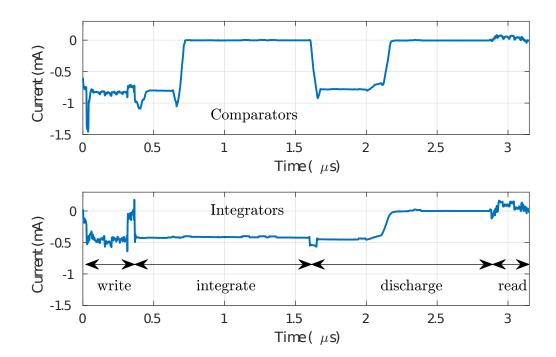

Figure 3.3: Timing diagram of the PWM-based CFS.

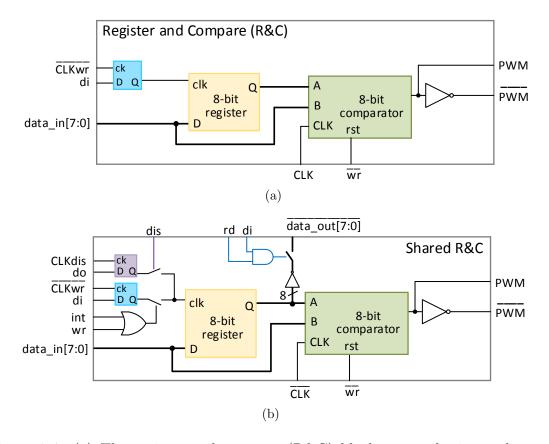

Figure 3.4: (a) The register and compare (R&C) block stores the input data and compares it with the counter value to generate the PWM signals. (b) The shared R&C block not only generates the PWM signals in the *integration* phase but also stores the counter value during the *discharge* phase to be read as the digital output data.

However, this system is expected to operate at clock frequencies higher than 100 MHz with a 1 V power supply voltage which reduces the leakage current. Secondly, unnecessary switching activities are minimized. This was done by carefully exploiting clock gating techniques throughout the design. Finally, power- and area-hungry resources are shared. For example, an array of  $M \times N$  multipliers have N outputs and M+N-1 inputs. Instead of assigning one counter per input and one per output, they could share one 8-bit counter for both digital-to-PWM (D/PWM) and PWM-to-digital (PWM/D) conversions. Moreover, each input and each output need an 8-bit register. However, since those registers are not utilized during the same time periods, they are shared to save even more area and power.

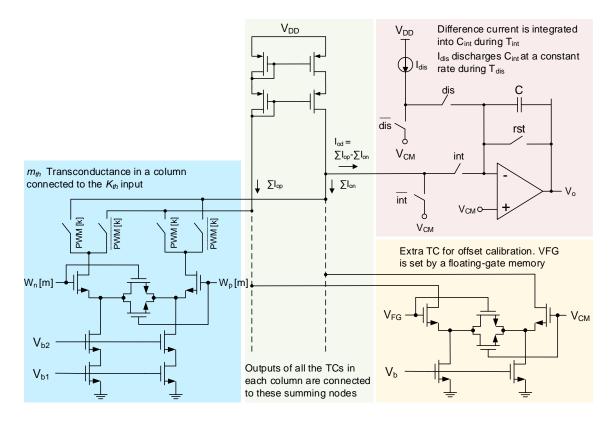

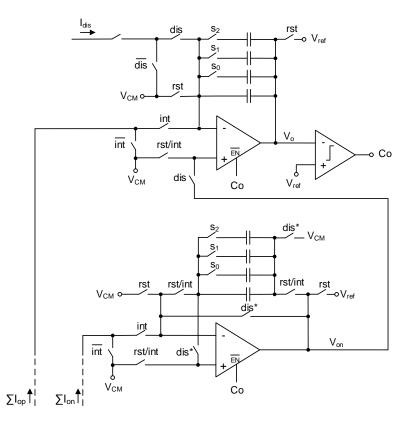

Figure 3.5: Detailed diagram illustrating the analog processing blocks and offset calibration circuit.

Figure 3.4(a) shows the block diagram of the register and compare (R&C) block. The R&C blocks store the input data during the *write* phase and generate the PWM signal by comparing it to the counter value during the *integration* phase. From a total of 64 R&C blocks, 41 of them are shared between the inputs and outputs. The block diagram of the shared R&C block is displayed in Figure 3.4(b). The main difference between the two blocks is that in addition to generating PWM signals during the *integration* phase, the shared R&C block stores the counter value when the analog comparator makes a decision during the *discharge* phase. This stored data is indeed the output data which is read out during the *read* phase. The timing diagram of the proposed CFS is depicted in Figure 3.3.

### 3.4 Analog Processing and Offset Calibration

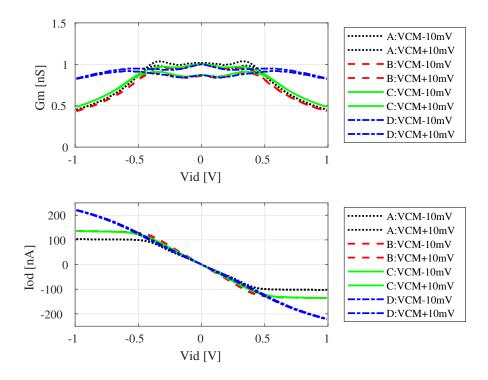

Figure 3.5 illustrates the analog processing blocks. The transconductance amplifier is a degenerated differential-pair operating in the sub-threshold region. As was mentioned before, a PWM signal controls the current flow to the summing nodes. In this design, there are 24 transconductance amplifiers at each column with their outputs connected to the summing nodes.

To compensate for the mismatch induced offset errors an extra transconductance amplifier is incorporated at each column. This transconductance amplifier is adjusted by a floating-gate memory. A cascode current mirror subtracts  $\Sigma I_{op}$  from  $\Sigma I_{on}$ (differential to single-ended conversion). The difference current  $I_{od}$  is then integrated into capacitor  $C_{int}$  during the *integration* phase. A current source discharges  $C_{int}$  at a constant rate at the *discharge* phase.

Figure 3.6 depicts the schematic of a class-AB OTA designed for integrator<sup>1</sup>. The class-AB operation allows the integrator to operate effectively in association with other high-speed blocks in the system while having a low quiescent bias current. In particular, it helps the integrator to settle faster in *reset* phase (reset happens during the *write* phase) by drawing instant high current from the power supply. To explain the operation of this OTA let's consider the end of a computation cycle where the  $C_{int}$  is discharged and the  $V_{OUT}$  value is close to ground and  $V_{IN+}$  is at  $V_{CM}$ . At this condition reset switch in Figure 3.5 closes as part of the preparedness phase for the next cycle. At this moment, transistor  $M_3$  turns off causing a voltage increase at node A. This increases the  $V_{GS}$  of  $M_5$ , drawing more current from  $M_2$  thus  $M_8$  and  $M_{10}$ . This considerable current flow instantly pulls the  $V_{OUT} = V_{IN-}$  voltage up to  $V_{CM}$ .

During the *discharge* phase and right after that the following comparator makes a decision, a network of switches deactivate the OTA to reduce the average power consumption. This reduction is noticeable at the bottom plot of Figure 3.27 which

<sup>&</sup>lt;sup>1</sup>Design credit goes to Tan Yang.

Figure 3.6: Schematic of the integrator OTA.

shows the power supply current profile of the integrators based on a post-layout simulation. To account for process variations and also to provide a flexible range for choosing the clock frequency of the system, the integration capacitor is made tunable to 8 different values. Table 3.1 shows the nominal value of  $C_{int}$  versus control bits.

| S              |       |       |       |  |

|----------------|-------|-------|-------|--|

| $C_{int}$ (fF) | $S_2$ | $S_1$ | $S_0$ |  |

| 167            | 0     | 0     | 0     |  |

| 334            | 0     | 0     | 1     |  |

| 467            | 0     | 1     | 0     |  |

| 634            | 0     | 1     | 1     |  |

| 768            | 1     | 0     | 0     |  |

| 935            | 1     | 0     | 1     |  |

| 1068           | 1     | 1     | 0     |  |

| 1235           | 1     | 1     | 1     |  |

Table 3.1: PWM-based CFS  $C_{int}$  Setting

# 3.5 Energy-Efficient Dynamic Comparator with a Fast Convergence Rate

The comparator is an essential building block in many applications that require analog to digital (A/D) conversion. The comparator plays a crucial role in the final performance of the systems. Although technology scaling has provided necessary means for low-power and high-speed comparator design, the offset voltage remains the main concern because by moving to deep submicron technology nodes not only the transistor mismatch does not improve but also degrades significantly [21]. To overcome this problem, several offset cancellation techniques have been reported in the literature. The conventional method utilizes a pre-amplifier with substantial gain to decrease the input-referred offset voltage which sometimes combines with auto-zeroing techniques implemented during negative feedback [36]. However, the maximum achievable gain for a single-stage amplifier has decreased in advanced technology nodes and adding more stages comes at the cost of extra power dissipation.

On the other hand, a dynamic comparator is a more attractive option since it does not consume any static power. Nevertheless, dynamic comparators suffer from even larger input referred offset compared to linear ones due to the extra mismatch caused by parasitic capacitors at the internal nodes. This indeed raises the necessity of implementing an effective offset calibration technique for dynamic comparators. In [43] offset calibration was implemented by digitally controlling the load capacitance of the dynamic latch. Yet the additional capacitance lowers the comparator speed and increases the chip area. Additionally, since in this method the calibration time is inversely proportional to the residual offset, it can take a significant amount of time before reaching the convergence for high-resolution A/D converters. In [2] a D/A converter controls the body voltage of input transistors in order to reduce the offset voltage. This technique realizes a 7-bit D/A converter with additional complex digital circuitry and takes 128 clock cycles to complete the calibration process. The offset cancellation method in [27], senses the offset by measuring the phase difference

Figure 3.7: Block diagram of the proposed offset calibration technique.

between the outputs and adjusts the body voltage of the input transistors. While this technique needs only a few clock cycles for calibration, the comparator speed is limited to under 7 MHz because of the phase detector resolution. An offset cancellation method using voltage-controlled current sources is presented in [31]. A charge pump circuitry changes the gate voltage of the current source which is in parallel with input transistor and compensates for the offset. Although this technique uses very few logic circuits to control the charge pump, it requires a long calibration time if a low residual offset is desired.

Here, a novel calibration technique is proposed with no static power dissipation which is able to converge rapidly while maintaining a high precision. The circuit uses a multi-rate charge pump circuitry controlled with simple logic circuits in order to achieve a short calibration time without sacrificing the accuracy and results in a better energy efficiency.

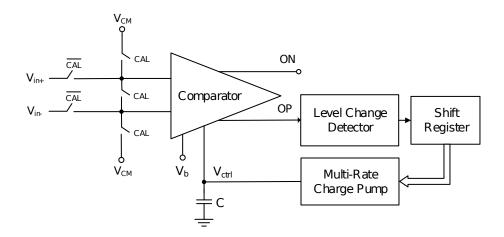

#### 3.5.1 Offset Calibration

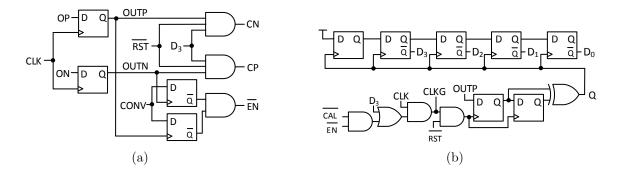

The block diagram of the proposed offset calibration technique is shown in Figure 3.7. In the calibration mode, comparator inputs are connected to a common-mode voltage. A digital block generates a pulse whenever a level change occurs at the comparator output (OP). This pulse goes into a shift register which generates a

Figure 3.8: (a) The digital block that generates CN and CP signals for the charge pump and  $\overline{EN}$  signal for the comparator. (b) The offset calibration flowchart.

digital sequence to control the charging/discharging rate in a multi-rate charge pump circuitry.

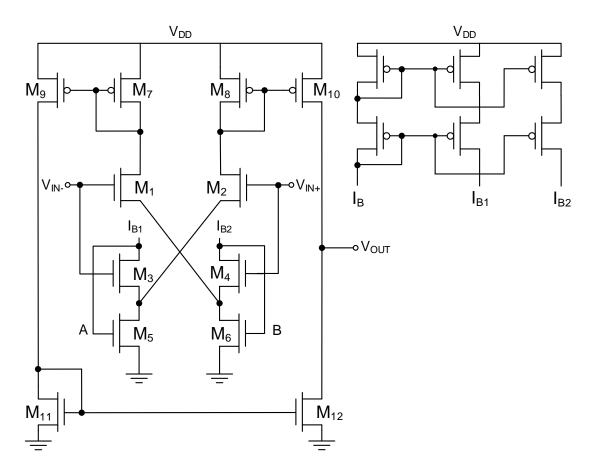

Figure 3.9: (a) The schematic diagram of the double-tail latched comparator and multi-rate charge pump circuitry, (b) The digital block that generates CN and CP signals for the charge pump and  $\overline{EN}$  signal for the comparator. (c) The level change detector and the following shift register that generates  $D_3$  to  $D_0$  bits.

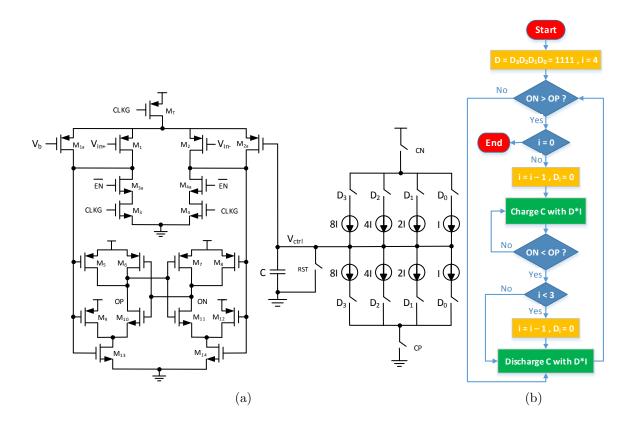

The schematic diagram of the comparator and the charge pump circuits are shown in Figure 3.8(a). The circuit is designed based on a double-tail latched comparator in [31]. The comparator is clocked with CLKG which is a gated version of the main CLK signal. The CLKG is only active during calibration and conversion phases. The circuit shuts down the CLKG after reaching the convergence in the calibration phase. Therefore the amount of time that the CLKG remains active during the calibration phase depends on the comparator initial offset. Moreover, transistors  $M_{3a}$  and  $M_{4a}$ disable the comparator when a decision has been made to save power. The clock gating approach combined with the fast convergence rate during the calibration phase, as well as, deactivating the comparator after making a decision during the conversion phase can have a significant impact on energy efficiency of the VLSI systems, where arrays of such comparators operate in parallel.

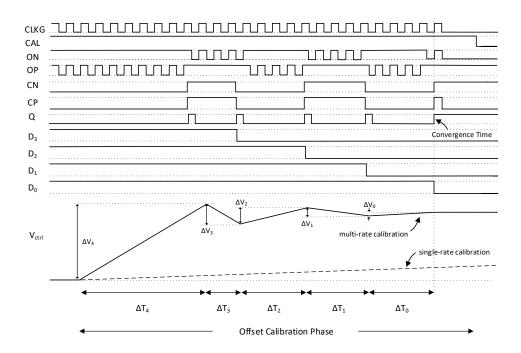

Transistors  $M_{1a}$  and  $M_{2a}$  are voltage controlled current sources. The gate of  $M_{1a}$  is connected to a reference voltage,  $V_b$ , and the gate of the  $M_{2a}$  is connected to capacitor C which holds the control voltage,  $V_{ctrl}$ . The  $V_{ctrl}$  which is regulated by the charge pump circuitry controls the gate of  $M_{1a}$  in order to balance out the mismatch caused by process variations by injecting current into internal nodes. The charge pump rate is controlled by 4 bits. The current sources and sinks are arranged in a binary weighted form as 8I, 4I, 2I, and I. Figure 3.10 illustrates the timing diagram and the typical waveforms during the offset calibration phase. At the beginning of the calibration phase, the capacitor C is initialized to the  $V_b$  and all the  $D_3$  to  $D_0$  bits are set to logic '1' and thus, all the current sources and sinks are connected to the  $V_{ctrl}$  node. The charge pump starts with the highest current of 15I which leads to the highest pump rate and then decreases the rate to 7I, 3I, and I as  $V_{ctrl}$ , approaches the final value. The digital sequence managing these transitions is generated by the level change detector and the shift register. This sequence is simply implemented by turning off  $D_3$  to  $D_0$  switches, one at a time when the *OP* changes from logic '1' to logic '0' or vice versa. This process continues until the last bit, i.e.  $D_0$  goes from logic

Figure 3.10: The timing diagram and typical waveforms during offset calibration phase.

'1' to logic '0', disconnecting the last current source and sink from the  $V_{ctrl}$  node, and ending the calibration phase.

It is worth mentioning that unlike the conventional method, in this method the charge pump is controlled by CN and CP signals rather than by comparator outputs (ON and OP). As shown in Figure 3.9(a) the CN and CP signals are generated by sampling comparator outputs at the rising edge of the CLK, and therefore, they remain at their current state until comparator outputs change. The level change detector and the shift register circuits are depicted in Figure 3.9(b). One of the outputs of the comparator is sampled at the rising edges of two consecutive CLKG signal in order to capture any logic level change. The indicator signal, Q is then used to clock a shift register circuit which simply shifts a logic '1' to the right and therefore generates  $D_3$  to  $D_0$  bits as shown in the timing diagram of Figure 3.10.

#### 3.5.2 Convergence Time

Thanks to the utilization of the multi-rate charge pump circuit, the proposed calibration scheme needs a very short time to reach the convergence. The dashed line in Figure 3.10 represents the  $V_{ctrl}$  node voltage in case of a conventional single-rate method with a current source I [31]. For the single-rate case, the calibration time for an initial offset value of  $V_{os}$  is equal to:

$$T_{cal,s} = V_{os} \cdot \frac{C}{I} \tag{3.3}$$

Based on this equation, for a short calibration time, one should use large I and small C. On the other hand, the residual offset voltage after calibration can be written as:

$$V_{res} = T_{clk} \cdot \frac{I}{C} \tag{3.4}$$

Clearly, the residual offset has an opposite proportionality to I and C, meaning that reaching low residual offset requires long calibration time. The total calibration time in the case of proposed multi-rate calibration, for the same residual offset, can be written as:

$$T_{cal,m} = \Delta T_0 + \Delta T_1 + \dots + \Delta T_4 \tag{3.5}$$

where  $\Delta T_i$  are the time intervals depicted in Figure 3.10. A simple calculation leads to:

$$T_{cal,m} = N \cdot T_{clk} + V_{os} \cdot \frac{C}{15I}$$

(3.6)

where N can be calculated from the current source ratios. If the current sources are binary weighted, N is close to 12. Thus, the first term on the right-hand side of (3.6) is constant for a given clock frequency. However, the second term depends on the  $V_{os}$  and has a 15X faster rate compared to the conventional single-rate method. As illustrated in the Figure 3.10, the total calibration time is significantly reduced compared to the single-rate approach, with the same goal for the residual offset.

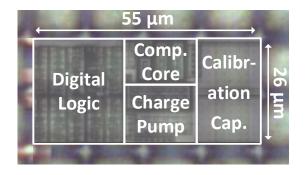

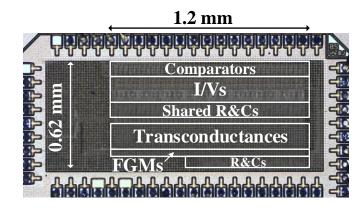

Figure 3.11: Chip micrograph of the comparator and offset calibration circuit.

#### 3.5.3Simulation and Experimental Results

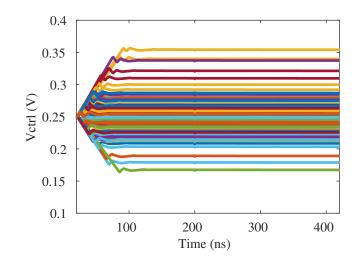

The comparator circuit was designed and fabricated in a  $0.13\mu$ m CMOS process. The chip micrograph is shown in Figure 3.11. To verify the effectiveness of the proposed technique over process variation and device mismatch, a statistical analysis was performed using the Monte-Carlo simulation. One hundred iterations were performed for the comparator with and without offset calibration. The circuit was

Figure 3.12: Convergence of the offset calibration for 100 Monte-Carlo iterations.

| Table 3.2: Convergence Time   |                        |             |  |

|-------------------------------|------------------------|-------------|--|

| Specification                 | multi-rate (this work) | single-rate |  |

| Mean $(\mu)$                  | 82 ns                  | 286 ns      |  |

| Standard deviation $(\sigma)$ | 15  ns                 | 680  ns     |  |

m. 0 m 1 1

Figure 3.13: Simulation results from 100 Monte-Carlo iterations (a) without calibration (b) with calibration.

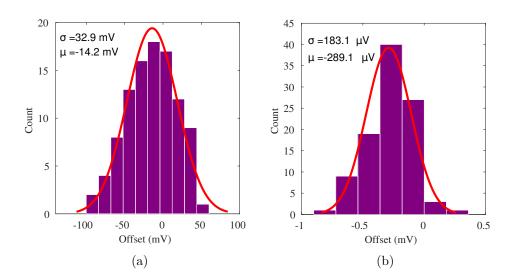

operating at 1 V power supply and 500 MHz clock frequency. Figure 3.12 shows the  $V_{ctrl}$  voltage during the time for the aforementioned Monte-Carlo simulation. While the maximum convergence time was only 139.6 ns, the average time was 82 ns with a standard deviation of 15 ns which is a significant improvement over the single-rate method, simulated at the same conditions, with an average of 286 ns and a standard deviation of 680.6 ns. Figure 3.13 shows the residual offset distribution of the comparator with and without calibration. As it is clear, the offset voltage without

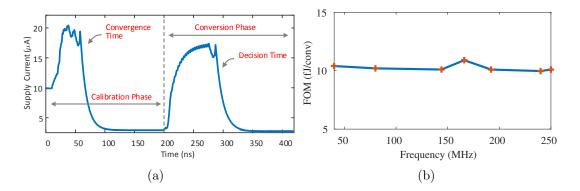

Figure 3.14: (a) Typical power supply current profile during offset calibration and conversion phases. (b) Measured FOM over clock frequencies from 40 MHz to 250 MHz.

| Table 5.5. Comparator Summary of Ferrormanee     |                        |  |

|--------------------------------------------------|------------------------|--|