Doctoral Dissertations Graduate School

8-2017

# MODELING AND SPICE IMPLEMENTATION OF SILICON-ON-INSULATOR (SOI) FOUR GATE (G4FET) TRANSISTOR

Md Sakib Hasan University of Tennessee, Knoxville, mhasan4@vols.utk.edu

### Recommended Citation

Hasan, Md Sakib, "MODELING AND SPICE IMPLEMENTATION OF SILICON-ON-INSULATOR (SOI) FOUR GATE (G4FET) TRANSISTOR." PhD diss., University of Tennessee, 2017. https://trace.tennessee.edu/utk\_graddiss/4626

This Dissertation is brought to you for free and open access by the Graduate School at Trace: Tennessee Research and Creative Exchange. It has been accepted for inclusion in Doctoral Dissertations by an authorized administrator of Trace: Tennessee Research and Creative Exchange. For more information, please contact trace@utk.edu.

### To the Graduate Council:

I am submitting herewith a dissertation written by Md Sakib Hasan entitled "MODELING AND SPICE IMPLEMENTATION OF SILICON-ON-INSULATOR (SOI) FOUR GATE (G4FET) TRANSISTOR." I have examined the final electronic copy of this dissertation for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Doctor of Philosophy, with a major in Electrical Engineering.

Syed K. Islam, Major Professor

We have read this dissertation and recommend its acceptance:

Benjamin J. Blalock, Nicole McFarlane, Ramakrishnan Kalyanaraman

Accepted for the Council: <u>Dixie L. Thompson</u>

Vice Provost and Dean of the Graduate School

(Original signatures are on file with official student records.)

# MODELING AND SPICE IMPLEMENTATION OF SILICON-ON-INSULATOR (SOI) FOUR GATE (G4FET) TRANSISTOR

A Dissertation Presented for the

**Doctor of Philosophy**

Degree

The University of Tennessee, Knoxville

Md Sakib Hasan

August 2017

# **DEDICATION**

This dissertation is dedicated to my parents,

Zahir Uddin Ahmed

and

Shirin Akhter Lovely.

### **ACKNOWLEDGMENTS**

I would like to express my earnest gratitude to my advisor Dr. Syed K. Islam for all the help and guidance he has provided me throughout my years of graduate study. His advice on matters, both technical and non-technical, has taught me how to grow as a successful engineer. Without his constant encouragement and direction, this journey would not have been possible.

Special thanks go to Dr. Benjamin J. Blalock for his guidance and support as well as for the excellent courses he taught. I have benefited greatly from the conversations we had about circuit design and G<sup>4</sup>FET.

I would like to extend my gratitude to Dr. Nicole McFarlane for serving on my committee and for her insightful suggestions about improving the work.

I would also like to thank Dr. Ramakrishnan Kalyanaraman for finding time from his busy schedule to serve on my Ph.D. committee.

I am grateful to The Institute of Biomedical Engineering at the University of Tennessee and the Min H. Kao Department of Electrical Engineering and Computer Science at the University of Tennessee, Knoxville for their financial support.

I have had the good fortune of benefiting from important discussions with various people which have helped me a lot in my research. I would specially like to thank Ifana Mahbub, Khandakar Abdullah Al Mamun, Md Habibullah Habib, Riyasat Azim, Ishtiaque Hossain and Shamim Ara for making my graduate life enjoyable. Finally, I would like to express my deepest gratitude to my parents, Zahir Uddin Ahmed and Shirin Akhter Lovely, my brother Rajib Hasan and my friends Arunodoy, Avijit, Shibani, Himadri, Zisan, Farah, Babu bhai, Sanjib, Dulal, Ratna and Monir vai.

### **ABSTRACT**

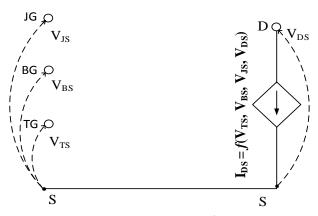

As the device dimensions have reduced from micrometer to nanometer range, new bulk silicon devices are now facing many undesirable effects of scaling leading device engineers to look for new process technologies. Silicon-on-insulator (SOI) has emerged as a very promising candidate for resolving the major problems plaguing the bulk silicon technology. G<sup>4</sup>FET [G4FET] is a SOI transistor with four independent gates. Although G<sup>4</sup>FET has already shown great potential in different applications, the widespread adoption of a technology in circuit design is heavily dependent upon good SPICE (*Simulation Program with Integrated Circuit Emphasis*) models. CAD (Computer Aided Design) tools are now ubiquitous in circuit design and a fast, robust and accurate SPICE model is absolutely necessary to transform G<sup>4</sup>FET into a mainstream technology.

The research goal is to develop suitable SPICE models for G<sup>4</sup>FET to aid circuit designers in designing innovative analog and digital circuits using this new transistor. The first phase of this work is numerical modeling of the G<sup>4</sup>FET where four different numerical techniques are implemented, each with its merits and demerits. The first two methods are based on multivariate Lagrange interpolation and multidimensional Bernstein polynomial. The third numerical technique is based on multivariate regression polynomial to aid modeling with dense gridded data. Another suitable alternative namely multidimensional linear and cubic spline interpolation is explored as the fourth numerical modeling approach to solve some of the problems resulting from single polynomial approximation.

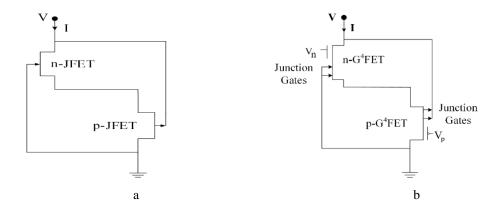

The next phase of modeling involves developing a macromodel combining already existing SPICE models of MOSFET (metal-oxide-semiconductor field-effect transistor) and JFET (junction-gate field-effect transistor). This model is easy to implement in circuit simulators and

provides good results compared to already demonstrated experimental works with innovative G<sup>4</sup>FET circuits. The final phase of this work involves the development of a physics-based compact model of G<sup>4</sup>FET with some empirical fitting parameters. A model for depletion-all-around operation is implemented in circuit simulator based on previous work. Another simplified model, combining MOS and JFET action, is implemented in circuit simulator to model the accumulation mode operation of G<sup>4</sup>FET.

# TABLE OF CONTENTS

| Chapter 1 – Introduction                                                                 | 1  |

|------------------------------------------------------------------------------------------|----|

| 1.1 Motivation                                                                           | 1  |

| 1.2 Research Goal                                                                        | 5  |

| 1.3 Dissertation Overview                                                                | 6  |

| Chapter 2 - Literature Review                                                            | 7  |

| 2.1 Previous Works on G <sup>4</sup> FET                                                 | 7  |

| 2.2 Previous Works on Numerical Modeling                                                 | 10 |

| 2.3 Previous Works on Macromodels                                                        | 13 |

| 2.4 Previous Works on Physics-based Compact Modeling                                     | 15 |

| Chapter 3 - Device Structure and Operating Mechanism of G <sup>4</sup> FET               | 21 |

| 3.1 Multiple Independent Gate Silicon-On-Insulator (SOI) Transistor                      | 21 |

| 3.2 G <sup>4</sup> FET Device Structure                                                  | 23 |

| 3.3 Principle of Operation                                                               | 24 |

| 3.4 Effect of Gate Bias on Conduction Path                                               | 26 |

| 3.5 Chapter Summary                                                                      | 29 |

| Chapter 4 - Numerical Modeling of G <sup>4</sup> FET                                     | 30 |

| 4.1 Overview                                                                             | 30 |

| 4.2 Numerical Method 1 (Multivariate Lagrange Interpolation Polynomial Model)            | 31 |

| 4.2.1 Model Formulation                                                                  | 31 |

| 4.2.2 Model Validation                                                                   | 34 |

| 4.2.2.1 An <i>n</i> -Channel G <sup>4</sup> FET Simulated with TCAD Sentaurus (Device 1) | 34 |

| 4.2.2.2 Experimental Data from an <i>n</i> -Channel G <sup>4</sup> FET (Device 2)        | 37 |

| 4.2.2.3 A p-Channel G <sup>4</sup> FET Simulated Using TCAD Sentaurus (Device 3)         | 39 |

| 4.2.2.4 Experimental Data from a <i>p</i> -Channel G <sup>4</sup> FET (Device 4)          | 42   |

|-------------------------------------------------------------------------------------------|------|

| 4.2.2.5 Incorporation of Device Geometry                                                  | 45   |

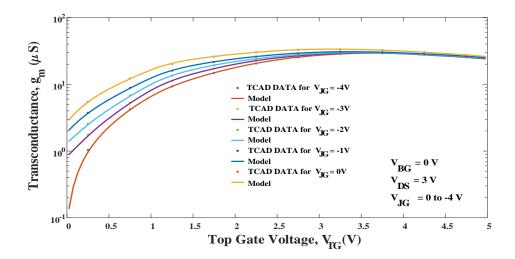

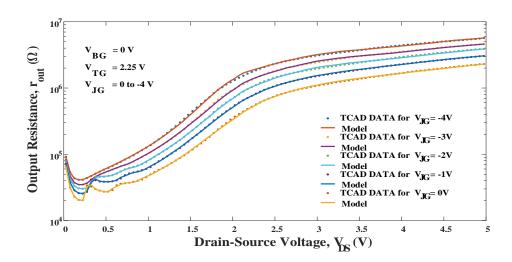

| 4.2.2.6 First Order Characteristics i.e. Transconductance and Drain Output Resistance     | 46   |

| 4.2.3 Implementation in Circuit Simulator                                                 | 46   |

| 4.2.4 Results from G <sup>4</sup> FET Circuit Simulation                                  | 49   |

| 4.3 Numerical Method 2 (Multidimensional Bernstein Polynomial Model)                      | 52   |

| 4.3.1 Model Formulation                                                                   | 52   |

| 4.3.2 Model Validation                                                                    | 53   |

| 4.3.2.1 An <i>n</i> -Channel G <sup>4</sup> FET Simulated Using TCAD Sentaurus (Device 1) | 53   |

| 4.3.2.2 Experimental Data from an <i>n</i> -Channel G <sup>4</sup> FET (Device 2)         | 55   |

| 4.3.2.3 A p-Channel G <sup>4</sup> FET Simulated Using TCAD Sentaurus (Device 3)          | 57   |

| 4.3.2.4 Experimental Data from a <i>p</i> -Channel G <sup>4</sup> FET (Device 4)          | 58   |

| 4.3.2.5 Incorporation of Device Geometry                                                  | 60   |

| 4.3.2.6 First Order Characteristics i.e. Transconductance and Drain Output Resistance     | 60   |

| 4.4 Numerical Method 3 (Multivariate Regression Polynomial Model)                         | 63   |

| 4.4.1 Model Formulation                                                                   | 63   |

| 4.4.2 Model Validation                                                                    | 65   |

| 4.4.2.1 An <i>n</i> -Channel G <sup>4</sup> FET Simulated Using TCAD Sentaurus (Device 1) | 65   |

| 4.4.2.2 Experimental Data from an <i>n</i> -Channel G <sup>4</sup> FET (Device 2)         | 69   |

| 4.4.2.3 A p-Channel G <sup>4</sup> FET Simulated Using TCAD Sentaurus (Device 3)          | 72   |

| 4.4.2.4 Experimental Data from a <i>p</i> -Channel G <sup>4</sup> FET (Device 4)          | 76   |

| 4.4.2.5 Modeling of Device Geometry                                                       | 79   |

| 4.4.2.6 First Order Characteristics (Device Transconductance and Drain Output Resistance) | 81   |

| 4.4.3 Circuit Simulator (SPICE and Spectre <sup>TM</sup> ) Implementation                 | 83   |

| 4.4.4 Results from G <sup>4</sup> FET Circuit Simulation                                  | 84   |

| 4.5 Numerical method 4 (Multidimensional Linear and Cubic Spline Interpolation Mode       | 1)86 |

| 4.5.1 Model Formulation                                                                   | 87   |

| 4.5.1.1 Linear Spline Model                                                               | 87   |

| 4.5.1.2 Cubic Spline Model                                                                | 88   |

| 4.5.2 Model Validation                                                                                 | 89     |

|--------------------------------------------------------------------------------------------------------|--------|

| 4.5.2.1 An <i>n</i> -Channel G <sup>4</sup> FET Simulated Using TCAD Sentaurus (Device 1)              | 89     |

| 4.5.2.2 Experimental Data from an <i>n</i> -Channel G <sup>4</sup> FET (Device 2)                      | 91     |

| 4.5.2.3 A p-Channel G <sup>4</sup> FET Simulated with TCAD Sentaurus (Device 3)                        | 93     |

| 4.5.2.4 Experimental Data from a p-Channel G <sup>4</sup> FET (Device 4)                               | 95     |

| 4.5.2.5 Incorporation of Device Geometry                                                               | 96     |

| 4.5.2.6 Validation of First Order Characteristics i.e. Device Transconductance and Output Drain Resist | ance97 |

| 4.5.3 Implementation in Circuit Simulator                                                              | 99     |

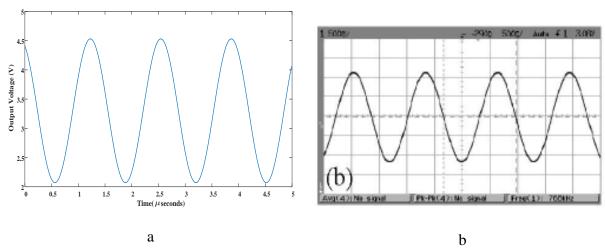

| 4.5.4 Results from G <sup>4</sup> FET Circuit Simulation                                               | 100    |

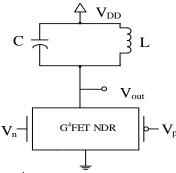

| 4.5.4.1 Negative Differential Resistance (NDR) LC oscillator:                                          | 100    |

| 4.5.4.2 High Voltage Differential Amplifier                                                            | 101    |

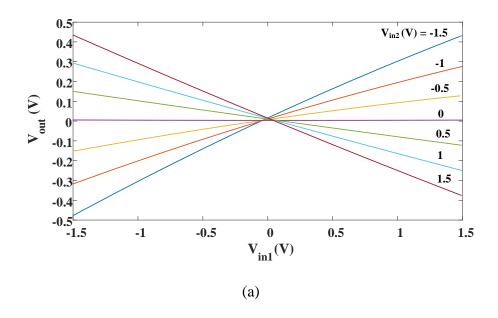

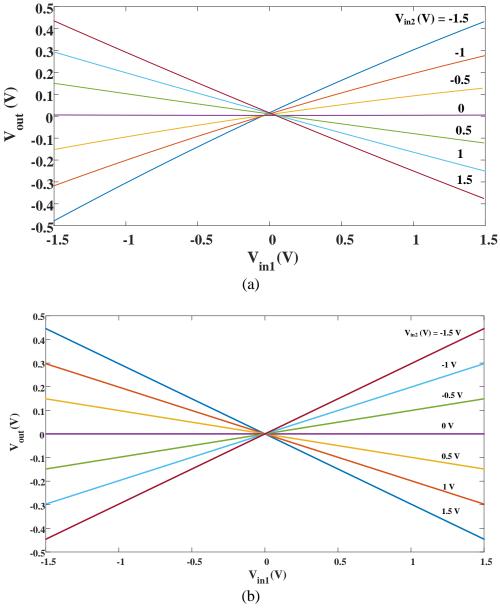

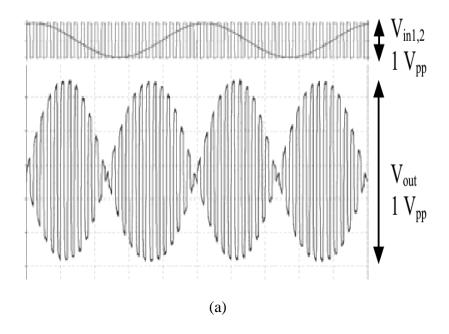

| 4.5.4.3 Four-Quadrant Analog Multiplier:                                                               | 102    |

| 4.6 Chapter Summary                                                                                    | 109    |

| Chapter 5 - Macromodel of G <sup>4</sup> FET                                                           |        |

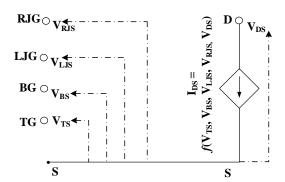

| 5.2 Model Formation                                                                                    |        |

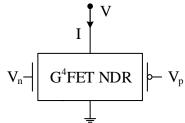

| 5.3 CAD Implementation for Circuit Design                                                              |        |

| 5.3.1 Negative Differential Resistance Circuit:                                                        |        |

| 5.3.2 Differential Amplifier:                                                                          |        |

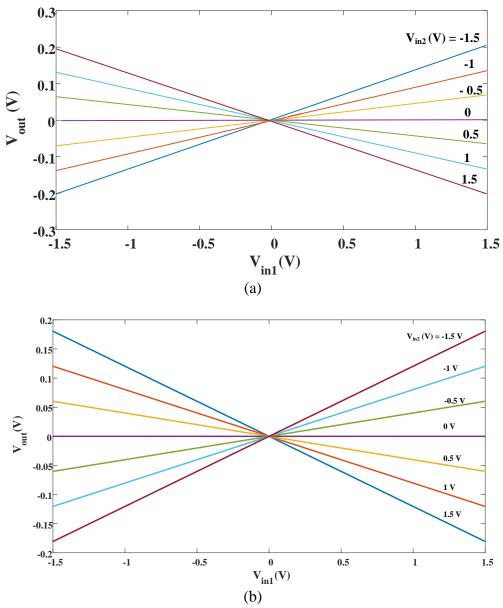

| 5.3.3 Four Quadrant Analog Multiplier :                                                                |        |

| 5.3.4 Multi-Threshold Inverter:                                                                        | 122    |

| 5.3.5 Universal and Programmable Gate:                                                                 | 122    |

| 5.3.6 Full Adder:                                                                                      | 124    |

| 5.4 Chapter Summary                                                                                    | 127    |

| Chapter 6 – Physics-Based Compact Model of G <sup>4</sup> FET                                          | 128    |

| 6.1 Motivation                                                                                         | 128    |

| 6.2 Depletion All Around (DAA) Model                                                                   | 128    |

|                                                                                                        | viii   |

| 6.2.1 Model Formulation                | 129 |

|----------------------------------------|-----|

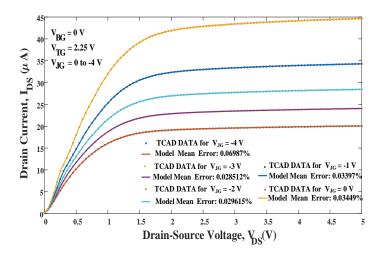

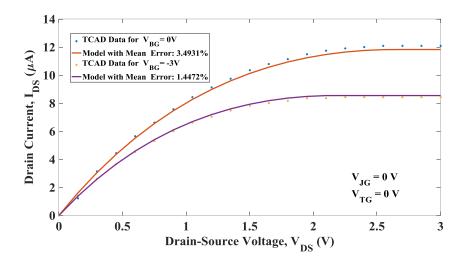

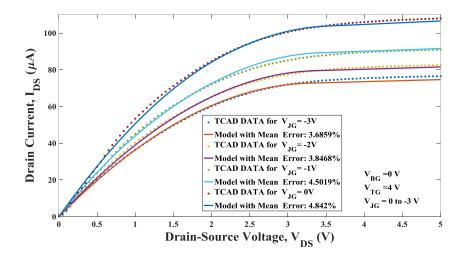

| 6.2.2 Model Validation                 | 131 |

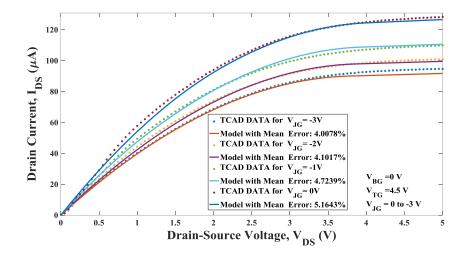

| 6.3 Front Surface Accumulation Model   | 134 |

| 6.3.1 Model Formulation                | 135 |

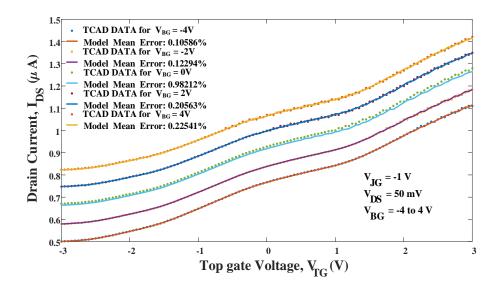

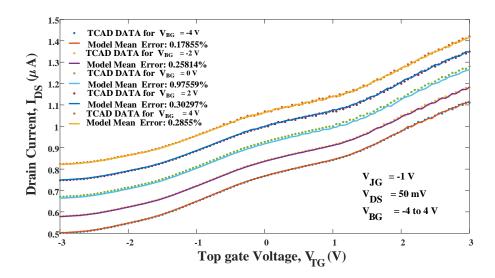

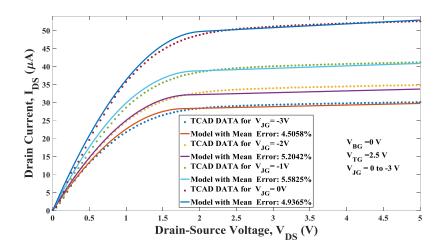

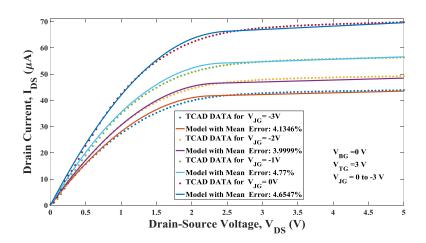

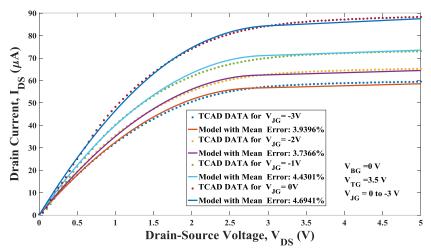

| 6.3.2 Model Validation                 | 136 |

| 6.4 Chapter Summary                    | 139 |

| Chapter 7 - Conclusion and Future Work | 140 |

| 7.1 Original Contributions             | 140 |

| 7.2 Dissertation Summary               | 142 |

| 7.3 Future Works                       | 143 |

| References                             | 145 |

| Vita                                   | 160 |

# LIST OF TABLES

| Table 4.1: Geometry, Doping and Biasing for an <i>n</i> -Channel G <sup>4</sup> FET       |

|-------------------------------------------------------------------------------------------|

| Table 4.2: Geometry, Doping and Biasing for a <i>p</i> -Channel G <sup>4</sup> FET        |

| Table 4.3: Computational Complexity of Lagrange Model                                     |

| Table 4.4: Computational Complexity of Regression Model                                   |

| Table 4.5: Comparison Between Experimental and Simulation Results for DC Transfer         |

| Characteristics of Configuration 1                                                        |

| Table 4.6: Comparison Between Experimental rand Simulation Results for DC Transfer        |

| Characteristics of Configuration 2                                                        |

| Table 5.1: Comparison Between Experimental and Simulation Results (Macromodel) for DC     |

| Transfer Characteristics of Analog Multiplier (Configuration 1)                           |

| Table 5.2: Comparison of Experimental and Simulation Results (Macromodel) for DC Transfer |

| Characteristics of Analog Multiplier (Configuration 2)                                    |

| Table 5.3: Truth Table of a Full Adder                                                    |

# LIST OF FIGURES

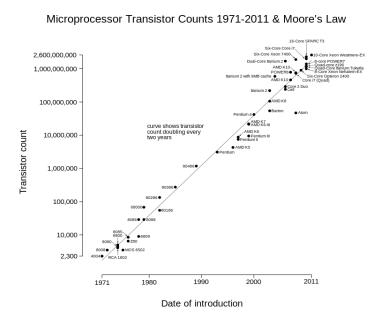

| Figure 1.1: Moore's Law dictating transistor counts in microprocessor over the years [9] 2                                             |

|----------------------------------------------------------------------------------------------------------------------------------------|

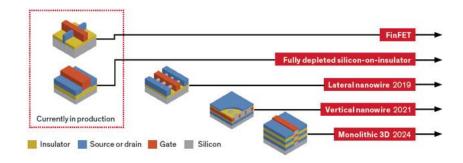

| Figure 1.2: Change of direction in gate length scaling from 2013 to 2015 ITRS report [13] 3                                            |

| Figure 1.3: Possible alternatives for extending Moore's law                                                                            |

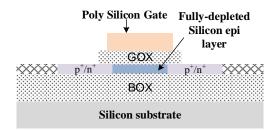

| Figure 3.1: Three layers of SOI wafer. 21                                                                                              |

| Figure 3.2: Cross-sectional schematic of a fully depleted (FD) SOI device                                                              |

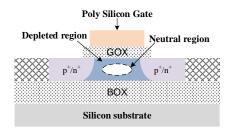

| Figure 3.3: Cross-sectional schematic of a partially depleted (PD) SOI                                                                 |

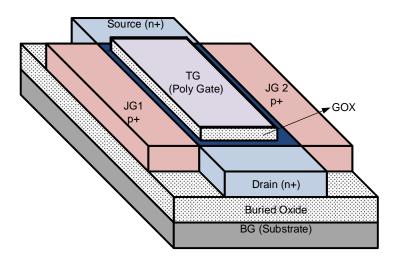

| Figure 3.4: 3-D Schematic of a G <sup>4</sup> FET structure.                                                                           |

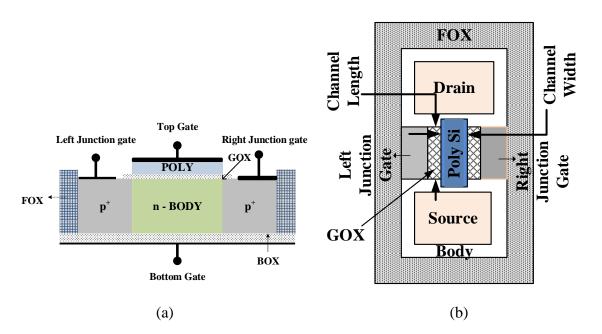

| Figure 3.5: G <sup>4</sup> FET structure: (a) cross section and (b) top view                                                           |

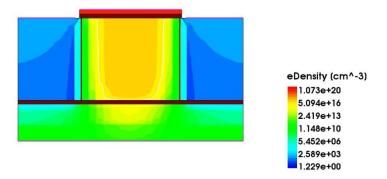

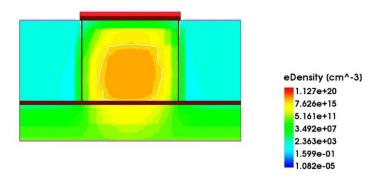

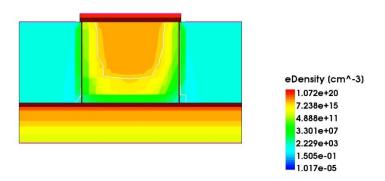

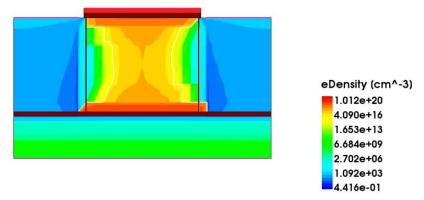

| Figure 3.6: Electron density in the top silicon film at $V_{TG} = 0$ V, $V_{BG} = 0$ V and $V_{JG} = 0$ V 27                           |

| Figure 3.7: Electron density in the top silicon film at $V_{TG} = -3$ V, $V_{BG} = 0$ V and $V_{JG} = 0$ V 27                          |

| Figure 3.8: Electron density in the top silicon film at $V_{TG} = 0$ V $V_{BG} = -3$ V $V_{JG} = 0$ V                                  |

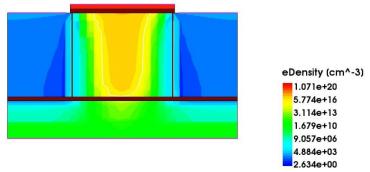

| Figure 3.9: Electron density in the top silicon film at $V_{TG} = -3$ V, $V_{BG} = -3$ V and $V_{JG} = 0$ V 28                         |

| Figure 3.10: Electron density in the top silicon film at $V_{TG} = 0$ V, $V_{BG} = 0$ V and $V_{JG} = -1$ V 28                         |

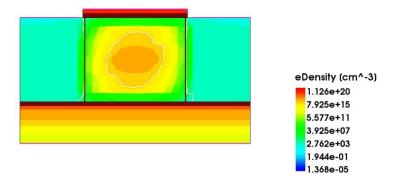

| Figure 3.11: Electron density in the top silicon film at $V_{TG} = 3 \text{ V}$ , $V_{BG} = 0 \text{ V}$ and $V_{JG} = 0 \text{ V}$ 28 |

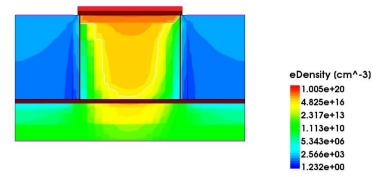

| Figure 3.12: Electron density in the top silicon film at $V_{TG} = 3$ V, $V_{BG} = 10$ V and $V_{JG} = 0$ V 29                         |

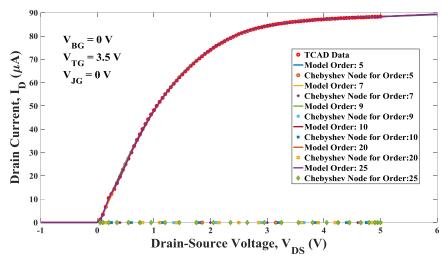

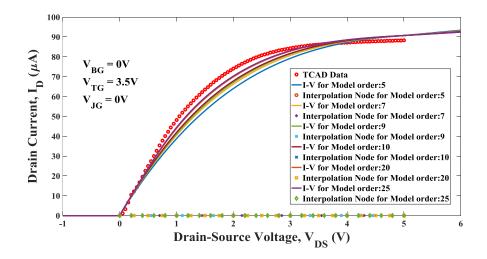

| Figure 4.1: Drain current versus drain-source voltage from TCAD data and Lagrange model for                                            |

| different orders of $V_{DS}$ for an $n$ -channel $G^4FET$                                                                              |

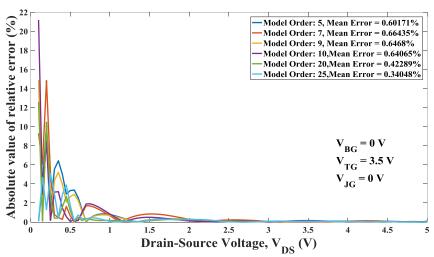

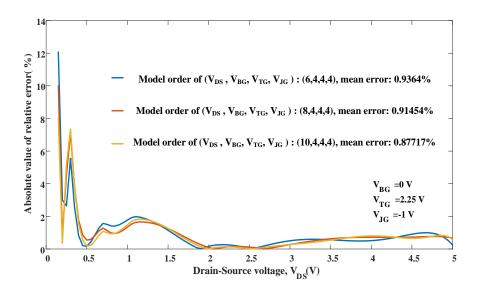

| Figure 4.2: Relative errors between TCAD data and Lagrange model for different orders of $V_{DS}$ for                                  |

| an <i>n</i> -channel G <sup>4</sup> FET. 36                                                                                            |

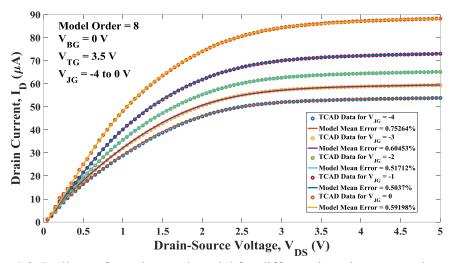

| Figure 4.3: Isolines of test data and model for different junction-gate voltages ranging from -4 V                                     |

| to 0 V in 1 V increment with order of $V_{DS}$ fixed at 8                                                                              |

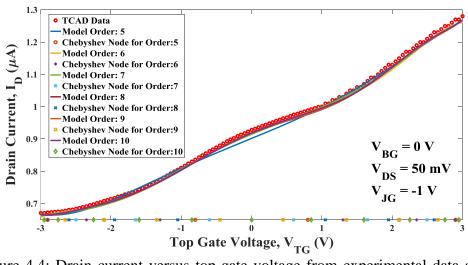

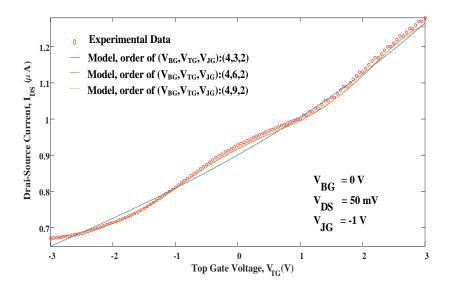

| Figure 4.4: Drain current versus top-gate voltage from experimental data and Lagrange model for               |

|---------------------------------------------------------------------------------------------------------------|

| different orders of $V_{TG}$ for an $n$ -channel G <sup>4</sup> FET (Device 2)                                |

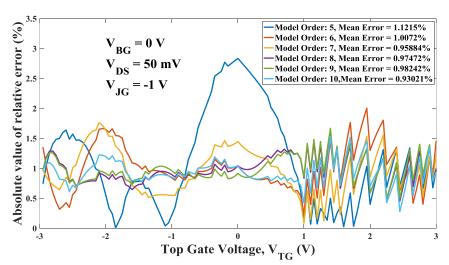

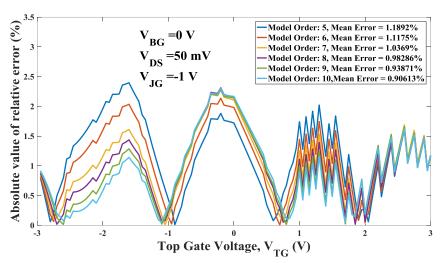

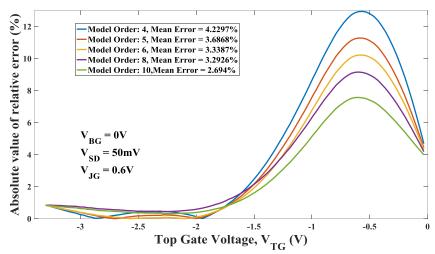

| Figure 4.5: Relative errors in model prediction for different orders of $V_{TG}$ for an $n$ -channel $G^4FET$ |

| (Device 2)                                                                                                    |

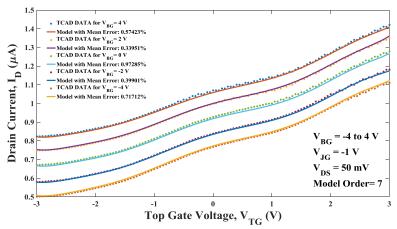

| Figure 4.6: Comparison between isolines of test data and Lagrange model for different bottom-                 |

| gate voltages ranging from -4 V to 4 V in 2 V increment with the model order for $V_{TG}$ fixed               |

| at 7 (Device 2)                                                                                               |

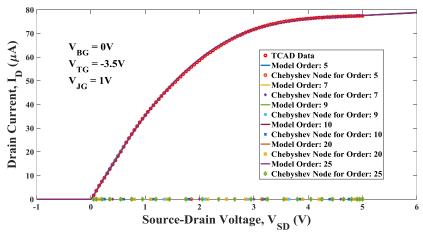

| Figure 4.7: Drain current versus source-drain voltage from TCAD data and Lagrange model for                   |

| different orders of $V_{SD}$ for a $p$ -channel G <sup>4</sup> FET (Device 3)                                 |

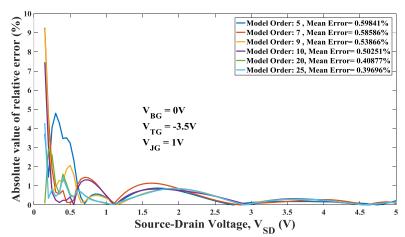

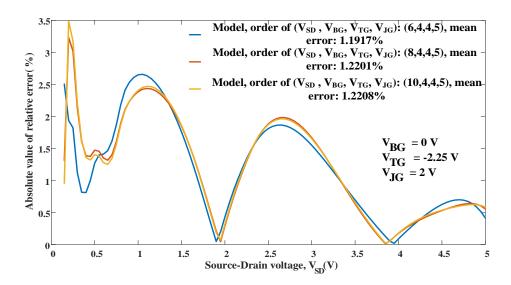

| Figure 4.8: Relative errors between TCAD data and Lagrange model for different orders of $V_{SL}$             |

| for a <i>p</i> -channel G <sup>4</sup> FET (Device 3)                                                         |

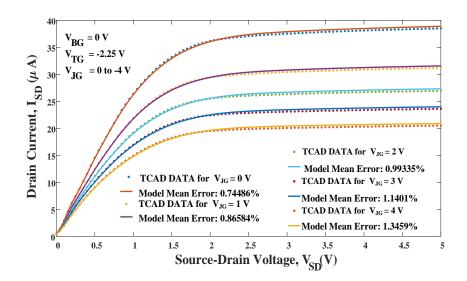

| Figure 4.9: Drain current versus source-drain voltage for different junction-gate voltages ranging            |

| from 0 V to 4 V in 1 V increment and corresponding mean relative error (Device 3) 42                          |

| Figure 4.10: Comparison of $I_D$ - $V_{TG}$ between experimental data and Lagrange model for different        |

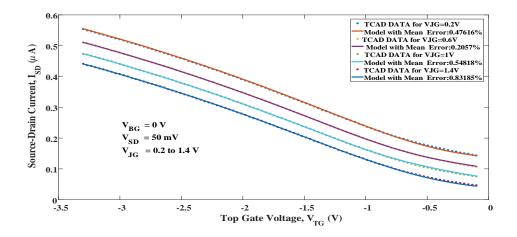

| orders of $V_{TG}$ for a $p$ -Channel G <sup>4</sup> FET (Device 4).                                          |

| Figure 4.11: Relative errors between experimental data and Lagrange model for different orders                |

| of $V_{TG}$ for a $p$ -Channel G <sup>4</sup> FET (Device 4).                                                 |

| Figure 4.12: Comparison between isolines of test data and model ( $10^{th}$ order $V_{TG}$ ) for different    |

| junction-gate voltages ranging from 0.6 V to 1.8 V in 0.4 V increment arranged from top to                    |

| bottom (Device 4)                                                                                             |

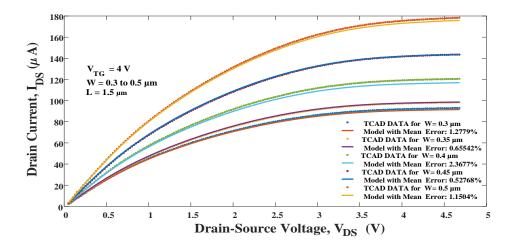

| Figure 4.13: Comparison of drain current versus drain-source voltage between TCAD data and                    |

| Lagrange model of test geometry for different orders                                                          |

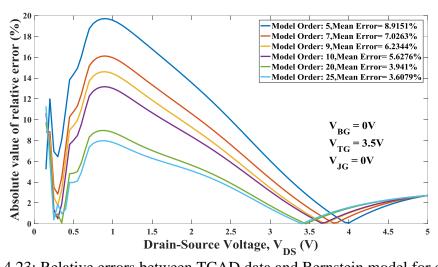

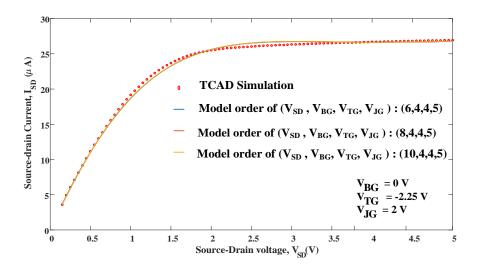

| Figure 4.27: Relative errors between TCAD data and Bernstein model for different orders of $V_{SD}$        |

|------------------------------------------------------------------------------------------------------------|

| for a <i>p</i> -channel G <sup>4</sup> FET (Device 3). 58                                                  |

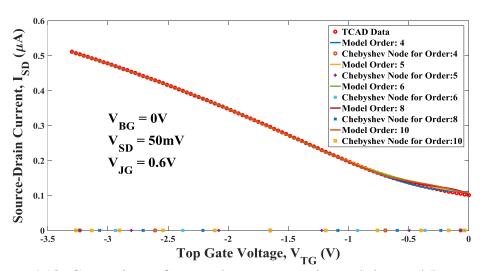

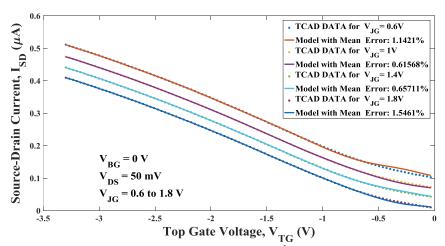

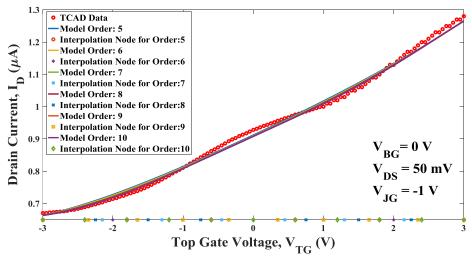

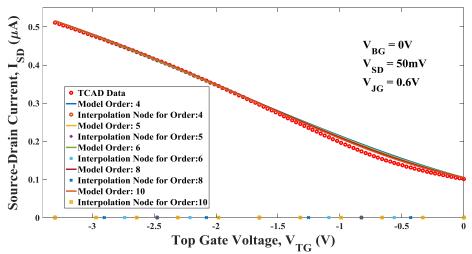

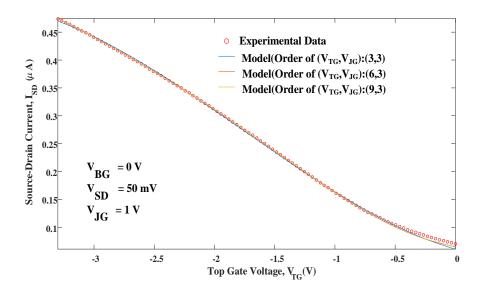

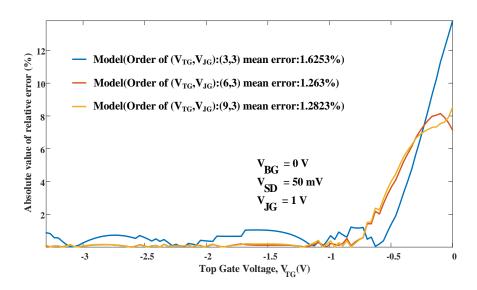

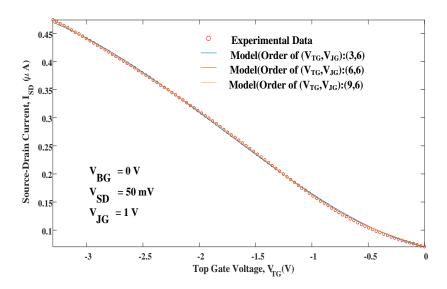

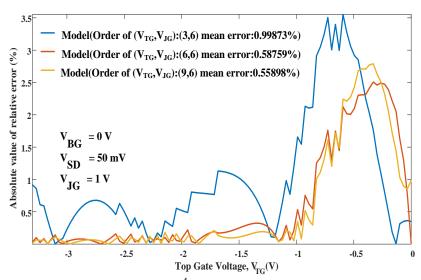

| Figure 4.28: Comparison of $I_{SD}$ - $V_{TG}$ between experimental data and Bernstein model for different |

| orders of $V_{TG}$ for a $p$ -channel G <sup>4</sup> FET (Device 4).                                       |

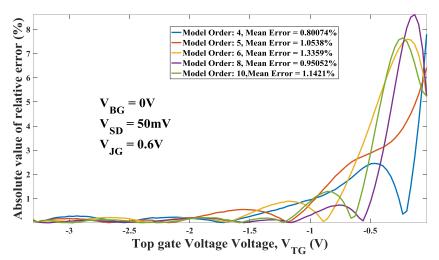

| Figure 4.29: Relative errors between experimental data and Bernstein model for different orders            |

| of $V_{TG}$ for a $p$ -channel G <sup>4</sup> FET (Device 4).                                              |

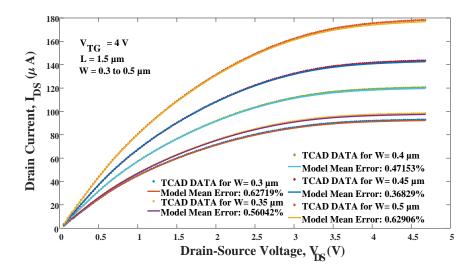

| Figure 4.30: Drain current versus drain-source voltage from TCAD data and Bernstein model of               |

| different orders for test geometry                                                                         |

| Figure 4.31: Relative errors between TCAD data and Bernstein model for test geometry 61                    |

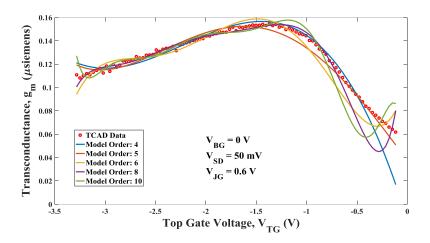

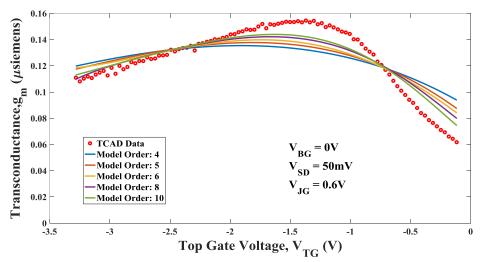

| Figure 4.32: Transconductance versus top-gate voltage from experimental data and Bernstein                 |

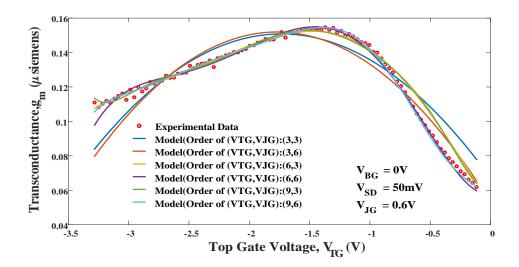

| model for different orders of $V_{TG}$ for a $p$ -channel G <sup>4</sup> FET (Device 4)                    |

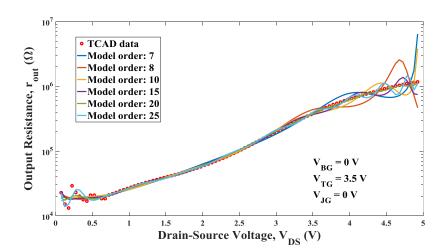

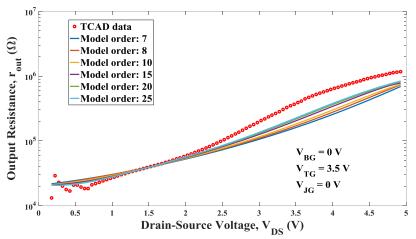

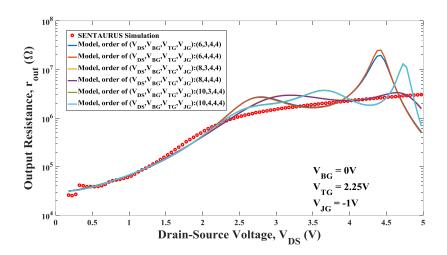

| Figure 4.33: Output resistance versus drain-source voltage from TCAD data and Bernstein model              |

| for different orders of $V_{DS}$ for an $n$ -channel G <sup>4</sup> FET (Device 1)                         |

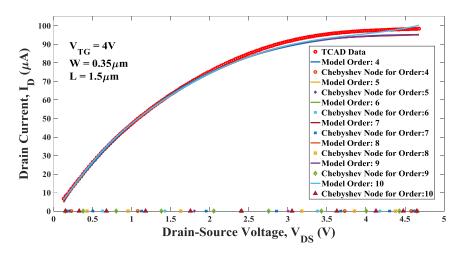

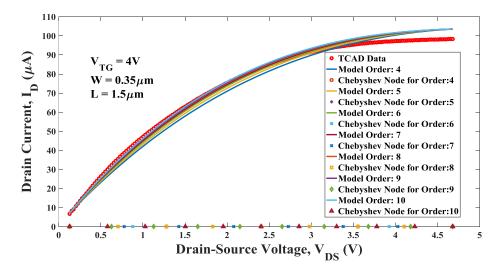

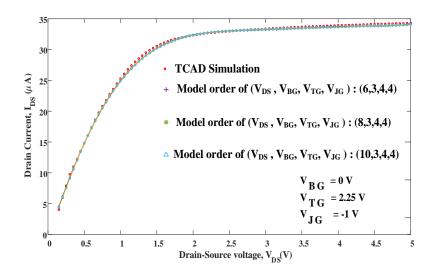

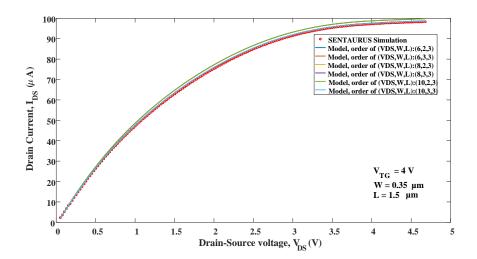

| Figure 4.34: Comparison of $I_{DS}$ - $V_{DS}$ between TCAD data and regression model for different orders |

| of $V_{DS}$ with order of $V_{BG}$ fixed at 3 for an $n$ -channel $G^4FET$                                 |

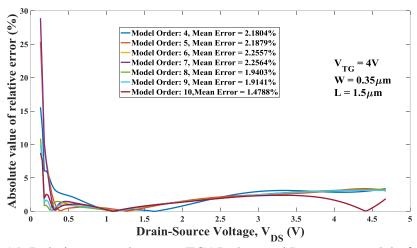

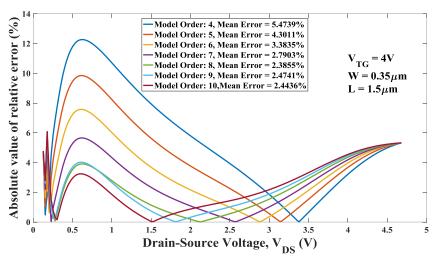

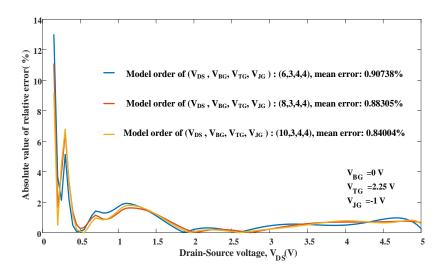

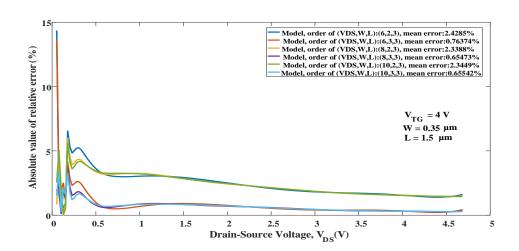

| Figure 4.35: Relative error between TCAD data and regression model for different orders of $V_{DS}$        |

| with $V_{BG}$ fixed at 3 for an $n$ -channel G <sup>4</sup> FET. 67                                        |

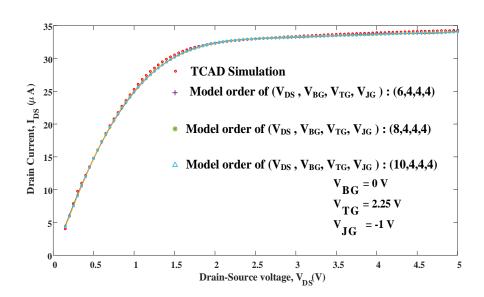

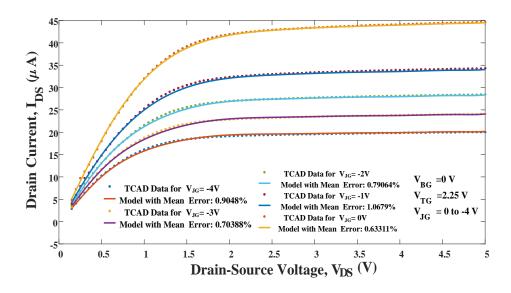

| Figure 4.36: Comparison of $I_{DS}$ - $V_{DS}$ between TCAD data and regression model for different orders |

| of $V_{DS}$ with order of $V_{BG}$ fixed at 4 for an $n$ -channel $G^4FET$                                 |

| Figure 4.37: Relative error between TCAD data and regression model for different orders of $V_{DS}$        |

| with order of $V_{BG}$ fixed at 4 for an $n$ -channel $G^4FET$                                             |

| Figure 4.38: Comparison between isolines of test data and regression model (order of $V_{DS}$ , $V_{BG}$ ,  |

|-------------------------------------------------------------------------------------------------------------|

| $V_{TG}$ , $V_{JG}$ respectively 10, 4, 5 and 5) for different junction-gate voltages ranging from -4 V to  |

| 0 V in 1 V increment arranged from bottom to top                                                            |

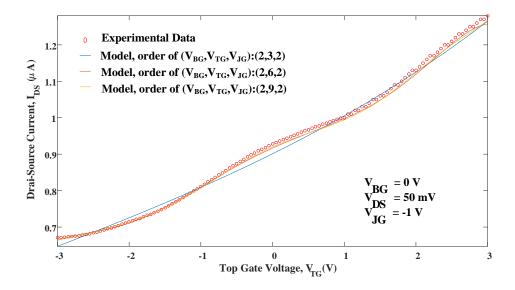

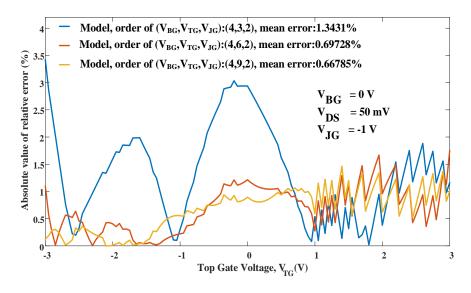

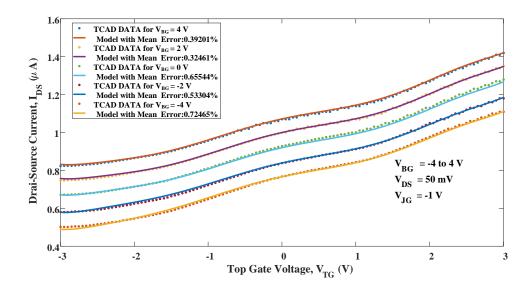

| Figure 4.39: Comparison of $I_{DS}$ - $V_{TG}$ between experimental data and regression model for different |

| orders of $V_{TG}$ with the order of $V_{BG}$ and $V_{JG}$ fixed at 2                                       |

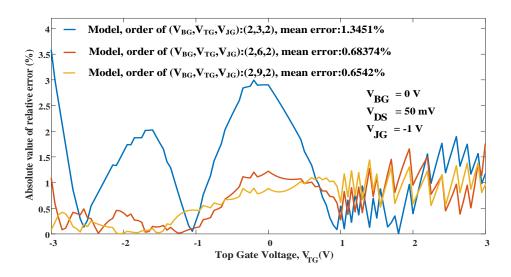

| Figure 4.40: Relative error between experimental data and regression model for different orders             |

| of $V_{TG}$ with the order of $V_{BG}$ and $V_{JG}$ fixed at 2                                              |

| Figure 4.41: Comparison of $I_{DS}$ - $V_{TG}$ between experimental data and regression model for different |

| orders of $V_{TG}$ with the order of $V_{JG}$ and $V_{BG}$ fixed at 2 and 4, respectively71                 |

| Figure 4.42: Relative error between experimental data and regression model for different orders             |

| of $V_{TG}$ with the order of $V_{JG}$ and $V_{BG}$ fixed at 2 and 4, respectively                          |

| Figure 4.43: Comparison between isolines of test data and regression model (order of $V_{BG}$ , $V_{TG}$ ,  |

| $V_{JG}$ respectively 3, 8 and 2) for different bottom-gate voltages ranging from -4 V to 4 V in 2          |

| V increment arranged from bottom to top                                                                     |

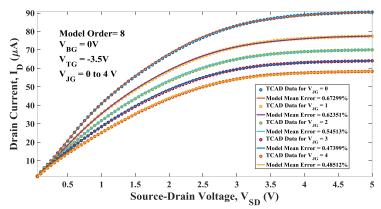

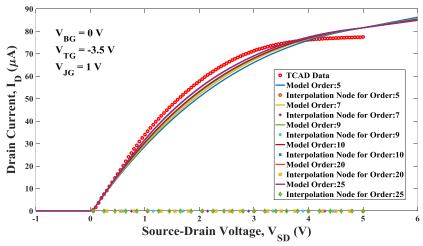

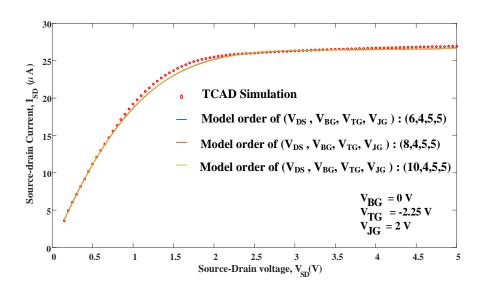

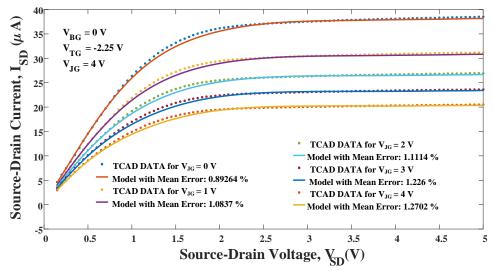

| Figure 4.44: Comparison of $I_{SD}$ - $V_{SD}$ between TCAD data and regression model for different orders  |

| of $V_{SD}$ with order of $V_{TG}$ fixed at 4 for a $p$ -channel $G^4FET$                                   |

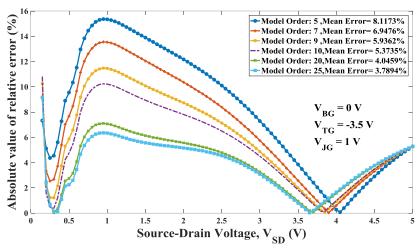

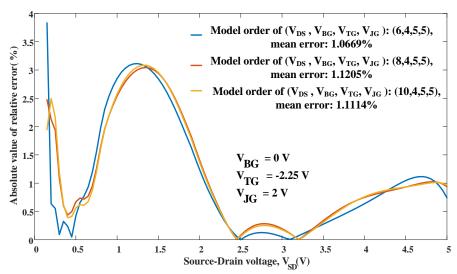

| Figure 4.45: Relative error between TCAD data and regression model for different orders of $V_{SD}$         |

| with order of $V_{TG}$ fixed at 4 for a $p$ -channel G <sup>4</sup> FET74                                   |

| Figure 4.46: Comparison of $I_{SD}$ - $V_{DS}$ between TCAD data and regression model for different orders  |

| of $V_{SD}$ with order of $V_{TG}$ fixed at 5 for a $p$ -channel $G^4FET$                                   |

| Figure 4.47: Relative error between TCAD data and regression model for different orders of $V_{SD}$         |

| with order of $V_{TG}$ fixed at 5 for a $p$ -channel G <sup>4</sup> FET75                                   |

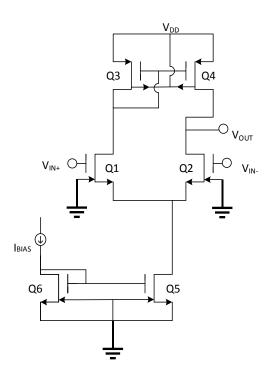

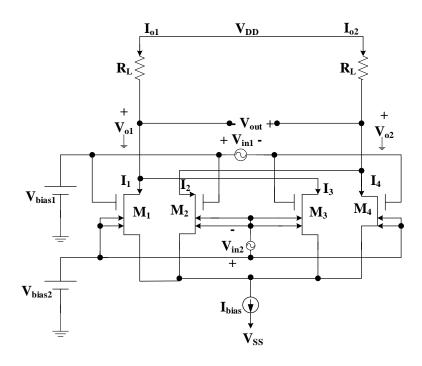

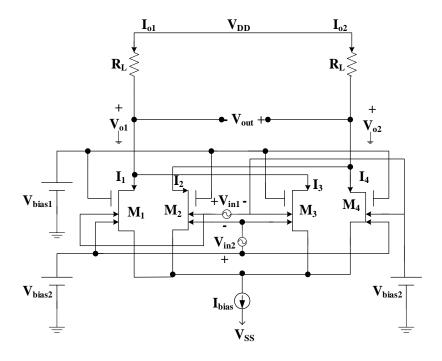

| Figure 4.60: Schematic of high voltage $G^4FET$ differential amplifier (Q 1,2: 0.3 $\mu$ m ×10/2.4 $\mu$ m,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $V_{JG} = 0 \text{ V}, V_{BG} = 0 \text{ V}; \text{ Q } 3,4: 0.35  \mu\text{m} \times 2/10  \mu\text{m}, V_{JG} = 0 \text{ V}, V_{BG} = 0 \text{ V}; \text{ Q } 5,6: 0.3  \mu\text{m} \times 10/2.4  0.35  \mu\text{m} \times 10/2.4$ |

| $\mu$ m, $V_{JG} = V_{DD}$ , $V_{BG} = 0$ V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

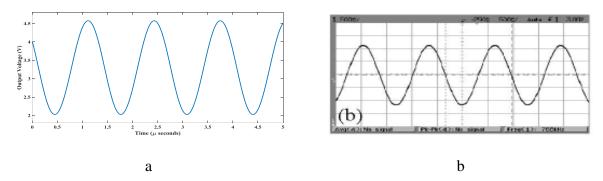

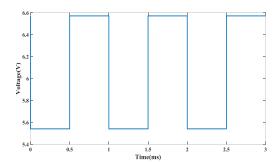

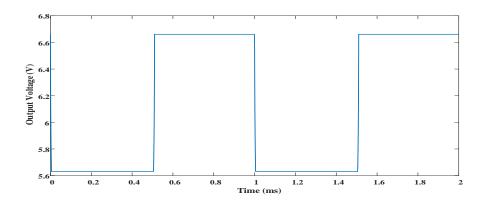

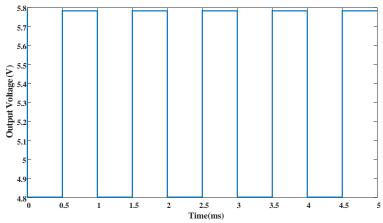

| Figure 4.61: Output of G <sup>4</sup> FET Differential amplifier (0.97 V <sub>p-p</sub> compared to experimental value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| of 1 $V_{p-p}$ ) in non-inverting unity gain configuration ( $V_{DD} = 10 \text{ V}$ , $V_{in} = 1 \text{ V}_{p-p}$ square wave                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| with 6 V offset)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Figure 4.62: Comparison between isolines of test data and linear spline model (Device 1) for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| different junction-gate voltages ranging from -4 V to 0 V in 1 V increment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Figure 4.63: Comparison between isolines of test data and cubic spline model (Device 1) for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| different junction-gate voltages ranging from -4 V to 0 V in 1 V increment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Figure 4.64: Comparison between isolines of test data and linear spline model (Device 2) and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| relative error for varying bottom-gate voltages from -4V to 4V in 2V increment arranged from                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| bottom to top                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Figure 4.65: Comparison between isolines of test data and cubic spline model (Device 2) and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| relative error for varying bottom-gate voltages from -4 V to 4 V in 2 V increment arranged                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| from bottom to top                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

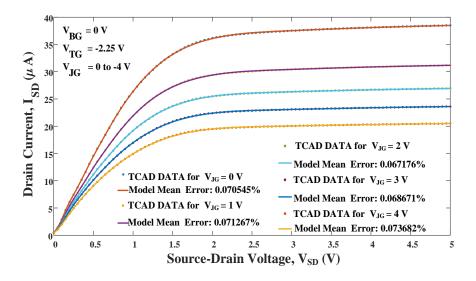

| Figure 4.66: Comparison of $I_{SD}$ - $V_{SD}$ between TCAD test data and linear spline model (Device 3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| for different junction-gate voltages ranging from 0 V to 4 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Figure 4.67: Comparison of $I_{SD}$ - $V_{SD}$ between TCAD test data and cubic spline model (Device 3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| for different junction-gate voltages ranging from 0 V to 4 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

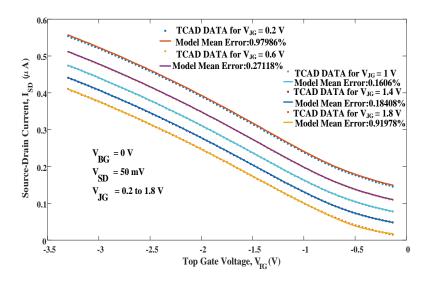

| Figure 4.68: Comparison between test data and linear spline model isolines (Device 4) for variation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

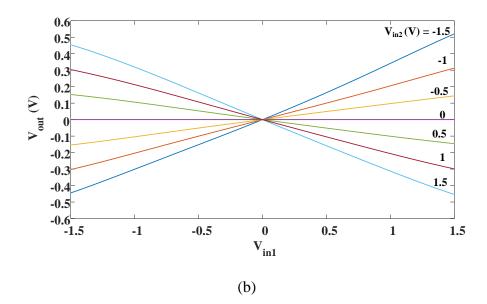

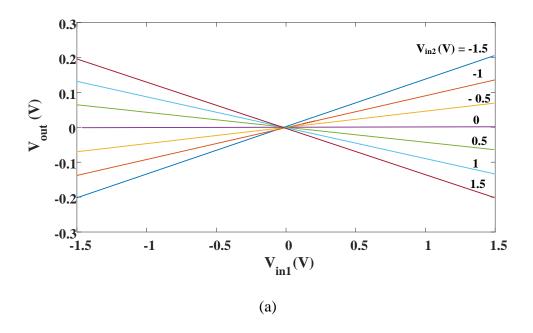

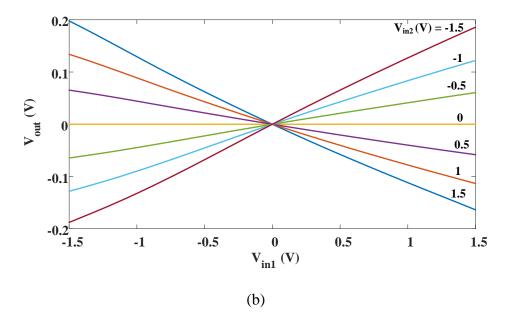

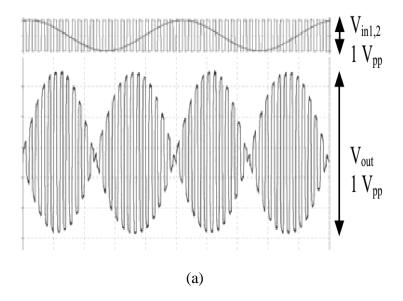

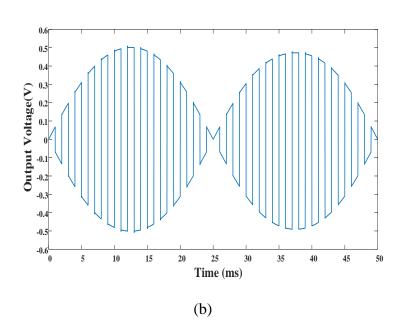

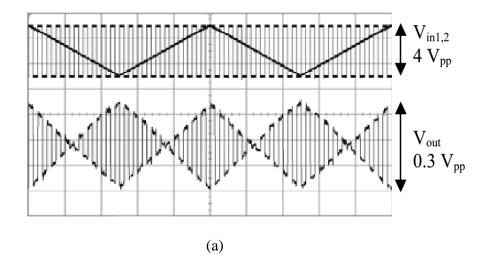

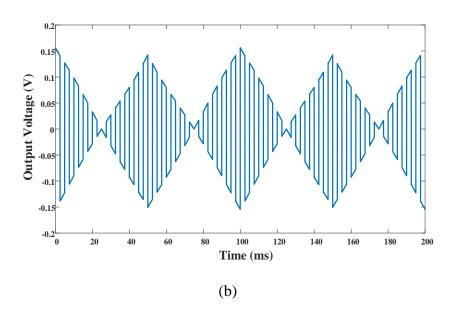

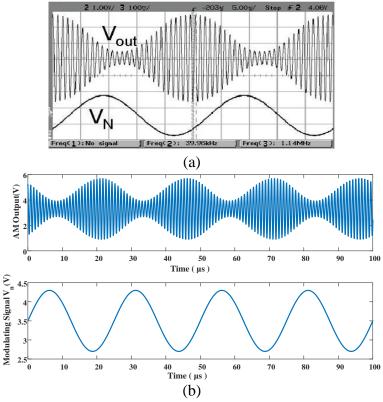

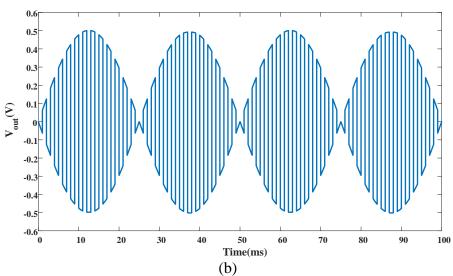

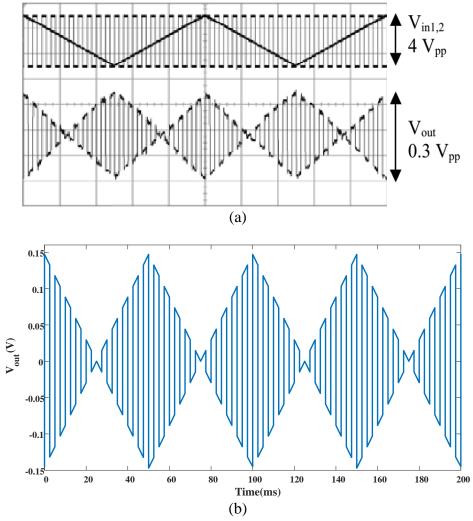

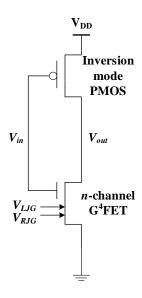

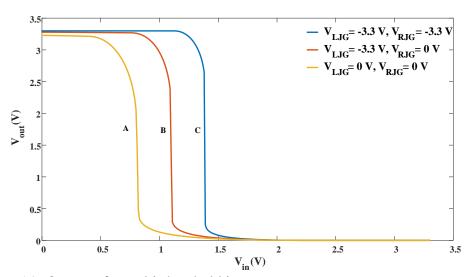

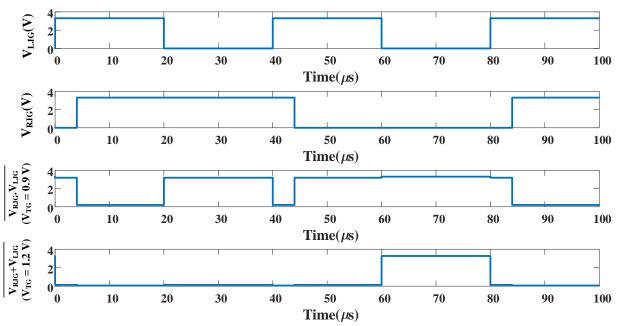

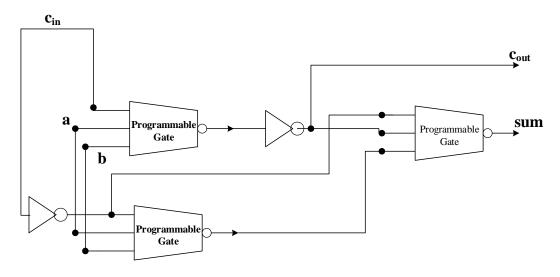

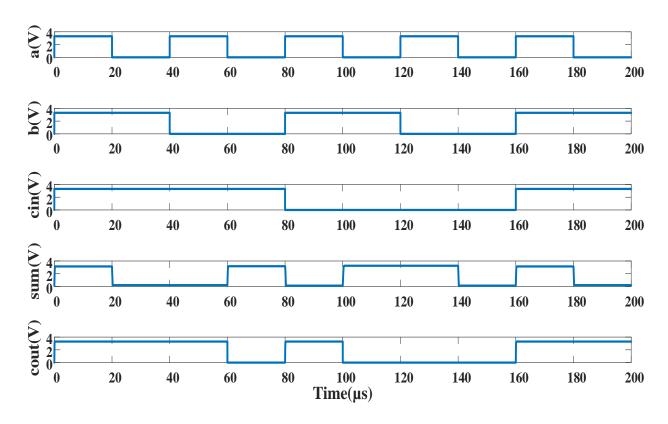

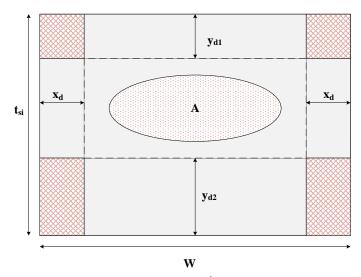

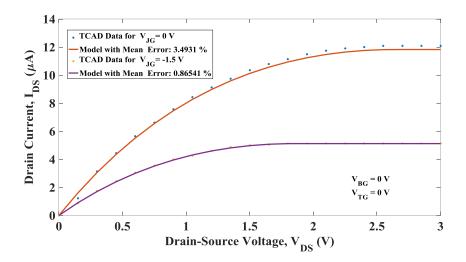

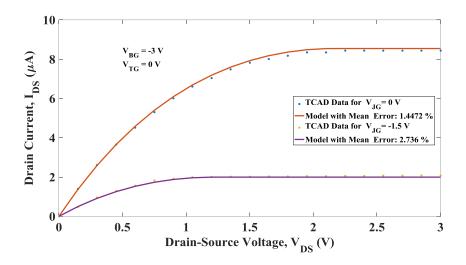

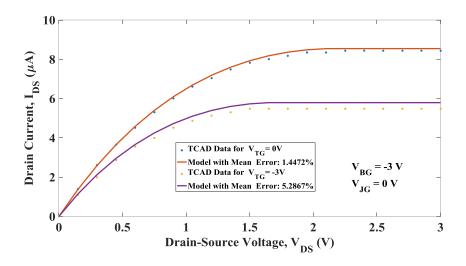

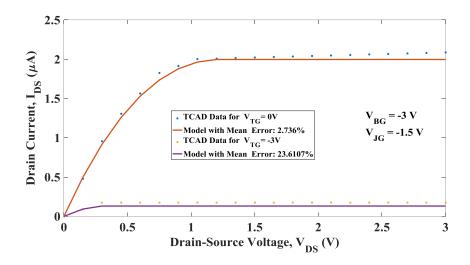

| in junction-gate voltages from 0.2 V to 1.8 V in 0.4 V increment arranged from top to bottom.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |