### University of Tennessee, Knoxville TRACE: Tennessee Research and Creative Exchange

**Doctoral Dissertations**

**Graduate School**

5-2017

### Programming Models' Support for Heterogeneous Architecture

Wei Wu University of Tennessee, Knoxville, wwu12@vols.utk.edu

Follow this and additional works at: https://trace.tennessee.edu/utk\_graddiss

Part of the Numerical Analysis and Scientific Computing Commons, Programming Languages and Compilers Commons, Software Engineering Commons, and the Systems Architecture Commons

#### **Recommended Citation**

Wu, Wei, "Programming Models' Support for Heterogeneous Architecture. " PhD diss., University of Tennessee, 2017. https://trace.tennessee.edu/utk\_graddiss/4510

This Dissertation is brought to you for free and open access by the Graduate School at TRACE: Tennessee Research and Creative Exchange. It has been accepted for inclusion in Doctoral Dissertations by an authorized administrator of TRACE: Tennessee Research and Creative Exchange. For more information, please contact trace@utk.edu.

To the Graduate Council:

I am submitting herewith a dissertation written by Wei Wu entitled "Programming Models' Support for Heterogeneous Architecture." I have examined the final electronic copy of this dissertation for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Doctor of Philosophy, with a major in Computer Science.

Jack Dongarra, Major Professor

We have read this dissertation and recommend its acceptance:

James Plank, Michael Berry, Yingkui Li

Accepted for the Council:

Dixie L. Thompson

Vice Provost and Dean of the Graduate School

(Original signatures are on file with official student records.)

# Programming Models' Support for Heterogeneous Architecture

A Dissertation Presented for the

Doctor of Philosophy

Degree

The University of Tennessee, Knoxville

Wei Wu

May 2017

© by Wei Wu, 2017 All Rights Reserved. To my wife and parents for their wholehearted love

### Acknowledgments

For the past six years spent at the University of Tennessee and Innovative Computing Laboratory (ICL), not a single day I did not appreciate how the school, my advisors and my fellow colleagues treated me. They have guided, inspired, and embraced me in so many ways that as a foreigner, I felt like home. For that, I am forever grateful and I will miss them deeply.

The University of Tennessee has a beautiful campus. It has a welcoming, passionate, and diverse environment that gave me not only a phenomenal academic life but also a productive after-school life. People on campus are so nice and easy. I greatly enjoyed my time here on campus and in Knoxville.

Dr. Jack Dongarra, a highly respected and reputable scientist, remain down to earth and approchable. He cares about every student and every staff member. It was a great privilege to join the ICL, to work with and have him as my advisor. His wisdom, his knowledge and his experiences will always be my guide and my example in my future work and life. I couldn't help but feel lucky to be a member of ICL everyday.

My project leader, Dr. George Bosilca, was an outstanding teacher. He didn't only care about the work I do at ICL, but he also cared about things such as what the grades I got on the classes I was taking. When it comes to my internships, he reviewed each position carefully and gave recommendations based on which position would further help me with my academic career. I feel so lucky to be his student. Dr. Bosilca taught me everything I know. He made me confident and competent to face all kinds of challenges forthcoming in my career.

I am grateful to my committee, Dr. James Plank, Dr. Michael Berry and Dr. Yingkui Li for agreeing to serve on my dissertation committee. I greatly appreciate their time and invaluable guidance on this dissertation.

I would also like to thank my wife. She is loving and caring. She supported me all the way and never complained about the long journey to get my PHD. She encourages me when I have difficulties and she was always by my side. She is my rock and I love her deeply.

To my parents, I would like to thank them for letting me leave home and came to the United States almost 10 years ago in the pursuit of my dreams. They always support and respect my decisions.

Last but not the least, I would like to thank my colleagues. Xi Luo, Chongxiao Cao, Anthony Danalis, Mathieu Faverge and Thananon Patinyasakdikul (Arm), to name a few. I enjoyed working with them very much. I wish them all the best.

Stay Hungry, Stay Foolish. - Steve Jobs

### Abstract

Accelerator-enhanced computing platforms have drawn a lot of attention due to their massive peak computational capacity. Heterogeneous systems equipped with accelerators such as GPUs have become the most prominent components of High Performance Computing (HPC) systems. Even at the node level the significant heterogeneity of CPU and GPU, i.e. hardware and memory space differences, leads to challenges for fully exploiting such complex architectures. Extending outside the node scope, only escalate such challenges.

Conventional programming models such as data-flow and message passing have been widely adopted in HPC communities. When moving towards heterogeneous systems, the lack of GPU integration causes such programming models to struggle in handling the heterogeneity of different computing units, leading to sub-optimal performance and drastic decrease in developer productivity. To bridge the gap between underlying heterogeneous architectures and current programming paradigms, we propose to extend such programming paradigms with architecture awareness optimization.

Two programming models are used to demonstrate the impact of heterogeneous architecture awareness. The PaRSEC task-based runtime, an adopter of the data-flow model, provides opportunities for overlapping communications with computations and minimizing data movements, as well as dynamically adapting the work granularity to the capability of the hardware. To fulfill the demand of an efficient and portable Message Passing Interface (MPI) implementation to communicate GPU data, a GPU-aware design is presented based on the Open MPI infrastructure supporting efficient point-to-point and collective communications of GPU-residential data, for both contiguous and non-contiguous memory layouts, by leveraging GPU network topology and hardware capabilities such as GPUDirect. The tight integration of GPU support in a widely used programming environment, free the developers from manually move data into/out of host memory before/after relying on MPI routines for communications, allowing them to focus instead on algorithmic optimizations.

Experimental results have confirmed that supported by such a tight and transparent integration, conventional programming models can once again take advantage of the state-of-the-art hardware and exhibit performance at the levels expected by the underlying hardware capabilities.

## **Table of Contents**

| 1 | Intr | troduction                    |                                                      |    |

|---|------|-------------------------------|------------------------------------------------------|----|

|   | 1.1  | Motivations and Contributions |                                                      |    |

|   |      | 1.1.1                         | Data-flow Programming Model                          | 4  |

|   |      | 1.1.2                         | Message Passing Programming Model                    | 6  |

|   | 1.2  | Disser                        | tation Outline                                       | 10 |

| 2 | Bac  | kgrou                         | nd and Literature Review of Related Works            | 11 |

|   | 2.1  | Data-                         | flow Programming Model                               | 11 |

|   |      | 2.1.1                         | DAG-Based Representation                             | 11 |

|   |      | 2.1.2                         | Parallel Runtime Scheduling and Execution Controller | 12 |

|   |      | 2.1.3                         | Tiled Dense Linear Algebra                           | 12 |

|   |      | 2.1.4                         | Literature Review                                    | 15 |

|   | 2.2  | GPU-                          | aware MPI                                            | 17 |

|   |      | 2.2.1                         | MPI Derived Datatype                                 | 17 |

|   |      | 2.2.2                         | MPI Point-to-point Communications                    | 19 |

|   |      | 2.2.3                         | MPI Collective Communications                        | 21 |

|   |      | 2.2.4                         | Literature Review                                    | 22 |

| 3 | PaF  | RSEC's                        | s Support for Heterogeneous System                   | 27 |

|   | 3.1  | Issues                        | of PaRSEC in Heterogeneous System                    | 27 |

|   |      | 3.1.1                         | Data Granularity of CPU/GPU Tasks                    | 28 |

|   |      | 3.1.2                         | Different Memory Spaces                              | 30 |

|   | 3.2 | Hierar | rchical DAG                                                | 31 |

|---|-----|--------|------------------------------------------------------------|----|

|   |     | 3.2.1  | Methodology                                                | 32 |

|   |     | 3.2.2  | Case Study: Cholesky Factorization                         | 33 |

|   |     | 3.2.3  | Hybrid Data Layout                                         | 36 |

|   |     | 3.2.4  | Hierarchical DAG Task Scheduler in PaRSEC                  | 37 |

|   | 3.3 | Emplo  | bying Multiple CUDA Streams                                | 38 |

|   | 3.4 | Data   | Coherence between CPU and GPUs                             | 39 |

|   | 3.5 | Out o  | f Core Execution                                           | 41 |

|   | 3.6 | CPU/   | GPU Load Balance                                           | 42 |

|   | 3.7 | Perfor | mance Evaluation                                           | 43 |

|   |     | 3.7.1  | Overhead from Runtime Task Subdivision                     | 44 |

|   |     | 3.7.2  | Number of CUDA Stream Tuning                               | 45 |

|   |     | 3.7.3  | Tile Size Tuning                                           | 47 |

|   |     | 3.7.4  | Shared Memory                                              | 49 |

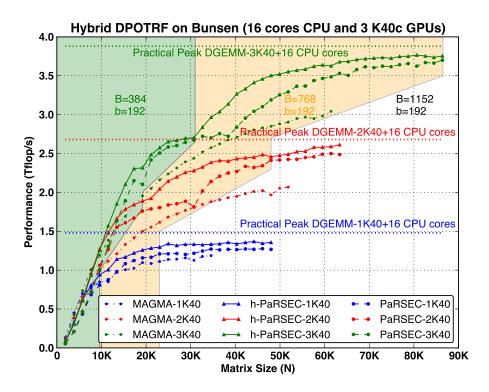

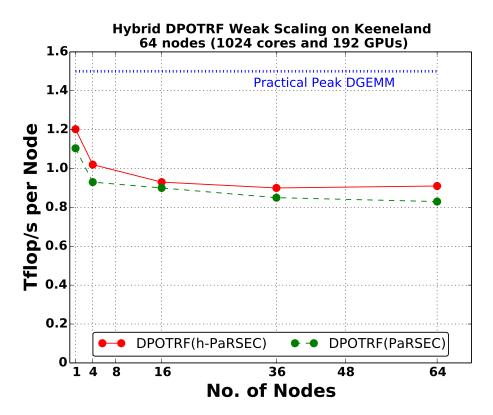

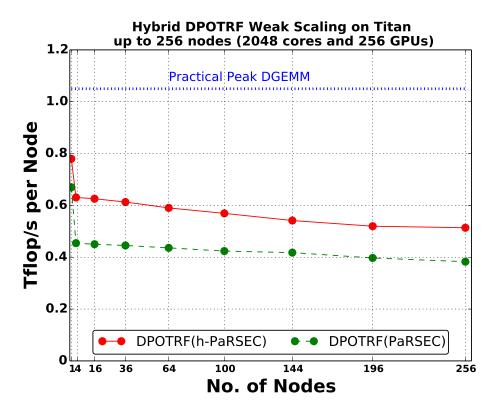

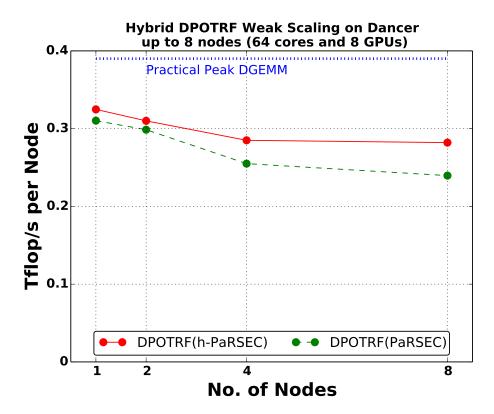

|   |     | 3.7.5  | Distributed Memory                                         | 51 |

|   | 3.8 | Summ   | nary                                                       | 54 |

| 4 | GP  | U-awa  | re Point-to-point Communication                            | 56 |

|   | 4.1 | Issues | of Point-to-point Communication of non-contiguous GPU Data |    |

|   |     | in Op  | en MPI                                                     | 56 |

|   | 4.2 | Design | n of GPU Datatype Engine                                   | 60 |

|   |     | 4.2.1  | Vector Type                                                | 60 |

|   |     | 4.2.2  | Less Regular Memory Patterns                               | 61 |

|   | 4.3 | Integr | ation of GPU Datatype Engine into Open MPI                 | 64 |

|   |     | 4.3.1  | RDMA Protocol                                              | 65 |

|   |     | 4.3.2  | Copy In/Out Protocol                                       | 68 |

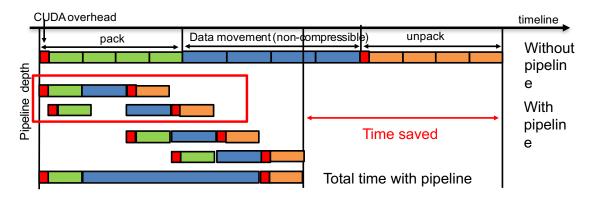

|   |     | 4.3.3  | Analysis of Pipelining of Pack/unpack with Data Movement . | 70 |

|   | 4.4 | Perfor | mance Evaluation                                           | 71 |

|   |     | 4.4.1  | Performance Evaluation for Datatype Engine                 | 72 |

|    |                 | 4.4.2                                                                | Full Evaluation: GPU-GPU Communication with MPI $\ . \ . \ .$ | 77  |  |

|----|-----------------|----------------------------------------------------------------------|---------------------------------------------------------------|-----|--|

|    |                 | 4.4.3                                                                | GPU Resources of Packing/Unpacking Kernels                    | 83  |  |

|    |                 | 4.4.4                                                                | Pipeline and Resource Contention Effects                      | 85  |  |

|    | 4.5             | Summ                                                                 | ary                                                           | 87  |  |

| 5  | GP              | U-awa                                                                | re Collective Communication                                   | 88  |  |

|    | 5.1             | Issues of Traditional Collective Communication Algorithms in Hetero- |                                                               |     |  |

|    |                 | geneo                                                                | us System                                                     | 88  |  |

|    |                 | 5.1.1                                                                | Multiple Networks                                             | 89  |  |

|    |                 | 5.1.2                                                                | Process Mapping                                               | 90  |  |

|    | 5.2             | Design                                                               | n of Topology-aware Collective Communication                  | 92  |  |

|    |                 | 5.2.1                                                                | Topology-aware Tree                                           | 92  |  |

|    |                 | 5.2.2                                                                | Algorithm Selection of Sub-trees                              | 94  |  |

|    |                 | 5.2.3                                                                | Collective Communication with Topology-aware Tree             | 96  |  |

|    |                 | 5.2.4                                                                | Minimize Communications Over PCI-Express                      | 97  |  |

|    |                 | 5.2.5                                                                | PCI-Express Switch Level Process Reorder                      | 100 |  |

|    |                 | 5.2.6                                                                | Offload Reduction Operation on GPU                            | 100 |  |

|    | 5.3             | Perfor                                                               | mance Evaluation                                              | 101 |  |

|    |                 | 5.3.1                                                                | Performance Scalability                                       | 102 |  |

|    |                 | 5.3.2                                                                | Strong Scalability                                            | 102 |  |

|    |                 | 5.3.3                                                                | Process Mapping                                               | 105 |  |

|    | 5.4             | Summ                                                                 | ary                                                           | 108 |  |

| 6  | Cor             | nclusio                                                              | ns and Future Directions                                      | 109 |  |

|    | 6.1             | Concl                                                                | usions                                                        | 109 |  |

|    | 6.2             | Future                                                               | e Directions                                                  | 111 |  |

| Bi | Bibliography 11 |                                                                      |                                                               |     |  |

| Vi | Vita 12         |                                                                      |                                                               |     |  |

## List of Tables

| 3.1 | Status transition of data copies of tile $A$ and $C$ after each task.(Only |    |

|-----|----------------------------------------------------------------------------|----|

|     | tiles $A$ and $C$ are presented as they are shared accessed by tasks) $$   | 40 |

5.1 Latency of different broadcast algorithms with Hockney model . . . . 95

## List of Figures

| The Framework of PaRSEC                                                         | 13                                              |

|---------------------------------------------------------------------------------|-------------------------------------------------|

| Cholesky factorization on matrix of $4 \times 4$ tiles                          | 13                                              |

| DAG representation of Cholesky factorization on matrix of $4\times 4$ tiles     | 14                                              |

| Performance of compute kernels on CPU and GPU depending on                      |                                                 |

| problem granularity                                                             | 29                                              |

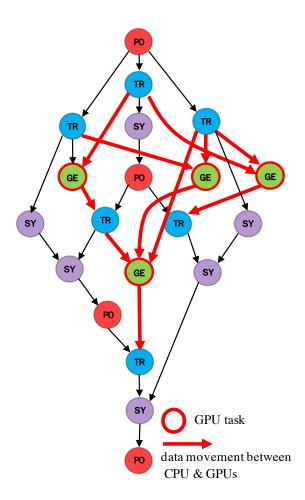

| DAG representation of Cholesky factorization on matrix of $4\times 4$ tiles     | 34                                              |

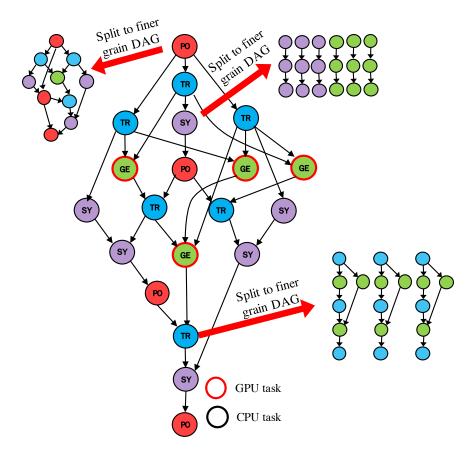

| DAG of "hierarchical DAG" Cholesky factorization, whose size is $4\times 4$     |                                                 |

| large tiles and then each CPU task is split into $3\times 3$ small tiles        | 35                                              |

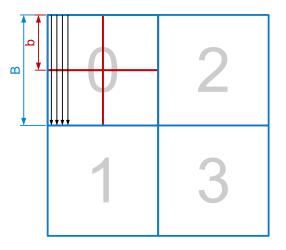

| Different data layout: tile and LAPACK. For sub-tiles in the fine grain         |                                                 |

| DAG (red), the data layout is the same as the LAPACK layout with                |                                                 |

| interleaved data, while tile layout (blue) is used for large tiles and          |                                                 |

| permits a much more efficient data transfer to/from the accelerators.           | 37                                              |

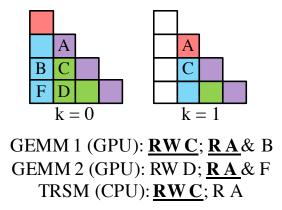

| Step 0 and step 1 of cholesky factorization of $4 \times 4$ tiles. RW refers to |                                                 |

| Read and Write of data; R refers to Read data                                   | 40                                              |

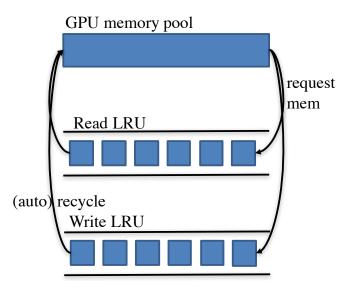

| GPU memory management strategy in PaRSEC                                        | 42                                              |

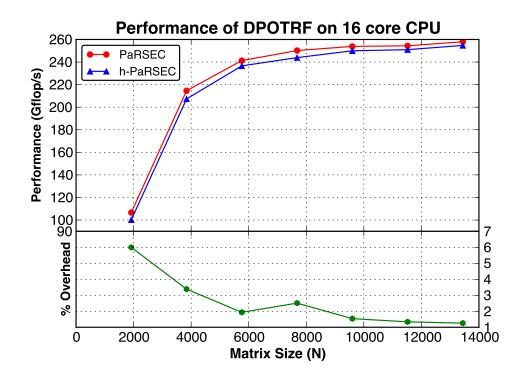

| Overhead incurred from the hierarchical DAG subdivision management              |                                                 |

| (DPOTRF, CPU only). The h-PaRSEC version uses an big tiling of                  |                                                 |

| B=900, all tasks are subdivided into small tiles of size b=180 (same as         |                                                 |

| standard PaRSEC)                                                                | 45                                              |

|                                                                                 | Cholesky factorization on matrix of 4 × 4 tiles |

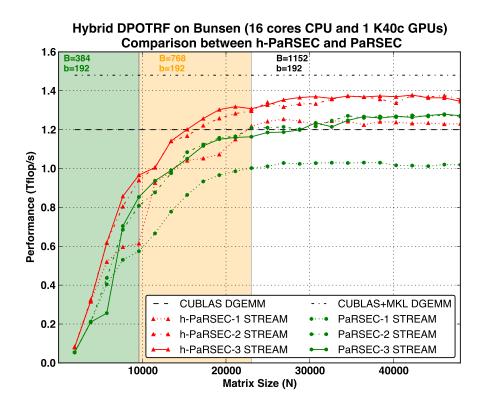

| 3.8  | Performance difference between hierarchical DAG and the standard                          |    |

|------|-------------------------------------------------------------------------------------------|----|

|      | version on DPOTRF with a varying number of CUDA streams (Bunsen                           |    |

|      | using 1 K40 GPU)                                                                          | 46 |

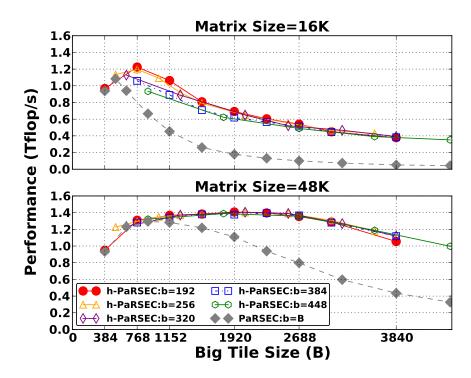

| 3.9  | Performance for different tile size parameters (DPOTRF, using 1 GPU                       |    |

|      | on Bunsen).                                                                               | 48 |

| 3.10 | Performance of h-PaRSEC DPOTRF with regular PaRSEC and                                    |    |

|      | MAGMA.                                                                                    | 50 |

| 3.11 | Weak Scalability: DPOTRF performance as a function of the number                          |    |

|      | of nodes, with a problem size scaled accordingly (KFS, $3\;\mathrm{M2090}\;\mathrm{GPUs}$ |    |

|      | and 16 cores per node)                                                                    | 52 |

| 3.12 | Weak Scalability: DPOTRF performance as a function of the number                          |    |

|      | of nodes, with a problem size scaled accordingly (Titan, 1 K20 GPU $$                     |    |

|      | and 8 cores per node)                                                                     | 53 |

| 3.13 | Weak Scalability: DPOTRF performance as a function of the number                          |    |

|      | of nodes, with a problem size scaled accordingly (Dancer, $1\ \mathrm{C2050\ GPU}$        |    |

|      | and 8 cores per node)                                                                     | 54 |

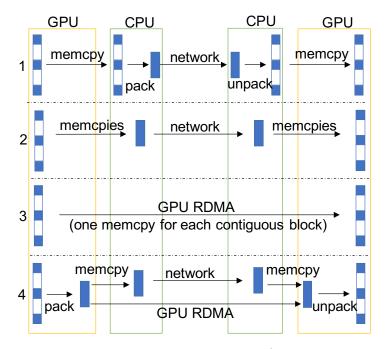

| 4.1  | Four possible solutions for sending/receiving non-contiguous data                         |    |

|      | residing in GPU memory                                                                    | 58 |

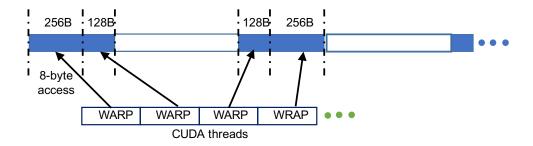

| 4.2  | Access pattern of GPU pack/unpack kernels of <i>vector</i> type. The size                 |    |

|      | of a CUDA block is a multiple of the warp size                                            | 61 |

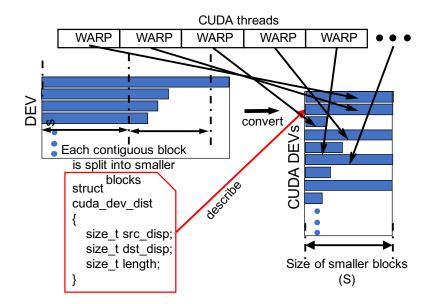

| 4.3  | Access pattern of GPU pack/unpack kernels using the DEV method-                           |    |

|      | ology. The left <i>struct</i> describes a work unit for a CUDA WARP                       | 63 |

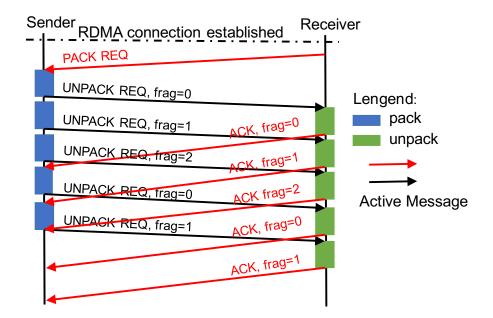

| 4.4  | Pipelined RDMA protocol for send/receive of non-contiguous GPU-                           |    |

|      | resident data.                                                                            | 65 |

| 4.5  | Communication time of using pipeline compared with communication                          |    |

|      | without pipeline.                                                                         | 69 |

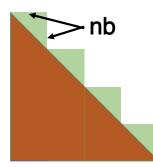

| 4.6  | Triangular matrix (red one) vs Stair triangular matrix (red and green                     |    |

|      | one), width and height of stair $nb$ is multiple of CUDA block size $\ . \ .$             | 72 |

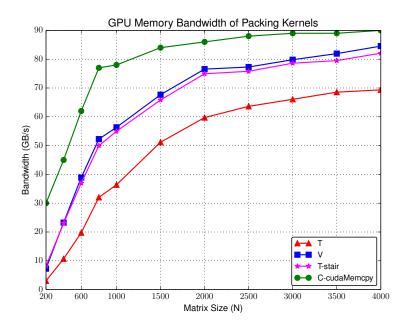

| 4.7  | GPU memory bandwidth of packing kernels for sub-matrix and lower       |    |

|------|------------------------------------------------------------------------|----|

|      | triangular matrix comparing with contiguous data of the same size.     |    |

|      | "T" represents triangular matrix, "V" represents sub-matrix, "C"       |    |

|      | represents contiguous matrix                                           | 74 |

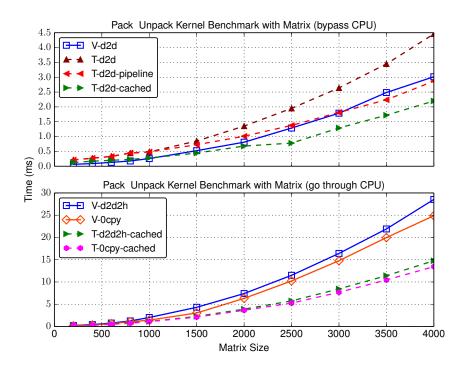

| 4.8  | Performance of pack and unpack sub-matrix and lower triangular         |    |

|      | matrix varies by matrix size                                           | 75 |

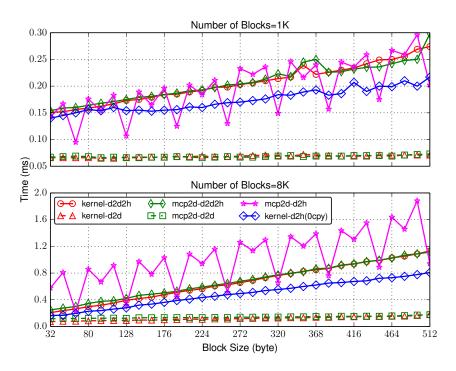

| 4.9  | vector pack/unpack performance vs cudaMemcpy2D. "kernel" repre-        |    |

|      | sents our pack/unpack kernels. "mcp2d" represents cudaMemcpy2D.        |    |

|      | "d2d" represents non-contiguous data packed into a GPU buffer.         |    |

|      | "d2d2h" represents "d2d" followed by a device-host data movement.      |    |

|      | "d2h" means non-contiguous GPU data moved directly into CPU buffer.    | 76 |

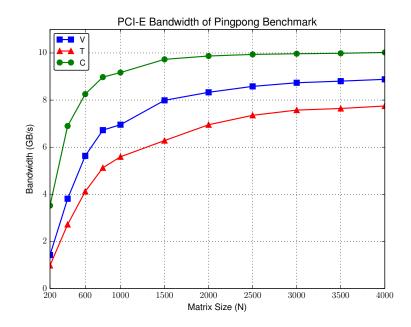

| 4.10 | PCI-Express bandwidth of vector and indexed data type comparing        |    |

|      | with contiguous data.                                                  | 78 |

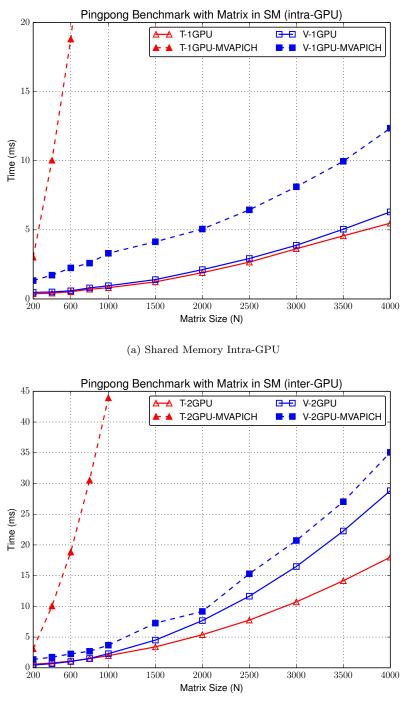

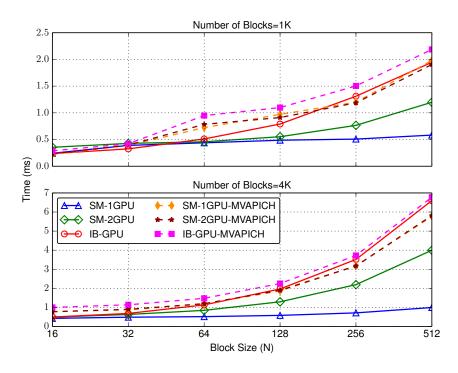

| 4.11 | Ping-pong benchmark with matrices on shared memory machine. "V"        |    |

|      | refers to sub-matrix, "T" refers to triangular matrix.                 | 79 |

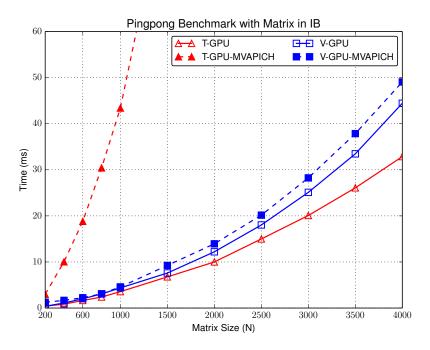

| 4.12 | Ping-pong benchmark with matrices on distributed memory machine.       |    |

|      | "V" refers to sub-matrix, "T" refers to triangular matrix              | 80 |

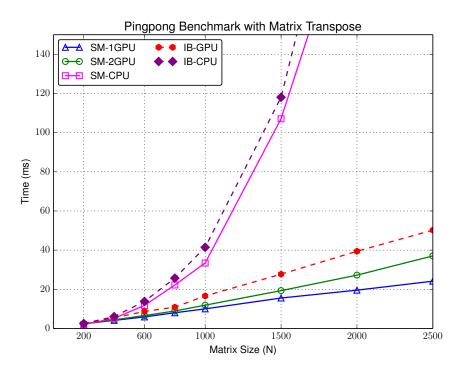

| 4.13 | Ping-pong benchmark with vector and contiguous data type               | 82 |

| 4.14 | Ping-pong benchmark for matrix transpose in both shared and dis-       |    |

|      | tributed memory environment                                            | 83 |

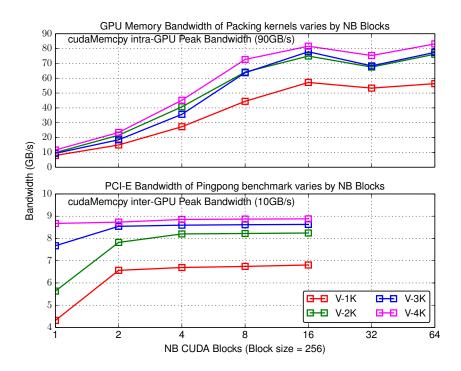

| 4.15 | GPU memory and PCI-Express bandwidth of pack/unpack sub-matrix         |    |

|      | "V" data types varies by number of blocks used for kernel launching.   |    |

|      | Matrix size varies from 1K to 4K                                       | 84 |

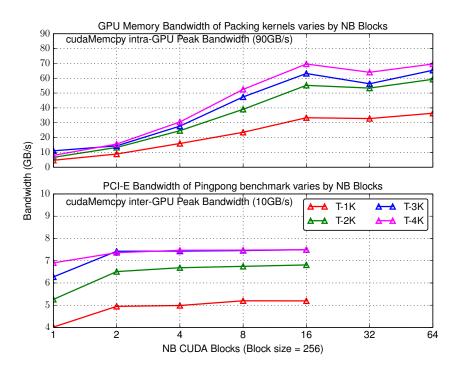

| 4.16 | GPU memory and PCI-Express bandwidth of pack/unpack triangular         |    |

|      | matrix "T" data types varies by number of blocks used for kernel       |    |

|      | launching. Matrix size varies from 1K to 4K                            | 85 |

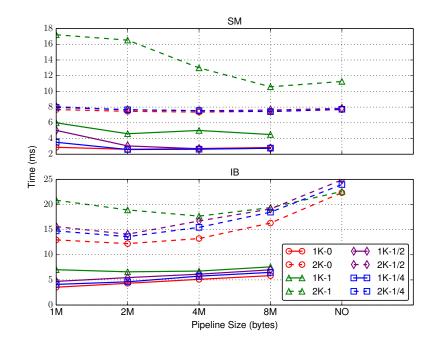

| 4.17 | Ping-pong benchmark with partial GPU resources available. In the       |    |

|      | legend, the number after the matrix size is the ratio of GPU resources |    |

|      | occupied                                                               | 86 |

|      |                                                                        |    |

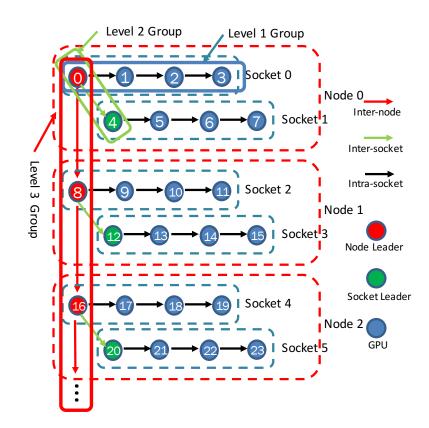

| 5.1 | Topology-aware tree of broadcast algorithm on multi-GPU cluster. (4  |     |

|-----|----------------------------------------------------------------------|-----|

|     | GPUs per socket and 2 sockets per node)                              | 93  |

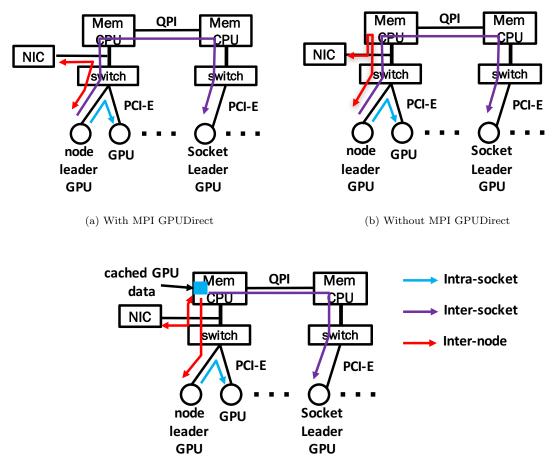

| 5.2 | Data flow of non-root node leader MPI process                        | 98  |

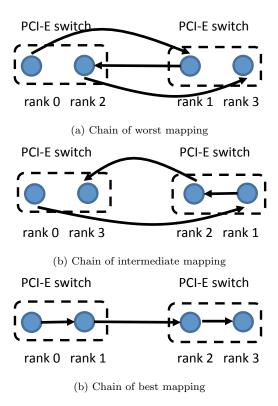

| 5.3 | Process mapping using hardware topology of PCI-Express switch        | 99  |

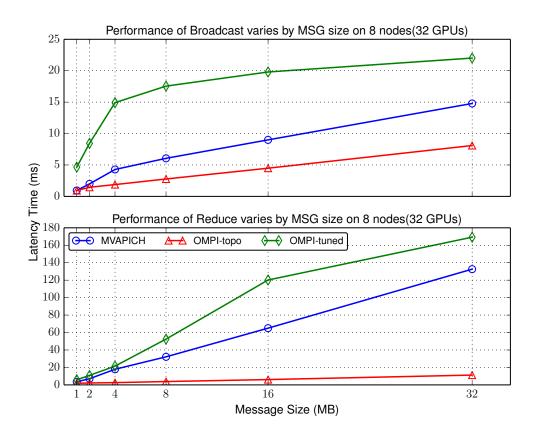

| 5.4 | Performance of broadcast and reduce with GPU data varies by message  |     |

|     | size using 8 nodes 32 GPUs                                           | 103 |

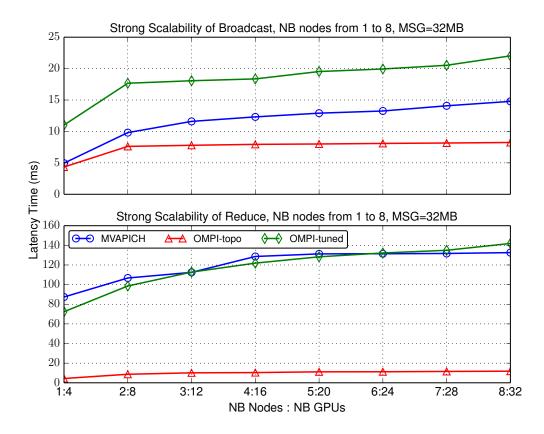

| 5.5 | Strong scalability of broadcast and reduce with GPU data varies by   |     |

|     | number of nodes, message size is 32 MB                               | 104 |

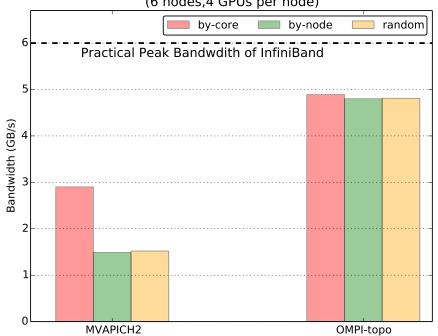

| 5.6 | Bandwidth of broadcast with GPU data varies by different process     |     |

|     | mapping with message size 32MB                                       | 106 |

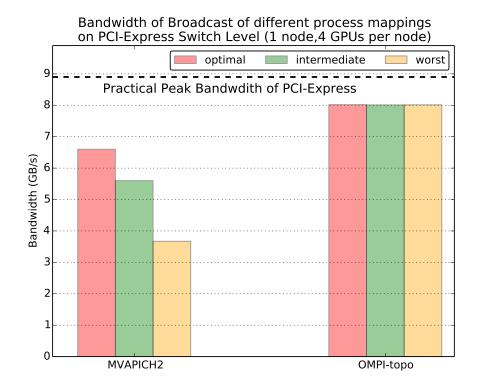

| 5.7 | Bandwidth of broadcast with GPU data on 1 nodes varies by different  |     |

|     | process mapping on the level of PCI-Express switch with message size |     |

|     | 32MB                                                                 | 107 |

### Chapter 1

### Introduction

#### **1.1** Motivations and Contributions

Throughput-oriented architectures, such as GPUs, are becoming ubiquitous assistants for computationally intensive tasks in scientific applications. Compared with traditional CPU, GPU has much higher peak performance and memory bandwidth. For example, the peak double precision floating point performance and memory bandwidth of the Nvidia Kepler K40 is approximately 1.43 Tflop/s and 288 GB/s, dwarfing the performance of any existing CPU family. As a consequence, an increasing number of production systems feature GPUs. In Top500 Top500 (2016) list, 20% of the top 500 machines and 40% of the top 10 machines are equipped with GPUs. Such trend is expected to persist in the future towards ex-scale machine: the coming machine, Oak Ridge National Laboratory's "Summit" and Lawrence Livermore National Laboratory's "Sierra", will both use GPUs as accelerators.

The hardware of CPU and GPU are significant different: GPU features thousands of light-weight cores while CPU features much less heavy-weight cores, and the cost of thread context switch of GPU is lower than CPU, but the latency of issuing instructions of GPU is relevantly higher than CPU, so the way of efficiently programming in GPU and CPU are different. Typically, GPU programs launch thousands of threads and switch contexts frequently to hide the latency of instructions. While CPU programs run on less threads and need minimal thread context switch. Therefore, GPU programming model extracts parallelism by operating on large granularity of data to achieve optimal occupancy of GPU. In contrast, CPU programming model is much more flexible with less restriction, hence less data granularity is able to feed a modern CPU. To fully exploit the resources of CPU and GPU, it is expected to select the proper execution unit for programs based on their degrees of available parallelism.

Machines equipped with accelerators, such as GPUs, are called heterogeneous systems, in which GPUs are connect to host machine as peripheral devices via PCI-Express. More recent advances, CPUs are connecting these GPUs with their own dedicated network, NVLink, allowing for a notable increase in the data movement capabilities, especially between accelerators. However, for a long time, GPUs have a separate memory space than the host. Explicit memory copy directives are necessary to move data between host and GPU, before being available to computations or communication on CPU/GPU. This memory separation has been fused with the introduction of the Unified Memory Architecture (UMA), allowing the host memory to be directly accessed from GPUs, and inversely, GPU memory to be directly accessed from CPUs. However, the connection between CPU and GPUs is bandwidth oriented not latency oriented, data parallel programs which involves frequently memory access of small independent data, is not able to fully utilize bandwidth. Therefore, it is always better to explicitly move data into GPU memory prior execution on GPU for such programs. Limited by CPU-GPU link bandwidth even with NVLink, such data transfers are expensive, hence, in order utilize both CPUs and GPUs efficiently, developers have to carefully overlap data movements between host and GPU with computations, as well as to minimize data movement and reuse data in GPU memory if available, in order to fully exploit the performance of both CPU and GPU.

Satisfying the increasing demand for computation from the scientific computing community, led to the trends of super large scale clusters. A typical large scale heterogeneous cluster usually is consisted of thousands of computer nodes. Computer node, the building block of super computers, usually contains multiple CPU sockets connected by high speed inter-socket connection (e.g. Intel QPI or AMD Hypertransport), and multiple GPUs. Scaling up, several computer nodes are coupled together through high performance network and form a computer blade, which are organized in racks and then finally large scale, super-computers. All these advances at the hardware level, cause a drastic increase in the hierarchization of different components, with wild differences between the different levels of the hierarchy. Communication cost between GPUs are dramatically different depending on location of GPUs: intra-socket communication is able to use CUDA Inter-process communication (CUDA IPC) NVIDIA (2016b) to achieve RDMA between two GPUs; inter-socket communication has to fall back to stage through CPU memory; internode communication can either use GPUDirect RDMA NVIDIA (2015) or go through intermediate CPU memory, Hence, maintaining good network performance requires efficiently utilization of all different networks and taking care of GPU locality as well as network topology.

Programming models such as data-flow and message-passing have been proved efficient for conventional distributed homogeneous systems. When moving towards distributed heterogeneous systems, the straight forward approach to port such programming models is to explicitly move data from GPU to host memory prior engaging CPU-based conventional programming model and move data back to GPU memory afterwards. However, such directly porting can not efficiently utilize resources of both CPU and GPU due to the lacking of architecture awareness optimization. Therefore, modifications of traditional programming models must take account of the characteristic of heterogeneous systems (significant hardware differences between CPU and GPU, different memory space of CPU and GPU, and complicated network topology of entire system). In the dissertation, we focus on two widely used programming models: data-flow programming model and messagepassing model.

#### 1.1.1 Data-flow Programming Model

Data-flow programming model has seen a revival, with the emergence of numerous task-based programming frameworks, where an algorithm is divided into computations entities (tasks) connected by data dependencies, and forms a Direct Acyclic Graph (DAG) (nodes and edges represent tasks and data dependencies of tasks respectively). This programming paradigm has been successfully used in different projects to depart from tightly coupled or fork-join programming paradigms, and express the parallelism in a form that allows for more execution flexibility and portability across many types of hardware resources. One of the early adopters of this programming paradigm is the PaRSEC Bosilca et al. (2012) framework, which encompasses a toolbox to help express algorithms in the data-flow programming paradigm, and a task runtime component whose role is to efficiently schedule the resultant DAG, on large scale distributed heterogeneous systems.

Tiled linear algebra algorithm is one of the beneficiaries of data-flow programming model Agullo et al. (2009). With tiled linear algebra, a matrix is divided into square tiles and each task operates on tiles. In heterogeneous systems, execution union of tasks can be either a CPU core or GPU. Lack of GPU knowledge, when deploying tasks, there are two common issues in traditional task-based runtime that could slow down performance. First, the size of tiles is one of the critical tuning parameters that impacts the efficiency of kernels, the degree of parallelism and the communication volume. As discussed before, due to different architectures of CPU and GPU, optimal data granularities (represented as tile size in the context of linear algebra) of GPU and CPU tasks are different: usually GPUs require large data set while CPUs benefit from smaller ones. Traditional tiled linear algebra algorithms Bosilca et al. (2011), which require all tasks to have a unique tile size to reach reasonable performance, but fail to provide the runtime with the means to achieve an adapted load-distribution on heterogeneous systems. Second, data dependencies indicate data transfers between tasks if they are executed in different execution units. As CPU and GPU have different memory space, most linear algebra GPU kernels are not able to beneficial from UMA because of their memory access pattern, therefore, it requires developers to explicitly move data into/out of GPU memory prior/after GPU tasks. Limited by the PCI-Express bandwidth, such data movement is expensive, hence serialization of the data movement and GPU kennels is not able to deliver optimal performance. Therefore, it is desired to overlap communication with computation. Application developers without rich experience in GPU programming are unlikely to efficiently handle such overlapping, which calls for task runtime to automatically infer data transfers between CPU and GPU, and provide better overlapping of communications with computations to fully exploit the resources of both CPU and GPU.

In this dissertation, we integrate the GPU knowledge including architecture and memory space into task runtime and achieve the following contributions:

- We propose a method called "hierarchical DAG" to adapt the granularity of tasks with a multi-level approach, where tiles of different sizes coexist in the runtime. In the hierarchical DAG approach, tasks operated on large granularity data (large tile size) are organized in an outer DAG level, which are executed on GPUs. When executed on CPU, each large granularity task can be dynamically subdivided into a finer granularity inner DAG, operating on smaller tiles, so that the larger number of finer granularity tasks increases the available parallelism to levels adequate for multi-core processors.

- We design a data coherence protocol to track the data copies in CPU and GPU memory With the help of coherence protocol, data is cached in GPU memory to reduce data movement. Later, data movement and GPU kernel execution are overlapped with each other by offloading them to different CUDA streams.

- We develop a multi-level GPU memory management, which reuses GPU memory based on Least Recent Used (LRU) strategy when running out of memory, and therefore, it support out of core execution (problem size larger than GPU memory size).

• We showcase a popular linear algebra algorithms - Cholesky factorization to motivate the need for "hierarchical DAG" design to adjust task granularity and integration the knowledge of separated memory space of CPU and GPU into task runtime to overlap communication with computation and minimize data movement.

#### 1.1.2 Message Passing Programming Model

In data-flow model, data flows from one task to another. There are several ways to implement the underlying data movement. One of the popular approach is to use message passing. Message passing model is another traditional programming paradigm used in distributed system. Processes communicate with each other by messages without resorting to shared variables. Message Passing Interface (MPI) is a standard, which defines a set of communication pattern with message passing. Since the MPI standard MPI Forum (1995) does not define interactions with GPUbased data, it is expected that application developers have to explicitly initiate data movements between host and device memory prior to use MPI to move data across node boundaries. Such approach imposes a significant complexity on programmers, renders explicit management of hierarchies which defeats performance portability. In heterogeneous system, it is expected MPI implementations to provide GPU-aware capability by unifying MPI routines for both CPU and GPU data, and freeing programmers from explicit CPU-GPU data movements. However, the current MPI implementations obviously can not satisfy the requirement of high efficiency and portability in communication of GPU-resident data. In this dissertation, we adapt Open MPI, one of the state-of-the-art MPI implementations, to heterogeneous system to provide efficient point-to-point and collective communication of GPU data.

#### Point-to-point Communication

Since point-to-point is the basic building block routines of MPI, the performance of point-to-point communication is critical. As many scientific applications operate on multi-dimensional data, manipulating parts of these data becomes complicated because the underlying memory layout is not-contiguous. The MPI standard proposes a rich set of interfaces to define regular and irregular memory patterns, the so called Derived Datatypes (DDT). The DDTs provide a general and flexible solution to describe any collections of contiguous and non-contiguous data with a compact format. Once constructed and committed, an MPI datatype can be used as an argument for any MPI communication routines. Thus, the scientific application developers do not have to manually pack and unpack data in order to optimize noncontiguous data transfers, but instead they can safely rely on the MPI runtime to make such operations trivial and portable. To improve point-to-point communication between GPUs, the GPUDirect technique are proposed to enable RDMA-like data movement between GPUs without staging through host memory. Recent state-ofthe-art implementations of MPI, such as MVAPICH and Open MPI already utilize GPUDirect to provide the capability of direct GPU data movement between processes. Unfortunately, these optimizations were designed with a focus on contiguous data, leaving the most difficult operations, the packing and unpacking of non-contiguous memory patterns, in the charge of developers. There are effective packing/unpacking implementations for datatypes in host memory Ross et al. (2003). However, exposing the same level of support for a non-contiguous MPI datatype based on GPU memory remains an open challenge.

Since MPI collective operations are based on point-to-point communication, DDT support is usually integrated in point-to-point level, and then collective communications are automatically able to support non-contiguous data layout. In this dissertation, we achieve the following contributions on non-contiguous point-topoint communication of GPU data:

- We present the design of a datatype engine for non-contiguous GPU-resident data, which is able to take advantage of the embarrassingly parallel nature of the pack and unpack operations and efficiently map them onto GPU threads.

- We incorporate the GPU datatype engine into the Open MPI infrastructure, and takes advantage of the latest NVIDIA hardware capabilities, such as GPUDirect, not only to minimize the overheads but also to decrease the overall energy consumption. For contexts where GPUDirect is not available, we provide a copy-in/copy-out protocol using host memory as an intermediary buffer.

- We present a light-weight pipeline protocol to allow pack and unpack operations to work simultaneously.

- We demonstrate the performance improvement of point-to-point communication of non-contiguous GPU data by comparing with state-of-the-art MVAPICH library via variety of benchmarks.

#### **Collective Communication**

Collective communications are another set of communication patterns, which messages are exchanged within a group of processors. Since collective communications are widely used in scientific and deep learning application, it is crucial for MPI libraries to sustain the parallel applications by providing the most optimal collective routines. According to underlying link properties between GPUs, a collective operation in heterogeneous systems includes inter-node, inter-socket and intra-socket communications, whose bandwidth and latency are different. Therefore, a smart collective algorithm should be able to utilize the knowledge of GPU network topology to rearrange the processes involved in the collective pattern, in order to shift the burden from low performance networks and minimize communications on these slow channels. However, traditional collective algorithms do not worry about hierarchical networks, resulting in sub-optimal performance when mapping of MPI processes does not strictly follow the hardware hierarchy of processors and topology of GPUs participated in collective communications. Indeed, recent advances in MPI collective communications have already demonstrated that such performance issues can be solved by integration of network topology information into collective operations Graham et al. (2011) Kandalla et al. (2010). However, insufficient cooperation of communications of different topology levels (i.e. intra-socket, inter-socket and inter-node levels) leads to sub-optimal overlapping and pipelining of different levels' communications, and to algorithms that are not adaptable to the fluctuating network conditions. This calls for a collaborative approach between multiple levels of collective algorithms, dedicated to holistically managing all levels of the network hierarchies.

In this dissertation, we propose a new GPU-aware collective framework by taking account of GPU network topology and achieve the following contributions:

- We present a topology-aware collective framework in Open MPI, which orchestrates collaborations between multiple levels of network, toward a common goal. Instead of creating isolated communicators for different levels, we incorporate all processes into process groups based on their closeness, build communication tree based on network topology. In such way, we eliminate all topology levels boundaries and allow for fine grain pipelining between the different communications. Also since network of different topology levels are independent, we allow for more concurrent communications, eventually providing more opportunities for offloaded communications to overlap.

- We minimize communications over PCI-Express by caching data in CPU memory, so that inter-node and inter-socket communications are directly use the cached data instead of pulling data from GPU memory. One directional of PCI-Express is used for intra-socket GPU RDMA communication, and the other is used for update cached data from CPU memory back to GPU memory, therefore, PCI-Express is fully utilized but no congestion.

- As a side-effect of using GPUs, we also have the opportunity minimize the cost of the reduction operations by offloading them on the accelerators.

- We showcase two popular collective operations broadcast and reduce to prove the advantage of our topology-aware collective framework over the state-of-theart MVAPICH.

#### **1.2** Dissertation Outline

The rest of this dissertation is organized as follows: Chapter ?? introduces taskbased runtime with an application of dense linear algebra and GPU-aware MPI, as well as a survey of the literature of these two aspects. Chapter 3 discusses the approaches developed for PaRSEC to optimal utilization of resources in heterogeneous systems for computational tasks, including "hierarchical DAG" for optimal occupancy of both CPU and GPU, data coherence protocol for minimize data movement and multi-level GPU memory management for out of core execution. Chapter 4 presents the implementation of non-contiguous point-to-point communication of GPU data with benchmarks to demonstrate the performance improvement over other MPI implementations. Next, Chapter 5 describes the design of GPU-aware collective communication by integrating the knowledge of GPU network topology and locality with MPI. Two collective operations, broadcast and reduce, are use as example to prove the higher performance obtained compared with other MPI implementations under any process placement. Finally, Chapter 6 concludes the dissertation and outlines the future work.

### Chapter 2

# Background and Literature Review of Related Works

#### 2.1 Data-flow Programming Model

#### 2.1.1 DAG-Based Representation

Different from traditional control-flow programming model, data-flow programming paradigm emphasizes the movement of data and models programs as a series of connections. Explicitly defined inputs and outputs data connect different tasks. A task runs as soon as all of its inputs become valid. Thus, data-flow programming paradigm are inherently parallel and can work well in large, decentralized systems. With data-flow programming model, applications are divided into a set of different type of tasks, and described as a DAG D = (V, E). Tasks, also called kernels, are a set of sequential computations, which is fundamental of an application. In a DAG representation, a vertex  $v \in V$  represent a task and a edge represents data dependencies between a task  $v_1$  and its predecessor task  $v_2$ . If an edge  $(v_1, v_2)$  exists in E, then the output data of task  $v_1$  should be transferred to the execution location of task  $v_2$  as its input data, and task  $v_2$  can not start until its all input data is ready.

#### 2.1.2 Parallel Runtime Scheduling and Execution Controller

In order to deploy tasks in DAGs efficiently to a proper execution unit including CPU and GPUs, it is desired to provide a task-based runtime system. The Parallel Runtime Scheduling and Execution Controller (PaRSEC) Bosilca et al. (2012), developed by Innovative Computing Laboratory, is a generic framework for architecture-aware scheduling and management of micro-tasks on distributed many-core heterogeneous architectures. PaRSEC is an adoption of data-flow program paradigm, which takes this DAG-based representation and assigns tasks to the computing resources, and uses a dynamic, fully-distributed scheduler based on cache awareness, data-locality and task priority.

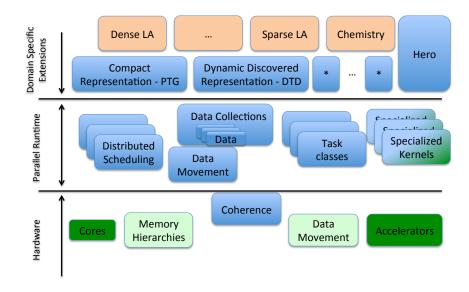

Figure 2.1 presents the detailed framework of PaRSEC, which is consisted of 3 levels. The first level is hardware level, which interacts with different hardware architecture, including multi-core CPUs, memory hierarchies and accelerators. The middle level is the functionalities of the parallel runtime in PaRSEC, including distributed scheduling, data distribution and movement, task management and creating specialized kernels. The third level is the extension for domain specific applications, including a concise format of representing tasks called Parameterized Task Graph (PTG) Cosnard et al. (1999), and a dynamic representation of tasks called Dynamic Task Discovery (DTD) Haidar et al. (2011).

#### 2.1.3 Tiled Dense Linear Algebra

In the area of dense linear algebra, DAGs have been demonstrated to be an extremely effective way to describe tiled linear algebra algorithms Agullo et al. (2009). In tiled linear algebra algorithms, an  $N \times N$  matrix is split into  $NT \times NT$  tiles, each of size  $B(\lceil N/B \rceil = NT)$ . A "tile" can be considered a sub-matrix of the original matrix. Therefore, instead of computing element by element, each computation task/kernel executes on tiles.

Figure 2.1: The Framework of PaRSEC.

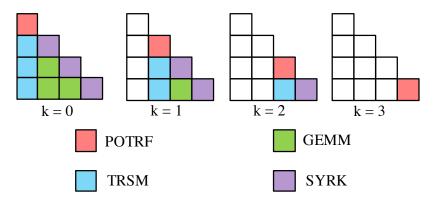

Figure 2.2: Cholesky factorization on matrix of  $4 \times 4$  tiles.

Cholesky factorizations is a classic linear algebra algorithms that are widely used for solving linear systems Ax = b, and as basic blocks in computing eigenvalues and singular values. It is composed of four kernels (POTRF, TRSM, SYRK and GEMM) Ltaief et al. (2011) that are successively applied on the trailing sub-matrix at each step, as illustrated in Figure 2.2 for matrices of  $4 \times 4$  tiles.

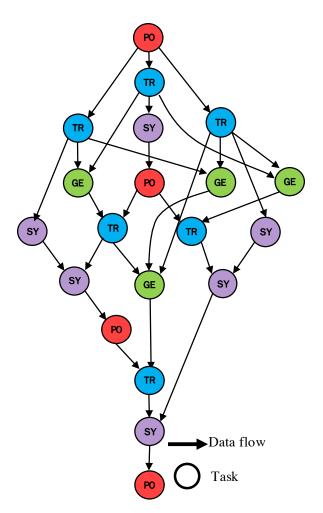

Figure 2.3: DAG representation of Cholesky factorization on matrix of  $4 \times 4$  tiles

- POTRF performs the untiled Cholesky factorization of a diagonal tile of the input matrix and overrides it with the final elements of the output matrix.

- SYRK is a symmetric rank-k update, which updates to a diagonal tile of the input matrix.

- TRSM is a triangular system solve, which applies transformation computed by POTRF to an off-diagonal tile below the diagonal tile operated by the last POTRF of the same column.

- GEMM is a matrix-matrix multiplication, used to update tiles in trailing matrix.

Figure 2.3 is the DAG representation of the Cholesky factorization shown on Figure 2.2. Usually, the execution location of a kernel is dynamic, which can be either a CPU core or an accelerator. With the help of task-based runtime such as PaRSEC, application developers only focus on translation of application into DAG representation; PaRSEC take care of data distribution and task scheduling: it automatically deploy tasks to a proper execution unit based on load balance and data locality. In this dissertation, Cholesky factorization is used to demonstrate the performance of GPU-aware design of PaRSEC.

#### 2.1.4 Literature Review

#### Dense Linear Algebra on Heterogeneous System

Dense linear algebra is one of the computing fields most likely to benefit early from any increase in the computational power of the hardware such as GPUs. Thus, it is not unexpected that every evolution at the hardware level is rapidly reflected in dense linear algebra libraries. MAGMA Agullo et al. (2009) Cao et al. (2013) is a linear algebra library designed for GPUs. It harnesses the power of both the GPU and the CPU by invoking CUDA, OpenCL, or multi-threaded BLAS kernels. Fogue et al. ported the existing PLAPACK library to GPU-accelerated clusters Fogue et al. (2010). However, both libraries are not driven by runtimes, their static scheduler distributes tasks equally among GPUs, resulting in potential load imbalance and poor portability. Beside, the current version of the MAGMA library doesn't support distributed memory systems.

#### Runtime Driven Dense Linear Algebra on Heterogeneous System

When towards heterogeneous system, more and more dense linear algebra libraries trend to transit to DAG-based representation and rely on runtime because of their better portability and load balance management. Quintana-Orti et al. extended the SuperMatrix runtime to shared-memory machines with GPUs Quintana-Ortí et al. (2009). LibFLAME is a another library for dense matrix computations in heterogeneous system Zee et al. (2009). However, in these solutions, only a particular type of computational kernel can execute on the CPU (the less compute-intensive diagonal blocks), which produces a load imbalance between CPUs and GPUs. As discussed in Chapter 1, because of hardware differences of CPU and GPUs, optimal data granularity (described as tile size in dense linear algebra) of CPU and GPU tasks are dramatically different. all these prior works mandate the use of an identical tile size, thereby preventing the adaptation of the task granularity to the considered execution resource.

There are a few prior works trying to resolve the tile size mismatch between CPUs and GPUs. Song et al. presented a heterogeneous tile algorithm Song et al. (2012) which divides square tiles into a skinny tall rectangle tile for the CPU and places the remainder on the GPU. It uses a non-uniform 1D partitioning, and data is statically distributed between GPUs, hence, it is likely to cause imbalance in the Cholesky factorization. Kim et al. adapted the libFLAME library to support different block sizes on different devices in a shared memory environment Kim et al. (2012). However, its write-through GPU data caching policy may incur too many unnecessary data movements between the host and the GPU. Lima et al. presented similar work for Intel Xeon Phi Lima et al. (2013). However, the decision to recursively split a task is made statically at submission time, without runtime insight. Furthermore, in their Cholesky factorization, only the POTRF kernel is recursively split.

Our approach uses a 2D block cyclic data distribution for each host, and data is dynamically assigned to GPUs to maintain good load balance. We maximize the throughput by allowing all operations with the GPU to be asynchronous, overlapping data movements and task submission to the GPU, and allowing threads to migrate between GPU management and CPU execution. Thanks to the parameterized DAG of our solution, the decision is taken dynamically at runtime and is not limited to a single kernel, an important distinction as several kernels can compose the critical path of an application. Moreover, our approach supports multiple node deployments with automatic network transfers and a distributed scheduler suited for large scale systems.

#### 2.2 GPU-aware MPI

The message passing model has emerged as an expressive, efficient, and wellunderstood paradigm for parallel programming. The process of creating a standard to enable portability of using message passing for application began at Message Passing Interface (MPI) Forum MPI Forum (1995). MPI is a message passing library standard, together with protocol and semantic specifications for how its features must behave in any implementation. Point-to-point and collective communications are two important and frequently used communication patterns in MPI Gropp et al. (1996). MPI is now already widely used for solving significant scientific and engineering problems on parallel computers. There are several state-of-theart MPI implementations such as Open MPI Gabriel et al. (2004), MPICH2 Gropp (2002), MVAPICH2 Huang et al. (2007) and Intel MPI. When towards heterogeneous systems, MPI implementations such as Open MPI and MVAPICH2 already provide some levels of support for data residing in GPU memory. With GPU-aware MPI, users can use MPI communication routine to transmit GPU data without hand-made moving data from GPU memory to host memory and vice versa. In this dissertation, we integrate GPU knowledge into Open MPI on both point-to-point and collective communications.

#### 2.2.1 MPI Derived Datatype

MPI provides a powerful and general way to describe arbitrary collections of data in memory. MPI Standard MPI Forum (1995) predefines its primitive data types such as MPI\_INT, MPI\_CHAR, MPI\_DOUBLE and so on, respecting to data type of int, char and double in C or Fortran language. Based on primitive data types, MPI also provides facilities for users to define their data structures, which is called MPI derived datatypes (DDT). MPI DDTs provide a flexible and general mechanism for working with arbitrary layouts (contiguous or non-contiguous) of data in memory. MPI defines data layouts of varying complexity:

- Contiguous: a number of repetitions of the same datatype without gaps inbetween

- Vector: defines a non-contiguous data layout that consists of equally spaced blocks of the same datatype.

- Indexed: specifies a noncontiguous data layout where neither the size of each block nor the displacements between successive blocks are equal.

- Struct: consists of location-blocklength-datatype tuples, allowing for the most flexible type of non-contiguous datatype construction.

Once constructed and committed, an MPI DDTs can be used as an argument for any point-to-point, collective, I/O, and one-sided functions. MPI DDTs allow users to treat non-contiguous data in a convenient manner as though it was contiguous in memory. Because current network is bandwidth-oriented instead of latency-oriented, large messages delivers better bytes per second transfer rates (network bandwidth). Without MPI DDTs, users must manually copy any data to be sent to a contiguous buffer, pass that to the send routine, and then unpack the data when it is received. With MPI DDTs, users can safely rely on MPI runtime to make such pack/unpack operations trivial and portable. Internally, the MPI datatype engine automatically packs and unpacks data based on the type of operation to be realized, in an efficient way while hiding the low-level details from users.

MPI DDTs provide a solution to avoid intermediate packing and unpacking of communication data that might otherwise be necessary when working with noncontiguous data manually, therefore, it is widely adopted by scientific applications. In the 2D stencil application of the Scalable HeterOgeneous Computing benchmark (SHOC) Danalis et al. (2010), two of the four boundaries are contiguous, and the other two are non-contiguous, which can be defined by a *vector* type. In the LAMMPS application from the molecular dynamics domain Schneider et al. (2012), each process keeps an array of indices of local particles that need to be communicated; such an access pattern can be captured by an *indexed* type. Hence, MPI datatypes help application developers alleviate the burden of manually packing and unpacking non-contiguous data. Recent MPI implementations have exhibited significant performance improvement for the handling of non-contiguous datatypes when handling CPU-based data Ross et al. (2003); Schneider et al. (2012). Therefore, it is urgent to extend the MPI DDTs support to GPU data for efficient programming in heterogeneous systems.

#### 2.2.2 MPI Point-to-point Communications

MPI point-to-point communications typically involve message exchanges between two MPI processes. One process is performing a send operation and the other process is performing a matching receive operation. As early as 1994, point-to-point communications have been included into the first MPI standard (MPI-1.1) MPI Forum (1995). MPI point-to-point communication is the basic communication routines, other communication patterns such as collective communication are build on top of pointto-point operations. Therefore, it is very important to deliver high performance point-to-point operations. MPI point-to-point operations can be categorized into two types based on the number of send and receive operations:

- Single send/receive: these types of routines issues only one send/receive operations at once, such as MPI\_Send and MPI\_Recv.

- Combined send/receive: these types of routines combine in one call the sending of a message to one destination and the receiving of another message, from another process, such as *MPI\_Sendrecv*.

Single send/receive routines support blocking and non-blocking mode. In blocking model, routines only return after it is safe to modify the users' data buffer for reuse. In

non-blocking model, routines return immediately without any communication events to complete, such as message copying from user memory to system buffer space or the actual arrival of message; actual communications are progressed only after the call to routine *MPI\_Wait/MPI\_Waitall*. Combined send/receive routines does not have non-blocking model since it force the sequence of receive after send, while non-blocking send/receive do not guarantee such sequence. No matter blocking or non-blocking model, the progressing of communications are the same; the only difference is the moment of progress (immediate or delayed). In this dissertation, we work on the layer of progressing point-to-point data transfer, hence, our work support both blocking and non-blocking point-to-point communications. The data type that is sent/received in MPI point-to-point routines can be either primitive or derived datatypes. The following subsections describe the API definition of single and combined send/receive operations in the MPI standard MPI Forum (1995)

#### Single Send/Receive

• Send

int MPI\_Send(const void \*buf, int count, MPI\_Datatype datatype, int dest, int tag, MPI\_Comm comm)

int MPI\_Isend(const void \*buf, int count, MPI\_Datatype datatype, int dest, int tag, MPI\_Comm comm, MPI\_Request \*request)

MPI\_Send blocks until the message is sent to the destination. MPI\_Isend is non-blocking; the sender should not modify any part of the send buffer after a nonblocking send operation is called, until the send completes.

• Receive

int MPI\_Recv(void \*buf, int count, MPI\_Datatype datatype, int source, int tag, MPI\_Comm comm, MPI\_Status \*status)

int MPI\_Irecv(void \*buf, int count, MPI\_Datatype datatype, int source, int tag, MPI\_Comm comm, MPI\_Request \*request)

MPI\_Recv is blocking: it returns only after the receive buffer contains the newly received message. A receive can complete before the matching send has completed (of course, it can complete only after the matching send has started). MPI\_Irecv is non-blocking; the receiver should not access any part of the receive buffer after a nonblocking receive operation is called, until the receive completes.

#### Combined Send/Receive

• Send/Receive

int MPI\_Sendrecv(const void \*sendbuf, int sendcount, MPI\_Datatype sendtype, int dest, int sendtag, void \*recvbuf, int recvcount, MPI\_Datatype recvtype, int source, int recvtag, MPI\_Comm comm, MPI\_Status \*status)

MPLSendrecv executes a blocking send and receive operation. Both send and receive use the same communicator, but possibly different tags. The send buffer and receive buffers must be disjoint, and may have different lengths and datatypes.

#### 2.2.3 MPI Collective Communications

MPI collective communications are abstracted from a wide variation of distributed parallel algorithms, which are another set of widely used communication patterns in MPI applications. MPI collective communications involve message exchanges among all processes in the scope of a communicator. Similar to point-to-point communications, collective communications are also included in the first MPI Standard (MPI-1.1) MPI Forum (1995). As well as point-to-point communication, collective communications are frequently used in all kinds of MPI applications. For example, broadcast and reduce are often used in All-Pairs-Shortest-Path algorithm Plaat et al. (1999) and deep learning applications Yu et al. (2014). In this dissertation, we focus on two types of widely used collective operations: broadcast and reduce, and the performance of these operations are greatly threatened by increasing amounts of data and hardware complexity especially when GPU is engaged. The performance of applications are usually sensitive to quality of implementations of these operations. The following subsections describe the API definition of single and combined send/receive operations in the MPI standard MPI Forum (1995).

#### Broadcast

int MPI\_Bcast ( void buffer , int count , MPI\_Datatype datatype , int root , MPI\_Comm comm)

MPLBcast sends a message from the root process to all processes within the communicator. It is called by all processes of the communicator with the same arguments for comm and root. Once returned, the contents of roots communication buffer has been copied to all processes.

#### Reduce

int MPI\_Reduce(const void \*sendbuf, void \*recvbuf, int count, MPI\_Datatype datatype, MPI\_Op op, int root, MPI\_Comm comm)

MPI\_Reduce performs a reduction operation "op" across all processes within the communicator. Data is gathered from send buffer (sendbuf) and final result is in receive buffer(recvbuf). This routine also support in-place mode, which converts the receive buffer into a send-and-receive buffer.

#### 2.2.4 Literature Review

#### **GPU-aware MPI Point-to-point Communication**

Heterogeneous systems equipped with both CPUs and GPUs are currently the most popular platform in high performance computing. Writing efficient applications for such heterogeneous systems is a challenging task as application developers need to explicitly manage two types of data movements: intra-process communications (device to host) and inter-process communications. Recent versions of well-known MPI libraries such as MVAPICH2 Wang et al. (2011b) and Open MPI already provide some levels of GPU support for point-to-point communications. With these GPU-Aware MPI libraries, application developers can use MPI constructs to transparently move data, even if the data resides in GPU memory. Similar efforts have been made to integrate GPU-awarness into other programming models. Aij et. al. propose the MPI-ACC Aji et al. (2012), which seamlessly integrates OpenACC with the MPI library, enabling OpenACC applications to perform end-to-end data movement. Lawlor presents the cudaMPI Lawlor (2009) library for communication between GPUs, which provides specialized data movement calls that translate to *cudaMemcpy* followed by the corresponding MPI call. Even though the paper discusses noncontiguous data support, the current implementation only includes support for vector types. For the PGAS programming model, Potluri et. al Potluri et al. (2013) extend OpenSHMEM to GPU clusters providing a unified memory space. However, as OpenSHMEM has no support for non-contiguous types, this implementation does not provide sufficient support to communicate non-contiguous GPU data. All these works focus on providing GPU-awarness for parallel programming models, and have been demonstrated to deliver good performance for contiguous data, but none of them provide full and efficient support for non-contiguous data residing in GPU memory.

More recent works have focused on providing non-contiguous MPI datatype functionality for GPU data. Wang et. al. have improved the MVAPICH MPI implementation to provide the ability to transparently communicate non-contiguous GPU memory that can be represented as a single vector, and therefore translated into CUDA's two-dimensional memory copy (*cudaMemcpy2D*) Wang et al. (2011a). A subsequent paper by the same authors tries to extend this functionality to many data-types by proposing a vectorization algorithm to convert any type of datatype into a set of vector datatypes Wang et al. (2014). Unfortunately, indexed datatypes such as triangular matrices, are difficult to convert into a compact vector type. Using Wang's approach, each contiguous block in such an indexed datatype is considered as a single vector type and packed/unpacked separately from other vectors by its own call to *cudaMemcpy2D*, increasing the number of synchronizations and consequently decreasing the performance. Moreover, no pipelining or overlap between the different stages of the datatype conversion is provided, even further limiting the performance.

Jenkins et. al. integrated a GPU datatype extension into the MPICH library Jenkins et al. (2014). His work focuses on the packing and unpacking of GPU kernels, but without providing overlaps between data packing/unpacking and other communication steps. Both Wang and Jenkins's work require transitioning the packed GPU data through host memory, increasing the load on the memory bus and imposing a significant sequential overhead on the communications. All of these approaches are drastically different from our proposed design, as in our work we favor pipelining between GPU data packing/unpacking and data movements, and also take advantage, when possible, of GPUDirect to bypass the host memory and therefore decrease latency and improve bandwidth.

#### **GPU-aware MPI Collective Communication**

In heterogeneous system, according to underlying link properties between processes, when data is residing in GPU memory, communications between any two processes could use different networks depending on the location of GPUs (discussed in Section 1.1). Therefore, message exchanges between processes involve different networks (intra-socket, inter-socket and inter-node). To minimize the data movement over the heavy channels, collective communication should be able to take care of GPU localities, which is represented by GPU network topology.

For data in host memory, several previous works have been done to use topology-aware idea for collective operations to take advantage of communication cost differences at every level in network. MagPIe Kielmann et al. (1999) creates hierarchical algorithms for clustered wide-area systems to avoid slow links. MPICH2 Zhu et al. (2009) implements several collective operations by exploits knowledge of the topology. But these works only consider two network layers. Karonis et. al. Karonis et al. (2000) extends the previous work and presents a multi-level topology-aware tree to support more network layers. Later, MVAPICH2 Kandalla et al. (2010) Subramoni et al. (2012a) introduce Neighbor-Joining techniques to detect network topology on switch level, and adds one more levels in the network hierarchy collective operations. However, all these approaches focus on exploring more and more network topology levels. While they provide interesting performance compared with a single-level approaches, but their inter and intra levels communications do not cooperate tightly, leading to non-communication overlap between different topology levels.

Other researchers try to take the benefit of shared memory and propose hierarchical collective operations. Tipparaju et. al. Tipparaju et al. (2003) uses shared memory as intermediate buffer to reduce number of memories. Cheetah Graham et al. (2011) is a hierarchical collective communication framework. In this framework, a Directed Acyclic Graph is constructed based on characteristics of communication topology. It can take advantage of shared memory for intra-node communications and point-to-point (p2p) or InfiniBand CORE-Direct for inter-node communications. Parsons et. al. Parsons and Pai (2014) decouples the choice of inter-node and intra-node communication algorithms. Similarly, all these work do not have communiation overlap between levels. HierKNEM Ma et al. (2012) enables tight collaboration between the collective algorithms pertaining to different layers of the hierarchy. It combines KNEM(an Linux kernel for memcpy in shared memory), pipelining and hierarchical idea to allow overlap of inter-node and intranode communication. But it only have two topology level and in each level the tree is fixed. Our algorithm can support multiple topology levels and each level can select different algorithms base on different characteristic of each group like number of processes and message size. Also HierKNEM is bind to shared memory, but our framework is much more flexible which supports different hardware like GPU.

State-of-the-art MPI libraries such as Open MPI and MVAPICH2 Singh et al. (2011) have provided CUDA-aware collective communications. But they never integrate GPU knowledge into their MPI, which still move data from GPU memory to host memory for reduction operations, without taking the parallelism feature of GPU to handle large parallel reduction operations. Later, Chu et. al. Chu et al. (2016) and Oden et. al. Oden et al. (2014) have proposed CUDA-aware reduce operations by leveraging CUDA kernels to handle reduction operations. Similarly NVidia introduces NCCL NVIDIA (2016), which is collective communication library targeted to shared memory multi-GPU platform. Overall, non of them take care of network hierarchical topology of GPU clusters. Awan et. al. Awan et al. (2016) have integrated NCCL into MVAPICH2 to provide hierarchical broadcast operations by using NCCL to handle intra-node communications. However, similar to MVAPICH2 in CPU clusters discussed before, there is no communication overlap between different topology levels. Moreover, they never consider the intra-node GPU locality (PCI-Express level). Our design is the first MPI implementation who is integrated with inter- and intra-node GPU network topology and allows communications overlap of inter and intra levels.

## Chapter 3

# PaRSEC's Support for Heterogeneous System

The portion of this chapter is drawn from the following publication of mine:

• W Wu, A Bouteiller, G Bosilca, M Faverge, J Dongarra, "Hierarchical dag scheduling for hybrid distributed systems", Parallel and Distributed Processing Symposium (IPDPS), 2015 IEEE International

## 3.1 Issues of PaRSEC in Heterogeneous System

Data-flow programming paradigm describes an application as a DAG where nodes represent tasks and edges represent data dependencies between tasks. Deploying a task promptly to a proper execution location is critical to performance of application, therefore, it is preferred to apply a task-based runtime to schedule DAGs to achieve fully exploiting of the computing resources in heterogeneous systems. In the context of linear algebra, DAGs have been demonstrated to be an extremely effective way to describe tiled linear algebra algorithms. PaRSEC, an adoption of data-flow program paradigm, takes this DAG-based representation and schedule tasks efficiently in homogeneous systems. However, when porting them to heterogeneous system to use both CPU and GPUs efficiently, there are several issues caused by the hardware differences and separated memory space between GPU and CPU. This chapter describes how we solve these issue and achieve high occupancy of both CPU and GPUs.

## 3.1.1 Data Granularity of CPU/GPU Tasks

Tiled linear algebra is a representative class of algorithms that can be expressed efficiently with a data-flow: the parallelism between operations is represented with a DAG that symbolizes the flow of data between several tasks called kernels, which are described as nodes in a DAG. As discussed in Chapter 2.1.3, in tiled linear algebra algorithms, each kernel works on tiles instead of element of matrix. The tile size is a key tuning parameter that affects the efficiency of kernels tremendously. In most linear algebra algorithms, the tile size has been assumed to be constant for all kernels.

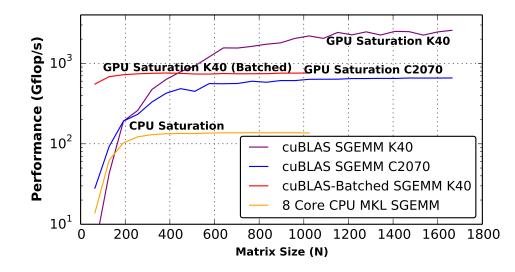

In most heterogeneous systems, a computing node features several CPU cores and one or more GPUs. Kernels are executed on CPU cores or GPUs depending on their performance profile and the occupancy on the target execution unit. Compared with CPU cores, a GPU has many more lightweight computing units; hence GPU tasks(kernels) usually require more data parallelism than CPU tasks to achieve high occupancy of GPU as they need to dispatch computation on many individual cores. The optimal data granularity of GPU tasks is larger than CPU. In tiled linear algebra algorithm, such data granularity is described as tile size. Therefore, GPU kernels reach their optimal efficiency when using larger tile sizes; on the other hand, CPU cores often reach good efficiency when using moderate or small tile sizes. Figure 3.1 shows the performance of the SGEMM (real single precision general matrix-matrix multiplication) kernel on different environments varies by tile size.

When running on a 8 cores Intel Nehalem Xeon E5520 CPU, the best CPU implementation of SGEMM (Intel MKL) reaches its peak performance starting from problem sizes larger than 200; while in the best GPU implementation of SGEMM

Figure 3.1: Performance of compute kernels on CPU and GPU depending on problem granularity

(cuBLAS), the optimal problem size is larger than 1000 on a Fermi C2070, and larger than 1500 on a Kepler K40. When problem size (matrix size) is fixed, the total number of tasks is directly depended on tile size. Therefore, in a heterogeneous system, selecting a optimal tile size becomes a dilemma:

- If small tile size (optimal for CPU) is used, GPU kernels can not achieve fully utilization of the GPU computing resources since the small problem size cannot efficiently span over all GPU execution units.

- If large tile size (optimal for GPU) is used, given a certain matrix size N, the amount of exploitable parallelism of a DAG is limited by the number of tiles, directly depending on the tile size (N/B). Therefore, when problem size is fixed, increasing the tile size proportionally decreases the parallelism. Furthermore, certain kernels (especially memory bound kernels) are less efficient than their functionally equivalent decomposition into smaller but more compute bound kernels. Executing these large kernels is thereby adding synchronous choke points that delay the execution of other dependent kernels, further decreasing the occupancy of all compute resources.