#### University of Tennessee, Knoxville

# TRACE: Tennessee Research and Creative **Exchange**

**Doctoral Dissertations**

Graduate School

12-2016

# Design and Analysis of a Fully-Integrated Resonant Gate Driver

Yu Long University of Tennessee, Knoxville, ylong@vols.utk.edu

Follow this and additional works at: https://trace.tennessee.edu/utk\_graddiss

Part of the Electrical and Electronics Commons

#### **Recommended Citation**

Long, Yu, "Design and Analysis of a Fully-Integrated Resonant Gate Driver." PhD diss., University of Tennessee, 2016.

https://trace.tennessee.edu/utk\_graddiss/4147

This Dissertation is brought to you for free and open access by the Graduate School at TRACE: Tennessee Research and Creative Exchange. It has been accepted for inclusion in Doctoral Dissertations by an authorized administrator of TRACE: Tennessee Research and Creative Exchange. For more information, please contact trace@utk.edu.

To the Graduate Council:

I am submitting herewith a dissertation written by Yu Long entitled "Design and Analysis of a Fully-Integrated Resonant Gate Driver." I have examined the final electronic copy of this dissertation for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Doctor of Philosophy, with a major in Electrical Engineering.

Benjamin J. Blalock, Major Professor

We have read this dissertation and recommend its acceptance:

Daniel Costinett, Syed K. Islam, Vasilios Alexiades

Accepted for the Council:

Carolyn R. Hodges

Vice Provost and Dean of the Graduate School

(Original signatures are on file with official student records.)

# Design and Analysis of a Fully-Integrated Resonant Gate Driver

A Dissertation Presented for the

Doctor of Philosophy

Degree

The University of Tennessee, Knoxville

Yu Long December 2016

# Acknowledgements

There are so many people I appreciate during my study at the University of Tennessee.

The first person is definitely my advisor, Dr. Benjamin Blalock. I am deeply indebted to your decision of accepting me as your graduate student. Without your guidance and patience, there is no way for me to stay, to study, and to improve during my whole PhD process.

I also greatly appreciate my colleagues at ICASL (Integrated Circuits and Systems Laboratory), my friends at CURENT (Center for Ultra-wide-area Resilient Electric Energy Transmission Networks) for all their knowledge and courage. I appreciate the discussion and help from my colleagues Jeffery Dix, Kyle Harris and George Niemela of ICASL for their knowledge in IC design. I also appreciate my CURENT colleagues Wen Zhang, Edward A. Jones, Gabriel A. Gabian, Chi Xu and Dr. Zheyu Zhang for their knowledge in power electronics and applications. I also appreciate my former team member, Dr. Weimin Zhang of CURENT. He is the first person to introduce me to the world of power electronics. The endless time spent together in the laboratory testing those "fragile" GaN devices is unforgettable. I deeply appreciate the guidance from Dr. Daniel J. Costinett and Dr. Fred Wang for their insightful advice on power electronics both from academic and industrial viewpoints.

My parents are always the ever-lasting spring of love and patience in my heart. I would also like thank my wife, Yuyuan Liu, the most considerate girl I have ever met, who give me the best family support I can imagine. I also appreciate the continuous support especially from my mother, Qingxiang Song, your endless love helps me to go through those difficult times during my lonely stay abroad.

I also appreciate years of uninterrupted financial support from the II-VI Foundation and the department of Electrical Engineering and Computer Science (EECS) of University of Tennessee.

Finally, I appreciate all my committee members for their patience and advice on this dissertation.

## Abstract

Several decades ago the resonant gate driving technique was proposed. Given the recent rapid growth in GaN HEMT power device applications for high-frequency power applications, research has been conducted in the power electronics field using resonant gate driving for GaN power devices. Previous research for resonant gate drivers for GaN HEMT devices mostly focused on implementing the gate driving function itself, and mostly for normally-on HEMT devices.

The normally-off (enhancement mode) GaN power device was introduced to the commercial market in 2009. A new resonate gate driver is proposed in this work to implement resonant gate driving for commercial high-speed normally-off GaN power devices. The desired resonant condition is configured by different turn-on and turn-off driving pulses with specific driving time and pulse width. Using synchronous timing control within the driver integrated circuit, the power device gate voltage is securely clamped within the expected gate voltage at switching frequencies beyond 10 MHz. In this research, a customized resonant gate driver IC was designed and developed on a commercially-available silicon CMOS process. Compared with current commercial gate driver ICs, our test results demonstrate the effectiveness, advantages and limitations of the proposed gate driver IC for the enhancement-mode GaN power device using alternative resonant gate driving techniques for the first time.

# Table of Contents

| Chapter 1  | Introduction                                                    |

|------------|-----------------------------------------------------------------|

| 1.1        | Background and Motivations                                      |

| 1.2        | Objectives2                                                     |

| 1.3        | Contributions                                                   |

| 1.4        | Organization3                                                   |

| Chapter 2  | High-frequency Resonant Gate Drivers for Power Devices4         |

| 2.1        | Introduction to GaN HEMT Devices                                |

| 2.2        | Conventional Gate Drivers for Power MOSFET's                    |

| 2.3        | Resonant Power MOSFET Gate Drivers                              |

| 2.4        | Resonant Gate Driver Design Considerations for Power GaN HEMT's |

|            |                                                                 |

| Chapter 3  | A Fully-Integrated Resonant Gate Driver for Power GaN Devices31 |

| 3.1        | Introduction to the eGaN FET                                    |

| 3.2        | Operation Principles of the Proposed Resonant Gate Driver       |

| 3.3        | Loss Analysis of the Proposed Resonant Gate Driver              |

| 3.4        | Design of the Low-side Resonant Gate Driver                     |

| 3.5        | Simulation Results                                              |

| Chapter 4  | Design Implementation, Experimental Results and Analysis        |

| 4.1        | Implementation of the MOSFET-Clamped Resonant Gate Driver       |

| 4.2        | Testing Results for Capacitive Load                             |

| 4.3        | Testing Results for Resistive and Inductive Load                |

| 4.4        | Experimental Results Analysis                                   |

| Chapter 5  | Conclusion and Future Work                                      |

| References | 86                                                              |

| Appendix   | 93                                                              |

| Vita       |                                                                 |

# List of Tables

| Table 2.1 | Material properties of Si, GaAs, SiC and GaN at 300°K6                                                                                                       |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 3.1 | Device characteristics for three typical power transistors with similar voltage and current capability and channel resistance                                |

| Table 3.2 | Truth table of the proposed non-clamping resonant gate driver 47                                                                                             |

| Table 3.3 | Truth tables of the proposed MOSFET-clamped resonant gate driver                                                                                             |

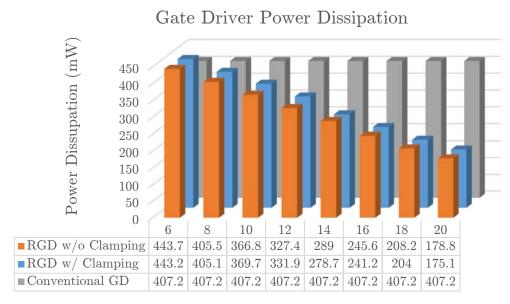

| Table 3.4 | Components' values used in Cadence Ultrasim simulations for conventional gate driver's types (a), resonant gate drivers type (b), (c), (d), (e), (f) and (g) |

# List of Figures

| Figure 2.1  | Bandgaps of the most important elemental and binary cubic                                                                                                                                                                                                                                 |  |  |  |  |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|             | semiconductors versus their lattice constant at $300^{\circ}\mathrm{K}\ [6]$                                                                                                                                                                                                              |  |  |  |  |  |

| Figure 2.2  | EPC eGaN ff FET structure [20]                                                                                                                                                                                                                                                            |  |  |  |  |  |

| Figure 2.3  | A p-AlGaN and i-AlGaN heterojuction implemented by gate injection transistor (GIT) displayed a depleted 2DEG for enhancement-mode operation [21]                                                                                                                                          |  |  |  |  |  |

| Figure 2.4  | SEM micrograph of an EPC eGaN FET [15]                                                                                                                                                                                                                                                    |  |  |  |  |  |

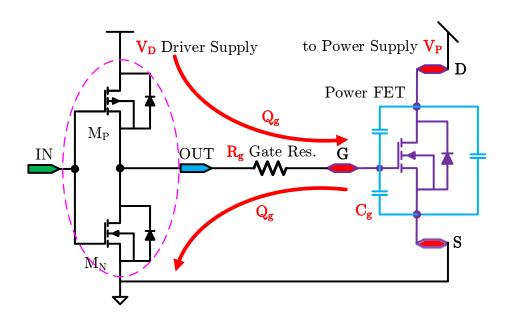

| Figure 2.5  | A simplified "totem-pole" output stage for a conventional power  MOSFET driver                                                                                                                                                                                                            |  |  |  |  |  |

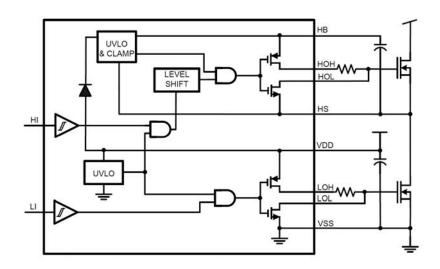

| Figure 2.6  | Block diagram of LM5113 [19]10                                                                                                                                                                                                                                                            |  |  |  |  |  |

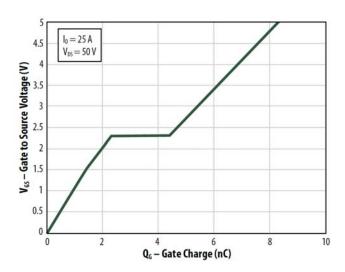

| Figure 2.7  | Gate charge versus Gate-source voltage for EPC2001 [30]                                                                                                                                                                                                                                   |  |  |  |  |  |

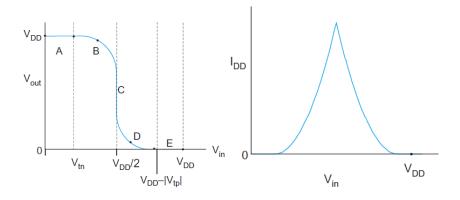

| Figure 2.8  | A CMOS inverter DC characteristics showing the dynamic short-circuit power loss. On the left is the output voltage vs. input voltage, on the right is the output current versus input voltage. "B", "C" and "D" means the region where PMOS or NMOS is in linear or saturated region [26] |  |  |  |  |  |

| Figure 2.9  | A resonant gate driver using extra resonant inductor and capacitors [34]                                                                                                                                                                                                                  |  |  |  |  |  |

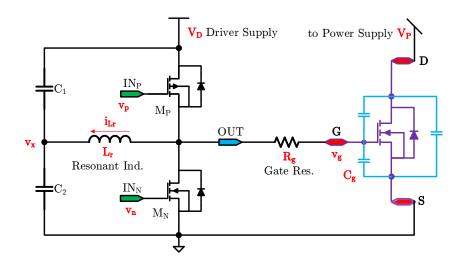

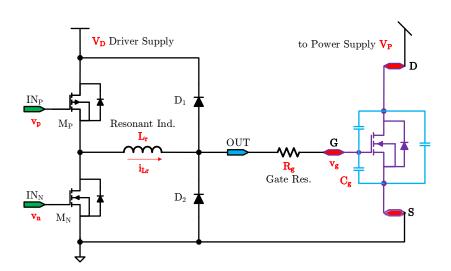

| Figure 2.10 | Simplified steady state waveforms of the gate driver in Figure 2.9, from top: driver output PMOS MP gate voltage vp, driver output NMOS MN gate voltage vn, resonant inductor Lr current iLr and power development of the gate G voltage vg                                               |  |  |  |  |  |

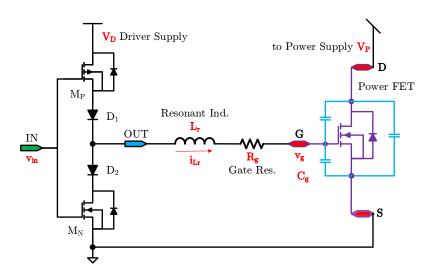

| Figure 2.11 | A resonant gate driver using gate inductor and reverse blocking diodes in series [36]                                                                                                                                                                                                     |  |  |  |  |  |

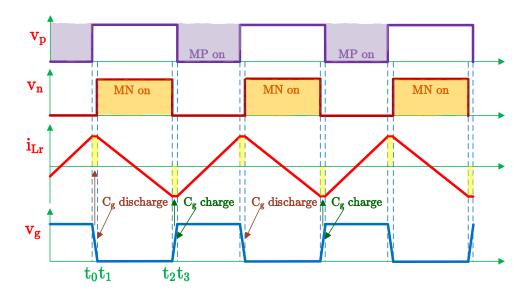

| Figure 2.12 | Simplified steady state waveforms of the gate driver in Figure 2.11, [from top:] driver control input IN voltage, resonant inductor Lr current and power device gate G voltage [36]                                                                                                       |  |  |  |  |  |

| Figure 2.13 | A resonant gate driver using gate inductor and gate clamping diodes parallel [38] [39]                                                                                                                                                                                                    |  |  |  |  |  |

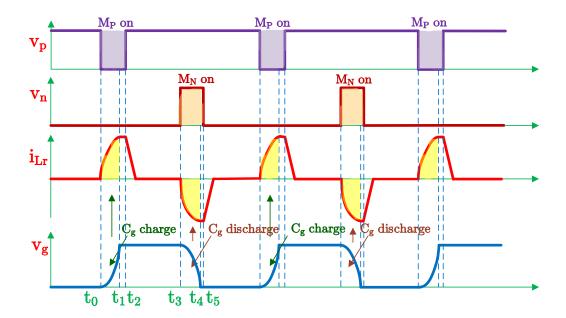

| Figure 2.14 | Simplified steady state waveforms of the gate driver in Figure 2.13, [from top:] gate driver PMOS MP gate control voltage vp, NMOS MN gate control voltage vn, resonant inductor Lr current iLr and power device gate G voltage vg [38] [39]                                              |  |  |  |  |  |

| Figure 2.15 | A resonant gate driver using gate inductor and gate clamping diodes in parallel [40] - [43]                                                                                                                                                                                               |  |  |  |  |  |

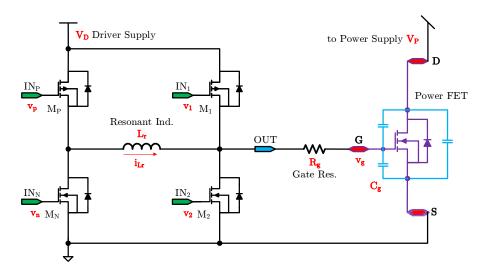

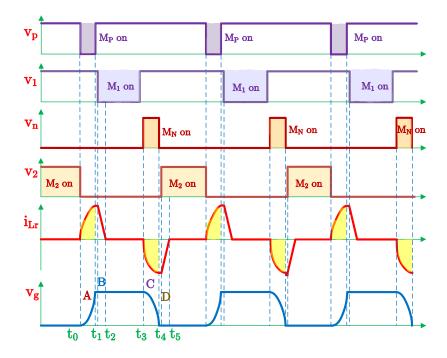

| Figure 2.16 | Simplified steady state waveforms of the gate driver in Figure 2.15, [from top:] gate driver PMOS MP gate control voltage vp, clamping PMOS M1 gate control voltage v1, driver NMOS MN gate control voltage vn, clamping NMOS M2 gate control voltage v2, resonant inductor Lr current iLr and power device gate G voltage vg [40] - [43] |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

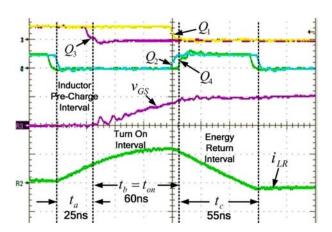

| Figure 2.17 | Measured waveforms of the turn-on process of a rectifier working at 1.5-MHz switching frequency. [From top:] M1 (Q1) and M2 (Q3) gating signals (10 V/div and 20 ns/div), MP (Q2) and MN (Q4) gating signals (10 V/div), power-MOSFET gate voltage Vg (5 V/div) and inductor current iLr (1 A/div) [43]                                   |

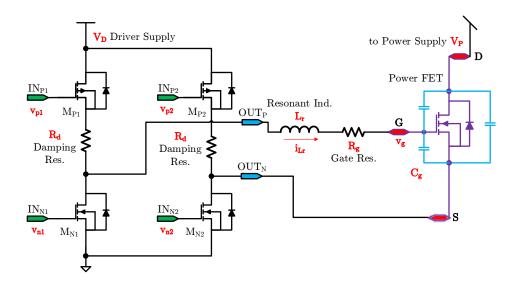

| Figure 2.18 | An H-bridge resonant gate driver using gate inductor in series [47] [48]                                                                                                                                                                                                                                                                  |

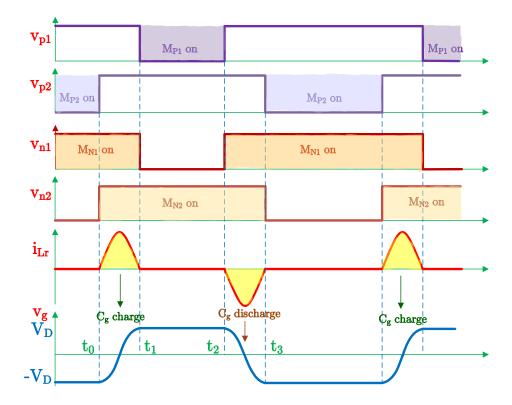

| Figure 2.19 | Simplified steady state waveforms of the H-bridge resonant gate [47] [48] [49]                                                                                                                                                                                                                                                            |

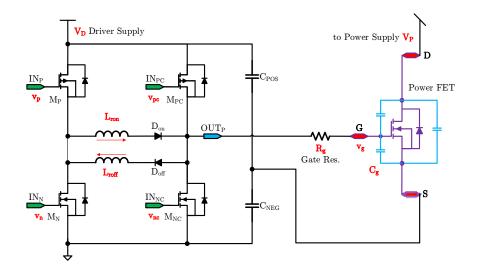

| Figure 2.20 | Another H-bridge resonant gate driver using gate inductor in series and capacitor voltage divider [51]                                                                                                                                                                                                                                    |

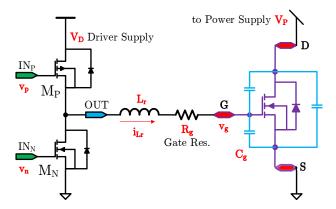

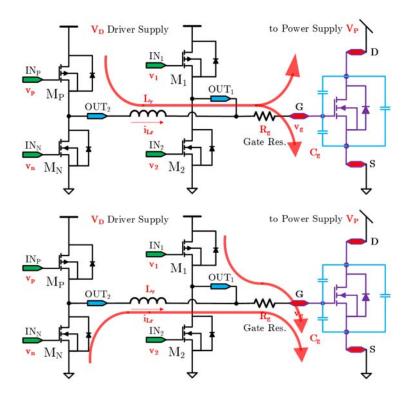

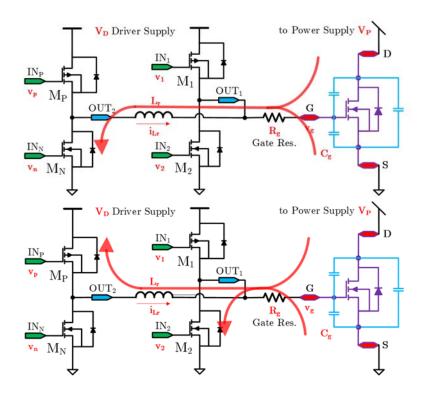

| Figure 3.1  | Proposed non-clamping resonant gate driver shared the same output structure as a conventional gate driver [62]                                                                                                                                                                                                                            |

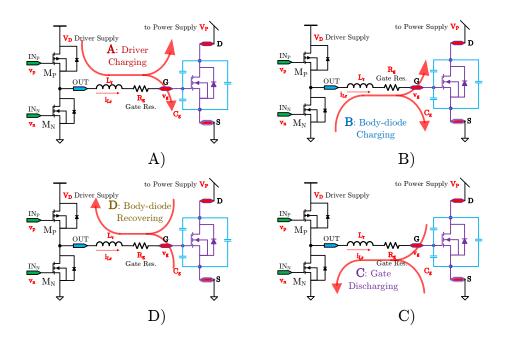

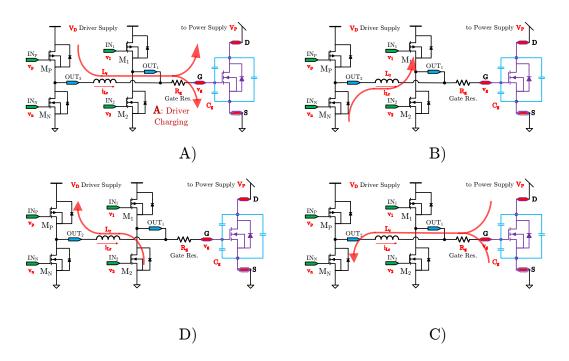

| Figure 3.2  | Four operation intervals for the proposed resonant gate driver, [from top-left clockwise:] A) driver charging, B) body-diode charging, C) gate discharging, D) body-diode recovery [62]                                                                                                                                                   |

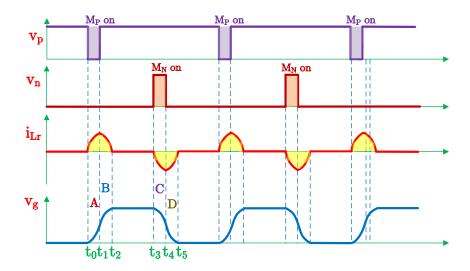

| Figure 3.3  | Simplified steady state waveforms of the proposed non-clamping resonant gate driver, the A, B, C and D shows the four operating intervals in Figure 3.2 [62]                                                                                                                                                                              |

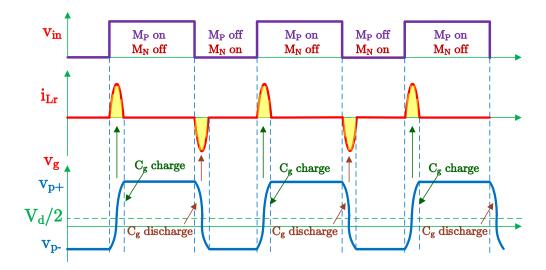

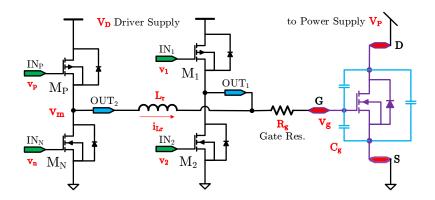

| Figure 3.4  | Proposed MOSFET-clamped resonant gate driver                                                                                                                                                                                                                                                                                              |

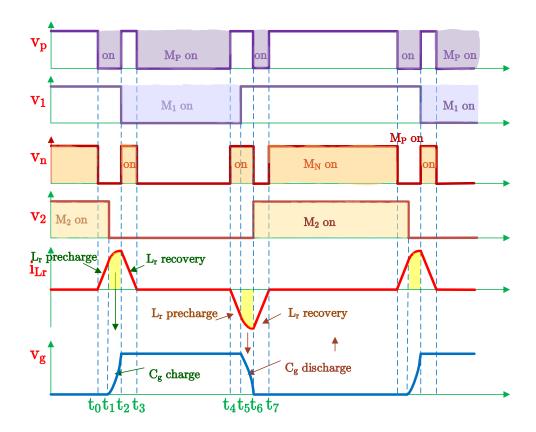

| Figure 3.5  | Four operation intervals for the proposed MOSFET-clamped resonant gate driver, [from top-left clockwise:] A) driver charging, B) charging recovery, C) gate discharging, D) discharging recovery                                                                                                                                          |

| Figure 3.6  | Simplified steady state waveforms of the proposed MOSFET-clamped resonant gate driver, the A, B, C and D shows the four operating intervals in Figure 3.5                                                                                                                                                                                 |

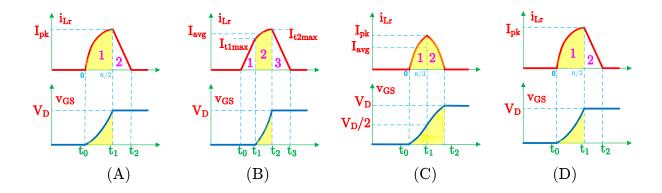

| Figure 3.7  | Simplified charging steady state inductor current and gate voltage waveforms of three resonant gate drivers, [from left:] (A) topology C [38] [55], (B) topology D [40], (C) proposed non-clamping topology [62] and (D) proposed MOSFET-clamped topology                                                                                 |

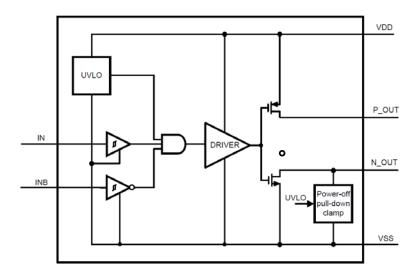

| Figure 3.8  | Block diagram of the low-side conventional gate driver LM5114 [26]                                                                                                                                                                                                                                                                        |

|             | 46                                                                                                                                                                                                                                                                                                                                        |

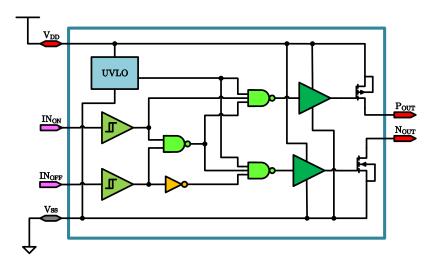

| Figure 3.9                                                                                                                                                                                     | Block diagram of the proposed non-clamping low-side resonant gate driver                                                                                                                                                                                                                                                                                      |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

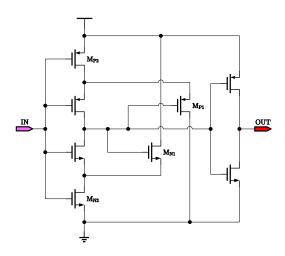

| Figure 3.10                                                                                                                                                                                    | Schematic diagram of the input Schmitt trigger                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| Figure 3.11                                                                                                                                                                                    | Cadence Spectre simulation of the Virtuosos schematic (in blue) and the Calibre xACT 3D extracted layout (in red)                                                                                                                                                                                                                                             |  |  |  |  |

| Figure 3.12                                                                                                                                                                                    | Schematic diagram of the proposed UVLO circuit, [circled area from left:] start-up circuit, BMR, differential-ended differential amplifier, comparator, single-ended differential amplifier                                                                                                                                                                   |  |  |  |  |

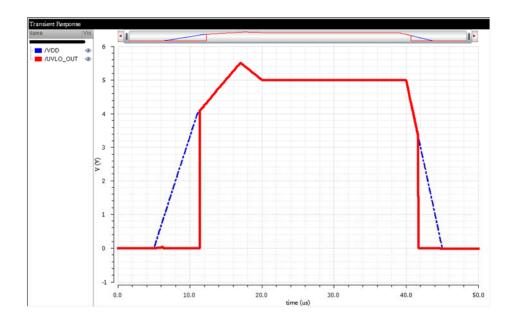

| Figure 3.13                                                                                                                                                                                    | Cadence Spectre simulation of the proposed UVLO in Figure 3.7, [from top:] the VDD input voltage; the UVLO output voltage                                                                                                                                                                                                                                     |  |  |  |  |

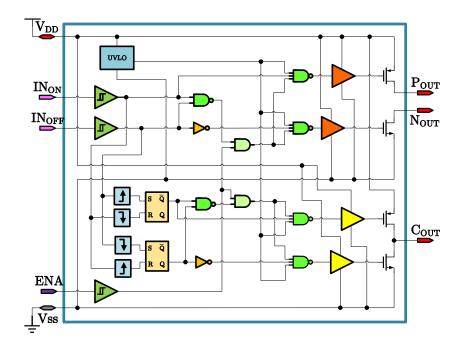

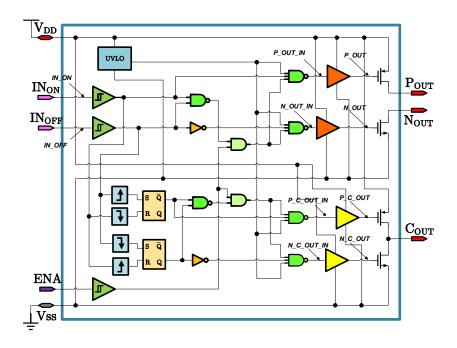

| Figure 3.14                                                                                                                                                                                    | Block diagram of the proposed MOSFET-clamped low-side resonant gate driver                                                                                                                                                                                                                                                                                    |  |  |  |  |

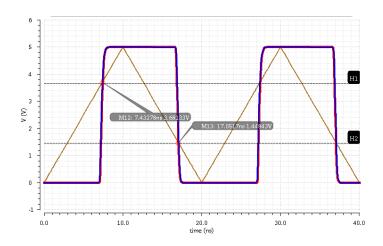

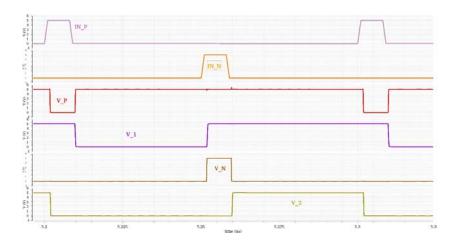

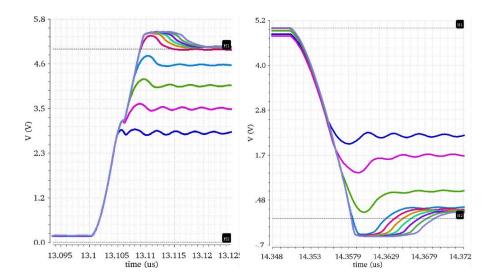

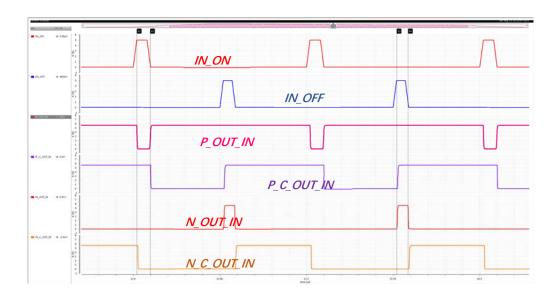

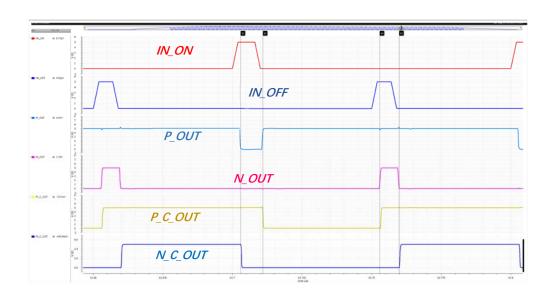

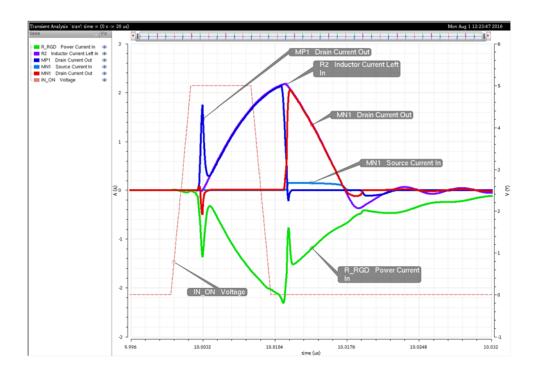

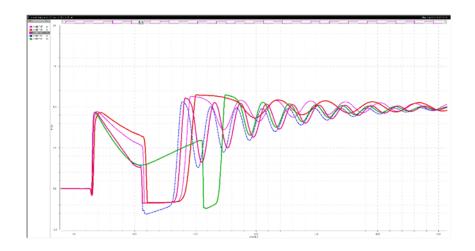

| Figure 3.15                                                                                                                                                                                    | Cadence Ultrasim simulation results for the voltage control outputs of the proposed MOSFET-clamped resonant gate driver (in Figure 3.4) working a4 10 MHz with 20 nH resonant inductor (type (g) in Table 3.4), [from top:] IN P and IN N, control inputs; V P, gate voltage of MP; V 1, gate voltage of M1; V N, gate voltage of MN; V 2, gate voltage of M2 |  |  |  |  |

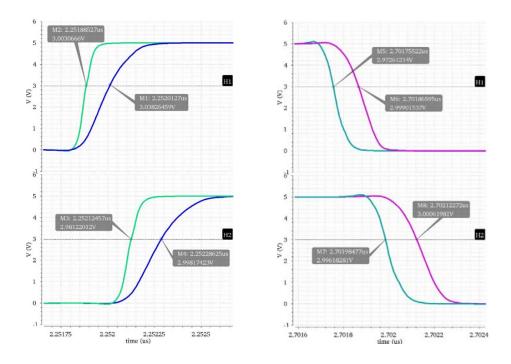

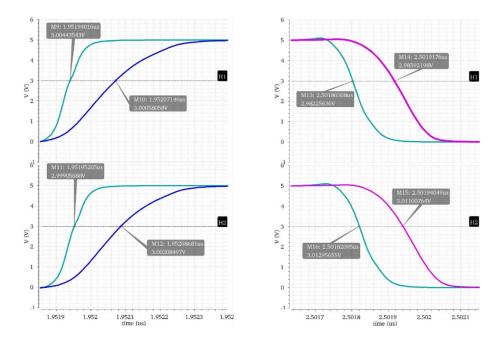

| Figure 3.16                                                                                                                                                                                    | Cadence Ultrasim simulation results for the transition delay at $25^{\circ}$ C (top) and $125^{\circ}$ C (bottom), [from left:] VN rising edge to V1 rising edge; VP falling edge to V2 falling edge                                                                                                                                                          |  |  |  |  |

| Figure 3.17                                                                                                                                                                                    | Cadence Ultrasim simulation results for the transition delay at 50 °C (top) with different process corner models, [from left:] fast NMOS slow PMOS (fs) models; slow NMOS fast PMOS (sf) models                                                                                                                                                               |  |  |  |  |

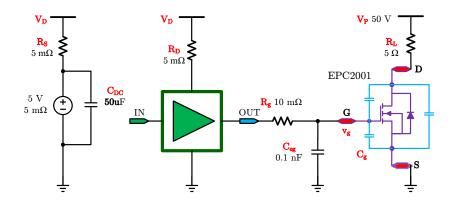

| Figure 3.18                                                                                                                                                                                    | Test circuit schematic diagram for several gate drivers' simulations                                                                                                                                                                                                                                                                                          |  |  |  |  |

| Figure 3.19                                                                                                                                                                                    | Schematic diagram for the gate drivers, [from left:] type (c) and type (g)                                                                                                                                                                                                                                                                                    |  |  |  |  |

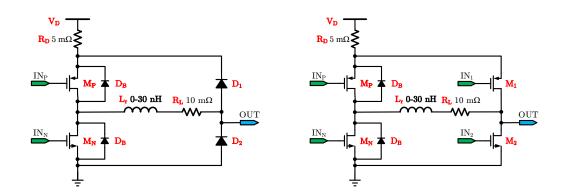

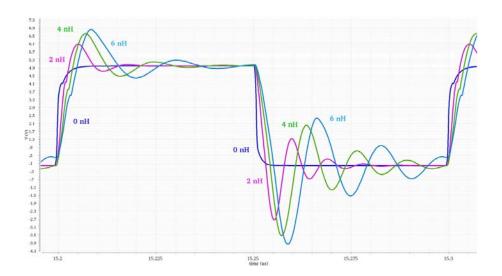

| Figure 3.20                                                                                                                                                                                    | Cadence Spectre schematic simulation of VGS voltage waveforms of EPC2001 for conventional gate driver type (a) with gate inductor values at 0, 2, 4, 6 nH                                                                                                                                                                                                     |  |  |  |  |

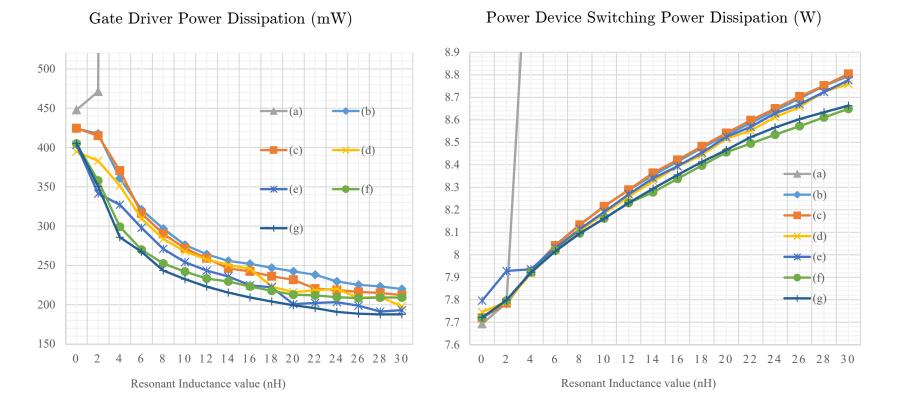

| Figure 3.21                                                                                                                                                                                    | Cadence Ultrasim schematic simulation of gate driving losses and power device switching losses at 10 MHz for the gate drivers type (a), (b), (c), (d), (e), (f) and (g) in Table 3.4with gate (resonant) inductance varies from 0 to 30 nH with the step of 2 nH                                                                                              |  |  |  |  |

| Figure 3.22 Cadence Spectre schematic simulation of VGS voltage waveform EPC2001 for resonant gate driver type (b), [from top:] VGS vol MN gate control signals with pulse width of 3 to 12 ns |                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

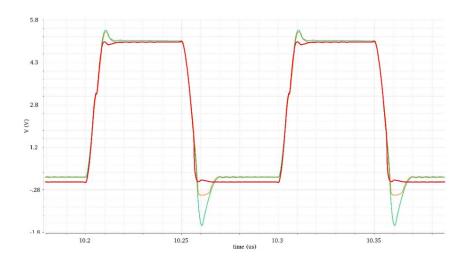

| Figure 3.23  | Cadence Ultrasim schematic simulation of gate-source voltage waveforms (VGS) of EPC2001 for resonant gate drivers [orange] (b), [green] type (d) and [red] type (f) in Table 3.4 with gate inductance of 16 nH                                                                                                                               |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

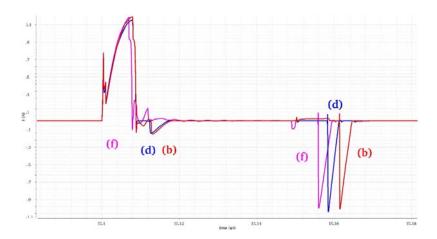

| Figure 3.24  | Cadence Ultrasim schematic simulation of gate driver power supply current waveforms (IGD) of EPC2001 for resonant gate drivers [red] type (b), [blue] type (d) and [pink] type (f) in Table 3.3 with gate inductance of 16 nH                                                                                                                |  |  |  |

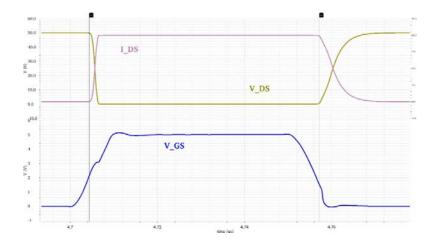

| Figure 3.25  | Cadence Ultrasim schematic simulation of GaN device voltage and current for the resonant gate driver with MOSFET clamp type (f) in Table 3.3 with gate inductance of 16 nH                                                                                                                                                                   |  |  |  |

| Figure 3.26  | Cadence Spectre simulation of a gate driver with a single EPC2001 power load switching at 10 MHz with a resistive load connected to 50 V power supply, [from inside to outside:] conventional gate driver without resonant inductance, resonant gate driver with clamping diodes [38] and resonant gate driver without clamping devices [62] |  |  |  |

| Figure 4.1   | Layout of Under Voltage Lock Out (UVLO) circuit (340 $\mu\mathrm{m}\times120$                                                                                                                                                                                                                                                                |  |  |  |

|              | μm)                                                                                                                                                                                                                                                                                                                                          |  |  |  |

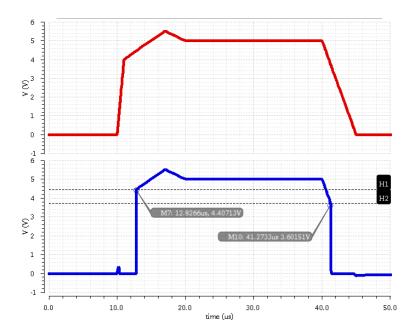

| Figure 4.2   | Extracted simulation of the UVLO in Figure 4.1                                                                                                                                                                                                                                                                                               |  |  |  |

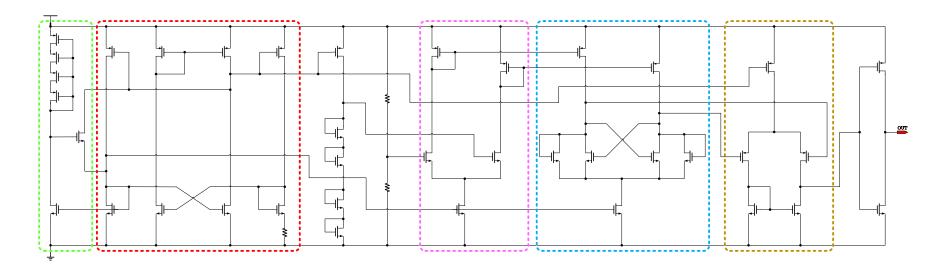

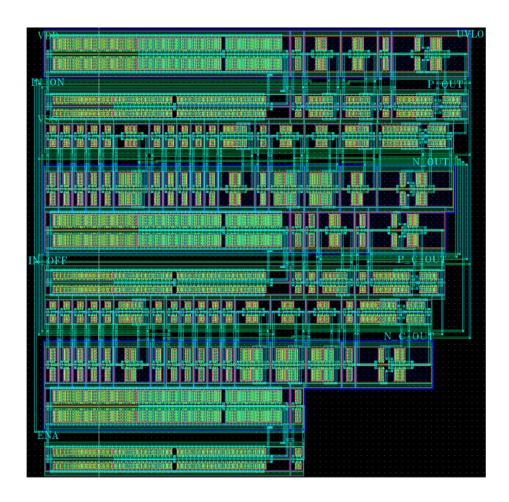

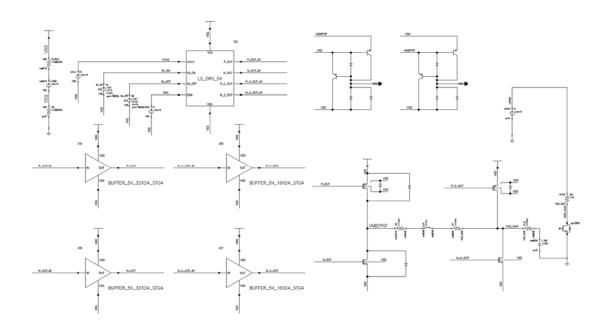

| Figure 4.3   | Layout of the control circuit (360 $\mu m \times 380 \ \mu m$ ) with schematic diagram shown in Figure 3.14                                                                                                                                                                                                                                  |  |  |  |

| Figure 4.4   | Schematic block diagram of Figure 4.3, 4.5 and 4.6                                                                                                                                                                                                                                                                                           |  |  |  |

| Figure 4.5.  | Extracted simulation of the control circuit in Figure 4.4                                                                                                                                                                                                                                                                                    |  |  |  |

| Figure 4.6.  | Extracted simulation of the control circuit in Figure 4.4                                                                                                                                                                                                                                                                                    |  |  |  |

| Figure 4.7.  | Layout of $64\times24(13/1.3)$ PMOS and $64\times24(8/1.6)$ NMOS FET's output buffer block (680 µm × 520 µm)                                                                                                                                                                                                                                 |  |  |  |

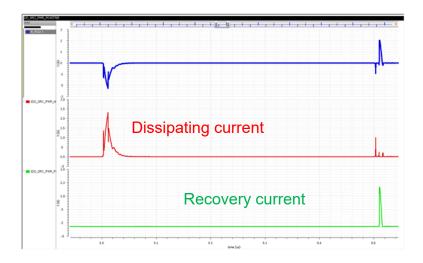

| Figure 4.8.  | Top-level schematic simulation RGD including the control, buffer, driver and output stage with the capacitive load                                                                                                                                                                                                                           |  |  |  |

| Figure 4.9.  | Simulation results of the gate driver power supply current flow in Figure 4.8                                                                                                                                                                                                                                                                |  |  |  |

| Figure 4.10. | Modified charging process from the stage (A) and (B) shown in Figure 3.5                                                                                                                                                                                                                                                                     |  |  |  |

| Figure 4.11. | Simulation current flows for the charging process in Figure 4.1074                                                                                                                                                                                                                                                                           |  |  |  |

| Figure 4.12. | Modified charging process from the stage (C) and (D) shown in Figure                                                                                                                                                                                                                                                                         |  |  |  |

|              | 3.574                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| Figure 4.13. | Simulation current flows for the discharging process in Figure 4.1275                                                                                                     |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

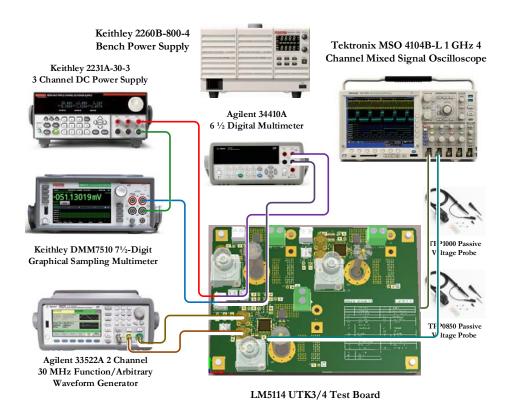

| Figure 4.14. | Test bench setup diagram                                                                                                                                                  |

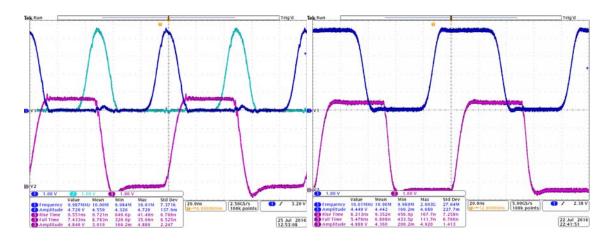

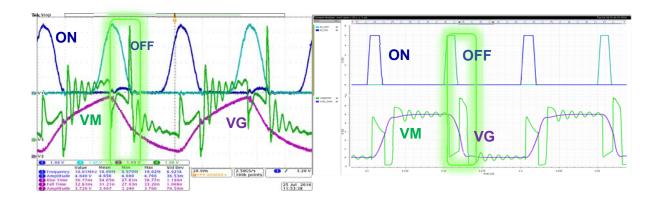

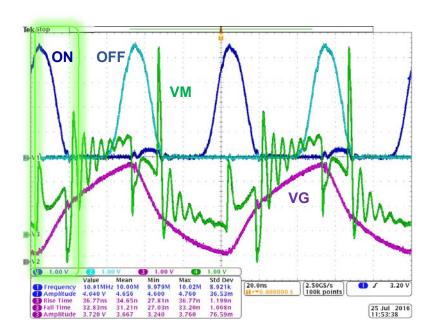

| Figure 4.15. | Measured waveforms for RGD (left) with 11 nH and LM5114 (right) at 1 nF load                                                                                              |

| Figure 4.16. | Measured waveforms for RGD (left) with 11 nH and LM5114 (right) at 2 nF load                                                                                              |

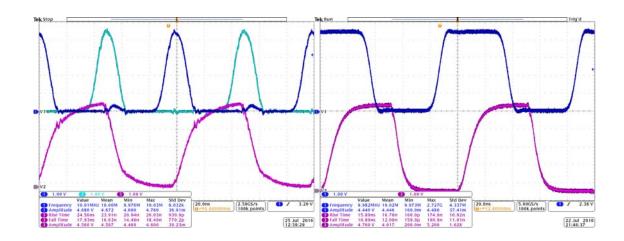

| Figure 4.17. | Measured waveforms for RGD (left) with 11 nH and LM5114 (right) at 3 nF load                                                                                              |

| Figure 4.18. | Measured waveforms for RGD (left) with 11 nH and LM5114 (right) at 4 nF load                                                                                              |

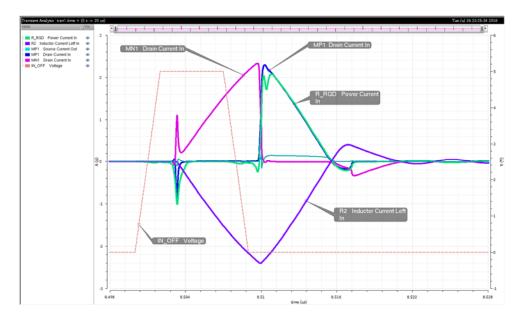

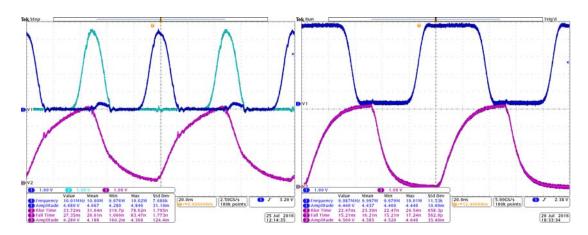

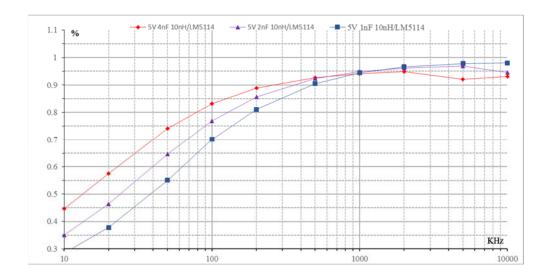

| Figure 4.19. | Measured gate driver power ratio of the RGD with 10 nH to LM5114 with switching frequency from 10 KHz to 10 MHz for capacitive loads of 1 nF, 2 nF and 4 nF               |

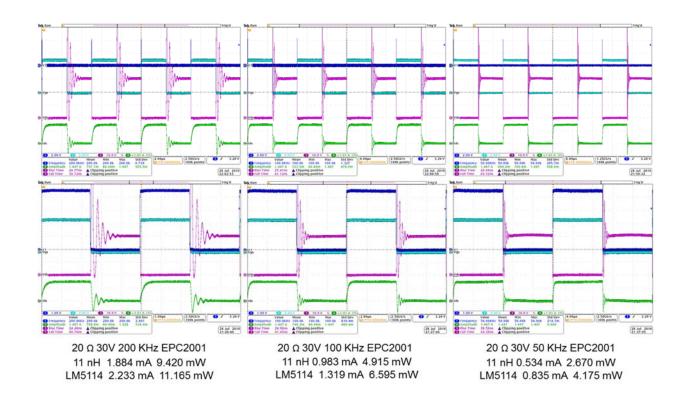

| Figure 4.20. | Captured oscilloscope window of resistive loading for RGD and LM5114 at 200 KHz, 100 KHz and 50 KHz                                                                       |

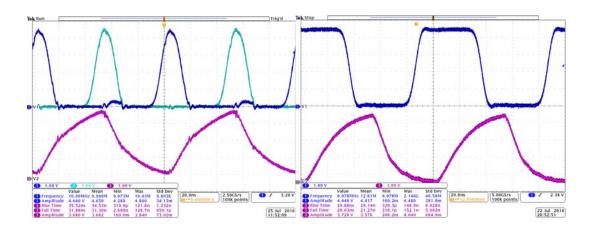

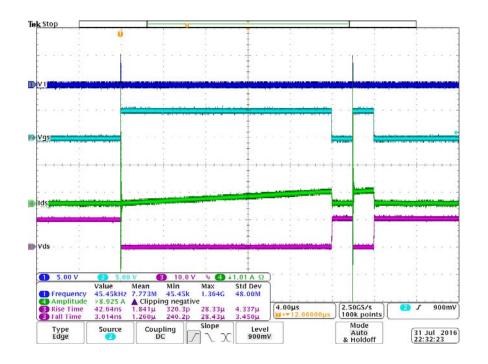

| Figure 4.21. | Measured waveforms of the double pulse test (DPT) of the proposed RGD                                                                                                     |

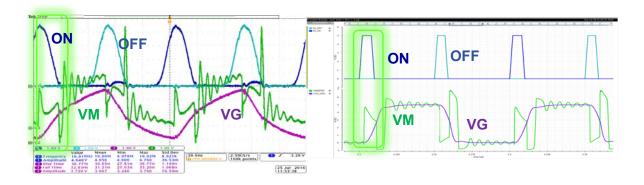

| Figure 4.22. | Measured vs. Simulated waveforms of RGD for 11 nH inductance and 4 nF load capacitance highlighted with turn-on transition                                                |

| Figure 4.23. | Measured vs. Simulated waveforms of RGD for 11 nH inductance and 4 nF load capacitance highlighted with turn-off transition                                               |

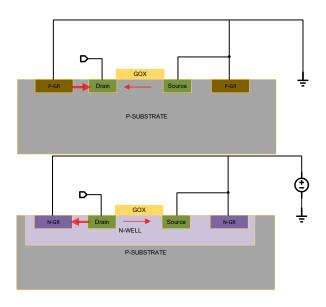

| Figure 4.24. | Cross-section of the body-diode conduction for NMOS MN (left) and PMOS MP (right) during the stage (B) and (D) in Figure 3.4 respectively                                 |

| Figure 4.25. | Simulation results for 10 MHz switching frequency, 16 ns control signals and reduced size of the output devices of the RGD with 11 nH inductor and 4 nF load capacitor    |

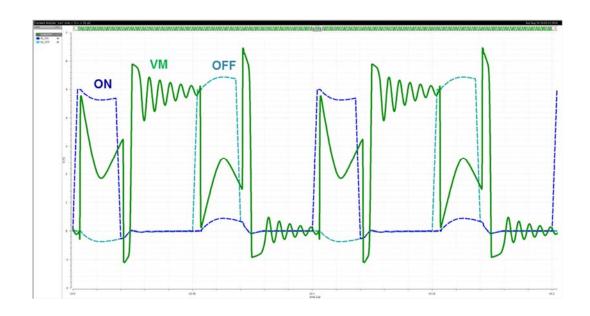

| Figure 4.26. | Measured waveforms for 10 MHz switching frequency, 16 ns control signals and reduced size of the output devices of the RGD with 11 nH inductor and 4 nF load capacitor or |

| Figure 4.27. | Simulation of turn-on transition mid-point voltage ( $V_M$ node of Figure 3.4) with control pulse width of 6 ns and 16 ns for different sizes of output devices           |

| Figure 4.28. | Simulation of turn-off transition mid-point voltage ( $V_M$ node of Figure 3.4) with control pulse width of 6 ns and 16 ns for different sizes of output devices          |

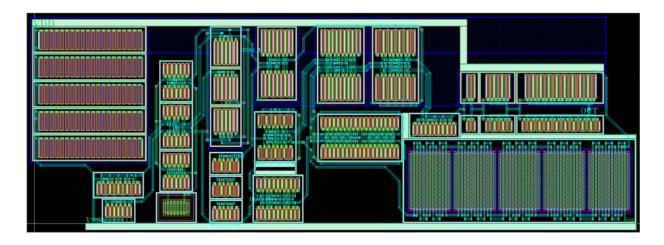

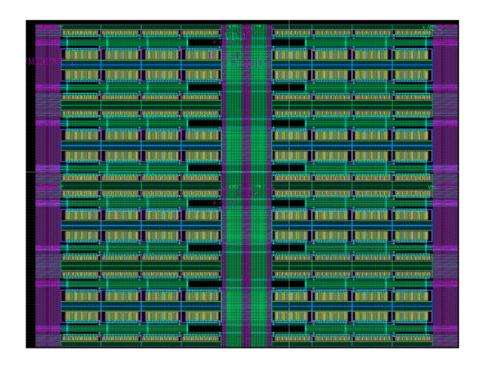

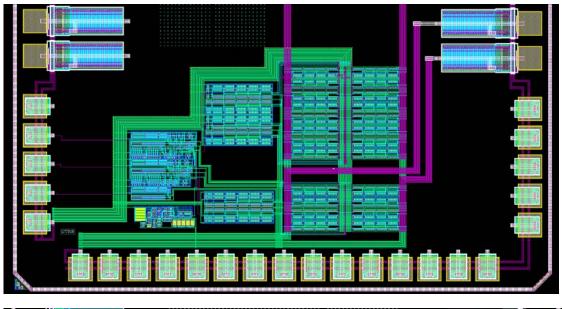

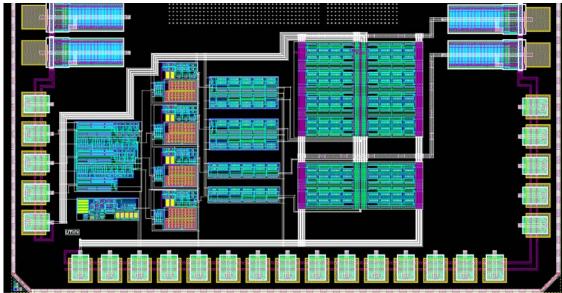

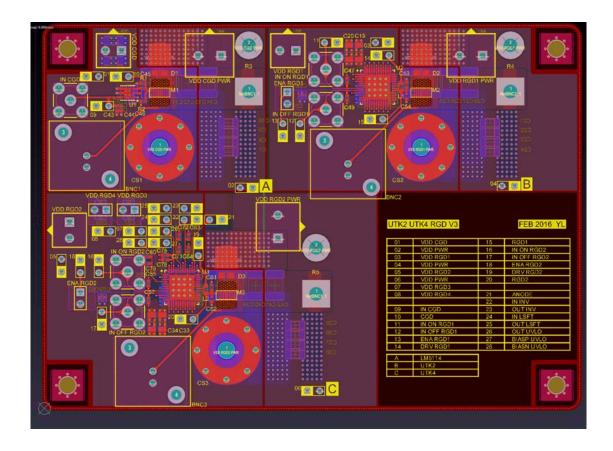

| Figure A.1. | Layout of the resonant gate driver, without level shifter (1600 $\mu m \times$                                                          |      |  |  |  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------|------|--|--|--|

|             | 1100 $\mu\mathrm{m})$ (top) with level shifter (2000 $\mu\mathrm{m}\times1100~\mu\mathrm{m})$ (bottom)                                  | . 94 |  |  |  |

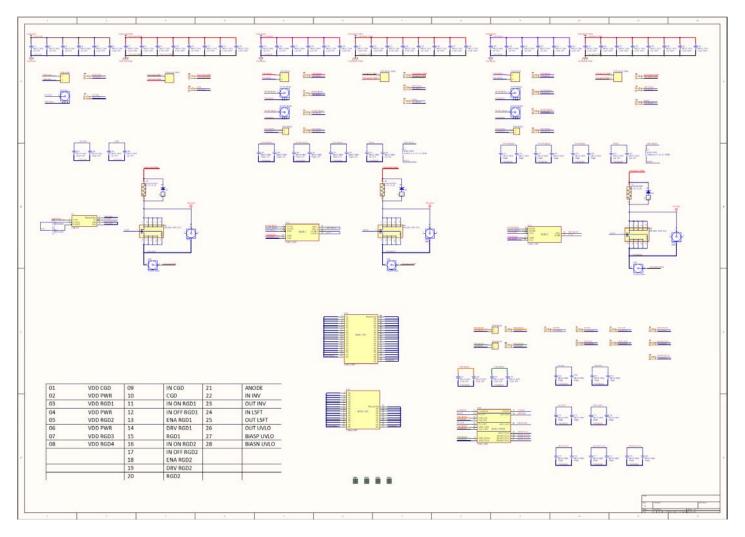

| Figure A.2. | Schematic of the testing PCB                                                                                                            | . 95 |  |  |  |

| Figure A.3. | Layout of the testing PCB $(4.56" \times 3.27")$                                                                                        | . 96 |  |  |  |

| Figure A.4. | 3D view of the testing PCB                                                                                                              | . 96 |  |  |  |

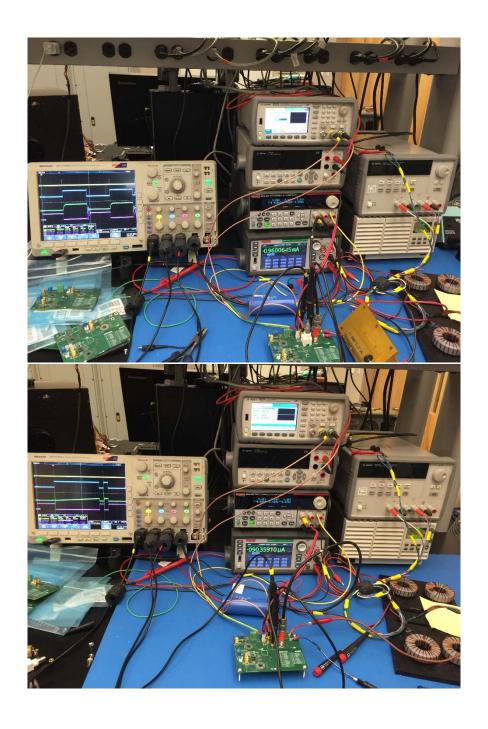

| Figure A.5. | Test bench setup for resistive load (top) and inductive load (bottom)                                                                   | ,    |  |  |  |

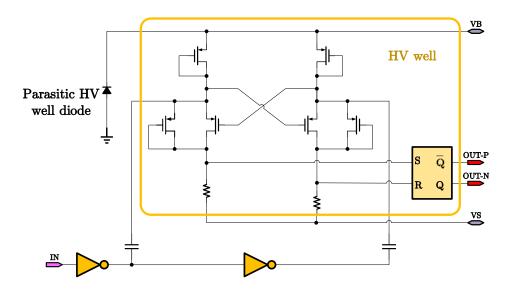

| Figure A.6. | Schematic diagram of the proposed capacitor coupled level shifter circuit                                                               | . 99 |  |  |  |

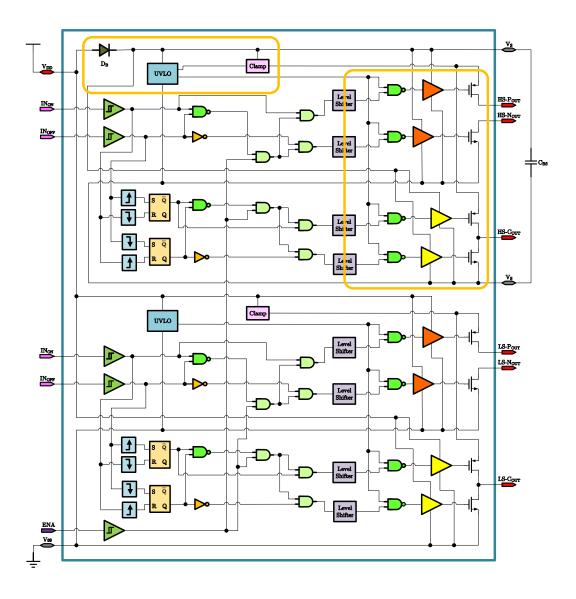

| Figure A.7. | Schematic block diagram of the proposed half bridge resonant gate driver, yellow ring represents high-voltage isolation well (high-side | 100  |  |  |  |

|             | supply clamping DB under investigation)                                                                                                 | TOO  |  |  |  |

## List of Abbreviations

MOS metal oxide semiconductor

FET field effect transistor

MOSFET metal oxide semiconductor field effect

transistor

BJT bipolar junction transistor

HEMT High-electron-mobility transistor

2DEG two dimensional electron gas

GaN Gallium Nitride

SEM scanning electron microscope

FET field effect transistor

SOI Silicon on isolator

ZVS zero voltage switching

ZCS zero current switching

VDMOS vertical diffused metal oxide

semiconductor

LDEMOSFET lateral-drain-extension MOSFET LDMOS laterally diffused metal oxide

semiconductor

RGD resonant gate driver

UVLO under-voltage lock-out

BMR beta multiplier reference

PCB printed circuit board

ESR equivalent series resistance

ESL equivalent series inductance

DRC design rule check

LVS layout versus schematic

PEX Calibre layout parasitic extraction QRC Assura layout parasitic extraction

DPT double pulse testing SMD surface mount device

# Chapter 1

## Introduction

#### 1.1 Background and Motivations

Recently GaN HEMT transistors, which were previously used only in RF and microwave regions since its invention decades ago, have been studied extensively. GaN-based power converters have appeared in power electronics, especially in low power high frequency DC-DC converters in recent years. In the past almost all GaN HEMT power transistors are deletion mode devices, which means normally-on when no voltage is applied at its gate (i.e.,  $V_{\rm GS}=0$  V). This greatly hindered the applications of this type of device in power electronics where a normally-off switch is greatly desired in power electronics. Usually a depletion-mode power device is potentially less reliable than a normally-off one from an applications perspective. It also needs a more specifically designed gate driver and control function since most gate drivers are designed to drive an enhancement mode device.

A breakthrough in processing GaN materials on a silicon substrate commercially made enhancement-mode GaN FETs finally a realistic alternative to conventional Si power devices. In 2009 Efficient Power Conversion Co. (EPC) announced eGaN ® series [1] enhancement-mode, a normally-off GaN HEMT power device. A power converter using GaN HEMT power switches could be as simple as using conventional Si MOSFET switches. Compared with their Si MOSFET counterparts, GaN HEMT power devices have much lower channel resistance due to higher electron mobility, significantly faster switching behavior due to much smaller gate charge and zero reverse recovery charge. However, unlike their Si counterpart, only several GaN gate drivers based on conventional to tem-pole driving topologies are available on the market [2]. The gate driver provided on EPC websites for their eGaN ® series power devices are low-side driver LM5114 and half-bridge driver LM5113 from Texas Instruments. These gate drivers are specially designed for EPC devices. However, these gate drivers are still based on the conventional totem-pole structure working as a push-pull stage that in essence is a RC charging or discharging process. For a complete RC gate charging and discharging process, all power will be finally dissipated through resistance. All gate charge accumulated on device gate during turning-on period will be finally dissipated to ground during the turning-off interval. If the switching speed of the gate driver continues increasing, the loss of the gate driver will increase as well. For GaN power devices expecting to be able to work at several MHz or even higher, the loss of the gate driver itself will be a limiting factor for their high-frequency applications.

To fully explore the advantages of GaN HEMT power devices, resonant gate driving techniques are a potential solution. However, currently there is no GaN gate driver IC designed for resonant gate driving conditions. The previously reported resonant gate driver for GaN devices using off-chip clamping diodes to implement resonant gate driving is not realistic for EPC eGaN devices and existing GaN gate drivers. Adding clamping diodes at the gate of EPC devices will significantly alter the working conditions of the GaN HEMT devices. Resonant gate drivers for customized depletion mode GaN devices have been reported but there is no resonant gate driver IC reported for enhancement mode GaN devices, such as commercial EPC eGaN series devices.

## 1.2 Objectives

As the maturity of GaN HEMT power devices continues growing, we can expect more and more gate drivers designed for this new type of power devices. This document is one of the efforts to design a new type of gate driver IC for EPC eGaN power device. The objective of the proposed work is to realize a resonant gate driving topology for eGaN devices (EPC2001 as an example), design a gate driver IC to support this topology and implement the proposed gate driving technique and compare the customized gate driver IC with the existing commercial gate driver ICs for EPC eGaN devices. By varying the resonant inductor and changing the driving sequences, the proposed resonant gate driver can work in different resonant driving conditions, or even the same way as the conventional gate driver. A more power efficient and more flexible gate driving technique is the purpose of this research work.

#### 1.3 Contributions

The proposed research work is to make contributions in the following aspects.

- Propose a new resonant gate driving topology for enhancement mode GaN HEMT power devices (EPC2001 selected as an exmaple), meeting different resonant conditions by adjusting driving control signals without hardware re-design or re-programming.

- Design a new low-side resonant gate diver IC for EPC eGaN HEMT power devices in a standard CMOS process.

- Experimentally compare the switching frequency, power consumption and driving waveforms between the commercial gate driver LM5114 and customized resonant gate driver.

- Based on the experimental results and analysis on the proposed resonant gate driver design, provide guidance for future design.

#### 1.4 Organization

This dissertation includes five parts. The first part is the introduction. It introduces the research background, motivations, objectives and contributions. Chapter 2 describes the GaN HEMT power devices and two associated gate driver topologies – conventional and existing resonant gate drivers. The limitations of these driver techniques are presented at the end of the chapter. The proposed work is in Chapter 3. First, a low-side resonant gate driving scheme using the proposed resonant structure is described. Then a half-bridge gate driver IC design using the same structure is proposed. Design blocks revealed and simulation results verified the proposed structures. Chapter 4 gives the experimental results. Finally, Chapter 5 is for conclusion and future work. After the conclusions in Chapter 5 the Appendix section includes some supplement materials such as customized IC and PCB layouts. The literature citations are listed in the References section.

# Chapter 2

# High-frequency Resonant Gate Drivers for Power Devices

#### 2.1 Introduction to GaN HEMT Devices

To describe a Si MOSFET conduction, we have to consider a mechanism called "channel inversion" in a lightly doped Si substrate. Likewise, for a GaN HEMT (High-electron-mobility transistor) device, we must know the mechanisms of so called "two-dimensional electron gas", or 2DEG in short. The phase 2DEG refers to the condition where the electrons have quantized energy levels in only one spatial direction, often perpendicular to the interface, but often have extremely high mobility to move free in the other two dimensions, often parallel to the interface. Generally speaking, bringing an n-type wide band gap semiconductor layer in touch with a narrow band gap semiconductor layer will lead to a band bending in the conduction band of the narrow band gap semiconductor. In this way, a triangular well is formed, in which the transferred electrons are confined and form a two dimensional conductive channel, or 2DEG [3].

The phenomena of confining electrons along a surface may be tracked back to as early as the 1950's [4]. In 1964 Dr. W. T. Sommer demonstrated a layer of charge on the surface of liquid helium [4]. In the experimental chamber the electron discharged by an ion source with dc voltage applied was confined in an energy barrier of liquid helium. No later than 1987, the 2DEG electron layer in solid semiconductor materials was realized by a heterojunction supperlatice between n-type AlGsAs and intrinsic GaAs by Dr. Dingle and his team at Bell Laboratories [5]. The invention of the HEMT based on an AlGaAs and GaAs heterojunction structure was contributed to Dr. T. Mimura at Fujitsu Laboratories in 1979 [6]. He realized the control of electrons in that superlattice by a Schottky gate contact over a single AlGaAs/GaAs heterojuntion. In 1981 Dr. T. Mimura and his teams successfully fabricated and tested the first HEMT IC [7]. In the next few years, the AlGaAs/GaAs HEMT was successfully commercialized and first used in a LNA (Low Noise Amplifier) for radio

telescope detection [8].

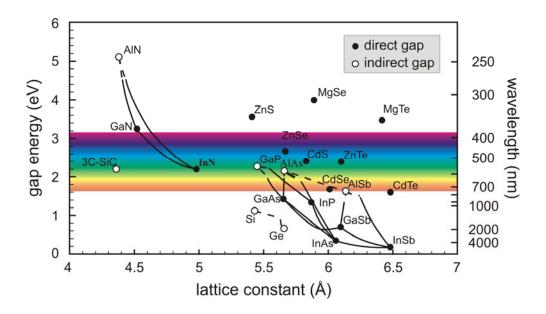

Similar to the AlGaAs/GaAs heterojunction structure made from III-V compounds, the AlGaN/GaN heterojunction has its unique advantages. Firstly, as shown in Figure 2.1 [9] the bandgap energy versus lattice constant for numerous III-V compound materials, the bandgap energy for GaN is 3.4 eV, while GaAs is only 1.42 eVas shown in Table 2.1. Considering 1.12 eV for popular Si and 3.2 eV for SiC, 3.4 eV of GaN is a wide bandgap material. This results in much higher breakdown voltage and higher operational temperature, which is attractive for power electronics. Second, large lattice and large conduction band mismatch between AlN and GaN leads to a spontaneous polarization at the interface and a piezoelectric field in AlN [6]. A deeper quantum well formed in GaN at the edge leads to a very high sheet electron charge density in GaN interface, this formed structure creates a better 2DEG characteristics than conventional GaAs heterojunction. To the device perspective, this means a smaller size, less parasitic effects and higher operating frequency. A power device based AlGaN/GaN HEMT structure could be very attractive for today's high-frequency switching power applications.

Figure 2.1. Bandgaps of the most important elemental and binary cubic semiconductors versus their lattice constant at 300°K [6].

The first AlGaN/GaN HEMT demonstrated by Dr. Asif Khan and his group in 1994 [10] was fabricated on sapphire substrate [11]. Then years later AlGaN/GaN HEMT grown on SiC substrate was reported [12] [13] and currently SiC is the substrate of choice for the epitaxial growth of high-

performance GaN HEMT devices with a thermal conductivity an order of magnitude greater than that of sapphire [14]. In the last decade or two, there has been a trend shift from the AlGaAs/GaAs HEMT to AlGaN/GaN HEMT. Currently the HEMT devices since its invention has been mostly used in microwave, high frequency low power applications. There are three potential substrate material for AlGaN/GaN structure, sapphire, SiC and Si. The sapphire substrate has poor thermal conductivity and large lattice mismatch to GaN. Expensive SiC has lower lattice mismatch and high thermal conductivity. Si substrate offers the the best trade-off considering the cost. Growing AlGaN/GaN heterojunction on Si substrate is one of the reasons hindering further expansion of this new device. Another obstacle for the application of AlGaN/GaN HEMT in power electronics is the difficulty of making a good enhancement mode device, which is especially preferred in power electronics.

Table 2.1: Material properties of Si, GaAs, SiC and GaN at 300°K [15] [16].

| Properties                   | Unit                       | Si   | GaAs | SiC-4H | GaN          |

|------------------------------|----------------------------|------|------|--------|--------------|

| Bandgap energy               | ${ m E_G~(eV)}$            | 1.12 | 1.42 | 3.2    | 3.44         |

| Breakdown voltage            | ${ m E_{BR}} \  m (MV/cm)$ | 0.3  | 0.4  | 3.5    | 3.3          |

| Electron saturation velocity | $ m V_S~(10^7~cm/s)$       | 1.0  | 1.8  | 2.2    | 2.5          |

| Electron mobility            | $\mu  ({ m cm^2/Vs})$      | 1450 | 8000 | 950    | 400 → 2000 ¹ |

| Thermal conductivity         | k (W/cmK)                  | 1.5  | 0.55 | 5      | 1.3          |

There are mainly two solutions to realize an enhancement-mode power GaN FET device without losing the outstanding characteristics of the inherent depletion mode GaN 2DEG channel. One method is directly fabricating a depleted channel from the 2DEG layer. This method is adopted by EPC [1] and Panasonic [17]. Another way is to cascode an enhancement-mode Si MOSFET to the depletion-mode GaN HEMT. Transphorm [18] and International Rectifier (IR) [19] have this cascaded type high voltage GaN power transistor. Due to the processing limits, the most reliable direct enhancement-mode device is targeted to 100 V or below applications while a cascaded version can easily work at 400 – 600 V conditions. In 2013, Panasonic announced its 600 V GaN power transistor using its Gate Injection Transistors (GIT) techniques with 15 A drain

$<sup>^1</sup>$  The 2DEG increases the electron mobility of GaN from 400 to above 2000  $\rm cm^2/Vs.$

current and 1.2 V threshold voltage [20].

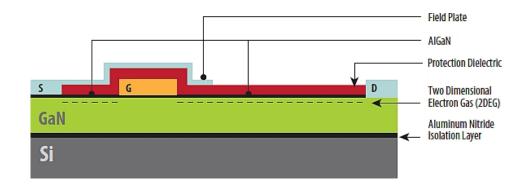

In June 2009 EPC, announced the first enhancement mode wide bandgap AlGaN/GaN HEMT grown on Si substrate and fabricated with standard Si manufacturing technology and facilities [21]. The eGaN ® FET named by EPC is targeted in the open market as a replacement for the traditionally Si power MOSFET widely used in low voltage applications. Figure 2.2 shows the GaN FET cross-section structure [2]. The GaN materials are grown on a seed layer of AlN that is grown on a Si substrate. The 2DEG charge layer is formed between the thin AlGaN and GaN layer at the AlGaN side, but the region below the gate is depleted of free electrons. So the whole channel is partially depleted to have the enhancement mode gate threshold voltage without sacrificing the benefit of high mobility of 2DEG.

Figure 2.2. EPC eGaN ® FET structure [2].

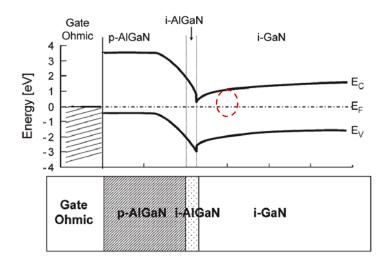

There are several techniques to shift the negative threshold voltage associated with conventional depletion mode AlGaN/GaN HEMT devices to a positive threshold voltage. One of the methods called "gate injection transistor" is to use a p-type AlGaN named crapping layer beneath the gate electrode [22]. The p-type material injects holes into the AlGaN/GaN interface, lifts up the potential of the channel and depletes the 2DEG. Figure 2.3 shows a p-type to intrinsic AlGaN layers grown in a GaN layer to deplete 2DEG on the GaN side. However, one drawbacks of this structure is the gate to channel isolation is depends on thin layers of p-AlGaN and i-AlGaN. The p-type material and n-type conduction channel forms a diode-like structure. This means the enhancement mode GaN HEMT is very sensitive to gate voltage. A small overvoltage on  $V_{\rm GS}$  could forward the gate-channel diode and destroy the device under high power conditions. Even though EPC did not disclose their techniques to manufacture an enhancement mode GaN device, the characteristics provided on the EPC datasheet illustrate the p-type hole injection or similar behavior.

Figure 2.3. A p-AlGaN and i-AlGaN heterojuction implemented by gate injection transistor (GIT) displayed a depleted 2DEG for enhancement-mode operation [21].

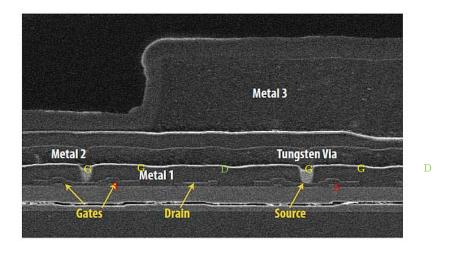

The cross-section of an EPC eGaN FET is shown in Figure 2.4 [2]. Each lateral FET cell is laid on the GaN bulk material with inter-digitated layout pattern as "... G S G D G S G D ...". The source nodes from each cell are routed to Metal 2 as in the graph. All these terminals are finally routed to top metal layers to the pads on the package. The characteristics associated with the electronic properties of the device will be described later in the gate driver design section.

Figure 2.4. SEM micrograph of an EPC eGaN FET [15].

#### 2.2 Conventional Gate Drivers for Power MOSFET's

Normally in power electronics applications the control signals are provided by a DSP, FPGA or other microcontroller IC's with voltages of 5 V, 3.3 V or even lower. Very few power devices can be directly driven by these digital signal outputs. An intermediate circuit is needed to convert the low power signals to drive the power switches. The gate driver IC is this circuit used to generate the voltage or current necessary to turn a power MOSFET, IGBT, or other semiconductor power switch on and off. For GaN HEMT FET, the gate driver IC is also needed.

The basic functions of a gate driver IC mainly include three aspects.

- Provide sufficient current/voltage control signals for power switching devices.

- Provide isolation or protection for control IC's from the large signal swings of the power switching devices.

- Provide protection for power switching devices under certain conditions.

There are possibly thousands of gate driver IC's for power devices on the market. Since the normally-off GaN HEMT is very similar to the conventional power MOSFET, which is also a voltage controlled threshold and capacitive induced channel device, we also call the GaN HEMT simply a GaN FET. Usually commercial FET gate drivers are based on the same topology called "totem-pole" structure for minimum transition time [23] [24] [25]. Figure 2.5 shows the simplified conventional "totem-pole" output stage driving a power MOSFET. The inverter-like  $M_P$  and  $M_N$  is the PMOS and NMOS transistors of the "totem-pole" respectively. The gate of the PMOS and NMOS are tied together to achieve fastest transient response. The drain nodes of the two transistors are connected together to form a push-pull output. Turning on the PMOS in the "totem-pole" will charge the output node and pull up the output potential to turn on the power device. Turning on the lower NMOS, the output node will be discharged below the threshold voltage of the FET device.

Among those thousands of various gate driver IC's, only three gate drivers from Texas Instruments — LM5113 [26], LM5114 [27] and UCC27611 [28] are listed on EPC website for the GaN FET's. Some other MOSFET gate drivers such as the ISL2110 [29] series from Intersil can also be used, but they are not specifically designed for EPC eGaN ® FET's. All of them have a "totem-pole" output structure with split pull-up and pull-down output pins. Figure 2.6

shows the block diagram of the LM5113 in which both high side and low side have the same "totem-pole" output [27].

Figure 2.5. A simplified "totem-pole" output stage for a conventional power MOSFET driver.

Figure 2.6. Block diagram of LM5113 [19].

To design a gate driver, we need to understand the power loss mechanisms for a "totem-pole" gate driving topology. Some literature defines the switching loss of output transistors and gate resistor loss separately [30], but they are all essentially due to capacitive loss. In this work we define three types of power losses associated with the gate driver push-pull process.

- Static power loss  $P_S$

- Dynamic capacitive power loss  $P_C$

- Dynamic short-circuit power loss  $P_{SC}$

The total gate driver power loss  $P_{GD}$  is the sum of the three types.

$$P_{CD} = P_S + P_C + P_{SC} \tag{2.1}$$

Figure 2.7. Gate charge versus Gate-source voltage for EPC2001 [30].

Static power loss is essentially due to transistor leakage current at its quiescent condition. There are two main sources of leakage, gate-channel leakage during turn on and drain-source leakage during transistor turn off. Other leakage like substrate leakage is common to all non-SOI (Silicon on Isolator) technologies [3]. Leakage loss usually is very small and can be neglected [3]. However, as temperature increases, leakage loss will increase dramatically [31].

Dynamic capacitive loss happens during the process of charging and discharging of load or any node capacitance on the drive signal path. Usually the load capacitance, which is the power device's effective gate capacitance, is much larger than other node capacitance. The Miller effect and other junction parasitics contribute to the nonlinearity of the device gate capacitance during operation. Figure 2.7 shows the gate charge versus gate voltage diagram for EPC2001 [32] as an example. Based on gate charge curve, the detailed loss analysis can be approximated by assuming a piecewise linear waveform and adding up three sections of loss during gate charging and discharging cycles [30].

However, a more systematic view can greatly simplify this analysis. Assuming the charging and discharging time is long enough such that the gate of the power device can be charged to the driver supply voltage and discharged to the ground potential, no matter what kind of resistance or nonlinear channel resistance there is, all the energy provided by the power supply will be dissipated during a complete switching cycle. Supposing the charge provided by driver supply without any leakage to the gate is  $Q_g$ , and the driver supply voltage is  $V_D$ , then the energy provided by the gate driver supply during a complete switching cycle is

$$E_{CG} = Q_{\sigma} V_{D} \tag{2.2}$$

The energy supplied to the gate in each switching cycle is  $E_G$ . The power loss is simply the energy times the switching frequency, where  $C_G$  is the equivalent gate capacitance during the switching, normally larger than the static input capacitance given as  $C_{ISS}$  in the datasheet. Even though during the charging and discharging process there is a switching loss of the driving transistors themselves, while the transistor is in a saturation mode with resistance value significant larger  $R_{DS(on)}$ , the equation (2.3) has already includes this portion of loss. Some report this switching loss separately [30], but from the view of the overall loss of the gate driver, the loss due to the driving transistors is not necessary to be accounted repeatedly.

$$P_{CG} = Q_{g} V_{D} f_{sw} = C_{G} V_{D}^{2} f_{sw}$$

(2.3)

The above equation shows that as switching frequency  $(f_{sw})$  increases, dynamic capacitive power loss will certainly increase. Normally the output stage consists of several stages of ratioed "totem-pole" structure. If we assume an optimal stage effort of four [33], then the total capacitive loss including a chain of stages before the final output stage can be approximately expressed as

$$P_{CG}' \simeq \left(1 + \frac{1}{4} + \frac{1}{16} + \dots\right) Q_g V_D f_{sw} = \frac{4}{4 - 1} Q_g V_D f_{sw} \simeq 1.34 C_G V_D^2 f_{sw}$$

$$(2.4)$$

Another portion of capacitive power loss for the gate driver is associated with the output parasitic capacitance of PMOS and NMOS FET's in the "totem-

pole" the gate driver. Since each PMOS and NMOS FET in an inverter has to charge the output capacitance to  $V_D$  during the turn-on stage and short it to ground during the turn-on stage, this portion of charge is completely dissipated during each switching cycle. The output parasitic capacitances associated with gate driver output stage are  $C_{Poss}$  and  $C_{Noss}$ , then gate driver dynamic output capacitive power loss is

$$P_{COSS} = \left(C_{Poss} + C_{Noss}\right) V_D^2 f_{sw} \tag{2.5}$$

Considering the inverter chain as a whole, the gate driver dynamic output capacitive power loss is

$$P_{COSS}' \simeq 1.34 (C_{Poss} + C_{Noss}) V_D^2 f_{sw}$$

(2.6)

Short-circuit power loss, or shoot-through power loss, happens during the transition of the upper PMOS FET and lower NMOS FET of the "totem-pole" structure. This is the same as a CMOS inverter behaves like a linear amplifier when both transistors are in the linear or saturated region [34]. This dynamic loss is unavoidable since we cannot have an ideal infinitely sharp transition region for the output stage. A portion of charge provided by the gate driver power supply has to be bypassed directly to ground without being routed to the gate of the power device. Even though short-circuit power loss is relatively much smaller than the capacitive loss, as switching frequency increases, this portion of loss also increases.

Figure 2.8. A CMOS inverter DC characteristics showing the dynamic short-circuit power loss. On the left is the output voltage vs. input voltage, on the right is the output current versus input voltage. "B", "C" and "D" means

the region where PMOS or NMOS is in linear or saturated region [26].

The short-circuit power loss can be estimated by a piecewise linear triangle approximation of the current waveform shown in Figure 2.8. Assuming the inverter-like "totem-pole" has a piecewise linear input slope, the short-through current is also a triangle waveform [35]. If the inverter equivalent transition time for pull-up or pull-down is  $t_{sc}$ , the peak short-circuit current is  $I_p$ , then short-circuit energy dissipated directly to ground is approximately [35]

$$E_{SC} = \frac{1}{2} V_D I_p t_{up} + \frac{1}{2} V_D I_p t_{down} = V_D I_p t_{sc}$$

(2.7)

Then the short-circuit power loss is

$$P_{SC} = V_D I_D t_{SC} f_{SW} \tag{2.8}$$

Similarly, consider an inverter chain of stage effort of four, the total short-circuit loss is estimated as

$$P_{SC}' \approx 1.34 V_D I_D t_{SC} f_{SW} \tag{2.9}$$

The dynamic short-circuit power loss is related to peak short-circuit current and transition time. There is a trade-off between the two parameters. Increasing the inverter PMOS and NMOS transistor sizes will increase the peak current and reduce the transition time. Increasing the inverter load capacitance will reduce the peak current but increase the transition time. The least short-circuit power loss depends on the sizes of the "totem-pole" output transistors and the gate capacitance of the power devices. A conventional gate driver will have least short-circuit power loss while driving for a specific power device loading condition. Changing the loading condition will increase short-circuit power loss and lower the gate driver power efficiency.

Based on the analysis above, the gate driver power loss for a conventional gate driver with four stages output and stage effort ratio of four can be expressed as

$$P_{GD} \approx 1.34 \left[ \left( C_G + C_{Poss} + C_{Noss} \right) V_D^2 + V_D I_p t_{sc} \right] f_{sw}$$

(2.10)

#### 2.3 Resonant Power MOSFET Gate Drivers

A resonant gate driver has been proposed decades ago. One of the mostly cited pioneering literature on the resonant gate driver was written by Dr. Maksimovic during the early 90's [36]. Since that paper, the most important characteristics of resonant gate drivers has not changed. Unlike the conventional "totem-pole" driving scheme, the gate driving energy is completely dissipated in the resistance during the process of charging and discharging the gate of a power MOSFET device. Given that this is an equivalent RC network, the only way to apply and remove the capacitive charge during a signal transition cycle is to dissipate the charge completely via a resistive element to ground. Resonant gate driving implements the charging and discharging process by a LC resonant network. For an ideal lossless network, the capacitive energy will resonate with the inductive energy, which means no loss occurs during a complete cycle. A resonant gate driver implements a quasi-square-wave voltage applied at the gate of a power device by employing a resonant process during the conventional charging and discharging process.

The driving forces of proposing a relatively new resonant gate driving topology rather than conventional "totem-pole" output driving stage can be contributed to two main aspects. Firstly, as switching frequency keeps increasing for power converters, gate driving loss is also proportionally increasing. In the past, this portion of power loss was often times negligible compared with the switching loss and conduction loss of the power devices. Today, for low power DC-DC converters, several MHz switching frequency is normal, and gate driving loss is by no means negligible. Second, soft switching techniques, such as zero-voltage-switching (ZVS) [31] and zero-current switching (ZCS) [31], are getting more and more popular. The switching loss of the power switches in the power loop has been reduced. However, soft switching can result in more circulating current, which leads to higher conduction loss. To reduce the conduction loss, devices with lower  $R_{ds(on)}$  are preferred. Normally there is a trade-off between the  $Q_g$  and  $R_{ds(on)}$ . The power MOSFET Figure-of-Merit (FOM,  $FOM = Q_g R_{ds(on)}$ ) [2] suggests this. A lower  $R_{ds(on)}$  normally means a higher  $Q_g$  for a given device technology at a given voltage rating. A higher  $Q_g$ will need a larger gate driver capability, such that a higher gate driving loss will be consumed if a conventional gate driver is still in use. So resonant gate driving techniques are developed to reduce the gate drive loss while allowing the increase of switching frequency or the device gate input capacitance.

Here we listed several candidate resonant gate drivers developed so far for detailed review. All of them are designed to drive a single power device as load. Other types of resonant gate drivers, especially those driving two MOSFET's with transformer coupled techniques, which is not suitable for low power applications and IC integration, will not be discussed in detail. Also, for low power applications, for power MOSFET or GaN HEMT, both of them can be treated as a non-linear gate capacitance to the gate driver. So the gate drivers discussed here are all capacitance loaded gate drivers.

### 2.3.1 Resonant Gate Driver - Topology A

Figure 2.9. A resonant gate driver using extra resonant inductor and capacitors [34].

Figure 2.9 shows a resonant gate driver proposed by Dr. Maksimovic in the early 90's [34]. The operation principle of the above resonant gate driver can be explained with the waveform diagram in Figure 2.10. The equivalent capacitance connected to net " $v_x$ " is much larger than the power device input capacitance  $C_G$ , such that the resonant conductor current can be approximated as triangle wave. Furthermore, if we assume an ideal lossless resonance and ideal timing condition, the resonant current will flow back and forth with the same amplitude. When p-channel FET  $M_P$  is turned on, the current  $i_{Lr}$  increases linearly, from the negative peak current  $-I_{Lr}$  to the positive peak current  $+I_{Lr}$ . Then  $M_P$  is turned off, the positive peak current will discharge the gate input

capacitance  $C_G$ . The gate charge energy will be ideally transferred to energy stored in the equivalent capacitance of  $C_I$  and  $C_2$ . As the gate capacitance is discharged to ground potential, the n-channel FET  $M_N$  is turned on, the inductor current  $i_{Lr}$  decreases linearly, from the positive peak current  $+I_{Lr}$  to the negative peak current  $-I_{Lr}$ . Then  $M_N$  is turned off, the negative peak current will charge the gate input capacitance  $C_G$  to the desired turn-on voltage, the gate driver supply voltage  $V_D$ . Then repeatedly,  $M_P$  is turned on again and  $i_{Lr}$  increases linearly.

Figure 2.10. Simplified steady state waveforms of the gate driver in Figure 2.9, from top: driver output PMOS  $M_P$  gate voltage  $v_p$ , driver output NMOS  $M_N$  gate voltage  $v_n$ , resonant inductor  $L_r$  current  $i_{L_r}$  and power device gate G voltage  $v_g$ .

The resonant gate driver showed in Figure 2.9 is essentially adding an extra resonant inductor and load capacitor to the "totem-pole" gate drive output to form an unloaded ZVS quasi-square-wave buck converter [37]. The most significant advantage of this resonant gate driver is the realization of the ZVS switching of the gate driver output transistors. However, it suffers other problems. Firstly, a significant larger resonant capacitance than the power device gate capacitance is necessary to maintain a triangle wave like inductor current. This could be costly to integrate on chip. Secondly, a separate inductor is needed to form the gate resonant loop. The inherent parasitic gate inductance cannot be incorporated into this inductor. Thirdly, a large continuous current flows through the LC resonant loop. The parasitic loop resistance, especially the

equivalent series resistance (ESR) of the inductor, will give rise to conduction loss.

## 2.3.2 Resonant Gate Driver – Topology B

Figure 2.11 shows another resonant gate driver published in 2002 [38]. This topology utilizes the gate inductance to form the charging or discharging by LC resonance. The simplified steady-state waveforms of control logics, inductor current and device gate voltage are shown in Figure 2.12. Assume the gate capacitance of power device  $C_G$  has been discharged to the lowest negative potential  $V_{p}$ , while  $M_N$  is on and  $M_P$  is off. The diode blocks the reverse flowing current with voltage of  $V_p$ . Then a rising edge of control signal drives  $M_P$  to turn on and  $M_N$  to turn off. A positive gate driver voltage  $V_D$  is applied across the series resonant tank composed of inductor  $L_r$  and device capacitance  $C_G$ . The  $C_G$  will be charged to its positive maximum potential  $V_{p+}$  through  $M_P$  and  $D_{I}$ , given the resonance is longer than a half period. The charging current will be a positive half sinusoidal waveform. The negative discharging current of a normal resonant cycle is automatically blocked by the series diode,  $D_I$ . The device  $C_G$  potential will be maintained at  $V_{p+}$  until a falling edge of control input signal occurs. At this moment, the device gate potential will be discharged through inductor  $L_r$ ,  $D_2$  and  $M_N$ . The inductor current will go through the negative half sinusoidal cycle to discharge the gate capacitance to the minimum potential of  $V_{p}$  and maintain this gate voltage level by the reversely blocking of  $D_2$ .

Figure 2.11. A resonant gate driver using gate inductor and reverse blocking diodes in series [36].

Figure 2.12. Simplified steady state waveforms of the gate driver in Figure 2.11, [from top:] driver control input IN voltage, resonant inductor  $L_r$  current and power device gate G voltage [36].

Compared to the gate driver with resonant transition [39], this resonant gate driver does not require a separate capacitance to assist gate resonance. The resonant inductor can be implemented by the parasitic inductance between the gate driver output and device gate input, or even possibly integrated on chip. Another advantage of this gate driver is the lower gate driver supply voltage. A resonant condition can make the positive charged gate voltage much higher than the gate driver voltage supply. This could be attractive for high gate voltage devices. However, for the current enhancement mode power GaN HEMT's, the optimum gate turn-on voltage is around 5 V or even less, further lowing the gate driver supply beyond that level will only create complexity by requiring an extra supply. Since the gate voltage completely relies on the exact values of resonant components, the desired gate turn-on and turn-off levels need carefully turned to these values. For example, if the minimum negative swing needs to be 0 V, the author recommended to increase the resonant capacitance by series capacitor, and a clamped Zener diode in parallel with the device gate input. To control the desired maximum positive gate voltage independently, the resonant inductor has to be split separately for the charging and discharging path, such that their resonant process can be controlled separately. All these problems make this solution not applicable to the desired gate driving for highfrequency switching with GaN HEMT's.

### 2.3.3 Resonant Gate Driver – Topology C

Even though the research on the resonant gate driver can be traced back to 1980's, the widespread interests on this topic started early this century. Among these papers published during that period, one of the most typical resonant gate driver papers proposed by Dr. Chen brought up the implementation of resonant gate driver "energy recovery" [40] [41] rather than the previous ideal "lossless" approach [34] [36]. Figure 2.13 shows the proposed resonant gate driver topology [38] [39]. We need to assume the Q factor of the resonant circuit is large enough such that an ideal resonance can be approximated.

The approximated waveforms are shown in Figure 2.14. The shaded area is the turn-on period of PMOS and NMOS driver switches. The highlighted portion of current is the actual charging and discharging gate current.

Before time  $t_{\theta}$  the gate capacitance of power device  $C_G$  has been discharged completely to ground, and both  $M_N$  and  $M_P$  are off. The turn-on and turn-off process can be divided into the following four intervals.

Figure 2.13. A resonant gate driver using gate inductor and gate clamping diodes in parallel [38] [39].

#### 1) $L_r$ resonant charge interval $t_0$ - $t_1$ :

At time of  $t_0$  a negative pulse on  $IN_P$  turns on the switch  $M_P$ , a positive current  $i_{L_r}$  will flow from the driver supply  $V_D$  through the resonant inductor  $L_r$  to charge the gate capacitance  $C_G$ . If the turn-on period of  $M_P$  is long enough, the gate capacitance  $C_G$  will be charged beyond gate driver voltage  $V_D$ . Due to

the paralleling diode  $D_I$ , the gate voltage will be clamped at  $V_D$  starting from  $t_I$ .

Figure 2.14. Simplified steady state waveforms of the gate driver in Figure 2.13, [from top:] gate driver PMOS  $M_P$  gate control voltage  $v_p$ , NMOS  $M_N$  gate control voltage  $v_p$ , resonant inductor  $L_r$  current  $i_{Lr}$  and power device gate G voltage  $v_g$  [38] [39].

#### 2) $D_1$ clamping and recovery interval $t_1$ - $t_2$ :

During the interval  $t_I$  -  $t_2$  the gate voltage clamping the inductor current will keep constant or clamped at its peak value via the freewheeling loop of  $M_P$ ,  $L_r$  and  $D_I$ . At time  $t_2$  the  $M_P$  will be turned off, inductor current cannot change promptly, it will continues flowing through the body diode of  $M_N$  and  $D_I$  back to the driver supply. The constant negative voltage applied across the inductor will discharge the inductor current linearly until it vanishes completely. During this charging recovery period, all the gate charge has been returned to the driver supply.

#### 3) $L_r$ resonant discharge interval $t_2$ - $t_3$ :