# University of Tennessee, Knoxville TRACE: Tennessee Research and Creative Exchange

**Doctoral Dissertations**

**Graduate School**

12-1992

# Development and Analysis of Non-Delay-Line Constant-Fraction Discriminator Timing Circuits, Including a Fully-Monolithic CMOS Implementation

David Martin Binkley University of Tennessee, Knoxville

Follow this and additional works at: https://trace.tennessee.edu/utk\_graddiss

Part of the Electrical and Computer Engineering Commons

## **Recommended Citation**

Binkley, David Martin, "Development and Analysis of Non-Delay-Line Constant-Fraction Discriminator Timing Circuits, Including a Fully-Monolithic CMOS Implementation." PhD diss., University of Tennessee, 1992.

https://trace.tennessee.edu/utk\_graddiss/4004

This Dissertation is brought to you for free and open access by the Graduate School at TRACE: Tennessee Research and Creative Exchange. It has been accepted for inclusion in Doctoral Dissertations by an authorized administrator of TRACE: Tennessee Research and Creative Exchange. For more information, please contact trace@utk.edu.

To the Graduate Council:

I am submitting herewith a dissertation written by David Martin Binkley entitled "Development and Analysis of Non-Delay-Line Constant-Fraction Discriminator Timing Circuits, Including a Fully-Monolithic CMOS Implementation." I have examined the final electronic copy of this dissertation for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Doctor of Philosophy, with a major in Electrical Engineering.

James M. Rochelle, Major Professor

We have read this dissertation and recommend its acceptance:

William Bugg, Paul Crilly, Vaugh Blalock, Donald Bouldin

Accepted for the Council:

Carolyn R. Hodges

Vice Provost and Dean of the Graduate School

(Original signatures are on file with official student records.)

To the Graduate Council:

I am submitting herewith a dissertation written by David Martin Binkley entitled "Development and Analysis of Non-Delay-Line Constant-Fraction Discriminator Timing Circuits, Including a Fully-Monolithic CMOS Implementation." I have examined the final copy of this dissertation for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Doctor of Philosophy, with a major in Electrical Engineering.

Dr. James M. Rochelle, Major Professor

We have read this dissertation and recommend its acceptance:

Accepted for the Council:

minkel

Associate Vice Chancellor and Dean of the Graduate School

# DEVELOPMENT AND ANALYSIS OF NON-DELAY-LINE CONSTANT-FRACTION DISCRIMINATOR TIMING CIRCUITS, INCLUDING A FULLY-MONOLITHIC CMOS IMPLEMENTATION

A Dissertation Presented for the Doctor of Philosophy Degree The University of Tennessee, Knoxville

> David Martin Binkley December 1992

Copyright © David Martin Binkley, 1992 All rights reserved.

## DEDICATION

This dissertation is dedicated to the memory of my mother, Carol Louise Dexter Binkley, who passed away in March 1991 during the early part of this research. Mother's enthusiasm, love of life, and courage set an example for all of us to follow. Her death at only fifty-six years of age is the greatest loss experienced by me, my father, Jerry W. Binkley, my sisters, Janet, Elaine, and Linda Binkley, mother's parents, William M. and Lucille W. Dexter, mother's brother and sisters, and many other relatives and friends. I hope this research will further encourage biochemical medical imaging with Positron Emission Tomography (PET) and contribute to better cancer detection, treatment, and the development of cures.

### ACKNOWLEDGMENTS

This research was only possible with the encouragement and support of many people, for whom I am very grateful. I start by thanking my wife, Jacqueline, for all her support during a time when our time together was limited greatly. Her support during this research once again reminded me that the best decision I have made in life was to request our marriage. Additionally, I thank my father, Jerry White Binkley, sisters, Janet, Elaine, and Linda Binkley, grandparents, William M. and Lucille W. Dexter, and Robert T. Binkley, and other members of the Binkley and Dexter families for their support during this research. I am especially grateful for my father's total commitment to mother during her lengthy illness.

It is a great opportunity to be employed at CTI PET Systems, Inc., which has the mission of making PET a widely-available, clinical, medical-imaging modality. The potential of improving the quality of human life and, indeed, saving human life through medical research and clinical practice is enormous using PET biochemical imaging. The research reported here, in fact, was funded in part by a grant (grant number 2 R44 CA49405-02A1) from the National Cancer Institute.

Many individuals at CTI PET Systems, Inc. were supportive of this research. While few senior managers would have permitted a small company (less than 250 employees) to venture into the development of sophisticated, custom, high-speed, analog CMOS integrated circuits, Ron Nutt permitted us to launch into such a development. Ron's entrepreneurial spirit and vision has permitted him to lead the research and development activities of an organization which leads the world in PET development. Mike Casey served as a primary sounding board for this research, and his extensive knowledge and feel for radiationdetection statistics was invaluable. Additionally, Clif Moyers and Wilfried Loeffler offered continuing support for this research. Mike Paulus assisted with integrated-circuit layout and was very helpful in areas of CMOS processing. Brian Swann and Steve Hudson assisted with integrated-circuit layout, developed computer programs that interchanged data between commercial SPICE programs and circuit-optimization programs which I wrote, and prepared many figures. Brian Williams also helped with integrated-circuit layout and made many difficult laboratory measurements of the prototype monolithic CMOS constant-fraction discriminator circuit developed in this work. Mark Long built a number of complex test circuits, and as typical of Mark's work, these test circuits were always fully operational at the start of prototype testing. Finally, Larry Byars provided C programming

advice, and Jonathan Frey provided technical-writing advice through proof reading of this dissertation.

A dissertation committee of world-class researchers helped to guide and review this research. Jim Rochelle served as the committee head, and I enjoyed frequent discussions with him on analog CMOS design topics. Jim is an enormously knowledgeable, creative, and thorough researcher and I consider it rare opportunity to study under such an individual. Don Bouldin, active in VLSI design research, Vaugh Blalock, active in nuclear instrumentation and low-noise electronics research, William Bugg, active in high-energy physics experimentation research, and Paul Crilly, active in signal reconstruction research, complimented Jim in their guidance and review of this research.

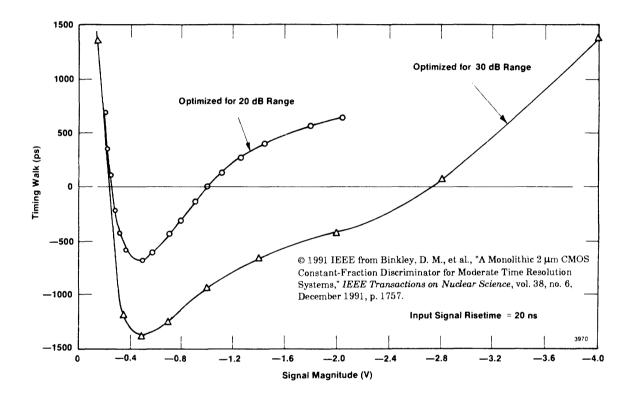

Figure 5-2 (page 227) is reprinted from: Binkley, D. M., M. L. Simpson, and J. M. Rochelle, "A Monolithic, 2 μm CMOS Constant-Fraction Discriminator for Moderate Time Resolution Systems," *IEEE Transactions on Nuclear Science*, vol. 38, no. 6, December 1991, p. 1757, with permission of the Institute of Electrical and Electronic Engineers.

## ABSTRACT

A constant-fraction discriminator (CFD) is a time pick-off circuit providing time derivation that is insensitive to input-signal amplitude and, in some cases, input-signal rise time. CFD time pick-off circuits are useful in Positron Emission Tomography (PET) systems where Bismuth Germanate (BGO)/photomultiplier scintillation detectors detect coincident, 511-keV annihilation gamma rays.

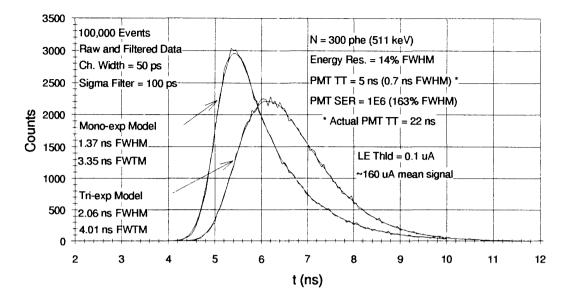

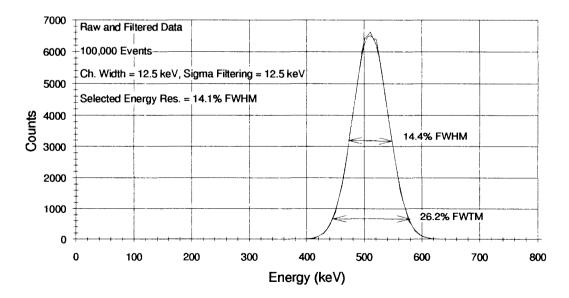

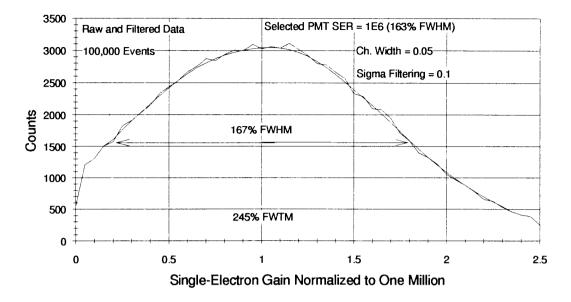

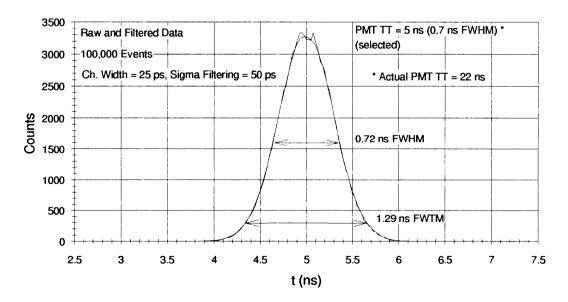

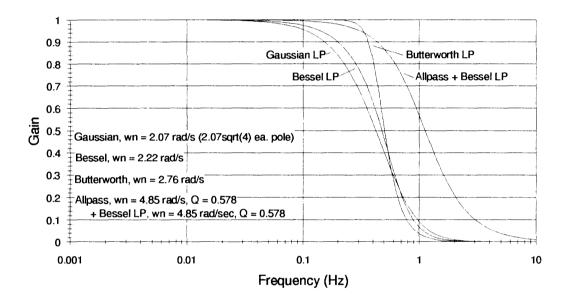

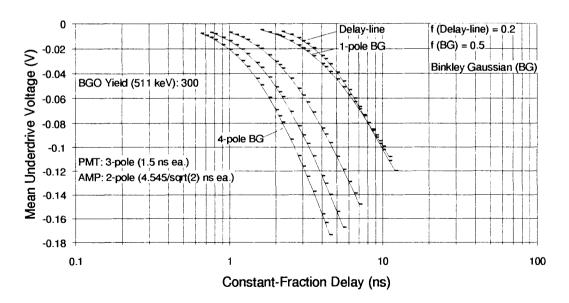

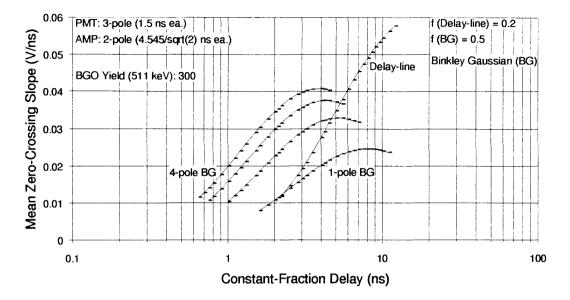

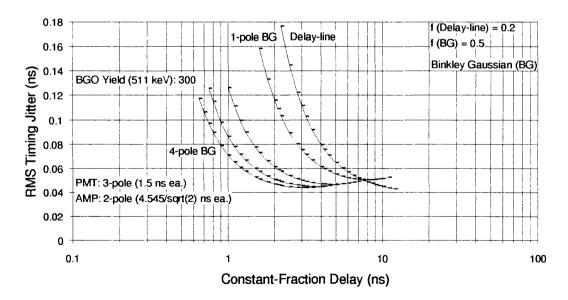

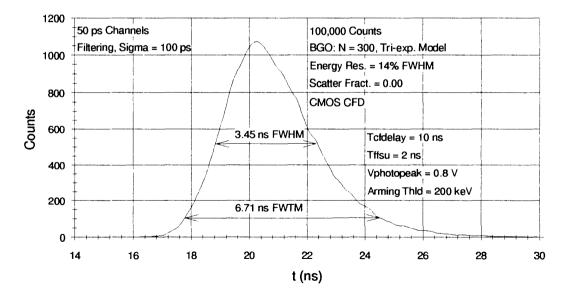

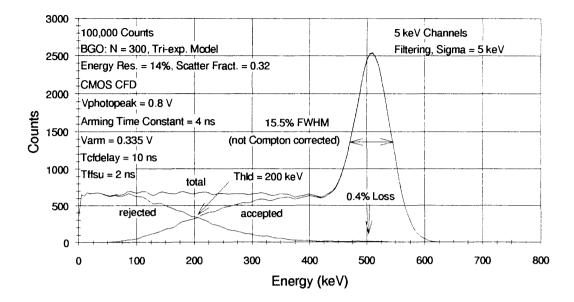

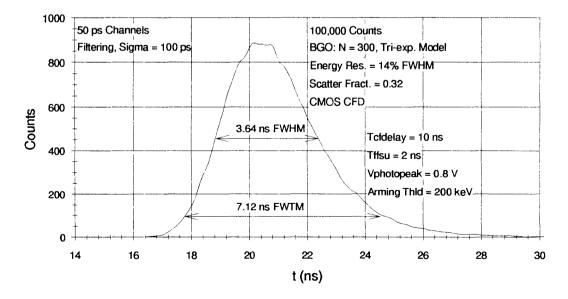

Time walk and noise-induced timing jitter in time pick-off circuits are discussed along with optimal and sub-optimal timing filters designed to minimize timing jitter. Additionally, the effects of scintillation-detector statistics on timing performance are discussed, and Monte Carlo analysis is developed to provide estimated timing and energy spectra for selected detector and time pick-off circuit configurations. The traditional delay-line CFD is then described with a discussion of deterministic (non statistical) performance and statistical Monte Carlo timing performance. A new class of non-delay-line CFD circuits utilizing lowpass- and/or allpass-filter delay-line approximations is then presented. The timing performance of these non-delay-line CFD circuits is shown to be comparable to traditional delay-line CFD circuits.

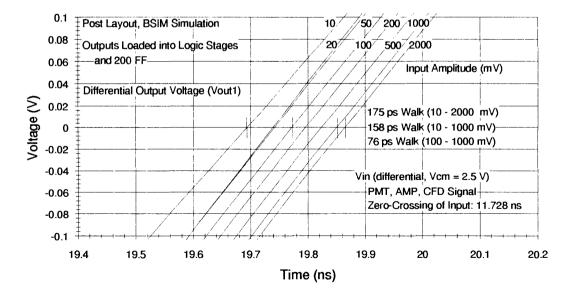

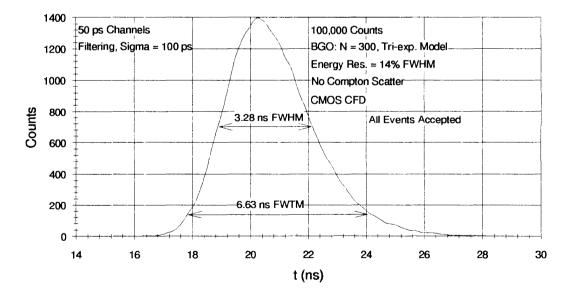

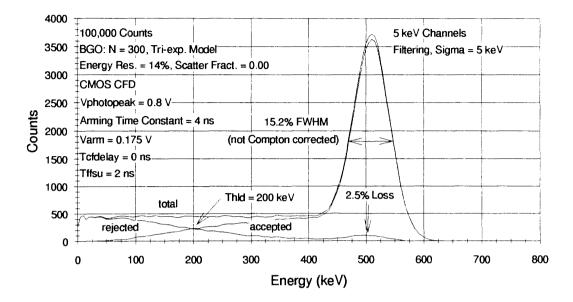

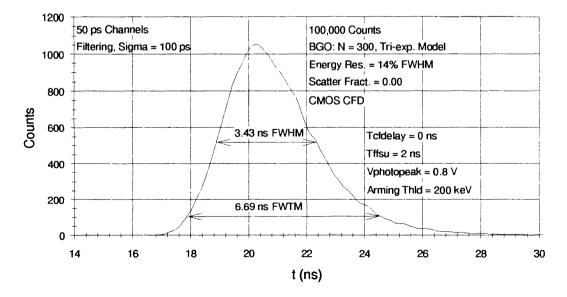

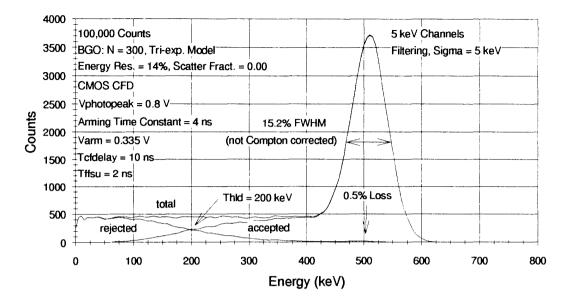

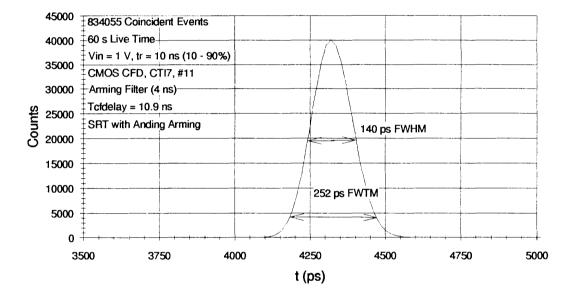

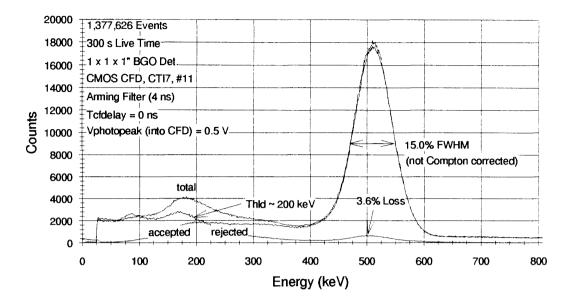

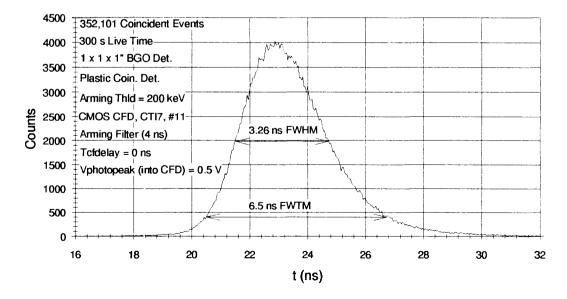

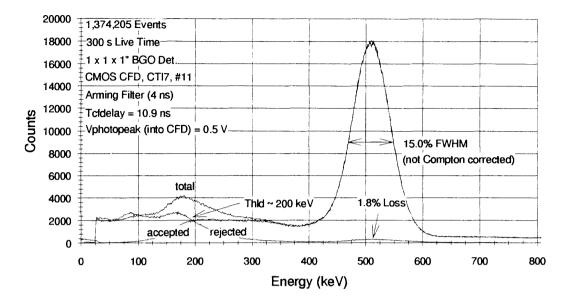

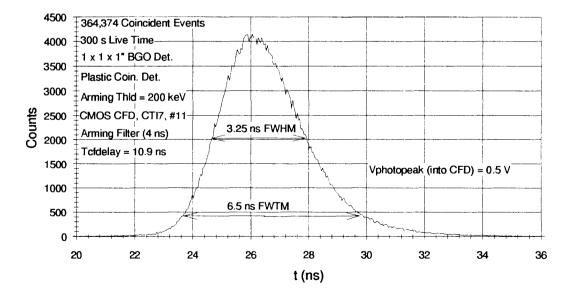

Following the development and analysis of non-delay-line CFD circuits, a fullymonolithic, non-delay-line CFD circuit is presented which was fabricated in a standard digital, 2- $\mu$ , double-metal, double-poly, n-well CMOS process. The CMOS circuits developed include a low time walk comparator having a time walk of approximately 175 ps for input signals with amplitudes between 10-mV to 2000-mV and a rise time (10 - 90%) of 10 ns. Additionally, a fifth-order, continuous-time filter having a bandwidth of over 100 MHz was developed to provide CFD signal shaping without a delay line. The measured timing resolution (3.26 ns FWHM, 6.50 ns FWTM) of the fully-monolithic, CMOS CFD is comparable to measured resolution (3.30 ns FWHM, 6.40 ns FWTM) of a commercial, discrete, bipolar CFD containing an external delay line. Each CFD was tested with a PET BGO/photomultiplier scintillation detector and a preamplifier having a 10-ns (10 - 90%) risetime. The development of a fully-monolithic, CMOS CFD circuit, believed to be the first such reported development, is significant for PET and other systems that employ many front-end CFD time pick-off circuits.

### PREFACE

The enormous complexity of PET-tomograph front-end electronics prompted the research and development staff of CTI PET Systems, Inc. to find a way to integrate this electronics into semicustom or custom integrated circuits. Such integration was vital to significantly reduce the cost, size, power consumption, and complexity of the front-end electronics, which is one of the requirements for making PET a widely-available, clinical, medical-imaging modality.

The idea to integrate PET front-end electronics into CMOS circuits originated while I was attending a course in analog CMOS design taught by Jim Rochelle at the University of Tennessee in Knoxville. We had been investigating the use of bipolar integration at CTI PET Systems, Inc., but the cost and power required using this technology would not permit us to reach the aforementioned objectives of significantly reducing the cost, size, power consumption, and complexity of PET front-end electronics.

As a result of the analog CMOS course, we began researching the feasibility at CTI PET Systems, Inc. of fabricating monolithic, high-speed (50 - 200 MHz bandwidth), analog CMOS circuits. Such circuits had previously seemed unfeasible given the low-speed (1 MHz bandwidth) of commercial CMOS analog integrated-circuit and standard-cell offerings. Following this feasibility research, CTI PET Systems, Inc., initiated the research and development of custom, high-speed, analog and digital CMOS circuits to replace the existing PET front-end circuitry consisting of high-speed bipolar operational amplifiers, CMOS digital-to-analog converters, and other circuits. A \$500,000 Small Business Innovative Research grant (grant number 2 R44 CA49405-02A1) was then successfully obtained from the National Cancer Institute to help fund the research and development. The fullymonolithic, CMOS constant-fraction discriminator described in this work is one part of the CMOS, integrated-circuit, front-end electronic development project.

# TABLE OF CONTENTS

|    | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1                                                                                            |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

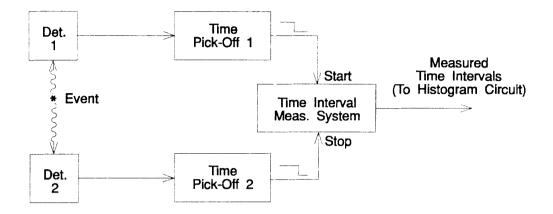

|    | Time-Measurement Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1                                                                                            |

|    | Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                                                                                            |

|    | The Constant-Fraction Discriminator As a Time Pick-Off Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1                                                                                            |

|    | Applications of Time-Measurement Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3                                                                                            |

|    | Experimental Physics and Industrial Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3                                                                                            |

|    | Positron Emission Tomography Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                              |

|    | Significance of Integrating a CFD into CMOS Technology for PET Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                              |

|    | PET System Detector and Front-End Electronics Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5                                                                                            |

|    | Advantages of Integrating PET Front-End Circuits into Custom                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | _                                                                                            |

|    | CMOS Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                              |

|    | Scope of Dissertation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                              |

|    | New Contributions Presented in Dissertation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                              |

|    | Organization of Dissertation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                              |

|    | References for Section 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                              |

| _  | Appendix for Section 1 — Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                              |

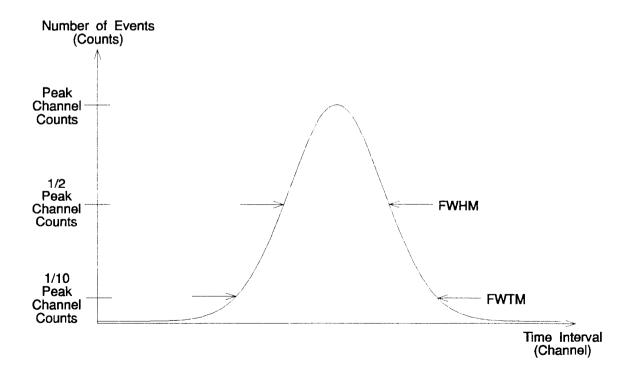

| 2. | Timing Performance Of Time Pick-Off Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                              |

|    | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                              |

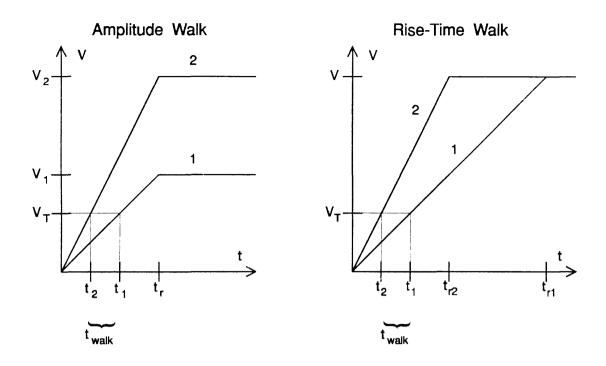

|    | Time Walk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                              |

|    | Leading-Edge Discriminator Time Walk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                              |

|    | Comparator Time Walk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                              |

|    | Time Pick-Off Circuit Walk Due to Comparator Time Walk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                              |

|    | Timing Jitter Due to Electronic Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                              |

|    | Evaluation of Timing Jitter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                              |

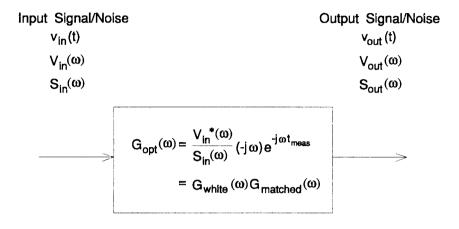

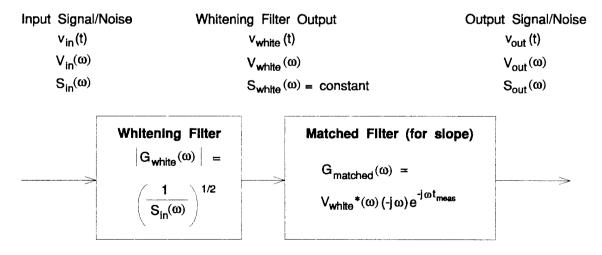

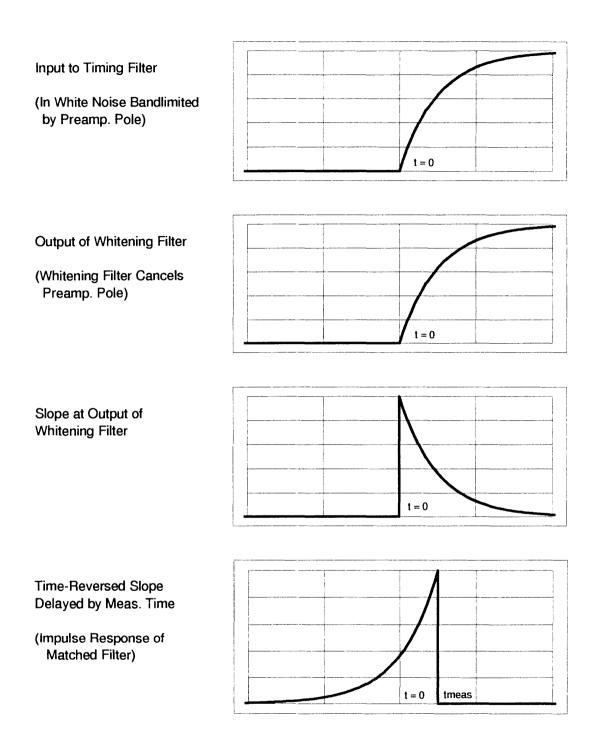

|    | The Optimum Filter for Timing<br>Optimum Timing Filter for a Semiconductor Detector with                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 20                                                                                           |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                              |

|    | Charge-Sensitive Preamplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 32                                                                                           |

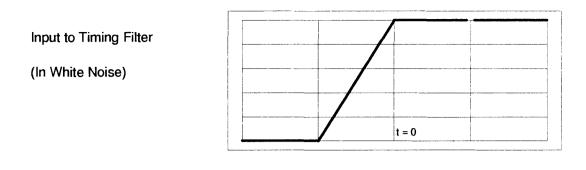

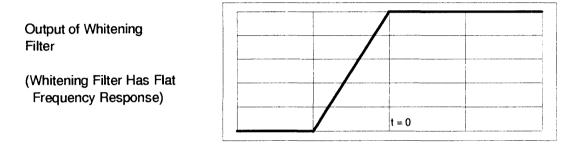

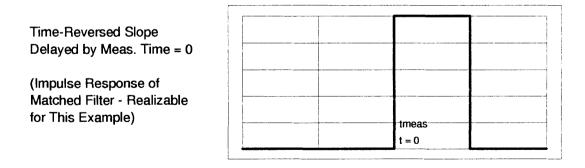

|    | Charge-Sensitive Preamplifier<br>Optimum Timing Filter for a Step Input in White Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                              |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                              |

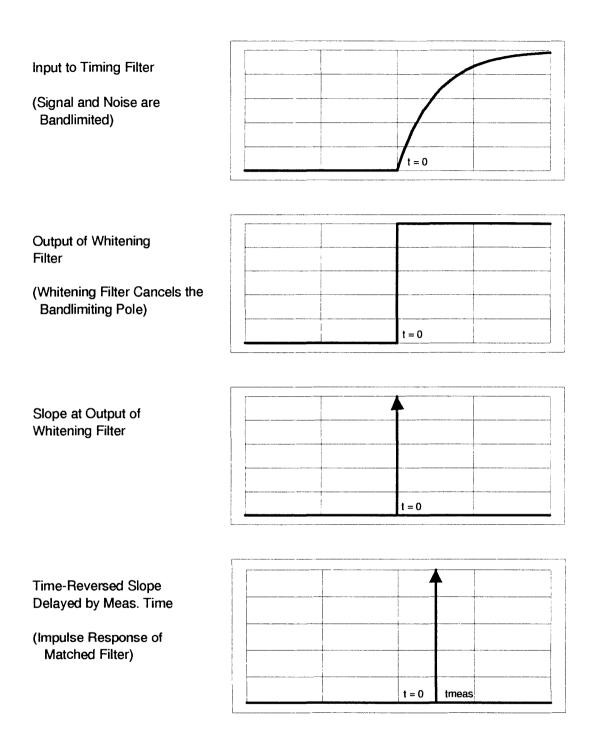

|    | Optimum Timing Filter for a Step Input in White Noise<br>Optimum Timing Filter for a Bandlimited Input in Bandlimited<br>Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 34                                                                                           |

|    | Optimum Timing Filter for a Step Input in White Noise<br>Optimum Timing Filter for a Bandlimited Input in Bandlimited                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 34                                                                                           |

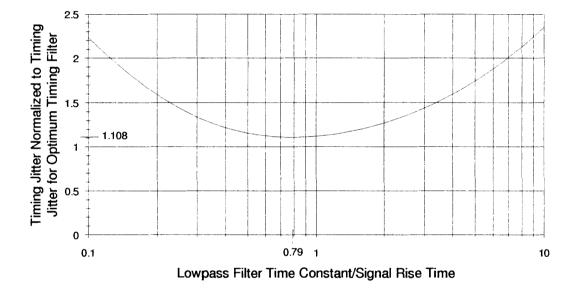

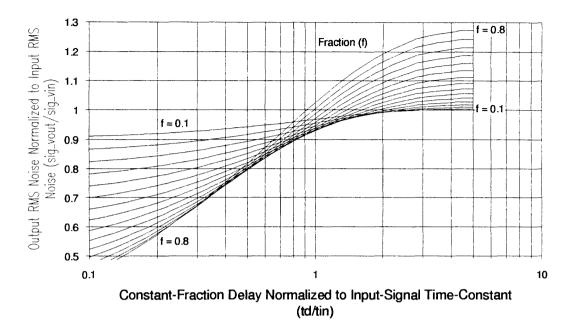

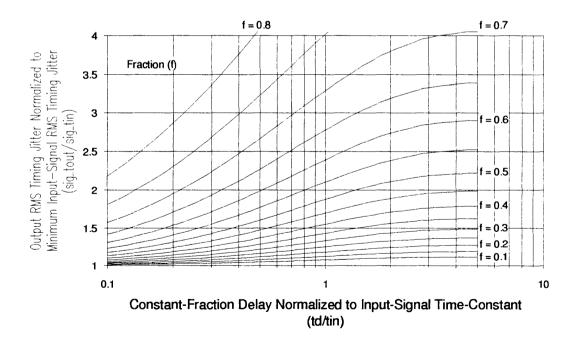

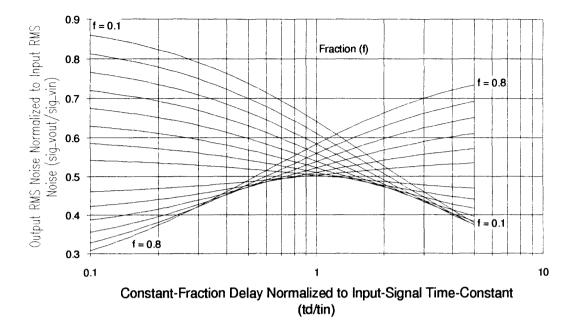

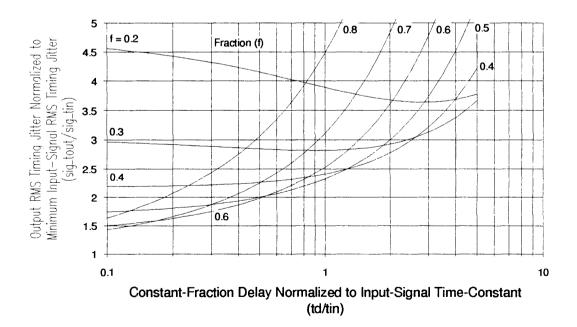

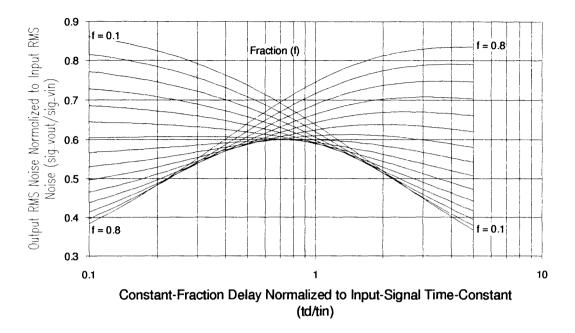

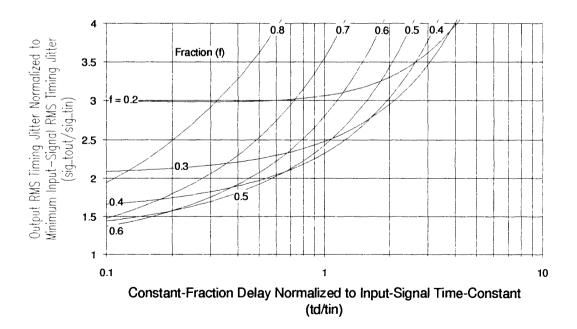

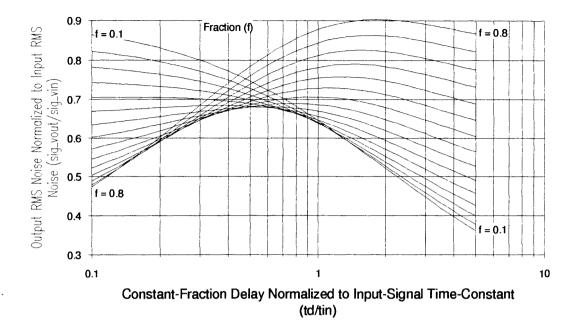

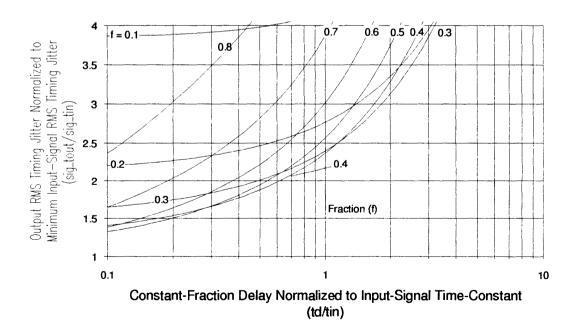

|    | Optimum Timing Filter for a Step Input in White Noise<br>Optimum Timing Filter for a Bandlimited Input in Bandlimited<br>Noise<br>Suboptimal Timing Filter for a Bandlimited Input in<br>Bandlimited Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 34<br>35<br>36                                                                               |

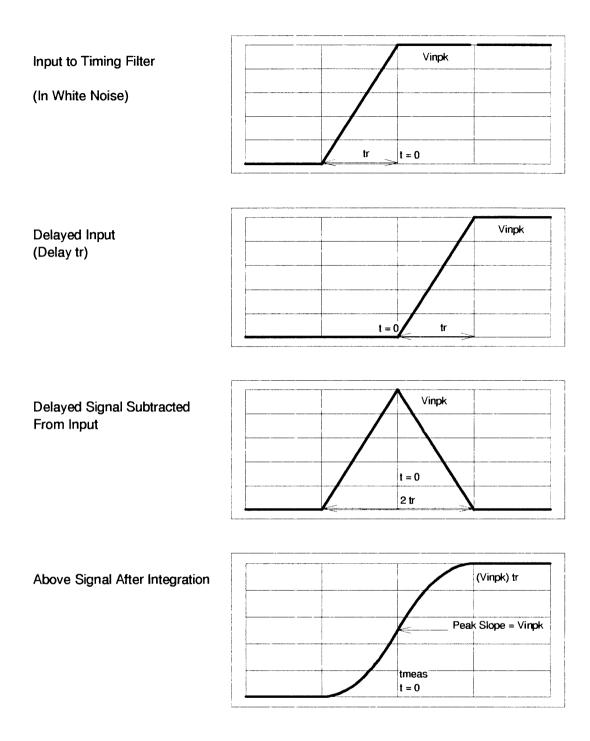

|    | Optimum Timing Filter for a Step Input in White Noise<br>Optimum Timing Filter for a Bandlimited Input in Bandlimited<br>Noise<br>Suboptimal Timing Filter for a Bandlimited Input in<br>Bandlimited Noise<br>Optimum Timing Filter for a Linear-Edge Input in White Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 34<br>35<br>36<br>39                                                                         |

|    | Optimum Timing Filter for a Step Input in White Noise<br>Optimum Timing Filter for a Bandlimited Input in Bandlimited<br>Noise<br>Suboptimal Timing Filter for a Bandlimited Input in<br>Bandlimited Noise<br>Optimum Timing Filter for a Linear-Edge Input in White Noise<br>Time-Variant Filters for Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 34<br>35<br>36<br>39<br>43                                                                   |

|    | Optimum Timing Filter for a Step Input in White Noise<br>Optimum Timing Filter for a Bandlimited Input in Bandlimited<br>Noise<br>Suboptimal Timing Filter for a Bandlimited Input in<br>Bandlimited Noise<br>Optimum Timing Filter for a Linear-Edge Input in White Noise<br>Time-Variant Filters for Timing<br>Time Drifts Due to Temperature and Aging Effects                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 34<br>35<br>36<br>39<br>43<br>44                                                             |

|    | Optimum Timing Filter for a Step Input in White Noise<br>Optimum Timing Filter for a Bandlimited Input in Bandlimited<br>Noise<br>Suboptimal Timing Filter for a Bandlimited Input in<br>Bandlimited Noise<br>Optimum Timing Filter for a Linear-Edge Input in White Noise<br>Time-Variant Filters for Timing<br>Time Drifts Due to Temperature and Aging Effects<br>References for Section 2                                                                                                                                                                                                                                                                                                                                                                                                                                 | 34<br>35<br>36<br>39<br>43<br>44<br>45                                                       |

|    | Optimum Timing Filter for a Step Input in White Noise<br>Optimum Timing Filter for a Bandlimited Input in Bandlimited<br>Noise<br>Suboptimal Timing Filter for a Bandlimited Input in<br>Bandlimited Noise<br>Optimum Timing Filter for a Linear-Edge Input in White Noise<br>Time-Variant Filters for Timing<br>Time Drifts Due to Temperature and Aging Effects<br>References for Section 2<br>Appendix for Section 2 — Figures                                                                                                                                                                                                                                                                                                                                                                                             | 34<br>35<br>36<br>39<br>43<br>43<br>45<br>47                                                 |

| 3. | Optimum Timing Filter for a Step Input in White Noise<br>Optimum Timing Filter for a Bandlimited Input in Bandlimited<br>Noise<br>Suboptimal Timing Filter for a Bandlimited Input in<br>Bandlimited Noise<br>Optimum Timing Filter for a Linear-Edge Input in White Noise<br>Time-Variant Filters for Timing<br>Time Drifts Due to Temperature and Aging Effects<br>References for Section 2<br>Appendix for Section 2<br>Timing Performance Of Scintillation-Detector Systems                                                                                                                                                                                                                                                                                                                                               | 34<br>35<br>36<br>39<br>43<br>43<br>45<br>45<br>47<br>58                                     |

| 3. | Optimum Timing Filter for a Step Input in White Noise<br>Optimum Timing Filter for a Bandlimited Input in Bandlimited<br>Noise<br>Suboptimal Timing Filter for a Bandlimited Input in<br>Bandlimited Noise<br>Optimum Timing Filter for a Linear-Edge Input in White Noise<br>Time-Variant Filters for Timing<br>Time Drifts Due to Temperature and Aging Effects<br>References for Section 2<br>Appendix for Section 2<br>Timing Performance Of Scintillation-Detector Systems<br>Overview                                                                                                                                                                                                                                                                                                                                   | 34<br>35<br>39<br>43<br>43<br>44<br>45<br>58<br>58                                           |

| 3. | Optimum Timing Filter for a Step Input in White Noise<br>Optimum Timing Filter for a Bandlimited Input in Bandlimited<br>Noise<br>Suboptimal Timing Filter for a Bandlimited Input in<br>Bandlimited Noise<br>Optimum Timing Filter for a Linear-Edge Input in White Noise<br>Time-Variant Filters for Timing<br>Time Drifts Due to Temperature and Aging Effects<br>References for Section 2<br>Appendix for Section 2<br>Timing Performance Of Scintillation-Detector Systems<br>Overview<br>Scintillation Detector Operation                                                                                                                                                                                                                                                                                               | 34<br>35<br>39<br>43<br>43<br>43<br>45<br>47<br>58<br>58<br>59                               |

| 3. | Optimum Timing Filter for a Step Input in White Noise<br>Optimum Timing Filter for a Bandlimited Input in Bandlimited<br>Noise<br>Suboptimal Timing Filter for a Bandlimited Input in<br>Bandlimited Noise<br>Optimum Timing Filter for a Linear-Edge Input in White Noise<br>Time-Variant Filters for Timing<br>Time Drifts Due to Temperature and Aging Effects<br>References for Section 2<br>Appendix for Section 2<br>Timing Performance Of Scintillation-Detector Systems<br>Overview<br>Scintillation Detector Operation<br>Overview of Timing Errors in Scintillation Detectors                                                                                                                                                                                                                                       | 34<br>35<br>39<br>43<br>43<br>43<br>45<br>47<br>58<br>58<br>59<br>59                         |

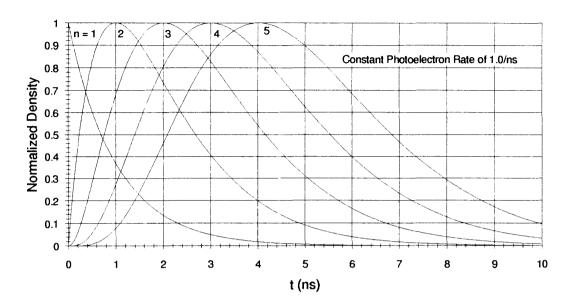

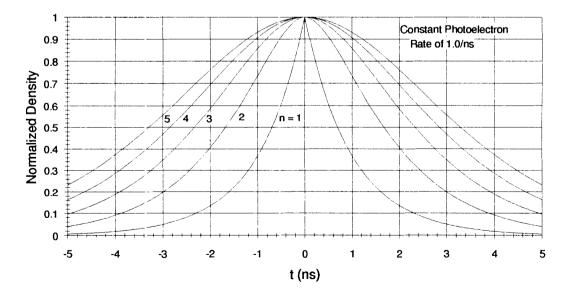

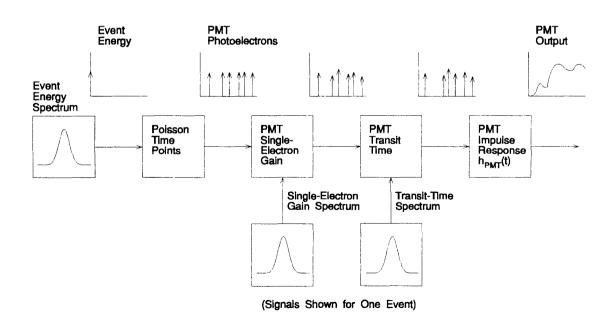

| 3. | Optimum Timing Filter for a Step Input in White Noise<br>Optimum Timing Filter for a Bandlimited Input in Bandlimited<br>Noise<br>Suboptimal Timing Filter for a Bandlimited Input in<br>Bandlimited Noise<br>Optimum Timing Filter for a Linear-Edge Input in White Noise<br>Time-Variant Filters for Timing<br>Time Drifts Due to Temperature and Aging Effects<br>References for Section 2<br>Appendix for Section 2 — Figures<br>Timing Performance Of Scintillation-Detector Systems<br>Overview<br>Scintillation Detector Operation<br>Overview of Timing Errors in Scintillation Detectors<br>Statistical Timing Performance of Scintillation Detectors                                                                                                                                                                | 34<br>35<br>39<br>43<br>43<br>44<br>45<br>47<br>58<br>59<br>59<br>60                         |

| 3. | Optimum Timing Filter for a Step Input in White Noise<br>Optimum Timing Filter for a Bandlimited Input in Bandlimited<br>Noise<br>Suboptimal Timing Filter for a Bandlimited Input in<br>Bandlimited Noise<br>Optimum Timing Filter for a Linear-Edge Input in White Noise<br>Time-Variant Filters for Timing<br>Time Drifts Due to Temperature and Aging Effects<br>References for Section 2<br>Appendix for Section 2 — Figures<br>Timing Performance Of Scintillation-Detector Systems<br>Overview<br>Scintillation Detector Operation<br>Overview of Timing Errors in Scintillation Detectors<br>Statistical Timing Performance of Scintillation Detectors<br>Photomultiplier Tube Timing Performance                                                                                                                     | 34<br>35<br>39<br>43<br>44<br>45<br>47<br>58<br>59<br>59<br>60                               |

| 3. | Optimum Timing Filter for a Step Input in White Noise<br>Optimum Timing Filter for a Bandlimited Input in Bandlimited<br>Noise<br>Suboptimal Timing Filter for a Bandlimited Input in<br>Bandlimited Noise<br>Optimum Timing Filter for a Linear-Edge Input in White Noise<br>Time-Variant Filters for Timing<br>Time Drifts Due to Temperature and Aging Effects<br>References for Section 2<br>Appendix for Section 2 — Figures<br>Timing Performance Of Scintillation-Detector Systems<br>Overview<br>Scintillation Detector Operation<br>Overview of Timing Errors in Scintillation Detectors<br>Statistical Timing Performance of Scintillation Detectors<br>Photomultiplier Tube Timing Performance<br>Overview of Photomultiplier Operation                                                                            | 34<br>35<br>39<br>43<br>44<br>45<br>59<br>59<br>59<br>60<br>66                               |

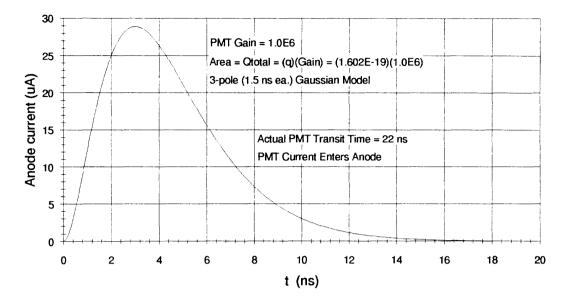

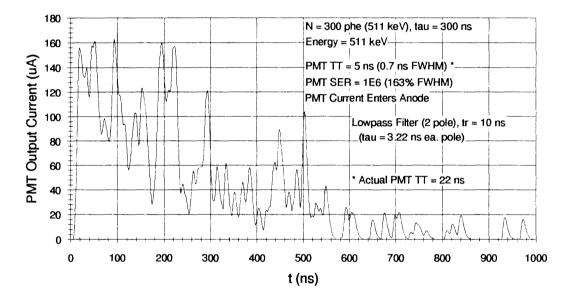

| 3. | Optimum Timing Filter for a Step Input in White Noise<br>Optimum Timing Filter for a Bandlimited Input in Bandlimited<br>Noise<br>Suboptimal Timing Filter for a Bandlimited Input in<br>Bandlimited Noise<br>Optimum Timing Filter for a Linear-Edge Input in White Noise<br>Time-Variant Filters for Timing<br>Time Drifts Due to Temperature and Aging Effects<br>References for Section 2<br>Appendix for Section 2<br>Figures<br>Timing Performance Of Scintillation-Detector Systems<br>Overview<br>Scintillation Detector Operation<br>Overview of Timing Performance of Scintillation Detectors<br>Statistical Timing Performance of Scintillation Detectors<br>Photomultiplier Tube Timing Performance<br>Overview of Photomultiplier Operation<br>Single-Electron Impulse Response                                  | 34<br>35<br>36<br>39<br>43<br>44<br>45<br>58<br>59<br>59<br>59<br>66<br>66<br>67             |

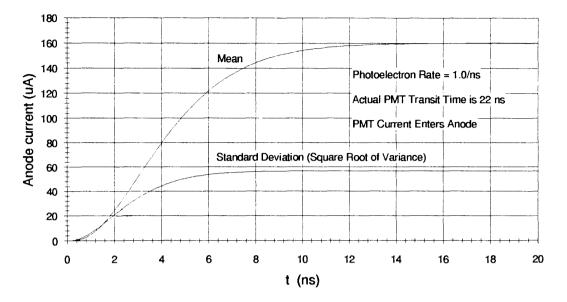

| 3. | Optimum Timing Filter for a Step Input in White Noise<br>Optimum Timing Filter for a Bandlimited Input in Bandlimited<br>Noise<br>Suboptimal Timing Filter for a Bandlimited Input in<br>Bandlimited Noise<br>Optimum Timing Filter for a Linear-Edge Input in White Noise<br>Time-Variant Filters for Timing<br>Time Drifts Due to Temperature and Aging Effects<br>References for Section 2<br>Appendix for Section 2 — Figures<br>Timing Performance Of Scintillation-Detector Systems<br>Overview<br>Scintillation Detector Operation<br>Overview of Timing Errors in Scintillation Detectors<br>Statistical Timing Performance of Scintillation Detectors<br>Photomultiplier Tube Timing Performance<br>Overview of Photomultiplier Operation<br>Single-Electron Impulse Response<br>Transit-Time Spread                 | 34<br>35<br>36<br>39<br>43<br>44<br>45<br>58<br>59<br>59<br>66<br>66<br>67<br>68             |

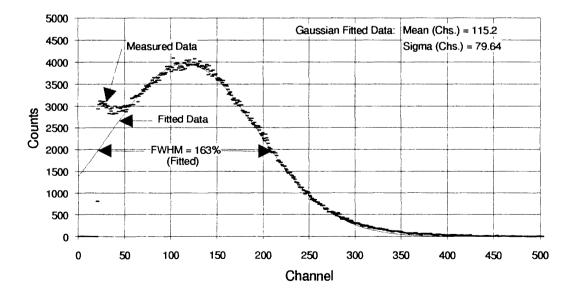

| 3. | Optimum Timing Filter for a Step Input in White Noise<br>Optimum Timing Filter for a Bandlimited Input in Bandlimited<br>Noise<br>Suboptimal Timing Filter for a Bandlimited Input in<br>Bandlimited Noise<br>Optimum Timing Filter for a Linear-Edge Input in White Noise<br>Time-Variant Filters for Timing<br>Time Drifts Due to Temperature and Aging Effects<br>References for Section 2<br>Appendix for Section 2<br>Figures<br>Timing Performance Of Scintillation-Detector Systems<br>Overview<br>Scintillation Detector Operation<br>Overview of Timing Performance of Scintillation Detectors<br>Statistical Timing Performance of Scintillation Detectors<br>Photomultiplier Tube Timing Performance<br>Overview of Photomultiplier Operation<br>Single-Electron Impulse Response<br>Single-Electron Gain Response | 34<br>35<br>36<br>39<br>43<br>44<br>45<br>58<br>59<br>59<br>66<br>66<br>66<br>68<br>69       |

| 3. | Optimum Timing Filter for a Step Input in White Noise<br>Optimum Timing Filter for a Bandlimited Input in Bandlimited<br>Noise<br>Suboptimal Timing Filter for a Bandlimited Input in<br>Bandlimited Noise<br>Optimum Timing Filter for a Linear-Edge Input in White Noise<br>Time-Variant Filters for Timing<br>Time Drifts Due to Temperature and Aging Effects<br>References for Section 2<br>Appendix for Section 2 — Figures<br>Timing Performance Of Scintillation-Detector Systems<br>Overview<br>Scintillation Detector Operation<br>Overview of Timing Errors in Scintillation Detectors<br>Statistical Timing Performance of Scintillation Detectors<br>Photomultiplier Tube Timing Performance<br>Overview of Photomultiplier Operation<br>Single-Electron Impulse Response<br>Transit-Time Spread                 | 34<br>35<br>36<br>39<br>43<br>44<br>58<br>59<br>59<br>66<br>66<br>66<br>66<br>69<br>69<br>69 |

| Timing Performance of Scintillation Detector and Time Pick-Off Circuit | 72  |

|------------------------------------------------------------------------|-----|

| Overview                                                               | 72  |

| Campbell's Theorem Analysis                                            | 73  |

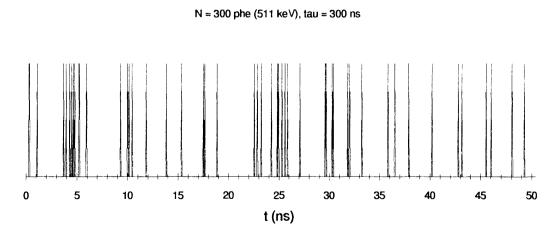

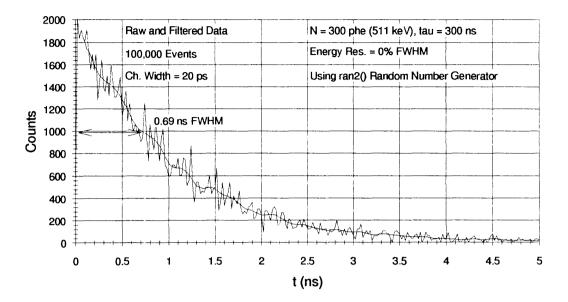

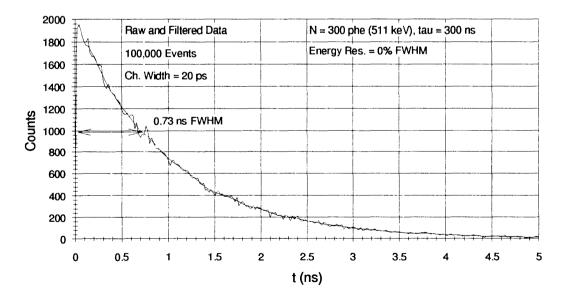

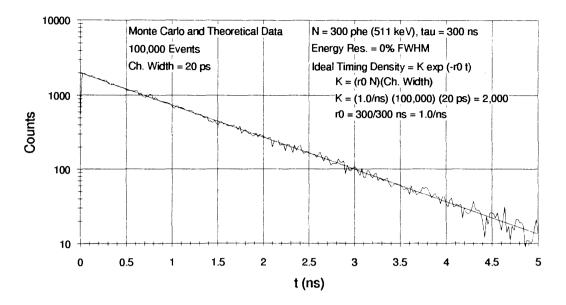

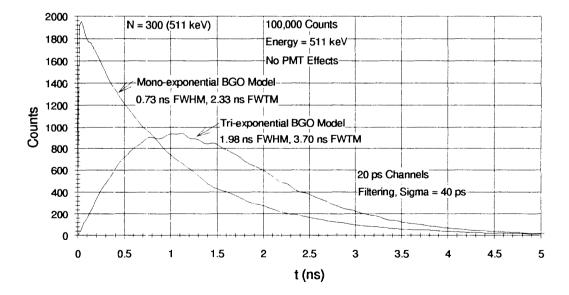

| Monte Carlo Simulation                                                 | 75  |

| Method                                                                 |     |

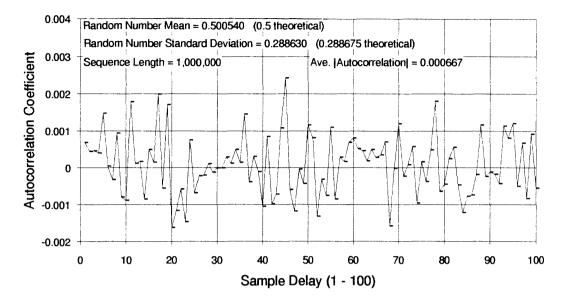

| Random Number Generation and Evaluation                                | 78  |

| Simulation of First Photoelectron Timing without                       |     |

| Photomultiplier Effects                                                | 80  |

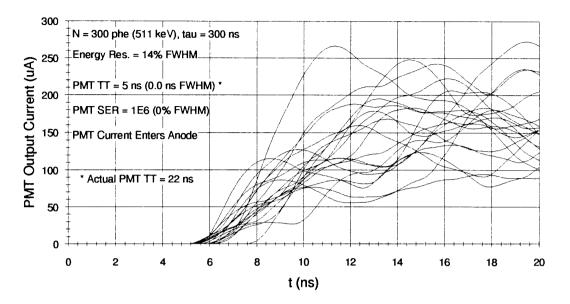

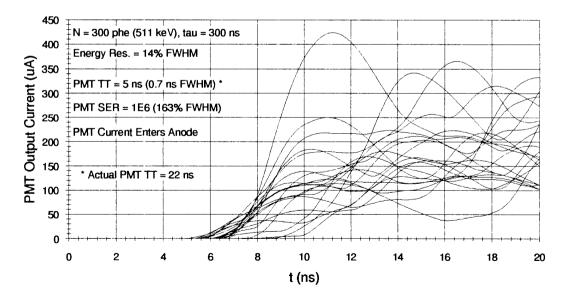

| Simulation of First Photoelectron Timing with Photomultiplier          |     |

| Effects                                                                | 82  |

| Simulation of General Scintillation-Detector Systems                   |     |

| References for Section 3                                               |     |

| Appendix for Section 3 — Figures                                       |     |

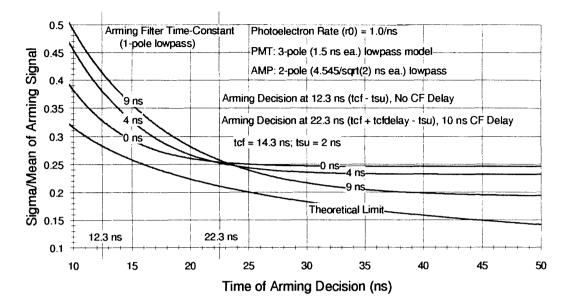

| 4. CFD Performance And Design                                          |     |

| Overview                                                               |     |

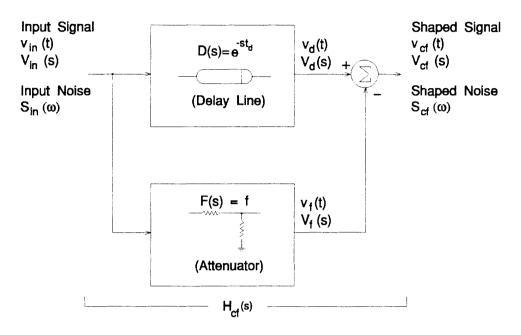

| Conventional (Delay-Line) CFD                                          |     |

| Performance with Linear-Edge Signals                                   |     |

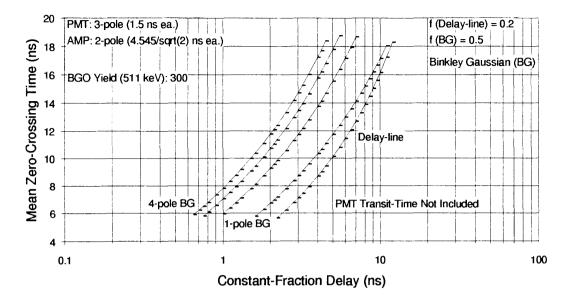

| Zero-Crossing Time                                                     |     |

| Shaping-Signal Amplitude and Slope                                     |     |

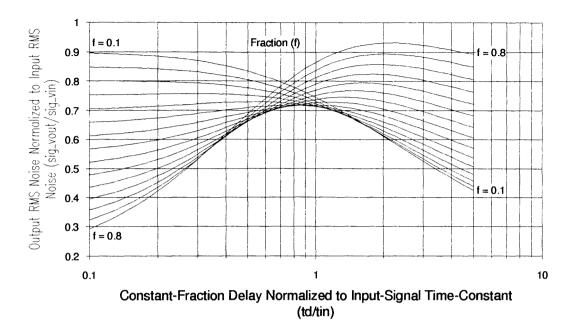

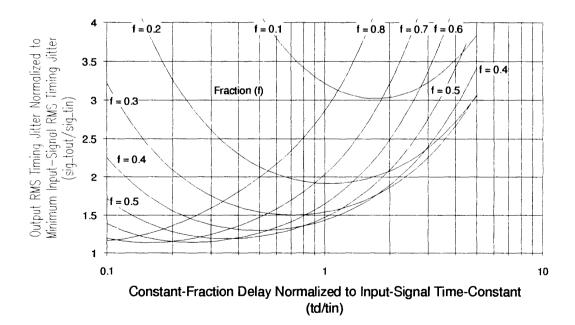

| Timing-Jitter Performance                                              |     |

| DC Baseline Effects on Timing Performance                              |     |

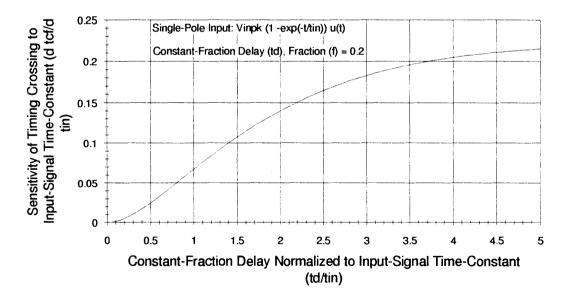

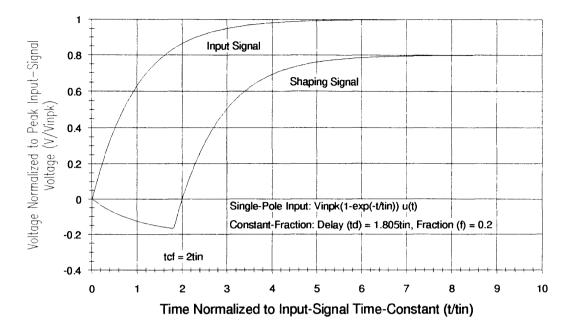

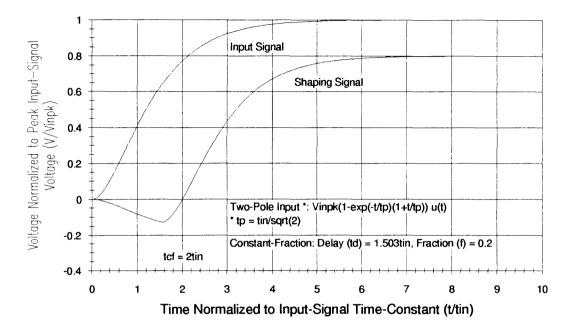

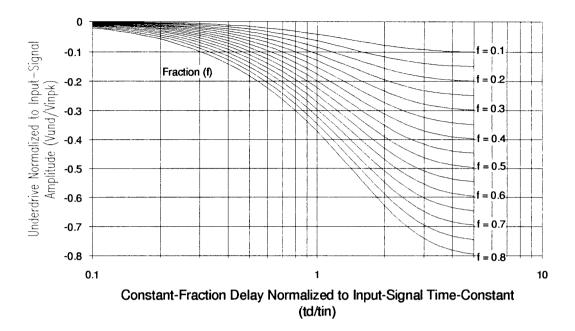

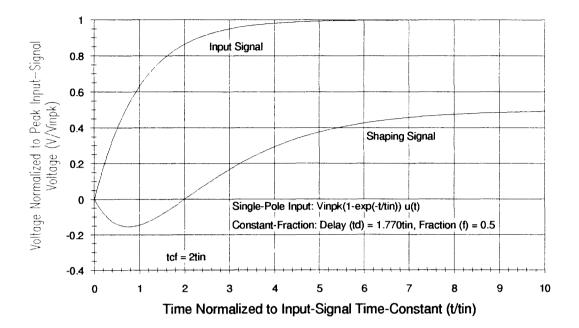

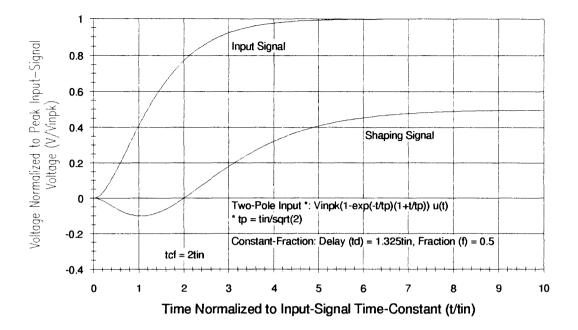

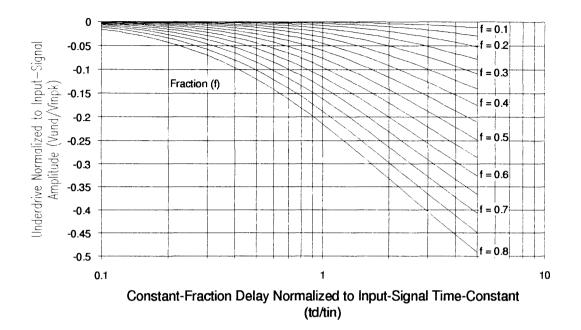

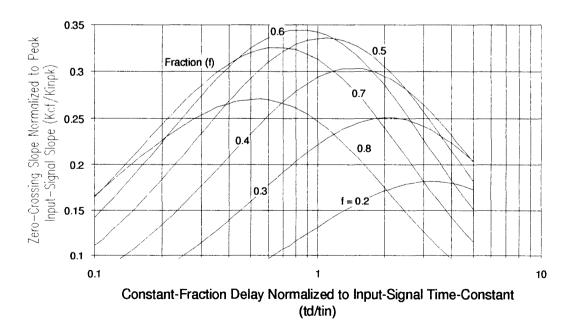

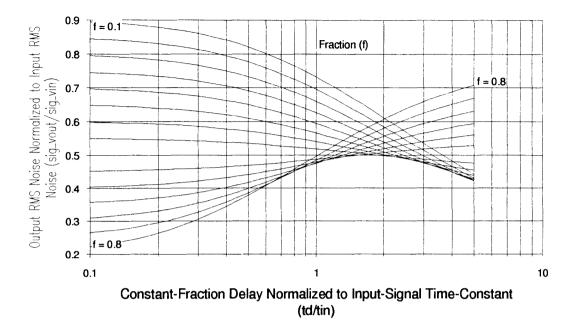

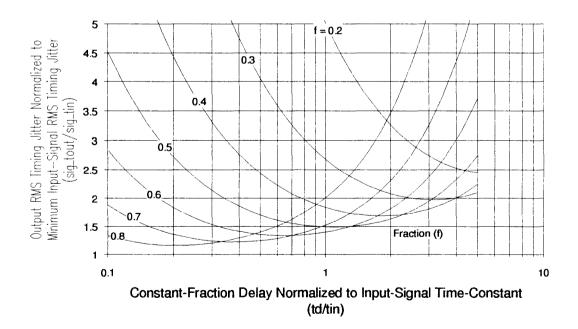

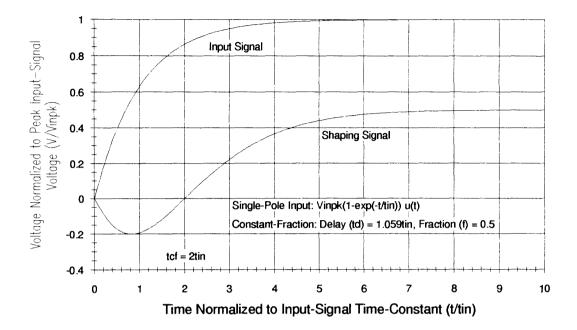

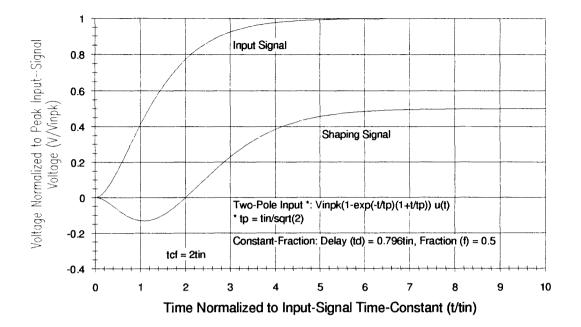

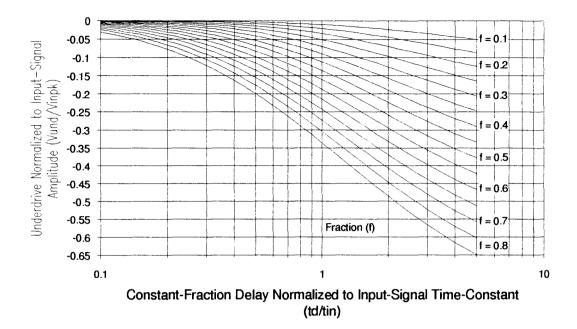

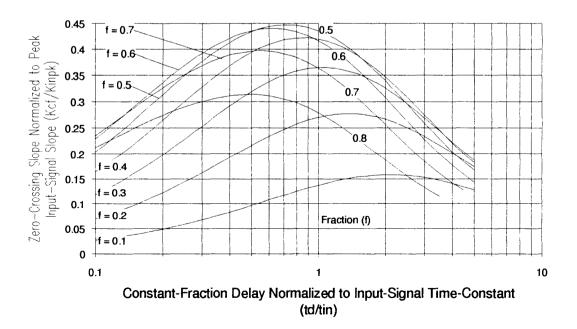

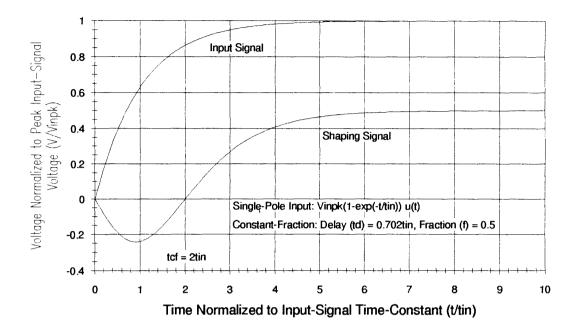

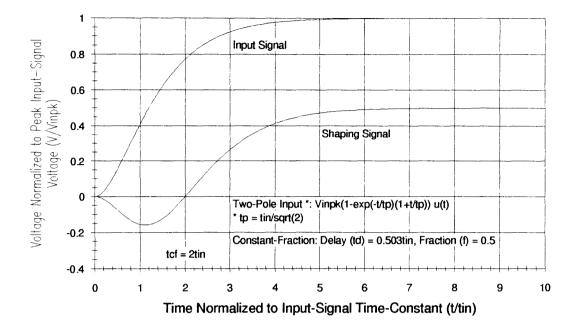

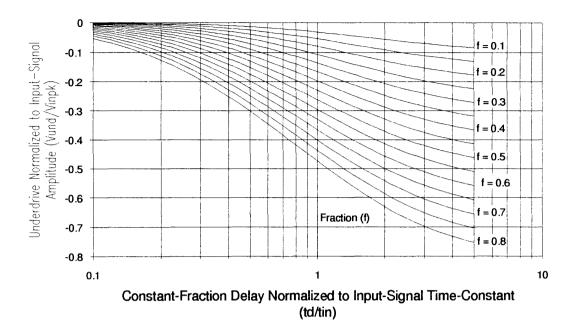

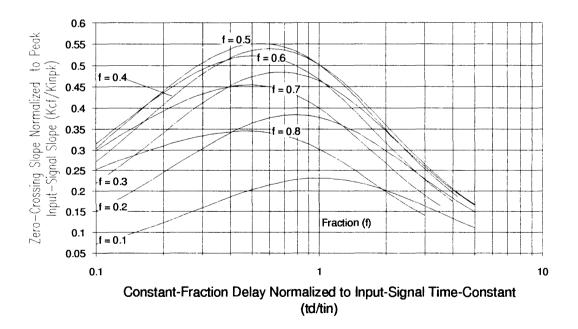

| Performance with Lowpass-Filtered Step Signals                         |     |

| Description of Lowpass-Filtered Step Signals                           |     |

| Derivation of Shaping Signal                                           |     |

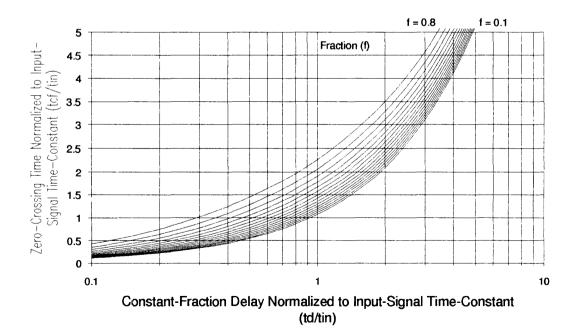

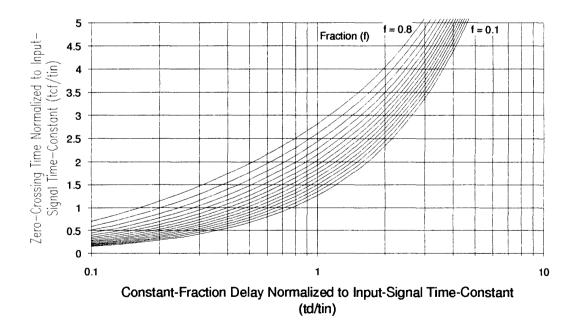

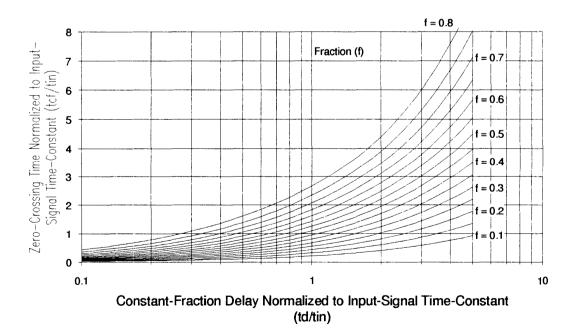

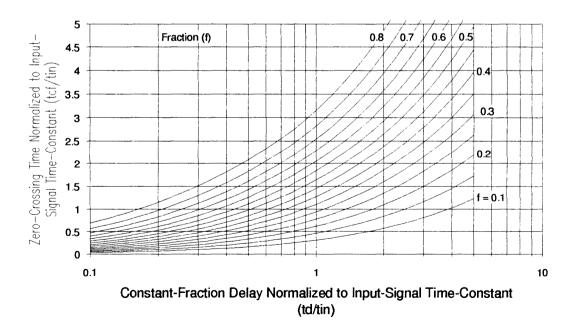

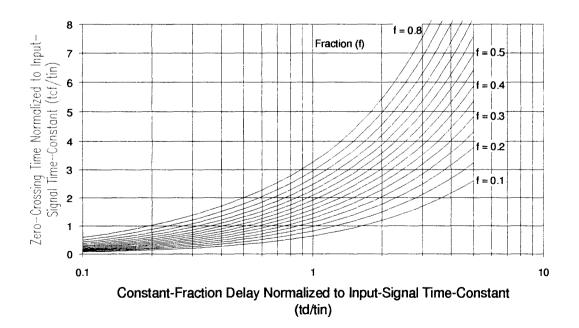

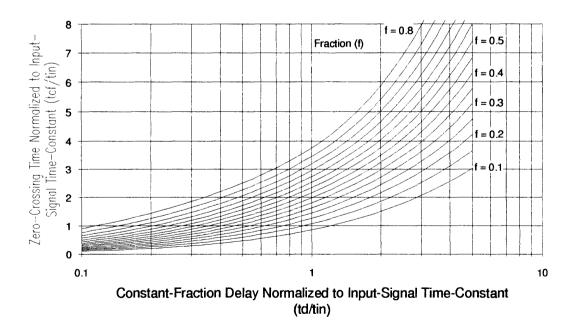

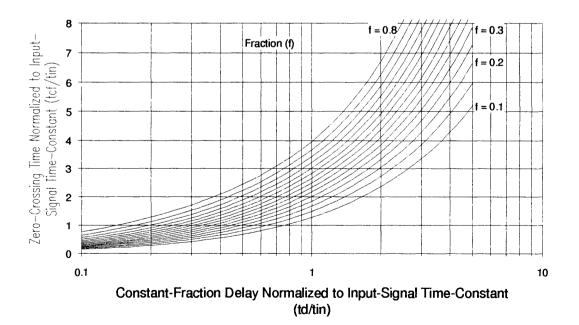

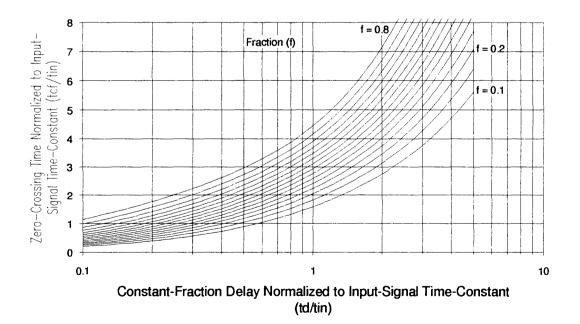

| Zero-Crossing Time                                                     |     |

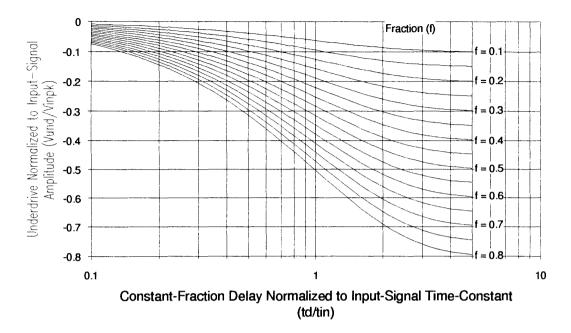

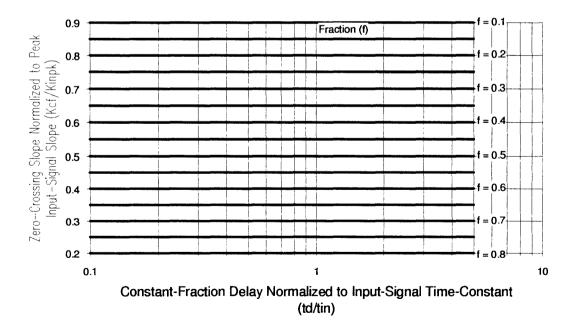

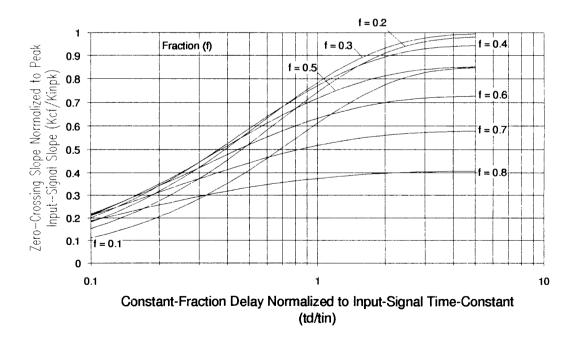

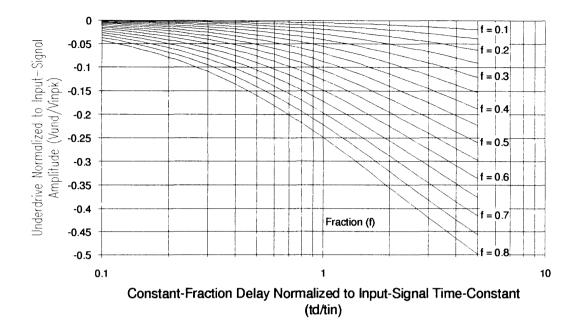

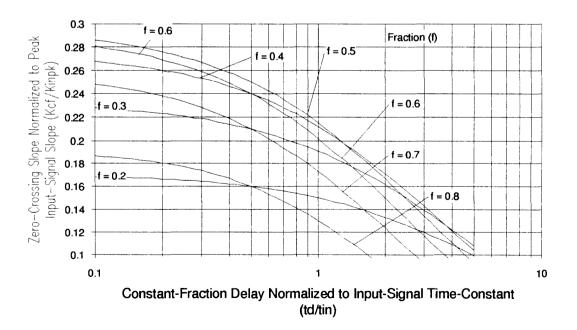

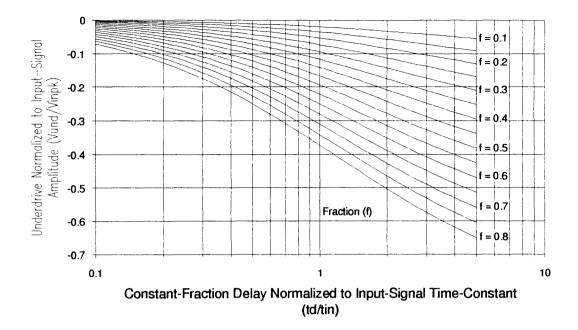

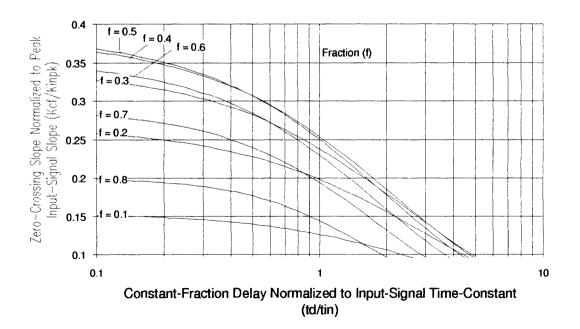

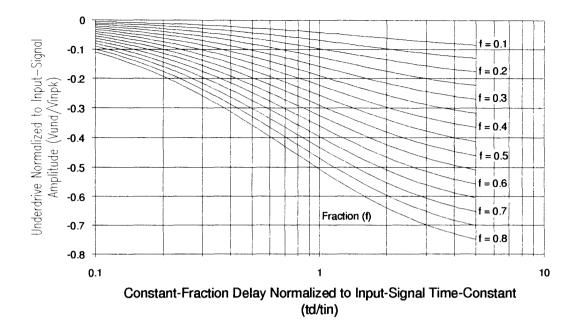

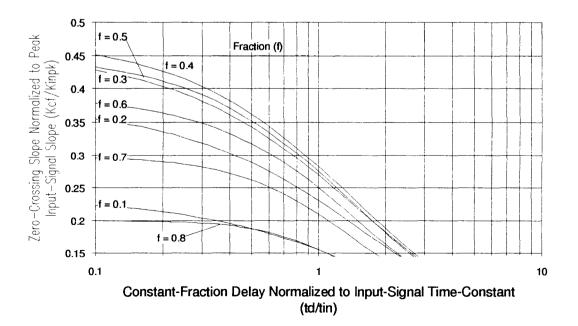

| Shaping-Signal Amplitude and Slope                                     |     |

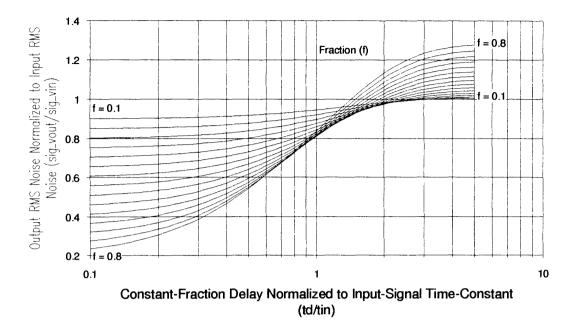

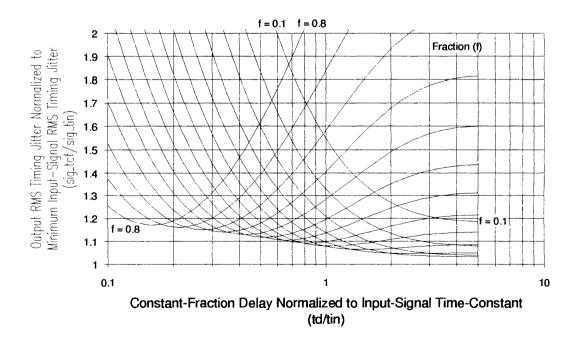

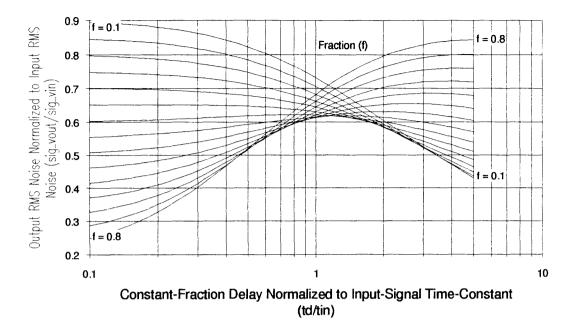

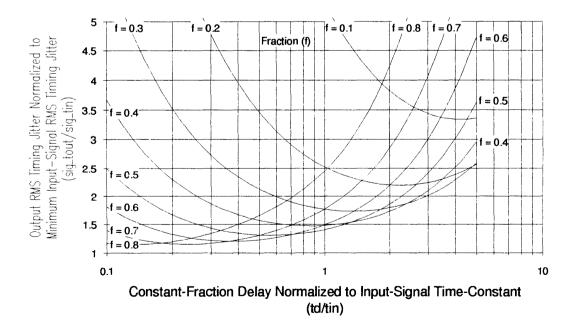

| Timing-Jitter Performance                                              |     |

| DC Baseline Effects on Timing Performance                              |     |

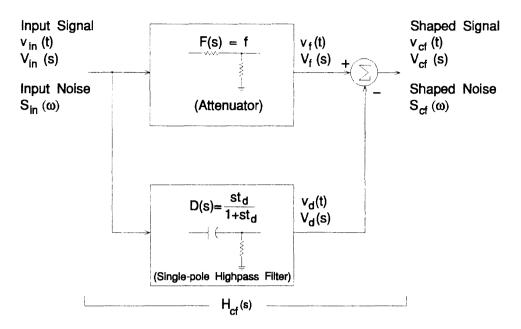

| Nowlin (Non-Delay-Line) CFD                                            |     |

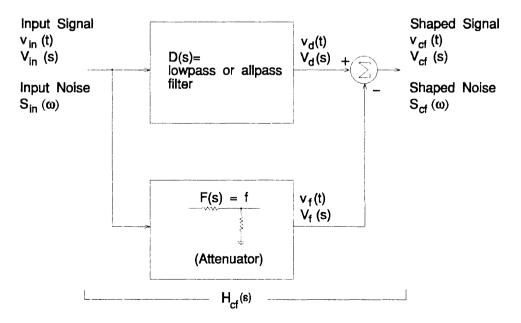

| Binkley (Non-Delay-Line) CFD                                           |     |

| Description                                                            |     |

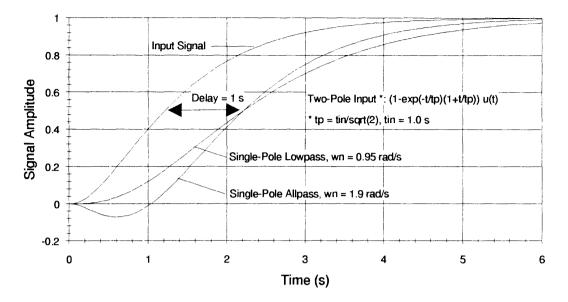

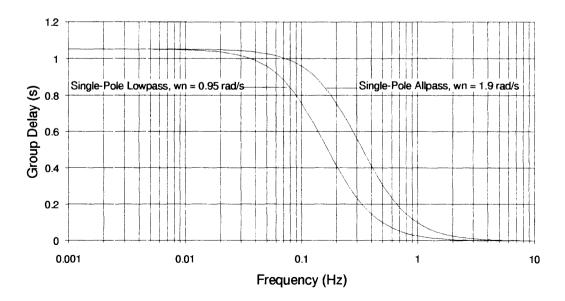

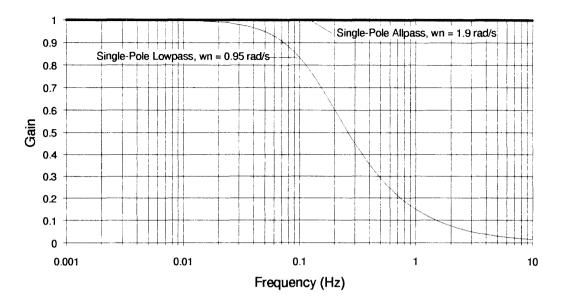

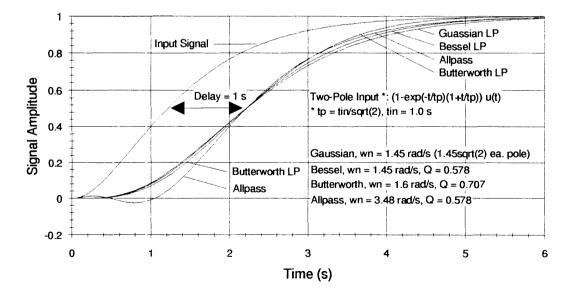

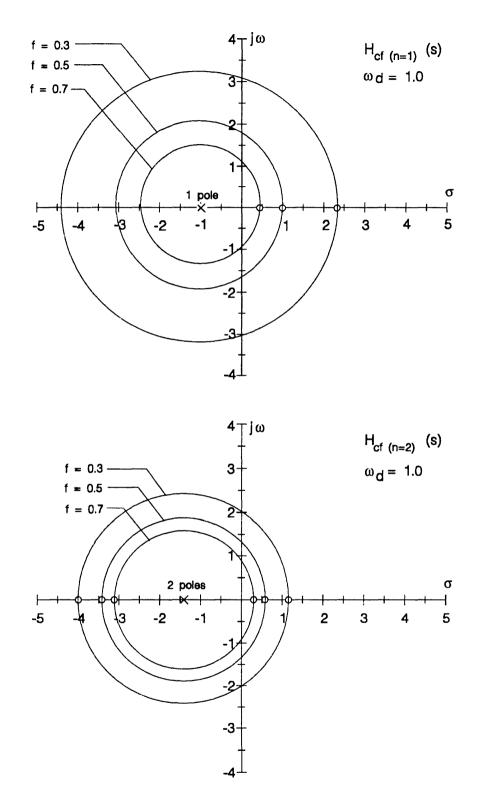

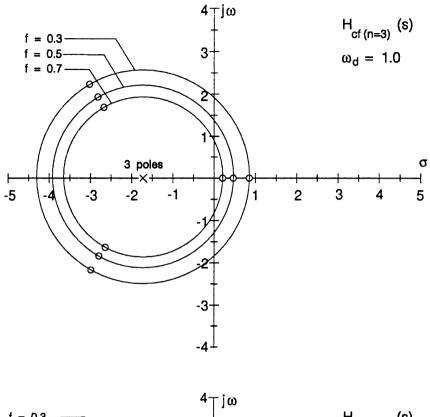

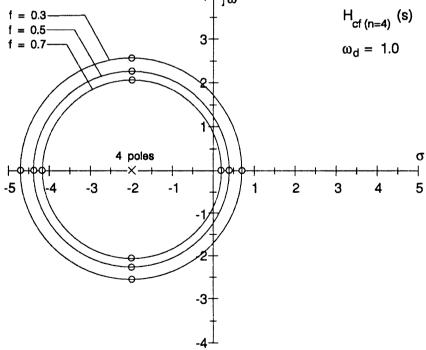

| Development of Delay-Line Approximation Filters                        |     |

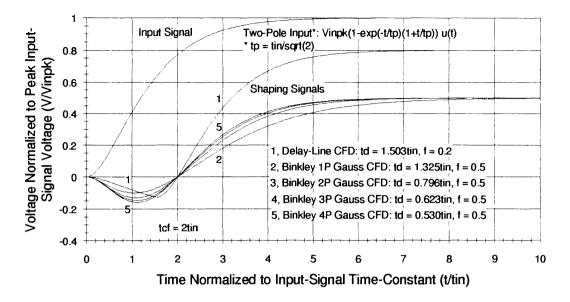

| Synthesis of Binkley CFD Circuits Using Gaussian Lowpass Filters       |     |

| Performance with Lowpass-Filtered Step Signals                         |     |

| Derivation of Shaping Signal                                           |     |

| Zero-Crossing Time                                                     |     |

| Shaping-Signal Amplitude and Slope                                     |     |

| Timing-Jitter Performance                                              |     |

| DC Baseline Effects on Timing Performance                              |     |

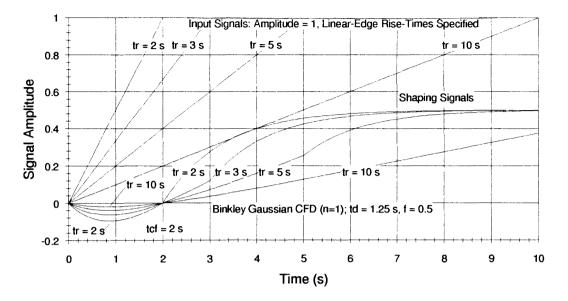

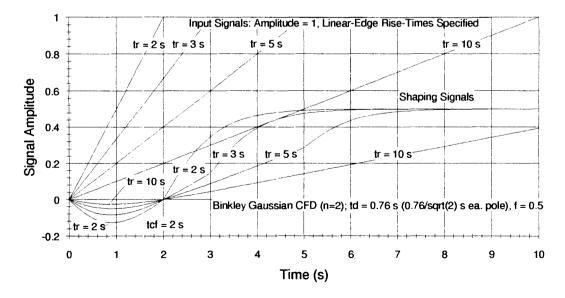

| Rise-Time Insensitivity of Binkley Gaussian CFDs with Linear-Edge      |     |

| Signals                                                                |     |

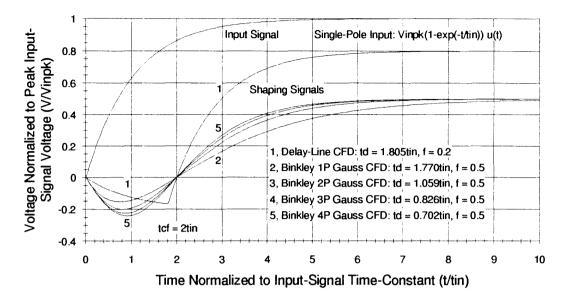

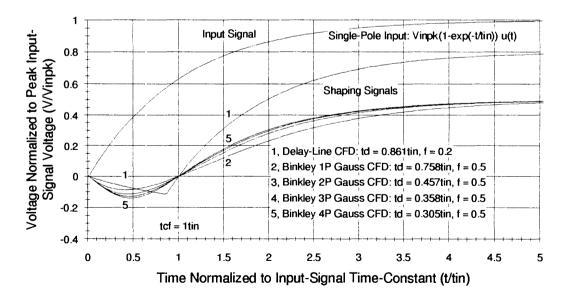

| Comparison of Delay-Line and Non-Delay-Line CFD Performance for        |     |

| Lowpass-Filtered Step Signals                                          | 137 |

| Comparison for Single-Pole Step Signals                                |     |

| Comparison for Two-Pole Step Signals                                   |     |

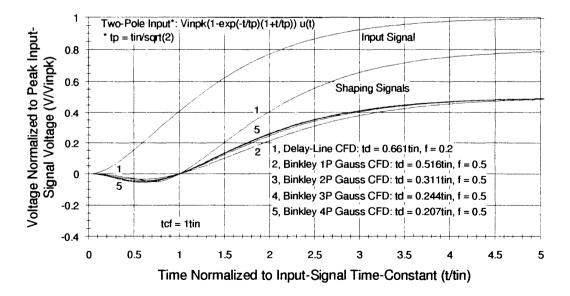

| CFD Performance with Scintillation Detectors                           |     |

| Timing-Discrimination Performance                                      |     |

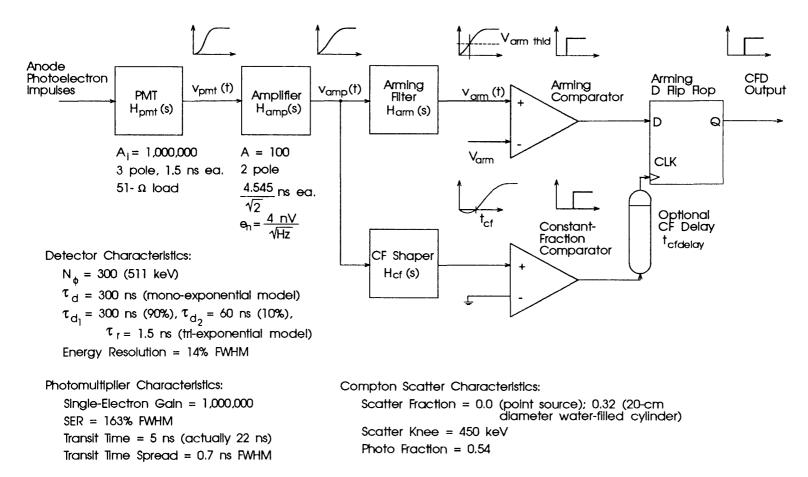

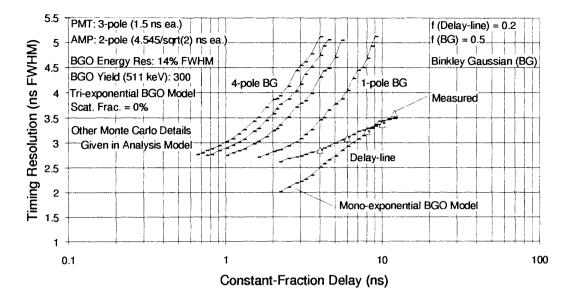

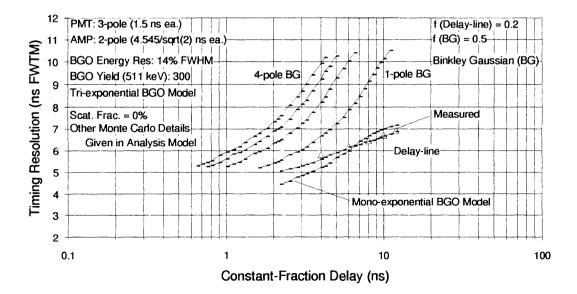

| Monte Carlo Simulation of Timing Resolution                            |     |

| Comparison of Monte Carlo Delay-Line and Non-Delay-Line                |     |

| CFD Timing Resolution                                                  | 145 |

| Energy-Discrimination Performance                                      |     |

| Statistical Analysis of Energy Discrimination                          |     |

|                                                                        |     |

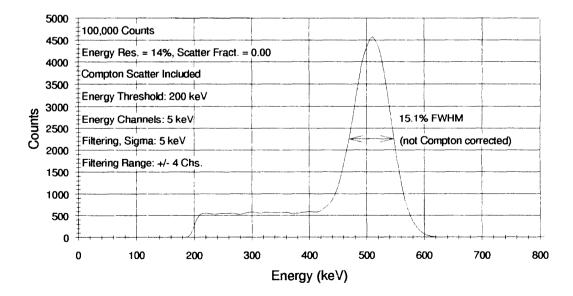

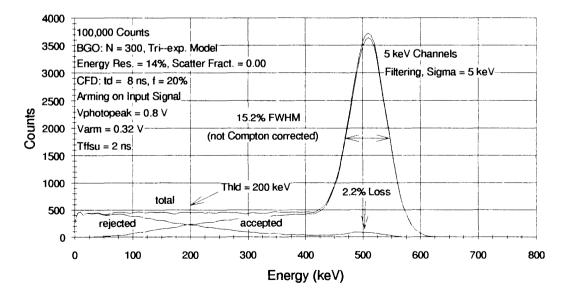

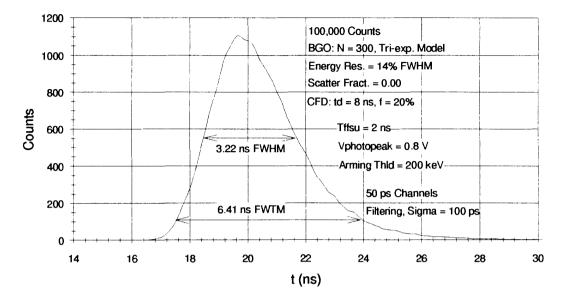

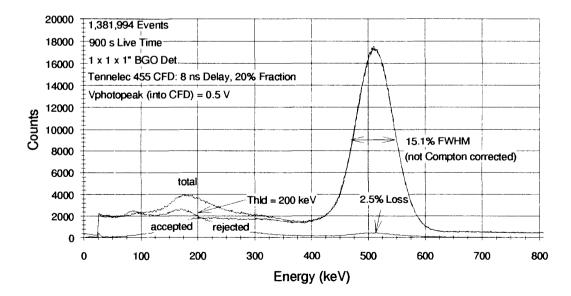

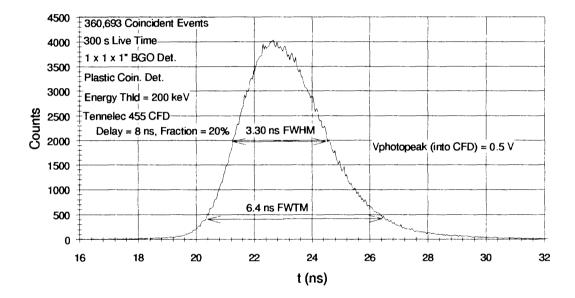

| Monte Carlo Simulation of Energy-Discrimination Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 150                                                                                                                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Comparison of Monte Carlo and Measured Energy-Discrimination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                          |

| and Timing Performance for a Commercial Delay-Line CFD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 151                                                                                                                                      |

| References for Section 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 153                                                                                                                                      |

| Appendix for Section 4 — Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 154                                                                                                                                      |

| 5. CFD Circuits, Including A Fully-Monolithic CMOS Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                          |

| Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                          |

| Review of CFD Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                          |

| Reported CFD Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                          |

| Other Reported Time Pick-Off Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                          |

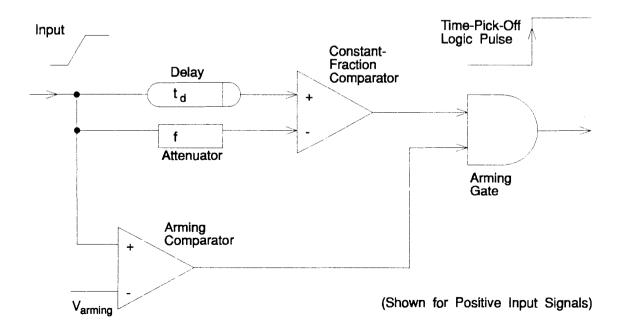

| Operation of CFD Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                          |

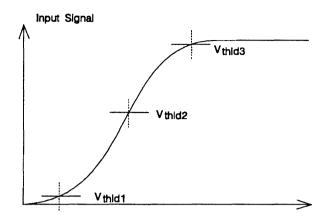

| Operation of CFD Arming and Constant-Fraction Comparators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                          |

| Operation of CFD Walk-Adjustment Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                          |

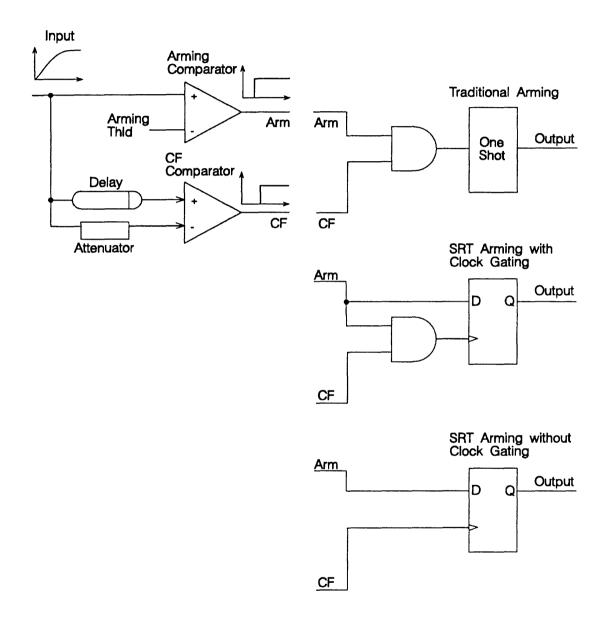

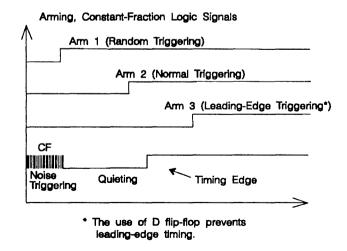

| Operation of CFD Arming Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                          |

| Design of a Fully-Monolithic CMOS CFD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                          |

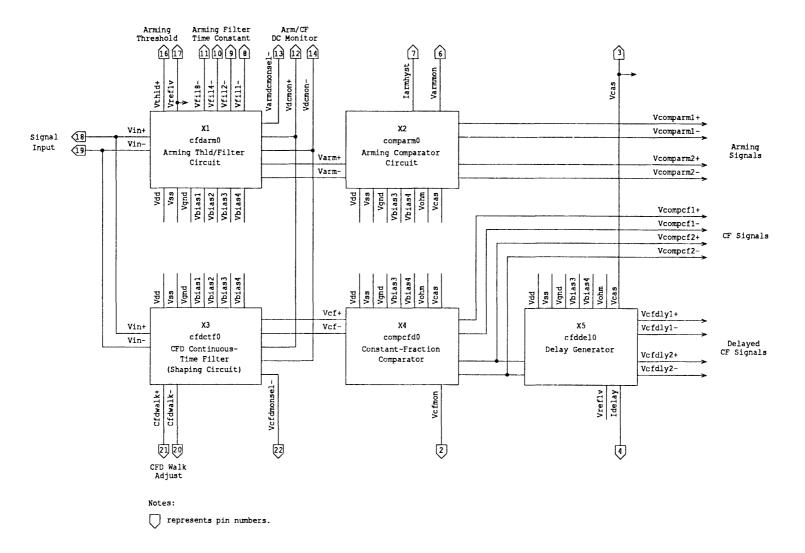

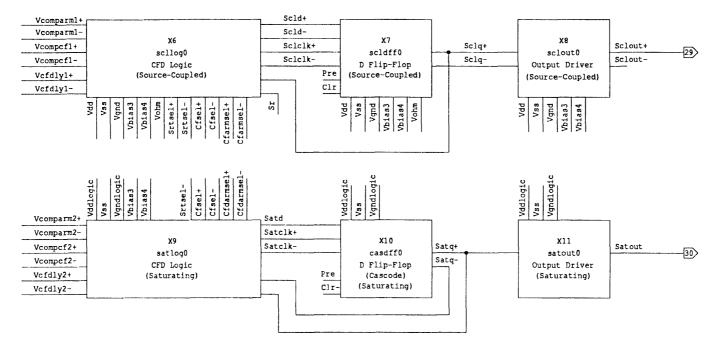

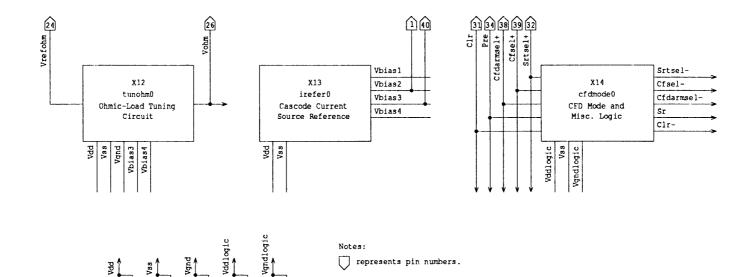

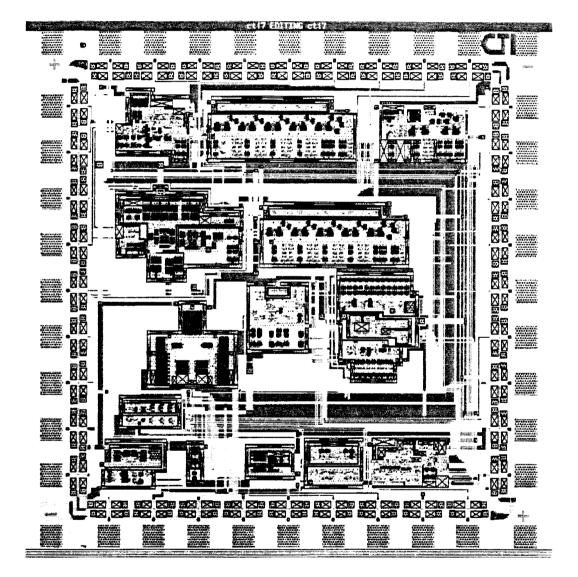

| Circuit Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                          |

| CMOS Process Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                          |

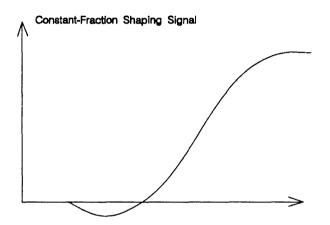

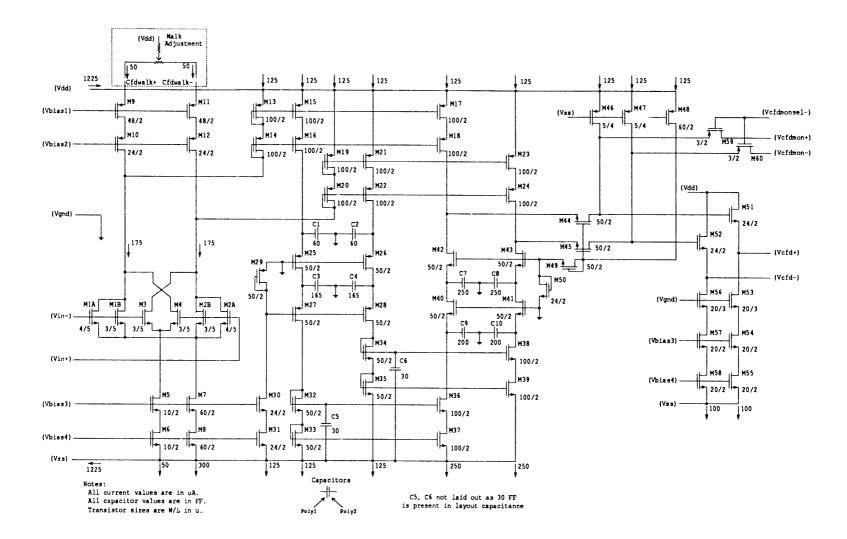

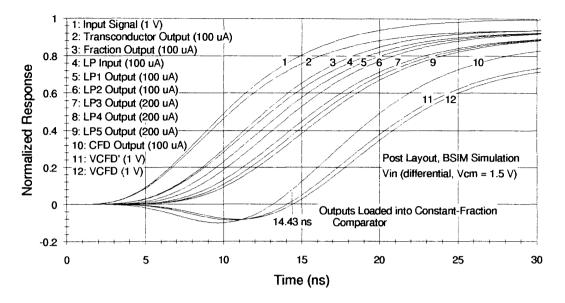

| Binkley Five-Pole Gaussian CFD Shaping Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                          |

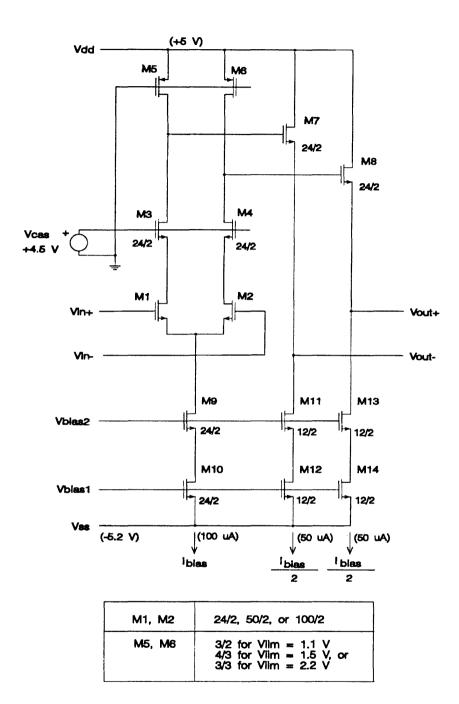

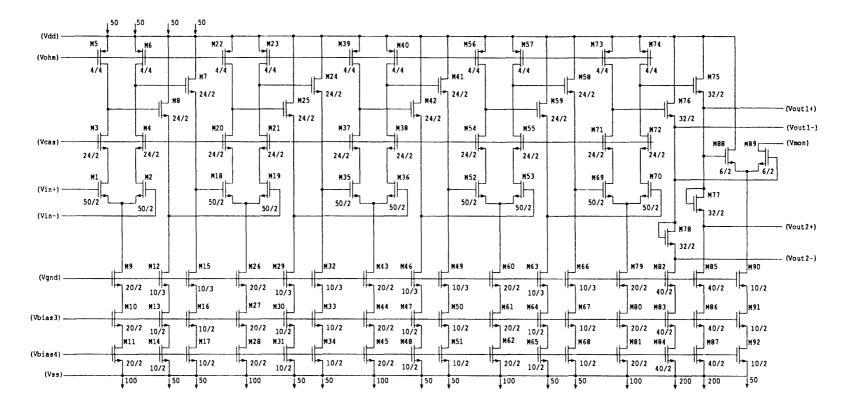

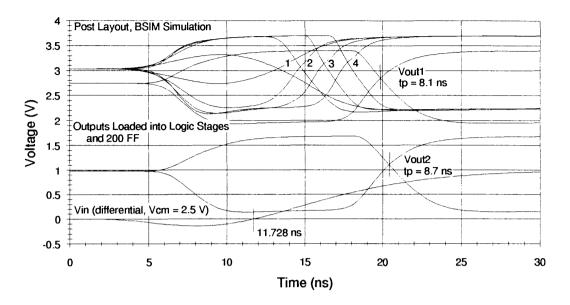

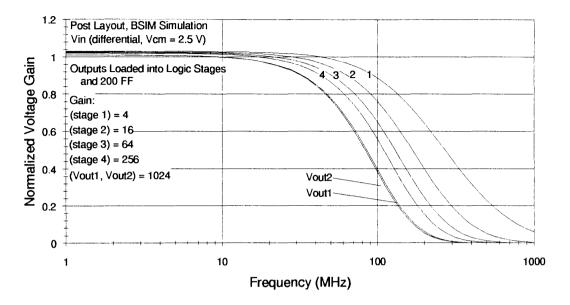

| Constant-Fraction Comparator Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                          |

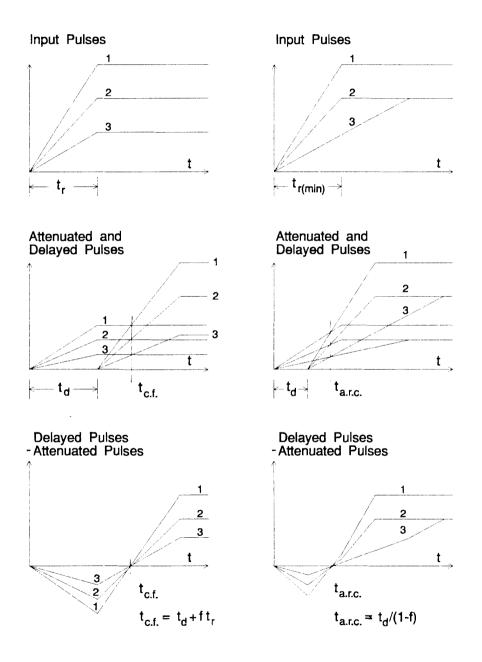

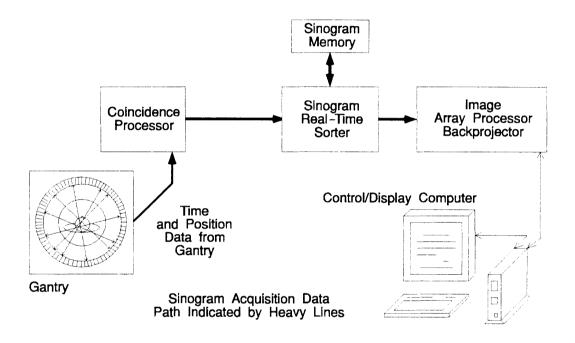

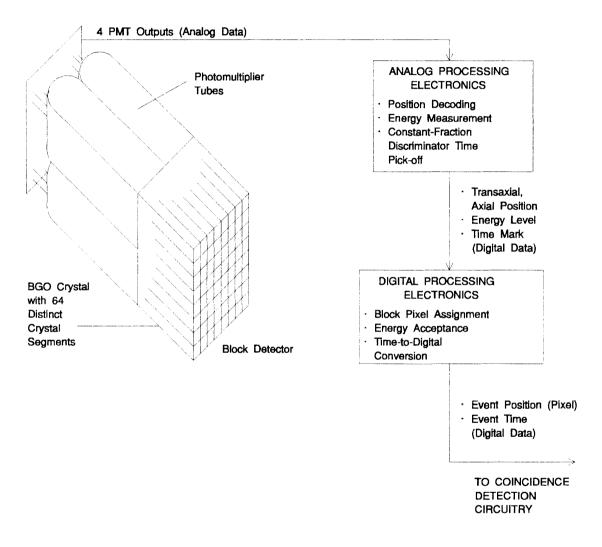

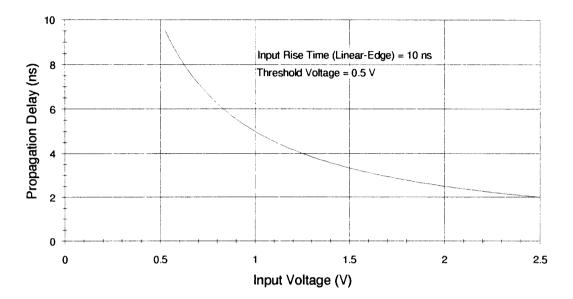

| Comparator Propagation-Delay Modeling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                          |

| Comparator Design Fundamentals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                          |