### University of Tennessee, Knoxville

# TRACE: Tennessee Research and Creative Exchange

**Doctoral Dissertations**

**Graduate School**

5-2016

# Feedback-Directed Management of Performance and Power for Emerging Computer Systems

Xing Fu

University of Tennessee - Knoxville, xfu1@vols.utk.edu

Follow this and additional works at: https://trace.tennessee.edu/utk\_graddiss

#### **Recommended Citation**

Fu, Xing, "Feedback-Directed Management of Performance and Power for Emerging Computer Systems." PhD diss., University of Tennessee, 2016. https://trace.tennessee.edu/utk\_graddiss/3694

This Dissertation is brought to you for free and open access by the Graduate School at TRACE: Tennessee Research and Creative Exchange. It has been accepted for inclusion in Doctoral Dissertations by an authorized administrator of TRACE: Tennessee Research and Creative Exchange. For more information, please contact trace@utk.edu.

To the Graduate Council:

I am submitting herewith a dissertation written by Xing Fu entitled "Feedback-Directed Management of Performance and Power for Emerging Computer Systems." I have examined the final electronic copy of this dissertation for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Doctor of Philosophy, with a major in Computer Engineering.

Xiaorui Wang, Major Professor

We have read this dissertation and recommend its acceptance:

Gregory D. Peterson, Seddik Djouadi, Mingjun Zhang

Accepted for the Council:

Carolyn R. Hodges

Vice Provost and Dean of the Graduate School

(Original signatures are on file with official student records.)

# Feedback-Directed Management of Performance and Power for Emerging Computer Systems

A Dissertation Presented for the Doctor of Philosophy

Degree

The University of Tennessee, Knoxville

Xing Fu

May 2016

© by Xing Fu, 2016

All Rights Reserved.

Dedicate to my family

# Acknowledgements

I appreciate my advisor Dr. Xiaorui Wang for his training preparing me well for research and academic career. Thanks for his patience while I am overcoming personal difficulties. I would like to express my sincere gratitude to Dr. Gregory Peterson and Dr. Seddik M. Djouadi. I learned a lot from their courses and obtained their recommendation letters when I applied for a faculty position of University of South Alabama. This dissertation would not have been possible without Dr. Mingjun Zhang's generous support. His insightful feedback improved the quality of dissertation significantly.

I am glad to have the opportunities to collaborate with Ming Chen, Yefu Wang, Xiaodong Wang at University of Tennessee. My experience at a VMWare core technology group will have profound impact on my career. I obtain deeper understanding of computer system research by collaborating with researchers from almost all well-known labs in the related field.

## Abstract

Emerging computing systems face the critical management challenge of both performance and power simultaneously. For example, distributed real-time embedded systems such as cyber-physical systems need to reduce power consumption while enforces CPU utilization bounds on multiple uniprocessors in order to meet end-to-end deadlines. Data centers operators attempt to oversubscribe data center power delivery networks to reduce throughput penalty during a power overload.

This dissertation presents latest development of a control framework which adopts novel control theoretic approaches to address emerging computing systems including multi-core real-time embedded systems, distributed real-time embedded systems, and data centers. The dissertation leverages task migration and cache partitioning mechanisms in multi-core systems to reduce power and energy consumption while control CPU utilizations. We then present a control algorithm for simultaneous temperature and utilization control for distributed real-time embedded systems. Algorithms and optimizations are presented to extend state-of-the-art model predictive control technique to overcome technical challenges such as scalability. We also adapt the parameter of a power controller widely adopted by IBM servers to improve its performance significantly. A power capping algorithm for an entire data center by shifting power between data center cooling systems and IT equipments is proposed for improving performance. Finally, we present a hierarchical heuristic to minimize energy consumption of Virtual Desktop Infrastructure without violating its performance constraints. Both theoretic analysis, hardware, and simulation

experiments demonstrate that our control algorithms can achieve better performance for those power-aware emerging computing systems compared to state-of-the-art baselines. The control framework also found successful applications in other systems such as cyber-physical surveillance systems. Results of feedback-directed management of performance and power based on control frameworks reveal wide potential applications in autonomic management in the era of cloud computing which consists of enormous mobile embedded devices and data centers.

# Table of Contents

| 1              | Introduction |                                                    |                                            | 1  |  |

|----------------|--------------|----------------------------------------------------|--------------------------------------------|----|--|

| 2 Related Work |              |                                                    | Vork                                       | 18 |  |

| 3              | Tas          | Task Consolidation in Multi-Core Real-Time Systems |                                            |    |  |

|                | 3.1          | System                                             | m Architecture                             | 26 |  |

|                | 3.2          | Core-l                                             | level Utilization Control                  | 28 |  |

|                |              | 3.2.1                                              | Task Model                                 | 28 |  |

|                |              | 3.2.2                                              | System Modeling                            | 29 |  |

|                |              | 3.2.3                                              | Controller Design and Analysis             | 31 |  |

|                | 3.3          | Proce                                              | ssor-level Task Consolidation              | 32 |  |

|                | 3.4          | System                                             | m Implementation                           | 34 |  |

|                | 3.5          | Evalu                                              | ation                                      | 37 |  |

| 4              | Cac          | he Pa                                              | rtitioning in Multi-Core Real-Time Systems | 43 |  |

|                | 4.1          | Proble                                             | em Formulation                             | 43 |  |

|                |              | 4.1.1                                              | Task Model                                 | 43 |  |

|                |              | 4.1.2                                              | Problem Formulation                        | 44 |  |

|                | 4.2          | Cache                                              | e-Aware Utilization Control                | 46 |  |

|                |              | 4.2.1                                              | System Modeling                            | 46 |  |

|                |              | 4.2.2                                              | Control Architecture                       | 49 |  |

|                | 4.3          | MOM                                                | IPC Controller Design                      | 52 |  |

|   |     | 4.3.1   | MOMPC Control                                       | 52 |

|---|-----|---------|-----------------------------------------------------|----|

|   |     | 4.3.2   | Primary Optimizer                                   | 53 |

|   |     | 4.3.3   | Secondary Optimizer                                 | 54 |

|   | 4.4 | Simula  | ation Environment                                   | 55 |

|   | 4.5 | Exper   | imental Results                                     | 58 |

| 5 | Pow | ver-Aw  | vare Utilization Control for Distributed RT Systems | 65 |

|   | 5.1 | Probe   | lm Formulation                                      | 65 |

|   |     | 5.1.1   | Task Model                                          | 65 |

|   |     | 5.1.2   | Problem Formulation                                 | 67 |

|   | 5.2 | End-to  | o-End Utilization Control                           | 68 |

|   |     | 5.2.1   | System Modeling                                     | 68 |

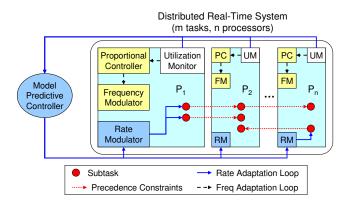

|   |     | 5.2.2   | Control Architecture                                | 70 |

|   | 5.3 | Task I  | Rate Adaptation Loop                                | 72 |

|   |     | 5.3.1   | System Model                                        | 72 |

|   |     | 5.3.2   | Controller Design                                   | 72 |

|   | 5.4 | CPU I   | Frequency Scaling Loop                              | 73 |

|   |     | 5.4.1   | System Model                                        | 73 |

|   |     | 5.4.2   | Controller Design                                   | 74 |

|   |     | 5.4.3   | Control Analysis for Model Variation                | 75 |

|   |     | 5.4.4   | Coordination Analysis                               | 76 |

|   | 5.5 | System  | m Implementation                                    | 77 |

|   | 5.6 | Empir   | rical Results                                       | 80 |

| 6 | Ten | nperat  | ure Control for Distributed Real-Time Systems       | 85 |

|   | 6.1 | Coord   | inated Control Solution                             | 85 |

|   |     | 6.1.1   | Task Model                                          | 85 |

|   |     | 6.1.2   | Control Architecture                                | 86 |

|   | 6.2 | Utiliza | ation Control Loop                                  | 88 |

|   |     | 6.2.1   | System Modeling                                     | 88 |

|   |     | 6.2.2  | Controller Design                                      | 89  |

|---|-----|--------|--------------------------------------------------------|-----|

|   | 6.3 | Thern  | nal Controller based on DVFS                           | 90  |

|   |     | 6.3.1  | System Model                                           | 90  |

|   |     | 6.3.2  | Controller Design                                      | 92  |

|   |     | 6.3.3  | Control Analysis for Model Variation                   | 93  |

|   | 6.4 | Thern  | nal Controller based on Rate Adaptation                | 95  |

|   |     | 6.4.1  | System Model                                           | 95  |

|   |     | 6.4.2  | Controller Design                                      | 96  |

|   |     | 6.4.3  | Control Analysis for Model Variation                   | 96  |

|   | 6.5 | Coord  | lination Analysis                                      | 98  |

|   |     | 6.5.1  | Coordinate Thermal Controller based on Rate Adaptation | 98  |

|   |     | 6.5.2  | Coordinate Thermal Controller based on DVFS            | 99  |

|   | 6.6 | System | m Implementation                                       | 100 |

|   |     | 6.6.1  | Testbed and Workload                                   | 100 |

|   |     | 6.6.2  | Control Components                                     | 101 |

|   |     | 6.6.3  | Simulations and Workload                               | 103 |

|   | 6.7 | Empir  | rical Results                                          | 104 |

| 7 | Pov | ver Ov | versubscription in Data Centers                        | 109 |

|   | 7.1 | Backg  | ground about Circuit Breaker                           | 109 |

|   | 7.2 | CB-A   | ware Adaptive Power Control                            | 113 |

|   |     | 7.2.1  | CB-Adaptive Control                                    | 113 |

|   |     | 7.2.2  | Temperature-aware CB-Adaptive                          | 116 |

|   | 7.3 | Discus | ssion                                                  | 117 |

|   | 7.4 | Imple  | mentation                                              | 121 |

|   | 7.5 | Evalu  | ation Results                                          | 123 |

|   | 7.6 | Power  | Provisioning Analysis                                  | 130 |

| 8 | Dat | a Cen  | ter Level Power Control                                | 133 |

|   | 8 1 | Syster | m Architecture                                         | 133 |

|    | 8.2              | The C   | Outer Loop Power Controller                           | 135  |

|----|------------------|---------|-------------------------------------------------------|------|

|    |                  | 8.2.1   | System Modeling                                       | 135  |

|    |                  | 8.2.2   | Controller design                                     | 137  |

|    |                  | 8.2.3   | Server Inlet Temperature Constraint                   | 139  |

|    |                  | 8.2.4   | Coordination Analysis                                 | 140  |

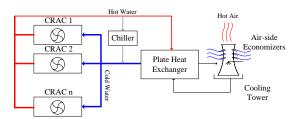

|    | 8.3              | Air-sic | de Economizer                                         | 140  |

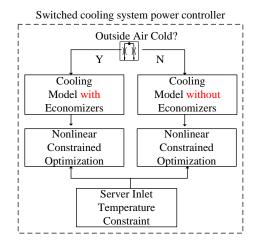

|    |                  | 8.3.1   | Switched cooling system power controller              | 141  |

|    | 8.4              | Evalua  | ation                                                 | 143  |

|    |                  | 8.4.1   | Baselines                                             | 143  |

|    |                  | 8.4.2   | Power Emergency                                       | 145  |

|    |                  | 8.4.3   | Control Accuracy and Application Performance          | 147  |

|    |                  | 8.4.4   | Enforcement of Thermal Constraint                     | 148  |

| 9  | End              | l-to-Er | nd Energy Management of Virtual Desktop Infrastructur | e150 |

|    | 9.1              | Energ   | y Management with Performance Guarantee               | 150  |

|    |                  | 9.1.1   | System Architecture                                   | 150  |

|    |                  | 9.1.2   | Performance Model                                     | 152  |

|    |                  | 9.1.3   | Optimization                                          | 155  |

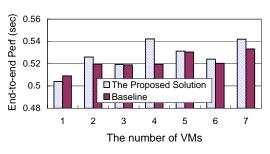

|    | 9.2              | Evalua  | ation Results                                         | 157  |

|    |                  | 9.2.1   | Implementation                                        | 157  |

|    |                  | 9.2.2   | Baseline                                              | 159  |

|    |                  | 9.2.3   | Experimental results                                  | 160  |

| 10 | ) Cor            | clusio  | n                                                     | 162  |

| Bi | Bibliography 160 |         |                                                       | 166  |

| V  | ita              |         |                                                       | 183  |

# List of Tables

| 4.1 | System model parameters in (4.6) for typical benchmarks | 56  |

|-----|---------------------------------------------------------|-----|

| 7.1 | Test bed circuit breaker at $40^{\circ}C$               | 111 |

| 7.2 | Overload capacity                                       | 120 |

| 7.3 | Power provisioning                                      | 132 |

| 8.1 | Comparison of Baseline 1 and No-CRAC-Throttle           | 145 |

| 9.1 | System Configuration                                    | 158 |

# List of Figures

| 3.1 | System architecture                                                     | 26 |

|-----|-------------------------------------------------------------------------|----|

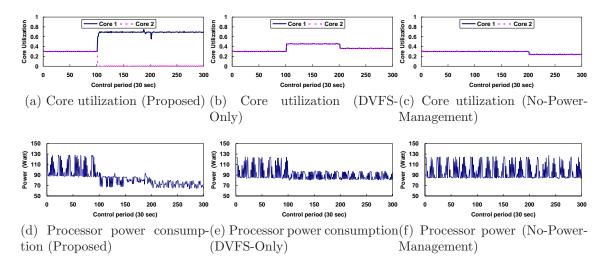

| 3.2 | Typical runs of three solutions (Proposed, DVFS-Only, and No-Power-     |    |

|     | Management) on the hardware testbed. The solutions are activated at     |    |

|     | the 100th control period and handle a 20% execution time reduction      |    |

|     | at the 200th control period                                             | 37 |

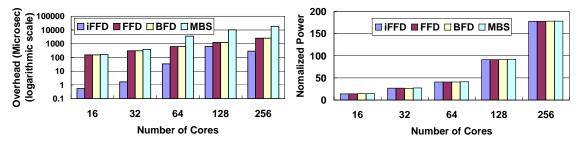

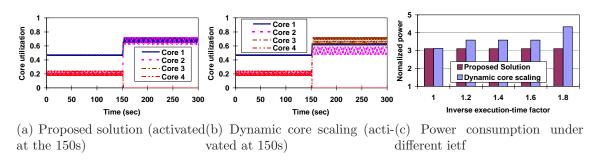

| 3.3 | Comparison among the three heuristics                                   | 39 |

| 3.4 | Comparison between the proposed solution and Dynamic core scaling.      | 40 |

| 4.1 | Two-level utilization control architecture                              | 50 |

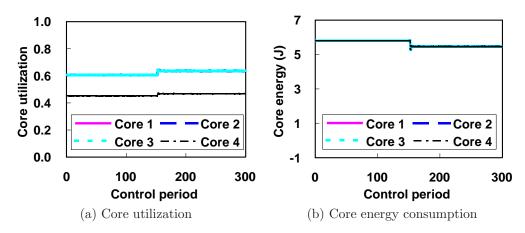

| 4.2 | A typical run of the proposed cache-aware control solution. The         |    |

|     | MOMPC controllers (primary optimizers) are activated at time 100 to     |    |

|     | control utilizations and the secondary optimizers are enabled at time   |    |

|     | 200 for energy optimization                                             | 58 |

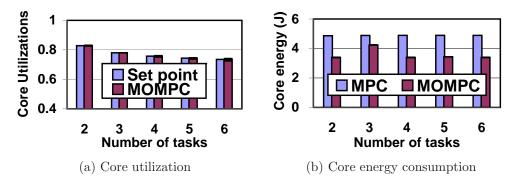

| 4.3 | The proposed cache-aware solution (i.e., MOMPC) controls core uti-      |    |

|     | lization to desired set points while saving more energy than MPC        | 62 |

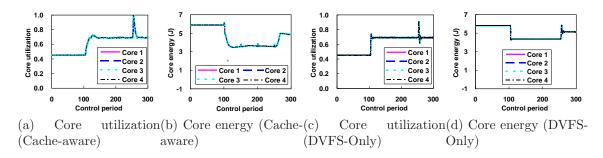

| 4.4 | A typical run of the baseline Dynamic repartitioning (activated at time |    |

|     | 150)                                                                    | 62 |

| 4.5 | Typical runs of cache-aware control and DVFS-Only under workload        |    |

|     | variations                                                              | 62 |

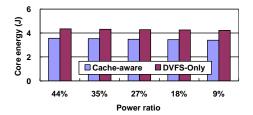

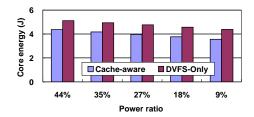

| 4.6 | Comparison with DVFS-Only when power ratio varies (before workload      |    |

|     | increases)                                                              | 63 |

| 4.7 | Comparison with DVFS-Only when power ratio varies (after workload        |     |

|-----|--------------------------------------------------------------------------|-----|

|     | increases)                                                               | 63  |

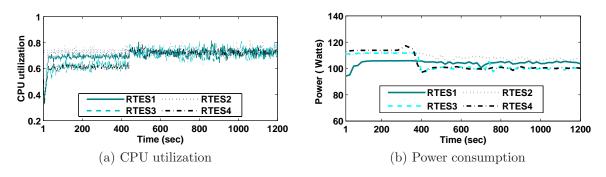

| 5.1 | Utilization control architecture                                         | 70  |

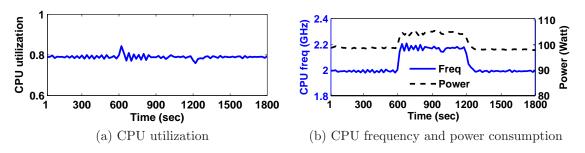

| 5.2 | CPU utilization control by frequency scaling under a workload increase   |     |

|     | from 600s to 1200s                                                       | 80  |

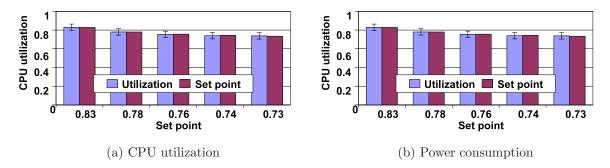

| 5.3 | CPU utilization control by frequency scaling under different set points. | 81  |

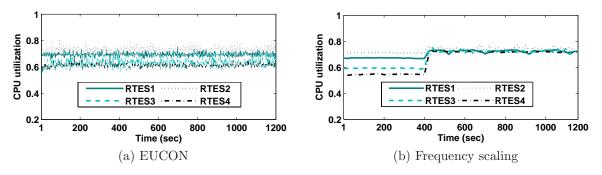

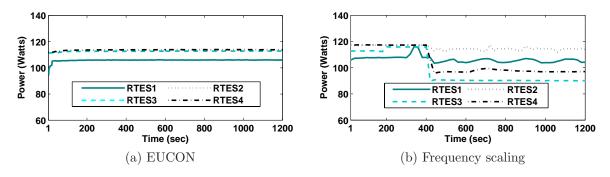

| 5.4 | Comparison of control accuracy between EUCON and the frequency           |     |

|     | scaling loop                                                             | 82  |

| 5.5 | Comparison of power consumption between EUCON and the frequency          |     |

|     | scaling loop                                                             | 82  |

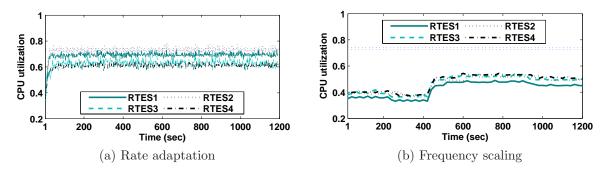

| 5.6 | Infeasible utilization control by frequency scaling or EUCON separately. | 84  |

| 5.7 | Result of the coordinated utilization control solution                   | 84  |

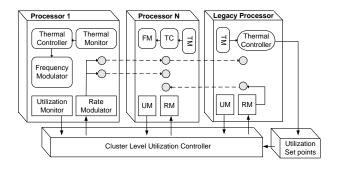

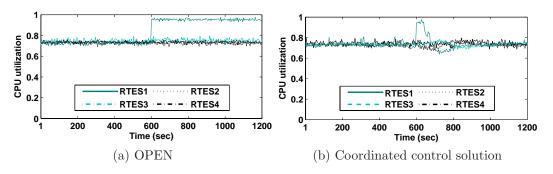

| 6.1 | Coordinated Control Architecture                                         | 86  |

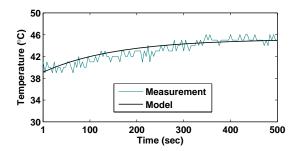

| 6.2 | Model Prediction vs. Measurement                                         | 92  |

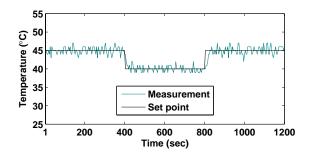

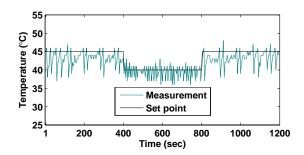

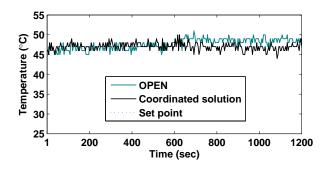

| 6.3 | Thermal Controller                                                       | 103 |

| 6.4 | Ad Hoc                                                                   | 103 |

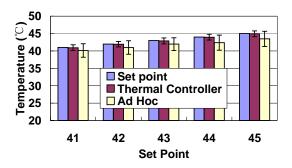

| 6.5 | Comparison of thermal controller and Ad Hoc under different temper-      |     |

|     | ature set points                                                         | 105 |

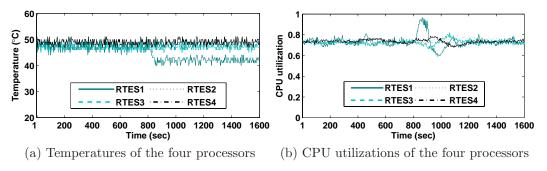

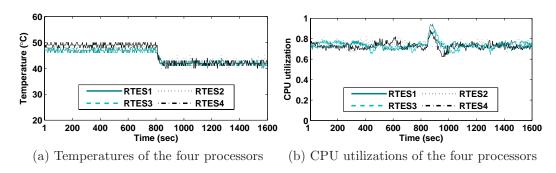

| 6.6 | Thermal variation on a single processor (RTES1)                          | 106 |

| 6.7 | Thermal variations on all the four processors                            | 106 |

| 6.8 | Variations of task execution times on a single processor (RTES1)         | 108 |

| 6.9 | Comparison of system temperature under the coordinated control           |     |

|     | solution and OPEN                                                        | 108 |

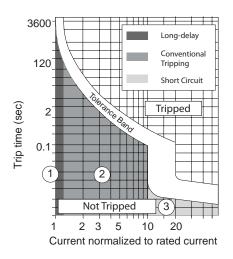

| 7.1 | The trip curve of a typical circuit breaker.                             | 111 |

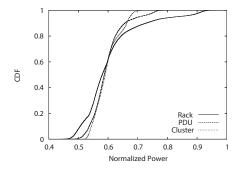

| 7.2 | Power CDF of a real Google data center from [46]                         | 118 |

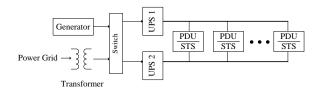

| 7.3 | A typical power delivery system of a data center                         | 119 |

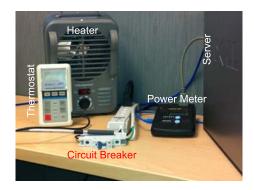

| 7.4 | Hardware test bed                                                        | 121 |

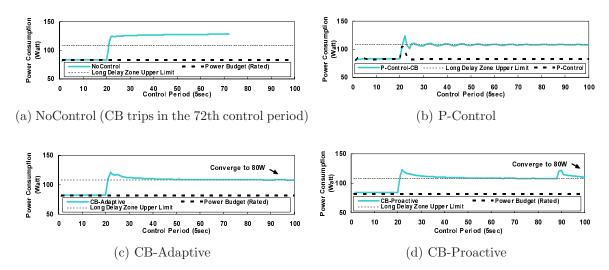

| 6.1  | The comparison of CB-Adaptive and CB-Proactive with baselines          | 120 |

|------|------------------------------------------------------------------------|-----|

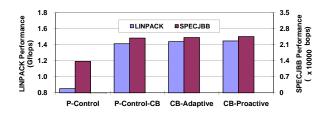

| 7.6  | The LINKPACK and SPECJBB performance comparison                        | 127 |

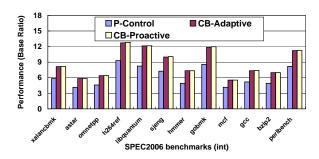

| 7.7  | The SPEC CPU2006 int performance comparison                            | 128 |

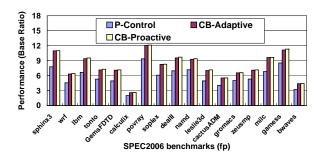

| 7.8  | The SPEC CPU2006 fp performance comparison                             | 128 |

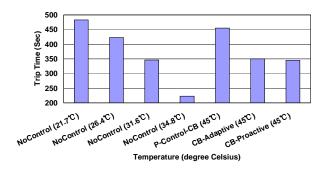

| 7.9  | The impact of temperature on NoControl and three CB-aware solutions.   | 130 |

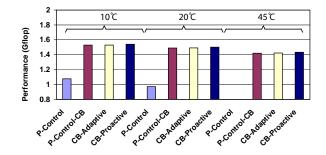

| 7.10 | Impact of temperature on LINPACK performance                           | 130 |

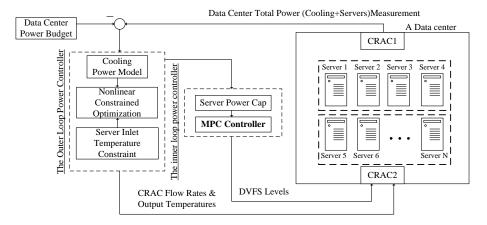

| 8.1  | System Architecture                                                    | 133 |

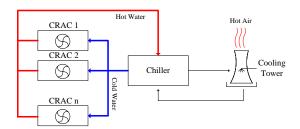

| 8.2  | Diagram of a Data Center Cooling System                                | 136 |

| 8.3  | Diagram of a Data Center Cooling System with a Chiller Bypass via      |     |

|      | Heat Exchanger Economizer Mode                                         | 141 |

| 8.4  | Switch Control                                                         | 142 |

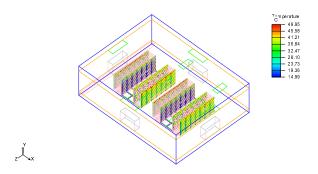

| 8.5  | The Simulated Data Center in AirPak and Fluent                         | 145 |

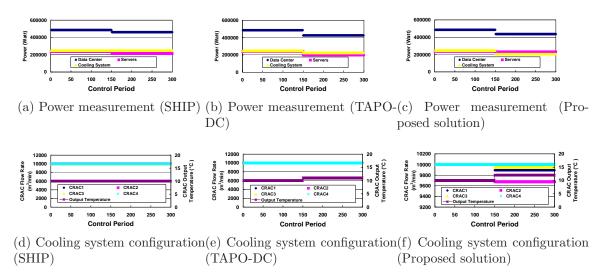

| 8.6  | Typical runs of three solutions (Proposed solution, SHIP, and TAPO-    |     |

|      | DC)                                                                    | 146 |

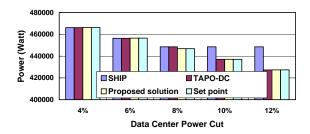

| 8.7  | Data center power                                                      | 147 |

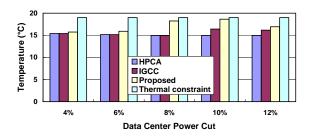

| 8.8  | Comparison of three solutions under various data center power budget   |     |

|      | reductions (Proposed solution, SHIP, and TAPO-DC)                      | 148 |

| 8.9  | Thermal threshold guarantee                                            | 149 |

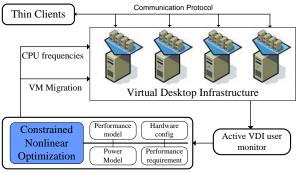

| 9.1  | Integrated management architecture for virtual desktop infrastructure. | 151 |

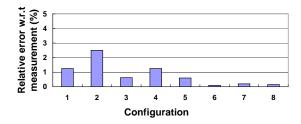

| 9.2  | Validation of the performance model against measurement                | 154 |

# Chapter 1

# Introduction

Traditionally, academic and industry focused on increasing CPU processor performance by shrinking feature sizes and increasing transistor density. With the continued scaling, power related issues now are first-priority design constraints of CPU design. Moreover, the number of huge data centers grows rapidly to accommodate the demand of cloud computing and supercomputing. The power related issues such as energy efficiency and thermal management and power capping rise in various computing systems from multi-core systems to data centers and are major hurdles on the road to future computing system. In this dissertation, several integrated control solution are proposed to effectively manage both power and performance by adopting novel control-theoretic methodologies for various emerging computing systems.

## Task Consolidation in Multi-Core Real-Time Systems

Multi-core processors have become a primary trend in the current processor development due to well-known technological barriers such as the "Power Wall" and "Instruction-level Parallelism Wall". As a result, future high-performance real-time embedded systems are anticipated to be equipped with multi-core processors, or even many-core processors (i.e., processors with tens or hundreds of cores). However, power consumption still remains the major constraint for the further throughput improvement of multi-core processors. Therefore, new scheduling algorithms must

be developed to minimize power consumption while achieving the desired timeliness guarantees for multi-core (and many-core) real-time embedded systems.

Although various power/energy-efficient scheduling algorithms have recently been proposed for multi-core real-time embedded systems (e.g., [119]), existing studies focus on open-loop solutions such as *static* speed scheduling and offline DVFS (dynamic voltage and frequency scaling) configurations. While those open-loop solutions can work effectively for traditional real-time embedded systems deployed in closed execution environments, they may incur degraded performance in terms of power/energy efficiency and real-time guarantees when applied to real-time embedded systems that execute in open and *unpredictable* environments in which workloads (*e.g.*, WCETs) are unknown and may vary significantly at runtime. Therefore, in order to achieve runtime power optimization and real-time guarantees, novel online strategies must be designed to dynamically respond to execution time variations for multi-core real-time embedded systems running in unpredictable environments.

Recently, feedback control techniques have been demonstrated to be a valid tool in providing timeliness guarantees for real-time embedded systems by adapting to workload variations based on dynamic feedback. In particular, feedback-based *CPU* utilization control [93] has been shown to be an effective way of providing real-time guarantees for soft real-time systems. The goal of utilization control is to enforce appropriate schedulable utilization bounds on all CPU cores in a real-time embedded system, despite significant uncertainties in system workloads. As a result, utilization control can guarantee all the real-time deadlines of the system without accurate knowledge of the workload, such as task execution times. However, existing utilization control algorithms are not designed to provide online power minimization for multicore real-time systems. A recent study [141] proposes a power-aware utilization control approach that adopts DVFS to achieve utilization control and power efficiency. While this solution can effectively reduce dynamic power consumption, it cannot minimize static (leakage) power consumption because it does not minimize the number of active CPU cores in response to workload variations. As chip feature sizes continue

to shrink, it becomes increasingly important to minimize leakage power since leakage power consumption is becoming a major contributor to the total power consumption of a multi-core processor [73].

To minimize the number of active CPU cores, it is necessary to migrate tasks among the cores for consolidation. In traditional multiprocessor real-time systems, tasks are often assigned to processors in a static way, at design time, due to the large overheads of online task migrations. A key advantage of the shared L2 caches in many multi-core real-time systems is that the overhead of migrating a task among cores is less than 40 microseconds, which is sufficiently small in many real systems [12][153]. This feature allows multi-core real-time systems to be more power-efficient since the leakage power consumption can be minimized by dynamic task consolidation. Although task migrations in multi-core processors may cause L1 cache misses, the typical penalty of an L1 cache miss is only 10-30 CPU cycles. In contrast, in traditional multiprocessor real-time systems, task migrations can be expensive by having frequent L2 cache misses, whose penalty is approximately 100-300 CPU cycles [12].

In this dissertation, we propose a novel *online* solution that integrates feedback control with optimization strategies to minimize (both dynamic and leakage) power consumption and guarantee timeliness for multi-core real-time embedded systems. Our solution monitors the utilization of each CPU core in the system and dynamically responds to execution time variations by conducting per-core DVFS and task consolidation among the cores in a multi-core processor. In our solution, each CPU core has a utilization controller that throttles the DVFS level of the core so that its utilization stays slightly below the schedulable bound for minimized dynamic power with real-time guarantees. To minimize leakage power, we dynamically consolidate real-time tasks onto a few of the most power-efficient cores on a longer timescale by utilizing the small overhead of migrating tasks among different cores within a multi-core processor. The migration is subject to the schedulable utilization bounds of the active cores. We then shut down unused CPU cores for minimized leakage power.

## Cache-Aware Utilization Control for Energy Efficiency in Multi-Core RT Systems

Despite a significant amount of existing work on power management for traditional multi-processor real-time systems, existing power management algorithms are not designed to sufficiently utilize the new features available in many multi-core processors, such as shared L2 caches and per-core DVFS (Dynamic Voltage and Frequency Scaling), to effectively minimize processor energy consumption while providing real-time guarantees. For example, most current power/energy management algorithms assume that all the cores of a processor can only have a uniform DVFS level while per-core DVFS is already available (e.g., AMD's Independent Dynamic Core Technology) to allow better power/energy efficiency. Intel's new 48-core processor also features per-tile DVFS with two cores within each tile. In addition, the current algorithms are not designed to dynamically partition the shared L2 caches among the different cores for better real-time performance and to conduct dynamic cache resizing to place rarely accessed cache units into low-power modes for minimized cache leakage power consumption. Therefore, novel power management algorithms are needed to utilize the shared L2 caches and per-core DVFS for maximized energy savings.

The existing research on power-aware utilization control primarily relies on DVFS by assuming that the task execution times can be adapted linearly with the CPU frequency. While this assumption is valid for real-time tasks that are computation intensive, memory-intensive tasks can have approximately 75% of their instructions that are load or store [104, 60]. Consequently, when a processor core is running memory-intensive tasks and the CPU frequency is set to the highest level, the utilization can still be above the desired schedulable bound, resulting in undesired deadline misses. In this case, the cache size partitioned to the core can be increased to reduce the cache miss rate and cache access latency due to reduced main memory access delay. As a result, the CPU utilization can be lowered for better real-time performance. Similarly, if the utilization is lower than the bound, even when the frequency is already throttled to the lowest level, the active cache size can be reduced

and rarely accessed cache units can be put into low-power modes to minimize cache leakage power.

In this dissertation, we propose a two-level utilization control solution for energy efficiency in multi-core real-time systems. At the core level, our solution utilizes both per-core DVFS and dynamic L2 cache partitioning to address two (often conflicting) optimization objectives: controlling the CPU utilization of each core to its desired schedulable bound and minimizing the core energy consumption. Since the utilization contributed by a periodic real-time task is determined by both its CPU frequencydependent and frequency-independent execution times [24], per-core DVFS and cache partitioning can be used to adapt the frequency-dependent and independent portions, respectively. A key challenge in our design is that traditional control theory, such as PID (Proportional-Integral-Derivative) and MPC (Model Predictive Control), cannot effectively handle multiple optimization objectives. Therefore, we propose a novel utilization controller, based on advanced Multi-Objective MPC control theory [96][22], to achieve both optimization objectives. At the processor level, a cache demand arbitrator is proposed to coordinate the cache size demand from each core and conduct dynamic cache resizing to minimize the leakage power consumption of the shared L2 caches.

#### Power-Aware Utilization Control for Distributed RT Systems

Traditional approaches to handling end-to-end real-time tasks, such as end-to-end scheduling [129] and distributed priority ceiling [111], rely on schedulability analysis, which requires a priori knowledge of the tasks' Worst-Case Execution Times (WCET). While such open-loop approaches work effectively in the closed execution environments of traditional real-time systems, they may violate the desired timing constraints or severely underutilize the system when task execution times are highly unpredictable. In recent years, a new category of real-time applications called Distributed Real-time Embedded (DRE) systems has been rapidly growing. DRE systems commonly execute in open and unpredictable environments in which workloads are unknown and vary significantly at runtime. Such systems include

data-driven systems whose execution is heavily influenced by volatile environments. For example, task execution times in vision-based feedback control systems depend on the content of live camera images of changing environments [62]. DRE systems call for a paradigm shift from classical real-time computing that relies on accurate characterization of workloads and platform.

Recently, feedback control techniques have shown a lot of promise in providing real-time guarantees for DRE systems by adapting to workload variations based on dynamic feedback. In particular, feedback-based CPU utilization control [93][144] has been demonstrated to be an effective way of meeting the end-to-end deadlines for soft DRE systems. The primary goal of utilization control is to enforce appropriate schedulable utilization bounds (e.g., the Liu and Layland bound for RMS) on all the processors in a DRE system, despite significant uncertainties in system workloads. In the meantime, it tries to maximize the system utility by controlling CPU utilizations to stay slightly below their schedulable bounds so that the processors can be utilized to the maximum degree. Utilization control can also enhance system survivability by providing overload protection against workload fluctuation [139].

However, previous research on CPU utilization control focuses exclusively on task rate adaptation by assuming task rates can be continuously tuned within specified ranges. While rate adaptation is an effective actuator for some DRE systems, it has several limitations. First, it is often infeasible to achieve desired utilization set points by rate adaptation alone [140]. For example, many DRE systems are configured based on tasks' WCETs. Consequently, even when all the tasks are running at their highest rates, CPU utilizations are still way below the desired set points, resulting in severely underutilized systems. In that case, CPU frequency scaling can be used for power savings while still guaranteeing task schedulability. Second, many tasks in DRE systems only support a few discrete rates. While optimization strategies [40][77] are developed to handle discrete task rates, they rely on the common assumption that task WCETs are known a priori and accurate, which makes them less applicable to DRE systems running in unpredictable environments. Third, the model of task

rate in many applications could be complex and vary at runtime based on application evolution [55][28]. As a result, the estimated task rate ranges are often inaccurate and may change significantly online, which may lead to unexpected rate saturation and even deadline misses when CPU utilizations are higher than the schedulable bounds and can be lowered down only by rate adaptation. Finally, some DRE systems may not allow rate adaptation for any tasks but their CPU utilizations still need to be controlled. Therefore, it is important to explore complementary ways for effective CPU utilization control.

In this paper, we propose to use Dynamic Voltage and Frequency Scaling (DVFS) in conjunction with rate adaptation for utilization control. Since the CPU utilization contributed by a real-time periodic task is determined by both its rate and its execution time, CPU frequency scaling can be used to adapt task execution time for power-efficient utilization control. The integration of DVFS in utilization control introduces several new challenges. First, a centralized controller for simultaneous rate adaptation and DVFS would have a Multi-Input-Multi-Output (MIMO) nonlinear model. Therefore, multiple linear control loops are more preferable for acceptable runtime overhead. Second, different control loops need to be carefully designed to coordinate together for the desired control functions. Finally, the control accuracy and global system stability of the coordinated control solution must be analytically assured.

This dissertation presents a two-layer coordinated CPU utilization control architecture. The primary control loop uses DVFS to locally control the CPU utilization of each processor. In the meantime, the secondary control loop adopts rate adaptation to control the utilizations of all the processors at the cluster level on a finer timescale.

The rest of this chapter is organized as follows. We formulate the new CPU utilization control problem in Section 5.1. Section 5.2 presents the system model and control architecture. Section 5.3 briefly introduces the rate adaptation loop while Section 5.4 provides the detailed design and analysis of the CPU frequency scaling

loop. Section 5.5 discusses the implementation of the control architecture in a realtime middleware system. Section 5.6 presents our empirical results on a physical testbed.

## Coordinated Temperature and Utilization Control for Distributed Real-Time Embedded Systems

A new class of real-time applications called distributed real-time embedded (DRE) systems has been rapidly growing. DRE systems include wireless sensor networks and cyber-physical systems. They commonly execute in open and *unpredictable* environments, in which both workloads and system conditions are unknown and may vary significantly at runtime. For example, task execution times in vision-based surveillance systems depend on the content of live camera images of changing environments [62]. Therefore, DRE applications commonly require runtime control and guarantees of end-to-end timeliness for their proper operation.

However, existing work on utilization control can only provide timeliness guarantees, while today's DRE systems face an increasing probability of overheating and even thermal failures, due to their continuously decreasing feature size and increasing demand for computation capabilities. For example, recent studies show that 50% of all electronics failures are related to overheating [152]. More specifically, the lifetime of a processor can be approximately halved if it runs 10-15°C higher than its normal temperature range [134]. Furthermore, a 15°C increase in temperature could double the failure rate of a disk drive [10]. Therefore, thermal constraints also need to be strictly enforced for DRE systems. Although some recent research has proposed optimization algorithms based on task allocation and configurations of processor voltage/frequency to achieve minimized system temperature and guaranteed real-time performance [37, 135], those open-loop solutions cannot be directly applied to DRE systems where workloads and system conditions may vary at runtime. While some dynamic thermal management (DTM) approaches have been proposed for general computer systems (e.g., [30]), they cannot provide desired real-time guarantees for

DRE systems. Therefore, existing work can only provide either timeliness guarantees or thermal control in an *isolated* manner.

Simultaneous thermal and utilization control is challenging because the desired guarantees cannot be achieved by simply putting the two control loops together. Without effective coordination, individual control solutions may conflict with each other. For example, many thermal management methods rely on dynamic voltage and frequency scaling (DVFS), which may significantly impact the execution times of the real-time tasks running in the systems. As a result, the timeliness guarantees provided by existing control solutions may be severely violated. In addition, although each control loop can be proven to be stable individually, system stability must be theoretically guaranteed for the entire system. Although previous work has approached the coordination problem by forcing one control loop to run on a significantly longer timescale than the other loop [142], both the thermal and utilization control loops prefer to run on small timescales for DRE systems, because both the thermal and timing constraints are critical and must be promptly enforced upon any violations. Hence, a new kind of coordination methodology must be designed and analyzed.

This dissertation proposes a novel coordinated thermal and utilization control solution to provide simultaneous thermal and timeliness guarantees for DRE systems. The thermal control loop locally controls the temperature of each processor, while the utilization control loop provides end-to-end timeliness guarantees at the cluster level.

#### Power Oversubscription in Data Centers

Server power consumption has become a first-order concern for modern enterprise data centers. In order to amortize the non-recurring investments in the power supply facility of a data center, it is preferable to operate the facility as close as possible to its maximum capacity [46]. An additional pressure on facility operators is that upgrades in power delivery systems are extremely expensive and often lag behind required increases in hosted servers to support new business. Both of these reasons result in

pressure to load as many servers as possible on the branch circuits that supply power to computer racks. Traditionally, branch circuits are provisioned conservatively based on server nameplate power ratings, which results in significant waste of the branch circuit's power supply capacity.

A promising solution is to oversubscribe the branch circuit. This involves placing more servers on it than it can support if all the servers use their maximum power consumption at the same time. To prevent overload of the circuit, *power capping* has been proposed to limit the aggregate server power to the branch circuit capacity. This provides better performance when power demand is below the branch circuit capacity and prevents undesired shutdowns by slowing down servers occasionally when the power demand is over the branch circuit capacity. Server manufacturers have responded by providing power capping as a standard feature to limit the power draw to a user-defined limit (power cap) [64][67].

An important issue for all power capping solutions is to select an appropriate power cap. In order to maximize the number of hosted servers in a data center, a common practice is to set the server power cap as the rated current limit of the branch circuit divided by the number of servers [64][57][46][113]. The main rationale of this practice is that *peak* power should never exceed the branch circuit capacity, otherwise the branch circuit's circuit breaker (CB) might trip and cause undesired server shutdowns, or even power outages. If the peak power becomes higher than the cap at runtime due to workload increases, immediate actions (such as processor throttling) are taken to maintain the power below the cap as soon as possible. Some studies even suggest having a safety margin below the cap to avoid any instantaneous power overloads [136].

We argue that this common practice is too conservative, even though power capping is already a step ahead of traditional power provisioning based on nameplate power ratings. This conservativeness can result in an unnecessarily low system performance because even a small, short-lived power overload causes servers to slow down in spite of the fact that the circuit breakers will not trip. If harmless power

overloads could be tolerated by power capping, then we can have higher performance, as well as more hosted servers with the same circuit capacity. We systematically study the tripping characteristics of a typical CB used in data centers. Our results on a physical test bed show that instantaneous violations of the rated CB power limit are not necessarily fatal because CBs are designed to sustain a certain amount of power overload. Whether a CB trips or not depends primarily on the transient behaviors of a power overload, such as the magnitude and time duration. The time interval for a CB to sustain a power overload is determined by the magnitude of the overload and normally, a higher magnitude leads to a shorter interval. Generally, a CB will trip only when the duration of an overload is longer than the allowed time interval. The allowed interval is also affected by the ambient temperature.

Based on those observations, we propose an adaptive power control strategy that utilizes the tripping characteristics of the equipped CB to aggressively optimize the system's performance without causing the CB to trip. The power controller is designed based on an advanced adaptive control theory for parameter tuning and to adapt to variations in ambient temperature.

#### Data Center Level Power Control

Power consumed by data centers has become a serious concern in era of Cloud computing. In addition to high electricity bills and negative environmental implications, increased power consumption may lead to system failures caused by power capacity overload or system overheating, as data centers increasingly deploy more and more servers for a higher utilization of their power budget. The goal of power control (also called power capping) is to have run-time measurement and control of the power consumed by a data center, so that the servers can achieve the highest system performance while keeping the power consumption below a given power budget.

Wang et al [138] proposed Scalable HIerarchical Power control (SHIP) to prevent system failures while allowing data centers to operate at peak efficiencies for a higher return on investment. While only the server power consumption is capped in SHIP, in this work, we propose to shift power between server racks and cooling systems (e.g., a set of Computer Room Air Conditioners (CRACs)) for further optimized system performance within a desired power cap for an entire data center. We mainly focus on the case that the total power consumption of the entire data center exceeds the power distribution capacity of the facility, and thus we must throttle the power draw of servers or/and cooling systems. This situation can be expected to occur soon as many data centers rapidly deploy new servers, while their power distribution and cooling systems have already approached the peak capacities [138][52][46]. Within the foreseeable stringent power budget, if we give too much power to servers and too little to the cooling systems, some servers may have overheating or even undesired shutdowns. On the other side, if we allocate too much power to the cooling systems, many servers have to be turned off while the data center is overcooled. Therefore, it is challenging to have a globally optimal power allocation that maximizes the data center's performance.

The remainder of the chapter is organized as follows: we describe the system architecture consisting of an inner power control loop and an outer power control loop in Section 8.1 and the detail design of the outer power control in Section 8.2. Further improvement of the outer power control loop based on air-side economizer are presented in Section 8.3. We presents extensive large-scale simulations in Section 8.4.

#### End-to-End Energy Management of Virtual Desktop Infrastructure

Virtual infrastructure allows data center operators to reduce IT costs, including electricity. Virtual machine consolidation increases the utilization of physical infrastructure, making the data center more efficient and reducing its carbon footprint. Closely following on the heels of server consolidation, enterprises are fast adopting virtual desktop infrastructure (VDI) to replace and consolidate existing physical desktops as well. In a VDI environment, a user's operating system instance and applications are run on a virtual machine hosted in the enterprise data center.

Users remotely control the virtual machines using thin clients such as stateless hardware terminals, smartphones or tablet PCs.

In this work, we minimize energy consumption by manipulating various knobs such as CPU DVFS levels and consolidating virtual machines. A key challenge is to guarantee that performance will not be adversely affected, leading to undesired violations of service level agreements. To address this challenge, we establish a performance model which predicts end-to-end performance of VDI workloads, given CPU DVFS levels and consolidation ratios etc. We select a collection of typical applications used by VDI users, and define a relevant end-to-end performance metric. We do this instead of adopting well-known CPU utilization or throughput metrics because they don't sufficiently reflect a user's experience with interactive applications (which is of prime importance in a VDI deployment).

The remainder of the paper is organized as follows. In Section 9.1 we describe endto-end energy management with performance guarantees. In Section 9.2, we present details of the system implementations and experimental results.

#### Contributions

Specially, this dissertation has the following contributions.

For Power-Aware Utilization Control:

- We derive an analytic model that captures the system dynamics of the new CPU utilization control problem.

- We design a two-layer coordinated control architecture and present detailed coordination analysis.

- We implement our control architecture in a real-time middleware system.

- We present empirical results to demonstrate that our control solution outperforms a state-of-the-art utilization controller that relies solely on rate adaptation.

For Task Consolidation:

- We propose a control theoretic solution for timeliness guarantees that minimizes both dynamic and leakage power consumption. Compared with traditional open-loop solutions, our solution can achieve better power efficiency and realtime performance when task execution times vary significantly at runtime in unpredictable environments.

- We design a two-level power optimization architecture that analytically integrates core-level utilization control with processor-level task consolidation to eliminate the complexity of one-level hybrid model-predictive control. The task consolidation problem is formulated as a bin-packing problem and several solutions are comparatively studied.

- While the majority existing work relies solely on simulations for evaluation, we present empirical results on a hardware multi-core testbed to demonstrate the efficacy of our integrated solution with the Mibench benchmarks [60]. Extensive simulation results also show that our solution can achieve more power savings than state-of-the-art algorithms in many-core systems.

#### For Cache Partitioning:

- We derive an analytic model that captures the system dynamics of the new cache-aware multi-core utilization control problem.

- We propose a two-level utilization control solution for energy efficiency that includes a core-level utilization controller and a processor-level cache demand arbitrator.

- We apply the recent advance in control theory, Multi-Objective MPC (MOMPC) theory, to design the utilization controller for achieving the two (often conflicting) optimization objectives.

- We present extensive experimental results (using the well-known *Miberch* [60] benchmarks) to demonstrate that our solution outperforms two state-of-the-art

power management algorithms that do not consider L2 caches or per-core DVFS by having more accurate utilization control and less energy consumption.

### For Temperature Control:

- While most existing work relies on open-loop optimization to minimize power and temperature for DRE systems with the assumption that task execution times and system thermal condition do not change significantly at runtime, we analytically model the temperature and CPU utilizations of a DRE system and design a feedback control solution for dynamic thermal and real-time guarantees for DRE systems running in *unpredictable* environments.

- While most existing closed-loop solutions provide either thermal or timeliness guarantee in an isolated manner, our solution coordinates the thermal and utilization control loops to provide simultaneous runtime guarantees. To our best knowledge, our solution is the first one that adopts robust control theory as a theoretical foundation such that both control loops can run on their respective desired timescales for prompt control actions with guaranteed system stability.

- While most existing work assumes that the processors support DVFS for thermal management, we design a task rate adaptation based thermal control loop for legacy processors without DVFS support. Our solution can achieve thermal guarantee for a heterogeneous cluster.

- While most existing work relies solely on simulations for evaluation, we present empirical results on a physical testbed to demonstrate the efficacy of our control solution and extensive simulations for a large-scale heterogeneous cluster.

#### For Power Oversubscription:

• We present a systematic study to investigate the tripping characteristics of a typical CB used in many data centers. While previous solutions simply assume that power can never exceed the CB's capacity, to the best of our knowledge,

our work is the first that utilizes transient CB tripping behaviors to optimize server performance or host additional servers. We also consider the impacts of ambient temperature on transient CB behaviors.

- In contrast to most existing power capping solutions that rely on simplistic heuristics, we use control theory to design an adaptive power controller that precisely controls the transient response of power overload to follow the designed CB trip curve. We also propose a proactive control solution to explore the practical upper bound of power oversubscription.

- Our extensive hardware results with the SPEC CPU2006, SPECJBB, and LINPACK benchmarks show that the proposed CB-aware power control solutions achieve 38% better performance, on average, than a state-of-the-art baseline that simply uses the CB capacity as the power cap without considering the CB's tripping characteristics.

- We conduct analyses to show that our adaptive power capping solutions allow a server rack to host three times more servers than traditional static power provisioning schemes and 54% more servers than the current power capping practice widely used in the industry.

For Data Center Level Power Control,

Specifically, this work makes several major contributions:

- while previous power control solutions assume that a data center cooling system always runs at its full capacity. Our work shifts power between a cooling system and servers.

- we adopt a two-level control technique to design an outer cooling system power controller and an inner server power controller. We present a systematic study of a data center cooling system and formulate the controller as a nonlinear constrained problem.

• our large-scale simulation results demonstrate the efficacy of the proposed solution and show the advantages compared to baselines.

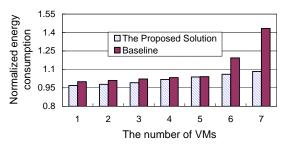

For End-to-End Energy Management:

- We derive an accurate performance model using a black-box modeling approach.

- Based on the model, we formulate an optimization problem to minimize the energy consumption while guaranteeing performance, and transform it into a canonical form which can be solved by standard optimization solvers. However, no polynomial time solvers exist to obtain the optimal solution. To scale the proposed solution in VDI deployments, which can have thousands of seats (VMs), a two-step heuristic algorithm is designed to reduce the algorithmic complexity significantly.

- We prototype the proposed solution and analyze the overhead of each component of the implementation to ensure that the overall solution will not introduce significant performance degradation or increased energy consumption. Experimental results from a hardware test bed demonstrate the efficacy of the proposed solution in terms of energy and performance. It significantly outperforms the state-of-the-art baseline widely adopted in industry today.

The rest of this dissertation is organized as follows. Chapter 2 discusses the related work. Chapter 3 presents Integrating Utilization Control with Task Consolidation for Power Optimization in Multi-Core Real-Time Systems and 4 presents Cache-Aware Utilization Control for Energy Efficiency in Multi-Core RT Systems, respectively. Chapter 5 presents Power-Aware Utilization Control for Distributed RT Systems. Chapter 6 presents Coordinated Temperature and Utilization Control for Distributed Real-Time Embedded Systems. Chapter 7 presents Power Oversubscription in Data Centers. Chapter 8 presents Data Center Level Power Control. Chapter 9 presents End-to-End Energy Management of Virtual Desktop Infrastructure. Chapter 10 concludes the dissertation.

# Chapter 2

# Related Work

#### Power-Aware Utilization Control for Distributed RT Systems

A survey of feedback performance control in computing systems is presented in [6]. Many projects that applied control theory to real-time scheduling and utilization control are closely related to this paper. Steere et al. and Goel et al. developed feedback-based schedulers [127][56] that guarantee desired progress rates for real-time applications. Abeni et al. presented control analysis of a reservation-based feedback scheduler [7]. Lu et al. developed a middleware service that adopts feedback control scheduling algorithms to control CPU utilization and deadline miss ratio [92]. Feedback control has also been applied to power control [82] and digital control applications [33].

Various CPU utilization control algorithms (e.g., [92] [126][87][139]) have been recently proposed to guarantee real-time deadlines. For example, Lu et al. designed constrained MIMO utilization control algorithm for multiple processors that are coupled due to end-to-end tasks [93]. Wang et al. proposed decentralized utilization control algorithm for large-scale distributed real-time systems [144]. Yao et al. developed an adaptive utilization control algorithm [151]. However, all those algorithms assume that task rates can only be continuously tuned. Hybrid control theory [77] and optimization strategies [40] are adopted to handle discrete task rates

based on the assumption that task WCETs are known a priori and accurate, which makes them less applicable to DRE systems running in unpredictable environments. In contrast to all the existing work that relies exclusively on rate adaptation, we present a two-layer control architecture that uses both rate adaptation and DVFS for power-efficient utilization control.

Energy-efficient real-time scheduling algorithms have been proposed [17, 149, 37, 116, 16]. Most existing work relies on detailed knowledge (e.g., WCETs) of workloads to minimize the energy consumption or temperature, or maximize the system reward in an *open-loop* manner. While they can effectively guarantee task schedulability in closed environments without a feedback loop for adaptation to workload variations, they may not be directly applied to DRE systems whose workloads may significantly change at runtime. In contrast, we use DVFS as a knob to dynamically react to unpredictable workload variations instead of minimizing the energy consumption of the entire DRE system. To our best knowledge, our paper is the first effort that adopts DVFS for end-to-end CPU utilization control.

# Integrating Utilization Control with Task Consolidation for Power Optimization in Multi-Core Real-Time Systems

Several projects have addressed the scheduling problems for multi-core real-time embedded systems. Anderson et al. proposed a cache-aware scheduling technique to avoid cache thrashing for real-time tasks on multi-core platforms [12]. Guan et al. presented test conditions for non-preemptive EDF and fixed priority scheduling [58]. However, these studies do not migrate tasks for power optimization. Sarkar et al. studied the impact of task migrations on the WCETs of real-time tasks [117]. Their work focused on WCET analysis instead of real-time scheduling. In addition, they assume non-shared L2 caches which can incur a much higher task migration overhead. Chattopadhyay et al. studied the WCET analysis for a unified cache multi-core processors [34]. All of these studies do not address the power optimization problem in multi-core real-time systems. In contrast, we attempt to minimize the

power consumption of multi-core real-time systems in addition to providing real-time guarantees.

Power management is an important problem for real-time embedded systems. Multiple projects have studied real-time scheduling with power management for uniprocessor systems (e.q., [75]). Aydin et al. considered the energy-aware partitioning of real-time tasks for multiprocessor systems [18]. However, the power models of [18] did not consider leakage power consumption. Chen et al. extended the power models adopted in [18] and proposed a real-time scheduling method that minimizes both dynamic and leakage energy consumption [36]. However, these studies focus on multi-processor real-time systems where task migration can be expensive due to state maintenance. See et al. studied energy efficient multi-core real-time scheduling [119]. Their assumption is that all cores must run at the same frequency (chip-wide DVFS). In contrast, we utilize the availability of per-core DVFS for further power savings. As a result, the problem formulation is significantly different. All the aforementioned studies assume that task execution times are known a priori. While these studies can optimize the system power consumption when execution times do not change dynamically, the optimality is not guaranteed under execution time variations. Although much work on feedback control scheduling exists, to the best of our knowledge, our work is the first one which integrates the utilization control with DPM. Recently, [50] proposed to dynamically partition shared last-level caches of multi-core processors to control the utilization while reduce the power consumption. [50] is complementary to this work and can be integrated to further reduce the power consumption while guarantee real-time.

## Cache-Aware Utilization Control for Energy Efficiency in Multi-Core RT Systems

In recent years, scheduling for multi-core real-time systems has received much attention. Many multiprocessor scheduling algorithms (e.g., [43, 103]) can be applied to multi-core processors. Bini et al. [25] proposed two abstractions to facilitate multi-core adoption for real-time systems and the corresponding schedulability analysis.

Nelis et al. [103] studied slack reclamation schemes to reduce the power of a multi-core real-time system. Block et al. [26] proposed an adaptive framework based on feedback which controls each task instead of the utilization of the task system. See et al. [119] studied energy efficient multi-core real-time scheduling using a chip-wide DVFS. However, all these studies do not explicitly consider the impact of shared L2 caches.

Several cache-aware multi-core real-time scheduling algorithms have been recently proposed. Anderson's group proposed various open-loop cache-aware global scheduling algorithms for multi-core real-time systems (e.g., [11]). Lakshmanan et al. [79] studied partitioned fixed-priority preemptive scheduling. Bui et al. [31] optimized the impact of cache partitioning on a multi-core real-time system. Guan et al. [59] also studied cache-aware scheduling. Yan et al. [150], Li et al. [84] and Hardy et al. [61] analyzed the impact of a shared L2 instruction cache on WCET estimation for shared L2 cache multi-core systems. Paolieri et al. [106] used L2 cache partitioning to solve the multi-core WCET problem. Suhendra et al. [128] proposed a similar cache partitioning and locking approach. All the aforementioned studies are different from ours because they do not address the power consumption of a shared L2 cache.

# Coordinated Temperature and Utilization Control for Distributed Real-Time Embedded Systems

Extensive work has been done to investigate power models of CPUs of computing systems. Power models are closely related to thermal managements because instantaneous temperatures are determined by instantaneous powers according to physic laws of thermal dynamics. Power models have been approached in several ways. [69] proposed a power model capturing architecture features of a processor. [35] observed that the power consumption of a CPU increases linearly with its CPU utilization under a particular workload pattern. [46] proposed a nonlinear power model and a simplified linear power model relating CPU utilizations to powers.

In this dissertation, we try to explicitly control the processor temperatures for DRE systems. Previous research on thermal management focuses mainly on general computer systems. For example, Brooks et al. [30] propose a dynamic thermal management scheme based on heuristics. Skadron et al. [122] present several DTM schemes including a control-theoretic algorithm. Donald et al. [42] develop a control-theoretic thermal management approach for multi-core processors. However, all the aforementioned work cannot provide timeliness guarantees for real-time systems.

Several studies have proposed thermal management algorithms for real-time systems. Bansal et al. [19][20] present online algorithms to solve real-time scheduling problems while guaranteeing thermal constraints. Chen et al. [39][38] design real-time scheduling algorithms with reactive CPU speed assignment and develop several optimization algorithms to minimize the maximum system temperature in a static way. Different from their work that relies on heuristics or optimizations, we propose a coordinated solution based on control theory to provide simultaneous thermal and timeliness guarantees despite various runtime thermal and execution time variations. Most recently, [53] proposed a thermal controller which handles input constraints. They use the linear power model which is similar to the linear power model in [46]. Our thermal controller based on rate adaptations use more accurate nonlinear model to improve the control performance. In addition, the thermal model in [53] can not capture transient process of temperature. One of disadvantages is that inevitable long control period of thermal controller increase chance of thermal failure.

Control-theoretic techniques have been applied to many computing systems. For example, various CPU utilization control algorithms (e.g., [92][93][144][139]) have been recently proposed to guarantee real-time deadlines. However, those algorithms cannot provide thermal guarantees. Recently, coordinated control solutions have been proposed for power/energy management. For example, Raghavendra et al. [110] propose a multi-layer controller for data center power management. Heo et al. [63] study the incompatibilities problems of conflicting control systems and propose a formal methodology to analyze conflicts. Another coordination strategy has been proposed in [142] by forcing different control loops to run on different timescales. In contrast, our solution is designed based on robust control theory to allow the thermal

and utilization control loops to run on their respective desired timescales for prompt control actions and simultaneous guarantees.

#### Power Oversubscription in Data Centers

Recently, the power management issue has attracted a large amount of attention from both academia and industry. For example, Meisner et al. [99] proposed a PowerNap scheme to reduce the server's idle power. Ahmad et al. [8] optimized the idle and cooling power in a data center. However, these studies focus primarily on power minimization instead of power provisioning.

Power provisioning is an important technique for data centers to avoid expensive upgrade costs and to maximize the power infrastructure utilization; thus, it becomes an important, practical issue in data center operation. Fan et al. [46] investigated the workload characteristics of the data center and demonstrate the existence of a great potential for oversubscription in the production data center. Lefurgy et al. [81] proposed a control-theoretic approach to power provisioning and showed the advantages of this method in terms of performance as compared with commercial ad hoc solutions. Pelley et al [108] proposed a novel power router to make the flexible power budget usable. Femal et al [47] investigated how to improve throughoutput given a fixed power budget. Yet, each of these studies still does not answer the question of how much power can be over-subscribed. Govindan et al. [57] adopted statistical profiling-based techniques to power provisioning. They considered the sustainable power budget; however, their soft fuse method is essentially an ad hoc approach.

The control-theoretic approach is a promising adaptation mechanism in power and thermal management. Donald et al.[41] proposed a PI-controller based solution for multicore thermal management. Skadron et al. [120] designed a PID controller approach for accurate and localized dynamic thermal management. Srikantaiah et al [125] adopted a reinforced oscillation resistant controller for shared cache management. Wang et al. [145] designed a model prediction controller. Those studies focus on power and thermal management issues for individual computer systems.

None of them consider the adaptation of control parameters since there is no design constraint on the settling times of controllers in those studies.

#### Power Capping in Data Centers

Ahmad et al. [8] proposed a hill climbing algorithm to minimize the total power consumption of cooling and servers, however, it assumes fixed CRAC flow rates. In contrast, our work enforces the power budget of a data center and configures the cooling and server power consumption optimally to maximize performance. Huang et al. [66] adjusts CRAC Output Temperature to reduce the power consumption of a data center cooling system. Their assumption is that a higher server fan speed is needed to remove the heat generated by a server since the CRAC Output Temperature increase will increase a server inlet temperature. Their adjustment is very coarse and they choose one CRAC output temperature among two based on the data center utilization which leads to a moderate power reduction. In contrast, our cooling system optimizer achieves more fine-grained control and adjusts CRAC flow rate as well. The inner control loop will control the total power consumption of servers.

Some existing work [8] adopts an ad hoc approach to minimize the cooling power. Specifically, CRACs are chosen to lower their output temperature step-by-step. It is extremely difficult to determine the step size. If the step is selected to be too small, it will take a long time for the proposed solution in [8] to settle. On the other hand, if the step is chosen to be too big and CRAC output temperatures are throttled too aggressively, the servers may be overheating. In contrast, we formulate the following optimization problem to adjust CRAC flow rate and output temperatures to minimize the cooling power consumption based on the model derived in Subsection 8.2.1.

#### End-to-End Energy Management of VDI

Many have studied aspects of energy management for pieces of a VDI system, such as networking [78][44], embedded and mobile devices [65][90][143] and data centers [71][52] etc. However, all existing work tackled these separately, as isolated components. An integrated solution for VDI energy management does not exist in industry today. A challenge in extending existing work and applying it to VDI

energy management is that they enforce performance (such as CPU utilization [65] or throughput) at the granularity of a server [78][52]. In contrast, a VDI deployment requires integrated management of end-to-end energy and performance.

# Chapter 3

# Task Consolidation in Multi-Core Real-Time Systems

# 3.1 System Architecture

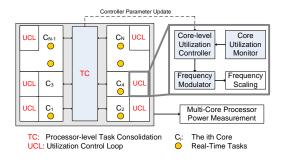

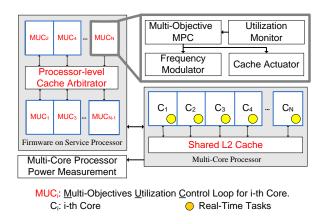

In this section, we present our system architecture. As shown in Figure 3.1, our system architecture features a task consolidation manager for the entire multi-core processor and a utilization control loop for each core in the processor.

First, for every core, a utilization controller exists that controls the CPU utilization of the core by scaling the core frequency. The controller is a Single-Input-Single-Output (SISO) controller since the change of core frequency only affects the utilization

Figure 3.1: System architecture

of the core. This control loop works as follows: (1) the utilization monitor on each core sends the utilization of the core to the local controller; (2) the controller computes a new CPU frequency and sends it to the frequency modulator on the core; and (3) the frequency modulator then changes the core frequency using DVFS.

Second, the processor-level task consolidation manager dynamically allocates tasks among the cores for task consolidation. It works as follows: (1) the task consolidation manager monitors all the tasks  $\{T_i|1 \leq i \leq m\}$  and measures their CPU utilizations at run-time; (2) the task consolidation manager computes an optimized new task allocation for the cores and sends the task migration requests to the operating system. The OS then redistributes the following releases (i.e., jobs) of the periodic tasks to the cores to enforce the migration of the periodic tasks; and (3) the OS changes the affinity of the tasks to the cores accordingly. The overhead of migrating a task among cores is less than  $40 \,\mu s$  which is sufficiently small in the majority of practical real-time systems. The detailed overhead measurement results can be found in [153].

In a real system, similar to the power management unit implemented in POWER7 [146], our control architecture can be implemented in service processor firmware to interact with the main processor and OS. Our solution can also be implemented in the OS as a periodic task with the highest priority. It is important to note that without effective integration, the processor-level task consolidation manager and the core-level utilization control loops may conflict with each other. The task consolidation manager may cause the core-level utilization control loop to be unstable, as it will change the system models used by the utilization controllers. As a result, the utilization control loops need to be configured with the proper controller parameters, according to task migration.

# 3.2 Core-level Utilization Control

In this section, we model, design, and analyze the core-level utilization control loop.

#### 3.2.1 Task Model

To maximize the throughput of a multi-core system, an application assigned to run on multi-core processors typically consists of multiple tasks running in parallel; thus, we adopt a commonly used independent periodic task model (e.g., in [12]). A system is comprised of m periodic tasks  $\{T_i|1 \leq i \leq m\}$  executing on n cores  $\{C_i|1 \leq i \leq n\}$  in a multi-core processor. Task  $T_i$  can be migrated among different cores. A core may host one or more tasks. Each task  $T_i$  has a soft deadline that is equal to its period.  $r_i$  is the inverse of the period of task  $T_i$ . A well-known approach for meeting the deadlines on a core is to ensure its CPU utilization remains below its schedulable utilization bound (e.g., Liu and Layland bound for RMS scheduling)[89]. Note that our task model can be extended to support aperiodic tasks by using the corresponding schedulable utilization bound. For example, a utilization bound has been derived for systems with aperiodic tasks in [5]. Task rate adaptation can also be used for utilization control in some real-time systems [93]. We focus on DVFS and task migration for a more general solution since the rates of many real-time tasks cannot be adapted.

Our task model has two important properties. First, while each task  $T_i$  has an estimated execution time  $c_i$  available at design time, a real-time task's actual execution time may differ from its estimation and vary at run-time due to two reasons: core frequency scaling by the DVFS and workload uncertainties. Modeling such uncertainties is important to systems operating in unpredictable environments. The estimated execution time can be an approximate estimation and is not necessarily the WCET. Second, the core frequency of each core  $C_i$  can be dynamically adjusted on a per-core basis within a range  $[F_{min}, F_{max}]$ . This assumption is based on the fact that more energy savings can be achieved with per-core DVFS when compared to

conventional chip-wide DVFS [74] and many today's microprocessors already support per-core DVFS (e.g., AMD Independent Dynamic Core Technology). Note that our solution does not rely on WCET estimation, which is a key advantage of our solution, because WCETs are often unavailable or mis estimated in real-time embedded systems running in open execution environments. In contrast, a fundamental limitation of open-loop power optimization solutions is that they may fail the optimization goal at runtime when the actual execution times are significantly different from the WCETs used in the optimization.

### 3.2.2 System Modeling