University of Tennessee, Knoxville Trace: Tennessee Research and Creative Exchange

**Doctoral Dissertations**

Graduate School

5-2007

# Process and Temperature Compensated Wideband Injection Locked Frequency Dividers and their Application to Low-Power 2.4-GHz Frequency Synthesizers

Rajagopal Vijayaraghavan University of Tennessee - Knoxville

### Recommended Citation

Vijayaraghavan, Rajagopal, "Process and Temperature Compensated Wideband Injection Locked Frequency Dividers and their Application to Low-Power 2.4-GHz Frequency Synthesizers." PhD diss., University of Tennessee, 2007. https://trace.tennessee.edu/utk\_graddiss/294

This Dissertation is brought to you for free and open access by the Graduate School at Trace: Tennessee Research and Creative Exchange. It has been accepted for inclusion in Doctoral Dissertations by an authorized administrator of Trace: Tennessee Research and Creative Exchange. For more information, please contact trace@utk.edu.

### To the Graduate Council:

I am submitting herewith a dissertation written by Rajagopal Vijayaraghavan entitled "Process and Temperature Compensated Wideband Injection Locked Frequency Dividers and their Application to Low-Power 2.4-GHz Frequency Synthesizers." I have examined the final electronic copy of this dissertation for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Doctor of Philosophy, with a major in Electrical Engineering.

Syed K. Islam, Major Professor

We have read this dissertation and recommend its acceptance:

Benjamin Blalock, Charles L. Britton, Stephen F. Smith, Dayakar Penumadu

Accepted for the Council: <u>Dixie L. Thompson</u>

Vice Provost and Dean of the Graduate School

(Original signatures are on file with official student records.)

To the Graduate Council:

I am submitting herewith a dissertation written by Rajagopal Vijayaraghavan entitled "Process and Temperature Compensated Wideband Injection Locked Frequency Dividers and their Application to Low-power 2.4-GHz Frequency Synthesizers." I have examined the final electronic copy of this dissertation for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Doctor of Philosophy, with a major in Electrical Engineering.

|                                                              | Syed K. Islam                           |

|--------------------------------------------------------------|-----------------------------------------|

|                                                              | Major Professor                         |

| We have read this dissertation and recommend its acceptance: |                                         |

| Benjamin Blalock                                             |                                         |

| Charles L.Britton                                            |                                         |

| Stephen F.Smith                                              |                                         |

| Dayakar Penumadu                                             |                                         |

|                                                              | Accepted for the Council:               |

|                                                              | Carolyn R. Hodges                       |

|                                                              | (Vice Provost and Dean the Graduate Sch |

(Original signatures are on file with official students records)

# Process and Temperature Compensated Wideband Injection Locked Frequency Dividers and their Application to Low-Power 2.4-GHz Frequency Synthesizers

A Dissertation

Presented for the

Doctor of Philosophy Degree

The University of Tennessee, Knoxville

Rajagopal Vijayaraghavan May 2007

# Dedication

This dissertation is dedicated to my wife Ramya my parents, my in-laws, my teachers and my dear god

### **ACKNOWLEDGEMENTS**

I would like to thank my advisor Dr. Syed K.Islam for all the support and encouragement he has given me through out my graduate studies. Special thanks to Dr. Benjamin Blalock, Dr. Charles Britton, Dr. Stephen Smith and Dr. Dayakar Penumadu for serving in my committee and critically reviewing my work. I am very thankful to Dr. Charles Britton for his complete confidence in my work and providing me with the opportunity to use the laboratory facilities at Oak Ridge National Labs.

I am extremely thankful to MOSIS Educational Program (MEP) Research for supporting the fabrication of the chip. The experience that was gained in the process of the taping out the chip proved very valuable to me in my current job with industry.

I doubt if I would have even been able to complete my Ph.D. with out the words of encouragement and support from my wife Ramya Desikan. She has stood by me during the tough times I encountered. Her warmth, affection and the complete trust and confidence in me was the impetus behind my achievements. Thanks to my parents, parent's in-law, the rest of my family and friends for their constant prayers and the confidence they instilled in me.

I would also like to thank all the members of Analog VLSI and Devices Laboratory and ICAS laboratory for their help in various aspects. Thanks to Mo Zhang, Chiahung Su and Md. Aminul Huque for their help with measurements. The long technical discussions

that I had with Wenchao Qu, Chandra Durisety and James Vandersand proved very valuable to me. I am also very thankful to Suheng Chen and Robert Greenwell for support with CAD issues. Thanks to Md. Hassanuzamman, Tohidur Rahman, Tim Grundman, and Benjamin Prothro for their valuable help with various research projects. I am very grateful to Dr.Aly E. Fathy (Univ of Tennessee), Dr. Paul Ewing, Dr. Gregory Hansen, Mr. Stephen Killough (ORNL) for helping me with testing facilities. Special thanks to Dr. M. Nance Ericson for his help with my measurements and his encouragement.

I would like to express my deepest gratitude to a good friend, Dr. Himanshu Arora, for all his valuable help with my dissertation. I would like to thank him for the MATLAB code and the Verilog code for implementing fractional-N PLLs that I have used in my dissertation. I learnt a lot from his dissertation on fractional-N PLLs. I really appreciate his continuous support and guidance.

I would like to thank my manager Mr.Stanley Herman Jones and the entire analog design team at Cadence Design Systems. Inc, Cary, NC for their support during the final phases my Ph.D.

Last but not the least I would like to thank the ECE Department, Dr. Larry Baylor, Dr. Leon Tolbert for the financial support and Ms. Judy Evans, Mr. Jerry Davis, Ms. Cheryl Smith, Ms. Frances Byrne, Mr. Joseph Wilder and Ms. Becky Powell for their help with

administrative issues. Thanks to every one in the IT support for the outstanding support services.

THANK GOD FOR THIS GREAT OPPURTUNITY AND PROVIDING ME A CHANCE TO INTERACT WITH SUCH WONDERFUL PEOPLE.

### **ABSTRACT**

There has been a dramatic increase in wireless awareness among the user community in the past five years. The 2.4-GHz Industrial, Scientific and Medical (ISM) band is being used for a diverse range of applications due to the following reasons. It is the only unlicensed band approved worldwide and it offers more bandwidth and supports higher data rates compared to the 915-MHz ISM band. The power consumption of devices utilizing the 2.4-GHz band is much lower compared to the 5.2-GHz ISM band. Protocols like Bluetooth and Zigbee that utilize the 2.4-GHz ISM band are becoming extremely popular.

Bluetooth is an economic wireless solution for short range connectivity between PC, cell phones, PDAs, Laptops etc. The Zigbee protocol is a wireless technology that was developed as an open global standard to address the unique needs of low-cost, low-power, wireless sensor networks. Wireless sensor networks are becoming ubiquitous, especially after the recent terrorist activities. Sensors are employed in strategic locations for real-time environmental monitoring, where they collect and transmit data frequently to a nearby terminal. The devices operating in this band are usually compact and battery powered. To enhance battery life and avoid the cumbersome task of battery replacement, the devices used should consume extremely low power. Also, to meet the growing demands cost and sized has to be kept low which mandates fully monolithic implementation using low cost process.

CMOS process is extremely attractive for such applications because of its low cost and the possibility to integrate baseband and high frequency circuits on the same chip. A fully integrated solution is attractive for low power consumption as it avoids the need for power hungry drivers for driving off-chip components. The transceiver is often the most power hungry block in a wireless communication system. The frequency divider (prescaler) and the voltage controlled oscillator in the transmitter's frequency synthesizer are among the major sources of power consumption. There have been a number of publications in the past few decades on low-power high-performance VCOs. Therefore this work focuses on prescalers.

A class of analog frequency dividers called as Injection-Locked Frequency Dividers (ILFD) was introduced in the recent past as low power frequency division. ILFDs can consume an order of magnitude lower power when compared to conventional flip-flop based dividers. However the range of operation frequency also knows as the locking range is limited. ILFDs can be classified as LC based and Ring based. Though LC based are insensitive to process and temperature variation, they cannot be used for the 2.4-GHz ISM band because of the large size of on-chip inductors at these frequencies. This causes a lot of valuable chip area to be wasted. Ring based ILFDs are compact and provide a low power solution but are extremely sensitive to process and temperature variations. Process and temperature variation can cause ring based ILFD to loose lock in the desired operating band.

The goal of this work is to make the ring based ILFDs useful for practical applications. Techniques to extend the locking range of the ILFDs are discussed. A novel and simple compensation technique is devised to compensate the ILFD and keep the locking range tight with process and temperature variations. The proposed ILFD is used in a 2.4-GHz frequency synthesizer that is optimized for fractional-N synthesis. Measurement results supporting the theory are provided.

# TABLE OF CONTENTS

| 1. IN        | TRODUCTION                                  | 1 |

|--------------|---------------------------------------------|---|

|              | 2.4-GHZ ISM BAND                            |   |

|              | 1.1.1 Wireless Local Area Networks (WLANs)  |   |

|              | 1.1.2 Bluetooth                             | 3 |

|              | 1.1.3 Home Networking                       | 3 |

|              | 1.1.4 Zigbee                                | 4 |

| 1.2          | RESEARH MOTIVATION                          | 5 |

| 1.3          | RESEARCH GOALS                              | 9 |

| 1.4          | DISSERTATION OVERVIEW                       | 1 |

| 2. IN        | JECTION-LOCKED FREQUENCY DIVIDER THEORY     |   |

| $\mathbf{A}$ | ND PRIOR ART                                | 1 |

| 3 W          | IDEBAND RING ILFD BASED ON NOVEL PROCESS    |   |

|              | ND TEMPERATURE COMPENSATION                 | 3 |

| 3.1          | MODIFIED SYMMETRIC DELAY CELL BASED         |   |

|              | WIDEBAND ILFD.                              | 3 |

| 3.2          | 2 PROCESS AND TEMPERATURE STABILIZED (PATS) |   |

|              | RING OSCILLATOR DESIGN                      | 3 |

| 3.3          | 3 TRACKING AND CALIBRATION CIRCUITRY        | 4 |

|              | 3.3.1 Tracking Circuitry                    | 4 |

|              | 3.3.2 Calibration Circuitry                 | 4 |

| 3.4          | POST-LAYOUT SIMULATION RESULTS              | 4 |

| 4. 2.        | 4-GHz FREQUENCY SYNTHESIZER BASED ON        |   |

| Pl           | ROCESS AND TEMPERATURE COMPENSATED RING     | _ |

|              | .FD                                         | 5 |

|              | PLL BASED FREQUENCY SYNTHESIS               | 5 |

| 4.2          | 2 VOLTAGE CONTROLLED OSCILLATOR(VCO) DESIGN | 6 |

|              | 4.2.1 VCO Architecture                      | 6 |

|              | 4.2.2 VCO Simulation Results                | 6 |

| 4.3          | 3 MULTI-MODULUS DIVIDER DESIGN              | 7 |

|              | 4.3.1 Divider Architecture                  | 7 |

| _            | 4.3.2 Divider Simulation Results            | 7 |

|              | CHARGE PUMP AND PHASE FREQUENCY DETECTOR    | 7 |

|              | 5 DIGITAL SIGMA-DELTA MODULATOR (SDM)       | 7 |

| 4.6          | FREQUENCY SYNTHESIZER IMPLEMENTATION AND    |   |

|              | SIMULATION                                  | 8 |

| 5. CHIP IMPLEMENTATION, TEST SETUP AND       |     |

|----------------------------------------------|-----|

| MEASUREMENT RESULTS                          | 99  |

| 5.1 CHIP IMPLEMENTATION                      | 99  |

| 5.2 PROCESS AND TEMPERATURE COMPENSATED ILFD |     |

| CHARACTERIZATION                             | 105 |

| 5.3 PROTOTYPE FREQUENCY SYNTHESIZER TESTING  | 126 |

| 6. CONCLUSION AND FUTURE WORK                | 136 |

| 6.1 ANTICIPATED ORIGINAL CONTRIBUTION        | 136 |

| 6.2 FUTURE WORK                              | 136 |

| REFERENCES                                   | 138 |

| VITA                                         | 145 |

# LIST OF TABLES

| Table 3.1.                                             | Delay cell transistor sizes.                                                                                                                                                                                                                                                                                                                                         | 38                         |

|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| Table 3.2.                                             | Locking range for different latch transistor sizes                                                                                                                                                                                                                                                                                                                   | 38                         |

| Table 3.3.                                             | Achieved and required change in V <sub>cntrl</sub> for process                                                                                                                                                                                                                                                                                                       |                            |

|                                                        | compensation                                                                                                                                                                                                                                                                                                                                                         | 49                         |

| Table 3.4.                                             | Threshold voltage simulation of the delay cell across                                                                                                                                                                                                                                                                                                                |                            |

|                                                        | process corners                                                                                                                                                                                                                                                                                                                                                      | 50                         |

| Table 3.5.                                             | Threshold voltage simulation of the delay cell with temperature                                                                                                                                                                                                                                                                                                      |                            |

|                                                        | for nominal process corner                                                                                                                                                                                                                                                                                                                                           | 50                         |

| Table 3.6.                                             | Locking range simulation for various control word                                                                                                                                                                                                                                                                                                                    | 52                         |

| Table 3.7.                                             | Comparison of locking range for divide-by-4 across process                                                                                                                                                                                                                                                                                                           |                            |

|                                                        | corners with and without compensation                                                                                                                                                                                                                                                                                                                                | 52                         |

| Table 3.8.                                             | Comparison of locking range for divide-by-6 across process                                                                                                                                                                                                                                                                                                           |                            |

|                                                        | corners with and without compensation                                                                                                                                                                                                                                                                                                                                | 53                         |

| Table 3.9.                                             | Worst-case power consumption of the ILFD, V <sub>DD</sub> =1.8V                                                                                                                                                                                                                                                                                                      | 53                         |

| Table 3.10                                             | . Comparison with previously published ILFDs                                                                                                                                                                                                                                                                                                                         | 53                         |

| Table 4.1.                                             | Bluetooth specifications                                                                                                                                                                                                                                                                                                                                             | 82                         |

| Table 4.2.                                             | PLL parameters                                                                                                                                                                                                                                                                                                                                                       | 98                         |

|                                                        | Measured natural frequency of oscillation of the ring oscillator                                                                                                                                                                                                                                                                                                     |                            |

|                                                        | on 6 different chips                                                                                                                                                                                                                                                                                                                                                 | 107                        |

| Table 3.8. Table 3.9. Table 3.10 Table 4.1. Table 4.2. | corners with and without compensation.  Comparison of locking range for divide-by-6 across process corners with and without compensation.  Worst-case power consumption of the ILFD, V <sub>DD</sub> =1.8V  Comparison with previously published ILFDs  Bluetooth specifications.  PLL parameters.  Measured natural frequency of oscillation of the ring oscillator | 53<br>53<br>53<br>82<br>98 |

# LIST OF FIGURES

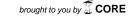

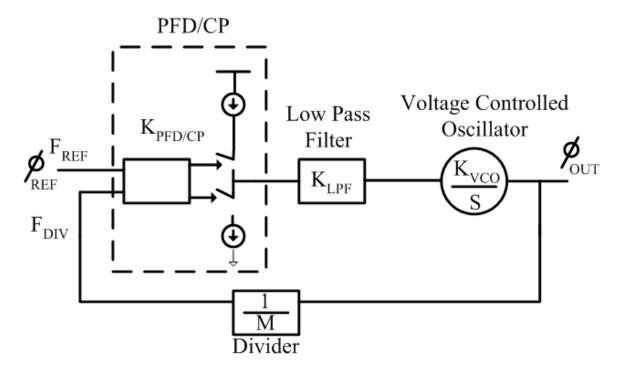

| Figure 1.1. Fractional-N PLL based frequency synthesizer 8                     |

|--------------------------------------------------------------------------------|

| Figure 2.1. Model for the ILFD.                                                |

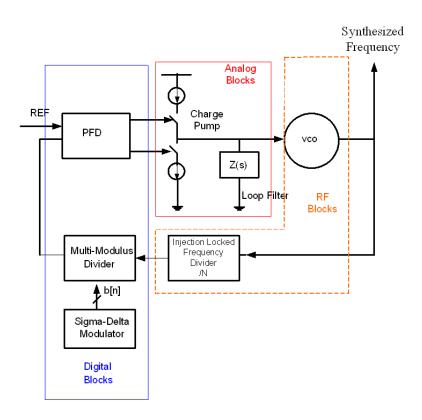

| Figure 2.2. Schematic of the ILFD.                                             |

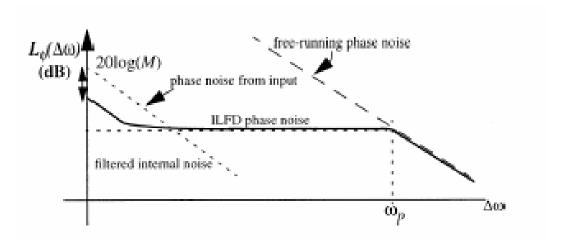

| Figure 2.3. Phase noise spectrum of an ILFD[5]                                 |

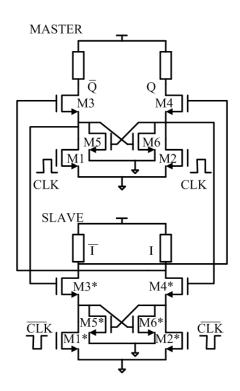

| Figure 2.4. Schematic of a static frequency divider                            |

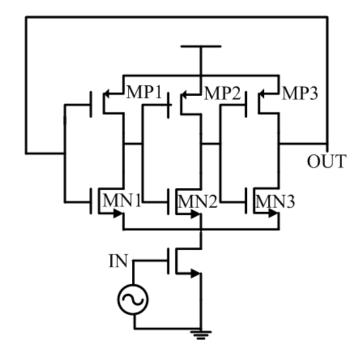

| Figure 2.5. ILFD based on a simple modification to a static divider            |

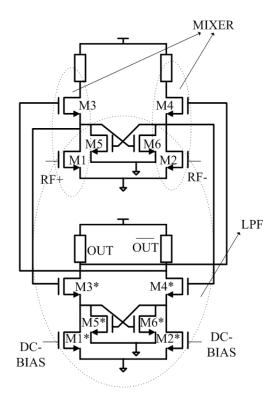

| Figure 2.6. Schematic of the conventional ILFD and the proposed QDL 23         |

| Figure 2.7. Conceptual diagram of the QDL                                      |

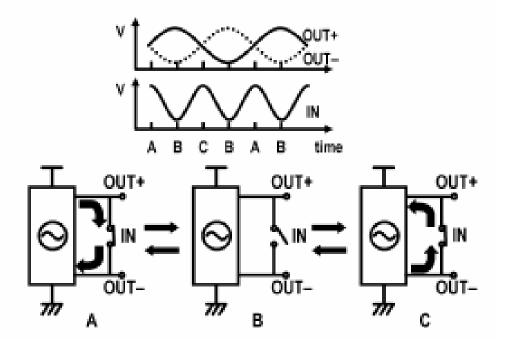

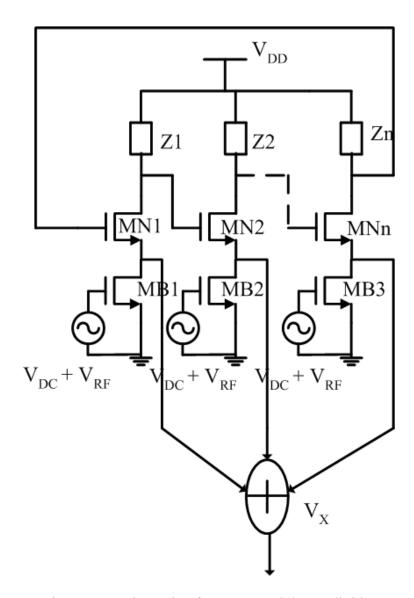

| Figure 2.8. Schematic of n-stage modulus-N divider                             |

| Figure 2.9. Modulo -3 divider                                                  |

| Figure 2.10. Modulo-5 divider.                                                 |

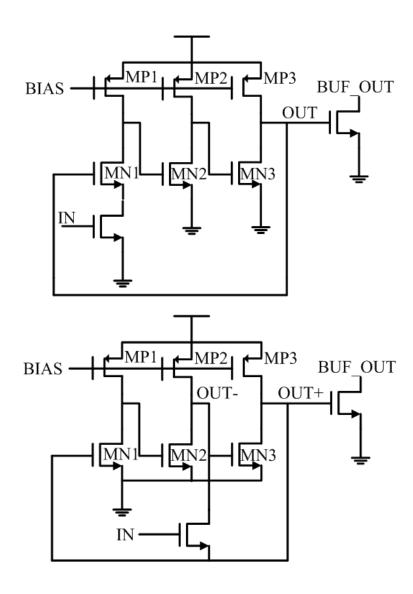

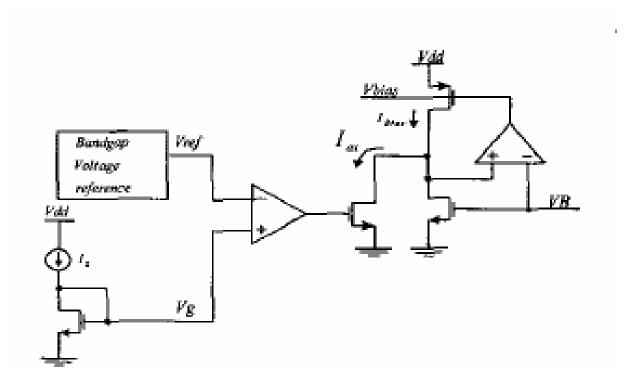

| Figure 2.11. Schematic of the bias control circuitry for the divider           |

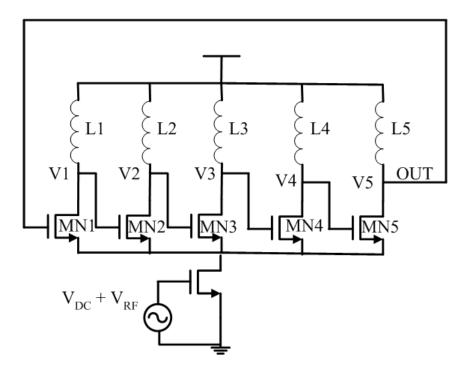

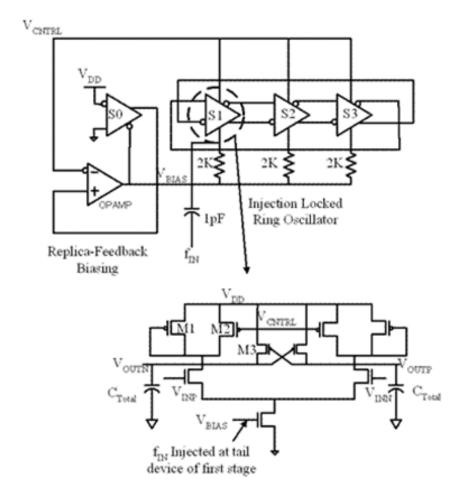

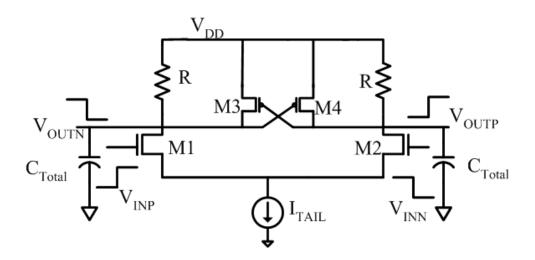

| Figure 3.1. Schematic of the ILFD based on symmetric load ring Oscillator 33   |

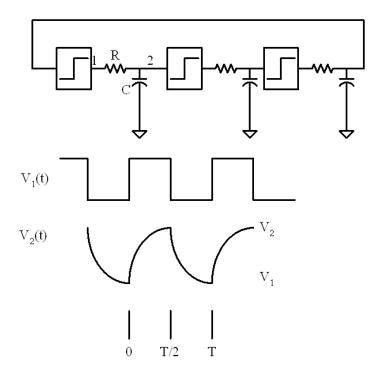

| Figure 3.2. Model for a ring oscillator with latches                           |

| Figure 3.3. Model for the delay cells                                          |

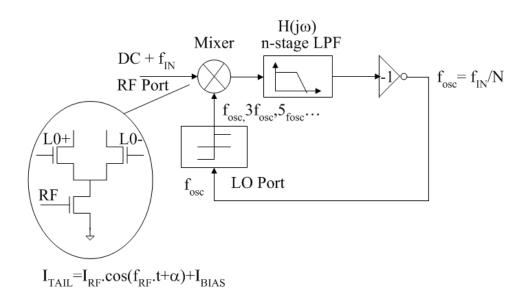

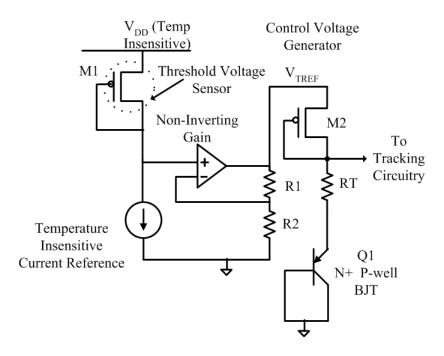

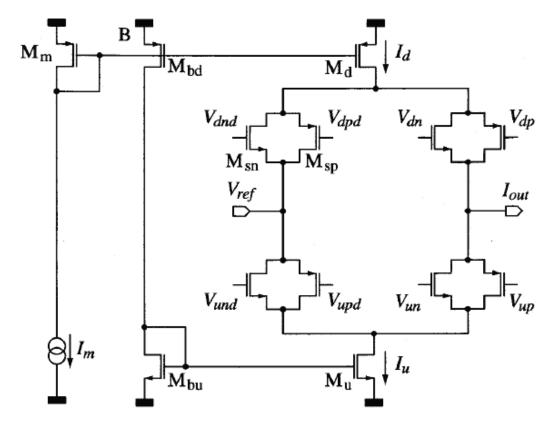

| Figure 3.4. Process and temperature compensation circuitry                     |

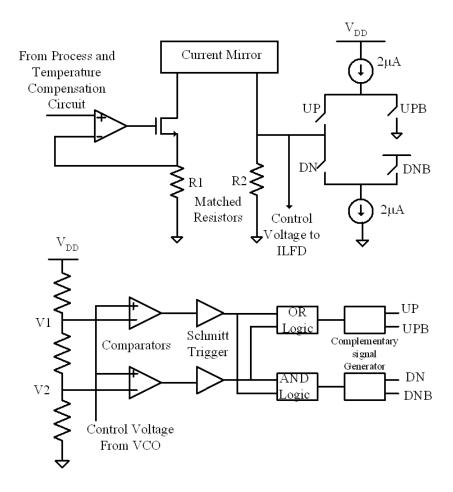

| Figure 3.5. Tracking circuitry                                                 |

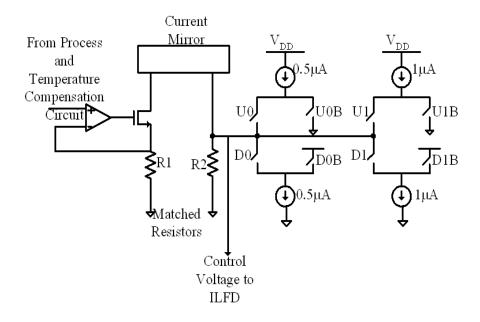

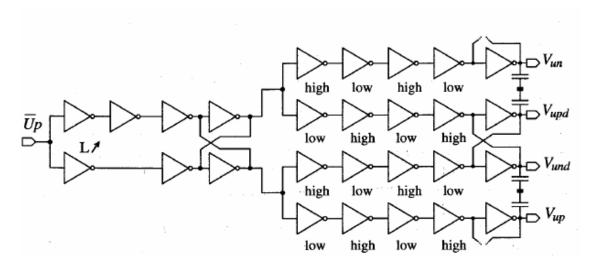

| Figure 3.6. Calibration circuitry                                              |

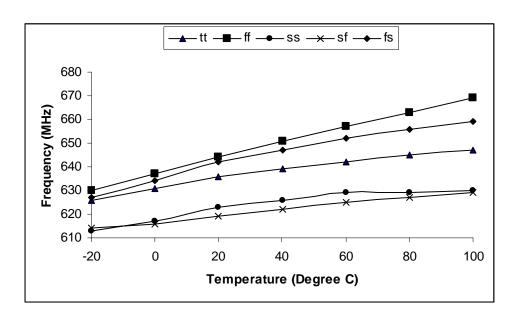

| Figure 3.7. f <sub>o</sub> Variation with process and temperature 50           |

| Figure 4.1. PLL based frequency synthesizers                                   |

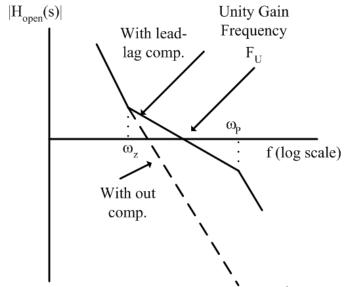

| Figure 4.2. Open-loop pole-zero plot of the 3 <sup>rd</sup> order PLL          |

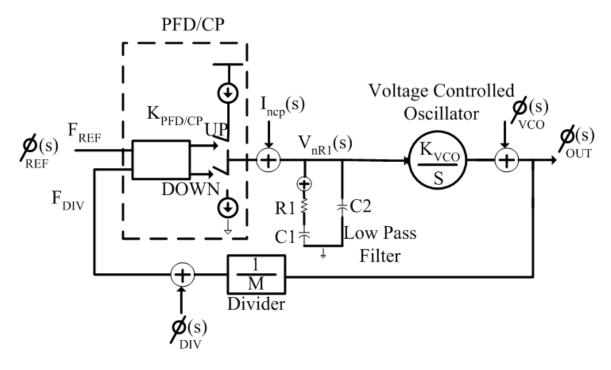

| Figure 4.3. PLL model with noise injected from various blocks                  |

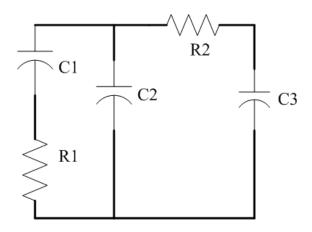

| Figure 4.4. Schematic of a 3 <sup>th</sup> order loop filter                   |

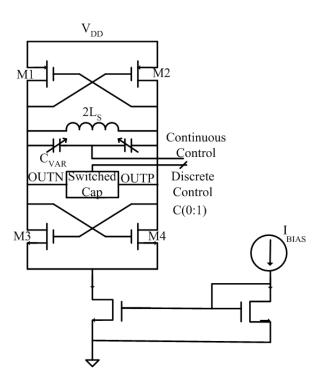

| Figure 4.5. LC VCO based on current-reuse topology and band switching 65       |

| Figure 4.6. Discrete and continuous tuning of the VCO [18]                     |

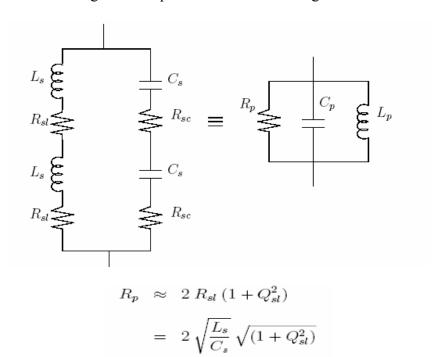

| Figure 4.7. Model of the LC tank with integrated inductors                     |

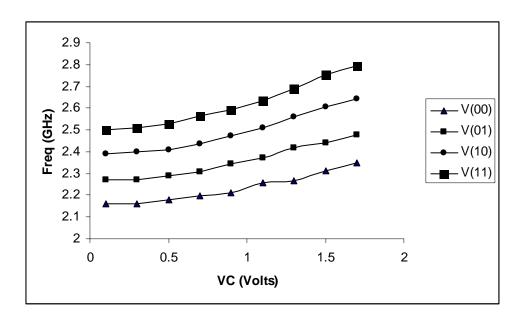

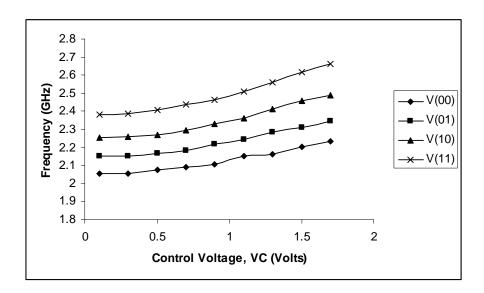

| Figure 4.8. Simulated tuning range of the VCO                                  |

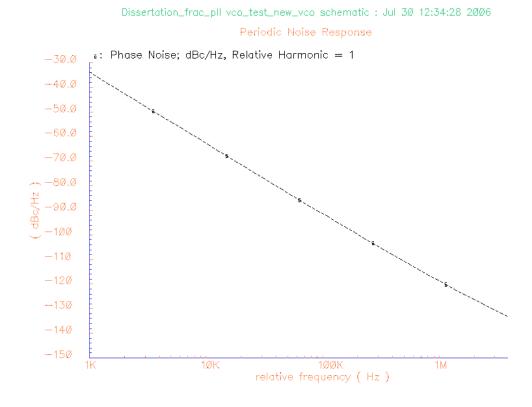

| Figure 4.9. VCO worst-case phase noise                                         |

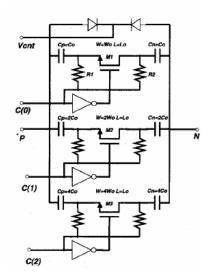

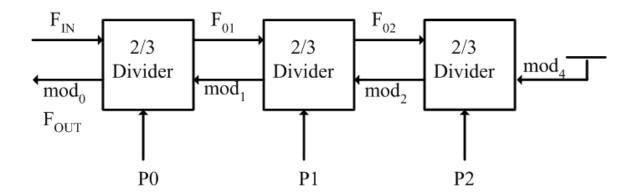

| Figure 4.10. Schematic of the multi-modulus divider                            |

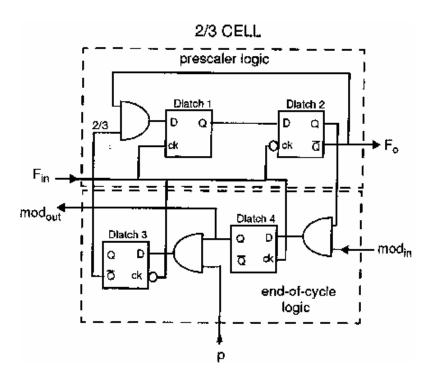

| Figure 4.11. Schematic of the 2/3 divider used in the multi-modulus Divider 72 |

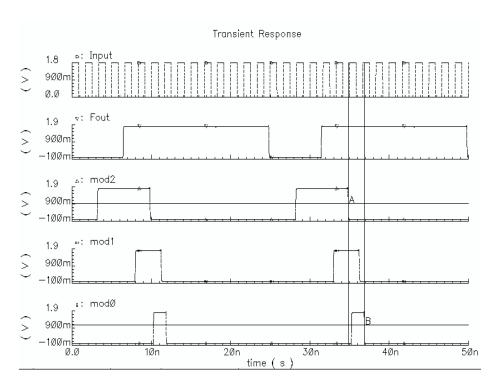

| Figure 4.12. Multi-modulus divider simulation results                          |

| Figure 4.13. Schematic of the charge pump. 75                                  |

| Figure 4.14. Timing circuitry for the charge pump.                             |

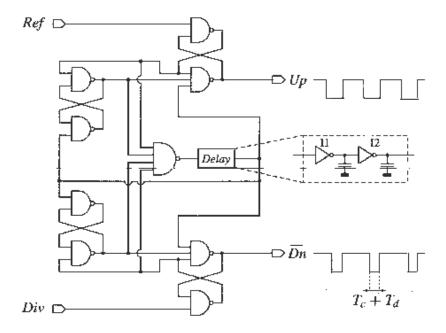

| Figure 4.15. Phase frequency detector for minimizing the dead zone of the      |

| PLL. 79                                                                        |

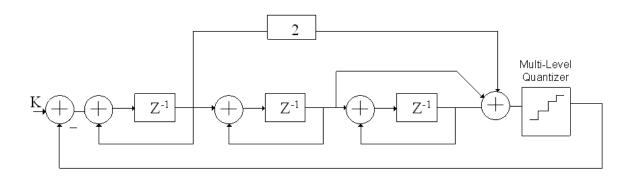

| Figure 4.16. 3 <sup>rd</sup> Order MBSL-I sigma-delta modulator                |

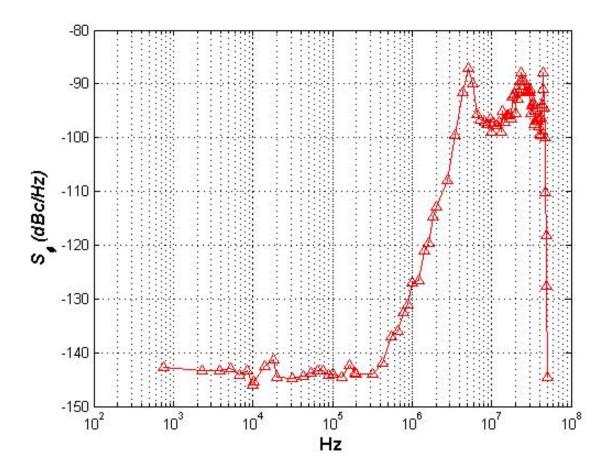

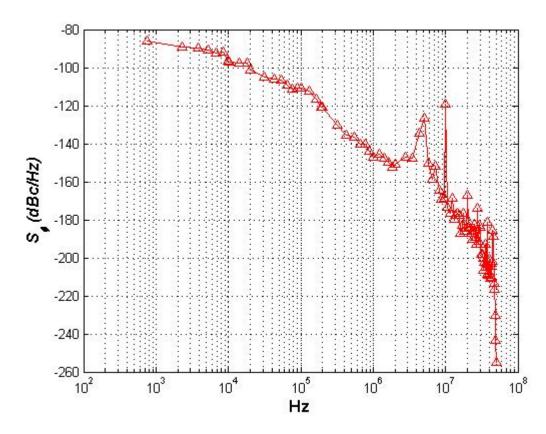

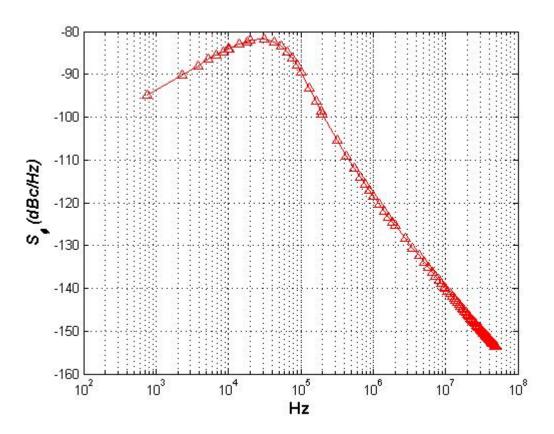

| Figure 4.17. Phase noise at the output of the MBSL-I SDM with a division       |

| step=185                                                                       |

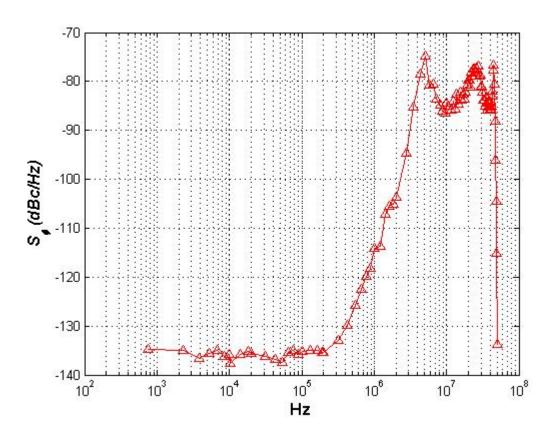

| Figure 4.18. Phase noise at the output of the MBSL-I SDM with a division       |

| step=486                                                                       |

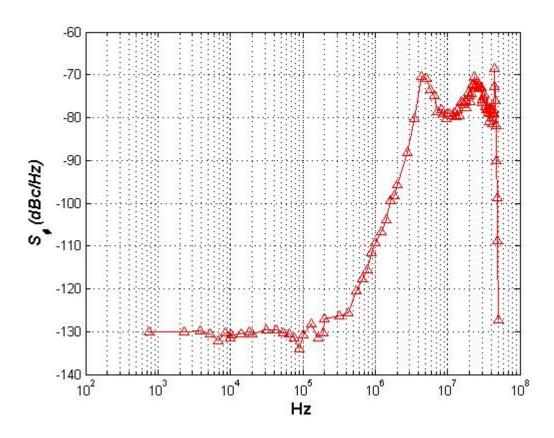

| Figure 4.19. Phase noise at the output of the MBSL-I SDM with a division       |

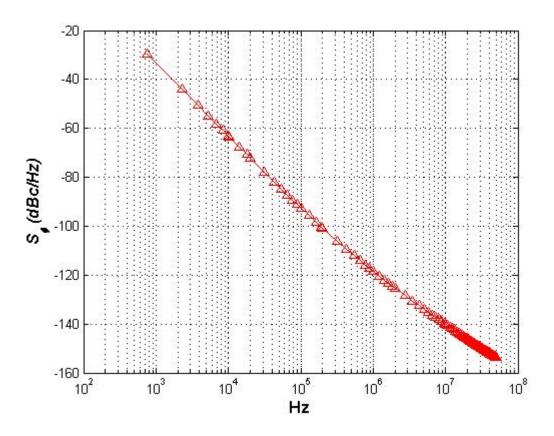

|               | step=8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 87  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

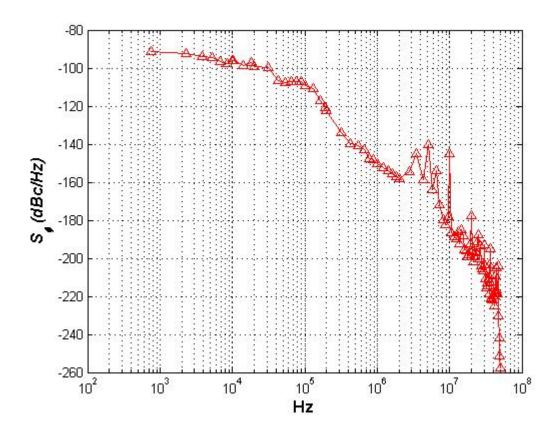

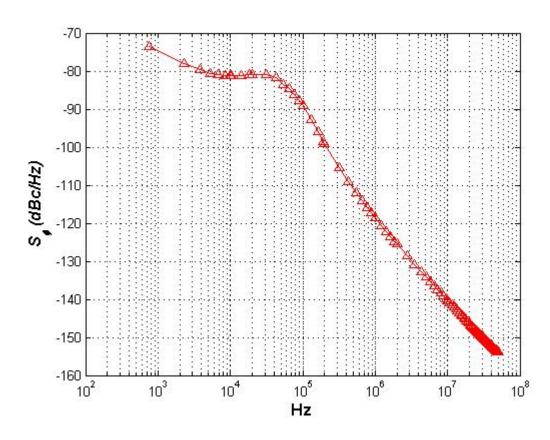

| Figure 4.20.  | Phase noise at the output of the PLL due to MBSL-I SDM with a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

|               | division step=1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 89  |

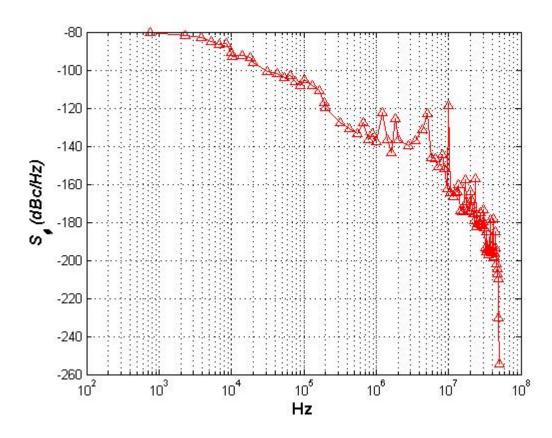

|               | Phase noise at the output of the PLL due to MBSL-I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

|               | SDM with a division step=4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 90  |

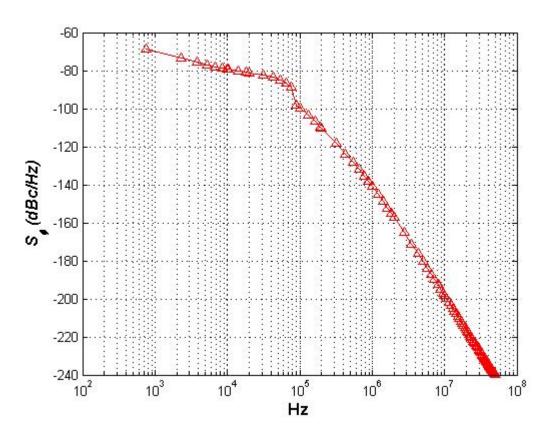

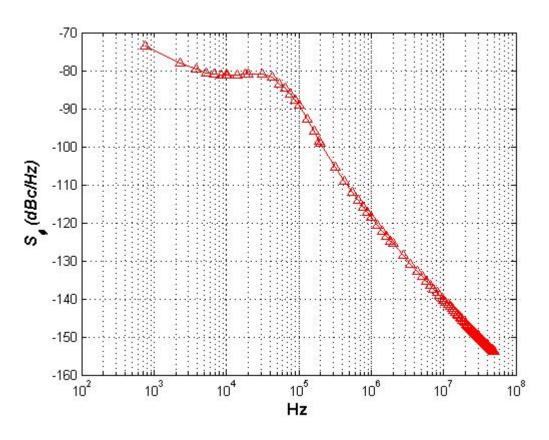

| Figure 4.22.  | Phase noise at the output of the PLL due to MBSL-I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

|               | SDM with a division step=8.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 91  |

| Figure 4.23.  | Phase noise at the output of the PLL due to the Charge Pump                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

|               | Noise.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 92  |

| _             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 93  |

|               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 94  |

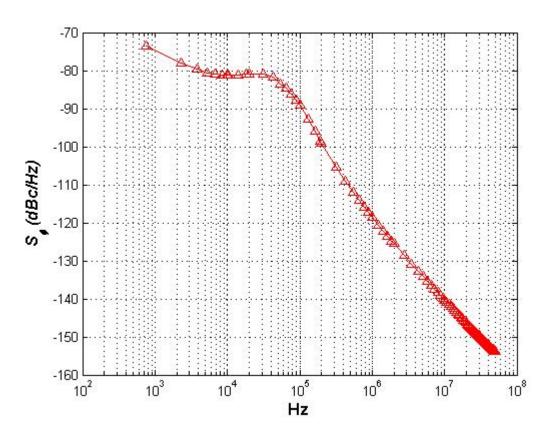

| Figure 4.26.  | Overall phase noise at the output of the PLL due to MBSL-I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

|               | SDM with a division step=1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 95  |

| Figure 4.27.  | Overall phase noise at the output of the PLL due to MBSL-I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

|               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 96  |

| Figure 4.28.  | Overall phase noise at the output of the PLL due to MBSL-I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

|               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 97  |

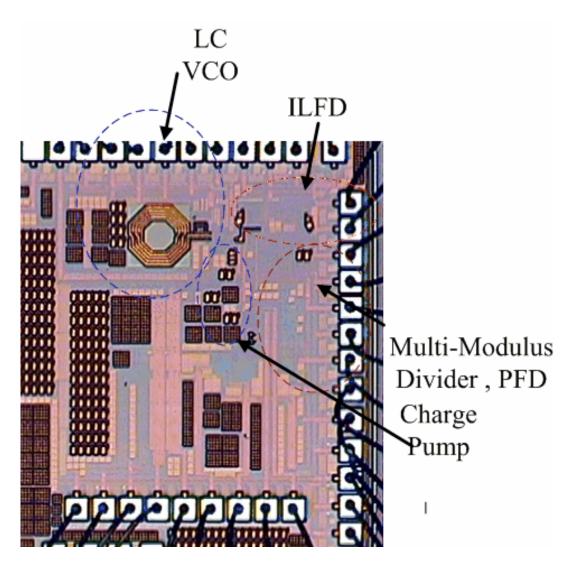

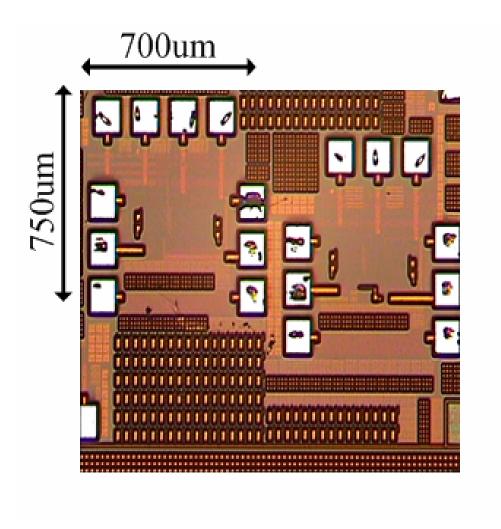

| Figure 5.1.   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 100 |

| Figure 5.2.   | 1 3 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 102 |

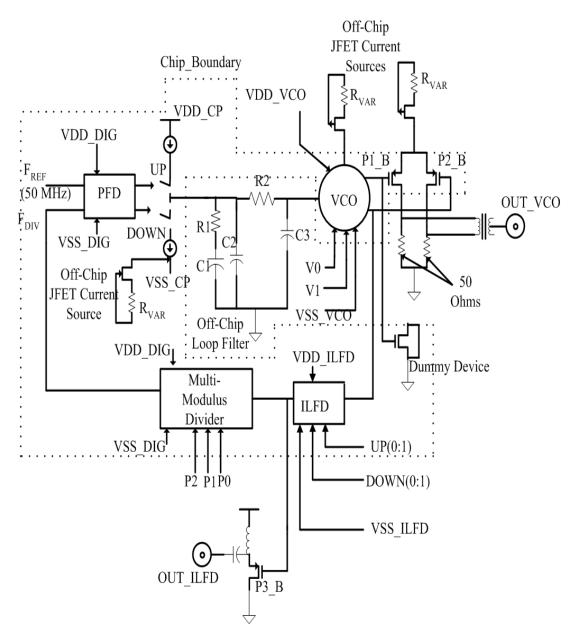

| Figure 5.3.   | 11 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 103 |

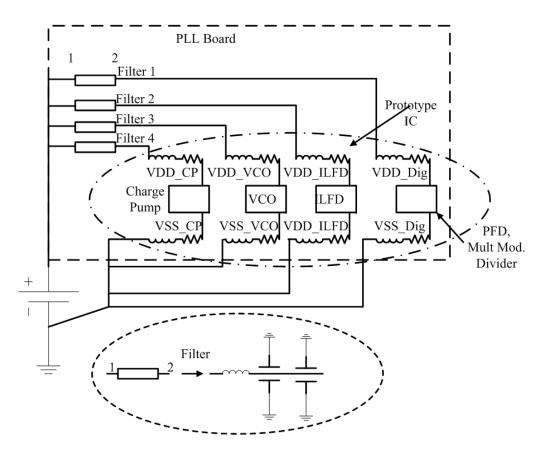

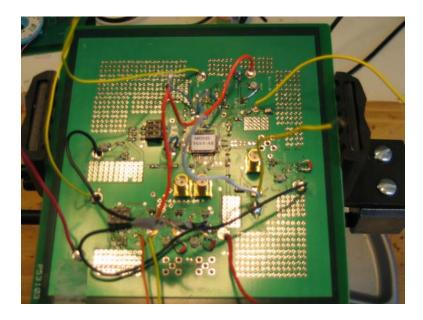

| Figure 5.4.   | 5 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 104 |

| Figure 5.5.   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 106 |

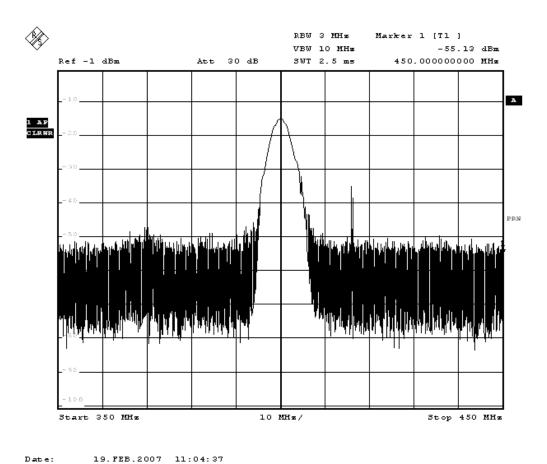

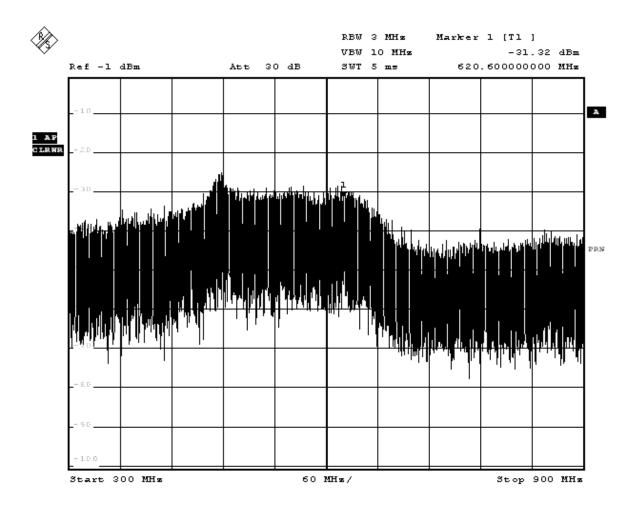

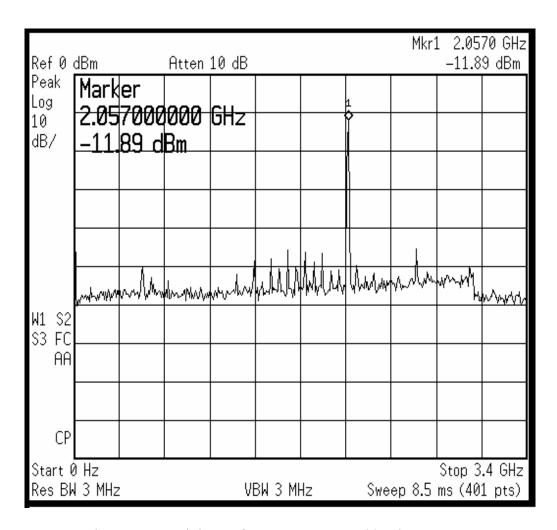

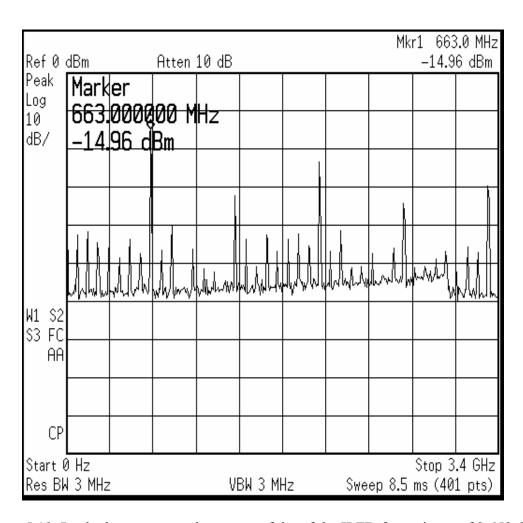

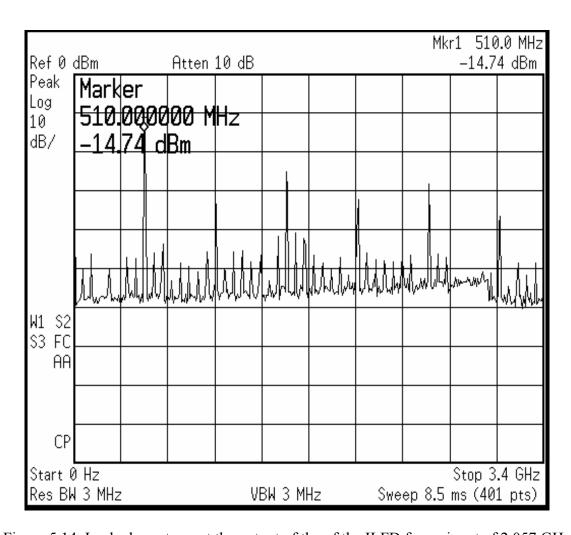

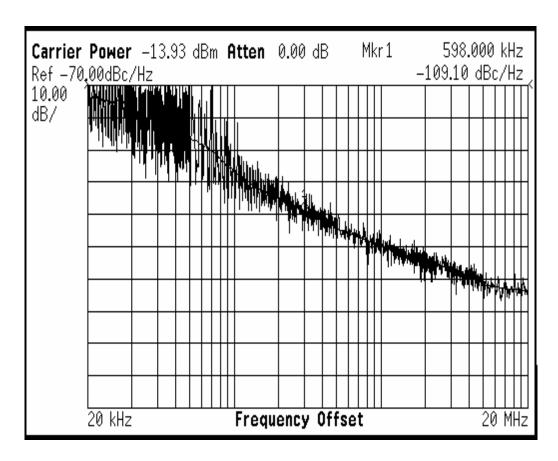

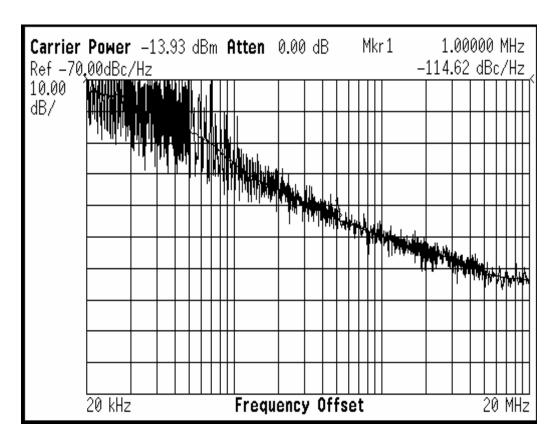

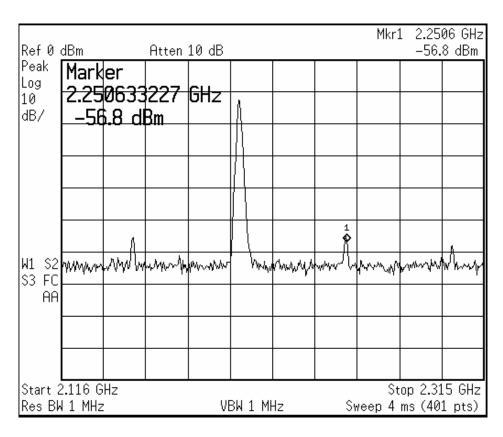

| Figure 5.6.   | Output spectrum of the ILFD for an input signal frequency = 1.8 GHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 109 |

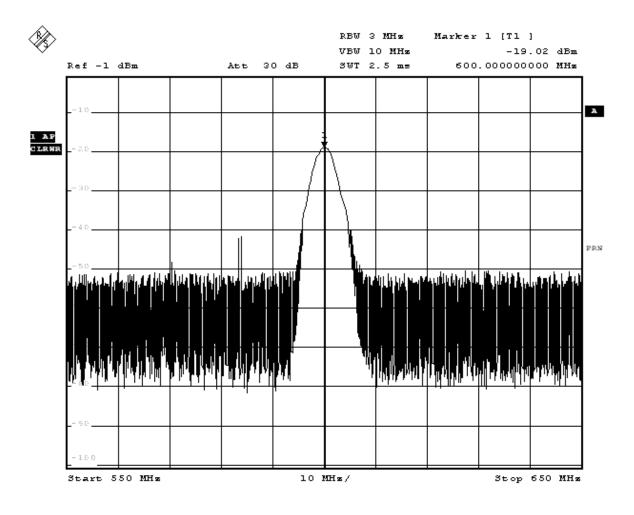

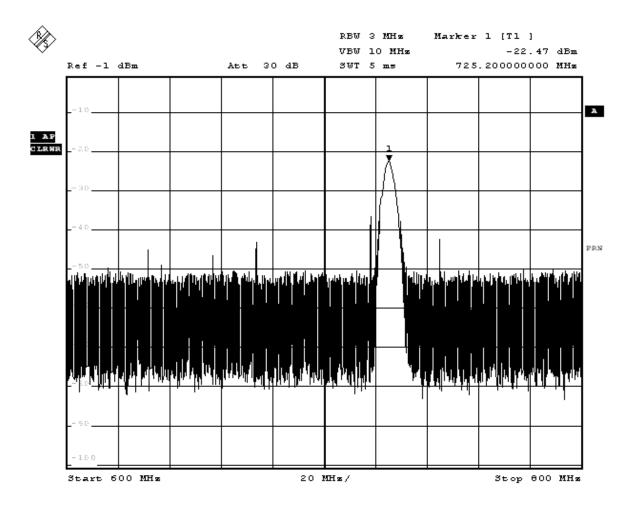

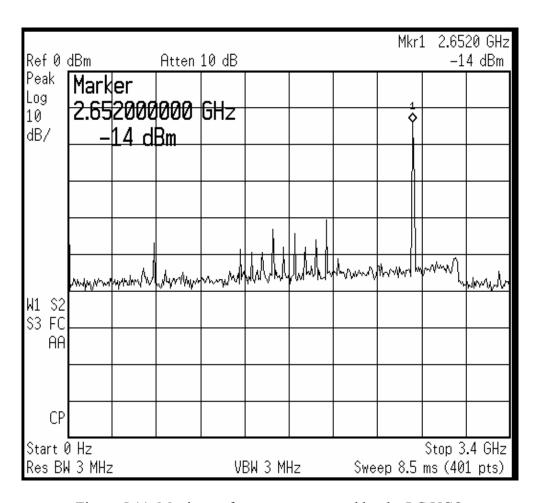

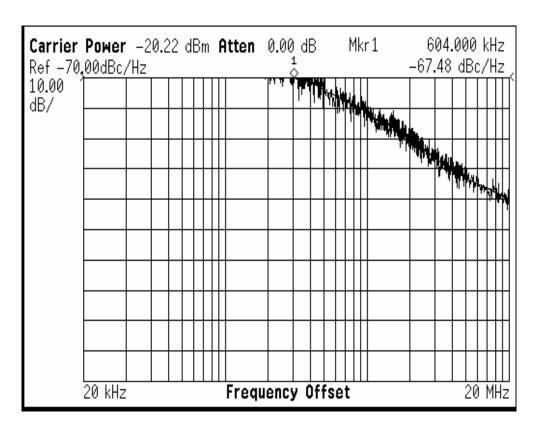

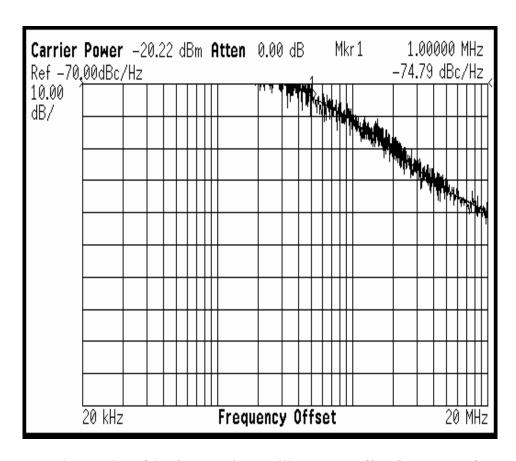

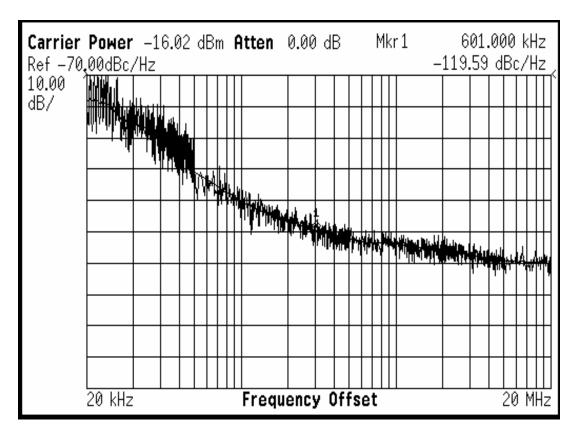

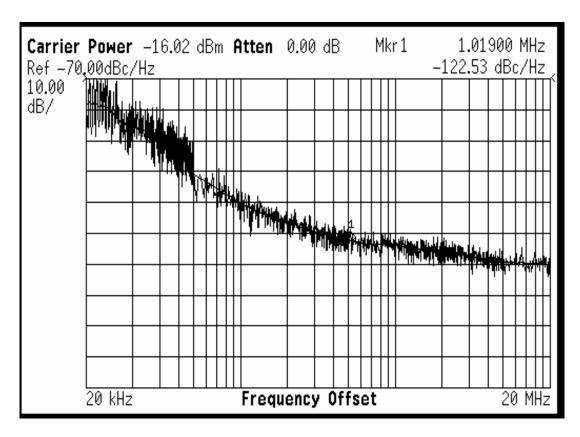

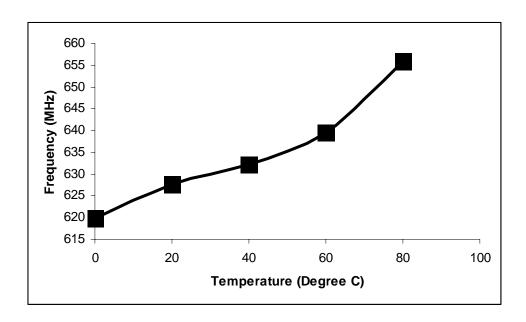

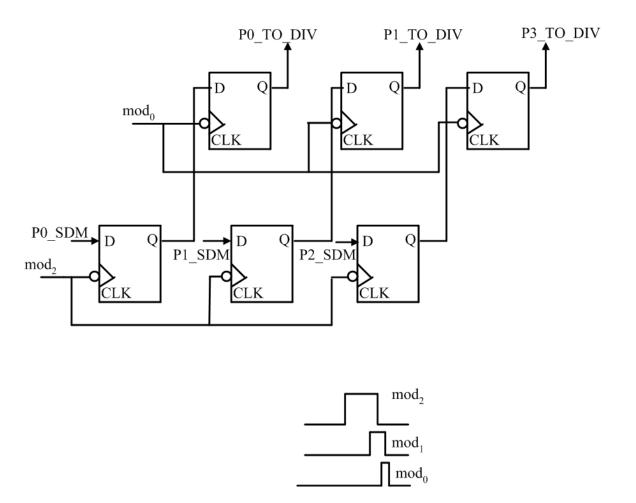

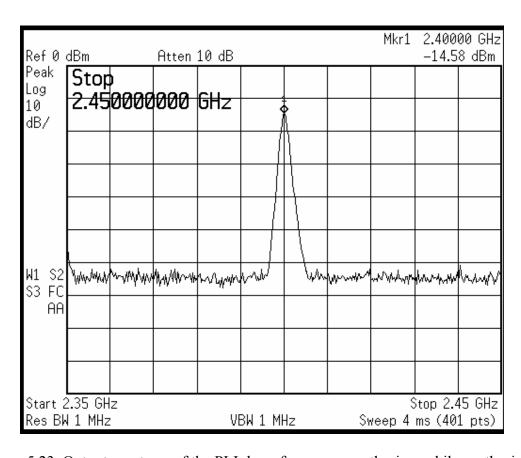

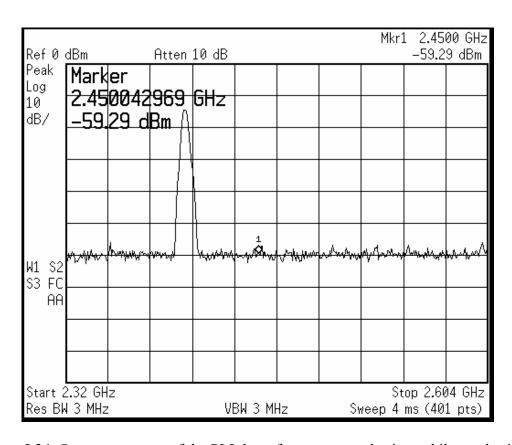

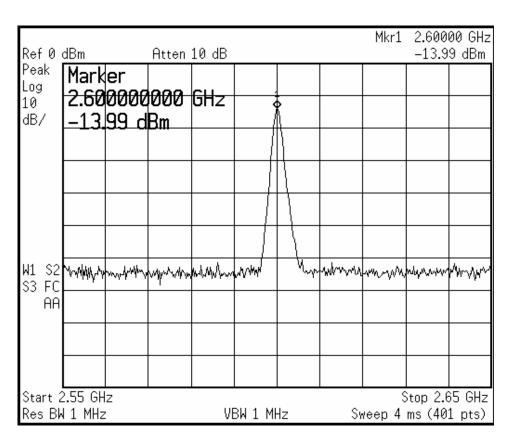

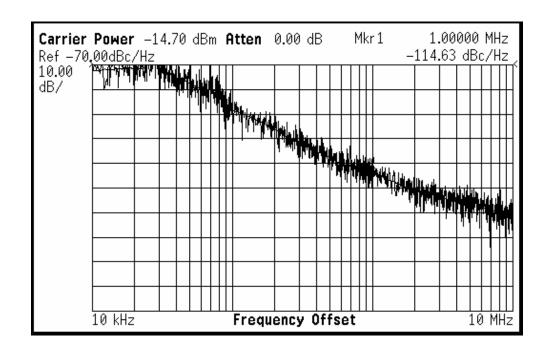

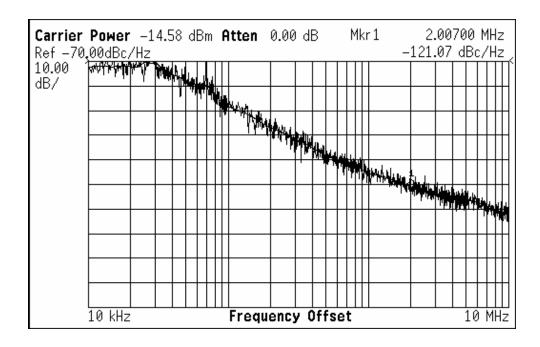

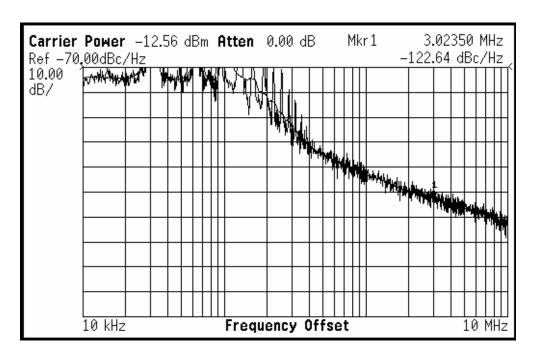

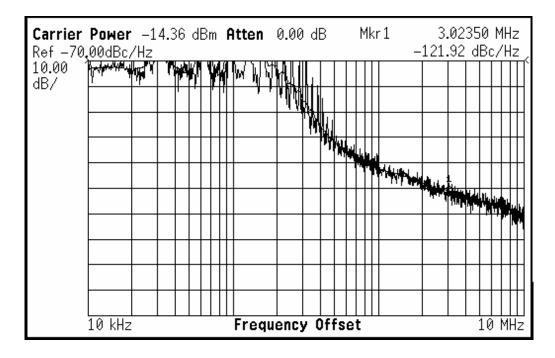

| Figure 5.7.   | Output spectrum of the ILFD for an input signal frequency $= 2.4$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |