### University of Tennessee, Knoxville TRACE: Tennessee Research and Creative Exchange

**Doctoral Dissertations**

**Graduate School**

12-2015

### **Batched Linear Algebra Problems on GPU Accelerators**

Tingxing Dong University of Tennessee - Knoxville, tdong@vols.utk.edu

Follow this and additional works at: https://trace.tennessee.edu/utk\_graddiss

Part of the Numerical Analysis and Scientific Computing Commons

#### **Recommended Citation**

Dong, Tingxing, "Batched Linear Algebra Problems on GPU Accelerators. " PhD diss., University of Tennessee, 2015. https://trace.tennessee.edu/utk\_graddiss/3573

This Dissertation is brought to you for free and open access by the Graduate School at TRACE: Tennessee Research and Creative Exchange. It has been accepted for inclusion in Doctoral Dissertations by an authorized administrator of TRACE: Tennessee Research and Creative Exchange. For more information, please contact trace@utk.edu.

To the Graduate Council:

I am submitting herewith a dissertation written by Tingxing Dong entitled "Batched Linear Algebra Problems on GPU Accelerators." I have examined the final electronic copy of this dissertation for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Doctor of Philosophy, with a major in Computer Science.

Jack Dongarra, Major Professor

We have read this dissertation and recommend its acceptance:

Jian Huang, Gregory Peterson, Shih-Lung Shaw

Accepted for the Council:

Carolyn R. Hodges

Vice Provost and Dean of the Graduate School

(Original signatures are on file with official student records.)

# Batched Linear Algebra Problems on GPU Accelerators

A Dissertation Presented for the

Doctor of Philosophy

Degree

The University of Tennessee, Knoxville

Tingxing Dong

December 2015

© by Tingxing Dong, 2015 All Rights Reserved. For my family: my parents, brother, sister and my beloved nephew Luke

## Acknowledgements

I would like to thank the University of Tennessee for letting me study and live here for five years. I have many beautiful memories left here. Knoxville is like my second hometown.

I would like to express my gratitude towards my advisor Jack Dongarra for providing me an incredible opportunity to do research in ICL and his supervision over my PhD career. I would also like to express my appreciation to Stanimire Tomov, Azzam Haidar, Piotr Luszczek for their guidance and advice, and being a source of motivation. Thank Mark Gate, Ichitaro Yamazaki and other people in ICL for their helpful discussion. Thank Tracy Rafferty and Teresa Finchum for their help in processing my paper work. ICL is a big family and like my home. I am alway proud to be an ICLer in my life.

I am grateful to my committee, Professor Jian Huang, Professor Gregory Peterson and Professor Shih-Lung Shaw for their valuable feedbacks during the writing of the dissertation.

I would also thank my friends in UT campus Chinese Bible study class. We had a wonderful fellowship every Friday night. I also thank Kai Wang for his effective proofreading of my dissertation.

Thank my friends for being there for me.

Love bears all things

### Abstract

The emergence of multicore and heterogeneous architectures requires many linear algebra algorithms to be redesigned to take advantage of the accelerators, such as GPUs. A particularly challenging class of problems, arising in numerous applications, involves the use of linear algebra operations on many small-sized matrices. The size of these matrices is usually the same, up to a few hundred. The number of them can be thousands, even millions.

Compared to large matrix problems with more data parallel computation that are well suited on GPUs, the challenges of small matrix problems lie in the low computing intensity, the large sequential operation fractions, and the big PCI-E overhead. These challenges entail redesigning the algorithms instead of merely porting the current LAPACK algorithms.

We consider two classes of problems. The first is linear systems with one-sided factorizations (LU, QR, and Cholesky) and their solver, forward and backward substitution. The second is a two-sided Householder bi-diagonalization. They are challenging to develop and are highly demanded in applications. Our main efforts focus on the same-sized problems. Variable-sized problems are also considered, though to a lesser extent.

Our contributions can be summarized as follows. First, we formulated a batched linear algebra framework to solve many data-parallel, small-sized problems/tasks. Second, we redesigned a set of fundamental linear algebra algorithms for highperformance, batched execution on GPU accelerators. Third, we designed batched BLAS (Basic Linear Algebra Subprograms) and proposed innovative optimization techniques for high-performance computation. Fourth, we illustrated the batched methodology on real-world applications as in the case of scaling a CFD application up to 4096 nodes on the Titan supercomputer at Oak Ridge National Laboratory (ORNL). Finally, we demonstrated the power, energy and time efficiency of using accelerators as compared to CPUs. Our solutions achieved large speedups and high energy efficiency compared to related routines in CUBLAS on NVIDIA GPUs and MKL on Intel Sandy-Bridge multicore CPUs.

The modern accelerators are all Single-Instruction Multiple-Thread (SIMT) architectures. Our solutions and methods are based on NVIDIA GPUs and can be extended to other accelerators, such as the Intel Xeon Phi and AMD GPUs based on OpenCL.

# **Table of Contents**

| 1 | Introduction                                        |                                   |                                                                  | 1  |  |

|---|-----------------------------------------------------|-----------------------------------|------------------------------------------------------------------|----|--|

|   | 1.1                                                 | Backg                             | round and Motivations                                            | 1  |  |

|   | 1.2                                                 | Relate                            | ed Work                                                          | 4  |  |

| 2 | Alg                                                 | $\mathbf{orithm}$                 | ns for Related Linear Algebra Problems                           | 8  |  |

|   | 2.1                                                 | One-s                             | ided Factorizations                                              | 8  |  |

|   | 2.2                                                 | 2 Forward/Backward Substitution   |                                                                  | 12 |  |

|   | 2.3                                                 | House                             | holder Bi-diagonalization                                        | 15 |  |

| 3 | Met                                                 | thodol                            | ogy and Implementation                                           | 18 |  |

|   | 3.1                                                 | Batched Design for Multicore CPUs |                                                                  |    |  |

|   | 3.2 Batched Methodology and Implementation for GPUs |                                   | ed Methodology and Implementation for GPUs                       | 19 |  |

|   |                                                     | 3.2.1                             | MAGMA                                                            | 19 |  |

|   |                                                     | 3.2.2                             | Batched BLAS Kernel Design                                       | 20 |  |

|   |                                                     | 3.2.3                             | Implementation of One-sided Factorizations and Bi-diagonalizatio | n  |  |

|   |                                                     |                                   | on GPUs                                                          | 23 |  |

|   |                                                     | 3.2.4                             | Algorithmic Innovation                                           | 28 |  |

|   |                                                     | 3.2.5                             | Optimization for Hardware Based on CUDA                          | 33 |  |

|   | 3.3 Auto-tuning                                     |                                   | tuning                                                           | 35 |  |

|   |                                                     | 3.3.1                             | Batched Level 3 BLAS GEMM Tuning                                 | 35 |  |

|   |                                                     | 3.3.2                             | Batched Level 2 BLAS GEMV Tuning                                 | 40 |  |

|   | 3.4                                                 | Batch                             | ed Problems of Variable Size                                     | 46 |  |

| 4                                | Results and Discussions            |                             |                                                            |    |  |  |  |

|----------------------------------|------------------------------------|-----------------------------|------------------------------------------------------------|----|--|--|--|

|                                  | 4.1 Hardware Description and Setup |                             |                                                            |    |  |  |  |

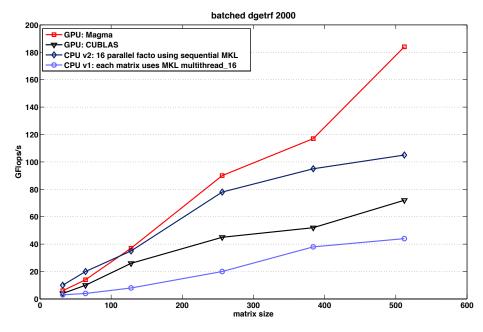

|                                  | 4.2                                | Performance on the K40c GPU |                                                            |    |  |  |  |

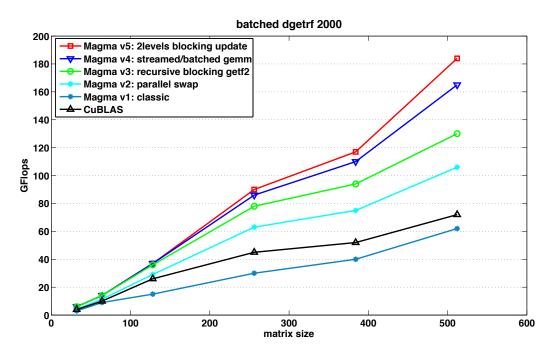

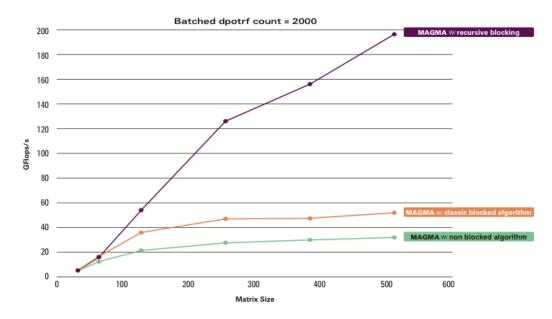

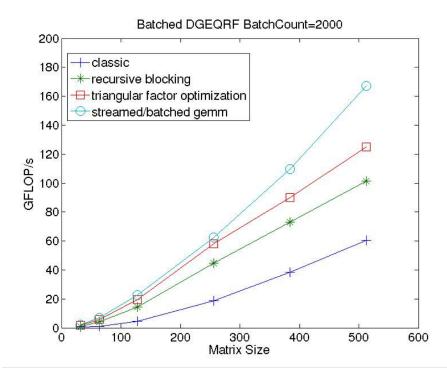

|                                  |                                    | 4.2.1                       | Performance of One-sided Factorizations                    | 54 |  |  |  |

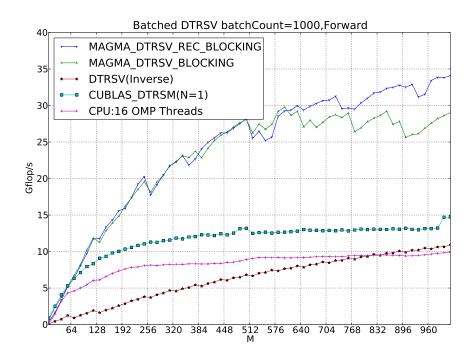

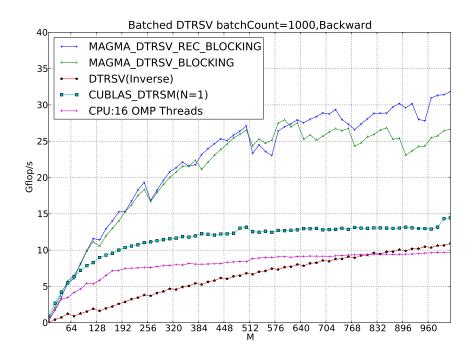

|                                  |                                    | 4.2.2                       | Performance of Forward/Backward Substitution               | 56 |  |  |  |

|                                  |                                    | 4.2.3                       | Performance of Bi-diagonalization                          | 57 |  |  |  |

|                                  | 4.3                                | Comp                        | arison to Multicore CPU Solutions                          | 64 |  |  |  |

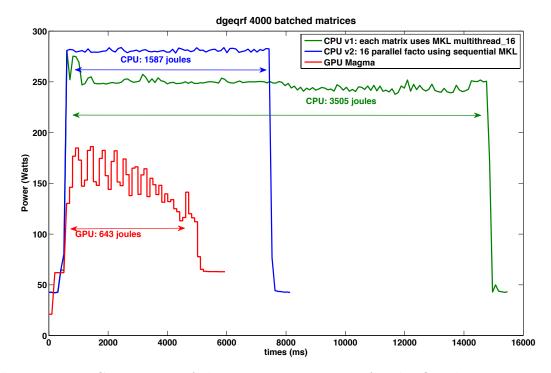

|                                  | 4.4 Power and Energy Consumption   |                             |                                                            |    |  |  |  |

| 5 Applications                   |                                    |                             |                                                            |    |  |  |  |

| 5.1 The BLAST Algorithm          |                                    |                             |                                                            | 70 |  |  |  |

|                                  | 5.2 Hybrid Programming Model       |                             |                                                            |    |  |  |  |

|                                  |                                    | 5.2.1                       | CUDA Implementation                                        | 74 |  |  |  |

|                                  |                                    | 5.2.2                       | MPI Level Parallelism                                      | 76 |  |  |  |

|                                  | 5.3 Results and Discussions        |                             |                                                            |    |  |  |  |

|                                  |                                    | 5.3.1                       | Validation of CUDA Code                                    | 78 |  |  |  |

|                                  |                                    | 5.3.2                       | Performance on a Single Node                               | 78 |  |  |  |

|                                  |                                    | 5.3.3                       | Performance on Distributed Systems: Strong and Weak Scala- |    |  |  |  |

|                                  |                                    |                             | bility                                                     | 78 |  |  |  |

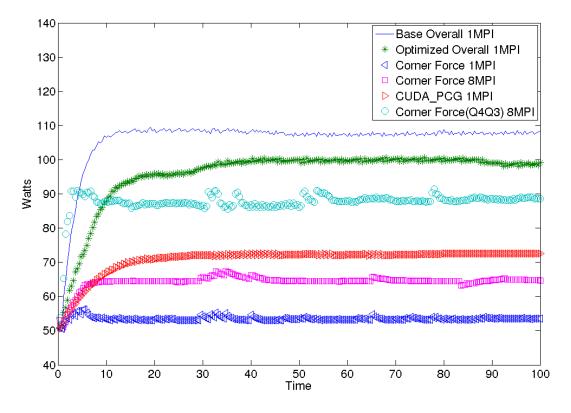

|                                  | 5.4                                | Energ                       | y Efficiency                                               | 79 |  |  |  |

| 6 Conclusions and Future Work 85 |                                    |                             |                                                            |    |  |  |  |

| Bibliography 87                  |                                    |                             |                                                            |    |  |  |  |

| A                                | Appendix 9                         |                             |                                                            |    |  |  |  |

| Vita                             |                                    |                             |                                                            |    |  |  |  |

## Chapter 1

### Introduction

#### **1.1** Background and Motivations

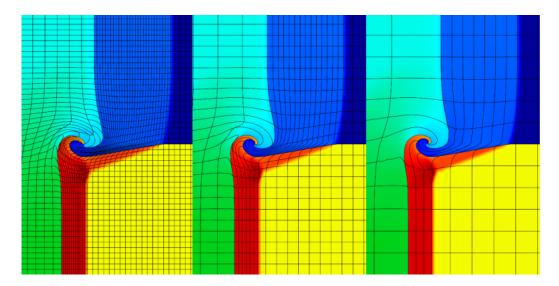

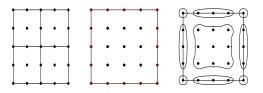

Solving many small linear algebra problems is called batched problem, which consists of a large number of independent matrices (e.g., from hundreds to millions) to be solved, where the size of each matrix is considered small. Various scientific applications require solvers that work on batched problems. For example, in magnetic resonance imaging (MRI), billions of 8x8 and 32x32 eigenvalue problems need to be solved. Also, a batched 200x200 QR decomposition is required to be computed in radar signal processing [5]. Hydrodynamic simulations with Finite Element Method (FEM) need to compute thousands of matrix-matrix (GEMM) and matrixvector(GEMV) products [13]. The size of matrices increases with the order of methods, which can range from ten to a few hundred. As shown in Figure 1.1, highorder methods result in large-sized problems but can reveal more refined physical details. As another example, consider an astrophysics ODE solver with Newton-Raphson iterations [28]. Multiple zones are simulated in one MPI task, and each zone corresponds to a small linear system with each one resulting in multiple sequential solving with an LU factorization [28]. The typical matrix size is 150x150. If the matrix is symmetric and definite, the problem is reduced to a batched Cholesky factorization, which is widely used in computer vision and anomaly detection in images [29, 10].

Figure 1.1: From left to right: shock triple-point problems using FEM with Q8Q7, Q4Q3, Q2Q1 methods, respectively.

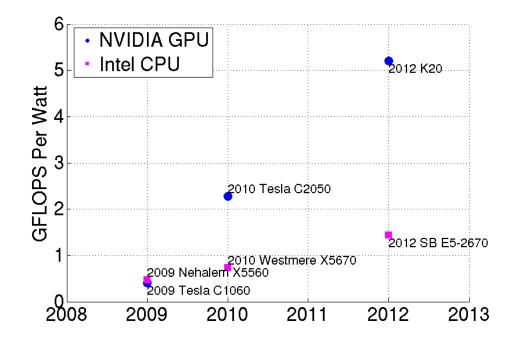

High performance computing (HPC) is increasingly becoming power and energy constrained. The average power of TOP 10 supercomputers climbed from 3.2MW in 2010 to 6.6MW in 2013, which is enough to power a small town[43]. Department of Energy has set a goal of 50MW for Exascale systems, which require one watt to yield 20 GFLOPS. Limited by the power budget, more and more computing systems seek to install accelerators, such as GPUs, due to their high floating-point operation capability and energy efficiency advantage over CPUs, as shown in Figure 1.2. The co-processor accelerated computing has become a mainstream movement in HPC. This trend is indicated in the ranking of the TOP 500 and the Green 500. In the June 2013 TOP 500 ranking, 51 supercomputers are powered by GPUs[43]. Although accelerated systems make up only 10% of the systems, they accomplish 33% of the computing power. In the June 2013 Green 500 ranking, the most power efficient system accelerated by K20 GPUs surpassed 3 GFLOPS per watt, up from 2 GFLOPS per watt in the June 2012 ranking[18].

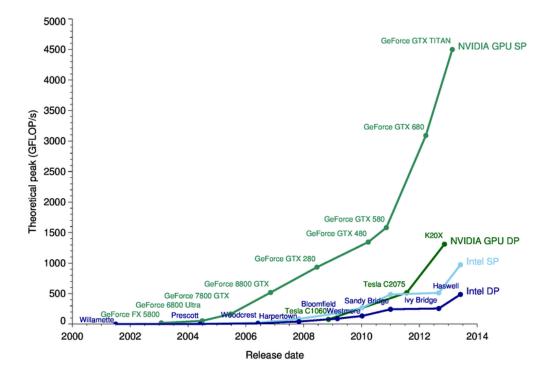

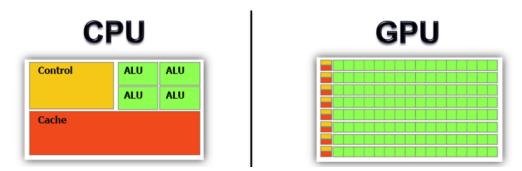

The vast difference between the computing capability of CPUs and GPUs (shown in Figure 1.3) is due to their architecture design. For CPUs, more transistors are used for caches or control units while they are devoted to arithmetic units for GPUs, as depicted in Figure 1.4. Different from CPUs, GPUs cannot run operating systems but are designed for compute-intensive, highly parallel computation purpose. Compared to CPUs, GPUs have limited cache size and cache level; therefore DRAM' latency is relatively high. Rather than caching data, GPUs launch thousands or even millions of light-weight threads for computation to hide the memory access latency.

Figure 1.2: GFLOPS per watt of NVIDIA GPUs and Intel CPUs in double precision.

The development of CPUs, as noted in Sections 1.2 and 3.1, can be done easily using existing software infrastructure. On the other hand, GPUs, due to their SIMD design, are efficient for large data parallel computation; therefore, they have often been used in combination with CPUs, which handle the small and difficult to parallelize tasks. Although tons of linear algebra libraries are on CPUs, the lack of linear algebra software for small problems is especially noticeable for GPUs. The need to overcome the challenges of solving small problems on GPUs is also

Figure 1.3: Single precision (SP) and double precision (DP) computing capability of NVIDIA GPUs and Intel CPUs [31].

related to the GPU's energy efficiency, often four to five times better than that of multicore CPUs. To take advantage of GPUs, code ported on GPUs must exhibit high efficiency. Thus, one of the main goals of this work is to develop GPU algorithms and their implementations on small problems to outperform multicore CPUs in raw performance and energy efficiency. In particular, we target three onesided factorizations (LU, QR, and Cholesky) and one two-sided factorizations bidiagonalization for a set of small dense matrices.

#### 1.2 Related Work

The questions are what programming and execution model is best for small problems, how to offload work to GPUs, and what should interact with CPUs, if anything. The offload-based execution model and the accompanying terms, *host* and *device*,

Figure 1.4: Differences between GPU and CPU.

have been established by the directive-based programming standards: OpenACC [35] and OpenMP [36]. While these specifications are *host-centric*, in the context of dense linear algebra computations, we recognize three different modes of operation: hybrid, native, and batched execution. The first employs both the host CPU and the device accelerator, be it a GPU or an Intel coprocessor, which cooperatively execute on a particular algorithm. The second offloads the execution completely to the accelerator. The third is the focus of this dissertation and involves execution of many small problems on the accelerator while the host CPU only sends the input data and receives the computed result in a pipeline fashion to alleviate the dearth of PCI-E bandwidth and long latency of the transfers.

Small problems can be solved efficiently on a single CPU core, e.g., using vendor supplied libraries such as MKL [23] or ACML [2] because the CPU's memory hierarchy would back a "natural" data reuse (small enough problems can fit into small, fast memory). Besides memory reuse, to further speed up the computation, vectorization to use SIMD processor supplementary instructions can be added either explicitly as in the Intel Small Matrix Library [22] or implicitly through the vectorization in BLAS. Batched factorizations then can be efficiently computed for multicore CPUs by having a single core factorize a single problem at a time (see Section 3.1). However, the energy consumption is higher than the GPU-based factorizations.

For GPU architectures, prior work has been concentrated on achieving highperformance for large problems through hybrid algorithms [42]. Motivations come from the fact that the GPU's compute power cannot be used on panel factorizations as efficiently as on trailing matrix updates [44]. Because the panel factorization is considered a latency-bound workload, which faces a number of inefficiencies on throughput-oriented GPUs, it is preferred to be performed on the CPU. As a result, various hybrid algorithms are developed in which panels are factorized on the CPU while the GPU is used for trailing matrix updates (mostly GEMMs) [1, 14]. Note that a panel's data transfer to and from the CPU is required at each step of the loop. For large enough problems, the panel factorization and associated CPU-GPU data transfers can be overlapped with the GPU work. For small problems, however, this application is not possible; and our experience has shown that hybrid algorithms would not be as efficient as they are for large problems.

Most batched work on GPUs comes from NVIDIA and their collaborators. Villa et al. [37], [38] obtained good results for batched LU developed entirely for GPU execution, where a single CUDA thread, or a single thread block, was used to solve one linear system at a time. Their implementation targets very small problems (of sizes up to 128). Their work is released in CUBLAS as the batched LU routine. Similar techniques, including the use of a warp of threads for a single factorization, were investigated by Wainwright [45] for LU with full pivoting on matrices of size up to 32. Although the problems considered were often small enough to fit in the GPU's shared memory (e.g., 48 KB on a K40 GPU), and thus to benefit from data reuse  $(n^2 \text{ data for } \frac{2}{3}n^3 \text{ flops for LU})$ , the performance of these approaches was up to about 20 Gflop/s in double precision and did not exceed the maximum performance due to memory bound limitations (e.g., 46 Gflop/s on a K40 GPU for DGEMV's  $2n^2$  flops on  $n^2$  data; see Table A.1).

In version 4.1 released in January 2012, NVIDIA CUBLAS added a batched GEMM routine. In v5.0 released in October 2012, CUBLAS added a batched LU and a batched TRSM routine with the dimension of the matrix limited to 32x32. Version 5.5 removed the dimension limit but still restricted the matrix on square ones. The latest v6.5 included a batched QR routine. In the latest MKL v11.3

released in May 2015, Intel added its first batched routine - GEMM on the Xeon Phi accelerator.

To our best knowledge, implementations of batched two-sided bi-diagonalization factorizations, either on CPUs or GPUs, have not been reported. Here we review the related algorithms. A two-sided matrix bi-diagonalization for multicore CPU based on tile algorithms was studied in [26]. Their implementation was based on Householder reflectors. Ralha proposed a one-sided bi-diagonalization algorithm[39], which implicitly tridiagonalized the matrix  $A^T A$  with a one-sided orthogonal transformation of A. This approach suffers from numerical stability issues, and the resulting matrix may lose its orthogonality properties. Ralha's approach was improved by Barlow et al. to enhance the stability by merging the two distinct steps to compute the bidiagonal matrix B [6]. In our batched implementation, we adopt Householder reflectors to perform the orthogonal transformation to guarantee the numerical stability. It is different from less computational expensive but less stable transformations, for example, the Gaussian elimination.

## Chapter 2

# Algorithms for Related Linear Algebra Problems

### 2.1 One-sided Factorizations

In this section, we present a brief overview of the linear algebra algorithms for the development of either Cholesky, Gauss, or the Householder QR factorizations based on block outer-product updates of the trailing matrix. Conceptually, one-sided factorization maps a matrix A into a product of matrices X and Y:

$$\mathcal{F}: \begin{bmatrix} A_{11} & A_{12} \\ A_{21} & A_{22} \end{bmatrix} \mapsto \begin{bmatrix} X_{11} & X_{12} \\ X_{21} & X_{22} \end{bmatrix} \times \begin{bmatrix} Y_{11} & Y_{12} \\ Y_{21} & Y_{22} \end{bmatrix}.$$

Algorithmically, this corresponds to a sequence of in-place transformations of A, whose storage is overwritten with the entries of matrices X and Y ( $P_{ij}$  indicates currently factorized panels):

$$\begin{bmatrix} A_{11}^{(0)} & A_{12}^{(0)} & A_{13}^{(0)} \\ A_{21}^{(0)} & A_{22}^{(0)} & A_{23}^{(0)} \\ A_{31}^{(0)} & A_{32}^{(0)} & A_{33}^{(0)} \end{bmatrix} \rightarrow \begin{bmatrix} P_{11} & A_{12}^{(0)} & A_{13}^{(0)} \\ P_{21} & A_{22}^{(0)} & A_{23}^{(0)} \\ P_{31} & A_{32}^{(0)} & A_{33}^{(0)} \end{bmatrix} \rightarrow$$

$$\rightarrow \begin{bmatrix} XY_{11} & Y_{12} & Y_{13} \\ X_{21} & A_{22}^{(1)} & A_{23}^{(1)} \\ X_{31} & A_{32}^{(1)} & A_{33}^{(1)} \end{bmatrix} \rightarrow \begin{bmatrix} XY_{11} & Y_{12} & Y_{13} \\ X_{21} & P_{22} & A_{23}^{(1)} \\ X_{31} & P_{32} & A_{33}^{(1)} \end{bmatrix} \rightarrow \begin{bmatrix} XY_{11} & Y_{12} & Y_{13} \\ X_{31} & P_{32} & A_{33}^{(1)} \end{bmatrix} \rightarrow \begin{bmatrix} XY_{11} & Y_{12} & Y_{13} \\ X_{21} & XY_{22} & Y_{23} \\ X_{31} & X_{32} & A_{33}^{(2)} \end{bmatrix} \rightarrow \begin{bmatrix} XY_{11} & Y_{12} & Y_{13} \\ X_{21} & X_{22} & Y_{23} \\ X_{31} & X_{32} & A_{33}^{(2)} \end{bmatrix} \rightarrow \begin{bmatrix} XY_{11} & X_{12} & Y_{13} \\ X_{21} & X_{22} & Y_{23} \\ X_{31} & X_{32} & XY_{33} \end{bmatrix} \rightarrow \begin{bmatrix} XY_{11} & Y_{12} & Y_{13} \\ X_{21} & XY_{22} & Y_{23} \\ X_{31} & X_{32} & XY_{33} \end{bmatrix} \rightarrow \begin{bmatrix} XY_{1} \\ XY_{1} \\ XY_{1} \\ X_{21} \\ XY_{22} \\ XY_{31} \\ XY_{31} \\ XY_{32} \\ XY_{33} \end{bmatrix} \rightarrow \begin{bmatrix} XY_{1} \\ XY_{1} \\ XY_{1} \\ XY_{31} \\ XY_{33} \\ XY_{33} \end{bmatrix} \rightarrow \begin{bmatrix} XY_{1} \\ XY_{1} \\ XY_{1} \\ XY_{33} \\ XY_{33} \end{bmatrix} \rightarrow \begin{bmatrix} XY_{1} \\ XY_{1} \\ XY_{33} \\ XY_{33} \\ XY_{33} \end{bmatrix} \rightarrow \begin{bmatrix} XY_{1} \\ XY_{1} \\ XY_{33} \\ XY_{33} \\ XY_{33} \end{bmatrix} \rightarrow \begin{bmatrix} XY_{1} \\ XY_{1} \\ XY_{33} \\ YY_{33} \\ XY_{33} \\ YY_{33} \\ XY_{33} \\ XY_{33} \\ XY_{33} \\ YY_{33} \\ YY$$

where  $XY_{ij}$  is a compact representation of both  $X_{ij}$  and  $Y_{ij}$  in the space originally occupied by  $A_{ij}$ .

**Table 2.1:** Panel factorization and trailing matrix update routines. x represents the precision, which can be single (S), double (D), single complex (C) or double complex (Z).

|                      | Cholesky          | Householder | Gauss             |

|----------------------|-------------------|-------------|-------------------|

| PanelFactorize       | xPOTF2            | xGEQF2      | xGETF2            |

|                      | $\mathbf{x}$ TRSM |             |                   |

|                      | xSYRK2            | xLARFB      | xLASWP            |

| TrailingMatrixUpdate | xGEMM             |             | $\mathbf{x}$ TRSM |

|                      |                   |             | xGEMM             |

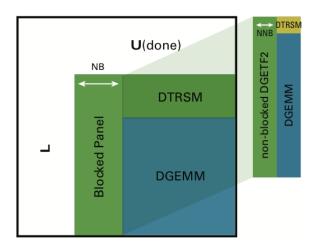

There are two distinct phases in each step of the transformation from [A] to [XY]: panel factorization (P) and trailing matrix update  $A^{(i)} \rightarrow A^{(i+1)}$ . Implementation of these two phases leads to a straightforward iterative scheme as shown in Algorithm 1. The panel factorization is accomplished by a non-blocked routine. Table 2.1 shows the BLAS and the LAPACK routines that should be substituted for the generic routines named in the algorithm.

Algorithm 1 is called blocked algorithm since every panel P is of size nb which allows the trailing matrix update to use the Level 3 BLAS routines. Note that if nb = 1 the algorithm falls back to the standard non-blocked algorithm introduced by LINPACK in the 1980s.

for  $P_i \in \{P_1, P_2, \dots, P_n\}$  do | PanelFactorize $(P_i)$ | TrailingMatrixUpdate $(A^{(i)})$ end

Algorithm 1: Two-phase implementation of a one-sided factorization.

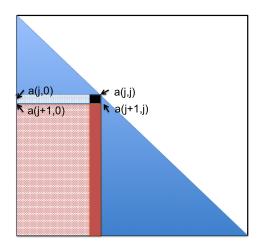

We use a Cholesky factorization (POTF2) of a symmetric positive definite matrix to illustrate the Level 2 BLAS-based non-blocked algorithm, as outlined Figure 2.1. Due to the symmetry, the matrix can be factorized either as an upper triangular matrix or as a lower triangular matrix (e.g., only the shaded data is accessed if the lower side is to be factorized). Given a matrix A of size  $n \times n$ , there are n steps. Steps go from the upper-left corner to lower-right corner along the diagonal. At step j, the column vector A(j : n, j) is to be updated. First, a dot product of the row vector A(j, 0 : j) is needed to update the element A(j, j)(in black). Then the column vector A(j+1:n-1,j) (in red) is updated by a GEMV  $A(j+1:n-1, 0: j-1) \times A(j, 0: j-1)$ followed by a scaling operation. This non-blocked Cholesky factorization involves two Level 1 BLAS routines (DOT and SCAL) and a Level 2 BLAS routine GEMV. Since there are n steps, these routines are called n times; thus, one can expect that POTF2's performance will depend on Level 1 and Level 2 BLAS operations' performance. Hence, it is a slow memory-bound algorithm. The non-blocked algorithm of LU and householder QR can be found in LAPACK [4].

The floating-point operation counts and elements access of related Level 2 and 3 BLAS and one-sided factorization LAPACK routines are shown in Table A.1. Level 1 and Level 2 BLAS operations (e.g., GEMV) are memory bound since they have much lower flops per element compared to Level 3 BLAS (e.g., GEMM). Note that both blocked and non-blocked algorithms inherently have the same floating-point operations. The difference is that the blocked algorithm explores the Level 3 BLAS

Figure 2.1: Non-blocked Cholesky factorization

by reducing the amount of Level 2 BLAS operations and achieves higher efficiency through the data and cache reuse [16].

The classical hybrid implementation as described in Algorithm 1 lacks efficiency because either the CPU or the GPU is working at a time and a data transfer to and from the CPU is required at each step. The MAGMA library further modified the algorithm to overcome this issue and to achieve closer-to-optimal performance. In fact, the ratio of the computational capability between the CPU and the GPU is orders of magnitude; thus, the common technique to alleviate this imbalance and keep the GPU loaded is to use lookahead.

for  $P_i \in \{P_1, P_2, \dots, P_n\}$  do CPU: PanelFactorize $(P_i)$ GPU: TrailingMatrixUpdate of only next panel of  $(A^{(i)}$  which is  $P_2)$ CPU and GPU work in parallel: CPU go to the next loop while GPU continue the update GPU: continue the TrailingMatrixUpdate of the remaining  $(A^{(i-1)})$  using the previous panel  $(P_{i-1})$ end Algorithm 2: Lookahead of depth 1 for the two-phase factorization.

Algorithm 2 shows a very simple case of lookahead of depth 1. The update operation is split into an update of the next panel and an update of the rest of

the trailing matrix. The splitting is done to overlap the communication and the panel factorization with the update operation. This technique lets us hide the panel factorization' memory-bound operations and keep the GPU loaded by the trailing matrix update.

In the batched implementation, however, we cannot afford such a memory transfer between CPU and GPU at any step since the trailing matrix is small and the amount of computation is not sufficient to overlap it in time with the panel factorization. Many small data transfers will take away any performance advantage enjoyed by the GPU. In the next Chapter 3, we describe our proposed implementation and optimization of the batched algorithm.

The performance is recognized as Gflop/s across the dissertation. The floatingpoint counts of related BLAS and LAPACK routines are demonstrated in Table A.1 [8]. Asymptotically, the lower-degree terms (< 3) of the flops can be omitted if the size is big enough.

#### 2.2 Forward/Backward Substitution

Solving linear systems Ax = b is a fundamental problem in linear algebra, where A is a  $n \times n$  matrix, b is the input vector of size n, and x is the unknown solution vector. Solving linear systems can fall into two broad classes of methods: direct methods and iterative methods. Iterative methods are less expensive in terms of flops but hard to converge. Preconditioning is usually required to improve convergence. Direct methods are more robust but more expensive. In our implementation, we consider direct methods.

Forward/backward substitution (TRSV) is used in solving linear systems, after matrix A is factorized into triangular matrices by one of the three one-sided factorizations. Although many dense matrix algorithms have been substantially accelerated on GPUs, mapping TRSV on GPUs is not easy due to its inherently sequential nature. In CUDA, execution of threads should be independent as much as possible to allow parallel execution. Orders among the threads in one warp (32 threads) should be avoided since any divergence will cause serialization execution. If one thread is in the divergence branch, the other 31 threads in the same warp will be idle. Unfortunately, in TRSV, computation (and thus, threads) must be ordered because of data dependence. Equation 2.2 is an example of forward substitution. The following solution depends all previous solutions. Therefore, the degree of parallelism in TRSV is limited. Although the operations' order cannot be changed, the sequential operations can be aggregated to improve the memory throughput by minimizing memory transactions in the blocked algorithm.

$$a_{11}x_1 = b_1$$

$$a_{21}x_1 + a_{22}x_2 = b_2$$

$$a_{31}x_1 + a_{32}x_2 + a_{33}x_3 = b_3$$

$$\vdots \qquad \vdots$$

$$a_{n1}x_1 + a_{n2}x_2 + \dots + a_{nn}x_n = b_n$$

To solve it,

- Step 1:  $x_1 = b_1/a_{11}$

- Step 2:  $x_2 = (b_2 a_{21} * x_1)/a_{22}$ ,  $x_2$  depends on  $x_1$

- Step 3:  $x_3 = (b_3 a_{31} * x_1 a_{32} * x_2)/a_{33}$ ,  $x_3$  depends on  $x_1$  and  $x_2$

- Step 4:  $x_4 = (b_4 a_{41} * x_1 a_{42} * x_2 a_{43} * x_3)/a_{44}$ ,  $x_4$  dpends on  $x_1$  to  $x_3$

- Step n:  $x_n$  depends on all previous results  $x_1, x_2, ..., x_{n-1}$

A blocked algorithm first sequentially computes  $x_1, x_2, ..., x_{nb}$  (*nb* is the blocking size), then applies a matrix-vector multiplication (GEMV) to obtain partial results of  $x_{nb+1}, x_{nb+2}, ..., x_{2nb}$ . In the above example, after  $x_1$  and  $x_2$  are sequentially computed in Step 1 and 2,  $a_{31} * x_1 - a_{32} * x_2$  and  $a_{41} * x_1 - a_{42} * x_2$  in Step 3 and 4, can be done by one GEMV routine to get partial results of  $x_3$  and  $x_4$ .  $x_3$  and  $x_4$  will be updated

to final ones in the next sequential solving. In GEMV, the computation is regular and there is no thread divergences.

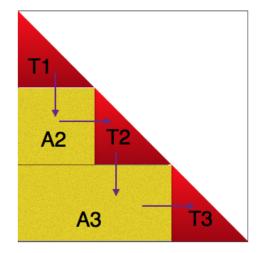

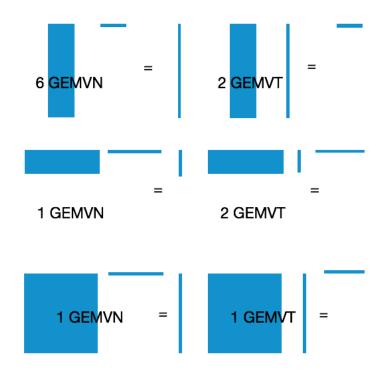

The blocked algorithm overview is given in Figure 2.2.We use forward substitution as an example. The original matrix is divided into triangular blocks  $T_i$  (in red) and rectangular blocks  $A_i$  (in yellow). The solution vector X is also divided into blocks Xi, where i = 1, 2, ..., n/nb. The triangular blocks are solved by the sequential algorithm. GEMV routines are applied on the rectangular blocks. The computation flow goes as follows. First, triangular block T1 is solved to get X1. A GEMV routine performs A2 \* X1 to get the partial result of X2 which will be updated to the final result in the next T2 solving. After T2, another GEMV routine will take A3 and X1, X2 to get the partial result of X3 which will be updated in T3 solving. Iteratively, all the blocks  $X_i$  are solved. Backward substitution is in a reverse order. Each triangular matrix  $T_i$  can be further blocked recursively, which becomes a recursive blocked algorithm. The performance of TRSV is bounded by the performance of GEMV on blocks  $A_i$  and triangular blocks  $T_i$  that are in the critical path. It is easy to see that TRSV is a Level 2 BLAS routine. Its floating-point operation count is shown in Table A.1.

Figure 2.2: Overview of the blocked algorithm for forward substitution

#### 2.3 Householder Bi-diagonalization

Two-sided factorizations, like the singular value decomposition (SVD) factorize a  $M \times N$  matrix A as  $A = UWV^*$ , where U is an orthogonal  $M \times M$  matrix and V is an orthogonal  $N \times N$  matrix. The diagonal elements of matrix W are non-negative numbers in descending order and all off-diagonal elements are zeros. The first min(m, n) columns of U and V are the left and right singular vectors of A. SVD is used to solve underdetermined and overdetermined systems of linear equations. It is also used to determine the rank, range and null space of a matrix. It is extensively used in signal processing and statistics. A high order FEM CFD simulation requires solving SVD in a batched fashion[13].

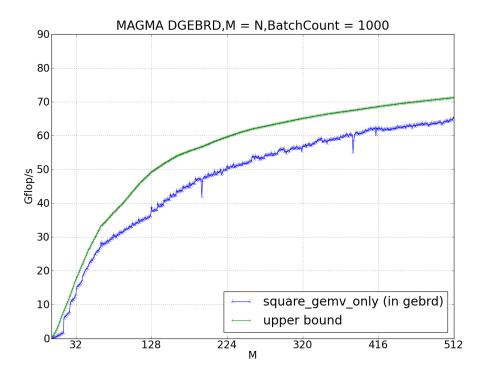

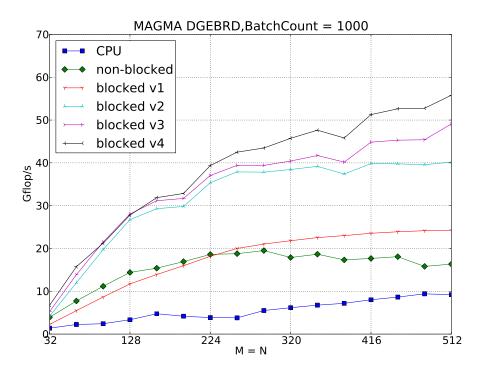

The singular decomposition algorithm reduces the matrix to bi-diagonal form in the first stage and then diagonalizes it using the QR algorithm in the second stage. Most efforts focus on the more complicated first stage, bi-diagonalization (or BRD for short). Previous studies show that BRD portion takes 90% - 99% of the time if only singular values are needed, or 30% -75% if singular vectors are additionally required [26].

The first stage of bi-diagonalization factorizes a  $M \times N$  matrix A as

$A = UBV^*$ , where U and V are orthogonal matrices. B is in upper diagonal form with only the diagonal and upper superdiagonal elements being non-zero.

Given a vector u with unit length, the matrix  $H = I - 2uu^*$  is a Householder transformation (reflection). For a given vector x, there exists a Householder transformation to zero out all but the first element of the vector x. The classic stable Golub-Kahan method (GEBRD) applies a sequence of Householder transformations from left to right to reduce a matrix into bi-diagonal form [17]. See Figure 2.3. In the left update of each step, a column vector is annihilated with Householder transformation and then the Householder reflector is applied to update the remaining matrix. Vectors defining the left Householder reflectors are stored as columns of matrix U. In the right update, a row vector is annihilated and again applied to update. The vectors defining the right Householder reflectors are stored in matrix V. This algorithm is sequential and rich in Level 2 BLAS GEMV routine that is applied in every step for updating the rest of the matrix.

The sequential algorithm can be blocked to aggregate the transformations to delay the update to improve the efficiency. The blocked algorithm is divided into two distinct phases: panel factorization and update of trailing matrix, as shown in Figure 2.4. The blocked two-phase algorithm is described in Algorithm 3. The factorization of the panel  $A_i$  proceeds in n/nb steps of blocking size nb. One step is composed by BLAS and LAPACK routines, with LABRD for panel factorization and GEMM for trailing matrix update. The panel factorization LABRD is still sequential. The saved left and right Householder reflectors are saved in matrix A in replace of annihilated elements. The accumulated transformations are saved in matrix X and Y, respectively. Once the transformations are accumulated within the panel, they can be applied to update trailing matrix once by Level 3 BLAS operations efficiently.

The total operations of GEBRD is  $8n^3/3$ , if we consider the square matrix size as n for simplicity. The sequential algorithm is rich in Level 1 and 2 BLAS operations. The blocked algorithm transforms half of the operations into Level 3 BLAS GEMM (for trailing matrix update) to make it overall similar to Level 2.5 BLAS. The other half is still Level 1 and 2 BLAS operations. Because Level 3 BLAS is much faster than Level 2 BLAS, the Level 2 BLAS in the panel factorization is the bottleneck. The peak performance of GEBRD is up to two times that of Level 2 BLAS GEMV as discussed Section 4.2.3.

for  $i \in \{1, 2, 3, ..., n/nb\}$  do  $\{A_i = A_{(i-1) \times nb:n, (i-1) \times nb:n}\}$   $\{C_i = A_{i \times nb:n, i \times nb:n}\}$ Panel Factorize LABRD( $A_i$ ), reduce  $A_i$  to bi-diagonal form, returns matrices X, Y to update trailing matrix  $C_i$ , U, V are stored in factorized ATrailing Matrix Update  $C_i = C_i - V * Y' - X * U'$  with gemm end for Algorithm 3: Two-phase implementation of the Householder BRD algorithm.

$$U_{1}^{*}A = \begin{bmatrix} \mathbf{x} & \mathbf{x} & \mathbf{x} & \mathbf{x} \\ \mathbf{0} & \mathbf{x} & \mathbf{x} & \mathbf{x} \end{bmatrix} \longrightarrow U_{1}^{*}AV_{1} = \begin{bmatrix} x & \mathbf{x} & \mathbf{0} & \mathbf{0} \\ 0 & \mathbf{x} & \mathbf{x} & \mathbf{x} \end{bmatrix} \longrightarrow U_{2}^{*}U_{1}^{*}AV_{1}V_{2} = \begin{bmatrix} x & x & 0 & 0 \\ 0 & \mathbf{x} & \mathbf{x} & \mathbf{x} \\ 0 & \mathbf{0} & \mathbf{x} & \mathbf{x} \end{bmatrix} \longrightarrow U_{2}^{*}U_{1}^{*}AV_{1}V_{2} = \begin{bmatrix} x & x & 0 & 0 \\ 0 & x & \mathbf{x} & \mathbf{0} \\ 0 & 0 & \mathbf{x} & \mathbf{x} \\ 0 & \mathbf{0} & \mathbf{0} & \mathbf{0} \end{bmatrix} = B.$$

**Figure 2.3:** A sequence of Householder transformations reduces the matrix into bi-diagonal form in the sequential algorithm.

Figure 2.4: The matrix is divided into panel and trailing matrix in blocked bidiagonalization algorithm.

### Chapter 3

### Methodology and Implementation

The purpose of batched routines is to solve a set of independent problems in parallel. When one matrix is large enough to fully load the device with work, batched routines are not needed; the set of independent problems can be solved in serial as a sequence of problems. Moreover, it is preferred to solve it in serial rather than in a batched fashion, to better enforce locality of data and increase the cache reuse. However, when matrices are small (for example, matrices of size less than or equal to 512), the amount of work needed to perform the factorization cannot saturate the device, either the CPU or the GPU); thus, there is a need for batched routines.

#### **3.1** Batched Design for Multicore CPUs

In broad terms, batched factorization on multicore CPUs can be approached in two main ways. The first is to parallelize each small factorization across all the cores, and the second is to execute each factorization sequentially on a single core with all the cores working independently on their own input data. With these two extremes clearly delineated, it is easy to see the third possibility: the in-between solution where each matrix is partitioned among a handful of cores, and multiple matrices are worked on at a time as the total number of available cores permits. We tested various levels of nested parallelism to exhaust all possibilities of optimization available on CPUs. The two extremes mentioned above get about 40 Gflop/s (one outer task and all 16 cores working on a single problem at a time – 16-way parallelism for each matrix) and 100 Gflop/s (16 outer tasks with only a single core per task – sequential execution each matrix), respectively. The scenarios between these extremes achieve somewhere in between in terms of performance. For example, with eight outer tasks with two cores per task, we achieve about 50 Gflop/s. Given these results and to increase the presentation's clarity, we only report the extreme setups in the results shown below.

# 3.2 Batched Methodology and Implementation for GPUs

#### **3.2.1 MAGMA**

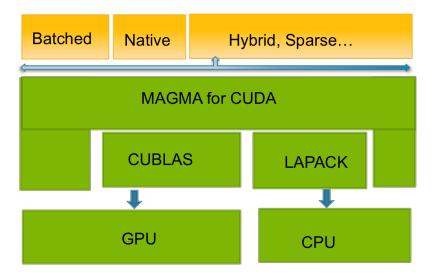

Our batched work is part of the Matrix Algebra on GPU and Multicore Architectures (MAGMA) project, which aims to develop a dense linear algebra library similar to LAPACK but for heterogeneous architectures, starting with current Multicore+GPU systems [21]. To address the complex challenges of the emerging hybrid environments, optimal software solutions will have to hybridize, combining the strengths of different algorithms within a single framework. Building on this idea, MAGMA aims to design linear algebra algorithms and frameworks for hybrid many-core and GPU systems that can enable applications to fully exploit the power that each of the hybrid components offers.

MAGMA is an open-sourced project. The latest release in May 2015 is v1.6.2. CUBLAS is the NVIDIA vendor CUDA library on GPUs. LAPACK is the Fortran library on CPUs. MAGMA calls some of CUBLAS and LAPACK routines but includes more advanced routines. MAGMA has several functionalities targeting corresponding types of problems, including dense, sparse, native and hybrid, as shown in Figure 3.1. Their assumptions of problem size and hardware are different. The hybrid functionality exploits both the CPU and the GPU hardware for large problems. The native functionality only exploits the GPU for large problems. The batched functionality solving many small problems is recently integrated in MAGMA. Throughout this dissertation, our batched routines are named as MAGMA batched routines. For example, our batched GEMM routine is referred to as MAGMA batched GEMM.

Figure 3.1: MAGMA software stack

#### 3.2.2 Batched BLAS Kernel Design

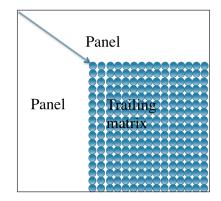

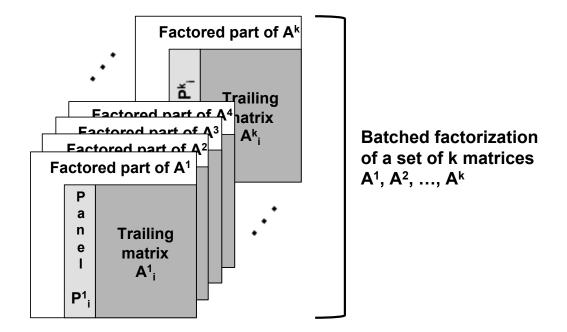

Our batched routines are based on batched BLAS, the way they are implemented and all the relevant optimizations that have been incorporated to achieve performance. All routines are batched and denoted by the corresponding LAPACK routine names. We have implemented them in the four standard floating-point precisions – single real, double real, single complex, and double complex. For convenience, we use the double precision routine name throughout this study. In a batched problem solution methodology that is based on batched BLAS, many small dense matrices must be factorized simultaneously (as illustrated in Figure 3.2), meaning that all the matrices will be processed simultaneously by the same kernel.

The batched kernel does not make any assumption about the layout of these matrices in memory. The batched matrices are not necessarily stored continuously in memory. The starting addresses of every matrix is stored in an array of pointers. The batched kernel takes the array of pointers as input. Inside the kernel, each matrix is assigned to a unique batch ID and processed by one device function. Device functions are low-level and callable only by CUDA kernels and execute only on GPUs.

The device function only sees a matrix by the batched ID and thus still maintains the same interface as the classic BLAS. Therefore, our batched BLAS is characterized by two levels of parallelism. The first level is the task-level parallelism among matrices. The second level of fine-grained data parallelism is inside each matrix through device functions to exploit the SIMT architecture.

The device function is templated with C++. The settings (like, the thread blocks size, tile size) are stored in C++ template parameters. In order to find the optimal setting for each type of problems, we adopt an auto-tuning technique, which will be discussed in Section 3.3.1 and 3.3.2.

#### Trade-offs between Data Reuse and Degrees of Parallelism

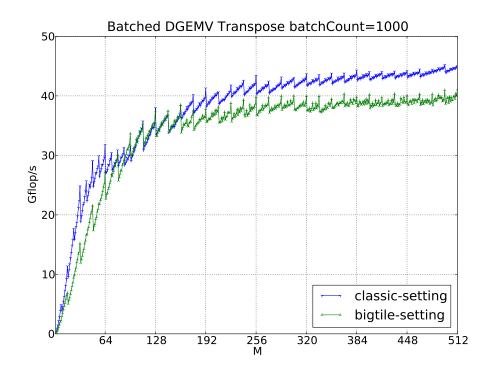

Shared memory is fast on-chip memory. The frequent accessed data of the matrix is loaded in shared memory before copying back to the main memory. However, shared memory can not live across multiple kernels and span thread blocks. When one kernel exits, the data in shared memory has to be copied back to the GPU main memory since the shared memory will be flushed. Therefore, many kernel launchings not only introduce launching overhead but potentially result in data movement, because the data has to be read again from GPU main memory in the next kernel, causing redundant memory access. Besides, shared memory is private per thread block. In standard large-sized problems, the matrix is divided into tiles with each tile loaded in shared memory. Different thread blocks access the tiles in an order determined by the algorithm. Synchronization of the computation of the tiles is accomplished by finishing the current kernel and relaunching another in the GPU main memory. However, in smallsized batched problems, too many kernel launchings should be avoided, especially for panel factorization where each routine has a small workload and a high probability of data reuse. Therefore, in our design, each matrix is assigned with one thread block. The synchronization is accomplished in shared memory and by barriers inside the thread block. We call this setting big-tile setting. The naming is based this observation: if the tile is big enough that the whole matrix is inside the tile, it reduces to the point that one thread block accesses the whole matrix.

However, compared to the big-tile setting, the classic setting with multiple thread blocks processing one matrix may have a higher degree of parallelism as different parts of the matrix are processed simultaneously, especially for matrices of big size. Thus, overall there is a trade-off between them. Big-tile setting allows data to be reused through shared memory but suffers a lower degree of parallelism. The classic setting has a higher degree of parallelism but may lose the data reuse benefits. The optimal setting depends on many factors, including the algorithm and matrix size, and is usually selected by practical tuning.

Multiple device functions can reuse the same shared memory as long as they are called in the same kernel. This design, device functions instead of kernels serve as the basic component, allows the computation of BLAS routines to be merged easily in one kernel and takes advantage of shared memory. Merging codes usually demodulize the BLAS-based structure of LAPACK algorithm. However, since device functions preserve the BLAS-like interface, the BLAS-based structure can be gracefully maintained.

### 3.2.3 Implementation of One-sided Factorizations and Bidiagonalization on GPUs

Algorithmically, one approach to the batched factorization problems for GPUs is to consider that the matrices are small enough, and, therefore factorize them using the non-blocked algorithm. The implementation is simple but the performance obtained turns out to be unacceptably low. Thus, the implementation of the batched factorization must also be blocked and thus must follow the same iterative scheme (*panel factorization* and *trailing matrix update*) shown in Algorithm 1. Note that the trailing matrix update consists of Level 3 BLAS operations (HERK for Cholesky, GEMM for LU and LARFB for QR) which are compute intensive and thus can perform very well on the GPU. Therefore, the most difficult phase of the algorithm is the panel factorization.

Figure 3.2 is a schematic view of the batched problem considered. Basic block algorithms, as the ones in LAPACK [4], factorize at step i a block of columns, denoted by panel  $P_i$ , followed by the application of the transformations accumulated in the panel factorization to the trailing sub-matrix  $A_i$ .

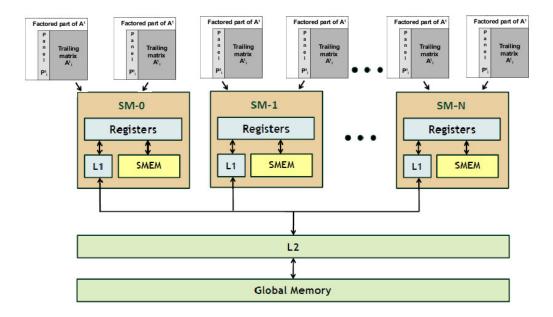

A recommended way of writing efficient GPU kernels is to use the GPU's shared memory – load it with data and reuse that data in computations as much as possible. The idea behind this technique is to perform the maximum amount of computation before writing the result back to the main memory. However, the implementation of such a technique may be complicated for the small problems considered as it depends on the hardware, the precision, and the algorithm. First, the current size of the shared memory is 48 KB per streaming multiprocessor (SMX) for the newest NVIDIA K40 (Kepler) GPUs, which is a low limit for the amount of batched problems data that can fit at once. Second, completely saturating the shared memory per SMX can decrease the memory-bound routines' performance, since only one thread-block will be mapped to that SMX at a time. Indeed, due to a limited parallelism in a small

Figure 3.2: A batched one-sided factorization problem for a set of k dense matrices

panel's factorization, the number of threads used in the thread block will be limited, resulting in low occupancy, and subsequently poor core utilization.

Due to the SIMT programming model, all active threads execute the same instruction but on different data (operands). The best performance is achieved when all the processors cores in SMX are busy all the time, and the device memory access and latency can be hidden completely. The advantages of multiple blocks residing on the same SMX is that the scheduler can swap out a thread block waiting for data from memory and push in the next block that is ready to execute [41]. This process is similar to pipelining in CPU. In our study and analysis, we found that redesigning the algorithm to use *a small amount* of shared memory per kernel (less than 10KB) not only provides an acceptable data reuse but also allows many thread-blocks to be executed by the same SMX concurrently, thus taking better advantage of its resources. See Figure 3.3. The performance obtained is three times better than the one in which the entire shared memory is saturated. Since the CUDA warp consists of 32 threads, it is recommended to develop CUDA kernels that use multiples of 32 threads per thread block.

For good performance of Level 3 BLAS in trailing matrix update, panel width nb is increased. Yet, this increases tension as the panel is a sequential operation because a larger panel width results in larger Amdahl's sequential fraction. The best panel size is usually a trade-off product by balancing the two factors and is obtained by tuning. We discovered empirically that the best value of nb for one-sided factorizations is 32, and 16 or 8 for two-sided bi-diagonalization. A smaller nb is better because the panel operations in two-sided factorization are more significant than that in one-sided.

Figure 3.3: Multiple factorizations reside on one streaming-multiprocessor to allow the scheduler to swap to hide the memory latency.

**Cholesky panel:** Provides the batched equivalent of LAPACK's POTF2 routine. At step j of a panel of size (m, nb), the column vector A(j : m, j) must be computed. This computation requires a **dot**-product using row A(j, 1 : j) to update element A(j, j), followed by a GEMV  $A(j + 1, 1) \ A(j, 1 : j) = A(j + 1 : m, j)$ , and finally a Scal on column A(j + 1 : m, j). This routine involves two Level 1 BLAS calls (Dot and Scal), as well as a Level 2 BLAS GEMV. Since there are nb steps, these routines are called nb times; thus, one can expect that the performance depends on the performances of Level 2 and Level 1 BLAS operations. Hence, it is a slow, memory-bound algorithm. We used shared memory to load both row A(j, 1 : j) and column A(j+1:m, j) to reuse them, and wrote a customized batched GEMV kernel to read and write these vectors from/into the shared memory.

LU panel: Provides the batched equivalent of LAPACK's GETF2 routine to factorize panels of size  $m \times nb$  at each step of the batched LU factorizations. It consists of three Level 1 BLAS calls (Idamax, Swap and Scal) and one Level 2 BLAS call (GER). The GETF2 procedure is as follows: Find the maximum element of the  $i^{th}$  column, swap the  $i^{th}$  row with the row owning the maximum, and scale the  $i^{th}$  column. To achieve higher performance and minimize the effect on the Level 1 BLAS operation, we implemented a tree reduction to find the maximum where all the threads contribute to find the max. Since it is the same column that is used to find the max then scaled, we load it to the shared memory. This is the only data that we can reuse within one step.

**QR panel:** Provides the batched equivalent of LAPACK's GEQR2 routine to perform the Householder panel factorizations. It consists of *nb* steps where each step calls a sequence of the LARFG and the LARF routines. At every step (to compute one column), the LARFG involves a norm computation followed by a Scal that uses the norm computation's results in addition to some underflow/overflow checking. The norm computation is a sum reduce and thus a synchronization step. To accelerate it, we implemented a two-layer tree reduction where for sizes larger than 32, all 32 threads of a warp progress to do a tree reduction similar to the MPLREDUCE operation, and the last 32 elements are reduced by only one thread. Another optimization is to allow more than one thread-block to execute the LARFG kernel meaning the kernel needs to be split over two: one for the norm and one for scaling in order to guarantee the synchronization. Custom batched implementations of both LARFG and the LARF have been developed.

**BRD panel:** Provides the batched equivalent of LAPACK's LABRD routine to reduce the first nb rows and columns of a m by n matrix A to upper or lower real bidiagonal form by a Householder transformation, and returns the matrices X and Y that later are required to apply the transformation to the unreduced trailing matrix. It consists of nb steps where each step calls a sequence of the LARFG and a set of GEMV and Scal routines. At every step, the LARFG computes one column and one row Householder reflectors, interleaved by a set of GEMV calls. The LARFG involves a norm computation followed by a Scal that uses the results of the norm computation in addition to some underflow/overflow checking. The norm computation is a sum reduce and thus a synchronization step. To accelerate it, we implemented a two-layer tree reduction where for sizes larger than 32, all 32 threads of a warp progress to do a tree reduction similar to the MPI\_REDUCE operation, and the last 32 elements are reduced by only one thread. The Householder reflectors are frequently accessed and loaded in shared memory. The GEMV calls is auto-tuned.

**Trailing matrix updates:** Mainly Level 3 BLAS operations. However, for small matrices it might be difficult to extract performance from very small Level 3 BLAS kernels. The GEMM is the best Level 3 BLAS kernel: it is GPU-friendly, highly optimized, and achieves the highest performance among BLAS. High performance can be achieved if we redesign our update kernels to be represented by GEMMs. For Cholesky, the update consists of the HERK routine. It performs a rank-*nb* update on either the lower or the upper portion of  $A_{22}$ . Since CUBLAS does not provide a batched implementation of this routine, we implemented our own. It is based on a sequence of customized GEMMs in order to extract the best possible performance. The trailing matrix update for the Gaussian elimination (LU) is composed of three routines: the LASWP that swaps the rows on the left and the right of the panel in consideration, followed by the TRSM to update  $A_{12} \leftarrow L_{11}^{-1}A_{12}$ , and finally a GEMM for the update  $A_{22} \leftarrow A_{22} - A_{21}L_{11}^{-1}A_{12}$ . The swap (or pivoting) is required to improve the numerical stability of the Gaussian elimination. However, pivoting can be a performance killer for matrices stored in column major format because

rows, in that case, are not stored continuously in memory, and thus can not be read in a coalesced way. Indeed, a factorization stored in column-major format can be  $2 \times$  slower (depending on hardware and problem sizes) than implementations that transpose the matrix in order to internally use a row-major storage format [44]. Nevertheless, experiments have shown that this conversion is too expensive for batched problems. Moreover, the swapping operations are serial, row by row, limiting the parallelism. To minimize this penalty, we propose a new implementation that emphasizes a parallel swap and allows coalescent read/write. We also developed a batched TRSM routine, which loads the small  $nb \times nb L_{11}$  block into shared memory, inverts it with the TRTRI routine, and then GEMM accomplishes the  $A_{12}$  update. Generally, computing the inverse of a matrix may suffer from numerical stability; but since  $A_{11}$  results from the numerically stable LU with partial pivoting and its size is just  $nb \times nb$ , or in our case  $32 \times 32$ , we do not have this problem [11]. For the Householder QR decomposition, the update operation is referred by the LARFB routine. We implemented a batched LARFB that is composed of three calls to the batched GEMM:  $A_{22} \leftarrow (I - VT^H V^H) A_{22} \equiv (I - A_{21}T^H A_{21}^H) A_{22}$ .

For Householder BRD, the update is achieved by two GEMM routines. The first one is GEMM of a non-transpose matrix with a transpose matrix (A = A - V \* Y'), followed by another GEMM of a non-transpose matrix with a non-transpose matrix (A = A - X \* U'). The update is directly applied on trailing matrix A.

## 3.2.4 Algorithmic Innovation

To achieve high performance of batched execution, the classic algorithms (like that in LAPACK) are reformulated to leverage the computing power of accelerators.

#### Parallel Swapping

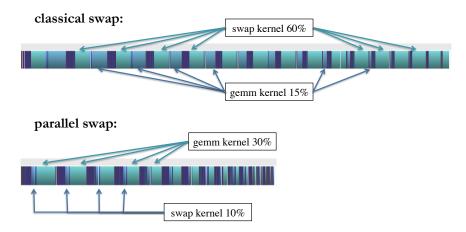

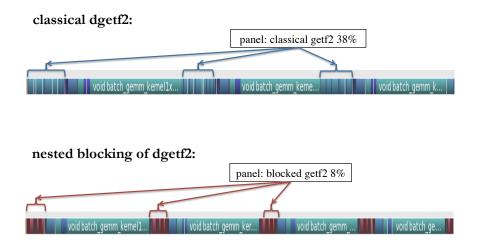

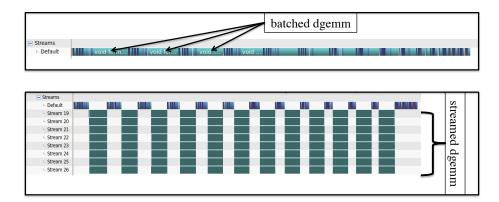

Profiling the batched LU reveals that more than 60% of the time is spent in the swapping routine. Figure 3.4 shows the execution trace of the batched LU for 2,000

matrices of size 512. We can observe on the top trace that the classic LASWP kernel is the most time-consuming part of the algorithm. The swapping consists of nb successive interchanges of two rows of the matrices. The main reason that this kernel is the most time consuming is because the nb row interchanges are performed in a sequential order. Moreover, the data of a row is not coalescent in memory, thus the thread warps do not read/write it in parallel. It is clear that the main bottleneck here is the memory access. Slow memory accesses compared to high compute capabilities have been a persistent problem for both CPUs and GPUs. CPUs alleviate the effect of the long latency operations and bandwidth limitations by using hierarchical caches. Accelerators, on the other hand, in addition to hierarchical memories, use thread-level parallelism (TLP) where threads are grouped into warps and multiple warps assigned for execution on the same SMX unit. The idea is that when a warp issues an access to the device memory, it stalls until the memory returns a value while the accelerator's scheduler switches to another warp. In this way, even if some warps stall, others can execute, keeping functional units busy while resolving data dependencies, branch penalties, and long latency memory requests. In order to overcome the bottleneck of swapping, we propose to modify the kernel to apply all *nb* row swaps in parallel. This modification will also allow the coalescent write back of the top nb rows of the matrix. Note that the first *nb* rows are those used by the TRSM kernel that is applied right after the LASWP, so one optimization is to use shared memory to load a chunk of the *nb* rows, and apply the LASWP followed by the TRSM at the same time. We changed the algorithm to generate two pivot vectors, where the first vector gives the final destination (e.g., row indices) of the top nb rows of the panel, and the second gives the row indices of the nb rows to swap and bring into the top nb rows of the panel. Figure 3.4 depicts the execution trace (bottom) when using our parallel LASWP kernel. The experiment shows that this optimization reduces the time spent in the kernel from 60% to around 10% of the total elapsed time. Note that the colors between the top and the bottom traces do not match each other because the NVIDIA profiler always puts the most expensive kernel in green. As a result, the performance gain obtained is about  $1.8 \times$ .

Figure 3.4: Execution trace of the batched LU factorization using either classic swap (top) or our new parallel swap (bottom).

#### **Recursive Nested Blocking**

The panel factorizations factorize the nb columns one after another, similar to the LAPACK algorithm. At each of the nb steps, either a rank-1 update is required to update the vectors to the right of the factorized column i (this operation is done by the GER kernel for LU and the LARF kernel for QR), or alternatively, a left looking update of column i by the columns on its left, before factorizing it (this operation is done by GEMV for the Cholesky factorization). Since we cannot load the entire panel into the GPU's shared memory, the columns to the right (in the case of LU and QR) or the left (in the case of Cholesky) are loaded back and forth from the main memory at every step. Thus, this is the most time-consuming part of the panel factorization. A detailed analysis using the profiler reveals that the GER kernel requires more than 80% and around 40% of the panel time and of the total LU factorization time respectively. Similarly for the QR decomposition, the LARF kernel used inside the panel computation needs 65% and 33% of the panel and the total QR factorization time respectively. Likewise, the GEMV kernel used within the

Cholesky panel computation needs around 91% and 30% of the panel and the total Cholesky factorization time, respectively. This inefficient behavior of these routines is also due to the memory access. To overcomes this bottleneck, we propose to improve the panel' efficiency and to reduce the memory access by using a recursive level of blocking technique as depicted in Figure 3.5. In principle, the panel can be blocked recursively until a single element remains. In practice, 2-3 blocked levels are sufficient to achieve high performance. The above routines must be optimized for each blocked level complicating the implementation. This optimization obtained more than 30% improvement in performance for the LU factorization. The same trend has been observed for both the Cholesky and the QR factorization.

Figure 3.5: Recursive nested blocking

#### Trading Extra Flops for Higher Performance

The challenge discussed here is the following: for batched problems, the use of low-performance kernels must be minimized on the GPU even if they are Level 3 BLAS. For the Cholesky factorization, this concerns the SYRK routine that is used to update the trailing matrix. The performance of SYRK is important to the overall performance since it takes a big part of the run-time. We implemented the batched SYRK routine as a sequence of GEMM routines, each of size M = m, N = K = nb. In order to exclusively use the GEMM kernel, our implementation writes both the

Figure 3.6: Execution trace of the batched LU factorization using either classic getf2 (top) or our recursive getf2 (bottom).

lower and the upper portion of the  $nb \times nb$  diagonal blocks of the trailing matrix resulting in  $nb^3$  extra operations for the diagonal block. However, since nb is small (e.g., nb = 32), these extra operations can be considered free. In practice, the extra operations allow us to use GEMM and thus achieve higher performance than the one that touches the lower/upper portion of the  $nb \times nb$  diagonal blocks. Tests show that our implementation of SYRK is twice as fast as the GEMM kernel for the same matrix size. Thus, our SYRK is very well optimized to reach the performance of GEMM (which is twice as slow because it computes double the flops).

We applied the same technique in the LARFB routine used by the QR decomposition. The QR trailing matrix update uses the LARFB routine to perform  $A_{22} = (I - VT^H V^H) A_{22} = (I - A_{21}T^H A_{21}^H) A_{22}$ . The upper triangle of V is zero with ones on the diagonal. In the classic LARFB,  $A_{21}$  stores V in its lower triangular part and R (part of the upper A) in its upper triangular part. Therefore, the above is computed using TRMM for the upper part of  $A_{21}$  and GEMM for the lower part. The T matrix is upper triangular, and, therefore, the classic LARFB implementation uses TRMM to perform the multiplication with T. If one can guarantee that the lower portion of T is filled with zeroes and the upper portion of V is filled zeros and ones on the diagonal, TRMM can be replaced by GEMM. Thus, we implemented a batched LARFB that uses three GEMM kernels by initializing the lower portion of T with zeros and filling up the upper portion of V with zeroes and ones on the diagonal. Note that this reformulation brings  $3nb^3$  extra operations; but again, the overall time spent in the new LARFB update using the extra computation is around 10% less than the one using the TRMM.

Similar to LARFB and TRMM, we implemented the batched TRSM (that solves AX = B) by inverting the small  $nb \times nb$  block A and using GEMM to get the final results  $X = A^{-1}B$ .

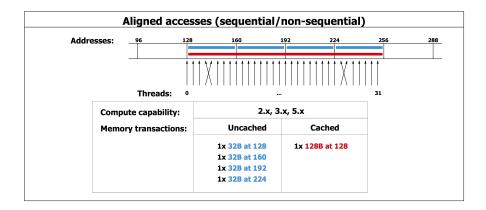

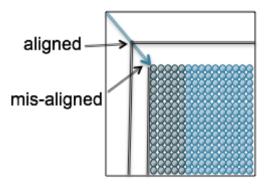

## 3.2.5 Optimization for Hardware Based on CUDA

In this section, we review some features of CUDA-based GPUs which have critical impacts on the performance of linear algebra problems. In CUDA, 32 consecutive threads are organized in one *warp* and are issued with the same instruction of memory access or execution. When a warp executes an instruction that accesses global memory, it coalesces the memory accesses into one transaction if the threads read consecutively from an aligned address. Otherwise, the warp may incur multiple transactions depending on the size of the word accessed by each thread and the distribution of the memory addresses across the threads. For example, if 32 words each of 4-byte are distributed in a striding manner in global memory such that each thread of one warp has to read a word separately, the throughput slows down 32 times compared to coalesced memory access.

The number of transactions affected also varies with other factors, like the compute capability of the device, alignment, and cache. Generally, the higher the compute capability, the lower the memory coalescing requirement. From computing capability 2.0, the cache is introduced to reduce the possibility of non-coalescing.

Figure 3.7 is an example of a warp of threads accessing global memory, with 4-byte for each, from an aligned address. In CUDA, this 128-byte segment is aligned in GPU memory. If the 128-byte segment is cached in L1, there is only one 128-byte

transaction for this warp. If a cache miss happens in L1, the L2 cache will service four 32-byte memory transactions since L2 has a cache line size of 32 bytes. A mis-aligned example is shown in Figure 3.8. If a cache hit, it incurs two memory transactions for this warp on computing capability of 2.0 and above as the data are located in two segments due to the mis-alignment. If a cache miss, again, there will be six 32-byte memory transactions compared to five in the aligned situation. The mis-aligned problem is serious in dense linear algebra. If the starting thread is from a mis-aligned address, the following threads (and thus warps) are all mis-aligned.

Figure 3.7: Aligned memory accesses by a warp of threads

| Addresses: | 96 12             | 28 160        | 192        | 224        | 256   |  |

|------------|-------------------|---------------|------------|------------|-------|--|

|            |                   | ///////X/     |            | ///X////   | '//// |  |

|            | Threads:          | )             |            |            | 31    |  |

| Comp       | ute capability:   | 2.x           | , 3.x, 5.x |            |       |  |

| Memo       | ory transactions: | Uncached      |            | Cached     |       |  |

|            |                   | 1x 32B at 128 | 1x 1       | 28B at 128 |       |  |

|            |                   | 1x 32B at 160 | 1x 1       | 28B at 256 |       |  |

|            |                   | 1x 32B at 192 |            |            |       |  |

|            |                   | 1x 32B at 224 |            |            |       |  |

|            |                   | 1x 32B at 256 |            |            |       |  |

Figure 3.8: Mis-aligned memory accesses by a warp of threads

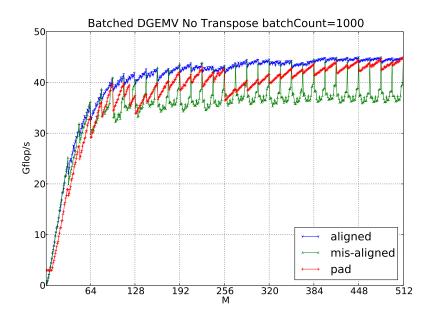

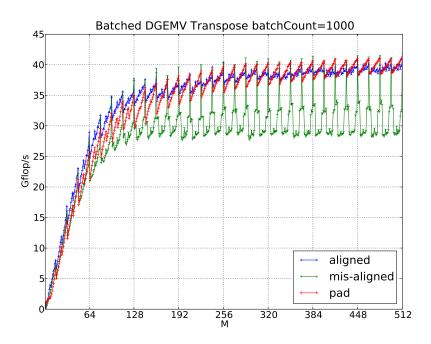

When the compiler allocates new space for the matrix, the starting address is always aligned in GPU memory. In Figure 3.9 and 3.10, the blue curves indicate the performance of GEMV transpose and non-transpose of double precision in the aligned situation, respectively. However, when the algorithm iterates the sub-portion of the matrix, the starting address may not be aligned, as shown in Figure 3.11 by the bi-diagonalization (BRD) algorithm. In Figure 3.9 and 3.10, the green curves depict the performance of the two GEMV in this situation. It fluctuates because when the starting address of the sub-matrix is aligned in memory, the peak performance is reached; otherwise, it drops drastically. The fluctuation is more serious for bigger matrices since most warps are in a mis-aligned way.

To overcome the fluctuation issue, we adopt a padding technique. The starting thread always reads from the recent upper aligned address. It introduces extra data reading. The extra reading is up to 15 elements per row because 16 threads fit in an aligned 128-byte segment as a double element is of 8 byte. Although more data is read, it is coalescing that the 128-byte segment can be fetched by only one transaction. By padding the corresponding elements in the multiplied vector as zeros, extra results are computed but finally discarded in the writing stage. Figure 3.9 and 3.10 show that our padding technique enables the GEMV in the BRD algorithm to run at a speed close to the aligned address' speed.

## 3.3 Auto-tuning

### 3.3.1 Batched Level 3 BLAS GEMM Tuning

The efforts of maximizing GEMM performance generally fall into two directions: writing assembly code and the source level code tuning. The vendor libraries (e.g. Intel MKL, AMD ACML, NVIDIA CUBLAS) supply their own routines on their hardware. To achieve performance, the GEMM routine is implemented in assembly code, like the CUBLAS GEMM on Kepler GPUs. The assembly code usually delivers high performance. A disadvantage is that it is highly architectural specific. The

Figure 3.9: Performance of batched DGEMV (non-transpose) in three situations: aligned, mis-aligned, and pad.

Figure 3.10: Performance of batched DGEMV(transpose) in three situations: aligned, mis-aligned, and pad.

Figure 3.11: The BRD algorithm accesses the sub-matrix step by step.

vendors maintain the performance portability across different generations of their architectures [46].

Another direction is to explore the source level code auto-tuning to achieve optimal performance. Different from assembly code, source code auto-tuning relies on the compilers to allocate registers and schedule instructions. The advantage is source code is architecturally independent and is easy to maintain. Our effort focuses on source code auto-tuning.

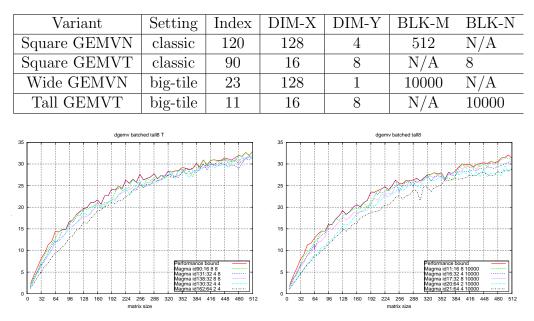

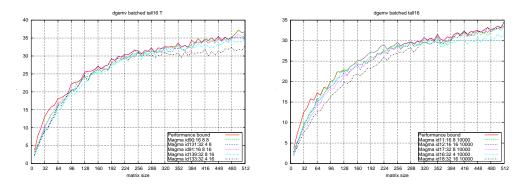

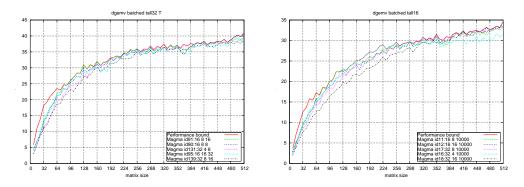

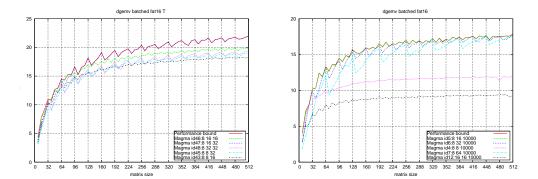

We tune our batched kernels under BEAST (Bench-testing Environment for Automated Software Tuning), which is an auto-tuning framework to explore and optimize the performance of computational kernels on accelerators [7]. The programmer needs to supply a templated kernel and define tuning parameter search space. The parameters of our batched GEMM include the number of threads, the size of shared memory, and the data tile size. Therefore, the search space size is DIM-X \* DIM-Y \* BLK-M \* BLK-N \* BLK-K. See Table 3.2 for the meaning of the parameters.

The search space can be very big, yet it would be efficiently pruned with a set of constraints. The derived constraints include correctness as well as hardware constraints and soft constraints. Hardware constraints stem from the realities of the accelerator architecture, like registers and shared memory size. For example, the maximum shared memory size is 48KB per SMX on Kepler GPUs. Based on these metrics, configurations violating the requirement will be discarded. The constraints may be soft in terms of performance. We require at least 512 threads per GPU Streaming Multiprocessor (SM) to ensure a reasonable occupancy.

After pruning, there are hundreds of valid configurations as shown in Table 3.1, reduced from thousands in search space. GEMM of single real precision (SGEMM) has the most valid configurations while GEMM of double complex precision (ZGEMM) has the least. An element of double complex precision is four times bigger than one in single precision. Many configurations in ZGEMM exceed 48KB shared memory hardware constraints and are eliminated in pruning.

However, tuning is a challenge as programmers face a typical conundrum of multivariable optimization. Not only is the number of parameters large and, therefore, so is the resulting search space, but the parameters are also usually linked by counterintuitive relationships (i.e., a seemingly beneficial setting for one prevents a reasonable setting for another). Decisions are usually made by finding piecewise optimums and trade-offs.

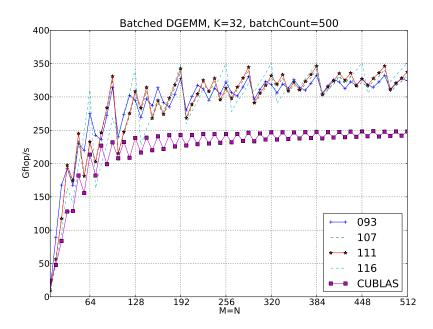

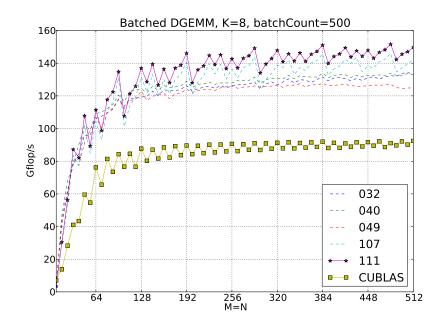

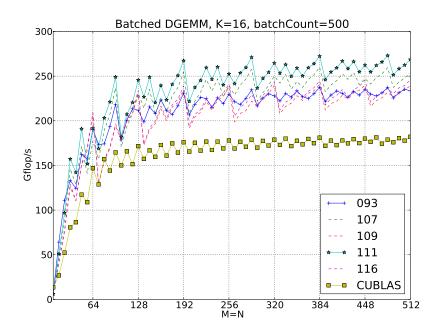

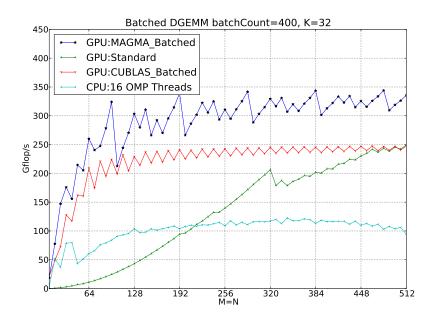

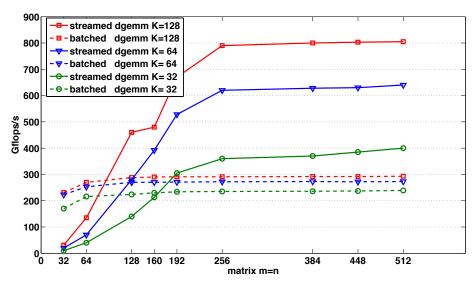

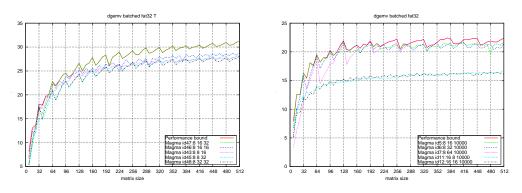

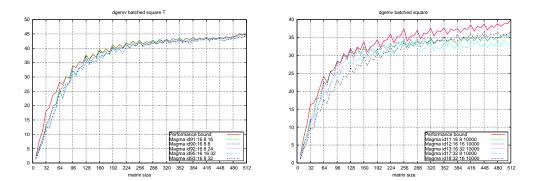

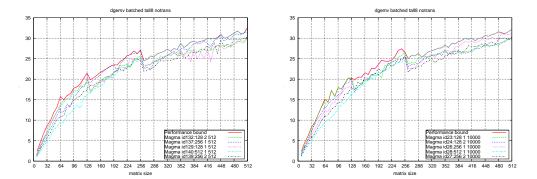

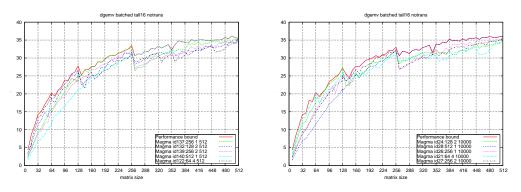

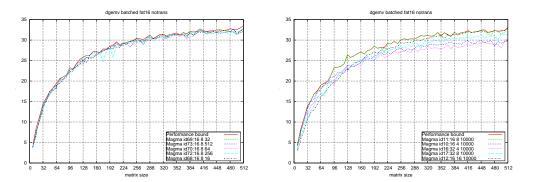

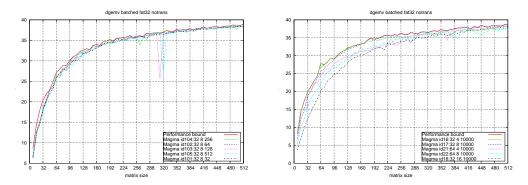

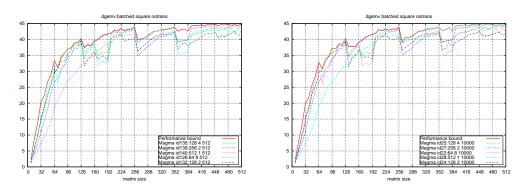

We consider a batched GEMM of double precision (DGEMM) with the rank-32 update (K = 32) as an example. This routine is called by batched LU factorization. Other precisions and shape are tuned and analyzed in the same way. There are 157 valid configurations for batched DGEMM with a non-transpose matrix and a non-transpose matrix. During tuning, each kernel is launched with one configuration. The four most performant kernels are shown in Figure 3.12. The kernel with configuration 111 outperforms others most of the time for matrices of size larger than 128 and is more stable than configuration 116, though the latter is able to reach the peak at certain size. For sizes less than 128, configuration 93 is more stable than configuration 111. Therefore, there is a switchover between configuration 111 and 93 at size 128. All the four configurations outperforms CUBLAS batched GEMM routine a lot. The details of the four configurations in Table 3.2 explain their behaviors. Configuration 93 has a smaller thread block and tile size, and, therefore, performs best for matrices of small size. The performance curve of configuration 116 shakes at every step size of 64 because its tile size is 64 (DIM-M). Configuration 107 and 111 are very similar except

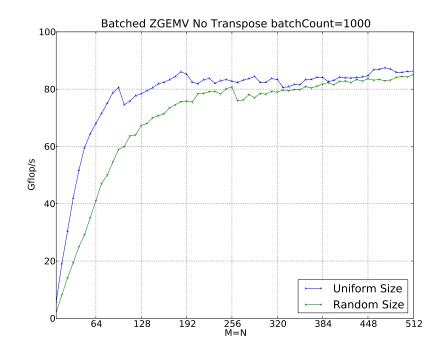

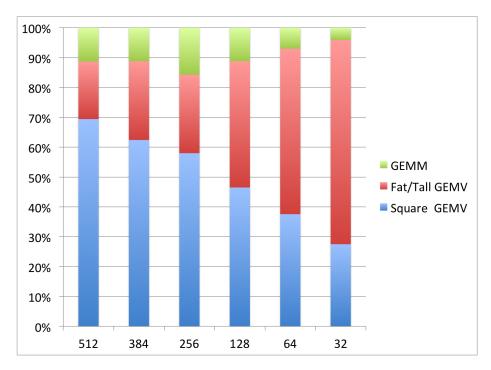

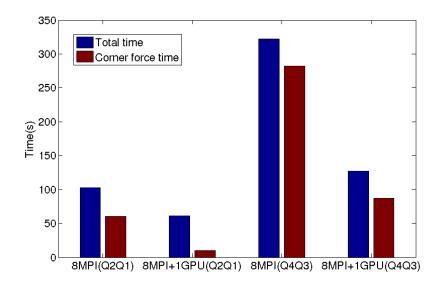

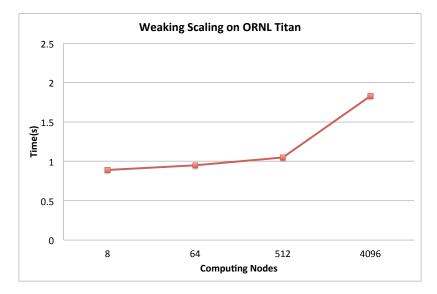

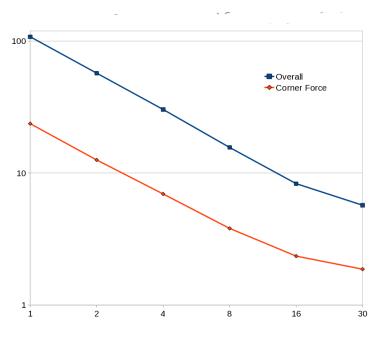

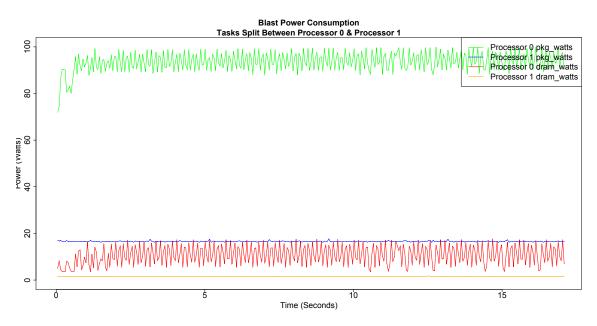

exchanging BLK-M and BLK-N, resulting in very similar performance. Configuration 111 is preferred since it proves to be optimal in other cases like K = 8 and K = 16.