University of Tennessee, Knoxville Trace: Tennessee Research and Creative Exchange

#### **Doctoral Dissertations**

Graduate School

8-2015

# Driving and Protection of High Density High Temperature Power Module for Electric Vehicle Application

Zhiqiang Wang University of Tennessee - Knoxville, zwang38@vols.utk.edu

#### **Recommended** Citation

Wang, Zhiqiang, "Driving and Protection of High Density High Temperature Power Module for Electric Vehicle Application." PhD diss., University of Tennessee, 2015. https://trace.tennessee.edu/utk\_graddiss/3480

This Dissertation is brought to you for free and open access by the Graduate School at Trace: Tennessee Research and Creative Exchange. It has been accepted for inclusion in Doctoral Dissertations by an authorized administrator of Trace: Tennessee Research and Creative Exchange. For more information, please contact trace@utk.edu.

To the Graduate Council:

I am submitting herewith a dissertation written by Zhiqiang Wang entitled "Driving and Protection of High Density High Temperature Power Module for Electric Vehicle Application." I have examined the final electronic copy of this dissertation for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Doctor of Philosophy, with a major in Electrical Engineering.

Leon M. Tolbert, Major Professor

We have read this dissertation and recommend its acceptance:

Fred Wang, Zhenxian Liang, Benjamin J. Blalock, Anming Hu

Accepted for the Council: <u>Dixie L. Thompson</u>

Vice Provost and Dean of the Graduate School

(Original signatures are on file with official student records.)

# **Driving and Protection of High Density**

# **High Temperature Power Module for**

# **Electric Vehicle Application**

A Dissertation Presented for the

**Doctor of Philosophy**

Degree

The University of Tennessee, Knoxville

**Zhiqiang Wang**

August 2015

## Acknowledgement

First of all, I would like to take this opportunity to express my deepest appreciation to my advisor, Dr. Leon M. Tolbert, for his continuous support and guidance in my Ph.D. studies. In the past four years, he always shows me how to do a good research with his profound knowledge, great wisdom, and patience. He also teaches me by personal example how to work with other people, and his excellent personality will keep influencing me in my life.

I would like to thank Dr. Fred Wang, for his valuable suggestions and comments during the weekly research meeting. With profound understanding and broad knowledge of power electronics, Dr. Wang leads me in conducting solid research work and exploring new research ideas. His characters of affability and humor teach me how to work with industry people.

I am also very grateful to my previous Ph.D. advisor at Virginia Tech, Dr. Fred C. Lee, who introduced me to the Center for Power Electronics Systems. He always asks the right questions that push me to think deeper. His unique vision, rigorous style, and indefatigable patience have impressed me in all of my research work.

I would like to thank Dr. Zhenxian Liang, Dr. Benjamin J. Blalock, and Dr. Daniel Costinett for their precious suggestions and comments during project meetings. Without their help, I cannot move forward smoothly in my research and finish this dissertation.

I would like to thank Dr. Anming Hu for serving as one of my committee members and giving me good suggestions on my dissertation.

I would like to thank Mr. Madhu Sudhan Chinthavali, who introduced me to the Power Electronics and Electric Machinery Group of Oak Ridge National Laboratory as a post-master's research associate in my last year of Ph.D. study. He discusses technical details with me frequently, shares good ideas with me, and encourages me to learn new knowledge from cutting-edge research projects.

I would like to thank all my colleagues in the power electronics lab in the University of Tennessee, Knoxville. They are Dr. Shengnan Li, Dr. Dong Jiang, Dr. Lijun Hang, Dr. Jingxin Wang, Dr.

Wenjie Chen, Dr. Xiaoling Yu, Dr. Wanjun Lei, Dr. Faete Filho, Dr. Mithat Can Kisacikoglu, Dr. Lakshmi Reddy Gopi Reddy, Dr. Zhuxian Xu, Dr. Fan Xu, Dr. Ben Guo, Dr. Zheyu Zhang, Dr. Jing Xue, Mr. Weimin Zhang, Mr. Bradford Trento, Dr. Bailu Xiao, Ms. Jing Wang, Ms. Yutian Cui, Mr. Yalong Li, Mr. Wenchao Cao, Mr. Yiwei Ma, Ms. Xiaojie Shi, Ms. Liu Yang, Ms. Yang Xue, Mr. Bo Liu, Mr. Edward Jones, Mr. Siyao Jiang, Mr. Yiqi Liu, Dr. Xuan Zhang, Dr. Xiaonan Lu, Dr. Haifeng Lu, Dr. Sheng Zheng, Mr. Fei Yang, Mr. Tong Wu, Mr. Shuoting Zhang, Mr. Chongwen Zhao, Ms. Ling Jiang, Ms. Lu Wang and Mr. Ren Ren.

I also want to thank all the staff members of the power electronics group at the University of Tennessee, Mr. Robert B. Martin, Mr. William Rhodes, Ms. Judy Evans, Ms. Dana Bryson, Mr. Erin Wills, Mr. Adam Hardebeck, Ms. Chien-fei Chen, and Mr. Chris Anderson, for making this lab a wonderful and safe place for research.

Finally, but most importantly, I would like to express my gratitude to my dearest parents and my wife Xiaojie Shi for their unconditional love. Without your support and encouragement, this work is definitely impossible. Special thanks to my wife Xiaojie, she also worked closely with me in the lab as a colleague and friend. You are the most beautiful girl in my heart, just like the fall colors in the Great Smoky Mountains.

This dissertation was partially funded by the II-VI Foundation and Oak Ridge National Laboratory under the U.S. Department of Energy's Vehicle Technologies Program. This dissertation made use of Engineering Research Center Shared Facilities supported by the Engineering Research Center Program of the National Science Foundation and the Department of Energy under NSF Award Number EEC-1041877 and the CURENT Industry Partnership Program.

### Abstract

There has been an increasing trend for the commercialization of electric vehicles (EVs) to reduce greenhouse gas emissions and dependence on petroleum. However, a key technical barrier to their wide application is the development of high power density electric drive systems due to limited space within EVs. High temperature environment inherent in EVs further introduces a new level of complexity. Under high power density and high temperature operation, system reliability and safety also become important.

This dissertation deals with the development of advanced driving and protection technologies for high temperature high density power module capable of operating under the harsh environment of electric vehicles, while ensuring system reliability and safety under short circuit conditions. Several related research topics will be discussed in this dissertation.

First, an active gate driver (AGD) for IGBT modules is proposed to improve their overall switching performance. The proposed one has the capability of reducing the switching loss, delay time, and Miller plateau duration during turn-on and turn-off transient without sacrificing current and voltage stress.

Second, a board-level integrated silicon carbide (SiC) MOSFET power module is developed for high temperature and high power density application. Specifically, a silicon-on-insulator (SOI) based gate driver board is designed and fabricated through chip-on-board (COB) technique. Also, a 1200 V / 100 A SiC MOSFET phase-leg power module is developed utilizing high temperature packaging technologies.

Third, a comprehensive short circuit ruggedness evaluation and numerical investigation of up-to-date commercial silicon carbide (SiC) MOSFETs is presented. The short circuit capability of three types of commercial 1200 V SiC MOSFETs is tested under various conditions. The experimental short circuit behaviors are compared and analyzed through numerical thermal dynamic simulation.

Finally, according to the short circuit ruggedness evaluation results, three short circuit protection methods are proposed to improve the reliability and overall cost of the SiC MOSFET based converter. A comparison is made in terms of fault response time, temperature dependent characteristics, and applications to help designers select a proper protection method.

## **Table of Contents**

| 1 | Int | roduction1                                                   | Ĺ        |

|---|-----|--------------------------------------------------------------|----------|

|   | 1.1 | Background and Motivation                                    | l        |

|   | 1.2 | Research Objectives and Approaches                           | 5        |

|   | 1.3 | Dissertation Organization                                    | 5        |

| 2 | Lit | erature Review                                               | }        |

|   | 2.1 | IGBT Switching Loss Reduction under Hard Switching Condition | )        |

|   | 2.2 | High Temperature Integrated Power Module                     | 3        |

|   | 2.3 | Short Circuit Capability of SiC MOSFETs                      | 3        |

|   | 2.4 | Short Circuit Protection of SiC MOSFETs                      | )        |

|   | 2.5 | Summary                                                      | 3        |

| 3 | Act | ive Gate Drive for IGBT Switching Loss Reduction24           | ŀ        |

|   | 3.1 | Analysis of IGBT Switching Characteristics                   | 1        |

|   | 3.2 | Proposed Active Gate Drive                                   | 5        |

|   |     | 3.2.1 Turn-on Control                                        | 5        |

|   |     | 3.2.2 Turn-off Control                                       | )        |

|   | 3.3 | Experimental Verification                                    | Į        |

|   |     | 3.3.1 Test and Measurement Setup                             | 2        |

|   |     | 3.3.2 Turn-on Performance Comparison                         | 1        |

|   |     | 3.3.3 Turn-off Performance Comparison                        | 7        |

|   | 3.4 | Conclusion                                                   | )        |

| 4 | Hig | h Temperature Integrated Power Module 42                     | 2        |

|   | 4.1 | Silicon-on-Insulator Gate Drive                              | <u>)</u> |

|   | 4.2 | High Temperature Power Module                                | ł        |

|   |     | 4.2.1 Phase-Leg Power Module Design                          | 1        |

|   |     | 4.2.2   | Static Characterization                          | 45 |

|---|-----|---------|--------------------------------------------------|----|

|   |     | 4.2.3   | Switching Characterization                       | 47 |

|   |     | 4.2.4   | Fault Characterization                           | 51 |

|   | 4.3 | Power   | Density Limitation                               | 53 |

|   | 4.4 | High '  | Femperature Continuous Operation                 | 57 |

|   |     | 4.4.1   | Thermal Simulation                               | 57 |

|   |     | 4.4.2   | Junction Temperature Measurement                 | 58 |

|   |     | 4.4.3   | Buck Converter Operation                         | 62 |

|   | 4.5 | Concl   | usion                                            | 64 |

| 5 | Sho | ort Cir | cuit Capability Evaluation of SiC MOSFETs        | 66 |

|   | 5.1 | Evalu   | ation Methodology and Hardware Test Setup        | 66 |

|   | 5.2 | Short   | Circuit Capability Evaluation                    | 69 |

|   |     | 5.2.1   | CREE 1G SiC MOSFETs                              | 69 |

|   |     | 5.2.2   | CREE 2G SiC MOSFETs                              | 72 |

|   |     | 5.2.3   | ROHM SiC MOSFETs                                 | 73 |

|   | 5.3 | Comp    | arison and Analysis                              | 74 |

|   |     | 5.3.1   | Delayed Failure Mode                             | 75 |

|   |     | 5.3.2   | Short Circuit Withstand Time and Critical Energy | 76 |

|   |     | 5.3.3   | Electro-Thermal Model                            | 78 |

|   |     | 5.3.4   | Leakage Current Model                            | 81 |

|   |     | 5.3.5   | Simulation Results                               | 83 |

|   |     | 5.3.6   | Repetitive Short Circuit Robustness              | 88 |

|   | 5.4 | Concl   | usion                                            | 90 |

| 6 | Sho | ort Cir | cuit Protection of SiC MOSFETs                   | 92 |

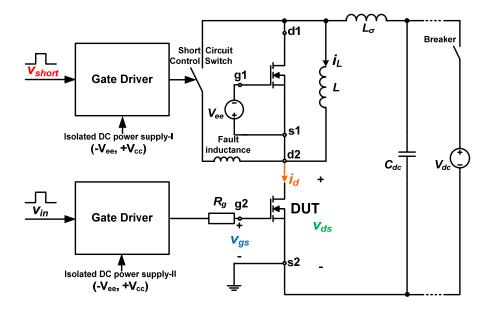

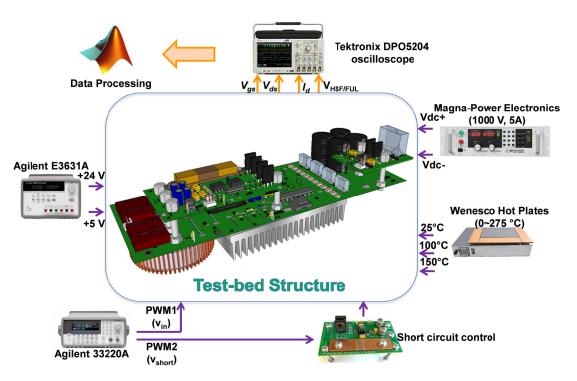

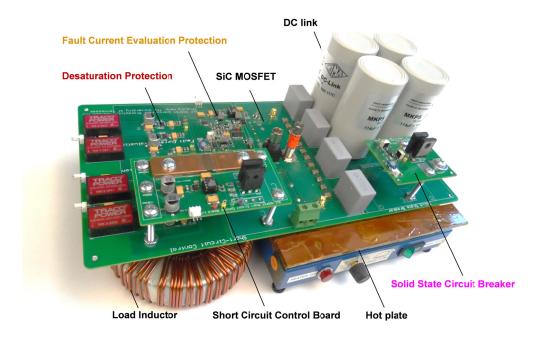

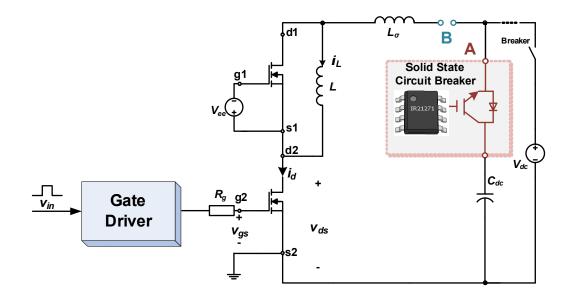

|   | 6.1 | Metho   | bology and Test Setup                            | 93 |

|      | 6.2  | Solid   | State Circuit Breaker             | 96  |

|------|------|---------|-----------------------------------|-----|

|      |      | 6.2.1   | Design Guideline                  | 97  |

|      |      | 6.2.2   | Impact of <i>dv/dt</i>            |     |

|      |      | 6.2.3   | Impact of Decoupling Capacitors   |     |

|      | 6.3  | Desati  | uration Technique                 |     |

|      |      | 6.3.1   | Blanking Time Delay               |     |

|      |      | 6.3.2   | False Triggering Suppression      |     |

|      |      | 6.3.3   | Performance Evaluation            |     |

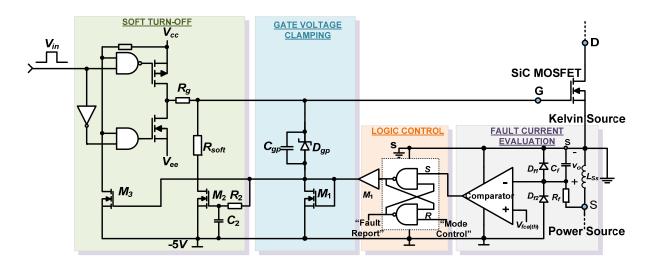

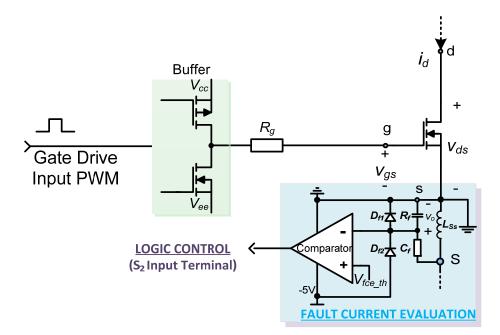

|      | 6.4  | Fault   | Current Evaluation Scheme         | 113 |

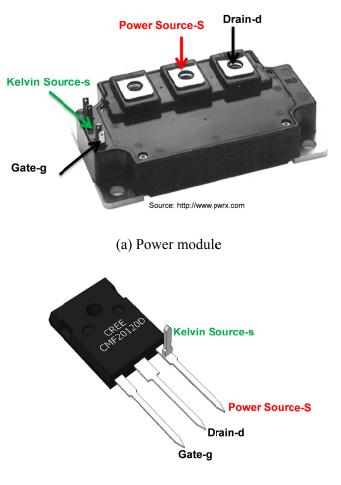

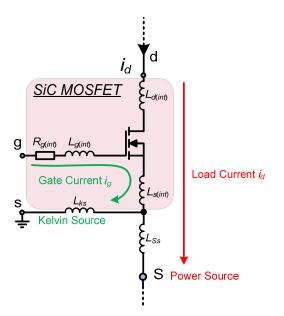

|      |      | 6.4.1   | Kelvin Source Connection          | 113 |

|      |      | 6.4.2   | Functionality Implementation      |     |

|      |      | 6.4.3   | Performance Evaluation            |     |

|      | 6.5  | Discu   | ssion                             |     |

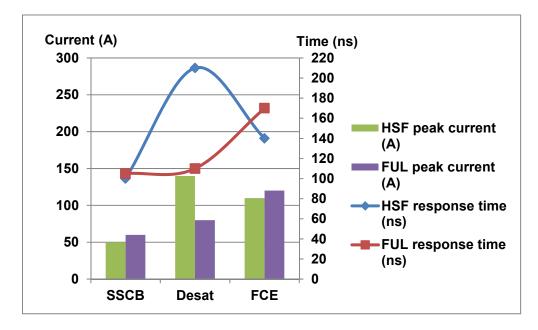

|      |      | 6.5.1   | Fault Response Time               |     |

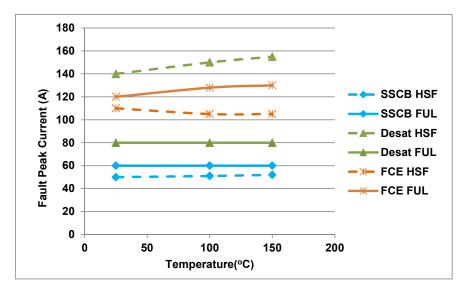

|      |      | 6.5.2   | Temperature Dependent Performance |     |

|      |      | 6.5.3   | Applications                      |     |

|      |      | 6.5.4   | Other Factors                     |     |

|      | 6.6  | Concl   | usion                             | 131 |

| 7    | Cor  | nclusio | on and Future Work                | 133 |

|      | 7.1  | Concl   | usion                             |     |

|      | 7.2  | Future  | e Work                            | 134 |

| Ref  | eren | ce      |                                   | 137 |

| Vita | a    | •••••   |                                   | 151 |

7

## List of Tables

| Table 1-1. Mechatronic maximum temperature ranges    4                                        |

|-----------------------------------------------------------------------------------------------|

| Table 2-1. Comparison of high temperature integrated gate drivers    17                       |

| Table 5-1. SiC MOSFETs under test [93]-[96]    66                                             |

| Table 5-2. Summary of typical data of failed devices    76                                    |

| Table 6-1. Comparison of IGBTs used for the SSCB                                              |

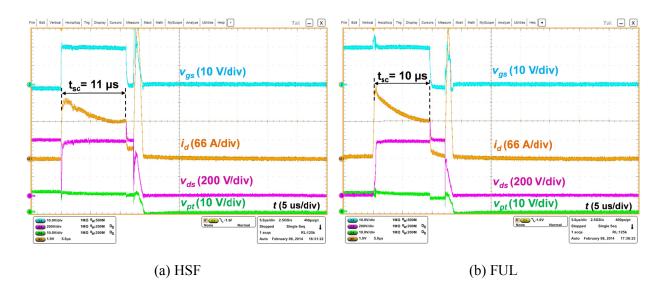

| Table 6-2. Comparison of fault response time for HSF and FUL using desaturation technique 111 |

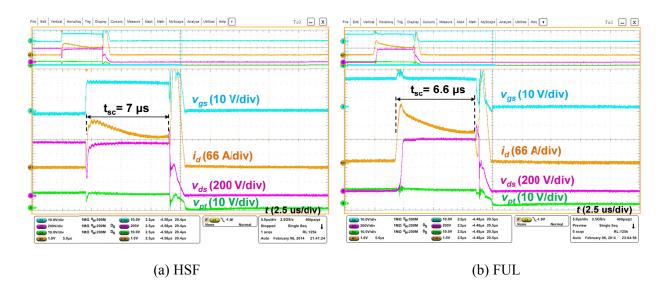

| Table 6-3. Comparison of fault response time for HSF and FUL using proposed technique 122     |

| Table 6-4. Comparison of the three protection methods                                         |

## **List of Figures**

| Figure 1-1. U.S. oil consumption in 2010.                                               | 1  |

|-----------------------------------------------------------------------------------------|----|

| Figure 1-2. Technical targets for the electric traction drive systems [4].              | 2  |

| Figure 1-3. System-level benefits by developing high density and high temperature power |    |

| module                                                                                  | 3  |

| Figure 1-4. Ambient temperatures for automotive electronics applications                | 4  |

| Figure 2-1. Conflicting requirements of conventional gate driver.                       | 9  |

| Figure 2-2. Multistage gate drive concept [13] [14].                                    | 10 |

| Figure 2-3. Feedforward active gate driver [18]                                         | 11 |

| Figure 2-4. Digital control based active gate driver [20]-[22]                          | 12 |

| Figure 2-5. 1200 V / 100 A SiC MOSFET module [40]                                       | 13 |

| Figure 2-6. 1200 V / 120 A SiC MOSFET module [41].                                      | 14 |

| Figure 2-7. 1200 V / 120 A SiC MOSFET module [42].                                      | 14 |

| Figure 2-8. High temperature SiC power modules.                                         | 15 |

| Figure 2-9. Integrated high temperature SiC MOSFET power module [51]                    | 16 |

| Figure 2-10. Commercial high temperature SOI gate driver [55].                          | 16 |

| Figure 2-11. IGBT short-circuit failure modes described in previous literature          | 19 |

| Figure 2-12. Direct current sensing based IGBT protection methods.                      | 22 |

| Figure 2-13. Indirect current sensing based IGBT protection methods                     | 23 |

| Figure 3-1. Switching waveforms of an IGBT under clamped inductive load                 | 24 |

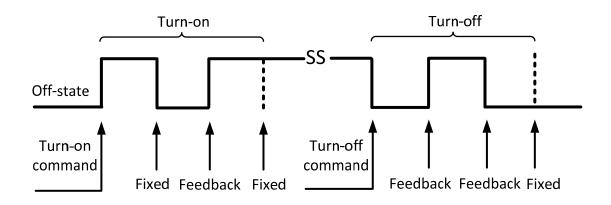

| Figure 3-2. Turn-on control diagram.                                                    | 25 |

| Figure 3-3. Circuit implementation of the turn-on control.                              | 27 |

| Figure 3-4. Turn-off control diagram                                                    | 29 |

| Figure 3-5. Circuit implementation of the turn-off control                                      | . 30 |

|-------------------------------------------------------------------------------------------------|------|

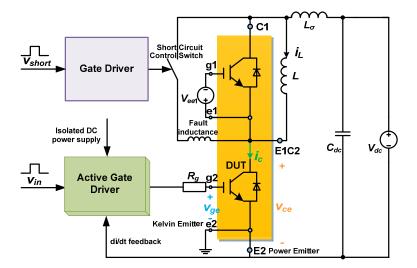

| Figure 3-6. Experimental test circuit.                                                          | . 32 |

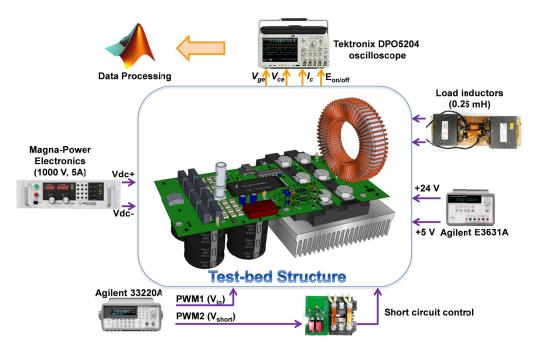

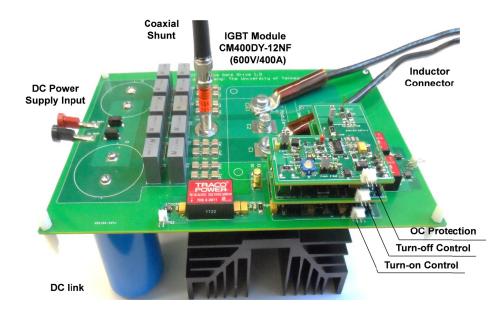

| Figure 3-7. Experimental test and measurement setup.                                            | . 33 |

| Figure 3-8. Hardware testbed for performance evaluation of the AGD.                             | . 33 |

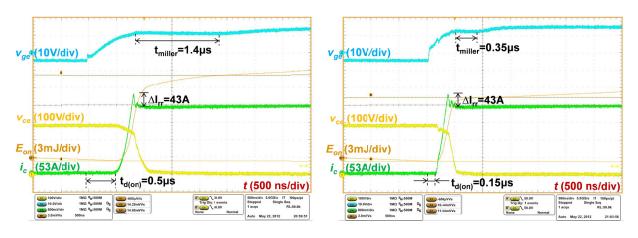

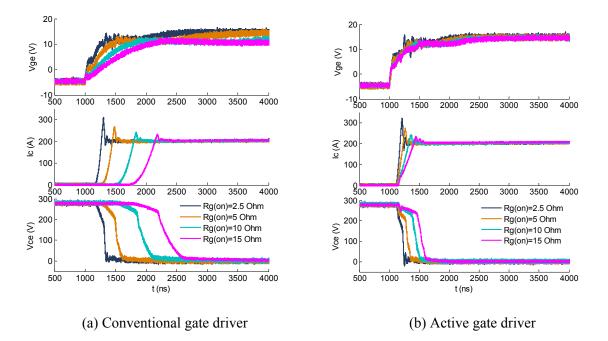

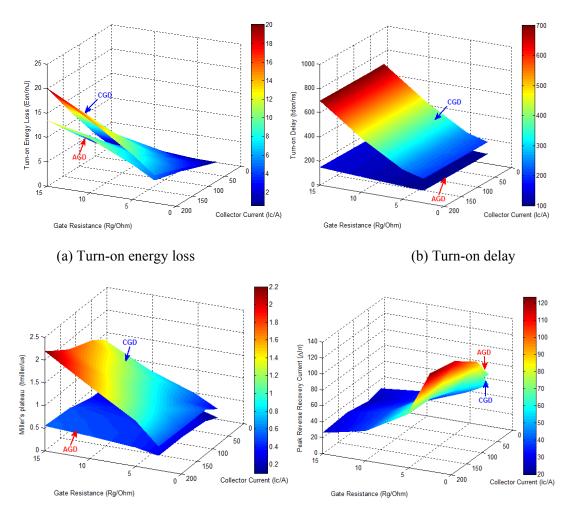

| Figure 3-9. Comparison of turn-on waveforms with different gate drivers                         | . 34 |

| Figure 3-10. Comparison of turn-on waveforms with different gate resistors using CGD and        |      |

| AGD.                                                                                            | . 35 |

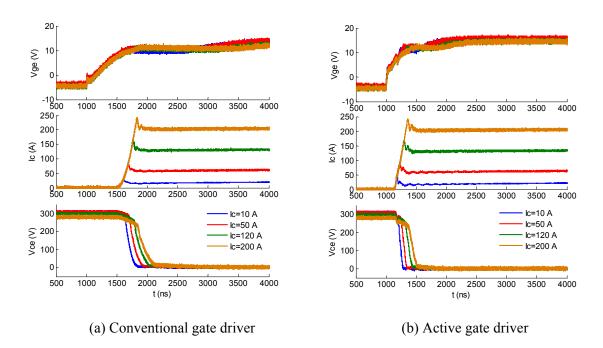

| Figure 3-11. Comparison of turn-on waveforms with different current levels using CGD and        |      |

| AGD.                                                                                            | . 35 |

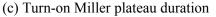

| Figure 3-12. Comparison of the two gate drivers under different current levels and gate resisto | ors. |

|                                                                                                 | . 36 |

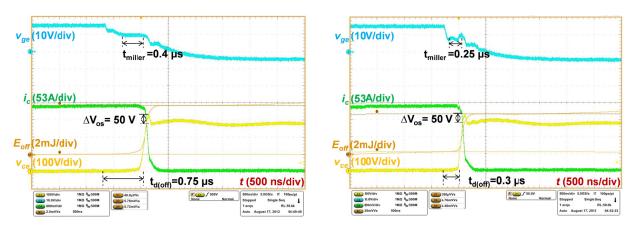

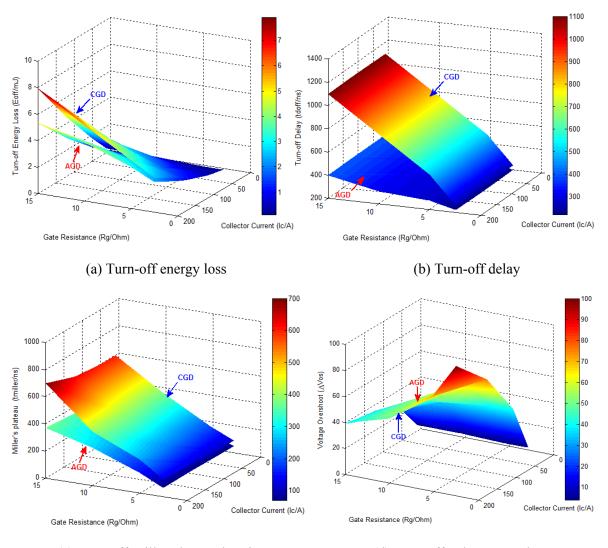

| Figure 3-13. Comparison of turn-off waveforms for the two methods.                              | . 37 |

| Figure 3-14. Comparison of turn-off waveforms with different gate resistors using CGD and       |      |

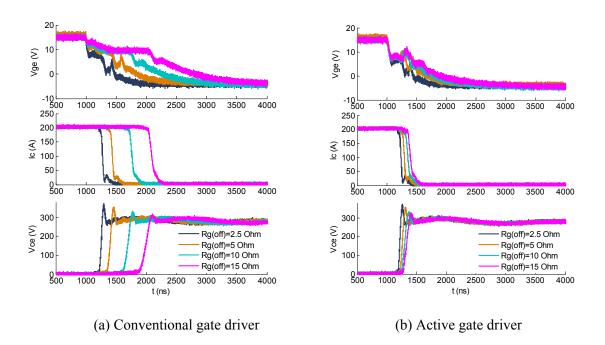

| AGD.                                                                                            | . 38 |

| Figure 3-15. Comparison of turn-off waveforms with different current levels using CGD and       |      |

| AGD.                                                                                            | . 39 |

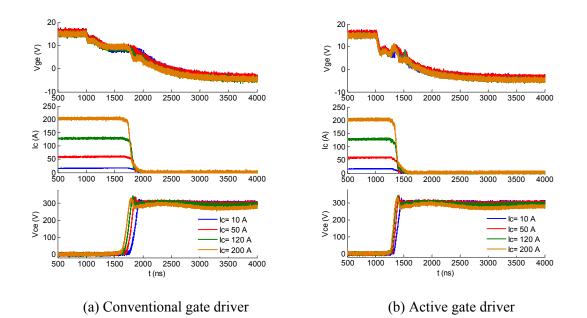

| Figure 3-16. Comparison of the two gate drivers under different current levels and gate         |      |

| resistances.                                                                                    | . 40 |

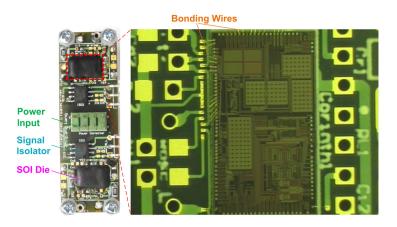

| Figure 4-1. SOI die placement on PCB with COB approach.                                         | . 43 |

| Figure 4-2. 1200 V / 100 A SiC MOSFET based high temperature phase-leg power module             | . 44 |

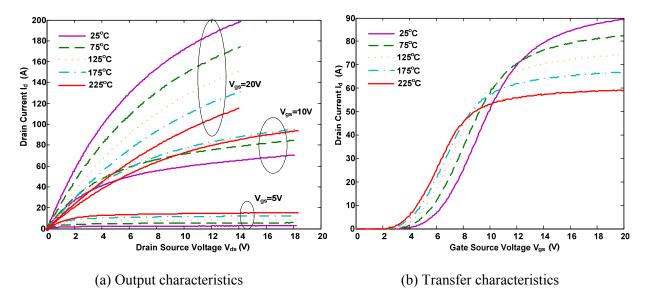

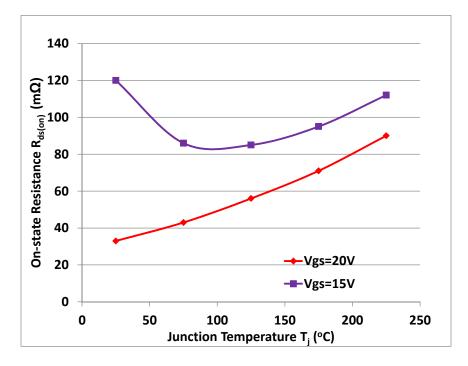

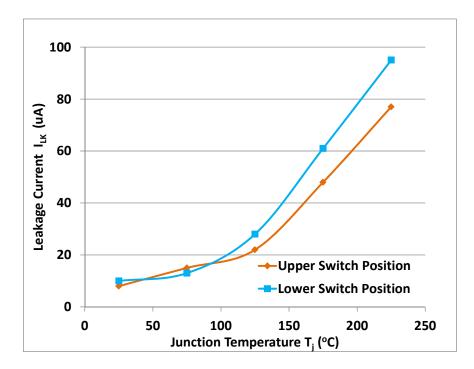

| Figure 4-3. Static characteristics of the SiC MOSFET (one die) at various temperatures          | . 46 |

| Figure 4-4. Temperature dependent on state resistance                                           | . 46 |

| Figure 4-5. Temperature dependent leakage current.                                              | . 47 |

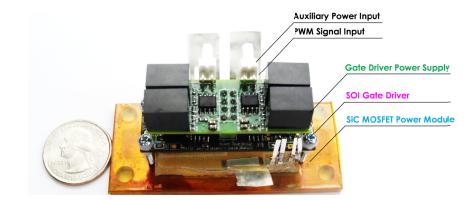

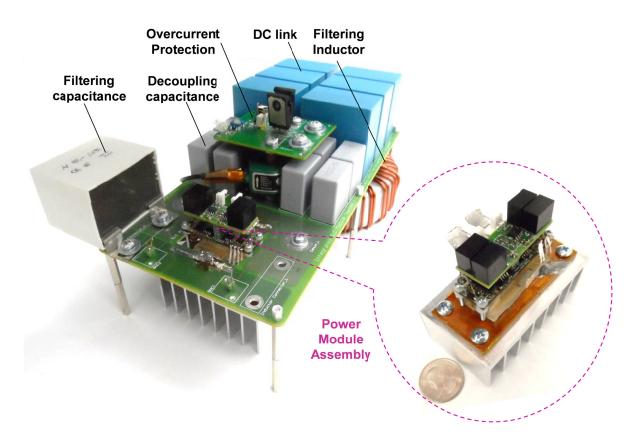

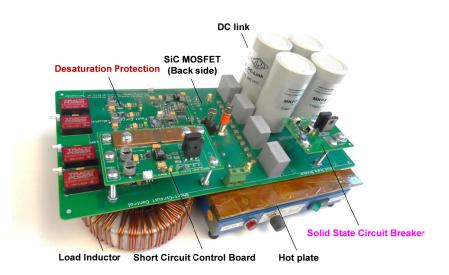

| Figure 4-6. Board-level integrated power module                                                 | 48   |

|-------------------------------------------------------------------------------------------------|------|

| Figure 4-7. Circuit diagram of the multifunction power stage.                                   | 48   |

| Figure 4-8. Hardware picture of the multifunction power stage                                   | 49   |

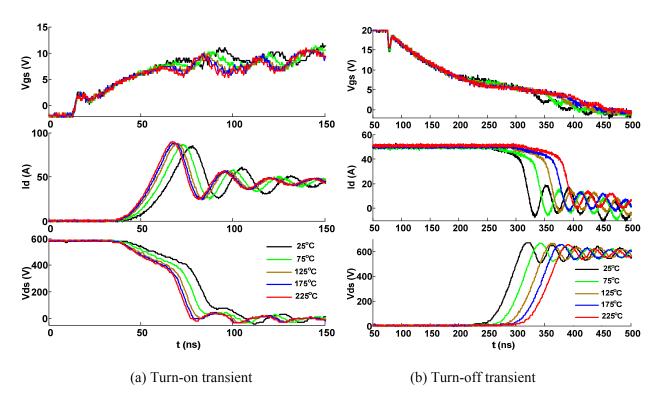

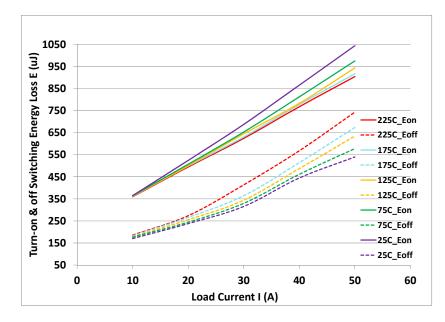

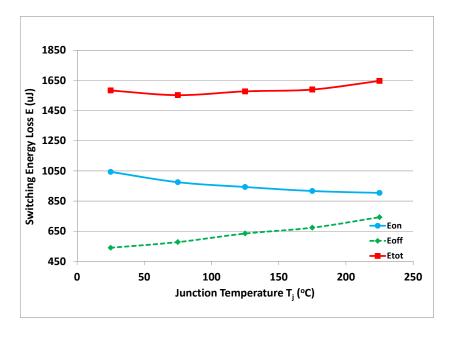

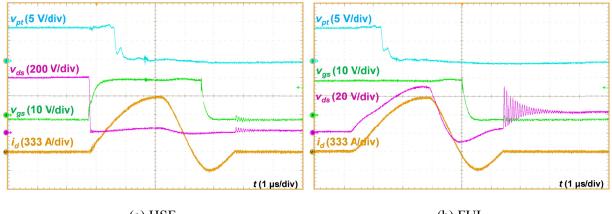

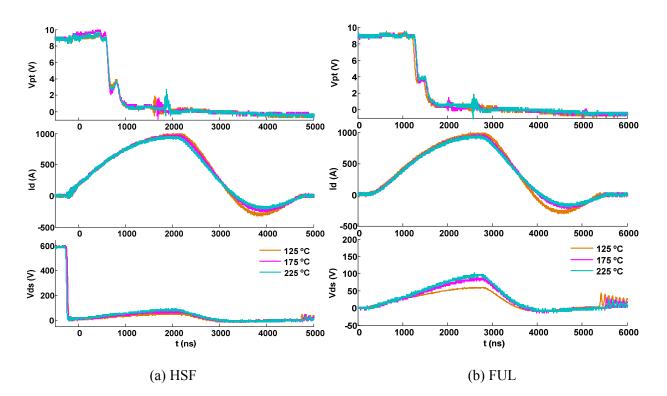

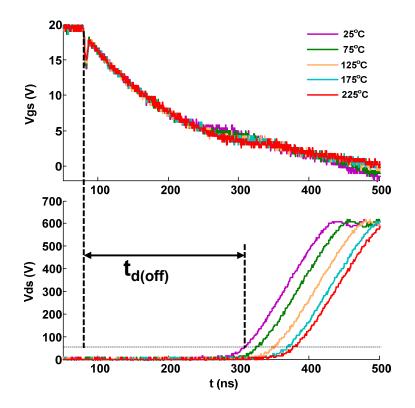

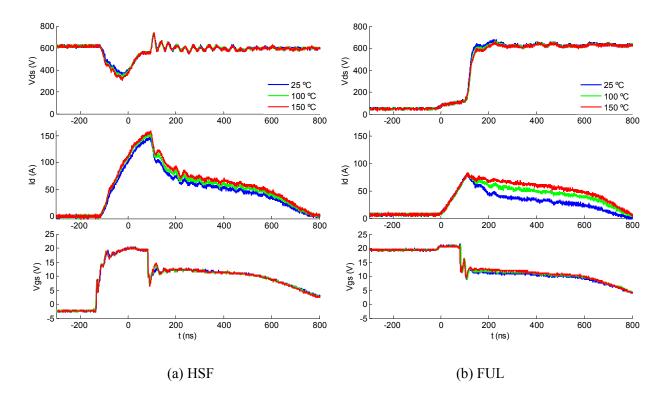

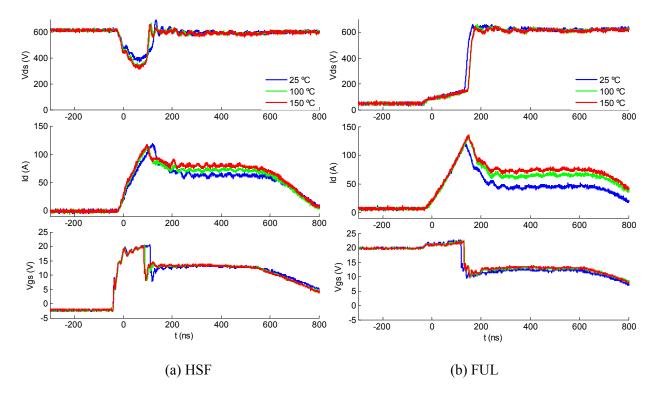

| Figure 4-9. Temperature dependent switching waveforms                                           | 50   |

| Figure 4-10. Temperature dependent switching energy loss.                                       | 51   |

| Figure 4-11. Short circuit protection waveforms at room temperature (25 °C)                     | 52   |

| Figure 4-12. Temperature dependent short circuit protection waveforms                           | 53   |

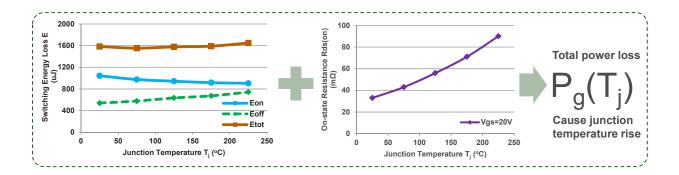

| Figure 4-13. Temperature dependent power loss                                                   | 54   |

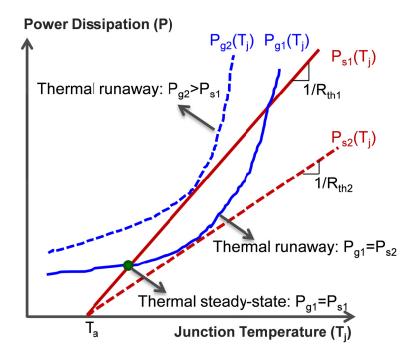

| Figure 4-14. Thermal runaway issue caused by increased power and/or thermal resistance          | 55   |

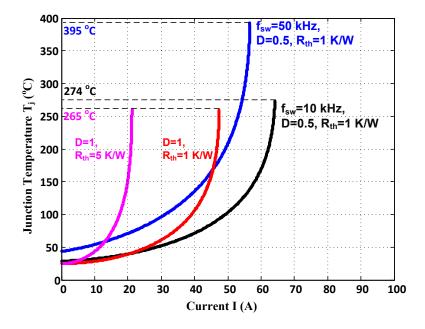

| Figure 4-15. Thermal runaway temperature under different operating conditions                   | 56   |

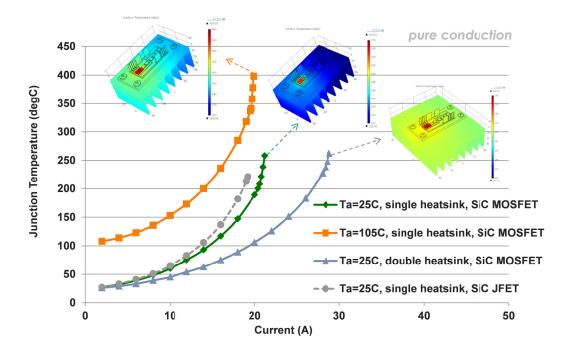

| Figure 4-16. Thermal simulation verification of thermal runaway temperatures                    | 57   |

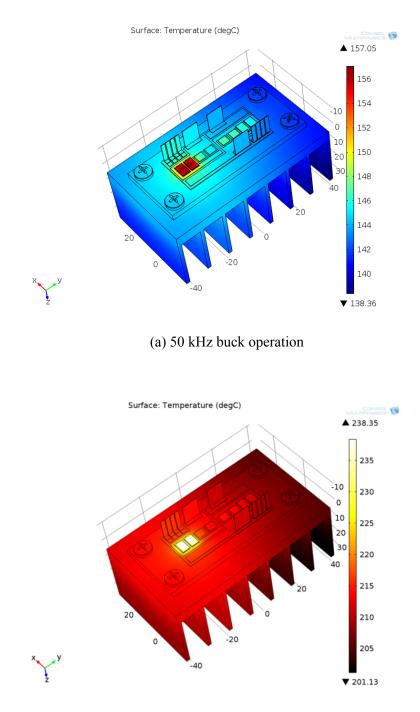

| Figure 4-17. Temperature distribution by thermal simulation                                     | 59   |

| Figure 4-18. Calibration curves under different load current levels and junction temperatures.  | . 61 |

| Figure 4-19. Turn-off waveforms under different junction temperatures                           | 61   |

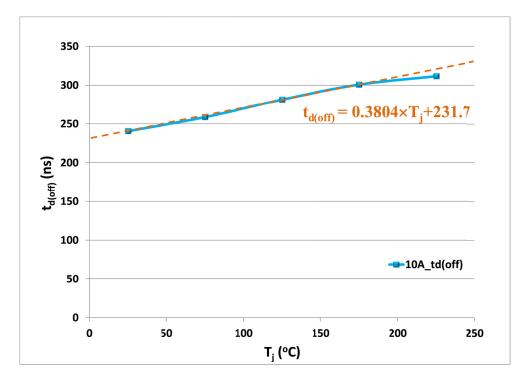

| Figure 4-20. Calibration curve with 10 A load current                                           | 62   |

| Figure 4-21. Hardware test setup for buck converter operation.                                  | 63   |

| Figure 4-22. Buck operation at a switching frequency of 50 kHz.                                 | 64   |

| Figure 4-23. Buck operation at a switching frequency of 100 kHz.                                | 64   |

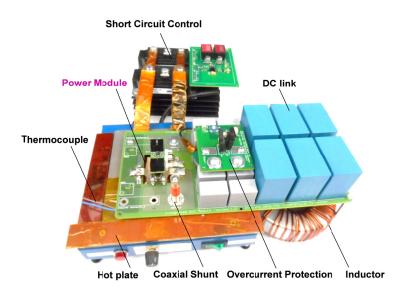

| Figure 5-1. Test circuit configuration for short circuit capability and protection evaluation   | 67   |

| Figure 5-2. Experimental test and measurement setup.                                            | 68   |

| Figure 5-3. Hardware testbed for short circuit capability and protection evaluation             | 68   |

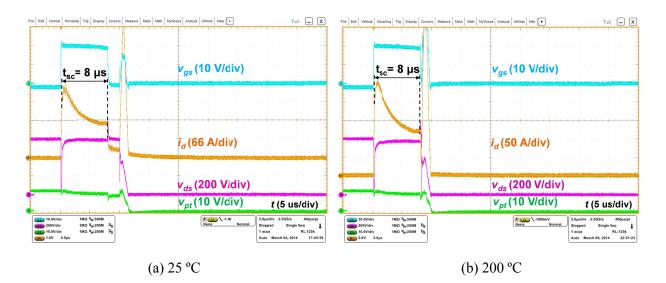

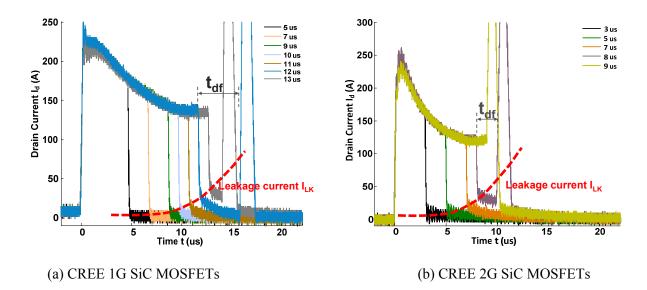

| Figure 5-4. Short circuit capability of CREE 1G SiC MOSFET with $V_{dc} = 600$ V and $T_c = 25$ | °C.  |

|                                                                                                 | 69   |

| Figure 5-5. Short circuit capability of CREE 1G SiC MOSFETs with $V_{dc} = 600$ V and $T_c = 200$    |

|------------------------------------------------------------------------------------------------------|

| °C71                                                                                                 |

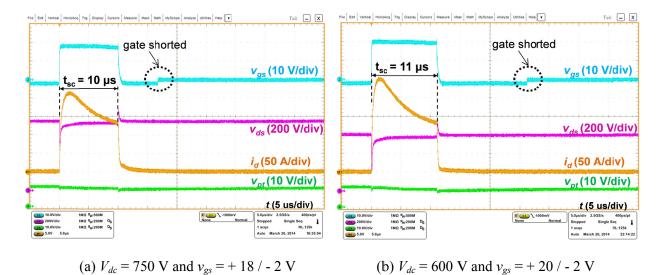

| Figure 5-6. Short circuit capability of CREE 1G SiC MOSFETs with $V_{dc} = 750$ V and $T_c = 200$    |

| °C                                                                                                   |

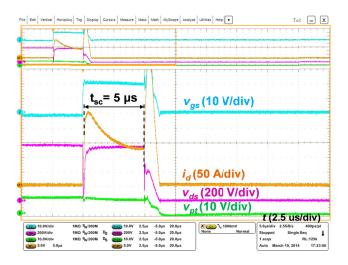

| Figure 5-7. Short circuit capability of CREE 2G SiC MOSFETs under different case                     |

| temperatures when $V_{dc} = 600 \text{ V}$                                                           |

| Figure 5-8. Short circuit capability of CREE 2G SiC MOSFET with $V_{dc} = 750$ V and $T_c = 200$ °C. |

|                                                                                                      |

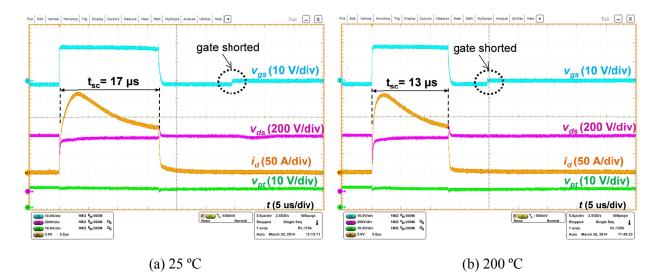

| Figure 5-9. Short circuit capability of ROHM SiC MOSFETs under different case temperatures           |

| when $V_{dc} = 600 \text{ V}$                                                                        |

| Figure 5-10. Short circuit capability of ROHM SiC MOSFETs with $T_c = 200$ °C                        |

| Figure 5-11. Evolution of delayed failure mode with different short circuit durations                |

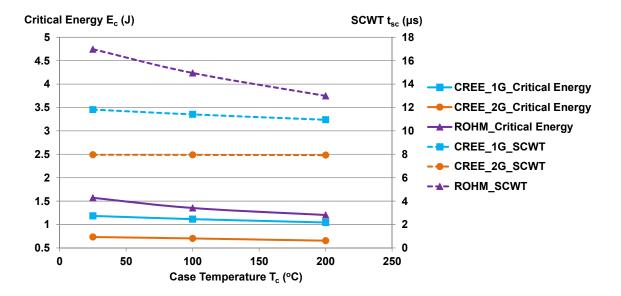

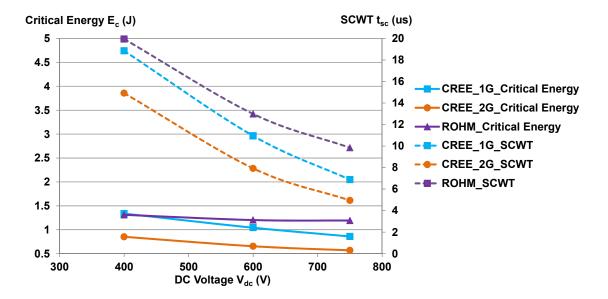

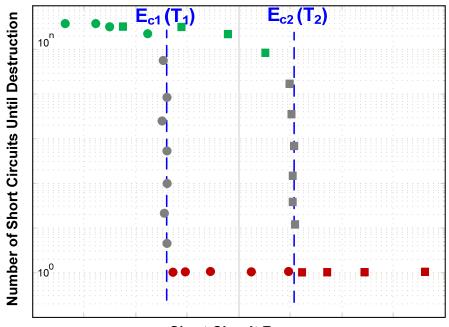

| Figure 5-12. Comparison of temperature dependent short circuit capability                            |

| Figure 5-13. Comparison of DC bus voltage dependent short circuit capability77                       |

| Figure 5-14. Electro-thermal model of SiC MOSFET with TO-247 package                                 |

| Figure 5-15. Comparison of saturation current density and junction temperature                       |

| Figure 5-16. Comparison of temperature distribution along vertical path                              |

| Figure 5-17. Comparison of total leakage current with different generation lifetimes                 |

| Figure 5-18. Calculated leakage current components of the three SiC MOSFETs                          |

| Figure 5-19. Numerical simulation results with different combinations of DC bus voltage and          |

| case temperature                                                                                     |

| Figure 5-20. Repetitive robustness of IGBTs and MOSFETs                                              |

| Figure 5-21. Numerical simulation results for repetitive short circuit analysis                      |

| Figure 6-1. Requirements for active protection schemes                                        | 92   |

|-----------------------------------------------------------------------------------------------|------|

| Figure 6-2. Overcurrent protection testing circuit.                                           | 94   |

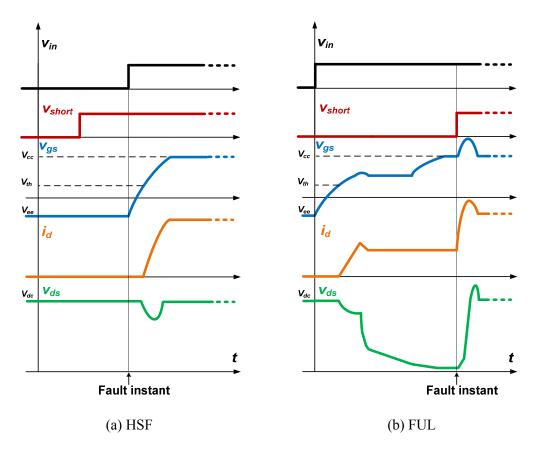

| Figure 6-3. Drive signal and ideal short-circuit waveforms.                                   | 94   |

| Figure 6-4. Experimental test and measurement setup.                                          | 95   |

| Figure 6-5. Hardware testbed for performance evaluation of the overcurrent protection scher   | mes. |

|                                                                                               | 96   |

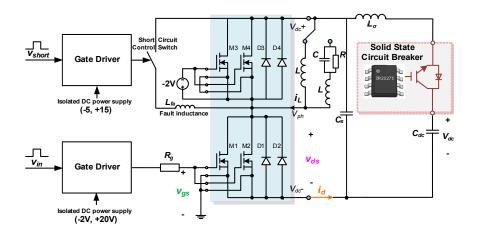

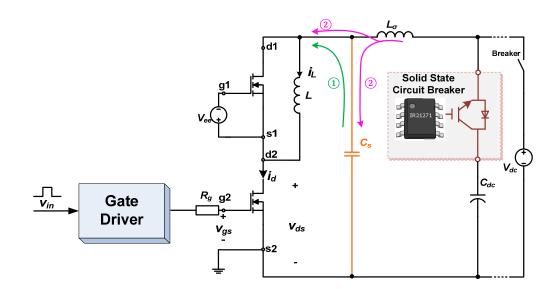

| Figure 6-6. Step-down converter with a SSCB                                                   | 96   |

| Figure 6-7. Circuit implementation of the SSCB                                                | 97   |

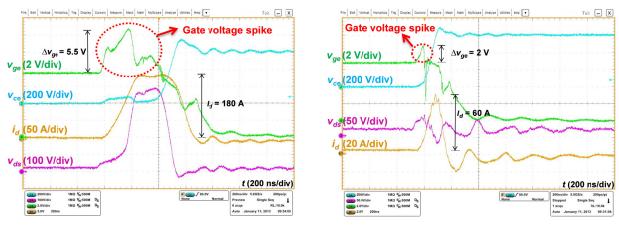

| Figure 6-8. Impact of $dV_{ce}/dt$ on the SSCB                                                | 98   |

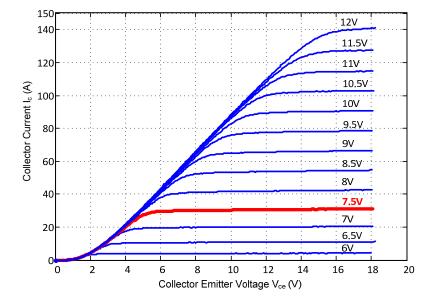

| Figure 6-9. Output characteristic of the selected IGBT                                        | 100  |

| Figure 6-10. Solid state circuit breaker with/without gate zener diode under HSF              | 101  |

| Figure 6-11. Solid state circuit breaker with/without gate zener diode under FUL.             | 101  |

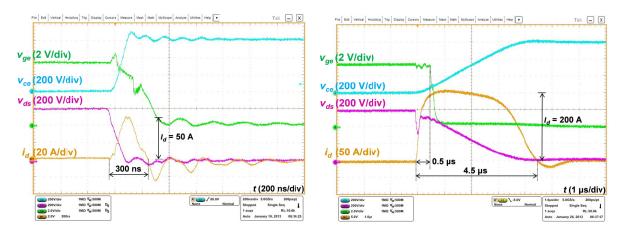

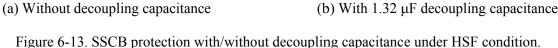

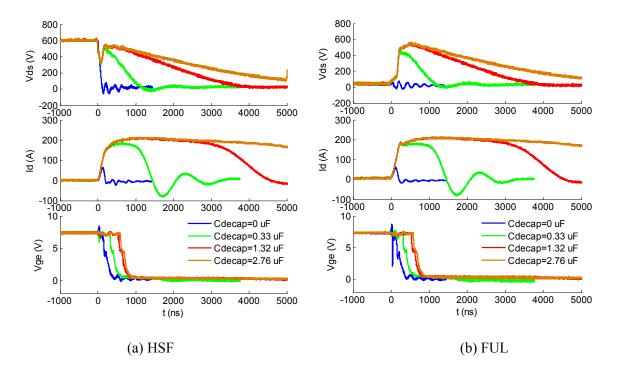

| Figure 6-12. Impact of decoupling capacitance.                                                | 102  |

| Figure 6-13. SSCB protection with/without decoupling capacitance under HSF condition          | 103  |

| Figure 6-14. Impact of different decoupling capacitances under HSF and FUL condition          | 104  |

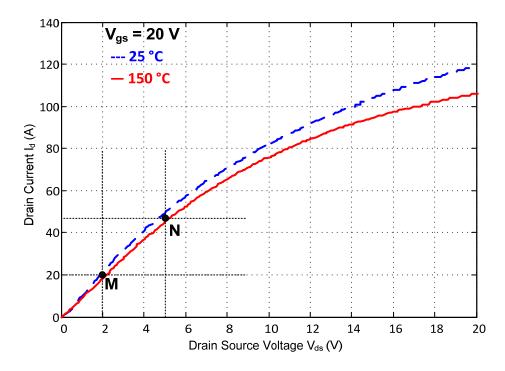

| Figure 6-15. Output characteristic of the device under different temperatures.                | 105  |

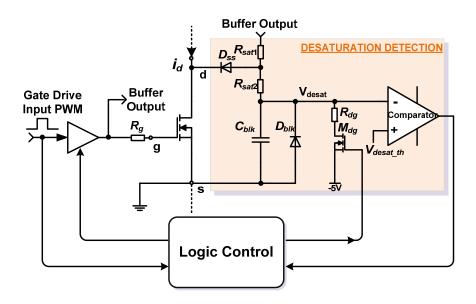

| Figure 6-16. Implementation of desaturation technique.                                        | 106  |

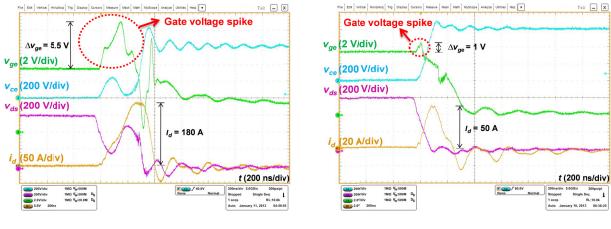

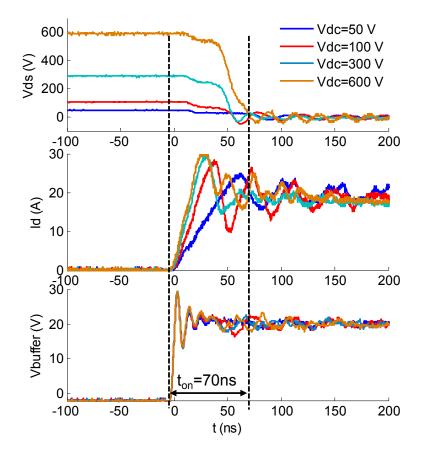

| Figure 6-17. Comparison of turn-on switching waveforms under different voltage levels         | 107  |

| Figure 6-18. False trigger suppression at normal switching transients                         | 108  |

| Figure 6-19. False trigger suppression at turn-off transient by auxiliary discharging switch. | 109  |

| Figure 6-20. False trigger suppression by different damping resistances                       | 110  |

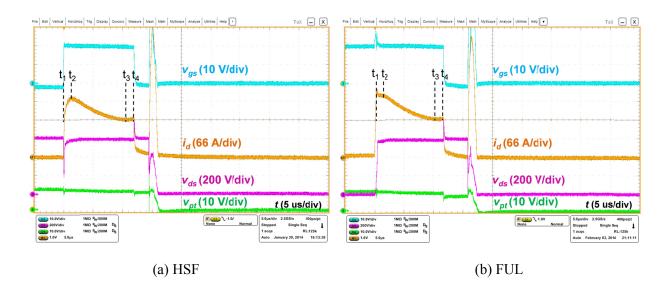

| Figure 6-21. Experimental waveforms with desaturation protection                              | 110  |

| Figure 6-22. Desaturation protection with different blanking time                             | 112  |

| Figure 6-23. Desaturation protection with different turn-on gate resistances             | 2 |

|------------------------------------------------------------------------------------------|---|

| Figure 6-24. Proposed fault current evaluation protection scheme                         | 3 |

| Figure 6-25. Physical Kelvin source connection of SiC MOSFETs 114                        | 1 |

| Figure 6-26. Proposed fault current evaluation protection scheme                         | 5 |

| Figure 6-27. Circuit implementation of fault current evaluation functionality            | 5 |

| Figure 6-28. Identification of stray inductance $L_{Ss}$ through experiment              | 7 |

| Figure 6-29. $L_{Ss}$ measurement through $V_{Ss}$ and $di_d/dt$ in experiment           | 3 |

| Figure 6-30. Current evaluation during turn-on transient 118                             | 3 |

| Figure 6-31. Measured filter output voltage $V_o$ and peak drain current                 | ) |

| Figure 6-32. Experimental waveforms with fault current evaluation protection             | 2 |

| Figure 6-33. Fault current evaluation protection with different threshold voltages       | 3 |

| Figure 6-34. Fault current evaluation protection with different turn-on gate resistances | 3 |

| Figure 6-35. Protection of HSF with different protection modes                           | 1 |

| Figure 6-36. Protection of FUL with different protection modes                           | 1 |

| Figure 6-37. Comparison of fault response time and peak current                          | 5 |

| Figure 6-38. Desaturation protection under different junction temperature                | 7 |

| Figure 6-39. Fault current evaluation under different junction temperature               | 3 |

| Figure 6-40. Comparison of temperature dependent fault peak current                      | 3 |

### **1** Introduction

This chapter starts with the introduction of the background of this research, driving and protection of high density high temperature power module for electric vehicle application. Then, the research objectives, approaches, and the organization of this dissertation are presented.

### **1.1 Background and Motivation**

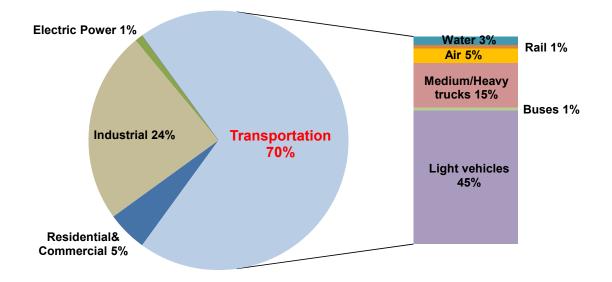

Petroleum is the largest energy source in the Unites States (U.S.), and it contributes to around 32.5% of total U.S. greenhouse gas emissions in 2010 [1]. In the consumption of petroleum, transportation accounts for 70% of U.S. petroleum consumption, with a dominant part in light vehicles, as shown in Figure 1-1 [2]. In order to reduce greenhouse gas emissions and dependence on petroleum, there has been an increasing trend for the commercialization of electric vehicles (EVs). According to the recent report from International Energy Agency (IEA), the global EVs sold more than doubled from 45,000 in 2011 to 113,000 in 2012 [3].

Figure 1-1. U.S. oil consumption in 2010.

Although EVs possess many advantages, a number of key issues in electric traction drive systems must be overcome, such as cost, volume and weight, efficiency, and reliability. The U.S. Department of Energy (DOE) technical targets for electric traction drive system are shown in Figure 1-2 [4], where the left table lists the targets at system level and the right part indicates an approximate distribution between electric motors and power electronics. The on-the-road technology status presented in [5] identifies the gaps between the current status and the targets. As reported, the key reason for the gaps is that the electric machine and drive electronics are packaged separately.

| Electric Traction Drive Systems (ETDS) |           |                  |                   |                          | Power Electronics (PE) |            |        |  |

|----------------------------------------|-----------|------------------|-------------------|--------------------------|------------------------|------------|--------|--|

| N                                      | Reduce    | Reduce           | Reduce            | Daduaa Enargy            | (\$/kW)                | (kW/kg)    | (kW/L) |  |

| Impact                                 | Cost      | Weight           | Volume            | Reduce Energy<br>Storage | 5                      | 12         | 12     |  |

| V                                      |           |                  |                   | Requirements             | 3.3                    | 14.1       | 13.4   |  |

| Year                                   | Cost      | Specific         | Power             | Efficiency               |                        |            |        |  |

|                                        | (\$/kW)   | Power<br>(kW/kg) | Density<br>(kW/L) | (%)                      | Elect                  | ric Motors | (EM)   |  |

| 2015                                   | 12        | 1.2              | 3.5               | >93                      | (\$/kW)                | (kW/kg)    | (kW/L) |  |

|                                        | 0         | 1.1              | 4.0               |                          | 7                      | 1.3        | 5      |  |

| 2020                                   | 8 1.4 4.0 | 4.0              | >94               | 4.7                      | 1.6                    | 5.7        |        |  |

Figure 1-2. Technical targets for the electric traction drive systems [4].

The most common on-the-road technology is to integrate all the power electronic converters (including bi-directional DC/DC converter, three-phase inverter, on-board battery charger, etc.) in a central box. This kind of power architecture is simple, while the expensive and bulky housing is difficult to be integrated in the engine compartment of existing vehicles. Therefore, the power electronic converters are not able to share the 105 °C engine coolant, and usually a separate 65 °C liquid cooling system is required to remove the heat generated by the electric traction drive system. Another disadvantage is that a lot of "overhead" items (e.g., shielded high-voltage connectors and cables) are necessary to transfer the power from the central box to various loads (motor, battery, ancillary loads, etc.), which contributes heavily to the overall volume, weight and cost.

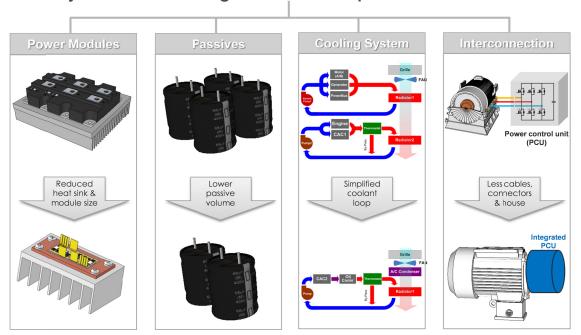

An alternative solution for the integration of electric traction drive systems is the so called "site-ofaction integration" [6]. Each power electronic converter is locally attached to the specific load it operates, and thus the interconnection cables can be greatly reduced. However, significant challenges originating from both the limitations on available installation space and harsh operating environment should be addressed. Continued advancement in power electronic components and packaging technologies, including the development of high power density semiconductor modules, will help to meet these challenges [4]. The system-level benefits by developing high density and high temperature power module is shown in Figure 1-3.

Major volume and weight contributor of power electronics converter

Figure 1-3. System-level benefits by developing high density and high temperature power module.

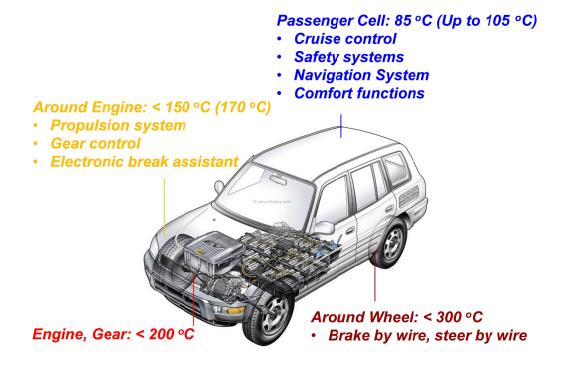

The high temperature environment inherent in electric vehicles introduce a new level of complexity in the design of the electric traction drive system. Reference [7] recently published a summary of automotive high temperature electronics requirements that is shown in Table 1-1. In addition, Figure 1-4 shows temperatures and related automotive electronic systems [8].

| On-Engine            | 150-200 °C                   |

|----------------------|------------------------------|

| In-Transmission      | 150-200 °C                   |

| On Wheel-ABS sensors | 150-250 °C                   |

| Cylinder pressure    | 200-300 °C                   |

| Exhaust sensing      | Up to 850 °C, ambient 300 °C |

Table 1-1. Mechatronic maximum temperature ranges

Figure 1-4. Ambient temperatures for automotive electronics applications.

In automotive electronics industry, electronics operating at 125 °C or above are considered as high temperature electronics. However, many of the automotive electronics components shown in Figure 1-4 have ambient temperature conditions above 150 °C. The development of high temperature capable power semiconductor modules and related control electronics will not only allow reliable operation under harsh environment, but also a significant increase in power density and reduced cooling.

On the other hand, while achieving higher power density (due to limited space and carrier capability) and high temperature electrical design (due to inherent harsh environment), the ability to guarantee the reliability and safety of power modules becomes critical [4]. One of the key reliability issues is the short circuit capability and protection of power semiconductor devices.

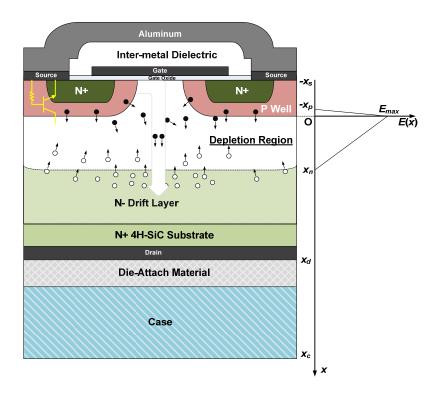

According to the classic transient thermal model, the short circuit capability of a power device can be expressed as a function of DC bus voltage ( $V_{dc}$ ) and saturation current / power density ( $J_{sat}$ ) [9], as shown in (1-1), where  $R_{th}$  and  $C_{th}$  are the thermal resistance and capacitance from junction to case,  $T_{jcrit}$  and  $T_c$  are the critical temperature and case temperature, and  $t_{sc}$  is the short circuit withstand time.

$$t_{sc} = \frac{R_{th}C_{th}}{ln\left(1 - \frac{1}{R_{th}} \cdot \frac{T_{jcrit} - T_c}{V_{dc} \cdot J_{sat}}\right)}$$

(1-1)

This equation indicates that under a given DC bus voltage and critical temperature point the short circuit capability will be reduced if the saturation current density or operating temperature is increased. The tradeoff between the high power density high temperature and high reliability needs to be carefully considered for a power module. Moreover, a fast short circuit / overcurrent protection scheme needs to be equipped for a power module.

### **1.2 Research Objectives and Approaches**

The objective of this research is to develop advanced driving and protection technologies for high temperature high density power module that is capable of operating under the harsh environment of electric vehicles, while ensuring system reliability and safety under short circuit conditions.

Corresponding to the challenges discussed in section 1.1, the research approaches are listed as follows.

(1) To adaptively reduce the switching energy loss of IGBT power modules, a novel *di/dt* feedback based active gate driver is proposed, which can reduce the turn-on and turn-off energy loss under different operating conditions. Moreover, it shares the same isolated power supply with the push-pull buffer, and high bandwidth detection and regulation circuits (e.g. current/voltage sensors, operational amplifier, etc.) are avoided, which is beneficial to the overall reliability and potential integration into a gate drive chip.

(2) To thoroughly exploit the benefits of SiC devices under high temperature environment, a SiC MOSFET and SOI gate drive based board-level integrated power module is built, with the goal of high temperature capability (up to 225 °C for power module, 200 °C for SOI gate driver), high frequency capability (up to 100 kHz), high sourcing and sinking current capability (up to 4 A for each gate driver channel), and low volume / size. In addition, a thermo-sensitive electrical parameter (TSEP) is proposed for the junction temperature measurement.

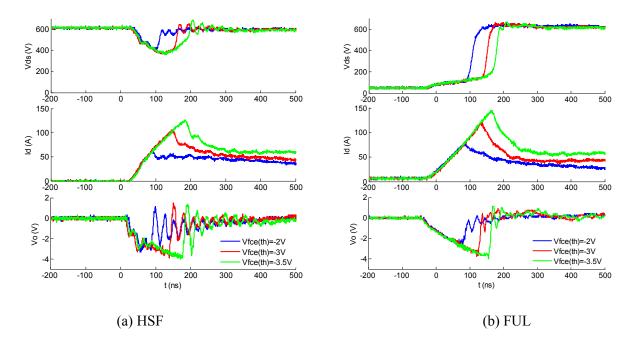

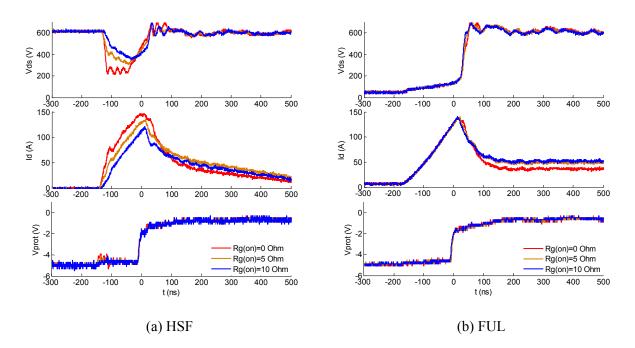

(3) To identify the key limiting factors, the short circuit capability of three types of commercial 1200 V SiC MOSFETs is evaluated under various case temperatures (from 25 °C to 200 °C), DC bus voltage levels (from 400 V to 750 V), and fault types (hard switching fault and fault under load). The associated failure mechanism has also been analyzed and compared through electro-thermal model and leakage current model.

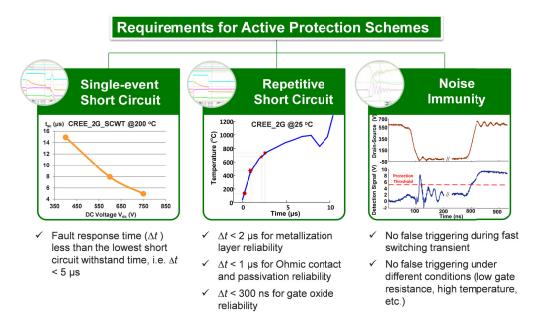

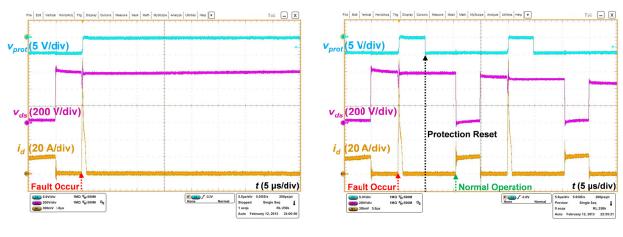

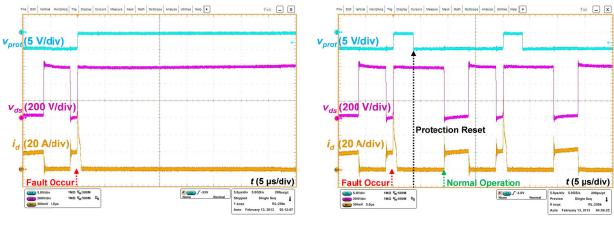

(4) Based on the short circuit capability evaluation, the protection requirement is first proposed for SiC MOSFETs considering single-event, repetitive short circuit, and noise immunity. To help designers select a proper protection method for SiC power MOSFETs, two conventional candidates are implemented, i.e. solid-state circuit breaker (SSCB) and desaturation technique, and a novel protection scheme based on the fault current evaluation is also proposed, with special focus on the design optimization, potential issues of each method, and their performance comparison.

#### **1.3 Dissertation Organization**

This research report is organized as follows:

Chapter 2 gives a detailed literature review on the key enabling technologies to develop a high temperature and high density power module. Based on the literature review, the associated challenges in each focused area are pointed out and addressed.

Chapter 3 introduces an active gate driver (AGD) for IGBT modules to improve their switching performance under normal condition. The design consideration and circuit implementation of AGD are discussed. Experimental results are presented and compared with conventional gate driving strategy.

Chapter 4 presents the design, development, and testing of a high temperature silicon carbide MOSFET power module with an integrated silicon-on-insulator based gate drive. The junction temperature limitation of the developed power module is discussed as well.

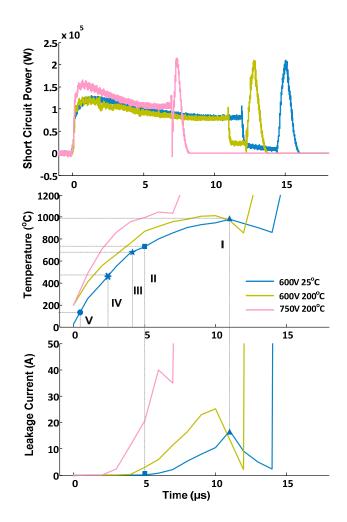

Chapter 5 discusses the temperature dependent short circuit capability of three different types of commercial SiC MOSFETs. The short circuit behavior and associated failure mechanism are compared and analyzed through transient thermal simulation.

Chapter 6 evaluates the performance of three protection schemes under various conditions, considering variation of fault type, decoupling capacitance, protection circuit parameters, etc. A comparison is made to help designers select a proper protection method.

Chapter 7 summarizes the dissertation and its key contributions, and provides suggestions for additional research in the future.

### 2 Literature Review

The high density high temperature power module is a basic element for the development of high density electric drive system. As described in [10] and [11], the relationship of the key factors to achieve a high power density and high temperature power module is given in (2-1)

$$\frac{\$}{kW} \propto \frac{S_{die}}{P} = \frac{(1-\eta)}{T_j - T_a} \cdot R_{ja(sp)}$$

(2-1)

where  $S_{die}$  is the power semiconductor device area; P is the total power handled by the corresponding power semiconductor devices;  $\eta$  is the efficiency;  $R_{ja(sp)}$  is the specific thermal resistance;  $T_j$  and  $T_a$ represent the junction temperature and ambient temperature, respectively.

As indicated in (2-1), there are several ways to increase the power density of a power module. The first way is reducing the power loss or increasing the efficiency of a power module. The second way is increasing the operating junction temperature of power devices utilizing high temperature packaging technologies and control electronics. Another way is reducing the thermal resistance through advanced cooling and packaging design. This dissertation presents the application of the first two techniques for the development of high density power module: reducing the switching loss of IGBT power modules and developing a high temperature integrated SiC MOSFET power module.

On the other hand, the reliability of the power module is also critical. Usually, with the increase of current density/power density and operating temperature, the device life time will decrease. This dissertation will only focus on the short-term ruggedness, and the long-term reliability issues are out of the scope of this work. Since the voltage source converters are widely used in the EVs, the short circuit capability and protection of SiC MOSFETs are studied, aiming at improving the reliability and overall cost of the SiC MOSFET based converter in future electric vehicles.

This section will first review the state-of-the-art research activities in the above mentioned areas. The issues and unsolved problems of previous research efforts are examined, and then the challenges of this research are addressed.

### 2.1 IGBT Switching Loss Reduction under Hard Switching Condition

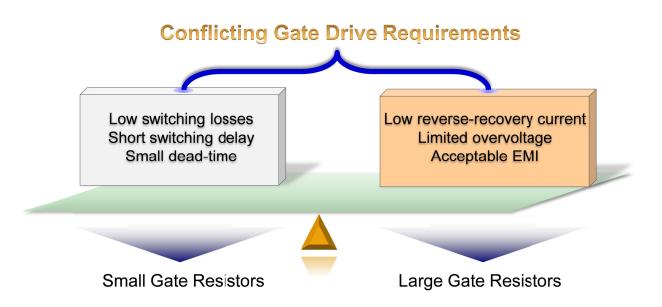

Electric vehicle applications have created new demands on IGBTs, e.g. higher current and voltage requirements, increased power density, faster switching speeds, higher efficiencies, reliable and fast protection [4]. Gate drivers serving as the interface between the IGBT power switches and the logic-level signals are expected to be optimized to meet these requirements. Conventional gate driver (CGD) circuits have employed fixed gate voltages and resistors, which are selected to minimize switching losses, suppress cross-talk and electromagnetic interference (EMI) noise, and also limit the switch stresses during switching transients and fault transients. However, these conflicting requirements, as shown in Figure 2-1, are difficult to be realized simultaneously in a CGD.

Figure 2-1. Conflicting requirements of conventional gate driver.

To deal with this issue, some research efforts have focused on reducing the switching losses by actively controlling gate drive signals. A gate drive circuit for IGBTs with a snubber circuit was proposed in [12]. This circuit utilizing the recycled energy from the snubber circuit to drive the IGBT cannot be directly applied to the hard-switched IGBTs. A multi-stage gate drive control concept has been proposed

in [13] and [14] to realize optimal turn-on and turn-off performance, as shown in Figure 2-2. The switching delay and switching losses are effectively reduced using large gate current, and the current rising/falling rate are limited using small gate current. The main issues of this method are control complexity for accurate detection of the instances for changes in driving modes, and poor adaptivity to various IGBTs with different thresholds, internal gate resistance and capacitance, etc., due to fixed control instants for certain switching stages.

Figure 2-2. Multistage gate drive concept [13] [14].

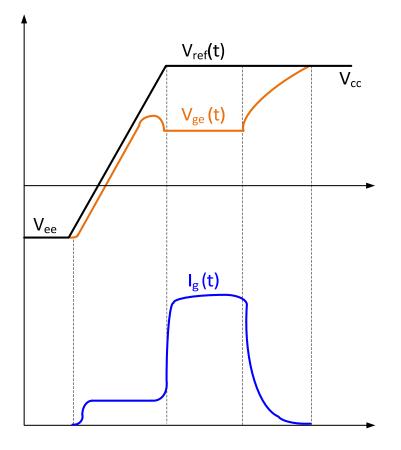

In [15]–[17], a gate driver based on the Miller plateau detection by a phase-locked loop was analyzed and proposed. This technique is able to reduce switching loss by injecting an additional gate current, however, it can result in poor operation under transient load current conditions, and the inherent one switching period delay of the updated control instructions impairs the overall effectiveness. References [18], [19] have described a sensorless gate driver with feedforward control of the turn-on dynamics to reduce switching losses, as shown in Figure 2-3. Without direct feedback control, high bandwidth current/voltage sensing and high sensitivity to EMI noise can be avoided. The gate signal reference comes from a ramp shape generator whose rising slope is designed based on data sheet parameters. The turn-off performance keeps unchanged, and turn-on delay is still quite large due to the intentionally designed low slew rate of the gate references.

(a) Circuit diagram

(b) Operating principle

Figure 2-3. Feedforward active gate driver [18].

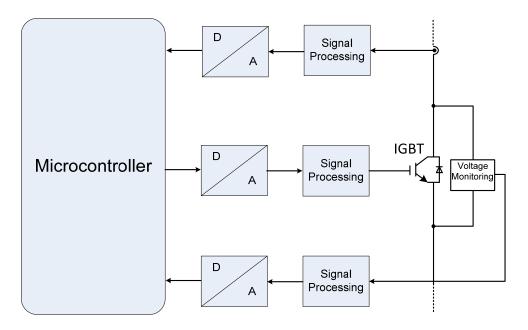

Recently, there have been several research efforts on improving the switching performances using digital approaches [20]–[22], as shown in Figure 2-4. These techniques could provide optimization among minimization of switching losses, reverse recovery current, and turn-off collector-emitter overvoltage by controlling the gate current in accordance with the desired switching operation. The main drawbacks associated with the digital method is large delay times of the D/A and A/D conversion in the signal paths, as well as considerable cost for high performance digital controllers.

Other references aiming at closed-loop/open-loop regulation of the collector current slope and collector-emitter voltage slope by means of either analog or digital approaches have been proposed and analyzed in [23]–[29]. Such techniques provide full di/dt or dv/dt control capability but sacrifice additional switching losses at switching transients.

Based on the literature survey, there is no active gate drive capable of adaptively reducing the switching energy loss of IGBTs by optimizing turn-on/off switching performance. Moreover, the existing switching energy loss reduction techniques are difficult to be integrated into a gate drive chip, which impedes the potential commercial application.

Figure 2-4. Digital control based active gate driver [20]-[22].

### 2.2 High Temperature Integrated Power Module

The trend of electrification in transportation applications, like electric vehicle, hybrid electric vehicle, and electric aircraft, brings severe challenges to future power electronic converters on both power devices and their gate drivers to operate in a high temperature environment with low weight and volume [30]–[33]. In terms of power devices, Si IGBTs are not suitable to be used in such conditions due to their limited junction temperature (<175 °C) and switching frequency (usually several tens of kilohertz). From the gate driver point of view, traditional silicon complementary metal oxide semiconductor (CMOS) based integrated circuit (IC) can only work reliably below 125 °C. The development of a high temperature integrated power module is quite challenging due to the lack of available materials and control electronics.

Featuring higher breakdown voltage, increased operating temperature, higher thermal conductivity, and lower switching and conduction loss, SiC devices are promising solutions to meet these challenges in transportation electrification [34]–[39]. Among the existing commercially available SiC devices, the SiC MOSFET is more preferable for widely used voltage-source converters because of its normally-off feature and compatible gate drive design with Si devices.

Low temperature SiC MOSFET power modules have recently become commercially available [40]– [42], as shown from Figure 2-5 to Figure 2-7. All of these modules are rated at 1200 V voltages and have a current rating of greater than 100 A. However, their junction temperatures, as indicated in the datasheets, are limited below 200 °C, due to the utilization of low temperature packaging materials.

Figure 2-5. 1200 V / 100 A SiC MOSFET module [40].

Figure 2-6. 1200 V / 120 A SiC MOSFET module [41].

Figure 2-7. 1200 V / 120 A SiC MOSFET module [42].

High temperature SiC modules are still at the research stage, as reported in [43]–[50] (shown in Figure 2-8). In [43], a 1200 V, 60 A SiC MOSFET module with optimized internal layout for fast switching speed and low turn-off overvoltage is presented. The power module is successfully operated at 100 kHz, with a junction temperature of 200 °C. Two generations of SiC MOSFET-JBS diode based multi-chip power modules are reported in [44] and [45] for 200 °C and 20 kHz operations. Reference [46] presented a line of 250 °C half-/full-bridge SiC power modules, which can be configured as either a half or full bridge through external bussing, and constructed with SiC MOSFETs, JFETs, or BJTs. Moreover, there are also some research efforts on high temperature SiC JFET power modules based on different packaging techniques [47]–[50]. All of these power modules are able to operate at a high junction temperature above 200 °C employing high temperature packaging technologies. Their full potential,

however, cannot be achieved without the presence of a high temperature gate driver (placed as close to the power module as possible for reduced volume, parasitic effect, fast switching speed, etc.) to operate them in high temperature environments.

(a) SiC MOSFET module in [43]

(b) SiC MOSFET module in [89]

(c) SiC module in [46]

(d) SiC JFET module in [47]

Figure 2-8. High temperature SiC power modules.

In order to thoroughly exploit the high temperature capability of SiC power modules, researchers from Arkansas Power Electronics International Inc. (APEI) have focused on the integration of high temperature gate drive with a SiC power module. In [51], a high temperature gate driver, composed of high temperature passive components and discrete silicon-on-insulator (SOI) active devices, is integrated into the power package and is rated for an ambient temperature of 250 °C, as shown in Figure 2-9. A similar integration technique has been applied to the design and development of a 4 kW three phase high temperature SiC inverter [52]–[54], which demonstrates the feasibility of the concept. However, the major

limitation of this concept is that only the basic driving function, i.e. totem-pole output buffer, is implemented using discrete SOI active devices. Also, the overall size, volume, sourcing and sinking current capability (below 2 A), and switching frequency (targeted at 15 kHz) of the integrated power module are limited by the high temperature gate driver based on discrete passive and active devices.

Figure 2-9. Integrated high temperature SiC MOSFET power module [51].

There are some commercial high temperature gate driver boards and one product from Cissoid is shown in Figure 2-10.

Figure 2-10. Commercial high temperature SOI gate driver [55].

A review of the state of the art of high temperature integrated gate drivers and the SOI gate driver used in this work (named as "Corinth") are summarized in Table 2-1.

|           | Temperature  | Driving Capability     | Frequency        | Process    | Input Isolation |

|-----------|--------------|------------------------|------------------|------------|-----------------|

|           |              |                        |                  | Technology |                 |

| Valle-    | Up to 225 °C | 150 mA                 | 200 kHz          | 1 μm SOI   | Transformer     |

| Mayorga   |              | without external       | Not capable of   | CMOS       | based,          |

| [56]      |              | driver stages          | DC operation     |            | on-board        |

| CISSOID   | –55 °C to    | 80 mA (low-side        | N/A              | N/A        | N/A             |

| Pallas    | 225 °C       | channel)               |                  |            |                 |

|           | junction     | 20 mA (high-side       |                  |            |                 |

|           |              | channel)               |                  |            |                 |

| CISSOID   | –55 °C to    | 1 A                    | 3 nF at up to    | N/A        | N/A             |

| Hyperion  | 225 °C       |                        | 500 kHz          |            |                 |

|           | junction     |                        |                  |            |                 |

| CISSOID   | –55 °C to    | 2 A                    | N/A              | N/A        | Possible with   |

| Themis    | 225 °C       | (two channels per chip |                  |            | additional chip |

| and Atlas | junction     | in parallel can output |                  |            | CHT-RHEA        |

|           |              | 4 A)                   |                  |            |                 |

| CISSOID   | 175 °C       | 2 A                    | 150 kHz          | Polyimide  | Transformer     |

| Hades     |              | (can be 4 A            |                  | РСВ        | based,          |

|           |              | through parallel       |                  |            | on-board        |

|           |              | drivers)               |                  |            |                 |

| Corinth   | -55 °C to >  | Sourcing: 5.5 A at     | Minimum: DC      | BCD-on-    | N/A             |

|           | 200 °C       | −55 °C, 4.5 A at       | (100% high-      | SOI 0.8-   |                 |

|           |              | 200 °C                 | side duty cycle) | micron, 2- |                 |

|           |              | Sinking: 6.0 A at      | Maximum: >       | poly, 3-   |                 |

|           |              | −55 °C, 5.0A at        | 200 kHz          | metal      |                 |

|           |              | 200 °C                 | (> 550 kHz       | process    |                 |

|           |              |                        | measured with    |            |                 |

|           |              |                        | adjusted charge  |            |                 |

|           |              |                        | pump input       |            |                 |

|           |              |                        | voltage)         |            |                 |

Table 2-1. Comparison of high temperature integrated gate drivers

CISSOID has commercialized several high-temperature integrated circuits developed on an SOI process, while the maximum on-chip source and sink current is around 2 A for each channel [55]. From the maximum current driving capability point of view, although the authors in [56] reported successful operation of a SOI gate drive chip at ambient temperatures greater than 200 °C, their on-chip output stage was limited to 150 mA. In order to increase the current capability of the SOI gate driver IC, an off-chip buffer stage based on discrete SiC JFETs are added to reach a driving capability of 5 A.

From the switching frequency point of view, all of these gate drivers are capable of high frequency operation (>150 kHz). However, there are currently no high-temperature integrated power modules based on either Cissoid's or Valle-Mayorga's solution. The only high-temperature integrated power module is reported by researchers from Arkansas Power Electronics International Inc. (APEI). Their gate driving solution is implemented using discrete SOI active devices and passive components, which limits the operating frequency and overall size/volume of the integrated power module.

In addition, during the testing of the aforementioned SiC power modules, the junction temperature measurement of the power module is either estimated through case temperature monitored by embedded thermocouples / thermistors close to the dies, or infrared radiation based measuring tool, e.g. thermal camera. All of these methods outlined necessitate visual or mechanical access to the die, which is not appropriate for an integrated power module. Is it possible to explore an online junction temperature monitoring technique for high temperature integrated power modules without any visual and mechanical access to the die?

### 2.3 Short Circuit Capability of SiC MOSFETs

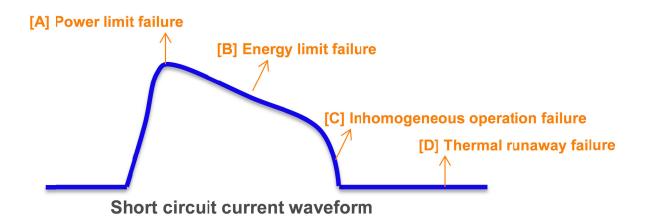

The short circuit capability of Si IGBTs has been investigated in lots of previous literature. As reported in [57], IGBT short-circuit failure mechanism can be divided into four major modes, as shown in Figure 2-11.

Figure 2-11. IGBT short-circuit failure modes described in previous literature

The four failure modes are described in detail as following:

[A]: The device failure occurs near the current peak due to I<sup>2</sup>t limitation. This failure mode is an important issue for high voltage class IGBTs, i.e. over 4.5 kV.

[B]: The high-energy dissipation during the short circuit transient causes a high local temperature, which prevents IGBTs from sustaining the maximum allowable collector-emitter voltage. This is the most common failure mechanism for various kinds of IGBTs.

[C]: Inhomogeneous operation failure is generally caused by using parallel-connected IGBTs with different gate resistances.

[D]: This failure mode is associated with the large leakage current caused thermal runaway. It has been observed in the short circuit test of FS-IGBT structure. When the device is turned off from a short circuit event, the temperature within the device is still so high such that the high temperature generated leakage current is able to cause a thermal runaway issue.

Several recent research efforts have focused on the short circuit capability testing of 1200 V SiC power MOSFETs. In [58], the short circuit capability of 1200 V / 100 m $\Omega$  SiC MOSFETs with active areas of 3.5 mm × 3.5 mm are studied and analyzed at 400 V DC bus voltage, 10 V / 15 V positive gate bias, and 25 °C case temperature. It is shown that the short circuit withstand time (SCWT) is around 80 µs

at 10 V gate voltage and 50  $\mu$ s at 15 V. Similar investigation of 1200 V commercially available devices is reported in [59], with a DC bus voltage of 400 V, gate voltage of +18 / 0 V, and case temperatures of 90 °C and 150 °C. A major concern of these testing results is that the short circuit test conditions may not represent the real application scenarios of 1200 V SiC MOSFETs that usually has a positive gate voltage as high as 20 V and DC bus voltage greater than 600 V. A more practical evaluation of short circuit capability can be found in [60] and [61] with 600 V DC bus voltage, 20 V / -5 V gate voltage, and 25 °C case temperature. However, the temperature dependent short circuit characteristics and associated failure mechanisms have not been investigated. In addition, it is still unclear what the key limiting factor (DC bus voltage level, temperature, fault type, device type, etc.) of short circuit capability is.

### 2.4 Short Circuit Protection of SiC MOSFETs

SiC MOSFETs are expected to be widely used in future converters. However, a key obstacle to its wide application is the lack of fast, reliable, low loss, and cost effective protection schemes for overcurrent/short-circuit faults. Like Si IGBTs that usually have at least 10 µs SCWT, SiC MOSFETs are also expected to have long enough SCWT for the protection circuit to detect and interrupt the fault.

Compared to overcurrent protection of Si devices and SiC JEFTs, overcurrent protection of SiC MOSFETs is more challenging in the following aspects.

From thermal point of view, SiC MOSFETs tend to have lower short circuit withstand capability compared to the Si IGBTs and MOSFETs due to smaller chip area and higher current density. According to [62], for 1200V/33A SiC MOSFETs experiencing a 600 V hard switching fault, the device failure occurs after approximately 13 µs. However, a significant leakage current is observed after 5 µs of the short-circuit condition, indicating degradation between gate and source electrodes during a short-circuit condition. As reported in [63], the short circuit withstand time of SiC MOSFETs in TO-247 package is around 8 to 10 µs under 700 V DC bus voltage and 18 V gate voltage. Recent investigation on SiC devices has shown that SiC MOSFETs present significantly lower ruggedness and robustness than SiC JFETs under short-circuit condition due to positive temperature coefficient of channel mobility up to 600

K [62]–[65]. The weaker short circuit withstand capability gives a higher pressure on the response time of the protection circuit to guarantee SiC MOSFETs operate within a safe operating area (SOA) margin.

Besides thermal breakdown, an overcurrent condition also has a negative impact on the long term stability of SiC MOSFETs, which have traditionally suffered gate oxide reliability issues induced by poor interface quality [66], [67]. Although it has been effectively mitigated by recent process improvements when operated below the maximum temperature specified by the manufacturer (125 °C), significant degradation resulting from Fowler–Nordheim tunneling current into the dielectric is evident if the temperature is raised above 125°C under overcurrent condition [68]–[70]. Low channel mobility of SiC MOSFETs requires higher positive gate bias (+20 V), i.e. higher gate electric field, and further worsens this problem [71]–[73]. In addition, as shown in [68]–[70], pulsed overcurrent operation at room temperature also results in degradation due to high junction temperature induced electron trapping, and the variation of threshold voltage increases with enhanced current levels, and increased frequencies.

Even when fast fault response time becomes the design focus of the protection scheme for SiC MOSFETs, the objective is quite challenging in a fast-switching environment. Since SiC MOSFET die has higher current density and smaller size than Si die, SiC MOSFETs tend to have lower junction capacitances and higher switching speed. Moreover, the switching speed presents different characteristics from other devices in that both the turn-on di/dt and dv/dt increases as junction temperature rises, due to the unique positive temperature coefficient of transconductance [72]. Under such high di/dt and dv/dt condition, fast response time and strong noise immunity of an overcurrent protection scheme would be a sharp contradiction. Unfortunately, currently no IEEE standard and published work exists on the allowable response time (which is a function of the amount of overcurrent, i.e. moderate overload, extensive overcurrent, and short-circuits), while a faster fault response time is always preferable to prevent it from damage and/or degradation as long as enough noise immunity can be guaranteed.

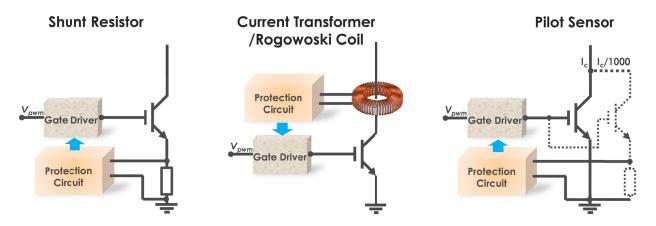

Various approaches have been proposed to protect IGBTs based on the measurement of the collector current, collector-emitter voltage, and gate voltage. The most reliable method is the direct current sensing concept, i.e. connecting a current sensor, e.g. current transformer, shunt resistor, in series with the power

devices [74], [75], as shown in Figure 2-12. The drawbacks of the current transformer are poor DC measurement, and also the need of a wide bandwidth magnetic core due to the rapid rising rate of the fault current. The drawbacks for a shunt resistor are the power consumption and also the potentially increased parasitic inductance of the power loop. In addition, costly additional sensors can make the main power circuit packaging more complicated, especially for a laminated planar busbar structure. Another similar protection scheme is based on a current mirror, realized by integrating a second sensing IGBT into the devices [76], [77]. The current mirror could indicate an overcurrent fault in that the current through the mirror is proportional to that of the main IGBT while this increases the manufacturing complexity, conduction losses, and overall cost of power modules.

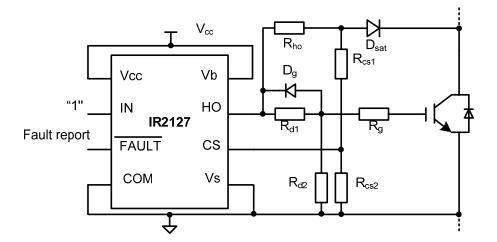

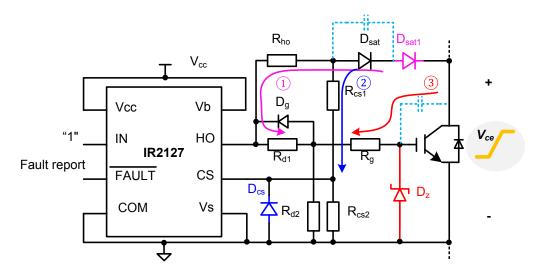

Figure 2-12. Direct current sensing based IGBT protection methods.

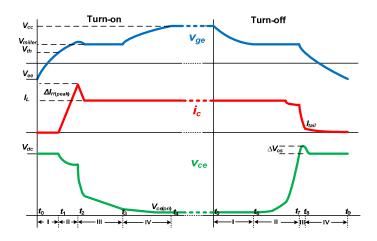

The other category of protection method is based on the indirect current sensing (Figure 2-13). The well-known desaturation technique uses a sensing diode to detect the collector-emitter voltage under overcurrent faults [78]–[80]. No dissipative current sensing element is required in the method. However, in order to avoid false triggering, it requires a programmed delay, so-called blanking time, of around 1  $\mu$ s to 5  $\mu$ s to allow collector-emitter voltage to drop below the predetermined threshold voltage (usually around 7 V) during turn-on switching transients. The fault current could surge to a very high value during the blanking time, resulting in degradation and damage of the device due to local heating.

Figure 2-13. Indirect current sensing based IGBT protection methods.

Recently, changes in the gate voltage and di/dt have been analyzed to identify a fault condition [81]– [84]. These protection methods present a small fault detection time and are preferable to be integrated within a gate driver chip. Nevertheless, these methods require complicated detection circuitry and are sensitive to parasitic inductance caused gate loop noise and diode reverse recovery current, and thus may be challenging for practical applications.

Although various active approaches are proposed to protect IGBTs there are no known publications discussing the short circuit protection of SiC MOSFETs since they became commercially available.

## 2.5 Summary

In this chapter, the literature is reviewed for the four specific topics in this dissertation, i.e. the active gate drive techniques for IGBT switching loss reduction, high temperature SiC power modules, short circuit capabilities and failure mechanisms, and short circuit protection of SiC MOSFETs. The advantages and drawbacks of the state-of-art techniques are discussed, and the challenges of these topics are identified.

# **3** Active Gate Drive for IGBT Switching Loss Reduction

In this chapter, the switching characteristics of IGBTs using a conventional gate driver are briefly analyzed. Based on the analysis, an active gate driver (AGD) for IGBT modules is proposed to reduce the switching energy loss through switching performance improvement. A step-down converter is built as well to evaluate the performance of the proposed driving schemes under various conditions, considering variation of turn-on/off gate resistance and current levels. Experimental results and detailed analysis are presented to verify the feasibility of the proposed approach.

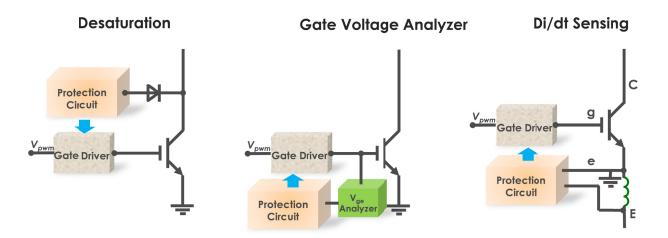

## 3.1 Analysis of IGBT Switching Characteristics

Figure 3-1 depicts the IGBT switching behavior during turn-on and turn-off transients. The turn-on transient can be divided into four stages. Stage I: The gate voltage  $v_{ge}$  rises from negative bias  $V_{ee}$  to its threshold  $V_{th}$ . Both the collector-emitter voltage  $v_{ce}$  and collector current  $i_c$  are unaffected during this stage. Stage II:  $v_{ge}$  continues increasing from  $V_{th}$  to the Miller plateau voltage  $V_{miller}$ , leading to the rapid increase of  $i_c$ . The high di/dt causes a current spike  $\Delta I_{rr(peak)}$  across the device when  $i_c$  approaches its final value  $I_L$ . Stage III:  $v_{ce}$  begins to fall rapidly, while the IGBT is carrying current  $I_L$ . A voltage tail is presented at the end of this stage due to nonlinear Miller capacitance. Stage IV:  $v_{ge}$  continues to increase from  $V_{miller}$  to its final value  $V_{cc}$ . Meanwhile, the  $v_{ce}$  attains the on steady-state value  $V_{ce(on)}$ .

Figure 3-1. Switching waveforms of an IGBT under clamped inductive load.

The turn-off transient also includes four stages. Stage I:  $v_{ge}$  decreases from positive bias  $V_{cc}$  to  $V_{miller}$ , without changing the current and voltage across the IGBT. Stage II: The collector-emitter voltage  $v_{ce}$  begins to increase while  $i_c$  maintains at the on steady-state current  $I_L$ .  $v_{ce}$  rises slowly at the beginning due to large Miller capacitance, while it quickly increases to the DC bus voltage  $V_{dc}$  at the end. Stage III:  $v_{ge}$  falls to its threshold  $V_{th}$  and the current flowing through the IGBT deceases rapidly, inducing a voltage overshoot of  $\Delta V_{os}$ . Stage IV: The current continues deceasing, with a current tail caused by the slow recombination of stored minority charge in the drift region.

## **3.2 Proposed Active Gate Drive**

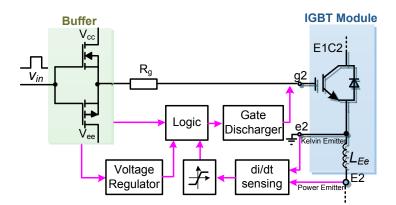

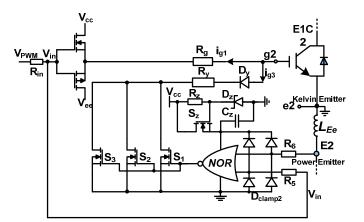

Under normal condition, the proposed AGD comprised of a turn-on and a turn-off control section, focuses on reducing the switching loss, delay time, and total switching time, while maintaining the switching stress and EMI noise level during both turn-on and turn-off transients.

### 3.2.1 Turn-on Control

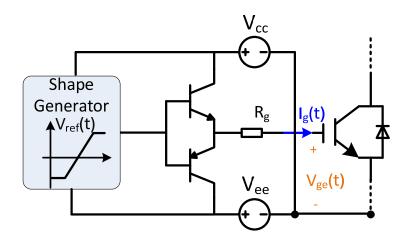

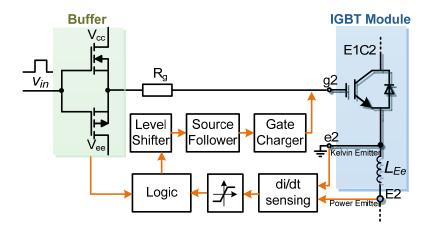

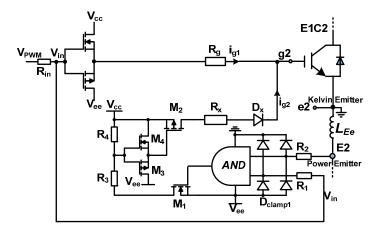

The block diagram of the turn-on AGD is shown in Figure 3-2. In addition to a conventional push-pull buffer, the proposed turn-on control is mainly composed of five parts: di/dt sensing, logic circuit, level shifter, source follower, and gate charger. The functionality of each part is described as follows.

Figure 3-2. Turn-on control diagram.

The di/dt sensing network is used to detect the different turn-on stages based on the voltage across the parasitic inductance  $L_{Ee}$  between the Kelvin emitter and power emitter of an IGBT module. This is a pragmatic choice since using a current sensor would make the circuit more complicated and expensive. Another benefit is that the voltage is converted into logic control signals, independent of the specific inductance value of an IGBT module.

The logic circuit powered by the negative power supply  $V_{ee}$  receives both the feedback signal and the enabling signal so that the circuit works properly at different stages. The detailed circuit operation will be explained below. Considering that the feedback signal may exceed the normal input voltage range of the logic circuit at high di/dt and large parasitic inductance  $L_{Ee}$ , a clamping circuit is employed to protect it from failure.

An open drain level shifter serves as an interface between the logic and source follower. The level shifter serves two purposes in this implementation: 1) it inverts the logic output, and 2) it references the logic output signal to the positive rail  $V_{cc}$  of the buffer. During operation of the level shifter, a small DC current flows in the level shifter keeping the source follower and gate charger biased in correct states. Both the buffer and the turn-on auxiliary circuit power are provided by a dc-dc power supply chip.

The source follower receives the logic signal from the level shifter, and activates/deactivates the gate charger. Another key function is that it reduces power loss of the level shifter, as will be explained later.

The gate charger, a voltage controlled current source driven by the source follower, injects an additional current into the gate at certain stages to minimize the turn-on delay time and switching losses. It also decouples the turn-on control from other parts of the whole AGD.

Figure 3-3 illustrates the circuit implementation of the turn-on AGD, and its operating principle is described as follows. When the turn-on command  $V_{in}$  is applied at the turn-on delay stage, the voltage across parasitic inductance  $L_{Ee}$  is zero since no current is flowing through the IGBT module. The output of the AND logic gate becomes high, which activates the level shifter's small-signal MOSFET M<sub>1</sub>, and subsequently the source follower MOSFET M<sub>3</sub> and gate charger MOSFET M<sub>2</sub> are turned on. Hence, the IGBT gate emitter capacitance  $C_{ge}$  is now charged by the conventional gate current  $i_{g1}$  together with the

current source  $i_{g2}$ . The delay time can be significantly reduced by adjusting the control gate resistor  $R_x$ . However, the resistance should not be too small to prevent potential gate loop oscillation. The resistance is selected for reasonable damping and low gate loop equivalent resistance, i.e.

$$2\xi \sqrt{\frac{L_G}{C_{ge}}} < R_x < R_g \tag{3-1}$$

where,  $\xi$  is the damping factor (usually around 0.707).

Figure 3-3. Circuit implementation of the turn-on control.

The additional gate current continuously charges the gate capacitance until the gate voltage hits the threshold  $V_{th}$  and the IGBT starts to conduct current. The collector current is increased with a rate of di/dt defined by (3-2)

$$\frac{di}{dt} = \frac{V_{cc} - v_{ge}}{L_{E1} + R_g C_{ies}/g_m}$$

(3 - 2)

where  $g_m$ ,  $C_{ies}$  (= $C_{ge}$ + $C_{gc}$ ), and  $L_{E1}$  represent the transfer conductance, the input capacitance, and common emitter inductance of the IGBT, respectively. Accordingly, a negative voltage drop across parasitic inductance  $L_{Ee}$  is induced. When

$$-L_{Ee}\frac{di}{dt} = V_{ILmax} \tag{3-3}$$

where  $V_{ILmax}$  is the maximum allowable low-level input voltage of the AND logic circuit, the output of the AND logic circuit is flipped to low level close to  $V_{ee}$ . The low level output deactivates the M<sub>1</sub> of the level shifter, and consequently M<sub>3</sub> and M<sub>2</sub> are turned off, while M<sub>4</sub> is turned on. The IGBT input capacitance is only charged by the conventional gate current  $i_{g1}$ , which means the di/dt, peak reverse recovery current, and the corresponding EMI noise level stay the same as for the conventional gate drive circuit. The energy loss during the current rising stage is also not changed.

The turn-on and turn-off speed of  $M_2$  depend on  $R_3$  and  $R_4$ , respectively. To have fast switching speed of  $M_2$ ,  $R_3$  and  $R_4$  should be small. However, the resistive loss of the level shifter is increased. Considering that the power dissipation of the small signal device (MOSFETs, diodes) and logic gates (AND) is very small (from several  $\mu$ W to several mW), the total loss of the auxiliary circuit  $P_s$  can be estimated by

$$P_{s} = Q_{2} \cdot V_{cc} \cdot f_{s} + \frac{V_{cc}^{2} \cdot D_{logic}}{R_{3} + R_{4}}$$

(3-4)

where  $Q_2$  is the gate charge of  $M_2$ ,  $f_s$  is the switching frequency, and  $D_{logic}$  is the duty cycle of the logic circuit's output signal. The first term represents the driving loss of  $M_2$ , which is much smaller than the resistive loss (usually in hundreds of mW) in the second term. The source follower is an integral part in accelerating the switching speed of  $M_2$  under the large resistance of  $R_3$  and  $R_4$ . The source follower effectively decouples  $M_2$ 's gate capacitance from the level shifter resistors.  $M_3$  and  $M_4$  are selected based on (3-5) to guarantee fast switching of  $M_2$ ,

$$C_{iss3} \approx C_{iss4} = \left(\frac{1}{5} \sim \frac{1}{10}\right) \cdot C_{iss2} \tag{3-5}$$

where  $C_{iss2}$ ,  $C_{iss3}$ , and  $C_{iss4}$  represent the input capacitance of M<sub>2</sub>, M<sub>3</sub> and M<sub>4</sub>, respectively.

At the end of the current rising stage, the reverse recovery current of the freewheeling diode (FWD) decays from its peak value back to zero. The FWD stops conducting and starts to block voltage. The device enters into the voltage falling stage. Since the current has reached its steady-state value, the output of the logic circuit is flipped back to a logic high level, and the gate charger is activated again. Higher

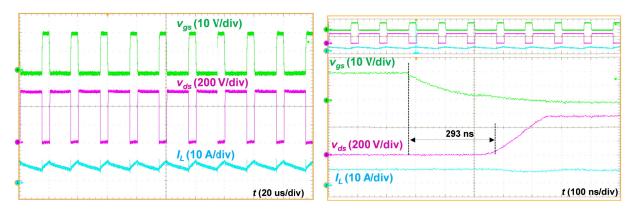

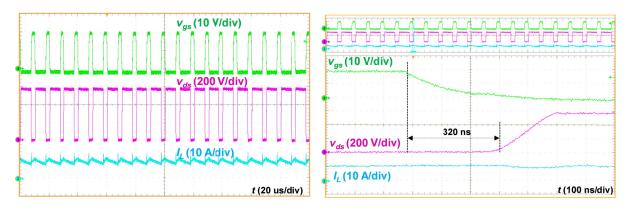

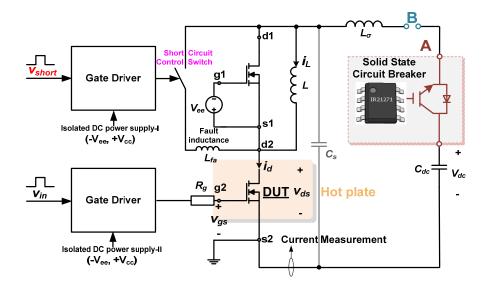

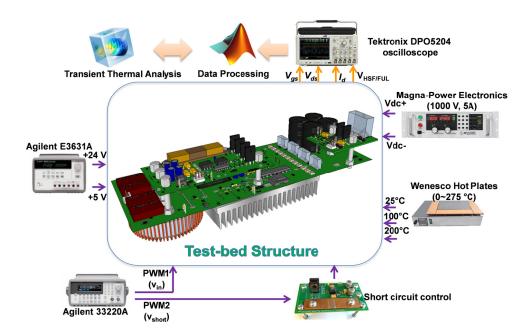

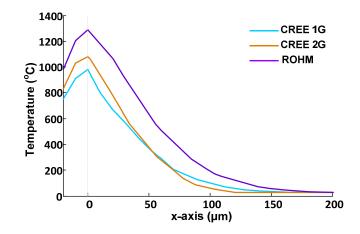

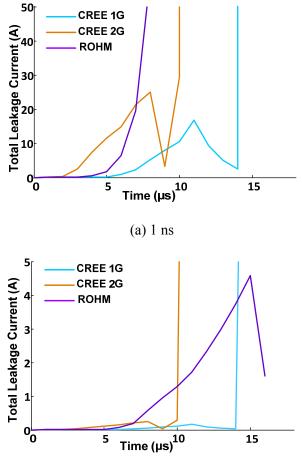

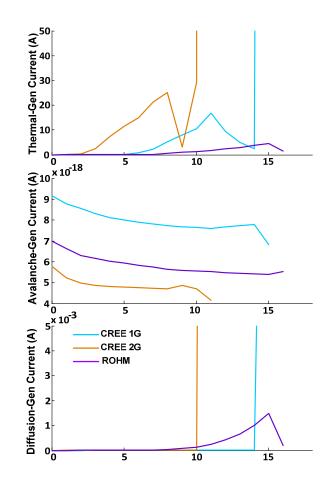

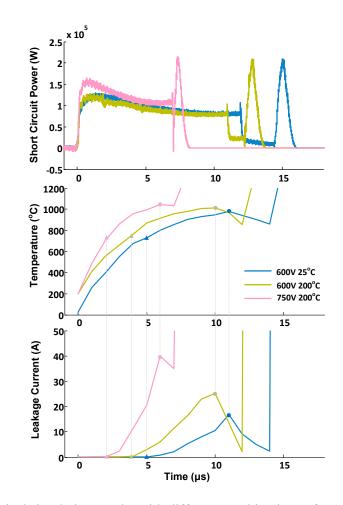

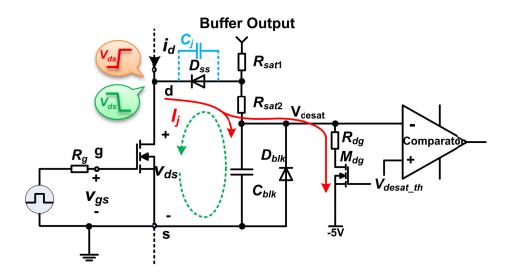

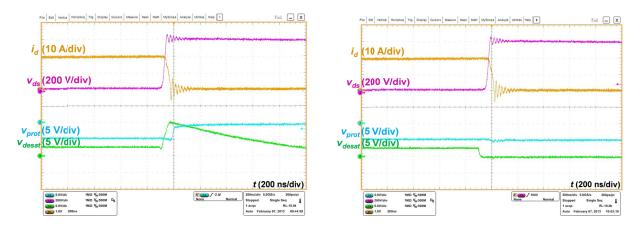

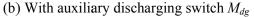

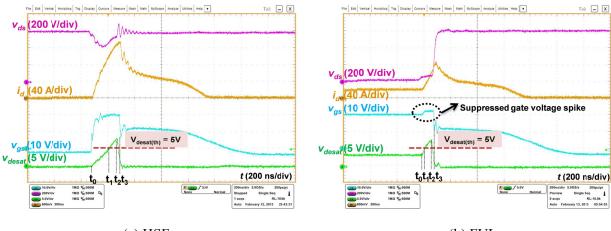

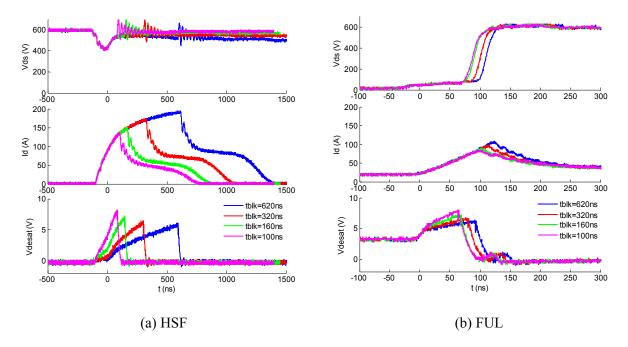

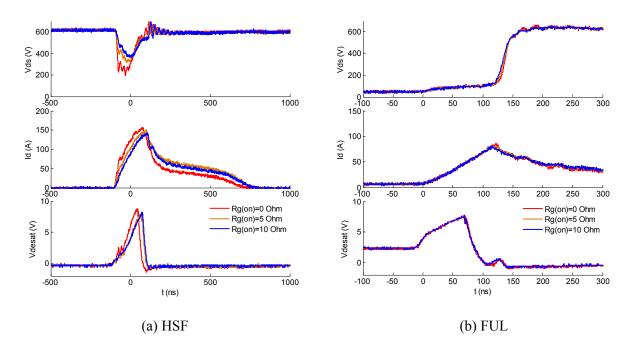

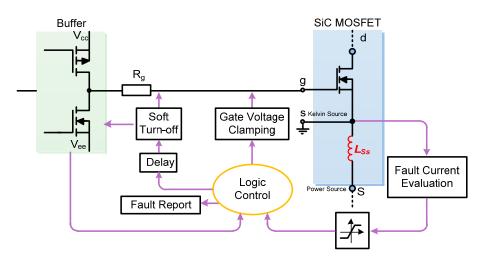

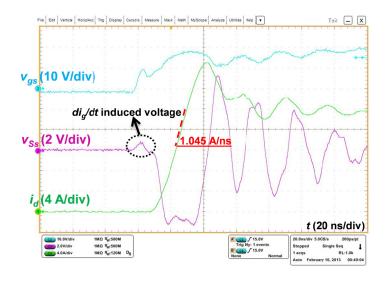

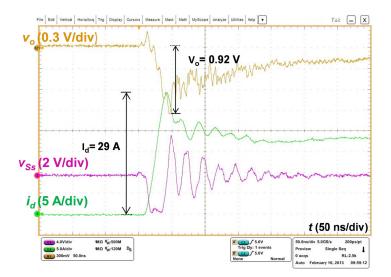

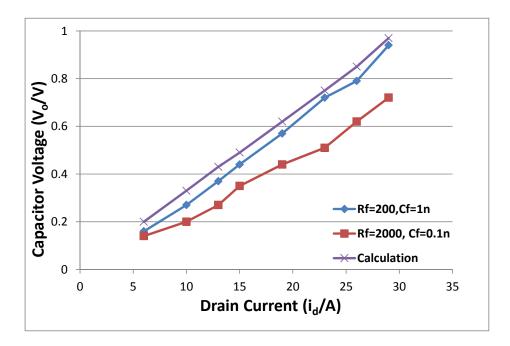

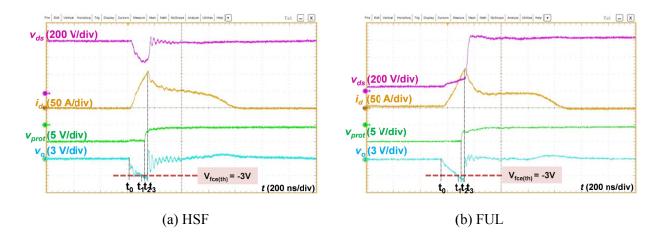

gate current charges the input capacitance more rapidly. As a result, the duration of the Miller plateau and the voltage tail are reduced. The turn-on energy loss due to the voltage tail is considerably reduced.