University of Tennessee, Knoxville Trace: Tennessee Research and Creative Exchange

**Doctoral Dissertations**

Graduate School

12-2014

# Improving GPU Shared Memory Access Efficiency

Shuang Gao University of Tennessee - Knoxville, sgao3@vols.utk.edu

#### **Recommended** Citation

Gao, Shuang, "Improving GPU Shared Memory Access Efficiency." PhD diss., University of Tennessee, 2014. https://trace.tennessee.edu/utk\_graddiss/3126

This Dissertation is brought to you for free and open access by the Graduate School at Trace: Tennessee Research and Creative Exchange. It has been accepted for inclusion in Doctoral Dissertations by an authorized administrator of Trace: Tennessee Research and Creative Exchange. For more information, please contact trace@utk.edu.

To the Graduate Council:

I am submitting herewith a dissertation written by Shuang Gao entitled "Improving GPU Shared Memory Access Efficiency." I have examined the final electronic copy of this dissertation for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Doctor of Philosophy, with a major in Computer Science.

Gregory D. Peterson, Major Professor

We have read this dissertation and recommend its acceptance:

Michael W. Berry, Michah Beck, Charles Collins

Accepted for the Council: <u>Carolyn R. Hodges</u>

Vice Provost and Dean of the Graduate School

(Original signatures are on file with official student records.)

Improving GPU Shared Memory Access Efficiency

A Dissertation Presented for the Doctor of Philosophy Degree The University of Tennessee, Knoxville

> Shuang GAO December 2014

Copyright © 2014 by Shuang GAO All rights reserved.

# DEDICATION

I dedicate this dissertation to my family and the faculty and staff who have supported me on every step of this journey.

# ACKNOWLEDGEMENTS

I would like to thank Greg Peterson for being a fantastic advisor, my committee members, and NSF for funding much of my graduate career.

Soli Deo Gloria

### ABSTRACT

Graphic Processing Units (GPUs) often employ shared memory to provide efficient storage for threads within a computational block. This shared memory includes multiple banks to improve performance by enabling concurrent accesses across the memory banks. Conflicts occur when multiple memory accesses attempt to simultaneously access a particular bank, resulting in serialized access and concomitant performance reduction. Identifying and eliminating these memory bank access conflicts becomes critical for achieving high performance on GPUs; however, for common 1D and 2D access patterns, understanding the potential bank conflicts can prove difficult. Current GPUs support memory bank accesses with configurable bit-widths; optimizing these bitwidths could result in data layouts with fewer conflicts and better performance.

This dissertation presents a framework for bank conflict analysis and automatic optimization. Given static access pattern information for a kernel, this tool analyzes the conflict number of each pattern, and then searches for an optimized solution for all shared memory buffers. This data layout solution is based on parameters for inter-padding, intrapadding, and the bank access bit-width. The experimental results show that static bank conflict analysis is a practical solution and independent of the workload size of a given access pattern. For 13 kernels from 6 benchmarks suites (RODINIA and NVIDIA CUDA SDK) facing shared memory bank conflicts, tests indicated this approach can gain 5%-35% improvement in runtime.

# TABLE OF CONTENTS

| CHAPTER 1 Introduction                                  | 1  |

|---------------------------------------------------------|----|

| CHAPTER 2 Prior work                                    | 5  |

| 2.1 Introduction                                        | 5  |

| 2.2 Interleaved Memory and Bank Conflict                | 5  |

| Conventional Low-order Bank Mapping Scheme and Analysis | 6  |

| Variant Mapping Schemes                                 | 7  |

| Bank Conflict for Multimedia Processors                 | 9  |

| GPU Bank Conflicts                                      | 9  |

| 2.3 Memory Access Patterns and Strides                  |    |

| 2.4 Padding Transformations                             | 14 |

| 2.5 Summary                                             |    |

| CHAPTER 3 Proposed Approach                             | 17 |

| 3.1 Background and Motivation                           | 17 |

| 3.2 Project Assumptions                                 | 19 |

| 3.3 Project Framework                                   |    |

| 3.4 Performance Improvement Expectation                 |    |

| 3.5 Summary                                             |    |

| CHAPTER 4 Single Vector Access Bank Conflict            |    |

| 4.1 Bank Mapping Function Descriptions                  |    |

| 4.2 Data Layout Transform and Bank Conflict             |    |

| 4.2.1 Inter-padding                                     |    |

| 4.2.2 Intra-padding                                     |    |

| 4.2.3 Bank Access Bit-width                             |    |

| 4.3 Single Vector Bank Conflict Analysis                |    |

| 4.3.1 1D Access Pattern and Bank Conflict Analysis      |    |

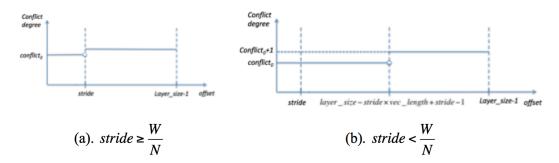

| 4.3.2 2D Access Pattern and Bank Conflict Analysis      |    |

| 4.4 Algorithm Analysis                                  |    |

| 4.4.1 1D Analysis Algorithm                             |    |

| 4.4.2 2D Access Analysis Algorithm                      |    |

| 4.5 Summary                                                              | 37 |

|--------------------------------------------------------------------------|----|

| CHAPTER 5 Single Expression Access Bank Conflict                         | 38 |

| 5.1 Basic Bank Conflict Analysis                                         | 39 |

| 5.1.1 1D Access Analysis and Algorithm                                   | 39 |

| 5.1.2 2D Access Analysis and Algorithm                                   | 43 |

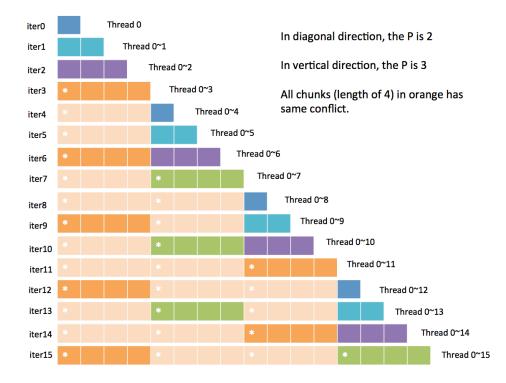

| 5.2 "for" Loop Wrapped Single Access Expression                          | 44 |

| 5.2.1 Motivation                                                         | 44 |

| 5.2.2 Solution                                                           | 45 |

| 5.3 "If" Condition Wrapped Single Access Expression                      | 46 |

| 5.3.1 Motivation                                                         | 46 |

| 5.3.2 Solution                                                           | 47 |

| 5.4 "for-if" Statement Wrapped Single Access Expression                  | 49 |

| 5.4.1 Motivation                                                         | 49 |

| 5.4.2 Solution                                                           | 50 |

| 5.5 Summary                                                              | 53 |

| CHAPTER 6 Parameter Optimization Strategy                                | 55 |

| 6.1 Parameter Optimization Space                                         | 55 |

| 6.2 Inter-padding Optimization                                           | 56 |

| 6.2.1 1D Strides                                                         | 56 |

| 6.2.2 2D Strides                                                         | 59 |

| 6.3 Intra-padding Optimization                                           | 59 |

| 6.3.1 1D Strides                                                         | 60 |

| 6.3.2 2D Strides                                                         | 61 |

| 6.4 Parameter Optimization Algorithm                                     | 62 |

| 6.5 Summary                                                              | 68 |

| CHAPTER 7 Application Study                                              | 69 |

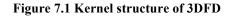

| 7.1 3DFD                                                                 | 69 |

| 7.2 ConvolutionSeperable: convolutionRowsKernel                          | 70 |

| 7.3 ConvolutionSeperable: convolutionColKernel                           | 71 |

| 7.4 Transpose: TransposeCoalesed, TansposeDiagonal, TransposeFineGrained | 71 |

| 7.5 Transpose: TransposeCoalesedGrained                                  | 72 |

| 7.6 shfl_scan: shfl_vertical_shfl                                          | 2 |

|----------------------------------------------------------------------------|---|

| 7.7 lud: lud_diagonal7                                                     | 3 |

| 7.8 lud: lud_perimeter                                                     | 4 |

| 7.9 NW                                                                     | 5 |

| 7.10 Summary                                                               | 7 |

| CHAPTER 8 Performance Experiments                                          | 8 |

| 8.1 Conflict Analysis Time Experiments                                     | 8 |

| 8.2 Application Optimization                                               | 5 |

| 8.3 Summary                                                                | 8 |

| CHAPTER 9 Conclusion and Future Work                                       | 9 |

| List of Reference                                                          | 0 |

| Appendix                                                                   | 6 |

| Appendix A-1: 1D Single Warp Analysis for Column-major Bank Mapping        | 7 |

| ODD STRIDE ANALYSIS                                                        | 7 |

| Appendix A-2: 2D access bank conflict analysis                             | 1 |

| Appendix A-3: Two-way Conflict for Column-major Bank Mapping with $R=2102$ | 2 |

| Vita                                                                       | 4 |

# LIST OF TABLES

| Table 4.1 Summary of features of bank mapping functions | . 25 |

|---------------------------------------------------------|------|

| Table 4.2 Summary of features of bank conflict problem  | . 29 |

| Table 4.3 2D stride pattern calculation                 | . 30 |

| Table 8.1 Information of application CUDA kernels       | . 86 |

# LIST OF FIGURES

| Figure 2.1 Conventional bank mapping                                                    | 7  |

|-----------------------------------------------------------------------------------------|----|

| Figure 2.2 Typical access patterns                                                      | 12 |

| Figure 2.3 Memory access by 1D warp                                                     | 12 |

| Figure 2.4 Memory access by 2D Warp                                                     | 12 |

| Figure 3.1 The relations of this project and related research areas                     | 19 |

| Figure 3.2 Framework of the project                                                     | 21 |

| Figure 4.1 1D Array data mapping for different mapping functions                        | 25 |

| Figure 4.2 Sample code                                                                  | 26 |

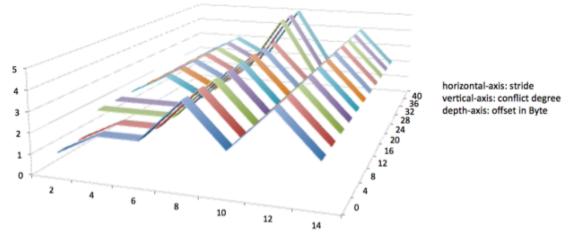

| Figure 4.3 Conflict degree of different offsets for different stride values             | 26 |

| Figure 4.4 Impact of offset for different access bit-width setting                      | 27 |

| Figure 4.5 Impact of intra-padding on bank conflict numbers                             | 27 |

| Figure 4.6 Impact of bank access width on bank conflict degree                          | 28 |

| Figure 4.7 shape of parallel memory access unit and base memory access patterns         | 30 |

| Figure 4.8 Examples of the base 2D access pattern transformation                        | 30 |

| Figure 4.9 for power-of-two stride                                                      | 32 |

| Figure 5.1 Conflict Analysis Modules                                                    | 38 |

| Figure 5.2 an example                                                                   | 42 |

| Figure 5.3 Examples of for loop wrapped memory accesses                                 | 45 |

| Figure 5.4 An example of loop which has 10 iterations, and P=3                          | 46 |

| Figure 5.5 An example of "if" statement used to filter the threads by thread ID         | 47 |

| Figure 5.6 Dividing threads into groups                                                 | 48 |

| Figure 5.7 An example of "for-if "wrapped single expression access                      | 50 |

| Figure 5.8 the example of "for-if" wrapped 1D array access                              | 51 |

| Figure 5.9 Analysis of the example of "for-if "scenario for 2D triangular access        | 52 |

| Figure 6.1 offset impacts on conflict number                                            | 56 |

| Figure 6.2 impact of offset on conflict degree for power-of-two strides                 | 57 |

| Figure 6.3 Conflict of stride=3, W=8, N=4, M=4                                          | 58 |

| Figure 6.4 Map the conflict pattern of a offset to one of <i>R</i> known distinct cases | 59 |

| Figure 6.5 Conflict degree examples for row-major bank mapping function                 | 60 |

| Figure 6.6 Conflict degree examples for column-major bank mapping function           | . 61 |

|--------------------------------------------------------------------------------------|------|

| Figure 6.7 Parameter optimization strategy                                           | . 63 |

| Figure 6.8 Option one: Strategy to reduce workload for intra-padding optimization    | . 65 |

| Figure 6.9 Candidate solutions in area of two columns                                | . 65 |

| Figure 6.10 Option two: Strategy to reduce workload for intra-padding optimization   | . 67 |

| Figure 7.1 Kernel structure of 3DFD                                                  | . 69 |

| Figure 7.2 Memory access pattern of 3DFD                                             | . 69 |

| Figure 7.3 Kernel structure of convolutionRowKernel                                  | . 70 |

| Figure 7.4 Memory access pattern of convolutionRowKernel                             | . 70 |

| Figure 7.5 Memory access pattern of convolutionColKernel                             | . 71 |

| Figure 7.6 Kernel structure of TransposeCoalesed                                     | . 72 |

| Figure 7.7 Memory access pattern of TransposeCoalesed                                | . 72 |

| Figure 7.8 Kernel structure shfl_vertical_shfl                                       | . 73 |

| Figure 7.9 Memory access pattern shfl_vertical_shfl                                  | . 73 |

| Figure 7.10 Kernel structure of lud_diagonal                                         | . 74 |

| Figure 7.11 Kernel structure of lud_perimeter                                        | . 75 |

| Figure 7.12 Kernel structure of nw                                                   | . 76 |

| Figure 7.13 Memory access pattern of nw                                              | . 76 |

| Figure 8.1 analysis module execution time                                            | . 79 |

| Figure 8.2 Loops used to test conflict estimation tool                               | . 80 |

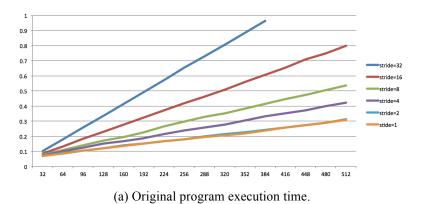

| Figure 8.3 Original program execution time                                           | . 81 |

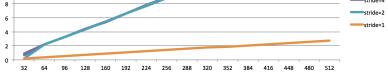

| Figure 8.4 Basic analysis method: enumerate all access and compute conflict number . | . 82 |

| Figure 8.5 Analysis with no "for" loop optimization                                  | . 82 |

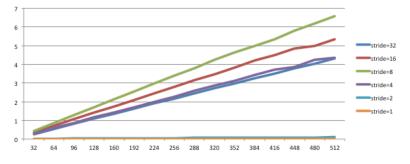

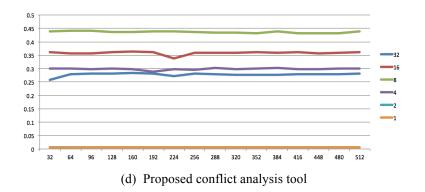

| Figure 8.6 Proposed conflict analysis tool execution time                            | . 83 |

| Figure 8.7 Loop used to test conflict estimation tool                                | . 83 |

| Figure 8.8 execution time comparison for "for-if" case                               | . 84 |

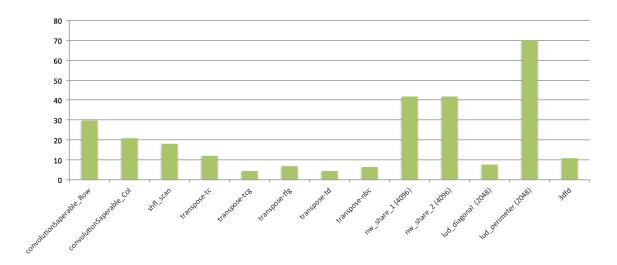

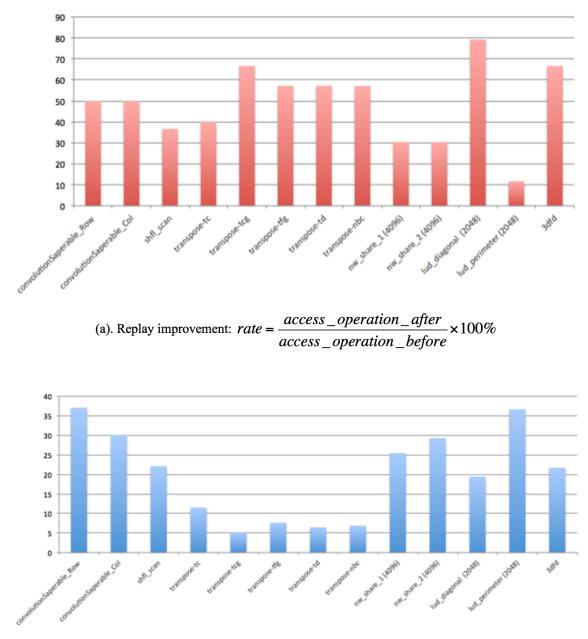

| Figure 8.9 Percentage of bank access replay among total executed instructions        | . 86 |

| Figure 8.10 Performance experiment of 13 kernels                                     | . 87 |

### **CHAPTER 1 INTRODUCTION**

In recent two decades, graphical processing unit (GPU) evolved from a graphicsoriented processor to a general-purpose parallel processor. NVIDIA CUDA (Compute Unified Device Architecture) and OpenCL[1] are two commonly used GPU programming models. Through such programing models, many HPC applications and libraries can exploit GPU accelerators to obtain performance improvements.

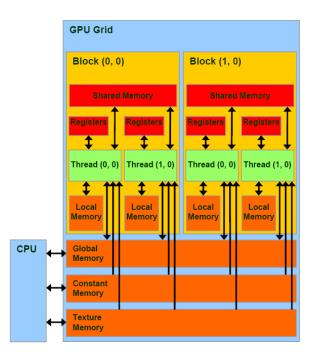

When developing GPU kernels, optimizing memory access efficiency is one of the main schemes for improving execution performance [2]. Among the different memory types defined in the CUDA programming model, shared memory plays a key role as a software manageable on-chip storage. As figure 1 shows, a shared memory buffer is allocated for one thread block and all threads in this thread block have access to it. The access latency of shared memory is much less than GPU device memory. Normally, shared memory is used for caching data to improve temporal locality [3], holding the data shared inside one thread block [4], and being temporary storage for data layout transforms to achieve better global memory performance [5]. A primary concerns of using shared memory is the penalty of potential bank conflicts for different memory access strides [1, 2].

CUDA shared memory is organized into banks. The bank mapping function is based on conventional low-order bank mapping [6], which maps n successive words to n successive banks. To improve bank access efficiency for different data types, it supports dynamic configurable bank access bit-width [7]. For example, 32 of 4-Byte elements can be uniformly mapped to 32 banks; and 32 of 8-Byte elements can also be uniformly mapped to these banks. In addition, multiple accesses to the same layer of the same bank cause no conflict.

Figure 1.1 CUDA programming model and memory hierarchy [1]

Bank conflict analysis of interleaved memory has been well studied since the 1970s [8-14]. When two accesses of the same bank occur inside the period of the bank response latency, the conflict happens and the two requests are processed serially. For non-vector accesses, by instruction scheduling and adding buffers, bank conflicts can be reduced [15, 16]. For parallel access, stride analysis is necessary to deal with bank conflicts [15, 16]. Based on stride analysis, many solutions have been proposed to obtain better support for different strides. CUDA shared memory bank organization is explained in programming guide. When designing CUDA kernels, developers should be aware of potential bank conflict issue and they can reduce or eliminate conflicts by modifying data layout, or changing memory access pattern. Researchers presented different data layout transformations to deal with shared memory bank conflict problem [3, 5, 17-19]. Among them, array padding is the easiest and most frequently used [5, 18].

Array padding has been used to solve varies issues related to memory access efficiency. Typical cases include cache conflicts, false sharing, and bank conflicts. There are two types of array padding: inter-padding and intra-padding [20]. Inter-padding adds dummy space between array variables; intra-padding inserts unused spaces inside one array. To deal with bank conflicts problem, intra-padding can be used to change the array

access stride and in turn impacts the conflict degree. Normally, CUDA kernel programmers try to use different padding sizes and choose the one that causes the least bank conflicts.

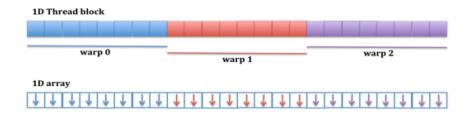

The motivation of this dissertation is to improve CUDA shared memory bank access efficiency. In the CUDA parallel execution model, since the memory access pattern of one grid's (1D to 3D) access requests is relatively complex, shared memory bank conflict analysis is not obvious. A warp is the CUDA hardware parallel execution unit; it includes a small group of threads. Based on the shape of a thread block, the threads in a warp could be organized in a 1D vector, 2D array, or even 3D array. Different transformations of these warp shapes can be mapped to arrays stored in memory, resulting in different memory access patterns.

This thesis analyzes CUDA shared memory bank conflict for 1D and some 2D array access patterns, and proposes a heuristic optimization solution. (1) Given an access pattern and a hardware-supported mapping function, the bank conflict degree is evaluated. (2) To reduce or eliminate bank conflicts, a heuristic scheme seeks an improved data layout through optimizing parameters of inter-padding, intra-padding, and different bank mapping function configurations. (3) Finally, the source code is transformed according to the chosen solution.

The contribution of this work includes:

- 1D/2D stride and bank conflict analysis of dynamic bank addressing;

- A method that calculates the overall conflict number of one pattern within a limited period which doesn't depend on memory access workload size of this pattern;

- Given the shared memory space limitation of one thread block, a model driven heuristic parameter optimization method that looks for a solution in a potential parameter optimization space:

- Bank mapping functions supported by hardware dynamic bank addressing;

- o Inter-variable-padding and changing variable definition sequences; and

- Array intra-padding size.

This thesis is organized into 8 chapters. Chapter 2 describes the prior work related to interleaved memory bank conflict analysis, memory access pattern study, and padding

related schemes. Chapter 3 introduces the framework of the proposed approach. Chapter 4 describes the single vector/warp conflict analysis, which is the kernel module of the work. In CUDA programming model, one memory access expression drives concurrent threads to access a sequence of data in parallel. Normally these threads belong to multiple vectors (warps). Chapter 5 takes single expression as a unit and analysis it bank conflict. Chapter 6 presents the parameter optimization strategy for inter-padding, intra-padding, and bank access bit-width configuration. Chapter 7 briefly lists the applications used for experiments and chapter 8 presents the experimental results.

### **CHAPTER 2 PRIOR WORK**

# 2.1 Introduction

This chapter studies three research areas that are related to the proposed project. We studied the prior works of interleaved memory bank conflict solutions, and then investigated the common 1D and 2D memory access patterns. Finally, we studied the prior works of padding. The proposed tool of this work uses padding as one of the main data layout transformation methods.

# 2.2 Interleaved Memory and Bank Conflict

Interleaved memory is used to improve memory throughput by dividing memory into multiple modules/sections/banks to allow them to work simultaneously. This is especially straightforward for vector processors; it enables parallel access to memories. [9, 21]

Bank conflict is one of the main concerns for designing efficient, interleaved memory. It occurs when multiple concurrent memory requests are issued to the same module/bank. In such a situation, the bank has to serve one request after another, degrading performance.

Bank conflicts exist in various system/processor designs. A vector processor has a bank conflict when one vector access request operates on data in the same banks. An example system is the Cray-1 [9]. It had 16 banks, and each bank was 64-bits wide. This design had bank conflicts when the access stride size was 8 or 16 words. Superscalar processors such as Intel's Sandy Bridge [22] also have the same issue when multiple memory accesses are grouped together. Normally some software/hardware modules are added to reduce or eliminate conflicts. Bank conflicts also impact other types of processors. VLIW processors, basically rely on compile time schemes to reduce the impact of bank conflict [23]. Multimedia processors and other application driven

hardware design also have bank conflict concerns due to their memory access patterns [24, 25].

Many hardware solutions have been proposed to deal with the memory bank conflict problem. Most existing solutions define a better bank mapping function that can support as many different strides as possible or provide perfect support for some special access patterns. Normally these bank mapping functions are designed based on the knowledge of some frequently used access patterns, such as the ones appearing in linear algebra calculations. Normally the number of banks is a power of two. Some researchers proposed using a prime number of memory banks to reduce bank conflict [10, 11]; however, prime number arithmetic is hard to implement in hardware. Some other research targets the bank conflict caused by multiple memory access instructions. Some well-designed scheduling schemes and extra buffers are used to avoid conflict or reduce bank conflict impact[15, 16].

In addition to hardware solutions, software solutions can also be used to reduce bank conflict. For example, by changing instruction sequences generated by a compiler [22], the memory operation instructions that cause bank conflict can be separated. From a high level programming perspective, changing memory access patterns in source code can also help to avoid or reduce bank conflict. [26]

#### Conventional Low-order Bank Mapping Scheme and Analysis

As shown in Figure 2.1, a conventional mapping function maps array elements sequentially on to N banks. The function can be described as  $bank\_id[i] = mod(i,N)$ . This function maps the i<sup>th</sup> word of data on to bank of  $bank\_id[i]$ . The bank conflict degree for different 1D access strides can be determined by gcd(S,N), in which N is the number of banks and S is the constant stride value. For a system which has power-of-two banks, the result of gcd(S,N) equals to 1 for any odd stride. In other words, odd stride access of N words has no bank conflicts. However, for even strides, the conflict exists because gcd(S,N) does not equals to 1. For example, when the stride is 2, the conflict is 2-way conflict since gcd(2,N) = 2.

| Bank0 | bank1 | bank2 | bank3 |

|-------|-------|-------|-------|

| 0     | 1     | 2     | 3     |

| 4     | 5     | 6     | 7     |

| 8     | 9     | 10    | 11    |

| 12    | 13    | 14    | 15    |

Figure 2.1 Conventional bank mapping

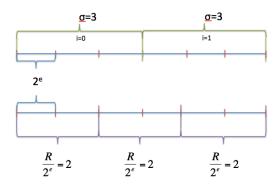

The notation "stride family" is defined for stride analysis purposes [4]. Basically, a stride family is described as  $S = \sigma \times 2^e$ , where  $\sigma$  is the sequence of odd numbers, and e is an integer which denotes a distinct family. For example,  $S = \{2, 6, 10, 14, 18, ...\}$  is the family with e = 2. For conventional mapping functions on a system with power-of-two banks, the stride family indicates the degree of conflict. For example when e = 2, the conflict is always 2. Oed and Lang presented detailed conflict analysis of conventional mapping function in [12].

GPU shared memory is based on a conventional low-order bank mapping function [2, 18]. The bank number is a power-of-two and the parallel access request number is the same as the bank number. To improve flexibility, it supports dynamic bit-width bank access. To avoid bank conflicts, programmers need to organize the data in proper ways. The most common ways to deal with bank conflict are: (1) choose a proper access mode provided by the GPU programming model [27]; (2) add padding to change access strides [5, 18]; (3) change the array index functions to make vector access uniformly mapped to every bank; and (4) algorithm level memory layout optimization [3]

#### Variant Mapping Schemes

Various bank mapping functions have been proposed to solve bank conflicts. The two main categories are XOR schemes [28] and skewing schemes [10, 29].

The **XOR** scheme was first proposed by Failong [13]. This scheme normally has the form of a linear transformation: y = Tx. Its input is an address x which is represented as a bit vector. This transformation maps x into another bit vector y which is the address

to which the data is mapped to. Some bits of such bit vectors indicate the bank index. The matrix T is the transform matrix. Each element in T is one-bit of data and its value is 0 or 1. This transform is realized by modulo 2 arithmetic, which is easy for hardware implementation.

The XOR scheme has better flexibility compared to skewing methods. By changing T, XOR can support different mapping strategies. For example, some existing transformations are designed to generate pseudorandom numbers to realize uniform data distribution across banks [14, 30]; some other transformations produce periodic sequences that can avoid bank conflict for some strides or access patterns [31].

Based on the XOR scheme, Gou presents SAMS [32] to support some stride families for 1D access. This method uses the XOR transform to reduce conflict degree and then increase the bank bit-width to remove remaining conflicts. This work also presents a 2D scheme 2DSMM, that uses two bank mapping functions,  $T_h$  and  $T_v$ , to support some 2D access patterns such as unit-stride/stride visit of row, column, diagonal, and block.

Harper proposed a dynamic strategy based on the XOR method [33]. Given a known stride, a proper XOR transform is selected to meet requirements.

The **Skewing** method was presented by Budnick and Kuck [10]. Normally it realizes conflict-free access for a subset of strides. Shapiro presented a review of the skewing method [29]. Basically a skewing method can be described as a linear mapping that maps consecutive data to banks resulting in less bank conflicts. Since no single skewing method can eliminate conflict for all different strides, many skewing methods have been proposed to support different stride types [29] [34-36].

No single skewing method can support all strides. Instead of eliminating all bank conflict, Harper proposed a skewing-based solution that optimizes overall performance by reducing bank conflict [37]. In addition, Harper presented a dynamic strategy based on the skewing method [8]. Based on known stride knowledge, this approach chooses a proper skewing scheme to eliminate conflict. Also et al [38] presented a runtime changeable skewing method, which determines the skewing scheme based on runtime stride information.

Some existing skewing schemes target 2D/3D access patterns [37, 39-41]. Harper et al [37] analyzes skewing performance for some commonly existing stride types from

linear algebra applications. Kaufman et al [40] presented a skewing method that supports 3D vector access of 26 different directions. To support different sub-array patterns in 2D space, Liu et al [41] uses linear skewing in the horizontal direction and non-linear skewing in the vertical direction.

#### Bank Conflict for Multimedia Processors

Multimedia accelerators generally require high memory bandwidth due to parallel 2D access patterns and fast multimedia processing speed. How to avoid or reduce bank conflict for these 2D-stride access patterns has been investigated to improve memory system performance. Some solutions are provided based on 2D-stride access analysis. Kuzmanov et al [24, 25] presented a parameterized pattern for a type of 2D parallel access; an interleaved memory organization is proposed accordingly. Different parameter configuration patterns use different bank mapping functions. Lentaris et al [42] presented a non-linear skewing based method to achieve efficient memory access for some 2D access patterns. This work also optimized the bank access requests for image access.

#### GPU Bank Conflicts

In the past decade, the traditional graphics process unit (GPU) architecture was adapted to support general purpose computing and became widely used for massively data parallel computing. Memory system efficiency is crucial for this massive parallel device. Sung et al [43] presented a bank conflict study of GPU global memory access. Using micro-benchmark with different access strides, they studied the bank conflict characteristics of global memory. By combining this knowledge with analysis of application memory access stride information, they could find optimized data layout transforms to improve access efficiency.

The bank conflict problem is a primary issue for making efficient use of GPU shared memory [1, 2, 27]. This memory is composed of power-of-two banks. Based on the conventional low-order mapping scheme, different generations of GPU devices have

different mapping functions. The newest improvement is dynamic bank access mode [7]. This mode provides different bit-width access mode to all banks. The motivation of this design is to support efficient parallel memory access for data types with different bit-widths. For example, when bank number equals to N, if data type size is 4-Byte, N sequential elements are mapped to N different banks; if data type size is 8-Byte, N sequential elements can still be mapped to N different banks. For both cases, there is no bank conflict.

Like conventional memory module mapping, these consecutive mapping functions have similar bank conflict issues. However, since they support different consecutive mapping strategies, they have different conflict characteristics regarding different stride size [27]. Moreover, unlike conventional mapping methods, these strategies sometimes have conflicts due to bank offsets of the base address (the address of the first element that is visited). Examples are described in chapter 4.

The GPU programming model leaves the shared memory bank conflict problem to programmers. With the knowledge of different mapping functions, programmers need to design their data layout carefully to achieve efficient data access to the banks. For many applications, it is not easy to understand how data are mapped to banks. Generally, programmers try to add a small padding to change the access stride, or redesign the data organization to improve the efficiency.

In chapter 4, we will discuss the stride analysis of this bank mapping solution.

### 2.3 Memory Access Patterns and Strides

For scientific computing applications, array access pattern analysis is very helpful for improving memory access efficiency. Related compile-time optimizations include loop transformation [44], loop prefetching [45, 46], and array padding [47-50]. Besides general optimization for various array access patterns, some previous work provides automatic analysis and optimization for code that have similar array access patterns [51]. Jaejer and Barthou proposed a stencil kernel generator which is based on access pattern analysis [50], it searches for better data layout transforms to improve memory access

efficiency. Sung et al [43] presented an automatic data layout transform scheme based on common access patterns of PDE solvers and structured grids. A source-to-source subscript transformation module is designed accordingly.

Program level optimizations regarding access pattern and memory efficiency have been well studied for different memory systems. Lee et al [52] summarized common array access patterns of typical applications. Corresponding optimization advice is presented as well.

For interleaved memory, bank access stride patterns directly impact the parallel access efficiency. Besides bank mapping functions, for linear array data layout (as in FORTRAN, C/C++), the knowledge of array access patterns is crucial to obtain the bank access stride information. For vector processors and multimedia/graphics accelerators, bank access efficiency directly depends on 1D/2D array access patterns.

Two aspects determine array access patterns: array definitions and array subindexing functions. Determining how to extract array access patterns from source code and properly represent them is the first step. The polyhedral model uses matrices to represent the sub-indexing functions that are based on loop iterator variables [18]. Each sub-indexing function is linear combinations of iterator variables. Sung et al uses a similar way to represent array sub-indexing for GPU parallel thread access [43]. In this work, we continue to use their representation for sub-indexing functions.

Commonly used array access patterns in linear algebra applications include row, column, backward/forward diagonal, and block. These patterns are generally considered when designing interleaved memory for vector processors. For multimedia processors/accelerators, 2D access patterns are more common. They include different block based patterns [25, 42] and even regular sampling patterns [42]. Please refer Figure 2.2, Figure 2.3, and Figure 2.4.

Figure 2.2 Typical access patterns

Figure 2.3 Memory access by 1D warp

Figure 2.4 Memory access by 2D Warp

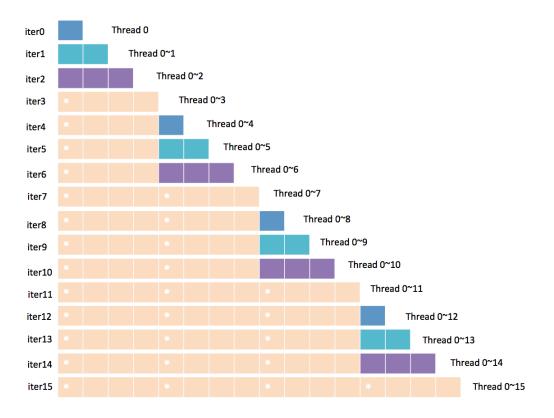

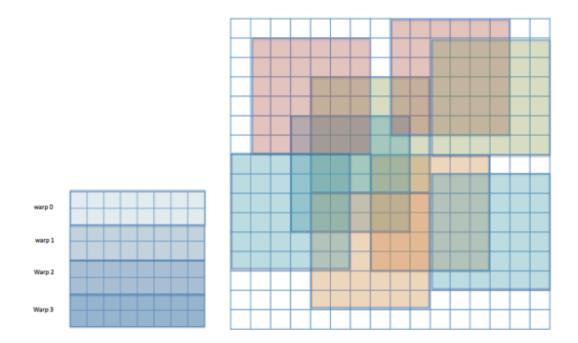

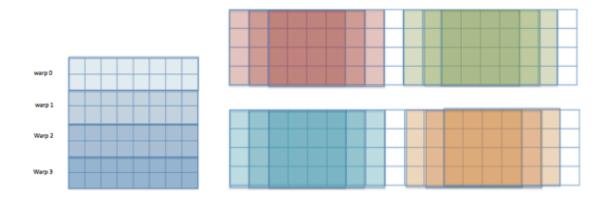

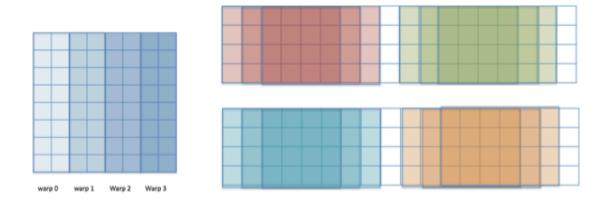

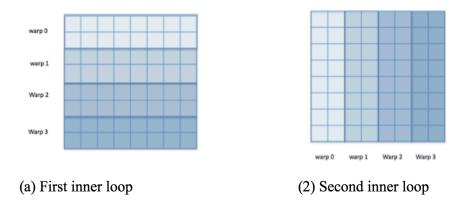

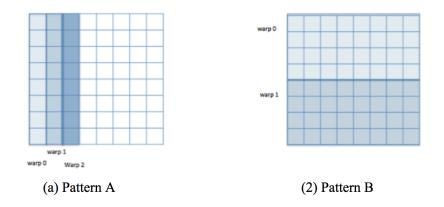

The CUDA GPU programming model supports parallel memory access by executing one parallel memory instruction for a group of threads. Concurrent threads can be organized in 1D to 3D grids. It makes thread execution structure match the array dimension and the code becomes easier to be manipulated. Beneath this structured parallel execution model, GPU hardware executes instructions in units of warps, which are a thread array of 16 or 32 threads. Each thread block is composed of one or more warps. Threads in one thread block are linearly mapped to a sequence of warps, and each warp could be mapping to a 1D to 3D array of threads. Figure 2.3 presents two basic cases of using thread block to visit arrays. Fig. 2.3 (a) is a 1D thread block composed of 3 warps; when it visits a 1D array, each warp visits a 1D sub-array. Fig 2.3 (b) is an example for 2D warps. Each warp visits a  $2 \times 4$  block in the 2D array. From these basic examples, it can be seen that for GPUs, the thread grid structure is another factor that impacts data access patterns.

The CUDA GPU memory system is composed of different types of memory. Various constraints are imposed on the programmer to obtain high memory access efficiency. GPU global memory is fixed length (such as 32-Byte or 128-Byte) vector access depending on cache or related configurations. These memory operations could achieve maximum bandwidth when the access patterns guarantee that a sequence of threads access consecutive data elements and they are properly aligned. Baskaran et al [18] presented code transforms based on Polyhedral models. Che et al [53] designed a set of APIs to reorganize the data to improve global memory access efficiency. Extra GPU kernels are used for data layout transform and memory access patterns are changed accordingly.

As previously mentioned, GPU shared memory bank conflict is a primary concern when designing GPU kernels and their data access patterns. How to avoid shared memory bank conflict is left to programmers to solve. To achieve better access efficiency, array access patterns need to be carefully designed to avoid or reduce bank conflict. Baskaran et al [18] presented a heuristic searching method to deal with this issue. It searches for the conflict function best padding width by examining bank with the gcd(*stride*, *bank\_number*). However, this solution is not enough. First of all, it only considers the basic conventional low-order mapping function. For mappings that support dynamic memory bank access, it requires a broader analysis scheme to estimate the bank conflict degree. Secondly, this solution cannot support other memory access patterns/strides besides constant 1D stride. This is not practical regarding the various access patterns used in GPU kernels [54].

Based on analysis of single parallel memory access patterns, the correlation information among consecutive parallel accesses can also be used to achieve better efficiency. In [42], after presenting the design of the bank-mapping scheme, Lentaris and Reisis also presented the definition of "MacroSquares", the area visited by a sequence of correlated memory accesses. He demonstrated that the proposed schemes work well for such a group-access pattern.

Beside memory access optimization for each GPU memory type, Jiang et al [54] proposed a scheme to choose among different memory types according to memory access pattern analysis.

# 2.4 Padding Transformations

Array padding is a commonly used method for data layout transformation. It is very useful for dense numerical algorithms such as linear algebra and iterative solvers. Padding is also a common optimization scheme adopted by compilers[55]. By adding unused spaces, the related memory access patterns are changed to improve memory visit efficiency. There are two types of padding: inter-padding and intra-padding [20]. Interpadding adds dummy space between array variables; intra-padding inserts unused spaces inside one array.

Padding is commonly used for improving memory usage efficiency. Cache/TLB conflict is one of the problems that array padding can be applied to [56-62]. By adding extra blank space at proper locations, the cache conflict due to memory accesses can be reduced. False sharing is another example. By adding padding, data near each other that cause the false sharing can be separated [63, 64]. Array padding is also an important method to deal with the memory bank conflict problem [26, 47-49]. By adding padding in one of the inner array dimensions, the memory access stride is changed, which has direct impact on concurrent bank access patterns. Taking conventional bank mapping as an example, when padding is added to make a stride change from an even number to an odd one, gcd(*stride,bank\_number*) equals to 1 and conflicts are eliminated. By adding padding before an array definition, it changes the offset of the array's base address. For

some bank mapping functions such as the ones supported by GPU dynamic bank access scheme, changing this offset might impact the bank conflict degree.

Array padding is easy to apply and it is practically efficient. In addition, unlike some other data transform methods, padding normally involves no extra source code transformation for array sub-indexing functions. Although it consumes some extra spaces, many problems can be solved with a relatively modest padding. Padding is generally used combined with other optimization schemes such as tiling [65-69], and prefetching [20, 70]. For example, Rivera et al presented a combination solution, which use tiling and padding to improve memory efficiency for some 3D iterative solvers [65]. In [68], a method combining intra-padding and tiling is used and proved to be efficient for matrix multiply. In [70] padding is used to avoid or reduce prefetching conflict.

Various automatic padding solutions are proposed for different purposes. Many of them are based on problem modeling [49, 57, 58, 65, 67], and then use heuristic methods [20, 71] or other searching methods [47, 60, 69] to find optimized solutions [66]. In [71] the author raised concerns with the relation between applying intra and inter padding; their solution always applies intra-padding prior to inter-padding.

Array padding is also commonly used for GPU program optimization. The two main purposes include improving global memory efficiency and reducing shared memory bank conflict. Based on the coarse-access principle for global memory access, padding could be used to transform data layout in global memory and coarse global memory access requests [72, 73]. Based on the GPU shared memory bank organization knowledge, small amounts of padding could be used to change memory access stride and in turn reduce or eliminate potential bank conflict [18, 19].

A compiler auto-padding solution for shared memory is proposed in [18]. A heuristic searching algorithm is used to search for a proper padding. For each candidate padding size, gcd(*stride,bank\_number*) is evaluated to get the conflict degree for each parallel array access. The padding size that results in the least conflict number will be used. Some other auto-padding schemes are developed for application-domain related optimizations. Jaeger et al [50] proposed an auto-padding scheme for stencil calculations. This work extends the usual padding into a multi-padding method, which uses non-

uniform but periodic padding at different locations. This extended padding method is shown to be efficient for alignment issues on different CPU/GPU architectures.

# 2.5 Summary

This chapter presents three areas of previous research that are related to this dissertation. First of all, since this work target GPU shared memory bank conflict, we studied the prior work on solving interleaved memory bank conflict solutions. Secondly, we investigated common 1D and 2D memory access patterns, which is widely studied for automatic optimization techniques. In order to transform source code to obtain better efficiency, the proposed tool needs to be able to recognize common patterns and find proper data layout solution. Finally, we studied the prior work on padding. Although it is a basic and simple optimization, it is commonly used for data layout transform, especially for GPU shared memory optimizations. The proposed tool uses padding as one of the main data layout transformation methods.

### CHAPTER 3 PROPOSED APPROACH

# 3.1 Background and Motivation

CUDA shared memory is software manageable on-chip storage, it is faster than device memory and its size is limited. Shared memory is commonly used for the following purposes: (1). Caching data to improve temporal locality. For the data which are visited multiple times, they can be cached in shared memory to avoid the long latency of global memory access. (2). Hosting data shared among threads of one thread block. An example is producer-consumer warps inside one thread block; they can communicate through shared memory. (3). Temporary storage for improving global memory access efficiency. In the kernel of matrix transpose, by using shared memory, access pattern of global memory can be changed to unit-stride row-major access. This helps to improve the performance by optimizing global memory access efficiency.

Bank conflict is a primary concern when using CUDA shared memory. Programmers are responsible to reduce or avoid bank conflict given the bank organization information [1, 2]. In earlier generations, CUDA shared memory used conventional low-order mapping; the value of bank number (denoted as *bank\_num*) equals to the vector access length (denoted as vec\_length). Programmer could use gcd(stride, bank\_num) to calculate the bank conflict degree and use array padding or other data layout transformation to avoid bank conflicts. However, the NVIDIA Kepler GPUs enables dynamic bank access mode, which is designed to improve efficiency for different bit-width accesses. This makes the bank conflict issue more complex for programmers. Traditional analysis methods of conventional mapping are not enough to solve the bank conflict problem for new bank access modes. Generally it is not obvious to understand how data layout causes bank conflicts; people just try different padding sizes or choose different mapping access bit-width settings. On the other hand, shared memory space is limited. When changing data layout to solve the bank conflict issue, the space constraint needs to be considered. Otherwise, device occupancy might decrease and performance might drop significantly. Based these observations, we believe more effort should be invested to reduce the difficulty of improving shared memory access efficiency.

This dissertation studies bank conflict issues of CUDA shared memory that supports dynamic bank access. Based on a generalized description of the bank organization and its access policy, the bank conflict analysis method is presented. Given bank conflict estimation results, a heuristic perimeter optimization algorithm is presented to find an efficient data layout solution. The first dimension of the searching space is bank mapping function options provided by the programming model; the second dimension is intravariable padding solutions; and the third one is the storage sequence of variables and potential inter-variable padding solutions. The heuristic perimeter optimization method looks for optimal or sub-optimal solution with the following two questions: (1). Does it reduce the overall bank conflict of one kernel? (2). How much extra space is needed? Does it exceed the space limitations?

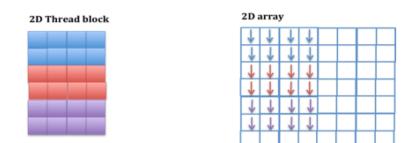

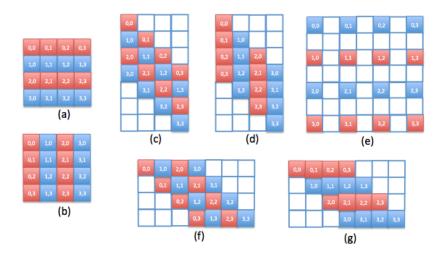

Figure 3.1 presents the relation between this work and related research areas. First of all, it is a project dealing with bank conflict issues of interleaved memory. It targets CUDA dynamic bank access mapping functions. In future, it could be used for other interleaved memory types with similar features. Secondly, it is based on memory access pattern knowledge of different data layouts. Thirdly, it tries to find an efficient solution based on intra-padding, inter-padding, and bank mapping function configuration. The goal is to make an automatic software solution that works at the programming level, and it realizes optimization through source code transformation.

Figure 3.1 The relations of this project and related research areas

# **3.2 Project Assumptions**

The following list is assumptions of this project:

(1). This is a static analysis.

(2). The bank number equals to the vector access length and its value is power-oftwo.

(3). The target application uses dense memory access only. Indirect accesses (such as those used in sparse matrix and irregular mesh processing) are not included.

(4). This project targets C/C++ CUDA programming. By default array data is stored in row-major style. Any array used in this work is based on row-major data layout.

(5). Some typical 2D patterns are supported, but not all. For loops, the assumption is that the consecutive memory access requests have similar patterns.

(6). Based on the situation that programmers are responsible for solving bank conflict, here we don't assume the existence of any particular shared memory bank conflict related compiler optimizations.

(7). When an auto transformation tool looks for an optimal/sub-optimal solution, it will consider using less extra space, but it cannot guarantee that extra space chosen to be added will not cause decreasing device occupancy. To avoid such penalty, programmers should give a space limitation for each thread block.

(8). The current implementation targets at transforming C/C++ CUDA programs. Implementation for OpenCL can be added in similar way.

# 3.3 Project Framework

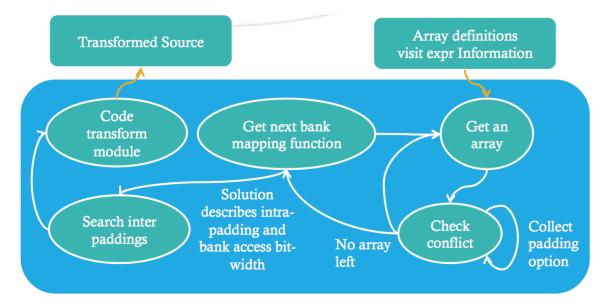

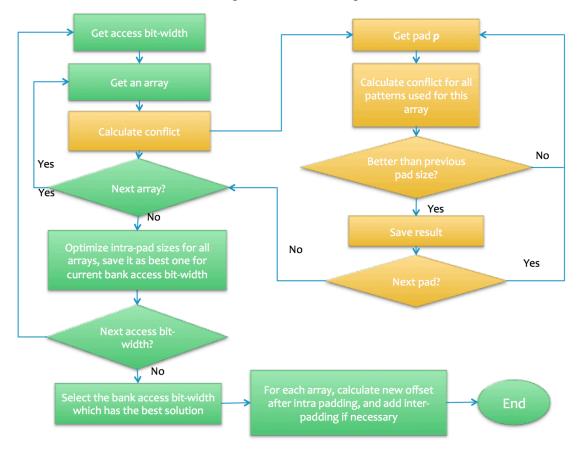

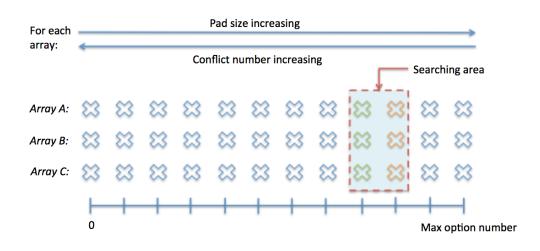

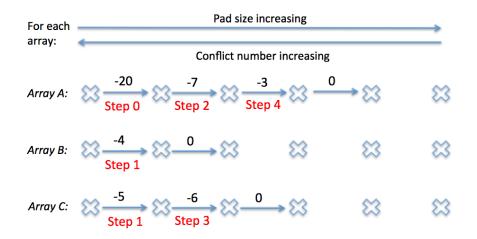

Figure 3.2 is the description of proposed approach. The work starts from a kernel source code and its memory access pattern description including: (1). Shared memory variable definitions; (2) Bank mapping functions defined by the programming model; (3) GPU thread block definitions; (4) array access stride; (5) other control information related to memory accesses. Basically, for different bank access bit-width settings, the tool analyzes the conflict replay number for each array, and then optimized the intrapadding size to obtain the optimal or sub-optimal solution. Among different bank access bit-width settings, the best option is the one that has the least conflict number and uses less memory. If the total conflict replay number is not zero, the tool looks for a proper inter-padding size for each array. Finally, according to the data layout solution, a source code transform is performed to modify the source code accordingly.

Figure 3.2 Framework of the project

# 3.4 Performance Improvement Expectation

The tool is designed to be able to improve GPU shared memory efficiency under following circumstances:

For a certain application kernel that uses 1D or 2D common shared memory access patterns, if its bank conflict problem can be eliminated or reduced by a combination optimization of (1) bank mapping function selection, (2) inter-padding, (3) intra-padding, then this tool can find an optimal or suboptimal solution automatically and transform data layout accordingly.

For an optimal/sub-optimal solution that can reduce the conflict degree from N to M, the memory access instruction replay number is reduced by  $\frac{N-M}{N} \times 100\%$ . It means that fewer cycles will be used for same purpose shared memory access. For applications that has bottleneck caused by shared memory bank conflicts, this transform may improve overall execution time.

# 3.5 Summary

This chapter introduces the background of GPU shared memory conflict issues, as well as the framework of this research. Due to the importance of shared memory access efficiency in GPU kernel performance tuning, and the difficulties of investigating the bank conflict for common access patterns, we made this effort to achieve automatic bank conflict optimization. The proposed work performs automatic source code transformation to optimize the data layout. This work includes a static bank conflict analysis and a heuristic parameter optimization method to find optimal or sub-optimal solutions.

### CHAPTER 4 SINGLE VECTOR ACCESS BANK CONFLICT

This chapter analyzes the bank conflict of single vector (warp) access. Firstly, the bank mapping functions are introduced, and the impacts of inter-padding, intra-padding, and bank access bit-width on bank conflict are presented. Then the bank conflict analysis module is designed to estimate the degree of 1D stride and 2D stride access patterns. The work in this chapter is the core in the proposed framework. Any bank conflict optimization task will finally be divided into sub-tasks of single vector conflict analysis.

## 4.1 Bank Mapping Function Descriptions

Based on bank mapping functions supported for current commercial GPU shared memory, we define a generalized description. N is the bank access mapping width in bytes, M is the instruction access data type size in bytes, and W is the layer width size of one bank in bytes. We call N the N-Byte mode, and M the M-Byte element. To describe the target problem we add the following constrains:

- 1. Values of M, N, and W are power-of-two.

- 2.  $4 \le M \le W, 4 \le N \le W$

- 3. W is constant in one system

4.

$$vec\_length >> \frac{W}{M}$$

There are following four different mapping functions as following:

- <u>Case One</u>: M = N and M < W. M = N means that the instruction access bit-width matches the bank mapping access bit-width. M < W means that this instruction access bit-width is smaller than the size of one layer of one bank. An example is M = N = 4, and W = 8. In this dissertation we call it case row-major mapping.</li>

- <u>Case Two</u>: M = N = W. M = N means that the instruction access bit-width matches the bank mapping access bit-width. M = W means that this instruction access bit-width equals to the size of one layer of one bank. An example is M = N = 8, W = 8.

- <u>Case Three</u>: M>N, M=W. M>N means that the instruction access bit-width is larger than the bank mapping access bit-width configuration. M=W means that the instruction access bit-width equals to the size of one layer of one bank. An example is N=4, M=W=8.

- <u>Case Four</u>: M<N, N=W. M<N means that the instruction access bit-width is smaller than the bank mapping access bit-width. N=W means that the bank access bit-width equals to the size of one layer of one bank. An example is M=4, N=W=8. This case is called column-major mapping.

Table 4.1 describes features of these four bank-mapping functions. When we describe the stride analysis, following definitions are used:

- *vector (or warp)*: execution unit of parallel memory access;

- *vector length*: the element number visited by each vector (warp) access;

- *offset*: the memory offset of the first element visited by a single vector access.

- stride family: a stride can be described as stride=σ×2<sup>e</sup> (σ is an odd, and, e∈Z). For all strides that have same e, they belong to the same stride family. For example, stride = {2,4,6,10,14,...} is the stride family that has e = 2.

- layer: One layer of a bank is a unit of space that multiple simultaneous accesses of it will cause no conflict. For example, for a layer size of 8B, the access of the upper 4B and the access of the lower 4B cause no conflict.

- *row*: For case one, two, and three, a layer of a bank has  $R = \frac{W}{M}$  rows. For example, for a layer size of 8B and a bank mapping access width of 4B, there are two rows in each layer. For case four, a layer of a bank has  $R = \frac{W}{M}$  rows.

Figure 4.1 is array data mapping examples for these bank mapping functions (Bank number is 4, W=8). This literature focuses on the **row-major data mapping (case one)** and **column-major data mapping (case four)**. Case-three is similar to row-major mapping function; case-two is conventional low-order bank mapping function.

| A[0]         | A[1] | A[2] | A[3]         | A[0] | A[1] | A[2] | A[3] |

|--------------|------|------|--------------|------|------|------|------|

| A[4]         | A[5] | A[6] | A[7]         |      |      |      |      |

| (1) N=M=4    |      |      | (2) N=M=8    |      |      |      |      |

| A[0] A[1]    |      | A[0] | A[2]         | A[4] | A[6] |      |      |

| A[2] A[3]    |      | A[1] | A[3]         | A[5] | A[7] |      |      |

| (3) N=4, M=8 |      |      | (4) N=8, M=4 |      |      |      |      |

Figure 4.1 1D Array data mapping for different mapping functions.

| Case  | Example Architecture | Bank | N  | М  | W  |

|-------|----------------------|------|----|----|----|

|       |                      | Num  |    |    |    |

| One   | NVIDIA Kepler        | 32   | 4B | 4B | 8B |

| Two   | NVIDIA Tesla         | 16   | 4B | 4B | 4B |

|       | NVIDIA Fermi         | 16   | 4B | 4B | 4B |

|       | NVIDIA Kepler        | 32   | 8B | 8B | 8B |

| Three | NVIDIA Kepler        | 32   | 4B | 8B | 8B |

| Four  | NVIDIA Kepler        | 32   | 8B | 4B | 8B |

Table 4.1 Summary of features of bank mapping functions

## 4.2 Data Layout Transform and Bank Conflict

In this section some basic experiments is used to exam the impact of data layout on bank conflict degree. The platform information is as following:

- GPU device: Tesla K20c,

- Shared memory:

- Bank number is 32;

- W=8B.

- Warp size: 32 threads.

- Compute capability: 3.5

- Programming model: CUDA 5.0

- Profiler: NVIDIA NVVP, release 5.0

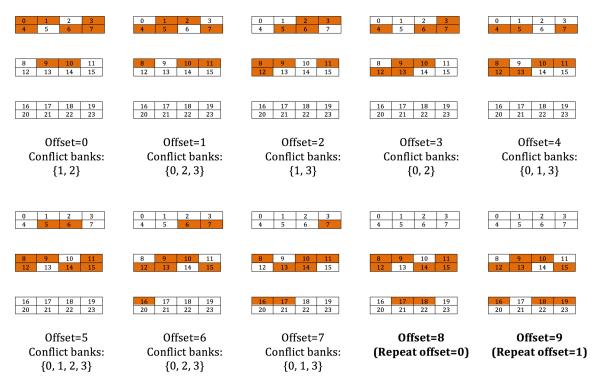

### 4.2.1 Inter-padding

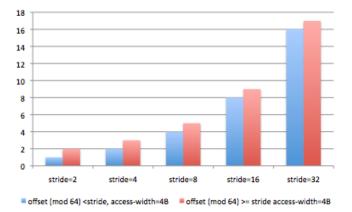

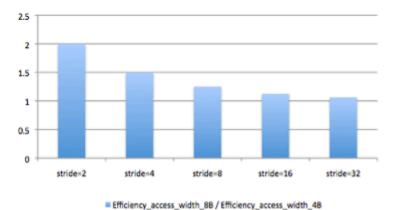

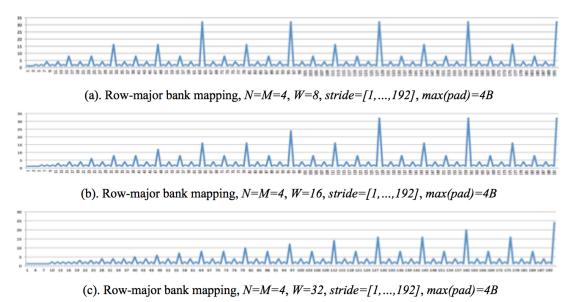

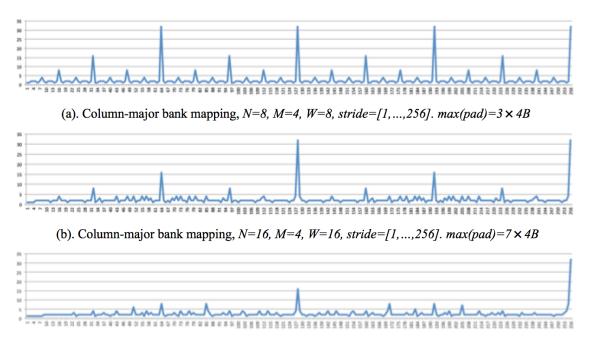

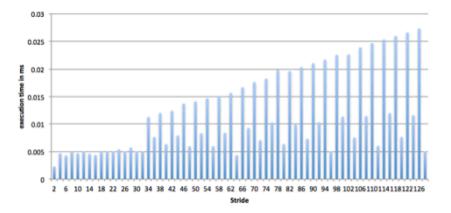

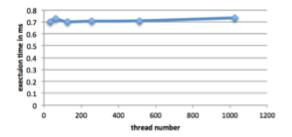

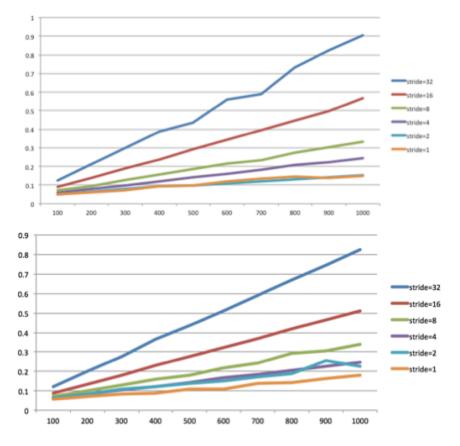

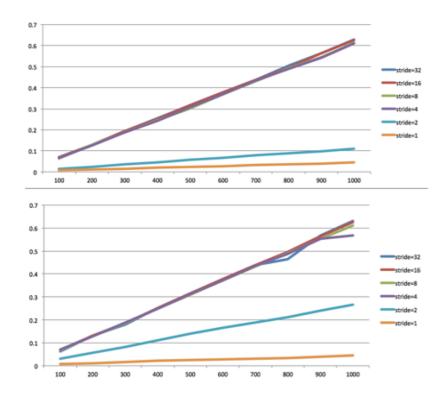

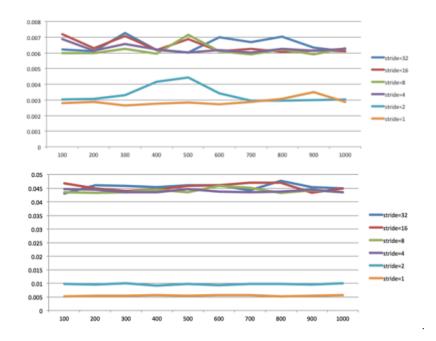

Inter-padding is a method used to change the memory access offset. This experiment shows the impact of access offset on bank conflict degree for the row-major data mapping function. Basically, the program reads shared memory by *stride* =  $2^e$ . When the offset varies, the conflict number changes. In the example code in Figure 4.2, by inserting dummy variable of different sizes, we can change the offset. Figure 4.3 shows the impact of offset for different strides: the effect of changing offset is "+0" or "+1" to the existing conflict degree. It means that for larger strides, the impact of offset is smaller. Figure 4.4 compares the offset is larger than 3, column major data mapping scheme is better than row-major data mapping scheme. Similarly, for the column-major data mapping function, the offset also could change the conflict degree. The detail will be discussed in chapter 6.

\_\_shared\_\_DATATYPE dummy[N]; \_\_shared\_\_DATATYPE A[SIZE]; Array\_in\_global[threadIdx.x] = A[threadIdx.x \* stride]; \_\_syncthreads();

Figure 4.2 Sample code

Figure 4.3 Conflict degree of different offsets for different stride values

Figure 4.4 Impact of offset for different access bit-width setting

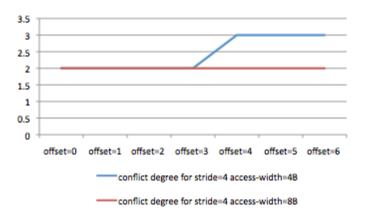

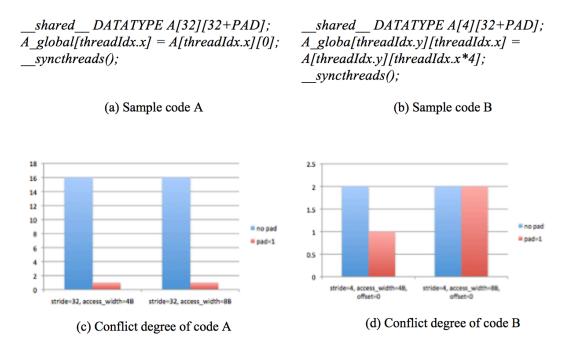

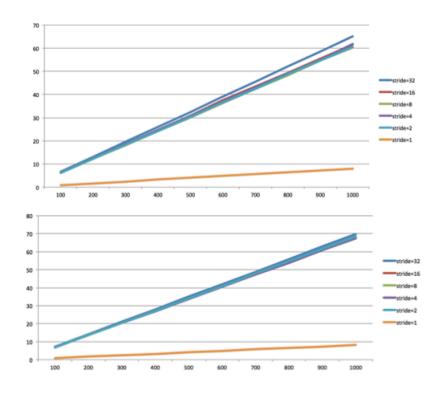

### 4.2.2 Intra-padding

This experiment exams the impact of array intra-padding. When the padding varies, the conflict degree changes. For example code in Figure 4.5 (a) and (b), we change the value of the macro PAD and check the conflict degree Figure 4.5 (c) and (d) shows the impact of intra padding on bank conflict degree.

Figure 4.5 Impact of intra-padding on bank conflict numbers

### 4.2.3 Bank Access Bit-width

This experiment shows the impact of bank access bit-width on bank conflict degree. When access bit-width changes, the conflict degree changes. In the example code in Figure 4.6 (a), we change bit-width through the API provided by the CUDA programming toolkits. Figure 4.6 (b) shows the difference of the conflict degree when offset=32B. Figure 4.4 also shows the difference when *offset* > 3 and *stride*  $\ge$  4 : when N = 8 it has better efficiency.

```

Host code:

cudaDeviceSetSharedMemConfig(cudaSharedMemBankSizeEightByte)

or

cudaDeviceSetSharedMemConfig(cudaSharedMemBankSizeFourByte)

Kernel code:

_______shared____DATATYPE dummy[N];

______shared____DATATYPE A[SIZE];

A__global[threadIdx.x] = A[threadIdx.x*stride];

______syncthreads();

```

(b) Rate of conflict degrees between 4B and 8B bank access modes

Figure 4.6 Impact of bank access width on bank conflict degree

## 4.3 Single Vector Bank Conflict Analysis

### 4.3.1 1D Access Pattern and Bank Conflict Analysis

Table 4.2 describes the features of bank conflict problem for **row-major bank mapping function** and **column major bank mapping function**. Basically, the bank conflict analysis module realizes following function:

bank\_conflict\_degree = func(bank\_num, W, N, M, stride, offset)

Based on the input parameters, the bank mapping type is determined, and the task is assigned to the routine that perform the analysis. Detailed analysis description of each type can be found in appendix A-1.

| Table 4.2 Summary o | of features | of bank | conflict problem | n |

|---------------------|-------------|---------|------------------|---|

|---------------------|-------------|---------|------------------|---|

| Туре       | Conflict analysis features                                                          |  |  |  |

|------------|-------------------------------------------------------------------------------------|--|--|--|

| Row-major  | Analysis process is based on gcd(stride, bank_number). However, since one layer     |  |  |  |

| data       | of all banks has multiple rows, only accesses to different layers cause bank        |  |  |  |

| mapping    | conflict. The analysis routine take offset and result of gcd(stride, bank_number)   |  |  |  |

|            | to calculate the bank conflict number.                                              |  |  |  |

| Column-    | Since each layer of all banks has multiple rows, and data are mapped in column      |  |  |  |

| major data | major direction, both odd stride and even stride could cause bank conflict. A       |  |  |  |

| mapping    | routine is designed for odd stride bank conflict analysis. Even stride analysis can |  |  |  |

|            | be transformed to either odd stride problem or conventional bank mapping            |  |  |  |

|            | problem.                                                                            |  |  |  |

### 4.3.2 2D Access Pattern and Bank Conflict Analysis

For 2D parallel memory access, we can describe a parallel execution unit by two types: a 1D vector, or a 2D rectangular grid (Figure 4.7 (a)). When such a vector accesses data in an array, we describe access pattern as:

< stride \_x, repeat \_x, stride \_y, repeat \_y >

(a) 1D vector and 2D grid (b) Basic memory access patterns

Figure 4.7 shape of parallel memory access unit and base memory access patterns

By defining an affine transform matrix in Homogeneous Coordinates, we can get the transformed 2D access patterns based on the basic access pattern in Figure 4.7 (b). We describe this transform matrix T as:

$$v' = Tv = \begin{pmatrix} a_{11} & a_{12} & c_1 \\ a_{21} & a_{22} & c_2 \\ 0 & 0 & 1 \end{pmatrix} \begin{pmatrix} threadIdx \, x \\ threadIdx \, y \\ 1 \end{pmatrix}$$

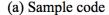

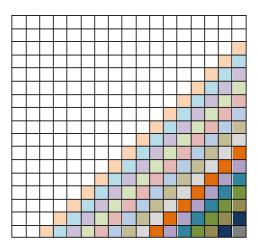

When the width of the 2D memory access execution unit is less than *vec\_legnth*, the 2D stride pattern can be obtained from the functions in Table 4.3. In these functions, the *blockDim.x* denotes the width of execution unit; width denotes the width of 2D array. Figure 4.8 shows some examples of the transformed access patterns.

Table 4.3 2D stride pattern calculation

| stride_x                               | repeat_x   | stride_y                               | repeat_y                 |

|----------------------------------------|------------|----------------------------------------|--------------------------|

| $a_{21} \times array \_width + a_{11}$ | blockDim.x | $a_{22} \times array \_width + a_{12}$ | vec_length<br>blockDim.x |

Figure 4.8 Examples of the base 2D access pattern transformation

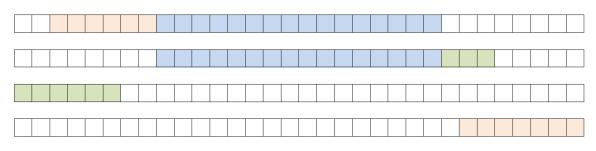

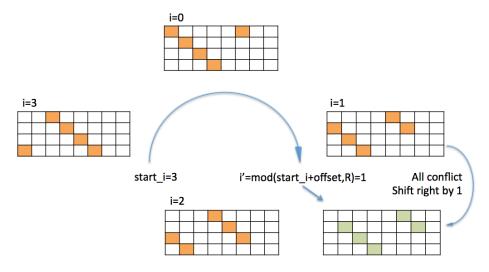

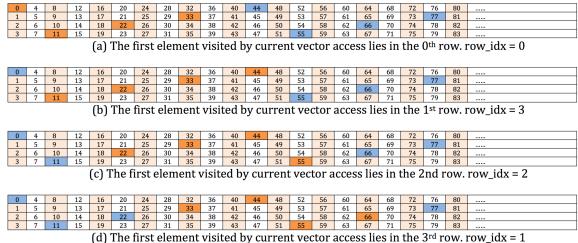

When we shift the offset of current parallel access, an observation is that the bank mapping of all visited elements repeat after a certain number of steps. For example, when row-major mapping function is in use, for

$$offset_{new} = offset_{original} + \frac{W \times bank \_num}{M}$$

it has

$$conflict_{new} = conflict_{original}$$

This means that we can firstly calculate bank conflict for a small and fixed number of offset values, and then for other offsets, get the conflict degree by mapping it to a known offset value. We call this small group as *base\_set*. In many GPU kernels, one parallel memory operation is executed for many times with different offsets. By computing the conflict for a small *base\_set*, this method can obtain the overall conflict in a limited time period which is independent of vector access number. For detail information about 2D bank conflict analysis, please refer appendix A-3.

## **4.4 Algorithm Analysis**

The single vector analysis is the basic component of the proposed framework. It works at the center of this work in that other modules are built upon it. This section introduces the algorithms used to realize single vector analysis; their time complexities are discussed as well.

## 4.4.1 1D Analysis Algorithm

#### **Row-major Bank Mapping Function**

For row-major bank mapping function, when stride is odd, for any W, N, and M, there is no bank conflict. For even strides, we divide them into two categories: (1) stride is power-of-two, (2) Other even stride.

When stride is power-of-two, the algorithm (algorithm 4.1) uses the result of gcd(*stride*, *bank\_num*) and the vector access offset to calculate the conflict degree. Since

the time complexity of gcd(*stride*, *bank\_num*) is *O*(*stride*), this function's time complexity is also *O*(*stride*). Basically, (1) when stride is larger than the element number that can be stored by one layer of all banks, all visited elements lie in different layers of the same bank, and any pair of them has conflict. (2) Otherwise, if the stride can be divided by *bank\_num*, all visit sites lines in same bank of one or multiple layers. Based on the value of offset, the conflict degree can be deduced from the result of gcd(*stride*, *bank\_num*). (3). Otherwise, it means that the *bank\_num* can be divided by stride, the result of gcd(*stride*, *bank\_num*) and the offset is used to calculate the conflict degree. Figure 4.9 describes this in details.

Given  $S = 2^s$ ,  $bank_num = 2^b$ , and  $row_num_per_layer = \frac{W}{N} = 2^e$ , when  $S \ge 2^b \times 2^r = 2^{b+r}$ . It has  $\frac{S}{2^{b+r}} = 2^{s-b-r} \ge 1$ . So each layer hosts at most one visited site. So the conflict degree is a constant which is as same as *vec\_length*.  $S < 2^b \times 2^r = 2^{b+r}$ . There are two possibilities:  $2^s < 2^b$ . Which means s < b. So the visited site number in each row is  $2^{b-s}$ .  $2^s \ge 2^b$ . Which means  $s \ge b$ . So all visited sites lie in the same bank, and every  $2^{s-b}$  rows have one visited site. In addition,  $2^{s-b}$  can be divided by  $2^r$ .

#### Figure 4.9 for power-of-two stride

When stride is other even numbers, the time complexity is also O(stride). For an even stride in stride family  $\sigma \times 2^e$ , the visited sites can be divided into  $2^e$  groups, each groups occupies  $\sigma$  rows. For the i<sup>th</sup> row of all groups, they visit same banks. So there must be conflict if not all of them lie in same layer. Inside each group, there is no conflict possibility. Based on such observation, the task becomes to check the conflict among i<sup>th</sup> rows of all groups (algorithm 4.2).

Algorithm 4.1 func\_row\_major\_power\_of\_two\_stride Input: bank\_num, W, N, M, stride, offset Output: res -- bank conflict degree.

gcd\_res = gcd(stride, bank\_num); R = W/N; res=1;

```

layer_size = bank_num * W;

vec_length = bank_num;

offset = offset % layer_size; //calculate offset in one layer.

If (stride >= bank_num * R)

res = vec_length;

else

If(stride % bank_num == 0)

res = (gcd_res*(stride/bank_num) + (R-1)) / R;

else

res = (gcd_res + (R-1)) / R;

end if

if(offset_impact==true)

res += 1;

end if

end if

end if

```

Algorithm 4.2 func row major other even stride Input: bank num, W, N, M, stride, offset *Output: res -- bank conflict degree.* //----gcd res = gcd(stride, bank num);R = W/N; res=1; *layer size* = *bank num* \* *W*; vec length = bank num; offset = offset % layer size; //calculate offset in one layer. *tau = tau(stride); //calculate stride family parameter tau e*=*e*(*stride*); //*calculate stride family parameter e*.  $if(2^{e} \ge bank_num)$ *if(stride > W\*bank num/M)* res = bank num; else res = ceil(offset/M + (vec length-1) \* stride + 1, bank num \* W/M) / (bank num \* W/M);end if end if *for row I in {0,..,tau-1}* for group in {0,..., 2^e-1} *if current layer(group)* != *previous layer(group) conflict* = *true*; *res*++; end if end for end for

#### **Column-major Bank Mapping Function**

For this bank mapping function, no matter stride is odd or even, there could be potential conflict, and we need to calculate conflict degree (algorithm 4.3). The time complexity of this method is  $O(R \times vec\_length)$ . Compares to enumerating every visit site of one vector access, this time complexity is worse because the later one has  $O(vec\_length)$ . However, it doesn't mean that this method is not helpful. Actually, it gives useful clues to take short cut for some cases. One important conclusion based on this method is about current commercial GPU shared memory. In appendix A, it is approved that the conflict is always 2-way when R = 2, with  $R = \frac{W}{M}$ . For other  $R \neq 1$ , the condition about *layer\_scope* could terminate the loop and help to avoid unnecessary calculations for non-valid pairs.

Algorithm 4.3 func column major odd stride Input: bank num, W, N, M, stride, offset *Output: res -- bank conflict degree.* //-----For vector visit start from r in 0 to R-1 //initialize bank layer info *For i=0 to bank num-1 std::pair<unsigned, std::set<unsigned int> > curr pair; curr pair.first* = *i*; *curr pair.second.clear()*; bank layer info.push back(curr pair); Endfor //.... //step 1: row idx = (offset % W) / M;//.... //step 2: For i = 0 to R-1 *calculate row offset[i]* Endfor For i = 0 to R-1 calculate imm col offset[i] Endfor //.... //step 3: For i = 0 to R-1 calculate row scope num[i]; Endfor //....

//step 4 (CASE-A): check every row-pair of CASE-A For i=0 to R-2For j=i+1 to R-1//For each pair of rows, check existence of conflicts. *bool conflict = false;* For diff\_y\_x = 0 to vec length/R-1calculate dist: the offset difference between visit x and visit y If ((dist > 0) && ((dist % bank num) == 0))*layer scope* = *dist* / *bank num;* If (layer scope <= (row scope num[i] - 1)) diff res = diff x v; *conflict = true;* break; Endif Endif Endfor If (conflict) For each pair of x and y that has difference of diff res calculate bank id; calculate layer y; calculate layer x; save these conflict information to bamk info[bank id]; Endfor Endif Endfor

Endfor

//.....//step 4 (CASE-B): check every row-pair of CASE-B

```

For i=0 to R-2

For j=i+1 to R-1

//For each pair of rows, check existence of conflicts.

bool conflict = false;

For diff y = 0 to vec length/R

{

calculate dist: the offset difference between visit x and visit y

If ((dist > 0) \&\& ((dist \% bank num) == 0))

int layer scope = dist / bank num;

If (layer scope <= (row scope num[j] - 1))

diff res = diff y x;

conflict = true;

break;

Endif

Endif

Endfor

If(conflict)

For each pair of x and y that has difference of diff res,

```

calculate bank id;

```

calculate layer_y;

calculate layer_x;

save these conflict information to bamk_info[bank_id];

Endfor

Endfor

For I in 0 to bank_num-1

If bank[i].layer_num > max;

Max = bank_info[i].layer_num;

Endif

Endfor

Endfor

```

For even stride, the problem can be transformed either to odd stride problem or directly to conventional bank access problem. Then the time complexity is either as same as the one for odd stride problem, or the one for conventional bank conflict problem. The table A-1-5 describes the rules of problem transformation.

### 4.4.2 2D Access Analysis Algorithm

When array is visited through a 2D stride, there are two cases: (1). Each warp accesses array in 2D pattern; (2). Each warp accesses array in 1D pattern. A simple example of the first case is 8x4 access by a warp of 32 threads. It means that for the first stride the repeat times is 8 and for the second stride it is 4. For the second case, even the access of a whole thread block is 2D, but since the repeat time of the first stride can be divided by vector length, then the problem can be transferred to a 1D cases for each warp. The algorithm 4.4 is the bank conflict calculation for row-major bank mapping. For column-major bank mapping function, the algorithm is similar except that different functions are used to calculate the bank indices and layer indices. This is a simple and straightforward solution. At the beginning, an array of bank information are defined and initialized, it is used to store the bank access information. Then, for each visited element, calculate its bank index and its layer offset, and record the distinct layer indices of same bank. Finally, it goes through all banks and finds the bank that has maximum distinct layer number. This number is the bank conflict degree of the current single warp 2D access.

```

Algorithm 4.4 2D row major stride

Input: bank num, W, N, M, stride, offset

Output: res -- bank conflict degree.

//-----

For I in 0 to bank num-1

Initialize bank info [i]

Endfor

For I in 0 to rep y-1

For j in 0 to rep x-1

Calculate bank idx and layer idx based on row-major bank mapping function

Done.

Done.

For I in 0 to bank num-1

If bank[i].layer num > max;

Max = bank info[i].layer num;

Endif

Endfor

```

For this algorithm the time complexity is composed of three parts are:  $O(bank\_num)$ .  $O(vec\_length) O(bank\_num)$ . Since we assume  $vec\_length$  equals to  $bank\_num$ , the overall time complexity of this algorithm is  $O(bank\_num)$ .

## 4.5 Summary

In this chapter we describe the bank conflict problem of single vector access, and introduced the method for bank conflict analysis. Section 4.1 introduces the information of bank mapping functions. In section 4.2, experimental evidences are used to show the impact of data layout on bank access efficiency. By changing bank access bit-width, adding inter padding, or adding intra padding, the data layout transformations reduce or eliminate the bank conflict. In section 4.3 and 4.4, the conflict analysis algorithms are presented.

Based on this single vector analysis module, in chapter 5, the analysis method of single expression memory access is constructed; in chapter 6, a heuristic parameter optimization method is built to look for the optimal or sub-optimal data layer solution.

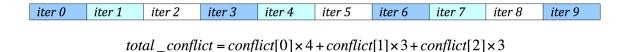

# CHAPTER 5 SINGLE EXPRESSION ACCESS BANK CONFLICT

In GPU programming model, one memory access expression drives concurrent threads to access a sequence of data in parallel. Normally these threads belong to multiple vectors/warps. In this chapter, we take single expression as a unit and analysis its bank conflict. Given an array access expression, the tool analyzes the overall bank conflict number of multiple warps that execute the memory operation. This work is based on the single vector bank conflict analysis presented in chapter 4. Since programmers determine the warp number, the ideal solution should be able to estimate conflict number and its time complexity shouldn't depend on the warp number. In this chapter, section 5.1 analyzes the bank conflict of basic array access expression. Section 5.2 analysis the "for" wrapped memory access, which is normally used to increase workload of each thread. Section 5.3 and 5.4 analyze "if" and "for-if" wrapped memory access ranges/patterns. Figure 5.1 presents the relations of these conflict analysis modules.

**Figure 5.1 Conflict Analysis Modules**

## 5.1 Basic Bank Conflict Analysis

### 5.1.1 1D Access Analysis and Algorithm

This section explains how to calculate the bank conflict number of single memory access expression when multiple warps are involved. This work is based on the algorithm for 1D single vector analysis presented in section 4.3. After the bank conflict of the first warp is obtained, the conflict result of other warps could be different from it in that their access offsets could be different. The memory access offset of the ith warp is:

$$offset[i] = offset[0] + i \times stride \times vec\_length \quad i = [1, 2, ..., warp\_num\_per\_block)$$

This formula shows that the offset of warp i is linear to the warp index i. In one layer of all banks, the in-layer offset is:

$$offset\_in\_layer[i] = mod(offset[i], bank\_num \times \frac{W}{M})$$