Doctoral Dissertations Graduate School

12-2014

# Lifetime Estimation of IGBTs in a Grid-connected STATCOM

Lakshmi Reddy Gopi Reddy University of Tennessee - Knoxville, lgopired@vols.utk.edu

#### Recommended Citation

Gopi Reddy, Lakshmi Reddy, "Lifetime Estimation of IGBTs in a Grid-connected STATCOM." PhD diss., University of Tennessee, 2014.

https://trace.tennessee.edu/utk\_graddiss/3130

This Dissertation is brought to you for free and open access by the Graduate School at Trace: Tennessee Research and Creative Exchange. It has been accepted for inclusion in Doctoral Dissertations by an authorized administrator of Trace: Tennessee Research and Creative Exchange. For more information, please contact trace@utk.edu.

#### To the Graduate Council:

I am submitting herewith a dissertation written by Lakshmi Reddy Gopi Reddy entitled "Lifetime Estimation of IGBTs in a Grid-connected STATCOM." I have examined the final electronic copy of this dissertation for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Doctor of Philosophy, with a major in Electrical Engineering.

Leon M. Tolbert, Major Professor

We have read this dissertation and recommend its acceptance:

Burak Ozpineci, Fei Wang, J. Wesley Hines

Accepted for the Council: Carolyn R. Hodges

Vice Provost and Dean of the Graduate School

(Original signatures are on file with official student records.)

## **Lifetime Estimation of IGBTs** in a Grid-connected STATCOM

A Dissertation Presented for the Doctor of Philosophy

Degree

The University of Tennessee, Knoxville

Lakshmi Reddy Gopi Reddy December 2014

## Copyright © 2014 by Lakshmi Reddy Gopi Reddy.

All rights reserved.

## Dedicated to my sources of inspiration, my parents

Mukunda Reddy GopiReddy

&

Swaroopa Reddy GopiReddy

#### **ACKNOWLEDGEMENTS**

I take this opportunity to express my sincere gratitude to my advisor Dr. Leon Tolbert for his guidance throughout this work. I am deeply indebted to him for his patience, guidance and encouragement. I would like to thank my supervisor at Oak Ridge National Laboratory, Dr. Burak Ozpineci who has been a great source of inspiration to me. His constructive suggestions all through this project have helped me have a better insight into analyzing research problems. I wish to extend my thanks to my committee members, Dr. Fred Wang and Dr. J. Wesley Hines, for their valuable comments and suggestions.

I would like to acknowledge Madhusudhan Chintavali, Dr. Zhingxing Liang from National Transportation Research Center, Michael Starke, and Muralidharan Govindarajan from Oak Ridge National Laboratory, for their time and helpful discussions about testing the IGBTs. I would like to offer my appreciation to Dr. Yan Xu, Tom Rizy, Phillip Iriminger, and Dr. Huijuan Li at Oak Ridge National Lab for helping me immensely in conducting experiments using the STATCOM setup at ORNL. I would like to thank Dr. Andy Wereszak and Dr. Kai Wang who helped me during the initial stages of the project to test single devices.

I express my thanks to all my colleagues and friends at the Power Electronics lab, Faete Filho, Sarina Adhikari, Lijun Hang, Xiaojie Shi, Zhiqiang Wang, Bo Liu, Jing Xue, Ben Guo, Mithat Kisacikoglu, Edward Jones, Kumaraguru Prabhakaran and many others for their friendly support through different periods of my study at UT. My special thanks to the staff of CURENT, Ms. Judy Evans, Mr. Adam Hardenbeck, and Mr. Erin Wills, who have always been helpful especially during conference travel. I would like to extend my grateful thanks Bob Martin, our Lab manager, in particular, with whose expert advice and assistance, the automatic experimental set up for my research was successfully set up and run with minimal intervention.

My friends at UT, Bharadwaj Venkatesan, Kaveri Thakur, Shilpa Sood, Gitika Shrivastav, Sarina Adhikari, Harika Tandra, and Sirisha Duvvuru have made my life at Knoxville memorable with their support and joyful company. My special thanks to them.

I am obliged to my parents, Mr. Mukunda Reddy and Ms. Swaroopa Reddy, for instilling in me the sense of following my passions that kept me grounded. I am eternally thankful to my family for their friendly advice, sacrifices, and above all, humor that have rescued me from peril more times than I can recall. Lastly, I am grateful to the almighty for everything.

#### **ABSTRACT**

Lifetime estimation of power semiconductor devices, and IGBT devices in particular, used in the power electronics integrated with power systems has gained technical importance in recent times with increased scope of distributed generation, renewable energy systems and FACTS. Since most of the common failures (wire bond and solder fatigue) are caused by thermo-mechanical stresses, the methodology of lifetime estimation starts with temperature estimation, cycle counting based on rainflow algorithm, and finally degradation calculation based on linear accumulation model.

Different number of RC cells for each packaging layer in the module for the thermal model, including the influence of encapsulant is proposed for temperature estimation of IGBTs in power modules. A modified rainflow algorithm with faster execution time and time dependent temperature calculation is introduced for cycle counting. Finally, the lifetime of the IGBT is estimated during STATCOM operation using real-time load profiles for power factor variation. For a power factor variation data for a building, the lifetime is estimated to be about 3 years. Similarly, a month long arc furnace load data is considered to compare the equivalent temperature based calculation to conventional tests. 4% more degradation is observed in the equivalent temperature based calculation than compared with conventional rainflow algorithm.

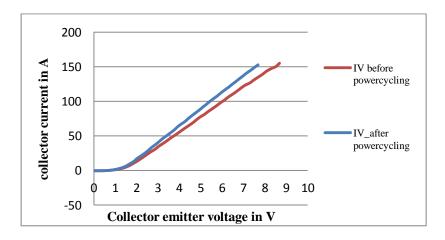

A simulation study on the operation parameter dependence on the stresses in a wire is considered to estimate lifetime from Finite Element Analysis (FEA) in COMSOL. Power cycling tests are conducted on two different modules (600 V, 50 A H-bridge module and a 1200 V, 150 A phase leg module) to determine failures and degradation testing for four months. The low power module was tested without any protection circuits and hence failed catastrophically. Wire melt-off or fusing failure was dominantly observed, following by dielectric based short circuit failure. The high power module was tested with protection circuits to prevent catastrophic damage for a maximum of 3.5 months. A maximum of 20%

degradation in static characteristics, with decreased on state resistance was observed in the modules. The degradation is attributed to increased junction temperature as the thermal resistance increases owing to solder fatigue.

## **Table of Contents**

| <b>CHA</b> | PT]                | ER I | INTRODUCTION                                                                   | 1  |

|------------|--------------------|------|--------------------------------------------------------------------------------|----|

| -          | 1.1                | Мот  | IVATION                                                                        | 6  |

|            | 1.2                | Con  | TRIBUTIONS                                                                     | 8  |

|            | 1.3                | Diss | ERTATION OUTLINE                                                               | 9  |

|            | <b>PT</b> ]<br>2.1 |      | I LITERATURE REVIEW                                                            |    |

| 2          | 2.2 T              | HERM | ial Models                                                                     | 11 |

|            | 2.                 | 2.1  | Deriving Cauer network from IGBT module dimensions:                            | 13 |

|            | 2.                 | 2.2  | Temperature Measurement                                                        | 14 |

| 2          | 2.3                | Life | TIME ESTIMATION: STRESS-STRAIN RELATIONSHIP TO LIFETIME AND RAINFLOW ALGORITHM | 24 |

|            | 2.                 | 3.1  | Introduction to Mechanical Stress-Strain                                       | 25 |

|            | 2.                 | 3.2  | Crack Growth Rate                                                              | 29 |

|            | 2.                 | 3.3  | Lifetime Models                                                                | 29 |

| 2          | 2.4                | CYC  | LE COUNTING                                                                    | 32 |

|            | 2.                 | 4.1  | Rainflow Algorithm                                                             | 32 |

|            | 2.                 | 4.2  | ASTM Standard (ASTM E1049-85)[73][74]                                          | 36 |

|            | 2.                 | 4.3  | Four Point Algorithm [79]                                                      | 36 |

|            | 2.                 | 4.4  | Graphical Rainflow [80]                                                        | 36 |

|            | 2.                 | 4.5  | Application to Equivalent Temperature-Time Dependent Fatigue Model             | 38 |

| 2          | 2.5                | Pow  | ER CYCLING TESTS                                                               | 40 |

|            | 2.                 | 5.1  | Design of Experiment: Planning Power Cycling Tests                             | 42 |

|            | 2.                 | 5.2  | Parameter Monitoring for Failure Detection                                     | 43 |

|            | 2.                 | 5.3  | Circuit Design                                                                 | 46 |

| 2.5.4 Choice of Operating Conditions                                                                         | 52         |

|--------------------------------------------------------------------------------------------------------------|------------|

| 2.6 Summary                                                                                                  | 53         |

| CHAPTER III ESTIMATING RELIABILITY OF POWER SEMICONDUCTO USING RC THERMAL MODEL, MODIFIED GRAPHICAL RAINFLOW |            |

| ALGORITHM, AND WIREBOND STRESS MODEL  3.1 INTRODUCTION                                                       |            |

|                                                                                                              |            |

| 3.2 RC THERMAL MODEL WITH ENCAPSULATION                                                                      | 56         |

| Methodology:                                                                                                 | 57         |

|                                                                                                              |            |

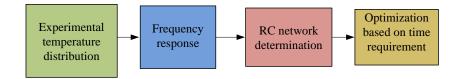

| 3.2.1 Experimental Temperature Distribution                                                                  | 57         |

| 3.2.2 Frequency Response                                                                                     | 58         |

| 3.2.3 RC Network Determination                                                                               | 59         |

|                                                                                                              |            |

| 3.2.4 Example to Demonstrate Thermal Model Development                                                       | 60         |

| 3.2.5 Encapsulant                                                                                            | 62         |

| 3.2.6 RC Cell Thermal Model of an IGBT                                                                       | 66         |

| 3.2.0 No Cell Methial Woder of all IGBT                                                                      | 00         |

| 3.3 Proposed Rainflow Methods                                                                                | 68         |

| 3.3.1 Fast Rainflow [88]                                                                                     | 68         |

| 2.2.2. Code Counting weign Madified Counting Detaffees Alexanders [00]                                       | 74         |

| 3.3.2 Cycle Counting using Modified Graphical Rainflow Algorithm[88]                                         | /1         |

| 3.3.3 Comparison with Other Rainflow Algorithm Approaches[87]                                                | 76         |

| 3.3.4 Example to Demonstrate the Equivalent Temperature Calculation in Conjunction with                      | h Rainflow |

|                                                                                                              | •          |

| Algorithm                                                                                                    | 79         |

| 3.4 IMPACT OF OPERATING PARAMETERS ON STRESSES IN A WIREBOND                                                 | 80         |

| 3.5 Summary                                                                                                  | 81         |

| 5.5 GONWAK I                                                                                                 |            |

| CHAPTER IV SIMULATION RESULTS                                                                                | 82         |

| 4.1 Introduction                                                                                             | 82         |

| 4.2 THERMAL MODEL OF POWER SEMICONDUCTOR                                                                     | 82         |

| 4.2.4 June 14.4 Francisco T. J. 1.4.4 J. J.                                                                  |            |

| 4.2.1 Impact of Frequency on Thermal Model                                                                   | 82         |

|           | 4.2.2      | Impact of number of RC cells                                                      | 85            |

|-----------|------------|-----------------------------------------------------------------------------------|---------------|

|           | 4.2.3      | Thermal Model of IGBT                                                             | 85            |

|           | 4.3 IMP    | ACT OF OPERATING PARAMETERS ON STRESSES IN A WIREBOND                             | 86            |

|           | 4.3.1      | Wire Model                                                                        | 86            |

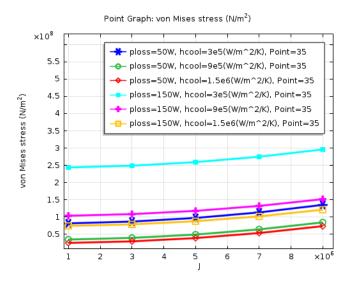

|           | 4.3.2      | Finite Element Simulation Results for Stress in the Wire                          | 92            |

|           | Cumul      | ative Influence of Operation Parameters on Stresses in the Wire:                  | 96            |

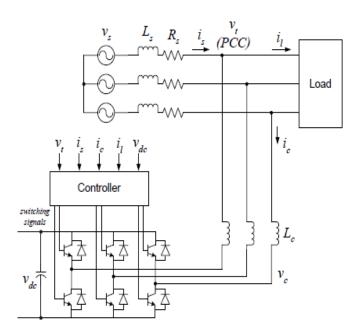

|           | 4.4 STA    | ATCOM SIMULATION IN EMTP                                                          | 97            |

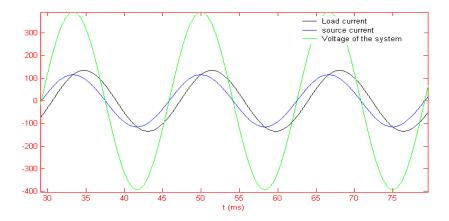

|           | 4.4.1      | Power Factor Correction                                                           | 98            |

|           | 4.4.2      | Analytical Loss Calculation                                                       | 99            |

|           | 4.4.3      | Thermal Model                                                                     | 101           |

|           | 4.4.4      | STATCOM Simulation Results                                                        | 101           |

|           | Power      | Factor Correction                                                                 | 101           |

|           | 4.4.5      | Lifetime Estimation for Power Factor Correction                                   | 102           |

|           | 4.5 Lift   | ETIME PREDICTION USING RAINFLOW ALGORITHM FOR A POWER FACTOR VARYING LO           | AD PROFILE    |

|           |            |                                                                                   | 104           |

|           | 4.5.1      | Using Proposed Rainflow Algorithms for a Power Factor Varying Load [88]           | 104           |

|           | 4.5.2      | Lifetime Estimation of IGBT in a STATCOM for an Arc furnace Load using Equivalent | t Temperature |

|           | Rainflow . | Algorithm[89]                                                                     | 107           |

|           | 4.6 Sun    | 1MARY                                                                             | 109           |

| <b>OT</b> |            |                                                                                   | 110           |

| СН        |            | V EXPERIMENTAL RESULTS                                                            |               |

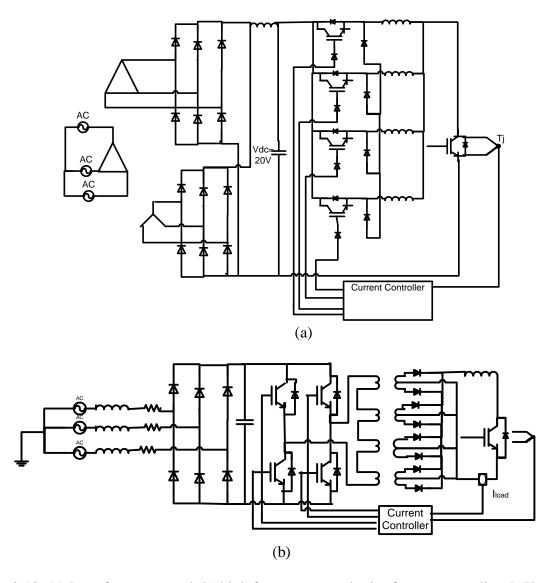

|           | 5.2 STA    | ATCOM EXPERIMENTAL SETUP                                                          | 110           |

|           | 5.3. Powi  | ER CYCLING TEST SETUP                                                             | 111           |

|           | 5.3.1      | Operating Conditions Determination                                                | 114           |

|           | 5.3.2      | Measurements                                                                      | 114           |

|              | 5.3.3                         | Protection Circuits                                        | . 115              |

|--------------|-------------------------------|------------------------------------------------------------|--------------------|

| 5            | .4 RESU                       | TS AND DISCUSSION                                          | 116                |

|              | 5.4.1                         | Failures in 600 V, 50 A IGBT module under DC power cycling | . 116              |

|              | 5.4.2                         | Degradation in 1200 V, 150 A Phase-leg IGBT Module         | . 120              |

| 5            | 5.4. Sumi                     | MARY                                                       | 122                |

|              |                               |                                                            |                    |

| CHA          | PTER                          | VI_CONCLUSIONS AND FUTURE WORK                             | .124               |

| <b>CHA</b> ] | PTER<br>5.1 Co                | VI CONCLUSIONS AND FUTURE WORK                             | <b>.124</b><br>124 |

| 6            | 5.1 Co                        | VI CONCLUSIONS AND FUTURE WORK                             | 124                |

| 6            | 5.1 Con<br>5.2 Con            | NCLUSIONS                                                  | 124<br>126         |

| 6<br>6       | 5.1 Coi<br>5.2 Coi<br>5.3 Fut | NCLUSIONS                                                  | 124<br>126<br>126  |

## LIST OF TABLES

| Table 1.1 Components of power semiconductor packaging [15]                                       |

|--------------------------------------------------------------------------------------------------|

| Table 2.1. Common temperature sensitive parameters used for semiconductors                       |

| Table 2.2. Comparison of the different thermal models from literature evaluating advantages and  |

| disadvantages of each model                                                                      |

| Table 2.3. Popular lifetime prediction models for various design parameters and variables30      |

| Table 2.4. Common Failure modes in semiconductors [16], [42]                                     |

| Table 2.5. Failure criteria expressed as a percentage increase in monitored DUT parameters       |

| [21]45                                                                                           |

| Table 2.6. Comparison of different power cycling tests in literature                             |

| Table 3.1. IGBT Module materials with their thermal properties and dimensions                    |

| Table 3.2. Derived RC parameters from the frequency response                                     |

| Table 3.3. Derived RC parameters from the frequency response                                     |

| Table 3.4. Modified graphical rainflow algorithm steps for load profile in Figure 3.6            |

| Table 3.5 Rainflow algorithms comparison for execution time, memory usage, and load sequence     |

| efficiency                                                                                       |

| Table 3.6. A step by step analysis of rainflow algorithm with and without equivalent temperature |

| calculation applied to the example profile in Figure 3.17                                        |

| Table 4.1. Dimensions and materials of wire model in COMSOL                                      |

| Table 4.2. List of parameters and descriptions.                                                  |

## LIST OF FIGURES

| Figure 1.1. IGBT module components                                                                      |

|---------------------------------------------------------------------------------------------------------|

| Figure 1.2. Block diagram of the steps involved in lifetime calculation of semiconductor5               |

| Figure 2.1. Two commonly used thermal models a) Foster Network and b) Cauer Network13                   |

| Figure 2.2. Modified Elmore technique applied to compact thermal model of two chips IGBT.               |

| [3]19                                                                                                   |

| Figure 2.3. Spacing of the thermal nodes within package and base-plate model [21]22                     |

| Figure 2.4 Stress-strain plot for plastic and elastic strain                                            |

| Figure 2.5. Hysteresis Stress-strain plot of a metal.                                                   |

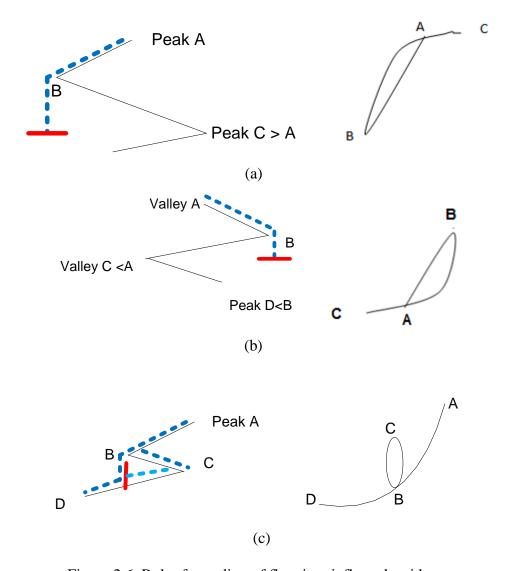

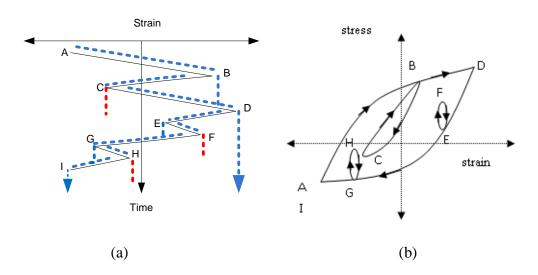

| Figure 2.6 Rules for ending of flow in rainflow algorithm (a) rain starting at peak ,A, encounters      |

| greater peak, C, (b) rain starting at valley, A, encounters lesser valley, B, (c) rain flow starting at |

| C towards D encounters previous flow from AB                                                            |

| Figure 2.7. "Rainflow" on (a) a load sequence and (b) its stress-strain plot                            |

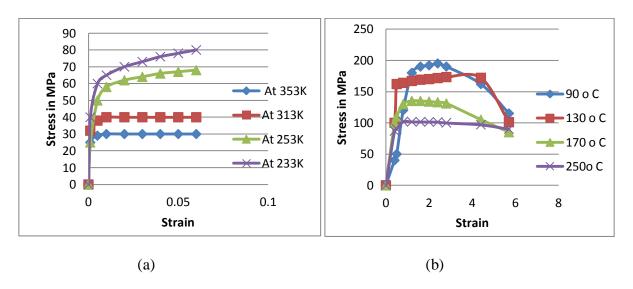

| Figure 2.8. Stress-strain graph variation with temperature of a) solder [44] and b) Aluminum for        |

| wire bonds [45]                                                                                         |

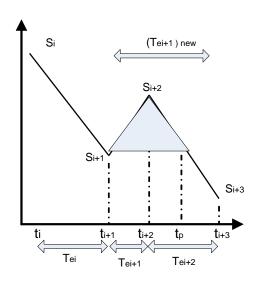

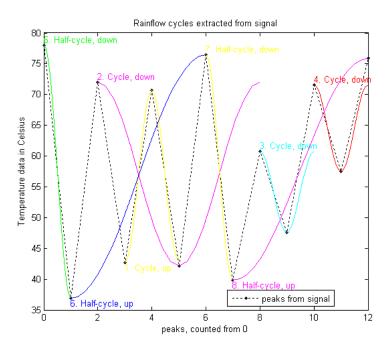

| Figure 2.9. Rainflow cycle extraction and equivalent temperature recalculation                          |

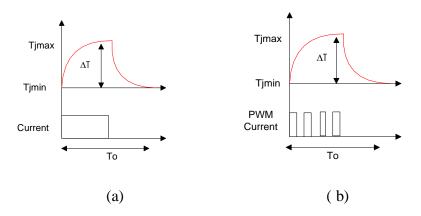

| Figure 2.10. DC and AC power cycling test concepts                                                      |

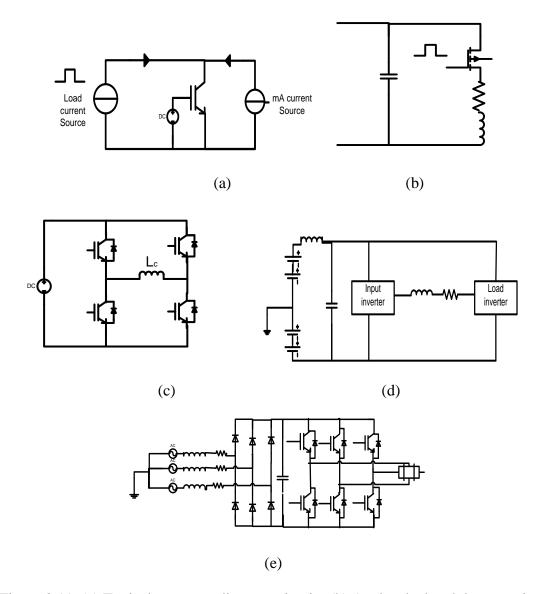

| Figure 2.11. (a) Typical power cycling test circuit, (b) Avalanche breakdown testing circuit, (c)       |

| Single phase, full bridge with inductive load, (d) Three phase back-back inverters test circuit,        |

| (e) Synchronous motor drive test circuit                                                                |

| Figure 2.12. (a) Low frequency and (b) high frequency topologies for cycling51                          |

| Figure 3.1. Steps in development of optimum RC thermal                                                       |

|--------------------------------------------------------------------------------------------------------------|

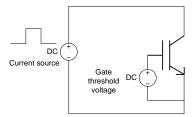

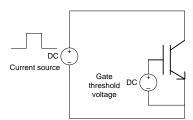

| Figure. 3.2. DC power cycling test circuit at gate the shold voltage                                         |

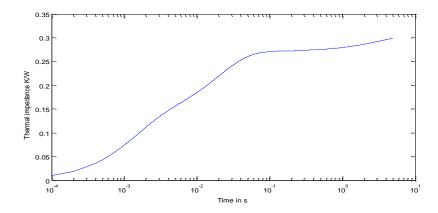

| Figure 3.3. Thermal impedance of an IGBT module for 100 W power loss                                         |

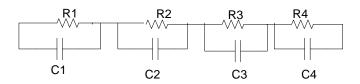

| Figure 3.4. RC thermal network of the example temperature profile                                            |

| Figure 3.5. Different number of RC thermal network of the example temperature profile for a                  |

| time scale of 2 ms                                                                                           |

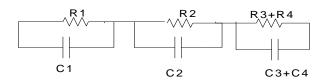

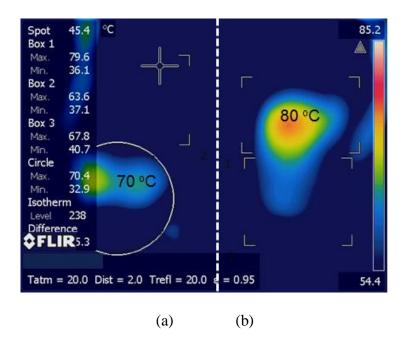

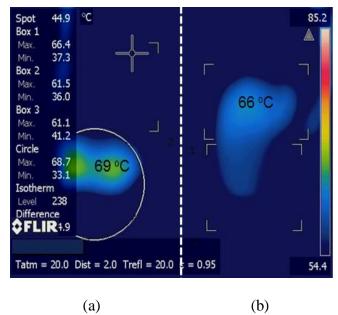

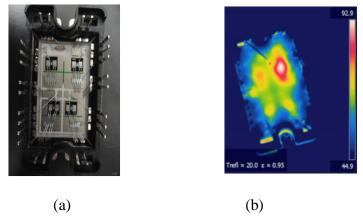

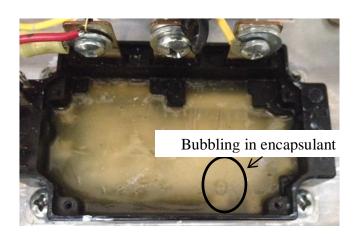

| Figure 3.6. Modules (a) with encapsulant and (b) most of the encapsulant removed are                         |

| connected for testing the top device and obtaining thermal images with thermal camera63                      |

| Figure 3.7. Thermal image of power module CM150DU after 80 s of 250 W power of the                           |

| module (a) with and (b) without encapsulant                                                                  |

| Figure 3.8. Thermal image of power module CM150DU after 5 s of power off (a) with                            |

| encapsulant and (b) without encapsulant. 65                                                                  |

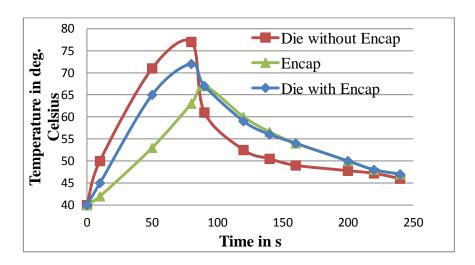

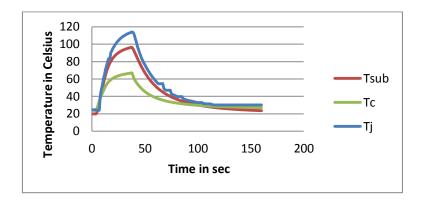

| Figure 3.9. Temperature variation of the encapsulant (green) and the dielectric with (blue) and              |

| without encapsulant (red)                                                                                    |

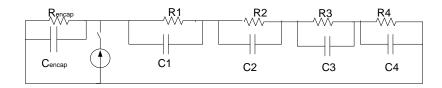

| Figure 3.10. Thermal model of the IGBT from Figure 3.3 including the encapsulant, as proposed                |

| by [38] Bagnoli et al66                                                                                      |

| Figure 3.11. Temperatures of the junction, $T_j$ , substrate $T_{sub}$ , and case, $T_c$ , of the IGBT power |

| module CM150DU for a power pulse of 160 W                                                                    |

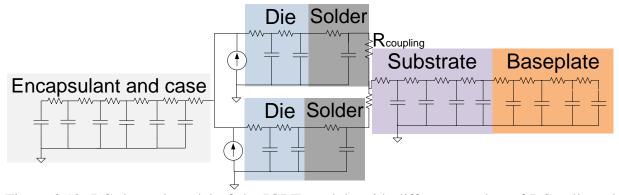

| Figure 3.12. RC thermal model of the IGBT module with different number of RC cells and                       |

| encapsulant thermal model                                                                                    |

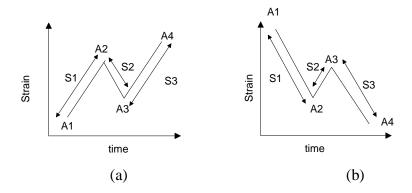

| Figure 3.13. Points and ranges in (a) peak cycle formation (b) valley cycle formation using four-            |

| point algorithm.                                                                                             |

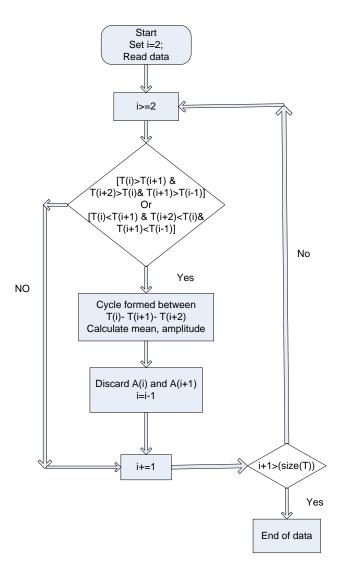

| Figure 3.14. Flow chart demonstrating the steps involved in fast rainflow algorithm70                                   |

|-------------------------------------------------------------------------------------------------------------------------|

| Figure 3.15. Example load profile to show shortcoming of graphical rainflow72                                           |

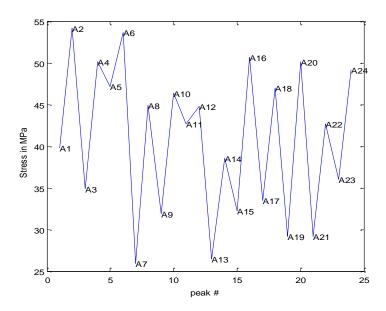

| Figure 3.16. Random load waveform for explaining MGRM                                                                   |

| Figure 3.17. Rainflow algorithm of a signal with cycle's information from code available in                             |

| MATLAB [83]79                                                                                                           |

| Figure 3.18. Block diagram illustrating the methodology of lifetime model development81                                 |

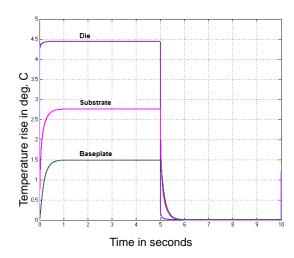

| Figure 4.1. Temperature rise with respect to the bottom layers of the dielectric, substrate and the                     |

| baseplate at 0.1 Hz83                                                                                                   |

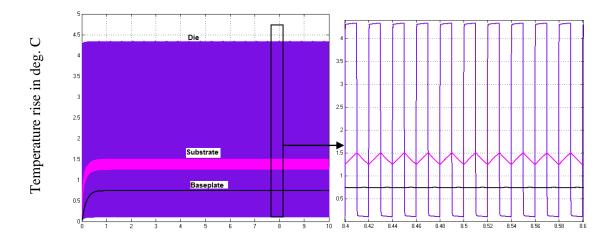

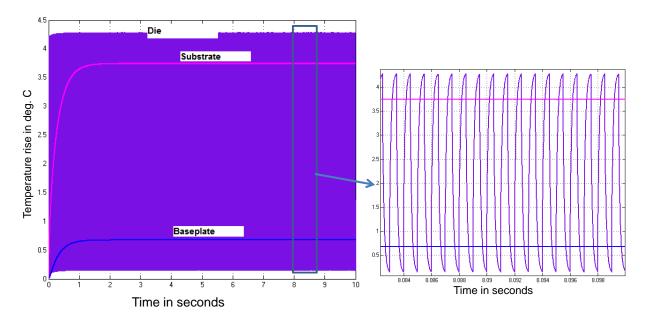

| Figure 4.2. Temperature rise with respect to the bottom layers of the dielectric, substrate and the                     |

| baseplate at 50 Hz84                                                                                                    |

| Figure 4.3. Temperature rise with respect to the bottom layers of the dielectric, substrate and the                     |

| baseplate at 1 kHz84                                                                                                    |

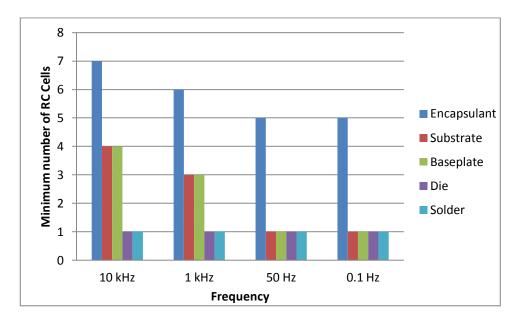

| Figure 4.4. Minimum number of RC cells for different layers at frequencies of 10 kHz, 1 kHz, 50                         |

| Hz and 0.1 Hz85                                                                                                         |

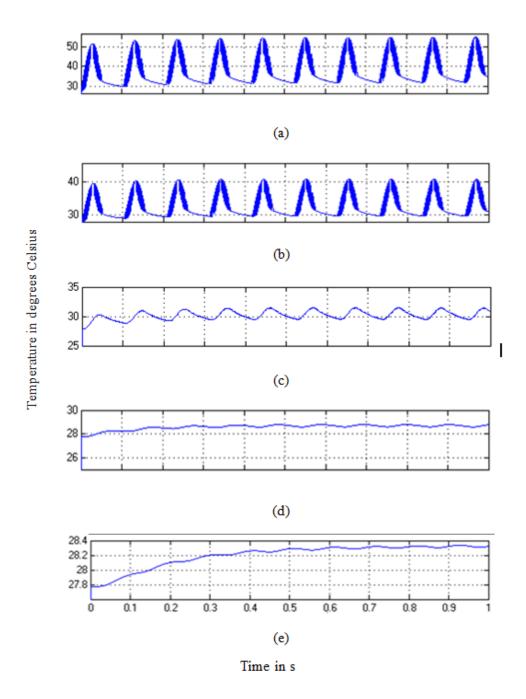

| Figure 4.5. Temperatures of a device in a phase leg module at 1 kHz switching frequency and 60                          |

| Hz operating line frequency, for power loss input of 100 W for (a) the dielectric, (b) solder, (c)                      |

| substrate,(d) baseplate, and (e)encapsulant                                                                             |

| Figure 4.6. a) IGBT device and b) its thermal image when upper left IGBT is power cycled to a                           |

| temperature of 100 °C by a total power of 75 W                                                                          |

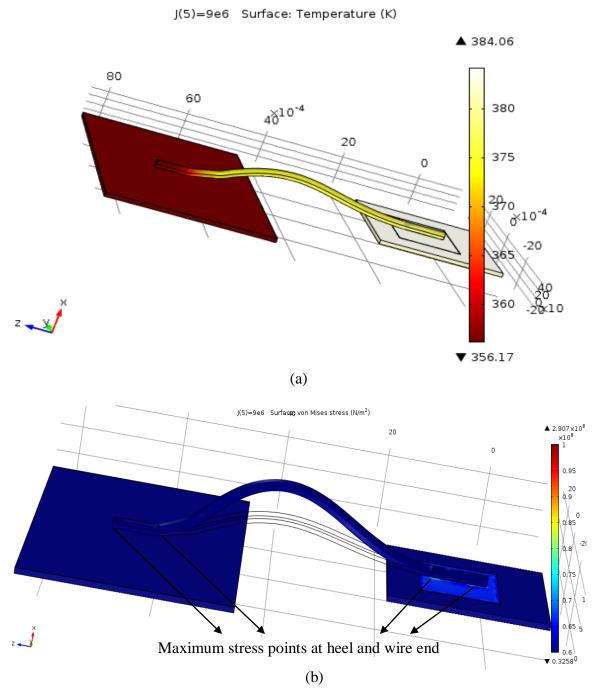

| Figure 4.7. Simplified wire connection model between copper pad and silicon dielectric, and (a)                         |

| the wire temperature in K and (b) stress in $N/m^2$ for $9\times10^6$ A/m <sup>2</sup> , 100 watt losses in the silicon |

| dielectric 90                                                                                                           |

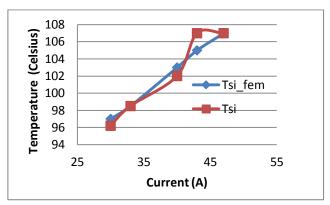

| Figure 4.8. Comparison of FEM simulation and experimental temperatures of the silicon for a                         |

|---------------------------------------------------------------------------------------------------------------------|

| 120 W of power loss in dielectric and with currents varying from 30 A to 50 A92                                     |

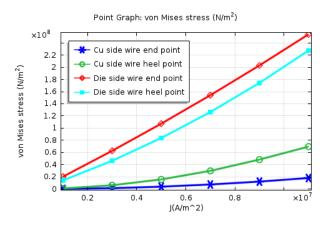

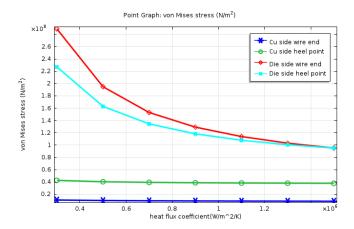

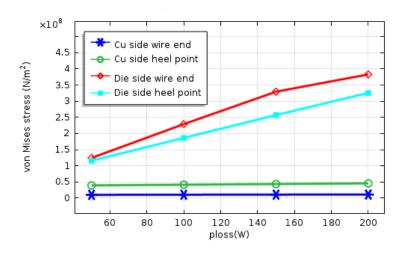

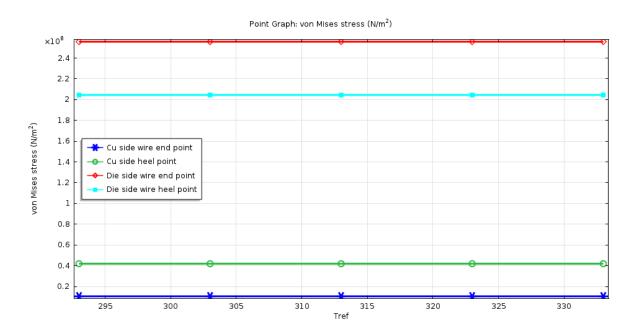

| Figure 4.9. Stress variation with current density variation from $1\times10^6$ to $8\times10^6$ A/m <sup>2</sup> 93 |

| Figure 4.10. Stress variation with heat flux coefficient variation from $3\times10^6$ to                            |

| $1.5 \times 10^6 \text{ W/(m}^2.\text{K})$                                                                          |

| Figure 4.11. Stress variation with power loss varying from 50 W to 200 W94                                          |

| Figure 4.12. Stress variation with ambient temperature, $T_{ref}$ , from 293 K to 343 K95                           |

| Figure 4.13. Stress variation with power loss in dielectric, $p_{loss}$ , and heat flux coefficient, $h_c$ 97       |

| Figure 4.14. STATCOM model connected to grid.                                                                       |

| Figure 4.15. The source voltage, load and source currents of the system for power factor                            |

| 99                                                                                                                  |

| Figure 4.16. Foster based thermal model of the device                                                               |

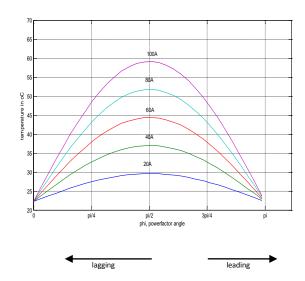

| Figure 4.17. Temperature of IGBT varying with power factor of load                                                  |

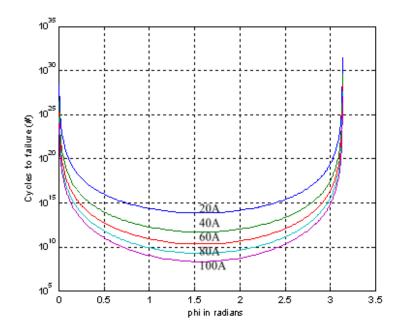

| Figure 4.18. Lifetime of IGBT in terms of number of cycles to failure varying with power factor                     |

| angle of the load                                                                                                   |

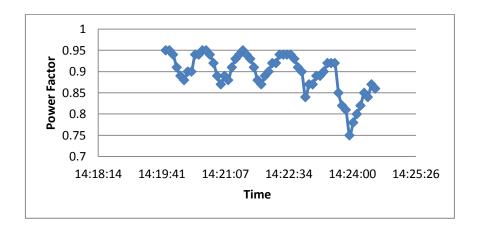

| Figure 4.19. Power factor variation of the 5 minute load data of a building                                         |

| Figure 4.20. Temperature of the IGBT of STATCOM for load profile of Figure 4.20                                     |

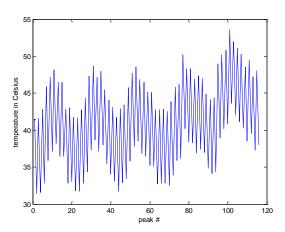

| Figure 4.21. Temperature cycle measurement from rainflow algorithm for the 5 minute power                           |

| factor variation load data                                                                                          |

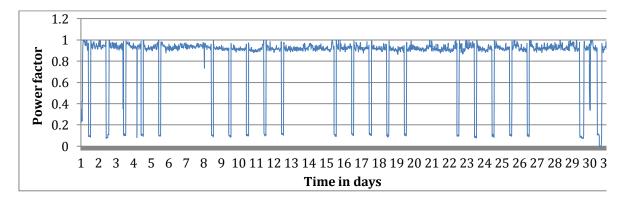

| Figure 4.22. Arc furnace based industrial load power factor variation monitored for every 15                        |

| minutes for a period of month                                                                                       |

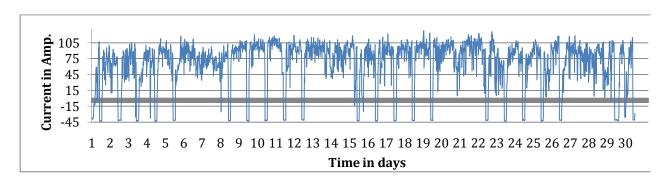

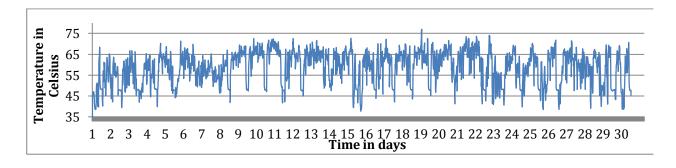

| Figure 4.23. Inverter current in amperes for unity power factor of the load                                         |

| Figure 4.24. IGBT temperature variation for the reactive compensation of the load                 |

|---------------------------------------------------------------------------------------------------|

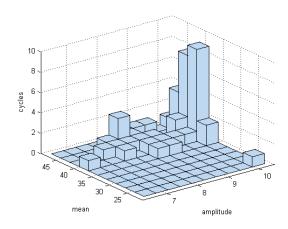

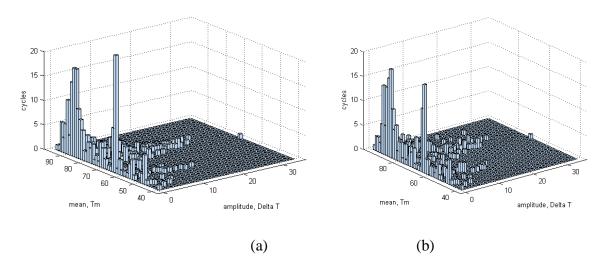

| Figure 4.25. Rainflow histogram of load profile in Fig. 4.23 with (a) conventional calculation    |

| and (b) equivalent temperature calculation                                                        |

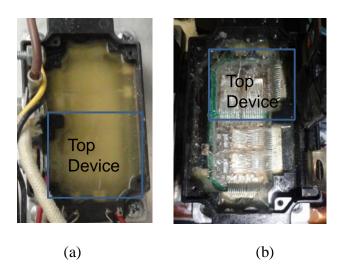

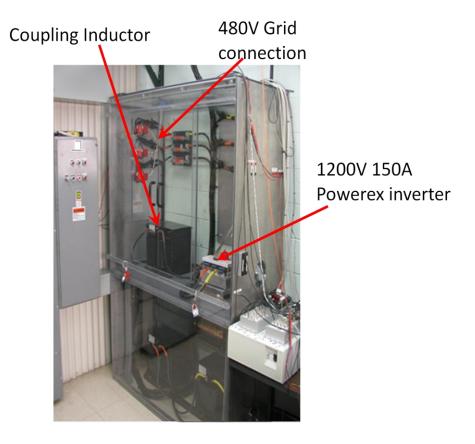

| Figure 5.1. STATCOM setup at ORNL                                                                 |

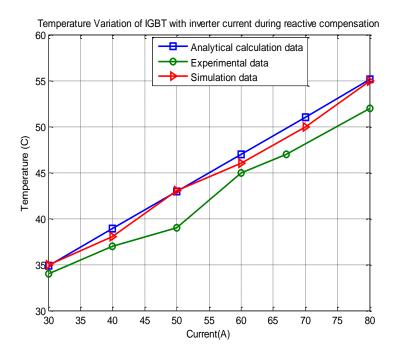

| Figure 5.2. Comparison of temperature data at different inverter loads for reactive               |

| compensation by analytical calculation, simulation and experimental results112                    |

| Figure 5.3. DC power cycling test circuit at gate threshold voltage                               |

| Figure 5.4. DC power cycling test set up in the CURENT power electronics laboratory115            |

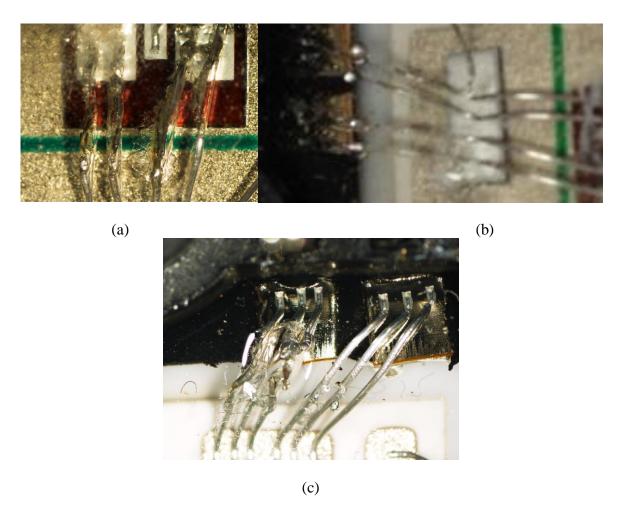

| Figure 5.5. Wire melt-off with (a) encapsulant blackening at the midpoint of the wire, (b) at the |

| maximum loop height at the source terminals, and (c) at the drain terminal connection117          |

| Figure 5.6. Wire crack failure in an IGBT device                                                  |

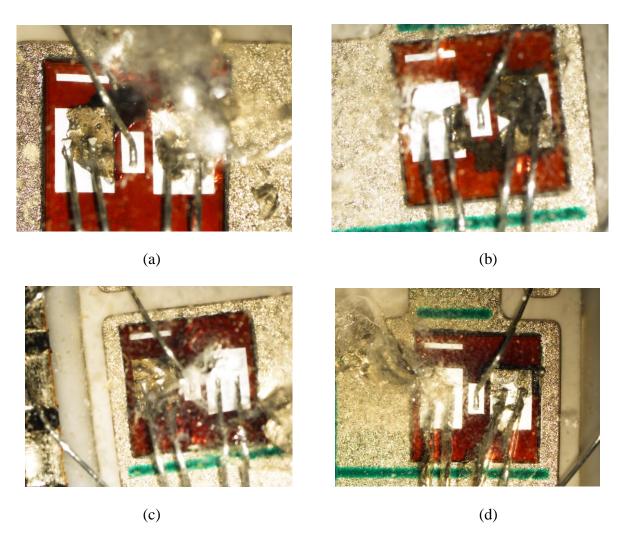

| Figure 5.7. Dielectric damage in different devices under test showing that the die bond pads on   |

| the outer edges of the device had frequent failures than the inner die bond-pads119               |

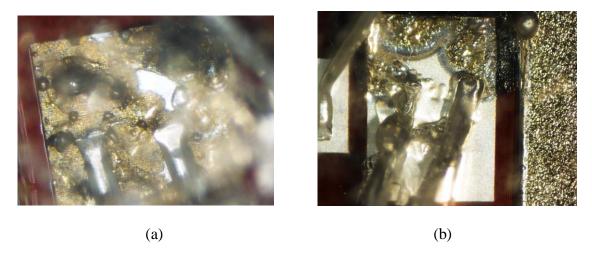

| Figure 5.8. (a) Source metallization melt-down and (b) dielectric degradation120                  |

| Figure 5.9. Change in static characteristics at $V_{ge}=15~V$ after cycling for 200000 power      |

| cycles                                                                                            |

| Figure 5.10. Cracks in encapsulant after (a) 150000 cycles and (b) 200000 cycles123               |

#### CHAPTER I

#### INTRODUCTION

Estimation of reliability and lifetime of semiconductor devices is as old as the manufacturing of semiconductors itself. Reliability gives insight about the operational life of the system, maintaining the operating conditions within limits, and scheduling maintenance. Many standards such as Military standards, IEC, JEDEC, etc. have been established and are followed by the manufacturing industries [1][2]. Reliability of power electronics has gained importance with the European automotive initiatives for traction like LESIT (Leistungs Elektronik Systemtechnik und Informations Technologie), a Swiss government funded research program, and the German project, RAPSDRA (Reliability of Advanced Power Semiconductor Devices for Railway Traction Application) [3][4]. Many lifetime estimation models for semiconductors have been developed, initiated by the above mentioned projects.

The lifetime and reliability testing of power semiconductors individually is a mature technology. Standard tests are conducted at constant conditions for Metal oxide semiconductor field effect transistor (MOSFET) and bipolar junction transistor (BJT). But the lifetime of the system and in turn the lifetime of the semiconductor largely depends on the application it is being used for. Hence, it is important to develop methods to estimate reliability based on an application [5][6][8][9][10][11][12][14]. Applications that are considered in reliability calculations for Insulated Gate Bipolar Transistor (IGBT) are adjustable speed drives, matrix converters, electric vehicle applications, aerospace applications, inverters integration for photovoltaic (PV) and wind applications, etc. [5][6][8][9][10][11][12][14].

Reliability of FACTS (Flexible AC Transmission Systems) is an important factor in determining the stability of the power system. However, little research has been found in reliability of IGBTs and the power converters in (FACTS) Flexible AC Transmission Systems applications.

On-line condition monitoring methods to detect degradation in based on monitored parameters is gaining wide application. ABB's MACH sense-p/r system is one such example to condition monitoring of motors based on electrical parameters (current and voltage), vibration and torque readings that are analyzed and send a detailed report to the consumer through wireless data transfer [84]. Similar monitoring system is available for circuit breakers also.

The focus of this work is to estimate lifetime of semiconductors in STATic COMpensator, (STATCOM) application. STATCOM is a shunt connected FACTS device, consisting of a voltage source converter, and a coupling passive element to control the voltage and reactive power [13]. Reactive current compensation for the grid connected STATCOM is achieved by using non-active power compensation theory in this work.

The first step in lifetime estimation is root cause analysis, which is to identify the common failure mechanism and mode analysis in the inverter system. In an inverter, the most unreliable elements are power semiconductors and capacitors [11][14]. With significant research available in the area of capacitor reliability, there is a need to focus on the reliability of power semiconductor modules.

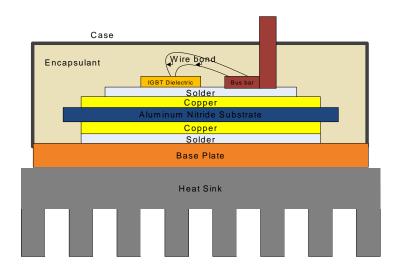

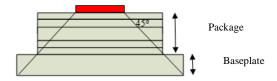

In Silicon (Si) based semiconductors, wafer level failures are least probable to occur due to mature manufacturing technology, if operated within ratings all the time. Packaging failures are the most common failures observed during operation of semiconductors in an application. The packaging layers of a power semiconductor, their purpose, and the commonly used materials are listed in Table 1.1 and illustrated in Figure 1.1 [15]. Among the packaging layers, cracks in solder and wire bond liftoff, are the two most common failures due to thermal fatigue observed in various applications of power converter.

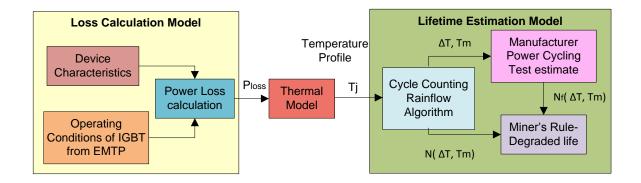

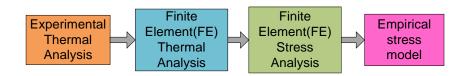

The methodology used for estimating reliability of semiconductors in power converters in this work consists of estimating the junction temperature, lifetime prediction method, and experimental verification by power cycle testing of the devices. A system overview is presented in Figure 1.2. The data from device characteristics and the operating condition values from the

Table 1.1 Components of power semiconductor packaging

|   | Packaging Layer  | Function                                 | Common materials                      |

|---|------------------|------------------------------------------|---------------------------------------|

| 1 | Base plate       | Mechanical strength to insulating        | Half hardened OFHC,                   |

|   |                  | substrate                                | Cu, Al,                               |

|   |                  | Thermal conductivity                     | CuMoCu laminate etc.                  |

|   |                  | Surface smoothness to avoid voids        |                                       |

| 2 | Insulating       | Support circuitry                        | Alumina,                              |

|   | substrate and    | Electrical insulation                    | Aluminum nitride,                     |

|   | metallization    | Thermal conductivity                     | SiC, SiO <sub>2</sub>                 |

|   |                  | Smoothness for adhesion and spacing      |                                       |

| 3 | Bonding Material | Electrical, thermal and mechanical       | a) Organic Epoxy,                     |

|   |                  | linkage between insulating substrate,    | Polyamide                             |

|   |                  | metal base-plate and semiconductor       | b)Metallurgical solder                |

|   |                  | chips.                                   | c) Silver filled glass                |

| 4 | Terminal power   | High current withstand capability        | Al wires                              |

|   | interconnection  | Low cost and the absence of voids at the | Gold wires                            |

|   |                  | interconnection with power chips.        | Cu bus bars                           |

| 5 | Encapsulant      | Protection of the power chip and wire    | Silicone gel, silicone,               |

|   |                  | assembly from chemical reactions due     | epoxy, Si <sub>3</sub> N <sub>4</sub> |

|   |                  | to moisture, chemicals etc.              |                                       |

|   |                  | Insulate against high voltage levels.    |                                       |

| 6 | Plastic case and | Protect the chip assembly from           | standard packages:                    |

|   | cover            | atmospheric reactions,                   | INT- A-PAK and                        |

|   |                  | Electrically insulate                    | double INT-A-PAK.                     |

Figure 1.1. IGBT module components.

simulation model are input to the electro-thermal model. The power losses are calculated and the thermal model of the IGBT is used to estimate junction temperatures. The lifetime prediction model is developed from temperature profiles using rainflow algorithm and manufacturer's data for power cycling tests. Miner's rule of linear accumulation of degradation is used to estimate the lifetime for a mission profile. Finally, the power cycling tests are verified using accelerated lifetime testing experiments.

A thermal model development is proposed to overcome some of the drawbacks of existing models, discussed in Chapter 2, listed below

- Unavailability of temperatures in each layer of package specifically in datasheet thermal models.

- 2) Thermal coupling in a multi-chip module (especially in Foster and Cauer networks)

Figure 1.2. Block diagram of the steps involved in lifetime calculation of semiconductor.

- 3) Computationally exhaustive and time consuming (Finite Element based thermal modeling, Fourier thermal model)

- 4) Determining number of thermal (RC) time constants for each layer (Cauer network, Elmore technique, Multi-exponential models)

- 5) Use of same number of time constants for each layer.

The proposed model determines the optimum number of time constants and uses different number of time constants for each layer by using network identification techniques to estimate temperatures accurately, is explained in Chapter 3.

After obtaining the thermal response of different layers of the package, the next step is to estimate the lifetime of each chip. A model relating mean temperature and temperature swing to lifetime, also described as Coffin-Manson-Arrhenius model, is considered to estimate life in this work, for manufacturer's based power cycling data. Cycle counting methods are used to obtain the stress-strain hysteresis cycles for a time-varying load profile. Rainflow algorithm is the most

popular counting algorithm [12], and different approaches have been proposed in literature and will be discussed in Chapter 2. A new rainflow algorithm which is an extension of "Graphical" rainflow algorithm is presented in Chapter 3. A stress model dependent on the operating conditions such as current, voltage, frequency, etc., and the dimensions of the device is proposed as a universal model.

Finally, the lifetime estimation results are verified using power cycling tests. Power cycling tests are accelerated tests where the devices are switched so that the temperature in the device is similar to thermal cycling tests. Power cycling tests are preferred to thermal cycling, as they include switching and are closer to the actual operation of the device. These tests mainly cause wire bond failure while thermal cycles result in solder cracks. Power cycling experimental set up is discussed in Chapter 2. The simulation results for the proposed methods are presented in Chapter 4 while the experimental results are presented in Chapter 5.

#### 1.1 Motivation

With the advent of Flexible AC Transmission Systems (FACTS), power electronics are integrated with power systems to improve stability, improve the transmission capacity within thermal limits, and avoid undesirable loading of certain transmission lines. Thus, FACTS technology ensures better coordinated control and improves system stability and security [17]. The more the power electronics are integrated to power systems in the form of distributed generation system, and FACTS, the more is the concern of their reliability affecting the system reliability. Better reliability of power electronics would further improve the scope of integration to power grid.

North American Electric Reliability Corporation (NERC), in its report on "Reliability Considerations from Integration of Smart Grid," has emphasized considering all the existing devices and systems such as Phasor Measuring Units, FACTS, etc., for assessing reliability of the bulk power system [18]. There is a need to study the individual reliability of these devices/systems to predict their impact on the grid.

Most applications considered for reliability studies have been for vehicular applications. Recently, renewable energy applications are gaining importance in reliability studies [5][6][8][9][10][11][12][14]. This research mainly focuses on the reliability of Insulated Gate Bipolar Transistor (IGBT) devices used in the STATCOM application.

For lifetime estimation of the semiconductors, the various important steps are thermal model development, cycle counting methods, and lifetime models. As most of the failures are caused by thermal fatigue, it is necessary to develop thermal model that estimates temperatures in different layers and materials of the module accurately, less time consuming and computationally exhaustive. Hence, there is a need to develop an accurate simple thermal model.

The temperature excursions estimated are used to obtain the fatigue stress-strain cycles using rainflow algorithm. The conventional rainflow algorithm used in semiconductor lifetime estimation does not consider time dependence of temperature on its cycle information. There is need to consider the equivalent temperature in semiconductor lifetime estimation using rainflow algorithm.

The lifetime estimation models, for solder fatigue and wirebond failures, based on physics of failure have gained technical importance in recent times. There is a need to develop a generalized lifetime estimation model based on the operating parameters of IGBTs.

Finally, power cycling tests are the accelerated tests conducted to detect weaker links, validate the lifetime models for the device under test, and to test and compare new packaging materials with that of conventional methods. DC power cycling tests use a simple circuit and are extensively used in testing reliability. Tests conducted should be analyzed to detect failure mechanisms.

This work is motivated to develop methods and models to overcome the problems associated with accurate lifetime estimation of power semiconductor devices.

#### 1.2 Contributions

The main contributions of this work are listed below

- Studied the stresses in wirebonds in an IGBT module based on finite element analysis, that

is dependent on the operating electrical parameters such as voltage, current, and frequency,

and the physical dimensions of the module.

- 2) Developed new rainflow counting algorithms improving the execution times of existing methods.

- 3) Applied time-dependent temperature calculation in rainflow algorithm to semiconductor lifetime estimation.

- 4) Developed different RC cells based thermal model for each layer in the semiconductor module with encapsulant.

#### 1.3 Dissertation Outline

#### **Chapter 1: Introduction**

The process of predicting reliability or remaining life involves thermal analysis and application of temperature data to lifetime models. A basic introduction to thermal models of semiconductors and the lifetime is discussed. The motivation of this dissertation is presented to give an understanding about its scope and contribution of the project.

#### **Chapter 2: Literature Review**

A literature review of the various methods used in compact thermal models is presented. Estimating the RC thermal networks from deconvolution methods and frequency analysis is analyzed. The need for counting algorithms is discussed in detail. The various counting algorithms and their drawbacks are discussed. The original rainflow algorithm is presented. A literature review on the various lifetime prediction models used for power semiconductors are discussed. The existing lifetime models are discussed. A literature review on various power cycling methods are studied, and a power cycling circuit for testing is chosen for this application.

#### **Chapter 3: Proposed Methods to Improve Lifetime Prediction Models**

Lifetime Prediction using different number of RC cells based thermal model, modified Graphical Rainflow algorithm, and the stresses in wirebond due to operation parameters are presented. The RC networks of the thermal model incorporating the impacts of encapsulant to represent the semiconductor is presented. A modified rainflow algorithm for lifetime prediction that overcomes the shortcomings of graphical rainflow method is proposed and explained. Finally, a study on the stresses in wirebonds on operating conditions and design parameters of the module is presented.

#### **Chapter 4: Simulation Results**

The results include IGBT related temperature and lifetime simulations for STATCOM operation under power factor correction and harmonic compensation. The results of lifetime prediction of IGBT for a sample load profile using rain flow algorithm are presented.

#### **Chapter 5: Experimental Results**

The experimental verification of the thermal model is presented and the accuracy of the model is discussed. The experimental set up of a STATCOM and its loading is discussed. The temperature profiles for power factor correction and harmonic compensation in a STATCOM are experimentally obtained and compared with the simulation results. Power cycling test set up and the failures observed during the tests are presented.

#### **Chapter 6: Conclusion and Future Work**

A summary of the proposed methods and their impact on lifetime calculation are discussed in this chapter. Future work to enhance the performance of the proposed methods and overcome some of the drawbacks will be presented.

#### **CHAPTER II**

#### LITERATURE REVIEW

#### 2.1 Introduction

The lifetime of semiconductor materials is based on the stress it can withstand. In semiconductor applications, different thermal expansions of the materials in the package cause different amounts of strain, and since the materials are bonded in a package, these strains cause shearing stresses in the material. Thus, stress is indirectly dependent on temperature. By observing temperatures of the different layers in the package of a semiconductor, and applying lifetime estimation equations, the remaining life of the semiconductors for an application can be found. There is a need to understand the current state of research in reliability studies to be able to apply to the STATCOM application. This chapter presents a literature review of thermal modeling of semiconductor devices, lifetime estimation based on cycle counting, different rainflow algorithms, and power cycling methods.

#### 2.2 Thermal Models

The conduction and switching power losses in the semiconductor devices generate heat in their components. Temperature is an important factor in estimating the lifetime of the inverter system. Temperature rise beyond the rated values will lead to more losses, due to the change in device characteristics with temperature, and will lead to thermal runaway. Thermal management of power converter systems involves heat sink design, and cooling methods (air, liquid).

Equation 2.1 describes the relation between power dissipated and the temperature of two layers of a module [19][21]

$$P = \frac{T_1 - T_2}{Z_{th}} , (2.1)$$

where P is the power losses in the device,

$T_1$  and  $T_2$  are the temperatures of the two layers, example case and ambient, of the device  $Z_{th}$  is the thermal impedance of the device.

Thermal impedance is defined by thermal resistance and capacitance. Thermal resistance is the resistance of the material to heat flow, expressed in Kelvin/Watt. Thermal capacitance is the amount of heat required to bring about a unit change in temperature of a unit mass, expressed in Joules/Kelvin.

For conduction, thermal resistance:

$$R_{th} = \frac{l}{k \cdot A}$$

(2.2)

where l is length, A is area of cross section, k is thermal conductivity

For convection, thermal resistance,

$$R_{th} = \frac{1}{h \cdot A}$$

(2.3)

where *h* is thermal coefficient of convection

Thermal capacitance:

$$C_{th} = Q/(\Delta T)$$

(2.4)

where Q is the heat energy dissipated,  $\Delta T$  is the temperature difference.

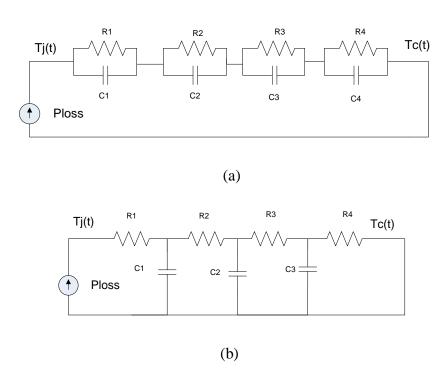

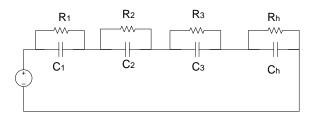

The Foster and Cauer networks are the simplest 1-dimensional RC thermal models. The Foster model, shown in Figure 2.1(a) is the most typical and easiest thermal model to obtain. It is commonly found in manufacturer datasheets. The Cauer model, shown in Figure 2.1(b), is based on the physical properties of the device.

In the Foster model, the individual RC elements do not represent the layer sequence. It is restricted to the specific application given in the datasheets and cannot be extended easily.

Deriving Foster network: From the thermal impedance curve, usually provided in the datasheet, a curve fit of three to four RC circuits is estimated to curve fit the thermal impedance curve. Thus, Foster network describes the thermal impedance of the whole device, and the individual points in the module cannot be considered [21]. The choice of number of RC circuits is not mentioned in literature, and it is basically a curve fitting model.

#### 2.2.1 Deriving Cauer Network from IGBT Module Dimensions:

Cauer network can be derived from experimental data or from the dimensions of the device. Each layer's thermal resistance and capacitance is found from its dimensions and thermal

Figure 2.1. Two commonly used thermal models: (a) Foster Network and (b) Cauer Network.

properties as shown in equations (2.2) through (2.4). Thermal model reduction from the 7-layer RC model to 3 layer RC model is described by Mussalam et al [23].

Cauer network allows adding of further layers by series connection to the model. The Cauer network nodes allow access to internal temperature of the layer sequence [21]. Another difference between Foster and Cauer models is that while the Foster network's node-to-node heat capacitances are not suitable for representing heat flow [19][21], the Cauer network includes only node-to-ground capacitances, and it represents a discretized image of the real heat-flow [19][21][24].

Cauer networks mostly approximate the thermal response of each layer to a corresponding RC network. However, for an accurate model of the thermal network, a network of 2 or more RC circuits is required. Foster and Cauer networks are interchangeable and with the knowledge of one of the networks, the other network can be derived.

Thermal Response Extraction: The thermal dynamic behavior of the device can be obtained from the thermal impedance response from experimental measurements, or physical simulation of the device using 3-D solvers based on finite element, finite differences, etc. While noise is a major concern for experimental measurement of responses, accuracy is a concern for physical simulations. The next section describes the different methods of temperature measurement.

#### 2.2.2 Temperature Measurement

Thermocouple measurement, infrared microscopy and the thermal sensitive electrical parameter (TSP) are commonly used methods to detect junction temperature [20]. Thermocouples require surface contact, but can be as small as 0.25 mm in diameter. They have a response time of about 10 ms, but bad thermal contacts can significantly affect the performance.

Despite this, thermocouples are the most popular of the direct techniques [19]. Optical fibers with phosphor sensors have response times of around 25 ms and can take measurements through the silicone gel, leaving the chip environment virtually unaltered [19]. Infrared microscopy can only be used to detect the unpackaged devices. Thus, to detect junction temperature of IGBTs, the package should be unsealed.

Temperature sensitive parameter (TSP) is defined as an electrical parameter of a semiconductor device that varies directly with junction temperature in an almost linear fashion. The common TSPs are the gate-cathode threshold voltage, on state collector-emitter voltage drop, and collector current [20][22][23][24][25][25]. Table 2.1 describes the temperature sensitive parameters commonly used for several semiconductor devices [20].

The junction temperature estimation using TSP consists of two processes, where one is offline characterization of the IGBT under test and the other is on-line estimation of junction temperature, based on the characterized data [26]. There is a wide range of the time-constants playing a role in the total thermal time response. Since temperature changes may occur in the

Table 2.1. Common temperature sensitive parameters used for semiconductors.

| Temperature sensitive parameter   | Semiconductor device              |

|-----------------------------------|-----------------------------------|

| Diode forward voltage, $V_f$      | Diodes, BJT, MOSFET,<br>Thyristor |

| Saturation voltage, $V_{ce\_sat}$ | BJT,IGBT                          |

| Gate turn-on Threshold, $V_{th}$  | MOSFET,IGBT                       |

| Collector current                 | BJT, IGBT                         |

| dv/dt                             | IGBT                              |

first 10-100 µs after the power onset and the final stabilization of the increased temperature requires 5-30 min or even more, depending on the mass of the package, the temperature responses are always plotted in logarithmic time scale [29].

Network Identification methods: Some of the early methods calculated the two to three time-constants from thermal response using the geometric and physical data of the device structure. These methods are usually approximate and involve an intuitive effort in realizing the number of time-constants.

#### **Simple Analytical Thermal Method** [35]:

If the thermal impedance is Z(t)

$$Z(t) = \sum_{i=1}^{N} (Z_i - Z_{i-1}) \nu(t - t_i)$$

(2.5)

where  $v(t-t_i)$  is the step function at  $t=t_i$

The Laplace transform gives

$$Z(s) = \sum_{i=1}^{N} (Z_i - Z_{i-1})e^{-st_i}$$

(2.6)

$$Re[Z(\omega)] = \sum_{i=1}^{N} (Z_i - Z_{i-1}) \cos\left(\frac{\omega}{2} (t_i + t_{i-1})\right) \times \frac{\sin\frac{\omega}{2} (t_i - t_{i-1})}{\frac{\omega}{2} (t_i - t_{i-1})}$$

(2.7)

$$\operatorname{Im}[Z(\omega)] = \sum_{i=1}^{N} (Z_i - Z_{i-1}) \sin\left(\frac{\omega}{2} (t_i + t_{i-1})\right) \times \frac{\sin\frac{\omega}{2} (t_i - t_{i-1})}{\frac{\omega}{2} (t_i - t_{i-1})}$$

(2.8)

By back substitution from the time responses at different times, the thermal network is derived.

#### Network Identification Methods by Deconvolution (NID) by Szekeley [29][30] [31]

Let the response be approximated by sum of exponential terms,

$$a(t) = \sum_{i=1}^{N} a_i (1 - \exp(-t/\tau_i))$$

(2.9)

Let  $R(z) = \lim_{\alpha \to 0} \frac{\text{magnitudes related to time constants between z and z} + \delta z}{\delta z}$

$$a(t) = \int_{-\infty}^{\infty} R(\zeta)(1 - \exp(-t/\exp(\zeta)))d\zeta$$

(2.10)

Let

$$z=ln\ t$$

(logarithmic of time) (2.11)

$$a(z) = \int_{-\infty}^{\infty} R(\zeta)(1 - \exp(-\exp(z - \zeta))d\zeta$$

(2.12)

This is convolution type integral equation for unknown  $R(\zeta)$  function. By differentiating a(z),

$$M_1 = \frac{d}{dz}a(z) = R(z) \otimes W(z)$$

(2.13)

where, W(z) = exp(z-exp(z)) and  $\otimes$  is convolution operator.

Thus, by deconvolving the differential of the logarithmic time response by the fixed function, W(z), the thermal network can be identified.

#### **Elmore Delay Technique [5]:**

In [5] by Ciappa et.al, a modified extraction method is developed. Most extraction methods use deconvolution method or multi-exponential fitting to calculate the thermal time constants. The Elmore technique assumes the IGBT module is a 1-dimensional thermal model as heat flows from top layer to lower layers. However, in the cases where the heat transfers laterally and the thermal interference laterally is significantly high, modified Elmore technique is used. In the

modified Elmore technique, the thermal impedance at each layer obtained from the step response of the Finite Element Modeling (FEM) model of IGBT is described as a first order approximation by two weighted exponentials, to estimate the temperature values close to FEM values described by (2.14).

$$Z_{thi} = \alpha_i R_i \left( 1 - \exp(\frac{-t}{\alpha_i R_i C_{1i}}) \right) + (1 - \alpha_i) R_i \left( 1 - \exp(\frac{-t}{(1 - \alpha_i) R_i C_{2i}}) \right)$$

(2.14)

The first time constant,  $\tau_{li}$ ,  $R_i$   $C_i$  is a short time constant (milliseconds) while  $\tau_{2i}$ ,  $R_iC_{2i}$  is a long time constant(seconds) to approximate the asymptotic behavior of thermal impedance curve both described in (2.15).

$$\tau_{1i} = \int_{0}^{\infty} \left[ 1 - \frac{Z_{thi}(t)}{R_{i}} \right] dt \text{ and } \frac{1}{\tau_{2i}} = \frac{1}{R_{i}} \frac{d}{dt} \left( Z_{thi}(t) \right)_{t=\theta}$$

(2.15)

Thus, the thermal impedance can be represented by 2n parallel resistor-capacitance couples and written as

$$Z_{thi} = \sum_{j=1}^{2n} R_j \left( 1 - \exp(\frac{-t}{\tau_j}) \right)$$

(2.16)

The modified Elmore technique is made up of Foster networks used to represent each layer independently and enables thermo-mechanical and reliability investigations.

Disadvantages: For very high frequencies, >100 kHz, the Foster network and hence the modified Elmore technique fails to be accurate.

Figure 2.2. Modified Elmore technique applied to compact thermal model of two chips IGBT [3].

Real time based thermal models were also described in [24] by M. Mussalam and C.M. Johnson, using FEM. FEM models though accurate, are limited due to high computation time. Similar methodology as Ciappa's model is used but instead of modified Elmore's method with two RC circuits, multi-exponentials method with four RC circuits is used [5][6][24].

Nyquist Plot[34]: According to Kawka et al, an accurate curve fitting model can be obtained with the number of RC time constants, n being no more than 3. Fast Fourier Transform is used to calculate the transient response to particular power dissipation. First, the parameters from the clearly visible circles are determined for each circle. Time constants are obtained by applying  $\omega t=1$  in the points where  $Imaginary\ part\ of\ [Zth(j\omega)]$  reaches a minimum. "A", the chord of the circle, and  $\alpha$  is extracted from the angle at which the center point is seen from the real axis. The curve fit is checked, if an extra circle with parameters tuned is needed for accuracy.

$$Z_{th} = \sum \frac{A_i}{(1 + jw\tau_i)^{1+\alpha_i}}$$

(2.17)

This method cannot be transformed as the impedance of an RC thermal network and hence for simulations in SPICE. Notice that the denominator of the thermal impedance function has a

power term ( $\alpha$ ) which makes it a non-linear expression. Time domain simulations based on the equations is possible.

Compact Thermal Models: Compact thermal models were developed to describe the thermal interference between different chips in a module. Network parameters are deployed using Deconvolution theory from Finite Element Methods (FEM). In [5][6], each layer is represented by two parallel RC networks in series as described by equation (2.10). The thermal impedance matrix and its relation to the temperatures and power dissipations are described in equation (2.18) [28].

$$Z_{\text{thi}} = R_{1} \left( 1 - \exp\left(\frac{t}{R_{1}C_{1}}\right) \right) + R_{2} \left( 1 - \exp\left(\frac{t}{R_{2}C_{2}}\right) \right)$$

(2.18)

$$\begin{bmatrix} T_{j1} \\ T_{j2} \\ T_{j3} \\ . \\ . \\ . \\ T_{jm} \end{bmatrix} = \begin{bmatrix} Z_{11}Z_{12}.....Z_{m} \\ Z_{21}Z_{22}.....Z_{m} \\ . \\ . \\ . \\ . \\ . \\ . \\ . \\ P_{m} \end{bmatrix} \begin{bmatrix} P_{j} \\ P_{2} \\ P_{3} \\ . \\ . \\ . \\ . \\ . \\ P_{m} \end{bmatrix}$$

$$(2.19)$$

Measurement of temperatures for experimental verification is based on diode sensor.

Fourier based thermal model [32][33] is based on the solution of the heat equation in 2D as shown in (2.20). The solution to (2.20) is of the form shown in (2.21).

$$\alpha_{i} \left( \frac{d^{2}T_{i}(x, y, t)}{dx^{2}} + \frac{d^{2}T_{i}(x, y, t)}{dy^{2}} \right) + G'_{i}(x, y, t) = \frac{dT_{i}(x, y, t)}{dt}$$

for i=1, 2,..,m (2.20)

$$T(x, y, t) = \sum_{m=0}^{\infty} \sum_{n=0}^{\infty} T_{mn}(t) \cos \frac{m\pi x}{W} \cos \frac{n\pi y}{L}$$

(2.21)

where x, y are the spatial terms, t is time,  $T_i$  is the temperature,  $\alpha_i$ ,  $G'_i$  are constants.

#### Finite Difference Thermal Model: Hefner Model: Reichl, Hefner et al [21]

Hefner model is developed from the thermal heat equations in 3D as described in (2.22).

$$A\rho c \frac{\partial T}{\partial t} = Ak \frac{\partial^2 T(z)}{\partial z^2}$$

(2.22)

where  $\rho$  is the density of the material with units  $g/cm^3$  and c is the specific heat of the material with units J/gK.

It should be noted that the heat diffusion equation describes the temperature gradient in all three dimensions of the rectangular coordinate plane (x, y, and z).

Thermal Coupling Consideration: The thermal model is derived from the heat equation in 3D in Saber using MAST models. The assumption of y and x axis symmetry simplifies the equation to a one dimensional heat flow in the z direction and is simplified using finite Difference Method.

Chip thermal model: Includes heat source option, i.e. heat dissipated as a function of depth and assumes triangular or trapezoidal heat sources. A quasi-logarithmical grid of evenly spaced nodes (grid) within a segment, where the segment size increases logarithmically with distance from heat source, is used for simulation.

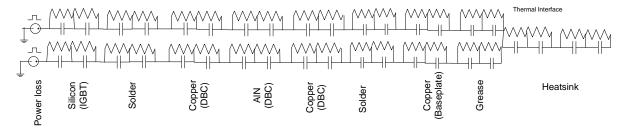

*DBC/* base plate: Heat spreading laterally from the silicon chip is assumed to be at 45° and cannot spread laterally beyond the DBC or base plate as shown in Figure 2.3. The effective heat flow approach describes a heat flow area that increases with depth into the package. This is done by combining the components of heat flow area due to cylindrical heat spreading along the edges of the chip, the spherical heat spreading at the corners of the chip, and the rectangular coordinate component of heat flow directly beneath the chip.

Thermal coupling: A coupling resistor is placed between the case nodes of the top IGBT chip and diode. The case node is the bottom node of the DBC layer that connects to the base-plate layer. Another coupling resistor is placed between the case nodes of the top IGBT and bottom diode. Finally, a resistor is placed between the case nodes of the bottom IGBT chip and diode.

Another coupling network must be considered between DBC's since each DBC shares a common base-plate. A capacitance is considered between DBC layers and represents the heat capacitance not accounted for in the vertical thermal networks. All remaining volume is accounted for in the periphery nodes.

Disadvantages: The heat transfer at the edges is assumed to be at 45° C when it is supposed to be based on the ratio of their thermal conductivities.

#### **Comparison**:

Table 2.2 compares the various thermal models for complexity, accuracy, and multi-chip interfaces. Most of the models are based and curve-fit on FEM analysis in literature and hence complicated. The Elmore technique and multi-exponential methods use a finite number of RC components for all layers of semiconductor packaging.

Figure 2.3. Spacing of the thermal nodes within package and base-plate model [21].

Table 2.2. Comparison of different thermal models from literature.

| Thermal<br>Method                    | Computation<br>Complexity in<br>analysis | Individual<br>layer<br>dimensions<br>required | Accuracy<br>(rank)                          | Experimental<br>input                          | Multi-chip<br>interface | Comments                                             |

|--------------------------------------|------------------------------------------|-----------------------------------------------|---------------------------------------------|------------------------------------------------|-------------------------|------------------------------------------------------|

| Foster                               | Simplest                                 | No                                            | Universal Less accurate at high frequencies | No                                             | No                      | Commonly used by manufacturers                       |

| Cauer                                | Less complex                             | Yes                                           | Universal<br>Accurate                       | No                                             | No,<br>Difficult<br>1D  | Commonly used                                        |

| FEM                                  | Less complex,<br>but time<br>consuming   |                                               |                                             | No                                             | modeled                 | Large computation time and memory                    |

| Modified<br>Elmore<br>(Ciappa)[5]    | Complex<br>Less time<br>consuming        | Yes                                           | Universal<br>More accurate                  | Experimental validation at certain points      | Modeled                 | Combines FEM and two RC parallel circuits            |

| FEM+<br>Multi<br>exponential<br>[24] | Complex<br>Less time<br>consuming        | Yes                                           | Most accurate                               | Experimental validation at certain points only | Modeled                 | Combines FEM and RC parallel (usually 4) circuits.   |

| Fourier(Sa<br>nti et<br>al)[32]      | Complex                                  | Yes                                           | Universal.                                  | No                                             | Modeled                 | Thermal diffusion<br>based, computation<br>time high |

| Hefner's model                       | Complex                                  | Yes                                           | Accurate                                    | No                                             | Modeled                 | Finite difference method                             |

#### **Number of RC cells**

Thermal models are an important factor in lifetime estimation of power semiconductors. Distributed thermal models are used to model the temperature distribution in different layers in the power module. Lumped models are used because of ease of modeling.

Ciappa et al proposed the Elmore technique based RC model to model the lateral distribution of heat using RC- models. Elmore based model uses two RC time constants, to model low frequency and high frequency components. Mussallam et al proposed the multi-exponential model for each layer, using four in their model. In [37], the number of RC cells in a thermal

model is shown to be dependent on the time-constant requirement. For example, for 2 ms time scale, 6 cells were used; 7 cells for 50 us; and 11 for 5 ns. The individual RC values are based on a size ratio that is determined by the user for accuracy. The reference [37] also shows that there are oscillations ("waviness") for a size ratio greater than 4:1. A detailed analysis of the model development was presented.

A new model reduction method was proposed by J. Antonios et al [36], showing the relation between the number of RC cells and the relative error in thermal model for each layer. According to their study, the lower the time constant, the less the number of RC cells required. However, the methodology in optimizing the RC cells was not clear, as their model used 400 RC cells for each layer to accurately model the temperature in an IGBT module. There is a need to systematically determine the number of RC cells in each layer in an IGBT model. Encapsulant is modeled in [38].

# 2.3 Lifetime Estimation: Stress-Strain Relationship to Lifetime and Rainflow Algorithm

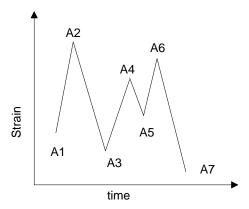

The following section introduces the relationship between stress-strain and the number of cycles to failure. Each strain swing (rise and fall) of same amplitude causes a closed hysteresis loop and is considered as a cycle. The total degradation for a given load profile, is calculated by considering the cumulative effect of each hysteresis loop. In such a case, cycle counting is necessary in order to be able to obtain stresses and also count the number of hysteresis loops in a given profile. Rainflow algorithm is a popular counting algorithm used for semiconductor reliability estimation.

#### 2.3.1 Introduction to Mechanical Stress-Strain

From the temperature profiles, the most common failures, wirebond lift-off and solder fatigue have to be modeled to estimate their respective lifetime and the IGBT lifetime. The stress on the metal (Al wires or solder) determines the degradation and the main cause of failure. Metals expand on heating, and the ratio of increase in length to the original length of the metal is known as strain. This strain causes a stress depending on the type of strain. For elastic strain, the stress and strain are related by Young's modulus. The strain due to thermal expansion is given by [39].

$$\gamma_i = c \times (T(i) - T_0) \times \Delta \alpha \tag{2.23}$$

where T(i) is the temperature increment,  $\gamma$  is the strain,  $\Delta \alpha$  is the ratio of temperature coefficients between two layers and c is the constraint ratio, c=1/(1-v), where v is the Poisson ratio.

The strain in different layers of the module causes a shearing stress on the binding, and is given by stress-strain plots. The stress  $\sigma$  for elastic strain is given by

$$\frac{\sigma}{\Delta T} = \Delta \alpha \times E \times C \tag{2.24}$$

where *E* is the Young's modulus of elasticity.

The total strain is the sum of elastic strain, plastic strain and creep as given by (2.25). Plastic strain is the main cause of permanent damage and so most models describe the plastic strain.

$$\varepsilon_{tot} = \varepsilon_{elastic} + \varepsilon_{plastic}$$

(2.25)

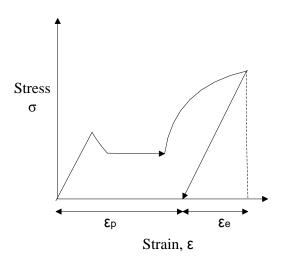

Linear elastic strain: The portion of strain which can be recovered upon unloading,  $\varepsilon_e$ , shown in Figure 2.4.

Plastic strain: The portion of strain that cannot be recovered upon unloading  $\varepsilon_p$ , shown in Figure 2.4. The relation between plastic strain and stress is given by equation (2.26)

$$\varepsilon_p = \left(\frac{\sigma}{k}\right)^{1/n} \tag{2.26}$$

where K is the strength coefficient, n is the strain hardening exponent.

The strength coefficient is defined in terms of true stress at fracture,  $\sigma_f$  and true strain

$\varepsilon_f$ , as

$$\mathbf{K} = \frac{\sigma_f}{\varepsilon_f^n} \tag{2.27}$$

Then plastic strain,

$$\varepsilon_p = \varepsilon_f \left(\frac{\sigma}{\sigma_f}\right)^{1/n}$$

(2.28)

Thus the total strain, the sum of elastic and plastic strains, is given by

$$\varepsilon_{t} = \varepsilon_{e} + \varepsilon_{p} \tag{2.29}$$

Substituting equation (2.2) and equation (2.28) in (2.29), we get

Figure 2.4. Stress-strain plot for plastic and elastic strain.

$$\varepsilon_t = \frac{\sigma}{E} + \varepsilon_f \left(\frac{\sigma}{\sigma_f}\right)^{1/n} \tag{2.30}$$

The lifetime prediction method would result in getting the stress from the stress-strain relationship after getting the strain based on temperature. For variable loads/stresses, most models assume linear accumulation of the cyclic fatigue especially for wire-bond reliability and Anand's model describes a non-linear accumulation [43].

For determining the lifetime, two different approaches are common, [39]

a) Stress-life model- Wohler: Empirical relation (power law) between stress and lifetime are estimates only.  $N=10^{(-c/b)}$  S<sup>(1/b)</sup> for 1000<N< 10<sup>6</sup>.

Disadvantage: This model cannot be used to estimate lifetimes below 1000 cycles. It does not account for plastic strain [39].

b) Strain-life model: For long lifetimes, where stress and strain are linearly related and plastic strain is negligible, stress-life and strain-life models are equivalent. For low cycle fatigue, i.e. high level loads, the cyclic stress-strain response and the material behavior are best modeled by strain-controlled conditions. Crack growth is not explicitly accounted. This model is commonly used in semiconductor lifetime prediction.

For strain-life approach, the material properties, the stress-strain history at the notch, cycle counting, mean stress effect incorporation and damage summation methods are needed.

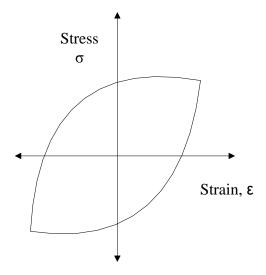

**Stress-Strain relationship**: A cyclic inelastic loaded metal has stress-strain in the form of a hysteresis loop, as shown in Figure 2.5. The total width of the loop is  $\Delta\varepsilon$  or the total strain range. The total height of the loop is  $\Delta\sigma$  or the total stress range. The total strain in terms of amplitudes is given by (2.31) [39]

$$\frac{\Delta\varepsilon}{2} = \frac{\Delta\sigma}{2E} + \left(\frac{\sigma}{2K}\right)^{1/n} \tag{2.31}$$

The factor of 2 in equation (2.31), compared to that in equation (2.30), is due to the inclusion of reversal amplitudes.

For stress-life data, the relation between stress and the cycles to failure  $N_f$  is given by

$$\frac{\Delta\sigma}{2} = \sigma_f'(2N_f)^b \tag{2.32}$$

Coffin-Manson plastic strain-life model is