## University of Tennessee, Knoxville TRACE: Tennessee Research and Creative Exchange

**Doctoral Dissertations**

**Graduate School**

8-2005

# Low-Voltage Analog Circuit Design Using the Adaptively Biased Body-Driven Circuit Technique

Stephen Christopher Terry University of Tennessee - Knoxville

Follow this and additional works at: https://trace.tennessee.edu/utk\_graddiss

Part of the Electrical and Electronics Commons

#### **Recommended Citation**

Terry, Stephen Christopher, "Low-Voltage Analog Circuit Design Using the Adaptively Biased Body-Driven Circuit Technique." PhD diss., University of Tennessee, 2005. https://trace.tennessee.edu/utk\_graddiss/2299

This Dissertation is brought to you for free and open access by the Graduate School at TRACE: Tennessee Research and Creative Exchange. It has been accepted for inclusion in Doctoral Dissertations by an authorized administrator of TRACE: Tennessee Research and Creative Exchange. For more information, please contact trace@utk.edu.

To the Graduate Council:

I am submitting herewith a dissertation written by Stephen Christopher Terry entitled "Low-Voltage Analog Circuit Design Using the Adaptively Biased Body-Driven Circuit Technique." I have examined the final electronic copy of this dissertation for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Doctor of Philosophy, with a major in Electrical Engineering.

Benjamin J. Blalock, Major Professor

We have read this dissertation and recommend its acceptance:

Syed K. Islam, Charles L. Britton, Jr., M. Nance Ericson, Vasilios Alexiades

Accepted for the Council:

Carolyn R. Hodges

Vice Provost and Dean of the Graduate School

(Original signatures are on file with official student records.)

To the Graduate Council:

I am submitting herewith a dissertation written by Stephen Christopher Terry entitled "Low-Voltage Analog Circuit Design Using the Adaptively Biased Body-Driven Circuit Technique". I have examined the final electronic copy of this dissertation for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Doctor of Philosophy, with a major in Electrical Engineering.

Benjamin J. Blalock

Major Professor

We have read this dissertation and recommend its acceptance:

Syed K. Islam

Charles L. Britton, Jr.

M. Nance Ericson

Vasilios Alexiades

Accepted for the Council:

Anne Mayhew

Vice Chancellor and Dean of Graduate Studies

(Original signatures are on file with official student records.)

### Low-Voltage Analog Circuit Design Using the Adaptively Biased Body-Driven Circuit Technique

A Dissertation Presented for the Doctor of Philosophy Degree

The University of Tennessee, Knoxville

Stephen Christopher Terry August, 2005

### Acknowledgments

I wish to thank the members of my committee, Drs. Blalock, Islam, Britton, Ericson, and Alexiades, for reviewing my dissertation and providing helpful feedback and guidance. I would especially like to express my sincere gratitude to Dr. Ben Blalock for providing me with employment in his laboratory at UT for the last three and a half years. Dr. Blalock's tireless efforts to secure funding for cutting-edge research projects, his leadership of the analog and mixed-signal lab at UT, and most importantly his friendship, are greatly appreciated. In addition, I would like to thank Robert Greenwell and Brandon Weathers for help with layout and verification, and Jesse Richmond and Sam Caylor for help with test and characterization.

Throughout the time that I have been a doctoral student I have had the opportunity to work on multiple research projects that have provided both funding and unique learning experiences. I would like to convey my earnest thanks to Dr. Mohammad Mojarradi and his group at the NASA Jet Propulsion Laboratory (JPL) for providing numerous challenging research projects. In addition, I would like to acknowledge the Defense Threat Reduction Agency (DTRA) and Boeing for providing funding for the Very Deep Sub-Micron (VDSM) research project, and the University of Tennessee Center for Environmental Biotechnology (UT-CEB) and NASA for providing funding for the bioluminescent bioreporter integrated circuit (BBIC) development project. Finally, I would like to thank Honeywell for providing university gift grants directly supporting research on body-driven circuits.

Most importantly I wish to acknowledge my family and friends for their support during my doctoral program. I would especially like to thank my wife, Becky, for providing much needed support and encouragement every step of the way.

### Abstract

The scaling of MOSFET dimensions and power supply voltage, in conjunction with an increase in system- and circuit-level performance requirements, are the most important factors driving the development of new technologies and design techniques for analog and mixed-signal integrated circuits. Though scaling has been a fact of life for analog circuit designers for many years, the approaching 1-V and sub-1-V power supplies, combined with applications that have increasingly divergent technology requirements, means that the analog and mixed-signal IC designs of the future will probably look quite different from those of the past. Foremost among the challenges that analog designers will face in highly scaled technologies are low power supply voltages, which limit dynamic range and even circuit functionality, and ultra-thin gate oxides, which give rise to significant levels of gate leakage current.

The goal of this research is to develop novel analog design techniques which are commensurate with the challenges that designers will face in highly scaled CMOS technologies. To that end, a new and unique body-driven design technique called adaptive gate biasing has been developed. Adaptive gate biasing is a method for guaranteeing that MOSFETs in a body-driven simple current mirror, cascode current mirror, or regulated cascode current source are biased in saturation—independent of operating region, temperature, or supply voltage—and is an enabling technology for high-performance, low-voltage analog circuits. To prove the usefulness of the new design technique, a body-driven operational amplifier that heavily leverages adaptive gate biasing has been developed. Fabricated on a 3.3-V/0.35-µm partially depleted silicon-on-

iv

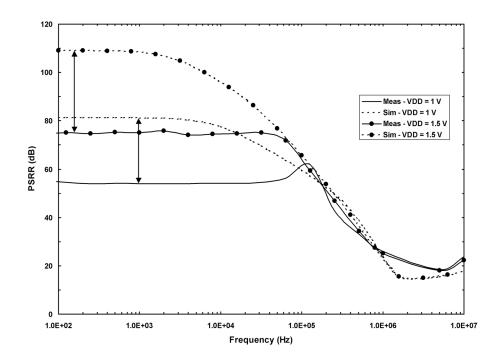

insulator (PD-SOI) CMOS process, which has nMOS and pMOS threshold voltages of 0.65 V and 0.85 V, respectively, the body-driven amplifier displayed an open-loop gain of 88 dB, bandwidth of 9 MHz, and PSRR greater than 50 dB at 1-V power supply.

### Table of Contents

| Chapter 1: | Intro | duction                                                        |   |

|------------|-------|----------------------------------------------------------------|---|

|            | 1.1:  | Trends in Analog and Mixed-Signal Integrated Circuit Design    | 1 |

|            | 1.2:  | Research Goals                                                 | 3 |

|            | 1.3:  | Overview of the Dissertation                                   | 4 |

|            |       |                                                                |   |

| Chapter 2: | СМО   | S Technology Trends and Implications for Analog Circuit Design | • |

|            |       | · · · · · · · · · · · · · · · · · · ·                          |   |

|            | 2.1:  |                                                                |   |

|            | 2.2:  | Scaling Trends for Digital and Analog CMOS Technologies        |   |

|            |       | 2.2.1: Introduction to Technology Scaling                      |   |

|            |       | 2.2.2: Scaling Trends for Digital CMOS Technologies 1'         |   |

|            |       | 2.2.3: Scaling Trends for Analog CMOS Technologies 14          | 4 |

|            | 2.3:  | The Low-Voltage Challenge to Analog Circuit Design 16          | 3 |

|            |       | 2.3.1: Power Supply Voltage and Power Dissipation 17           | 7 |

|            |       | 2.3.2: Power Supply Voltage and Circuit Functionality 22       | 2 |

|            |       | 2.3.3: Gate Leakage Current 29                                 | 9 |

|            |       | 2.3.4: The Future of Analog Circuit Design                     | 6 |

|            | 2.4:  | Low-Voltage Analog Design Techniques                           |   |

|            |       | 2.4.1: Circuit-Level Design Techniques 39                      |   |

|            |       | 2.4.2: Transistor-Level Design Techniques                      |   |

|            |       | 2.4.3: Comparison of the Low-Voltage Design Techniques 49      |   |

|            | 2.5:  | Conclusion                                                     | 1 |

|            |       |                                                                |   |

| Chapter 3: | Intro | duction to Body Driving53                                      | 2 |

| Chapter 5. | 3.1:  |                                                                |   |

|            | 3.2:  | Technology Choices for Body Driving                            |   |

|            | 5.2.  | 3.2.1: Standard Bulk CMOS                                      |   |

|            |       | 3.2.2: Twin-Well Bulk CMOS                                     |   |

|            |       | 3.2.3: Partially Depleted Silicon-on-Insulator                 |   |

|            |       | 3.2.4: Semiconductor Technology Chosen for This Work 6         |   |

|            | 3.3:  | DC Biasing Considerations                                      |   |

|            | 3.4:  | Small-Signal Models for Body-Driven MOSFETs 63                 |   |

|            |       | 3.4.1: Complete Electrical Model                               |   |

|            |       | 3.4.2: DC Model                                                | 6 |

|            |       | 3.4.3: AC Model                                                |   |

|            | 3.5:  | SPICE Model                                                    |   |

|            |       | 3.5.1: Intrinsic Models—BSIM3V3 vs. EKV2.6                     | 4 |

|            |       | 3.5.2: Extrinsic Models 77                                     |   |

|            | 3.6:  | Temperature Characteristics 80                                 | C |

|            | 3.7:  | Conclusions                                                    | 2 |

| Chapter 4: | Liter | ature Review                                                     |

|------------|-------|------------------------------------------------------------------|

|            | 4.1:  | Introduction                                                     |

|            | 4.2:  | Literature Review—Body-Driven Current Mirrors                    |

|            |       | 4.2.1: Simple Current Mirror I                                   |

|            |       | 4.2.2: Simple Cascode Current Mirror                             |

|            |       | 4.2.3: Simple Current Mirror II                                  |

|            |       | 4.2.4: Regulated Cascode Current Mirror                          |

|            |       | 4.2.5: Comparison of the Body-Driven Current Mirrors 95          |

|            | 4.3:  | Literature Review—Body-Driven Differential Pairs                 |

|            |       | 4.3.1: Differential Pair with Static Gate Bias                   |

|            |       | 4.3.2: Complementary Body-Driven Differential Pairs 100          |

|            |       | 4.3.3: Differential Pair with "Floating Battery" Gate Bias 102   |

|            |       | 4.3.4: Comparison of the Body-Driven Differential Pairs 104      |

|            | 4.4:  | Literature Review—Body-Driven Operational Amplifiers 104         |

|            |       | 4.4.1: Body-Driven OTA                                           |

|            |       | 4.4.2: Body-Driven Op-Amp I                                      |

|            |       | 4.4.3: Body-Driven Op-Amp II                                     |

|            |       | 4.4.4: Comparison of the Body-Driven Amplifiers                  |

|            | 4.5:  | Conclusion                                                       |

|            |       |                                                                  |

|            |       |                                                                  |

| Chapter 5: | Desi  | gn and Measurement of a High-Performance Body-Driven Opera-      |

| •          |       | I Amplifier                                                      |

|            | 5.1:  | Introduction                                                     |

|            | 5.2:  | Designing Body-Driven Current Mirrors with Adaptive Gate Bias .  |

|            |       |                                                                  |

|            |       | 5.2.1: A Universal MOSFET V <sub>DSAT</sub> Extractor            |

|            |       | 5.2.2: Body-Driven Simple Current Mirror with Adaptive Gate Bias |

|            |       |                                                                  |

|            |       | 5.2.3: Body-Driven Cascode Current Mirrors with Adaptive Gate    |

|            |       | Bias 125                                                         |

|            | 5.3:  | Design and Measurement of Op-Amp I                               |

|            |       | 5.3.1: Design Goals 128                                          |

|            |       | 5.3.2: Op-Amp Design 130                                         |

|            |       | 5.3.3: Measurement Results 140                                   |

|            |       | 5.3.4: Conclusion                                                |

|            | 5.4:  | Design and Measurement of Op-Amp II 146                          |

|            | ••••  | 5.4.1: Op-Amp Design                                             |

|            |       | 5.4.2: Op-Amp Measurement Results                                |

|            | 5.5:  | Comparison of the Body-Driven Op-Amp to Other Low-Voltage Op-    |

|            | 2.0.  | Amps 172                                                         |

|            |       | 5.5.1: Defining Op-Amp Power Efficiency                          |

|            |       | 5.5.2: Op-Amp Comparisons                                        |

|            | 5.6:  | Conclusions                                                      |

| Chapter 6:  | The Application of Body-Driven Circuits to Analog and Mixed-Signal |                                                                                |  |  |

|-------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------|--|--|

|             | -                                                                  | ms                                                                             |  |  |

|             | 6.1:                                                               | Introduction                                                                   |  |  |

|             | 6.2:                                                               | Power Efficiency of a Two-Stage Body-Driven Amplifier 182                      |  |  |

|             |                                                                    | 6.2.1: Power Efficiency of a "Buffer" Circuit                                  |  |  |

|             |                                                                    | 6.2.2: Power Efficiency of a High-Resolution Circuit 186                       |  |  |

|             |                                                                    | 6.2.3: Conclusion                                                              |  |  |

|             | 6.3:                                                               | Body Driving with Absolute Minimum Circuits                                    |  |  |

|             | 6.4:                                                               | Body Driving and the Future of Analog Circuit Design 205                       |  |  |

| Chaptor 7   | Conol                                                              | lusion                                                                         |  |  |

| Chapter 7:  | 7.1:                                                               |                                                                                |  |  |

|             | 7.1.<br>7.2:                                                       | Conclusion       207         Original Contributions of This Research       208 |  |  |

|             | 7.2.<br>7.3:                                                       | Future Research Directions                                                     |  |  |

|             | 7.5.                                                               |                                                                                |  |  |

| References  |                                                                    |                                                                                |  |  |

|             |                                                                    |                                                                                |  |  |

| Appendices  |                                                                    |                                                                                |  |  |

|             |                                                                    |                                                                                |  |  |

| Appendix A: | -                                                                  | mp Measurement Set-Ups 220                                                     |  |  |

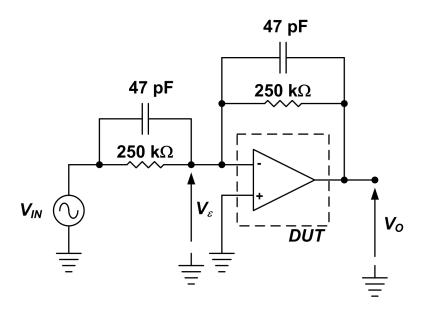

|             | A.1:                                                               | Open-Loop Voltage Gain 220                                                     |  |  |

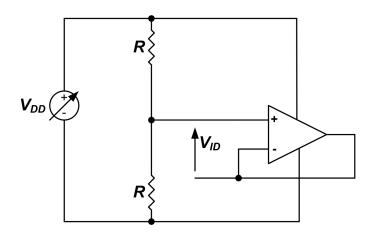

|             | A.2:                                                               | Power Supply Rejection Ratio (PSRR) 222                                        |  |  |

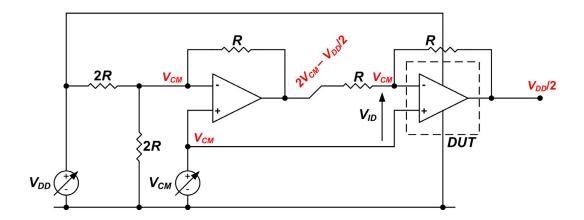

|             | A.3:                                                               | Common-Mode Rejection Ratio (CMRR) 223                                         |  |  |

| Vita        |                                                                    |                                                                                |  |  |

|             |                                                                    | ······································                                         |  |  |

## List of Tables

| Negative and positive effects of scaling critical MOSFET parameters $~\ldots~10$ $V_{DD}$ and $V_{TH}$ for HP, LOP, and LSP Digital Technologies at the 45-nm node |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Gate oxide thickness for HP, LOP, and LSP digital Technologies at the 45-                                                                                          |

| nm node                                                                                                                                                            |

| Key parameters for extrinsic MOSFET model [27]                                                                                                                     |

| Measured performance parameters for state-of-the-art body-driven opera-<br>tional amplifiers                                                                       |

| Summary of key measured parameters for the Mysia amplifier 171                                                                                                     |

| Comparison of low-voltage amplifiers reported in the literature 177                                                                                                |

| Comparison of the two buffer op-amp designs 185                                                                                                                    |

| Comparison of the two pipeline ADC op-amp designs 194                                                                                                              |

|                                                                                                                                                                    |

# List of Figures

| Figure 2.1:  | Cross section of a n-type bulk-Si MOSFET showing process parameters and device dimensions which are scaled                          |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2.2:  | Scaling trend for digital CMOS power supply voltage                                                                                 |

| Figure 2.3:  | Scaling trend for digital CMOS threshold voltage                                                                                    |

| Figure 2.4:  | Digital CMOS scaling trend for channel length and oxide thickness 14                                                                |

| Figure 2.5:  | Required CMOS scaling trend for highest-performance analog applications                                                             |

| 1 igure 2.0. | 16                                                                                                                                  |

| Figure 2.6:  | Simple analog circuit used to explore the relationship between SNR, power supply voltage, and power dissipation                     |

| Figure 2.7:  | Circuit showing the minimum power supply voltage required for an analog cir-                                                        |

|              | cuit 23                                                                                                                             |

| Figure 2.8:  | $V_{DD}$ overhead ( $V_{DD} - V_{DDmin}$ ) for the circuit of Figure 2.7 at the 45-nm node for all possible technology combinations |

| Figure 2.9:  | Power supply voltage required for a simple differential-input, single-ended output amplifier                                        |

| Figure 2.10: | $V_{DD}$ overhead ( $V_{DD} - V_{DDmin}$ ) for the circuit of Figure 2.9 at the 45-nm node                                          |

|              | for all possible technology combinations                                                                                            |

| Figure 2.11: | Power supply voltage required for a complementary differential pair 28                                                              |

|              | $V_{DD}$ overhead ( $V_{DD} - V_{DDmin}$ ) for the circuit of Figure 2.11 at the 45-nm node                                         |

|              | for all possible technology combinations                                                                                            |

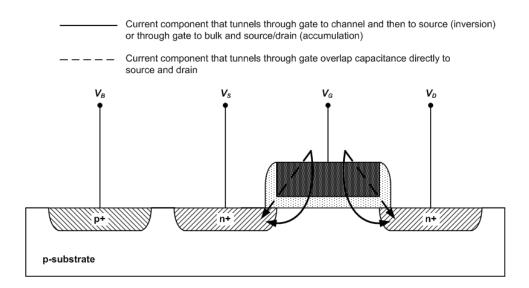

| Figure 2.13: | Cross section of a bulk CMOS MOSFET showing primary tunneling current                                                               |

|              | components [12]                                                                                                                     |

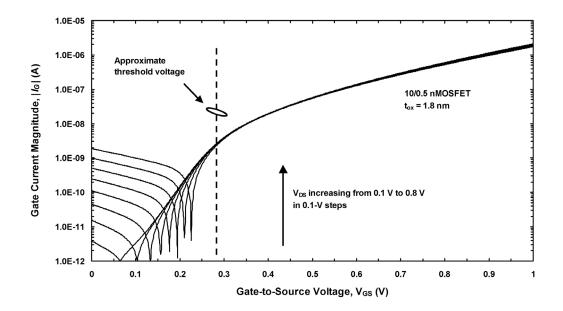

| Figure 2.14: | Simulated gate current versus $V_{GS}$ and $V_{DS}$ for a 10/0.5 nMOSFET with $t_{\text{ox}}$                                       |

| Figure 2.15  |                                                                                                                                     |

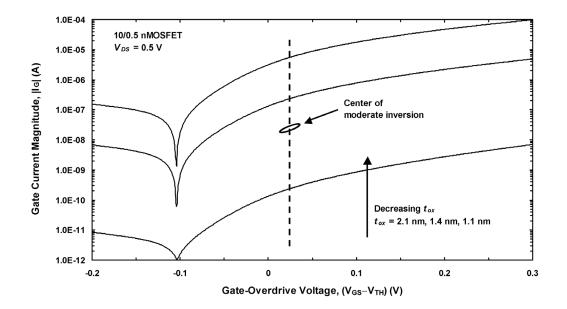

| Figure 2.15. | Simulated gate current versus gate-overdrive voltage ( $V_{GS}-V_{TH}$ ) and $t_{ox}$ for a 10/0.5 nMOSFET with $V_{DS}$ = 0.5 V    |

| Figure 2.16: | Simplified schematic of an op-amp circuit with common-mode level shifting                                                           |

| •            | at the input                                                                                                                        |

| Figure 2.17: | Common-mode level shifting for low-voltage complementary differential pairs                                                         |

| •            |                                                                                                                                     |

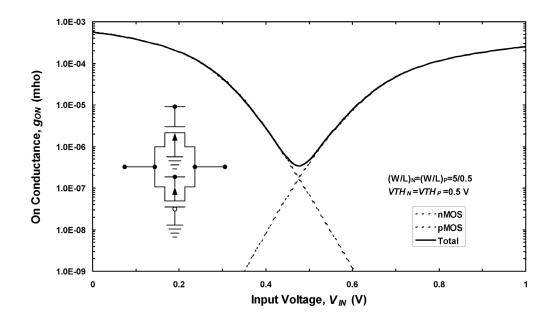

| Figure 2.18: | On conductance of a CMOS switch as a function of input voltage, $V_{DD}$ = 1 V                                                      |

| U            | 43                                                                                                                                  |

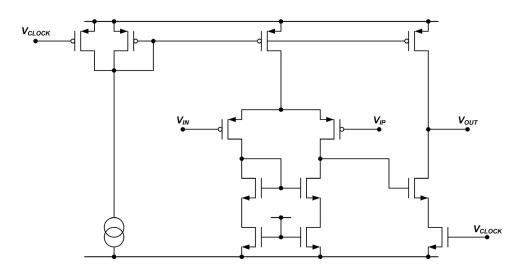

| Figure 2.19: | An example of a switched op-amp 44                                                                                                  |

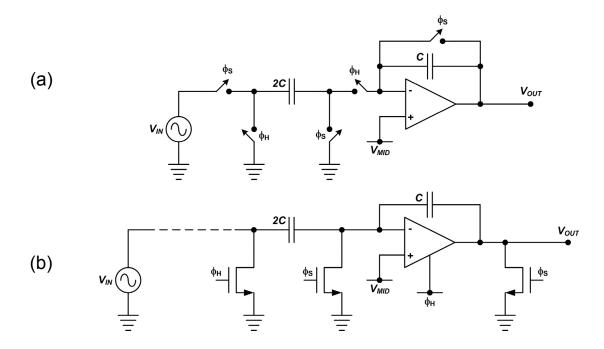

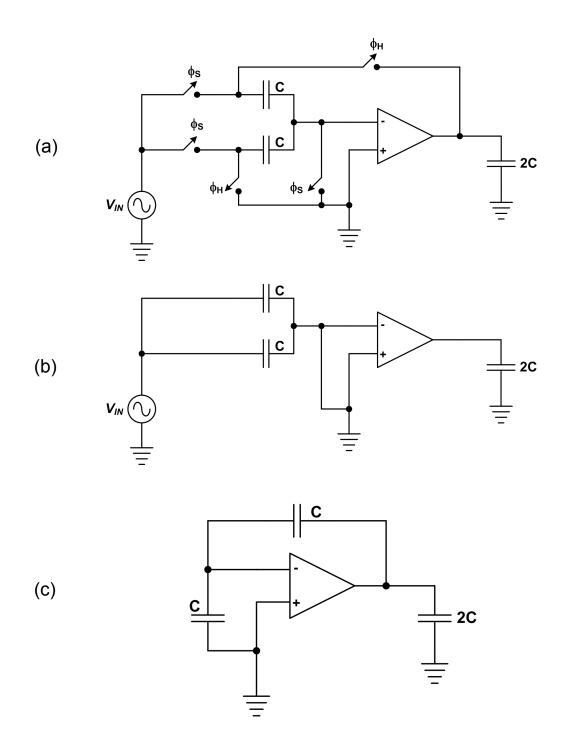

| •            | Example of (a) a standard switched-capacitor multiply-by-two stage and (b)                                                          |

| 0            | a switched-opamp multiply-by-two stage with no series switches 44                                                                   |

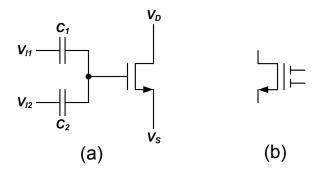

| Figure 2.21: | Floating gate MOSFET: (a) Schematic representation and (b) schematic                                                                |

|              | symbol [17]                                                                                                                         |

| Figure 2.22: | Schematics of (a) a floating-gate simple current mirror and (b) a floating-gate                                                     |

|              | differential pair [17]                                                                                                              |

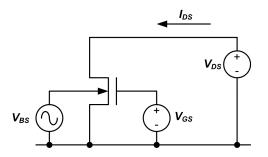

| Figure 2.23: | Schematic of a body-driven MOSFET 48                                                                                                |

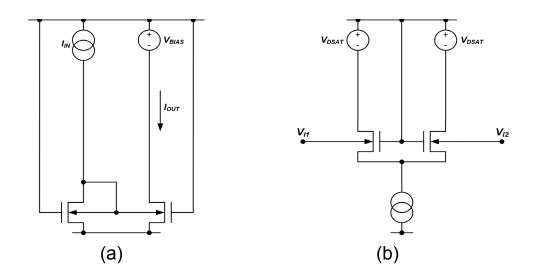

| Figure 2.24: | Schematics of (a) a body-driven simple current mirror and (b) a body-driven                                                         |

|              | differential pair [19]                                                                                                              |

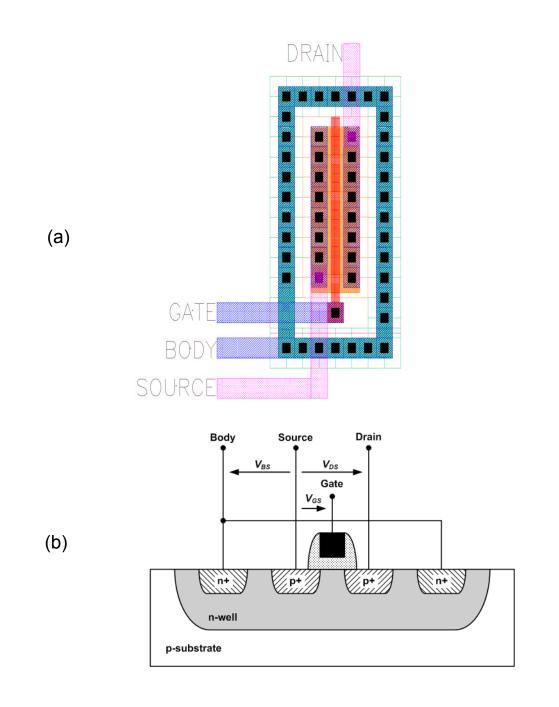

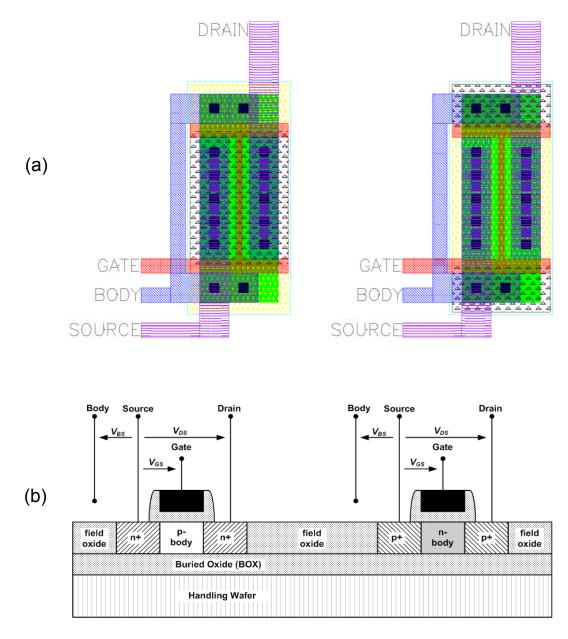

| Figure 3.1:  | A 10/0.5 pMOS body-driven MOSFET on a 0.5-µm n-well bulk CMOS process: (a) layout and (b) cross section                                                                                                                                    |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

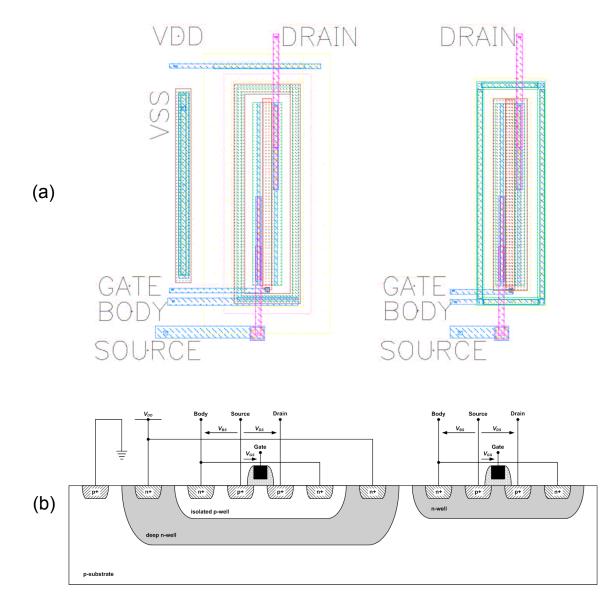

| Figure 3.2:  | 10/0.5 nMOS and 10/0.5 pMOS body-driven MOSFETs on a 0.12- $\mu$ m n-well                                                                                                                                                                  |

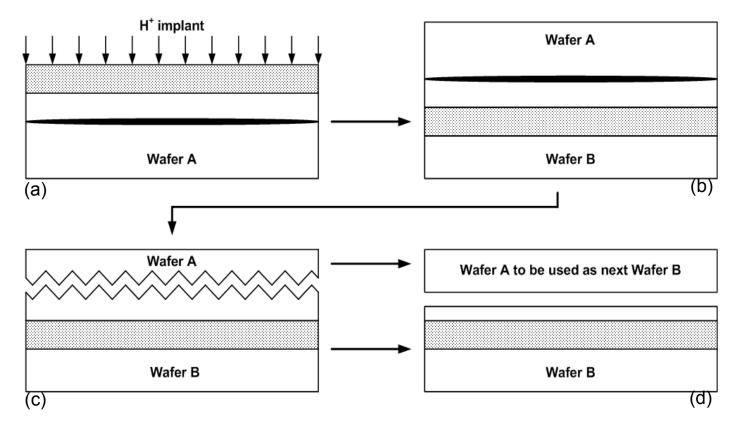

| Figure 3.3:  | (twin-well) bulk CMOS process: (a) layout and (b) cross section 56<br>Steps in the Smart-Cut® process: (a) hydrogen implant, (b) wafer bonding,<br>(c) wafer splitting, (d) polishing, and wafer A becomes future wafer B [25]58           |

| Figure 3.4:  | 10/0.5 nMOS and 10/0.5 pMOS body-driven MOSFETs on a $0.35$ -µm PD-<br>SOI CMOS process: (a) layout and (b) cross section (Note that the body con-<br>tact are at each end of the channel, but cannot be shown in the cross sec-<br>tion.) |

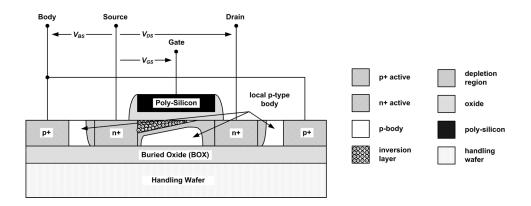

| Figure 3.5:  | Cross section of a PD-SOI MOSFET biased in strong inversion, saturation [1]                                                                                                                                                                |

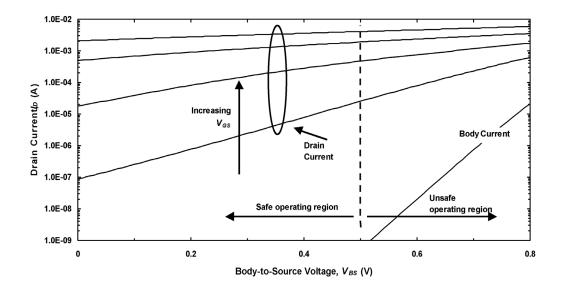

| Figure 3.6:  | Measured I <sub>D</sub> –V <sub>BS</sub> –V <sub>GS</sub> for a 8/0.5 M=16 (total W/L = 128/0.5) PD-SOI nMOSFET [1]                                                                                                                        |

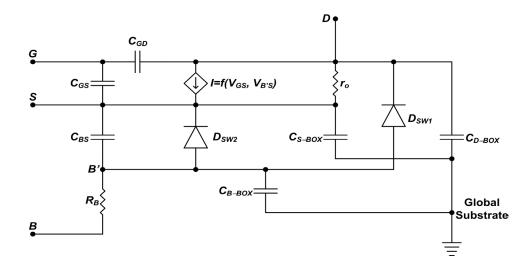

| Figure 3.7:  | Complete electrical model for a PD-SOI MOSFET                                                                                                                                                                                              |

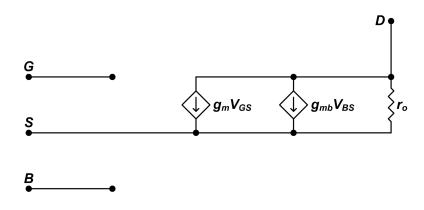

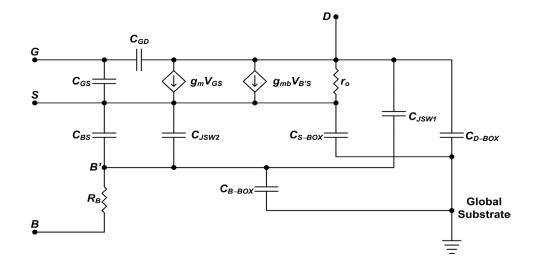

| Figure 3.8:  | Small-signal DC model for a MOSFET                                                                                                                                                                                                         |

| Figure 3.9:  | Small-signal AC model for a PD-SOI MOSFET                                                                                                                                                                                                  |

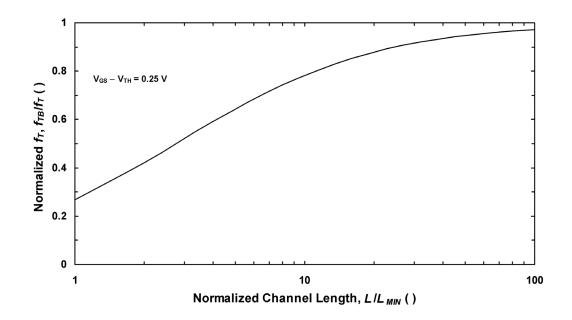

| Figure 3.10: | Normalized $f_T$ ( $f_{T,BD}/f_{T,GD}$ ) vs. normalized channel length (L/L <sub>MIN</sub> ) for a 0.35-<br>µm PD-SOI nMOSFET                                                                                                              |

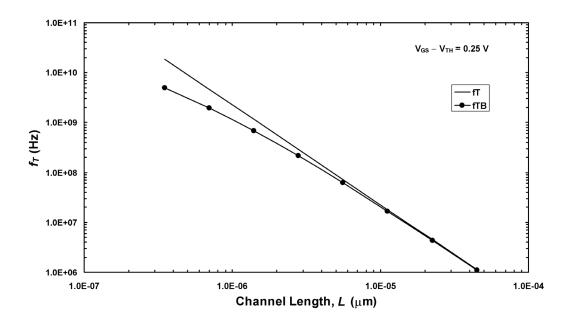

| Figure 3.11: | Body-driven and gate-driven f <sub>T</sub> versus channel length for a 0.35-μm PD-SOI nMOSFET                                                                                                                                              |

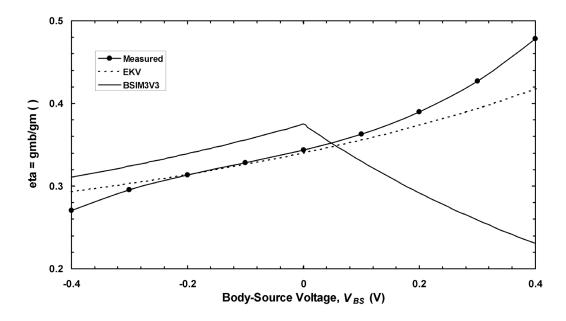

| Figure 3.12: | Comparison of measured and simulated (BSIM3V3 and custom generated EKV2.6) $\eta$ –V <sub>BS</sub> for an 8/0.5 M=16 PD-SOI nMOSFET                                                                                                        |

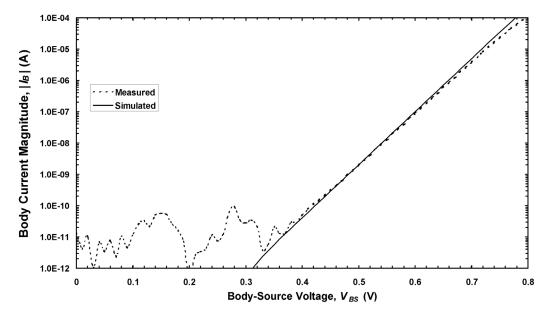

| Figure 3.13: | Comparison of measured and simulated (using a fitted parameter for JSW) $I_B - V_{BS}$ for an 8/0.5 M=16 PD-SOI nMOSFET                                                                                                                    |

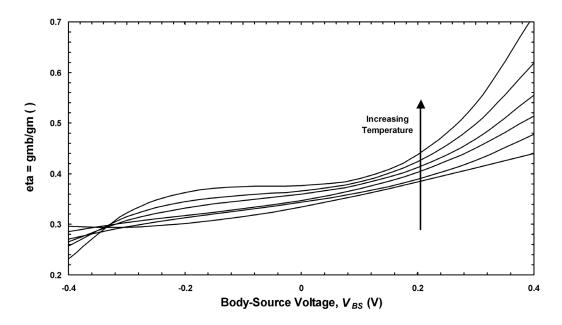

| Figure 3.14: | Measured $\eta$ –V <sub>BS</sub> for an 8/0.5 M=16 PD-SOI MOSFET; temperature is swept from 0°C to +125°C in 25°C steps                                                                                                                    |

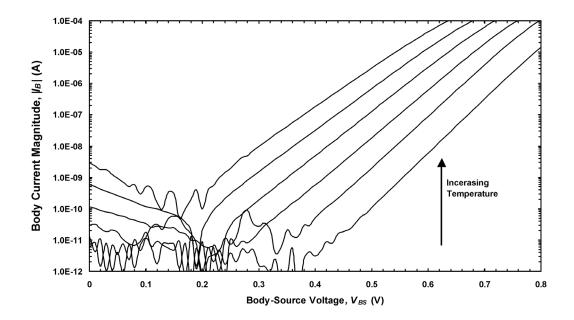

| Figure 3.15: | Measured I <sub>B</sub> –V <sub>BS</sub> for an 8/0.5 M=16 PD-SOI MOSFET; temperature is swept from 0°C to +125°C in 25°C steps                                                                                                            |

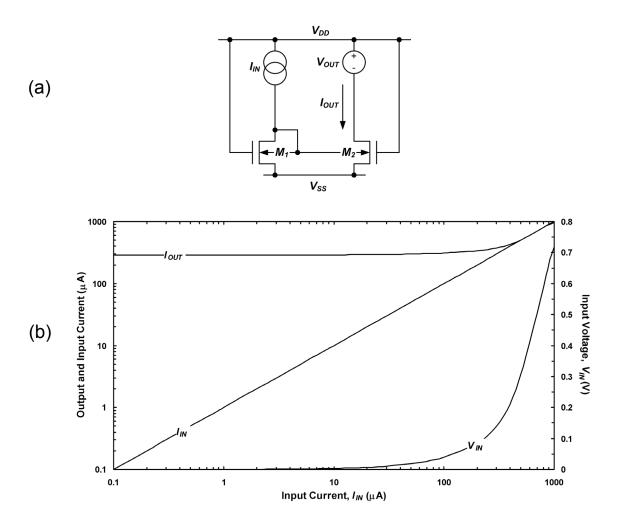

| Figure 4.1:  | Body-driven simple current mirror with static gate bias: (a) schematic [33] and (b) simulated transfer characteristic                                                                                                                      |

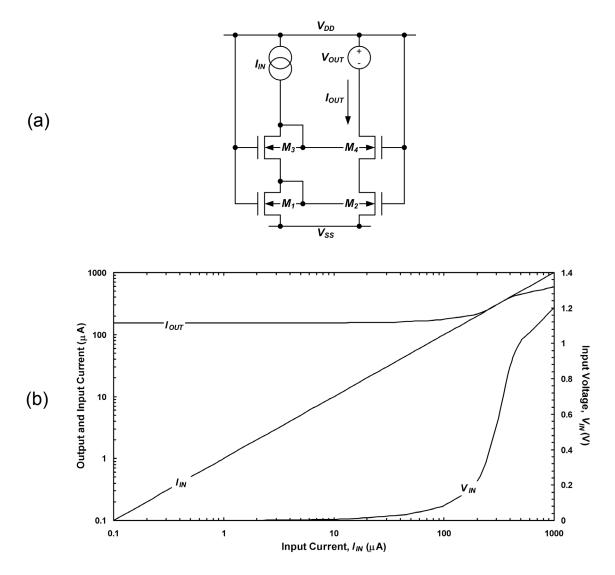

| Figure 4.2:  | Body-driven simple cascode current mirror with static gate bias: (a) schemat-<br>ic [34] and (b) simulated transfer characteristic                                                                                                         |

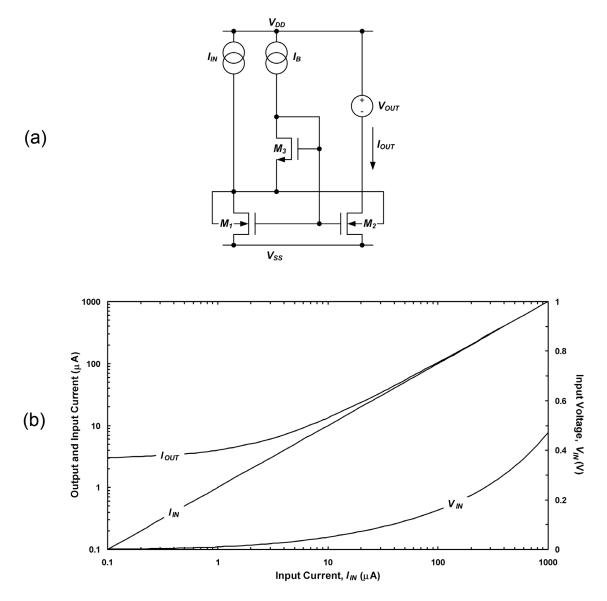

| Figure 4.3:  | Body-driven simple current mirror with level-shifted, dynamic gate bias: (a) schematic [35] and (b) simulated transfer characteristic (Bias current $I_B$ is 100 nA.)                                                                      |

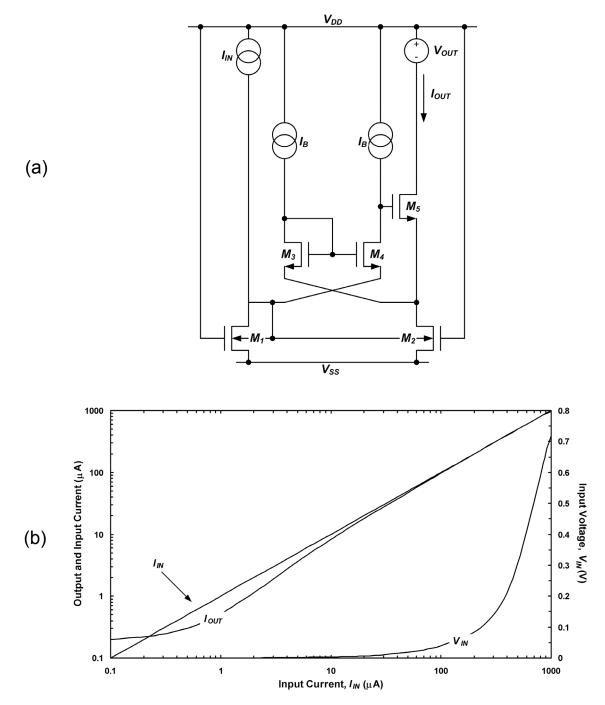

| Figure 4.4:  | Body-driven regulated cascode current mirror: (a) schematic [36] and (b) simulated transfer characteristic (I <sub>B</sub> is equal to 100 nA.)                                                                                            |

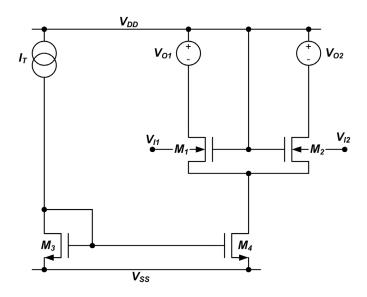

| Figure 4.5:  | Body-driven differential pair with static gate bias [19]                                                                                                                                                                                   |

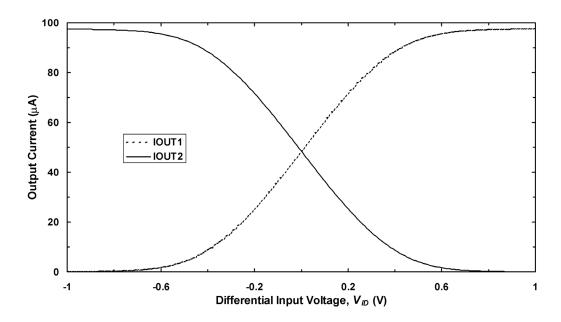

| Figure 4.6:  | Simulated IOUT-VID transfer characteristic for the body-driven differential                                                                                                                                                                |

| 0            | pair with static gate bias ( $M_1$ and $M_2$ are sized 8/0.5 M=4.)                                                                                                                                                                         |

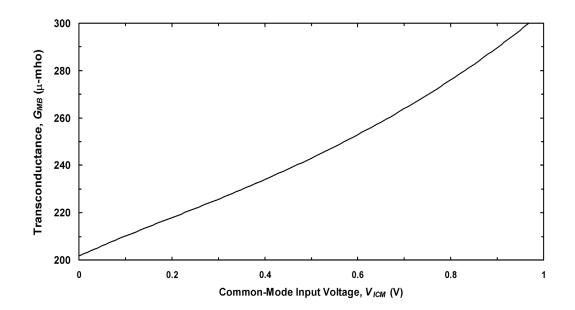

| Figure 4.7:  | Simulated $g_{mb}$ – $V_{ICM}$ for the body-driven differential pair with static gate bias (M <sub>1</sub> and M <sub>2</sub> are sized 8/0.5 M=4.)                                                                                        |

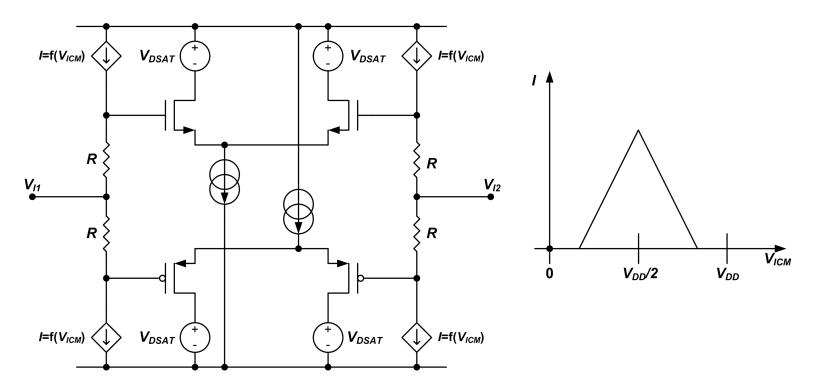

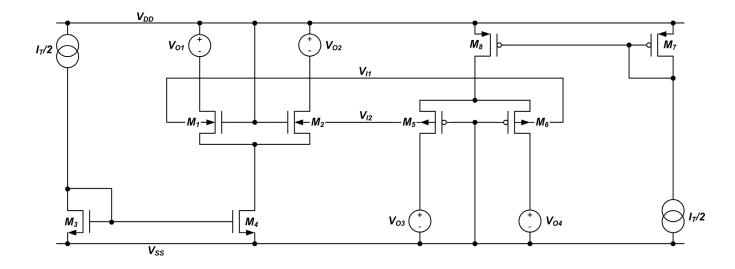

| Figure 4.8:  | Complementary body-driven differential pairs with static gate bias [19]. 101                                                                                                                                                               |

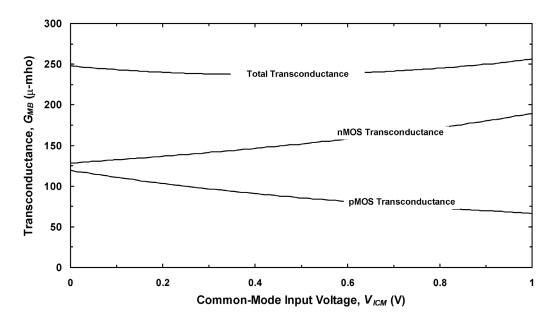

| Figure 4.9:  | Simulated $g_{mb}$ -V <sub>ICM</sub> for complementary body-driven differential pairs . 102                                                                                                                                                |

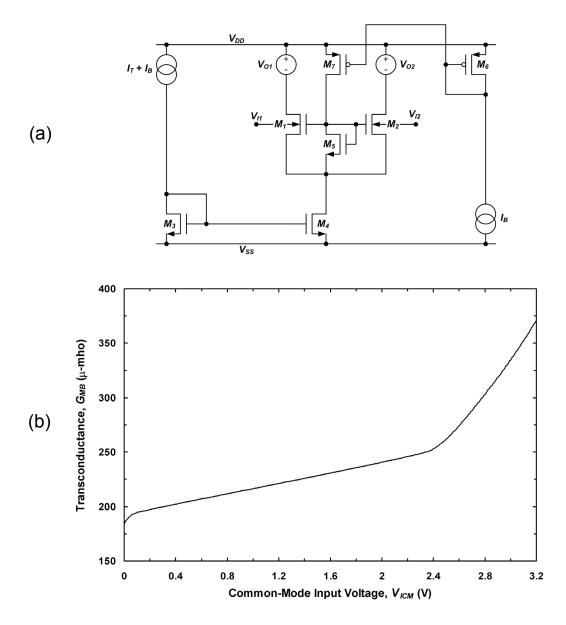

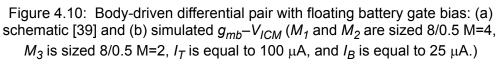

| Figure 4.10:                | Body-driven differential pair with floating battery gate bias: (a) schematic [39]                                                                     |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

|                             | and (b) simulated $g_{mb}$ –V <sub>ICM</sub> (M <sub>1</sub> and M <sub>2</sub> are sized 8/0.5 M=4, M <sub>3</sub> is sized 8/                       |

|                             | 0.5 M=2, $I_T$ is equal to 100 $\mu$ A, and $I_B$ is equal to 25 $\mu$ A.) 103                                                                        |

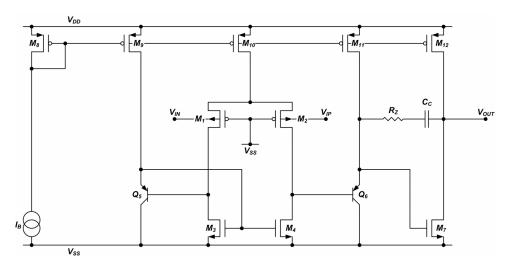

|                             | Early example of a body-driven OTA [34]                                                                                                               |

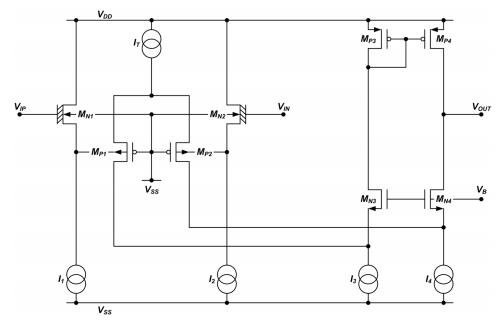

|                             | First two-stage body-driven op-amp [19] 107                                                                                                           |

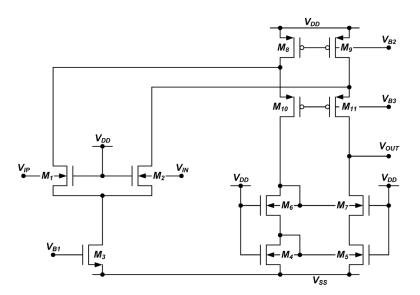

| Figure 4.13:                | Wide-ICMR input stage utilizing depletion-mode, gate-driven nMOS and                                                                                  |

|                             | body-driven pMOS [41] 108                                                                                                                             |

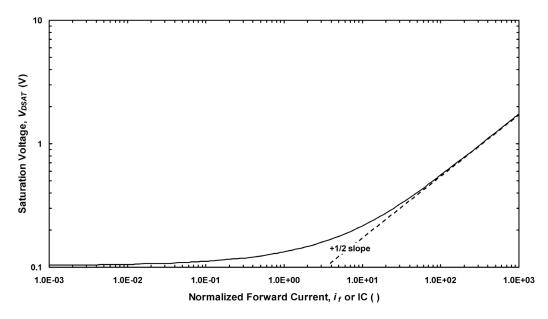

| Figure 5.1:                 | Plot of theoretical V <sub>DSAT</sub> –IC, a=17 118                                                                                                   |

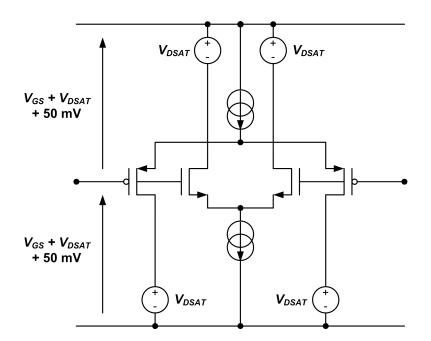

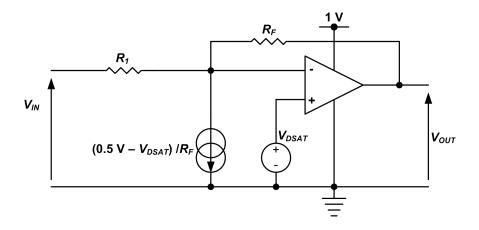

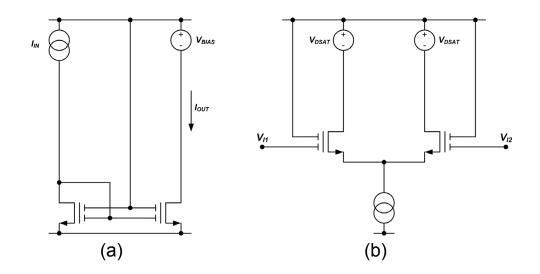

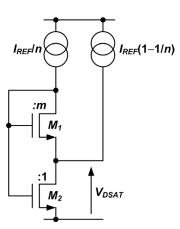

| Figure 5.2:                 | Circuit for extracting saturation voltage [44] 119                                                                                                    |

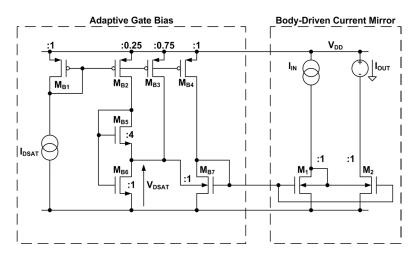

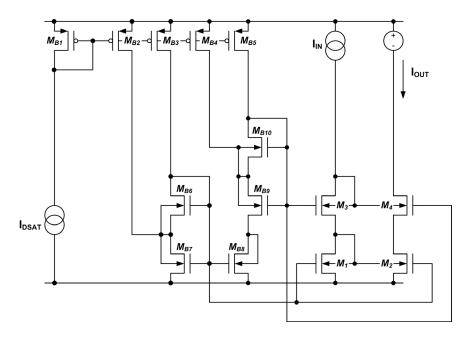

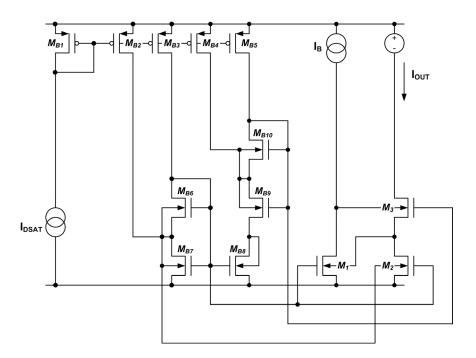

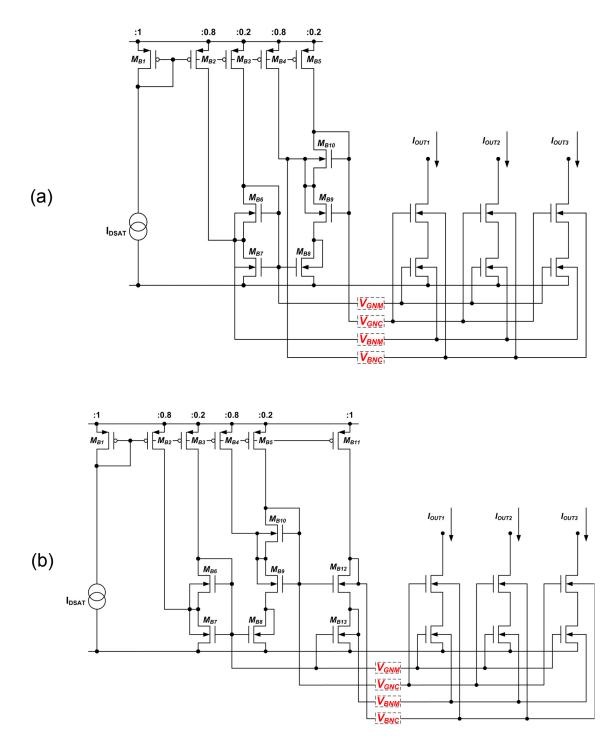

| Figure 5.3:                 | One implementation of a body-driven current mirror with adaptive gate bias-                                                                           |

|                             | ing [1]                                                                                                                                               |

| Figure 5.4:                 | An improved implementation of a body-driven current mirror with adaptive                                                                              |

| Figuro 5 5                  | gate biasing                                                                                                                                          |

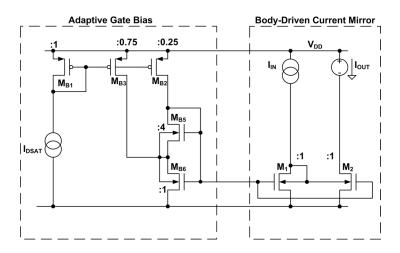

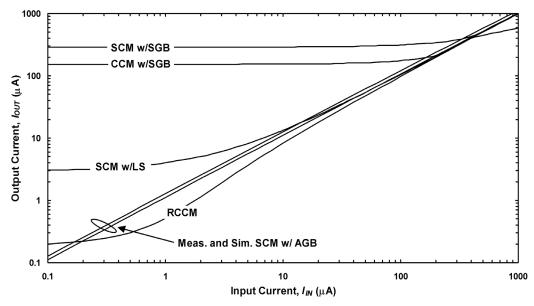

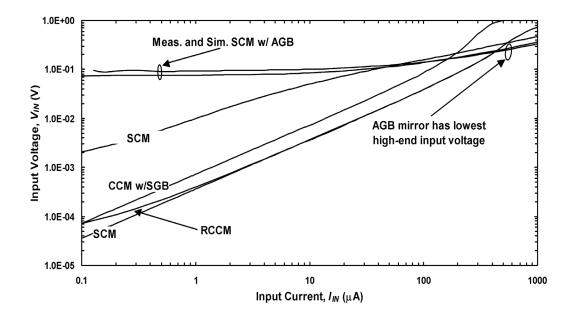

| Figure 5.5:                 | Simulated and measured I <sub>OUT</sub> –I <sub>IN</sub> for the adaptive gate bias current mirror and comparison to prior-art current mirrors        |

| Figure E 6:                 | • •                                                                                                                                                   |

| Figure 5.6:                 | Simulated and measured $V_{IN}$ - $I_{IN}$ for the adaptive gate bias current mirror and comparison to prior-art current mirrors                      |

| Figure 5.7:                 | Schematic of a body-driven cascode current mirror utilizing adaptive gate bi-                                                                         |

| rigure 0.7.                 | asing                                                                                                                                                 |

| Figure 5.8:                 | Schematic of a body-driven regulated cascode current source utilizing adap-                                                                           |

| rigule 5.0.                 | tive gate biasing                                                                                                                                     |

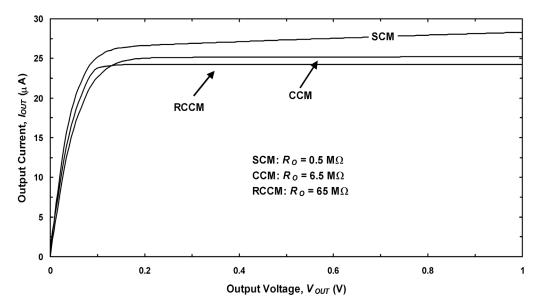

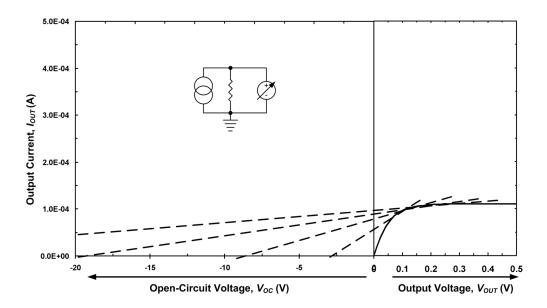

| Figure 5.9:                 | Simulated $I_{OUT} - V_{OUT}$ for adaptively biased simple current mirror, cascode                                                                    |

| rigure 5.9.                 | current mirror, and regulated current mirror biased at 25 $\mu$ A                                                                                     |

| Eiguro 5 10:                | •                                                                                                                                                     |

|                             | Example of a 1-V gate-driven op-amp [47]                                                                                                              |

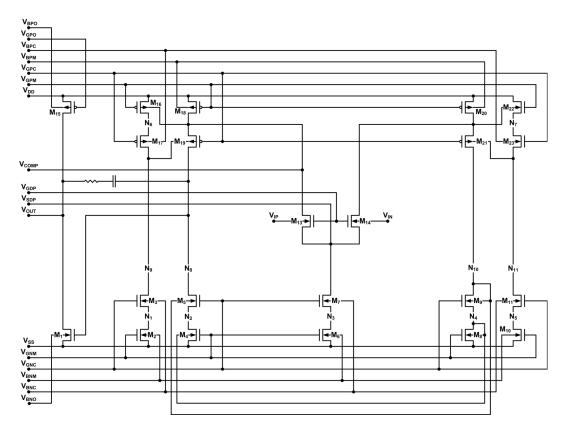

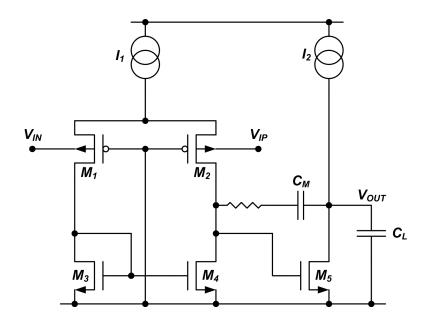

| -                           | Schematic of the core amplifier from the Macedonia chip                                                                                               |

|                             | Schematic of the voltage bias generator from the Macedonia chip 132                                                                                   |

| Figure 5.13:                | I <sub>OUT</sub> –V <sub>OUT</sub> transfer function for a generalized current source, and tangent lines showing the approximate open-circuit voltage |

| Figure E 14:                |                                                                                                                                                       |

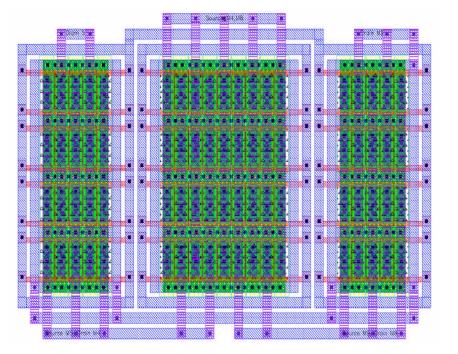

|                             | Layout and schematic of a body-driven cascode current mirror 139                                                                                      |

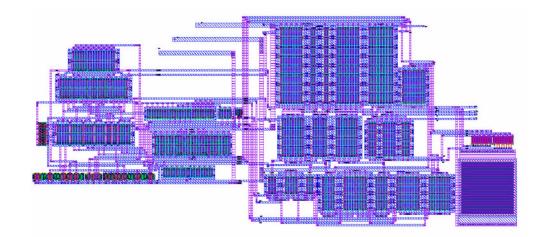

| Figure 5.15:                | Layout of the complete Macedonia amplifier (dimensions are 800 $\mu$ m X 350                                                                          |

| <b>E</b> imuna <b>E</b> 40. | μm)                                                                                                                                                   |

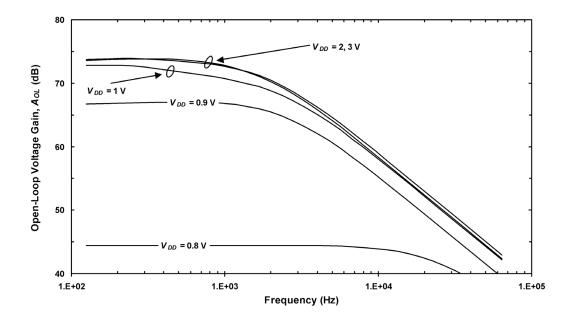

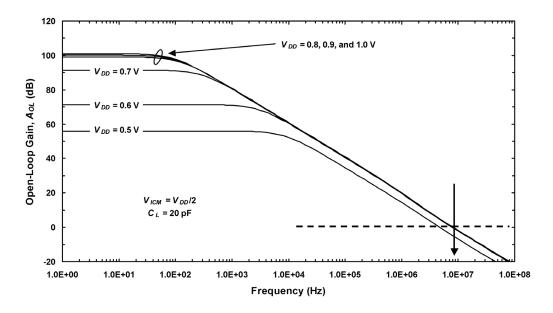

| Figure 5.16:                | Measured open-loop gain (typical) versus frequency at several different op-                                                                           |

|                             | erating voltages for the Macedonia amplifier 141                                                                                                      |

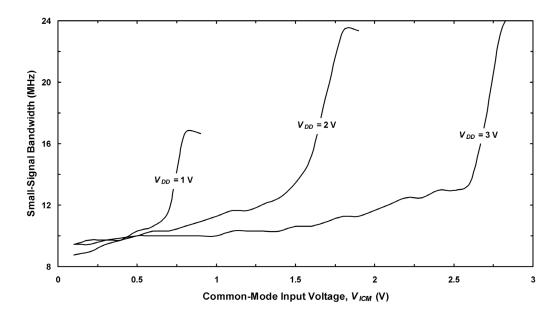

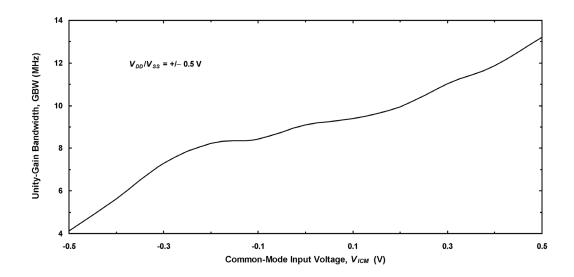

| Figure 5.17:                | Measured unity-gain bandwidth (typical) versus common-mode input at $V_{DD}$                                                                          |

|                             | = 1 V, 2 V, and 3 V for the Macedonia amplifier                                                                                                       |

| Figure 5.18:                | Measured offset voltage versus power supply voltage for the Macedonia am-                                                                             |

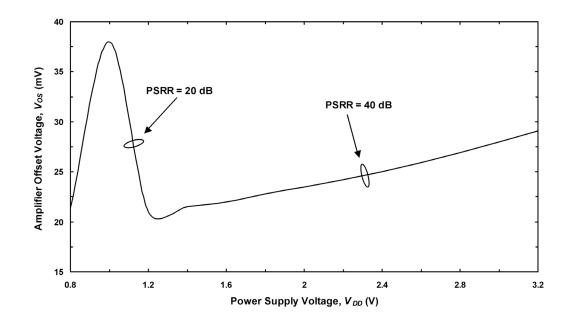

|                             | plifier                                                                                                                                               |

| Figure 5.19:                | Measured offset voltage versus common-mode voltage with $V_{DD}$ = 1 V, 2 V,                                                                          |

|                             | and 3 V for the Macedonia amplifier 145                                                                                                               |

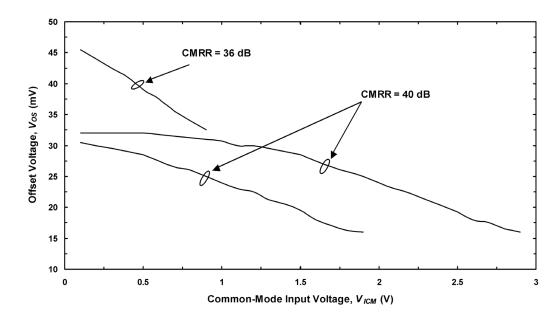

| Figure 5.20:                | Simulated offset voltage versus power supply voltage for the Macedonia am-                                                                            |

|                             | plifier (does not include device mismatch) 147                                                                                                        |

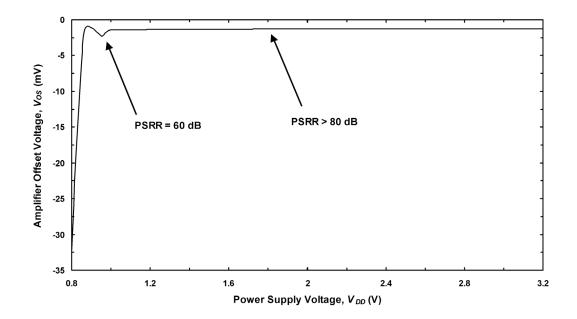

| Figure 5.21:                | Monte Carlo simulation (200 permutations) of the Macedonia op-amp pre-                                                                                |

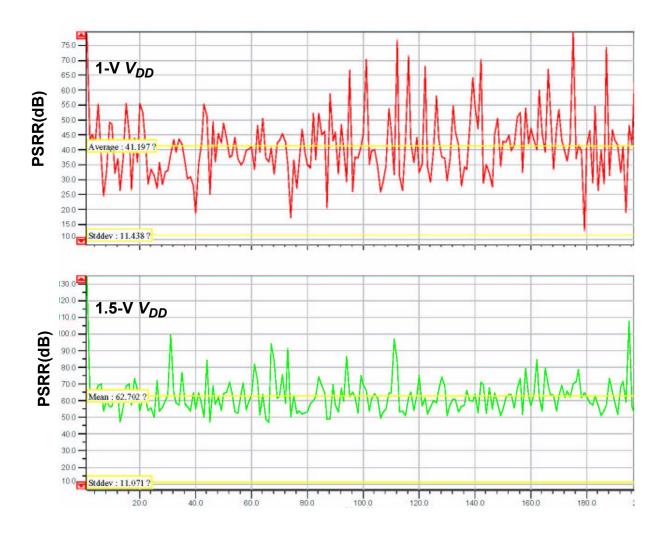

|                             | dicting PSRR at $V_{DD}$ = 1 V and $V_{DD}$ = 1.5 V 149                                                                                               |

| Figure 5.22:                | Schematic showing (a) the problem and (b) the solution for the body-driven                                                                            |

|                             | regulated cascode current mirror 150                                                                                                                  |

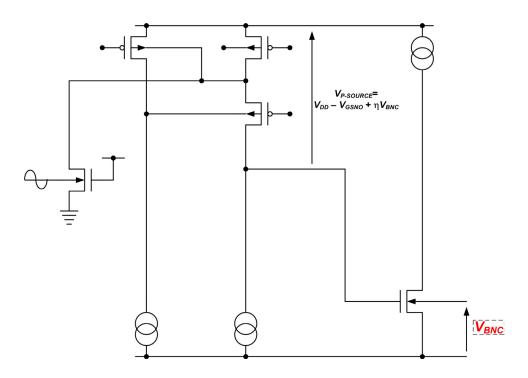

| Figure 5.23:                | Schematic showing a pMOS adaptive gate bias generator (a) without and (b)                                                                             |

|                             | with an nMOS level shifter 152                                                                                                                        |

|                             |                                                                                                                                                       |

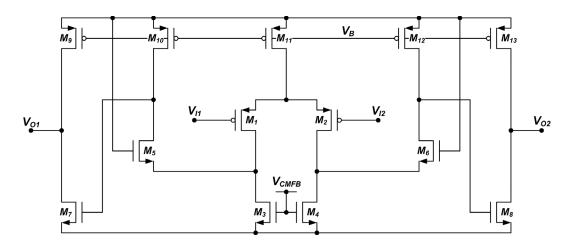

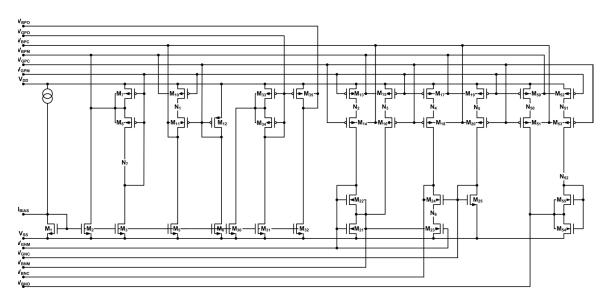

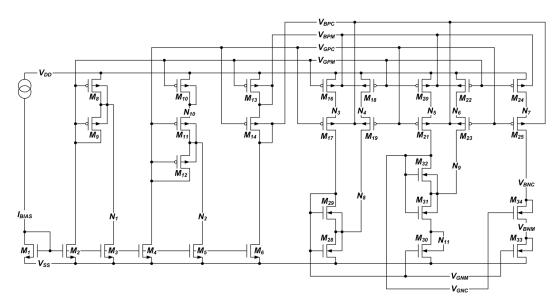

| Figure 5.24: | Schematic of the core amplifier from the Mysia chip 154                                           |

|--------------|---------------------------------------------------------------------------------------------------|

| Figure 5.25: | Schematic of the voltage bias generator from the Mysia chip 154                                   |

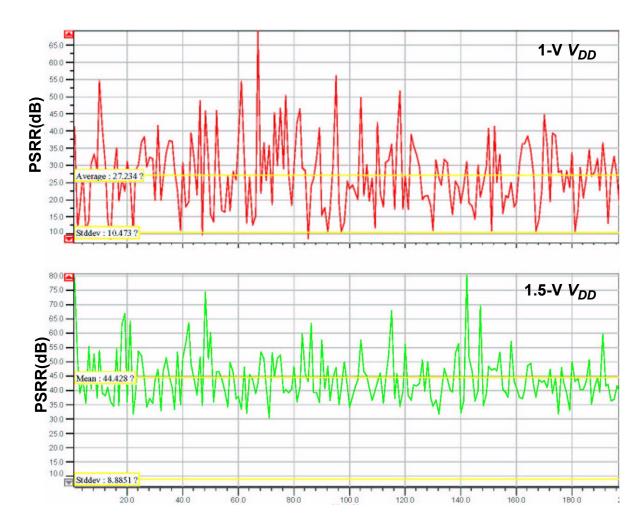

|              | Monte Carlo simulation (200 permutations) of the Mysia op-amp PSRR at                             |

| -            | V <sub>DD</sub> = 1 V and V <sub>DD</sub> = 1.5 V                                                 |

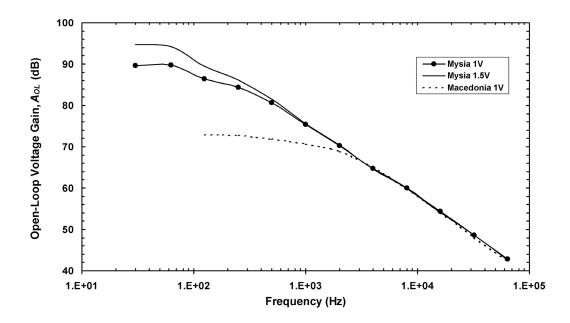

| Figure 5.27: | Comparison of the measured open-loop voltage gain for the Mysia and                               |

| 0            | Macedonia amplifiers                                                                              |

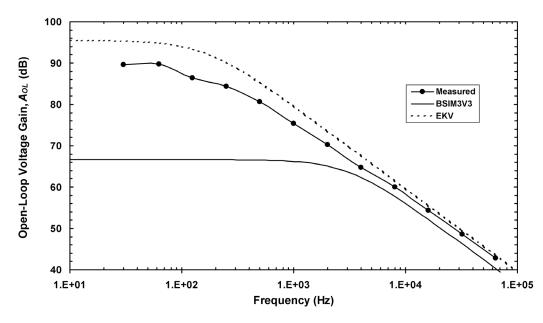

| Figure 5.28: | Comparison of simulated and measured open-loop gain for the Mysia ampli-                          |

|              | fier                                                                                              |

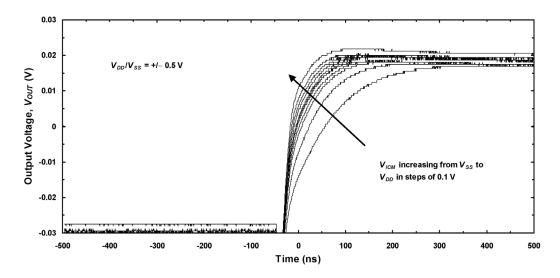

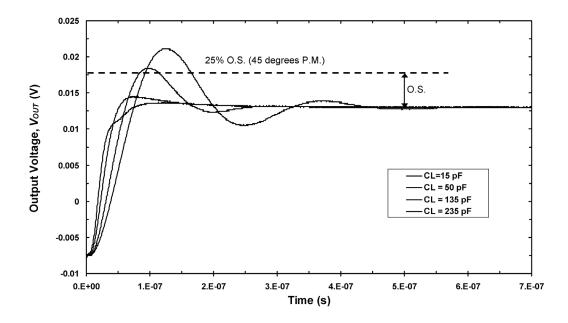

| Figure 5.29: | Measured small-signal step response of the Mysia amplifier as a function of                       |

| -            | common-mode level                                                                                 |

| Figure 5.30: | Measured unity-gain bandwidth versus common-mode level for the Mysia                              |

| -            | amplifier                                                                                         |

| Figure 5.31: | Measured small-signal step response as a function of capacitive load for the                      |

| -            | Mysia amplifier                                                                                   |

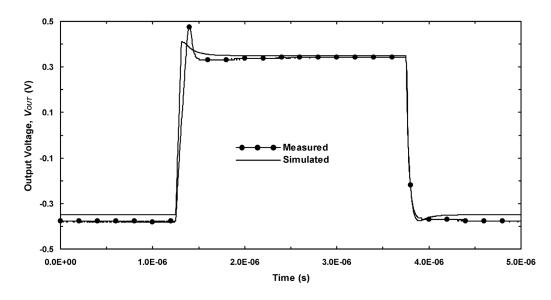

| Figure 5.32: | Measured and simulated large-signal step response for the Mysia amplifier                         |

|              |                                                                                                   |

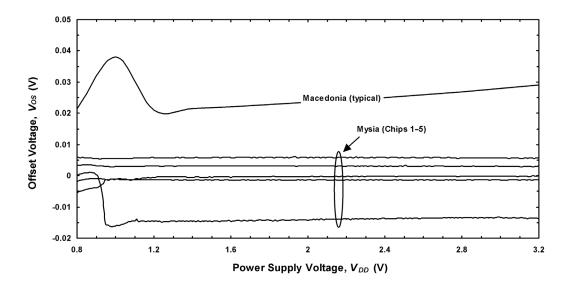

| Figure 5.33: | Measured $V_{OS}V_{DD}$ for five Mysia chips and comparison to a typical Mace-                    |

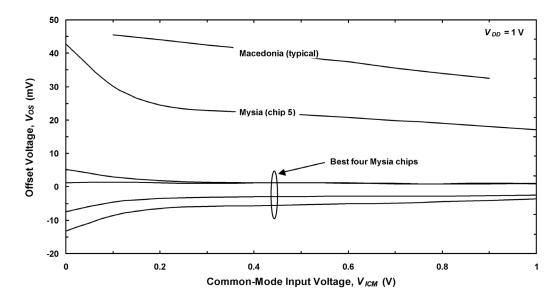

|              | donia amplifier                                                                                   |

| Figure 5.34: | Comparison of measured and simulated (without mismatch effects) AC                                |

| -            | PSRR for the Mysia amplifier at $V_{DD}$ = 1 V and 1.5 V                                          |

| Figure 5.35: | Measured V <sub>OS</sub> –V <sub>ICM</sub> for five Mysia chips and comparison to a typical Mace- |

|              | donia amplifier                                                                                   |

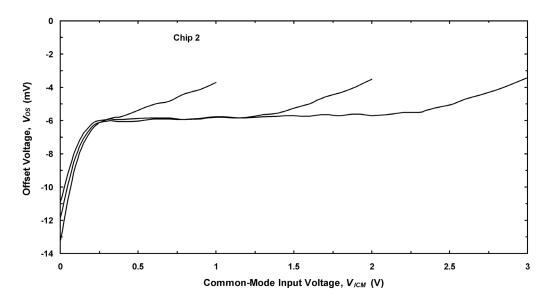

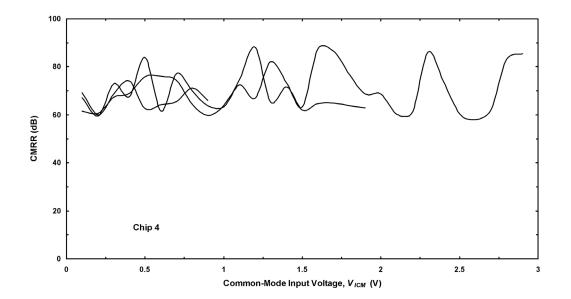

| Figure 5.36: | Measured $V_{OS} - V_{ICM}$ for Mysia chip 2 at $V_{DD}$ = 1 V, 2 V, and 3 V 168                  |

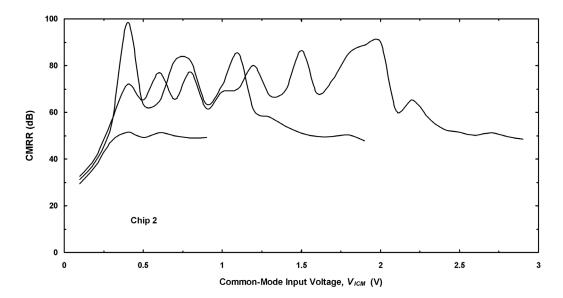

| Figure 5.37: | Measured CMRR– $V_{ICM}$ for Mysia chip 2 at $V_{DD}$ = 1 V, 2 V, and 3 V 168                     |

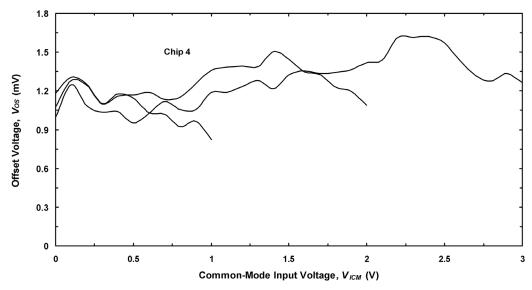

| Figure 5.38: | Measured $V_{OS}-V_{ICM}$ for Mysia chip 4 at $V_{DD}$ = 1 V, 2 V, and 3 V 170                    |

| Figure 5.39: | Measured CMRR– $V_{ICM}$ for Mysia chip 4 at $V_{DD}$ = 1 V, 2 V, and 3 V 170                     |

| Figure 6.1:  | Schematic of a two-stage, Miller-compensated op-amp 182                                           |

| Figure 6.2:  | Flip-around multiply- by-two stage: (a) complete circuit, (b) in sample phase,                    |

|              | and (c) in hold phase 188                                                                         |

| Figure 6.3:  | Bias circuitry for nMOS cascode current source array using (a) standard                           |

|              | adaptive gate bias technique and (b) absolute minimum bias circuit 199                            |

| Figure 6.4:  | Simplified schematic of first and second amplifier gain stages 201                                |

| Figure 6.5:  | Amplifier bias cell developed using absolute minimum bias techniques. 204                         |

| Figure 6.6:  | Simulated open-loop gain vs. frequency and V <sub>DD</sub> for the core Mysia amplifier           |

|              | plus absolute minimum bias voltage generator                                                      |

| Figure A.1:  | Circuit for measuring open-loop gain 221                                                          |

| Figure A.2:  | Circuit for measuring PSRR 223                                                                    |

| Figure A.3:  | Circuit for measuring CMRR (node voltages shown) 224                                              |

### **Chapter 1**

### Introduction

"Solutions in active threshold regulation, substrate biasing, and novel design architecture will be required to extend the trend for lower supply voltages for mixed-signal applications."

*—International Technology Roadmap for Semiconductors*: Process Integration, Devices, and Structures Chapter, p. 25, 2001 edition; Radio Frequency and Analog/Mixed-Signal Technologies for Wireless Communications Chapter, p. 30, 2003 edition

#### 1.1 Trends in Analog and Mixed-Signal Integrated Circuit Design

The scaling of MOSFET dimensions and power supply voltage, in conjunction with an increase in system- and circuit-level performance requirements, are the most important factors driving the development of new technologies and design techniques for analog and mixed-signal integrated circuits. Though scaling has been a fact of life for analog circuit designers for many years, the approaching 1-V and sub-1-V power supplies, combined with applications that have increasingly divergent technology requirements, means that the CMOS analog and mixed-signal IC designs of the future will probably look quite different from those of the past. Foremost among the challenges that analog designers will face in the highly scaled technologies of the future are very low supply voltages and ultra-thin gate oxides. Very low power supply voltages (< 1 V) are a challenge because

dynamic range and even circuit functionality are limited; whereas ultra-thin gate oxides are a challenge because they give rise to significant levels of gate leakage current.

Commensurate with the changing landscape of CMOS technology, there has been an explosion of interest in novel analog and mixed-signal design techniques that can deal with these challenges. Foremost among these design techniques are (in alphabetical order) body-driven MOSFETs, common-mode level shifting, floating-gate MOSFETs, and switched op-amp. Of these, no single design technique has emerged as the best in all situations; rather, each is useful in certain situations. For instance, switched-op-amp design is useful for low-voltage switched-capacitor circuits; whereas common-mode level shifting with resistors is useful for wide voltage dynamic range, continuous-time signal processing. While no design technique has emerged as the best in all situations, it is the opinion of this author that body driving is one of the least favored and yet one of the potentially most useful of all the low-voltage analog design techniques [1].

Body driving refers to using the MOSFET body terminal as a signal and/or bias input, and it is a useful low-voltage design technique because there is no threshold voltage associated with the body terminal, thus dynamic range is increased. The potential of body driving is illustrated by the fact that it can be used to implement a host of functions important to both continuous-time and discrete-time analog circuits—including a single polarity differential pair with rail-to-rail input common-mode range (ICMR) and simple current mirrors with input *and* output voltages close to  $V_{DSAT}$ . However, body driving also has several drawbacks; two of which, the possibility of excessively forward biasing the body–source junction and the roughly three times reduction in transconductance for a body-driven MOSFET compared to a gate-driven MOSFET, are the among most often cited reasons for not using the body-driven design technique [2].

#### 1.2 Research Goals

The goals of this research can be summarized as follows:

- to investigate the viability of body driving as a low-voltage analog circuit design technique,

- to develop, as necessary, novel body-driven circuit primitives (e.g., current mirrors and differential pairs) that will enable reliable, high-performance body-driven circuits, and

- to prove the usefulness of the new circuit techniques by successfully prototyping a high-performance body-driven operational amplifier.

To meet these ends, previous work in body-driven circuit design has been studied, and the fundamental problems which plagued body driving have been isolated and understood. In addition, a new design technique called adaptive gate biasing has been developed, which has led to the design of robust body-driven simple current mirrors, simple cascode current mirrors, and regulated cascode current mirrors—all of which are capable of operating within a 1-V power supply system. To prove the viability of this design technique an operational amplifier circuit has been designed that operates from a power supply voltage ranging from 1 V to 3.3 V, but which is fabricated on a 3.3-V/0.35-µm partially depleted silicon-on-insulator (PD-SOI) technology that has nMOS and pMOS threshold voltages of 0.65 V and 0.85 V, respectively. This is the first operational amplifier to make almost exclusive use of body-driven analog primitives, including body-driven simple current mirrors, body-driven simple cascode current mirrors, and body-driven regulated cascode current sources. Furthermore, in terms of power efficiency, open-loop voltage gain, small-signal unity-gain bandwidth, slew rate, input common-mode range, common-mode rejection ratio, and power supply rejection ratio, this body-driven operational amplifier is competitive with other 1-V operational amplifiers that use various other design techniques—thus proving the viability of body driving as a low-voltage analog technique.

#### 1.3 Overview of the Dissertation

This dissertation presents a study in the design of low-voltage analog and mixed-signal circuits using the body-driven circuit technique. Chapter 2 presents a review of scaling trends for CMOS technology, explores how these trends will affect analog circuit design, and then reviews the most promising design techniques for highly scaled CMOS. From this review it is shown that body driving has great potential as a low-voltage analog design technique. Chapter 3 presents a thorough introduction to the operation of body-driven transistors, including technology considerations, small-signal models, frequency performance, SPICE models, and temperature characteristics. In Chapter 4 a literature review describing previous work in body-driven current mirrors, differential pairs, and amplifiers is presented. Chapter 4 serves as both a review of the state of the art in body-driven circuit design, and an introduction to body-driven design techniques. Chapter 5 presents the original contributions of this research, including a detailed development of the adaptive gate bias technique, the design and characterization of two body-driven

operational amplifiers, and a comparison of the newly developed body-driven op-amp to other published low-voltage amplifiers. Chapter 6 presents a general discussion about the application of body-driven techniques in analog and mixed-signal systems. Finally, Chapter 7 concludes this dissertation. The conclusion includes both a summary of the contributions of this research, and a discussion of future directions for body-driven research.

### **Chapter 2**

# CMOS Technology Trends and Implications for Analog Circuit Design

#### 2.1 Introduction

In 1965, on the basis of scant evidence, Gordon Moore predicted that the density of integrated circuits would double roughly every year for the next ten years [3]. In 1975, when this prophetic prediction proved true, it was codified as Moore's Law that the density of integrated circuits would continue to increase exponentially for the forseeable future [4], [5]. Quantitatively described by technology scaling or simply "scaling", this irresistible trend has defined the integrated circuit industry from its earliest times until today. While Moore's Law is a well-known quantity to circuit designers, its implications for modern CMOS technology and modern CMOS analog circuit design are perhaps less well known. Therefore at this time it is useful to present a brief review of the present and predicted future trends for CMOS technology, and to discuss the implications of these trends for analog circuit design. From this discussion it will be shown that, due to the significant challenges that highly scaled CMOS technologies pose for analog circuit design, novel design techniques, including body driving, will be required in the future.

Section 2.2 discusses MOSFET scaling trends for CMOS technology, highlighting those factors which have an impact on analog circuit design. In Section 2.3 the impact of scaling on analog circuit design, specifically the impact of reduced power supply voltages and gate leakage current, will be examined and the challenges facing analog circuit

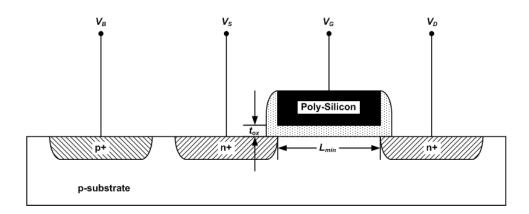

Figure 2.1: Cross section of a n-type bulk-Si MOSFET showing process parameters and device dimensions which are scaled

designers will be highlighted. In Section 2.4 the most promising new analog design techniques, including body-driven MOSFETs, common-mode level shifting, floating-gate MOSFETs, and switched op-amp, will be introduced and compared. From this discussion it will be shown that body driving is an extremely important design technique which has great potential for low-voltage analog applications. Finally, Section 2.5 concludes this chapter.

#### 2.2 Scaling Trends for Digital and Analog CMOS Technologies

#### 2.2.1 Introduction to Technology Scaling

Simply put, technology scaling refers to a reduction in MOSFET dimensions which allows increased packing densities and higher performance in integrated circuits. More than any other factor, it has been the ability to scale CMOS technology in a predictable and consistent manner that has led to the proliferation of CMOS ICs we see today [6]. In this section the fundamental trade-offs associated with technology scaling are reviewed, using the approximation of a long-channel MOSFET. Figure 2.1 presents a simplified dia-

gram of a bulk Si nMOSFET and shows the key device dimensions, gate-oxide thickness  $t_{ox}$  and minimum channel length  $L_{min}$ , which will be considered in this discussion of scaling. Not shown on the diagram are the important voltages related to MOSFET operation, power supply voltage  $V_{DD}$  and threshold voltage  $V_{TH}$ .

As the primary goals of scaling are to increase the density and improve the performance of digital integrated circuits, the main lever for achieving these improvements is the gate length. The general approach in scaling is to introduce a new generation roughly every three years, and for each generation to have a minimum gate length that is 30% smaller than the previous generation. If the aspect ratios of the devices within a given circuit are held constant, then a 30% reduction in gate length yields a roughly 50% reduction in gate area, or a doubling of the packing density. To gauge the increase in performance with scaling, a common figure of merit is the intrinsic MOSFET delay  $\tau$  [7], given by

$$\tau = \frac{C_{tot}V_{DD}}{I_{DSAT}},$$

(2.1)

where  $C_{tot}$  is the total gate capacitance of a MOSFET and  $I_{DSAT}$  is the maximum saturation current (that is, the saturation current at  $V_{GS} = V_{DD}$ ). Using the MOSFET square-law equation,  $\tau$  can be calculated as

$$\tau = \frac{C_{ox}WLV_{DD}}{\frac{\mu C_{ox}(W/L)}{2}(V_{DD} - V_{TH})^2} = \frac{2L^2}{\mu} \cdot \frac{V_{DD}}{(V_{DD} - V_{TH})^2},$$

(2.2)

where  $C_{ox}$  is the gate oxide capacitance per unit area,  $\mu$  is the MOSFET mobility, and W

and *L* are the MOSFET gate width and length, respectively. Equation 2.2 shows that the intrinsic MOSFET delay scales as  $L^2$ , assuming that  $V_{DD}$  and  $V_{TH}$  are constant.

While it is straightforward to improve MOSFET speed by decreasing *L*, this solution also creates the problem of increasing electric fields within the device. For instance, the maximum transverse (i.e., source–drain) electric field is given by

$$E_{T,Max} = \frac{V_{DD}}{L}.$$

(2.3)

If the electric fields within the device get too large, device lifetime and reliability will be compromised. Likewise, the dynamic power dissipation of a digital circuit is described by

$$P_D \propto f V_{DD}^2, \tag{2.4}$$

where *f* is the operating frequency of the circuit. To limit both electric field intensity within the device and dynamic power dissipation, it is typically necessary to scale the power supply voltage along with the channel length.

The final two parameters that will be considered are oxide thickness  $t_{ox}$  and threshold voltage. As  $V_{DD}$  is scaled down, the maximum vertical electrical field (i.e., gate–channel) will be reduced, which limits the transistor drive current. Therefore oxide thickness must be scaled along with power supply and channel length, in order to maintain drive current. Drive current is also dependent on gate-overdrive ( $V_{DD} - V_{TH}$ ), which implies that  $V_{TH}$  should scale down with the other parameters. However, threshold voltage sets the

| MOSFET Parameter<br>Scaled | Positive Effect                                                  | Negative Effect                    |

|----------------------------|------------------------------------------------------------------|------------------------------------|

| V <sub>DD</sub>            | reduces dynamic power<br>dissipation, increases reli-<br>ability | reduces speed                      |

| V <sub>TH</sub>            | increases speed                                                  | increases static power dissipation |

| t <sub>ox</sub>            | increases drive current                                          | decreases reliability              |

| L                          | reduces area, increases speed                                    | decreases reliability              |

Table 2.1: Negative and positive effects of scaling critical MOSFET parameters

sub-threshold leakage current  $I_{SUB}$  (the drain current at  $V_{GS} = 0$ ), which is given by [8]

$$I_{SUB} = 2n\mu C_{ox}(W/L) U_T^2 \exp\left(\frac{-V_{TH}}{nU_T}\right),$$

(2.5)

where *n* is the sub-threshold slope factor and  $U_T$  is the thermodynamic voltage (approximately 26 mV at room temperature). Sub-threshold current, which is exponentially dependent on threshold voltage and independent of power supply voltage, is the key factor in determining static power dissipation in digital circuits (at least for processes with gate lengths > 65 nm). In order to minimize static power dissipation, threshold voltage is typically not scaled, or scaled only very weakly, from one CMOS process generation to another.

Table 2.1 presents a summary of the negative and positive effects of scaling critical MOSFET parameters. This table considers scaling from a digital circuit perspective.

Each row in the table considers the effect of scaling one parameter, assuming that all other parameters are held constant.

#### 2.2.2 Scaling Trends for Digital CMOS Technologies

The purpose of the previous section was to provide the reader with an understanding of the basic factors affecting technology scaling in digital circuits. In this section the scaling trends most important for circuit design:  $V_{DD}$ ,  $V_{TH}$ ,  $t_{ox}$ , and  $L_{min}$ , are presented. The data presented here span the years 2001–2009, and therefore represent the recent past, present, and predicted future trends for CMOS technology. The data comes from two sources: the 2003 *International Technology Roadmap for Semiconductors* (ITRS), which provided predictions about future trends, and a paper published in the *Proceedings of the IEEE*, which provided information about historical trends [6], [7].

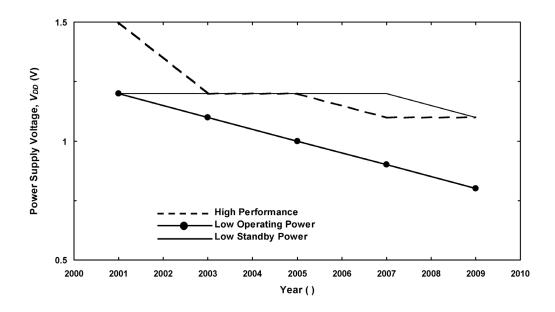

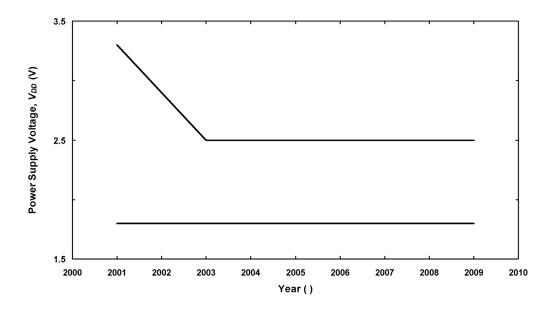

Figure 2.2 presents the scaling trends for CMOS power supply voltage for the years 2001–2009. Looking at this plot, one will immediately notice that there are three different trends shown for power supply voltage. These three curves are labeled high performance (HP), low operating power (LOP), and low standby power (LSP), and they each represent a  $V_{DD}$  scaling trend that has been optimized for a distinct, but broad category of digital circuits. Thus, high performance refers to digital circuits whose primary concern is speed and that operate from an effectively unlimited power source; desktop and server computers are the best examples of HP applications. Low operating power refers to systems that still need to operate at high speeds, but also must operate within a limited power budget; laptop computers are a good example of an LOP application. Finally low

Figure 2.2: Scaling trend for digital CMOS power supply voltage

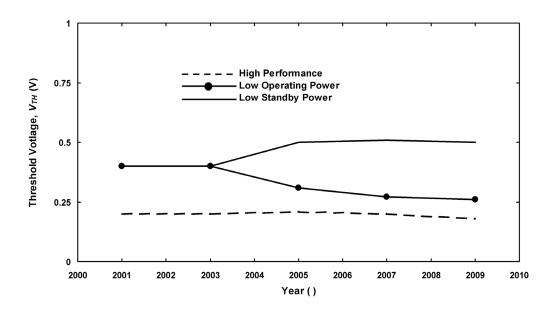

standby power refers to systems for which minimizing power dissipation, both static and dynamic, is of paramount importance; the digital circuits within a cellular telephone are a good example of an LSP application. Figure 2.3 presents the scaling trend over the same period for MOSFET threshold voltage, and also uses the designations of high performance, low operating power, and low standby power.

The main reason that CMOS technology is forced to offer multiple power supply and threshold voltages within a given technology generation is that  $V_{DD}$  and  $V_{TH}$  are now so low that it is not possible to meet the performance requirements of the wide range of differing applications with a single choice of operating voltages. As an example, note that in 2005 the  $V_{DD}$  for HP and LSP is 1.2 V, while it is only 1 V for LOP. Conversely the  $V_{TH}$  is 0.2 V for HP, 0.3 V for LOP, and 0.5 V for the LSP technology option. Thus we can see

Figure 2.3: Scaling trend for digital CMOS threshold voltage

that the HP CMOS option has the highest  $V_{DD}$  and lowest  $V_{TH}$  to maximize speed, at the cost of increased power. LSP has a  $V_{DD}$  equal to the HP  $V_{DD}$ , but also has the highest  $V_{TH}$ , which allows it to minimize sub-threshold leakage at the cost of reduced speed. Finally the LOP option has the lowest  $V_{DD}$  and a  $V_{TH}$  in between the other two, resulting in moderate speed and moderate levels of leakage current. Considering the trends as a whole,  $V_{DD}$  is between 1.5 V and 1.2 V in 2001 and scales to values of 1.2 V and 0.8 V in 2009. On the other hand, threshold voltage scales very little because it must generally be chosen for leakage current minimization, which is independent of power supply voltage. From 2005 onwards the available threshold voltages will be close to 0.2 V, 0.26 V, and 0.5 V.

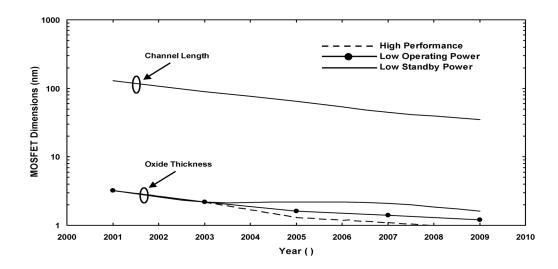

Figure 2.4: Digital CMOS scaling trend for channel length and oxide thickness

Figure 2.4 presents the scaling trends for both CMOS channel length and oxide thickness. The channel length runs from 120 nm in 2001 to only 35 nm in 2009. Oxide thickness starts at just above 3 nm in 2001, and then splits in 2003 to three different trends *as per* the HP, LOP, LSP discussion above. The gate oxide thickness in 2009 will range between 0.9 nm and 1.6 nm.

#### 2.2.3 Scaling Trends for Analog CMOS Technologies

The previous discussions about the trade-offs inherent in technology scaling, and the scaling trends predicted for the future, referred to what can be called digital CMOS technology; that is, a CMOS technology which has been optimized for digital applications. This is an appropriate approach to the problem because CMOS technology is predominantly used for digital applications, and digital applications will always be the prime

mover for technology scaling. However, in recent years analog circuit applications, including high-performance ADCs and RF power amplifiers, have become essential components of mixed-signal systems and are increasingly being recognized as technology drivers in their own right [9]. The problem with including analog applications in the calculus of technology scaling is that the technology needs of digital and analog circuits are often at odds. Specifically, one of the major differences is that very low power supply voltages represent a major hurdle for analog circuits, while low power supply voltage is generally an advantage, or at least not a problem, for digital circuits.

One popular strategy for factoring analog (i.e., higher  $V_{DD}$ ) considerations into the process flow is to include a thicker oxide option that would allow devices to operate at the higher  $V_{DD}$  needed by some analog applications. This thick-oxide option has the added purpose of allowing high-voltage I/O capability for interfacing off-chip with digital circuits that use a higher operating voltage. Figure 2.5 presents the power supply trend that will be required for proper operation of some analog circuits—specifically including higher performance ADCs and RF power amplifiers [9]. The two curves in this plot represent the upper and lower limits for analog power supply voltage, which are 2.5 V and 1.8 V, respectively, for most of the decade. Certainly this is much more manageable than the 0.8 V to 1.2 V range predicted for the digital technology options. However, the power supply data presented in Figure 2.2 and Figure 2.5 should not be considered equally realistic. The trends presented for digital CMOS technology are much more detailed, and since all CMOS technologies will be first optimized for digital applications, they will offer options very close to what was presented in Figures 2.2 and 2.3. On the other hand, the

Figure 2.5: Required CMOS scaling trend for highest-performance analog applications

predictions for analog power supply only describe what will be needed for some analog design applications. There is no guarantee that an analog designer will have these power supply options to work with. Frequently, analog circuit designers will have to design within the power supply and threshold voltage constraints dictated by digital CMOS scaling trends. These issues will be described in more detail in the next section. Nonetheless, the fact that analog circuit needs are being factored into the technology roadmap is significant, and must be considered when trying to understand what the complete field of analog circuit design will look like in the future.

#### 2.3 The Low-Voltage Challenge to Analog Circuit Design

In Section 2.2 the scaling trends that can be expected for CMOS technology were presented; in this section the implications of these scaling trends for analog circuit design will be explored. Since analog circuit design is a broad field with many different applications that have different performance requirements and utilize different circuit topologies, it is not possible to exhaustively consider the effects of technology scaling on every aspect of analog circuit design. Instead, this section considers three of the most important consequences of scaling: how reduced power supply voltage affects power dissipation, how reduced power supply voltage affects circuit functionality, and how gate leakage current affects circuit functionality. In Section 2.3.1 an analysis of the relationship between power supply voltage and power dissipation in analog circuits is presented, and it is shown that for high-performance (i.e., high-speed, high-resolution) applications power dissipation is the limiting factor in determining power supply voltage. In Section 2.3.2 the limitations on analog circuit functionality due to reduced power supply voltage are analyzed by considering the power supply and threshold voltage requirements for several benchmark circuits. In Section 2.3.3 the levels of gate leakage current that will be present in highly scaled technologies, and the effects of gate leakage current on analog circuits, will be studied. Finally, in Section 2.3.4 some predictions about the future state of analog circuit design are made, based on the analysis presented in the previous sections.

#### 2.3.1 Power Supply Voltage and Power Dissipation

Analog circuits can be differentiated from digital circuits by the fact that in analog circuits the precise values of input and output voltages are important. The fundamental limitation to the precision that an analog circuit can achieve is noise, which is present in all electronic systems due to the random thermal motion of electrons. A useful figure of merit for the precision of analog systems is the signal-to-noise ratio (SNR), which is essentially the ratio of the maximum to minimum signal that an amplifier can resolve, and is quantitatively described by

$$SNR = \frac{P_{SIGNAL}}{P_{NOISE}},$$

(2.6)

where  $P_{SIGNAL}$  is the maximum signal power at the output of a circuit, and  $P_{NOISE}$  is the noise power at the output of a circuit. In this section the relationship between power supply voltage and power dissipation is studied for a standard analog circuit, under the assumption that the SNR and bandwidth of the circuit are held constant. To proceed with this analysis, one must compute SNR in terms of the critical circuit parameters. Because of its generality, a single-pole operational transconductance amplifier (OTA) is used as the benchmark analog circuit in this study.

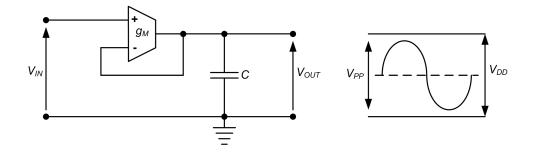

Figure 2.6 presents the schematic of a simple analog circuit, consisting of an OTA connected as a unity-gain follower and loaded by a capacitor, that will be used in this study. Assuming a single-tone input, the maximum, mean-square signal power at the output of

Figure 2.6: Simple analog circuit used to explore the relationship between SNR, power supply voltage, and power dissipation

this circuit can be calculated as

$$P_{SIGNAL} = \frac{V_{PP}^2}{8}.$$

(2.7)

The closed-loop frequency response of the circuit can be calculated as

$$H(f) = \frac{1}{1 + j\frac{f}{f_o}},$$

(2.8)

where  $f_o$  is the small-signal unity-gain bandwidth given by

$$f_o = \frac{g_M}{2\pi C},\tag{2.9}$$

and  $g_M$  is the transconductance of the OTA's input differential pair. The mean-square noise power at the output of the circuit can be calculated as

$$P_{NOISE} = \overline{e_{ni}^2} \int_{0}^{\infty} \frac{df}{1 + \left(\frac{f}{f_o}\right)^2},$$

(2.10)

where  $\overline{e_{ni}^2}$  represents the input-referred voltage noise density. Assuming that the input noise is dominated by the thermal noise of the input pair, it can be calculated as

$$\overline{e_{ni}^2} = 8kT\gamma \frac{1}{g_M},$$

(2.11)

where *k* is Boltzmann's constant, *T* is absolute temperature, and  $\gamma$  is a constant roughly equal to 2/3. Finally, the output noise power can be calculated by evaluating the integral

in Equation 2.10

$$P_{NOISE} = \frac{2\gamma kT}{C},$$

(2.12)

and the SNR can be expressed as

$$SNR = \frac{V_{PP}^2 C}{16\gamma kT}.$$

(2.13)

To understand how voltage scaling affects the power dissipation of an analog circuit, assume that  $V_{PP} \approx V_{DD}$  and that  $V_{DD}$  is scaled by a factor  $1/\alpha$  ( $\alpha > 1$ ). In this case the scaled peak-to-peak output swing  $V_{PPs}$  will be

$$V_{PPs} \Rightarrow \frac{V_{PP}}{\alpha}$$

(2.14)

To maintain a constant SNR the load capacitance must scale as

$$C_s \Rightarrow \alpha^2 C,$$

(2.15)

and to maintain the bandwidth  $f_{o}$  , the  $g_{\boldsymbol{M}}$  must also scale as

$$g_{Ms} \Rightarrow \alpha^2 g_M.$$

(2.16)

If we assume that the transconductance efficiency  $g_{M}\!/I_{D}$  of the input pair devices in the

transconductor remains constant, the bias current of the OTA must scale as

$$I_{Ts} \Rightarrow \alpha^2 I_T,$$

(2.17)

where  $I_T$  is the tail current for the OTA. Finally, if we assume that the OTA supply current is in direct proportion to the tail current, we can see how the power dissipation of this analog circuit will scale with power supply voltage, assuming SNR and bandwidth are constant:

$$P_{Ds} = (V_{DD}/\alpha)(\alpha^2 I_T) \Longrightarrow \alpha P_D.$$

(2.18)

Equation 2.18 shows that the power dissipation of an analog circuit is inversely proportional to power supply voltage, assuming SNR and bandwidth are constant. This is a fundamental result of thermodynamics and is independent of circuit topology and device technology. Furthermore, although a simple OTA was used in this analysis, this basic relationship is true for all analog circuits [8]. The most significant conclusion that can be drawn from this analysis is that for the highest performance analog circuits, such as ADCs with resolution greater than 12 bits and operating speeds greater than 10 MHz, the power dissipation will become prohibitively large if the power supply voltage is scaled to one volt. It is for these applications that an analog power supply voltage in the range of 1.8 to 2.5 V has been defined, as in Figure 2.5.

#### 2.3.2 Power Supply Voltage and Circuit Functionality

The previous section showed that for the highest performance analog circuits, power dissipation and operating speed will be the limiting factors in determining the allowable power supply voltage. However, there are many other analog circuits which perform at low to moderate speeds (e.g., DC to 10 MHz) and have an SNR in the 10- to 12-bit range. For these applications circuit functionality, instead of power dissipation, will often be the limiting factor in determining power supply voltage. Furthermore, since these applications can theoretically run at very low power supply voltages, it will be expected that they operate at the standard digital power supply voltages discussed in Section 2.2.2, and use the digital CMOS threshold voltages also described in that section. In this section the limitations of analog circuit functionality at low supply voltage will be studied by analyzing the power supply voltage required for several benchmark analog circuits.

#### 2.3.2.1 Minimum Analog Power Supply Voltage

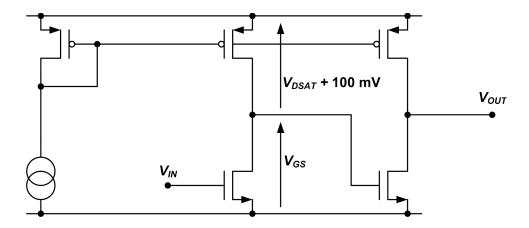

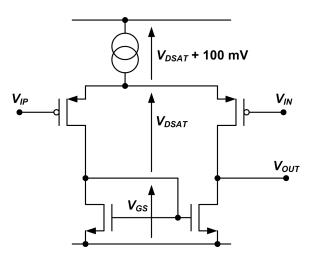

Figure 2.7 presents a schematic of a simple analog circuit, which has only two transistors connected in series between  $V_{DD}$  and  $V_{SS}$  and therefore shows the minimum required power supply voltage for an analog circuit. The minimum  $V_{DD}$  required for this circuit is

$$V_{DDmin} = V_{GS} + V_{DSAT} + 100 mV,$$

(2.19)

where the 100 mV term is included to allow the internal high-impedance node adequate dynamic range to respond to an input signal, and to account for any shifts in threshold voltage over process. If we assume that all of the transistors are operating at the center

Figure 2.7: Circuit showing the minimum power supply voltage required for an analog circuit

of moderate inversion, then the  $V_{GS}$  is equal to  $V_{TH}$  + 25 mV and  $V_{DSAT}$  is equal to 150 mV, therefore the minimum power supply voltage can be calculated as

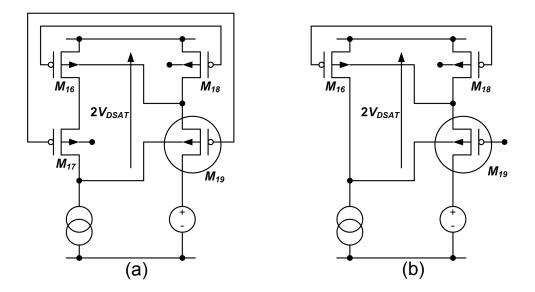

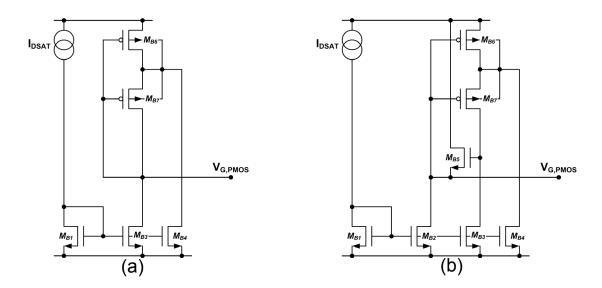

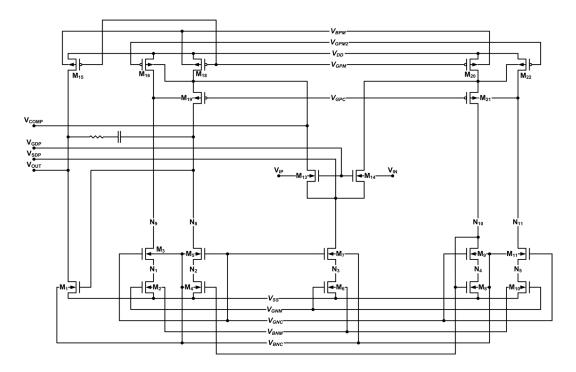

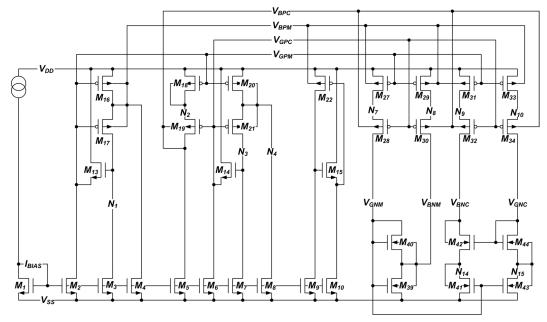

$$V_{DDmin} = V_{TH} + 275 mV. (2.20)$$