# University of Tennessee, Knoxville TRACE: Tennessee Research and Creative

**Doctoral Dissertations**

Graduate School

**Exchange**

12-2003

# Analytical Modeling of High Performance Reconfigurable Computers: Prediction and Analysis of System Performance.

Melissa C. Smith University of Tennessee - Knoxville

Follow this and additional works at: https://trace.tennessee.edu/utk\_graddiss

Part of the Electrical and Computer Engineering Commons

#### **Recommended Citation**

Smith, Melissa C., "Analytical Modeling of High Performance Reconfigurable Computers: Prediction and Analysis of System Performance.. " PhD diss., University of Tennessee, 2003. https://trace.tennessee.edu/utk\_graddiss/2370

This Dissertation is brought to you for free and open access by the Graduate School at TRACE: Tennessee Research and Creative Exchange. It has been accepted for inclusion in Doctoral Dissertations by an authorized administrator of TRACE: Tennessee Research and Creative Exchange. For more information, please contact trace@utk.edu.

To the Graduate Council:

I am submitting herewith a dissertation written by Melissa C. Smith entitled "Analytical Modeling of High Performance Reconfigurable Computers: Prediction and Analysis of System Performance.." I have examined the final electronic copy of this dissertation for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Doctor of Philosophy, with a major in Electrical Engineering.

Gregory D. Peterson, Major Professor

We have read this dissertation and recommend its acceptance:

Don W. Bouldin, Hairong Qi, Michael Langston, Lynne Parker

Accepted for the Council:

Carolyn R. Hodges

Vice Provost and Dean of the Graduate School

(Original signatures are on file with official student records.)

| To the Graduate Council: | To the | Graduate | Council: |

|--------------------------|--------|----------|----------|

|--------------------------|--------|----------|----------|

I am submitting herewith a dissertation written by Melissa C. Smith entitled "Analytical Modeling of High Performance Reconfigurable Computers: Prediction and Analysis of System Performance." I have examined the final electronic copy of this dissertation for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Doctor of Philosophy, with a major in Electrical Engineering.

|                                                              | Gregory D. Peterson                      |

|--------------------------------------------------------------|------------------------------------------|

|                                                              | Major Professor                          |

| We have read this dissertation and recommend its acceptance: |                                          |

| Don W. Bouldin                                               |                                          |

| Hairong Qi                                                   |                                          |

| Michael Langston                                             |                                          |

| Lynne Parker                                                 |                                          |

|                                                              | Acceptance for the Council:              |

|                                                              | Anne Mayhew                              |

|                                                              | Vice Provost and Dean of Graduate Studie |

(Original signatures are on file with official student records.)

# Analytical Modeling of High Performance Reconfigurable Computers: Prediction and Analysis of System Performance

A Dissertation

Presented for the

Doctor of Philosophy

Degree

The University of Tennessee, Knoxville

Melissa C. Smith

December 2003

Copyright © 2003 by Melissa C. Smith

All rights reserved.

# **DEDICATION**

This dissertation is dedicated to my husband, Harrison, for always believing in me, my girls, Allison and Courtney, for being the joy of my life, and to the rest of my family, for their love and support, inspiring me and encouraging me to reach higher and strive harder.

### **ACKNOWLEDGEMENTS**

I would like to send a big thank you to everyone who stood by me and helped me complete this long journey. I have been very fortunate to have had the support of numerous people over the years as I struggled through this degree. First, I would like to thank my family who sacrificed plenty and suffered the brunt of my frustrations and stress much of the time. My parents and my brother who have always been there to provide support and encouragement when I had second thoughts and doubted myself. I am truly blessed to have them in my life. A very special thanks goes out to my husband, Harrison, who has always been there for me no matter what the circumstances. Without his love and patience, none of this would have been possible. He kept me centered, grounded, and always focused on the end goal. I love him dearly. And most importantly, my girls, Allison and Courtney. Although you will not remember all the hours mommy spent working so diligently on her research (because you were only six months old when she finished), you helped her everyday and provided inspiration and motivation. I always knew, no matter how difficult the day had been, I could always count on both of you for your unconditional love. Your smiles and hugs carried me through many tough days. You are my inspiration, my joy, my life, and I love both of you more than words can say.

My advisor, Greg Peterson was the force that kept me going. His guidance and advice were key in molding this dissertation. Somehow he managed to keep me focused, extracting my best, even when I doubted myself. In addition, I would like to thank the other members of my committee who also played key roles in my success, Don Bouldin, Michael Langston, Hairong Qi, and Lynne Parker. Their comments and encouragement greatly improved my dissertation and I am indebted to them for their service. Thanks to all of you.

Many others have played seemingly small roles but without them, I could not have finished. Gary Alley, for standing by me and fighting for my best interest. I hope to make you proud. Bill Holmes for his telecommuting advice and expertise. I would also like to extend my appreciation to all my colleagues at the Oak Ridge National Laboratory for being so supportive during my trials and tribulations. Also, thanks to everyone involved in our HPRC research group (Mahesh, Chandra, Adam, Kirk, Joe, Bahnu, Ashwin, Venky, Jason) you each played an integral part in my success. My friends in Hong Kong who helped with the Pilchard machines especially Hok, I could not have done it without you.

Many gracious thanks to those who supported my research with funding and equipment. The HPRC computers and other equipment provided through the SInRG project at UT and funded by the National Science Foundation (contracts NSF 0075792 and NSF 9972889). For their financial support, I would also like to thank the Engineering Science and Technology Division at the Oak Ridge National Laboratory and the Air Force Research Laboratory (AFRL contract F30602-00-D-0221). The work contained in this dissertation was developed in part based upon technology licensed and developed by SRC Computers, Inc.

Last but not least, many thanks to all my friends who helped me "reset" on occasions and many other good deeds. These include Renee, Joely, Gail, Gayle, Janice, Missy, TJ, Trudi, Judy, Kelly, and many others who I have no doubtedly forgot, I hope they can forgive me! There have been so many people that have helped me enjoy (and survive) this time. Thanks to all of you. Finally, thanks to God for giving me the knowledge, patience, perseverance, and placing these individuals in my life to make it all happen.

### **ABSTRACT**

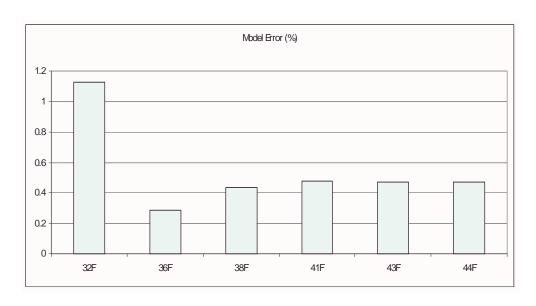

The use of a network of shared, heterogeneous workstations each harboring a Reconfigurable Computing (RC) system offers high performance users an inexpensive platform for a wide range of computationally demanding problems. However, effectively using the full potential of these systems can be challenging without the knowledge of the system's performance characteristics. While some performance models exist for shared, heterogeneous workstations, none thus far account for the addition of Reconfigurable Computing systems. This dissertation develops and validates an analytic performance modeling methodology for a class of fork-join algorithms executing on a High Performance Reconfigurable Computing (HPRC) platform. The model includes the effects of the reconfigurable device, application load imbalance, background user load, basic message passing communication, and processor heterogeneity. Three fork-join class of applications, a Boolean Satisfiability Solver, a Matrix-Vector Multiplication algorithm, and an Advanced Encryption Standard algorithm are used to validate the model with homogeneous and simulated heterogeneous workstations. A synthetic load is used to validate the model under various loading conditions including simulating heterogeneity by making some workstations appear slower than others by the use of background loading. The performance modeling methodology proves to be accurate in characterizing the effects of reconfigurable devices, application load imbalance, background user load and heterogeneity for applications running on shared, homogeneous and heterogeneous HPRC resources. The model error in all cases was found to be less than five percent for application runtimes greater than thirty seconds and less than fifteen percent for runtimes less than thirty seconds.

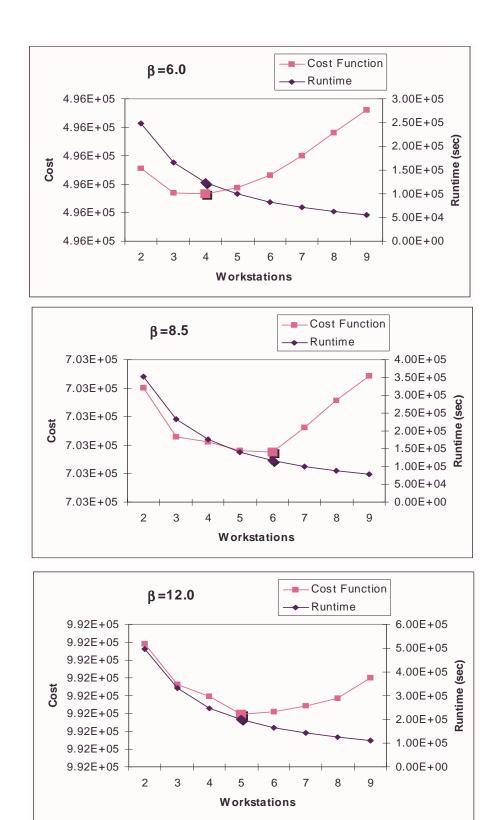

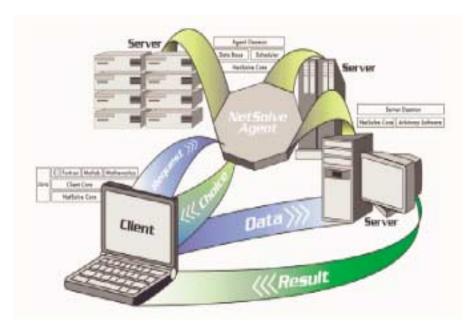

The performance modeling methodology enables us to characterize applications running on shared HPRC resources. Cost functions are used to impose system usage policies and the results of the modeling methodology are utilized to find the optimal (or near-optimal) set of workstations to use for a given application. The usage policies investigated include determining the computational costs for the workstations and balancing the priority of the background user load with the parallel application. The applications studied fall within the Master-Worker paradigm and are well suited for a grid computing approach. A method for using NetSolve, a grid middleware, with the model and cost functions is introduced whereby users can produce optimal workstation sets and schedules for Master-Worker applications running on shared HPRC resources.

# **CONTENTS**

| 1.  | Introduction                                        | 1        |

|-----|-----------------------------------------------------|----------|

| 1.1 | Motivation                                          | 1<br>2   |

| 1.2 | General Problem Statement                           |          |

| 2.  | Background and Related Work                         | 9        |

| 2.1 | Introduction                                        | 9        |

| 2.2 | Building the HPRC Architecture                      | 9<br>11  |

| 2.3 | Performance Evaluation, Analysis and Modeling       | 18<br>19 |

| 2.4 | Performance Metrics                                 | 26       |

| 2.5 | Resource Allocation, Scheduling, and Load Balancing | 29       |

| 2.6 | Development Environment                             | 33<br>35 |

| 3.  | Parallel Applications                               | 40       |

| 3.1 | Introduction                                        | 40       |

| 3.2 | Boolean Satisfiability                              |          |

| 3.3 | Matrix-Vector Multiplication                        |          |

| 3.4 | Encryption Using AES                                |          |

| 3.5 | CHAMPION Demo Algorithms                            |          |

| 4.  | Model Development                                                                                                                                                                                | 50               |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 4.1 | Introduction                                                                                                                                                                                     | 50               |

| 4.2 | General Model Description                                                                                                                                                                        | 50               |

| 4.3 | HPC Analysis                                                                                                                                                                                     | 53<br>54         |

| 4.4 | RC Node Analysis                                                                                                                                                                                 | 56               |

| 4.5 | HPRC Multi-Node Analysis                                                                                                                                                                         | 61               |

| 4.6 | Load Imbalance Model  4.6.1 Introduction  4.6.2 General Load Imbalance Model  4.6.3 Application Load Imbalance Model  4.6.4 Background Load Imbalance Model  4.6.5 Complete Load Imbalance Model | 68<br>69<br>71   |

| 5.  | Model Validation                                                                                                                                                                                 | 78               |

| 5.1 | Validation Methodology                                                                                                                                                                           | 78               |

| 5.2 | Accuracy of Modeling Communication Times                                                                                                                                                         | 82               |

| 5.3 | Accuracy of Single Node RC Model  5.3.1 Wildforce Measurements  5.3.2 Firebird Measurements  5.3.3 Pilchard Measurements  5.3.4 Single Node Boolean SAT Solver Comparisons                       |                  |

| 5.4 | HPRC Model Validation                                                                                                                                                                            | 93               |

|     | 5.4.1 No-Load Imbalance Results                                                                                                                                                                  | 99<br>104<br>115 |

| 6.  | Application of Model                                                                                                                                                                             | 124              |

| 6.1 | Application Scheduling                                                                                                                                                                           |                  |

|     |                                                                                                                                                                                                  |                  |

| 6.2   | Scheduling in a NetSolve Environment | 151 |

|-------|--------------------------------------|-----|

| 7.    | Conclusions and Future Work          | 153 |

| 7.1   | Conclusions                          | 153 |

| 7.2   | Future Work                          | 156 |

| Bibli | iography                             | 158 |

| Appo  | endix                                | 169 |

| Vita  |                                      | 192 |

# LIST OF TABLES

| TABLE 2.1         | HPC Architecture Examples [75, 17]                                            | 10     |

|-------------------|-------------------------------------------------------------------------------|--------|

| TABLE 2.2         | HPRC Development Platforms                                                    | 18     |

| TABLE 4.1         | Symbols and Definitions                                                       | 52     |

| TABLE 5.1         | Validation Experiments and Goals                                              | 80     |

| TABLE 5.2         | Model Parameters for Wildforce from Benchmark Application                     | 85     |

| TABLE 5.3         | Runtime Predictions and Measurements (time in seconds)                        | 86     |

| TABLE 5.4         | Model Parameters for Firebird from Benchmark Application                      | 88     |

| TABLE 5.5         | Model Parameters for Pilchard from Benchmark Applications                     | 89     |

| TABLE 5.6         | SAT Software-Only Runtime Comparisons (time in seconds)                       | 90     |

| TABLE 5.7         | SAT RC Node Runtime Comparisons (time in seconds)                             | 92     |

| TABLE 5.8         | Overhead for RC systems (time in minutes)                                     | 92     |

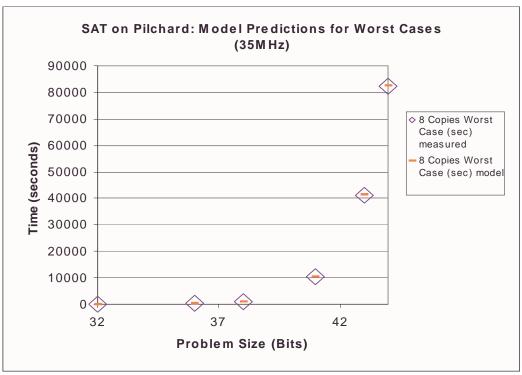

| TABLE 5.9         | Worst Case Values (time in seconds)                                           | 93     |

| <b>TABLE 5.10</b> | MPI SAT Solver No-Load Imbalance Results                                      | 94     |

| <b>TABLE 5.11</b> | MPI AES Algorithm No-load Imbalance Results                                   | 95     |

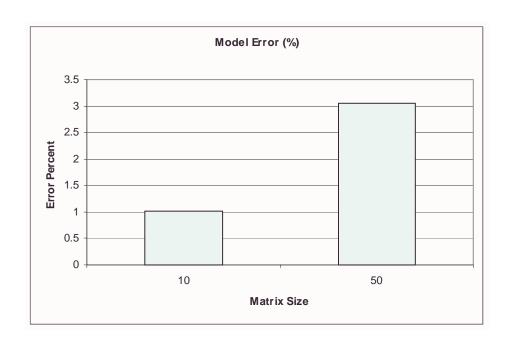

| TABLE 5.12        | MPI Matrix Vector Multiplication Algorithm No-load Imbalance Results          |        |

| <b>TABLE 5.13</b> | MPI SAT Solver Application Load Imbalance Results                             | 102    |

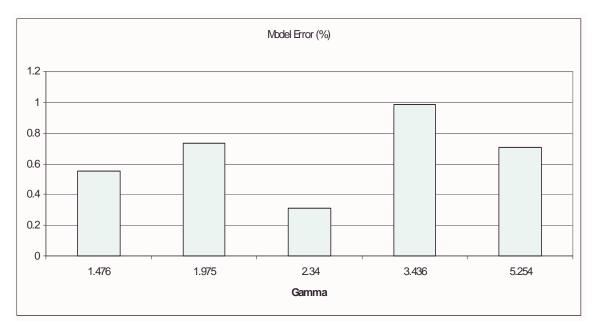

| <b>TABLE 5.14</b> | MPI Matrix Vector Algorithm Application Load Imbalance Results                | 104    |

| TABLE 5.15        | Typical factors for moderately Loaded Homogeneous Nodes Using PS Mode         | el 106 |

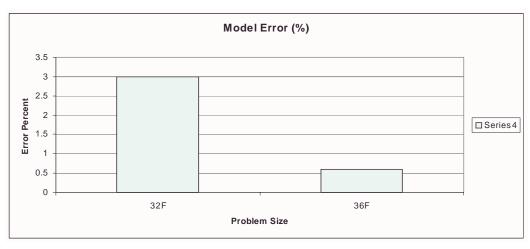

| <b>TABLE 5.16</b> | MPI SAT Solver Background Load Imbalance Results (Problem Size 32F)           | 108    |

| TABLE 5.17        | MPI SAT Solver Background Load Imbalance Results (Problem Size 36F)           | 109    |

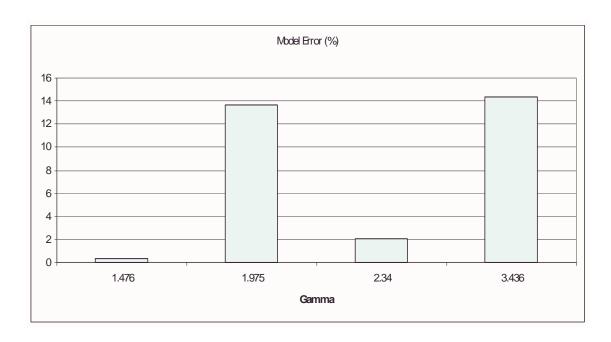

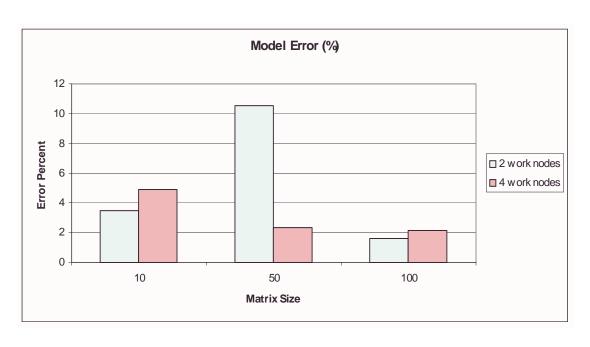

| TABLE 5.18        | MPI Matrix Vector Algorithm Background Load Imbalance Results                 | 111    |

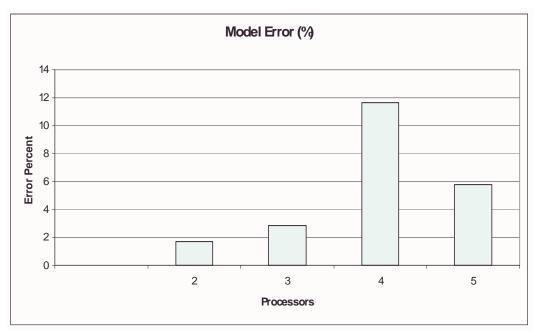

| <b>TABLE 5.19</b> | MPI AES Encryption Algorithm Background Load Imbalance Results                | 113    |

| TABLE 5.20        | MPI SAT Solver Application and Background Load Imbalance Results              | 115    |

| <b>TABLE 5.21</b> | MPI SAT Solver Application and Background Load Imbalance Results              | 116    |

| TABLE 5.22        | MPI Matrix Vector Algorithm Application and Background Load Imbalance Results |        |

| TABLE 5.23        | MPI SAT Solver Heterogeneous Resources Results                                |        |

| TABLE 5.24        | MPI Matrix Vector Algorithm Heterogeneous Resources Results                   |        |

| TABLE 5.25        | MPI AES Encryption Algorithm Heterogeneous Resources Results                  |        |

| TABLE 6.1         | Modeled Costs of Surrounding States of Near-Optimal Solution for AES on S     |        |

| 171022 0.1        | Heterogeneous Workstations (x=5, c=1)                                         |        |

| TABLE 6.2         | Constrained Runtime                                                           |        |

| TABLE 6.3         | Constrained Cost                                                              |        |

| TABLE a.1         | Communication Measurements: Message Round Trip Time                           |        |

| TABLE a.2         | Communication Measurements: Network Bandwidth (vlsi4)                         |        |

| TABLE a.3         | SAT Solver No-load Data (sec)                                                 |        |

| TABLE a.4         | SAT Solver Application Load Imbalance Data (sec)                              |        |

| TABLE a.5         | SAT Solver Background Load Imbalance Data (sec)                               |        |

| TABLE a.6         | SAT Solver Application and Background Load Imbalance Data (sec)               |        |

| TABLE a.7         | Matrix Vector Multiplication Algorithm No-load and Application Load Data      |        |

|                   | (msec)                                                                        |        |

| TABLE a.8  | Matrix Vector Multiplication Algorithm Background and Application Load Data |

|------------|-----------------------------------------------------------------------------|

|            | (msec) Part I                                                               |

| TABLE a.9  | Matrix Vector Multiplication Algorithm Background and Application Load Data |

|            | (msec) Part II                                                              |

| TABLE a.10 | Matrix Vector Multiplication Algorithm Background and Application Load Data |

|            | (msec) Part III                                                             |

| TABLE a.11 | Matrix Vector Multiplication Algorithm Background and Application Load Data |

|            | (msec) Part IV                                                              |

| TABLE a.12 | AES Algorithm No-load Data (msec)                                           |

| TABLE a.13 | AES Algorithm Background Load Imbalance Data (msec) (2 Nodes)               |

| TABLE a.14 | AES Algorithm Background Load Imbalance Data (msec) (3 Nodes)184            |

| TABLE a.15 | AES Algorithm Background Load Imbalance Data (msec) (4 Nodes)185            |

| TABLE a.16 | AES Algorithm Background Load Imbalance Data (msec) (5 Nodes)186            |

| TABLE a.17 | Runtime AES Application Homogeneous Resources Data                          |

| TABLE a.18 | AES Application Optimum Set Cost Function Homogeneous Resources Data 188    |

| TABLE a.19 | AES Application Cost Function Based on Load Homogeneous Resources           |

|            | Data                                                                        |

| TABLE a.20 | Runtime AES Application Heterogeneous Resources Data                        |

| TABLE a.21 | AES Application Optimum Set Cost Function Heterogeneous Resources Data 190  |

| TABLE a.22 | SAT Solver Application Optimization Space Homogeneous Resources Data 193    |

|            |                                                                             |

# LIST OF FIGURES

| FIGURE 1.1  | Flynn's Taxonomy                                                            | 2    |

|-------------|-----------------------------------------------------------------------------|------|

| FIGURE 1.2  | High Performance Reconfigurable Computer (HPRC) Architecture                | 3    |

| FIGURE 1.3  | Fork-Join Class of Algorithms                                               | 6    |

| FIGURE 2.1  | Block Diagram of the Pilchard Board                                         | . 14 |

| FIGURE 2.2  | Wildforce Architecture [5]                                                  | . 15 |

| FIGURE 2.3  | Firebird Architecture [5]                                                   | . 16 |

| FIGURE 2.4  | Area Density for Conventional Reconfigurable Devices [47]                   | . 28 |

| FIGURE 2.5  | RP-Space (a) Interconnect vs. Configuration and (b) Logic vs. Configuration | . 28 |

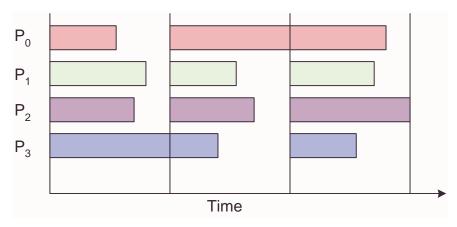

| FIGURE 3.1  | Synchronous Iterative Algorithm running on 4 processors                     | . 40 |

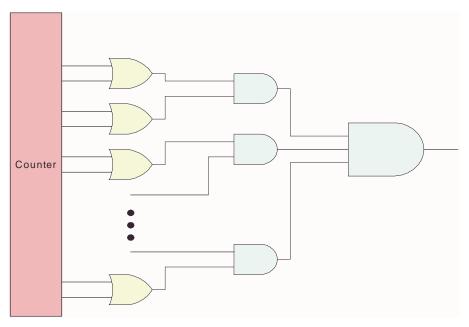

| FIGURE 3.2  | SAT Solver Core                                                             | . 44 |

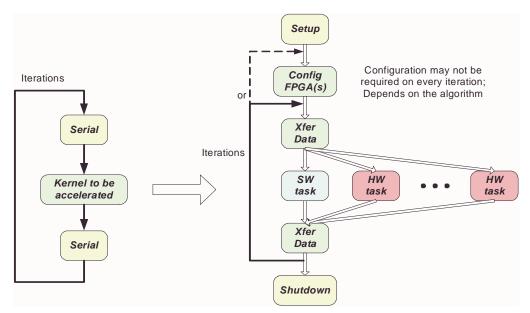

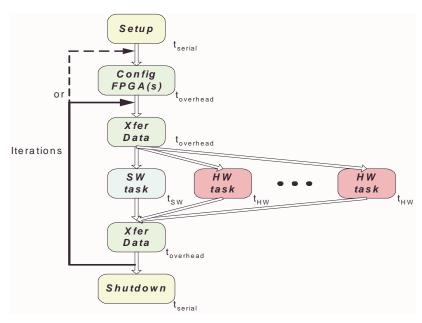

| FIGURE 4.1  | Synchronous Iterative Algorithm                                             | . 57 |

| FIGURE 4.2  | Flow of Synchronous Iterative Algorithm for RC Node                         | . 58 |

| FIGURE 4.3  | HPRC Architecture                                                           | . 61 |

| FIGURE 4.4  | Flow of Synchronous Iterative Algorithm for Multi Node                      | . 63 |

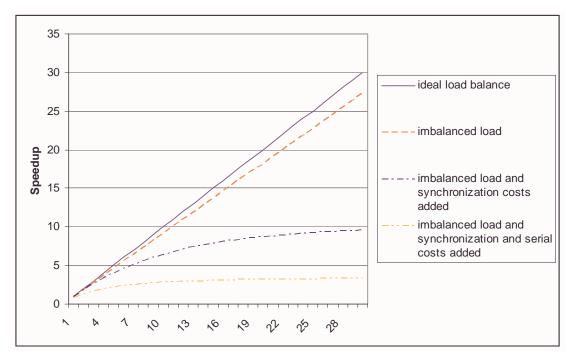

| FIGURE 4.5  | Speedup Curves                                                              | . 67 |

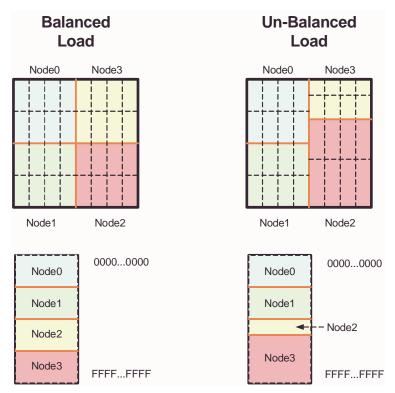

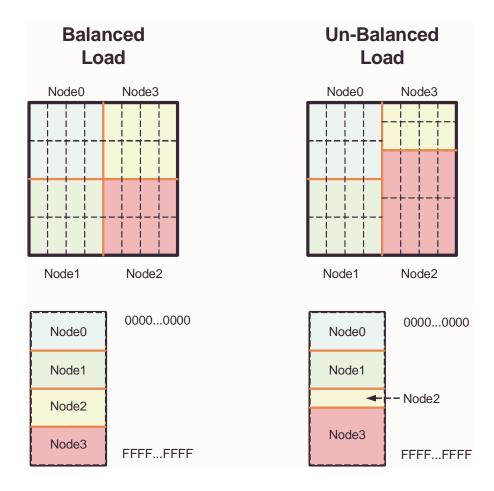

| FIGURE 4.6  | Application Load Distribution for SAT Solver Application                    | .72  |

| FIGURE 5.1  | Phases of Model Development                                                 | . 79 |

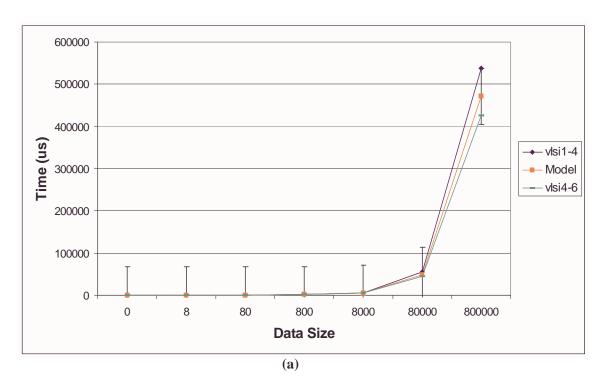

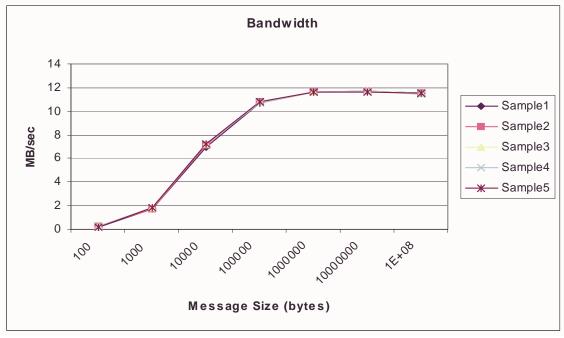

| FIGURE 5.2  | Communication Measurement Results                                           | . 84 |

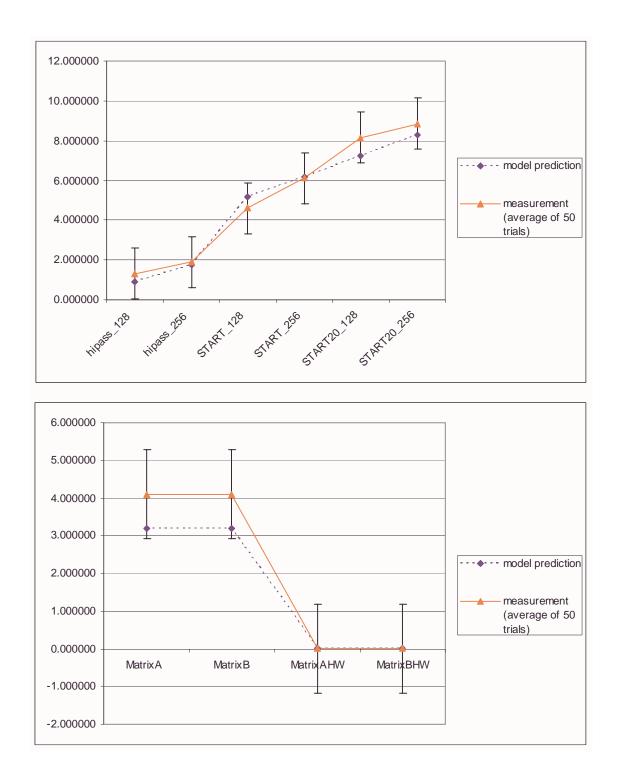

| FIGURE 5.3  | Comparison of RC Model Prediction with Measurement Results on Wildforce     | . 87 |

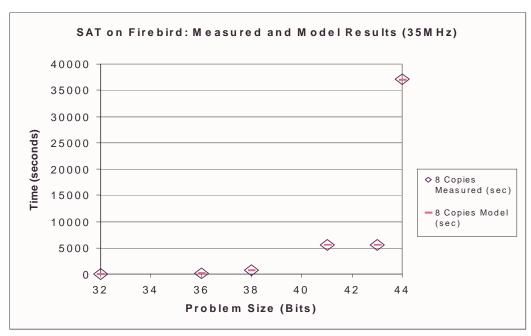

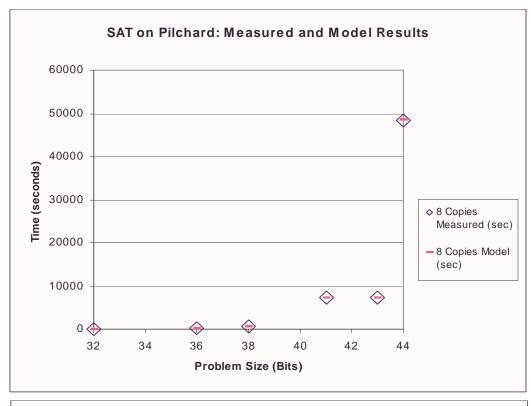

| FIGURE 5.4  | Boolean SAT Measured and Model Results on Firebird                          | .90  |

| FIGURE 5.5  | Boolean SAT Measured and Model Results on Pilchard                          | .91  |

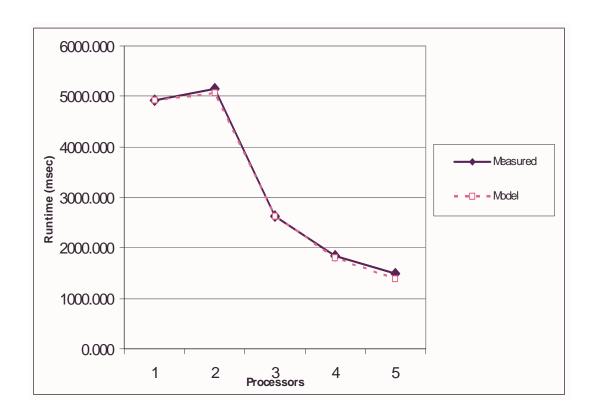

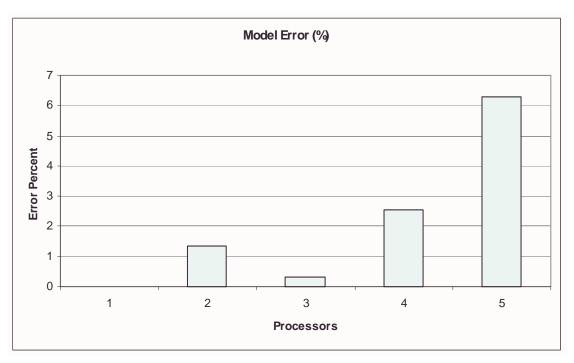

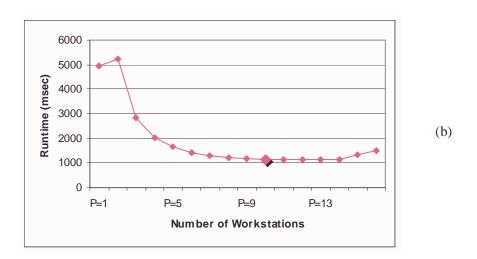

| FIGURE 5.6  | SAT Solver No-Load Imbalance Results                                        | .95  |

| FIGURE 5.7  | AES Algorithm No-Load Imbalance Results                                     | .96  |

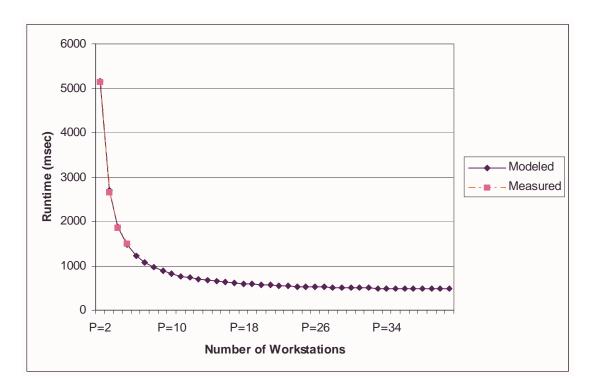

| FIGURE 5.8  | Matrix Vector Algorithm No-Load Imbalance Results                           | .98  |

| FIGURE 5.9  | Application Load Distribution for SAT Solver Application                    | 100  |

| FIGURE 5.10 | SAT Solver Application Load Imbalance Results                               | 102  |

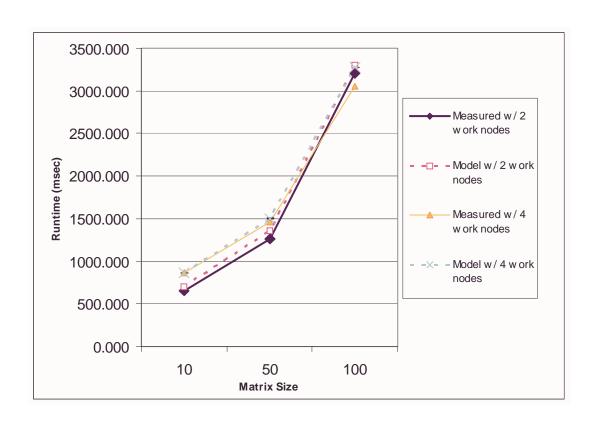

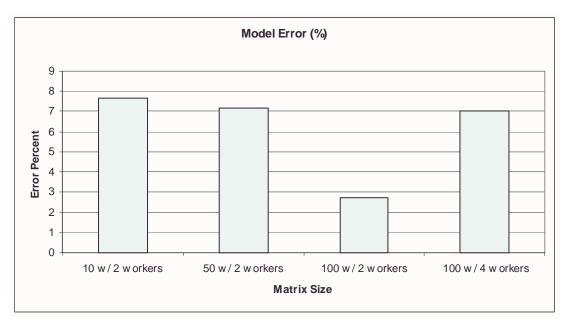

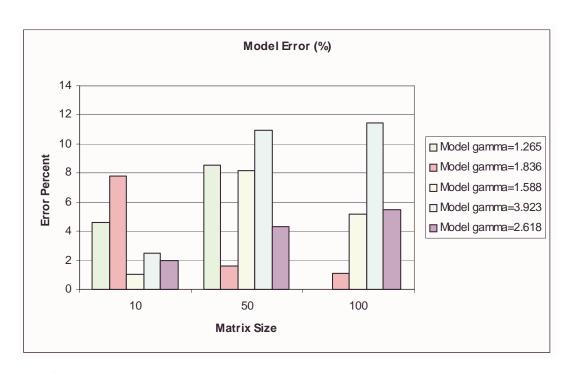

| FIGURE 5.11 | Matrix Vector Algorithm Application Load Imbalance Results                  | 105  |

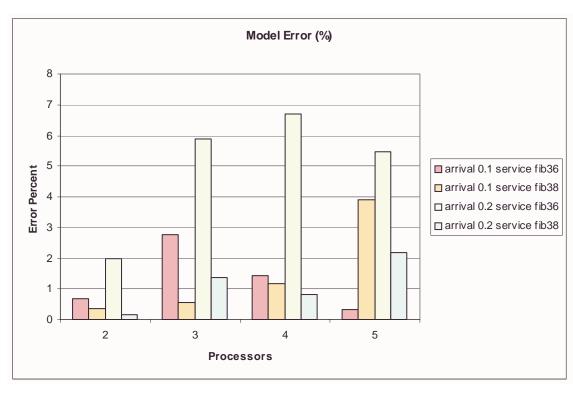

| FIGURE 5.12 | SAT Solver Background Load Imbalance Results                                | 110  |

| FIGURE 5.13 | Matrix Vector Algorithm Background Load Imbalance Results                   |      |

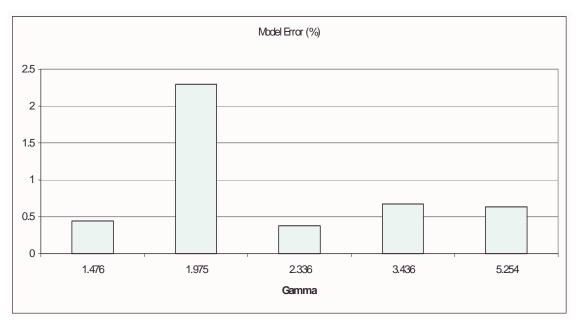

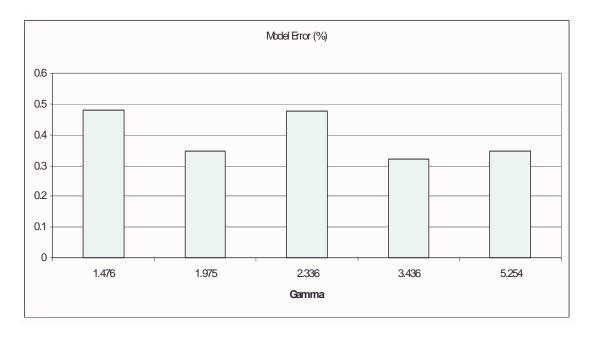

| FIGURE 5.14 | AES Algorithm Background Load Imbalance Results                             | 114  |

| FIGURE 5.15 | SAT Solver Application and Background Load Imbalance Results                | 117  |

| FIGURE 5.16 | Matrix Vector Algorithm Application and Background Load Imbalance           |      |

|             | Results                                                                     |      |

| FIGURE 5.17 | SAT Solver Heterogeneous Resources Results                                  |      |

| FIGURE 5.18 | Matrix Vector Algorithm Heterogeneous Resources Results                     |      |

| FIGURE 5.19 | AES Encryption Algorithm Heterogeneous Resources Results                    |      |

| FIGURE 6.1  | Algorithm for Minimum Runtime on Homogeneous Resources [102]                |      |

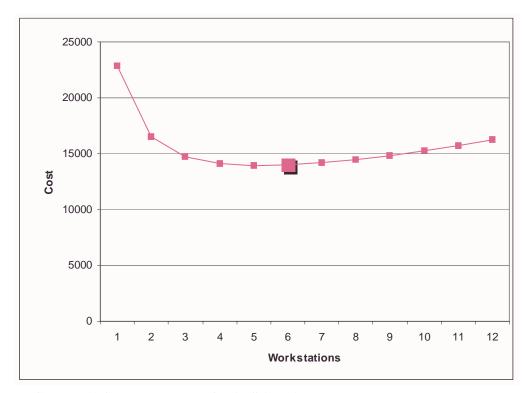

| FIGURE 6.2  | Optimum Set of Homogeneous Resources for AES Algorithm                      | 127  |

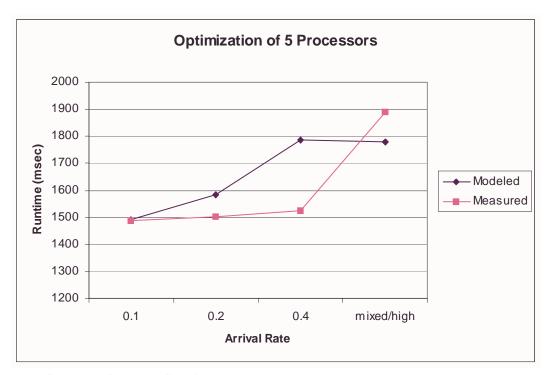

| FIGURE 6.3  | Optimum Set of 5 Homogeneous Resources, Mixed Background Arrival Rates      | 128  |

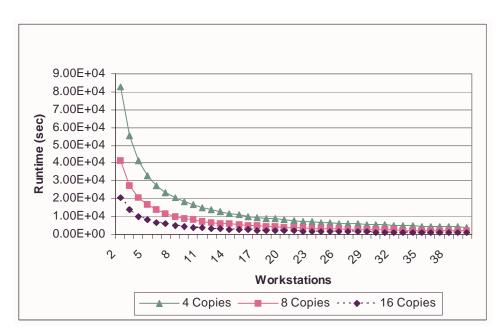

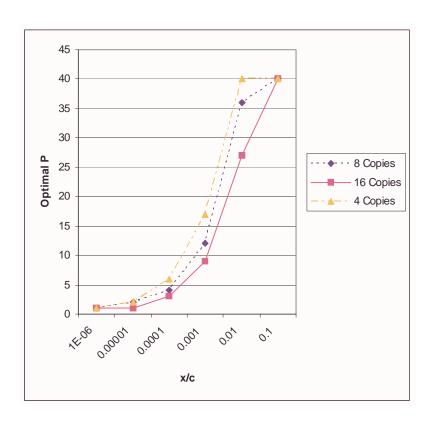

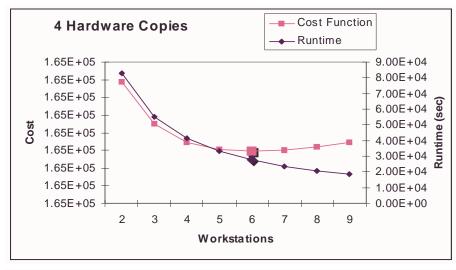

| FIGURE 6.4  | Optimum Set of Homogeneous Resources for SAT Solver: Compare number o       |      |

|             | Hardware Copies                                                             |      |

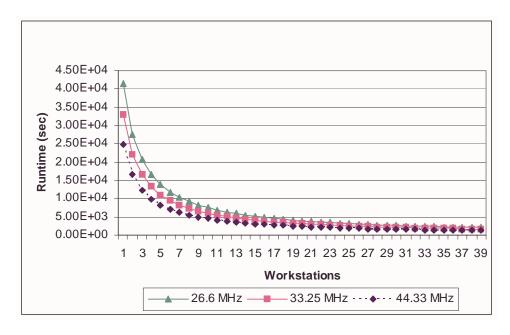

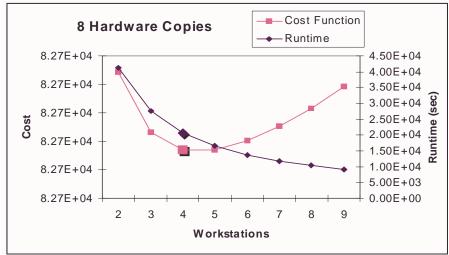

| FIGURE 6.5  | Optimum Set of Homogeneous Resources for SAT Solver: Compare Hardware         |

|-------------|-------------------------------------------------------------------------------|

|             | Speed                                                                         |

| FIGURE 6.6  | Greedy Heuristic for Minimum Runtime on Heterogeneous Resources [102]131      |

| FIGURE 6.7  | Near-Optimum Set of Heterogeneous Resources for AES Algorithm: (a) 8 nodes    |

|             | and (b) 16 nodes                                                              |

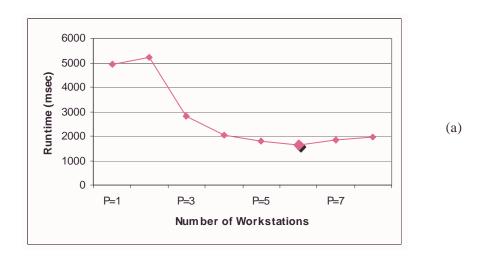

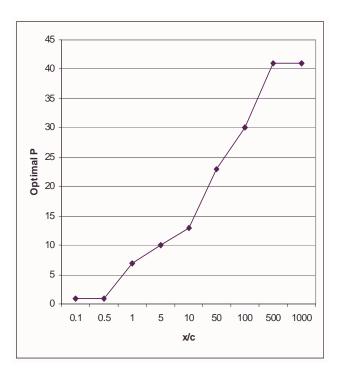

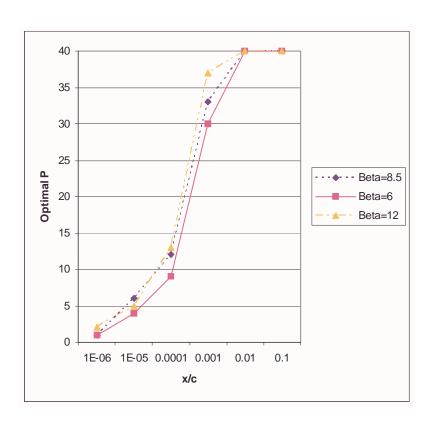

| FIGURE 6.8  | Optimal Set of Homogeneous Processors for AES Algorithm                       |

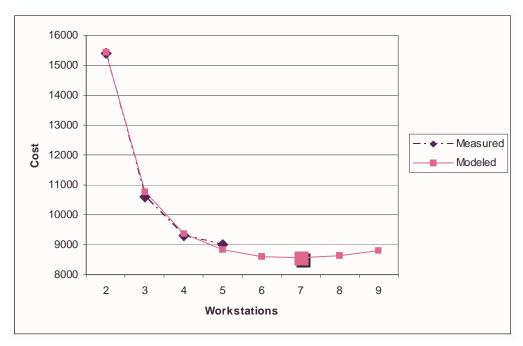

| FIGURE 6.9  | Cost for AES Algorithm on Homogeneous Processors (x=1, c=1)136                |

| FIGURE 6.10 | Optimal Set of Heterogeneous Processors for AES Algorithm                     |

| FIGURE 6.11 | Cost based on load for AES Algorithm on Homogeneous Processors                |

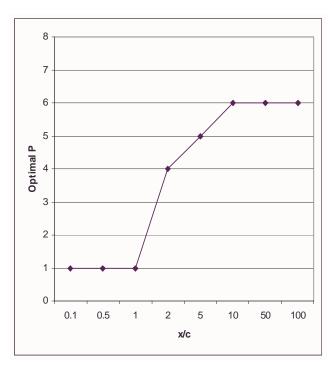

| FIGURE 6.12 | Optimal Set of Homogeneous Resources for SAT Solver, Varying the Number of    |

|             | Hardware Copies                                                               |

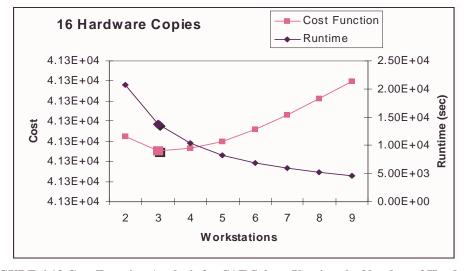

| FIGURE 6.13 | Cost Function Analysis for SAT Solver, Varying the Number of Hardware Copies  |

|             | (x/c = 0.0001)                                                                |

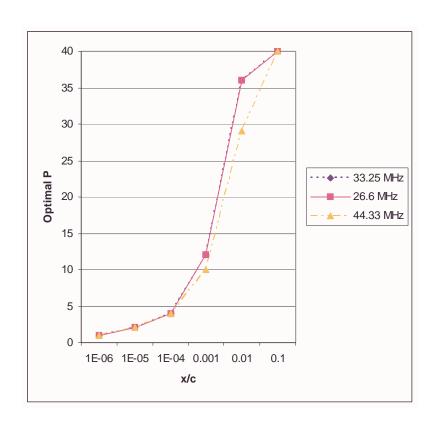

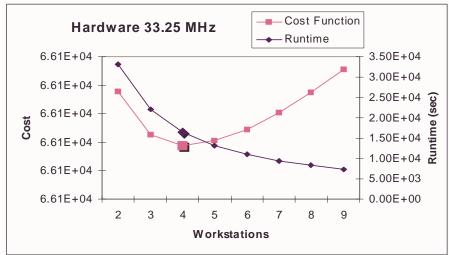

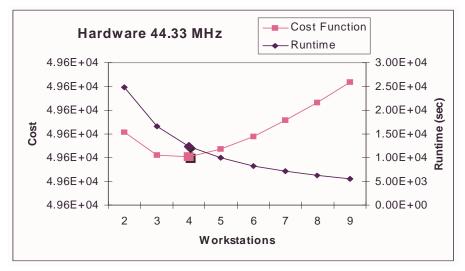

| FIGURE 6.14 | Optimal Set of Homogeneous Resources for SAT Solver, Varying the Hardware     |

|             | Speed                                                                         |

| FIGURE 6.15 | Cost Function Analysis for SAT Solver, Varying the Hardware Speed ( $x/c =$   |

|             | 0.0001)                                                                       |

| FIGURE 6.16 | Optimal Set of Homogeneous Resources for SAT Solver, Varying the Application  |

|             | Load Imbalance                                                                |

| FIGURE 6.17 | Cost Function Analysis for SAT Solver, Varying the Application Load Imbalance |

|             | (x/c = 0.0001)                                                                |

| FIGURE 6.18 | The NetSolve System [35]                                                      |

## **CHAPTER 1**

## **INTRODUCTION**

#### 1.1 Motivation

Integrating the architecture and techniques from parallel processing or High Performance Computing (HPC) with those of Reconfigurable Computing (RC) systems offers high performance users with the potential of increased performance and flexibility for a wide range of computationally demanding problems. HPC architectures and RC systems have independently demonstrated performance advantages for many applications such as digital signal processing, circuit simulation, and pattern recognition among others. By exploiting the near "hardware specific" speed of RC systems in a distributed network of workstations there is promise for additional performance advantages over other software-only or uniprocessor solutions.

#### **1.1.1** What is HPC?

High Performance Computing is the use of multiple processors or processing nodes collectively on a common problem. The primary motivation for HPC is to overcome the speed bottleneck that exists with a single processor. The classic taxonomy for classifying computer architectures as defined by Flynn in 1972 [59] is shown in Figure 1.1. Flynn's taxonomy is based on the two types of information flow into a processor: *instructions* and *data*. Machines are classified according to the number of streams for each type of information. The four combinations are *SISD* (single instruction stream, single data stream), *SIMD* (single instruction stream, multiple data streams), *MISD* (multiple instruction streams, single data stream), and *MIMD* (multiple instruction streams, multiple data streams). HPC systems can also be classified based on their memory struc-

1

|               | Single<br>Instruction | Multiple<br>Instruction |

|---------------|-----------------------|-------------------------|

| Single Data   | SISD                  | MISD                    |

| Multiple Data | SIMD                  | MIMD                    |

FIGURE 1.1 Flynn's Taxonomy

ture. The common programming models are *shared memory*, *distributed memory* (message passing) and *globally addressable*. We will discuss these more in a later section and focus our modeling on distributed memory MIMD architectures.

#### **1.1.2** What is RC?

Reconfigurable Computing is the combination of reconfigurable logic (most commonly in the form of Field Programmable Gate Arrays or FPGAs) with a general-purpose microprocessor. The architectural intention is to achieve higher performance than normally available from software-only solutions while at the same time providing flexibility not available with Application Specific Integrated Circuits (ASICs). In RC architectures, the microprocessor performs those operations that cannot be done efficiently in the reconfigurable logic such as loops, branches, and possible memory accesses, while computational cores are mapped to the reconfigurable hardware [43] to achieve the greatest performance advantage. We will discuss more details regarding RC systems in a later section including some representative architectures.

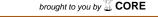

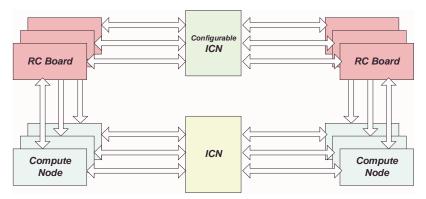

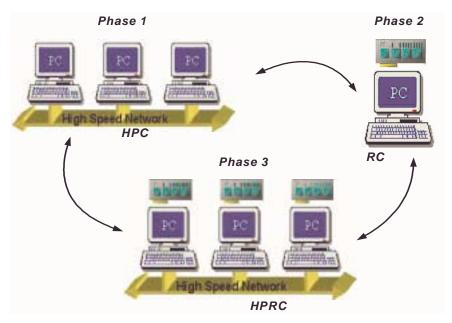

FIGURE 1.2 High Performance Reconfigurable Computer (HPRC) Architecture

#### 1.1.3 What is HPRC?

High Performance Reconfigurable Computing or HPRC is the proposed combination of High Performance Computing and Reconfigurable Computing. The proposed HPRC platform shown in Figure 1.2 consists of a number of distributed computing nodes connected by some interconnection network (ICN) (switch, hypercube, systolic array, etc.), with some or all of the computing nodes having RC element(s) associated with them. The HPRC platform will potentially allow users to exploit the performance speedups achievable in parallel systems in addition to the coprocessing performance of the RC element. Many computationally intensive applications stand to benefit from this architecture: image and signal processing, simulations, among others. The focus of our modeling will be on algorithms and applications that fit into the *fork-join* class and more specifically *synchronous iterative algorithms*. More discussion on this class of algorithms and limitations follows in a later section.

An additional configurable network between RC elements may offer some applications such as discrete event simulation even more performance advantages by providing a less inhibited

route for synchronization, data exchange, and other communications necessary between processing nodes. Research by Chamberlain indicates the potential performance improvement from a dedicated synchronization network for synchronous, discrete-event simulations [38, 97, 98]. The parallel reduction network (PRN) proposed by Reynolds, et al., demonstrated the performance advantages from dedicated hardware to support synchronization in parallel simulations [111, 112, 113]. The PRN separates the synchronization computation from the application computation, offloading the synchronization overhead from host processors and the host communication network. This additional network could vastly improve performance for not only applications with barrier synchronization events but any application requiring the exchange of large amounts of data between nodes. Other research by Underwood, et al. [123, 124, 125], confirms the performance benefits of a specialized configurable network interface card in a Beowulf cluster. A Beowulf cluster is an approach to building a supercompter as a cluster of commodity off-the-shelf personal computers, interconnected with an ICN. The idea is to build a cost effective, high performance computer. The Intelligent Network Interface Card (INIC) developed by Underwood, et al., uses reconfigurable computing to assist with both network communications and computational operations enhancing both the network and processor capabilities of the cluster. The results presented for a 2-D Fast Fourier Transform (FFT) and an integer sorting algorithm show significant performance benefit for both applications as the cluster size increases. The resulting performance for the two test applications is significantly better than on a Beowulf cluster with commodity network interface cards.

HPC and RC individually are challenging to program and utilize effectively. Combining these powerful domains will require new analysis tools to aid us in understanding and exploiting the design space to its full potential. A performance modeling framework with models describing this new architecture will not only help in understanding and exploiting the design space but will

be a building block for many of these tools. The system performance is affected by architecture variables such as number of nodes, number of FPGAs, FPGA type and size, processing power, memory distribution, network performance and configuration, just to name a few, and the available permutations make the design space extremely large. Without a modeling framework to assist with the analysis of these issues, tradeoffs cannot be effectively analyzed potentially resulting in grossly inefficient use of the resources.

### 1.2 General Problem Statement

Networks or clusters of workstations can provide significant computational capabilities if effectively utilized. Adding to this powerful architecture the capabilities of RC systems introduces challenging problems in efficient utilization of resources. Performance analysis and architecture design for HPC and RC systems are challenging enough in their individual environments. For the proposed HPRC architecture, these issues and their interaction are potentially even more complex. Although substantial performance analysis research exists in the literature with regard to High Performance Computing (HPC) architectures [22, 23, 41, 67, 74, 92, 97, 98, 102, 106, 108, 122] and even some with respect to Reconfigurable Computing (RC) [47, 48, 72, 73], the analysis of these architectures working together has received little attention to date and currently there is a gap in the performance analysis research with regard to an HPRC type of architecture. To evaluate the tradoffs associated with this architecture, we need an accurate understanding of the computational system, including the workstations, the RC units, the distributed applications, and the effect of competing users of the resources. As part of this dissertation, we develop an accurate performance modeling methodology for synchronous iterative algorithms, a sub-class of fork-join algorithms, running on shared, heterogeneous resources.

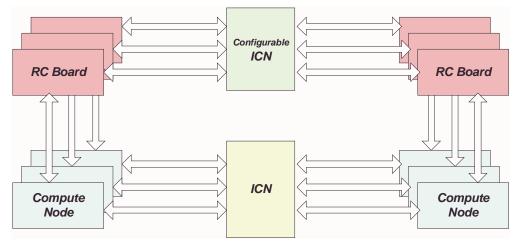

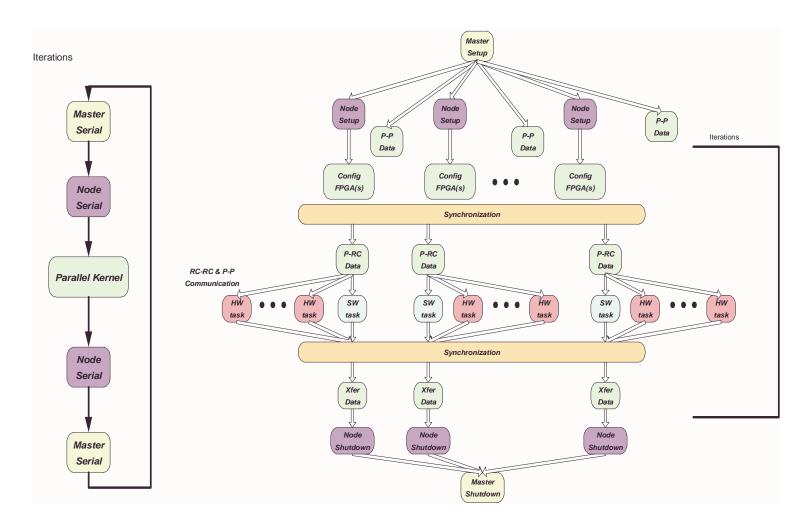

FIGURE 1.3 Fork-Join Class of Algorithms

### 1.2.1 Fork-Join and Synchronous Iterative Algorithms

As the name implies, *Synchronous Iterative Algorithms (SIAs)*, also known as *multi-phase algorithms* in the literature, are iterative in nature with each processor performing some portion of the required computation each iteration. Many computationally intensive parallel applications fall into this large class of algorithms. SIAs are a sub-class of a much broader set of algorithms known as fork-join algorithms (see Figure 1.3). Also within the class of SIAs we find those with identical and independent iterations where the iterations of the algorithm are independent from one another and identical. In fork-join algorithms, a main process or thread forks off some number of other processes or threads that then continue in parallel to accomplish some portion of the overall work before rejoining the main process or thread. Numeric computations such as discrete-event simulation (excluding Time Warp), numeric optimizations, Gaussian elimination, FFTs, Encryption (Data Encryption Standard - DES and Advanced Encryption Standard - AES), sorting algorithms, solu-

tions of partial differential equations, and others are all members of this class of algorithms. The modeling methodology developed here is applicable to members of the fork-join class.

We develop a performance model for fork-join type algorithms that takes into account division of computation between the workstation processor and the reconfigurable unit, variance in the computational requirements of the application across the set of workstations, background loading (due to shared resources), and workstation heterogeneity. The development of an analytic performance model is a significant contribution that facilitates resource management optimization. By helping users understand the performance tradoffs in the computer architecture, one can quickly determine the optimium application mapping for given constraints or identify the best set of workstations for optimium runtime.

As an application of the performance model, we consider the scheduling algorithms employed in distributed systems. Many of the scheduling algorithms do not account for the performance implications of design choices [102]. We use the modeling results of this dissertation to improve the scheduling of applications and achieve better performance. We explore the impact of load conditions, workstation make-up, and other constraints using our modeling results as input to a scheduler.

We assume for our HPRC platform shown in Figure 1.2 that we have a network of shared heterogeneous workstations to which we will map our distributed applications. According to Flynn's taxonomy, we have a loosely-coupled distributed memory, MIMD processing environment. To facilitate distributed processing with these workstations, the Message Passing Interface (MPI) [118] system is used. MPI supports message-passing and the control of processes on heterogeneous distributed computers.

In the next chapter, a brief survey is given which discusses important related literature. Following this survey, we consider three fork-join type of applications which are used throughout the dissertation to compare our analytic modeling results to the empirical measurements. We then develop a performance modeling methodology for describing the performance of these algorithms executing on a cluster of shared heterogeneous workstations. Next, using the empirical results from the test applications, we validate the performance model. With the performance model validated, we then apply the model to optimizing the resource management of the cluster. Finally, we present conclusions of this dissertation and discuss future work to extend the applicability of the model and optimization results.

## **CHAPTER 2**

## BACKGROUND AND RELATED WORK

### 2.1 Introduction

In this chapter we will review some of the architectures found in High Performance Computing (HPC) and Reconfigurable Computing (RC) and introduce the High Performance Reconfigurable Computing (HPRC) platform. We will also look at some performance metrics common in these architectures and how they relate to HPRC. Next we will look at the issues of performance evaluation and the methods we can employ to develop a modeling methodology or framework for HPRC. Finally, we will look at the development tools and environments that are available today for HPC and RC and how we can use them in the new HPRC platform.

## 2.2 Building the HPRC Architecture

The architecture of a computer system affects the performance, whether good or bad, of a given application. Issues such as dedicated and non-dedicated resources, memory size and distribution, communication structure, and instruction set all affect the performance capability of the system. In this section, we will review some of the common architectures in High Performance and Reconfigurable Computing and look at how they can be used in HPRC.

## 2.2.1 High Performance Computing and Networks of Workstations

The results found in High Performance Computing research confirm performance advantages over single processor machines for many computationally intensive applications. However, many HPC platforms have been limited to the relatively small research oriented market due to the

TABLE 2.1 HPC Architecture Examples [75, 17]

|               | SIMD                 | MIMD                  |                      |

|---------------|----------------------|-----------------------|----------------------|

| Shared Memory | Hitachi S3600 series | KSR1                  | HP/Convex C4 series  |

|               | Vector Machines      | Cray C90, J-90,       | Tera MTA             |

|               | XMP                  | SV1ex                 | Hitachi S3800 series |

|               |                      | YMP                   |                      |

|               |                      | DASH                  |                      |

| Distributed   | CPP                  | BBN                   | Sun Fire 3800-15K    |

| Memory        | CM-1, CM-2           | nCube                 | Paragon              |

|               | DEC MPP              | CM-5                  | SP2                  |

|               | MasPar MP1, MP2      | Intel iPSC            | NOWs                 |

|               | AMT DAP              | Cray T3E              | Clusters             |

|               |                      | Hitachi SR8000 Series |                      |

high costs normally incurred in acquiring, developing and programming them. Although trends indicate a changing market [17, 50, 52] as venders migrate toward clusters and networks of workstations the cost of ownership still often precludes mass market use. These specialized machines dedicated to parallel processing often consist of an array of tightly coupled homogeneous processors connected by an optimized network. Furthermore, their architecture is often specialized for a specific genre of applications thus perpetuating the high costs associated with ownership and limiting the efficiency for applications other than the target application.

As discussed in Chap. 1, computer architectures can be divided into four main categories as described in Flynn's taxonomy [59]: *SISD*, *SIMD*, *MISD*, and *MIMD*. While examples of the MISD class are almost non-existent, examples of the SISD or von Neuman architecture include mainframes, early generation PCs and MACs. Examples of SIMD and MIMD architectures are given in Table 2.1.

By taking advantage of cheaper microprocessor technology and ever improving interconnection networks, today massively parallel systems can achieve higher performance for less cost. The task of harnessing the full potential of these systems is difficult at best but the results can be quite dramatic, with speedups many times that of a serial processor [67].

From a hardware standpoint, the recent HPC research in the area of Beowolf clusters is confirming high performance at reduced cost. Beowolf clusters consist of relatively inexpensive commodity workstations connected by a general-purpose network [82]. These systems, although they may not be recognized as Beowolf clusters, currently exist throughout industry, academia, and government. It has been shown that many of these workstations are often idle up to ninety-five percent of the time [33, 84] leaving most of their computing power unused. A means of harnessing the unused computing cycles of these workstations can provide a cost-effective and powerful HPC platform.

Another architectural alternative, *grid computing*, enables geographically distributed resources to be shared, allowing them to be used as a single, unified resource for solving large-scale computing problems. Like Beowolf clusters, grid computers offer inexpensive access to resources but irrespective of their physical location or access point. The Scalable Intra-campus Research Grid (SInRG) at the University of Tennessee [16] is a grid computer with special system software that integrates high performance networks, computers and storage systems into a unified system that can provide advanced computing and information services (data staging, remote instrument control, and resource aggregation).

## 2.2.2 Reconfigurable Computing

Reconfigurable computing (RC) is the coupling of reconfigurable units (often in the form of FPGAs) to general-purpose processors. The performance advantage of reconfigurable hardware

devices such as Field Programmable Gate Arrays (FPGAs) now rivals that of custom ASICs but with the added run-time design flexibility not available in custom hardware. The role of FPGAs and reconfigurable computing in the present and near future include improving the performance of many scientific and signal processing applications [70, 71]. Many of today's computationally intensive applications can benefit from the speed offered by application specific hardware co-processors, but for applications with multiple specialized needs, it is not feasible to have a different co-processor for every specialized function. Such diverse applications stand to benefit the most from the flexibility of RC architectures since one RC unit can potentially provide the functionality of several ASIC co-processors. Several research groups have demonstrated successful RC architectures [30, 47, 63, 64, 72, 73, 11, 80, 87, 93, 94, 126, 131].

There are several RC options available from companies such as Annapolis Microsystems [5], Nallatech [13], Virtual Computer Corporation (VCC) [20], and research organizations such as University of Southern California's Information Sciences Institute (ISI) [11], The Chinese University of Hong Kong [87], and Carnegie Mellon University [64, 94]. The Wildforce [5] and Firebird [5] units from Annapolis Microsystems are both PCI-bus cards with onboard memory. The Ben-NUEY RC system from Nallatech [13], the H.O.T. I and H.O.T. II systems from VCC [20], and the SLAAC units from ISI [11] are all PCI-bus cards. The Pilchard architecture developed by The Chinese University of Hong Kong [87] interfaces through the memory bus and is more closely coupled to the processor. The PipeRench reconfigurable fabric from Carnegie Mellon [64] is an interconnected network of configurable logic and storage elements which uses pipeline reconfiguration to reduce overhead.

Another research area in which the use of reconfigurable devices is becoming popular is Systems on a Chip (SoC). Known as SoPC (Systems on a Programmable Chip), Xilinx [128],

Altera [4], Atmel [6] and others have developed programmable devices which give the user the flexibility to include user reconfigurable area in addition to sophisticated intellectual property cores, embedded processors, memory, and other complex logic all on the same chip.

**RC Hardware.** For testing and validation of the HPRC model, we will use three RC coprocessors: Pilchard [87], Annapolis Microsystems' Wildforce and Firebird [5].

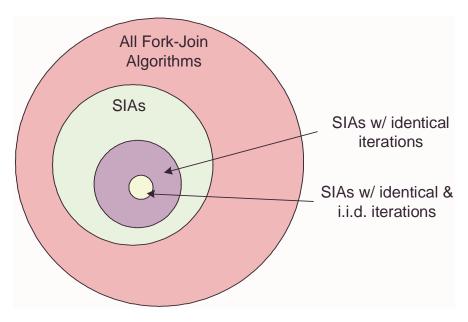

The Pilchard architecture (Figure 2.1) consists of a Xilinx Virtex 1000E FPGA interfaced to the processor via the SDRAM DIMM slot [87]. The logic for the DIMM memory interface and clock generation is implemented in the FPGA. The board also provides an expansion header for interfacing to external logic, memory or analyzer. The FPGA is configured using the download and debug interface which is separate from the DIMM interface and as such requires a separate host program to configure the FPGA. The Pilchard architecture addresses the bandwidth bottleneck of the PCI bus between the RC unit and the processor by placing the RC unit on the memory bus. However, this interface may be limited since it is less flexible than a PCI bus.

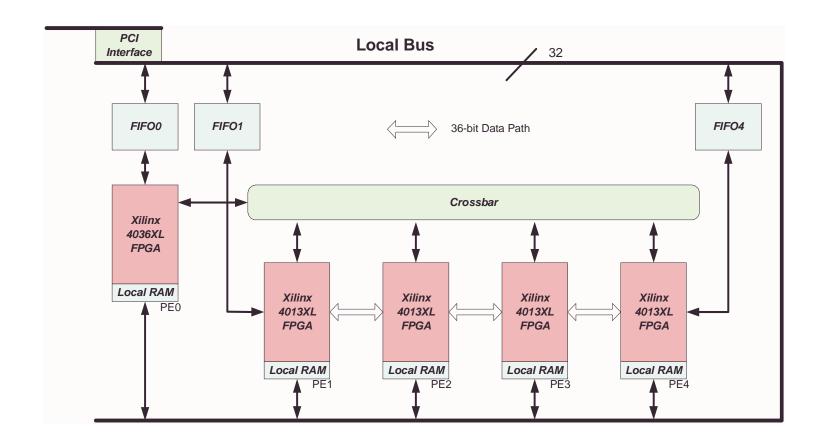

The Wildforce board from Annapolis Micro Systems [5] is a PCI-bus card, which contains four Xilinx XC4013XL chips for computational purposes and a Xilinx XC4036XL chip for communicating with the host computer. Each FPGA on the board has a small daughterboard, which allows external interfaces with the programmable elements (PEs). Each of the PEs on our Wildforce board has 32 KByte of 32-bit SRAM on its daughterboard. A dual-port memory controller is included on the daughterboards to allow both the PEs and the host computer access to the SRAM. A simplified block diagram of the Wildforce board is shown in Figure 2.2.

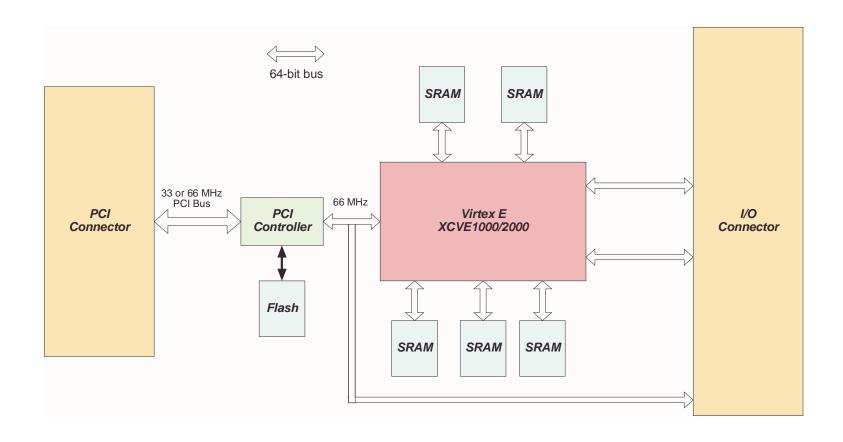

The Firebird board shown in Figure 2.3 consists of a single Xilinx Virtex 1000E FPGA.

The board is PCI based and includes an onboard PCI controller so that valuable FPGA resources

FIGURE 2.1 Block Diagram of the Pilchard Board

FIGURE 2.2 Wildforce Architecture [5]

FIGURE 2.3 Firebird Architecture [5]

are not used for PCI functions. The device is runtime reconfigurable through the host interface but not partially reconfigurable. The PCI bus interface supports 66MHz and the five 64 bit wide SRAM banks offer up to 5.4GBytes/sec memory bandwidth. The board also features an I/O connector for external interfaces.

### 2.2.3 High Performance Reconfigurable Computing (HPRC)

The proposed HPRC platform is a combination of the HPC and RC architectures. HPRC consists of a system of RC nodes connected by some interconnection network (switch, hypercube, array, etc.). Each of the RC nodes may have one or more reconfigurable units associated with them. This architecture as stated before provides the user with the potential for more computational performance than traditional parallel computers or reconfigurable coprocessor systems alone.

The HPRC architecture has almost limitless possibilities. Starting with the roots of HPC, there are many network topologies (hypercube, switch, etc.), memory distributions (shared, distributed), and processor issues (instruction set, processing power, etc.) to consider. These options alone make performance analysis complicated and interesting. Adding in the options available in RC such as coupling of FPGA to processor (attached unit, coprocessor, etc.), number of FPGA units, size of FPGA(s), separate or shared memory for FPGA(s), dedicated interconnection network, among others, and the analysis problem becomes enormous. Getting a handle on these issues and their affect on the system's performance with the use of a modeling framework will be integral in exploiting this potentially powerful architecture.

**HPRC Hardware.** Two HPRC clusters were available for developing and validating the model. The Air Force Research Laboratory in Rome, NY has assembled a two chassis, 48 node Heterogeneous HPC from HPTi, which marries the benefits of Beowolf cluster computing with the recon-

**TABLE 2.2 HPRC Development Platforms**

| Platform                  | Number<br>of Nodes | Number<br>of<br>FPGAs/<br>Node | FPGA Type  | Gates per<br>Node | I/O<br>Technology | Type of RC<br>Card |

|---------------------------|--------------------|--------------------------------|------------|-------------------|-------------------|--------------------|

| Wildforce                 | 1                  | 5                              | XC4013 (4) | 88K               | PCI Bus           | Wildforce          |

|                           |                    |                                | XC4036 (1) |                   |                   |                    |

| Firebird                  | 1                  | 1                              | XCVE1000   | 1M                | PCI Bus           | Firebird           |

| Heteroge-<br>neous<br>HPC | 48                 | 2                              | XC2V6000   | 12M               | PCI Bus           | Firebird           |

| Pilchard<br>Cluster       | 8                  | 1                              | XCVE1000   | 1M                | Memory Bus        | Pilchard           |

figurability of FPGAs. Each node harbors an Annapolis Micro Systems [5] Wildstar II which is populated with two Xilinx XC2V6000 FPGAs. The system is designed for a throughput of 845 GFLOPS (SP) or 422 GFLOPS (DP), from the Beowolf cluster, and 34 FIR TeraOPS from the FPGAs [3]. The HPRC cluster at UT consists of eight Pentium nodes populated with Pilchard boards. Listed in Table 2.2 are the HPRC platforms used to develop our modeling framework.

We will work with a MIMD, distributed memory, Beowolf cluster of eight Pentium nodes populated with one Pilchard reconfigurable card per node. Each of the Pilchard cards has on-board FPGA memory and no dedicated network between RC units.

# 2.3 Performance Evaluation, Analysis and Modeling

#### 2.3.1 Overview

Development of a model for studying system performance requires selection of a modeling tool or technique and definition of metrics for evaluation. The metrics selected will depend on the architecture features and the issues of interest. Other issues of interest include effective resource management and usage cost determination. We will now look at some performance evaluation techniques followed by some of the performance modeling research on fork-join and SIAs found in the literature.

### **2.3.2** Performance Evaluation Techniques

Significant research has been conducted in performance analysis and performance modeling for HPC. Performance models will be necessary tools for understanding HPRC issues and potentially determining the best mapping of applications to HPRC resources. There are three broad classes of performance evaluation techniques: *measurement*, *simulation*, and *analytical models* [74]. Each technique has variations and selection of the most suitable alternative is often difficult. Issues to consider are the desired result or application of the model, the accuracy needed, the development stage of the computer system, and the model development cost. With these issues in mind we now look at the three techniques and determine the best approach for our needs.

Measurement. The technique of measurement when used for performance evaluation is based on the direct measurements of the system under study using software and/or hardware monitors. This technique provides the most accurate representation but requires that the system be available. Measurement techniques are very often used in *performance tuning* whereby the information gathered can be used later to improve performance [74]. For example, frequently used segments of the software can be optimized with performance tuning thereby improving the performance of the whole program. Similarly, the resource utilizations of the system can also be obtained and performance bottlenecks identified. Other common uses of measurements is gathering data for other models (parameterization and calibration), characterizing workloads, or validating a system model [74]. Since there are unavoidable disturbances to the system during measurements such as loading and other overhead caused by the probes or monitors, the data collected must be analyzed and

scrutinized with statistical techniques in order to draw meaningful conclusions. Care must also be taken in selecting the output parameters to be measured, how they will be measured, and how and what inputs will be controlled to avoid corrupting results with invalid stimuli [81]. Other issues that must be considered are the costs involved to instrument the system and gather data, the practicality of measuring for the desired parameters, and performance perturbations from probes and monitoring devices.

The use of measurement as a performance evaluation tool has a number of drawbacks. First, measurements must be meaningful, accurate, and within the capabilities of available monitors. Second, monitors and probes are characteristically intrusive and can perturb system performance resulting in corrupted data. Finally, the real system must be implemented and available which does not allow for prediction of system performance and/or analysis of different system configurations.

**Simulation Models.** Simulation involves constructing a model for the system's behavior and driving it with an abstracted workload or trace data. It is often used to predict the performance of a system or to validate other analytical models and it is not necessary that the system exist enabling the examination of a larger set of options than with measurement techniques alone. The major advantages of simulation are generality, visibility, controllability, and flexibility [81] and the collection of data does not modify the system behavior as in measurement. However, like measurement, simulation modeling has some disadvantages. Simulation modeling also requires careful attention to the experiment design, data gathering process, and subsequent data analysis since the end results will only be as accurate as the model. The level of detail of the model should be carefully considered since it is often not necessary to duplicate the complete detailed behavior of the system. As the detail and complexity of the model increases, typically so do the model runtime and

development costs. Again like measurement, the amount of data can be enormous and statistical methods must be used to analyze the results.

One of the major drawbacks of simulation is the performance; on sequential machines, large simulations can take enormous amounts of time and the simulation runs must be long enough that startup transient effects do not impact results. Other problems with simulations are difficulty in model validation and balancing the model's fidelity. Completely validating simulation models is impractical since all possibilities cannot conceivably be tested. Additionally, highly detailed models may reflect microscopic behavior while at the expense of the ability to examine the macroscopic behavior. High fidelity models also require more coding and debugging time. Another drawback of simulation is the inability to draw general conclusions about the system's performance from a single simulation since multiple simulations are required to understand sensitivity to parameters. Despite the limitations, simulation provides valuable information in cases where measurement is restricted by physical constraints or analytical modeling is limited by mathematical intractability.

Analytic Models. Analytic models are widely used in performance evaluation due to their power and flexibility [81]. Analytic modeling involves constructing a mathematical model at the desired level of detail of the system and solving it [81]. The main advantage of analytic models is that they allow for exploration of system performance when it is impractical to build a system prior to construction. The main difficulty with analytic models is obtaining a model with sufficient detail that is tractable. However analytical models have some major advantages over the previous two techniques: (a) valuable insight into the workings of the system even if the model is too difficult to solve; (b) remarkably accurate results even for simple analytic models, (c) better predictive value from results than those obtained from measurement and simulation and (d) insight into perfor-

mance variations with individual parameters. Hence, analytic models can often be used to optimize a system with respect to a set of parameters such as the number of processors or work load distribution.

Analytic models also have their disadvantages. Models must be evaluated for correctness against the real system and any simplifying assumptions made during analysis to maintain tractability must be carefully validated. Even when an accurate model cannot be developed due to tractability or other limitations, analytic models are often useful for determining performance trends or for comparing the performance of different algorithms.

One of the classic analytical modeling techniques is queueing models [29, 85]. Queueing models are attractive because they often provide the simplest mathematical representations that either have closed form solutions or very good approximation techniques such as Mean Value Analysis (MVA) [81]. However, for many systems (such as those with internal concurrency), the model is too complex and closed form solutions are not obtainable requiring the use of simulation. In these cases, queueing models fit better in the category of simulation models rather than analytical models. In either event, the initial analysis begins from an analytical approach therefore we include them here with analytical models.

Queueing network models can be viewed as a small subset of the techniques of queueing theory and they can be solved analytically, numerically, or by simulation. Queueing systems are used to model processes in which customers arrive, wait for service, are serviced, and then depart. Characterization of systems thus requires specification of [74]: inter-arrival time probability density function (A), service time probability density function (S), number of servers (M), system capacity (buffers, queues) (B), population size (K), and queueing discipline (SD).

A common notation used in the queueing literature to specify these six parameters is -A/S/m/B/K/SD. In general, if there are no buffer space or population size limitations and the queueing discipline is FCFS (First Come First Serve), the notation is shortened to A/S/m. The most widely used distributions for A and S are: (1) M – Markov, exponential distribution, (2) D – Deterministic, all customers have the same value, and (3) G – General, arbitrary distribution [74].

Several researchers have explored the use of queuing networks [29], petri net models [108], and markov models [29] in the performance evaluation and analysis of HPC systems. Mohapatra et.al. [91, 92] use queuing models to study the performance of cluster-based multiprocessors with multistage interconnection networks. The performance model developed is for a shared-memory cluster of multiprocessors. A queueing network model is developed for the complete system using hierarchical decomposition resulting in a two-level model. Significant changes to the model would be required to represent our distributed memory system.

We will use analytic modeling in our model development and employ queueing theory in the analysis and development of the background load portion of the model.

### 2.3.3 Performance Modeling

The performance of algorithms are often described by their asymptotic behavior as the problem size varies. With this approach, one must be careful to provide an accurate representation of the runtime performance. Often, scale factors and lower-order polynomial terms can have a dramatic performance impact, but are not reflected in asymptotic models [102]. We will focus our attention on *fork-join* types of algorithms and more specifically *synchronous iterative* (or *multiphase*) algorithms. In the remainder of this section we review some performance results for this class of problems which include optimization techniques, simulation, and many numerical methods.

The performance of synchronous iterative algorithms is dramatically impacted by the random effects in the per iteration runtime of each processor. Differences in processor runtime caused by load imbalances affect the completion time of the algorithm and degrade the overall performance. Modeling these affects analytically is difficult due to the mathematical complexity [102]. Dubois and Briggs describe the performance of these algorithms on shared-memory multiprocessors [54]. To model load imbalance, they represent the amount of work that each processor completes by a sampled random variable and apply *order statistics* [44] to describe the expected runtime of the last processor to complete and thus the overall runtime of the algorithm. Govindan and Franklin address the dynamic load imbalance across iterations of a synchronous iterative algorithm [60, 65]. Their work differs from other models in that they do not assume that the task distribution at any iteration is independent of the distribution at previous iterations.

For synchronous discrete-event simulation, Chamberlain and Franklin develop a performance model that predicts the execution time assuming a known load imbalance scale factor [37]. Peterson and Chamberlain validate this model for simulation of queueing networks and investigate the impact of load imbalance [103, 104, 105, 102]. Agrawal and Chakradhar use Bernoulli trials to determine the number of events at each processor allowing for an analytic solution of the application load imbalance of the performance model [21]. Accurate performance models exist for these algorithms running on *dedicated processors* where the load imbalance results entirely from the uneven distribution of the application workload. Modeling load imbalance on *shared machines* requires the use of order statistics and other techniques to model the randomness of the load imbalance due to other users.

For shared resources, the randomness of the load imbalance complicates performance evaluation. Two factors contribute to the load imbalance: *application load imbalance* and *back*-

ground load imbalance. Application load imbalance is the result of an unequal distribution of the workload among processors while background load imbalance is the result of computing resources being shared with other tasks. Much of the work regarding load imbalance modeling for dedicated resources can be applied to the application load imbalance modeling for shared resources.

Several groups have studied the performance of distributed and parallel systems of various architectures and focused on the performance impact of background load imbalance. Atallah et.al. developed a performance model for compute-intensive tasks running simultaneously on a shared network of workstations [23]. They include the performance impact of other users of the shared resources by the "duty cycle"  $\eta_i$ . The duty cycle is defined as the ratio of clock cycles that a workstation i commits to local or other user tasks to the number of clock cycles available to the distributed application. They do not consider application load imbalance or discuss how to find the duty cycle values for each workstation. They also use this model to develop algorithms to optimize the scheduling problem for shared resources. Efe and Schaar extended this work to find the optimal mean response time for executing multiple batch jobs on the networked workstations [55]. In [56], Efe optimizes the scheduling algorithms to reduce their runtime for SPMD (Single Program Multiple Data) applications.

Peterson and Chamberlain [102, 103, 104, 105, 106] study application performance in a shared, heterogeneous environment. Their analytic performance model focuses on synchronous iterative algorithms and includes the effects of application and background load imbalance. Issues unaccounted for include network communication and contention models. Their work however provides a thorough investigation of performance evaluation and specifically the background and application load models used in this dissertation.

Clement and Quinn [41] developed an analytical performance model for multicomputers however the assumptions and restrictions limit this model to specific architectures and applications. Another paper by Clement [42] focuses on the network performance of PVM (Parallel Virtual Machine, a discussion of PVM is included later in this chapter) clusters. A communication model for ATM and Ethernet networks is developed including a factor to account for contention in the network. Other work related to the performance of PVM clusters include that by Dongarra and Casanova [34, 51, 53]. Nupairoj and Ni have studied the performance of MPI on some workstation clusters [99]. Zhang and Yan [130, 132] have developed a performance model for non-dedicated heterogeneous Networks of Workstations (NOWs) where heterogeneity is quantified by a "computing power weight", owner workload requests are included as binomial distributions, and the network is limited to Ethernet.

We shall combine the results of the research on background load imbalance modeling on shared resources, application load imbalance modeling on dedicated resources, and communication modeling for shared resources to model distributed applications running on shared resources. Our contribution will be to modify these models for use in HPRC and more specifically, account for the new contributions of the RC elements.

# 2.4 Performance Metrics

HPC performance is commonly measured in terms of speedup and efficiency. *Amdahl's Law* [22] for "fixed-size" speedup and *Gustafson's Law* [67] for "fixed time" speedup are common representations for the limitations to parallel efficiency.

Metrics for reconfigurable computing are limited in the literature. In Dehon's thesis on reconfigurable architectures, he presents a high-level characterization of reconfigurable systems using size metrics [47, 48] to project the performance of a reconfigurable system.

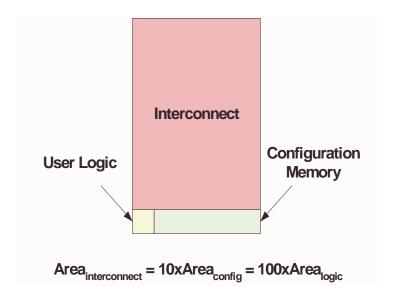

Dehon's characterization model uses size estimates to compare the efficiency of different architectures [47]. From an empirical survey, he concludes that reconfigurable devices have lower performance than dedicated hardware but higher than general purpose processors. He also concludes that the performance density variation from dedicated hardware to reconfigurable devices to processors, results from the increasing amount of instruction memory and distribution resources (area overhead) per active computing element. Dedicated hardware typically has very little overhead while reconfigurable devices and general purpose processors have significantly more overhead. Dehon points out that eighty to ninety percent of the area of conventional reconfigurable devices is dedicated to interconnect and associated overhead such as configuration memory. The actual area used for logic function only accounts for a few percent (Figure 2.4).

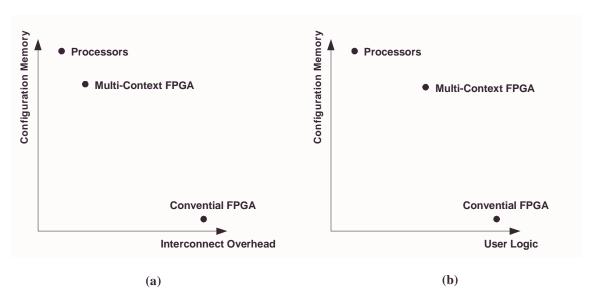

The conventional FPGA represents an interconnection overhead extreme. Another extreme occurs where the configuration memory dominates the physical area as with general purpose processors. Figure 2.5 shows the area trade-offs for Dehon's Reconfigurable Processing or RP-space. For conventional FPGAs, multi-context FPGAs and general purpose processors, Figure 2.5 graphically shows where processors and FPGAs are in the characterization space for (a) interconnect overhead versus configuration memory and (b) user logic versus configuration memory.

Dehon's RP-space provides a method for characterizing reconfigurable devices or FPGAs and even includes some abstraction of processors onto the RP-space. RC architectures however

FIGURE 2.4 Area Density for Conventional Reconfigurable Devices [47]

$FIGURE\ 2.5\ RP\text{-}Space\ (a)\ Interconnect\ vs.\ Configuration\ and\ (b)\ Logic\ vs.$  Configuration

consist of FPGA(s) and a processor working together making their projection into the RP-space somewhat difficult because we must consider how the RC system is constructed. We have to account for the FPGA(s) (or reconfigurable unit(s)), the workstation (or microprocessor), the communication interface between them, and any external memories connected to the reconfigurable unit(s). With the plethora of RC architectures available, each architecture would effectively map differently into the RP-space. To effectively compare trade-offs in the RC and ultimately the HPRC environment, other metrics often used in RC systems, such as cost and power, may be more practical and useful.

Developing a cost metric should be straightforward based on the processors, FPGAs, memory, and interconnect under consideration. A cost function can be developed relating execution time or speedup as determined from the model proposed in this dissertation to the cost of the system. Similarly a power metric cost function can be developed relating execution time determined from the proposed model to the total power used by the system. The metrics of interest will depend on the issue to be optimized (runtime, system utilization, system cost, etc.). We will touch on this analysis more in Chap. 6.

# 2.5 Resource Allocation, Scheduling, and Load Balancing

To effectively exploit computational resources, access to these resources must be somehow managed. Operating systems are normally tasked with the management and allocation of resources among competing service requests. The allocation policy must also preserve fairness among users allowing resource access to all, prevent deadlock to ensure work can be performed and maintain security [120]. Handling these service requests for distributed applications on networks of workstations can be significantly more complicated than managing a single workstation. For parallel or distributed applications, it is necessary to partition the work into subproblems and map them onto a set of processors. Data parallelism is often exploited to create subproblems that perform computations with minimum interaction between subproblems. These

subproblems are then mapped onto a set of processors where the goal is to minimize the amount of

communication between processes and maximize processor utilization [110]. Mapping subproblems onto a distributed system can be viewed as a restricted case of the general scheduling problem. The parallel scheduling problem is NP-Hard [61], so finding optimal scheduling solutions for

general problems is not feasible. Research has as a result focused on techniques for restricted cases

or near-optimal solutions. These techniques are referred to as *static* if the scheduling decisions are

predetermined, or *dynamic* if the scheduling decisions are made at execution time [36].

Although parallel scheduling is known to be difficult, load balancing techniques have been used to improved the performance of parallel applications [33]. Many researchers have investigated both static and dynamic load balancing approaches. Wang and Morris propose a simple load distribution classification method based on whether the load distribution is source or receiver initiated and the level of information dependency [127]. Information dependency refers to the level at which a resource has information about the current state or workload of other resources. Since most current distribution techniques are sender initiated, the coarseness of this classification method provides little distinction between members of this class and it is not extensive enough. Casavant and Kuhl provide a pivotal taxonomy that includes both local and global scheduling of load balancing algorithms [36]. Their classification, designed for distributed computing systems, is based on strategic design choices such as static or non-static and distributed versus non-distributed. The complete taxonomy consists of a hierarchical and flat classification. The hierarchical classification is used to show where some characteristics are exclusive and the flat classification gives definitions of attributes that are not exclusive. Again this classification method does not pro-