University of Tennessee, Knoxville Trace: Tennessee Research and Creative Exchange

**Doctoral Dissertations**

Graduate School

5-2005

## Active Harmonic Elimination in Multilevel Converters

Zhong Du University of Tennessee - Knoxville

#### **Recommended** Citation

Du, Zhong, "Active Harmonic Elimination in Multilevel Converters." PhD diss., University of Tennessee, 2005. https://trace.tennessee.edu/utk\_graddiss/1944

This Dissertation is brought to you for free and open access by the Graduate School at Trace: Tennessee Research and Creative Exchange. It has been accepted for inclusion in Doctoral Dissertations by an authorized administrator of Trace: Tennessee Research and Creative Exchange. For more information, please contact trace@utk.edu.

To the Graduate Council:

I am submitting herewith a dissertation written by Zhong Du entitled "Active Harmonic Elimination in Multilevel Converters." I have examined the final electronic copy of this dissertation for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Doctor of Philosophy, with a major in Electrical Engineering.

Leon M. Tolbert, Major Professor

We have read this dissertation and recommend its acceptance:

John N. Chiasson, Jack S. Lawler, Suzanne Lenhart

Accepted for the Council: <u>Dixie L. Thompson</u>

Vice Provost and Dean of the Graduate School

(Original signatures are on file with official student records.)

To the Graduate Council:

I am submitting herewith a dissertation written by Zhong Du entitled "Active Harmonic Elimination in Multilevel Converters." I have examined the final electronic copy of this dissertation for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Doctor of Philosophy, with a major in Electrical Engineering.

Leon M. Tolbert

Major Professor

We have read this dissertation and recommend its acceptance:

John N. Chiasson

Jack S. Lawler

Suzanne Lenhart

Accepted for the Council:

Anne Mayhew

Vice Chancellor and Dean of Graduate Studies

(Original signatures are on file with official student records.)

# **Active Harmonic Elimination in**

# **Multilevel Converters**

A Dissertation Presented for the Doctoral of Philosophy Degree The University of Tennessee, Knoxville

Zhong Du

May 2005

### Acknowledgements

First and foremost, I would like to express my deepest appreciation to my major advisor, Dr. Leon M. Tolbert, for his support, all of his help and instructions during my study and research. Also, I would like to thank Dr. John N. Chiasson, for his help and instructions.

Many thanks to Dr. Jack S. Lawler and Dr. Suzanne Lenhart for their serving on my thesis committee, reading this thesis and providing invaluable suggestions and constructive comments. In addition, I would like to thank the other faculty, staff and students in the Power Electronics laboratory: Keith McKenzie, Kaiyu Wang, Johnson Weston, Jianqing Chen .....who create a friendly working environment, encouraging open dialogue, and the sharing of ideas.

Finally, I would like to express my great gratitude to my wife, my parents and parents-in-law for their continuous encouragement and support. There are no words that can show my appreciation to them for all the sacrifices they made to help me taking care of my lovely daughter.

### Abstract

The modulation technique for multilevel converters is a key issue for multilevel converter control. The traditional pulse width modulation (PWM), space vector PWM, and space vector control methods do not completely eliminate specified harmonics. In addition, space vector PWM and space vector control method cannot be applied to multilevel converters with unequal DC voltages. The carrier phase shifting method for traditional PWM method also requires equal DC voltages. The number of harmonics that can be eliminated by the selective harmonic elimination method is restricted by the number of unknowns in the harmonic equations and available solutions.

For these reasons, this thesis develops a new modulation control method which is referred to as the active harmonic elimination method to conquer some disadvantages for the existing methods. The active harmonic elimination method contributes to the existing methods because it not only generates the desired fundamental frequency voltage, but also completely eliminates any number of harmonics without the restriction of the number of unknowns in the harmonic equations and available solutions for the harmonic equations. Also the active harmonic elimination method can be applied to both equal DC voltage cases and unequal DC voltage cases. Another contribution of the active harmonic elimination method is that it simplifies the optimal system performance searching by making a tradeoff between switching frequency and harmonic distortion.

Experiments on an 11-level multilevel converter validate the active harmonic elimination method for multilevel converters.

## **Table of Contents**

Chapter

| 1. | Introduction                                                              | 1  |

|----|---------------------------------------------------------------------------|----|

|    | 1.1. Background                                                           | 1  |

|    | 1.2. Problem Statement                                                    | 4  |

| 2. | Literature Survey                                                         | 9  |

|    | 2.1. Introduction                                                         | 9  |

|    | 2.2. Topology of Multilevel Converters                                    | 9  |

|    | 2.2.1. Diode-Clamped Converter                                            | 9  |

|    | 2.2.2. Capacitor-Clamped Converter                                        |    |

|    | 2.2.3. Cascaded H-bridge Converter                                        |    |

|    | 2.2.4. Cascaded DC Sources Multilevel Converter and Cascaded Transformers |    |

|    | Multilevel Converter                                                      |    |

|    | 2.2.5. Generalized Multilevel Topology                                    |    |

|    | 2.2.6. Mixed-Level Hybrid Multilevel Converter                            |    |

|    | 2.2.7. Unequal DC Sources Multilevel Converter                            |    |

|    | 2.2.8. Soft-Switched Multilevel Converter                                 |    |

|    | 2.3. Control and Modulation Techniques of Multilevel Converters           | 26 |

|    | 2.3.1. Classification of Modulation Strategies                            |    |

|    | 2.3.2. Multilevel SPWM                                                    |    |

|    | 2.3.3. Space Vector PWM Modulation                                        |    |

|    | 2.3.4. Space Vector Control                                               |    |

|    | 2.3.5. Selective Harmonic Elimination                                     |    |

|    | 2.4. Balance Control Problems in Multilevel Converters                    | 36 |

|    | 2.5. The Next Steps                                                       | 37 |

| 3. | Fundamental Frequency Switching Control                                   | 39 |

|    | 3.1. Fourier Series and Harmonics Elimination Theory                      | 39 |

|    |                                                                           |    |

|    | <b>3.2. Resultant Method for Transcendental Equations Solving</b>         |    |

|    | 3.2.1. Resultant Theory                                                   |    |

|    | 3.2.2. Solutions to the Harmonic Equations by Resultant Theory            | 43 |

Page

| 3.2.3. Solution Results                                                  |         |

|--------------------------------------------------------------------------|---------|

| <b>3.3. Transcendental Equations Solving for Higher Order Harmon</b>     |         |

| 3.4. Compensation with the Triplen Harmonics                             |         |

| 3.5. Simulation                                                          |         |

| 3.6. Experiment                                                          |         |

| 3.7. Summary                                                             |         |

| 4. Active Harmonic Elimination for Low Modulation Index Cont             | trol 79 |

| 4.1. Active Harmonic Elimination Method                                  |         |

| 4.1.1. Resultant Method for Multilevel Converter                         |         |

| 4.1.2. Active Harmonic Elimination Method                                | 80      |

| 4.2. Simulation Study                                                    | 84      |

| 4.2.1. Output Waveform Simulation and FFT Analysis                       |         |

| 4.2.2. Switching Control Strategy                                        |         |

| 4.3. Switching Number for the Control Strategy                           |         |

| 4.4. Experiment                                                          |         |

| 4.5. Summary                                                             |         |

| 5. Active Harmonic Elimination for Multilevel Converters with U Voltages |         |

| 5.1. Resultant Method for Unipolar Switching Scheme Converter            | 's 98   |

| 5.2. Optimal Combination Method for THD Control                          |         |

| 5.3. Active Harmonic Elimination Method                                  |         |

| 5.4. Simulation Study                                                    | 107     |

| 5.5. Switching Control Strategy                                          |         |

| 5.6. Experiment                                                          |         |

| 5.7. Summary                                                             |         |

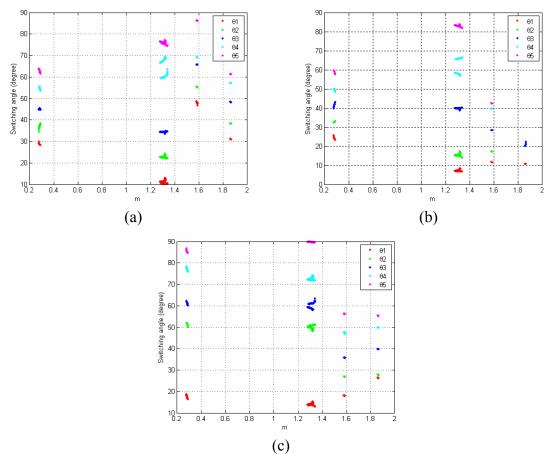

| 6. | Optimization of Active Harmonic Elimination                                                                                | 123 |

|----|----------------------------------------------------------------------------------------------------------------------------|-----|

|    | 6.1. Optimization of Active Harmonic Elimination Method with Fundamenta<br>Frequency Switching Scheme                      |     |

|    | 6.2. High Order Harmonic Elimination Optimization of Active Harmonic<br>Elimination Method with Unipolar Switching Scheme  | 128 |

|    | 6.3. Optimization of Active Harmonic Elimination Method with Unipolar<br>Switching Scheme Using the Newton Climbing Method | 129 |

|    | 6.4. Simulation                                                                                                            | 137 |

|    | 6.5. Experiment                                                                                                            | 137 |

|    | 6.5.1. Experiment for Optimized Active Harmonic Elimination Method with<br>Fundamental Frequency Switching Scheme          |     |

|    | 6.5.2. Experiment for Optimized Active Harmonic Elimination Method with Unipolar Switching Scheme                          | 142 |

|    | 6.6. Summary                                                                                                               | 142 |

| 7. | Hardware Implementation                                                                                                    | 152 |

|    | 7.1. FPGA Controller Implementation                                                                                        | 152 |

|    | 7.2. Motor Load Experiments                                                                                                | 155 |

|    | 7.3. Summary                                                                                                               | 158 |

| 8. | Conclusions and Recommendations                                                                                            | 159 |

|    | 8.1. Conclusions                                                                                                           | 159 |

|    | 8.2. Contributions                                                                                                         | 161 |

|    | 8.3. Recommendations for Future Work                                                                                       | 162 |

| R  | eferences                                                                                                                  | 164 |

| V  | ita                                                                                                                        | 169 |

## List of Tables

| Table 2.1: Switch states and the output voltages for diode-clamped multilevel co                                    | onverter   |

|---------------------------------------------------------------------------------------------------------------------|------------|

|                                                                                                                     | 12         |

| Table 2.2: Switch states and the output voltages for capacitor-clamped r           converter.                       | nultilevel |

| <b>Table 3.1:</b> Comparison of the modulation index range with and without triplen compensation.                   |            |

| <b>Table 5.1:</b> $THD = \frac{\sqrt{V_5^2 + V_7^2 + \dots + V_{49}^2}}{V_1} \times 100\%$ ( <i>m</i> = 2.86) under | different  |

| conditions                                                                                                          | 119        |

## List of Figures

| Figure 1.1: Sine-triangle PWM control (a) sinusoidal reference signal and triangle ca    | rrier |

|------------------------------------------------------------------------------------------|-------|

| signal; (b) switching signal                                                             | 2     |

| Figure 2.1: Neutral point diode-clamped converter                                        | 11    |

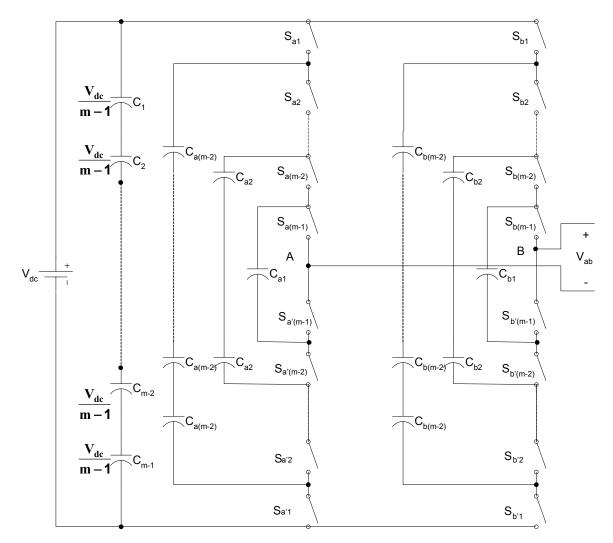

| Figure 2.2: Two-phase diode-clamped multilevel converter                                 | 11    |

| Figure 2.3: Topology of a capacitor-clamped multilevel converter                         |       |

| Figure 2.4: Two-phase capacitor-clamped multilevel converter                             |       |

| Figure 2.5: Single H-bridge topology                                                     | 16    |

| Figure 2.6: H-bridge cascaded multilevel converter with s separate DC sources            | 17    |

| Figure 2.7: Staircase sinusoidal waveform generated by H-bridge cascaded multileve       |       |

| converter                                                                                |       |

| Figure 2.8: Cascaded multilevel converter with transformers using standard three-pha     | ase   |

| bi-level converters                                                                      |       |

| Figure 2.9: Topology of cascaded DC sources multilevel converters                        | 20    |

| Figure 2.10: Topology of cascaded transformers multilevel converters                     | 21    |

| Figure 2.11: Generalized P2 multilevel converter topology                                |       |

| Figure 2.12: Mixed-level hybrid unit configuration using the three-level diode-clamp     | ed    |

| converter as the cascaded converter cell to increase the voltage levels                  | 24    |

| Figure 2.13: Unequal DC sources multilevel converter                                     | 25    |

| Figure 2.14: Classification of multilevel modulation methods                             | 27    |

| Figure 2.15: Multi-carrier control (a) control signal and carrier signals; (b) output    |       |

| voltage                                                                                  | 28    |

| Figure 2.16: Output voltage with carrier phase shift (a) phase shift 0°; (b) phase shift |       |

| 90°; (c) phase shift 120°                                                                | 29    |

| Figure 2.17: Space vector diagram (a) three-level; (b) five-level; (c) seven-level       | 31    |

| Figure 2.18: 21-level space vectors                                                      |       |

| Figure 2.19: Output waveform of virtual stage PWM control                                | 34    |

| Figure 2.20: Unipolar switching output waveform                                          |       |

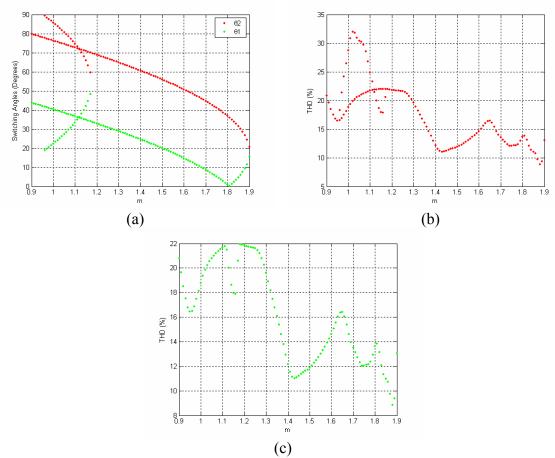

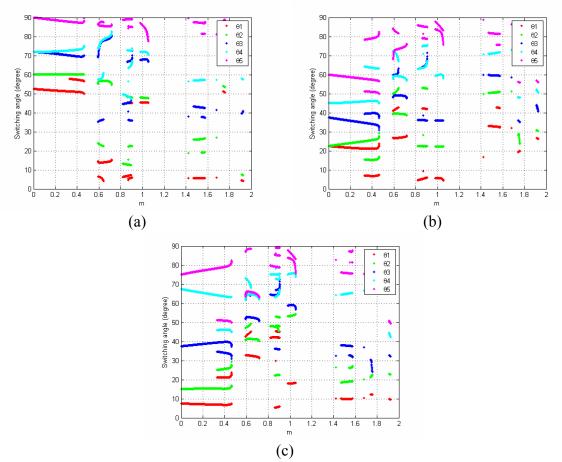

| Figure 3.1: Solutions for 5-level multilevel converter (a) switching angles; (b) THD t   | for   |

| all solutions; (c) lowest THD                                                            |       |

| Figure 3.2: Solutions for 7-level multilevel converter (a) switching angles; (b) THD t   | for   |

| all solutions; (c) lowest THD.                                                           | 48    |

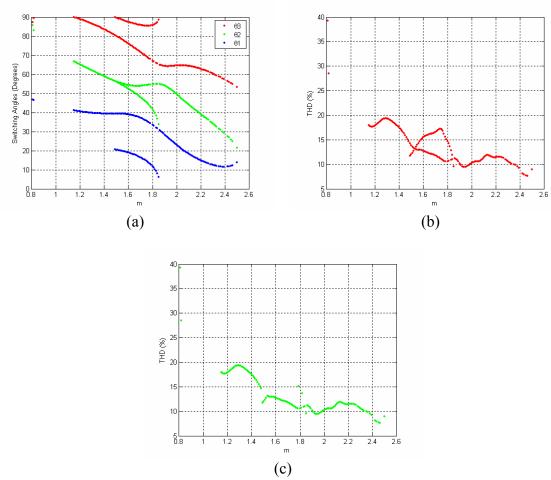

| Figure 3.3: Solutions for 9-level multilevel converter (a) switching angles; (b) THD t   | for   |

| all solutions; (c) lowest THD                                                            | 50    |

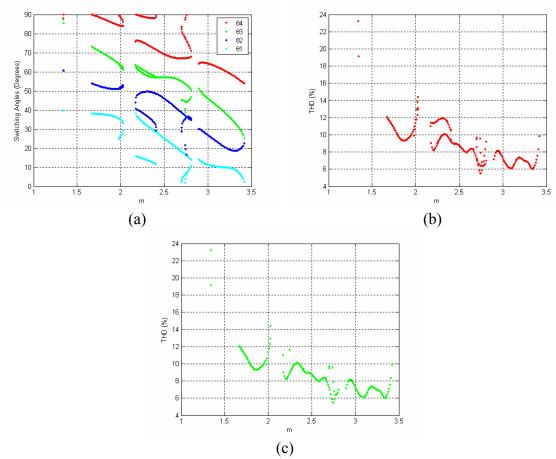

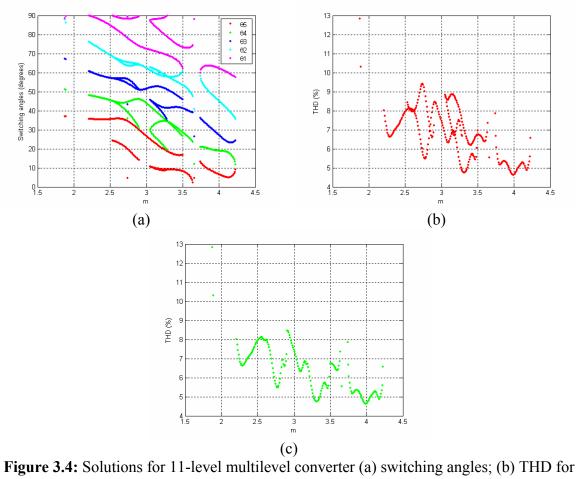

| Figure 3.4: Solutions for 11-level multilevel converter (a) switching angles; (b) THD    |       |

| all solutions; (c) lowest THD                                                            | 52    |

| Figure 3.5: Solutions for 13-level multilevel converter (a) switching angles; (b) THD    | for   |

| all solutions; (c) lowest THD.                                                           |       |

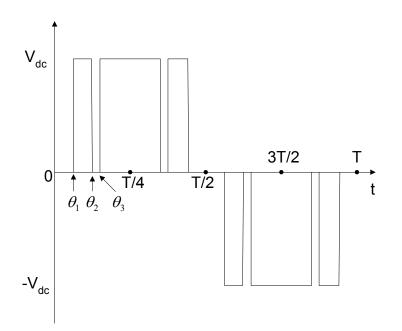

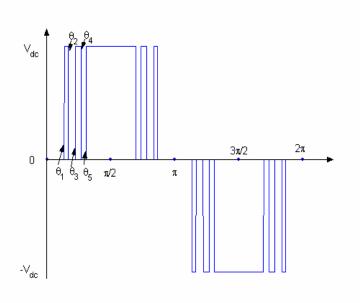

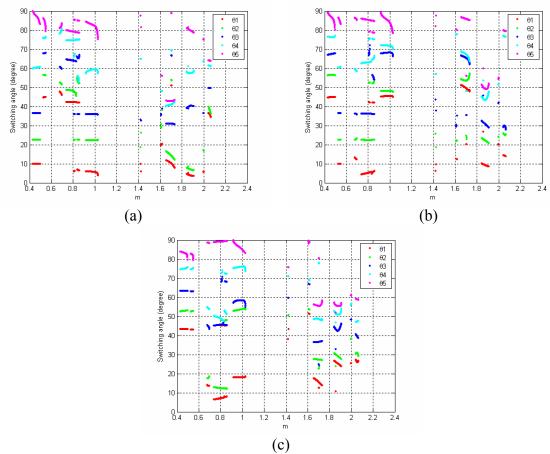

| Figure 3.6: 5-angle unipolar converter output voltage                                    |       |

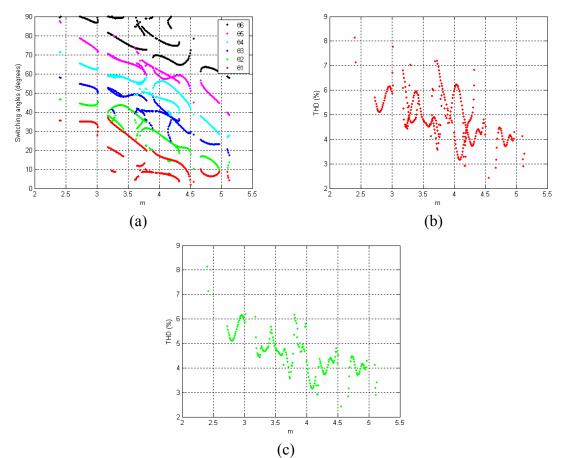

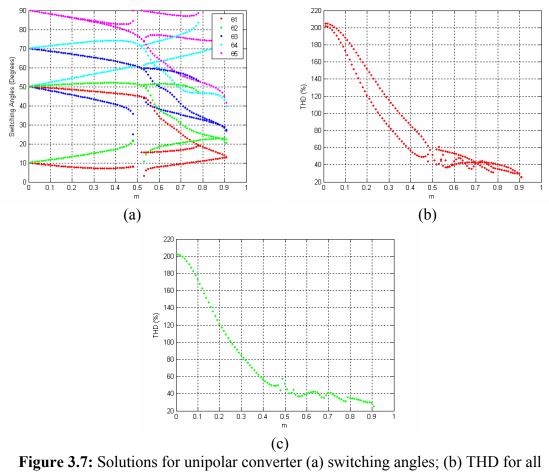

| Figure 3.7: Solutions for unipolar converter (a) switching angles; (b) THD for all       |       |

| solutions; (c) lowest THD                                                                | 57    |

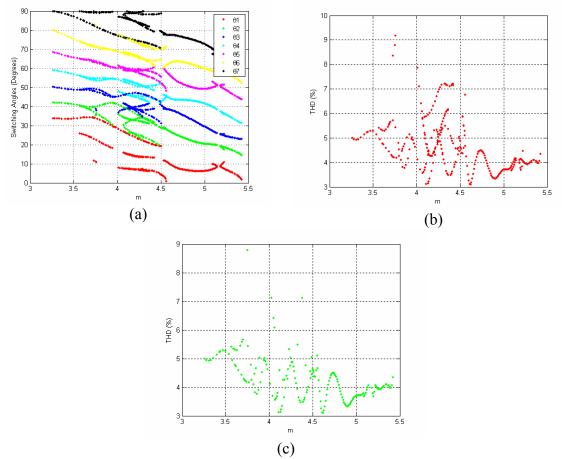

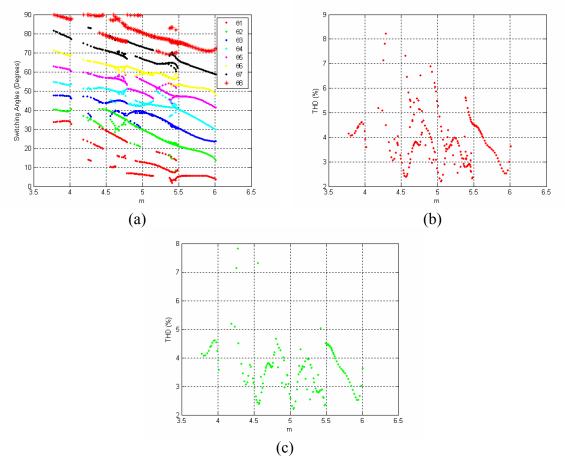

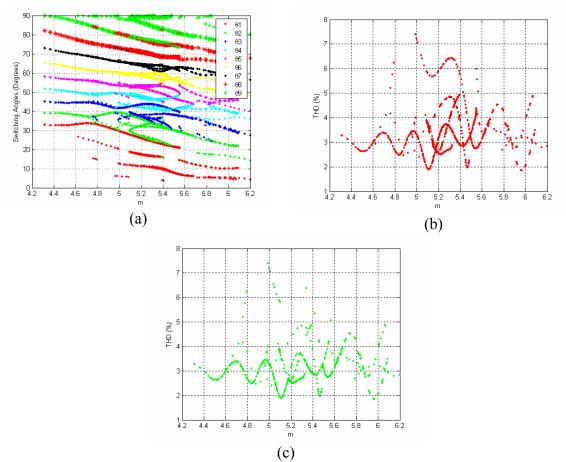

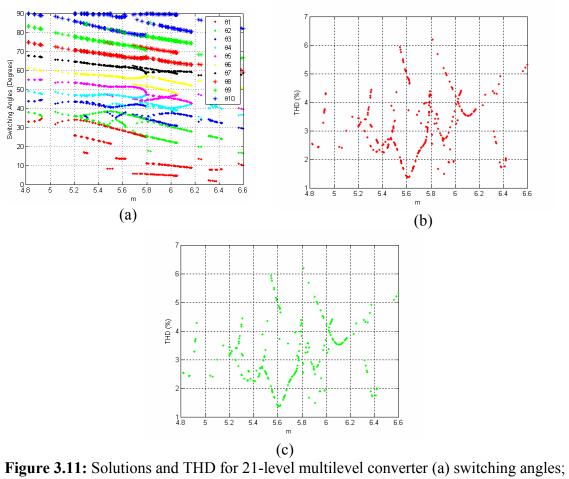

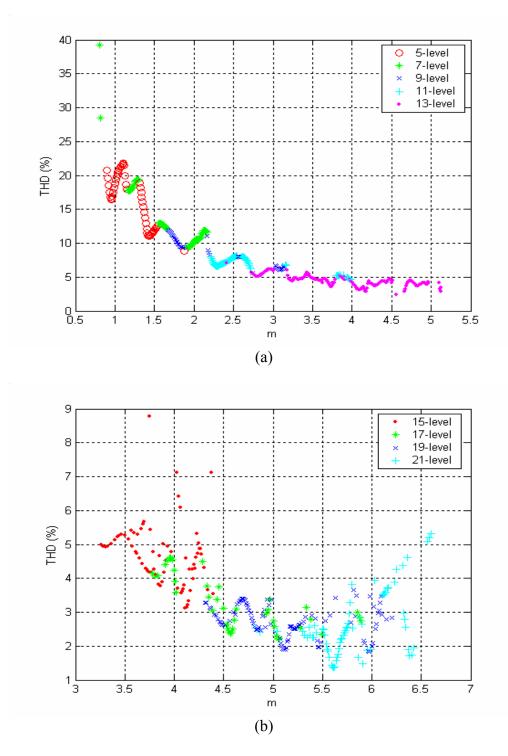

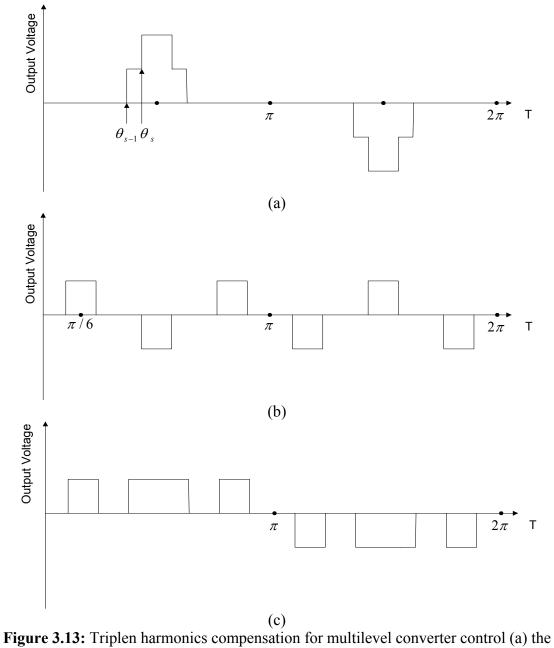

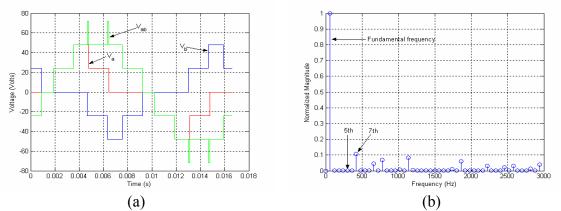

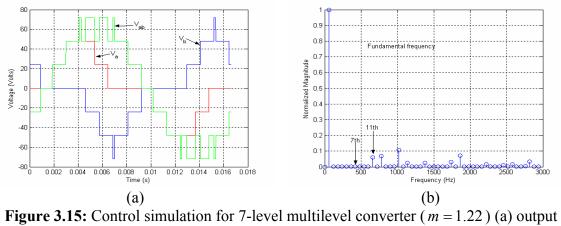

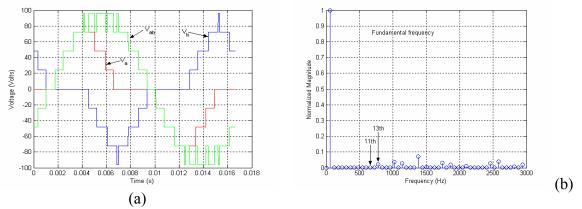

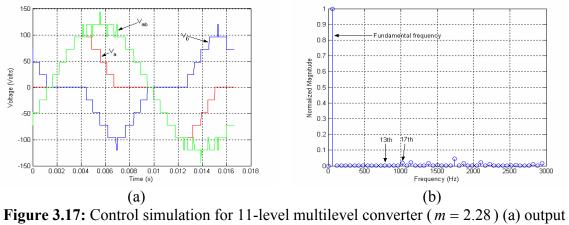

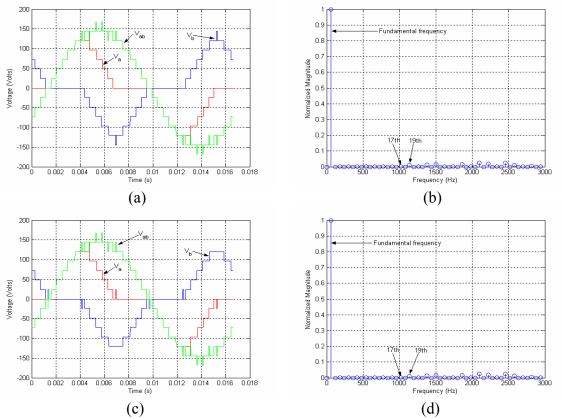

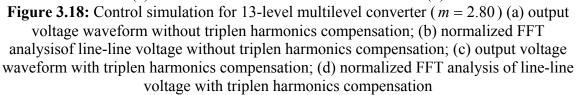

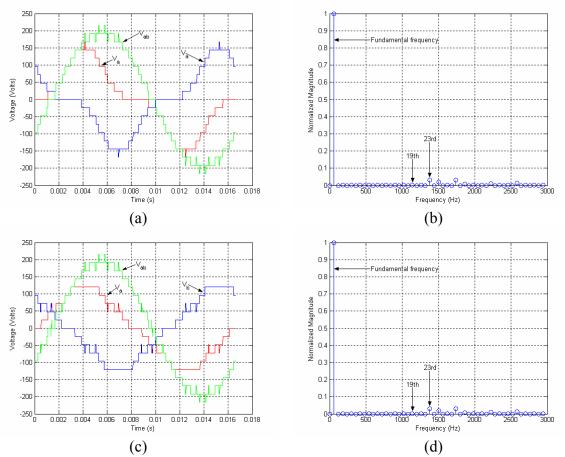

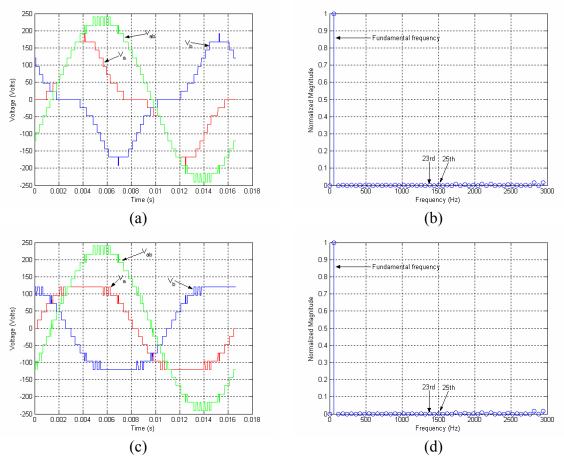

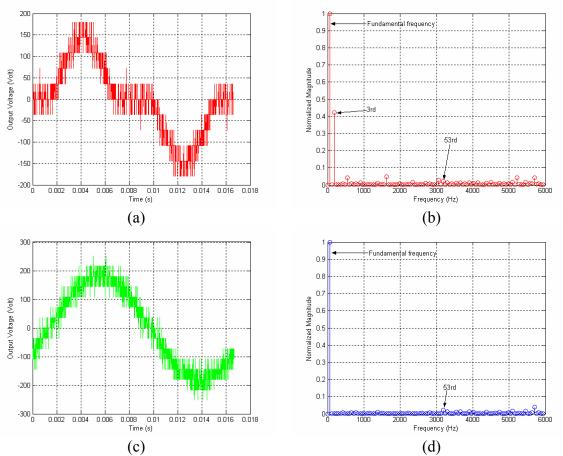

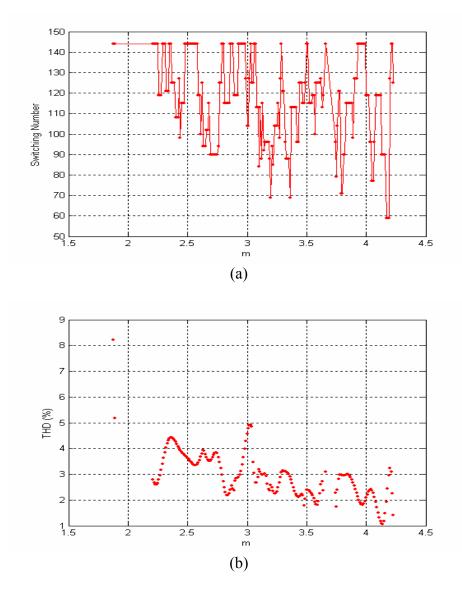

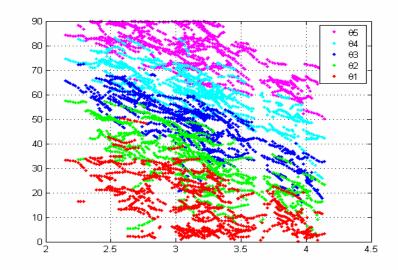

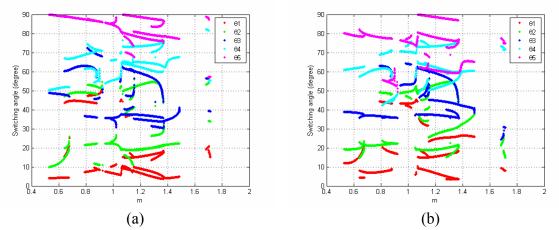

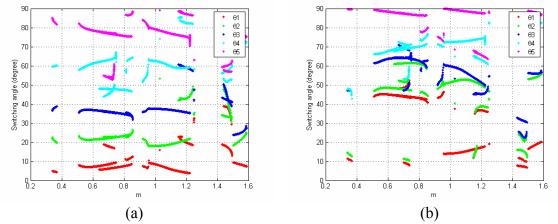

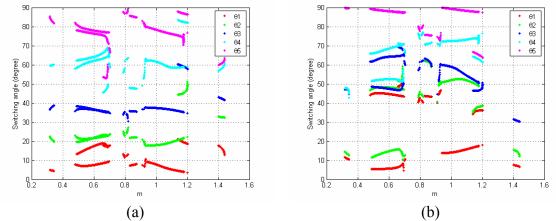

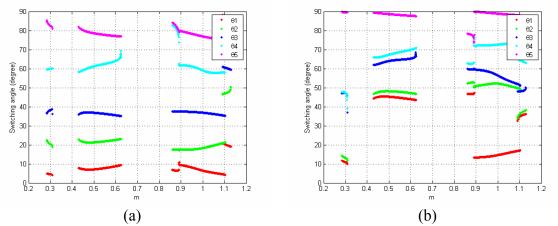

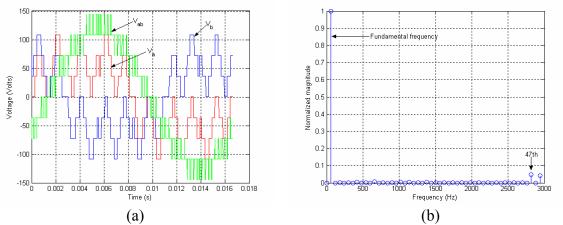

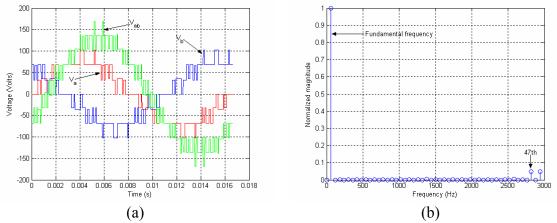

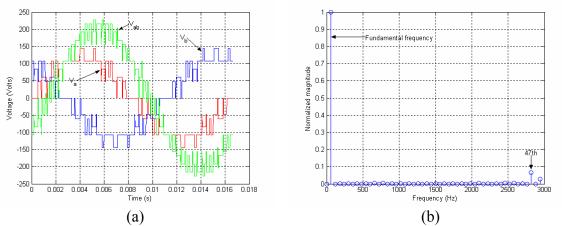

Figure 3.8: Solutions and THD for 15-level multilevel converter (a) switching angles; (b) Figure 3.9: Solutions and THD for 17-level multilevel converter (a) switching angles; (b) Figure 3.10: Solutions and THD for 19-level multilevel converter (a) switching angles: Figure 3.11: Solutions and THD for 21-level multilevel converter (a) switching angles: Figure 3.12: THD for fundamental frequency switching control (a) lowest THD for 5-13 level multilevel converters; (b) lowest THD for 15-21 level multilevel converters. 64 Figure 3.13: Triplen harmonics compensation for multilevel converter control (a) the output voltage waveform without triplen harmonic compensation; (b) the triplen harmonic for compensation; (c) the output voltage waveform with triplen harmonic Figure 3.14: Control simulation for 5-level multilevel converter (m = 0.99) (a) output Figure 3.15: Control simulation for 7-level multilevel converter (m = 1.22) (a) output **Figure 3.16:** Control simulation for 9-level multilevel converter (m = 1.74) (a) output Figure 3.17: Control simulation for 11-level multilevel converter (m = 2.28) (a) output Figure 3.18: Control simulation for 13-level multilevel converter (m = 2.80) (a) output voltage waveform without triplen harmonics compensation; (b) normalized FFT analysis of line-line voltage without triplen harmonics compensation; (c) output voltage waveform with triplen harmonics compensation; (d) normalized FFT **Figure 3.19:** Control simulation for 15-level multilevel converter (m = 3.50) (a) output voltage waveform without triplen harmonics compensation; (b) normalized FFT analysis of line-line voltage without triplen harmonics compensation; (c) output voltage waveform with triplen harmonics compensation; (d) normalized FFT Figure 3.20: Control simulation for 17-level multilevel converter (m = 3.95) (a) output voltage waveform without triplen harmonics compensation; (b) normalized FFT analysis of line-line voltage without triplen harmonics compensation; (c) output voltage waveform with triplen harmonics compensation; (d) normalized FFT Figure 3.21: Control simulation for 19-level multilevel converter (m = 4.67) (a) output voltage waveform without triplen harmonics compensation; (b) normalized FFT analysis of line-line voltage without triplen harmonics compensation; (c) output voltage waveform with triplen harmonics compensation; (d) normalized FFT Figure 3.22: Control simulation for 21-level multilevel converter (m = 4.92) (a) output

voltage waveform without triplen harmonics compensation; (b) normalized FFT analysis of line-line voltage without triplen harmonics compensation; (c) output

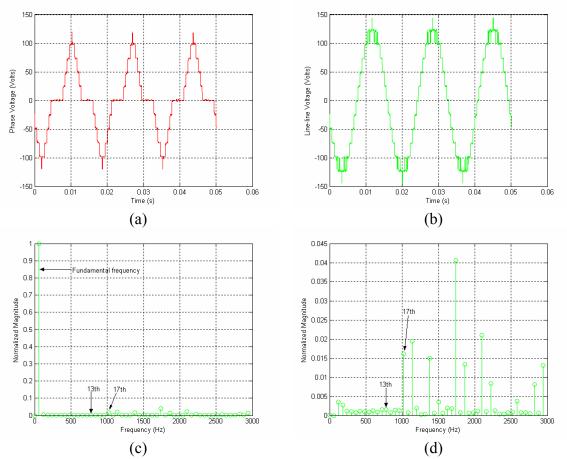

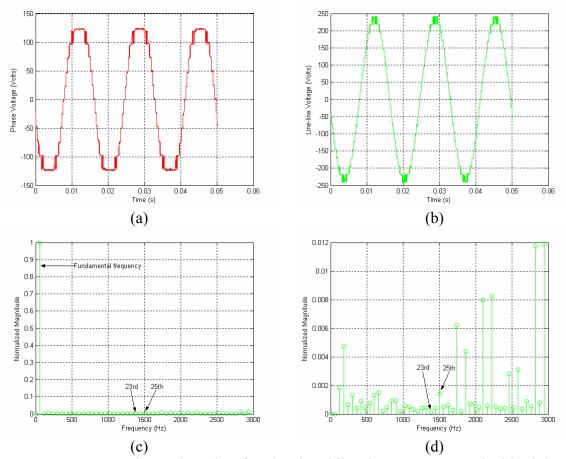

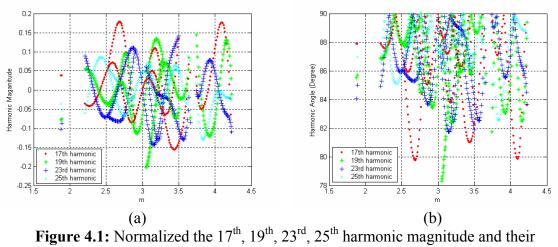

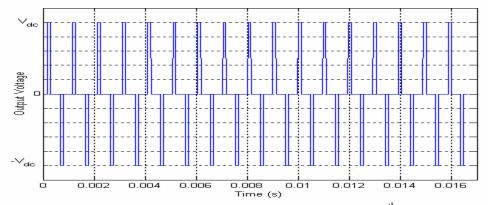

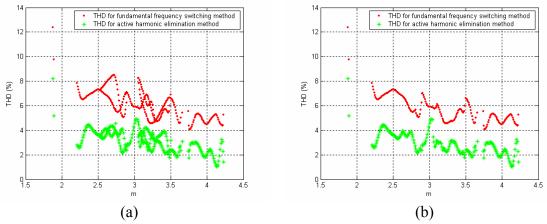

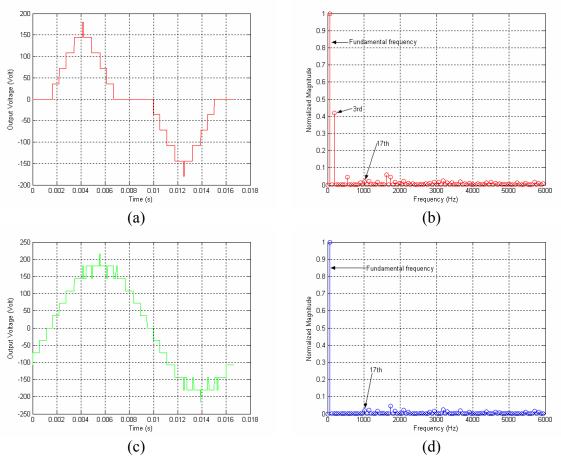

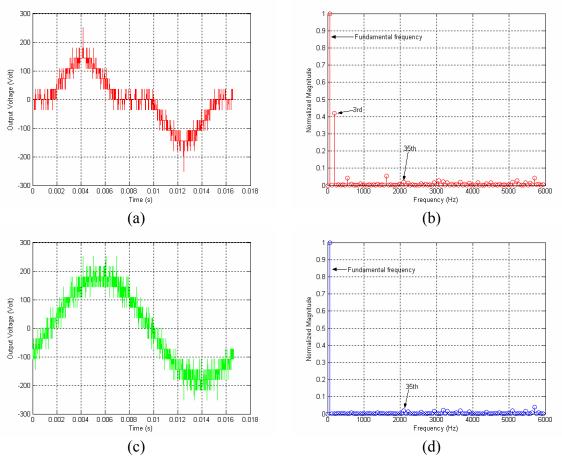

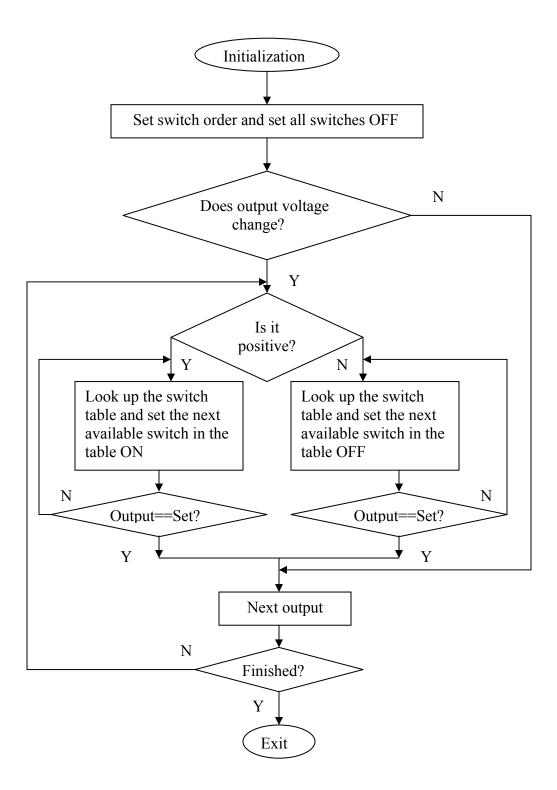

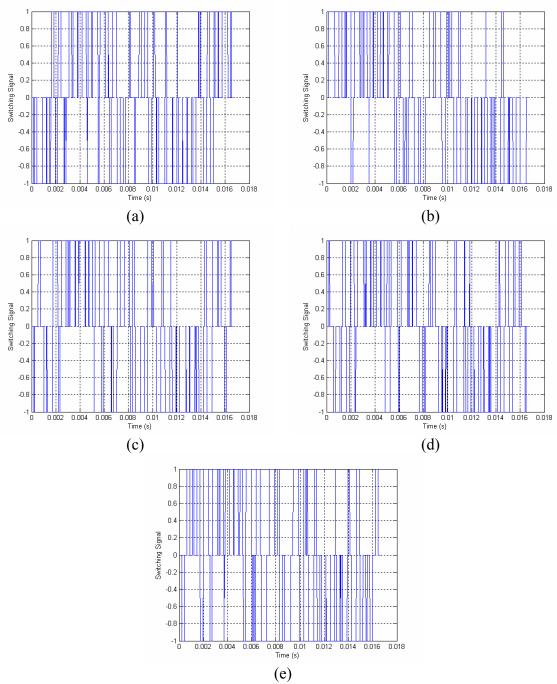

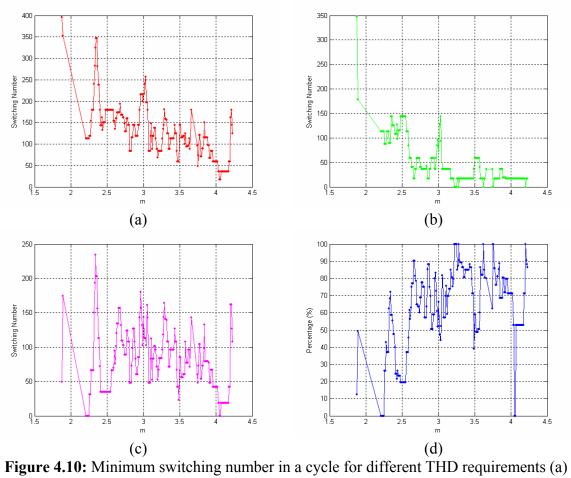

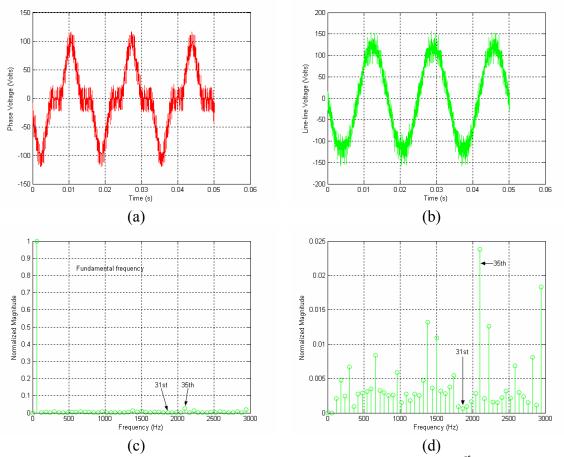

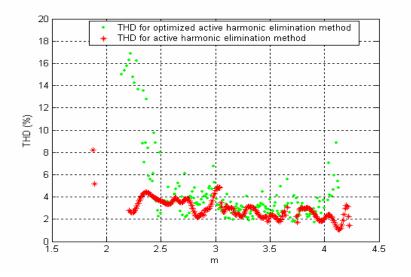

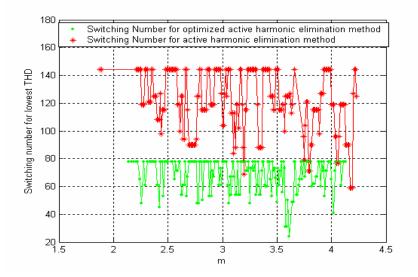

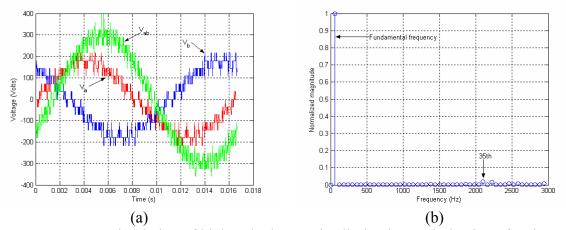

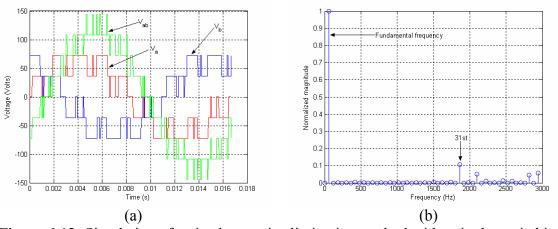

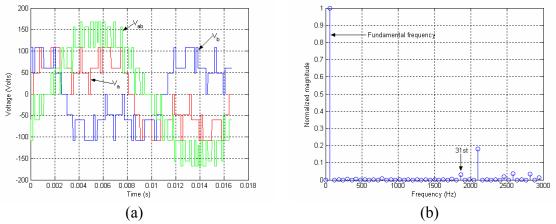

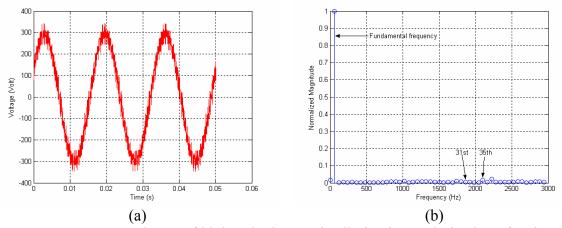

voltage waveform with triplen harmonics compensation; (d) normalized FFT analysis of line-line voltage with triplen harmonics compensation......74 Figure 3.23: Experimental results of 11-level multilevel converter control (m = 2.28) (a) phase voltage; (b) line-line voltage; (c) normalized FFT analysis of line-line voltage; (d) normalized harmonic contents of line-line voltage with fundamental content Figure 3.24: Experimental results of 17-level multilevel converter control with triplen harmonics compensation (m = 3.95) (a) phase voltage; (b) line-line voltage; (c) normalized FFT analysis of line-line voltage; (d) normalized harmonic contents of Figure 4.1: Normalized the 17<sup>th</sup>, 19<sup>th</sup>, 23<sup>rd</sup>, 25<sup>th</sup> harmonic magnitude and their compensation switching angles (a) normalized magnitudes; (b) compensation angles Figure 4.3: THD for fundamental frequency switching method and active harmonic Figure 4.4: Fundamental frequency switching case simulation (m = 2.28) (a) phase voltage; (b) normalized FFT analysis of phase voltage; (c) line-line voltage; (d) Figure 4.5: Harmonic elimination up to the  $31^{st}$  case simulation (m = 2.28) (a) phase voltage; (b) normalized FFT analysis of phase voltage; (c) line-line voltage; (d) **Figure 4.6:** Phase voltage with the 5-31<sup>st</sup> odd, non-triplen harmonic eliminated with Figure 4.7: Harmonic elimination up to the 49th case simulation (m = 2.28) (a) phase voltage; (b) normalized FFT analysis of phase voltage; (c) line-line voltage; (d) **Figure 4.9:** Switching signals based on first-on, first-off strategy (a) switching signal 1; (b) switching signal 2; (c) switching signal 3; (d) switching signal 4; (e) switching Figure 4.10: Minimum switching number in a cycle for different THD requirements (a) for 3% THD; (b) for 5% THD; (c) additional switching number for decreasing THD from 5% to 3%; (d) increased percentage of switching number for 2% THD Figure 4.11: Switching number in a cycle to eliminate harmonics below the 31<sup>st</sup> and its **Figure 4.12:** Experimental results for harmonic elimination up to the  $31^{st}$  (THD = 4.0%) (a) phase voltage; (b) line-line voltage; (c) normalized FFT analysis of line-line voltage; (d) normalized harmonic contents of line-line voltage with fundamental **Figure 4.13:** Experimental results for harmonic elimination up to the  $49^{\text{th}}$  (THD = 2.89%) (a) phase voltage; (b) line-line voltage; (c) normalized FFT analysis of lineline voltage; (d) normalized harmonic contents of line-line voltage with

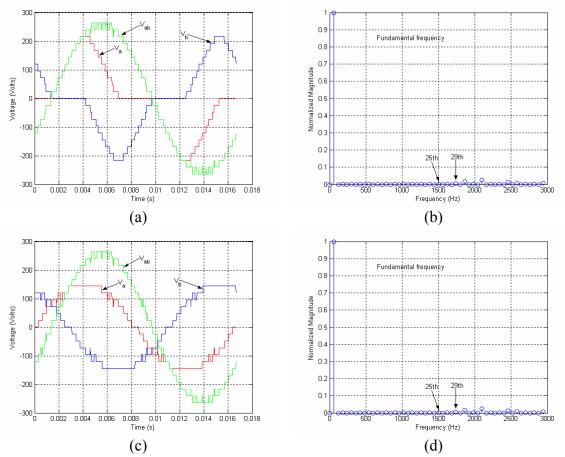

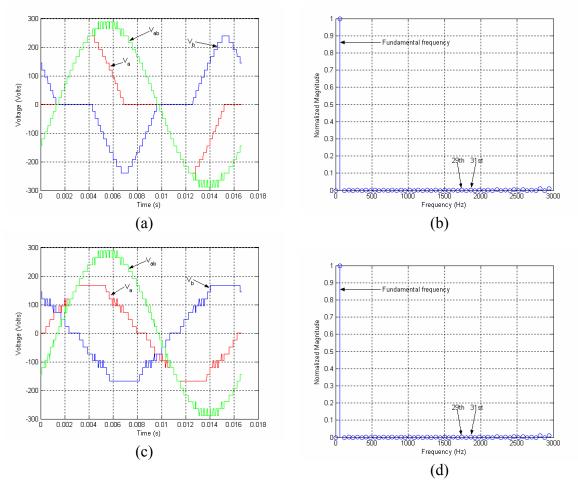

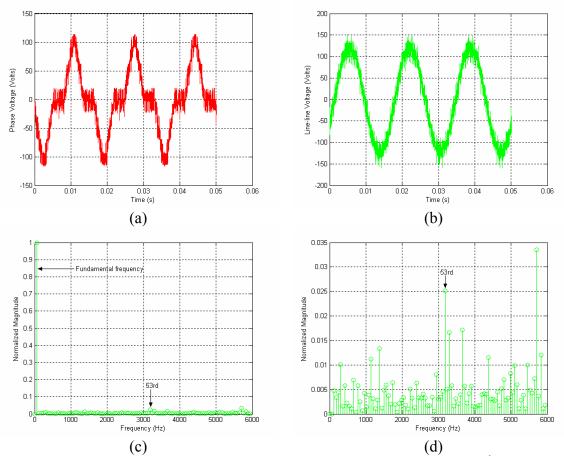

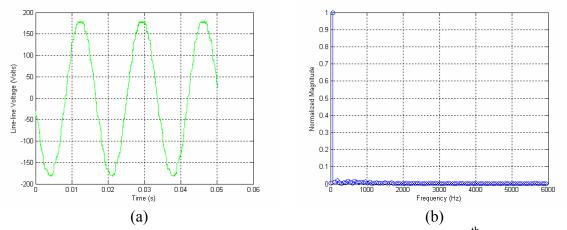

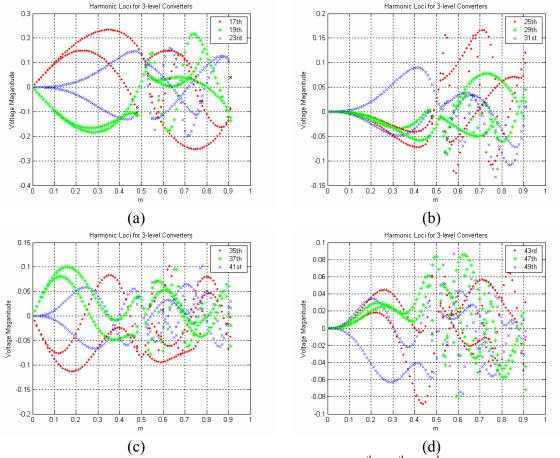

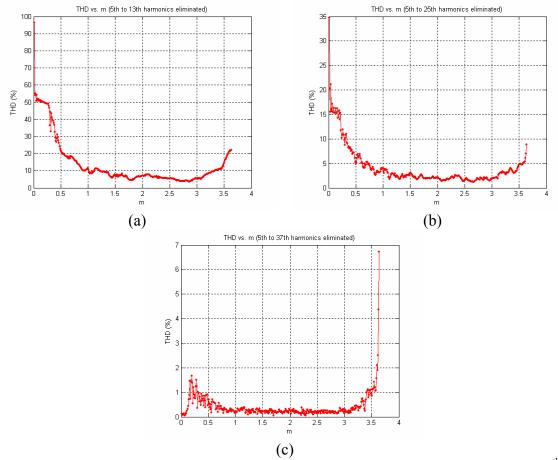

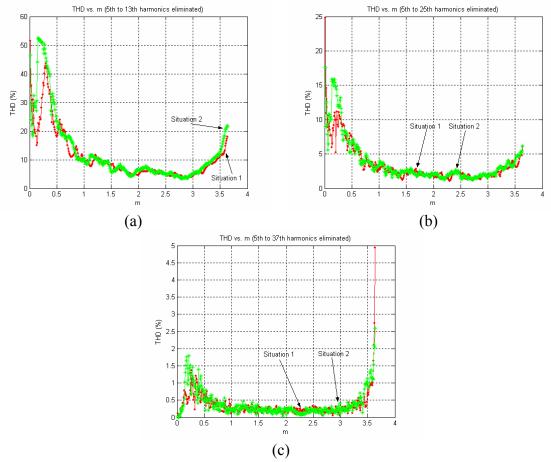

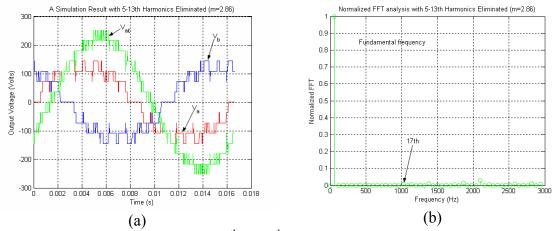

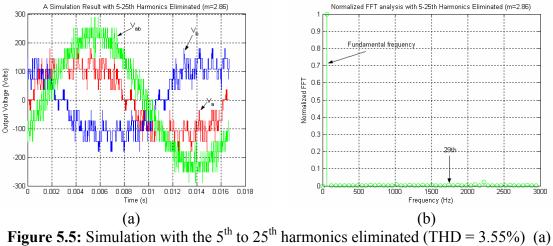

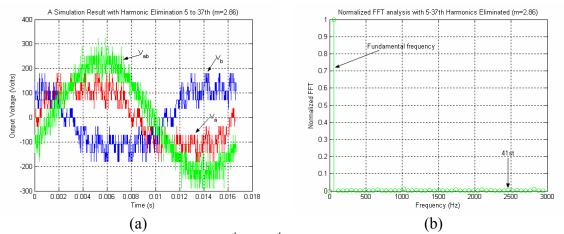

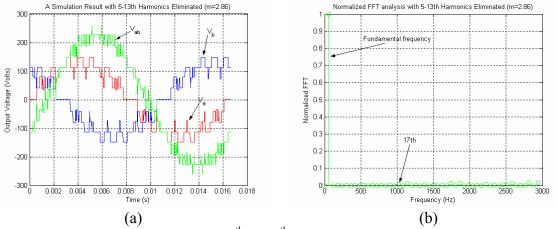

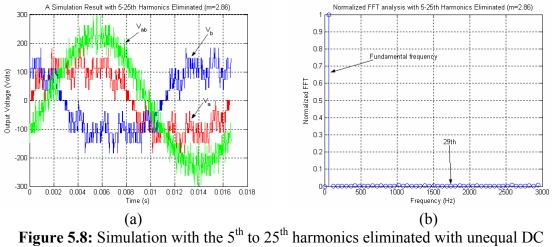

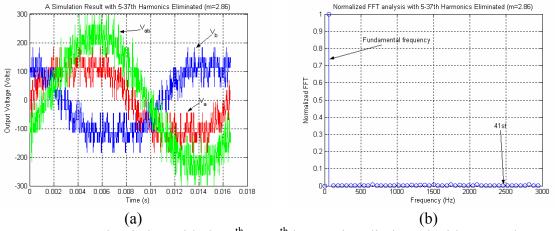

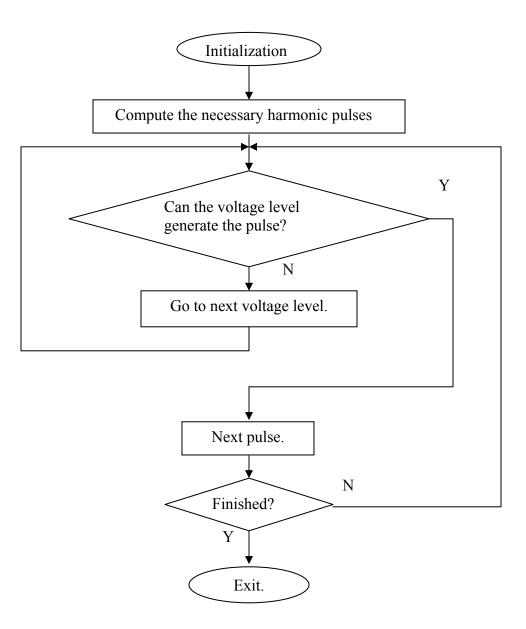

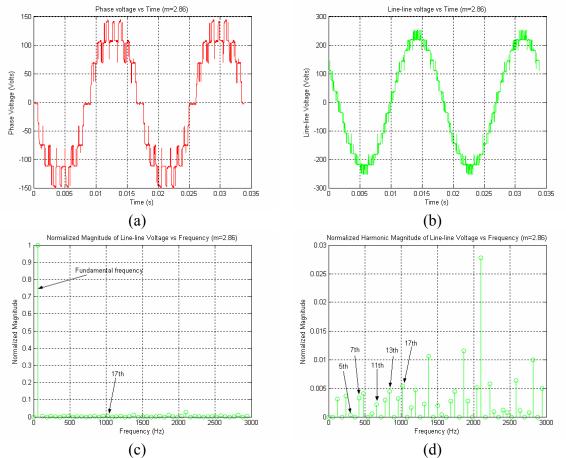

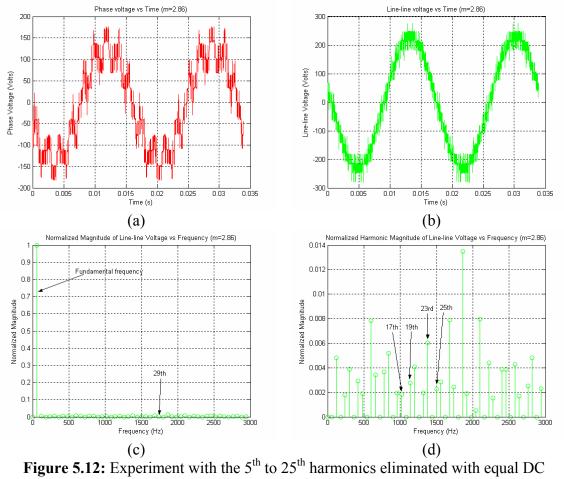

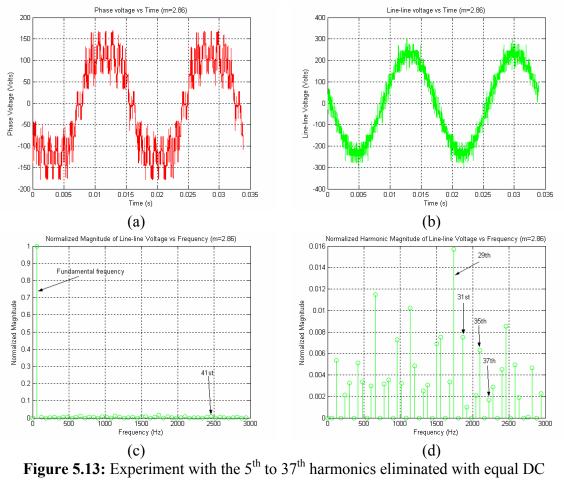

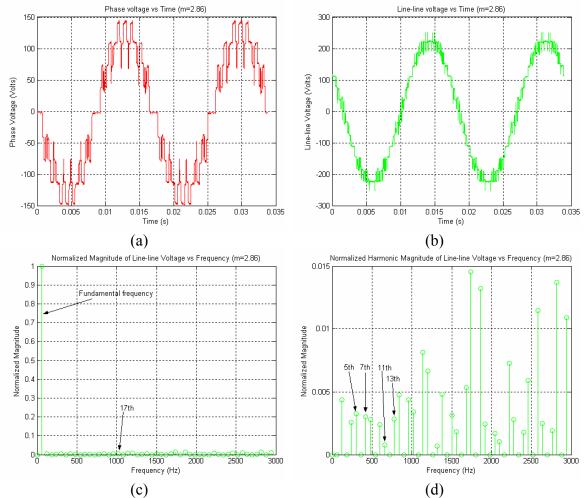

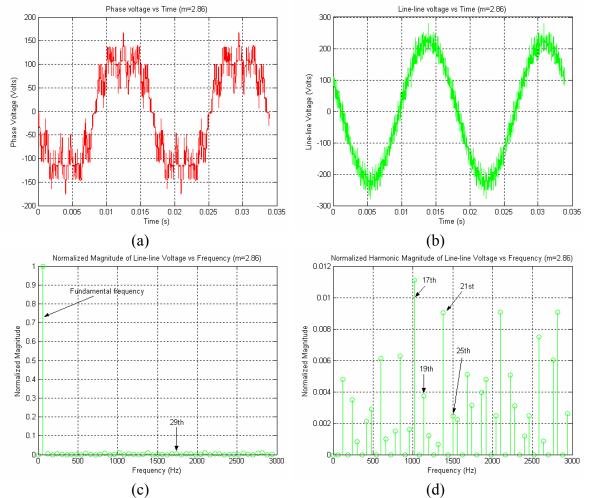

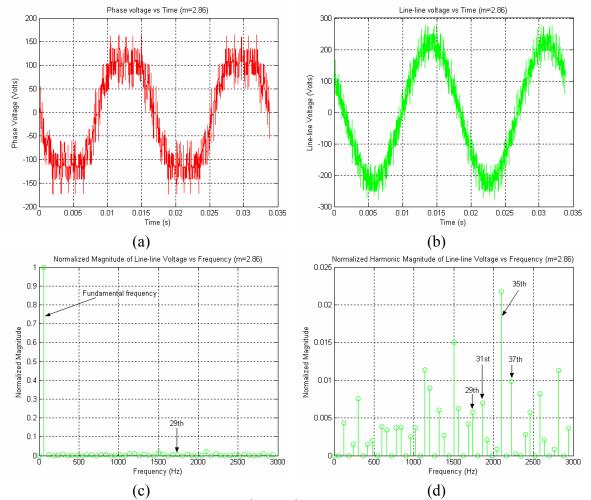

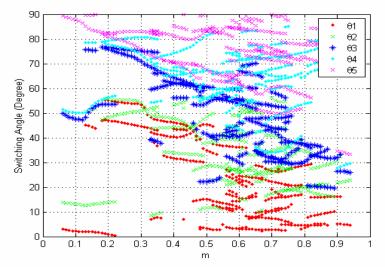

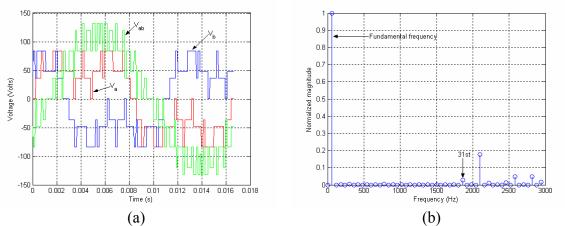

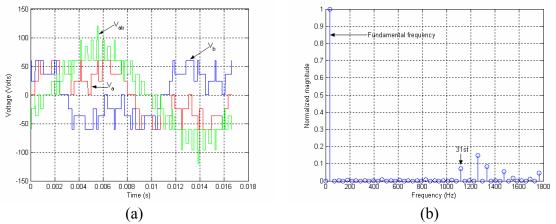

**Figure 4.14:** Experimental results for harmonic elimination up to the 49<sup>th</sup> with a 10  $\mu$ F capacitor filter (THD = 2.26%) (a) line-line voltage; (b) normalized FFT analysis of **Figure 5.1:** Harmonic loci for unipolar converter (a) 17<sup>th</sup>, 19<sup>th</sup>, 23<sup>rd</sup> harmonic loci; (b) 25<sup>th</sup>, 29<sup>th</sup>, 31<sup>st</sup> harmonic loci; (c) 35<sup>th</sup>, 37<sup>th</sup>, 41<sup>st</sup> harmonic loci; (d) 43<sup>rd</sup>, 47<sup>th</sup>, 49<sup>th</sup> Figure 5.2: Minimum THD for equal DC voltages (a) harmonic elimination to the 13<sup>th</sup>; (b) harmonic elimination to the 25<sup>th</sup>; (c) harmonic elimination to the 37<sup>th</sup> ...... 103 Figure 5.3: Minimum THD for unequal DC voltages (a) harmonic elimination to the 13<sup>th</sup>; (b) harmonic elimination to the 25<sup>th</sup>; (c) harmonic elimination to the 37<sup>th</sup> .... 105 Figure 5.4: Simulation with the 5<sup>th</sup> to 13<sup>th</sup> harmonics eliminated (THD = 3.70%) (a) phase voltage and line-line voltage; (b) normalized FFT analysis of line-line voltage Figure 5.5: Simulation with the 5<sup>th</sup> to  $25^{th}$  harmonics eliminated (THD = 3.55%) (a) phase voltage and line-line voltage; (b) normalized FFT analysis of line-line voltage Figure 5.6: Simulation with the 5<sup>th</sup> to 37<sup>th</sup> harmonics eliminated (THD = 2.36%) (a) phase voltage and line-line voltage; (b) normalized FFT analysis of line-line voltage **Figure 5.7:** Simulation with the 5<sup>th</sup> to 13<sup>th</sup> harmonics eliminated with unequal DC voltages (THD = 3.59%) (a) phase voltage and line-line voltage; (b) normalized **Figure 5.8:** Simulation with the 5<sup>th</sup> to 25<sup>th</sup> harmonics eliminated with unequal DC voltages (THD = 1.79%) (a) phase voltage and line-line voltage; (b) normalized **Figure 5.9:** Simulation with the 5<sup>th</sup> to 37<sup>th</sup> harmonics eliminated with unequal DC voltages (THD = 1.65%) (a) phase voltage and line-line voltage; (b) normalized Figure 5.10: Switching control flow chart for multilevel converters with unequal DC Figure 5.11: Experiment with the 5<sup>th</sup> to 13<sup>th</sup> harmonics eliminated with equal DC voltages (THD = 3.60%) (a) phase voltage; (b) line-line voltage; (c) normalized FFT analysis of line-line voltage; (d) normalized harmonic contents of line-line voltage Figure 5.12: Experiment with the 5<sup>th</sup> to 25<sup>th</sup> harmonics eliminated with equal DC voltages (THD = 2.08%) (a) phase voltage; (b) line-line voltage; (c) normalized FFT analysis of line-line voltage; (d) normalized harmonic contents of line-line voltage Figure 5.13: Experiment with the 5<sup>th</sup> to 37<sup>th</sup> harmonics eliminated with equal DC voltages (THD = 2.86%) (a) phase voltage; (b) line-line voltage; (c) normalized FFT analysis of line-line voltage; (d) normalized harmonic contents of line-line voltage Figure 5.14: Experiment with the 5<sup>th</sup> to 13<sup>th</sup> harmonics eliminated with unequal DC voltages (THD = 3.24%) (a) phase voltage; (b) line-line voltage; (c) normalized FFT

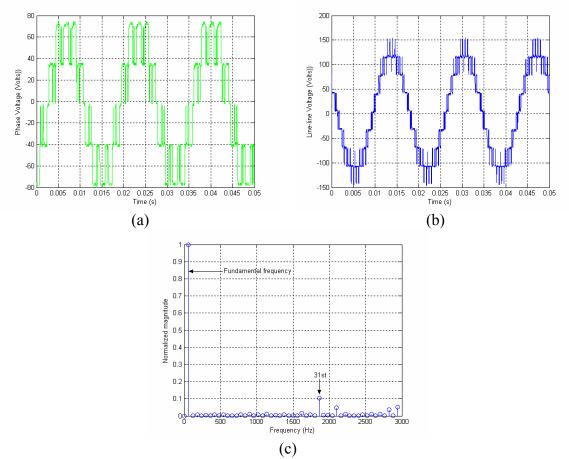

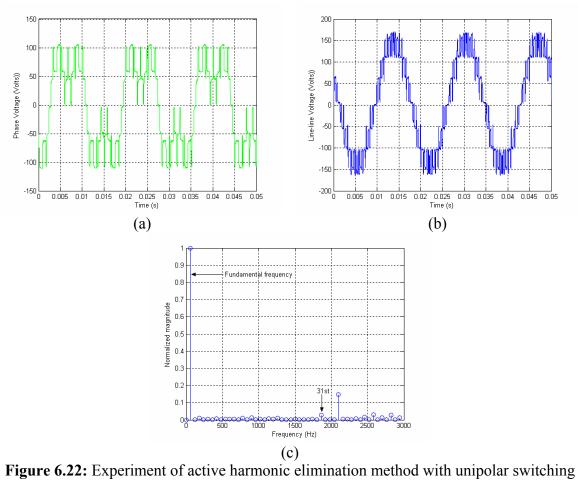

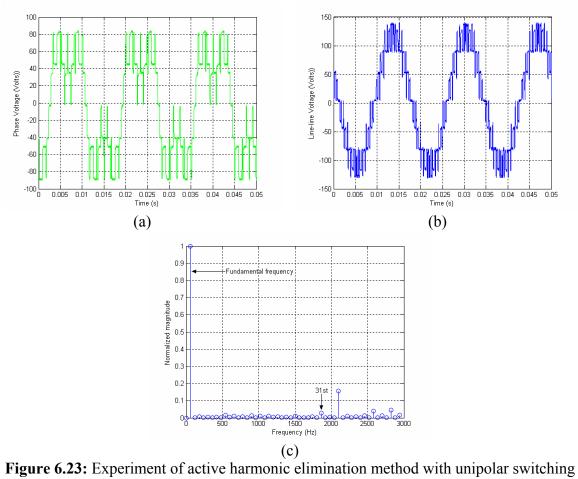

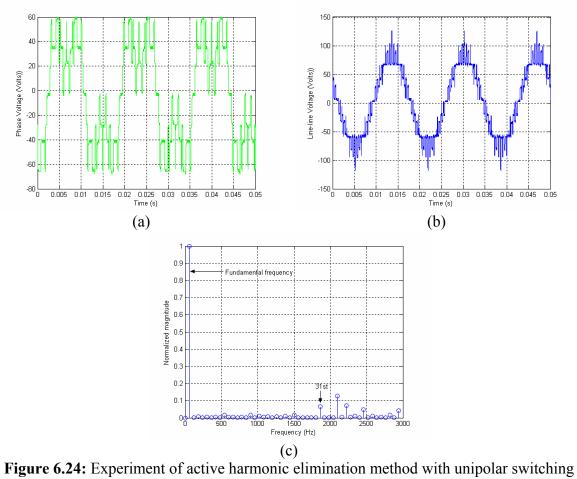

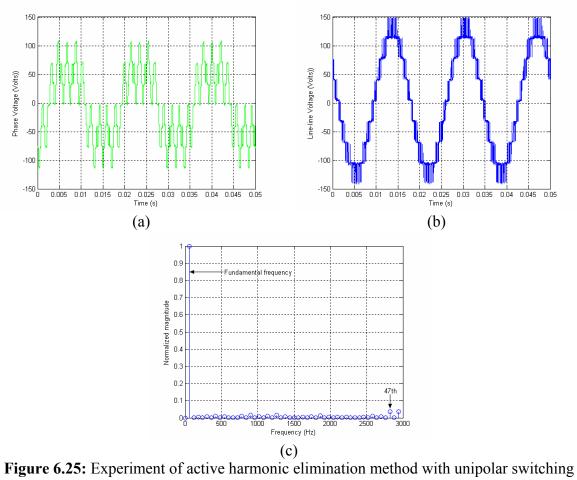

Figure 6.13: Simulation of active harmonic elimination method with unipolar switching scheme (a) voltage waveform; (b) normalized FFT analysis of line-line voltage ( $k_1$  = Figure 6.14: Simulation of active harmonic elimination method with unipolar switching scheme (a) voltage waveform; (b) normalized FFT analysis of line-line voltage ( $k_l =$ Figure 6.15: Simulation of active harmonic elimination method with unipolar switching scheme (a) voltage waveform; (b) normalized FFT analysis of line-line voltage ( $k_1$  = Figure 6.16: Simulation of active harmonic elimination method with unipolar switching scheme (a) voltage waveform; (b) normalized FFT analysis of line-line voltage ( $k_l =$ Figure 6.17: Simulation of active harmonic elimination method with unipolar switching scheme (a) voltage waveform; (b) normalized FFT analysis of line-line voltage ( $k_1$  = Figure 6.18: Simulation of active harmonic elimination method with unipolar switching scheme (a) voltage waveform; (b) normalized FFT analysis of line-line voltage ( $k_1$  = Figure 6.19: Simulation of active harmonic elimination method with unipolar switching scheme (a) voltage waveform; (b) normalized FFT analysis of line-line voltage ( $k_1$  = Figure 6.20: Experiment of high order harmonic elimination optimization of active harmonic elimination method with fundamental switching scheme (a) line-line voltage; (b) normalized FFT analysis of line-line voltage (m = 3.79, THD = 3.52%) Figure 6.21: Experiment of active harmonic elimination method with unipolar switching scheme (a) phase voltage waveform; (b) line-line voltage; (c) normalized FFT analysis of line-line voltage ( $k_1 = k_2$ ,  $V_{dc} = 36$  V, m = 1.460, THD = 13.3%)...... 143 Figure 6.22: Experiment of active harmonic elimination method with unipolar switching scheme (a) phase voltage waveform; (b) line-line voltage; (c) normalized FFT analysis of line-line voltage ( $k_1 = 0.8$ ,  $k_2 = 1$ ,  $V_{dc} = 60$  V, m = 1.120, THD = 15.8%) Figure 6.23: Experiment of active harmonic elimination method with unipolar switching scheme (a) phase voltage waveform; (b) line-line voltage; (c) normalized FFT analysis of line-line voltage ( $k_1 = 0.75$ ,  $k_2 = 1$ ,  $V_{dc} = 48$  V, m = 1.080, THD = Figure 6.24: Experiment of active harmonic elimination method with unipolar switching scheme (a) phase voltage waveform; (b) line-line voltage; (c) normalized FFT analysis of line-line voltage ( $k_1 = 0.67, k_2 = 1, V_{dc} = 36V, m = 0.960, THD =$ Figure 6.25: Experiment of active harmonic elimination method with unipolar switching scheme (a) phase voltage waveform; (b) line-line voltage; (c) normalized FFT analysis of line-line voltage ( $k_1 = 1, k_2 = 1, k_3 = 1, V_{dc} = 36V, m = 1.500, THD =$

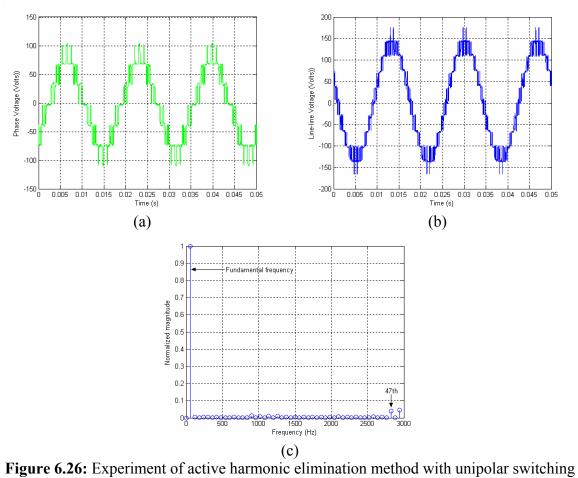

| Figure 6.26: Experiment of active harmonic elimination method with unipolar switching           |

|-------------------------------------------------------------------------------------------------|

| scheme (a) phase voltage waveform; (b) line-line voltage; (c) normalized FFT                    |

| analysis of line-line voltage ( $k_1 = 0.9, k_2 = 0.95, k_3 = 1, V_{dc} = 38V, m = 1.660$ , THD |

| = 6.42%)                                                                                        |

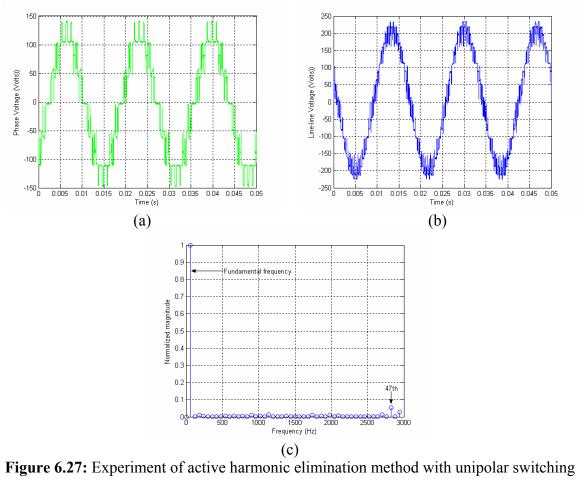

| Figure 6.27: Experiment of active harmonic elimination method with unipolar switching           |

| scheme (a) phase voltage waveform; (b) line-line voltage; (c) normalized FFT                    |

| analysis of line-line voltage ( $k_1 = 0.6, k_2 = 0.8, k_3 = 1, V_{dc} = 60V, m = 1.580, THD =$ |

| 6.54%)                                                                                          |

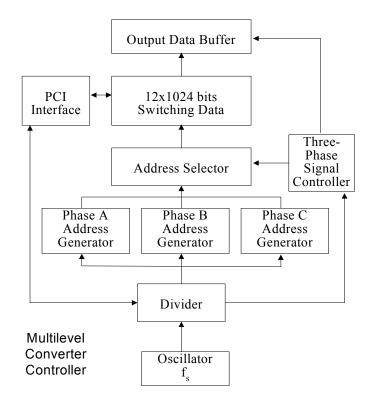

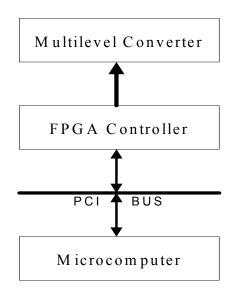

| Figure 7.1: Block diagram for FPGA controller                                                   |

| <b>Figure 7.2:</b> System block                                                                 |

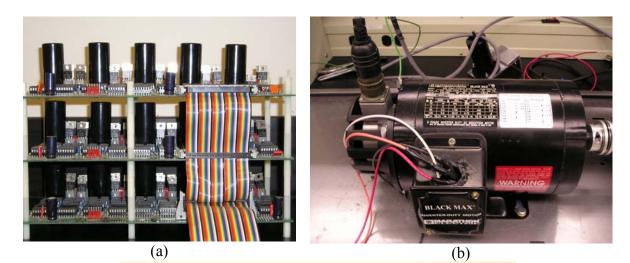

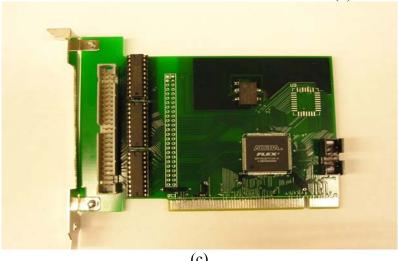

| <b>Figure 7.3:</b> Experiment setup (a) 10 kW H-bridge multilevel converter prototype; (b)      |

| induction motor load; (c) FPGA controller board156                                              |

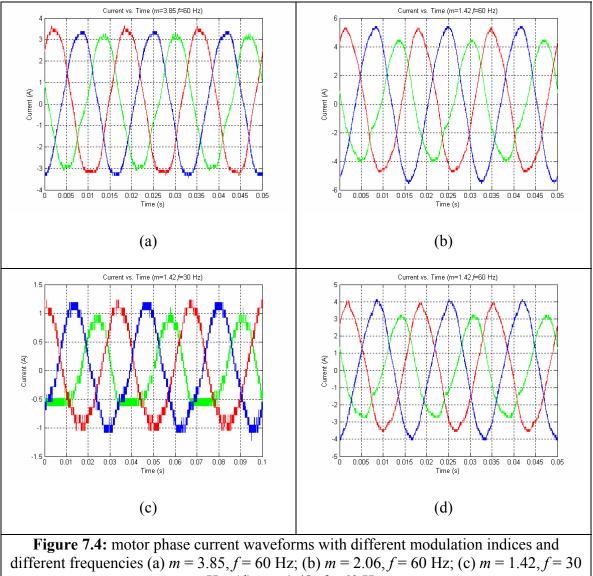

| Figure 7.4: motor phase current waveforms with different modulation indices and                 |

| different frequencies (a) $m = 3.85, f = 60$ Hz; (b) $m = 2.06, f = 60$ Hz; (c) $m = 1.42, f$   |

| = 30 Hz; (d) $m = 1.42, f = 60$ Hz                                                              |

|                                                                                                 |

## 1. Introduction

#### 1.1. Background

Electricity plays an important role in modern society since it was first used about one century ago. To utilize electricity for all kinds of tasks, many different electrical and electronic devices have been invented. Among these, the DC-AC converter is one of the most important power electronic devices.

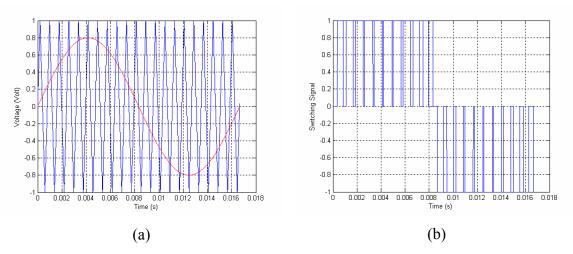

One of the most widely used strategies for controlling the AC output of power electronic converters is the technique known as pulse width modulation (PWM), which varies the duty cycle of the converter switches at a high switching frequency to achieve a target average low-frequency output voltage or current. A traditional sine-triangle PWM is shown in Figure 1.1.

Three significantly different PWM methods for determining the converter switching ON times have been usefully proposed for fixed-frequency modulation systems [1]. These PWM methods are:

- 1. Naturally sampled PWM: Switching at the intersection of a target reference waveform and a high-frequency carrier.

- 2. Regular sampled PWM: Switching at the intersection between a regularly sampled reference waveform and a high-frequency carrier.

- 3. Direct PWM: Switching so that the integrated area of the target reference waveform over the carrier interval is the same as the integrated area of the converter switched output.

Other PWM methods are variations of these three basic PWM methods. Even the well-known space vector modulation strategy, which is often claimed to be a completely different modulation approach, is really just a variation of regular sampled PWM which specifies the same switched pulse widths but places them a little differently in each carrier interval [1].

Figure 1.1: Sine-triangle PWM control (a) sinusoidal reference signal and triangle carrier signal; (b) switching signal

In recent years, multilevel converters have been developed for several reasons.

- 1. Industry has begun to demand higher power equipment, which now reaches the megawatt level. Controlled AC drives in the megawatt range are usually connected to the medium-voltage network. Today, it is hard to connect a single power semiconductor switch directly to medium voltage grids (such as 15 kV) [13].

- 2. Multilevel converters can solve problems with some present bi-level PWM adjustable-speed drives (ASDs). ASDs usually employ a front-end diode rectifier and a converter with PWM-controlled switching devices to convert the DC voltage to variable frequency and variable voltage for motor speed control. Motor damage and failure have been reported by industry as a result of some ASD converters' high-voltage change rates (dv/dt), which produce a common-mode voltage across the motor windings. High-frequency switching can exacerbate the problem because of the numerous times this common mode voltage is impressed upon the motor each cycle. The main problems are reported as "motor bearing failure" and "motor winding insulation breakdown" because of circulating currents, dielectric stresses, voltage surge, and corona discharge. The failure of some ASDs is because the voltage

change rate (dv/dt) sometimes can be high enough to induce corona discharge between the winding layers [2].

3. With the development of modern power electronic devices, these can switch at higher frequency and higher voltages, which can generate broadband electromagnetic interference (EMI). Although the high-frequency switching can increase the motor running efficiency and is well above the acoustic noise level, the (dv/dt) associated dielectric stresses between insulated winding turns are also greatly increased [2].

The multilevel converter is one of the more promising techniques for mitigating the aforementioned problems. Multilevel converters utilize several DC voltages to synthesize a desired AC voltage. For this reason, multilevel converters can reduce (dv/dt) to conquer the motor failure problem and EMI problem. Multilevel converters also have emerged as the solution for working with higher voltage levels. Multilevel converters include an array of power semiconductors and capacitor voltage sources, which generate output voltages with stepped waveforms. The commutation of the switches permits the addition of the capacitor voltages, which reach high voltage at the output, while the power semiconductors must withstand only reduced voltages.

One application for multilevel converters is distributed power systems. Multilevel converters can be implemented using distributed energy resources such as photovoltaic and fuel cells, and then be connected to an AC power grid. If a multilevel converter is made to either draw or supply purely reactive power, then the multilevel converter can be used as a reactive power compensator. For example, a multilevel converter being used as a reactive power compensator could be placed in parallel with a load connected to an AC system. This is because a reactive power compensator can help to improve the power factor of a load [14].

Another application for multilevel converters is to interconnect different power grids. For example, two diode-clamped multilevel converters can be used to produce such a system. One multilevel converter acts as a rectifier for the utility interface. The other multilevel converter acts as an converter to supply the desired AC load. Such a system can be used to connect two asynchronous systems and acts as a frequency changer, a

phase shifter, or a power flow controller.

#### **1.2. Problem Statement**

For many power converter applications, it is desirable for the converter to output a desired waveform with minimum distortion. For example, a DC-AC converter is desired to output a purely sinusoidal waveform. But for the practical converters, they can just output a series of rectangular waves. The key issues for the control of the converters are to get the modulation methods to control the output rectangular waves to synthesize the desired waveforms. Therefore, a modulation control method needs to generate desired fundamental frequency voltage and eliminate other higher order harmonics as much as possible.

After Jean Baptiste Joseph Fourier (1768 – 1830) discovered the Fourier Series, it is possible to represent periodic functions by an infinite sum of trigonometric functions that are harmonically related. In other words, each trigonometric term in this infinite series has a frequency equal to an integer multiple of the fundamental frequency of the original periodic function. To express these ideas in mathematical form, Fourier showed that a periodic function f(t) could be expressed as

$$f(t) = a_0 + \sum_{n=1}^{\infty} c_n \cos(2\pi n f_o t + \varphi_n)$$

(1.1)

where *n* is the set of integer numbers  $1, 2, 3, ..., \infty$ , and  $\varphi_n$  is the initial phase for the  $n^{th}$  harmonic.

In (1.1),  $a_0$  and  $c_n$  are called the Fourier coefficients. These terms are determined from f(t). The term  $f_o$  is the fundamental frequency of the periodic function f(t). The integer multiples of  $f_o$ , such as  $2f_o$  and  $3f_o$ , are known as the harmonic frequencies of f(t). Therefore, the term  $nf_o$  is the  $n^{th}$  harmonic of f(t).

Today, the Fourier transformation method has been used to develop all kinds of modulation methods.

The most popular modulation method for bi-level converters is the PWM method. Traditional PWM methods employ switching frequencies on the order of several kHz. The traditional PWM methods employ much higher switching frequencies for two reasons. The first reason concerns harmonics. Undesirable harmonics occur at much higher frequencies. Thus, filtering is much easier and less expensive. The second reason concerns audible noise. Several kHz is well above the acoustic noise level. Also, if the generated high frequency harmonics are above the bandwidth of some actual systems, there is no power dissipation due to these harmonics [14].

But as mentioned above, traditional PWM schemes have the inherent problems of producing electromagnetic interference (EMI). Rapid changes in voltages (dv/dt) are a source of EMI. The presence of a high dv/dt can cause damage to electrical motors. A high dv/dt produces common-mode voltages across the motor windings. Furthermore, higher switching frequencies can make this problem worse due to the increased number of times these common-mode voltages are applied to the motor during each fundamental cycle. Problems such as motor bearing failure and motor winding insulation breakdown can result due to circulating currents and voltage surges [2]. Also, long current-carrying conductors connecting equipment can result in a considerable amount of EMI.

Multilevel converters inherently tend to have a smaller dv/dt due to the fact that switching involves several smaller voltages. Furthermore, switching at the fundamental frequency will also result in decreasing the number of times these voltage changes occur per fundamental cycle.

The key issue for multilevel converter modulation is the harmonics elimination. The multilevel fundamental switching method inherently provides the opportunity to eliminate certain higher order harmonics by varying the times at which certain switches are turned "on" and turned "off", which is also called varying the switching angles. Harmonic elimination is performed for several reasons. The first reason is harmonics are a source of EMI. Without harmonic elimination, designed circuits would need more protection in the form of snubbers or EMI filters [14]. As a result, designed circuits would cost more. The second reason is that EMI can interfere with control signals used to control power electronics devices and radio signals. The third reason is that harmonics can create losses in power equipment. For example, harmonic currents in an electrical induction motor will dissipate power in the motor stator and rotor windings. There will

also be additional core losses due to harmonic frequency eddy currents. The fourth reason is that harmonics can lower the power factor of a load. Increased harmonic content will decrease the magnitude of the fundamental relative to the magnitude of the entire current. As a result, the power factor would decrease [14].

It was mentioned earlier that an increase in the number of DC voltages in a multilevel converter results in a better approximation to a sinusoidal waveform. Furthermore, the increased number of DC voltages provides the opportunity to eliminate more harmonic contents. Eliminating harmonic contents will make it easier to filter the remaining harmonic content. As a result, filters will be smaller and less expensive.

The second advantage of multilevel converters concerns switch ratings. Since multilevel converters usually utilize a large number of DC voltages, several switches are required to block smaller voltages. Since switch stresses are reduced, required switch ratings are lowered.

The third advantage of multilevel converters concerns system reliability. If a component fails on a multilevel converter, most of the time the converter will still be usable at a reduced power level. Furthermore, multilevel converters tend to have switching redundancies. In other words, there might be more than one way to produce the desired voltage [14].

The fourth advantage of multilevel converters concerns application practicality. As an example, consider designing a converter for a large HEV. Such an application would require excessively large components to deal with the relatively large working voltages and currents. These large components are expensive, bulky, and generally not reliable. However, multilevel converters allow for the utilization of smaller, more reliable components.

One disadvantage of multilevel converters is that they require more devices than traditional converters. The system cost may increase (part of the increased cost may be offset by the fact switches with lower ratings are being used). Using more devices also means the probability of a system failure will increase.

Another disadvantage of multilevel converters concerns control of the switches. The increased number of switches will result in more complicated control. There are four kinds of control methods for multilevel converters. They are the selective harmonic elimination method, space vector control method, traditional PWM control method and space vector PWM method. The traditional PWM, space vector PWM and space vector modulation methods cannot completely eliminate harmonics. Another disadvantage is space vector PWM and space vector modulation methods can not be applied to multilevel converters with unequal DC voltages. The carrier phase shifting method for traditional PWM method also requires equal DC voltages. Until now, the number of harmonics the selective harmonic elimination method can eliminate is not more than the number of the switching angles in the transcendental equations. Due to the difficulty of solving the transcendental equations, real-time control of multilevel converters with unequal DC voltages is impossible now. No such method can be used to directly compute the output voltage pulses to eliminate any number of the harmonics without any restriction of the number of unknowns in the harmonic equations and available solutions for the equations.

For these reasons, in this thesis, a new modulation control method for multilevel converters is developed and referred to as the active harmonic elimination method.

The active harmonic elimination method contributes to the existing methods on it not only generates the desired fundamental frequency voltage, but also completely eliminates any number of the specified harmonics without the restriction of the number of unknowns in the harmonic equations and available solutions for the harmonic equations. Also the active harmonic elimination method can be applied to both equal DC voltage cases and unequal DC voltage cases. The method is referred to as the active harmonic elimination method because the converter itself can eliminate a specific harmonic. For a traditional bi-level converter, to eliminate a specific harmonic in the output voltage, a specific filter is required.

The second contribution of the active harmonic elimination method is it expands the scope of the traditional selective harmonic elimination method. In a traditional selective harmonic elimination method, the number of harmonics to be eliminated is limited by the unknowns in the harmonic equations and available solutions. If there are no solutions for some modulation index range, the traditional selective harmonic elimination cannot be used. But for the active harmonic elimination method, if the harmonic equations have no solutions for a set of harmonics, they may have solutions for other sets of harmonics. The cost is just additional switchings.

The third contribution of the active harmonic elimination method is that it simplifies the optimal system performance searching by making a tradeoff between switching frequency and harmonic distortion since it can vary its switching frequency for different modulation indices.

The thesis is arranged as follows:

Chapter 2 presents a summary of the existing literature and the state-of-art in multilevel converter topologies and control technologies. The advantages and disadvantages of various multilevel converter topologies and control technologies are discussed. At the end of the chapter, a summary of "what is already done" and "what needs to be done next" will be given.

Chapter 3 explains the resultant method used to eliminate the low order harmonics for a multilevel converter, and develops the Newton Climbing method to eliminate higher order harmonics based on the harmonics elimination theory. The triplen harmonic compensation method to extend the modulation index range and decrease the required DC voltage level number is developed in this chapter, too.

Chapter 4 presents the active harmonic elimination method for equal DC voltage cases.

Chapter 5 extends the active harmonic elimination method for multilevel converters with unequal DC voltages.

Chapter 6 optimizes the active harmonic elimination method and improves its control performance. It can be seen in this chapter that the active harmonic elimination method dramatically expands the scope of the traditional selective harmonic elimination method.

Chapter 7 presents implementation of the active harmonic elimination method on an 11-level multilevel converter. Experiments validate the active harmonic elimination method.

Chapter 8 concludes the thesis's work and gives future research directions.

### 2. Literature Survey

In the previous chapter, the advantages and disadvantages of multilevel converters have been summarized briefly. Before going into system level studies, more information on the topologies and modulation techniques of multilevel converters is required to understand the systems research better. In this chapter, the present topologies and modulation techniques will be reviewed. Finally, a summary of previous research will be given and the remaining research work will be discussed.

#### 2.1. Introduction

There are three main types of multilevel converters: diode-clamped, capacitorclamped, and cascaded H-bridges [13]. The detailed advantages and disadvantages of the three multilevel converters will be discussed in this chapter.

Modulation techniques that have been proposed include traditional PWM method, space vector PWM method, space vector control method, and selective harmonics elimination method [13].

Applications that have been proposed include multilevel rectifiers, DC/DC converters, large motor drives, distributed energy applications (such as static volt-ampere reactive (VAR) compensation), back-to-back high-voltage intertie, and adjustable speed drives (ASD) [13].

#### 2.2. Topology of Multilevel Converters

#### 2.2.1. Diode-Clamped Converter

The simplest diode-clamped converter is commonly known as the neutral point clamped converter (NPC) which was introduced by Nabae *et al.* [4]. The NPC consists of two pairs of series switches (upper and lower) in parallel with two series capacitors where the anode of the upper diode is connected to the midpoint (neutral) of the capacitors and

its cathode to the midpoint of the upper pair of switches; the cathode of the lower diode is connected to the midpoint of the capacitors and divides the main DC voltage into smaller voltages, which is shown in Figure 2.1. In this example, the main DC voltage is divided into two. If the point *O* is taken as the ground reference, the three possible phase voltage outputs are  $-1/2V_{dc}$ , 0, or  $1/2V_{dc}$ . The line-line voltages of two legs with the capacitors are:  $V_{dc}$ ,  $1/2V_{dc}$ , 0,  $-1/2V_{dc}$  or  $-V_{dc}$ . To generate a three-phase voltage, three phases are necessary.

The five-level output voltage can be generated by controlling the switches. Table 2-1 shows the proper switching states. The switches  $(S_{a1} \text{ and } S_{a'1})$  and  $(S_{a2} \text{ and } S_{a'2})$  are complementary pairs. When  $S_{a1}$  is on  $(S_{a1} = 1)$ ,  $S_{a'1}$  is off  $(S_{a'1} = 0)$ . Other switch pairs are similar.

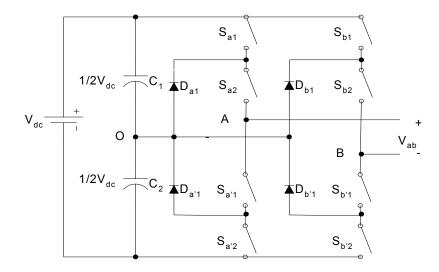

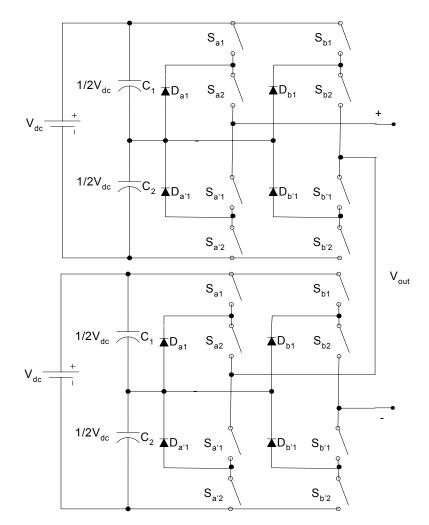

Figure 2.2 shows a two-phase diode-clamped multilevel converter.

Some disadvantages of the diode-clamped multilevel converter may be observed. Using extra diodes in series becomes impractical when the number of levels *m* increases, requiring (m-1)(m-2) diodes per phase if all the diodes have equal blocking voltages. Note that the voltages for diodes in different positions are not balanced. For example, diode  $D_{a2}$  must block two capacitor voltages,  $D_{a(m-2)}$  must block (m-2) capacitor voltages. Also, the switch duty cycle is different for some of the switches requiring different current ratings. In addition, the capacitors do not share the same discharge or charge imbalance can be controlled by using a back-to-back topology, connecting resistors in parallel with capacitors, or using redundant voltage states [4].

The advantages for the diode-clamped converter are the following:

(1) A large number of levels yields a small harmonic distortion.

(2) All phases share the same DC bus.

(3) Reactive power flow can be controlled.

(4) Control is simple.

Figure 2.1: Neutral point diode-clamped converter

Figure 2.2: Two-phase diode-clamped multilevel converter

| S <sub>a1</sub> | S <sub>a2</sub> | $S_{a'l}$ | S <sub>a'2</sub> | $S_{b1}$ | $S_{b2}$ | $S_{b'l}$ | $S_{b'^2}$ | V <sub>ao</sub>             | $V_{bo}$     | $V_{ab}$                 |

|-----------------|-----------------|-----------|------------------|----------|----------|-----------|------------|-----------------------------|--------------|--------------------------|

| 0               | 0               | 1         | 1                | 1        | 1        | 0         | 0          | $-1/2V_{dc}$                | $1/2V_{dc}$  | - <i>V</i> <sub>dc</sub> |

| 0               | 0               | 1         | 1                | 0        | 1        | 1         | 0          | $-1/2V_{dc}$                | 0            | $-1/2V_{dc}$             |

| 1               | 1               | 0         | 0                | 1        | 1        | 0         | 0          | $1/2V_{dc}$                 | $1/2V_{dc}$  | 0                        |

| 0               | 0               | 1         | 1                | 0        | 0        | 1         | 1          | -1/2 <i>V</i> <sub>dc</sub> | $-1/2V_{dc}$ | 0                        |

| 0               | 1               | 1         | 0                | 0        | 0        | 1         | 1          | 0                           | $-1/2V_{dc}$ | $1/2V_{dc}$              |

| 1               | 1               | 0         | 0                | 0        | 0        | 1         | 1          | $1/2V_{dc}$                 | $-1/2V_{dc}$ | $V_{dc}$                 |

**Table 2.1:** Switch states and the output voltages for diode-clamped multilevel converter

The disadvantages are the following:

- (1) Different voltage ratings for clamping diodes are required.

- (2) Real power flow is difficult because of the capacitors' imbalance.

- (3) Different current ratings for switches are required due to their conduction duty cycle.

#### 2.2.2. Capacitor-Clamped Converter

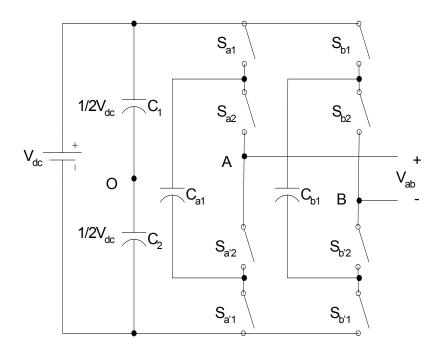

The capacitor-clamped multilevel converter or flying-capacitor converter [6], [12] is similar to the diode-clamped topology, which is shown in Figure 2.3. However, the capacitor-clamped multilevel topology allows more flexibility in waveform synthesis and balancing voltage across the clamped capacitors. For a three-level capacitor-clamped multilevel converter, if the *O* point is taken as the ground reference, a single phase can produce three output levels  $(-1/2V_{dc}, 0 \text{ and } 1/2V_{dc})$ . Likewise for the diode-clamped converter structure, a three-phase converter needs three phases.

The advantages of the capacitor-clamped multilevel converter are:

- (1) Large *m* allows the capacitors extra energy during long discharge transient.

- (2) Flexible switch redundancy for balancing different voltage levels

- (3) A large number of levels yields a small harmonic distortion.

- (4) Active and reactive power flow can be controlled.

Figure 2.3: Topology of a capacitor-clamped multilevel converter

The disadvantages are:

(1) Large number of capacitors are bulky and more expensive than the clamping diodes used in the diode-clamped multilevel converter.

(2) Control for maintaining the capacitors' voltage balance is complicated.

(3) Poor switching utilization and efficiency for real power transmission.

Table 2.2 shows the possible switch combinations to generate the five-level output waveform. An output voltage can be produced by using different combinations of switches. The topology allows increased flexibility in how the majority of the voltage levels may be chosen. In addition, the switches may be chosen to charge or discharge the clamped capacitors, which balance the capacitor voltage.

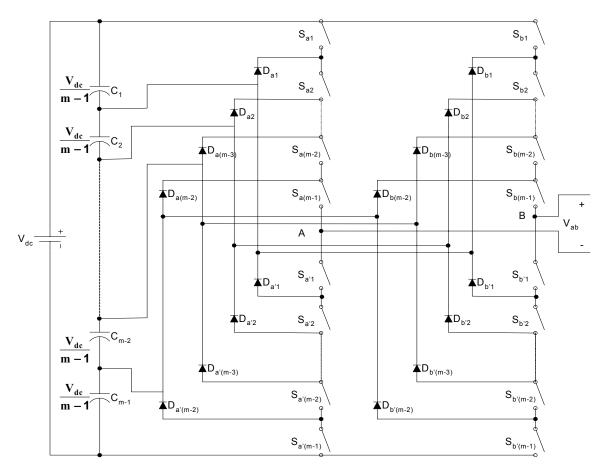

The general *m*-level capacitor-clamped multilevel converter has an *m*-level output phase voltage. Thus, two phases would produce a (2m-1) level output voltage, or line voltage, which is shown in Figure 2.4. Similar to the diode-clamped multilevel converter, the capacitors have different ratings. These capacitors result in a bulky, and expensive converter when compared to the diode-clamped converter.

| Sal | S <sub>a2</sub> | S <sub>a'1</sub> | $S_{a'2}$ | $S_{b1}$ | $S_{b2}$ | $S_{b'l}$ | $S_{b'^2}$ | V <sub>ao</sub> | $V_{bo}$                    | V <sub>ab</sub>   |

|-----|-----------------|------------------|-----------|----------|----------|-----------|------------|-----------------|-----------------------------|-------------------|

| 0   | 0               | 1                | 1         | 1        | 1        | 0         | 0          | $-1/2V_{dc}$    | $1/2V_{dc}$                 | - V <sub>dc</sub> |

| 0   | 0               | 1                | 1         | 0        | 1        | 1         | 0          | $-1/2V_{dc}$    | 0                           | $-1/2V_{dc}$      |

| 0   | 1               | 1                | 0         | 1        | 1        | 0         | 0          | 0               | $1/2V_{dc}$                 | $-1/2V_{dc}$      |

| 1   | 0               | 0                | 1         | 1        | 1        | 0         | 0          | 0               | $1/2V_{dc}$                 | $-1/2V_{dc}$      |

| 1   | 1               | 0                | 0         | 1        | 1        | 0         | 0          | $1/2V_{dc}$     | $1/2V_{dc}$                 | 0                 |

| 0   | 0               | 1                | 1         | 0        | 0        | 1         | 1          | $-1/2V_{dc}$    | $-1/2V_{dc}$                | 0                 |

| 0   | 1               | 1                | 0         | 0        | 0        | 1         | 1          | 0               | $-1/2V_{dc}$                | $1/2V_{dc}$       |

| 1   | 1               | 0                | 0         | 0        | 1        | 1         | 0          | $1/2V_{dc}$     | 0                           | $1/2V_{dc}$       |

| 1   | 0               | 0                | 1         | 0        | 0        | 1         | 1          | 0               | $-1/2V_{dc}$                | $1/2V_{dc}$       |

| 1   | 1               | 0                | 0         | 0        | 0        | 1         | 1          | $1/2V_{dc}$     | -1/2 <i>V</i> <sub>dc</sub> | $V_{dc}$          |

Table 2.2: Switch states and the output voltages for capacitor-clamped multilevel

converter

Figure 2.4: Two-phase capacitor-clamped multilevel converter

#### 2.2.3. Cascaded H-bridge Converter

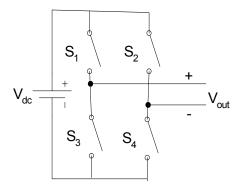

A cascaded H-bridge converter is several H-bridges in series configuration [2], [7], [8], [12]. A single H-bridge is shown in Figure 2.5.

A single H-bridge is a three-level converter. The four switches  $S_1$ ,  $S_2$ ,  $S_3$  and  $S_4$  are controlled to generate three discrete outputs  $V_{out}$  with levels  $V_{dc}$ , 0 and  $-V_{dc}$ . When  $S_1$  and  $S_4$  are on, the output is  $V_{dc}$ ; when  $S_2$  and  $S_3$  are on, the output is  $-V_{dc}$ ; when either pair  $S_1$  and  $S_2$  or  $S_3$  and  $S_4$  are on, the output is 0.

A H-bridge cascaded multilevel converter with *s* separate DC sources is shown in Figure 2.6.

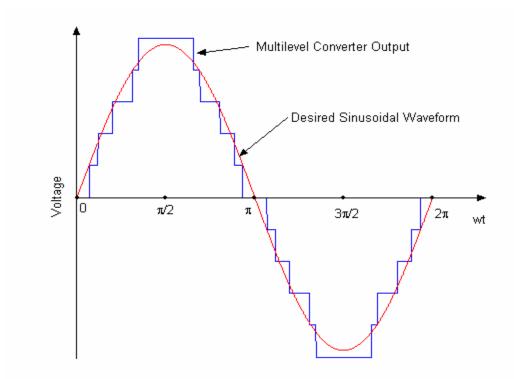

A staircase sinusoidal waveform can be generated by combining specified output levels, which is shown in Figure 2.7. The number of output phase voltage levels m in a cascade converter with s separate DC sources is m = 2s + 1.

Load balance control for each H-bridge and each DC source can be acquired by rotating the switching angles to the H-bridges [2].

The advantages for cascaded multilevel H-bridge converter are the following:

- (1) The series structure allows a scalable, modularized circuit layout and packaging due to the identical structure of each H-bridge.

- (2) No extra clamping diodes or voltage balancing capacitors is necessary.

Figure 2.5: Single H-bridge topology

Figure 2.6: H-bridge cascaded multilevel converter with *s* separate DC sources

Figure 2.7: Staircase sinusoidal waveform generated by H-bridge cascaded multilevel converter

(3) Switching redundancy for inner voltage levels is possible because the phase voltage is the sum of each bridge's output.

The disadvantage for cascaded multilevel H-bridge converter is the following:

(1) Needs separate DC sources;

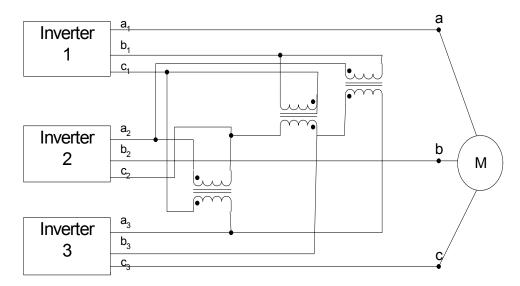

Another kind of cascaded multilevel converters with transformers using standard three-phase bi-level converters has recently been proposed [8]. The circuit is shown in Figure 2.8. The converter uses output transformers to add different voltages. In order for the converter output voltages to be added up, the outputs of the three converters need to be synchronized with a separation of 120° between each phase. For example, obtaining a three-level voltage between outputs *a* and *b*, the output voltage can be synthesized by  $V_{ab}$ =  $V_{a1-b1}+V_{b1-a2}+V_{a2-b2}$ . An isolated transformer is used to provide voltage boost. With three converters synchronized, the voltages  $V_{a1-b1}$ ,  $V_{b1-a2}$ ,  $V_{a2-b2}$ , are all in phase; thus, the output level can be tripled [13].

Figure 2.8: Cascaded multilevel converter with transformers using standard three-phase bi-level converters

The advantage for the cascaded multilevel converters with transformers using standard three-phase bi-level converters is the three converters are identical. So control would be simple. The topology has two disadvantages. The first is the three converters need separate DC sources; the second is it needs a transformer to add up the output voltages.

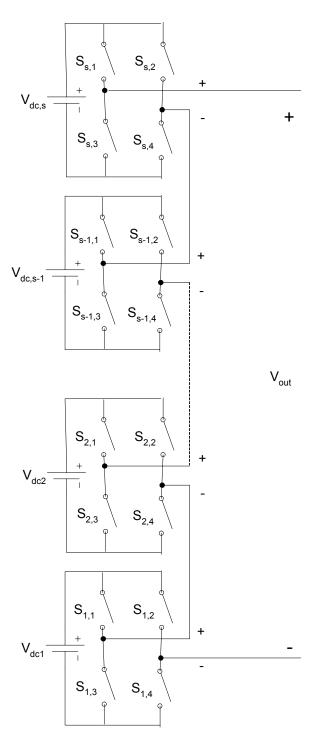

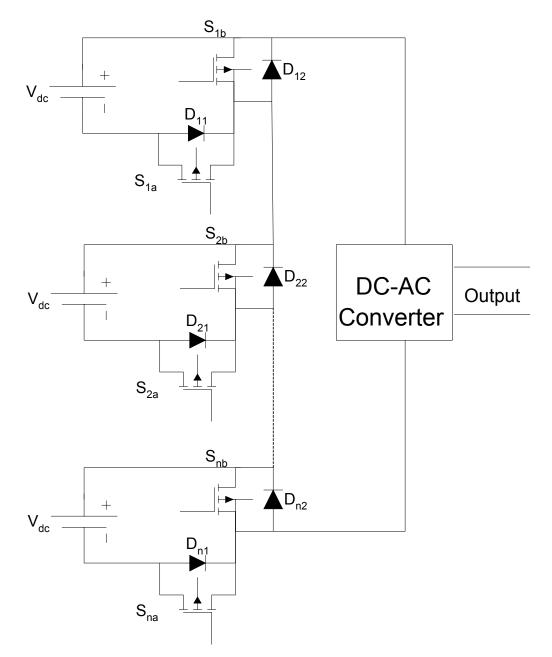

### 2.2.4. Cascaded DC Sources Multilevel Converter and Cascaded Transformers Multilevel Converter

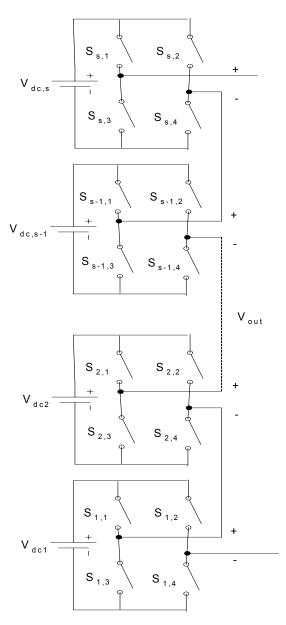

There are other kinds of topologies for multilevel converters. Figure 2.9 is a cascaded DC sources multilevel converter [16]. The states of the switches  $S_{ia}$  and  $S_{ib}$  decide if the level is to be connected into the circuit. If  $S_{ia}$  is ON,  $S_{ib}$  is OFF: this level is connected into the circuit. If  $S_{ia}$  is OFF,  $S_{ib}$  is ON: this level is disconnected from the circuit. This topology is proposed for fuel cell applications. The output voltage of a fuel cell will decrease when the load increases, therefore control of the fuel cell number connected into the circuit can keep the output voltage constant [16].

Figure 2.9: Topology of cascaded DC sources multilevel converters

The advantage of the topology is it can reduce the input voltage ripple for the output converter.

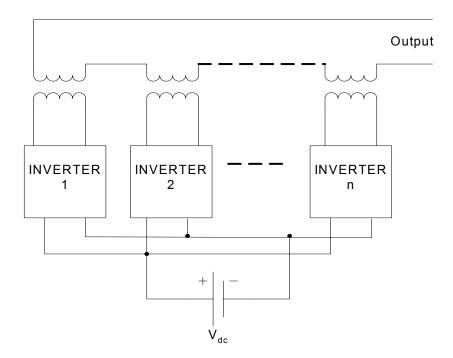

Another topology for multilevel converters is the cascaded transformer multilevel converter [15], which is shown in Figure 2.10.

This topology uses a single DC source and several transformers to generate high voltage output. The topology is similar to topology of the cascaded H-bridge multilevel converters [15].

The advantage for the topology is the system is simple and the converters could be identical. Therefore the control would be simple. Another advantage is that a single common DC voltage source is used. The disadvantage is that the system needs output transformers to add up the output voltages.

Figure 2.10: Topology of cascaded transformers multilevel converters

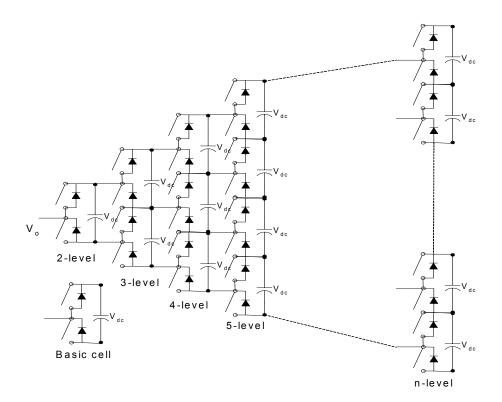

## 2.2.5. Generalized Multilevel Topology

Existing multilevel converters such as diode-clamped and capacitor-clamped multilevel converters can be derived from the generalized converter topology called *P2* topology proposed by Peng [9], which is shown in Figure 2.11. Moreover, the generalized multilevel converter topology can balance each voltage level by itself regardless of load characteristics, active or reactive power conversion, and without any assistance from other circuits at any number of levels automatically. Thus, the topology provides a complete multilevel topology that embraces the existing multilevel converters in principle.

Figure 2.11 shows the *P2* multilevel converter structure per phase leg. Each switching device, diode, or capacitor's voltage is 1  $V_{dc}$ , i.e., 1/(m-1) of the DC-link voltage. Any converter with any number of levels, including the conventional bi-level converter can be obtained using this generalized topology [13].

Figure 2.11: Generalized P2 multilevel converter topology

## 2.2.6. Mixed-Level Hybrid Multilevel Converter

To reduce the number of separate DC sources for high-voltage, high-power applications with multilevel converters, diode-clamped or capacitor-clamped converters can be used to replace the full-bridge cell in a cascaded converter [10]. An example is shown in Figure 2.12. The nine-level cascade converter incorporates a three-level diode-clamped converter as the cell. The original cascaded H-bridge multilevel converter requires four separate DC sources for one phase leg and twelve for a three-phase converter. If a five-level converter replaces the full-bridge cell, the voltage level is effectively doubled for each cell. Thus, to achieve the same nine voltage levels for each phase, only two separate DC sources are needed for one phase leg and six for a three-phase converter.

The configuration has mixed-level hybrid multilevel units because it embeds multilevel cells as the building block of the cascade converter.

The advantage of the topology is it needs less separate DC sources. The disadvantage for the topology is its control will be complicated due to its hybrid structure.

#### 2.2.7. Unequal DC Sources Multilevel Converter

For some applications, it is possible to have different voltage levels among the cells [11]. Therefore the circuit can be called an unequal DC sources multilevel converter. The voltage levels depend on the availability of DC sources. This feature allows more possible output voltage levels to be produced, and thus it is possible to reduce the harmonic contents with less cascade cells required. For example, in Figure 2.13,  $V_{dc1}$ ,  $V_{dc2}$ ,...  $V_{dcs}$  can be different from each other. This kind of topology is also called asymmetric cascade multilevel converters [13].

Figure 2.12: Mixed-level hybrid unit configuration using the three-level diode-clamped converter as the cascaded converter cell to increase the voltage levels

Figure 2.13: Unequal DC sources multilevel converter

Although it is possible to reduce the harmonic contents with less cascaded cells required for unequal DC sources multilevel converters, the control for unequal DC sources multilevel converters is very complicated. Until now, most of the available control methods are for equal DC sources multilevel converters. This is its main disadvantage.

## 2.2.8. Soft-Switched Multilevel Converter

Several soft-switching methods can be implemented for different multilevel converters to reduce the switching loss and to increase efficiency. For the cascaded converter, because each converter cell is a bi-level circuit, the implementation of soft switching is not at all different from that of conventional bi-level converters. For capacitor-clamped or diode-clamped converters, soft-switching circuits have been proposed with different circuit combinations. One of them is zero-voltage-switching types including auxiliary resonant commutated pole (ARCP), coupled inductor with zero-voltage transition (ZVT), and their combinations. [13].

## 2.3. Control and Modulation Techniques of Multilevel Converters

#### 2.3.1. Classification of Modulation Strategies

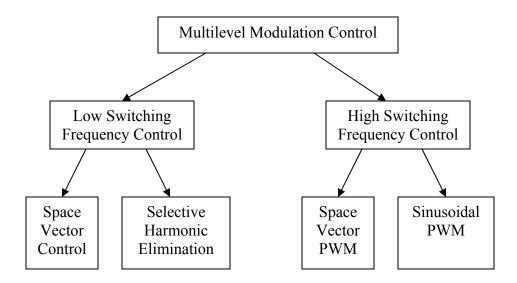

The modulation methods used in multilevel converters can be classified according to switching frequency [13], [24], [25], as shown in Figure 2.14. Methods that work with high switching frequencies have many commutations for the power semiconductors in one cycle of the fundamental output voltage.

The popular methods for high switching frequency methods are classic carrierbased sinusoidal PWM (SPWM) [7], [26] and space vector PWM. The popular methods for low switching frequency methods are space vector modulation (SVM) method and selective harmonic elimination method.

A very popular method with high switching frequency in industrial applications is the classic carrier-based sinusoidal PWM (SPWM) that uses the phase-shifting technique to increase the effective switching frequency. Therefore, the harmonics in the load voltage can be reduced [27].

Figure 2.14: Classification of multilevel modulation methods

Another interesting method is the SVM strategy [24], which has been used in three-level converters. Methods that work with low switching frequencies generally perform one or two commutations of the power semiconductors during one cycle of the output voltages to generate a staircase waveform. Representatives of this family are the multilevel selective harmonic elimination [30], [31] based on elimination theory [3], [28], [29] and the space-vector control (SVC) [32].

#### 2.3.2. Multilevel SPWM

Multilevel SPWM usually needs multiple carriers. Each DC source needs its own carrier. Several multi-carrier techniques have been developed to reduce the distortion in multilevel converters, based on the classical SPWM with triangular carriers. Some methods use carrier disposition and others use phase shifting of multiple carrier signals [12], [26], [33], [34].

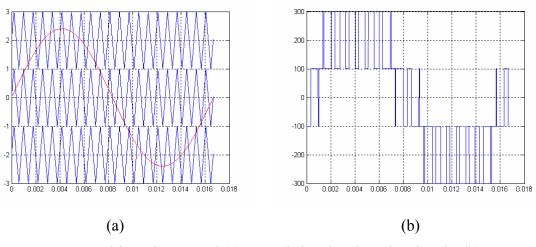

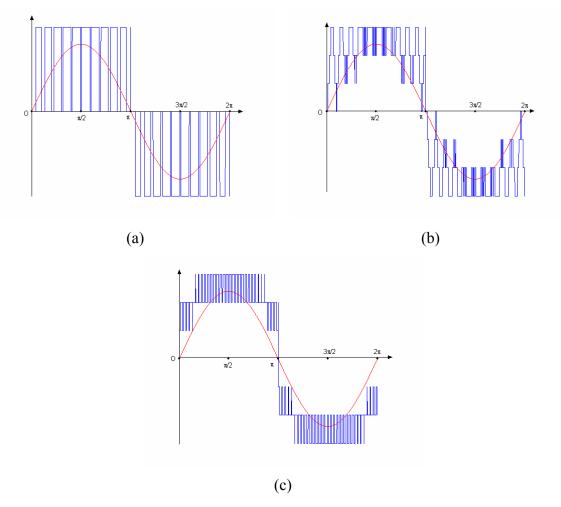

This common SPWM method is the extension of bi-level SPWM. One reference signal is used to compare to the carriers. This can be shown in Figure 2.15 (a). If the reference signal is higher than the carrier, the corresponding converter cell outputs positive voltage; otherwise, the corresponding converter cell outputs negative voltage. The output voltage of the converter is shown in Figure 2.15 (b).

**Figure 2.15:** Multi-carrier control (a) control signal and carrier signals; (b) output voltage

A number of cascaded cells in one phase with their carriers shifted by an angle and using the same control voltage produce a load voltage with the smallest distortion [27]. The effect of this carrier phase-shifting technique can be clearly observed in Figure. 2.16. This result has been obtained for the multi-cell converter in a seven-level configuration, which uses three series-connected cells in each phase. The smallest distortion is obtained when the carriers are shifted by an angle of 120°. A very common practice in industrial applications for the multilevel converter is the injection of a third harmonic in each cell to increase the output voltage [7], [10]. Another advantageous feature of multilevel SPWM is that the effective switching frequency of the load voltage is much higher than the switching frequency of each cell, as determined by its carrier signal.

The advantage of the method is it is very simple. But it has two disadvantages. The first is the method cannot completely eliminate the low order harmonics. Therefore the low order harmonics cause loss and high filter requirements. The second is the high switching frequency causes high switching loss and low efficiency.

**Figure 2.16:** Output voltage with carrier phase shift (a) phase shift 0°; (b) phase shift 90°; (c) phase shift 120°

#### **2.3.3. Space Vector PWM Modulation**

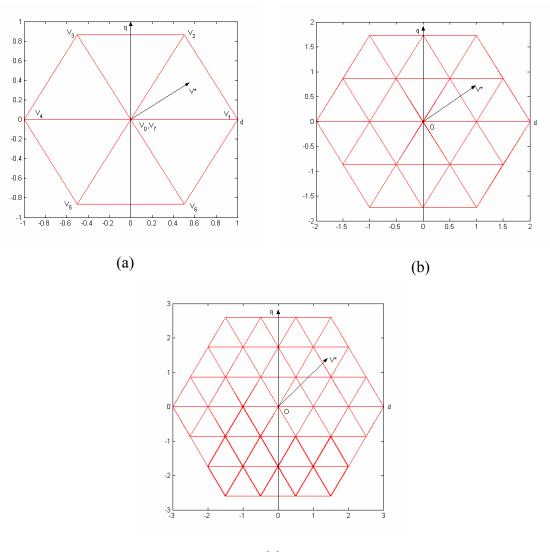

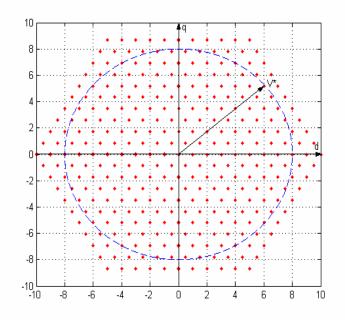

The space vector PWM modulation technique is popular for bi-level PWM converter control. It can be extended to multilevel converters [35]-[41]. Figure. 2.17 shows space vectors for the traditional three-, five-, and seven-level converters. These vector diagrams are universal regardless of the topology of multilevel converter. Therefore it can be used for diode-clamped, capacitor-clamped, or cascaded converters. The adjacent three vectors can synthesize a desired voltage vector by computing the duty cycle for each vector according to the following:

$$\vec{V}^* = \frac{T_j \vec{V}_j + T_{j+1} \vec{V}_{j+1} + T_{j+2} \vec{V}_{j+2}}{T}$$

(2.1)

Space-vector PWM methods generally have the following advantages:

(1). Good utilization of DC-link voltage, low current ripple.

(2). Control is relatively easy, the hardware implementation can be easy by a digital signal processor (DSP).

These advantages make it popular for converter control. But one disadvantage is as the number of levels increases, redundant switching states and the complexity of selecting switching states increase dramatically [13]. Another disadvantage is it cannot completely eliminate the low order harmonics.

To conquer the computation difficulty, some authors have used decomposition of the five level space-vector diagram into two three-level space-vector diagrams with a phase shift to minimize ripples and simplify control [38].

Additionally, a simple space-vector selection method, which was called spacevector control method, is introduced for multilevel converter control without duty cycle computation of the adjacent three vectors.

## 2.3.4. Space Vector Control

A conceptually different control method for multilevel converters, based on the space-vector theory, has been introduced, which is called space vector control (SVC) [25].

(c)

Figure 2.17: Space vector diagram (a) three-level; (b) five-level; (c) seven-level

The control strategy works with low switching frequencies but does not generate the mean value of the desired load voltage in every switching interval, which is the principle of space-vector PWM method. Figure. 2.18 shows the 311 different space vectors generated by a 21-level converter. The reference load voltage vector is also included in this figure. The key idea in SVC is to deliver to the load a voltage vector that minimizes the space error or distance to the reference vector. The high density of vectors produced by the 11-level converter will generate only small errors in relation to the reference vector; it is, therefore, unnecessary to use a more complex modulation method involving the three vectors adjacent to the reference. The hexagon of Figure 2.18 is the boundary of highest proximity, when the reference voltage is located in this area, the vector can be selected. Then the vector that has the greatest proximity to the reference is chosen. This method is simple and attractive for high number of levels. The advantages of SVC are the computation is very easy and the switching frequency is very low, near the fundamental switching frequency. But the disadvantage is as the number of levels decreases, the error in terms of the generated vectors with respect to the reference will be higher [13].

Figure 2.18: 21-level space vectors

#### 2.3.5. Selective Harmonic Elimination

The popular selective harmonic elimination method is also called fundamental switching frequency method which is based on the harmonic elimination theory developed by Patel *et al* [28][29]. As shown in Figure. 2.7, a multilevel converter can produce a quarter-wave symmetric stepped voltage waveform synthesized by several DC voltages [2].

By applying Fourier series analysis, the output voltage can be expressed as

$$V(t) = \sum_{n=1,3,5...}^{\infty} \frac{4}{n\pi} (V_1 \cos(n\theta_1) + V_2 \cos(n\theta_2) + ... + V_s \cos(n\theta_s)) \sin(n\omega t)$$

(2.2)

where s is the number of DC sources, and  $V_1$ ,  $V_2$  ...  $V_s$  are the level of DC voltages. The switching angles must satisfy the condition  $0 < \theta_1 < \theta_2 < \cdots < \theta_s < \frac{\pi}{2}$ . However, if the switching angles do not satisfy the condition, this method no longer exists. If  $V_1 = V_2 = ... = V_s$ , this is called equal DC voltages case. To minimize harmonic distortion and to achieve adjustable amplitude of the fundamental component, up to s-1 harmonic contents can be removed from the voltage waveform. In general, the most significant low-frequency harmonics are chosen for elimination by properly selecting angles among different level converters, and high-frequency harmonic components can be readily removed by using additional filter circuits. To keep the number of eliminated harmonics а constant level, all switching angles must satisfy the condition at  $0 < \theta_1 < \theta_2 < \dots < \theta_s < \frac{\pi}{2}$ , or the total harmonic distortion (THD) increases dramatically. Due to this reason, this modulation strategy basically provides a narrow range of modulation index, which is one of its disadvantages [13].

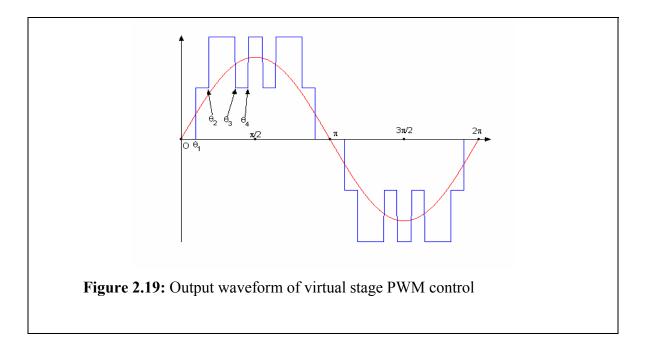

In order to achieve a wide range of modulation indexes with minimized THD for the synthesized waveforms, a generalized selective harmonic modulation method [30], [31] was proposed, which is called virtual stage PWM [14]. An output waveform is shown in Figure 2.19.

By applying Fourier series analysis, the output voltage can be expressed as

$$V(t) = \sum_{n=1,3,5...}^{\infty} \frac{4}{n\pi} (V_1 \cos(n\theta_1) \pm V_2 \cos(n\theta_2) \pm V_3 \cos(n\theta_3) \pm ... \pm V_s \cos(n\theta_s)) \sin(n\omega t)$$

(2.3)

where *s* is the number of switching angles, and  $V_1$ ,  $V_2$  ...  $V_s$  are the level of DC voltages. In this expression, the positive sign implies the rising edge, and the negative sign implies the falling edge. Similar to the fundamental switching frequency method, the switching angles must satisfy the condition  $0 < \theta_1 < \theta_2 < \cdots < \theta_s < \frac{\pi}{2}$ . However, if the switching angles do not satisfy the condition, this method no longer exists.

Therefore, the modulation control problem is converted into a mathematic problem to solve the following equations for a three-phase system. Here, m is modulation index.

$$V_{1}\cos(\theta_{1}) \pm V_{2}\cos(\theta_{2}) \pm V_{3}\cos(\theta_{3}) \pm ... \pm V_{s}\cos(\theta_{s}) = m$$

$$V_{1}\cos(5\theta_{1}) \pm V_{2}\cos(5\theta_{2}) \pm V_{3}\cos(5\theta_{3}) \pm ... \pm V_{s}\cos(5\theta_{s}) = 0$$

$$\vdots$$

$$V_{1}\cos(n\theta_{1}) \pm V_{2}\cos(n\theta_{2}) \pm V_{3}\cos(n\theta_{3}) \pm ... \pm V_{s}\cos(n\theta_{s}) = 0$$

(2.4)

The Virtual Stage PWM is a combination of Unipolar Programmed PWM and fundamental frequency switching scheme [14]. The output waveform of Unipolar Programmed PWM is shown in Figure 2.20. When Unipolar Programmed PWM is employed on a multilevel converter, typically one DC voltage is involved, where the switches connected to the DC voltage are switched "on" and "off" several times per fundamental cycle. The switching pattern decides what the output voltage waveform looks like.

When the multilevel fundamental switching method is used, all of the DC voltages are typically involved, where all of the switches are turned "on" and "off" only once per fundamental cycle. The multilevel fundamental switching method also refers to exactly one switching pattern.

For fundamental switching frequency method, the number of switching angles is equal to the number of DC sources. However, for the Virtual Stage PWM method, the number of switching angles is not equal to the number of DC voltages. For example, in Figure 2.19, only two DC voltages are used, whereas there are four switching angles.

Figure 2.20: Unipolar switching output waveform

Bipolar Programmed PWM and Unipolar Programmed PWM could be used for modulation indices too low for the applicability of the multilevel fundamental frequency switching method. Virtual Stage PWM can also be used for low modulation indices. Virtual Stage PWM will produce output waveforms with a lower THD most of the time [14]. Therefore, Virtual Stage PWM provides another alternative to Bipolar Programmed PWM and Unipolar Programmed PWM for low modulation index control.