# University of Tennessee, Knoxville TRACE: Tennessee Research and Creative Exchange

**Doctoral Dissertations**

**Graduate School**

5-2006

# Materials Integration and Device Fabrication of Active Matrix Thin Film Transistor Arrays for Intracellular Gene Delivery

Seung-lk Jun University of Tennessee - Knoxville

Follow this and additional works at: https://trace.tennessee.edu/utk\_graddiss

Part of the Engineering Commons

### **Recommended Citation**

Jun, Seung-Ik, "*Materials Integration and Device Fabrication of Active Matrix Thin Film Transistor Arrays for Intracellular Gene Delivery*." PhD diss., University of Tennessee, 2006. https://trace.tennessee.edu/utk\_graddiss/1778

This Dissertation is brought to you for free and open access by the Graduate School at TRACE: Tennessee Research and Creative Exchange. It has been accepted for inclusion in Doctoral Dissertations by an authorized administrator of TRACE: Tennessee Research and Creative Exchange. For more information, please contact trace@utk.edu.

To the Graduate Council:

I am submitting herewith a dissertation written by Seung-Ik Jun entitled "*Materials Integration* and Device Fabrication of Active Matrix Thin Film Transistor Arrays for Intracellular Gene Delivery." I have examined the final electronic copy of this dissertation for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Doctor of Philosophy, with a major in Materials Science and Engineering.

Philip D. Rack, Major Professor

We have read this dissertation and recommend its acceptance:

Michael L. Simpson, David C. Joy, Thomas T. Meek

Accepted for the Council:

Carolyn R. Hodges

Vice Provost and Dean of the Graduate School

(Original signatures are on file with official student records.)

## To the Graduate Council:

I am submitting herewith a dissertation written by <u>Seung-Ik Jun</u> entitled "*Materials Integration and Device Fabrication of Active Matrix Thin Film Transistor Arrays for Intracellular Gene Delivery.*" I have examined the final electronic copy of this dissertation for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Doctor of Philosophy, with a major in Materials Science and Engineering.

Philip D. Rack

Major Professor

We have read this dissertation and recommend its acceptance:

Michael L. Simpson

David C. Joy

Thomas T. Meek

Accepted for the Council:

Anne Mayhew

Vice Chancellor and Dean of Graduate Studies

(Original signatures are on file with official student records.)

# Materials Integration and Device Fabrication of Active Matrix Thin Film Transistor Arrays for Intracellular Gene Delivery

A Dissertation Presented for the

Doctor of Philosophy Degree

The University of Tennessee, Knoxville

Seung-Ik Jun

May 2006

## Dedication

I would like to dedicate this Doctoral dissertation to my wife, Gun-Myong, whose unending support and encouragement during the course of my graduate study. There is no doubt in my mind that without her continued support I could not have completed this process. I also want to dedicate this work to my parents and parents-in-law, Jong-Hyub Jun, Byung-Lim Min, Noh-Hwan Park, and Kwi-Nam Lee for their continuous love and support throughout my study. Dedication is also to my daughter, Erin, making me more joyful since her birth.

### Acknowledgements

I owe thanks to many people, whose assistance was indispensable in completing this study. First among them is Dr. Philip D. Rack, advisor and committee chair, for his thoroughness and deep scientific perspective in advising my work in progress. The members of my dissertation committee, Dr. Michael L. Simpson, Dr. David C. Joy, and Dr. Thomas T. Meek, have generously given their time and expertise to better my work. I am very appreciative of their contribution and their valuable support for me. I would like to thank the members of our research group in the University of Tennessee and Oak Ridge National Laboratory, Dr. Jason Fowlkes, Dr. Steven Randolph, Dr. Yuepeng Deng, Daryl Smith, Ryan Rucker, Jung-Won Park, Timothy McKnight, Dr. Anatoli Melechko, Kate Klein, Dr. Laura Edwards, Dale Hensley, Darrell Thomas, and Richard Kasica for whose help and support I am greatly appreciative. Without their efforts, this work would not be possible. Finally, I am especially grateful for the support and guidance from my undergraduate and graduate advisors in Korea, Dr. Sung-Sik Kim and Dr. Duck-Kyun Choi.

### Abstract

Materials and process integration of a thin film transistor array for intra/extracellular probing are described in this study. A combinatorial rf magnetron sputter deposition technique was employed to investigate the electrical characteristics and micro-structural properties of molybdenum tungsten (MoW) high temperature electrodes as a function of the binary composition. In addition to the composition, the effect of substrate bias and temperature was investigated. The electrical resistivity of MoW samples deposited at room temperature with zero bias followed the typical Nordheim's rule as a function of composition. The resistivity of samples deposited with substrate bias is uniformly lower and obeyed the rule of mixtures as a function of composition. The metastable  $\beta$ -W phase was not observed in the biased films even when deposited at room temperature. High resolution scanning electron microscopy revealed a more dense structure for the biased films, which correlated to the significantly lower film resistivity.

In order to overcome deficiencies in sputtered silicon dioxide (SiO<sub>2</sub>) films the rf magnetron sputtering process was optimized by using a full factorial design of experiment (DOE). The optimized SiO<sub>2</sub> film has a 5.7 MV/cm breakdown field and a 6.2 nm/min deposition rate at 10 W/cm<sup>2</sup> RF power, 3 mTorr pressure, 300 °C substrate temperature, and 56 V substrate bias. Thin film transistors (TFTs) were also fabricated and characterized to show the prospective applications of the optimized SiO<sub>2</sub> films.

The effect that direct current (DC) substrate bias has on radio frequency (RF)sputter-deposited amorphous silicon (a-Si) films was also investigated. The substrate bias produces a denser a-Si film with fewer defects compared to unbiased films. The reduced number of defects results in a higher resistivity because defect-mediated conduction paths are reduced. Thin film transistors (TFT) that were completely sputter-deposited were fabricated and characterized. The TFT with the biased a-Si film showed lower leakage (off-state) current, higher on/off current ratio, and higher transconductance (field effect mobility) than the TFT with the unbiased a-Si film.

The crystallization properties of amorphous silicon (a-Si) thin film deposited by rf magnetron sputter deposition with substrate bias have been thoroughly characterized. The crystallization speed can be increased and the crystallization temperature can be drastically lowered relative to unbiased a-Si even though the stress state of biased a-Si film is highly compressive. The substrate bias enhances defect formation (vacancies, dislocations, stacking faults) via ion bombardment during the film growth, which effectively increases the driving force for crystallization of the films.

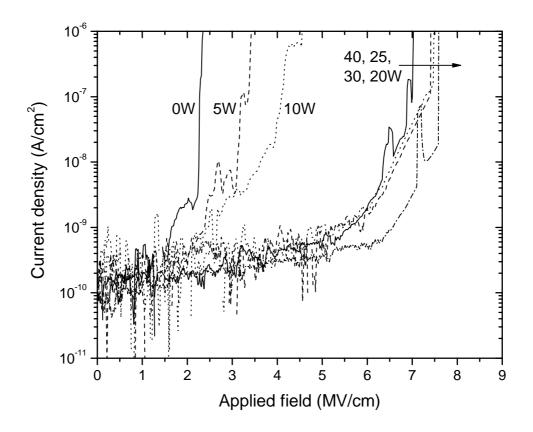

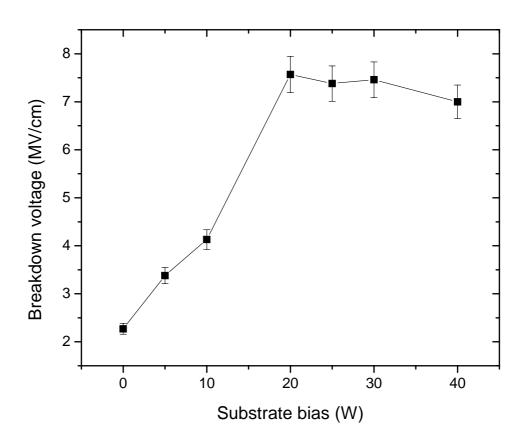

The electrical and optical properties of sputter-deposited silicon nitride  $(SiN_x)$  and  $n^+$  amorphous silicon  $(n^+ a-Si)$  films as a function of substrate bias during sputter deposition were investigated. The breakdown voltage of sputter-deposited SiN<sub>x</sub> with 20 W (125 V) substrate bias is 7.65 MV/cm which is equivalent to that of plasma enhanced chemical vapor deposition (PECVD) SiN<sub>x</sub> films. The conductivity of  $n^+$  a-Si films are also enhanced by applying substrate bias during the sputter deposition. To verify the effect of substrate bias, amorphous silicon thin film transistors (TFTs) were fabricated with substrate biased thin films and compared their electrical properties with conventional sputter deposited TFTs.

Lastly, electrochemical measurements were analyzed using gold and pyrrole solution to verify the active addressability of the TFT array fabricated by entirely by sputter deposited thin films below 200 °C temperature.

# **Table of Contents**

| Chap | ter 1 Introduction                                              | 1  |

|------|-----------------------------------------------------------------|----|

| 1.1  | Microelectrode array (MEA) for extra/intracellular cell probing | 1  |

| 1.2  | Active matrix addressing and Thin film transistor (TFT)         | 7  |

| 1.3  | Vertically aligned carbon nanofibers (VACNFs)                   | 14 |

| Chap | Chapter 2 Materials integration issues for the active matrix thin film transistor |        |  |

|------|-----------------------------------------------------------------------------------|--------|--|

|      | array of intracellular probes                                                     | 28     |  |

| 2.1  | Gate electrode, molybdenum-tungsten (MoW)                                         | 28     |  |

| 2.2  | Gate dielectric (I); silicon oxide (SiO <sub>2</sub> )                            | 49     |  |

| 2.3  | Gate dielectric (II); silicon nitride (SiN <sub>x</sub> )                         | 63     |  |

| 2.4  | Semiconductor (I); hydrogenated intrinsic amorphous silicon (a-Si:H)              | 72     |  |

| 2.5  | Semiconductor (II); extrinsic amorphous silicon ( $n^+$ a-Si) for S/D ohmic co    | ontact |  |

|      |                                                                                   | 79     |  |

| 2.6  | Low temperature crystallization of sputter deposited a-Si films                   | 84     |  |

|      |                                                                                   |        |  |

| Chap | oter 3 Device processing issues                                                   | 98     |  |

| 3.1  | Design of photolithographic masks                                                 | 98     |  |

| 3.2  | TFT device processing                                                             | 104    |  |

| 3.3  | TFT-VACNF processing for Intracellular probe                                      | 146    |  |

| Chap  | ter 4 Electrical characterization of thin film transistors 1                     | .54     |

|-------|----------------------------------------------------------------------------------|---------|

| 4.1   | Definitions and thin film transistor operation 1.                                | .54     |

| 4.2   | Thin film transistor fabrication and parameter extraction1.                      | 56      |

| 4.3   | Electrical property characterization of thin film transistor fabricated with sub | bstrate |

|       | biased sputter deposition 1                                                      | 63      |

|       |                                                                                  |         |

| Chap  | ter 5 Electrochemical analysis 1'                                                | .77     |

| 5.1   | Electrochemistry analysis with TFT-VACNF using gold and pyrrole solution         | n       |

|       | 1                                                                                | 77      |

| 5.2   | Electrochemical analysis of TFT array with fully active addressed scheme 1       | 84      |

|       |                                                                                  |         |

| Chap  | ter 6 Conclusions 1                                                              | .97     |

|       |                                                                                  |         |

| Refer | ences 20                                                                         | 200     |

|       |                                                                                  |         |

| Appe  | ndixRun sheet for TFT-VACNF processing2                                          | 213     |

|       |                                                                                  |         |

| Vita  | 2:                                                                               | 221     |

# List of Tables

| Table 2-1. | Representative gate electrode materials for fabrication of TFTs.    | 29         |

|------------|---------------------------------------------------------------------|------------|

| Table 2-2. | Experiment conditions for the MoW work.                             | 34         |

| Table 2-3. | Result summary of the 2 <sup>nd</sup> experimental series.          | 45         |

| Table 2-4. | Experimental conditions of variable factors and quantitative result | lts of the |

|            | responses for the sputtered silicon dioxide insulator study.        | 55         |

| Table 2-5. | Optimized process conditions of individual and mixed factors.       | 59         |

| Table 3-1. | Major factors effecting on TFT characteristics.                     | 141        |

# List of Figures

| FIG. 1 <b>-</b> 1.  | Micrograph of a microelectrode array (MEA).                        | 2         |

|---------------------|--------------------------------------------------------------------|-----------|

| FIG. 1 <b>-</b> 2.  | Principle of light-addressed sub-µm contacting of excitable cells. | 6         |

| FIG. 1-3.           | Active matrix addressing scheme and one example of applications.   | 8         |

| FIG. 1-4.           | Various cross-sectional structures of TFT.                         | 10        |

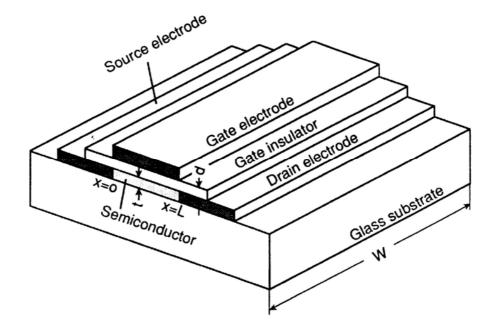

| FIG. 1-5.           | The coplanar TFT structure used for electrical characterization.   | 12        |

| FIG. 1-6.           | Typical operating scheme of a-Si TFT.                              | 15        |

| FIG. 1 <b>-</b> 7.  | Schematic diagrams of carbon nanofiber and nanotube.               | 16        |

| FIG. 1-8.           | STEM image of a carbon nanofiber grown by DC C-PECVD.              | 17        |

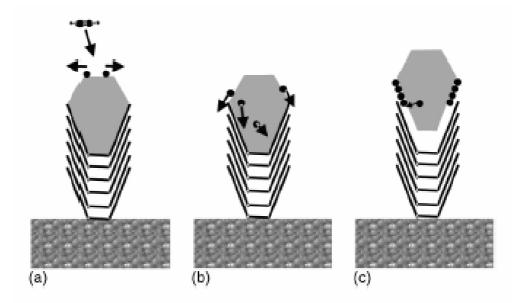

| FIG. 1 <b>-</b> 9.  | Growth mechanism of carbon nanofiber.                              | 20        |

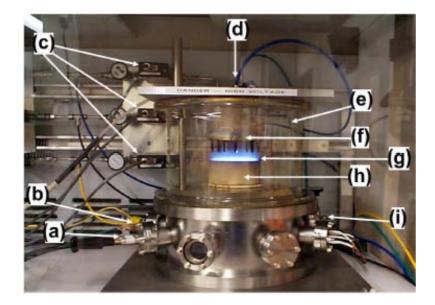

| FIG. 1-10.          | DC-PECVD reactor for the growth of VACNFs.                         | 23        |

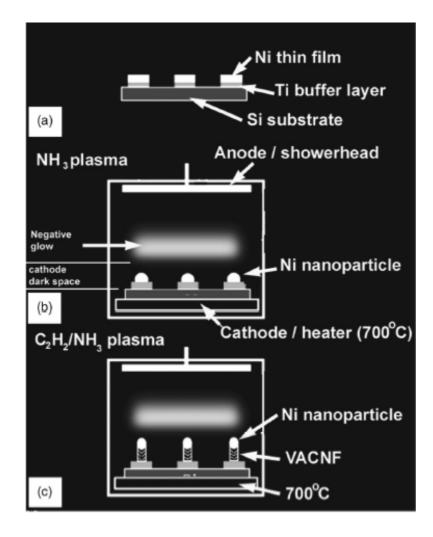

| FIG. 1 <b>-</b> 11. | Schematic representation of the PECVD process for growing VAC      | NFs.      |

|                     |                                                                    | 25        |

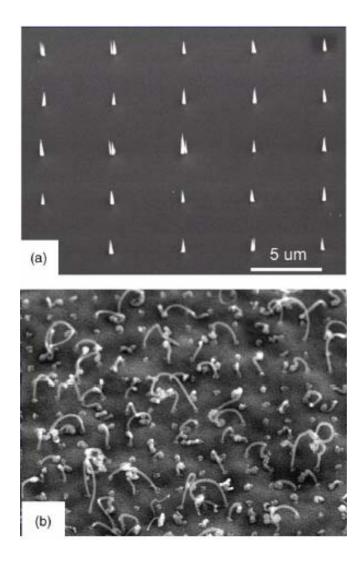

| FIG. 1-12.          | SEM images of two types of carbon nanofibers.                      | 26        |

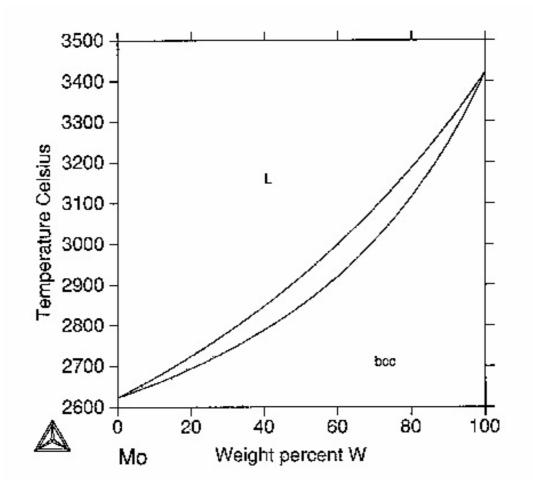

| FIG. 2-1.           | Equilibrium phase diagram of Mo-W binary system.                   | 32        |

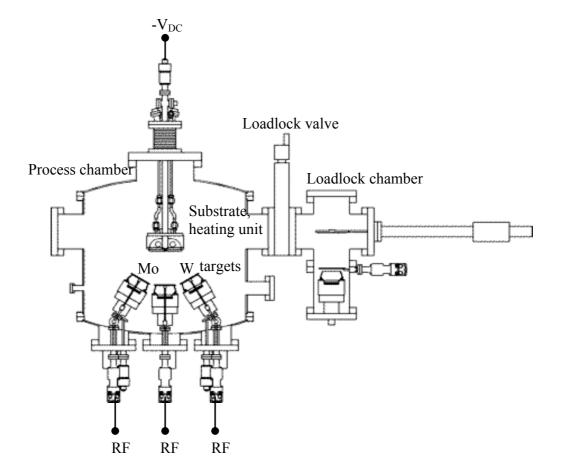

| FIG. 2-2.           | Schematic diagram of an AJA ATC2000 RF magnetron sputtering        | g system  |

|                     | equipped with DC bias supply.                                      | 33        |

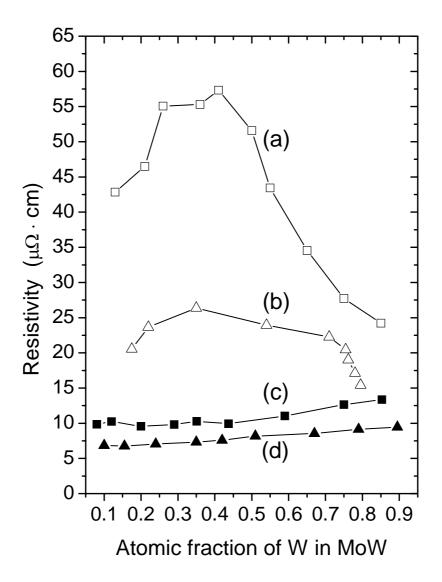

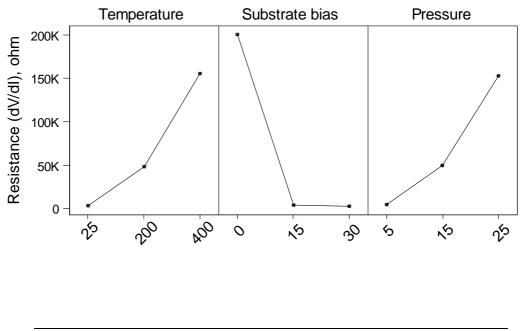

| FIG. 2-3.           | Electrical resistivity of MoW as a function of composition, temp   | oerature, |

|                     | applied bias, and process pressure.                                | 36        |

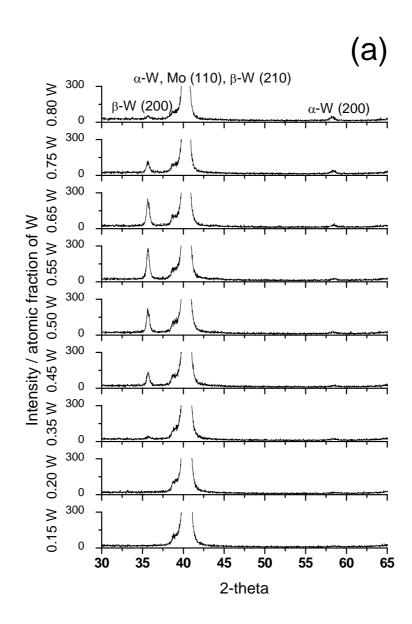

| FIG. 2-4.           | XRD results of MoW as a function of W atomic fraction.             | 39        |

| FIG. 2 <b>-</b> 5. | The relationship between $\beta$ -W fraction and electrical properties of | of MoW |

|--------------------|---------------------------------------------------------------------------|--------|

|                    | as a function of composition.                                             | 41     |

- FIG. 2-6. SEM images of MoW surface morphology as a function of the W atomic fraction in MoW thin films for samples deposited at room temperature with and without substrate bias. 44

- FIG. 2-7. Dry etching profile of MoW (0.35 atomic fraction of W) just before reaching the end point. 48

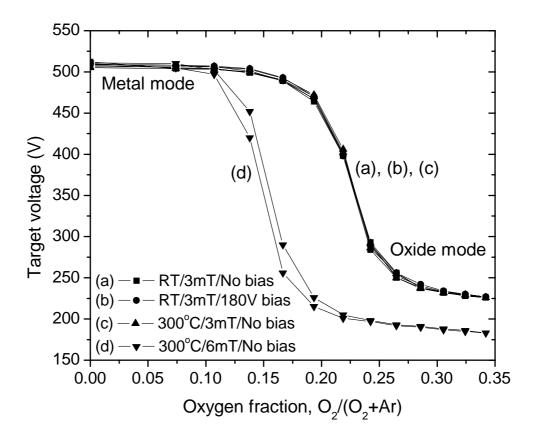

- FIG. 2-8. Hysteresis of magnetron target voltage for a silicon target sputtered in  $Ar/O_2$  mixed gas as a function of oxygen fraction. 53

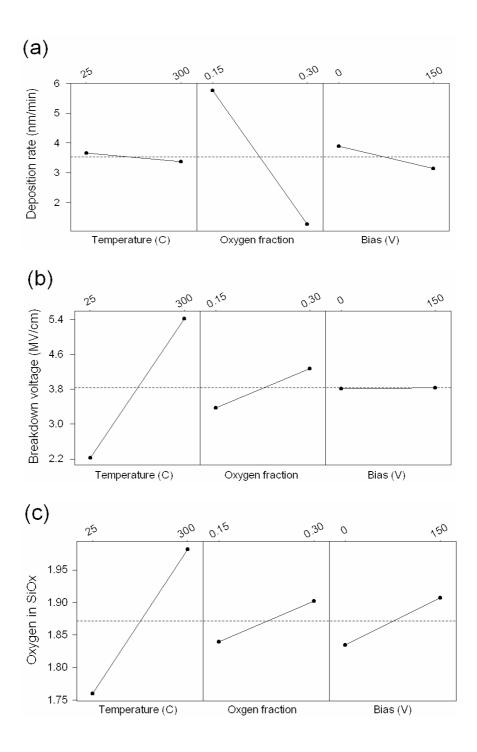

- FIG. 2-9. Graphical expression of results from statistical design of experiments.

```

56

```

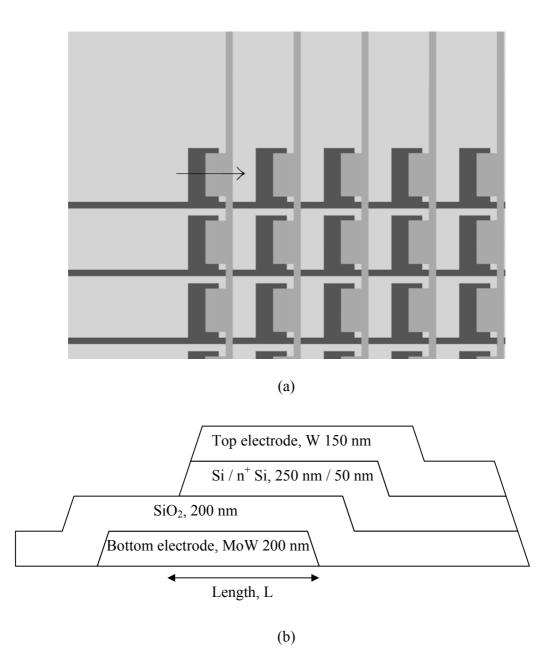

- FIG. 2-10. Device design for fabricating MIS switching device with  $20 \times 20$  row and column electrodes. 60

- FIG. 2-11. Current-voltage transfer characteristics of MIS switching devices fabricated by sputtered silicon oxide, intrinsic silicon, and  $n^+$  silicon.

62

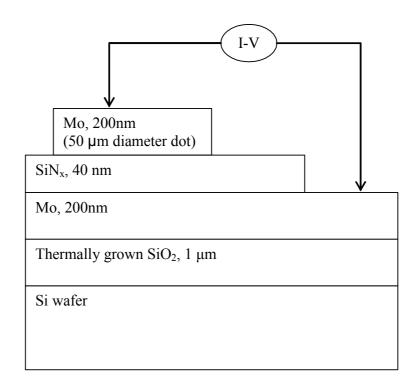

- FIG. 2-12. Schematic diagram of sample preparation for current density and breakdown measurement. 66

- FIG. 2-13. Current densities versus applied field of sputtered  $SiN_x$  thin films as a function of DC substrate bias. 67

- FIG. 2-14. The changes in breakdown field and deposition rate of sputtered  $SiN_x$  thin films as a function of substrate bias. 68

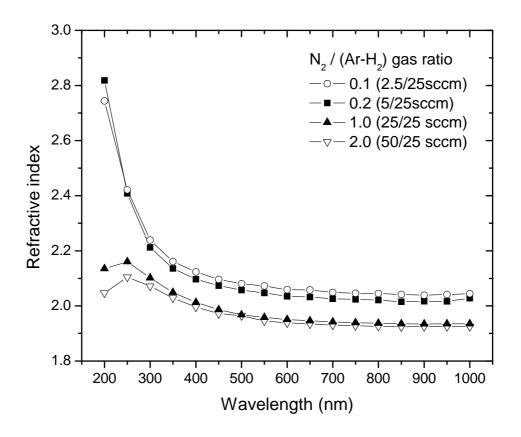

- FIG. 2-15. The change in refractive index of sputter-deposited  $SiN_x$  films as a function of the  $N_2 / (Ar-H_2)$  sputtering gas ratio. 70

- FIG. 2-16. Deposition rate and refractive index of sputter-deposited  $SiN_x$  films as a function of DC substrate bias during the sputter deposition. 71

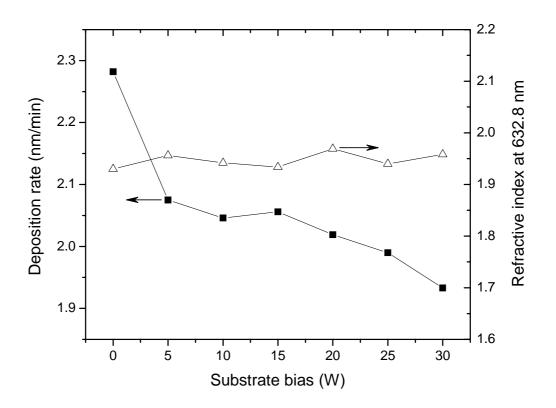

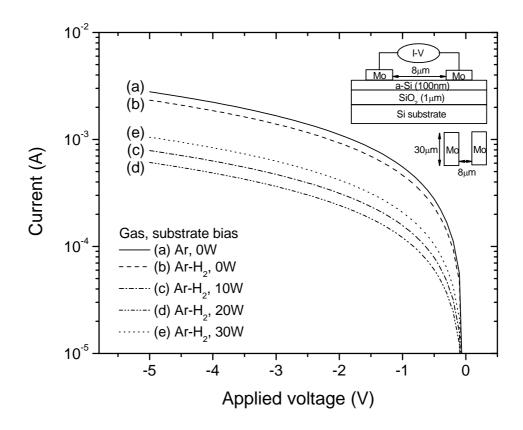

- FIG. 2-17. Current-voltage characteristics of sputtered a-Si thin films in Ar (zero bias) and Ar-H<sub>2</sub> as a function of DC substrate bias during sputter deposition.

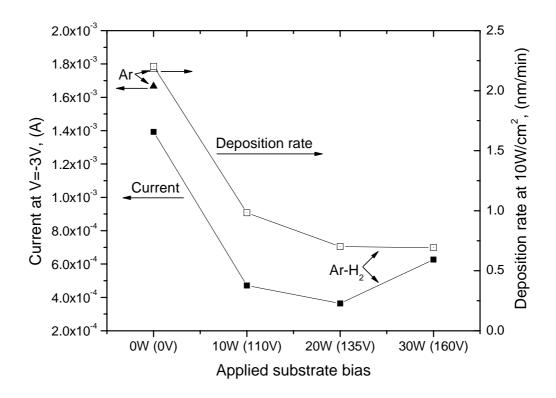

75

- FIG. 2-18. Current (at -3V) and deposition rate changes as a function substrate bias for films sputter-deposited in Ar-H<sub>2</sub>. 77

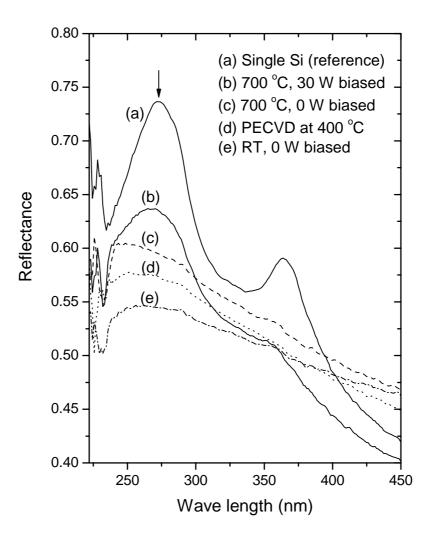

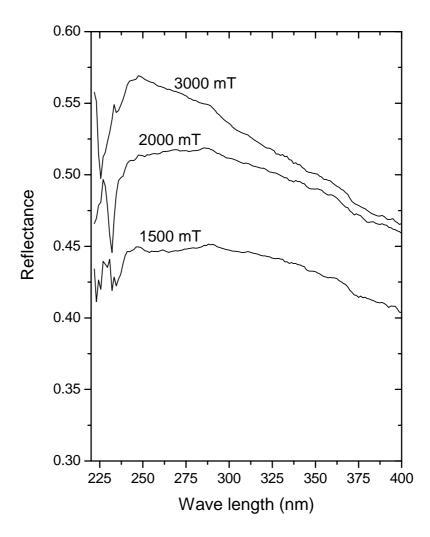

- FIG. 2-19.UV reflectance spectra of Si films deposited by unbiased and biasedsputter deposition at high temperature (700 °C).78

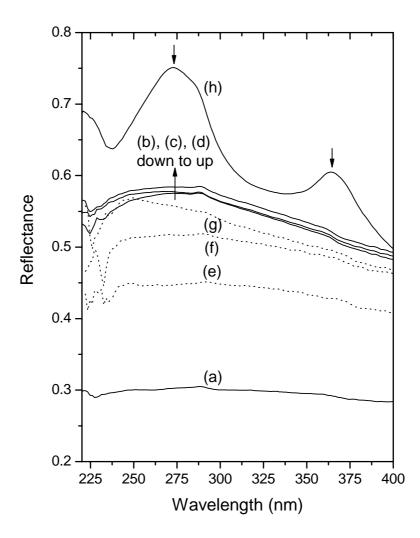

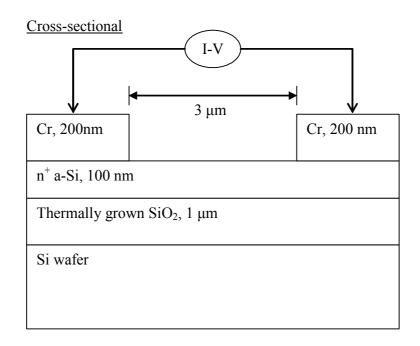

- FIG. 2-20. UV reflectance spectra of sputter and PECVD deposited n<sup>+</sup> a-Si; 0W, 15W, 30W, 45W substrate biased sputter films. 80

- FIG. 2-21. Schematic diagram of sample preparation for resistance measurements of  $n^+$  a-Si thin films. 82

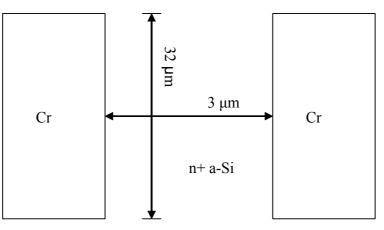

- FIG. 2-22. The changes in reflectance and resistance of sputtered  $n^+$  a-Si thin films as a function of substrate bias. 83

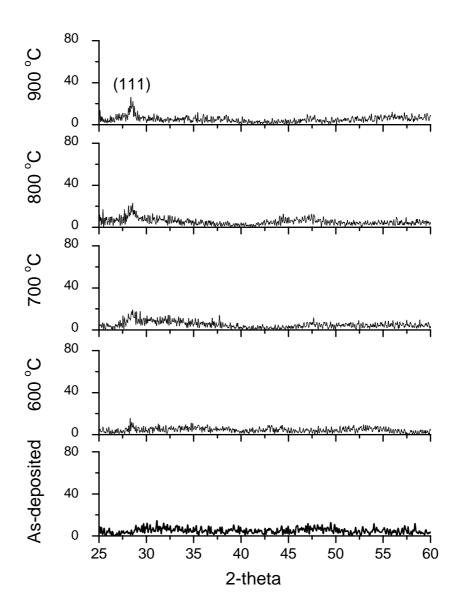

FIG. 2-23. XRD spectra of annealed Si films deposited by unbiased sputter deposition.

89

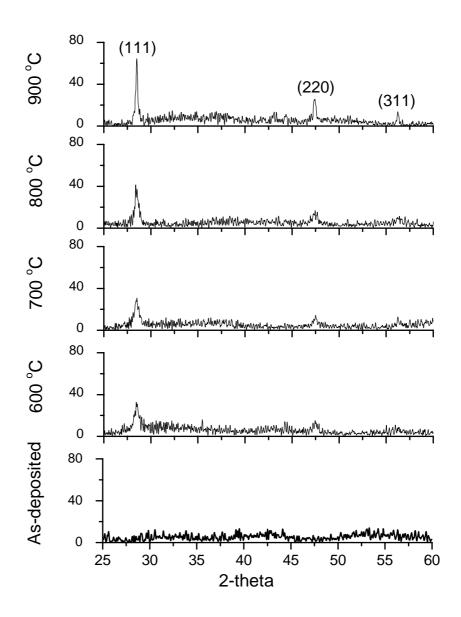

FIG. 2-24.XRD spectra of annealed Si films deposited by 30 W (215 V) biasedsputter deposition.90

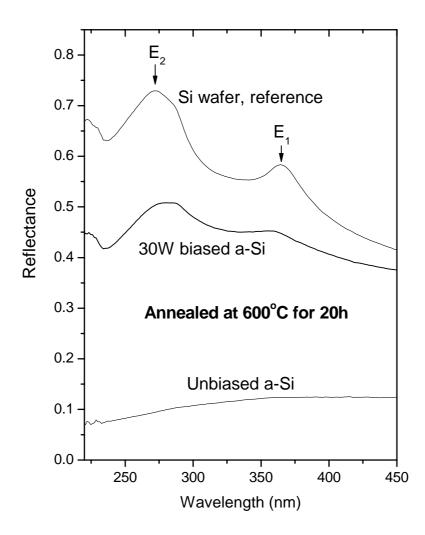

| FIG. 2-25.        | UV reflectance spectra of annealed Si films deposited by unb   | iased and  |

|-------------------|----------------------------------------------------------------|------------|

|                   | biased sputter deposition.                                     | 91         |

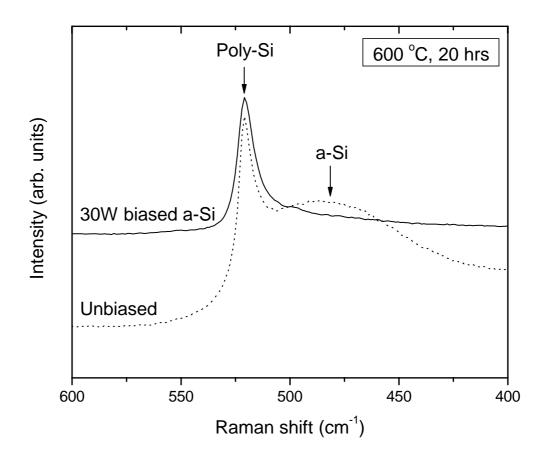

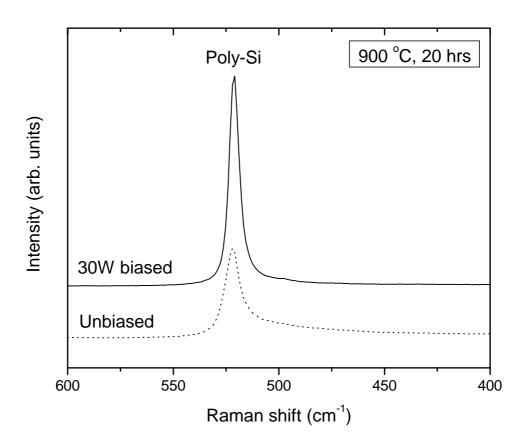

| FIG. 2-26.        | Raman spectra of annealed Si films deposited by unbiased an    | nd biased  |

|                   | sputter deposition.                                            | 93         |

| FIG. 2-27.        | Raman spectra of annealed Si films deposited by unbiased an    | nd biased  |

|                   | sputter deposition.                                            | 94         |

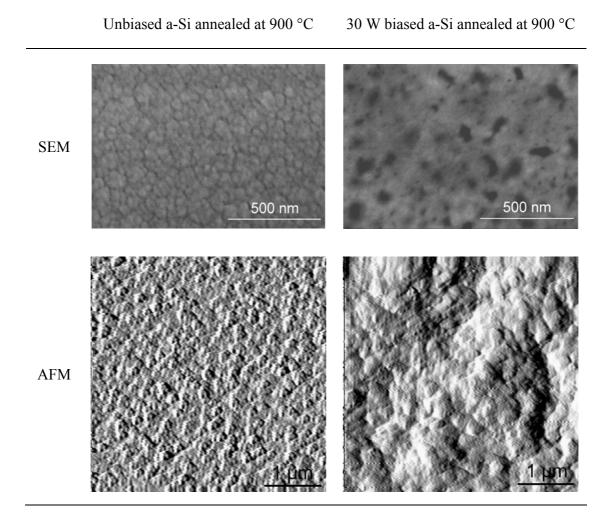

| FIG. 2-28.        | Surface morphology of annealed Si films taken by SEM and AFM   | <i>I</i> . |

|                   |                                                                | 95         |

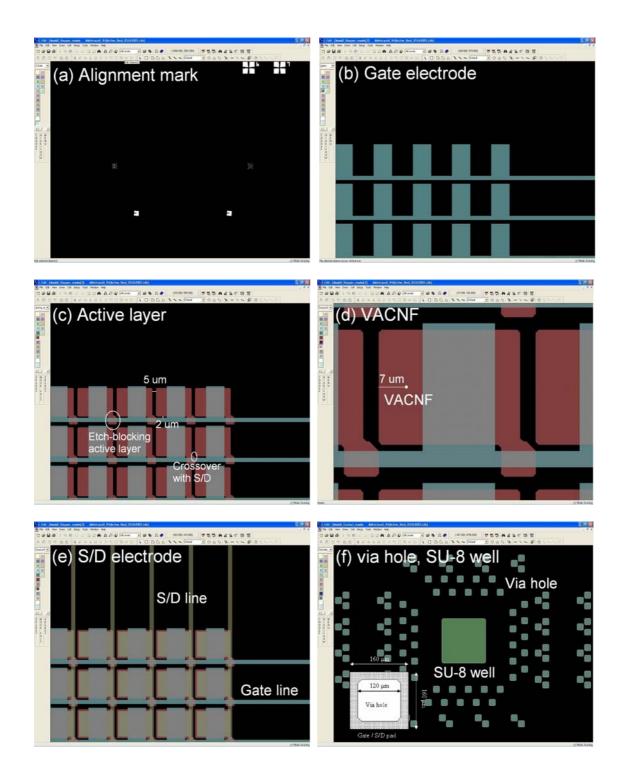

| FIG. 3-1.         | Mask design for TFT-VACNF designed by Tanner L-Edit softwa     | re.        |

|                   |                                                                | 99         |

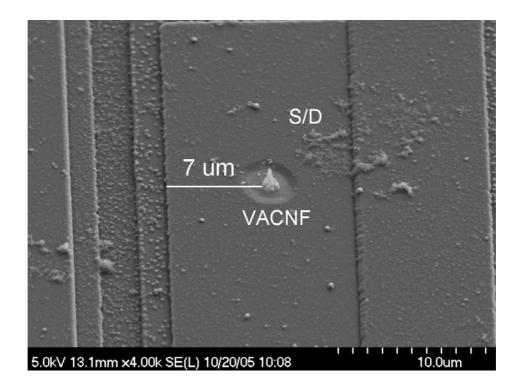

| FIG. 3-2.         | Distance margin between VACNF and the edge of S/D elec         | trode for  |

|                   | precise S/D patterning.                                        | 102        |

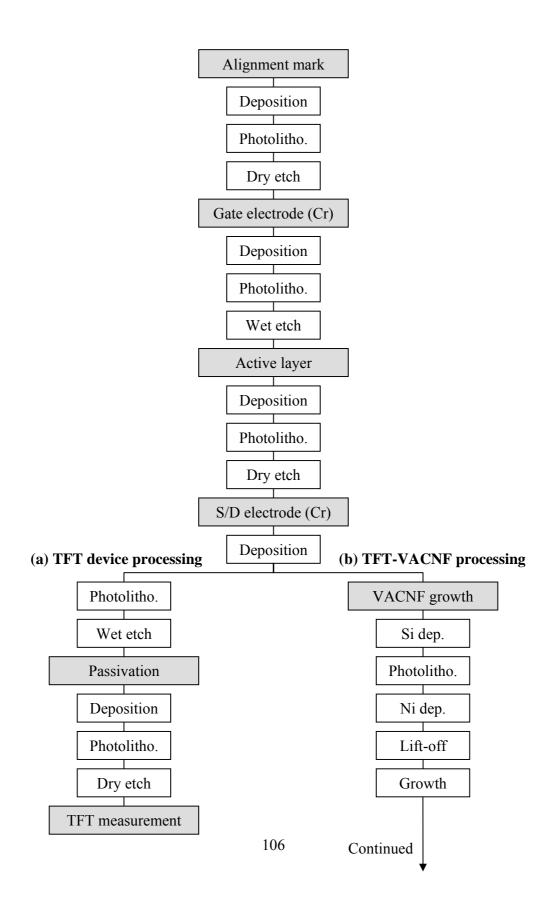

| FIG. 3-3.         | Overall process flow for TFT and TFT-VACNF.                    | 105        |

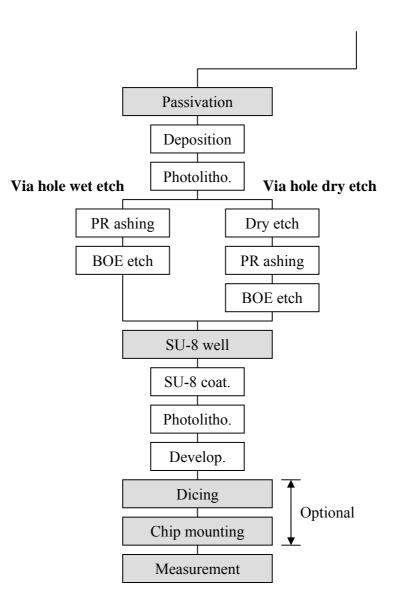

| FIG. 3-4.         | Adhesion promotion by HMDS priming.                            | 108        |

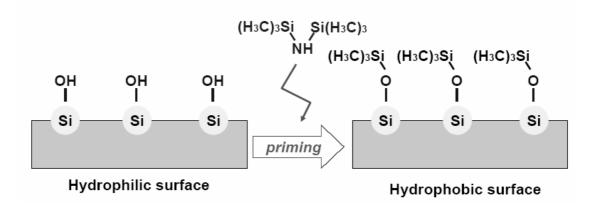

| FIG. 3-5.         | Various SEM images of tapered gate electrodes.                 | 110        |

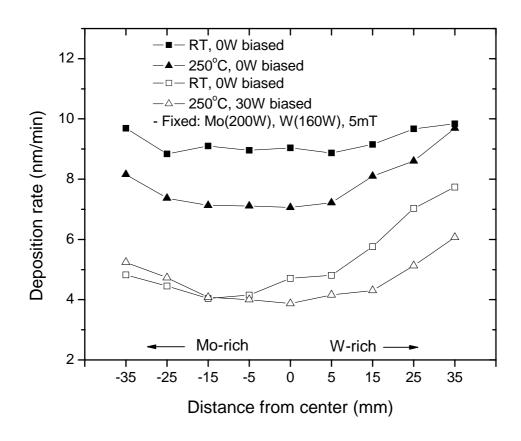

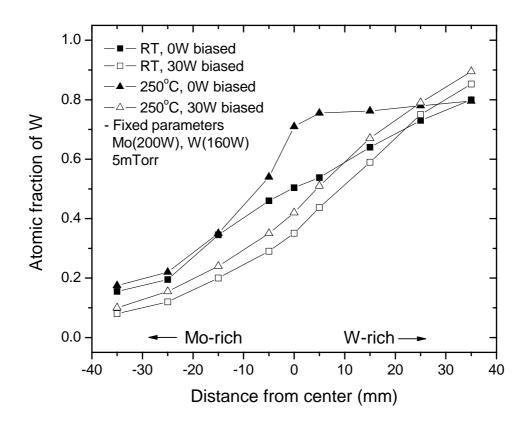

| FIG. 3-6.         | Deposition of MoW as a function of position in a wafer for com | binatorial |

|                   | analysis.                                                      | 112        |

| FIG. 3-7.         | Atomic fraction change of W with the distance from c           | enter for  |

|                   | combinatorial analysis.                                        | 113        |

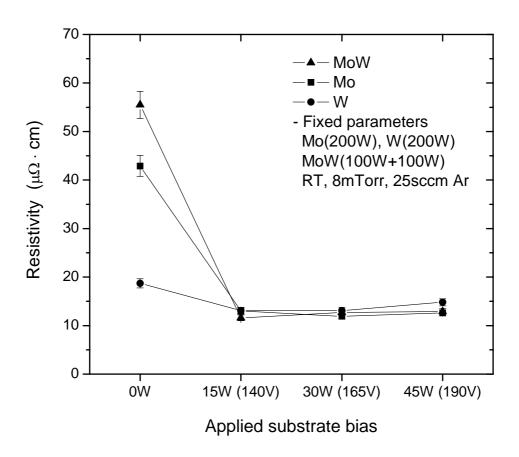

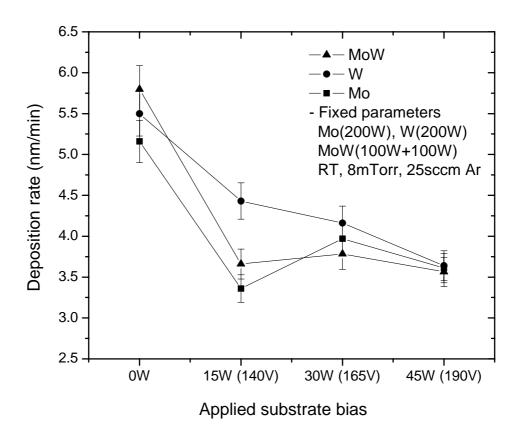

| FIG. <b>3-8</b> . | Electrical resistivity change of Mo, W, and MoW as a fu        | nction of  |

|                   | substrate bias in sputter deposition.                          | 115        |

| FIG. <b>3-9</b> . | Deposition rate change of Mo, W, and MoW as a function of                   | substrate |

|-------------------|-----------------------------------------------------------------------------|-----------|

|                   | bias in sputter deposition.                                                 | 116       |

| FIG. 3-10.        | Electrical resistivity of MoW as a function of atomic fraction              | of W in   |

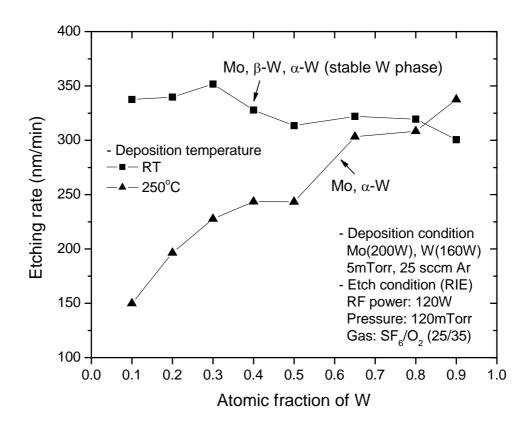

|                   | MoW films with a change of process pressure.                                | 117       |

| FIG. 3-11.        | Dry etch rate of MoW film as a function of composition in MoW               | film.     |

|                   |                                                                             | 118       |

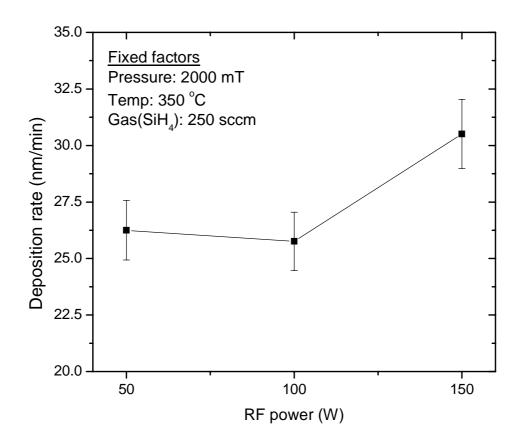

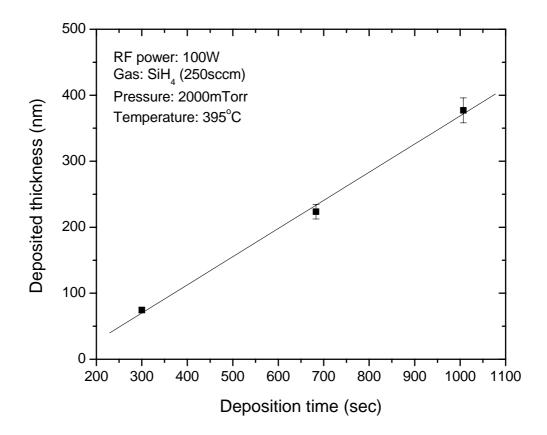

| FIG. 3-12.        | Deposition rate of PECVD a-Si as function of RF power.                      | 123       |

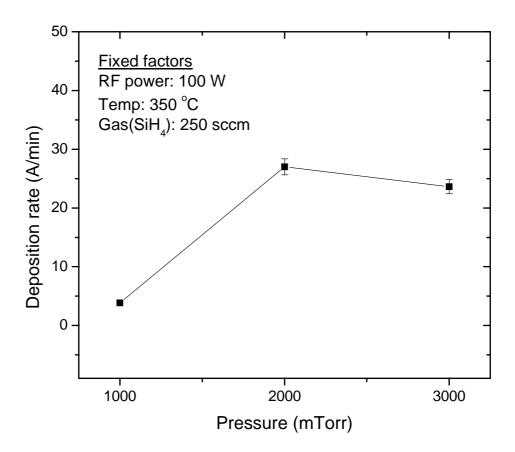

| FIG. 3-13.        | Deposition rate of PECVD a-Si as function of process pressure.              | 124       |

| FIG. 3-14.        | Reflectance spectra of a-Si deposited by PECVD as a function o              | f process |

|                   | pressure.                                                                   | 125       |

| FIG. 3-15.        | Deposited thickness of PECVD a-Si:H film as a function of d                 | eposition |

|                   | time.                                                                       | 126       |

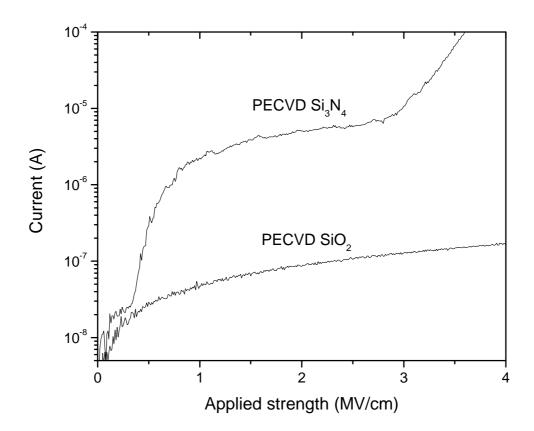

| FIG. 3-16.        | Current changes of PECVD deposited $SiN_x$ and $SiO_2$ films as a fu        | nction of |

|                   | applied strength.                                                           | 128       |

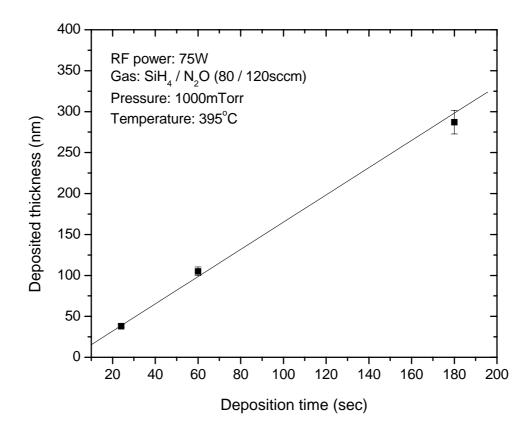

| FIG. 3-17.        | Deposited thickness of PECVD SiO <sub>2</sub> film as a function of deposit | ion time. |

|                   |                                                                             | 129       |

| FIG. 3-18.        | Deposition rate of sputter deposited $\mathrm{SiN}_{x}$ as a function of DC | substrate |

|                   | bias.                                                                       | 131       |

| FIG. 3-19.        | Deposition rate of a-Si thin film as a function of DC substrate bi          | as at two |

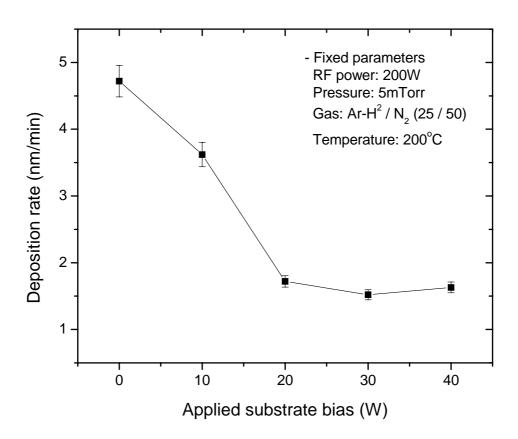

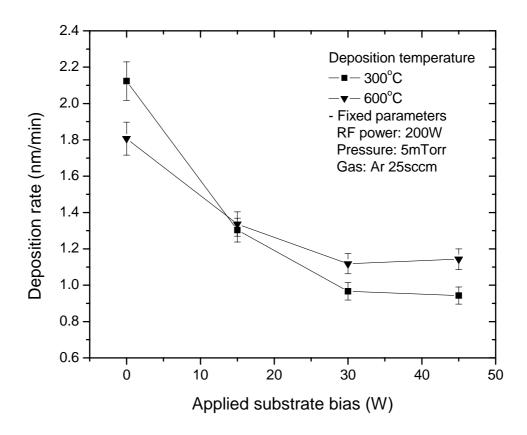

|                   | different temperatures.                                                     | 132       |

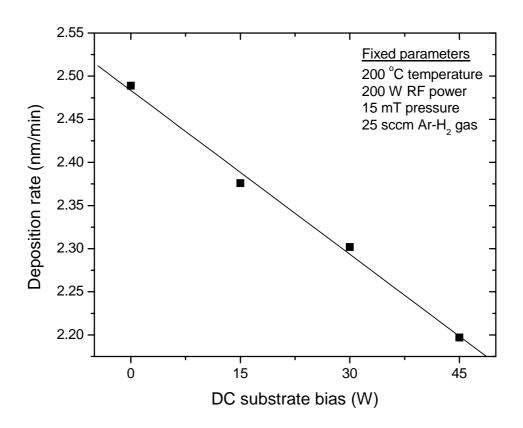

| FIG. 3-20.        | Deposition rate of $n^+$ a-Si as a function of substrate bias.              | 133       |

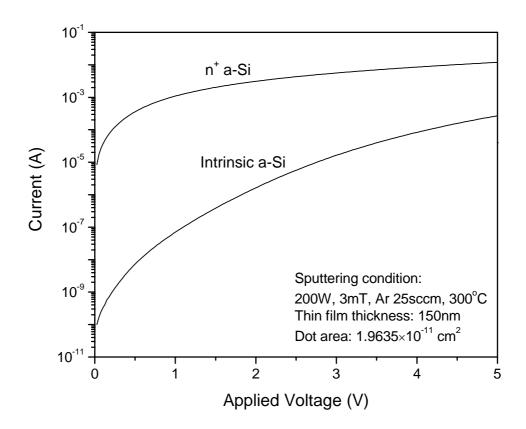

| FIG.3-21.  | Induced current of $n^+$ a-Si and intrinsic a-Si thin films as a fur-   | oction of |

|------------|-------------------------------------------------------------------------|-----------|

|            | applied voltage.                                                        | 134       |

| FIG. 3-22. | Effect of process factors on electrical resistance of $n^+$ a-Si film a | analyzed  |

|            | by statistical method.                                                  | 136       |

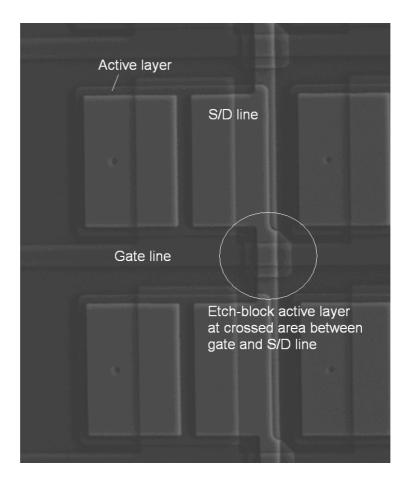

| FIG. 3-23. | Etch-block active layer at the crossed area between gate and S/D li     | ne        |

|            | (circled).                                                              | 138       |

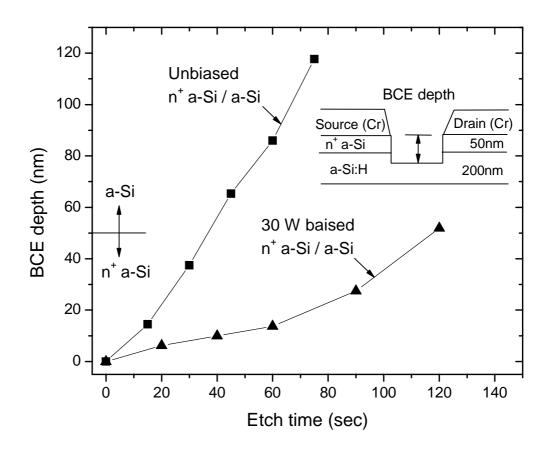

| FIG. 3-24. | Back channel etch depth of $n^+$ a-Si / a-Si deposited with/without su  | ıbstrate  |

|            | bias sputter deposition.                                                | 143       |

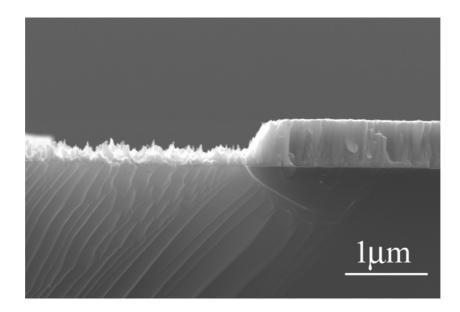

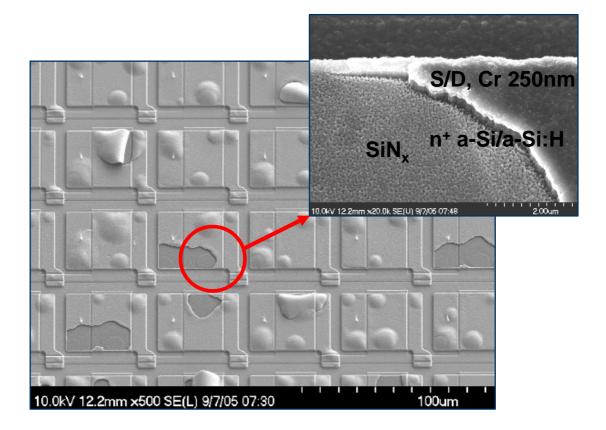

| FIG. 3-25. | SEM image of TFT-VACNF showing a device failure due to intern           | nal       |

|            | stress after VACNF growth at 550 °C.                                    | 148       |

| FIG. 3-26. | Breakdown failure is not shown after VACNF growth at low tem            | perature  |

|            | growth $\sim 550~^\circ C$ and on the unbiased $n^+$ a-Si / a-Si.       | 150       |

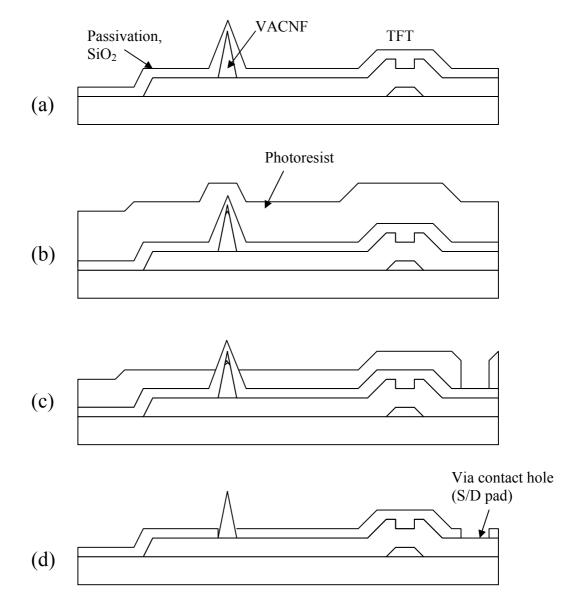

| FIG. 3-27. | Process sequence for TFT-VACNF passivation (I) for via hole             | etch and  |

|            | exposing tips of VACNF.                                                 | 151       |

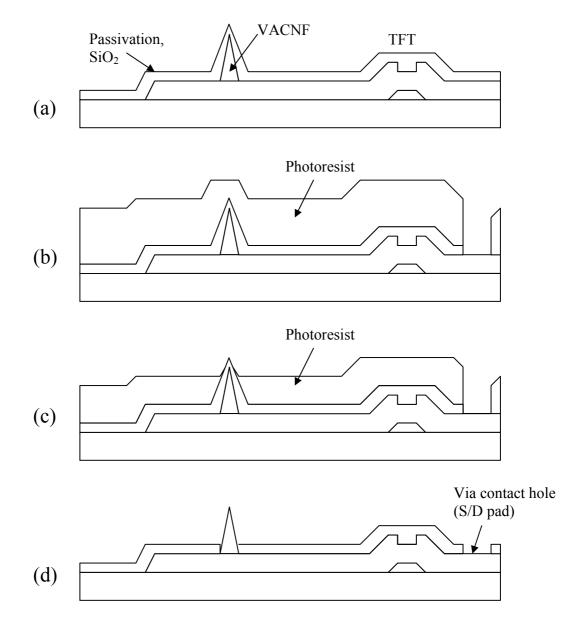

| FIG. 3-28. | Process sequence for TFT-VACNF passivation (II) for via hole            | etch and  |

|            | exposing tips of VACNF.                                                 | 152       |

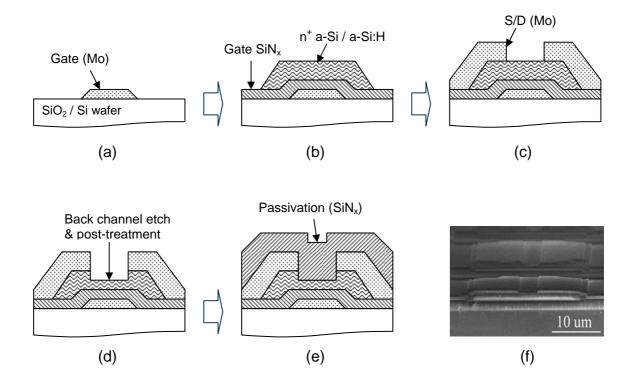

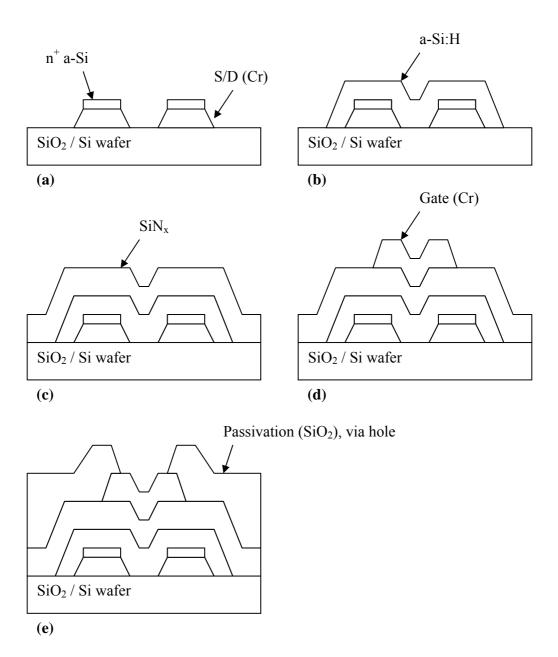

| FIG. 4-1.  | Process sequence of TFT fabrication with back channel etch struct       | ure.      |

|            |                                                                         | 157       |

| FIG. 4-2.  | Process sequence of TFT fabrication with staggered structure (top-      | gated).   |

|            |                                                                         | 160       |

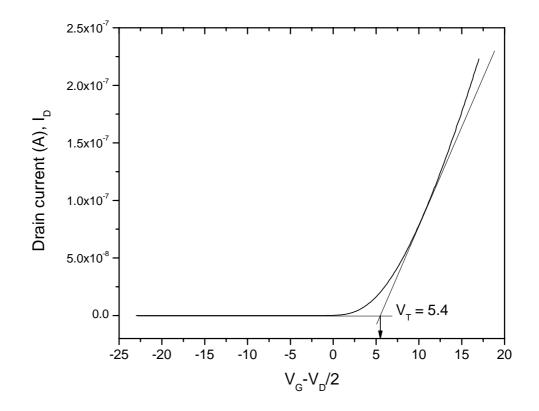

| FIG. 4-3.  | Example of illustrating the calculation of threshold voltage.           | 162       |

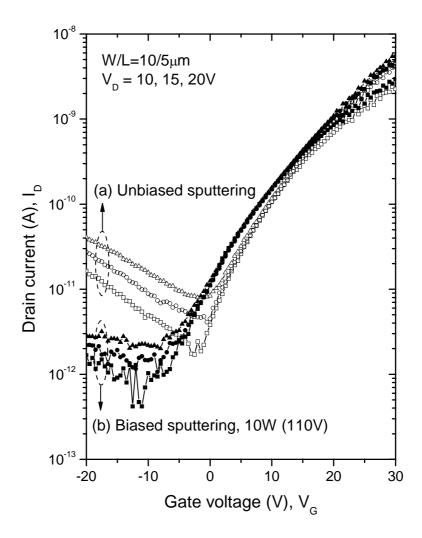

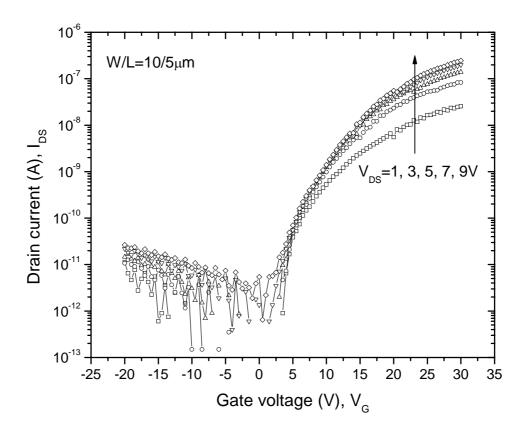

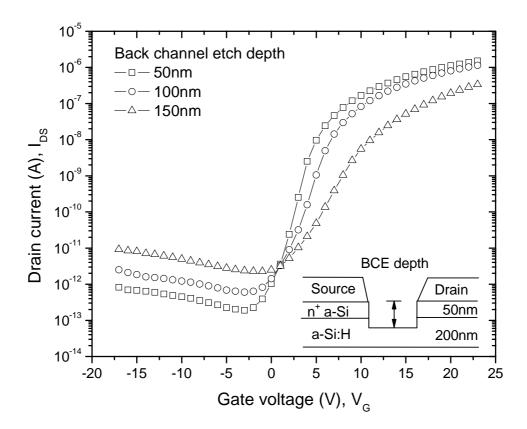

| FIG. 4-4.  | Transfer characteristics of TFTs.                                       | 165       |

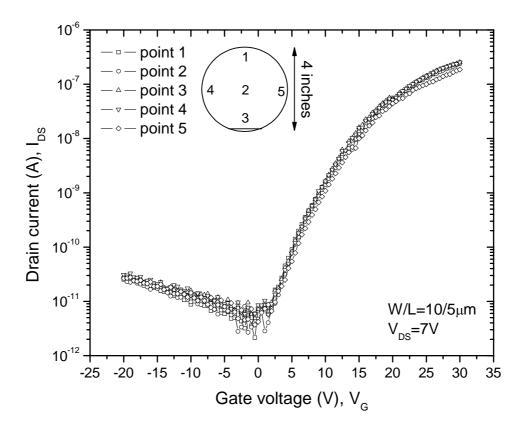

| FIG. 4-5.  | Current-voltage characteristics of TFT devices as a function of the wafer |                       |  |

|------------|---------------------------------------------------------------------------|-----------------------|--|

|            | position which illustrates the stability of the device characteristics    | . 166                 |  |

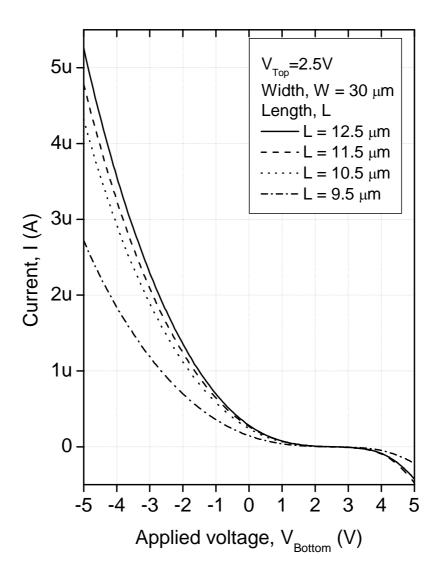

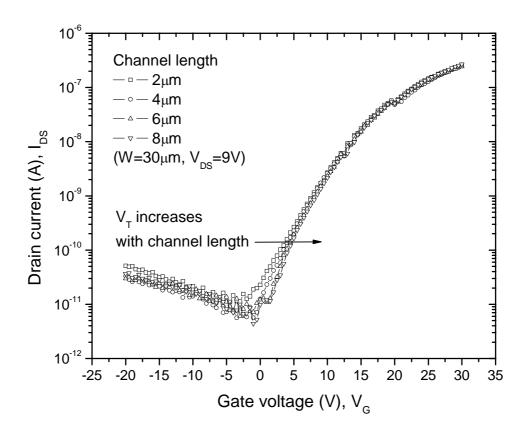

| FIG. 4-6.  | Current-voltage characteristics of a fully sputtered TFT.                 | 168                   |  |

| FIG. 4-7.  | Current-voltage characteristics of fully sputter-deposited TF             | Ts as a               |  |

|            | function of channel length.                                               | 169                   |  |

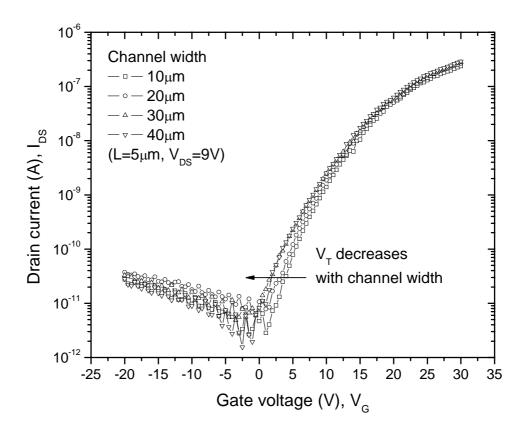

| FIG. 4-8.  | Current-voltage characteristics of fully sputter-deposited TF             | Ts as a               |  |

|            | function of channel width.                                                | 170                   |  |

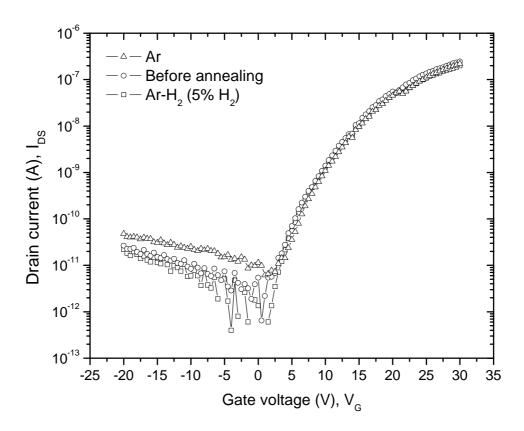

| FIG. 4-9.  | The electrical properties of fully sputter-deposited TFTs as a fu         | nction of             |  |

|            | the annealing ambient.                                                    | 171                   |  |

| FIG. 4-10. | Electrical property changes of fully sputter-deposited TFTs w             | rith back             |  |

|            | channel etch depth.                                                       | 173                   |  |

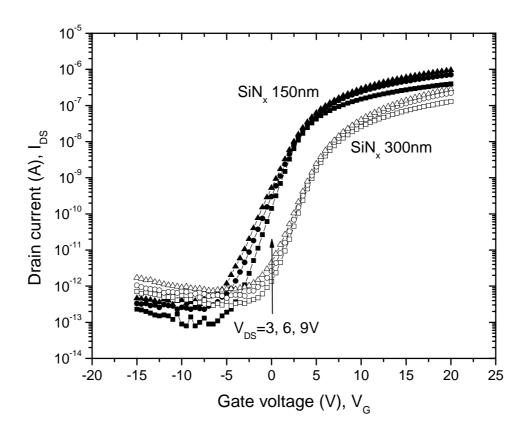

| FIG. 4-11. | Electrical property changes of fully sputter-deposited TFTs with g        | gate SiN <sub>x</sub> |  |

|            | thickness.                                                                | 176                   |  |

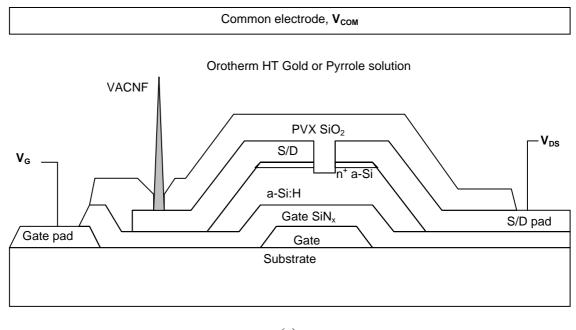

| FIG. 5-1.  | A schematic diagram of TFT-VACNF for electrochemical analysi              | S.                    |  |

|            |                                                                           | 178                   |  |

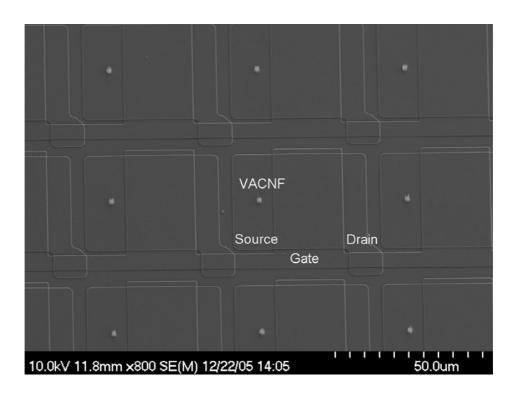

| FIG. 5-2.  | SEM images of TFT-VACNF.                                                  | 182                   |  |

| FIG. 5-3.  | Current change of common electrode as a function of applied ve            | oltage on             |  |

|            | common electrode.                                                         | 183                   |  |

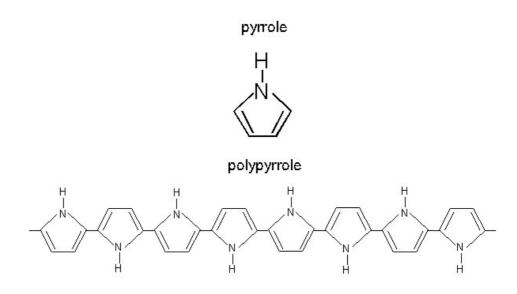

| FIG. 5-4.  | Molecules structure of unit pyrrole (monomer) and polypyrrole.            | 185                   |  |

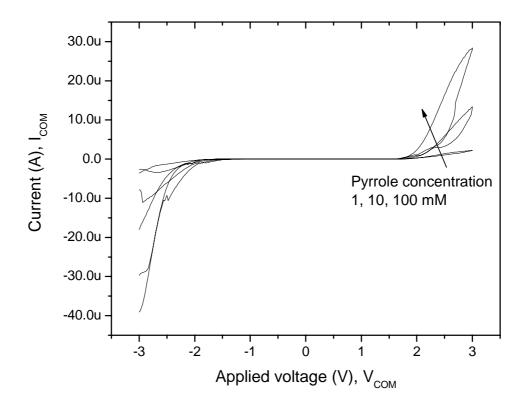

| FIG. 5-5.  | Current-voltage characteristics on common electrode as a fur              | nction of             |  |

|            | pyrrole concentration.                                                    | 186                   |  |

xvi

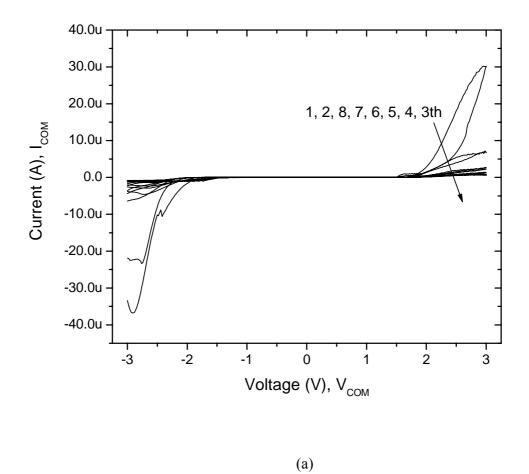

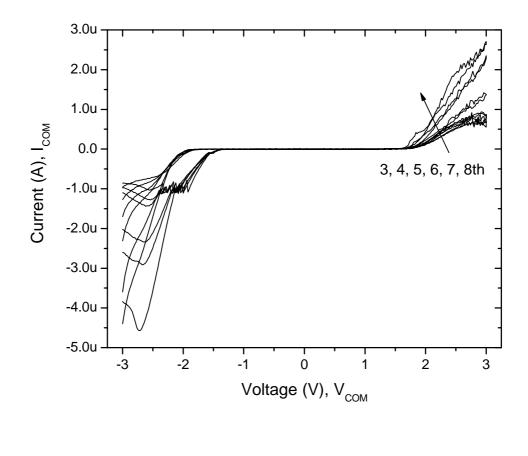

| FIG. 5-6.  | Current-voltage characteristics of pyrrole electrochemistry wi   | th cycle |

|------------|------------------------------------------------------------------|----------|

|            | analysis.                                                        | 187      |

| FIG. 5-7.  | A typical current-voltage characteristic of a-Si:H TFT.          | 190      |

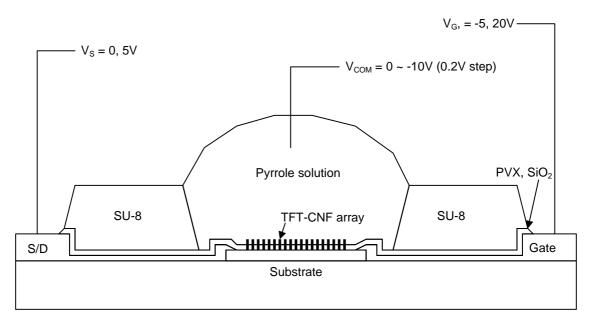

| FIG. 5-8.  | A diagram of active addressing scheme using TFT array.           | 191      |

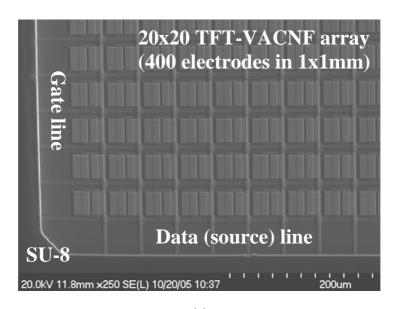

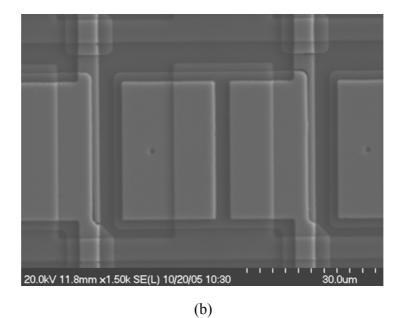

| FIG. 5-9.  | SEM images of 20×20 TFT array with via hole for electrochemistr  | y.       |

|            |                                                                  | 192      |

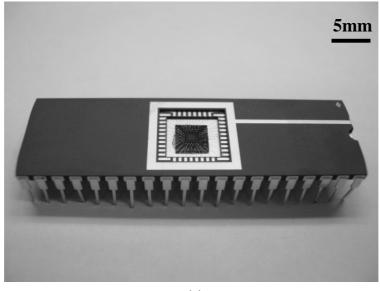

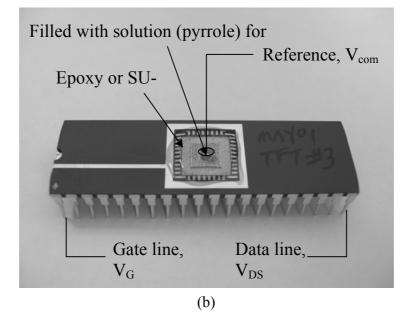

| FIG. 5-10. | 20×20 TFT array chip after dicing, wire bonding, and mounting.   | 193      |

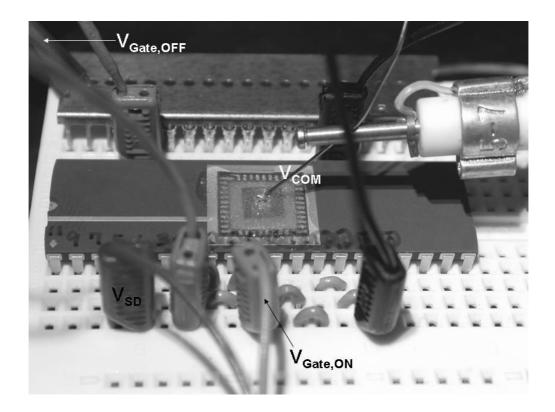

| FIG. 5-11. | A scheme picture of active addressing which is mounted or        | n multi- |

|            | functional slots.                                                | 194      |

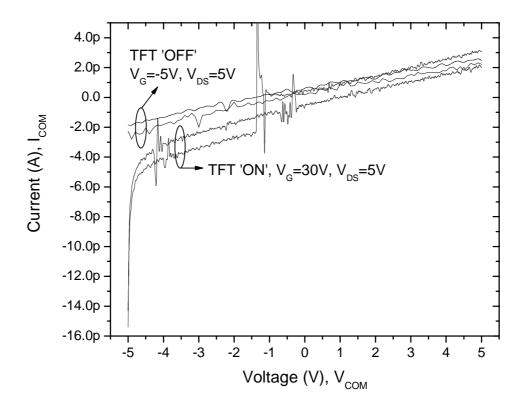

| FIG. 5-12. | Current-voltage characteristics of TFT array with gold solution. | 196      |

### **Chapter 1** Introduction

1.1 Microelectrode array (MEA) for extra/intracellular cell probing

1.1.1 Definition and application of Microelectrode arrays (MEA)

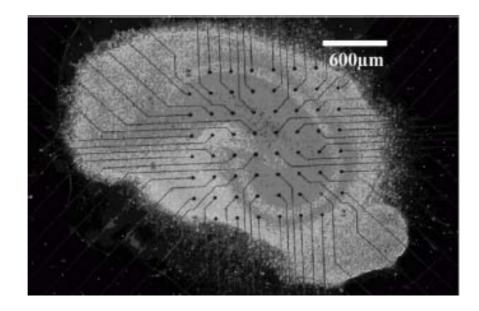

Microelectrode arrays (MEA) have been studied to investigate electrogenic cells and tissues by intra/extracellular stimulating and recording.<sup>1</sup> A microelectrode array (MEA) is an arrangement of typically more than a few tens of electrodes with  $100 \sim 500$ µm pitch allowing the probing of several sites for cell stimulation and extracellular recording at once (Fig. 1-1).<sup>1</sup> An extracellular recording system is composed of following components; signal source (cells or tissue), cell-sensor interface (biocompatible electrolyte), biosensor (MEA), filter amplifier, and recording hardware and software. In these days, the devices are fabricated by conventional semiconductor fabrication processes (thin film deposition, lithography, and wet / dry chemical etching) with a high density of electrodes.

The cell membrane is semi-permeable and is separated by different ion concentrations (charges) on the inner and outer side of the membrane. The cell membrane, therefore, has the electrical properties like a plate capacitor. The electrochemical gradient due to the concentration difference induces a membrane potential that can be measured directly by an intracellular (or extracellular) electrode. When ion channels are opened due to chemical or electrical stimulation, the resultant ions

FIG. 1-1. Micrograph of a microelectrode array (MEA). Only the cells on the electrodes can be measured and the cells lying on between the electrodes are not analyzed.

V. Bucher, B. Brunner, C. Leibrock et al., Biosensors & Bioelectronics 16 (3), 205 (2001).

are moved along the electrochemical gradient. In other words, the resistance of the membrane is lowered, resulting in an inward or outward flow of ions measured as a transmembrane current.

In the case of extracellular probing, the space between signal source (cells or tissue) and electrode is also conductive and the extracellular current results in a small voltage that can be measured with extracellular electrodes and reference electrode according to Ohm's law ( $V = I \times R$ , where V is voltage, R is resistance, and I is current). Extracellular signals are smaller than trans-membrane potentials measured by intracellular probing and the potential depends on the distance between the signal source and the extracellular electrode. Due to resistance properties of the extracellular space, the level of extracellular signal decreases with increasing distance of the signal source to the electrode. Therefore, a high spatial resolution of the electrode array corresponding to high electrode density and/or a close interface between electrode and cell membrane is a very important factor to get a high signal-to-noise (S/N) ratio.<sup>2</sup>

Over the past decades, non-invasive extracellular recording devices using multiple electrodes has been developed using standard microelectronic fabrication processes. Systems and methods have been greatly improved, leading to more features, lower costs, and higher throughput. Almost all excitable or electrogenic cells and tissues can be used for extracellular recording in vitro, for example, central or peripheral neurons, heart cells, retina, or muscle cells.<sup>3,4,5</sup>

MEAs can be used to inspect the activities of whole cells and tissues rather than simple single cell measurements and can measure the interaction of several cells in a culture or in their natural environment or even in whole organs. The rising applications of monitoring biological signals generated during nerve excitation, quantitative release of molecules, and cell-to-cell communication has stimulated the development of new methodologies and materials for novel applications of bio-applicable devices in basic science, laboratory analysis and therapeutic treatments.<sup>5</sup>

The classical methods need complex and expensive micro-processes for electrode positioning, which are limited to 2 or 3 units per recording cells and produce inevitably serious damage to the interior of cell that limits the duration of the recording and reproductivity of the recording over the same cell. Solid-state microelectrode arrays overcome many of these drawbacks and allow several of the following advantages: 1) recording electrical signals with higher fidelity signal-to-noise ratios without destroying the intracellular domain, 2) monitoring simultaneously the activity of various cells belonging to a complex network, 3) repeating periodically the recordings on the same cells over long periods of time.

However, the main drawback of the MEA is that the only cells lying on the electrodes can be measured and the cells outside of the electrodes cannot be analyzed due to the still relatively low electrode density relative to the size of the cells. In addition, cells usually do not adhere exactly on the electrodes and cell-electrode contact is often very poor in this device. As a consequence, the signal to noise ratio is not optimized and often the signal is not detected properly.

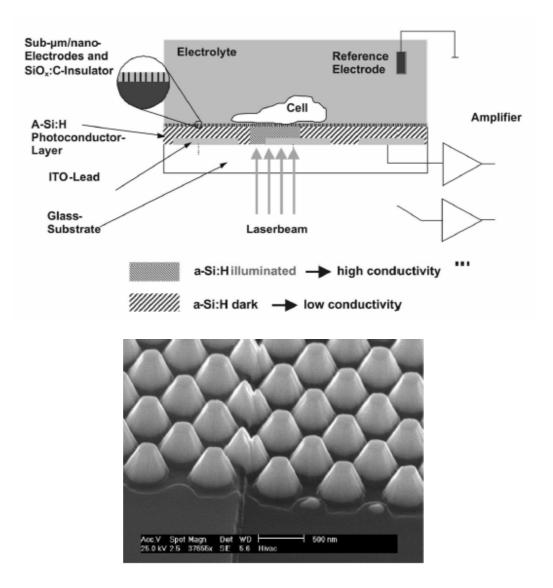

#### 1.1.2 Light-addressed extracellular probing device

To overcome the low electrode density of MEAs, V. Bucher *et al.* proposed an array of light-addressable sub-µm electrodes.<sup>6,7</sup> Each electrode, as shown in Fig. 1-2, can be addressed individually by switching a photoconductor layer by means of a focused laser beam. The array provides a great number of electrodes on a photoconductor layer (hydrogenated amorphous silicon). Each electrode in the device is operated under the illumination of laser light with 488 nm wavelength and the current can be induced to the electrode stimulating cells.

Although having higher density of electrode, it has several disadvantages due to in driving scheme. Firstly, the device needs additional equipment on the periphery to be driven due to its passive-addressed driving scheme; for instance a laser source, amplifier, addressing tools, and mounting tools.

Secondly, it is so hard to focus at a specific electrode to stimulate a cell because mechanical addressing to focus at a coordinate cannot be precisely controlled. The failure of a precise focus makes cross-talking and addressing delays a problem in the whole active area. To simplify the driving scheme while maintaining the high electrode density, we propose an active addressed microelectrode array using thin film transistors.

FIG. 1-2. Principle of light-addressed sub-µm contacting of excitable cells. Electrodes over the illuminated photoconductor are switched through.

V. Bucher, J. Brugger, D. Kern et al., Microelectronic Engineering 61-62, 971 (2002).

#### 1.2 Active matrix addressing and Thin film transistor (TFT)

### 1.2.1 Definition of passive and active matrix addressing

The passive addressing is a scheme that the charge of a unit cell (pixel) is maintained by directly applied voltage on the row and column electrodes. Even though this has a very simple driving scheme and structure, it requires high driving voltages and complex peripheral devices relative to an active addressing scheme due to its inability to maintain charge on other pixel elements that are not simultaneously addressed.

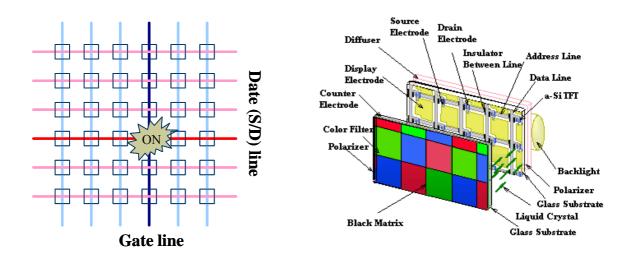

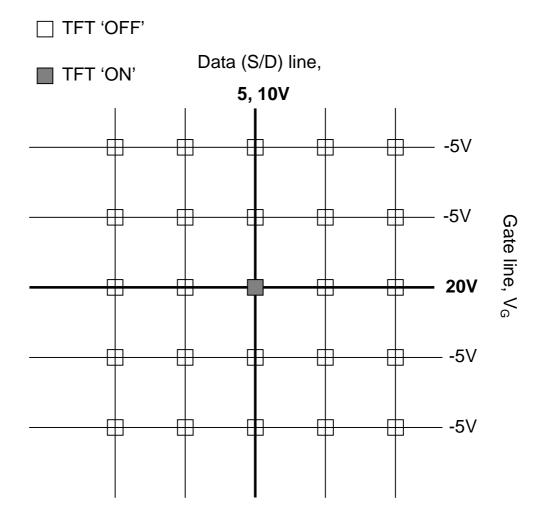

For the active matrix addressing scheme, as shown in Fig. 1-3, each unit cell is attached to a switching device (TFT, Field effect transistor or FET) which actively maintains the cell state while other cells are being addressed. This scheme also prevents crosstalk from inadvertently changing the state of an unaddressed pixel. The active addressing scheme is usually used in the fabrication of flat panel display devices such as thin film transistor-liquid crystal displays (TFT-LCD) and TFT-organic electroluminescence display (TFT-OELD).

### 1.2.2 Amorphous silicon TFT and parameter extraction

Thin film transistors (TFTs) were proposed by Weimer in 1961.<sup>8</sup> The semiconducting layer and gate dielectric of the TFT were made of cadmium sulfide and

FIG. 1-3. Active matrix addressing scheme and one example of applications. Thin film transistor - liquid crystal display (TFT-LCD).

silicon monoxide by conventional evaporation. Soon after this, various semiconducting materials have been studied for example Cadmium Selenide (CdSe).

Hydrogenated amorphous silicon thin film transistors (a-Si:H TFTs) were initially proposed by LeComber as electronic switching devices in 1979.<sup>9,10,11</sup> It has been demonstrated that TFTs are effective driving and read-out devices in the microelectronic applications such as liquid crystal displays (LCDs) <sup>12,13</sup>, optoelectronic sensors <sup>14</sup>, and chemical/biological sensors.<sup>15,16</sup> Recently novel devices such as the radiation sensors <sup>17</sup>, medical imaging sensors (Digital X-ray detector) <sup>18,19</sup>, and MEMS (Micro Electro Mechanical Systems) <sup>20</sup> have been successfully fabricated on the basis of TFT technologies. Additionally, chemical and biological sensing devices driven by TFTs are currently being studied throughout the world.<sup>15</sup>

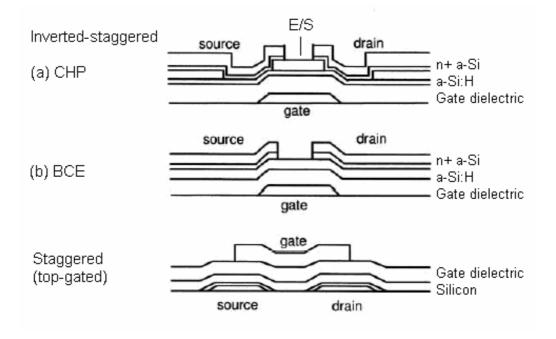

Fig. 1-4 shows various cross-sectional TFT structures. The staggered and inverted-staggered structures are used in a-Si:H TFTs. The inverted-staggered structure is more popular than the staggered structure because of the lower interfacial density of states between the gate dielectric and a-Si:H films.<sup>21</sup> An inverted-staggered TFT is usually fabricated with following mask steps; gate, active region, source/drain, and via hole. As shown in Fig. 1-4, electrons injected from the source electrode cross the a-Si:H layer, travel through the channel at the interface between the gate dielectric and a-Si:H, cross the a-Si:H layer again, and reach the drain electrode. Since the channel thickness is estimated to be several tens of nanometers, the interface properties between gate dielectric and a-Si:H play a critical role in TFT characteristics.<sup>22</sup>

FIG. 1-4. Various cross-sectional structures of TFT. (a) Channel-passivated (CHP), (b) back-channel etched (BCE), and staggered (top-gated) TFTs.

Kuo Yue, Journal of the Electrochemical Society 142 (1), 186 (1995).

The basic current-voltage characteristics of a TFT can be analyzed in a similar fashion compared to a metal-oxide-semiconductor field effect transistor (MOSFET) and polycrystalline devices. The following assumptions are defined for the formulation; (1) the carrier mobility in the channel is constant, (2) the gate capacitance is constant and independent of the gate voltage, (3) the source and drain electrodes are electrically ohmic contacts to the semiconductor, (4) the initial charge density in the semiconductor is  $n_{\theta}$ , and (5) the gradual cannel approximation can be applied. The gradual channel approximation means that the transverse field in the channel is greater than the longitudinal field ( $E_x$ ). To define TFT parameters, a coplanar TFT structure shown in Fig. 1-5 is used for the analysis. The coplanar structure is not common in a-Si:H TFT but this structure illustrates well how the TFT characteristics are extracted using this simple configuration.<sup>23,24</sup>

The application of a gate voltage  $V_g$  induces charge density  $\Delta n(x)$  in channel region. This is given by;

$$e\Delta n(x) = \left(\frac{C_i}{t}\right) \left[V_g - V(x)\right]$$

where  $C_i$  is the gate capacitance per unit area ( $=\varepsilon_i/d$ ), *t* is the a-Si:H thickness, *d* is the gate insulator thickness, and V(x) is the drain voltage at distance *x* from the source. If the thickness *t* is assumed to be sufficiently small, the drain current  $I_d$  is given by

$$I_{d} = tW[\sigma_{0} + \Delta\sigma(x)]E_{x} = tWe\mu_{n}[n_{0} + \Delta n(x)]E_{x}$$

where  $\sigma_0$  and  $\Delta \sigma(x)$  are initial conductivity and incremental conductivity from  $\Delta n(x)$ , respectively. From combining above two equations,  $I_d$  is given by

FIG. 1-5. The coplanar TFT structure used for electrical characterization. In a-Si:H TFTs, the staggered electrode configuration is generally adopted. Therefore, the analytical model is different from the actual device characteristics. However, the current-voltage characteristics from this device model can be described well by the analytical results obtained using this model.

Toshihisa Tsukada, "TFT/LCD: Liquid Crystal Displays Addressed by Thin-film Transistors-Japanese Technology Review," 29 (1996)

$$I_{d} = W\mu_{n}C_{i}\left[\left(\frac{etn_{o}}{C_{i}}\right) + V_{g} - V(x)\right]\left(\frac{dV(x)}{dx}\right)$$

$$I_{d}\int_{0}^{L}dx = W\mu_{n}C_{i}\int_{0}^{V_{d}}\left[\left(\frac{etn_{0}}{C_{i}}\right) + V_{g} - V(x)\right]dV(x)$$

Then, drain current is given by

$$I_{d} = \mu_{n} C_{i} \left(\frac{W}{L}\right) \left[ (V_{g} - V_{t}) V_{d} - \left(\frac{V_{d}^{2}}{2}\right) \right]$$

where  $V_t \approx -etn_0/C_i$ . The threshold voltage  $V_t$  depends on the initial charge density  $n_0$ . This equation is valid for a voltage range of  $0 \le V_d \le V_g - V_t$ . Beyond this range, the current is assumed to be constant as in insulated-gate field effect transistor. Low  $V_d$  values correspond to the region of linear output characteristics where the drain conductance,  $g_d$ , and the transconductance,  $g_m$ , are given by

$$g_{d} = \frac{\partial I_{d}}{\partial V_{d}} \Big|_{V_{d} \to 0} = \mu_{n} C_{i} \left(\frac{W}{L}\right) (V_{g} - V_{t})$$

$$g_{m} = \frac{\partial I_{d}}{\partial V_{g}} = \mu_{n} C_{i} \left(\frac{W}{L}\right) V_{d}$$

The drain conductance is a linear function of  $V_g$ , and the transconductance is proportional to  $V_d$ . Saturation of the drain current occurs when  $\partial I_d / \partial V_d = 0$ , due to pinchoff of the conducting channel in the region near the drain. In this case, the saturation current,  $I_{dsat}$ , is given by

$$I_{dsat} = \left(\frac{1}{2}\right) \mu_n C_i \left(\frac{W}{L}\right) (V_g - V_t)^2$$

For  $V_d \ge V_g - V_t$ , the transconductance in the saturation region is given by

$$g_m = \mu_n C_i \left(\frac{W}{L}\right) (V_g - V_t) = \left[2\mu_n C_i \left(\frac{W}{L}\right) I_{dsat}\right]^{1/2}$$

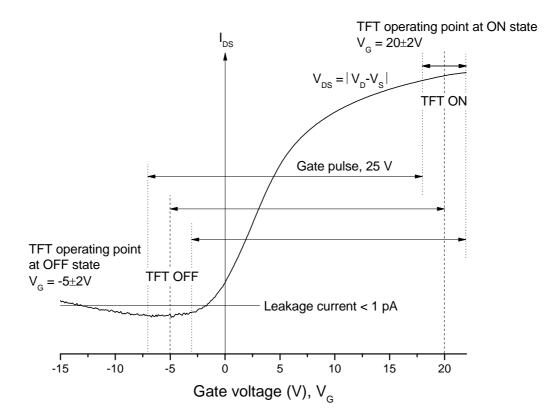

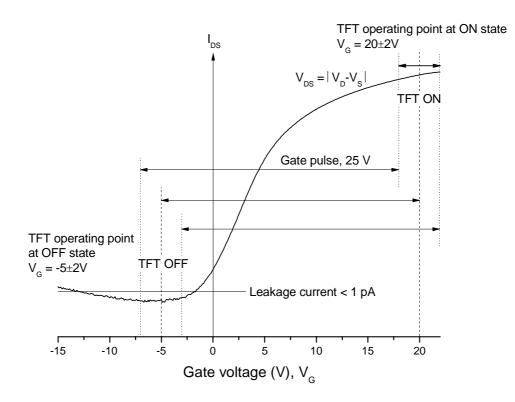

The typical operating scheme of a-Si TFT is shown in Fig. 1-6. TFT usually operates in the range of  $20 \pm 2$  V for ON state and  $-5 \pm 2$  V for OFF state. The on/off current ratio is generally defined as the current ratio of the ON and OFF state.

### 1.3 Vertically aligned carbon nanofibers (VACNFs)

#### 1.3.1 Definition and overview of VACNF

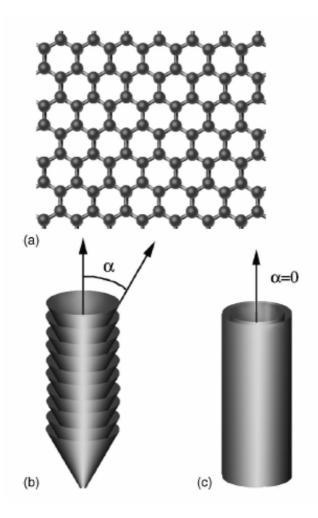

Carbon nanofibers (CNFs) can be defined as cylindrical or conical structures with diameters from a few to hundreds of nanometers and lengths ranging from less than a micron to millimeters. Fig. 1-7 (a) shows a graphene structure with covalently bonded carbon atoms arranged in a hexagonal network. There are two types of carbon nanostructures according to the angle between the fiber axis and the graphene sheet near the sidewall surface; stacked cone structure nanofiber and nanotube; Fig. 1-7 (a) and (b) respectively.<sup>25,26</sup>

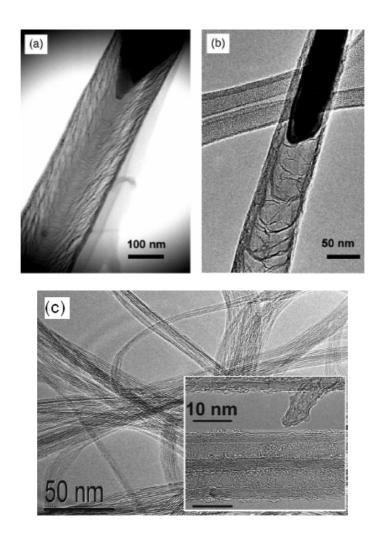

Fig. 1-8 shows tunneling electron microscopy (TEM) image of carbon nanofiber and carbon nanotubes grown by direct current catalytic plasma enhanced chemical vapor deposition (DC C-PECVD); (a) with Ni catalyst, and (b) bamboo-type carbon nanofiber with Fe catalyst; (c) bundles of single-walled carbon nanotubes.

FIG. 1-6. Typical operating scheme of a-Si TFT.

FIG. 1-7. Schematic diagrams of carbon nanofiber and nanotube. (a) Graphene layer, (b) stacked cone nanofiber, and (c) nanotube.

M. Endo, Y. A. Kim, T. Hayashi et al., Applied Physics Letters 80 (7), 1267 (2002).A. Krishnan, E. Dujardin, M. M. J. Treacy et al., Nature 388 (6641), 451 (1997).

FIG. 1-8. STEM image of a carbon nanofiber grown by DC C-PECVD. (a) With Ni catalyst, (b) a bamboo-type carbon nanofiber grown with Fe catalyst, and (c) bundles of single-walled carbon nanotubes.

A. V. Melechko, V. I. Merkulov, T. E. McKnight et al., Journal of Applied Physics 97 (4), 41301 (2005).

1.3.2 Synthesis process and growth mechanism of catalytic thermal chemical vapor deposition

There are several methods for synthesizing carbon nanostructures; laser evaporated deposition,<sup>27</sup> arc discharge,<sup>28,29</sup> catalytic chemical vapor deposition (C-CVD), and catalytic plasma enhanced chemical vapor deposition (C-PECVD). In the case of laser ablation and arc discharge deposition, although they have several advantages of being high quality nanotube materials with high efficiency, controlling spatial arrangement of nanostructures is intractable using these deposition technologies. In addition to this drawback, extra purification processes are needed to remove amorphous carbon particles for highly purified materials. On the other hand, C-CVD and C-PECVD allow the controlled deterministic synthesis to achieve a specific location, alignment, size, shape, structure of individual carbon nanofibers.

In using conventional CVD, there are process sequence steps to deposit a condensed phase on substrate; desorption, evolution, and incorporation of vapor species on substrate. The conventional CVD deposition occurs by heat flux at high temperature, 400 to 1000 °C. C-CVD uses a catalyst in the decomposition of vapor species on the catalyst surface and somewhat differs from the conventional CVD.<sup>30</sup> There are two methods to introduce the catalyst onto the substrate; supported and floating catalyst. The supported catalyst is deposited onto the substrate directly and the floating catalyst is formed by flowing a reactive gas.<sup>31,32</sup> Carbon nanostructures have been successfully

synthesized by C-CVD and recently it has been used to successfully grow multi-walled carbon nanotubes (MWCNTs)<sup>33</sup> and single-walled carbon nanotubes (SWCNTs).<sup>32</sup>

The growth mechanism of carbon nanofibers has been widely studied by many researchers. Baker et al. showed small amount of metal particles generate carbon nanofibers during the decomposition of acetylene.<sup>34</sup> They used in situ electron microscopy to take images of the growth sequence and measured the growth rate to determine the kinetic parameters involved in the process. They conclude that the growth mechanism follows these steps (Fig. 1-9): (1) adsorption and decomposition of the reactive hydrocarbon molecule on the surface of catalyst, (2) dissolution and diffusion of carbon species through and around the metal particles, and (3) precipitation of carbon on the reverse surface of the catalyst particles to structure the nanofibers. In the step (3), the precipitation occurs on the bottom surface of the catalyst particle and then the particles are lifted up toward top of the carbon nanofiber remaining crystalline graphite. At the first stage of the study, the temperature gradient was regarded as the dominant kinetic factor of carbon diffusion through the catalyst due to exothermic reaction of decomposition on the catalyst surface.<sup>34</sup> Later, it turned out that the dominant driving force for diffusion of carbon into the catalyst is the concentration gradient. Kock et al. also suggested that the driving force for carbon diffusion is the concentration gradient of carbon content of sub-stoichiometric carbides, therefore the carbon content decreases with the direction of the metal-carbon interface.<sup>35</sup>

FIG. 1-9. Growth mechanism of carbon nanofiber. (a) Adsorption and decomposition of reactive hydrocarbon molecule on the surface with catalyst, (b) dissolution and diffusion of carbon species through or around metal particles, and (c) precipitation of carbon on the reverse surface of the catalyst particles and incorporation into graphite layers.

R. T. K. Baker, M. A. Barber, R. J. Waite et al., Journal of Catalysis 26 (1), 51-62 (1972).

1.3.3 Synthesis process and growth mechanism of catalytic plasma enhanced chemical vapor deposition (C-PECVD)

Plasma enhanced chemical vapor deposition (PECVD) is one of the widely used deposition techniques which utilizes a plasma to reduce activation energy. By decreasing the activation energy, the growth temperature of thin films can be also lowered and can be suitable for low temperature deposition. By introducing catalysts in PECVD system (C-PECVD), carbon nanostructures are successfully grown at low temperature relative to conventional CVD.<sup>36</sup> In recent study, Boscovic *et al.* suggested that a high field of radio frequency (rf) provides selective heating on catalyst particle in the growth of carbon nanostructures even though the substrate temperature is very low.<sup>37</sup> Other effects should be considered, however, as there are some possibilities of simple resistive (Joule) heating by induced current. That is, there is a possibility of Joule heating that contributes to the catalyst heating as well as the heating by high frequency movement of catalyst.

Prior to understanding the growth mechanism of carbon nanofibers, it is instructive to review the deposition theory of PECVD. PECVD is a technique commonly used in microfabrication to deposit insulating thin films amorphous or polycrystalline silicon. The plasma is used to stimulate a reaction on the substrate surface the species from the gas phase. The plasma helps break up the parent molecules and allows the reaction to deposit species at a lower temperature than conventional thermal CVD. The major advantage of PECVD is in fact, the lower temperature capability with respect to other systems such as conventional CVD. For example, while deposition temperatures of 500-900 °C are required for silicon deposition in CVD, temperatures in the range 250-350 °C are sufficient in PECVD systems. In the PECVD deposition process, a glow discharge plasma is sustained within vacuum chamber. The radio frequency ranging from 100 kHz to 40 MHz is usually employed as a power source at 50 mTorr to 5 Torr pressure range. When the plasma turns on, the density of electrons and positive ions are between  $10^9$  and  $10^{12}$  /cm<sup>3</sup>, and average electron energy is from 1 to 10 eV. The sufficiently energized discharge decomposes gas molecules into several kinds of species; electrons, ions, atoms, free radicals, and molecules in ground and excited states. PECVD is commonly utilized to deposit silicon dioxide (SiO<sub>2</sub>) and silicon nitride (Si<sub>3</sub>N<sub>4</sub>) for insulating layer of microelectronics. SiO<sub>2</sub> films are formed by reacting silane and nitrous oxide gases. Si<sub>3</sub>N<sub>4</sub> films are deposited either by reacting silane and ammonia gases or by reacting silane in a nitrogen discharge. The following is a reaction sequence for producing SiNH films from silane and nitrous oxide.

$$\begin{split} SiH_4 + 4N_2O &\rightarrow SiO_2 + 4N_2 + 2H_2O \\ SiH_4 + NH_3 &\rightarrow SiNH + 3H_2 \\ 2SiH_4 + N_2 &\rightarrow 2SiNH + 3H_2 \end{split}$$

In the case of direct-current PECVD system to grow carbon nanofibers, the substrate is usually placed on a substrate heater that is a cathode. To grow isolated VACNFs, the metal catalyst is essential as described previously. Among many kinds of metal catalyst, patterned 40 nm dimeter Ni dots on a Si substrate is preferentially used to synthesize isolated VACNFs.<sup>38</sup> Fig. 1-10 shows dc-PECVD system to grow VACNFs. The process sequence to grow VACNFs is the following; 1) pump down to base pressure, 2) after reaching base pressure below  $1 \times 10^{-5}$  Torr, ammonia (NH<sub>3</sub>) gas is introduced into

FIG. 1-10. DC-PECVD reactor for the growth of VACNFs. (a) High current heater wiring, (b) thermocouple wiring, (c) mass flow controllers for acetylene, ammonia, and other gases, (d) gas inlet, (e) glass cylinder vacuum chamber, (f) gas showerhead and anode, (g) cathode glow of acetylene/ammonia plasma above a 100-mm diam Si wafer, (h) substrate heater and cathode, and (i) pressure transducer.

A. V. Melechko, V. I. Merkulov, T. E. McKnight et al., Journal of Applied Physics 97 (4), 41301 (2005).

the chamber and the sample is pretreated with the NH<sub>3</sub> plasma. As a result of the treatment, discrete catalyst nanoparticles are formed from the deposited catalyst dot as shown in Fig. 1-11 (b). These nanoparticles play an important role of forming seeds for the catalytic growth of isolated VACNFs. After the pretreatment, 3) acetylene ( $C_2H_2$ ) gas is introduced into the chamber with maintaining NH<sub>3</sub> plasma and then the growth of VACNF is initiated vertically. Fig. 1-12 shows SEM images of VACNFs with a tip-type and non-aligned base-type CNFs grown by dc PECVD. Melechko *et al.* showed that the kinetics of the CNF growth also plays a role in various kinds of growth mode; base-type and tip-type CNFs can be simultaneously grown on the same substrate and using same catalyst by changing the ratio of gas flow.<sup>36</sup>

## 1.3.4 Electrical and electrochemical properties

Lee *et al.* reported recently the electrical properties of individual VACNF by measuring current-voltage characteristics of suspended nanofiber bridge.<sup>39</sup> The nanofibers showed typical linear current-voltage characteristics at low applied voltage both positive and negative. The estimated range of resistivity was calculated to be from  $10^{-6}$  to  $10^{-5} \Omega$ ·m with the assumption that the electrical conductivity is equal within the entire cylindrical cross-sectional area of the nanofiber.

Carbon nanofibers have been widely used as electrodes in electrochemical measurements since it provides low fabrication cost, stability in aqueous solutions, and

FIG. 1-11. Schematic representation of the PECVD process for growing VACNFs. (a) Catalyst deposition, (b) catalyst pretreatment / nanoparticle formation, and (c) growth of carbon nanofibers.

A. V. Melechko, V. I. Merkulov, T. E. McKnight et al., Journal of Applied Physics 97 (4), 41301 (2005).

FIG. 1-12. SEM images of two types of carbon nanofibers. (a) Vertical alignment of carbon nanofibers in a tip-type growth mode, and (b) nonaligned growth of base-type carbon nanofibers by DC PECVD process.

A. V. Melechko, V. I. Merkulov, D. H. Lowndes et al., Chemical Physics Letters 356 (5-6), 527 (2002).

excellent electrochemical reactivity. McKnight *et al.* studied the electrochemical properties of VACNF electrodes as electrochemical probes which were grown by dc-PECVD using a Ni catalyst.<sup>40</sup> The VACNFs showed very prospective possibilities in the application of nanoscaled carbon electrodes into multi-element array such as individually addressable probing devices providing unique platforms to introduce a high level of parallelism into electro-physiological and electro-analytical techniques.

Recently, VACNFs were also used as gene delivering device to introduce genetic materials into live cells. In this application, individual VACNFs were used for the direct injection and delivery of genetic materials into the intracellular and nuclear domains of eukaryotic cells. McKnight et al. used VACNF arrays in the as a parallel microinjection-based method.<sup>41</sup>

# Chapter 2 Materials integration issues for the active matrix thin film transistor array of intracellular probes

2.1 Gate electrode, molybdenum-tungsten (MoW)

#### 2.1.1 Background

For TFTs to achieve high-speed, high-density, and low-power consumption, a low-resistivity gate and / or source-drain metal electrode is essential. As shown in Table 2-1, molybdenum (Mo) (and Mo alloys), aluminum (Al) (and Al alloys), and copper (Cu) are generally used as gate electrodes in manufacturing electronic displays and semiconductor devices. In choosing a metal material for the gate electrode, there is a trade-off between resistivity and thermal/chemical stability. Al and Cu, for example, have very low electrical resistivity and therefore have a significant advantage and attraction to applications in high speed and large-scaled thin film devices. However, their thermal stability is very poor, especially, for processing temperatures in excess of 500 °C. One of the main problems occurs during heat treatment of the Al (Cu)-Si contact because Al (or Cu)-Si inter-diffusion is significant above 500 °C. This interdiffusion can, for example, create silicon precipitates in Al which reduces the overall conductivity of the lines. In addition, Al can suffer from electromigration, which is a metal mass transport due to an electric current. Al atoms move in the direction of electron flow, toward the anode, and vacancies remain in the Al thin film. Consequently, Al whisker growth can

| Table 2-1. Representative gate electrode materials for fabricati | on of TFTs. |

|------------------------------------------------------------------|-------------|

|------------------------------------------------------------------|-------------|

| Material        | Resistivity<br>(μΩ·cm)                  | Stress resistance | Taper angle in dry etching |

|-----------------|-----------------------------------------|-------------------|----------------------------|

| МоТа            | 40-45                                   | Excellent         | Good                       |

| MoW             | 15-20 (conventional)<br>7-10 (our work) | Excellent         | Excellent                  |

| Al alloy (AlNd) | 5-7 (post-annealed)                     | Fair              | Good (AlNd)                |

| Al-Cu           | 4-5                                     | Fair              | Fair                       |

| Al              | 4-5                                     | Poor              | Fair                       |

| Cu              | 3-4                                     | Good              | Fair                       |

be observed between Al and Si films. If the whiskers contact other layers, for example dielectric layers, they can cause additional device failures. When Al is passivated by a dielectric, hillock formation can cause cracking of such films. To prevent hillock formation, in the case of using Al as a gate electrode, a Mo layer can be added to form a Mo/Al bilayer.<sup>42</sup> The bi-layer deposition and dry etch processes, however, are more complicated. The dry etch process is particularly difficult because the Mo and Al etch chemistries are different.

When fabricating TFT devices, the etching profile of the gate electrode is also very important. This is especially true for an invert-staggered TFT structure where the gate electrode is the bottom layer (typically used in TFT-liquid crystal displays). These structures require a tapered etch profile for several reasons. Firstly, it provides better step-coverage in subsequent deposition patterning processes. Secondly, the sharp edged (undercut) gate is a main source of dielectric breakdown due to the concentration of electric field at this sharp-edged point. Thirdly, the tapered gate electrodes influence the electrical properties of a TFT and can lower threshold voltages and facilitate steep swing characteristics.

For the past several years, the molybdenum tungsten (MoW) alloy has been studied and used as gate electrodes by Thin Film Transistor-Liquid Crystal Display (TFT-LCD) manufacturing companies because of its excellent thermal and chemical stability, reasonably low resistivity, and easily controllable etch taper angle.<sup>43,44</sup> In spite of its excellent properties, problems with larger substrate size and higher device driving speed have been encountered. Some of the problems include flicker, cross-talking, and line

delay due to relatively high resistivity of MoW (15~20  $\mu\Omega$ ·cm). To compensate the high resistance, MoW thin films require wider and thicker patterns. The wider and thicker MoW causes some fabrication problems in large-scaled integration and planarization of the device which can also lead to device failure. Therefore a thorough investigation of the process-property relationships of the MoW alloy is necessary to extend the utility of this alloy to advanced semiconductor applications. Although MoW has many advantages in microelectronics, especially high temperature applications, there is not much published work on this thin film alloy. In this work, we present electrical and micro-structural properties as a function of the MoW composition for films sputtered under various process conditions (temperature and bias).

As shown in Fig. 2-1, the Mo-W binary system has complete solid solubility since they satisfy the requirements to make the complete solid solution; same crystal structure (body-centered cubic, BCC), similar electronegativity (Mo-2.16, W-2.36) and below 3 % of lattice parameter difference (Mo-0.3147 nm, W-0.3164 nm).

#### 2.1.2 Experimental

The details of the sputtering conditions used to deposit the MoW specimens are shown in Table 2-2. An AJA ATC2000 RF magnetron sputtering system equipped with heated and DC biased substrate holder was utilized for the deposition of Mo, W, and MoW thin films (Fig. 2-2). The films were deposited on thermally oxidized  $SiO_2(1 \ \mu m)$  / Si (100) substrates. The substrate holder can be rotated if uniform thickness and

FIG. 2-1. Equilibrium phase diagram of Mo-W binary system.

(P. Gustafson et al., 79 (6), 1988, p388-396, SGTE Phase Diagram Collection at www.met.kth.se)

FIG. 2-2. Schematic diagram of an AJA ATC2000 RF magnetron sputtering system equipped with DC bias supply.

|                        | ID  | RF power (W) |     | DC bias       | Pressure | Temp. |

|------------------------|-----|--------------|-----|---------------|----------|-------|

| Run No.                |     | Мо           | W   | (Watt / Volt) | (Pa)     | (°C)  |

| 1 <sup>st</sup> series | (a) | 200          | 160 | 0 / 0         | 0.66     | RT    |

|                        | (b) | 200          | 160 | 0 / 0         | 0.66     | 250   |

|                        | (c) | 200          | 160 | 30 / 165      | 0.66     | RT    |

|                        | (d) | 200          | 160 | 30 / 165      | 0.66     | 250   |

| 2 <sup>nd</sup> series | (a) | 200          | 0   | 0 / 0         | 1.06     | RT    |

|                        | (b) | 200          | 0   | 15 / 140      | 1.06     | RT    |

|                        | (c) | 200          | 0   | 30 / 165      | 1.06     | RT    |

|                        | (d) | 200          | 0   | 45 / 190      | 1.06     | RT    |

|                        | (e) | 0            | 200 | 0 / 0         | 1.06     | RT    |

|                        | (e) | 0            | 200 | 15 / 140      | 1.06     | RT    |

|                        | (f) | 0            | 200 | 30 / 165      | 1.06     | RT    |

|                        | (g) | 0            | 200 | 45 / 190      | 1.06     | RT    |

|                        | (h) | 200          | 200 | 0 / 0         | 1.06     | RT    |

|                        | (i) | 200          | 200 | 15 / 140      | 1.06     | RT    |

|                        | (j) | 200          | 200 | 30 / 165      | 1.06     | RT    |

|                        | (k) | 200          | 200 | 45 / 190      | 1.06     | RT    |

Table 2-2. Experiment conditions for the MoW work.

(Fixed parameters: 25 sccm Ar gas, 70 mm gap between substrate and target)

composition are desired and produces a  $Mo_{1-x}W_x$  (0.1 < x < 0.9) gradient when the sample is not rotated (combinatorial mode). As shown in Fig. 2-2, the system has three targets each equipped with an rf matching network and power supply. The sources can be tilted and the z-position of the substrate holder can be varied in-situ to change the deposition profile. The sputtering targets have a 50 mm diameter and a 6 mm thickness. The base pressure prior to the sputtering deposition was below  $5.0 \times 10^{-6}$  Pa and the total flow rate of argon used in these experiments was fixed at 25 sccm for all conditions. The substrate is heated by quartz lamps and the temperature is controlled within  $\pm 1$  °C temperature range. The resistance was analyzed via four point probe measurements (Veeco FPP-5000) at a fixed film thickness (~300 nm). The crystal structure characteristics of the films were analyzed with a Phillips X-pert Pro X-ray diffraction (XRD) system, and the microstructure was analyzed by using a Hitachi S-4700 scanning electron microscope (SEM). The first series of experiments was designed to analyze electrical properties and microstructures as a function of Mo-W composition, applied bias, and substrate temperature. The second series was designed to explore the effects of the applied bias on the electrical and micro-structural properties of MoW.

## 2.1.3 Results and discussion

#### A. Films deposited without negative bias at room temperature and 250 °C

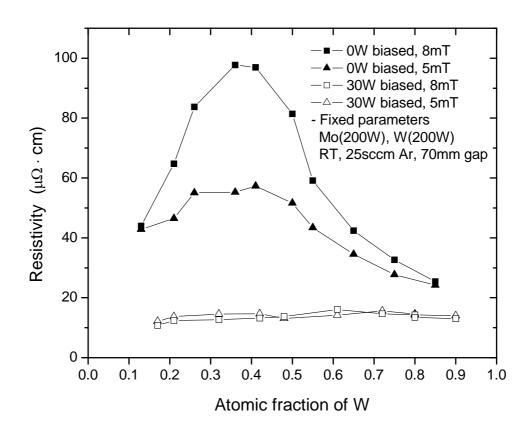

The electrical resistivity of the MoW alloy as a function of atomic fraction of W is shown in Fig. 2-3. In the figure, (a) and (c) are processed at room temperature and (b)

FIG. 2-3. Electrical resistivity of MoW as a function of composition, temperature, applied bias, and process pressure. (a) No bias / RT, (b) No bias / 250 °C, (c) 30 W (165 V) bias / RT, and (d) 30 W (165 V) bias / 250 °C from the  $1^{st}$  series.

and (d) are at 250 °C. And (a) and (b) are processed without bias and (c) and (d) are under a 30W (165V) dc bias. The resistivity results as a function of W fraction for (a) and (b) samples that are processed without bias follow a typical Nordheim relationship. In a metallic material, the electron scattering due to the perturbations such as solute atoms, second phases, impurities, dislocations, vacancies, and grain boundaries increase electrical resistivity. As demonstrated in Fig. 2-3 (a) and (b), the electrical resistivity of the MoW binary system increases with increasing solute concentration, and it has the maximum at  $\sim 0.5$  atomic fraction of solute atoms because of high electron scattering due to defects from mixing of the solid solution. The resistivity of binary alloys can be expressed by the well-known Nordheim's equation:

(1)

$$\rho_I = Cx(1-x)$$

where x is the fraction of solute atoms and C is Nordheim coefficient. This expression is valid for binary systems having the same valency. Therefore, the total resistivity of the metal alloy can be described with Matthiessen's rule;

(2)

$$\rho = \rho_T + \rho_R + \rho_R$$

Combining 1 and 2 yields:

(3)

$$\rho = \rho_T + \rho_R + Cx(1-x)$$

where,  $\rho_T$  is the resistivity due to scattering from thermally activated vibration;  $\rho_R$  is the residual resistivity due to the scattering from crystal defects, dislocations, vacancies, and impurities, etc.;  $\rho_I$  is the resistivity arising from solute atoms. The Nordheim coefficients of (a) and (b) in Fig. 2-3 are 118 and 70  $\mu\Omega$ ·cm, respectively. The sputtering temperature provides energy to the arriving species which enhances their surface mobility and allows

the species to occupy a lower energy state. This leads to a more ordered structure which reduces the electron scattering, and lowers the electrical resistivity.

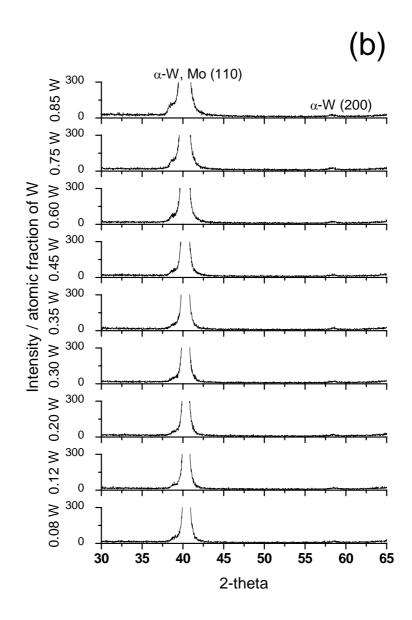

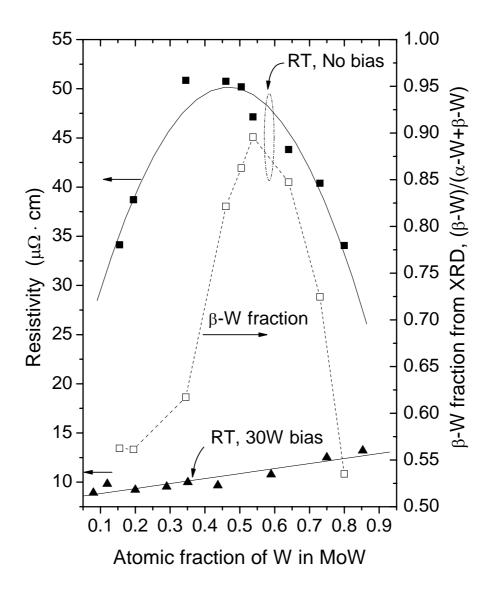

Fig. 2-4 shows XRD results of MoW as a function of W fraction at several sputtering conditions; (a) room temperature with no bias, (b) room temperature with 30 W (165 V) bias, 250 °C with no bias, and 250 °C with 30 W (165 V) bias. The XRD result of Fig. 2-4 (b) is identical to the RT / 30 W bias, 250 °C / no bias, and 250 °C / 30 W bias sputtering conditions. In the XRD spectra, the strong peak around  $2\theta = 40^{\circ}$  is a confluence of several peaks from α-W (40.26°, 110 plane), β-W (39.89°, 210 plane), and Mo (40.51°, 110 plane). The weak peak around  $2\theta = 38^{\circ}$  is a noise signal from the aluminum sample holder. As shown in Fig. 2-4 (a), at room temperature and without bias, a second metastable phase ( $\beta$ -W) is observed which correlates well with the resistivity, i.e. higher  $\beta$ -W content correlates with higher resistivity. The intensity of  $\beta$ -W (200) changes significantly with the atomic fraction of W in MoW alloy and has a maximum at  $\sim 0.5$  W. It is opined that the  $\beta$ -W fraction in MoW is highest at the ~ 0.5 W composition because the strain induced by the lattice mismatch between Mo and W is highest at  $\sim 0.5$  W which helps nucleate the metastable  $\beta$ -W. The  $\beta$ -W has a 5.05 Å lattice constant and its lattice mismatch with  $\alpha$ -W is about 37.3 % in transforming from  $\beta$ -W to stable  $\alpha$ -W phase. It has an A15 crystal structure and W atoms are positioned at (0, 0, 0),  $(\frac{1}{2}, \frac{1}{2}, \frac{1}{2})$ ,  $(\frac{1}{4}, \frac{1}{2}, 0)$ ,  $(\frac{3}{4}, \frac{1}{2}, 0)$ ,  $(0, \frac{1}{4}, \frac{1}{2})$ ,  $(0, \frac{3}{4}, \frac{1}{2})$ ,  $(\frac{1}{2}, 0, \frac{1}{4})$ , and  $(\frac{1}{2}, 0, \frac{3}{4})$  sites.<sup>45</sup> It appears that the presence of metastable  $\beta$ -W causes electron scattering which increases the electrical resistivity of the MoW thin film. The relationship between the amount of  $\beta$ -W from the XRD results and electrical resistivity of the MoW is shown in Fig. 2-5. The relative

FIG. 2-4. XRD results of MoW as a function of W atomic fraction. (a) RT / no bias.

FIG. 2-4. Continued. (b) RT / 30 W bias.

FIG. 2-5. The relationship between  $\beta$ -W fraction and electrical properties of MoW as a function of composition. (The  $\beta$ -W fraction at room temperature/30 W bias is zero because  $\beta$ -W phase is not present under all biased sputtering conditions even at room temperature sputtering.)

amount of  $\beta$ -W to  $\alpha$ -W is calculated from the intensities of the (200) planes located at 58.27 ° ( $\alpha$ -W) and 35.52 ° ( $\beta$ -W), respectively, and compared to the intensities expected from the standard diffraction patterns of each phase. This iteration was used because the (200) planes were the only peaks that did not have significant overlap with any other peaks. For the room temperature and un-biased sputter deposited sample, Fig. 2-5 shows that the presence of the second phase  $\beta$ -W significantly affects the resistivity. As the XRD peak intensity of  $\beta$ -W increases, the electrical resistivity also increases and has a maximum value at the point of ~ 0.5 atomic fraction W.

The sample deposited at 250 °C and un-biased does not contain the  $\beta$ -W phase over the entire composition range as illustrated in Fig. 2-4 (b). This correlates to Fig. 2-3 (c) which shows that resistivity of the 250 °C sample decreases relative to the room temperature deposited sample. This decrease is well correlated to the elimination of the second phase  $\beta$ -W. The higher temperature deposition could also induce a slightly more ordered lattice with fewer lattice defects which could also contribute to the lower resistivity. This contribution is not expected to be significant, however, due to the refractory properties of this alloy system. Therefore, the major factor that the 250 °C insitu heating has on the MoW film is to slightly order the material and inhibit the metastable  $\beta$ -W phase from forming.

#### B. Films deposited with negative bias (30W, -165V) at room temperature and 250 °C

Comparing Fig. 2-3 (a) and (b) to (c) and (d), respectively, illustrates the effect that substrate bias has on the MoW alloy resistivity. A significant reduction in the film

resistivity over the entire composition range is realized for each condition. Unlike the un-biased samples, however, the resistivity of the biased samples do not follow Nordheim's rule. Rather, these samples obey a rule of mixtures relationship  $\rho_{MoW} = x_{Mo}\rho_{Mo} + x_W\rho_W$  as a function of W fraction in MoW as shown in Fig. 2-3 (c) and (d). In this case the following relationship applies:

(4)

$$\rho = \rho_T + \rho_R + (x_{Mo}\rho_{Mo} + x_W\rho_W)$$

where  $x_{Mo}$  and  $x_W$  are atomic fraction of Mo and W, respectively, and  $\rho_{Mo}$  and  $\rho_W$  are the resistivity of Mo and W, respectively.

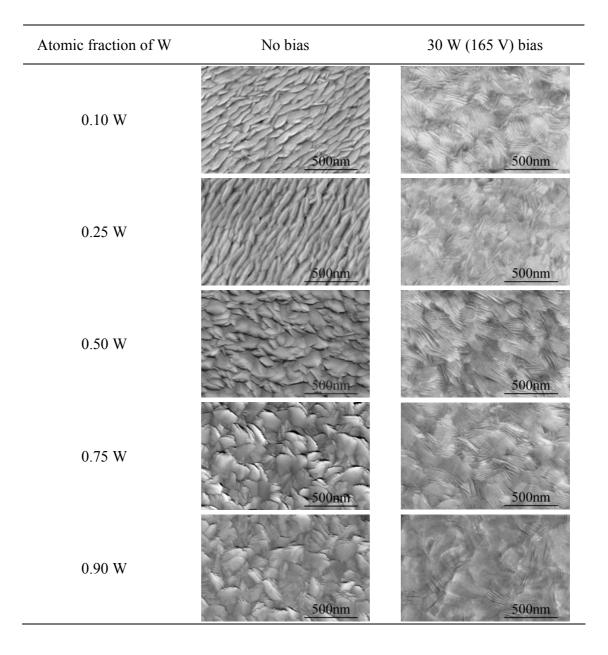

With bias sputtering of ~ 30W (-165 V), the metastable  $\beta$ -W is not present, even at room temperature as shown in Fig. 2-4 (b). Fig. 2-6 shows a series of SEM images as a function of the tungsten fraction for samples deposited at room temperature with and without substrate bias. From the figure, it can be seen that the biased microstructure is denser and has less void space between grains. Table 2-3 illustrates the effect that substrate bias has on the lattice constant measured normal to the substrate. The substrate bias increases the lattice parameter of the MoW alloy and qualitatively it is shown that the induced strain in the z-direction is a result in a change in the bi-axial stress in the plane of the substrate which is tensile without substrate bias and compressive with substrate bias. While the magnitude of the stress was not specifically determined, thicker (1 µm) thick MoW films deposited with substrate bias peeled off subsequent to deposition, whereas un-biased 1 µm thick films did not.

Another interesting observation from Fig. 2-3 and Fig. 2-5 is that the biased tungsten-rich alloy has a higher resistivity than biased molybdenum-rich alloy, (c) and (d).

FIG. 2-6. SEM images of MoW surface morphology as a function of the W atomic fraction in MoW thin films for samples deposited at room temperature with and without substrate bias.

|        | Applied bias<br>Watts (V) | Resistivity<br>µΩ∙cm | Deposition rate nm/min | XRD<br>(110) 2θ | *1 Lattice constant nm |

|--------|---------------------------|----------------------|------------------------|-----------------|------------------------|

| Мо     | 0                         | 42.9                 | 5.16                   | 40.59           | 0.3141                 |

|        | 15 (140 V)                | 13.0                 | 3.36                   | 40.33           | 0.3161                 |

|        | 30 (165 V)                | 11.9                 | 3.97                   | 40.33           | 0.3162                 |

|        | 45 (190 V)                | 12.6                 | 3.61                   | 40.33           | 0.3161                 |

| W      | 0                         | 18.7                 | 5.50                   | 40.37           | 0.3157                 |

|        | 15                        | 13.1                 | 4.43                   | 40.17           | 0.3172                 |

|        | 30                        | 13.1                 | 4.16                   | 40.15           | 0.3173                 |

|        | 45                        | 14.8                 | 3.64                   | 40.15           | 0.3173                 |

| *2 MoW | 0                         | 55.5                 | 11.59                  | 40.46           | 0.3150                 |

|        | 15                        | 11.6                 | 7.32                   | 40.29           | 0.3163                 |

|        | 30                        | 12.7                 | 7.57                   | 40.29           | 0.3163                 |

|        | 45                        | 12.9                 | 7.13                   | 40.28           | 0.3164                 |

Table 2-3. Result summary of the 2<sup>nd</sup> experimental series.

<sup>\*1</sup> Lattice constant of  $\alpha$ -phase

$^{*2}$  0.5 atomic fraction of W

Fixed parameters: 0.66 Pa, room temperature, 25 sccm Ar gas, 70 mm electrodes-gap

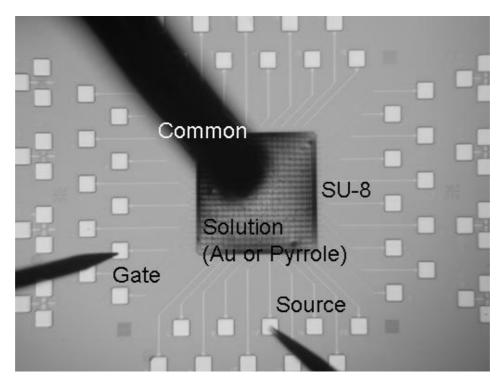

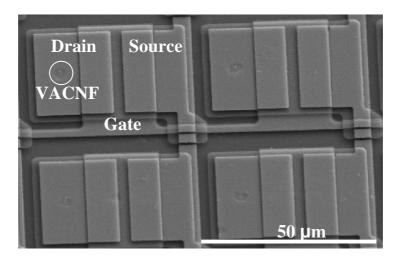

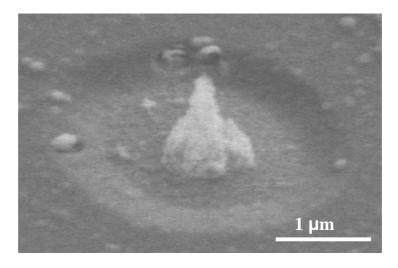

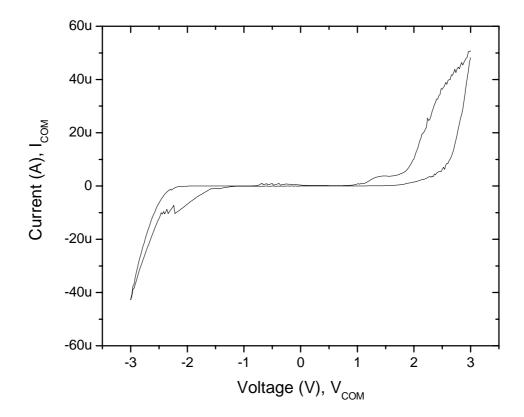

It is well known that the resistivity of bulk tungsten ( $\alpha$ -W, 5.49  $\mu$ \Omega·cm) is slightly lower than that of molybdenum (Mo, 5.78  $\mu\Omega$ ·cm) at room temperature. The reason for the higher resistivity for the tungsten-rich end of the biased samples can be explained by the dislocation density of tungsten relative to molybdenum. H. B. Shukvsky and L. D. Whitmire et al. showed that the dislocation resistivity of tungsten is higher than that of molybdenum. Specifically, the dislocation resistivity of tungsten and molybdenum are reported to be  $6.7 \times 10^{-11}$  and  $5.8 \times 10^{-13} \ \mu\Omega \cdot cm^3$ , respectively.<sup>46,47,48</sup> During sputter deposition on a biased substrate, the deposited MoW film is subjected to ion bombardment by highly energized ions and these ions can produce ion-radiated defects such as dislocation loops and point defects.<sup>45</sup> The electron scattering from dislocations in tungsten is nearly two orders of magnitude higher than molybdenum; therefore the tungsten-rich MoW alloy has a higher resistivity than the molybdenum-rich alloy. While the dislocation density in the films increases the resistivity of the tungsten-rich end, the overall effect of substrate bias improves the resistivity of the entire alloy. The substrate bias inhibits the  $\beta$ -W alloy from forming and produces a much denser film structure. While dislocations are likely generated by the impinging energetic species, the lattice structure has fewer vacancies and a more ordered overall structure.