University of Tennessee, Knoxville Trace: Tennessee Research and Creative Exchange

### **Doctoral Dissertations**

Graduate School

5-2013

# New Application for Indium Gallium Zinc Oxide thin film transistors: A fully integrated Active Matrix Electrowetting Microfluidic Platform

Jiyong Noh jnoh3@utk.edu

#### **Recommended** Citation

Noh, Jiyong, "New Application for Indium Gallium Zinc Oxide thin film transistors: A fully integrated Active Matrix Electrowetting Microfluidic Platform. " PhD diss., University of Tennessee, 2013. https://trace.tennessee.edu/utk\_graddiss/1765

This Dissertation is brought to you for free and open access by the Graduate School at Trace: Tennessee Research and Creative Exchange. It has been accepted for inclusion in Doctoral Dissertations by an authorized administrator of Trace: Tennessee Research and Creative Exchange. For more information, please contact trace@utk.edu.

To the Graduate Council:

I am submitting herewith a dissertation written by Jiyong Noh entitled "New Application for Indium Gallium Zinc Oxide thin film transistors: A fully integrated Active Matrix Electrowetting Microfluidic Platform." I have examined the final electronic copy of this dissertation for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Doctor of Philosophy, with a major in Materials Science and Engineering.

Philip D. Rack, Major Professor

We have read this dissertation and recommend its acceptance:

Michael L. Simpson, Thomas T. Meek, Syed Islam

Accepted for the Council: <u>Dixie L. Thompson</u>

Vice Provost and Dean of the Graduate School

(Original signatures are on file with official student records.)

## New Application for Indium Gallium Zinc Oxide thin film transistors: A fully integrated Active Matrix Electrowetting Microfluidic Platform

A Dissertation Presented for the Doctor of Philosophy Degree The University of Tennessee, Knoxville

> Jiyong Noh May 2013

Dedicated to Hyunju Cha, Christina S. Noh, Eric H. Noh,

and my parents and parents in law

#### Acknowledgements

I would like to thanks my advisor Dr. Philip D. Rack for his support, his idea for this project, and continuous stimulating discussions. Most of all I would like to thank Dr. Joo Hyon Noh for mentoring and training me in all aspects of characterization, fabrication, and electrical testing. I would also like to Seyeoul Kwon for working closely with and giving me valuable advice for this dissertation. I also would like to thank Dr. Jason Heikenfeld and Dr. Ian Papautsky in University of Cincinnati. Dr. Michel L. Simpson, Dr. Thomas T. Meek, and Dr. Syed K. Islam, have generously served their expertise to my study. I would like to thank the people at Center for Nanophase Materials Science, Oak Ridge National Laboratory, Oak Ridge, TN for their support. Most of all, I would like to thanks my family, Hyunju Cha have given endless love, support, and pray for me and Christina S. Noh, and Eric H. Noh have given me happy to see her and his growth. I am especially grateful for the support and pray from my parents and parents in law in Korea.

#### Abstract

The characterization and fabrication of active matrix thin film transistors (TFTs) has been studied for applying an addressable microfluidic electrowetting channel device. Amorphous Indium Gallium Zinc Oxide (a-IGZO) is used for electronic switching device to control the microfluidic device because of its high mobility, transparency, and easy to fabrication. The purpose of this dissertation is to optimize each IGZO TFT process including the optimization of a-IGZO properties to achieve robust device for application. To drive the IGZO TFTs, the channel resistance of IGZO layer and contact resistance between IGZO layer and source/drain (S/D) electrode are discussed in this dissertation. In addition, the generalization of IGZO sputter condition is investigated by calculation of IGZO and Oxygen  $(O_2)$  incorporation rate at different oxygen partial pressure and different sputter targets. To develop the robust IGZO TFTs, the different passivation layers deposited by Radio Frequency (RF) magnetron sputter are investigated by comparing the electrical characteristics of TFTs. The effects Plasma Enhanced Chemical Vapor Deposition (PECVD) of Silicon Dioxide (SiO<sub>2</sub>) passivation layers on IGZO TFTs is studied the role of hydrogen and oxygen with analyzed and compared the concentration by the Secondary Ion Mass Spectroscopy (SIMS).

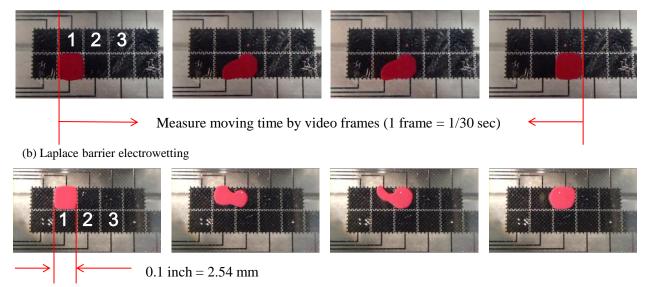

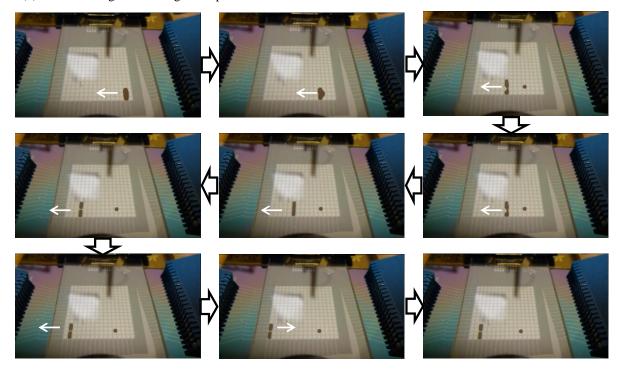

In addition, the preliminary electrowetting tests are performed for electrowetting phenomena, the liquid droplet actuation, the comparison between conventional electrowetting and Laplace barrier electrowetting, and the different size electrode effect for high functional properties. The active matrix addressing method are introduced and investigated for driving the electrowetting microfluidic channel device by Pspice simulation. Finally, the high resolution electrowetting

microfluidic device (16x16 matrix) is demonstrated by driving liquid droplet and channel moving using active matrix addressing method and fully integrated IGZO TFTs.

### **Table of Contents**

### 1 Introduction

| 1.1 Moti  | vation of this work1                                                              |

|-----------|-----------------------------------------------------------------------------------|

| 1.2 Thin  | film Transistors (TFT)2                                                           |

| 1.2.1     | Historical background4                                                            |

| 1.2.2     | Basic TFTs operation                                                              |

| 1.2.3     | TFTs structure7                                                                   |

| 1.2.4     | Electrical characterization of TFTs10                                             |

| 1.2.      | 4.1 Threshold voltage ( $V_{th}$ ) and turn on voltage ( $V_{ON}$ )10             |

| 1.2.      | 4.2 Field effective mobility ( $\mu_{FE}$ )                                       |

| 1.2.      | 4.3 Subthreshold gate swing slope and current on/off ratio14                      |

| 1.2.5     | Metal oxide semiconductor TFTs16                                                  |

| 1.2.      | 5.1 Overview of transparent electronics and amorphous oxide semiconductors (AOSs) |

|           |                                                                                   |

| 1.2.      | 5.2 Electronic structure and carrier transport model of amorphous oxide           |

|           | semiconductors                                                                    |

|           |                                                                                   |

| 1.3 Elect | rowetting and microfluidic channel in Lab on a chip device                        |

| 1.3.1     | Overview of Electrowetting Phenomena24                                            |

| 1.3.2     | Electrowetting on dielectric (EWOD) in a lab on a chip                            |

### 2 Device fabrication and characterization

| 2.1 Fabrication of IGZO TFTs |

|------------------------------|

|------------------------------|

| 2.1.1 (  | Gate electrode                                                                | 33        |

|----------|-------------------------------------------------------------------------------|-----------|

| 2.1.2    | Gate insulator                                                                | 36        |

| 2.1.3 \$ | Semiconductor                                                                 |           |

| 2.1.4    | Source and drain electrode                                                    | 39        |

| 2.1.5 H  | Passivation layer                                                             | 44        |

| 2.1.6 H  | Post annealing for TFTs activation                                            | 44        |

| 2.2 Fabr | rication of the lab on a chip system which is fully integrated on the IGZO TH | FTs array |

|          |                                                                               | 47        |

## 3 Basic characteristics and generalization of IGZO layer

| 3.1 Chan | nel resistance and contact resistance              | 49 |

|----------|----------------------------------------------------|----|

| 3.1.1    | Introduction                                       | 49 |

| 3.1.2    | Experiments                                        | 49 |

| 3.1.3    | Results and discussion                             | 51 |

| 3.1.4    | Conclusion                                         | 60 |

| 3.2 Gene | eralization the rf sputter condition of IGZO layer | 61 |

| 3.2.1    | Introduction                                       | 61 |

| 3.2.2    | Experiments                                        | 63 |

| 3.2.3    | Results and discussion                             | 63 |

| 3.2.4    | Conclusion                                         | 72 |

### 4 Characterization of Passivation layer

| 4.1 Introduction                                                   | 73 |

|--------------------------------------------------------------------|----|

| 4.2 Characterization of IGZO TFTs with different passivation layer | 77 |

| 4.3 Characterization of PECVD SiO <sub>2</sub> passivation layer   | 84 |

| 4.4 Conclusion                                                     | 99 |

### 5 Preliminary Electrowetting Basic Test

| 5.1 Introduction                                                               | 100 |

|--------------------------------------------------------------------------------|-----|

| 5.2 Electrowetting phenomena experiment                                        | 100 |

| 5.3 Droplet actuation in simple electrode structure                            | 109 |

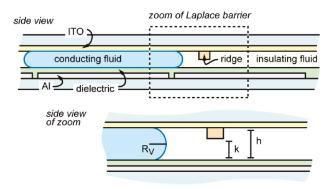

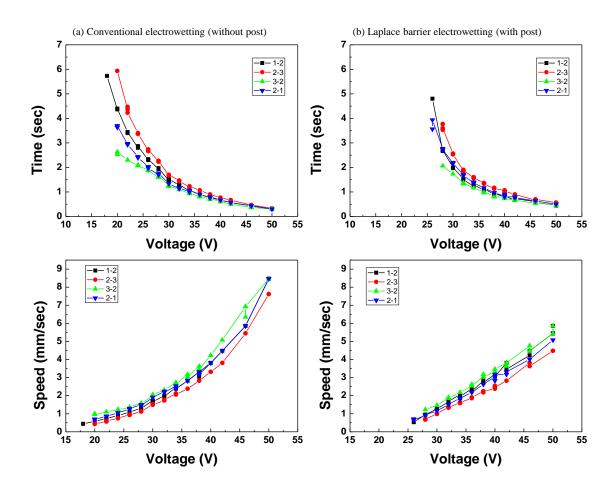

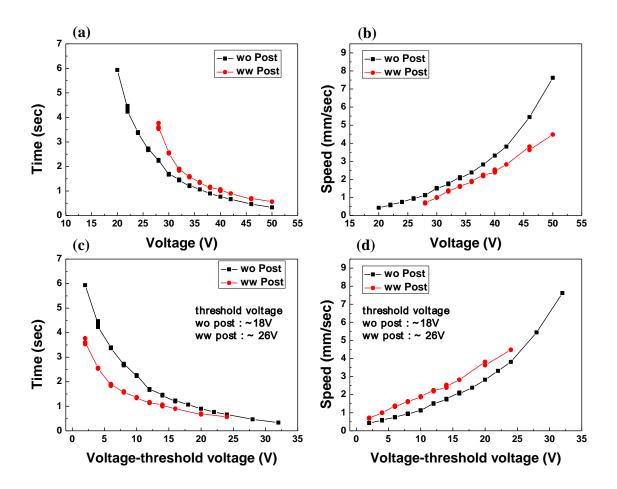

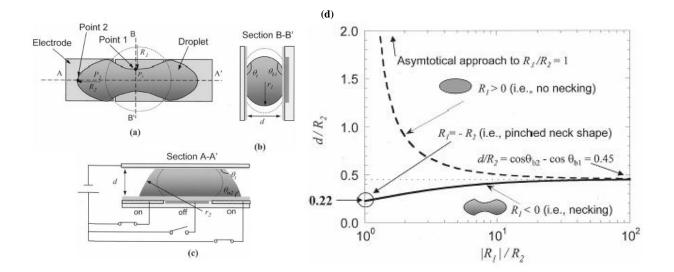

| 5.4 Conventional electrowetting microchannel & Laplace barriers electrowetting | 113 |

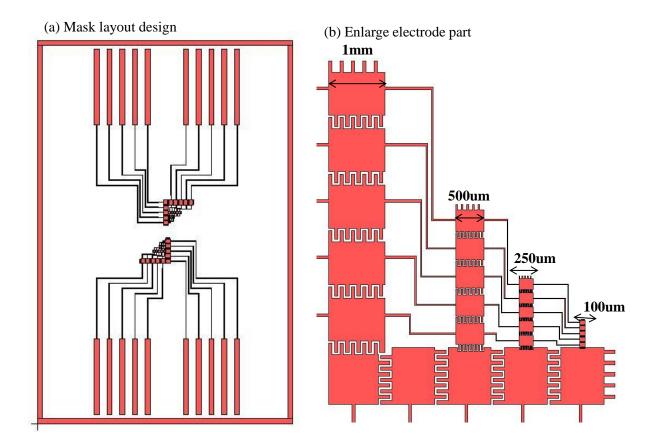

| 5.5 Split the different size electrodes                                        | 120 |

| 5.6 Conclusion                                                                 | 125 |

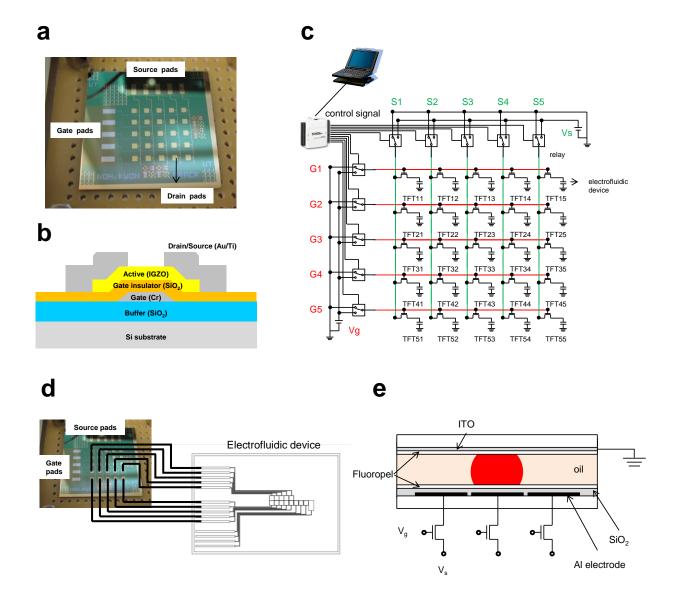

### 6 Active matrix driving for electrofluidic device using IGZO TFTs

| 6.1 Introduction            |     |

|-----------------------------|-----|

| 6.2 Experiments             | 127 |

| 6.3 Results and Discussions | 126 |

| 6.4 Conclusion              | 131 |

### 7 Full integration TFTs and Electrowetting device

| 7.1 Introduction | 145 |

|------------------|-----|

| 7.2 Experiments  | 147 |

| 7.3 Results and discussions                                                       | 154 |

|-----------------------------------------------------------------------------------|-----|

| 7.4 Conclusion                                                                    | 167 |

| 8 Conclusions                                                                     | 168 |

| * List of References                                                              | 170 |

| * Appendix A: Run sheet for IGZO TFTs processing                                  | 185 |

| * Appendix B: Run sheet for Full integrated electrowetting device using IGZO TFTs | 188 |

| *Vita                                                                             | 194 |

### LIST OF TABLES

| Table 1-1. Comparison of characteristics which has different kinds of semiconductor layers in                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| thin film transistor                                                                                                                                             |

| Table 2-1. Resistivity of different metals at 20-25°C, and temperature coefficient resistance35                                                                  |

| Table 2-2. Work function of different metals                                                                                                                     |

| Table 3-1. Summary of electrical characteristics of a-IGZO TFT with different TFT size (W/L)                                                                     |

| at $V_{DS}$ = 10.1V                                                                                                                                              |

| Table 3-2. The sputter parameters of IGZO deposition with same oxygen and IGZO flux67                                                                            |

| Table 3-3. TFT characteristics of the same $\Phi_{O_2}$ and $\Phi_{IGZO}$ which have different oxygen partial                                                    |

| pressure and deposition rate                                                                                                                                     |

| Table 3-4. TFT characteristics of the same $\Phi_{O_2}$ and $\Phi_{IGZO}$ with different sputter targets71                                                       |

| Table 4-1. The sputter deposition conditions of different passivation layer Al <sub>2</sub> O <sub>3</sub> , SiO <sub>2</sub> , Hf <sub>2</sub> O <sub>3</sub> , |

| and Y <sub>2</sub> O <sub>3</sub>                                                                                                                                |

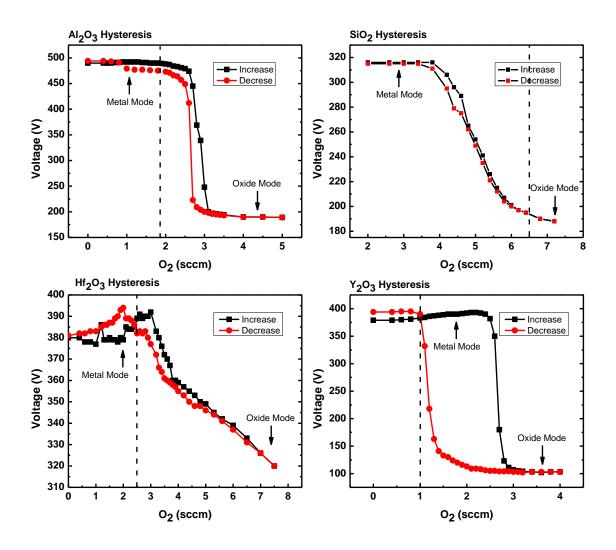

| Table 4-2. TFT characteristics of different passivation layers, $Al_2O_3$ , $SiO_2$ , $Hf_2O_3$ , and $Y_2O_3$ 83                                                |

| Table 4-3. Summarization refractive indexes (n) collected at 600nm wavelength and film                                                                           |

| densities of passivation PECVD SiO <sub>2</sub> layer of a-IGZO TFTs93                                                                                           |

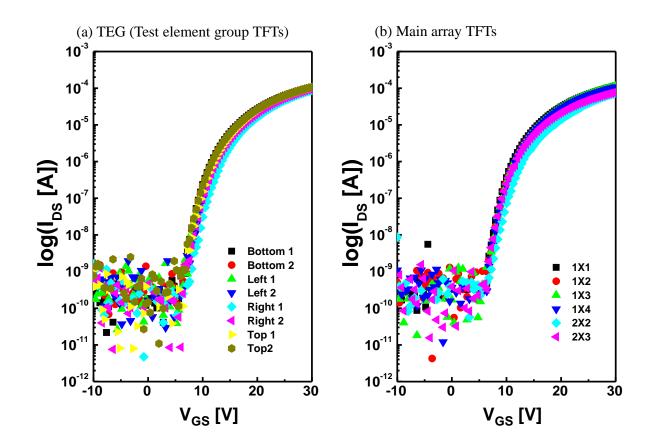

| Table 7-1. Transfer characteristics of TEG 8TFTs and Main array 6TFTs    163                                                                                     |

### LIST OF FIGURES

| Figure 1-1. (a) The basic structure of TFT and corresponding energy bond diagrams as viewed                 |

|-------------------------------------------------------------------------------------------------------------|

| through the gate for several biasing conditions: (b) equilibrium, $V_{GS}=0$ [V], (c) $V_{GS} < 0$          |

| [V], and (d) $V_{GS} > 0$ [V]6                                                                              |

| Figure 1-2. Cross section of the various TFT structure as S/D electrodes: (a) normal staggered              |

| TFT structure (b) inverted staggered TFT structure                                                          |

| Figure 1-3. Cross section of the various TFT structure as gate electrodes: (a) Bottom gate TFT              |

| structure (b) Top gate TFT structure9                                                                       |

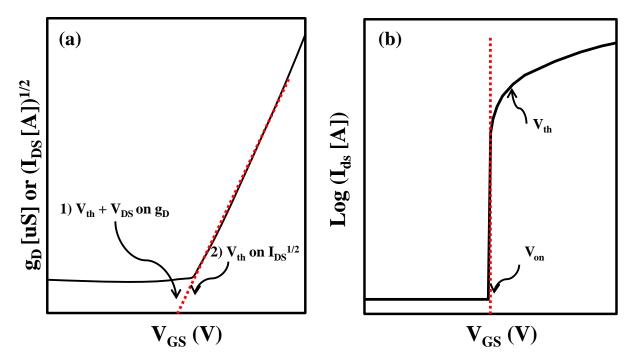

| Figure 1-4. Schematic diagram for definition of $V_{th}$ , $V_{ON}$ : (a) Output conductance gate to source |

| voltage $(g_D - V_{GS})$ characteristic illustration threshold voltage estimation (b) Log (I <sub>D</sub> - |

| $V_{GS}$ ) transfer characteristics showing the turn on voltage, $V_{ON}$ , and the threshold               |

| voltage, V <sub>th</sub> for the same device12                                                              |

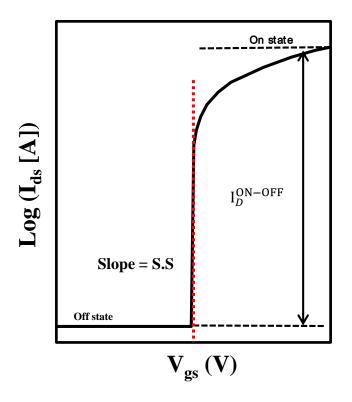

| Figure 1-5. Schematic diagrams for definition of subthreshold slope and drain current                       |

| ratio $I_D^{ON-OFF}$ 15                                                                                     |

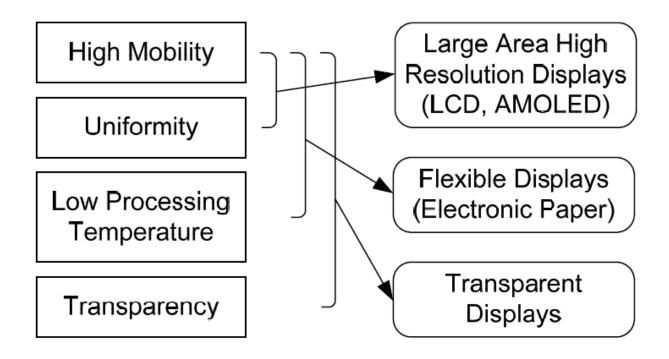

| Figure 1-6. Besides transparency. Amorphous AOS TFTs have additional useful characteristics                 |

| to compete with existing technologies                                                                       |

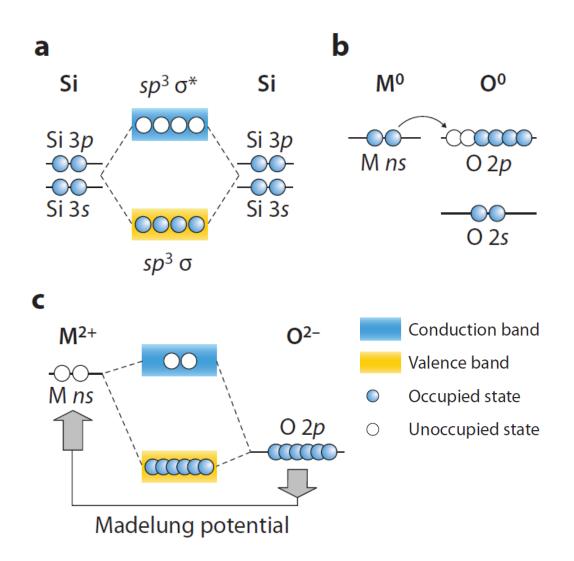

| Figure 1-7. Schematic electronic structures of silicon and ionic oxide semiconductors. (a-c)                |

| Bandgap formation mechanisms in (a) covalent and (b, c) ionic semiconductors.                               |

| Closed and open circles denote occupied and unoccupied states, respectively20                               |

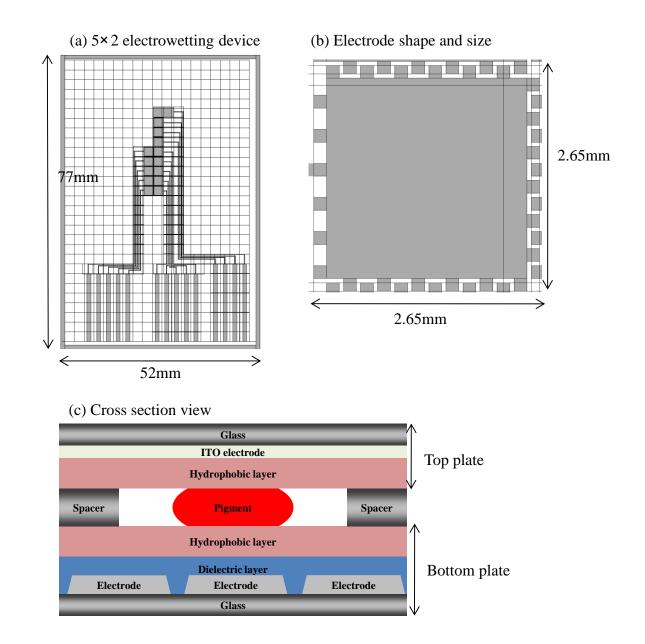

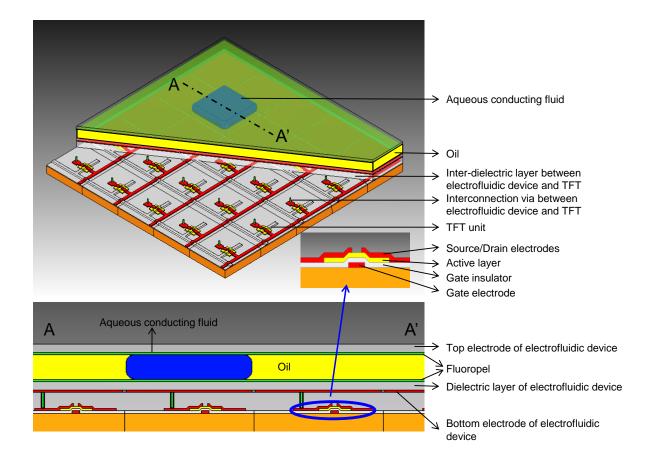

- Figure 1-13. Schematic diagram of a typical lab on a chip device: EWOD consist of metal electrode, insulator layer (dielectric), and hydrophobic layer on top and bottom plates.Pigment droplet which is filled with oil lay on between top and bottom electrodes. ..29

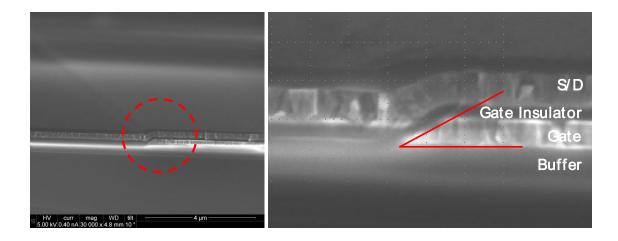

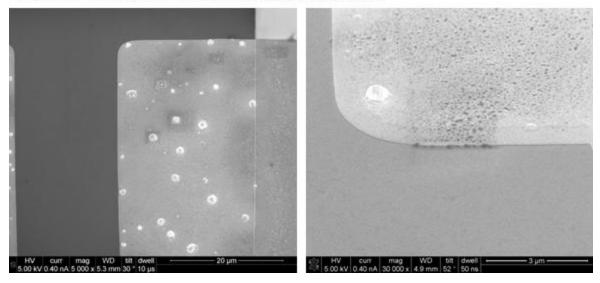

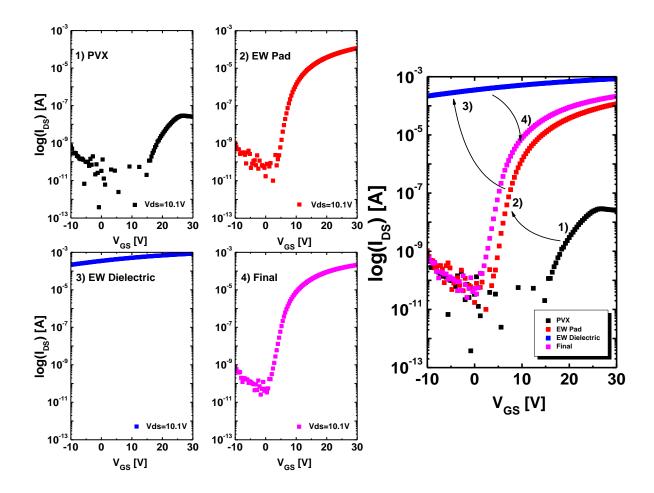

| Figure 2-2. SEM images of TFTs represent the step coverage of gate insulator on Cr gate                                               |

|---------------------------------------------------------------------------------------------------------------------------------------|

| electrode                                                                                                                             |

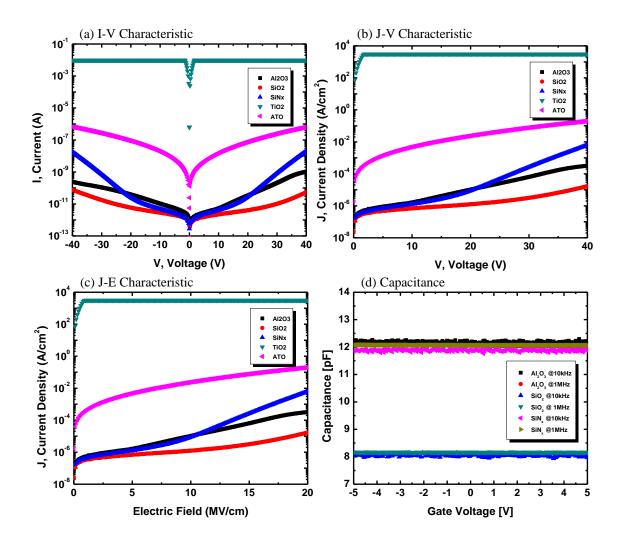

| Figure 2-3. I-V characteristics, J-V characteristics, J-E characteristics, and capacitance of                                         |

| different gate insulator layers (Al <sub>2</sub> O <sub>3</sub> , SiO <sub>2</sub> , SiN <sub>x</sub> , TiO <sub>2</sub> , and ATO)37 |

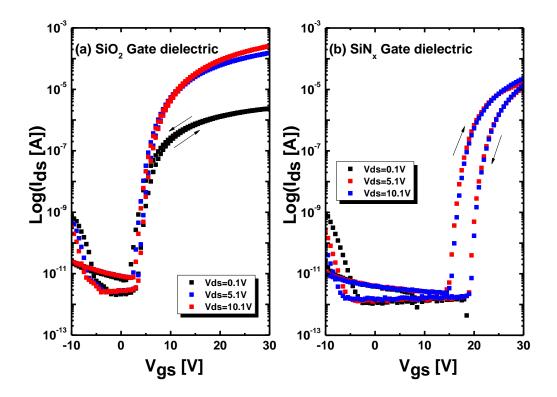

| Figure 2-4. Transfer hysteresis curves of different gate dielectric layers                                                            |

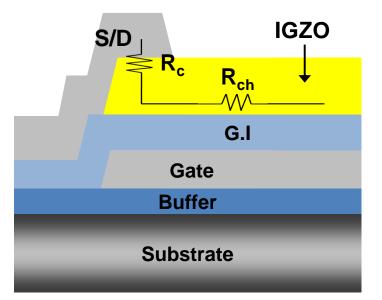

| Figure 2-5. Schematic diagram the S/D contact resistance between S/D and IGZO layer, and                                              |

| channel resistance of IGZO layer                                                                                                      |

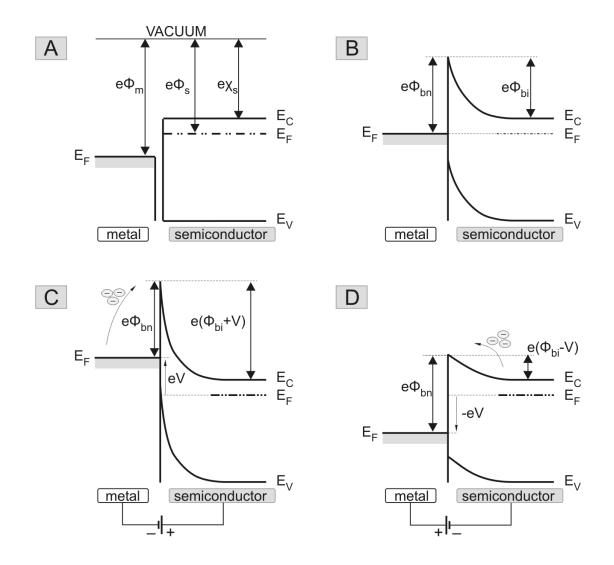

| Figure 2.6 Band diagram the match-up between S/D metal and semiconductor layer (a) metal and                                          |

| n-type semiconductor before contact (b) metal and n-type semiconductor after contact                                                  |

| (c) metal and n-type semiconductor contact with reverse bias (d) metal and n-type                                                     |

| semiconductor with forward bias42                                                                                                     |

| Figure 2-7. Micro oven temp history during the post annealing in air atmosphere                                                       |

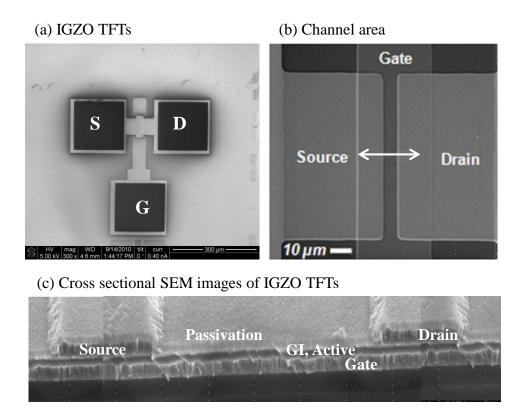

| Figure 2-8. SEM images of IGZO TFTs, (a) Overview of IGZO TFT, (b) Channel area, and (c)                                              |

| Cross sectional SEM images of IGZO TFTs46                                                                                             |

| Figure 2-9. The whole layout of electrowetting device, (a) $5 \times 2$ electrodes device, (b) Electrode                              |

| shape, and (c) Cross section view                                                                                                     |

| Figure 3-1. Schematic diagram for TLM pattern and TFT structure: (a) Transmission line method                                         |

| (TLM) Pattern, (b) Structure of IGZO TFTs50                                                                                           |

| Figure 3-2. The schematic drawing the physical origin of the resistance components                                                    |

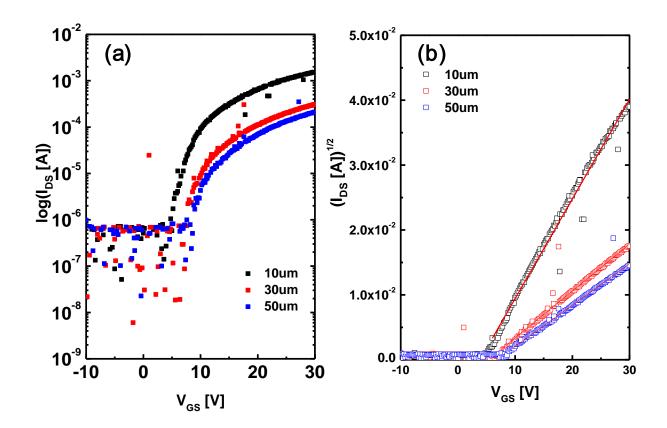

| Figure 3-3. The transfer curve characteristics as different length TLM pattern TFTs, all TFTs                     |

|-------------------------------------------------------------------------------------------------------------------|

| have 200um width. (a) $Log(I_{DS}) - V_{GS}$ (b) $(I_{DS})^{1/2} - V_{GS}$                                        |

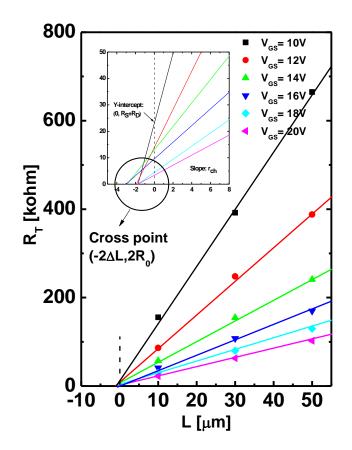

| Figure 3-4. The total TFT ON resistance $(R_T)$ versus channel length $(L)$ for several levels of V <sub>GS</sub> |

|                                                                                                                   |

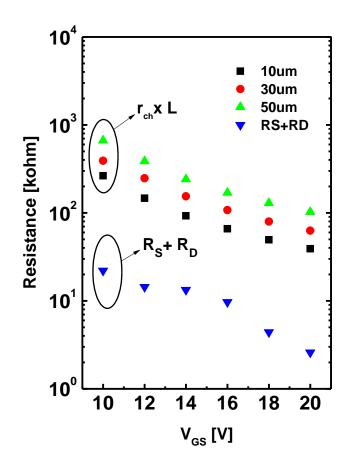

| Figure 3-5. The Contact resistance $(R_S + R_D)$ and the channel resistance $(R_{ch} \times L)$ as a function of  |

| V <sub>GS</sub>                                                                                                   |

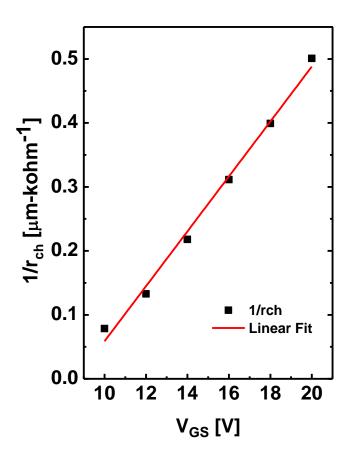

| Figure 3-6. Extracting the intrinsic field-effect mobility and threshold voltage by plotting $1/r_{ch}$           |

| versus V <sub>GS</sub>                                                                                            |

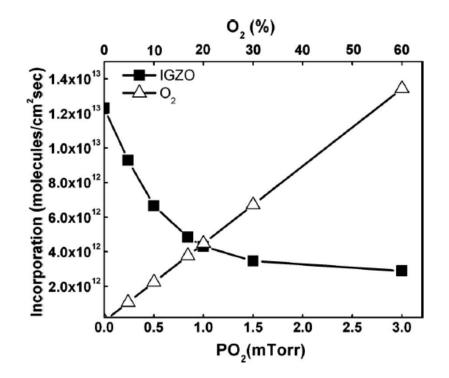

| Figure 3-7. Molecules incorporation of IGZO and $O_2$ with oxygen partial pressure in growing                     |

| IGZO film during sputtering62                                                                                     |

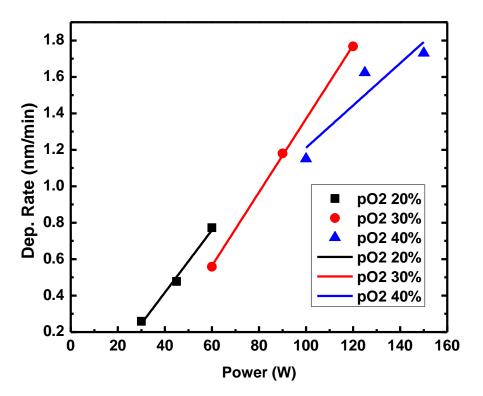

| Figure 3-8. Deposition rate of IGZO layer with different oxygen partial pressure and different rf                 |

| power                                                                                                             |

| Figure 3-9. The power conditions corresponded the deposition rate which has the same oxygen                       |

| and IGZO flux67                                                                                                   |

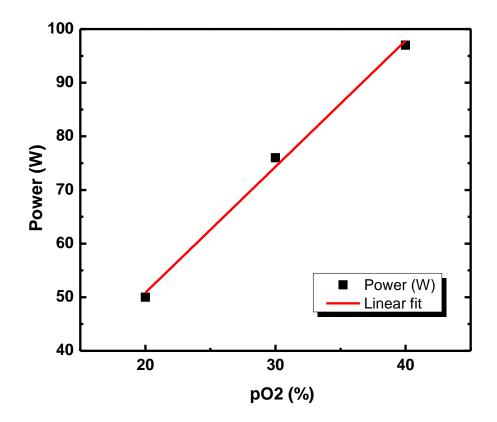

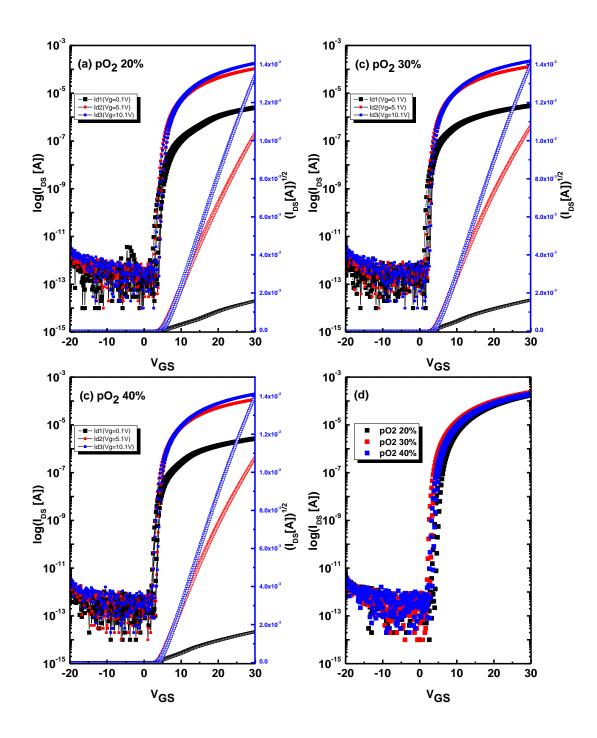

| Figure 3.10. The transfer curves of the same $\Phi_{0_2}$ and $\Phi_{IGZO}$ which have different oxygen partial   |

| pressure and deposition rate: (a) $pO_2 = 20\%$ , (b) $pO_2 = 30\%$ , (c) $pO_2 = 40\%$ , and (d)                 |

| merge the transfer curves of three TFTs at V <sub>DS</sub> =10.1[V]69                                             |

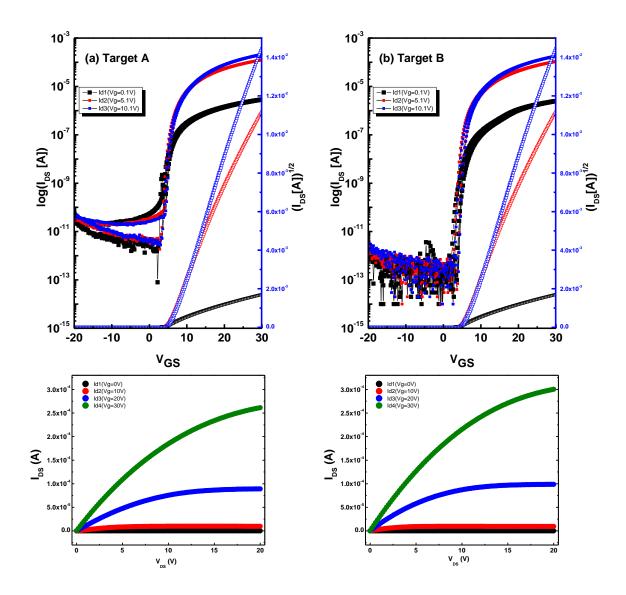

| Figure 3-11. The transfer and output curves of the same $\Phi_{O_2}$ and $\Phi_{IGZO}$ of different sputter       |

| targets (a) Sputter target A (b) Sputter target B70                                                               |

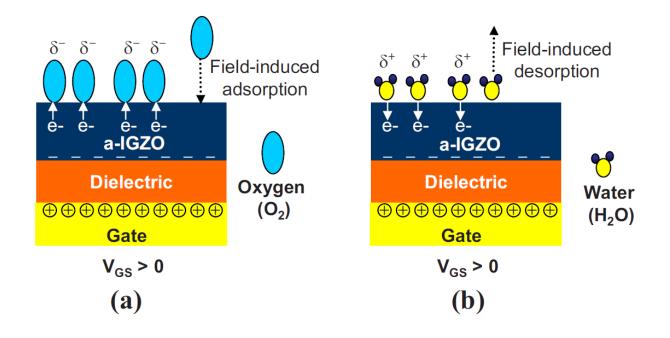

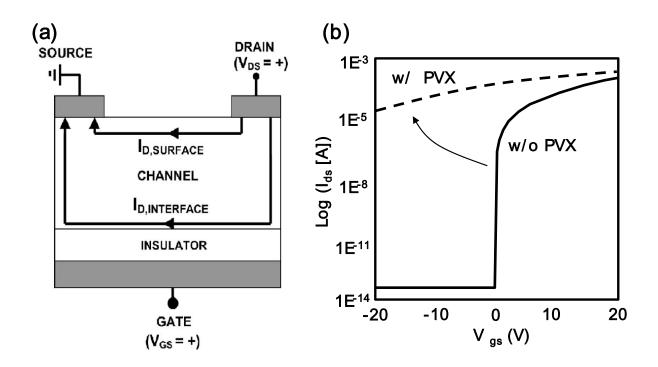

| Figure 4-1. (a) Schematic showing the electric field induced adsorption of oxygen molecules                                                                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| from the ambient atmosphere (b) Schematic showing the electric field induced                                                                                                             |

| desorption of water molecules into the ambient atmosphere75                                                                                                                              |

| Figure 4-2. (a) Schematic showing the electric field induced desorption of water molecules into                                                                                          |

| the ambient atmosphere (b) Transfer curve change before passivation layer and after                                                                                                      |

| passivation layer76                                                                                                                                                                      |

| Figure 4-3. (a) Schematic structure of different passivation layer samples (b) Transfer curves of                                                                                        |

| IGZO TFTs before passivation layer                                                                                                                                                       |

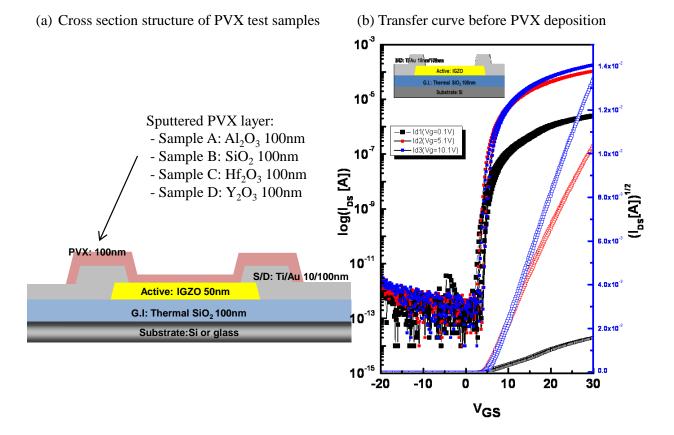

| Figure 4-4. Hysteresis curves with oxygen gas flow with 4 kinds of metal sputter targets for the                                                                                         |

| rf reaction sputtering                                                                                                                                                                   |

| Figure 4-5. Transfer curves with different passivation layers, Al <sub>2</sub> O <sub>3</sub> , SiO <sub>2</sub> , Hf <sub>2</sub> O <sub>3</sub> , and Y <sub>2</sub> O <sub>3</sub> 82 |

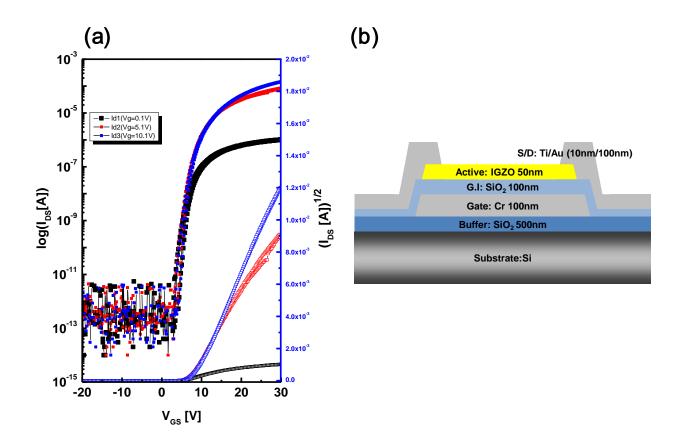

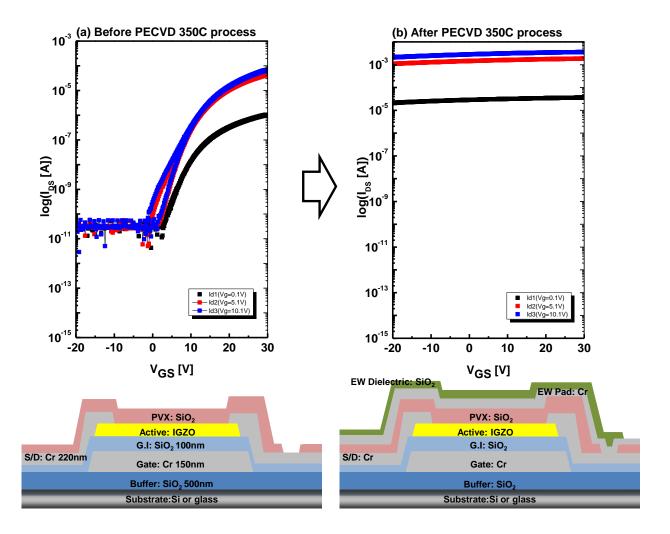

| Figure 4-6. (a) Transfer characteristics of a-IGZO TFTs without passivation layer. [annealed at                                                                                          |

| 350°C N <sub>2</sub> 1hr, TFT W/L=50/20 um, $V_{DS} = 0.1, 5.1, 10.1 \text{ V}$ ], (b) Bottom gate structure                                                                             |

| of un-passivated TFTs87                                                                                                                                                                  |

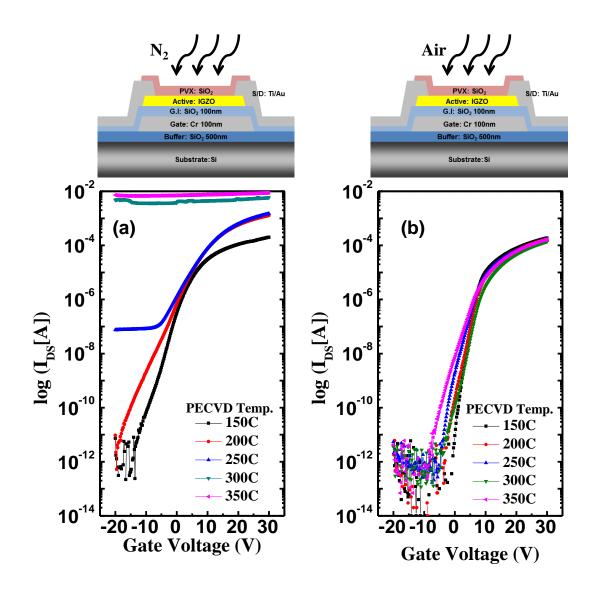

| Figure 4-7. (a) Transfer characteristics of a-IGZO TFTs with different temperature PECVD $SiO_2$                                                                                         |

| passivation layers after $N_2$ 350°C 1hr. (b) Transfer characteristics of a-IGZO TFTs                                                                                                    |

| with different temperature PECVD SiO <sub>2</sub> passivation layers after air 350°C 1hr. [TFT                                                                                           |

| size W/L=50/20um, V <sub>DS</sub> =10.1V                                                                                                                                                 |

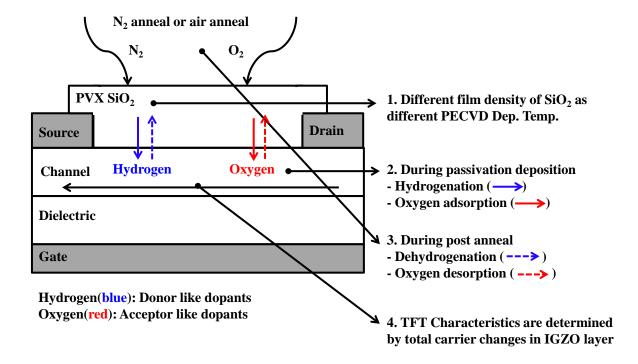

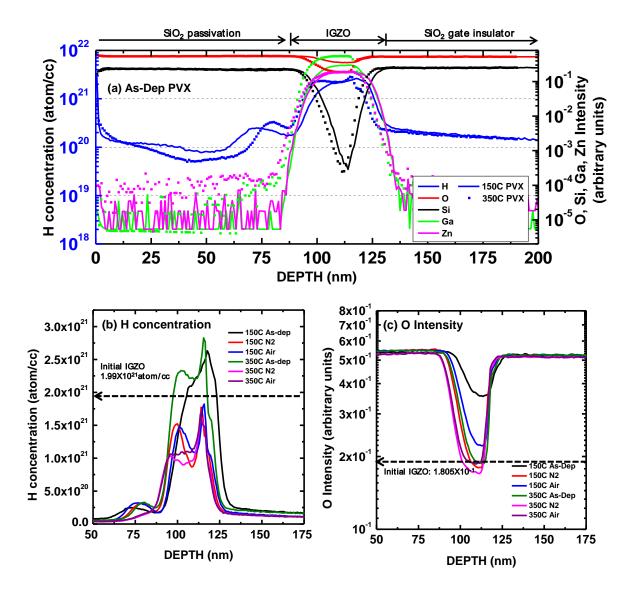

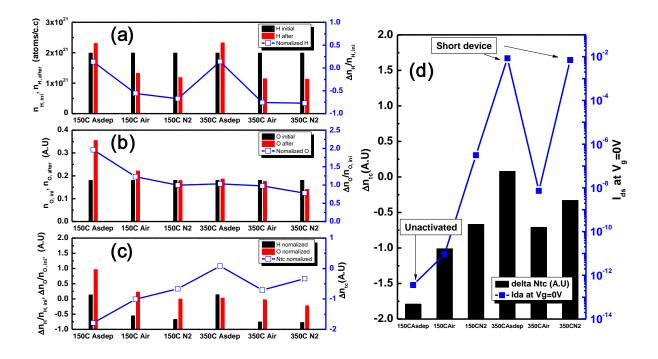

- Figure 4-10. Compare the concentration of hydrogen and oxygen with initial and after passivation or post annealing (a) hydrogen concentration, (b) oxygen intensity, (c) total carrier change ratio ( $\Delta n_{tc, \ total \ carrier \ change}$ ), and (d) compare total carrier change and I<sub>DS</sub> [A] at V<sub>GS</sub> = 0V in different passivation and post annealing samples .98

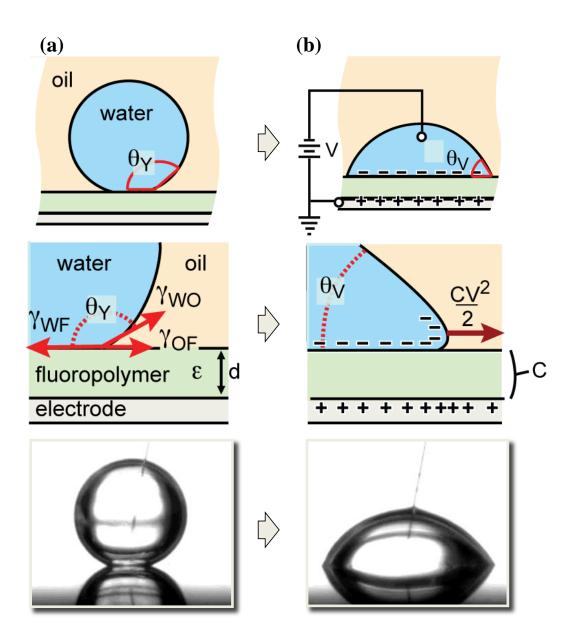

Figure 5-1. Three interfacial surface tension (a) with un-biased, (b) with biased .....103

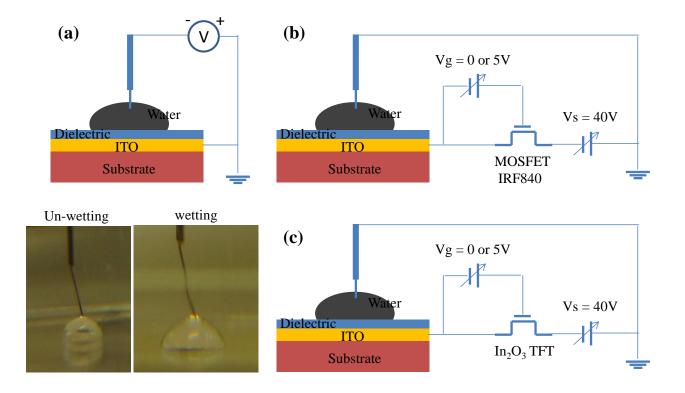

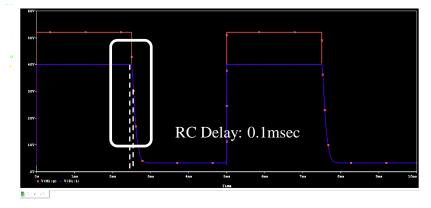

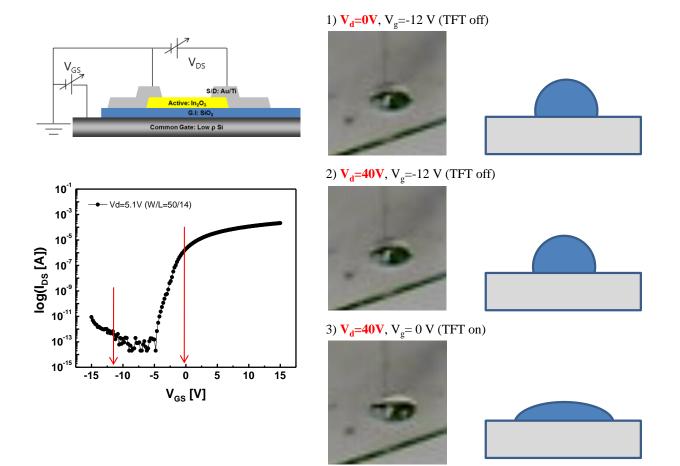

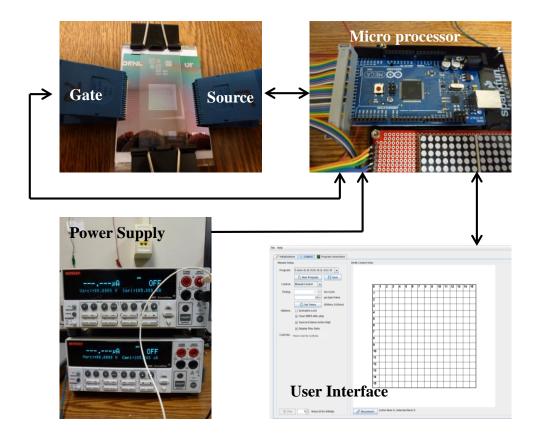

- Figure 5-2. The schematic basic electrowetting test system (a) Direct connect with Power supply, (b) MOSFET (IRF840), (c) In<sub>2</sub>O<sub>3</sub> TFT ......104

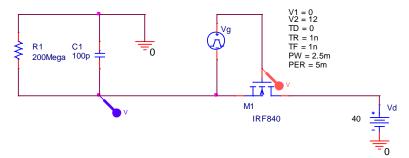

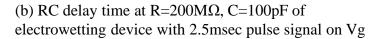

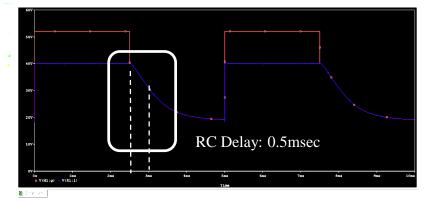

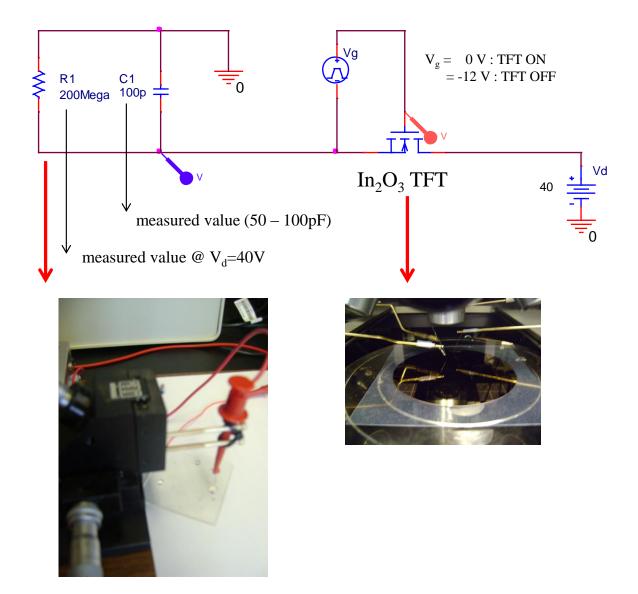

- Figure 5-3. (a) The circuit diagram of electrowetting device, (b)-(c) The RC delay at 200M $\Omega$  and  $2k\Omega$  of electrowetting device in Pspice simulation ......105

Figure 5-4. The experiment set up for electrowetting test using In<sub>2</sub>O<sub>3</sub> TFT ......107

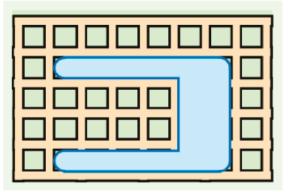

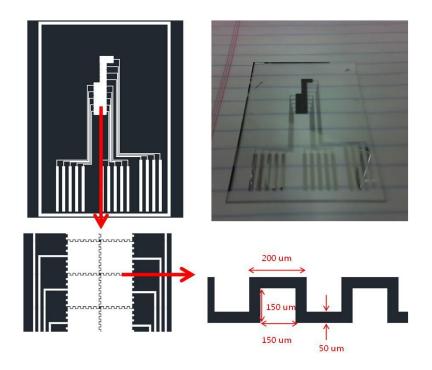

Figure 5-9. Mask layout of 2×5 electrowetting device, and sample picture ......116

Figure 5-14. Mask layout design of different electrode size (1mm, 500um, 250um, 100um) ...123

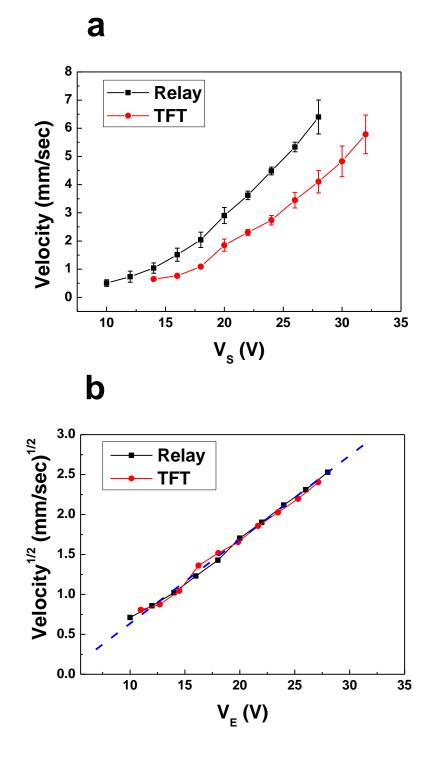

| Figure 6-3. (a) | Electrowetting   | transfer   | velocity    | as a   | function               | of | V <sub>S</sub> . | (b) | Square | root | of | the |

|-----------------|------------------|------------|-------------|--------|------------------------|----|------------------|-----|--------|------|----|-----|

| electr          | owetting transfe | r velocity | y plot as a | ı func | tion of V <sub>I</sub> | 3  |                  |     |        |      | 1  | 34  |

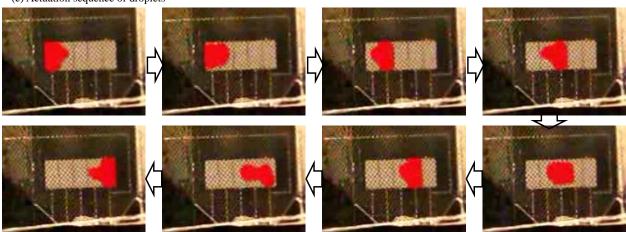

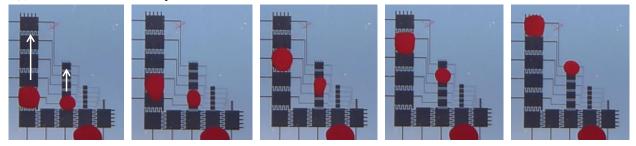

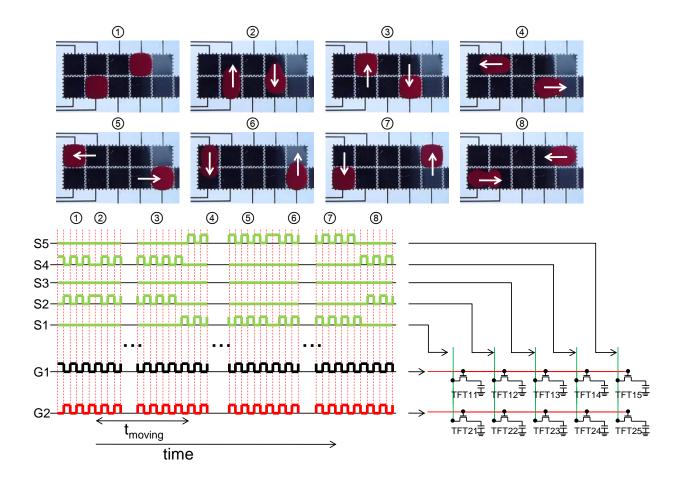

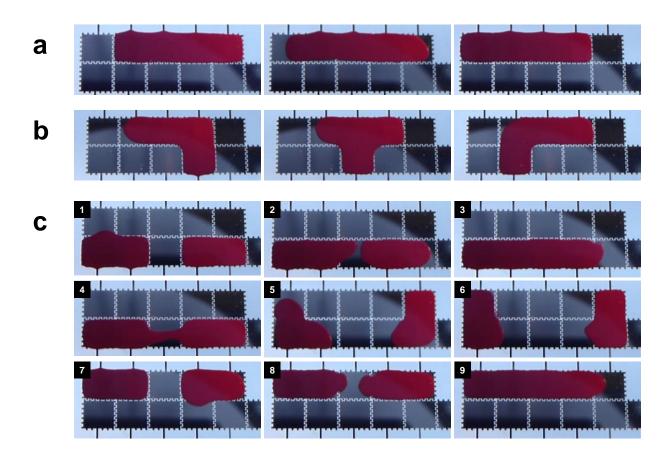

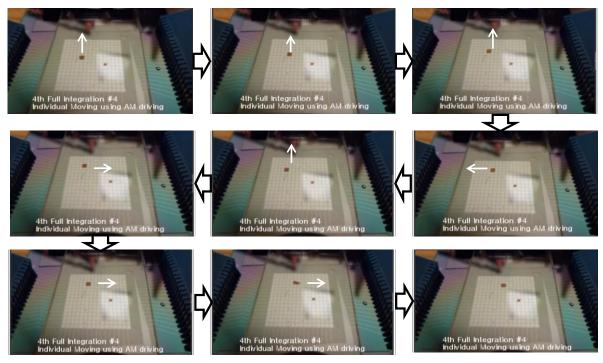

- Figure 6-5. Electrofluidic functionalities using AM driven electrofluidic device for Lab-on-chip application. Continuous channel formation (a) on one row and (b) across rows (c) One droplet control on the adjacent row when continuous channel was formed on one row.

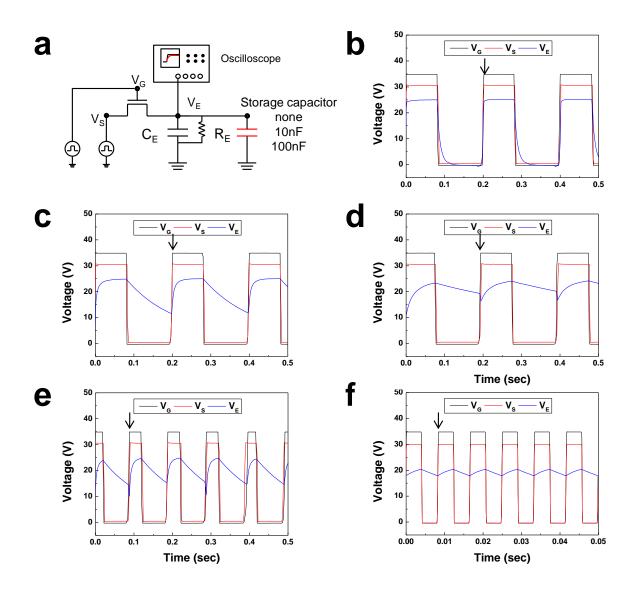

- Figure 6-6. (a) Schematic diagrams of wave form measurement. Gate, source, and electrowetting voltage waveforms as a function of external storage capacitor with gate pulse width of 100 msec; (b) only electrofluidic device, (c) electrofluidic device + 10 nF external storage capacitor, and (d) electrofluidic device + 100 nF external storage capacitor.

| Voltage waveforms for the electrofluidic device + 10 nF    | external storage capacitor |

|------------------------------------------------------------|----------------------------|

| with gate pulse frequency of (e) 10 Hz and (f) 120 Hz (50% | duty ratio)142             |

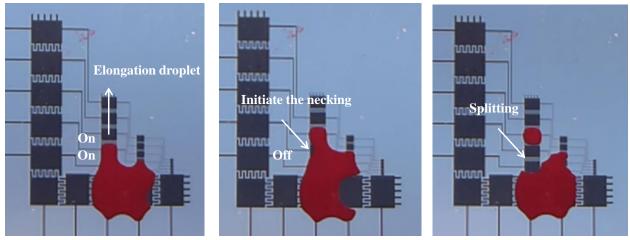

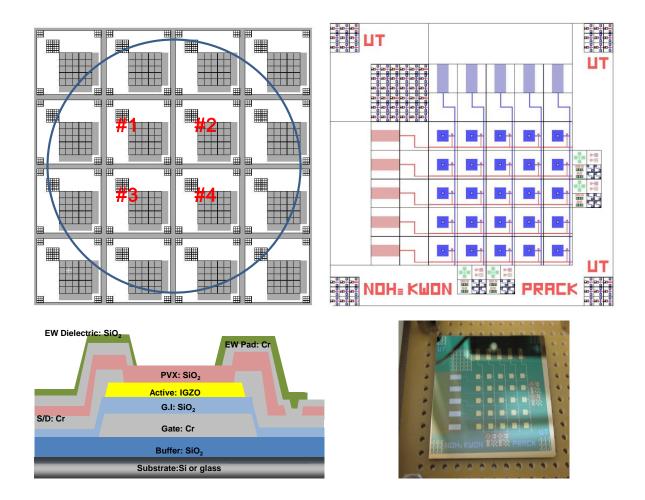

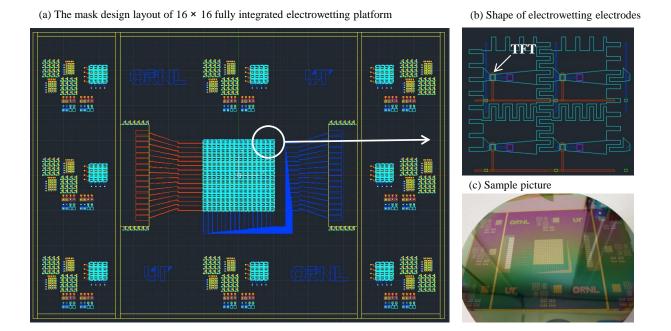

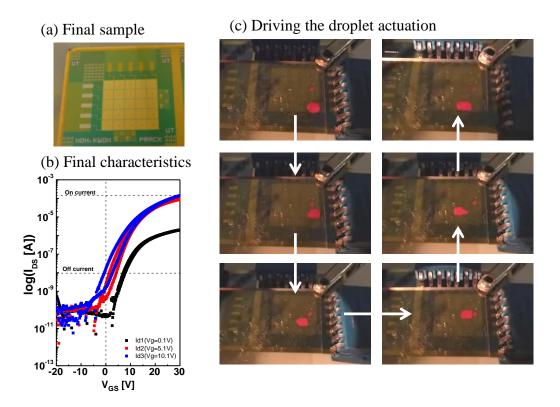

Figure 7-1. Prospective schematic diagram of electrofluidic device integrated on the TFTs array.

Figure 7-2. Mask designs, the cross section structure, and sample picture of 5x5 full integrated

|                               | 1                                     | 4.0 | C) |

|-------------------------------|---------------------------------------|-----|----|

| I F I S electrowetting device | 1                                     | 42  | ×  |

| 11 15 clock of welling device | · · · · · · · · · · · · · · · · · · · |     | 2  |

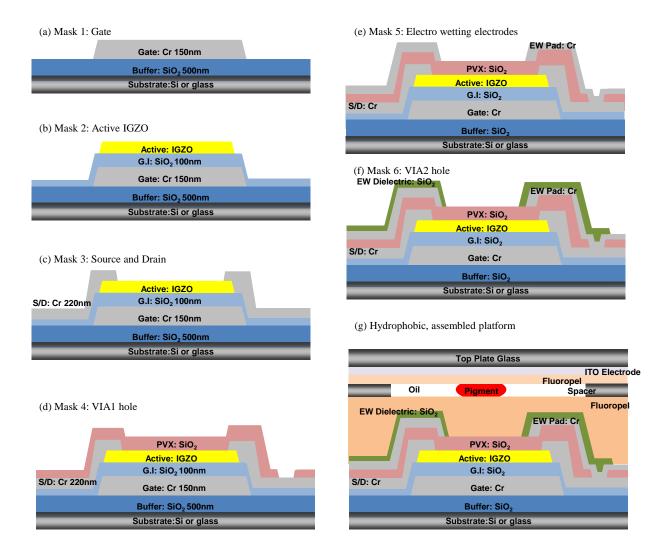

Figure 7-4. Process flows of full integration TFTs electrowetting device ......152

Figure 7-5. Sample preparation and assembly full integration device ......153

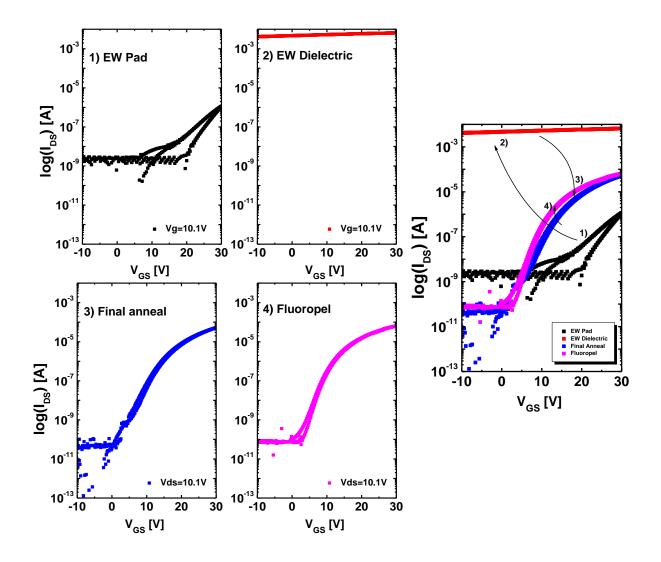

Figure 7-6. The degradation of TFT characteristics after electrowetting dielectric PECVD 350°C

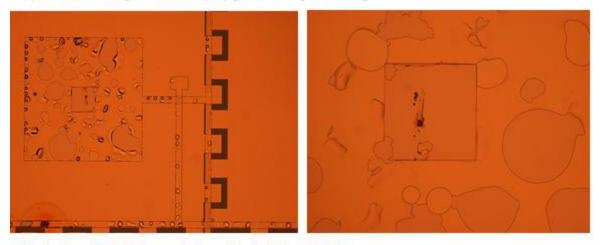

Figure 7-8. Fabrication issues of full integration TFTs electrowetting device ......159

Figure 7-9. TFT characteristics change of finally optimized the fabrication process ......160

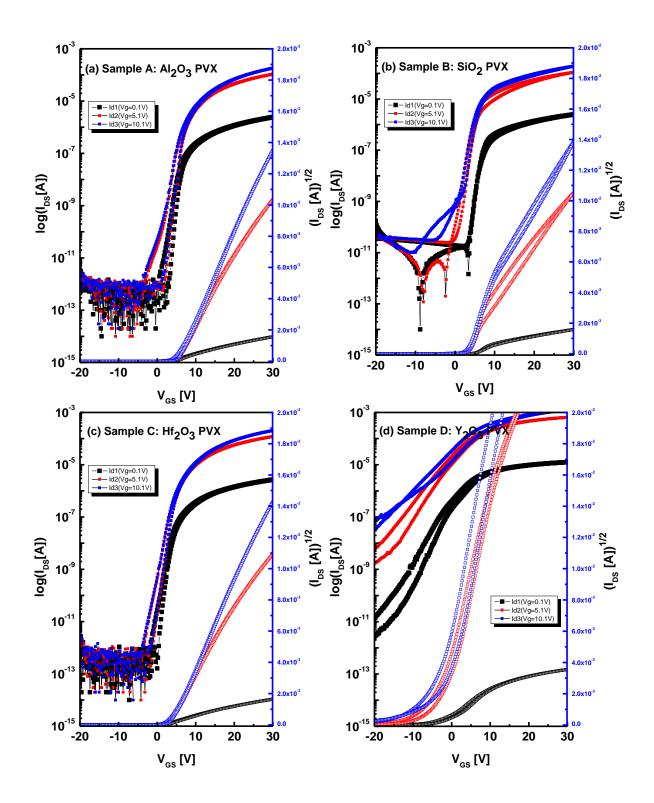

### Chapter 1

### Introduction

### 1.1 Motivation of this work

A lab on a chip (LOC) is a device that integrates one or several laboratory functions on a single chip of only millimeters to a few square centimeters in size. To control the small amount liquid in LOC devices many researchers have studied the electrowetting (EW) and electrowetting-ondielectric (EWOD) principles applied to microfluidic devices [1]. Over the past decade there has been growing the interest in the development of experimental ways for controlling small amounts of liquid, reducing the driving voltage, realizing multi-functional liquid movement, and achieving high resolution LOC devices for bio-applications [1-6]. LOCs may provide many advantages to standard alternative procedures. There is low fluid volume consumption of liquid, faster response of the system, multi-functional droplets using small amount volume, and low fabrication cost. Although they have many advantages for LOC device, they have limitations of high resolution device for driving multi-functional droplet moving and real LOC device because of the number of control lines from high numbers of electrodes. To solve this limitation, we will apply to active matrix driving which has widely has been used in the flat panel display industry and integrated Indium Gallium Zinc Oxide TFTs (Thin Film Transistors) for high resolution LOC device. In this dissertation, we have focused on the optimization of thin film materials processing methods and electrical characterization of IGZO TFTs, the method of applying the active matrix driving for high resolution electrowetting LOC device, and demonstration of high resolution multi-functional microfluidic and electro wetting LOC device with fully integrated IGZO TFTs.

#### 1.2 Thin Film Transistor (TFT)

Thin film transistors (TFTs) are a special kind of field effect transistor made by depositing thin films of a semiconductor active layer as well as dielectric layer and metallic contacts over a supporting substrate. TFTs have been used as electronic switching elements to control electronic devices such as displays, semiconductors, flash memories, and so on. Currently, many researchers have studied many kinds of semiconducting layers for thin film transistor such as Sibased TFTs [7-11], metal oxide semiconductors [12-14], organic materials [15-17], and polymers [18-20]. Table 1-1 shows the comparison of TFTs characteristic made by different kinds of semiconductor layers. Conventionally, the main applications for TFTs has been flat panel display such as liquid crystal displays (LCDs) and active matrix organic light emitting displays (AMOLEDs) which are used in amorphous Si (a-Si) semiconductor layer or poly silicon (poly-Si) semiconductor layers. Recently, in commercial flat panel display industry, many demands about large size, high resolution, and low power consumption for displays necessitate new semiconductor layers instead of a-Si and poly-Si. The a-Si semiconductor layers have low field effective mobility (below than 1 cm<sup>2</sup>/Vs) and poly-Si also has a difficulty for large sized fabrication for their high temperature process and laser crystallization process. Therefore, they have a solution for metal oxide semiconductor layer instead of a-Si and poly-Si, because of their high field mobility, transparency, good uniformity, and easy fabrication at room temperature. In this dissertation we focus on the metal oxide semiconductor using a-IGZO semiconductor layer to control our electrowetting based microfluidic device.

Table 2-1. Comparison of characteristics which has different kinds of semiconductor layers in thin film transistor

|                                   | Metal Oxide<br>(a-IGZO)          | a-Si   | poly-Si     | Polymer<br>Organic |

|-----------------------------------|----------------------------------|--------|-------------|--------------------|

| Field Effect Mobility<br>(Cm²/Vs) | 10~50                            | 0.5~1  | 30~300      | Up to 0.1          |

| Process Temperature<br>(°C)       | <350°C                           | ~350°C | >450°C      | <150°C             |

| Transparency<br>(%)               | >80                              | <20    | <20         | >80                |

| Uniformity                        | Good                             | Good   | Fair        | Medium             |

| Reliability                       | $\mathrm{Low} \to \mathrm{High}$ | Low    | Medium/High | Low                |

| Fabrication Difficulty            | Easy                             | Easy   | Difficult   | Easy               |

| (# of Mask layer)                 | 5                                | 5      | (7~10)      | (4~5)              |

#### 1.2.1 Historical background of TFTs

Thin film transistors (TFTs) have been used as a capacitor and electronic computer in the past 60 years. The basic operation concept is similar those of the metal oxide semiconductor fieldeffect transistors (MOSFETs). The first operation concept of TFTs was suggested by Lilienfeld [21], Brody [22], and Heil [23]. They introduced the MOSFET and established the concept of 3terminal operation (gate, source and drain) using field driven by a capacitor. After that, the thin film transistor was demonstrated by P. K Weimer (1962) who used a top gate staggered structure with a microcrystalline cadmium sulfide (CdS) active layer [24]. Since Weimer's work, TFTs based on a wide variety of semiconductor materials including organic and polymer, and amorphous and polycrystalline materials have been developed. Nowadays, the most dominant TFT technology is based on hydrogenated amorphous silicon (a-Si:H) which was proposed by LeComber as an electronic switching device in 1979 [11]. Using amorphous silicon, lower leakage current can be achieved to apply the low current applications such as liquid crystal flat panel displays [10,25], and solar cell panels [26,27]. In addition, poly-Si based TFTs based on many kinds of crystallization methods to increase field effect mobility and improve stability of TFT characteristic such as solid phase crystallization (SPC), metal induced crystallization (MIC), and sequential lateral crystallization (SLS), and so on [7-9,28,29]. More recently, for large size, transparent and flexible flat panel display applications, metal oxide semiconductors were introduced by Hosono's group in 1994 [13].

#### 1.2.2 Basic TFT operation

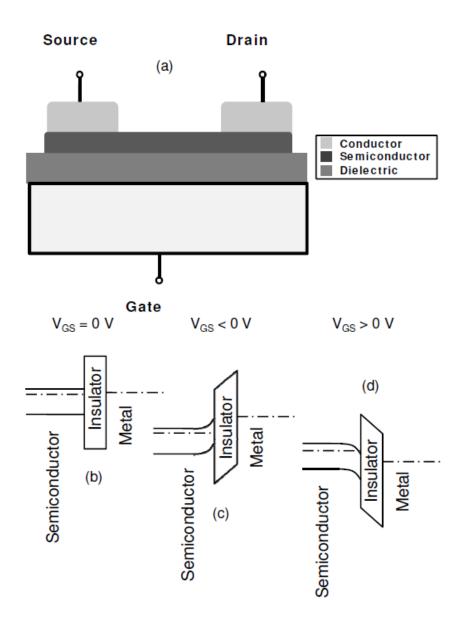

Figure 1-1 shows the basic structure of n-type semiconductor TFT and energy band diagrams with the gate bias [30]. In Figure 1-1(b), the device is in equilibrium state with 0V gate bias.

Figure 1-1(c) shows an energy band diagram with the negative bias on the gate. This applied negative bias repels the mobile electrons from channel region at the interface between semiconductor and dielectric layer. The absence of mobile electrons in channel region creates a depletion layer in the semiconductor layer. The depletion layer reduces the conductance of the semiconductor layer, and inhibits current between the source and drain. In Figure 1-1(d), when a positive voltage is applied at the gate electrode, the mobile electrons are attracted in the channel region, and results in the "accumulation mode" in the TFT device. The channel layer accumulates mobile electrons and has low resistance and high conductivity. Devices with positive gate bias results in a high current path between the source and drain electrodes. This describes the simple operation of TFT devices which are referred to as the on-state and off-state of the electronic switching device.

Figure 1-7. (a) The basic structure of TFT and corresponding energy bond diagrams as viewed through the gate for several biasing conditions: (b) equilibrium,  $V_{GS}=0$  [V], (c)  $V_{GS} < 0$  [V], and (d)  $V_{GS} > 0$  [V]

C. R. Kagan et al. "Thin-film transistors"[30]

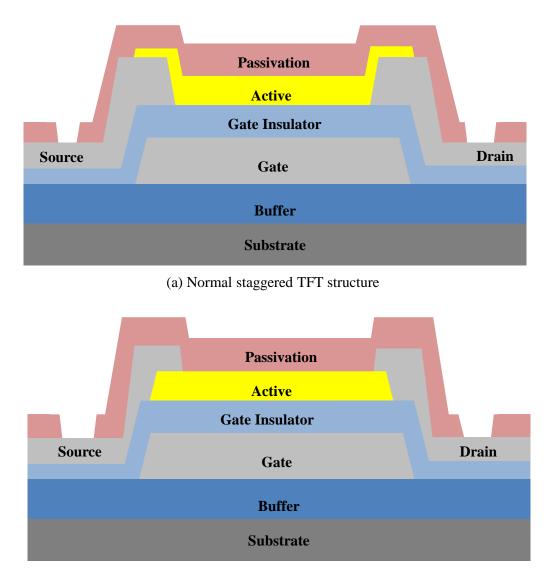

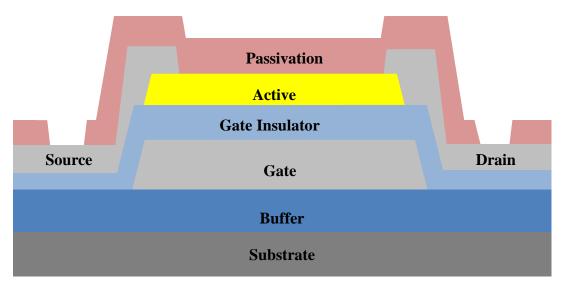

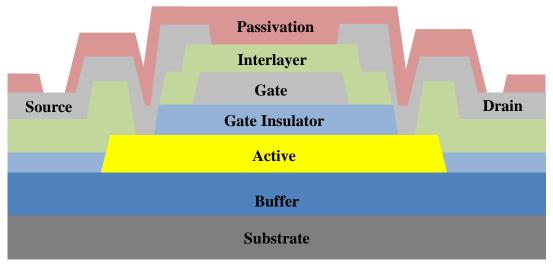

#### 1.2.3 TFT structure

There are two types of classification method for TFT structures. One is inverted or normal staggered structure of TFTs which is classified by formation of source drain electrodes (S/D). The other is top gate and bottom gate structure which changes the sequence of formation of gate electrodes. Figure 1-2 and 1-3 represent the structure of TFTs depends on S/D and gate electrodes. In Figure 1-2(a), this structure is normal staggered structure of TFTs which is proposed earlier than the inverted structure as shown Figure 1-2(b). This structure has difficulty in making ohmic contact layers between the semiconductor layer and S/D electrodes (normally in case of a-Si, n<sup>+</sup> a-Si layer is used for the ohmic contact). Furthermore, degradation of the electrical characteristics of TFTs can occur due to exposure to atmosphere and etch damage on interface between gate dielectric and a-Si layer during S/D patterning process. To enhance the TFT characteristics, this inverted TFT structure is widely used in a-Si and metal oxide semiconductor TFTs. This structure has advantage in formation n<sup>+</sup> a-Si layer for ohmic contact and inhibition from degradation of TFT characteristics during S/D formation. However this structure is very sensitive to back channel effects and damage of semiconductor layer. Figure 1-3 shows the bottom gate structure and top gate structure depending on the gate location. In Figure 1-3(a), bottom gate structure is normally used in a-Si based TFTs and metal oxide semiconductors. As already mentioned, this structure has advantage of ohmic contact and minimal degradation of TFT characteristics. However, in case of poly-Si based TFTs the bottom gate structure has limitation of gate electrode material due to high temperature process (~600°C) for crystallization of a-Si. Therefore poly-Si based TFTs normally use the top gate structure as shown Figure 1-3(b). Recently, many researchers have studied and changed the basic TFT's

structure to enhance the electric characteristics of TFT and improve its stability and reliability of biased stress, temperature stress, and time dependence.

(b) Inverted staggered TFT structure

Figure 1-8. Cross section of the various TFT structure as S/D electrodes: (a) normal staggered TFT structure (b) inverted staggered TFT structure

(a) Bottom gate TFT structure

(b) Top gate TFT structure

Figure 1-9. Cross section of the various TFT structure as gate electrodes: (a) Bottom gate TFT structure (b) Top gate TFT structure

This section discusses several important TFT figures-of-merit, threshold voltage (V<sub>th</sub>), field effective channel mobility ( $\mu_{FE}$ ), subthreshold gate swing (S.S), and on/off current ratio (( $I_D^{ON-OFF}$ ).

#### 1.2.4.1 Threshold voltage ( $V_{th}$ ) and turn on voltage ( $V_{ON}$ )

Threshold voltage,  $V_{th}$ , is an important TFT parameter indicative of the onset of drain current [31,32]. However, it is not possible to uniquely define  $V_{th}$ , which sometimes leads to ambiguous or misleading conclusion. Therefore, an alternative figure of merit for the onset of drain current, the turn on voltage ( $V_{ON}$ ), is introduced at the end of this section.  $V_{th}$  can be estimated graphically by plotting the TFT output conductance,  $g_D$ , as a function of the gate-source voltage,  $V_{GS}$ . The drain current ( $I_d$ ) is given by

$$I_{\rm D} = \mu C_I \frac{W}{L} V_{DS} V_{GS} - V_{th} - \frac{V_{DS}^2}{2} , \qquad (1.1)$$

where W is the width of the TFT, L is the length between source and drain,  $\mu$  is the mobility in the semiconductor layer,  $C_I$  is the capacitance density of the gate insulator,  $V_{DS}$  is the drainsource voltage, and  $V_{GS}$  is the gate-source voltage. Estimating  $g_D$  as the derivative of  $I_D$  with respect to  $V_{DS}$  leads to

$$g_{\rm D} = \frac{\partial I_D}{\partial V_{DS}} = \mu C_I \frac{W}{L} (V_{GS} - V_{th} - V_{DS}).$$

(1.2)

Figure 1-4(a) shows the schematic diagram for definition of  $V_{th}$ .  $G_D$ - $V_{GS}$  plot should be an extrapolation of the linear portion of this curve to the  $V_{GS}$  axis is equal to  $V_{th} + V_{DS}$ . An alternative procedure for assessing the initiation of current flow in a TFT is to employ a

log  $I_D - V_{GS}$  curve and to define a turn on voltage,  $V_{ON}$ , as the voltage which  $I_D$  begins to increase with  $V_{GS}$ . Figure 1-4(b) shows a log  $I_D - V_{GS}$  plot which represents the difference between  $V_{th}$  and  $V_{ON}$ . The other way to extract  $V_{th}$  in the transfer curve of TFTs will be extracted by extrapolating in the saturation region on the  $I_{DS}^{1/2} - V_{GS}$  characteristic plot as shown in Figure 1-4(a). In this dissertation we will use the second method to extract the  $V_{th}$  using  $I_{DS}^{1/2} - V_{GS}$ graph.

Figure 1-10. Schematic diagram for definition of  $V_{th}$ ,  $V_{ON}$ : (a) Output conductance gate to source voltage ( $g_D - V_{GS}$ ) characteristic illustration threshold voltage estimation or extract  $V_{th}$  from  $I_{DS}^{1/2}$  graph, (b) Log( $I_D$ - $V_{GS}$ ) transfer characteristics showing the turn on voltage,  $V_{ON}$ , and the threshold voltage,  $V_{th}$  for the same device

### 1.2.4.2 Field effective mobility ( $\mu_{FE}$ )

There are three methods to extract the field effect mobility of semiconductor layers[31,33]. The mobility is a measure of the mobile carrier transport in the semiconductor related to the current drive of the TFT. Average mobility ( $\mu_{AVG}$ ) is an estimate of the mobility of all carriers induced into the semiconductor by an applied gate bias, V<sub>GS</sub>. Average mobility is calculated using

$$\mu_{AVG} V_{GS} = \frac{LG_D^{LIN}(V_{GS})}{WC_l(V_{GS} - V_{ON})},$$

(1.3)

where W and L are the width and length of the TFT,  $C_1$  is the gate insulator capacitance, and  $G_D^{LIN}$  is the output conductance as a function of applied gate bias calculated in the linear region. The output conductance is evaluated at small values of  $V_{DS}$  and is calculated as

$$G_D^{\text{LIN}} V_{GS} = \frac{I_D V_{GS}}{V_{DS}} _{V_{DS} \to 0},$$

(1.4)

Incremental mobility is the mobility of charges incrementally added to the semiconductor by a corresponding incremental change in  $V_{GS}$ . Incremental mobility is calculated as

$$\mu_{\rm INC} V_{GS} = \frac{LG_D^{LIN'} V_{GS}}{WC_l} V_{DS \to 0} , \qquad (1.5)$$

where  $G_D^{LIN'} V_{GS}$  is the change in output conductance due to a corresponding change to V<sub>GS</sub>.

$$G_D^{LIN'} V_{GS} = \frac{\partial G_D^{LIN}}{\partial V_{GS}} {}_{V_{DS} \to 0}, \qquad (1.6)$$

A third mobility, saturation mobility, is extracted from a  $I_D - V_{GS}$  plot, measured with the device held in saturation. Saturation mobility is calculated as

$$\mu_{\text{SAT}} = \frac{2Lm^2}{WC_l} \sum_{V_{DS} \gg V_{GS} - V_{ON}},\tag{1.7}$$

where m is the slope of a plot of  $\overline{I_{D,SAT}}$  of  $I_D - V_{GS}$  plot. This slope is calculated as

$$m = \frac{\partial \overline{I_{D,SAT}}}{\partial V_{GS}},\tag{1.8}$$

In this study, we will extract the field effect mobility from the saturation region because this region is relatively insensitive to the magnitude of the source-drain resistance (contact resistance), and independent of  $V_{DS}$ , unlike linear region.

# 1.2.4.3 Subthreshold gate swing slope and current on/off ratio

The subthreshold swing (S.S) and the current on/off ration are estimated using a log plot of the transfer characteristics taken at high  $V_{DS}$  (i.e.  $V_{DS} > V_{DSAT} = V_{GS} - V_{ON}$ ) as shown Figure 1-5. S.S is the maximum slope in the transfer curve,

$$S.S = \left(\frac{\partial \log_{10} I_D}{\partial V_{GS}}\right)^1_{max} , \qquad (1.9)$$

S.S is very useful values of how efficiency the device turns on and is typically less than 1V/decade. Current on/off ratio ( $I_D^{ON-OFF}$ ) is a parameter for switching application and device performance. Current on/off ration is calculated as

$$I_D^{ON-OFF} = \frac{I_D^{ON}}{I_D^{OFF}},\tag{1.10}$$

The value of  $I_D^{ON-OFF}$  is usually ~10<sup>8-9</sup>.

Figure 1-11. Schematic diagrams for definition of subthreshold slope and drain current ratio  $I_D^{ON-OFF}$ .

#### 1.2.5 Metal oxide semiconductor based TFTs

# 1.2.5.1 Overview of transparent electronics and amorphous oxide semiconductors (AOSs)

The phenomenon of a material being optically transparent and electrically conductive was first observed in 1907 with a cadmium oxide film [34]. However, it was not until the 1940s that transparent conducting oxides (TCOs), specifically tin oxide (SnO<sub>2</sub>), found widespread use as electric defrosters for airplane windscreens. After that, the birth of transparent electronics using CuAlO<sub>2</sub> can be dated to the first port of a highly conductive p-type TCOs [35]. TCOs have been used for their optical properties as infrared reflecting coatings in a variety of markets including energy conserving low emissivity widows, glasses, and oven windows [36,37]. Using both its optical and electrical properties, TCOs have been an enabling technology for flat panel liquid crystal displays, touch panel displays, and the front electrodes of solar cells [36-38]. In 2003, transparent electronics development took off with the contemporaneous report of a ZnO TFT or TTFT by three groups [33,39,40]. Transparent oxide semiconductors that are attracting the most interest can be broadly divided two categories; polycrystalline oxide semiconductor (POS) such as ZnO, and amorphous oxide semiconductors (AOS) including InZnO, InSnO, ZnSnO, InZnSnO, and InGaZnO (a-IGZO) [41-44]. There materials have large Bandgap and wide controllability of carrier concentration, which can make them useful for transparent thin film transistor (TFTs) applications. In the case of POS TFTs, they have high field effect mobilities comparable to low temperature poly-silicon (LTPS) TFTs, but the polycrystalline structure have limitations for uniformity which affects the grain boundaries that can deteriorate the reproducibility. On the other hand, AOS TFTs have good uniformity and reasonably high field effect mobilities ( $\sim 10 \text{ cm}^2/Vs$ ) even though deposited at room temperature because of their

amorphous structure. From the advantages of AOS TFTs there are lots of new applications such as transparent displays using large band gap materials, flexible display using plastic or stainless substrate, large sized high resolution display in flat panel display industry. Recently, Samsung and LG electronics demonstrated a 55" FHD AMOLED display in 2013 CES conference, flexible displays, and transparent displays using amorphous Indium Gallium Zinc Oxide (IGZO) TFTs. Figure 1-6 summarized the advantages and possible application of using AOS TFTs.

Figure 1-12. Besides transparency. Amorphous AOS TFTs have additional useful characteristics to compete with existing technologies

Wager et al, "Transparent electronics" (2008) [45]

1.2.5.2 Electronic structure and carrier transport model of amorphous oxide semiconductors

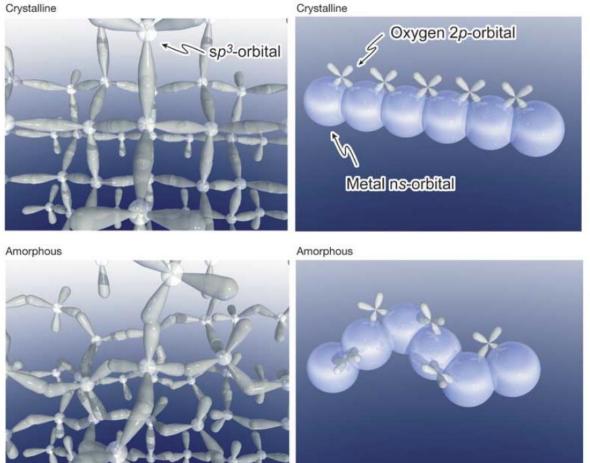

The conduction mechanism in amorphous oxide semiconductors (AOSs) is very different from that in conventional Si-based semiconductors. Usually, amorphous silicon has poor carrier transport properties ( $\sim 1 \text{ cm}^2/Vs$ ) relative to single crystalline silicon materials ( $\sim 500 \text{ cm}^2/Vs$ ). This is related to the structure and conduction mechanism between amorphous and single crystal materials. Si has a strong covalent bond, and the conduction band minimum (CBM) and valence band maximum (VBM) are made of anti-bonding  $(sp^3 \sigma^*)$  and bonding  $(sp^3 \sigma)$  states of Si hybridized orbitals, and its band gap is formed by the energy splitting of the  $\sigma - \sigma^*$  level shown by Figure 1-7(a) [46]. The mobility of a-Si:H (hydrogenated amorphous silicon) is limited to  $(\sim 1 \text{ cm}^2/Vs)$ , as carrier transport is controlled by hopping between localized tail-states and band conduction is not achieved [13]. Therefore, this hopping mechanism is strongly related to the local range order or structure, such as the strained and disordered chemical bonds from rather deep and high density of localized states below conduction band minimum (CBM) and above valence band maximum (VCM), causing the carrier trapping process. On the other hands, the amorphous oxide semiconductors have strong ionicity and charge transfer occurs from heavy metal ion to oxygen atoms shown by Figure 1-7(b). When heavy metal ions and oxygen ions comes close, charge transfer occurs due to largely different electron affinity and ionization potential (Figure 1-7(c)). In addition, the Madelung potential which comes from the difference between cations and anions by virtue of their opposing charges stabilizes the ionized states during the ionic bonding process. As a result, in Figure 1-7(c), the Madelung potential induces the energy splitting and the conduction band minimum (CBM) is occupied the 2p orbital of oxygen and the valence band maximum un-occupied by ns orbital of cations. The CBMs with large spatial sized s-orbital of heavy cations overlaps with the neighboring metal s orbital, and

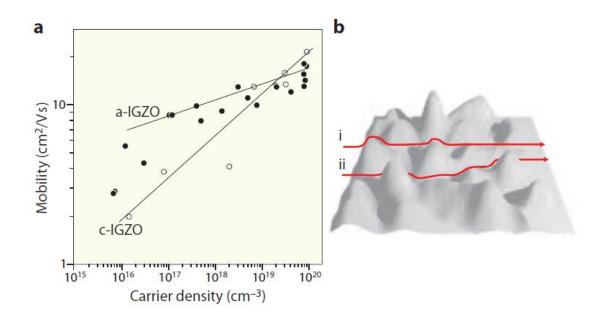

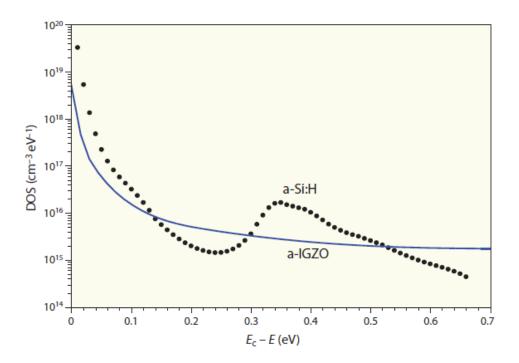

makes the conduction path for carriers which are not influenced largely by disordered local structure. This is the reason why the metal oxide semiconductors have high mobility ( $\sim 10 \text{ cm}^2$ / Vs) even though there are amorphous structure. Figure 1-8 shows the schematic drawing of the structure Si-based and metal oxide semiconductors structure. Figure 1-8(a) is the Si semiconductor layer which has the hopping mechanism to transfer the electron carriers. In single crystal structure, there is a transfer path with hopping mechanism because of the long range order in crystal structure using sp<sup>3</sup> hybridization orbitals, and have large amount of electron field mobility. However, the amorphous structure doesn't have any long range order in this structure, and electron carriers cannot move fast in this structure because of the barrier with random structure. In metal oxide semiconductor, large sized s-orbital of metal ion have an overlapping between an adjacent atoms, and there provide the current path of electron carrier. Even though there have amorphous structure in metal oxide layer, s-orbital is easy to overlap as shown Figure 1-8(b). Figure 1-9(a) demonstrates the relation between the hall mobility and carrier density in a-IGZO and c-IGZO. The hall mobility increases with carrier density, and this trend is opposite to that observed in simple crystalline semiconductors having ionized impurity scattering in highly doped semiconductor due to the percolation model [46]. The basic concept of percolation model is that there are different electron conduction path as shown Figure 1-9(b). Amorphous semiconductors have a potential fluctuation above the mobility edge and the distribution of potential barriers exists in the conduction band. These different paths cause the different conductance for the electron transmission over the potential barrier. In other words, the carrier density creates the degenerated conduction for a-IGZO and c-IGZO. Figure 1-10 shows the trap density in a-IGZO and a-Si:H. The density of states of a-IGZO near conduction band are lower than a-Si:H [47]. The low defect density in the a-IGZO layer is the reason why a-IGZO has good subthreshold slope in the transfer curve. This is therefore possible to apply the low voltage driven TFTs for having low power consumption.

Figure 1-7. Schematic electronic structures of silicon and ionic oxide semiconductors. (a–c) Bandgap formation mechanisms in (a) covalent and (b, c) ionic semiconductors. Closed and open circles denote occupied and unoccupied states, respectively.

Kamiya et al, NPG Asia Mater, Vol. 2, Pages 15-22(2010) [46]

#### а

Covalent semiconductors, for example, silicon Crystalline b

Post-transition-metal oxide semiconductors

Figure 1-8. Schematic orbital drawings for the carrier transport paths in crystalline and amorphous semiconductors. (a) Covalent semiconductors with  $sp^3$  orbitals (b) metal oxide semiconductors with s-orbital overlap of metal cation

Nomura et al, Nature, Vol. 432, Issue 7016, pages 488-492 [13]

Figure 1-9. Carrier transport in a-IGZO (a) Relationship between Hall mobility and carrier density for c-IGZO and a-IGZO (b) Illustration of percolation conduction model showing examples of (i) a shorter path and (ii) a longer winding path

Kamiya et al, Science and Technology of Advanced Materials, vol. 11, Issue 4 (2010) [48]

Figure 1-10. Subgap density of states in a-IGZO obtained by the C–V method. Data for a-Si:H are shown for comparison.

Kamiya et al, NPG Asia Mater, Vol. 2, Pages 15-22(2010) [46]

# 1.3 Electrowetting and microfluidic channel in lab on a chip device

# 1.3.1 Overview of electrowetting phenomena

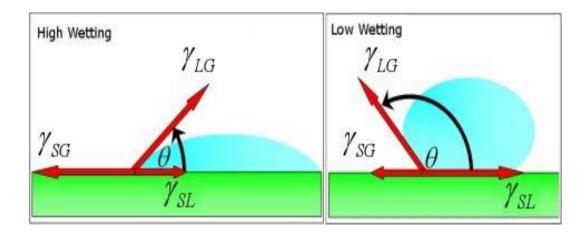

Some decades after Young's discoveries, in 1805, a French physicist named Gabriel Lippmann investigated effects of electrocapillarity using mercury, and after that Froumkin studied how surface charge changed the shape of water droplet in 1936 [49]. The term of electrowetting was introduced in 1981 to describe an effect proposed for designing a new type of display [50]. Surface tension at the interface of two materials depends on their mutual properties. The below equation is Young's equation in which the contact angle  $\theta$ , the angle created between the outer surface of the liquid and the surface on which it lies, depends on three surface tensions.

$$\gamma_{\rm LG}\cos\theta = \gamma_{SG} - \gamma_{SL},\tag{1.11}$$

The surface tension between the liquid and the air is  $\gamma_{SL}$ , between the surface and the air is  $\gamma_{SG}$ , and between the liquid and the air is  $\gamma_{LG}$ . Figure 1-11 schematically represents the relative forces operative to obtain Young's equation. In electrowetting, one is generically dealing with droplets of partially wetting liquids on planar solid substrates. Based on Lippmann's work, a term due to electro polarization was added the Young's equation.

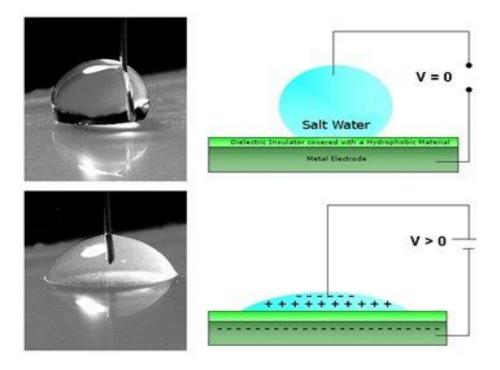

$$\gamma_{\rm LG}\cos\theta = \gamma_{SG} - \gamma_{SL} + 1/2CV^2, \tag{1.12}$$

In this Young-Lippmann equation, V is the electric voltage and C is the electric capacitance per unit area in the region of contact between the metal electrode and the drop. Therefore, the electric charges in the liquid are free to move, and the operation voltage is concentrated in different locations in droplet. The operation force on the charges within the liquid causes the contact region between drop and the metal electrode to widen, or flatten out the droplet. Figure 1-12 represents the electrowetting properties which changes the wetting angle of droplet when a voltage is applied between the liquid droplet and biased substrate. A few years ago, Bruno Berge added the insulation layer between liquid and metal electrode to overcome to electrochemical reactions during operation [51]. It is possible to control without electrical conduction between the water droplet and the metal. This method is called EWOD "Electro Wetting On Dielectric". This was a significant technical breakthrough because the electrowetting created was stable for a long period of time.

Figure 1-11. Different degrees of wetting: On the left there is high wetting and the contact angle is small. On the right side little wetting and there is a high contact angle.

Romi et al, Physicaplus, Issue 9 (2007) [52]

Figure 1-12. Liquid droplet on an insulated surface with and without applied voltage: Applying the voltage creates the wetting on the surface.

Romi et al, Physicaplus, Issue 9 (2007) [52]

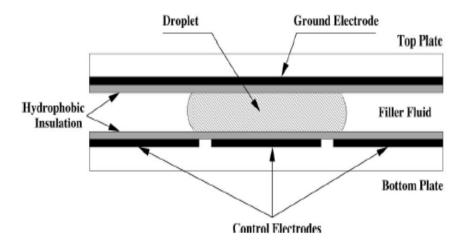

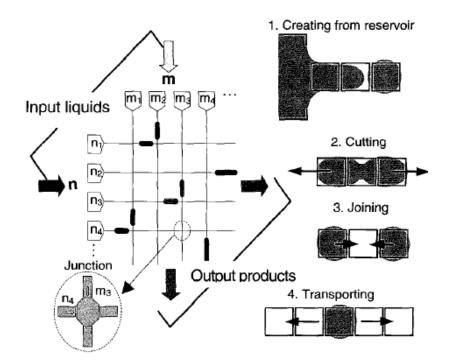

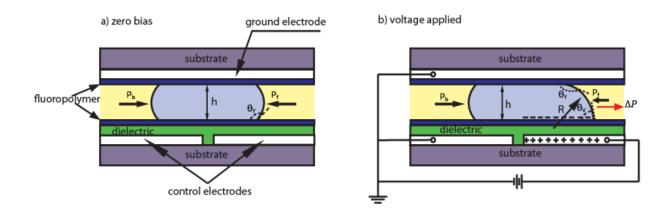

#### 1.3.2 Electrowetting on dielectric (EWOD) in a lab on a chip

Lab on a chip applications of electrowetting were mainly promoted by the laboratories of Richard Fair at Duke University [6] and Kim at UCLA [5] with several other groups joining later. Figure 1-13 shows the basic schematic EWOD structure consisting of a hydrophobic layer, insulator and metal electrodes. The principal of EWOD is to provide a substrate with electrode arrays allowing for moving droplets along an arbitrary path with a programmable activation sequence of the electrodes. Several operations can be performed including splitting, merging, mixing and forming microfluidic channel [3]. The actuation of a liquid droplet depends on the applied voltage of electrodes and capacitance of dielectric layer, and hydrophobic layer. Currently, many researchers have reported the various aspects of EWOD. The limitation of high voltage of EWOD driving can be overcome by thinning the dielectric layer on an EWOD to lower voltage driving of electrowetting, improve the wettability of liquid, and hydrophobic layer [1,3,4,6]. As this effort of electrowetting technology, the improvement of droplets moving speed on EWOD can be adopted for multi-functional moving and micro-channel devices. Figure 1-14 shows four fundamental droplet manipulation mechanisms in a digital microfluidic circuit [5]. With this kind of liquid handling technique a general electrowetting LOC device can be controlled by pressure control as well as electrowetting techniques.

Figure 1-13. Schematic diagram of a typical lab on a chip device: EWOD consist of metal electrode, insulator layer (dielectric), and hydrophobic layer on top and bottom plates. Pigment droplet which is filled with oil lay on between top and bottom electrodes.

Cho et al, Journal of Microelectromechanical Systems, vol.12, issue1, p70-80 (2003) [3]

Figure 1-14. Envisioned digital microfluidic circuit and the four fundamental droplet operations necessary

Cho et al, Journal of Microelectromechanical Systems, vol.12, issue1, p70-80 (2003) [3]

# Chapter 2

## **Device Fabrication and characterization**

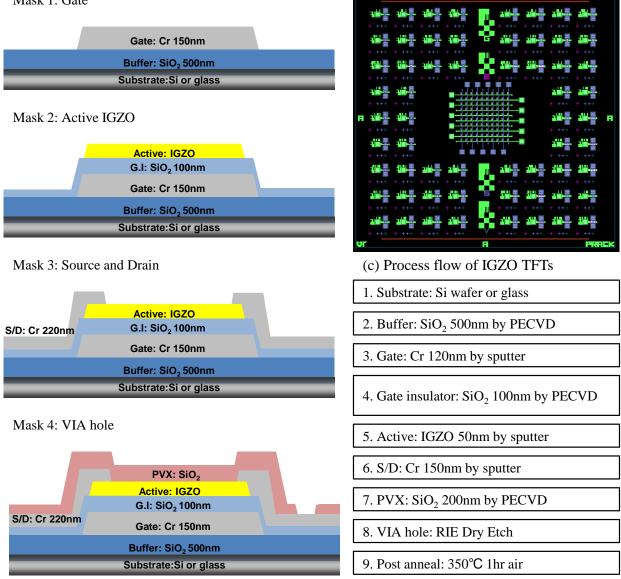

# 2.1 Fabrication of IGZO TFTs

In this study, we are focused on the inverted staggered bottom gate structure which is normally used in a-IGZO TFT structure. This structure has the below advantages: 1) protects the interface between gate dielectric and semiconductor layer without any exposure of external atmosphere 2) improve the contact resistance between IGZO layer and source drain electrodes 3) reduce the number of masks for IGZO TFTs. Figure 2-1 shows the schematic the inverted staggered bottom gate structure of IGZO TFTs with passivation layer, mask design of IGZO TFTs, and process flow of IGZO TFTs. We normally use 4 masks for IGZO TFTs. To test IGZO TFTs we have different sizes of TFTs, test elements group (TEG pattern) in our layout design. In this section we explain the fabrication methods and conditions of each step for TFTs and electrowetting devices.

(a) Schematic structure of IGZO TFTs

Mask 1: Gate

Figure 2-1. The schematic structure of IGZO TFTs (a) Schematic structure of IGZO TFTs with process sequence (b) Layout design of IGZO TFTs (c) Process flow chart of IGZO TFTs

(b) Layout design of IGZO TFTs

TJH 문

#### 2.1.1 Gate electrode

The selection of metal electrode material for gate electrode must consider several factors. First of all, a low resistivity gate is essential for high speed operation and low power consumption because of RC delay for TFT operation. Low resistivity gate electrodes reduce the charging time to the gate dielectric layer and affect the inducing time in semiconductor layer. The resistance of metal line must be sufficiently low from the following equation,

$$\mathbf{R} = \rho \frac{L}{A} = \rho \frac{L}{Wd} = \frac{\rho}{d} \frac{L}{W} = R_s \frac{L}{W},$$

(2.1)

Where  $\rho$  resistivity of metal electrode, *L* and *W* are the length and the width of metal line, the *d* is the thickness of metal thin film, and *R<sub>s</sub>* is the sheet resistance. Table 2.1 shows the electrical properties of different metals [53]. In this study, chromium (Cr) was used for gate electrode because it has reasonably low resistivity, as well as high selectivity during fluorine based plasma etching (SF<sub>6</sub>) during VIA hole etch process. In addition, chromium has a good thermal stability compared to aluminum and copper electrodes. Usually, the chromium gate layer deposited by rf magnetron sputter with DC substrate bias of 5W(125~126V) at 5mTorr working pressure using Ar gas which has the electrical properties of chromium layer in Figure 2.2 [54]. In our condition, chromium has 1.85X10<sup>-5</sup>*ohm* · *cm* and deposition rate of Cr is 3.0nm/min. The chromium layer is lithographically pattered using wet chemical etchant including Ceric Ammonium Nitrate and Acetic Acid diluted by water (22% Ce(NH<sub>4</sub>)<sub>2</sub>(NO<sub>3</sub>)<sub>6</sub> + 9% CH<sub>3</sub>COOH +69% H<sub>2</sub>O). The wet etch mechanism is the below process.

$$\mathrm{HClO}_4 \to H^+ + ClO_4^-, \tag{2.2}$$

$$\operatorname{Cr} + 6\operatorname{Ce}_{4}^{+} + 4H_{2}O \to CrO_{4}^{2-} + 6Ce_{3} + 8H^{+},$$

(2.4)

The etch rate is ~66.7nm/min at a room temperature without agitation, and for 150nm chromium requires  $150 \sim 160$  sec which includes a 20% over etch time. The wet etch process is an isotropic etch which creates sidewalls with a typically shallow edge (~45°). This is ideal for good step coverage for the next thin dielectric SiO<sub>2</sub> layer. Figure 2-2 represents the SEM image of chromium gate and SiO<sub>2</sub> gate dielectric layer which has good step coverage.

| Metal | Resistivity<br>at 20-25°C<br>(μΩ-cm) | Temperature Coefficient<br>Resistance<br>(10 <sup>-3</sup> °C) |

|-------|--------------------------------------|----------------------------------------------------------------|

| Ag    | 1.59                                 | 4.100                                                          |

| Al    | 2.65                                 | 4.290                                                          |

| Au    | 2.35                                 | 4.000                                                          |

| Cr    | 12.90                                | 3.000                                                          |

| Cu    | 1.67                                 | 6.800                                                          |

| Ir    | 5.30                                 | 3.925                                                          |

| Мо    | 5.20                                 | -                                                              |

| Nb    | 12.50                                | -                                                              |

| Pt    | 10.60                                | 3.927                                                          |

| Та    | 12.45                                | 3.830                                                          |

| Ti    | 42.00                                | -                                                              |

| W     | 5.65                                 | -                                                              |

Table 2-1. Resistivity of different metals at 20-25°C, and temperature coefficient resistance

Figure 2-2. SEM images of TFTs represent the step coverage of gate insulator on Cr gate electrode

#### 2.1.2 Gate insulator

Silicon dioxide (SiO<sub>2</sub>) has been widely used as a gate dielectric layer of thin film transistor devices. In metal oxide semiconductors the gate dielectric requires a high electrical resistance to minimize gate leakage current at the overlapped area of S/D, and high compatibility to semiconductor layer such as interface properties and interface reactions. Many researchers have studied the optimized gate insulator layer using different gate dielectric layers such as SiO<sub>2</sub>, SiN<sub>x</sub>, Al<sub>2</sub>O<sub>3</sub>, ATO (Al<sub>2</sub>O<sub>3</sub>TiO<sub>2</sub>) [55-59]. In this study, SiO<sub>2</sub> (100nm) gate dielectric material is deposited by plasma enhanced chemical vapor deposition (PECVD). The standard deposition condition of PECVD SiO<sub>2</sub> film is 20W RF power, 1000mTorr pressure, 5% SiH<sub>4</sub>-Ar/N<sub>2</sub>O (85/157sccm) gas flow, and 350°C temperature. The deposition rate is 68.9nm/min. Figure 2-3 shows the leakage current of different gate dielectric layers are deposited by rf sputter.

All thicknesses of dielectric layers are 200nm and the electrode area is  $3.24 \times 10^{-6}$  cm<sup>2</sup>. In case of

SiO<sub>2</sub> layer the current density (J) has below  $10^{-8}$ A leakage current up to 15MV/cm and the capacitance of SiO<sub>2</sub> layer is about 8.0pF in this sample (Figure 2-3(d) represents only Al<sub>2</sub>O<sub>3</sub>, SiO<sub>2</sub>, SiN<sub>x</sub> dielectric. In case of TiO<sub>2</sub> and aluminum-titanium oxide (ATO) dielectric we cannot measure the capacitance because of the high leakage current.). This is a good dielectric property of IGZO TFT, and also have good hysteresis characteristic in transfer curve of IGZO TFT. Figure 2-4 shows the hysteresis of transfer curve of IGZO TFTs with SiO<sub>2</sub> and SiN<sub>x</sub> gate insulator. As we can see the transfer curves of SiO<sub>2</sub> and SiN<sub>x</sub>, hysteresis of SiO<sub>2</sub> dielectric layer is smaller than that of SiN<sub>x</sub> (less than 1V of SiO<sub>2</sub>, ~5V of SiN<sub>x</sub>), and V<sub>th</sub> represents ~10V of SiO<sub>2</sub> and ~20V of SiN<sub>x</sub>. Based on these results, we choose the SiO<sub>2</sub> gate dielectric layer for our full integrated TFT - electrowetting devices.

Figure 2-3. I-V characteristics, J-V characteristics, J-E characteristics, and capacitance of different gate insulator layers ( $Al_2O_3$ ,  $SiO_2$ ,  $SiN_x$ ,  $TiO_2$ , and ATO)

Figure 2-4. Transfer hysteresis curves of different gate dielectric layers

#### 2.1.3 Semiconductor layer

As already mentioned the chapter 1, a-IGZO ( $In_2O_3Ga_2O_3ZnO=1:1:1 \mod \%$ ) is used as the semiconductor layer in our device, and normally a-IGZO is very sensitive to the deposition condition because the oxygen vacancy concentration controls the carrier concentration. During rf magnetron reactive sputtering with Ar and O<sub>2</sub> mixture gas, the total carrier concentration is determined by the oxygen partial pressure. In this study, we already optimized the deposition condition which is rf power 97W, pO<sub>2</sub> 40%, and working pressure 5mTorr. In this condition the deposition rate of IGZO film has 1.18nm/min. The a-IGZO was patterned by a wet etch process using the 0.01% diluted buffer oxide etchant solution (based on HF). The a-IGZO 50nm was completely etched after ~30sec including 20% over etch time; the etch rate is around 120nm/min. In this study, we include the basic characteristics of the IGZO layer and the effects of the sputter deposition conditions in the next chapter 3.

### 2.1.4 Source and Drain electrode

Chromium was mainly used for the source and drain electrode in our study. In the TFT device, the total turn-on resistance ( $R_{total}$ ) of the thin film transistor (TFT) is expressed as

$$R_{\text{total}} = R_S + R_{CH} + R_D, \tag{2.5}$$

where  $R_S$  is the resistance associated with the source contact,  $R_D$  is the resistance associated with the drain contact, and  $R_{CH}$  is the channel resistance of semiconductor layer. Figure 2-5 shows the schematic diagram the turn-on resistance of TFTs. There are many factors to select the source drain electrode of a-IGZO semiconductor and many researchers have reported the contact issues for different materials of source drain electrodes [60-67]. First of all, the work function of the metal is key factor that controls the so-called Schottky barrier height and contact resistance of the metal on semiconductor which is related flat band and threshold voltages of the metal oxide semiconductor device. The occurrence of the Schottky barrier between the metal and semiconductor arises due to the requirement that the Fermi levels in the two materials match up. Such a barrier to charge transfer between the metal and the semiconductor is the result of the unequal work functions of these materials. We can predict the contact and behavior between the metal and semiconductor by comparing the work functions. Table 2-2 lists the selected values of the work function of the metals of interest [53]. Figure 2-6 shows the schematic band diagram which creates the bend bending between the semiconductor layer and metal electrodes [68]. The work function of a-IGZO films have a reported value from 4.3eV~5.01eV [69]. In this study, chromium (Cr) or Ti/Au metal layers are used as source/drain electrodes in our TFTs because of its relative low resistivity, ohmic contact between IGZO and S/D electrode, and high etch selectivity between IGZO and Cr electrode during S/D wet etch. The Cr source/drain electrode is deposited 200nm thick by rf magnetron sputter with substrate bias 5V to decrease resistivity and film stress (as already reported chapter 2 gate electrode section), and patterned by wet etching using Cr etchant, which has selectivity of Cr/a-IGZO=13 [70].

Figure 2-5. Schematic diagram the S/D contact resistance between S/D and IGZO layer, and channel resistance of IGZO layer

Figure 2.6 Band diagram the match-up between S/D metal and semiconductor layer (a) metal and n-type semiconductor before contact (b) metal and n-type semiconductor after contact (c) metal and n-type semiconductor contact with reverse bias (d) metal and n-type semiconductor with forward bias

# D.A. Neamen et al, "Semiconductor Physics and Devices" [68]

|       | Work Function                |

|-------|------------------------------|

| Matal |                              |

| Metal | $\mathbf{\Phi}_{\mathrm{m}}$ |

|       | (eV)                         |

| Ag    | 4.73                         |

| Al    | 4.08                         |

| Au    | 4.82                         |

| Cr    | 4.60                         |

| Cu    | -                            |

| Co    | 4.40                         |

| Mo    | 4.20                         |

| Nb    | 4.01                         |

| Pt    | 5.34                         |

| Та    | 4.19                         |

| Ti    | ~4                           |

| W     | 4.52                         |

Table 2-2. Work function of different metals

#### 2.1.5 Passivation layer

A passivation layer in a TFT commonly has been used to protect the device from subsequent post processing and the external environment. In case of AOSs, the passivation layer affects the electrical characteristics of TFTs and the stability because of the sensitive back-channel effects of semiconductor layer. This topic will be studied in detail in chapter 4. We deposit the different passivation materials (such as SiO<sub>2</sub>, SiN<sub>x</sub>, Hf<sub>2</sub>O<sub>3</sub>, Al<sub>2</sub>O<sub>3</sub>, and Y<sub>2</sub>O<sub>3</sub>) using different deposition methods. We optimize the material of passivation layer and deposition method, and we investigate the mechanism why and how the passivation layer affects the electronic characteristics of a-IGZO TFTs. Currently our standard process of passivation layer consists of a 200nm SiO<sub>2</sub> which is deposited by 200°C PECVD process. After photolithographic patterning, in order to contact the gate and S/D electrodes we etch the VIA hole process using RIE dry etch using SF<sub>6</sub> + Ar gas chemistry.

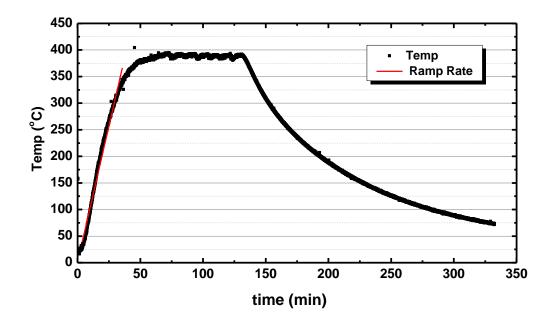

#### 2.1.6 Post annealing for TFTs activation

The a-IGZO TFTs are typically thermally activated by furnace annealing in an  $N_2$  or air ambient to recover the electronic characteristics of TFTs during the process steps. The post annealing effect on the a-IGZO TFT have been reported based on different atmosphere, temperature and time [71-73]. In this study we takes the post annealing in  $N_2$  or air atmosphere of 350°C 1hr. The temperature ramping rate is ~ 10°C/min in tube furnace or ~15°C/min in box furnace and cool down to room temperature. Figure 2-7 represents a standard temperature profile during the post annealing. In chapter 4, we investigate the effect of different atmospheres during the post annealing process. Currently, the whole process of IGZO TFTs is mentioned the above. Figure 2-8 represents the SEM image of our TFT samples including the cross sectional SEM images.

Figure 2-7. Micro oven temp history during the post annealing in air atmosphere

Figure 2-8. SEM images of IGZO TFTs, (a) Overview of IGZO TFT, (b) Channel area, and (c) Cross sectional SEM images of IGZO TFTs

2.2 Fabrication of the lab on a chip system which is fully integrated on the IGZO TFTs array

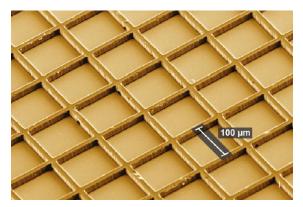

In this section, we introduce the design of electrodes for electrowetting on dielectric device (EWOD) and the fabrication of the EWOD device. As mentioned the chapter 1, the electrowetting device consists of a bottom and top plate. Bottom plates are fabricate on a glass substrate, with the electrowetting electrode of Al or Cr layer using rf sputter or e-beam evaporation and is connected to the applied voltage for droplet actuation. The electrowetting dielectric is normally a 200nm thick SiO<sub>2</sub> layer deposited by PECVD. After that, we coat the hydrophobic layer (Fluoropel 0.5um) with a dip coater, and cure this layer at 190°C 30min on a hot plate. The top plate consists of a 100nm ITO layer (In<sub>2</sub>O<sub>3</sub>SnO<sub>2</sub>, 10wt % SnO<sub>2</sub>) which is connected to ground. A thin hydrophobic layer coating (Fluoropel 0.5um) is also deposited onto the ITO layer to make it hydrophobic. The deposition condition of ITO layer is pO<sub>2</sub> 3.8%, working pressure 5mtorr, rf power 150W, and deposition rate is about 6.06nm/min. An aqueous solution is mixed with a pigment (a 10 wt % red pigment with 0.01 wt% of sodium lauryl sulfate was dispersed in the fluid) and insulating silicone oil (Dow Corning OS-30 oil) is infiltrated into the gap between the plates. Figure 2-9 shows the layout and cross section schematic drawing of electrowetting device.

Figure 2-9. The whole layout of electrowetting device, (a)  $5 \times 2$  electrodes device, (b) Electrode shape, and (c) Cross section view

# Chapter 3

### Basic characteristics and generalization of IGZO layer

3.1 Channel resistance and contact resistance

## 3.1.1 Introduction

In this chapter we investigate the basic characteristics of amorphous indium gallium zinc oxide layer as used by semiconductor layer in our TFTs. In previous works, we reported the electrical resistivity of IGZO layer with oxygen partial pressure, optical properties compared with free carrier concentration, surface roughness, and basic structural studies of IGZO layers with annealing temperature dependence. Based on previous studies, we developed the optimized condition of IGZO semiconductor layer using rf magnetron sputter. In this study we investigate the channel resistivity and contact resistance of IGZO TFTs between S/D and IGZO layer when TFT is in the ON state. In addition, we investigate which resistance component of TFT channel layer is dominant for driving our IGZO TFTs.

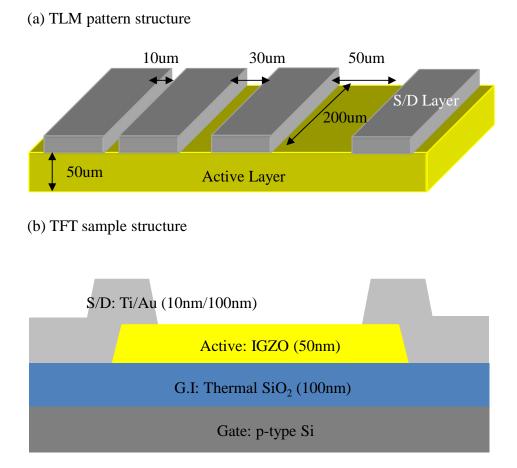

#### 3.1.2 Experiments

Figure 3.1 shows the schematic drawing of transmission line method (TLM) pattern and structure of IGZO TFTs. For the TFT fabrication we use the common gate with heavy doped p-type Si wafer, and then 100nm SiO<sub>2</sub> 100nm grown by LPCVD as the gate insulator layer. The a-IGZO active layer (50nm) is deposited with  $pO_2 = 40\%$  at fixed total gas flow rate (25sccm) and rf power 97W during sputtering. The source/drain electrodes are Ti/Au (10nm/100nm) evaporated by e-beam evaporation, and patterned by lift-off process. Finally, the post annealing was  $350^{\circ}$ C1hr at N<sub>2</sub> atmosphere. After annealing process we measured the TFT electrical

characteristics in TLM pattern with different size electrodes, and I-V characteristics between different size patterns to extract the channel resistivity and contact resistance.

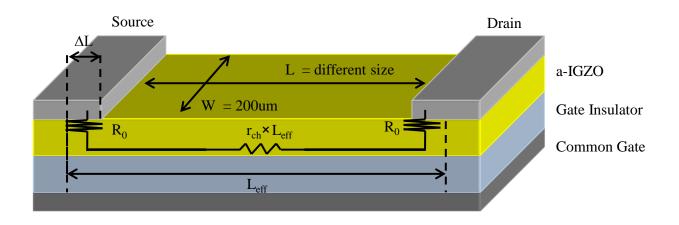

Figure 3-1. Schematic diagram for TLM pattern and TFT structure: (a) Transmission line method (TLM) Pattern, (b) Structure of IGZO TFTs

#### 3.1.3 Results and discussion

The electric characteristic of IGZO TFTs is the extraction of the total TFT ON resistance ( $R_T$ ) and the source/drain (S/D) contact resistance using transmission line analysis method (TLM) [74]. In Figure 3-2, the term "channel length (L)" is defined as the physical distance between the source and drain electrodes. However, the actual current in the channel cannot be addressed in an edge of S/D contacts. The real current path needs to extend a distance under the S/D electrodes which is usually recognized as channel length bias ( $\Delta L$ ). The total TFT ON resistance ( $R_T$ ) can be described by

$$R_T = \frac{v_{DS}}{i_D} = R_S + R_D + r_{ch} \cdot L, \tag{3.1}$$

where  $r_{ch}$  is the TFT channel resistance per unit length,  $R_S$  and  $R_D$  are contact resistance of source electrode and drain electrode. From the general MOSFET equation, the drain current represents by

$$I_{\rm D} = \frac{W}{L} \cdot C_{OX} \cdot \mu \cdot (V_{GS} - V_{th}) \cdot V_{DS}, \qquad (3.2)$$