### University of Tennessee, Knoxville

# TRACE: Tennessee Research and Creative Exchange

**Doctoral Dissertations**

**Graduate School**

12-2012

# A Charge-Recycling Scheme and Ultra Low Voltage Self-Startup Charge Pump for Highly Energy Efficient Mixed Signal Systems-On-A-Chip

Chandradevi Ulaganathan culagana@utk.edu

Follow this and additional works at: https://trace.tennessee.edu/utk\_graddiss

Part of the Electrical and Electronics Commons, and the VLSI and Circuits, Embedded and Hardware Systems Commons

### **Recommended Citation**

Ulaganathan, Chandradevi, "A Charge-Recycling Scheme and Ultra Low Voltage Self-Startup Charge Pump for Highly Energy Efficient Mixed Signal Systems-On-A-Chip. " PhD diss., University of Tennessee, 2012. https://trace.tennessee.edu/utk\_graddiss/1593

This Dissertation is brought to you for free and open access by the Graduate School at TRACE: Tennessee Research and Creative Exchange. It has been accepted for inclusion in Doctoral Dissertations by an authorized administrator of TRACE: Tennessee Research and Creative Exchange. For more information, please contact trace@utk.edu.

To the Graduate Council:

I am submitting herewith a dissertation written by Chandradevi Ulaganathan entitled "A Charge-Recycling Scheme and Ultra Low Voltage Self-Startup Charge Pump for Highly Energy Efficient Mixed Signal Systems-On-A-Chip." I have examined the final electronic copy of this dissertation for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Doctor of Philosophy, with a major in Electrical Engineering.

Benjamin J. Blalock, Major Professor

We have read this dissertation and recommend its acceptance:

Charles L. Britton, Jeremy Holleman, Xiaobing Feng

Accepted for the Council:

Carolyn R. Hodges

Vice Provost and Dean of the Graduate School

(Original signatures are on file with official student records.)

# A Charge-Recycling Scheme and Ultra Low Voltage Self-Startup Charge Pump for Highly Energy Efficient Mixed Signal Systems-On-A-Chip

A Dissertation

Presented for the

Doctor of Philosophy Degree

The University of Tennessee, Knoxville

Chandradevi Ulaganathan December 2012 Copyright © 2012 by Chandradevi Ulaganathan

All rights reserved

To my parents

& AT

# Acknowledgements

I would like to express my sincere gratitude to my advisor Dr. Benjamin J. Blalock whose constant support, guidance and patience helped me in completing this dissertation. I'm thankful to him for providing me with employment at the Integrated Circuits and Systems Laboratory (ICASL) for the past 6 years. Dr. Blalock's tireless efforts to secure funding for cutting-edge research are very much appreciated. I also thank him for fostering a collaborative atmosphere in the lab and for giving me the freedom to pursue my interests.

I'm grateful to Dr. Charles L. Britton for his valuable advice, help and for being a source of inspiration during this research. I wish to thank Dr. Jeremy Holleman and Dr. Xiaobing Feng for serving on my committee and providing me with helpful suggestions and encouragement throughout this work. I thank Dr. Bimal K. Bose for his support and mentoring during my graduate studies. I'm grateful to Ryan Lind, Clif Jones and the Home Audio Amplifiers group at TI for their support.

I would like to thank all my current and former colleagues in ICASL for their support. It has been a great pleasure working with you. I'm grateful to Drs. Neena Nambiar, Suheng Chen and Robert Greenwell for their encouragement, friendship and support. In addition, I would like to thank Pollob, Junjie and Kai for their help with the chip submissions. I wish to thank the administrative and the IT staff at the Department of Electrical Engineering and Computer Science for all their help.

I wish to express my deepest gratitude to my friends Aparna Thyagarajan, Ezhilarasi Manickavasagam, Sukanya Iyer, Sangeetha Swaminathan, Srivatsan Sundararajan, Ankit Master and Anton D'Silva. I'm grateful to Lalitha Aunty for her unconditional love and support.

Most importantly, I wish to thank my parents Mrs. Saroja and Mr. Ulaganathan, and my sisters Arthi and Vaishnavi, for their unconditional love, support and faith in me. I'm eternally grateful to you for all the difficult decisions that you have made to help me realize my dreams.

### **Abstract**

The advent of battery operated sensor-based electronic systems has provided a pressing need to design energy-efficient, ultra-low power integrated circuits as a means to improve the battery lifetime. This dissertation describes a scheme to lower the power requirement of a digital circuit through the use of charge-recycling and dynamic supply-voltage scaling techniques. The novel charge-recycling scheme proposed in this research demonstrates the feasibility of operating digital circuits using the charge scavenged from the leakage and dynamic load currents inherent to digital design. The proposed scheme efficiently gathers the "ground-bound" charge into storage capacitor banks. This reclaimed charge is then subsequently recycled to power the source digital circuit.

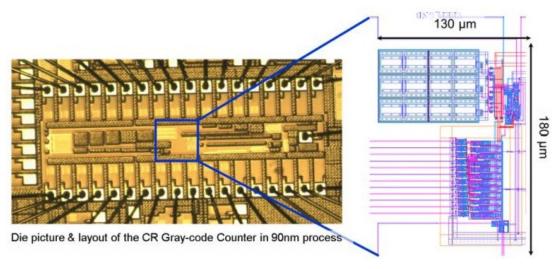

The charge-recycling methodology has been implemented on a 12-bit Gray-code counter operating at frequencies of less than 50 MHz. The circuit has been designed in a 90-nm process and measurement results reveal more than 41% reduction in the average energy consumption of the counter. The total energy savings including the power consumed for the generation of control signals aggregates to an average of 23%. The proposed methodology can be applied to an existing digital path without any design change to the circuit but with only small loss to the performance. Potential applications of this scheme are described, specifically in wide-temperature dynamic power reduction and as a source for energy harvesters.

The second part of this dissertation deals with the design and development of a self-starting, ultra-low voltage, switched-capacitor (SC) DC-DC converter that is essential to an energy harvesting system. The proposed charge-pump based SC-converter operates from 125-mV input and thus enables battery-less operation in ultra-low voltage energy harvesters. The charge pump does not require any external components or expensive post-fabrication processing to enable low-voltage operation. This design has been implemented in a 130-nm CMOS process. While the proposed charge pump provides significant efficiency enhancement in energy harvesters, it can also be incorporated within charge recycling systems to facilitate adaptable charge-recycling levels.

In total, this dissertation provides key components needed for highly energy-efficient mixed signal systems-on-a-chip.

# **Contents**

| CHAPTER 1 | INT  | RODUCTION                                                   | 1          |

|-----------|------|-------------------------------------------------------------|------------|

|           | 1.1  | Motivation                                                  | 1          |

|           | 1.2  | Research Goals                                              | 3          |

|           | 1.3  | Dissertation Overview                                       | 4          |

| CHAPTER 2 | LIT  | ERATURE REVIEW                                              | 6          |

|           | 2.1  | Introduction                                                | 6          |

|           | 2.2  | Power Consumption                                           | 6          |

|           | 2.3  | Scaling Trends for CMOS Technologies                        | 8          |

|           | 2.4  | Low Energy Design Techniques                                | 10         |

|           |      | 2.4.1 Power Supply Voltage Scaling                          | 10         |

|           |      | 2.4.2 Leakage power reduction                               | 12         |

|           |      | 2.4.3 Charge-recycling systems                              | 13         |

|           | 2.5  | Conclusion                                                  | 19         |

| CHAPTER 3 | DES  | IGN AND ANALYSIS OF THE PROPOSED                            | CHARGE     |

| RECYCLING | SCHE | EME                                                         | 21         |

|           | 3.1  | Introduction                                                | 21         |

|           |      | 3.1.1 Switching or Dynamic Power dissipation                | 22         |

|           |      | 3.1.2 Optimum power supply voltage                          | 27         |

|           |      | 3.1.3 Feasibility of Charge Recycling                       | 28         |

|           | 3.2  | Proposed Charge-Recycling Methodology                       | 29         |

|           | 3.3  | Design of the proposed charge-recycling system              | 31         |

|           |      | 3.3.1 Charge-Recycling Process – Design and Control         | 31         |

|           |      | 3.3.2 Estimation of the Charge-Recycling Capacitor Size     | 33         |

|           |      | 3.3.3 Low-Power Comparator                                  | 34         |

|           | 3.4  | Analysis of Energy Consumption in the Charge-Recycling Sc   | heme38     |

|           |      | 3.4.1 Estimation of Virtual Power Supply Voltage levels and | CR cycle39 |

|           |      |                                                             |            |

|           |        | 3.4.2 Estimation of Energy Saved using CR Scheme    | 45    |

|-----------|--------|-----------------------------------------------------|-------|

|           | 3.5    | Implementation of the charge-recycling methodology  | 51    |

|           |        | 3.5.1 Design Methodology                            | 52    |

|           |        | 3.5.2 Physical Implementation                       | 55    |

|           | 3.6    | Simulation Results and Performance Analysis         | 58    |

|           |        | 3.6.1 Energy Saving                                 | 59    |

|           |        | 3.6.2 Effect on Circuit's Speed and Delay           | 61    |

|           |        | 3.6.3 Leakage Current Reduction                     | 63    |

|           | 3.7    | Summary and Conclusions                             | 63    |

| CHAPTER 4 | CHA    | ARACTERIZATION OF THE CHARGE-RECYCLING              | GRAY- |

| CODE COUN | ΓER    |                                                     | 65    |

|           | 4.1    | Test Setup                                          | 65    |

|           |        | 4.1.1 Power Supply Generation and Partitions on PCB | 65    |

|           |        | 4.1.2 On-board Supply Regulators                    | 67    |

|           |        | 4.1.3 Digital Buffers on PCB                        | 68    |

|           |        | 4.1.4 Reset signal generation                       | 68    |

|           | 4.2    | Test Procedure                                      | 69    |

|           | 4.3    | Measurement Results                                 | 72    |

|           |        | 4.3.1 Energy Reduction due to Charge-recycling      | 75    |

|           |        | 4.3.2 Efficiency of Charge-recycling scheme         | 81    |

|           | 4.4    | Techniques to improve the proposed CR scheme        | 84    |

|           | 4.5    | Summary and Conclusion                              | 86    |

| CHAPTER 5 | DES    | IGN & ANALYSIS OF THE ULTRA-LOW VOLTAGE             | DC-DC |

| CONVERTER | •••••• |                                                     | 88    |

|           | 5.1    | Introduction and Motivation.                        | 88    |

|           | 5.2    | Literature Review                                   | 90    |

|           |        | 5.2.1 Switched Capacitor Charge Pump topologies     | 90    |

|           |        | 5.2.2 Low voltage self-startup in converters        | 99    |

|           |        | 5.2.3 Ultra-low voltage SC converters               | 100   |

|           |        |                                                     |       |

|           | 5.3 | Design of the proposed low-voltage, self-starting DC-DC convert | er106  |

|-----------|-----|-----------------------------------------------------------------|--------|

|           |     | 5.3.1 Architecture of the Converter                             | 106    |

|           |     | 5.3.2 Choice of CP topology                                     | 108    |

|           |     | 5.3.3 Design of Ring Oscillator                                 | 109    |

|           |     | 5.3.4 Design of Non-Overlapping (NOV) phase generator           | 114    |

|           |     | 5.3.5 Design of the Proposed Linear Charge Pump (LCP)           | 115    |

|           | 5.4 | Efficiency of the Proposed Charge Pump                          | 135    |

|           |     | 5.4.1 Output voltage of the Charge Pump                         | 135    |

|           |     | 5.4.2 Input current consumption of the Charge Pump              | 140    |

|           |     | 5.4.3 Conversion Efficiency of the Charge Pump                  | 141    |

|           | 5.5 | Implementation of the DC-DC Converter                           | 142    |

|           | 5.6 | Simulation Results                                              | 143    |

|           |     | 5.6.1 LCP simulation results                                    | 145    |

|           |     | 5.6.2 Performance of the Proposed CP topology with increase in  | number |

|           |     | of CP stages                                                    | 150    |

|           | 5.7 | Summary                                                         | 152    |

| CHAPTER 6 | CHA | ARACTERIZATION OF LOW-VOLTAGE SELF-STA                          | ARTUP  |

|           |     |                                                                 |        |

|           |     | Test Setup                                                      |        |

|           | 6.1 |                                                                 |        |

|           |     | 6.1.1 Power Supply Partition & Generation on the PCB            |        |

|           | ( ) | 6.1.2 Ring Oscillator control signal generation                 |        |

|           | 6.2 |                                                                 |        |

|           | 6.3 | Prototype Characterization                                      |        |

|           |     | 6.3.1 Ring Oscillator                                           |        |

|           |     | 6.3.2 Charge Pump Output Voltage                                |        |

|           |     | 6.3.3 Charge Pump Startup Voltage                               |        |

|           |     | 6.3.4 Charge Pump Drive Capability                              |        |

|           |     | 6.3.5 Charge Pump Efficiency                                    |        |

|           | 6.4 | Techniques to improve efficiency                                |        |

|           |     | 6.4.1 Adaptive Frequency control                                | 172    |

|           |     |                                                                 | V111   |

|            |        | 6.4.2 Charge Recycling                                   | 172 |

|------------|--------|----------------------------------------------------------|-----|

|            | 6.5    | Summary and Conclusion                                   | 172 |

| CHAPTER 7  | CON    | ICLUSION                                                 | 175 |

|            | 7.1    | Original contributions                                   | 176 |

|            | 7.2    | Directions for future work                               | 176 |

|            |        | 7.2.1 Charge recycling based low power digital operation | 176 |

|            |        | 7.2.2 Charge pump                                        | 177 |

| REFERENCES | ······ |                                                          | 179 |

| VITA       | •••••  |                                                          | 187 |

# **List of Figures**

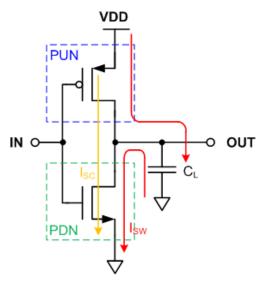

| Figure 2.1 Inverter illustrating current paths during operation                                  | 7  |

|--------------------------------------------------------------------------------------------------|----|

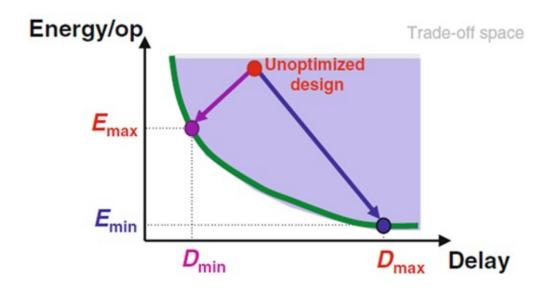

| Figure 2.2 Energy-delay optimization and tradeoff in digital circuit design [7], [8]             | 11 |

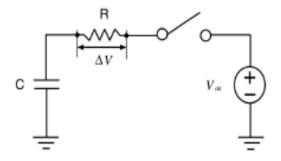

| Figure 2.3 Charging and discharging action in switch [16]                                        | 13 |

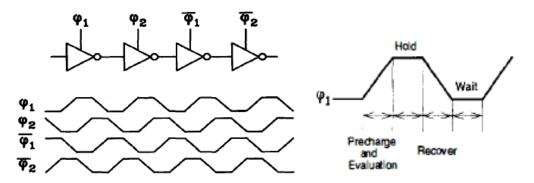

| Figure 2.4 Charging and discharging action in switch [16], [17]                                  | 15 |

| Figure 2.5 Charge recycling system based on vertically-stacked logic cells [24]                  | 16 |

| Figure 2.6 Conceptual schematic of the charge recycling scheme [26].                             | 18 |

| Figure 2.7 Conceptual schematic of charge-recycling scheme [28]                                  | 19 |

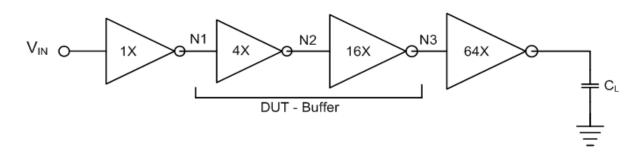

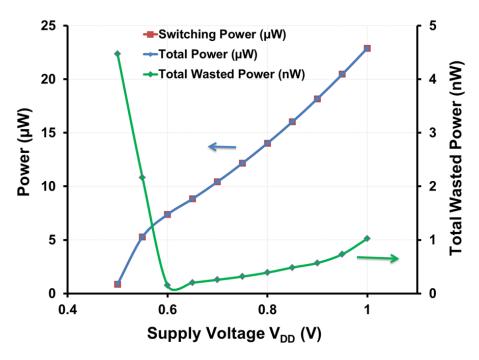

| Figure 3.1 Block level schematic of FO4 inverter stages                                          | 24 |

| Figure 3.2 NanoSim simulation results of power consumption across $V_{DD}$ variation in the FO4  |    |

| buffer                                                                                           | 25 |

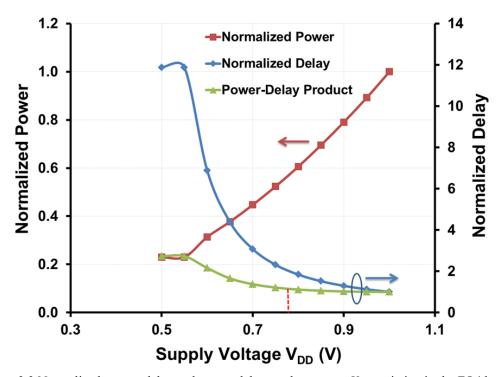

| Figure 3.3 Normalized power, delay and power-delay product across $V_{DD}$ variation in the FO4  |    |

| buffer                                                                                           | 26 |

| Figure 3.4 Block level schematic of the charge-recycling scheme                                  | 30 |

| Figure 3.5 Schematic illustrating operation during charge-accumulation phase                     | 31 |

| Figure 3.6 Schematic illustrating operation during charge-recycling phase                        | 32 |

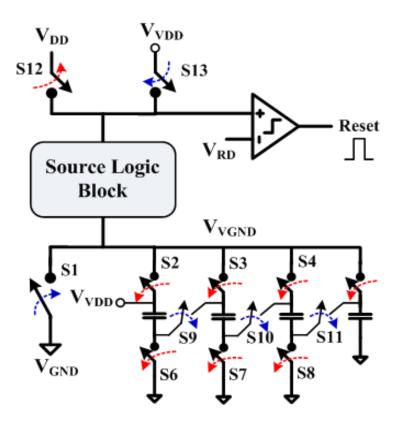

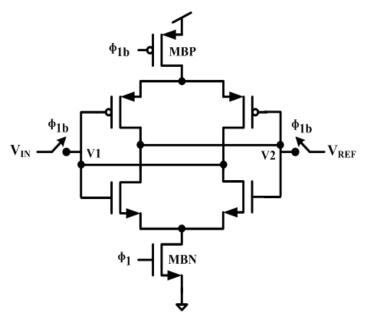

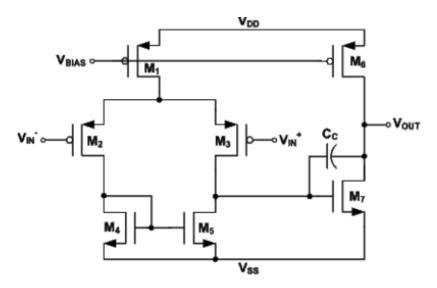

| Figure 3.7 Schematic of the low-power comparator.                                                | 35 |

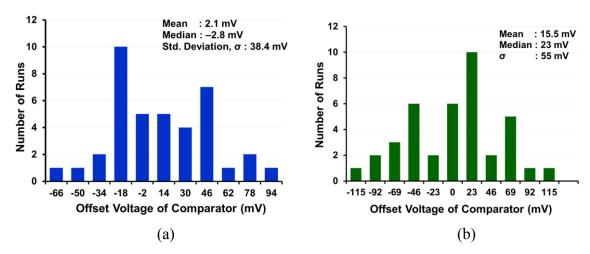

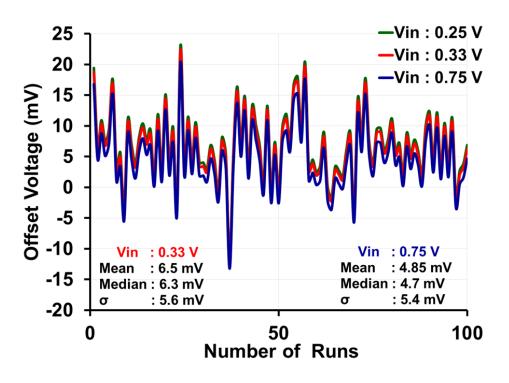

| Figure 3.8 Histogram of comparator's offset voltage distribution from Monte-Carlo simulations    | 36 |

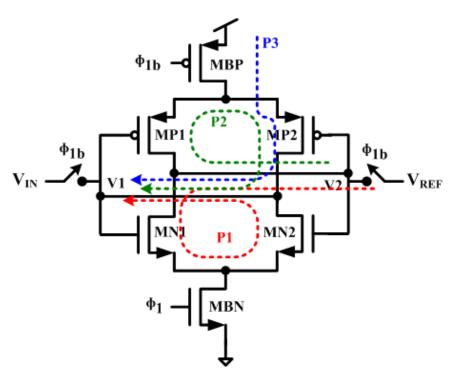

| Figure 3.9 Comparator schematic illustrating the leakage paths to be investigated                | 37 |

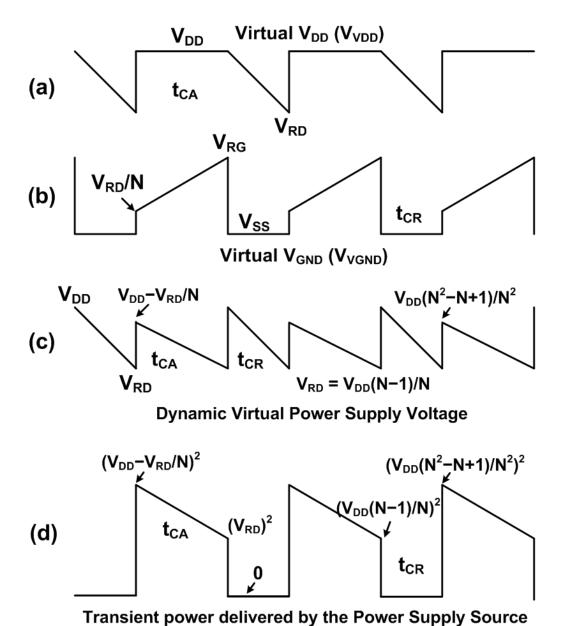

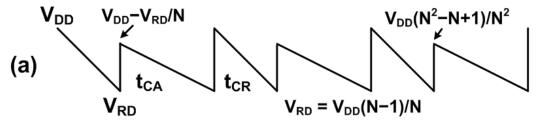

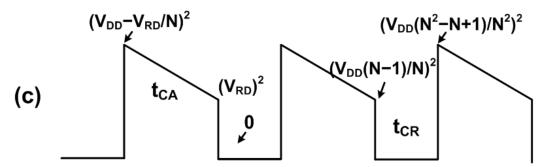

| Figure 3.10 Virtual power supply voltage levels in the charge-recycling scheme                   | 40 |

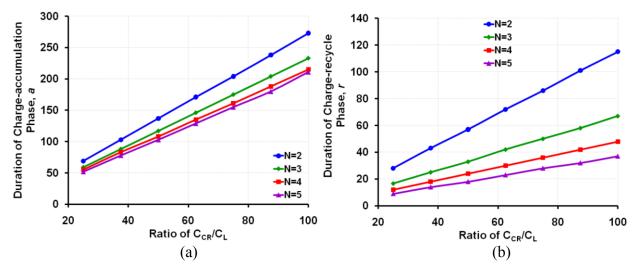

| Figure 3.11 Duration of CR cycle as a function of $C_{CR}/C_L$ across number of stages (N)       | 45 |

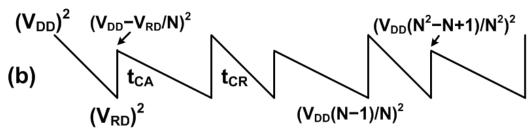

| Figure 3.12 Virtual power supply voltage levels and power consumption in the CR system           | 46 |

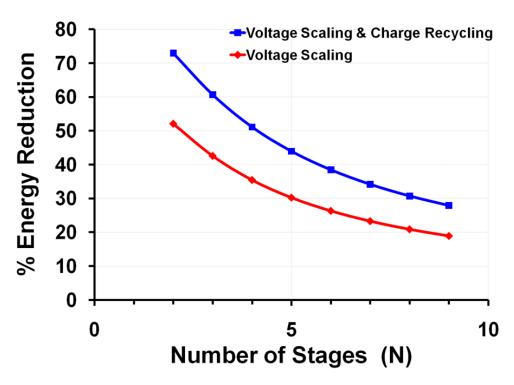

| Figure 3.13 Percentage energy saved by employing the proposed charge recycling technique         | 50 |

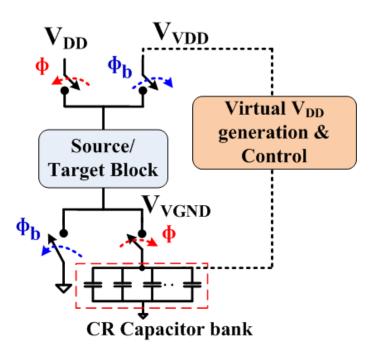

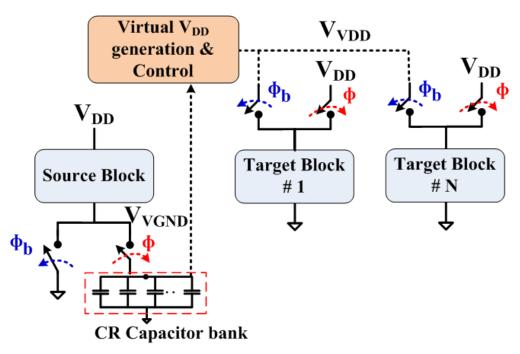

| Figure 3.14 Functional schematic of partially-self powered charge-recycling system               | 51 |

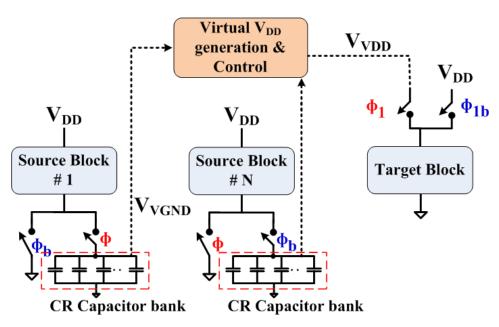

| Figure 3.15 Schematic illustrating time-multiplexed virtual $V_{DD}$ generation                  | 52 |

| Figure 3.16 Alternate implementation of CR scheme to support multiple target blocks              | 53 |

| Figure 3.17 Simplified schematic of the analog buffer used to monitor the virtual supply nodes.  | 55 |

| Figure 3.18 Input referred offset voltage of the analog buffer across the input voltage range of |    |

| interest                                                                                         | 56 |

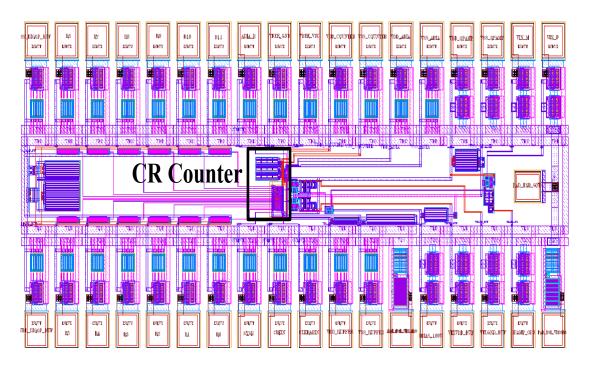

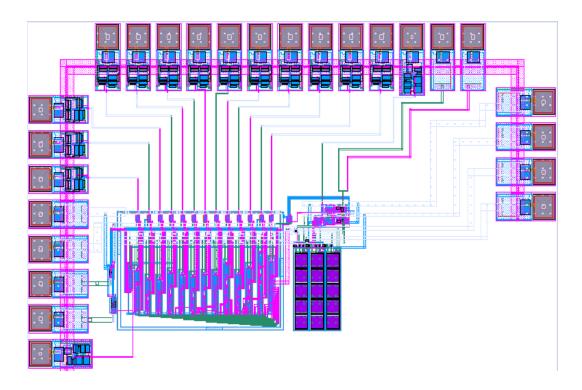

| Figure 3.19 Layout of Gray-code counter with CR scheme in 90-nm process                      | 57    |

|----------------------------------------------------------------------------------------------|-------|

| Figure 3.20. Layout of Gray-code counter with CR scheme in 0.5-μm process                    | 57    |

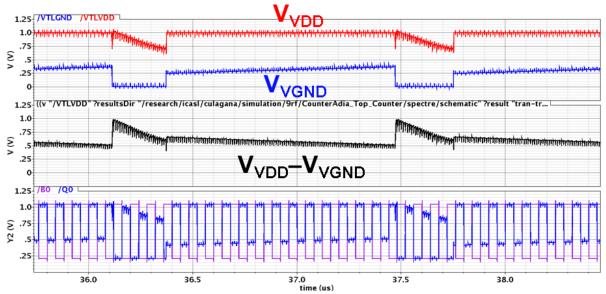

| Figure 3.21 Transient simulation results of CR counter in 90-nm process                      | 58    |

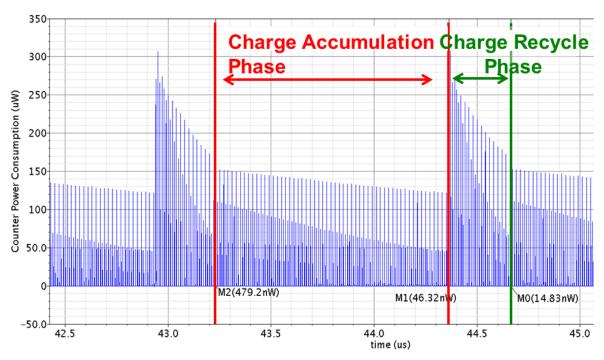

| Figure 3.22 Simulated power consumption of the CR Gray-code counter                          | 59    |

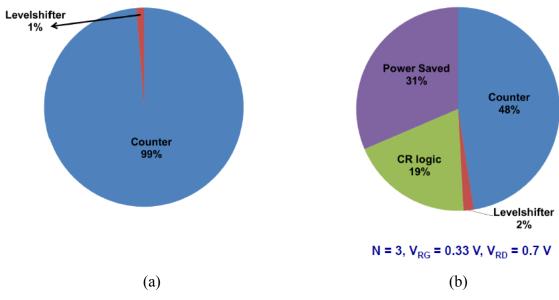

| Figure 3.23 Power consumption in the 12-bit Gray code counter in 90-nm implementation        | 60    |

| Figure 4.1 Die photo of the charge-recycling Gray-code counter in 90-nm process              | 66    |

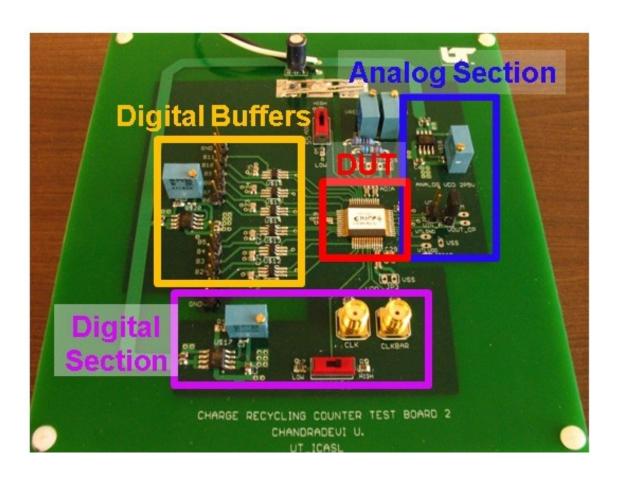

| Figure 4.2 Layout of test board to characterize charge-recycling Gray-code counter (90-nm    |       |

| process)                                                                                     | 66    |

| Figure 4.3 Cross-section of the test board showing the layer stack-up                        | 67    |

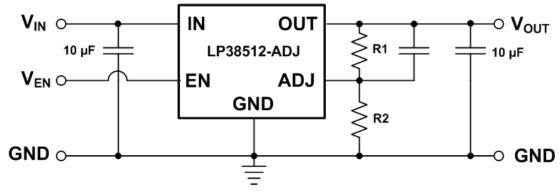

| Figure 4.4 Schematic of LDO voltage-regulator circuit on the test board [65]                 | 68    |

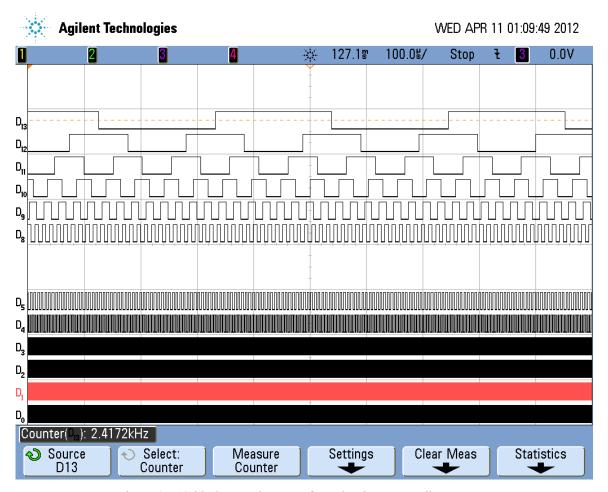

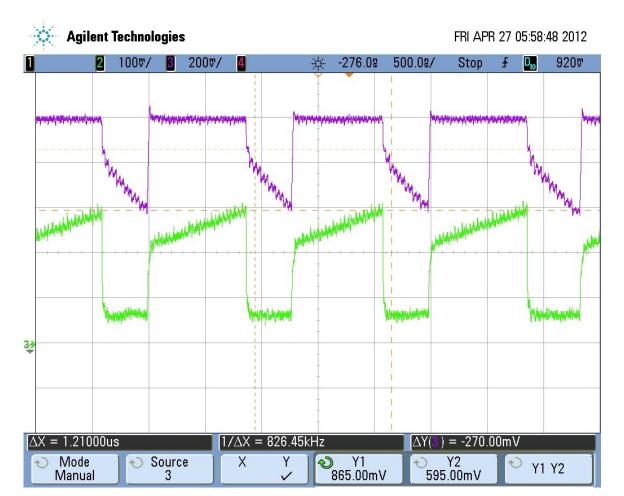

| Figure 4.5 12-bit Gray-code output from the charge recycling counter                         | 70    |

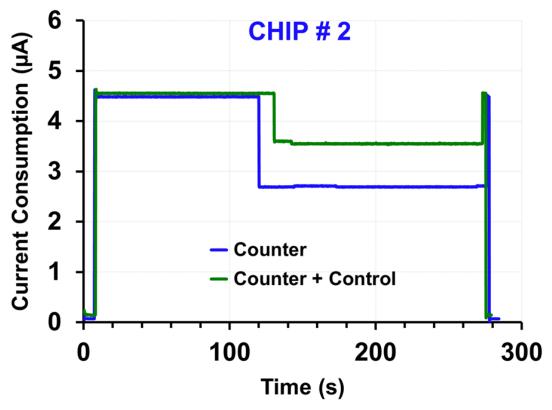

| Figure 4.6 Transient measurement results demonstrating power reduction in the counter        | 71    |

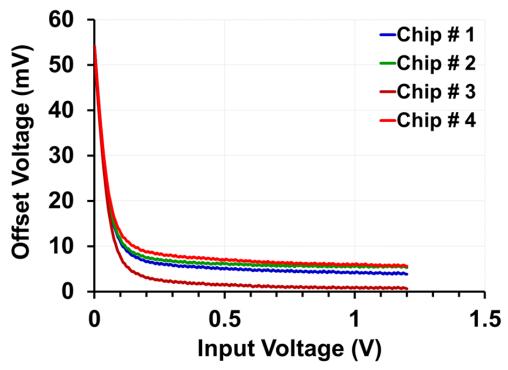

| Figure 4.7 Measured input offset voltage of analog buffers                                   | 72    |

| Figure 4.8 Transient measurement results illustrating virtual supply rails in the CR counter | 73    |

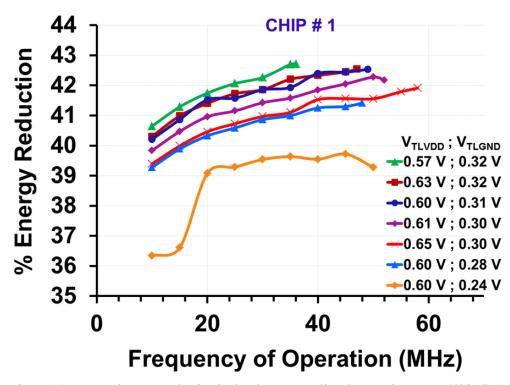

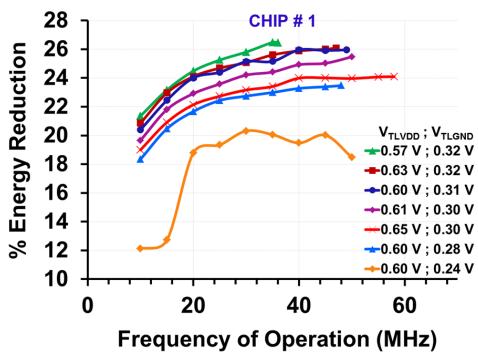

| Figure 4.9 Measured energy reduction in the charge-recycling Gray-code counter (Chip # 1)    | 75    |

| Figure 4.10 Measured energy reduction in the charge-recycling Gray-code counter, including   |       |

| power dissipated by the control logic (Chip # 1)                                             | 76    |

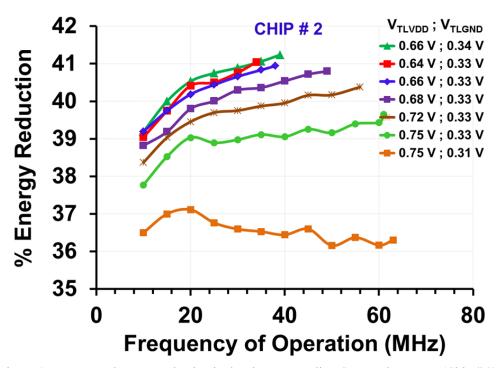

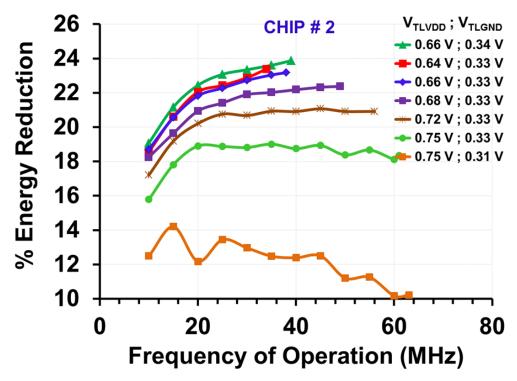

| Figure 4.11 Measured energy reduction in the charge-recycling Gray-code counter (Chip # 2)   | 77    |

| Figure 4.12 Measured energy reduction in the charge-recycling Gray-code counter, including   |       |

| power dissipated by the control logic (Chip # 2)                                             | 78    |

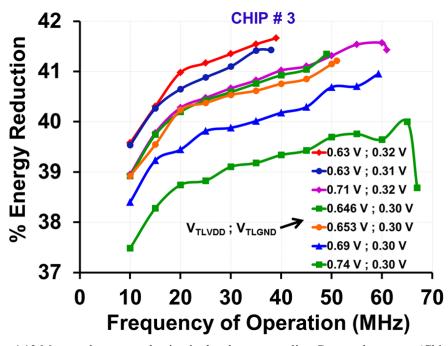

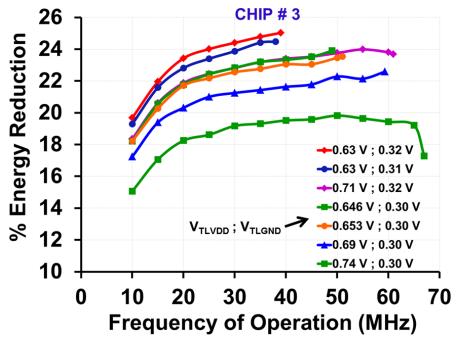

| Figure 4.13 Measured energy reduction in the charge-recycling Gray-code counter (Chip # 3)   | 79    |

| Figure 4.14 Measured energy reduction in the charge-recycling Gray-code counter, including   |       |

| power dissipated by the control logic (Chip # 3)                                             | 79    |

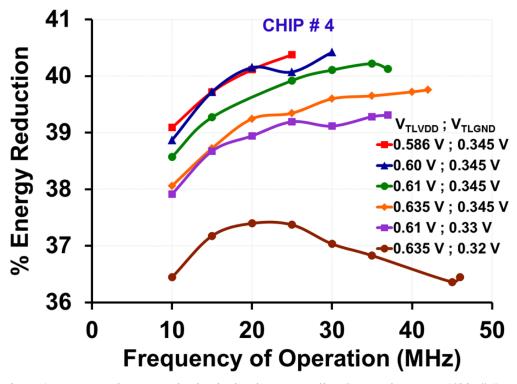

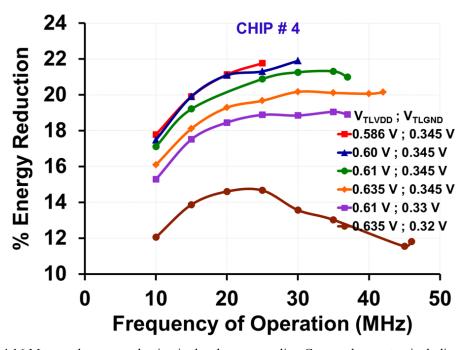

| Figure 4.15 Measured energy reduction in the charge-recycling Gray-code counter (Chip # 4)   | 80    |

| Figure 4.16 Measured energy reduction in the charge-recycling Gray-code counter, including   |       |

| power dissipated by the control logic (Chip # 4)                                             | 81    |

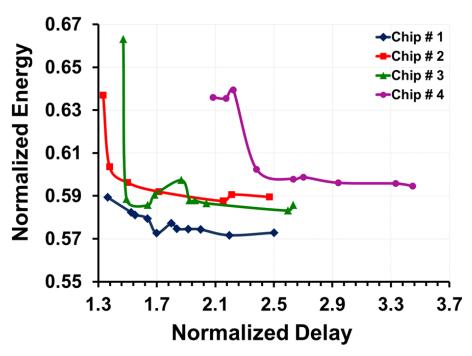

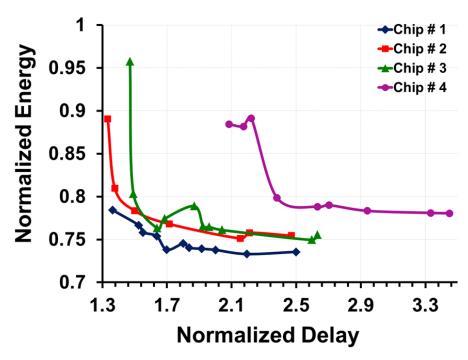

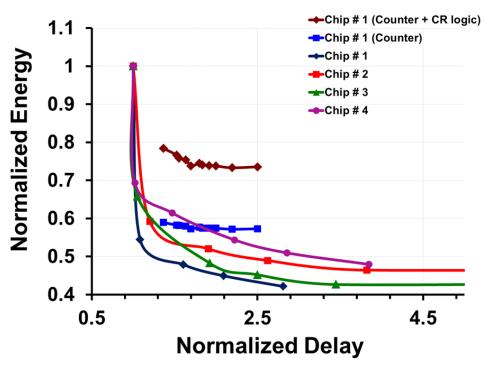

| Figure 4.17 Normalized energy in Counter versus normalized delay due to CR scheme            | 82    |

| Figure 4.18 Normalized energy (including CR logic) versus normalized delay due to CR scheme  | e .82 |

| Figure 4.19 Normalized energy versus normalized delay as a result of reduction in $V_{DD}$   | 83    |

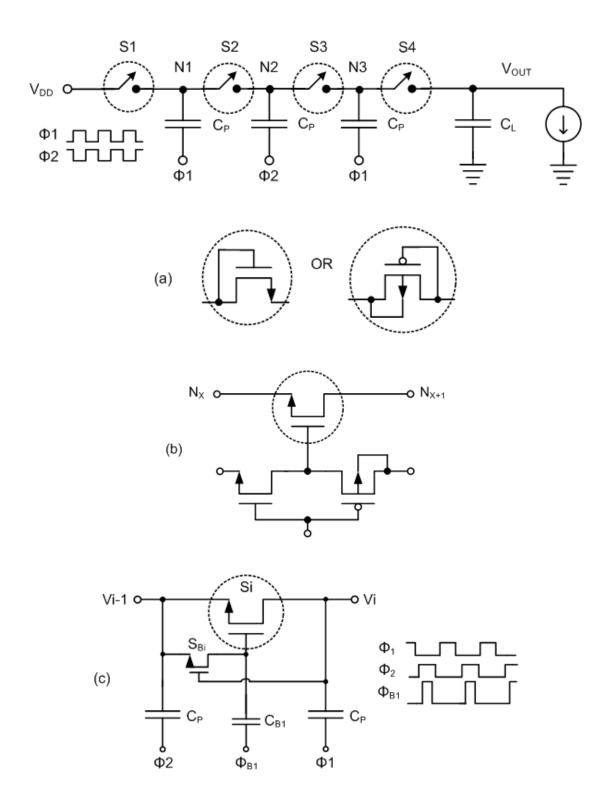

| Figure 5.1 Simplified schematic of a three-stage linear charge pump with charge transfer swi                              | tch               |

|---------------------------------------------------------------------------------------------------------------------------|-------------------|

| (CTS) implementations (a) CMOS diode CTS (b) CTS with gate control generato                                               | r                 |

| and (c) Bootstrapped CTS.                                                                                                 | 92                |

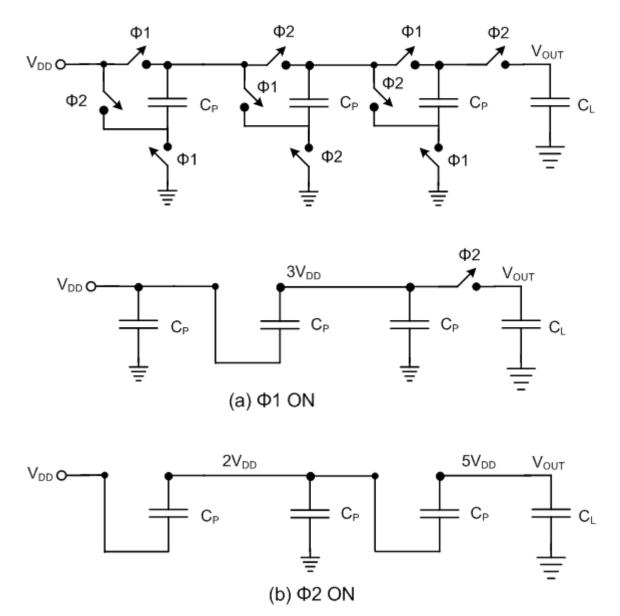

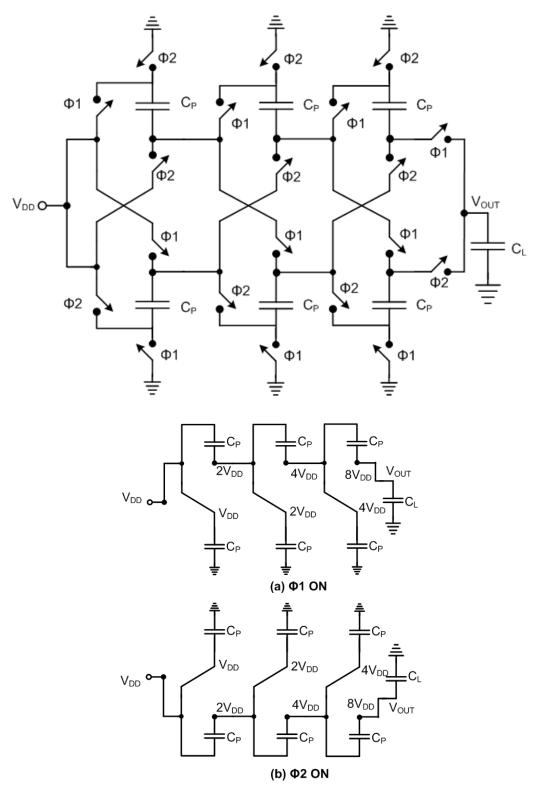

| Figure 5.2 Simplified schematic of a three-stage Fibonacci charge pump (a) $\Phi_1$ is active (b) $\Phi_2$                | D <sub>2</sub> is |

| active.                                                                                                                   | 95                |

| Figure 5.3 Simplified schematic of exponential charge pump (a) $\Phi_1$ is active (b) $\Phi_2$ is active .                | 96                |

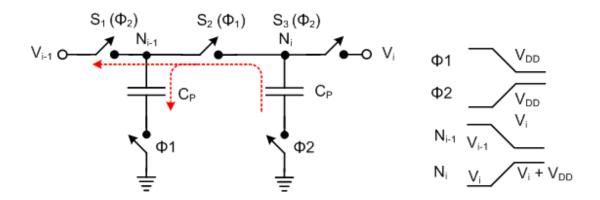

| Figure 5.4 Simplified schematic of linear charge pump's stage illustrating reverse current los                            | s98               |

| Figure 5.5 Schematic of the low-voltage charge pump in [46]                                                               | 100               |

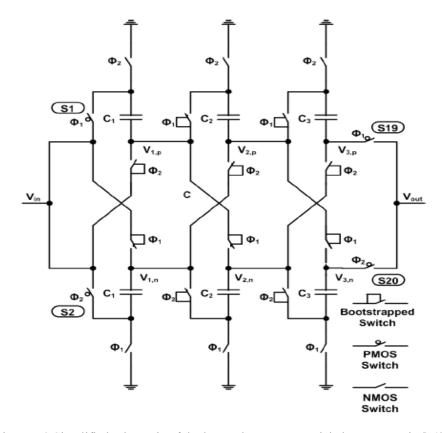

| Figure 5.6 Simplified schematic of the low-voltage charge pump in [45]                                                    | 101               |

| Figure 5.7 Simplified schematic of the low-voltage charge pump in [49]                                                    | 102               |

| Figure 5.8 Simplified schematic of the low-voltage exponential charge pump in [50]                                        | 104               |

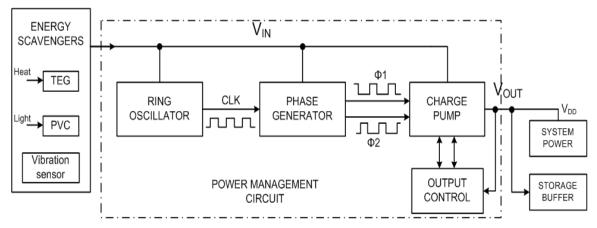

| Figure 5.9 Topology of the proposed self-starting converter                                                               | 107               |

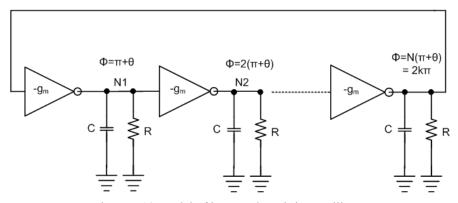

| Figure 5.10 Model of inverter-based ring oscillator                                                                       | 109               |

| Figure 5.11 RO's startup voltage across device ratio for typical process corner                                           | 112               |

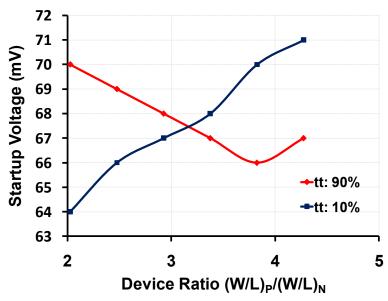

| Figure 5.12 RO's voltage across device ratio for worst-case process corners                                               | 113               |

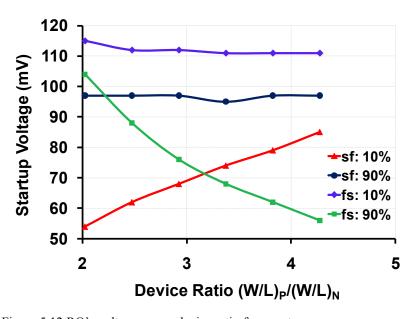

| Figure 5.13 Schematic of the 5-stage ring oscillator                                                                      | 114               |

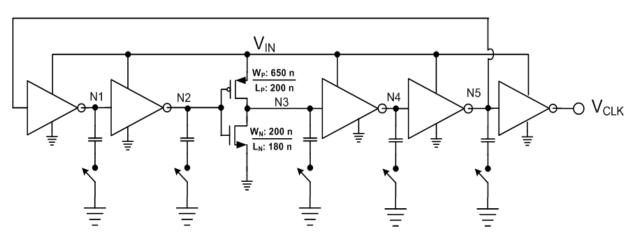

| Figure 5.14 Schematic of the non-overlapping phase generator                                                              | 115               |

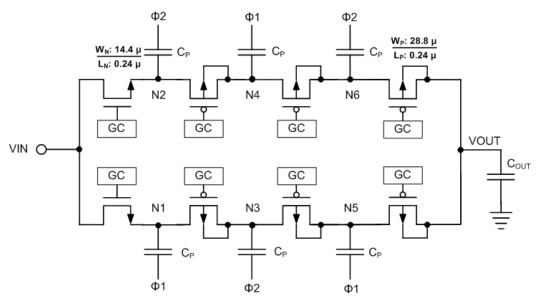

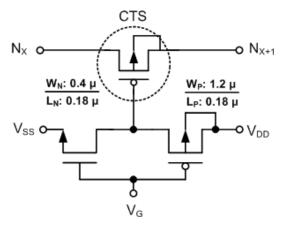

| Figure 5.15 Simplified schematic of the proposed LCP                                                                      | 117               |

| Figure 5.16 Schematic of the level-shifter used to generate the CTS control in the proposed L                             | .CP .118          |

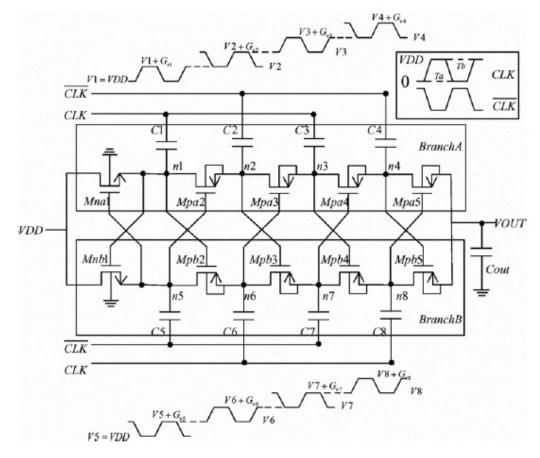

| Figure 5.17 Simplified schematic of the proposed LCP along with the GC generation                                         | 119               |

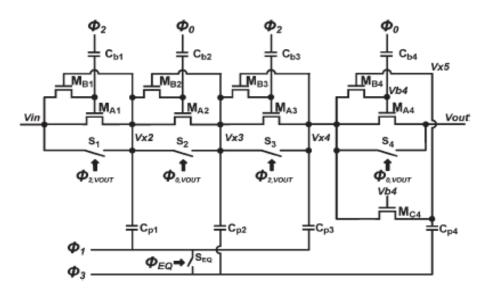

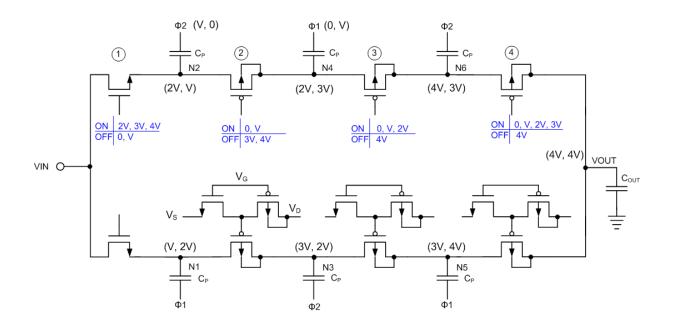

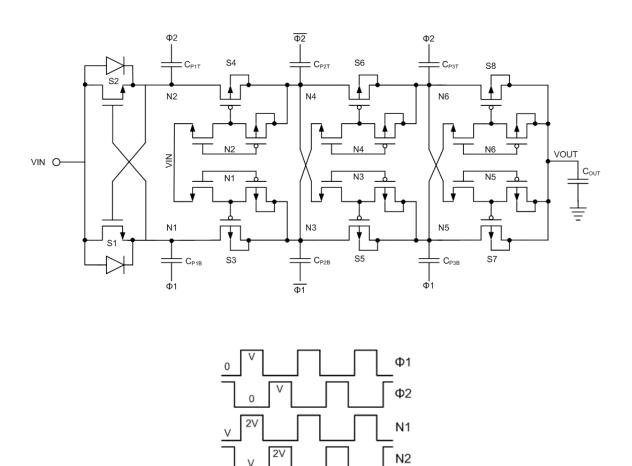

| Figure 5.18 Schematic of the proposed self-starting linear charge pump                                                    | 122               |

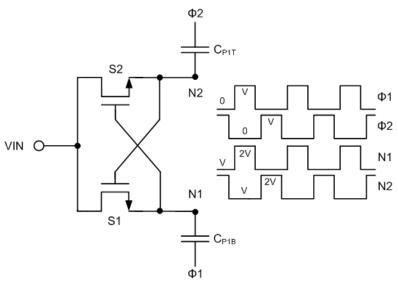

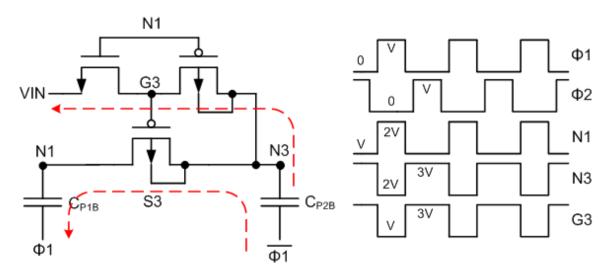

| Figure 5.19 Schematic illustrating control signals and charge transfer in the first stage of LCI                          | P124              |

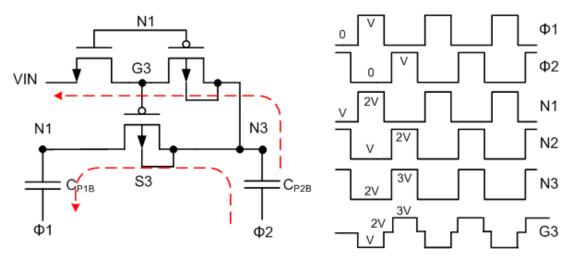

| Figure 5.20 Schematic illustrating control signals and charge transfer in the second stage of I                           | CP.125            |

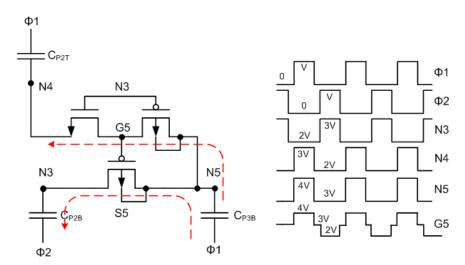

| Figure 5.21 Schematic illustrating control signals and charge transfer in the third stage of LC                           | P126              |

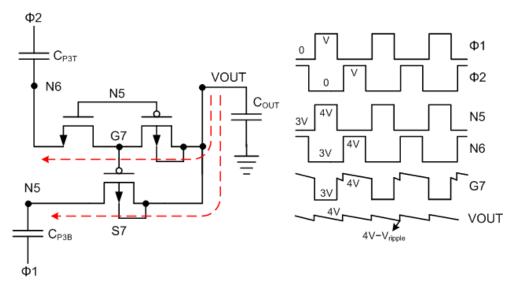

| Figure 5.22 Schematic illustrating control signals and charge transfer in the last stage of LCP                           | 127               |

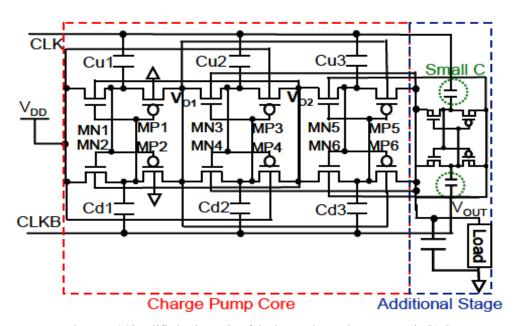

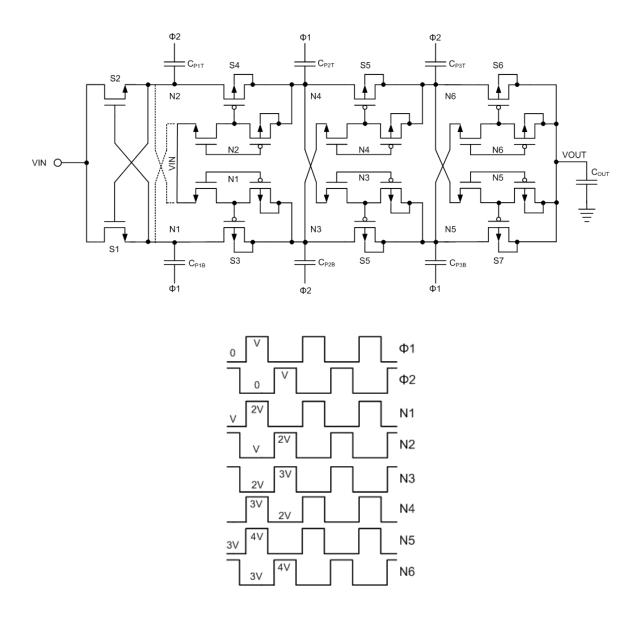

| Figure 5.23 Schematic of the proposed improved self-starting charge pump - version 2                                      | 129               |

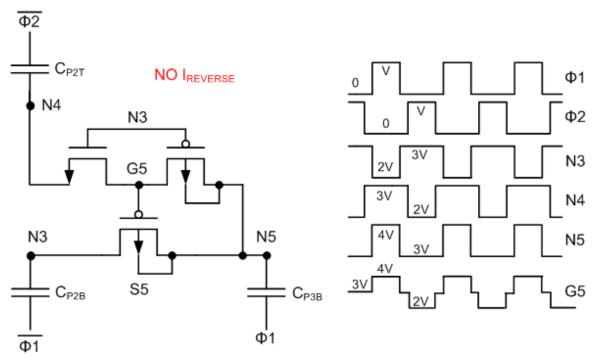

| Figure 5.24 Schematic illustrating control signals and charge transfer in the second stage of I                           | LCP               |

| V2                                                                                                                        | 130               |

| Figure 5.25 Schematic illustrating control signals and charge transfer in the 2 <sup>nd</sup> -to3 <sup>rd</sup> stage of |                   |

| LCP V2                                                                                                                    | 132               |

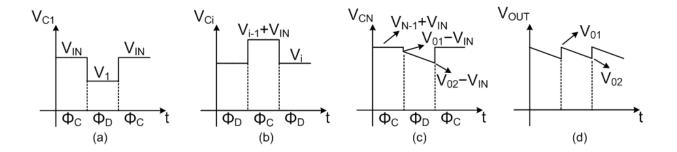

| Figure 5.26 Voltage across charge pump capacitors during charging ( $\Phi_C$ ) and discharging ( $\Phi_D$ ) |     |

|-------------------------------------------------------------------------------------------------------------|-----|

| phase of operation for (a) First stage CP capacitor, (b) i-th stage CP capacitor, (c)                       |     |

| Last or N-th stage CP capacitor, and (d) the output capacitor                                               | 137 |

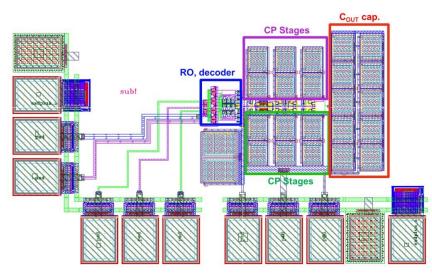

| Figure 5.27 Layout of the low-voltage charge pump V1 in 130-nm process                                      | 142 |

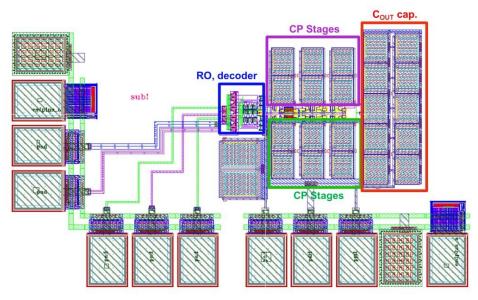

| Figure 5.28 Layout of the low-voltage charge pump V2 in 130nm process                                       | 143 |

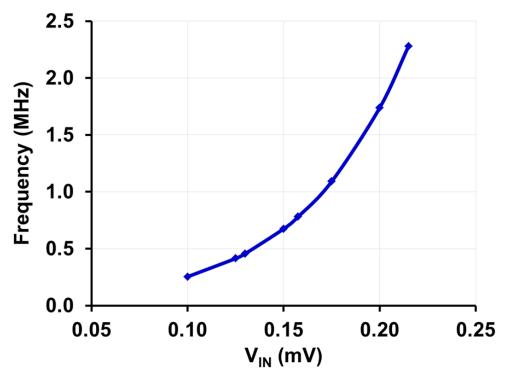

| Figure 5.29 Ring oscillator's output frequency across input voltage variations                              | 144 |

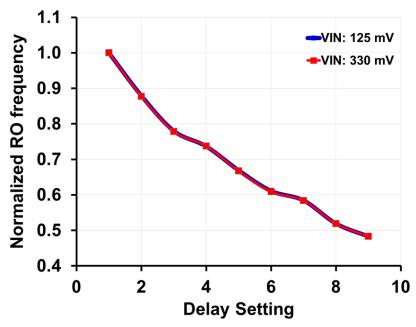

| Figure 5.30 Ring oscillator's output frequency control with delay network                                   | 144 |

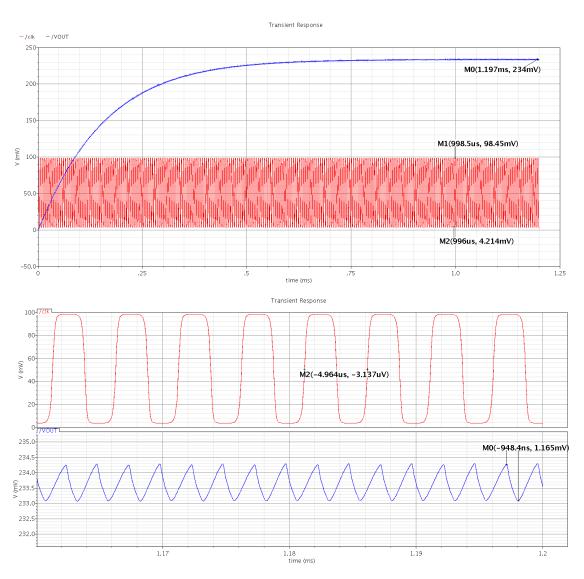

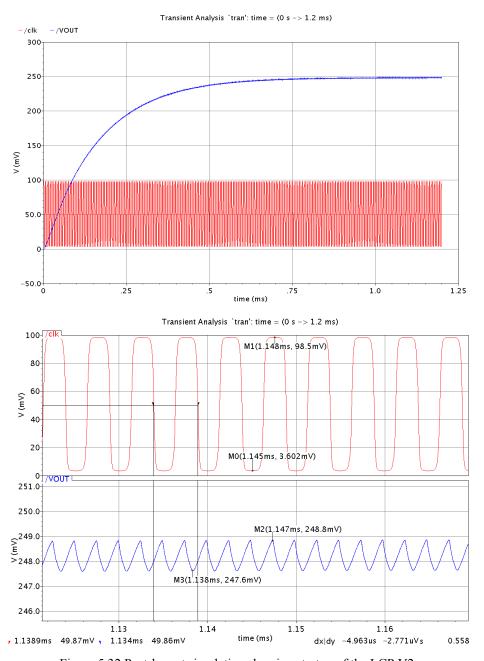

| Figure 5.31 Post-layout simulation showing startup of the LCP V1                                            | 146 |

| Figure 5.32 Post-layout simulation showing startup of the LCP V2                                            | 147 |

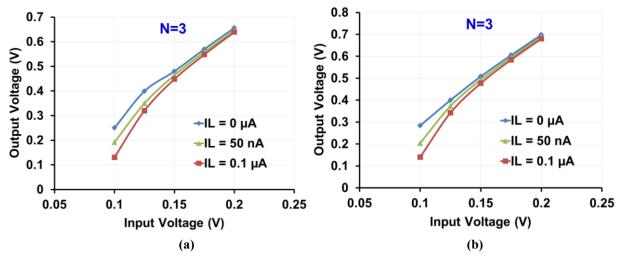

| Figure 5.33 Plot of LCP's output voltage across varying input voltages for different load                   |     |

| conditions                                                                                                  | 148 |

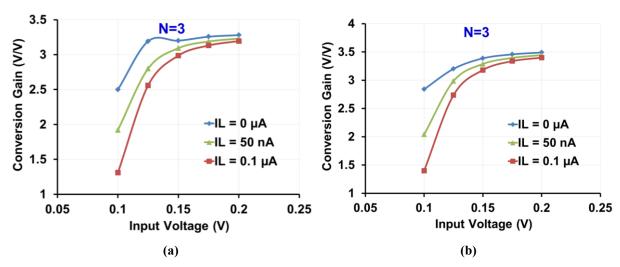

| Figure 5.34 Plot of LCP's conversion gain across varying input voltages for different load                  |     |

| conditions                                                                                                  | 148 |

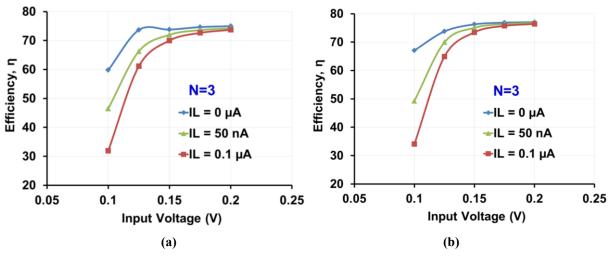

| Figure 5.35 Plot of charge pumps' efficiency across varying input voltages and different load               |     |

| conditions                                                                                                  | 149 |

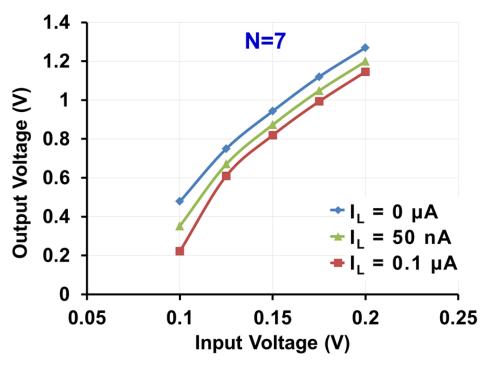

| Figure 5.36 Seven-stage LCP V2's output voltage across varying input voltages for different loa             | ıd  |

| conditions                                                                                                  | 150 |

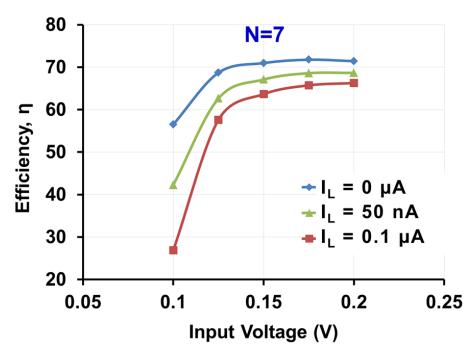

| Figure 5.37 Seven-stage LCP V2's efficiency across varying input voltages and different load                |     |

| conditions                                                                                                  | 151 |

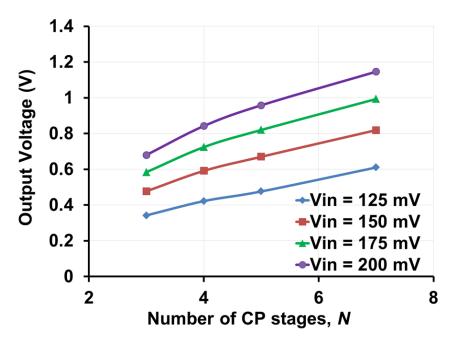

| Figure 5.38 Plot of LCP V2's output voltage across varying number of pumping stages (N)                     | 151 |

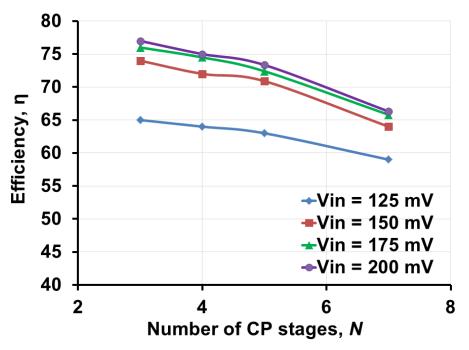

| Figure 5.39 Plot of LCP V2's efficiency across varying number of pumping stages (N)                         | 152 |

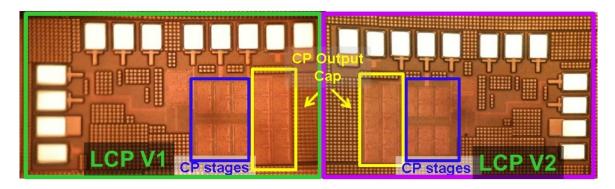

| Figure 6.1 Microphotograph of the fabricated die                                                            | 154 |

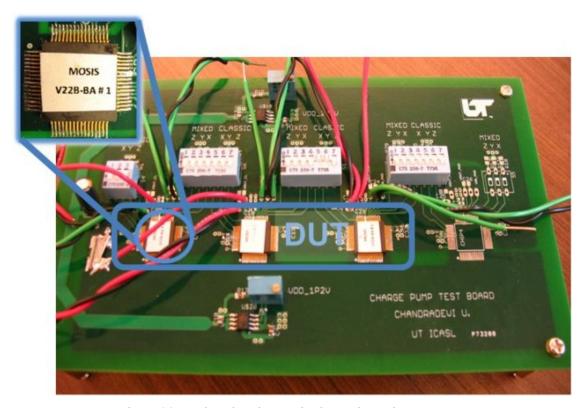

| Figure 6.2 Test board to characterize low-voltage charge pumps                                              | 154 |

| Figure 6.3 Cross-section of the test board showing the layer stack-up                                       | 155 |

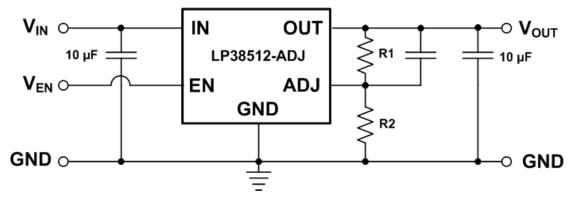

| Figure 6.4 Schematic of LDO voltage-regulator circuit on the test board [65]                                | 156 |

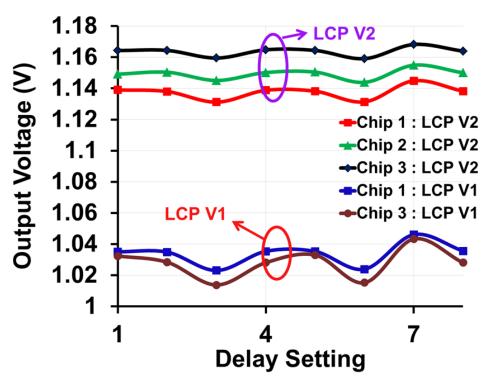

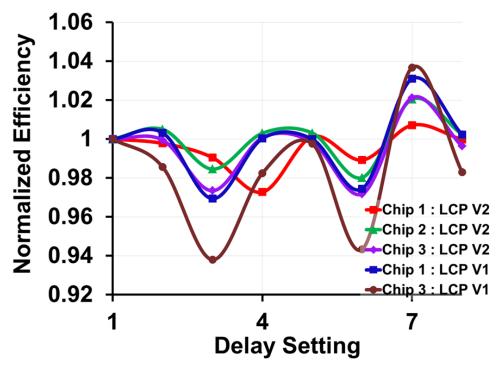

| Figure 6.5 Measured charge pump output voltage across frequency of operation ( $V_{IN}$ at 0.33 V).         | 158 |

| Figure 6.6 Measured charge pump efficiency across frequency of operation, normalized to                     | 158 |

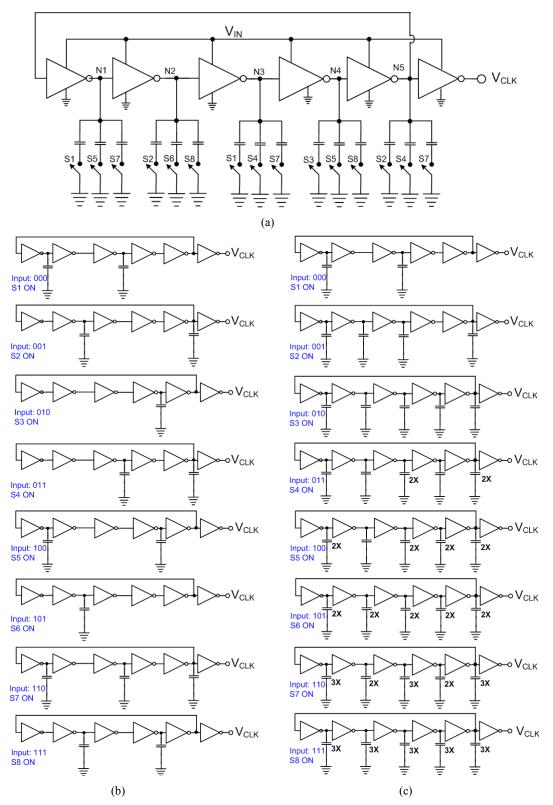

| Figure 6.7 Frequency tuning in ring oscillator (a) simplified schematic of RO illustrating delay            |     |

| cells, (b) Realized RO schematic, and (c) Required RO schematic, across different                           |     |

| delay (switch) settings                                                                                     | 159 |

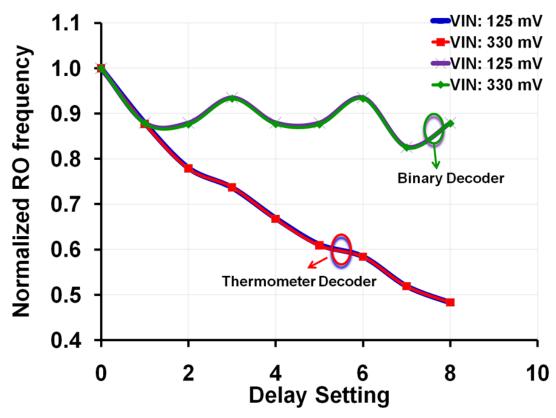

| Figure 6.8 Simulated RO's output frequency, normalized to the free-running frequency, across   |     |

|------------------------------------------------------------------------------------------------|-----|

| delay settings for $V_{IN}$ at 0.125 V and 0.33 V.                                             | 160 |

| Figure 6.9 Measured charge pump output voltage across variations in input voltage and DC load  |     |

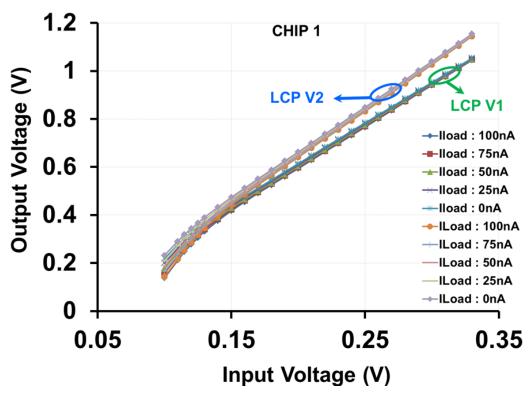

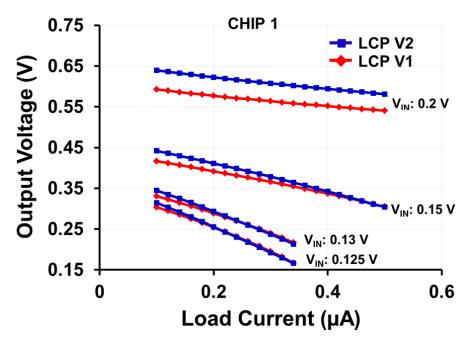

| current for Chip 1                                                                             | 161 |

| Figure 6.10 Measured charge pump output voltage across variations in input voltage and DC      |     |

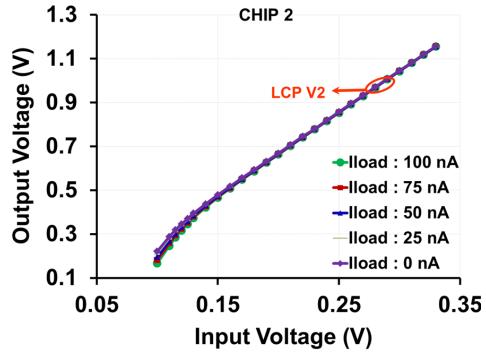

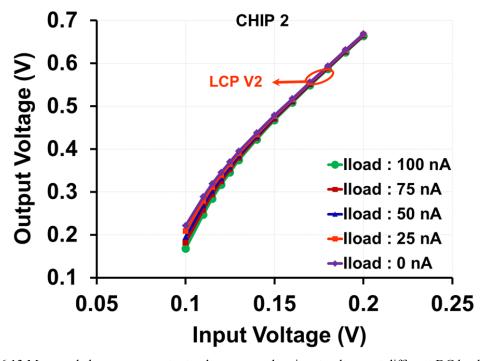

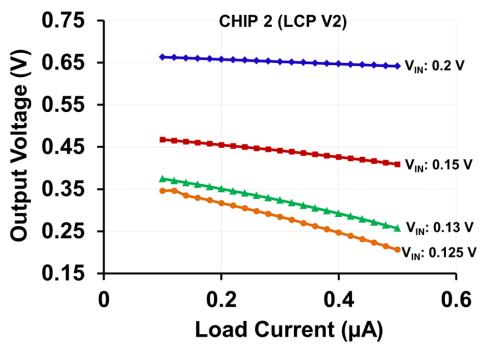

| load current for Chip 2                                                                        | 161 |

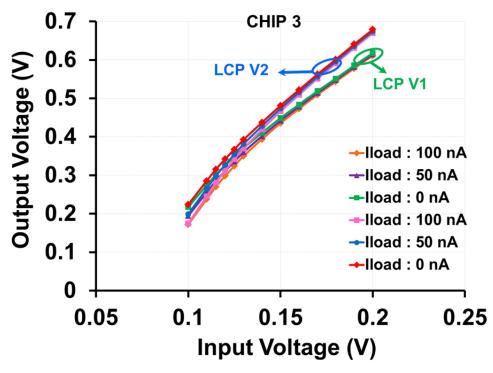

| Figure 6.11 Measured charge pump output voltage across variations in input voltage and DC      |     |

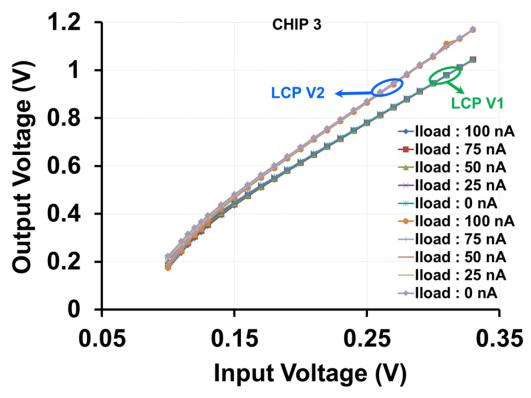

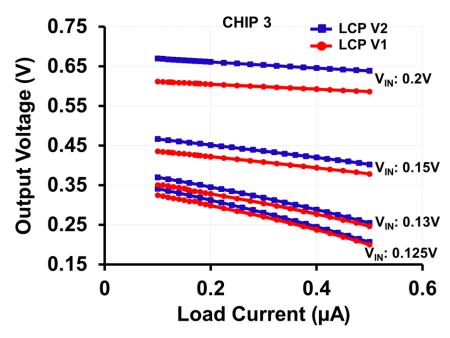

| load current for Chip 3                                                                        | 162 |

| Figure 6.12 Measured charge pump output voltage across low input voltages at different DC load |     |

| current conditions for Chip 1                                                                  | 163 |

| Figure 6.13 Measured charge pump output voltage across low input voltages at different DC load |     |

| current conditions for Chip 2                                                                  | 163 |

| Figure 6.14 Measured charge pump output voltage across low input voltages at different DC load |     |

| current conditions for Chip 3                                                                  | 164 |

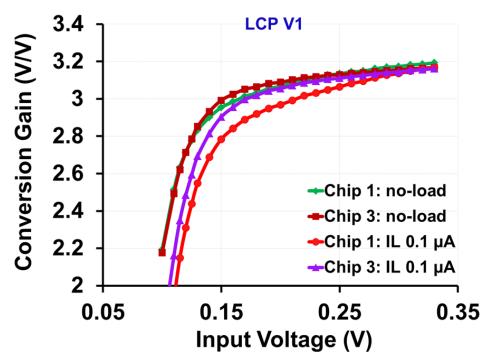

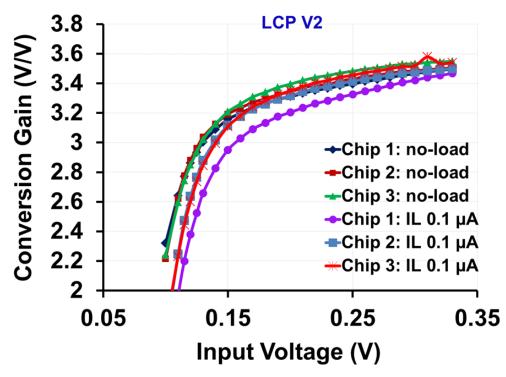

| Figure 6.15 LCP V1's conversion gain across low input voltages and load conditions             | 165 |

| Figure 6.16 LCP V2's conversion gain across low input voltages and load conditions             | 165 |

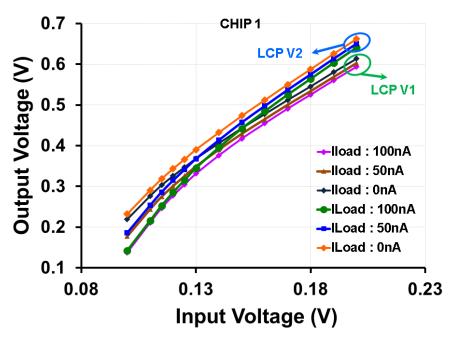

| Figure 6.17 Output voltage of LCP across varying load conditions for chip 1                    | 167 |

| Figure 6.18 Output voltage of LCP across varying load conditions for chip 2                    | 167 |

| Figure 6.19 Output voltage of LCP across varying load conditions for chip 3                    | 168 |

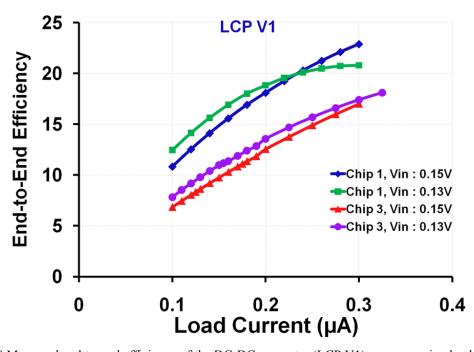

| Figure 6.20 Measured end-to-end efficiency of the DC-DC converter (LCP V1) across varying      |     |

| load conditions                                                                                | 169 |

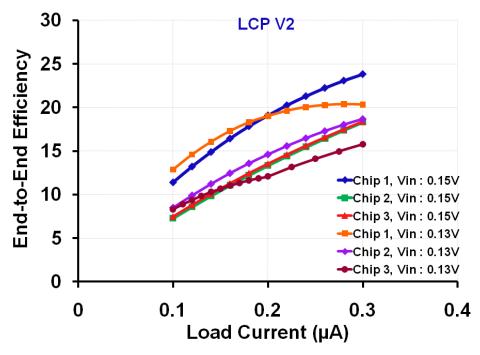

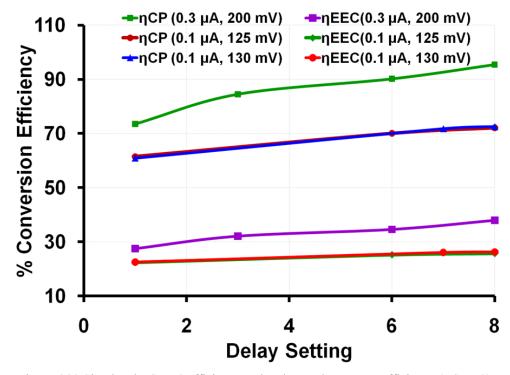

| Figure 6.21 Measured end-to-end efficiency of the DC-DC converter (LCP V2) across varying      |     |

| load conditions                                                                                | 170 |

| Figure 6.22 Simulated LCP V2 efficiency and end-to-end converter efficiency (LCP V2)           | 170 |

# **List of Tables**

| Table 2.1 Comparison of the state-of-the-art Charge-recycling based low power techniques20        |

|---------------------------------------------------------------------------------------------------|

| Table 3.1 Partially Self-Powered Circuit's performance with and without Charge-Recycling at 50    |

| MHz61                                                                                             |

| Table 3.2 Energy reduction of system with and without Charge-Recycling at 100MHz (90-nm           |

| design)62                                                                                         |

| Table 3.3 Propagation delay with and without Charge-Recycling                                     |

| Table 4.1 Offset voltage of the comparators used in CR control logic                              |

| Table 4.2 Comparison of the state-of-the-art Charge-recycling based low power techniques87        |

| Table 5.1 Summary of the state-of-art low-voltage DC-DC converters with startup mechanisms10      |

| Table 6.1 Charge pump startup voltage across different load conditions                            |

| Table 6.2 Performance comparison of the proposed charge pump with state-of-the-art converters .17 |

# **Chapter 1 Introduction**

### 1.1 Motivation

The fast-paced growth of the semiconductor industry has facilitated the development of highly integrated electronic systems with sophisticated functionalities. Our dependence on these ubiquitous, pervasive electronic systems and the increasing concerns over global warming has placed efficient energy consumption as a significant topic of research. The International Technology Roadmap for Semiconductors (ITRS) [1] has identified power consumption and leakage power consumption as focus topics for research for the next 15 years [2]. Also, reducing the power consumption of the integrated circuits (ICs) in portable electronics is critical for long battery life between recharge cycles and thus to the performance of the system. Energy efficiency is important in wired applications as well, where low power consumption directly translates to lower utility bills and improved reliability due to lower heat generation.

With this pressing need for efficient power utilization, many low-power IC design techniques have been put forth over the past two decades. Foremost among these digital design techniques are supply and threshold voltage scaling [11], [21], sub-threshold operation [7], body-biasing [20], power-gating [19], and adiabatic computation [13], [16]. Each of these techniques has a different power-performance tradeoff and has been successfully used in microprocessors along with power management systems. Sensor-based mixed-signal circuits represent a niche class of systems that requires low-cost, highly energy efficient operation. Often, the generation of multiple supply voltages or the use of sophistication power management ICs presents a large overhead on these systems. In such applications, highly aggressive low-power design with efficient, integrated power management scheme is required to meet the power constraints of the system.

Additionally, the CMOS device scaling trend has resulted in the degradation of analog device performance at Ultra-Deep-Submicron (UDSM) scale processes. This has necessitated the use of digital assist techniques to improve the overall system performance, improve reproducibility, and provide a simple and powerful interface [1]. With the increasing dependence

on such digital housekeeping circuits for otherwise straightforward analog implementations, a power reduction technique that encompasses these power-constrained UDSM circuits would be very valuable.

It is the opinion of the author that adaptive voltage scaling techniques would be the potentially most effective way to achieve energy efficiency, especially in the presence of process and temperature variations. The Adaptive Voltage Scaling (AVS) technique automatically adjusts the power supply voltage to achieve energy efficient operation at a required performance level, across variations in the operating conditions. Majority of voltage-scaling based energy reduction techniques focus on the methods to reduce energy consumption by employing multiple supply voltages, but do not account for the generation of these multiple supply voltage levels. While the energy expended for the generation of multiple supply levels is validated by the significant energy savings achieved in large computation systems, it presents a major overhead to severely power-constrained, mixed-signal systems. Hence, this research addresses the challenge of adopting VS techniques in these small mixed-signal systems.

This dissertation focuses on the design and implementation of charge-recycling (CR) based voltage-scaling (VS) schemes to improve the efficiency of power-constrained mixed-signal circuits. Furthermore, the proposed scheme can be easily adapted to AVS scheme. As with any VS technique, reduction in power comes at the expense of some performance degradation [3]. The power-reduction and performance-loss tradeoff in the system is analyzed in this work.

The realization of charge-recycling scheme with an adjustable power-supply voltage that compensates for performance or temperature variations requires a low-voltage DC-DC converter that functions as the power delivering unit. Further, power autonomy can be achieved with a self-starting DC-DC converter that is powered by the recycled charge (or harvested energy) to generate the output power-supply voltage. Additionally, ultra-low voltage charge pumps are widely exploited in energy harvesting systems, sensor nodes, as well as in smart power management ICs. Hence, the second part of this dissertation explores the design of an ultra-low voltage, self-starting charge pump which is an essential component in ultra-low voltage DC-DC conversion. Furthermore, unassisted self-startup capability in the ultra-low voltage regime

provides significant efficiency enhancements in micro-energy harvesters and thus presents a very attractive challenge for research.

### 1.2 Research Goals

The goals of this research can be summarized as follows:

- To investigate the feasibility of recycling charge from switching and leakage currents that are inherent to digital operation.

- To explore energy-efficient means to use the reclaimed charge.

- To design and implement a charge-recycling (CR) methodology that lowers the total power consumption of digital circuits in a mixed-signal system. Further, the proposed CR technique should be easily adaptable to existing digital circuits and independent of the process technology employed.

- To study the performance-power design trade-off as a result of implementing the proposed CR scheme.

- To investigate ultra-low voltage DC-DC conversion topologies that enable power autonomy, and offer variable conversion gains depending on the input voltage.

- To design and implement an unassisted self-starting, ultra-low voltage charge pump which forms an integral component in micro-energy harvesters.

- To characterize the startup voltage and the performance of the proposed charge pump.

- To determine possible applications of the proposed CR scheme and the ultra-low voltage charge pump.

To meet these goals, the state-of-the-art low-power designs have been studied and the various factors that limit power reduction have been understood. To investigate charge-recycling as a means to lower energy consumption, a methodology is proposed to analyze existing digital cells and the best possible way to adopt CR is studied. A prototype has been designed and implemented in 90-nm CMOS and 0.5-µm SiGe BiCMOS processes. The energy reduction for

one cycle of operation in these test prototypes has been characterized and the performance of the proposed CR scheme has been discussed.

In the second part of this dissertation, the factors that affect self-startup and operation of DC-DC converters at ultra-low voltages have been analyzed. A self-starting, switched-capacitor charge pump has been designed and implemented in a 130-nm CMOS process. The performance of the fabricated prototypes has been characterized across varying input and load conditions. Further, the performances of the designed prototypes have been compared with the current state-of-the-art designs in order to study the effectiveness of the proposed circuits.

### 1.3 Dissertation Overview

Chapter 2 reviews trends in CMOS technology and the challenges of low-power design. A literature survey of state-of-the-art power reduction techniques is presented. Chapter 3 provides an in-depth look at charge-recycling based dynamic voltage scaling in digital cells. The design considerations and methodology to optimize power consumption are presented. Further, an estimate of the percentage energy reduction due to charge-recycling is derived. The physical design and implementation of the proposed CR scheme for a 12-bit Gray-code counter are described. Furthermore, to show its effectiveness, the CR scheme has also been ported to a 0.5-µm SiGe BiCMOS process and the efficiency of the two systems has been compared with simulation results.

Chapter 4 describes the test-board design and the procedure employed to characterize the energy savings in the test chips. Further, the design trade-offs and the realized energy savings in the system are analyzed in detail. Directions for future work with techniques to improve the proposed CR scheme are discussed. The chapter concludes with the performance comparison of the proposed CR scheme with the current state-of-the-art low-power designs. The applications of the CR technique are also explored in this chapter.

Chapter 5 reviews the current state-of-the-art self-starting DC-DC converters and establishes the design goals for this research. The proposed switched-capacitor-based, self-starting DC-DC converter topology is introduced and its design is presented. Next, the operational losses and their effect on the efficiency of the converter are analyzed. Further, an

output voltage equation that accurately models the CP's operational losses is derived. Finally, the improvements obtained using the proposed topologies are illustrated with the simulation results.

Chapter 6 presents the test-board design and the methodology employed to verify the operation of the proposed self-starting charge pumps. The startup voltage and the performance of the proposed low-voltage charge pumps are characterized and compared with the current state-of-the-art designs.

Chapter 7 provides a summary and conclusion to this work. The original contributions made in this research are presented. Finally, the possible directions for future work are discussed.

# **Chapter 2 Literature Review**

### 2.1 Introduction

Traditionally, digital design optimization was targeted at improving the computation speed until the advent of battery operated systems which necessitated power and energy optimization techniques to extend the lifetime of the battery. For more than a decade, energy optimization has been one of the actively researched areas in IC design. A literature review of the various low-power design techniques along with an analysis of the implementation challenges helps to illustrate the contribution of this dissertation research to the state of the art low power methodologies. Section 2.2 presents a brief overview of the different sources of power dissipation that are inherent to digital operation. Section 2.3 discusses the role of CMOS technology scaling in the design of energy-efficient mixed-signal ICs. Low-power, energy-efficient design techniques and their challenges are explored in Section 2.4. Finally, Section 2.5 summarizes and concludes this chapter.

### 2.2 Power Consumption

The average power consumption in a conventional CMOS digital circuit is given by

$$P_{average} = \frac{1}{T} \int_{0}^{T} I_{VDD}(t) \cdot V_{DD} \cdot dt$$

(2.1)

where  $V_{DD}$  is the power supply voltage, and  $I_{VDD}(t)$  the instantaneous supply current consumed by the circuit in the time period, T. To examine the different components of power dissipation, consider the CMOS inverter schematic shown in Figure 2.1. At equilibrium state, only one of the transistors is ON thereby eliminating any conductive path between the supply rails. Hence,  $I_{VDD}(t)$  current is primarily drawn from the supply only during a transition (or switching) of the output logic state. The load capacitance ( $C_L$ ) at the output node is charged to  $V_{DD}$  during a LOW-to-HIGH transition or discharged to ground during a HIGH-to-LOW logic transition. A charge of  $C_LV_{DD}$  is thus moved from  $V_{DD}$  to  $C_L$  through the pull-up network (PMOS transistor) or from  $C_L$  to ground by the pull-down network (NMOS transistor) for the respective transitions. Thus, the energy expended for a digital transition is given by  $(1/2)C_LV_{DD}^2$ . This switching current

Figure 2.1 Inverter illustrating current paths during operation

component which is essential for digital operation represents one of the dynamic components of power dissipation. The dynamic power dissipated per switching cycle can be approximated as [3]

$$P_{dyn,switching} = \alpha \left( C_L \cdot V_{DD}^2 \cdot \frac{1}{t} \right) \tag{2.2}$$

where  $\alpha$  is the probability of a switching transition and 1/t is the frequency of operation. The load capacitance at the output node comprises of the reverse-biased diffusion capacitances of the driving circuit, gate capacitance of the fanout load, interconnection wire capacitance, and any external load capacitance connected to the output node.

Furthermore, during the switching transitions, when one transistor is being turned ON, the other is being switched OFF. Therefore, there exists a short period of time when both the transistors are ON, resulting in a short-circuit current ( $I_{SC}$ ) through the direct conductive path from  $V_{DD}$  to ground. This undesirable current component is dependent on the slope of input transition and can be controlled by proper transistor sizing and fanout ratios. However, this  $I_{SC}$  forms a small percentage of the total dynamic power required for digital operation.

Additionally, in current UDSM technologies, there exists a static component of power consumption that is caused by the small static leakage currents that flow through the transistors even in the OFF state. This static component of power dissipation is primarily determined by the

subthreshold leakage and the gate leakage currents in UDSM processes [5]. Thus the total average power dissipated for digital operation can be summarized as [3]

$$P_{total,avg} = \alpha \left( C_L \cdot V_{DD}^2 \cdot f_{CLK} \right) + I_{SC} \cdot V_{DD} + I_{Lkg} \cdot V_{DD}$$

(2.3)

where the first two terms summarize the dynamic power dissipation, representing the switching and the short-circuit components while the static power dissipation due to leakage currents is represented by the last term. Typically, the switching component of dynamic power approximates the total power consumed and thus forms the target for most power reduction techniques.

### 2.3 Scaling Trends for CMOS Technologies

The consistent scaling of CMOS process technologies has been driven by the everincreasing need for low power, high performance and high packing density. With constant-field CMOS scaling, the device dimensions (width W, length L), gate-oxide thickness ( $t_{ox}$ ), threshold voltage ( $V_{TH}$ ), along with the power supply voltage ( $V_{DD}$ ) are scaled by a factor of S (about  $\sqrt{2}$ ) for every process node. However, material parameters such as silicon bandgap and built-in junction potential do not scale with reduced voltages or dimensions and thus present challenges in device design [6]. So, the modern processes follow the generalized scaling model, where the device dimensions are scaled by S but the  $V_{DD}$ ,  $V_{TH}$  and doping follow a different scaling factor (U) which is smaller than S [3].

To gauge the effects of scaling on energy efficiency, the critical digital design parameters of intrinsic delay and power are considered in this section. The intrinsic delay associated with long-channel MOSFET (with  $V_{GS} = V_{DD}$ ) is given by [3]

$$\tau = \frac{C_G \cdot V_{DD}}{I_{DSAT}} = \frac{C_{OX} \cdot WL \cdot V_{DD}}{\frac{1}{2} \mu C_{OX} W/L (V_{DD} - V_{TH})^2} = \frac{2L^2}{\mu} \cdot \frac{V_{DD}}{(V_{DD} - V_{TH})^2}$$

(2.4)

where  $C_G$  is the gate capacitance,  $C_{OX}$  is the gate-oxide capacitance per unit area,  $I_{DSAT}$  is the saturation drain current at  $V_{GS} = V_{DD}$  and  $\mu$  is MOSFET mobility. As seen in (2.4) the delay scales with the device length as  $L^2$  and thus device scaling results in quadratic increase in the maximum achievable speed (performance) for a given  $V_{DD}$  and  $V_{TH}$ . However, in modern UDSM processes, the small device length presents undesirable short-channel effects such as carrier velocity

saturation, drain-induced barrier lowering (DIBL) and severe channel-length modulation. For nominal supply voltages, the electric field across short-channel lengths is high enough to cause velocity saturation and thus it is safe to assume that all modern logic devices are affected by short-channel effects. Once velocity saturation occurs, the saturation drain current  $I_{DSAT}$  has a linear dependence on the  $V_{GS}$  and can be approximated as [3]

$$I_{DSAT} = \mu C_{OX} W/L \cdot V_{DSAT} \left( V_{GS} - V_{TH} - \frac{V_{DSAT}}{2} \right)$$

(2.5)

where  $V_{DSAT}$  is the drain-source voltage at which velocity saturation occurs, and is usually less than  $V_{GS}$ - $V_{TH}$  for short-channel devices. The saturated carrier velocity  $v_{sat}$  is given by  $(V_{DSAT} \mu)/L$ . Now, the intrinsic delay  $\tau$  for short-channel devices can be derived similar to (2.4) and is linearly dependent on L as shown below:

$$\tau = \frac{C_{OX} \cdot WL \cdot V_{DD}}{\mu C_{OX} W/_{I} \cdot V_{DSAT} (V_{DD} - V_{TH} - V_{DSAT}/2)} = \frac{L}{v_{sat}} \cdot \frac{V_{DD}}{(V_{DD} - V_{TH} - V_{DSAT}/2)}$$

(2.6)

where  $v_{sat}$  is constant above  $V_{DSAT}$ . Thus there is a linear increase in the maximum attainable switching frequency (performance) with device scaling in short-channel length devices.

For most digital applications with  $V_{DD} >> V_{TH}$ , the switching power dissipation approximates the total power consumption and is proportional to the product of load capacitance  $C_L$  and  $V_{DD}^2$  as in (2.2). The dynamic power dissipation associated with the maximum operating frequency for short-channel devices can be written using (2.6) as

$$P_{Dyn,Swt} = \alpha C_L V_{DD}^2 \cdot \frac{1}{\tau} = \alpha \frac{C_{OX}}{S} \cdot \frac{V_{DD}^2}{U^2} \cdot \frac{v_{sat} S}{L} \cdot \frac{(V_{DD} - V_{TH} - V_{DSAT}/2)}{V_{DD}}$$

(2.7)

where  $\alpha$  is the switching activity factor. The power consumption scales quadratically with the power supply reduction. For a fixed frequency of operation, choosing a smaller feature size results in much lower active power which is scaled by  $I/(SU^2)$ , where S is the  $t_{ox}$  (dimension) scaling factor and U is the  $V_{DD}$  scaling factor. Also, from (2.6) and (2.7), the energy per operation (i.e. power-delay product) is reduced by scaling technology. Further, the UDSM processes also provide different flavors of devices with varying  $V_{TH}$  to cater to low-operating power (LOP), low-standby power (LSP), or high-performance (HP) circuit applications. Thus,

depending on the application, the choice of technology and the available device types can be exploited to design for low energy consumption. Specifically, the excess performance offered by technology scaling can be exchanged for energy-efficient computation.

### 2.4 Low Energy Design Techniques

Design techniques to lower computation energy have been implemented at different levels such as device level, logic level and at architectural level. Device level techniques employ threshold scaling, supply-voltage scaling or frequency scaling in order to lower the circuit's power dissipation by varying the operating conditions of the devices. At the logic level, the choice of circuit topology and the logic implementation, such as dynamic versus static logic, true single phase clocking (TSPC) logic etc., is employed. Architectural level techniques include parallel-computing, time-multiplexed, or pipelined system architecture to improve the system performance when operating at low power levels [3]. Since this work applies to device level optimization techniques, this literature study is limited to device level techniques.

### 2.4.1 Power Supply Voltage Scaling

As evident from (2.3),  $V_{DD}$  scaling presents a straight-forward and an effective method to lower power consumption in digital systems. The extent of  $V_{DD}$  scaling depends on the performance and energy-efficiency requirements in these circuits. However, the reduction in  $V_{DD}$  results in an increase in the propagation delay and thus lowers the maximum frequency of operation. Hence, there exists a power-performance, power-delay or energy-delay tradeoff with supply-voltage scaling. Figure 2.2 [7], [8] illustrates the energy-delay tradeoff in digital circuits. The energy-delay curve represents the optimal operating point to achieve a given performance with minimal energy consumption, or to operate at the maximum speed possible within a fixed energy constraint. The optimal energy-delay curve is derived for a system based on a set of design parameters such as activity level, transistor size, and  $V_{TH}$  levels. Thus any change in these design parameters would cause a shift in the energy-delay curve [8].

An unoptimized design's energy-efficiency can be improved by operating with minimum energy dissipation that corresponds to  $(E_{min},D_{max})$  co-ordinates in Figure 2.2, by relaxing the performance requirement, or by speeding up the system to operate at  $(E_{max}, D_{min})$  point by

Figure 2.2 Energy-delay optimization and tradeoff in digital circuit design [7], [8]

increasing the power consumption. Thus,  $V_{DD}$  scaling techniques operate at an optimum  $V_{DD}$  voltage for a required performance such that the power-delay product i.e. the energy per operation is at a minimum level [3], [7].

### 2.4.1.1 Multiple $V_{DD}$ schemes

Supply voltage islands or multiple  $V_{DD}$  are commonly used to optimize the energy consumption across a chip [9], [10]. Circuits that have high activity, i.e. large switching power component, use low  $V_{TH}$  devices and are biased at low  $V_{DD}$ . Similarly, low activity circuits that have appreciable leakage power are biased at high  $V_{DD}$  and employ high  $V_{TH}$  devices. Generation of multiple supply-voltages results in an increase in the total chip power and area.

### 2.4.1.2 Dynamic & Adaptive $V_{DD}$ schemes

Conventional dynamic voltage scaling (DVS) schemes vary the supply voltage to establish low power levels for the required frequency of operation [9], [10]. The critical path's delay associated with  $V_{DD}$  is monitored using ring-oscillator or FO4-based logic, and then a look-up-table is used to specify the optimum  $V_{DD}$  voltage that provides the required performance at the given temperature.

Some adaptive  $V_{DD}$  techniques employ closed-loop control systems to preserve minimum energy operation with  $V_{DD}$  variations. In [11], the authors present a control circuit that automatically adjusts both the  $V_{DD}$  and  $V_{TH}$  such that minimum power consumption is maintained across process and temperature variations. The control circuit determines the body bias voltage needed to obtain the optimum  $V_{TH}$  so that the ratio of the dynamic switching current to the static leakage current remains at a fixed level. In another  $V_{DD}$  adaptive low-power design work [12], the transistor gate-size ratio is varied with change in  $V_{DD}$  in order to maintain minimum energy point across different operating regions of the gate. This ensures that the large transistor sizes required for subthreshold operation does not increase the power when  $V_{DD}$  is set above the threshold voltage. A 6X reduction in the power-delay product was obtained.

### 2.4.2 Leakage power reduction

Highly energy-constrained applications such as energy harvesters that operate at ultralow voltages (ULV), low-speeds use subthreshold digital operation to achieve energy efficiency. While low-voltage operation reduces the dynamic switching power, the static leakage of the devices increases. Thus the minimum energy point (MEP) in these applications is primarily set by the supply voltage for which the switching power is equal to the leakage power [18]. Since the static leakage currents in ULV operation form a considerable percent of the total power, techniques to reduce the leakage currents are necessary.

At stand-by mode of operation, the power dissipated by static leakage currents can be eliminated by power gating [19]. Pass-transistors are used to connect the circuit to the power supply or ground terminal. When the system is in idle state, the pass-transistors are switched off and thereby disconnecting the circuit from the supply terminal. Now, the power consumption is mainly due to the leakage current flowing through the pass-transistor.

Transistor stacking technique uses stacked transistor gates to reduce the subthreshold leakage current. When both the transistors are switched "off", the gate-to-source voltage of the top transistor is negative and the increase in  $V_{TH}$  due to body effect results in lower subthreshold leakage currents [19].

Several dynamic/adaptive body biasing techniques that vary the device  $V_{TH}$  have been effectively used to reduce leakage current [20], [21]. To minimize the stand-by power, the  $V_{TH}$  of

devices are adaptively increased by varying levels of reverse body-bias. Some recent works have shown that simultaneous supply voltage scaling and bidirectional body is effective in achieving high performance in standby as well as active mode of operation.

### 2.4.3 Charge-recycling systems

Charge-recycling (CR) or energy-recovery refers to the low-power design approach that recovers some of the charge stored in the load capacitances ( $C_L$ ). Figure 2.3 shows a simple RC circuit that models an inverter's switching action (charge-discharge of  $C_L$ ) with R representing the on-resistance (Ron) of the active device and C is the load capacitance. A digital transition from LOW to HIGH requires that the load capacitance is charged to  $V_{DD}$ . The energy expended by the power supply, for this transition, is  $C_LV_{DD}^2$  and the energy stored in the load capacitance is  $C_LV_{DD}^2/2$  while the switch (Ron) dissipates the remaining energy. A switching transition of HIGH to LOW discharges the load capacitor to ground and this process dissipates the energy stored ( $C_LV_{DD}^2/2$ ) in the capacitor. Thus, for one clock cycle of operation, the energy dissipated by the power supply is  $C_LV_{DD}^2$  and the charge supplied is  $C_LV_{DD}$ . While adiabatic computing techniques work on reducing the actual energy expended ( $C_LV_{DD}^2$ ) by the power supply, charge-recycling techniques aim at recovering the stored charge ( $C_LV_{DD}^2$ ) from one computation and reusing for subsequent computations. Note that the entire charge from the load capacitor can potentially be recycled in the charge-recovery process.

Several implementations of charge-recycling or energy-recovery systems have been reported as in [13]-[17], [22]-[27]. Some of the energy recovery systems are discussed with

Figure 2.3 Charging and discharging action in switch [16]

reference to adiabatic computing. The latter part of this section focuses on charge-recycling approaches that use the recovered charge to supply power for other computations, and are directly relevant to this research effort.

### 2.4.3.1 Adiabatic Energy-recovery Logic

The principle behind energy-efficient adiabatic logic is to dissipate very low energy during charging of load capacitances and recovering most of the energy back to the power-supply during the discharge phase. This is accomplished by the use of clocked power-supply that is derived from the clock signal. The energy recovery process and the power supply waveform are illustrated in Figure 2.4. With controlled, slow edge-transitions, the voltage drop across the PMOS transistors is small and the output voltage follows the slope of the power-supply clock. This results in lower peak charging-current and thus low energy dissipation during the charge of  $C_L$ . During the hold phase of the power supply clock, the output voltage is sampled or evaluated in the subsequent stage. During the recovery phase, the power-supply transitions to zero and the charge stored in the load capacitor is transferred back to the supply. The total energy dissipated by adiabatic switching is approximately

$$E_{DISS} = \frac{RC}{T_S} C V_{DD}^2 \tag{2.8}$$

where R is the effective "on" resistance of the gate, C is the load capacitance,  $T_S$  is the edge transition time of the power supply clock and  $V_{DD}$  the power supply voltage. Ideally with very slow clock transitions, the energy expended per operation can be made very low. Multiple clock phases are employed to synchronize the stages such that the hold time of a stage falls during the evaluate phase of the subsequent stage. Four-phase clock with 90° phase shift is recommended for effective energy saving [17].

The main challenge in adiabatic computing is the generation of efficient power supply sources that transfer bidirectional energy to and from the circuit [17]. The transition time of the power-clock which needs to be large enough to reduce the energy consumption also results in large propagation delay in the path. Additionally, the circuitry overhead associated with the energy-recovery process would reduce the overall efficiency.

Figure 2.4 Charging and discharging action in switch [16], [17]

### 2.4.3.2 Vertically-stacked $V_{DD}$ techniques

The charge-recycling technique based on vertically-stacked computation logics has been explored by *Rajapandian et al.* [22]-[24] and *Gu et al.* [25]. Implicit charge-recycling is accomplished by vertically stacking identical logic units such that the ground-bound charge from a digital *HIGH* to *LOW* transition in upper tier (domain) logic cells can be reused for a *LOW* to *HIGH* transition in the lower stack (domain). Thus this scheme is effective for large computation systems that are made of several identical logic unit blocks with similar energy consumption, performance and concurrent operation.

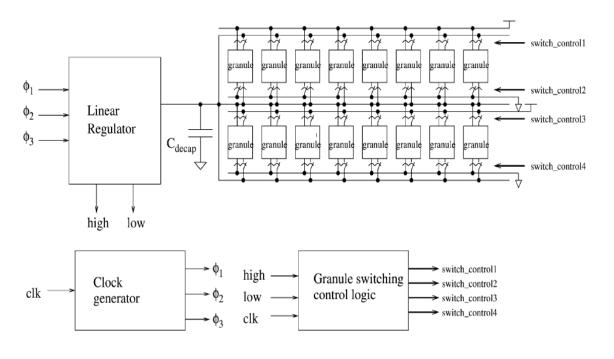

The goal of *Rajapandian's* work was to achieve energy-efficient on-chip dc-dc conversion to supply power for digital circuits using *CR*. Figure 2.5 shows the charge-recycling prototype presented in [24]. A 16x16 carry-save array multiplier is split into 16 logic partitions (granules) and connected in vertical stacks with different supply voltages. A linear push-pull regulator controls the ground reference voltage of the upper domain which is also the power supply voltage of the lower domain granules. Additionally, the regulator monitors the transient current consumption of both the domains. When perfectly matched, the entire current demand of the lower domain granules is supplied by the upper domain. An imbalance between domains would require the regulator to supply the current difference. When a current source-sink imbalance of more than a permissible amount is detected between the domains, the granule switching control logic randomly chooses a granule from the appropriate domain and switches it over to the other domain. This automatic charge (current)-balancing scheme between the logic

domains improves the energy-efficiency of the system and a measured efficiency of 85% was reported for  $V_{DD}/2$  conversion [24].

Vertical voltage-stacking (logic-domain) reduces the total current flowing in each power supply route by 50% (without CR) for the same supply voltage levels. With charge-recycling between domains, the external (off-chip) current requirement is further decreased. The amount of current reduction depends on the number of logic domains employed and the switching activity in the domains. A direct consequence of lower supply current is a significant reduction in the IR and Ldi/dt noise associated with each supply. Furthermore, the current requirements on the linear regulator and thus the size of the pass transistor and on-chip decoupling capacitor are reduced. Hence, charge-recycling based  $V_{DD}$  stacking proves to be an effective method of power delivery through dc-dc down conversion.

Another implementation of multi-story logic based charge-recycling has been presented by *Gu and Kim* [25]. Their approach is similar to *Rajapandian et al.* [22]-[24] in the use of stacked logic to reuse the charge discarded by upper domain for computations in the lower domain. Their implementation differs in the current balancing technique where digital voltage

Figure 2.5 Charge recycling system based on vertically-stacked logic cells [24]

regulation is achieved by adjusting the switching activity of the functional units in all the logic stacks. This is accomplished by sensing the supply voltage variation and by controlling the digital inputs to the functional units such that the supply voltage is regulated. The focus of their efforts was to use logic stacking as a means of low-noise, power supply delivery. Ring oscillators, 16-bit LFSR and ALUs were used to evaluate the effectiveness of this scheme. Simulation results were presented to quantify the *IR* noise reduction to be 66% and *Ldi/dt* noise reduction of 67% with total power savings of 5% [25].

The main drawback of the stacked  $V_{DD}$  technique is that the current balancing between the logic stacks is critical to ensure the charge from higher stacks is efficiently recycled in the lower domain stacks. A current monitoring mechanism that regulates the current consumption across the stacked domains would dissipate power and might not be a viable option for all mixed signal systems. Voltage-level converters that are necessary to communicate between the different power domains would also consume power. Additionally, in order to avoid severe body-effect or possible device breakdown, the body connections of NMOS transistors in the upper voltage domains need to be isolated and tied to their respective ground reference voltages. So, silicon-on-insulator (SOI) or triple-well processes would be essential for logic domain ( $V_{DD}$ ) stacking to work.

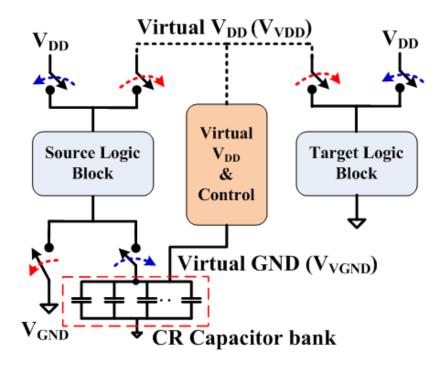

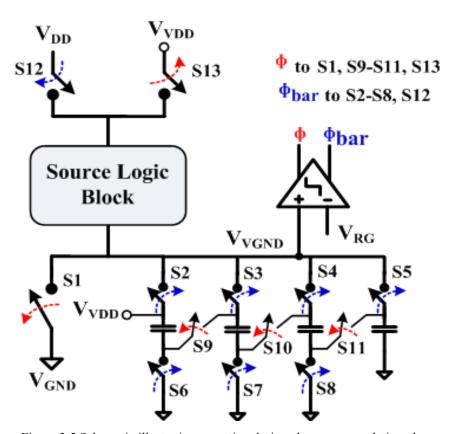

### 2.4.3.3 Charge-pump based charge-recycling Schemes

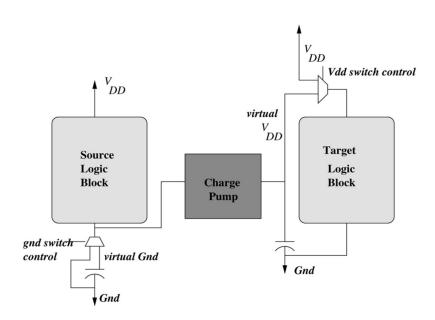

A charge-pump based recycling scheme using virtual supply and virtual ground has been published by *Manne et al.* [26]. This scheme works on the principle of collecting the ground-bound charge during the discharge of load capacitance. Once the virtual ground reaches a threshold voltage, the charge is boosted by a charge pump to  $V_{DD}$  and is then used as a supply voltage. Figure 2.6 shows the architecture of this recycling scheme.

To improve the energy efficiency, the charge pump uses adiabatic charge boosting techniques where the charge transfer to the charge-pump's output capacitor happens in voltage increments. This energy conscious charge-pump action presents an inherent delay to boost the virtual  $V_{DD}$  node to the required supply voltage. This delay is overlapped with the computational delays within the digital system. Hence, the application of this method is constrained to digital systems with considerable computation time and pipelined operation. Also, the generation of

control signals, the threshold voltages and the incremental voltages for adiabatic charge pump action would consume finite power that would reduce the system's energy efficiency. This design was implemented in digital signal processing (DSP) circuits to reduce the energy consumption by as much as 18% (on average of 9.9%) without perceptible loss in performance [26].

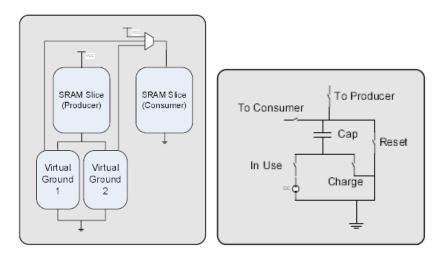

A modified version of this recycling scheme that reduces the power required to generate the control signals for monitoring the various virtual nodes was published by  $Keung\ et\ al.$  [28]. A single-stage charge pump along with a DC voltage source boosts the recycled charge to  $V_{DD}$ . Figure 2.7 presents the conceptual schematic of the memory slice along with the virtual ground modules. This system uses two time-multiplexed charge accumulation capacitors to recycle charge. Once the capacitor reaches a fixed threshold voltage, it is disconnected from the "producer" slice and the stored voltage is pumped up to the required power supply voltage of the "consumer" slice. Energy savings of 25% was reported on SRAM L2 caches based on SPICE simulations.

Figure 2.6 Conceptual schematic of the charge recycling scheme [26].

Figure 2.7 Conceptual schematic of charge-recycling scheme [28]

### 2.5 Conclusion

The literature review is not a comprehensive discussion of all the reported low-power digital design techniques but includes design methodologies relevant to this work. The above discussed techniques have been targeted for large computational digital systems such as microprocessors, DSP chips, memories etc. For a small mixed-signal system, such as an ADC where digital control circuits consume appreciable amount of power, techniques that integrate the advantages of these low-power design techniques are required to accomplish energy-efficient computations. Also, low-power technique that achieves energy-efficient, low-cost operation across wide operating range offers significant advantage. Hence, this research employs continuous voltage scaling as well as charge-recycling methodologies as a means of lowering power consumption in mixed-signal systems.

Table 2.1 presents a comparison of the state-of-the-art charge-recycling based methodologies that reduce the power dissipated in digital systems. While the vertical stacking of digital blocks [24] provides large power reduction, it is not conducive to mixed-signal systems where matching of current consumption might not be possible. While the single-stage charge-pump design [28] require external charge pump clock, the three-stage charge-pump based voltage boosting design [26] also requires a considerable startup time that is masked within the

logic paths. The literature study has thus directed this research effort to address these keys concerns in order to extend the application of charge-recycling techniques to mixed-signal systems.

Table 2.1 Comparison of the state-of-the-art Charge-recycling based low power techniques

| Reference | % Power Saving                                           | Features                 | Comments                                         |

|-----------|----------------------------------------------------------|--------------------------|--------------------------------------------------|

| [24]      | 33 % ( $V_{DD}$ stacks)<br>85 % ( $V_{DD}/2$ conversion) | $V_{DD}$ stacks          | Current balancing critical                       |

| [25]      | 5 % (dual V <sub>DD</sub> stacks)                        | $V_{DD}$ stacks          | About 66 % reduction in noise                    |

| [26]      | 10 %                                                     | Adiabatic Charge pump    | External, multiple<br>phase CP clock<br>required |

| [28]      | 25 %*                                                    | Single-stage Charge pump | External boost voltage required                  |

<sup>\*</sup> Simulation results

# Chapter 3 Design and Analysis of the Proposed Charge Recycling Scheme

This chapter is revised based on the paper published by Chandradevi Ulaganathan et al. [32]:

C. Ulaganathan, C. L. Britton, Jr., J. Holleman, and B. J. Blalock, "A Novel Charge Recycling Approach to Low-Power Circuit Design," *Intl. Conference on Mixed Design of Integrated Circuits and Systems*, pp. 208–213, May 2012.

My primary contribution to this paper include (i) identification of the scope of research, (ii) compilation of a literature review of previously published work, (iii) design of the proposed solution, (iv) analysis of simulation results, and (v) preparation of the manuscript.

The objectives of this research include:

- To investigate the feasibility of charge-recycling (CR) based low-power design

- To propose a novel CR methodology that overcomes the limitations of the state-of-the-art CR designs.

- To insure that the proposed scheme should be easily adaptable to existing digital circuits and independent of the process technology employed.

# 3.1 Introduction

An important figure-of-merit in energy efficient systems is the minimization of energy per cycle of operation,  $E_{TOT}$ .  $E_{TOT}$  is the total power-delay product, given by  $P_{TOT} \cdot T_{clk}$ , which is the power  $(P_{TOT})$  consumed to perform all required computations within one clock cycle  $(T_{clk})$ . The minimization of  $E_{TOT}$  maximizes the energy efficiency [4]. In this section, the factors governing digital power consumption, and the path or propagation delay are examined to explore the feasibility of charge-recycling based energy reduction techniques.

#### 3.1.1 Switching or Dynamic Power dissipation

As discussed in chapter 2, the power consumption in a digital circuit can be approximated as

$$P_{total} = \alpha \left( C_L \cdot V_{DD}^2 \cdot f_{CLK} \right) + I_{SC} \cdot V_{DD} + I_{Lkg} \cdot V_{DD}$$

(3.1)

The switching component of total power dissipation can be reduced by minimizing the load capacitance  $C_L$  that is charged or discharged at each logic transition, or by reducing the logic voltage level (i.e. the power-supply voltage  $V_{DD}$ ), or by lowering the frequency of the logic transitions (i.e. frequency of operation  $f_{CLK}$ ). The impact of these design parameters on power reduction and their tradeoffs will be examined in this section.

As evident in (3.1), the node capacitance ( $C_L$ ) and  $V_{DD}$  determine the amount of charge drawn from the power supply for each digital transition. Hence, minimization of  $C_L$  helps in reducing the power consumption. The load capacitance encompasses the diffusion and gate-drain (Miller) capacitances at the driver output, gate capacitance of the load, interconnect (wire) capacitance, and any external capacitance connected to that node. The device capacitances are in turn determined by the transistor sizing that is controlled by the drive-strength requirement (i.e. fanout) of the path, power and area specifications. Minimum-sized gates have the lowest diffusion and gate capacitances, and thus the least  $C_L$ , are suitable for low-power, area-efficient designs. However, larger PMOS ratios are often essential to have symmetric rise and fall transitions, and good noise margin for robust circuit operation. The general design methodology is to optimize the sizing ratio of the transistors in order to achieve a given performance, area, energy or power specification [29].

A CMOS buffer is used to illustrate how device sizing affects the power consumption and the performance of the circuit. The propagation delay of an inverter is given by

$$t_{pd} = \frac{t_{pHL} + t_{pLH}}{2} = 0.69 \cdot C_L \left(\frac{R_{eqN} + R_{eqP}}{2}\right)$$

(3.2)

where  $C_L$  is the load capacitance at the output node and  $R_{eqN}$ ,  $R_{eqP}$  are the equivalent "ON" resistances of the NMOS and PMOS transistors. The load capacitance at the output is given by [29]

$$C_L = C_{dn1} + \beta C_{dn1} + C_{gn2} + \beta C_{gn2} + C_w$$

(3.3)

where  $\beta$  is the sizing ratio of the PMOS to NMOS transistors,  $C_{dn1}$  includes the diffusion and gate-drain Miller capacitance of the driver,  $C_{gn2}$  is the gate capacitance of the load, and  $C_w$  is the interconnect capacitance. The equivalent "ON" resistance of the transistor can be approximated as [29]

$$R_{eq} \approx \frac{3}{4} \frac{V_{DD}}{I_{DSAT}} \text{ where } I_{DSAT} = K' \frac{W}{L} \left( (V_{GS} - V_{TH}) V_{DSAT} - \frac{V_{DSAT}^2}{2} \right)$$

(3.4)