#### University of Tennessee, Knoxville

# TRACE: Tennessee Research and Creative Exchange

**Doctoral Dissertations**

Graduate School

12-2012

#### **Exploring Computational Chemistry on Emerging Architectures**

David Dewayne Jenkins *University of Tennessee - Knoxville*, ddj@utk.edu

Follow this and additional works at: https://trace.tennessee.edu/utk\_graddiss

Part of the Computer and Systems Architecture Commons, Numerical Analysis and Scientific Computing Commons, and the Other Chemistry Commons

#### **Recommended Citation**

Jenkins, David Dewayne, "Exploring Computational Chemistry on Emerging Architectures." PhD diss., University of Tennessee, 2012.

https://trace.tennessee.edu/utk\_graddiss/1531

This Dissertation is brought to you for free and open access by the Graduate School at TRACE: Tennessee Research and Creative Exchange. It has been accepted for inclusion in Doctoral Dissertations by an authorized administrator of TRACE: Tennessee Research and Creative Exchange. For more information, please contact trace@utk.edu.

To the Graduate Council:

I am submitting herewith a dissertation written by David Dewayne Jenkins entitled "Exploring Computational Chemistry on Emerging Architectures." I have examined the final electronic copy of this dissertation for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Doctor of Philosophy, with a major in Computer Engineering.

Gregory D. Peterson, Major Professor

We have read this dissertation and recommend its acceptance:

Robert J. Hinde, Robert J. Harrison, Itamar Arel

Accepted for the Council:

Carolyn R. Hodges

Vice Provost and Dean of the Graduate School

(Original signatures are on file with official student records.)

Doctoral Dissertations Graduate School

12-2012

# Exploring Computational Chemistry on Emerging Architectures

David Dewayne Jenkins *University of Tennessee - Knoxville*, ddj@utk.edu

#### To the Graduate Council:

I am submitting herewith a dissertation written by David Dewayne Jenkins entitled "Exploring Computational Chemistry on Emerging Architectures." I have examined the final electronic copy of this dissertation for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Doctor of Philosophy, with a major in Computer Engineering.

Gregory D. Peterson, Major Professor

We have read this dissertation and recommend its acceptance:

Robert J. Hinde, Robert J. Harrison, Itamar Arel

Accepted for the Council: Carolyn R. Hodges

Vice Provost and Dean of the Graduate School

(Original signatures are on file with official student records.)

# Exploring Computational Chemistry on Emerging Architectures

A Dissertation

Presented for the

Doctor of Philosophy

Degree

The University of Tennessee, Knoxville

David Dewayne Jenkins

December 2012

© by David Dewayne Jenkins, 2012 All Rights Reserved. This dissertation is dedicated to my beautiful fiancée, Priya, for her love and support.

# Acknowledgments

First, I would like to thank my advisors, Dr. Gregory Peterson and Dr. Robert Hinde, for their support and guidance throughout my research. They provided invaluable insight and inspiration that helped shape my research to what it is today. Without their assistance and incessant motivation, there is no telling if I would have ever finished this work.

I would also like to thank Dr. Robert Harrison for serving on my committee and providing some of the computational resources used in this research. In addition, I would like to thank Dr. Itamar Arel for serving on my committee and for allowing me to audit his random processes class so that I could better understand the statistical properties of the application used in this work. I would also like to thank Dr. Harry Richards for his continued financial and educational support.

Without the motivation from friends, I would not have continued to pursue this research. I would like to thank Nicholas Lineback and Dylan Storey for their numerous and long conversations about computers, science, sci-fi movies and TV shows, and everything in between. Their camaraderie has proved to be a helpful release from the trials of research.

Family has played an important role throughout this work. My family put up with listening to me complain about work, not coming home as often as I should, and being a complete zombie when I did come home. Without their understanding and support, there is no telling how my life would have turned out. There is nothing that I could do to ever repay them for their support.

Most of all, I would like to thank my wonderful fiancée, Priya, for standing by me throughout this entire journey with nothing but pure motivation and support. From long talks to making delicious dinners, she has been the cornerstone of my sanity throughout this work. Without her, I would not have continued pursuing my Ph.D. I cannot thank her enough.

Personal funding was supplied by the SCALE-IT fellowship (NSF grant DGE-0801540). Computational resources were supplied through the National Science Foundation grant NSF CHE-0625598.

Everyone you will ever meet knows something you don't. - Bill Nye

#### Abstract

Emerging architectures, such as next generation microprocessors, graphics processing units, and Intel MIC cards, are being used with increased popularity in high performance computing. Each of these architectures has advantages over previous generations of architectures including performance, programmability, and power efficiency. With the ever-increasing performance of these architectures, scientific computing applications are able to attack larger, more complicated problems. However, since applications perform differently on each of the architectures, it is difficult to determine the best tool for the job. This dissertation makes the following contributions to computer engineering and computational science. First, this work implements the computational chemistry variational path integral application, QSATS, on various architectures, ranging from microprocessors to GPUs to Intel MICs. Second, this work explores the use of analytical performance modeling to predict the runtime and scalability of the application on the architectures. This allows for a comparison of the architectures when determining which to use for a set of program input parameters. The models presented in this dissertation are accurate within 6%. This work combines novel approaches to this algorithm and exploration of the various architectural features to develop the application to perform at its peak. In addition, this expands the understanding of computational science applications and their implementation on emerging architectures while providing insight into the performance, scalability, and programmer productivity.

# Contents

| 1 | Intr | roduction                                    | 1  |

|---|------|----------------------------------------------|----|

|   | 1.1  | Motivation                                   | 1  |

|   | 1.2  | Problem                                      | 2  |

|   | 1.3  | Approach                                     | 3  |

|   | 1.4  | Contribution                                 | 4  |

|   | 1.5  | Outline                                      | 4  |

| 2 | Bac  | ekground and Related Work                    | 6  |

|   | 2.1  | Monte Carlo Simulations                      | 6  |

|   | 2.2  | Variational Path Integral Monte Carlo Method | 7  |

|   | 2.3  | Survey of Architectures                      | 12 |

|   |      | 2.3.1 Microprocessors                        | 12 |

|   |      | 2.3.2 GPUs                                   | 13 |

|   |      | 2.3.3 Intel MIC                              | 14 |

|   | 2.4  | Performance Modeling                         | 14 |

|   | 2.5  | Architectures for Monte Carlo                | 16 |

|   |      | 2.5.1 Random Number Generation for MC        | 18 |

| 3 | Mic  | croprocessors and Intel MIC                  | 19 |

|   | 3.1  | Basic Algorithm overview                     | 19 |

|   | 3.2  | Code Overview                                | 21 |

|   |      | 3.2.1 Step 1: Initialization                 | 21 |

|          |      | 3.2.2   | Step 2: Gaussian Displacements        | 22         |

|----------|------|---------|---------------------------------------|------------|

|          |      | 3.2.3   | Step 3: Potential Energy Calculations | 24         |

|          |      | 3.2.4   | Step 4: Accept or Reject a Move       | 25         |

|          |      | 3.2.5   | Step 5: Snapshotting                  | 26         |

|          |      | 3.2.6   | Step 6: Finalization                  | 26         |

|          | 3.3  | Micro   | processor Implementation              | 27         |

|          |      | 3.3.1   | Serial                                | 27         |

|          |      | 3.3.2   | Parallel - Vectorization              | 33         |

|          |      | 3.3.3   | Parallel - Threads                    | 36         |

|          |      | 3.3.4   | Parallel - MPI                        | 37         |

|          | 3.4  | Intel 1 | MIC Implementation                    | 43         |

| 4        | Gra  | phics   | Processing Units                      | <b>4</b> 5 |

|          | 4.1  | NVID    | IA GPU Architectures                  | 45         |

|          |      | 4.1.1   | Tesla                                 | 46         |

|          |      | 4.1.2   | Fermi                                 | 47         |

|          | 4.2  | GPU :   | Programming Synopsis                  | 48         |

|          |      | 4.2.1   | CUDA                                  | 48         |

|          |      | 4.2.2   | OpenCL                                | 49         |

|          | 4.3  | VPI I   | mplementation                         | 49         |

|          |      | 4.3.1   | CUDA                                  | 50         |

|          |      | 4.3.2   | OpenCL                                | 57         |

|          |      | 4.3.3   | Multi-GPU Support                     | 58         |

| <b>5</b> | Disc | cussior | n of Results                          | 60         |

|          | 5.1  | Micro   | processor Results                     | 61         |

|          |      | 5.1.1   | Serial Optimizations                  | 61         |

|          |      | 5.1.2   | Vectorization                         | 64         |

|          |      | 5.1.3   | Threads                               | 66         |

|          |      | 5.1.4   | MPI                                   | 79         |

|    | 5.2    | Intel N | MIC                         | 82  |

|----|--------|---------|-----------------------------|-----|

|    | 5.3    | GPU     |                             | 85  |

|    | 5.4    | Archit  | ecture Comparisons          | 97  |

| 6  | Per    | forman  | ace Modeling                | 102 |

|    | 6.1    | Microp  | processor Performance Model | 102 |

|    |        | 6.1.1   | Single Core Model           | 103 |

|    |        | 6.1.2   | Parallel                    | 115 |

|    | 6.2    | Graph   | ics Processing Units        | 131 |

|    |        | 6.2.1   | NVIDIA Tesla c1060          | 132 |

|    |        | 6.2.2   | Fermi Architecture          | 138 |

| 7  | Fut    | ure Wo  | ork and Conclusions         | 145 |

|    | 7.1    | Future  | • Work                      | 145 |

|    | 7.2    | Conclu  | isions                      | 146 |

| Bi | ibliog | graphy  |                             | 150 |

| V  | ita    |         |                             | 166 |

# List of Tables

| 2.1  | Parameters for the HFDB-He calculations in equation 2.5       | 10  |

|------|---------------------------------------------------------------|-----|

| 4.1  | Hardware interpolation parameters                             | 55  |

| 5.1  | Processors and compilers tested                               | 60  |

| 5.2  | GPUs tested                                                   | 61  |

| 5.3  | Parameters used for correctness tests                         | 63  |

| 5.4  | Speedups for the vectorized microprocessor implementation     | 65  |

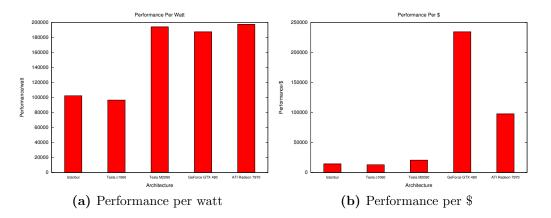

| 5.5  | Power consumption and current price for each compute device   | 98  |

| 6.1  | QSATS specific parameters for the performance model           | 104 |

| 6.2  | Break down of times in the QSATS program                      | 106 |

| 6.3  | Operation cycles used in the microprocessor performance model | 108 |

| 6.4  | Parameters to the single core microprocessor model            | 113 |

| 6.5  | Parameters for the MPI models                                 | 119 |

| 6.6  | Parameters for the Kraken supercomputer                       | 123 |

| 6.7  | Model results of the single master implementation             | 123 |

| 6.8  | Accuracy of the multi-master MPI model                        | 128 |

| 6.9  | Tesla c1060 model parameters                                  | 136 |

| 6.10 | Fermi model parameters                                        | 140 |

# List of Figures

| 1.1  | Architectures that are explored in this dissertation              | 3  |

|------|-------------------------------------------------------------------|----|

| 3.1  | General flowchart of the VPI method                               | 20 |

| 3.2  | Actual potential energy function versus interpolated values       | 23 |

| 3.3  | Accept/reject regions                                             | 26 |

| 3.4  | Runtime composition of serial C code                              | 28 |

| 3.5  | Code snippets of the potential energy lookup table initialization | 29 |

| 3.6  | Diagram of the inner and outer regions of neighbors               | 31 |

| 3.7  | Predetermination regions for accepting or rejecting a move        | 34 |

| 3.8  | Memory packing for SSE vectorization                              | 35 |

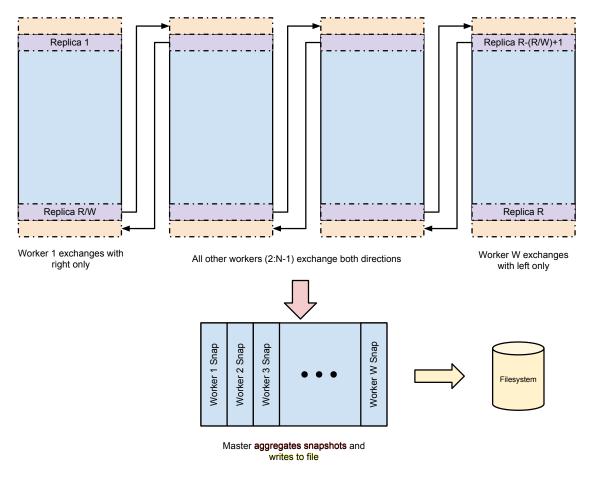

| 3.9  | Exchange of work among workers                                    | 40 |

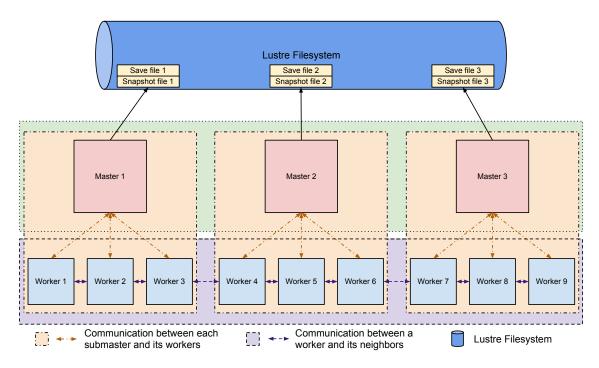

| 3.10 | Multiple master MPI approach                                      | 42 |

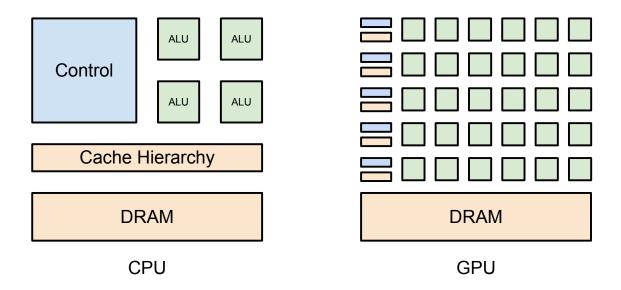

| 4.1  | CPU Architecture versus the GPU                                   | 49 |

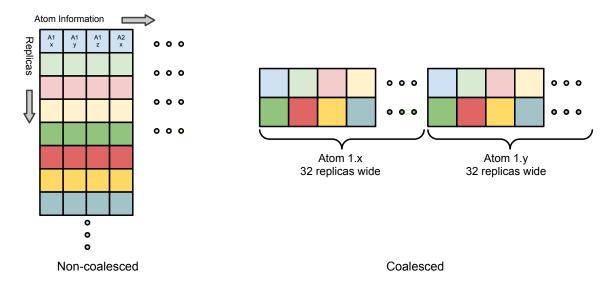

| 4.2  | GPU data layout allowing for coalesced accesses                   | 51 |

| 4.3  | GPU log-scale potential energy lookup table                       | 56 |

| 4.4  | Statistical correctness for GPU implementation                    | 56 |

| 5.1  | Serial optimizations                                              | 62 |

| 5.2  | Check for microprocessor C statistical correctness                | 63 |

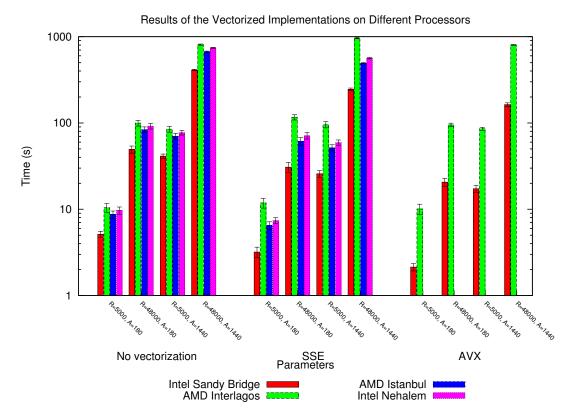

| 5.3  | Vectorization runtime results                                     | 64 |

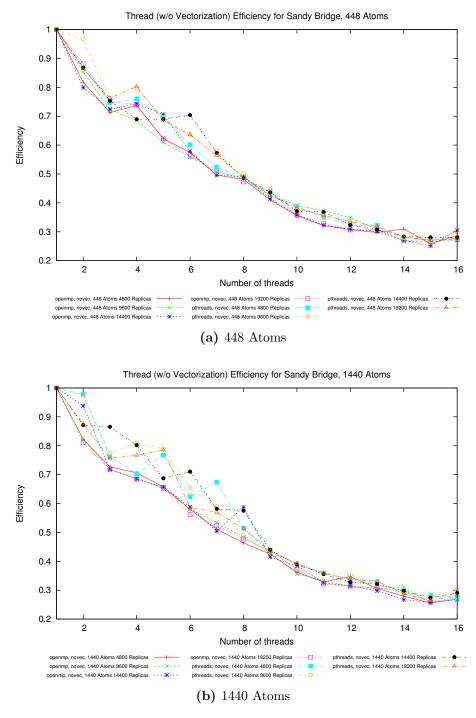

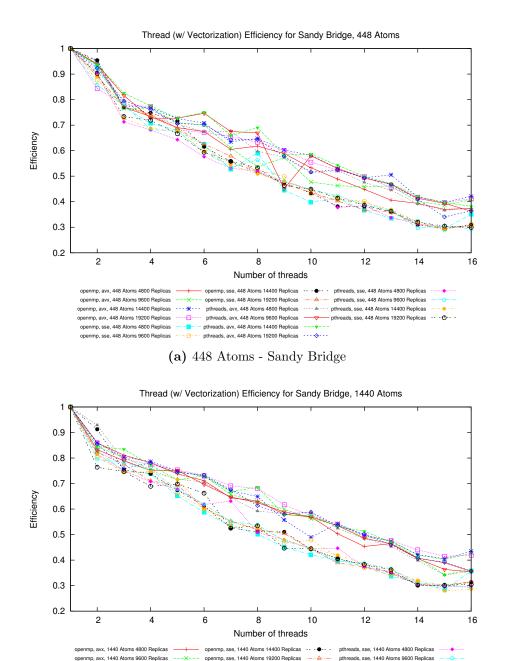

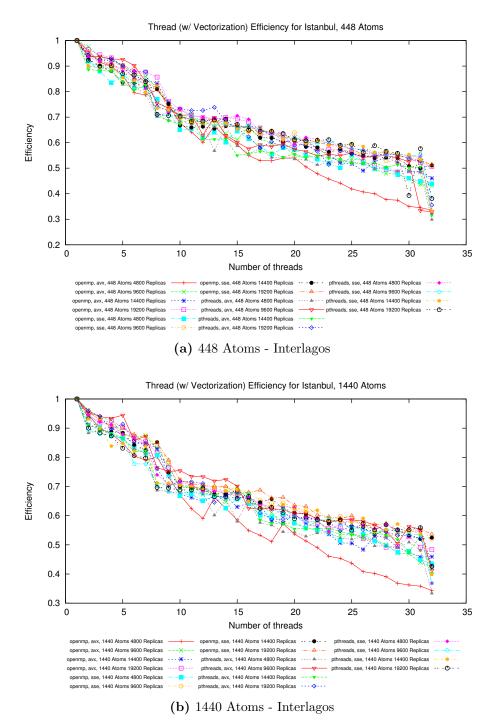

| 5.4  | Threaded results for the Sandy Bridge processor                   | 67 |

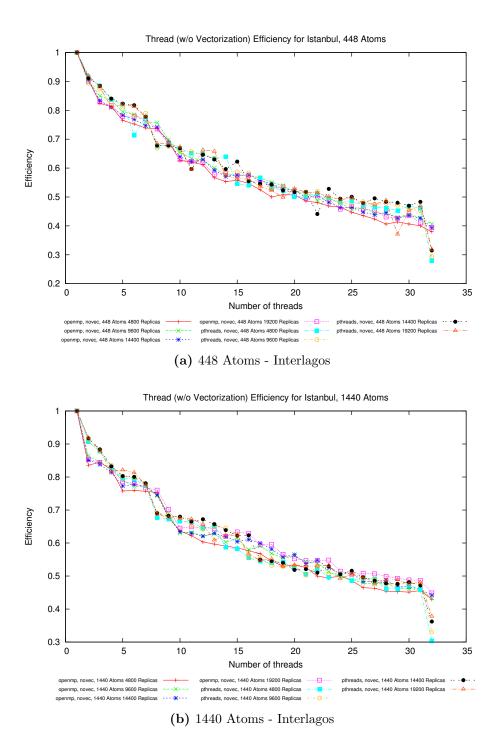

| 5.5  | Threaded results for the Interlagos processor                     | 68 |

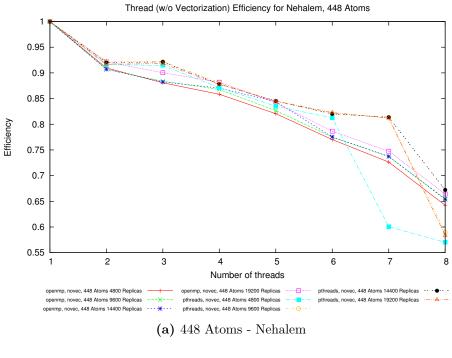

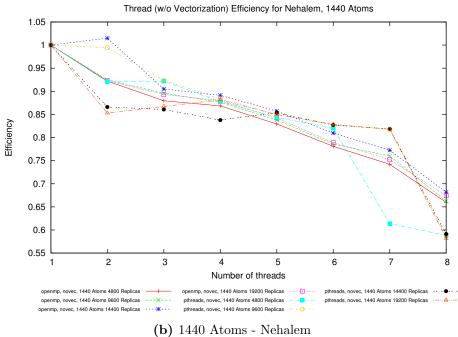

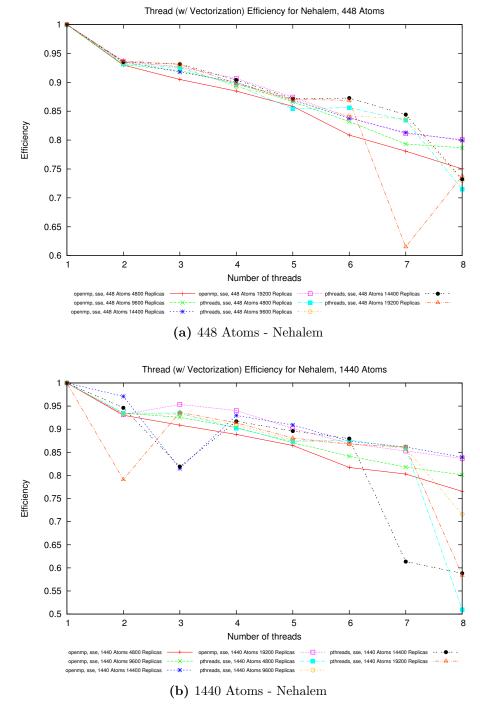

| 5.6  | Threaded results for the Nehalem processor                        | 69  |

|------|-------------------------------------------------------------------|-----|

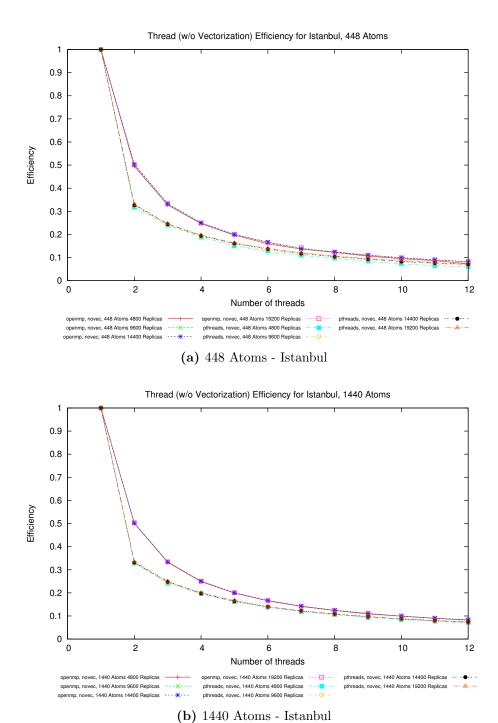

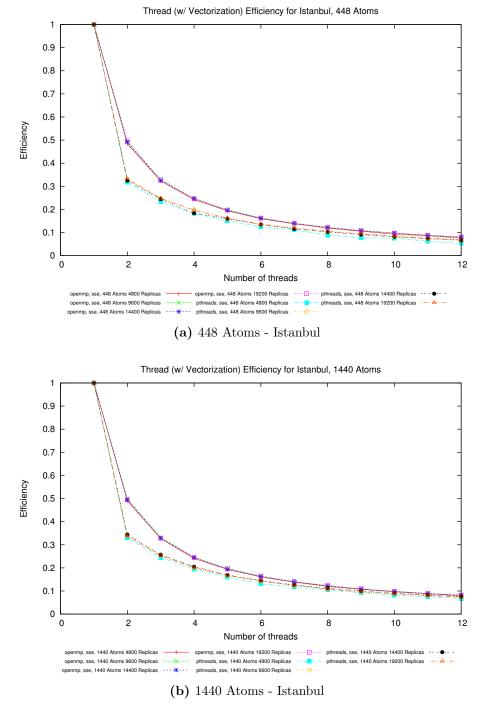

| 5.7  | Threaded results for the Istanbul processor                       | 70  |

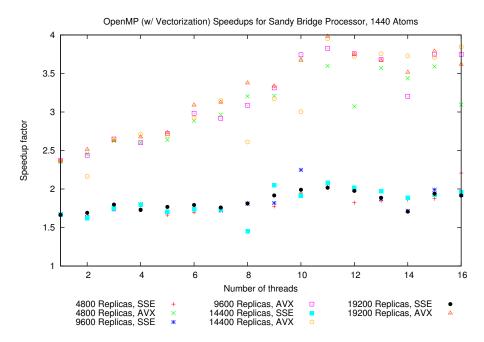

| 5.8  | OpenMP with vectorization speedups for the Sandy Bridge processor | 71  |

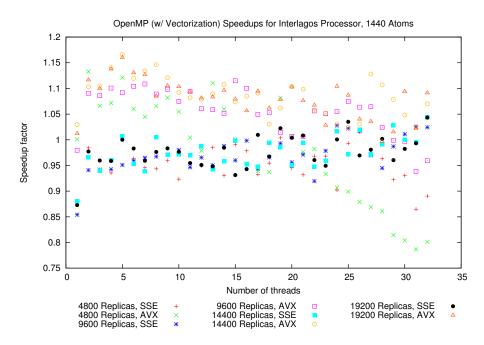

| 5.9  | OpenMP with vectorization speedups for the Interlagos processor   | 72  |

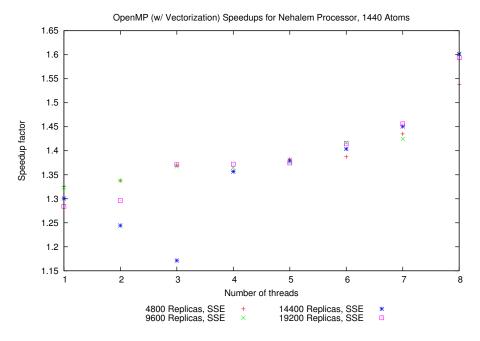

| 5.10 | OpenMP with vectorization speedups for the Nehalem processor      | 72  |

| 5.11 | OpenMP with vectorization speedups for the Istanbul processor     | 73  |

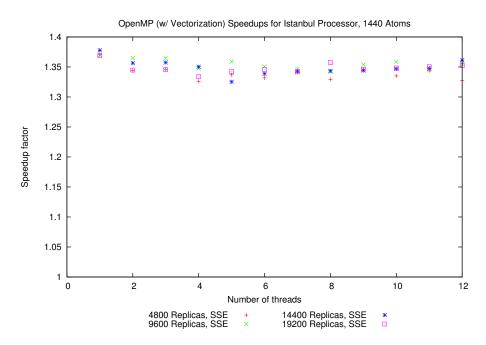

| 5.12 | Threaded vectorized results for the Sandy Bridge processors       | 74  |

| 5.13 | Threaded vectorized results for the Interlagos processors         | 75  |

| 5.14 | Threaded vectorized results for the Nehalem processors            | 76  |

| 5.15 | Threaded vectorized results for the Istanbul processors           | 77  |

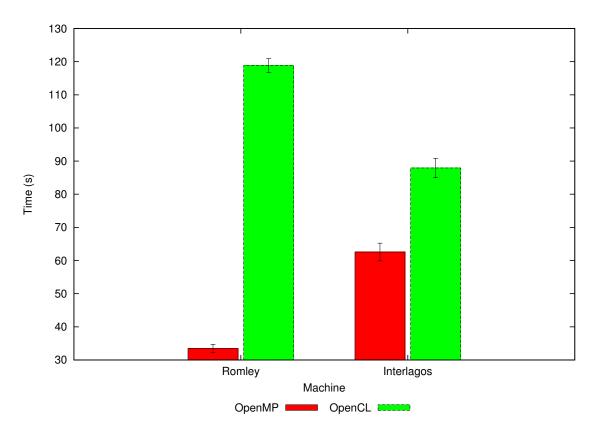

| 5.16 | OpenCL comparison to OpenMP threaded multiprocessor code          | 78  |

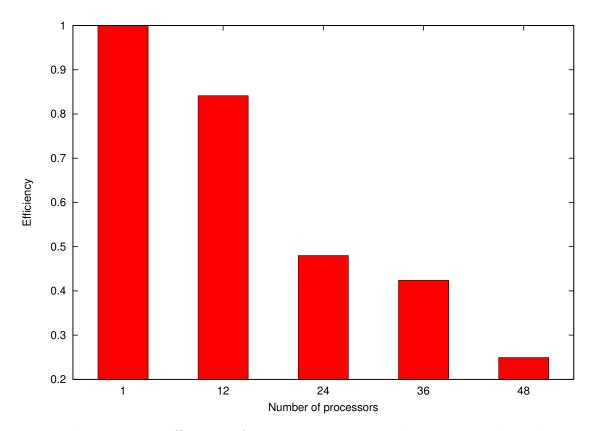

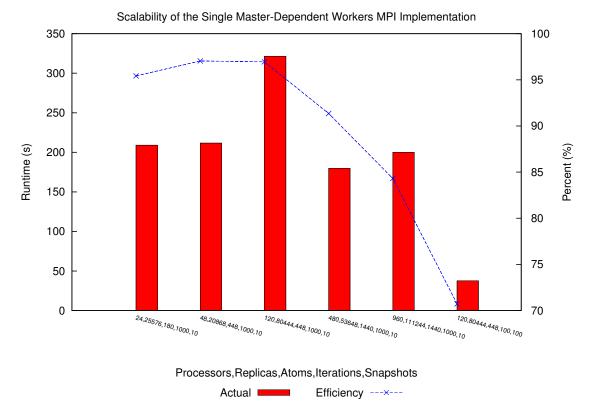

| 5.17 | Efficiency of the single master - independent worker code         | 79  |

| 5.18 | Single master performance rates and efficiency                    | 81  |

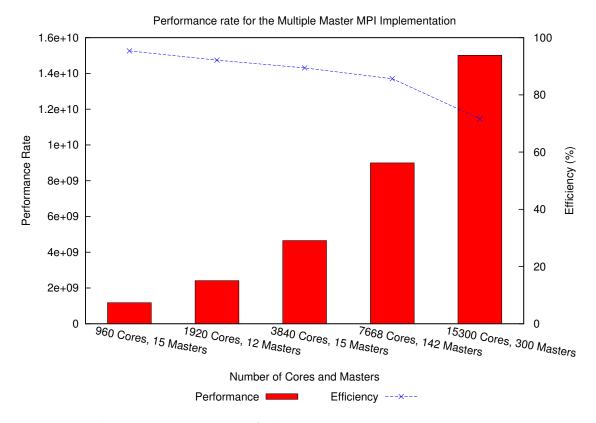

| 5.19 | Results of the multiple masters implementation                    | 82  |

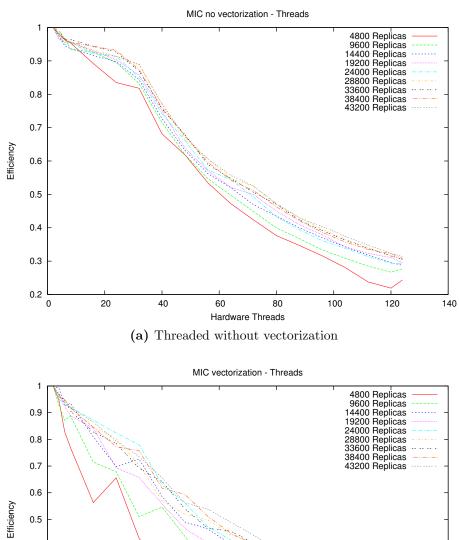

| 5.20 | Intel MIC threaded results                                        | 83  |

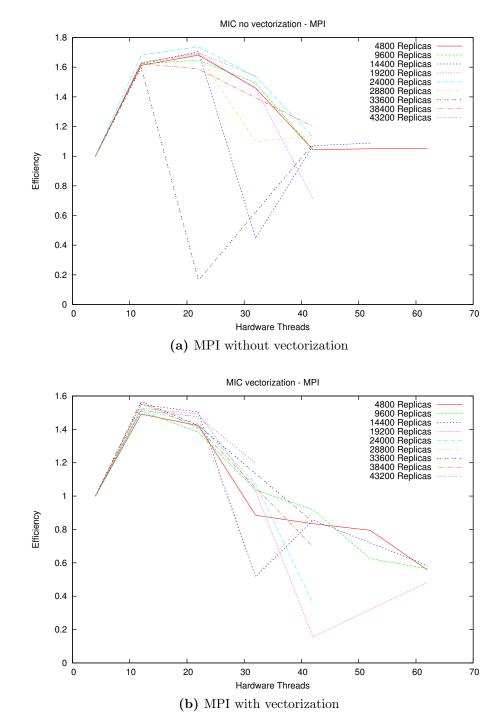

| 5.21 | Intel MIC MPI results                                             | 84  |

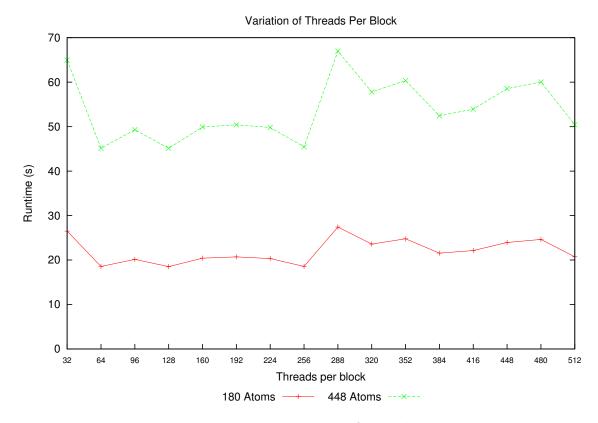

| 5.22 | Varying number of threads per block                               | 86  |

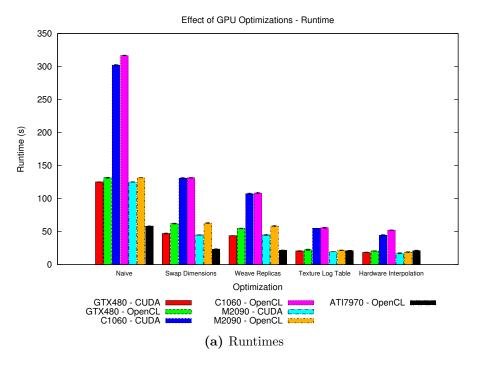

| 5.23 | GPU optimization results over naïve implementation                | 87  |

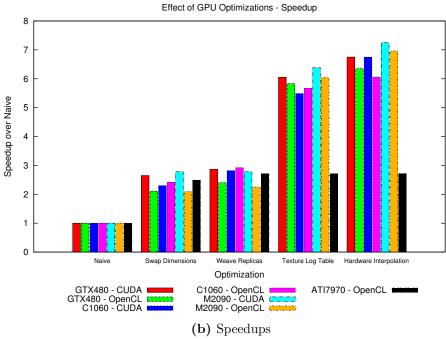

| 5.24 | Tesla C1060 runtimes with varying numbers of replicas             | 89  |

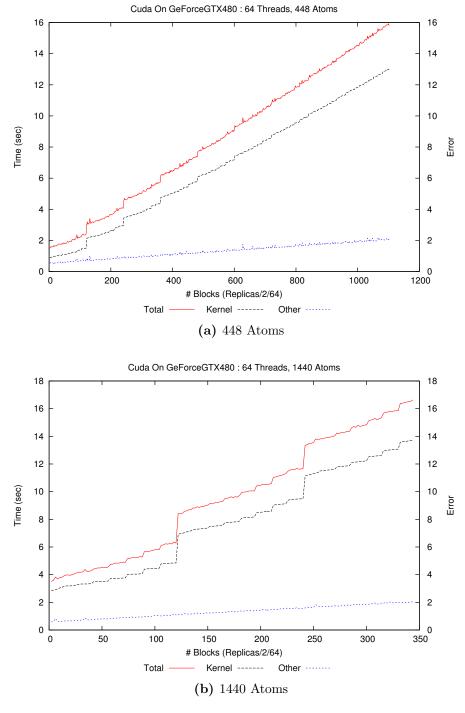

| 5.25 | GeForce GTX 480 runtimes with varying numbers of replicas         | 90  |

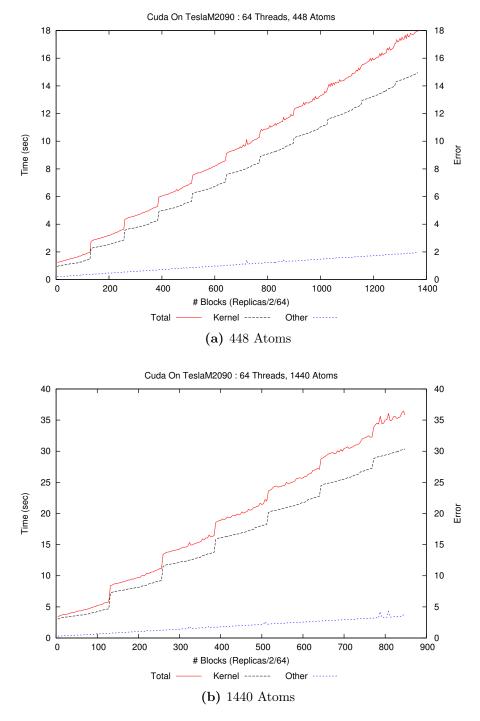

| 5.26 | Tesla M2090 runtimes with varying numbers of replicas             | 91  |

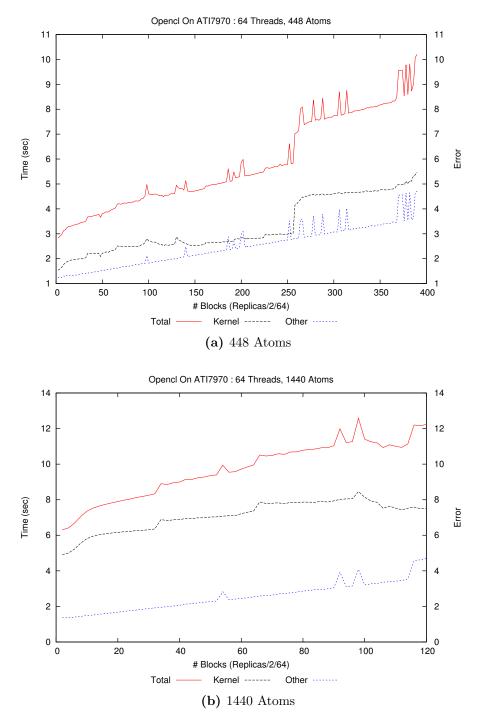

| 5.27 | ATI Radeon 7970 runtimes with varying numbers of replicas         | 92  |

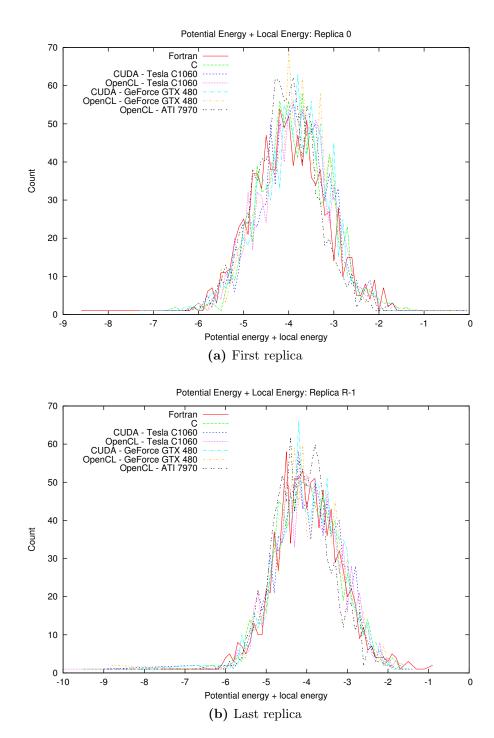

| 5.28 | Check for GPU statistical correctness                             | 94  |

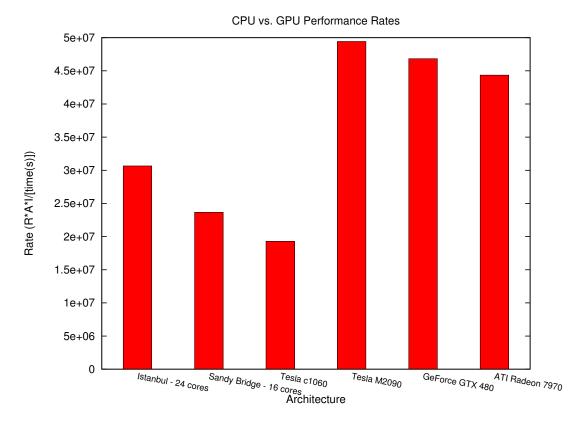

| 5.29 | Performance rates of the CPU and GPU implementations              | 95  |

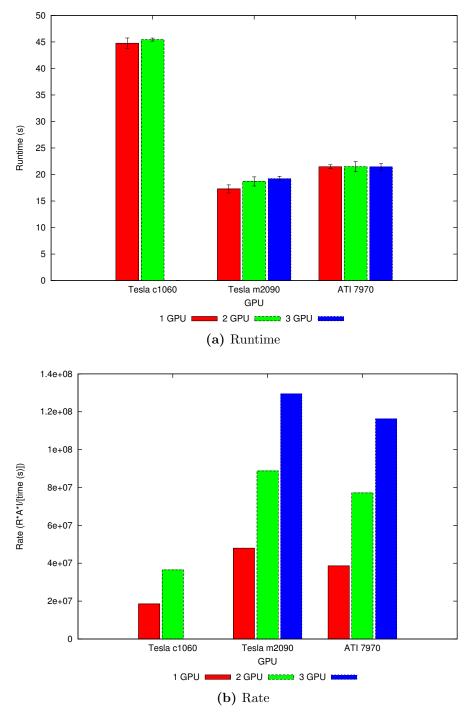

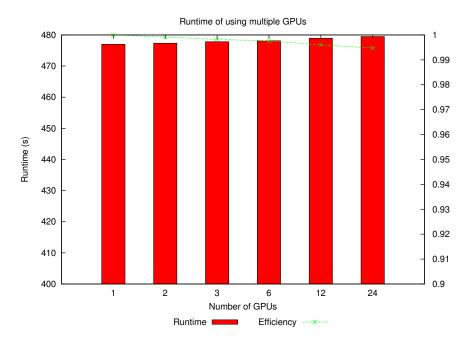

| 5.30 | Results of the multi GPU implementation                           | 96  |

| 5.31 | Multiple GPU runs on Keeneland                                    | 97  |

| 5.32 | Architecture performance per watt and dollar                      | 98  |

| 6.1  | Complexity of the QSATS steps                                     | 105 |

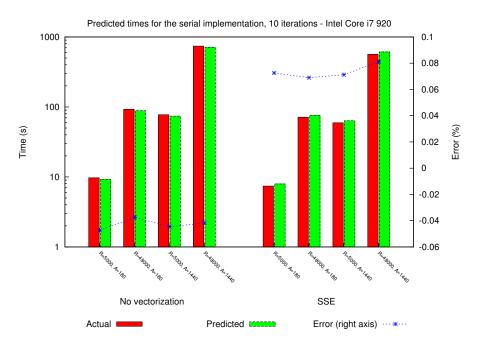

| 6.2  | Serial, single core model accuracy for the Intel Core i7 920                    | 115 |

|------|---------------------------------------------------------------------------------|-----|

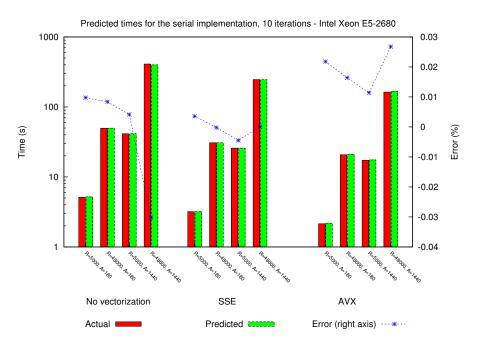

| 6.3  | Serial, single core model accuracy for the Intel E5-2680                        | 116 |

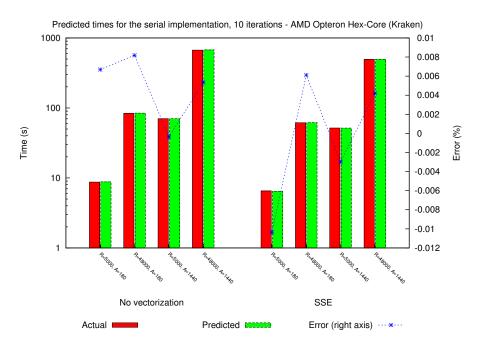

| 6.4  | Serial, single core model accuracy for the AMD Opteron Istanbul $$              | 117 |

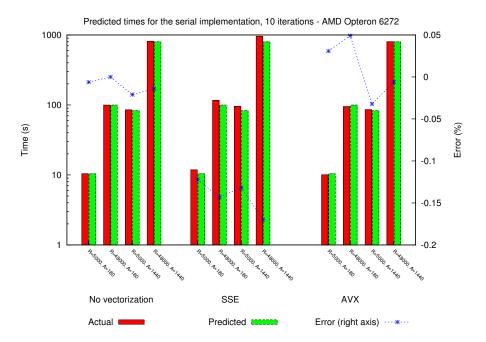

| 6.5  | Serial, single core model accuracy for the AMD Opteron 6272                     | 118 |

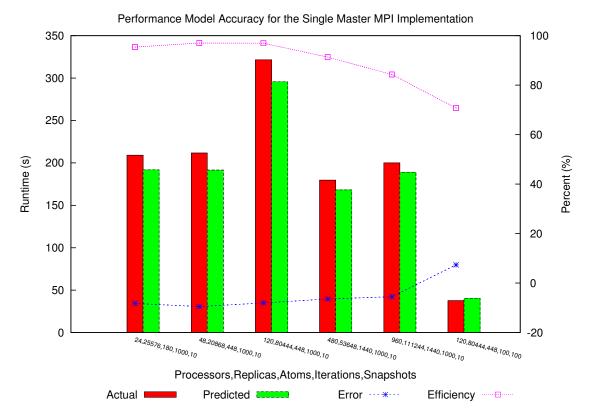

| 6.6  | Model results of the single master implementation                               | 124 |

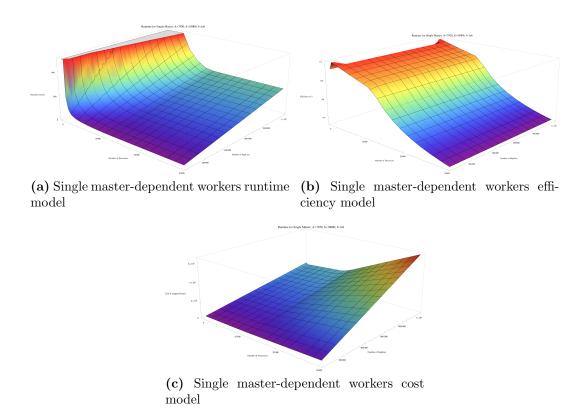

| 6.7  | Single master-dependent workers models                                          | 125 |

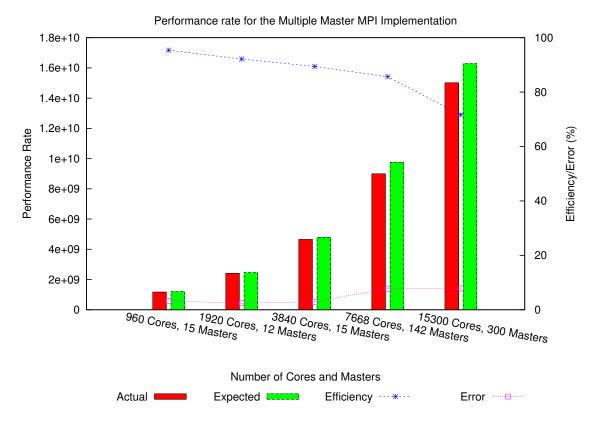

| 6.8  | Accuracy of the multi-master scalability model                                  | 129 |

| 6.9  | Multi master-dependent workers models                                           | 130 |

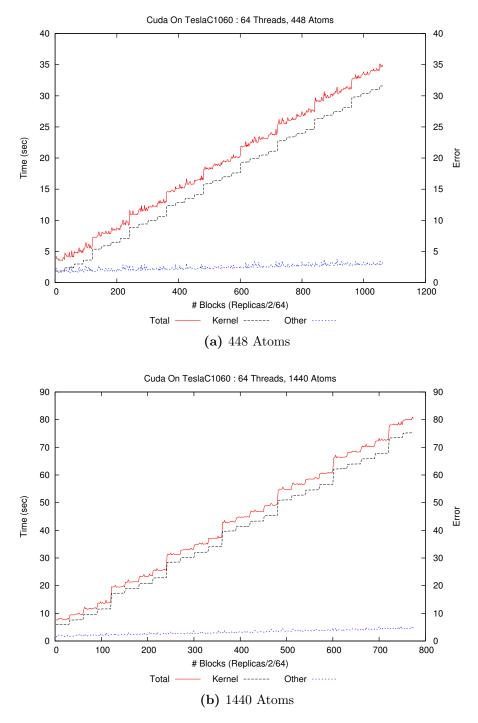

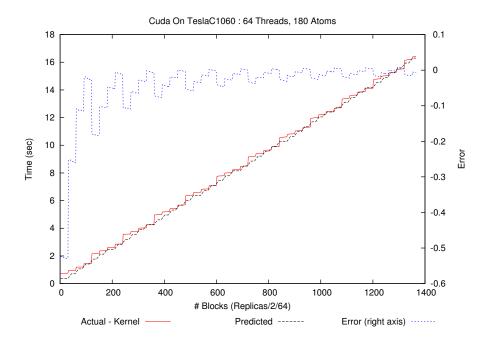

| 6.10 | Model accuracy for the TeslaC1060 GPU - 180 Atoms                               | 136 |

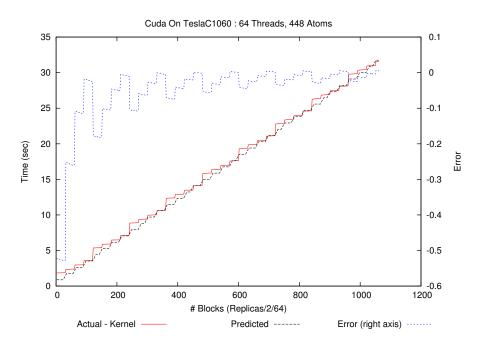

| 6.11 | Model accuracy for the TeslaC1060 GPU - 448 Atoms                               | 137 |

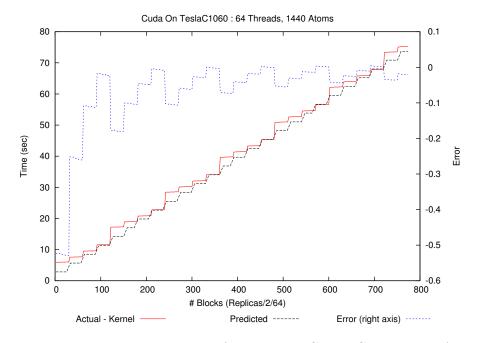

| 6.12 | Model accuracy for the TeslaC1060 GPU - 1440 Atoms                              | 137 |

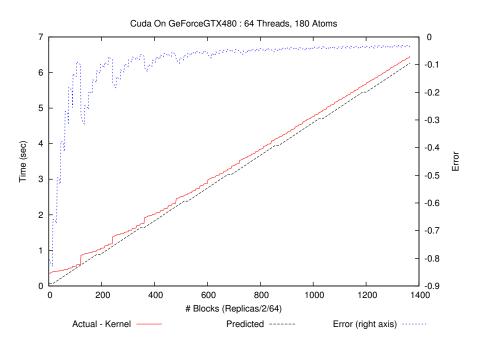

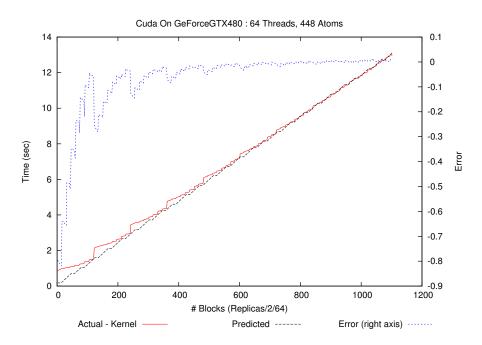

| 6.13 | Model accuracy for the GeForce GTX 480 GPU - 180 Atoms                          | 141 |

| 6.14 | Model accuracy for the GeForce GTX 480 GPU - 448 Atoms                          | 142 |

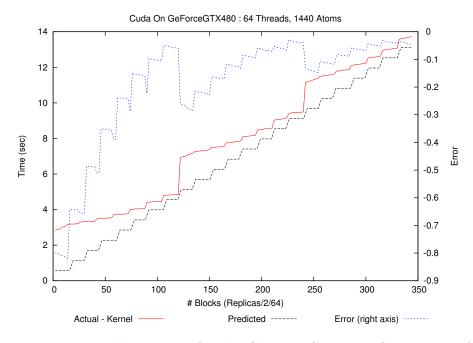

| 6.15 | Model accuracy for the GeForce GTX 480 GPU - 1440 Atoms $\ \ldots \ .$          | 142 |

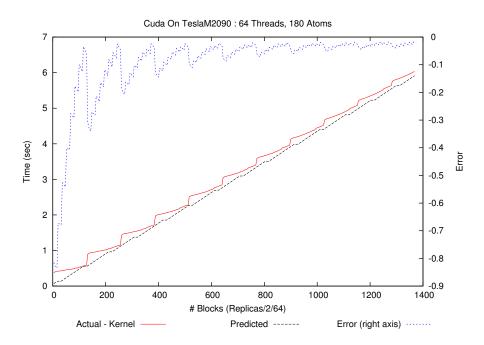

| 6.16 | Model accuracy for the Tesla M2090 GPU - 180 Atoms $\ \ldots \ \ldots \ \ldots$ | 143 |

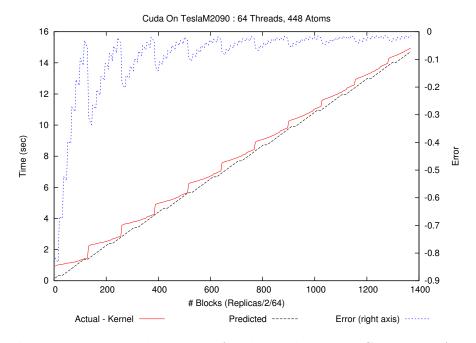

| 6.17 | Model accuracy for the Tesla M2090 GPU - 448 Atoms                              | 143 |

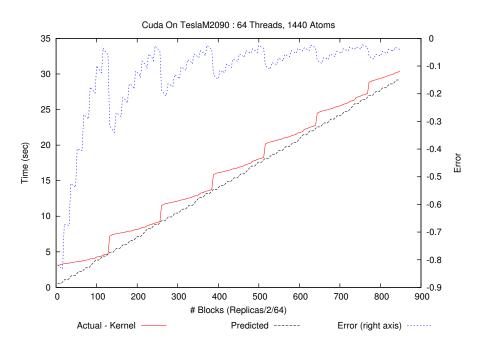

| 6.18 | Model accuracy for the Tesla M2090 GPU - 1440 Atoms                             | 144 |

# Nomenclature

$\alpha$  Time to execute the VPI algorithm per atom per replica per

iteration

$\beta$  Percent of times the potential energy of the outer pairs is calculated

$\Delta \tau$  Time Step

$\rho$  Density

A Number of Atoms

$AMAT_{lookup}$  Average memory access time for a potential energy lookup

$B_{maxwrite}$  Maximum filesystem write bandwidth

$B_{read}$  Filesystem read bandwidth

$B_{send}$  Interprocess communication bandwidth

$B_{write}$  Filesystem write bandwidth

$c_{op}$  Number of cycles to execute operation, op

D Speed of writing a file to disk in bytes per second

I Number of Iterations

L Interprocess communication latency

M Number of MPI Masters and work groups

Number of MPI Processes

$n\_tex\_pts$  Number of points in the texture lookup table

P Number of Interacting Pairs

$P_I$  Number of Inner Interacting Pairs

$P_O$  Number of Outer Interacting Pairs

R Number of Replicas

$R_w$  Number of Replicas Per Worker

S Number of Snapshots

$S_I$  Number of Iterations Between Snapshots =  $\frac{I}{S}$

T Number of Threads

V Number of Doubles in a Vector (i.e. 1-No Vectorization, 2-SSE,

4-AVX, 8-MIC)

W Number of MPI Workers

$W_g$  Number of MPI Workers in a group

$x_{max}$  Maximum log of squared distance held in the texture lookup table

$x_{min}$  Minimum log of squared distance held in the texture lookup table

# Chapter 1

### Introduction

#### 1.1 Motivation

The National Science Foundation describes computational science as a field of study that is "well recognized by the scientific community as a critical enabling discipline underpinning modern research and development in all fields of science, engineering, and medicine." [1] In addition, the NSF has shown major interest in developing new hardware and cyberinfrastructure to help scientists perform computational work.

The increasing amount of computational resources fuels the growth of potential research possibilities in computational science. The development of computational resources and the benefits they bring spur an increased interest in the type of questions that can be answered with computational sciences. These resources enable research to examine areas of science that were previously too difficult or even impossible to explore experimentally. From microprocessors to graphics processing units (GPUs) to Intel Many Integrated Cores (MIC), it is important to decide which architecture is best for the application for high performance.

Historically, high performance computing systems use tightly connected microprocessors through ultra high speed networks (e.g. Jaguar [2] at Oak Ridge National Laboratory). However, within the past decade, heterogeneous computing has become an ever-growing trend in computing. From cell processor workstations and clusters [3, 4] to massively parallel co-processors [5] to GPU enabled supercomputers [6, 7, 8], it is safe to say that heterogeneous computing is more than just a trend. It is a revolution in the computing research field. This is due to the potential for extremely high performance (more than 20 petaflops with the upcoming Titan supercomputer at Oak Ridge National Laboratory [7]) and excellent performance to watt ratios.

#### 1.2 Problem

This dissertation explores the use of emerging architectures such as graphics processing units (GPUs) and supercomputers for accelerating computational science applications that use Quantum Monte Carlo methods. Using the power of analytical performance models, this work explores the viability of different architectures for use on this type of problem as well as the scalability of this problem on large computing systems.

In particular, the Quantum Monte Carlo method [9] leads to computational and memory intensive applications depending on various input parameters. However, these applications can be better managed with more advanced computational resources; in fact, it becomes a necessity to exploit these resources. Without these emerging architectures, performing simulations beyond simple toy problems becomes impossible. This is due to the larger number of atoms used, replicas needed, iterations needed, and other physical characteristics of the problem increasing the total amount of work needed to be performed. This work develops analytical performance models to describe the runtime and scalability of an implementation of a variant of a Quantum Monte Carlo application, Variational Path Integral Monte Carlo [10, 11].

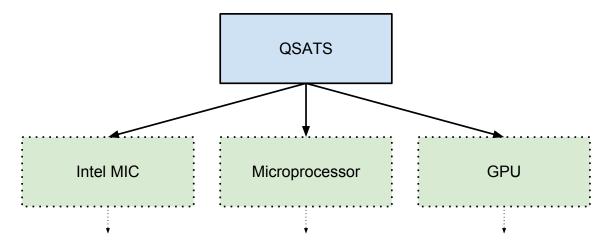

Figure 1.1: Architectures that are explored in this dissertation

#### 1.3 Approach

This dissertation uses the Quantum Monte Carlo simulation method, Variational Path Integral Monte Carlo (named QSATS: Quantum Simulations of Atomic Solids), as a tool to explore the use of the emerging architectures shown in figure 1.1 for computational chemistry applications. This application is based on [12] in that it provides a new MPI implementation to produce a new optimized code. In order to perform this task, this work analyzed and profiled the code to determine bottlenecks and various ways to improve the program. Profiling the code highlighted a number of hot spots in the code that needed to be altered to optimize communications and computations thus increasing performance and scalability of the application. In addition to the MPI implementation, this work also produced a GPU implementation that exploits the highly parallel architecture with fast floating point arithmetic units to produce a code that has significantly higher performance than the microprocessor implementation. The last implementation is for the currently unreleased Intel MIC (many integrated core) using various parallelization techniques (e.g. MPI, threads, vector units).

In addition to the actual implementations, this work also develops analytical performance models that are used to explore different architectures and predict runtime and scalability of the program. This allows for predicting the performance on future architectures that include different processing and networking possibilities. This also allows for the ability to compare architectures and tradeoffs for using each.

#### 1.4 Contribution

This dissertation has the following contributions to the computer engineering and computational science fields:

- This work develops a highly scalable MPI implementation of a Quantum Monte Carlo method, Variational Path Integral Monte Carlo (VPI), that scales to hundreds of cores with greater than 90% efficiency.

- This work develops a high-performance graphics processing unit implementation of VPI, providing a significant improvement over other architectures and previous implementations.

- A packaged code that is ready for release and easy deployment by other users is developed for this VPI implementation.

- This work is the first to develop performance models for VPI in regards to scalability and runtime on supercomputers and graphics processing units.

#### 1.5 Outline

The rest of this dissertation is as follows:

Chapter 2 provides an overview of the VPI method. It also supplies a survey of work implementing applications onto emerging architectures in the computational science realm. Finally, it provides a survey of performance modeling techniques and research.

Chapter 3 describes the microprocessor and Intel MIC implementations.

Chapter 4 details the graphics processing unit implementation and the optimization steps that this work has taken to produce a near optimal design.

Chapter 5 presents an analysis and comparison of the microprocessor, Intel MIC, and GPU implementations.

Chapter 6 presents the performance models developed for the implementations. This chapter will describe in depth how these models were obtained and their significance to this work.

Chapter 7 concludes this dissertation describing remarks about this work and future work.

# Chapter 2

# Background and Related Work

This chapter gives an overview of a type of simulation that is commonly used in computational chemistry: Quantum Monte Carlo. The Quantum Monte Carlo simulation method is used extensively in this work as a tool to explore the use of various emerging architectures in the realm of computational sciences. This chapter will also delve into the emerging architectures themselves and their programming and development environments. Also, it will survey related previous work in the areas of computational sciences, computer architectures, and performance modeling.

#### 2.1 Monte Carlo Simulations

In order to find statistical solutions for problems that were intractable to solve analytically or experimentally, Metropolis and Ulam [13] created the Monte Carlo method in 1949. These methods typically generate a Markov chain of configurations (or states) of a physical system, and estimate observable properties by averaging the value of the property over the configurations visited along the Markov chain. As the length of the Markov chain approaches infinity, the estimate will converge to an actual value thus giving a solution to the problem at hand. The transitions from one configuration to the next are calculated with random numbers, causing the need to have high-quality random number generators such as the ones in [14, 15].

There are a number of different types of Monte Carlo methods, but all of them follow this general description. Monte Carlo methods are considered to be one of the 13 "dwarfs" of parallel computing [16, 17] thus showing their importance in the high performance computing realm. Monte Carlo methods are inherently parallel in a number of ways. For instance, when attempting to solve a Monte Carlo problem, it is best to perform many simulations (sometimes called walkers) with independent random number streams. Each of these simulations is independent from the others, thus they are embarrassingly parallel.

#### 2.2 Variational Path Integral Monte Carlo Method

In systems that are composed of small, light atoms, such as helium and neon, quantum mechanical effects are more pronounced due to the atoms' low masses. Sets of atoms form a crystal structure whose quantum-mechanical movements and behaviors are very difficult to predict. The quantum mechanical properties of a many-atom system can, in principle, be determined by solving the Schrödinger equation. The wave function,  $\Psi$ , is used in this equation to describe the quantum state of the particles. The wave function is used to give the probability distribution of the location of the particles by equation 2.1

$$P(x) = \Psi^2 \tag{2.1}$$

where x represents the instantaneous configuration of the many-atom system. This wave function is a function of a large number of variables (3A where A is the number of atoms) making it very difficult to solve the Schrödinger equation analytically for  $\Psi$ . This leads to the need for statistical analysis such as the variational path integral (VPI) method.

The VPI method (also known as path integral ground state, PIGS, Monte Carlo method [11]) is a quantum Monte Carlo simulation method that allows for the computation of the evolution of replicas (individual "copies" of the structure that

have different configurations of atoms) in a polymer chain that move around in a 3A dimensional space [11, 10, 12]. The VPI method projects the system's ground state wave function out of a suitably chosen trial wave function [12]. The VPI method is an alternative method from the diffusion quantum Monte Carlo (DQMC) method. VPI is preferable because DQMC suffers from complications with fluctuating numbers of walkers and walkers with different levels of importance [18]. VPI uses traditional Metropolis [13, 19] Monte Carlo methods. However, unlike typical Monte Carlo applications, VPI does not use walkers but instead uses a large number of replicas. This is to avoid the complications that are present in the DQMC method [18].

The QSATS VPI implementation follows algorithm 2.1. The physical system's configuration is defined by a set of 3-vectors, one for each atom, that specify the displacement of that atom from its crystal lattice site. These vectors are called displacement vectors below. The VPI system's configuration consists of a set of A displacement vectors for each of R different replicas of the physical system. For each iteration, we loop through all the odd replicas then even replicas. It does not matter whether we do evens or odds first so long as we keep alternating them. These are done due to the independence of the two sets of replicas where the odd-numbered replicas are independent of each other but dependent on the even-numbered replicas and vice-versa. For each replica, we have a series of steps.

First, we calculate the displacements for the new, proposed step. For all replicas except the two "end" replicas, this is done by first averaging the j-1 and the j+1 replicas as shown in equation 2.2 where  $s_{k;j}$  is the displacement vector for the  $k^{th}$  atom in the  $j^{th}$  replica. This equation does not hold for the end replicas (replicas with j=1 and j=R). In this case, we set the new displacement vector to  $(j\pm 1)^{th}$  for the first and last replicas respectively. Once we have these average displacements, we then add a Gaussian displacement to each component of the vector to randomize the step. The Gaussian displacement is related to a finite-time approximation to the quantum mechanical kinetic energy operator for free particles and follows with the central limit theorem. We use the Box-Muller transformation [20] to generate these

#### Algorithm 2.1 QSATS algorithm

```

Store the initial configuration, C

I := number of iterations

R := set of replicas

A := number of atoms

for i \in I do

for j \in odd R then j \in even R do

for k \in A do

Compute the displacement for the new state

Calculate the potential energy, dv, for moving to the new state

if dv < 0 or e^{-dv} > URN then

Accept move

else

Reject move

end if

end for

end for

end for

```

Gaussian random numbers.

$$s_{k;j}^* = \frac{1}{2} * (s_{k;j-1} + s_{k;j+1}); \ 1 < j < R$$

(2.2)

$$s_{k:1}^* = s_{k:2} \tag{2.3}$$

$$s_{k:R}^* = s_{k:R-1} \tag{2.4}$$

Second, we calculate the potential energy arising from the interactions between the k-th atom and all of the atoms that are nearby. (The number of nearby atoms is specified by the experiment and model in question, i.e., 56 in the case of this work.) This calculation is performed twice, once for the old position of the k-th atom, and once for the new position of the k-th atom. For the potential energy function, QSATS uses the HFDB-He potential [21] as shown in equation 2.5. The parameters for this calculation are given in table 2.1.

**Table 2.1:** Parameters for the HFDB-He calculations in equation 2.5.

| Parameter  | Value       |

|------------|-------------|

| A          | 1.8443101e5 |

| $\alpha$   | 10.43329537 |

| eta        | -2.27965105 |

| D          | 1.4826      |

| $c_6$      | 1.36745214  |

| $c_8$      | 0.42123807  |

| $c_{10}$   | 0.17473318  |

| $r_m$      | 5.59926     |

| $\epsilon$ | 10.948      |

$$V_{HFDB} = \epsilon \left( A * e^{-\alpha x + \beta x^2} - \left( \frac{c_6}{x^6} + \frac{c_8}{x^8} + \frac{c_{10}}{x^{10}} \right) * \left( \begin{cases} e^{-\left(\frac{D}{x} - 1\right)^2}, & \text{if } x < D \\ 1, & \text{if } x \ge D \end{cases} \right) \right)$$

(2.5)

where

$$x = \frac{r}{r_m} \tag{2.6}$$

Once the potential energies associated with the old and new positions are calculated, we subtract the two to get the difference in potential energies, dv.

Third, we have to decide to accept or reject this move. If the dv is less than or equal to zero, we will accept the move. If dv is greater than zero, we will generate a uniform random number. If this random number is less than the exponential of -dv, we accept the move. More precisely, the move is accepted with a probability of

$$exp(\frac{-\Delta t \Delta V}{\hbar}) \tag{2.7}$$

Otherwise, the algorithm rejects the move and the atom stays in the same place until the next iteration. This whole process is repeated until the specified number of iterations is complete.

Throughout the simulation, the QSATS program takes snapshots of some of the replicas in order to calculate the crystal's ground state energy later with another program.

From a science perspective, being able to execute VPI on a large crystal structure is important for a few reasons. The VPI simulations tell us the total ground state (zero-temperature) energy of the crystal as a function of its density. This information can be used to derive the zero-temperature equation of state for the crystal, which tells us the pressure needed to compress the crystal to a particular density. Both the ground state energy and the equation of state can be compared to experimental results. This will show that the simulations are correct and coincide with the experimental results. If the simulations are deemed worthy enough to be equivalent, they can be used to explore experiments that cannot physically be performed, such as ones that involve extremely high pressures.

For this work, the algorithm only focuses on two-body interactions. However, using three-body interactions is an interesting extension to this code, as it would provide a more detailed and accurate description of the actual interactions among the atoms. In addition, this work only focuses on simulating the <sup>4</sup>He atom structures. However, the VPI method is also applicable to other types of crystals such as solid para-H<sub>2</sub> and solid Ne.

A number of papers have been published on the use of VPI such as [22, 23]; however, none of these look at accelerating the process with emerging architectures. Hinde [12] previously wrote QSATS using Fortran and MPI to work across many compute nodes. Mudhasani [24] and Kakani [25] developed the VPI simulation for the GPU; however, this dissertation provides a different, higher performance approach, which will be explained later.

#### 2.3 Survey of Architectures

This subsection gives an overview of the different types of architectures available for exploration for scientific applications. There are a number of benefits to each architecture as well as downfalls. Each will be described here.

#### 2.3.1 Microprocessors

Traditionally, microprocessors have been the "go-to" architecture for any application, whether it is everyday applications or high performance computing. Due to its history, the microprocessor has a long line of support when it comes to languages, compilers, and users. Microprocessors not only give a high level of support for users, but they also have the potential to provide architectures for high performance computing applications. With vector units such as SSE and AVX that allow for 128 and 256 bit wide units, it is possible to achieve a 4x [26] or 8x [27] speedup in single precision over non-vectorized codes. All of this speedup comes with a minimal power gain [27]. For multicore, single node codes, applications that exploit the shared memory model typically use threads such as pthreads [28] or OpenMP [29]. It is even possible to use portable languages such as OpenCL [30] that can work many different types of microprocessors and GPUs. Libraries such as MPI [31] are available to provide communication capabilities between processes across many nodes. MPI is the most common and accepted way to perform high performance computing on clusters and large supercomputers.

Microprocessors have been a major contender for computational science applications. Chemistry applications such as GAMESS [32] and NWChem [33] have been parallelized using threaded and MPI techniques. Biology applications such as BLAST [34], HMMER [35], and NAMD [36] have been parallelized to thousands of cores. These are just a few examples, but they give a glimpse into the way computational science can take advantage of highly parallel microprocessor systems.

#### 2.3.2 GPUs

Developers traditionally used graphics processing units (GPUs) for 3D graphics rendering for video games. As video gamers began to demand better graphics and high resolutions, GPU developers had to fight to meet demand. This led to the development of many architectural design improvements such as high core counts These highly parallel devices were soon adopted by at lower clock frequencies. developers outside of the gaming industry as they saw the potential to accelerate other applications, specifically scientific computing [37]. Currently, these GPUs support IEEE-compliant single- and double-precision arithmetic, making them acceptable for a variety of computational science codes. The main GPU companies at the time of writing are NVIDIA and AMD/ATI, both of which have their advantages in terms of performance and programmability. NVIDIA developed their proprietary programming language, Compute Unified Device Architecture (CUDA) [38] as an extension to C/C++ that allows for threaded programming on a large set of NVIDIA GPUs. AMD/ATI also had their own language called Brook+ [39]; however, they later decided to put full effort into assisting Khronos in developing an open language to work across many different devices called OpenCL [30].

These languages are centered around a Single Program, Multiple Data (SPMD) programming model. In particular, CUDA has a model that consists of a computation grid that has a set of blocks (maximum of 65535 at the time of writing), each containing a set of threads (maximum of 512 or 1024 depending on the device)[38]. These blocks get assigned to the stream multiprocessors where each thread works in a Single Instruction, Multiple Thread (SIMT) fashion where multiple threads execute the same instruction at the same time. The traditional CUDA model requires explicit data transfers from the host to the device using the runtime library. However, with newer architectures, CUDA allows for a unified address space so that data does not need to be explicitly copied to the device [38].

Developers have ported a large number of applications to the GPU ranging from computational biology [40, 41, 42, 43], chemistry [33, 44, 45], and mathematics [46, 47, 48] to even everyday applications such as Matlab and Mathematica [49]. In addition, researchers have built large machines that depend on GPUs to run these types of applications [6, 50].

#### 2.3.3 Intel MIC

In the near future, Intel will release their many integrated core (MIC) architecture, a new form of general-purpose processor. Built off the 22nm manufacturing process, the MIC will scale to more than 50 cores [5]. This next generation of co-processors is able to achieve more than one teraflop of performance while computing a DGEMM (double precision general matrix multiplication) as demonstrated at Supercomputing 2011 in Seattle, WA[51]. Intel also announced that the MIC architecture will have a 512 bit wide vector unit that will help exploit parallelism even more [52]. The lack of information in this section is due to the nondisclosure agreement that surrounds my interaction with the product. All information is freely available by doing a simple search online [53, 52].

There have been a few applications that have been developed for the Intel MIC such as a protein folding application, molecular dynamics, SGEMM, and LU factorization [54]. Also, at the Supercomputing 2011 Oak Ridge National Lab booth, other MIC applications were presented such as NWChem, Enzo, and some computational fluid dynamics codes.

#### 2.4 Performance Modeling

Researchers use performance modeling for a number of reasons. One reason is to determine how to best map the application to a set of resources. Hu and Gordon [55] describe three different modeling techniques: measurement, simulation, and analytical

modeling. Measurement is the obtaining of the performance on the machine in question by doing many measurements. The machine must be present in order to perform this type of modeling; however, it can be simple to do. Hu and Gordon also note that this cannot be used for performance prediction or applied to other systems. Due to background noise and other possible hindrances, the output parameters must be chosen carefully and gathered using statistical methods in order to draw meaningful conclusions [56]. Measurements can be expensive and have large workloads.

Simulation, on the other hand, allows one to have a computerized model of the desired system that mimics the behavior and functionality. Because it is a computerized model, it does not depend on the system to be available for testing thus simulations methods are capable of simulating any system possible, giving generality and flexibility [56]. However, for large complex designs, simulating an application may not be reasonable as simulations can take a long time to complete. Simulations are common when designing an FPGA circuit. Making simulation models more difficult is the need for validation that the simulation is correct. The simulation only includes the factors and effects that are included in the simulator. As with measurement modeling, there also needs to be a set of representative tests that show the full behavior of the model.

Finally, analytical models allow for a mathematical model to describe the performance of the application without simulations or access to the desired machine. The power of analytical models comes at the price of being difficult to develop or solve when trying to incorporate a large amount of detail. Smith [57] details a few advantages to analytical models:

- Insight into the inner workings of the system

- Accurate results even for basic models

- Better predictive value from results

- Ability to use differentiation to optimize various aspects of the application

There have been many examples that have used performance models to describe their application performance. Peterson [58] used performance modeling for implementations of synchronous-iterative algorithms, a type of fork-join algorithm, which includes application and background load imbalance. Smith and Peterson [59] extended this work to use this model to determine a way to best distribute a parallel application to a set of resources using FPGAs in a near optimal way. Hong and Kim [60] use analytical models to describe the deep inner workings of a GPU all the way down to the register level. This work shed light on the underlying architecture of the GPU so that developers can better understand how to tune their codes; however, this does not account for newer GPU architectures that contain global memory caching. Sim et al. [61] does consider the cache parameters and discuss their tools to extract various parameters of a CUDA program. However, at the time of writing, their static analysis and instruction analyzer tools are not available to the public so this modeling technique is not used in this dissertation. Volkov and Demmel [46] performed measurement based modeling to tune a high performance DGEMM for GPUs. Gothandaraman [62] used performance models to describe her implementations of her Quantum Monte Carlo application on FPGAs, microprocessors, and GPUs. Ipek et al. [63] explored the use of neural networks on a set of input program and platform input parameters to develop a model that described the performance of their application. Baghsorkhi et al. [64] discussed the development of memory hierarchy models using stochastic Monte Carlo techniques.

#### 2.5 Architectures for Monte Carlo

Due to a wide variety of methods and applications, Monte Carlo (MC) methods have been implemented in numerous ways on various architectures. Researchers have extensively implemented MC methods onto microprocessor machines, clusters, and supercomputers. Abdikamalov et al. [65] explores modeling neutrino transport in core-collapse supernova in an astrophysics MC application on a computer cluster using

thousands of cores using OpenMP and MPI. Moral et al. [66] uses microprocessors to perform MC simulations for approximate Bayesian computations. Jenkins and Peterson [41] use tens of microprocessors using MPI to implement Gillespie's algorithm, a Monte Carlo method to simulate the time evolution of chemically reacting species [67]. CASINO is a Quantum Monte Carlo simulation software package that uses MPI to obtain parallelism on parallel machines [68]. Most related to this dissertation, Hinde [12] used tens of processors to implement the Variational Path Integral Quantum MC method to simulate the atom interactions in a helium crystal structure.

Monte Carlo methods are not restricted to microprocessor implementations. Many researchers have explored the use of graphics processing units due to their highly parallel capabilities and the embarrassingly parallel nature of Monte Carlo methods. Li and Petzold [69] and Jenkins and Peterson [41, 70, 71] implemented Gillespie's method on CUDA-enabled GPUs achieving significant speedups. Heymann and Siebenmorgen [72] use GPUs to perform MC simulations of dust radiative transfer applied to active galactic nuclei in a computational astrophysics application. Anderson et al. [73] provide a GPU implementation of QMcBeaver to perform Quantum Monte Carlo implementations. Gothandaraman [62] uses FPGAs and CUDA-enabled NVIDIA GPUs for Quantum MC simulations. Related to this dissertation, Mudhasani [24] and Kakani [25] developed the VPI simulation for the GPU with moderate performance gains. This dissertation uses a different, high performance approach that will be discussed later.

Implementations of Monte Carlo applications are also available for reconfigurable computing architectures (not explored in this dissertation). Reconfigurable architectures (such as field programmable gate arrays [FPGAs]) have been used for radiative heat transfer [74], pricing derivatives of interest rate models [75], mixed precision studies of MC methods [76], and Quantum MC simulations [45, 62].

This list is by no means exhaustive but is representative of the different architectures that have been used for MC simulations.

#### 2.5.1 Random Number Generation for MC

Since Monte Carlo simulations require a large number of random numbers, statistically high quality random number generators are needed to produce uncorrelated results. There are many random number generators available that provide for high quality numbers. The most notable software package that supplies a variety of random number generators is SPRNG [15]. Random number generators that are provided by the package include a Multiplicative Lagged Fibonacci Generator, Combined Multiple Recursive Generator, Modified Lagged Fibonacci Generator, and 48-bit and 64-bit Linear Congruential Generator. Each of these have varying periods and statistics that are good for different applications making it ideal for MC methods. Previous research provides FPGA and GPU implementations (called HASPRNG [77] and GASPRNG [78]) that are helpful for developing MC applications on accelerators. There are a couple of random number generation algorithms developed for the GPU such as GASPRNG [78] and CURAND [79]. For this work, a custom Combined Multiple Recursive Generator [14] is used due to its customizability and ease of use.

# Chapter 3

# Microprocessors and Intel MIC

This chapter provides an overview of the microprocessor and Intel MIC implementations of the Variational Path Integral Quantum Monte Carlo method, including the serial, threaded, and MPI implementations for both architectures. This work uses this algorithm to simulate the movement and interaction of helium atoms in a crystal structure as described in section 2.2.

# 3.1 Basic Algorithm overview

This implementation follows the algorithm listed in 2.1 for the QSATS VPI implementation. Essentially, there are 6 main steps:

- Initialization (1)

- For each iteration, replica, and atom

- Calculate a Gaussian random displacement (2)

- Calculate potential energy for moving to new state (3)

- Accept or reject the move (4)

- Occasionally, take a snapshot of the current state (5)

- Finalization (6)

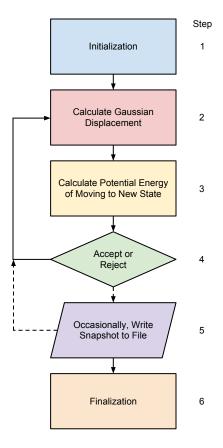

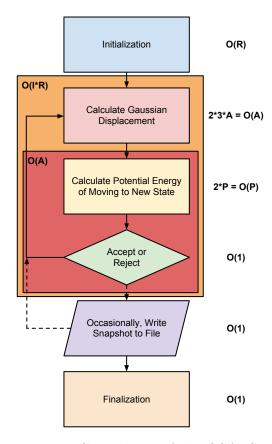

Figure 3.1: General flowchart of the VPI method

These steps can be visualized in figure 3.1 and each step will be referred to throughout this chapter by the color, name, and step number of the box.

As mentioned in 2.2, this implementation seeks to expand and optimize the previous QSATS implementation developed by Hinde [12]. First, a serialized CPU implementation is written to test various algorithmic and memory optimizations. Second, threaded versions using OpenMP and Pthreads is written to compare the performance on a shared memory system. Third, this work developed several MPI implementations to compare the scalability on various systems. For each of these implementations, this work also provides vectorized SSE and AVX codes developed using intrinsics.

Throughout the rest of this dissertation, any references to the implementations will use the term QSATS since this work is a new version of the original. For any

notation not described here, refer to the Nomenclature section on page xiv at the beginning of this dissertation.

### 3.2 Code Overview

This section provides an overview of the code. For more discussions about the background of the algorithm, refer to section 2.2.

### 3.2.1 Step 1: Initialization

The initialization step (the blue box in figure 3.1) first reads in the crystal lattice structure file. This file consists of a total of A+2 lines. The first line specifies the number of atoms in the simulation box, A. This number is here to ensure that the rest of the file is not malformed. The second line gives the lengths of the edges, in Bohr radius units,  $a_0$ , of the simulation box in the x, y, and z directions. QSATS uses this number to scale the coordinates of the lattice sites and the edges of the box to create the crystal in the correct atomic density given at run time. The remaining N lines are the (x, y, z) coordinates of the lattice site positions.

Next, QSATS allocates the the storage space for the displacement vector (variable: path), random number generator vector (variable: rstatv), and the potential energy look-up table (variable: v). The double precision path variable is used to hold the displacements of each atom in each replica from their "ideal" position (i.e., a displacement of 0 means the atom is in its desired position) and is allocated to 3\*A\*R double precision elements (3 for x,y,z coordinates and R to hold the displacements for each replica). At this step, if a save file is specified to continue a previous run, it is read and stored into this variable. Otherwise, path variables are initialized to their ideal position, 0.

The rstatv variable holds the random number generator (RNG) state values for all of the replicas so it is allocated as 8\*R. Each replica has 8 RNG state variables: 6

for the uniform RNG and 2 for the Gaussian RNG. We have to first seed the RNG by inputting values into each of the 6 uniform RNG state variables. For the first replica, all 6 values are set to 12345. For the remaining replicas, the seeds need to be chosen in such a way to avoid overlapping random number streams. To do this, QSATS uses the "jump-ahead" matrices given in [80]. The other two values in the state vector are used for the Gaussian RNG. Since the Box-Muller transformation generates two Gaussian random numbers at a time, one is returned from the function while one is stored in one of the extra spaces in the state vector. The last free spot in the state vector is a flag stating whether to use the stored number or not.

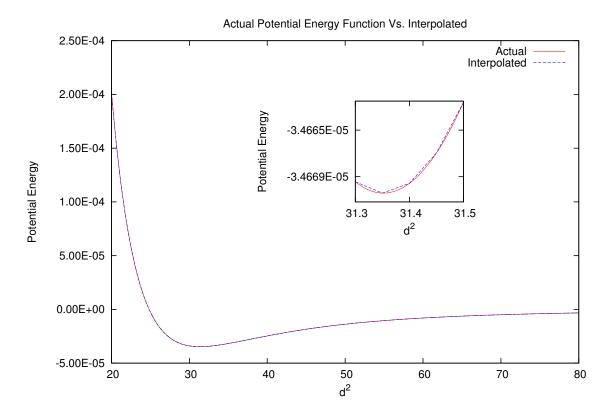

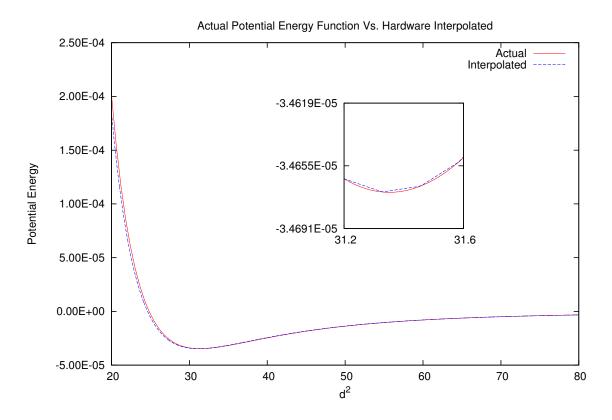

Next, the v vector has 20,000\*2 elements allocated. This vector holds a look-up table for the potential energy function in equation 2.5 for a given distance<sup>2</sup> value. There are a total of 20,000 bins, each containing two values that are used for the linear interpolation of the function. The first value of which is the y-intercept and the second is the slope. Figure 3.2 shows the interpolated table overlaid with the actual computed function. The lookup tables are discussed in more detail in section 3.2.3.

Finally, QSATS generates a list of interacting atoms and their separation vectors for each atom. The list is sorted in order of their ideal separation distances in ascending order. The reason for this will be described later as part of the optimizations in section 3.3.1.

Once the initialization phase is complete, the simulation can begin. This includes the red, yellow, green, and purple boxes (steps 2-5) in figure 3.1.

## 3.2.2 Step 2: Gaussian Displacements

The first step in the simulation is to calculate the displacement that each atom will potentially move (the red box in figure 3.1). For each atom, a, in the replica, r,

Figure 3.2: Actual potential energy function versus interpolated values

QSATS will calculate the average displacement of the neighboring replicas. That is,

$$new\_path(r, a_{\{x,y,z\}}) = \frac{1}{2} * \left( path(r-1, a_{\{x,y,z\}}) + path(r+1, a_{\{x,y,z\}}) \right)$$

(3.1)

For the edge cases where r=0 or r=R-1, the displacement of the atom in the neighboring replica is used (i.e., path(1,  $a_{\{x,y,z\}}$ ) and path(R-2,  $a_{\{x,y,z\}}$ ), respectively).

Next, QSATS adds the Gaussian displacement to each component of averaged move vector to randomize the step. The Gaussian displacement is related to a finite-time approximation to the quantum mechanical kinetic energy operator for free particles and follows with the central limit theorem. To generate the Gaussian random numbers, QSATS uses the Box-Muller transformation [20].

Calculating the average and Gaussian displacements is an  $\mathcal{O}(2*3*A) = \mathcal{O}(A)$  operation. It is possible to do both steps in one pass, however, the compiler is able to better auto-vectorize the average and Gaussian generation calculations when the loops are separated thus increasing performance. The 3 factor comes from having to perform each operation three times, one for each of the vector components in the x, y, and z directions.

### 3.2.3 Step 3: Potential Energy Calculations

Calculating the difference in potential energy to move the atom is the most time consuming part of the entire program. The potential energy that QSATS is calculating is the difference in potential energy, dv, of the old,  $v_{old}$ , and new,  $v_{new}$ , location, as shown in equation 3.2.

$$dv = v_{old} - v_{new} (3.2)$$

To calculate each of the potential energies, QSATS first calculates the difference between the two locations and all of the atom's closest neighbors. The number of neighbors, P, is a configurable option in the program that is dependent on the experiment at hand. In the case of this dissertation, this number is 56. Equation 3.3 shows the calculation of these squared distance,  $d_{\{old|new\}}^2$ , values, where r is the current replica,  $a_{\{old|new\},\{x,y,z\}}$  is the current atom's old/new x, y, z displacement, and  $a_{i,\{x,y,z\}}$  is the i<sup>th</sup> neighbor's displacement.

$$d_{\{old|new\},i}^{2} = (a_{\{old|new\},x} - a_{i,x})^{2} + (a_{\{old|new\},y} - a_{i,y})^{2} + (a_{\{old|new\},z} - a_{i,z})^{2}$$

$$i \in Neighbors$$

(3.3)

Once all the squared distances are calculated, QSATS uses them to compute the potential energy by doing a table look-up on each one as shown in equations 3.4 and 3.5 and summing them together as in equation 3.6. The bin width is set to .05.

$$lookup(d2) = v[bin * 2] + v[bin * 2 + 1] * d2$$

(3.4)

$$bin = \frac{d2}{bin\_width} \tag{3.5}$$

$$v_{old|new} = \sum_{i=1}^{P} lookup(d_{\{old|new\}i}^2)$$

(3.6)

The difference of potential energies, dv, is now calculated using 3.2. This is where sorting the neighbors in idealized distance order comes into play. Because the calculated squared distances will be roughly sorted in increasing order, accesses to the potential energy table will be within a similar range thus increasing cache reuse.

Calculating the difference in potential energy is  $\mathcal{O}(2P) = \mathcal{O}(P)$ . The 2P represents two passes over the data: one to calculate the squared distances and one to calculate the potential energies. This is to facilitate optimizations that will be discussed later.

## 3.2.4 Step 4: Accept or Reject a Move

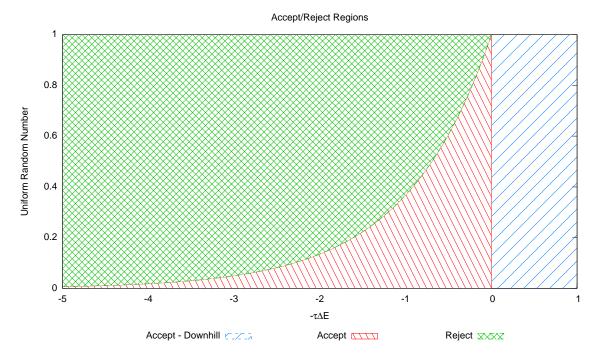

Now that the difference in potential energy of the old and new positions is calculated, it is time to decide whether to accept or reject the move. This is done based on the graph shown in figure 3.3.

The first check QSATS does is to see if the new location is an "uphill" move. This means if dv is less than or equal to zero, we will accept the move. If dv is greater than zero, we sample a uniform random number. If the exponential of -dv is greater than the uniform random number, then we again accept the move. In other words, the move is accepted with a probability of

$$exp(\frac{-\Delta t \Delta V}{\hbar}) \tag{3.7}$$

Figure 3.3: Accept/reject regions

Otherwise, the move is rejected and the atom remains in the same location.

Sections 3.2.3 through 3.2.4 are repeated A times and sections 3.2.2 through 3.2.4 are repeated R\*I times. That is, each atom in each replica attempts to move for the entirety of the simulation (i.e., I iterations).

## 3.2.5 Step 5: Snapshotting

Every  $S_I$  iterations, QSATS will take a snapshot of the states of every  $11^{th}$  replica and write all the atom coordinates to a file. These snapshots are used later by an auxiliary program to analyze the crystal's ground state energy.

## 3.2.6 Step 6: Finalization

Lastly, QSATS will write a file that saves the last displacement state and RNG state information of all of the replicas in the simulation. This gives the user the ability to continue a run from the current state instead of starting from the idealized positions.

Once the save file is written, all allocated memory is freed including the displacement, RNG states, and potential energy lookup table.

## 3.3 Microprocessor Implementation

#### 3.3.1 Serial

Before attacking the parallel implementations, the first step is to implement the algorithm serially to ensure correctness of the algorithm and explore different core level optimizations. The original QSATS code was written in Fortran, so it was converted to C for ease of implementing SSE and AVX versions (discussed in section 3.3.2).

The serial implementation goes as follows. For each of the odd numbered replicas, potential new atom locations are calculated. All of the odd replicas are independent of each other, but rely on the even replicas to aid in the calculation of the displacement. This repeats over all the even replicas. As with the odd replicas, the even replicas are also independent of each other but are dependent on the odd replicas. If it is the  $S_I^{th}$  iteration, a snapshot is written to a file. This is repeated for I iterations serially making this an  $\mathcal{O}(I*R*(2*A+A*2*P)) = \mathcal{O}(I*R*A*(1+P))$  algorithm. Before moving on to parallelizing the program, the serial version must be optimized.

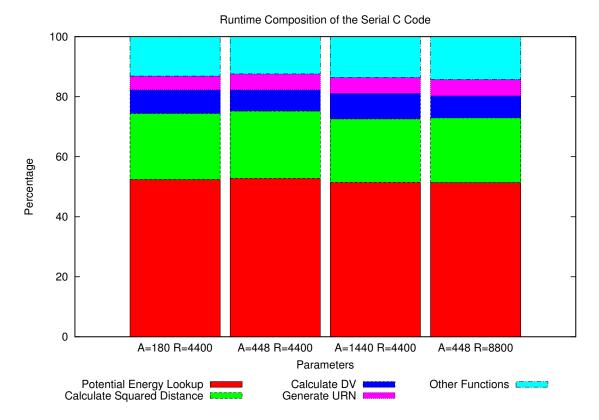

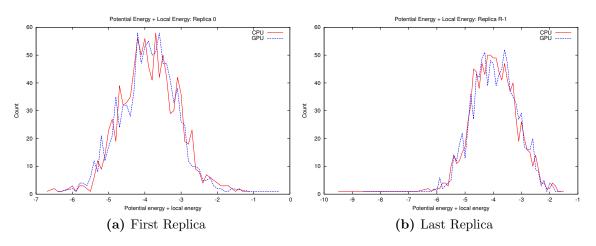

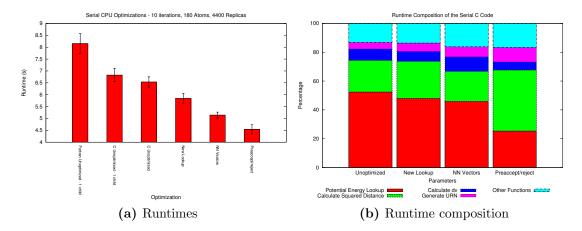

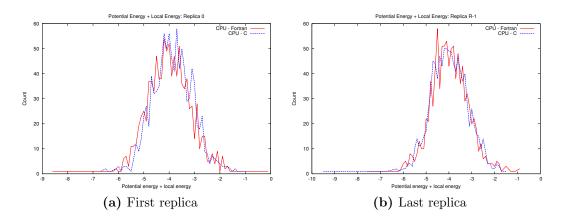

Figure 3.4 shows the breakdown of function contributions to the overall runtime of the unoptimized C code for a variety of parameters as obtained from gprof. From here, we can see that the most expensive portions of the code come from looking up the potential energy and calculating the squared distances. These are prime areas for performance improvements since the majority of the runtime is consumed in these portions.

Figure 3.4: Runtime composition of serial C code

#### Optimization: Potential Energy Lookup

From the profiling, it is obvious that the most time consuming portion of the code is looking up the potential energy. For each squared distance, there are a total of seven double precision operations and 2 memory accesses, as shown in equations 3.8 and 3.9.

$$lookup_{original}(d2) = v[bin * 2] + v[bin * 2 + 1] * (d2 - d2min - .05 * bin)$$

(3.8)

$$bin = (d2 - d2min) * 20 (3.9)$$

The potential energy lookup table, v, is set up using the code snippet in 3.5a. We can simplify the table lookup calculations using the changes in the code snippet

```

/* Hartree to kelvin conversion factor */

/* Hartree to kelvin conversion factor */

const double hart = 315774.65;

const double hart = 315774.65;

d2min = 9.0;

d2min = 0.0;

bin = .05;

bin = .05:

binvrs = 1.0/bin;

binvrs = 1.0/bin;

for(uint32_t i=0; i<NVBINS; i++)</pre>

for(uint32_t i=0; i<NVBINS; i++)</pre>

double d2 = (i) * (bin) + (d2min);

double d2 = (i) * (bin) + (d2min);

v[i * 2] = hfdbhe(d2);

v[i * 2] = hfdbhe(d2);

for(uint32_t i=0; i<NVBINS-1; i++)

for(uint32_t i=0; i<NVBINS-1; i++)</pre>

v[i * 2 + 1] = (v[(i + 1) * 2] - v[i * 2]) / (bin);

v[i * 2 + 1] = (v[(i + 1) * 2] - v[i * 2]) / (bin);

for(uint32_t i=0; i<NVBINS; i++)</pre>

double d2 = d2min + (double)(i)*bin;

v[i * 2] = (v[i*2 + 1] * d2);

(a) Original lookup table

(b) Improved lookup table

```

Figure 3.5: Code snippets of the potential energy lookup table initialization

in figure 3.5b. With this reordering, the table can be accessed using equation 3.4, reducing the overall number of floating point operations to 3 per lookup (more than 50%).

#### Optimization: Neighbor Localization

One optimization is to maintain an array of vector distances of the ideal crystal sorted in order of increasing distance. This allows for better caching for the potential energy lookup table because if the atoms stay within the relative same area, they should have similar distances with their neighbors. Since the R2 values are calculated in a roughly sorted order, access to the lookup table should be within the same proximity of memory locations, thus allowing for potentially better performance by decreasing the number of L1 cache misses.

#### Optimization: Potential Energy Lookup Reduction

Profiling the code indicates that the potential energy lookups and squared distance calculations are the most time consuming portions of the code: requiring approximately 70% of the runtime. It is logical to examine that code section to see how the performance can be improved. First, the most computationally expensive portion of this step is the calculation of the squared distances in equation 3.3. All of these distances need to be calculated for further steps such as the potential energy calculations. The neighboring atoms are not guaranteed to be in consecutive memory (e.g., atom 1 may interact with atoms 1, 3, 4, 12, ... and not 1, 2, 3, 4, ...) so the loop is not vectorizable by the compiler nor is it advantageous to do vectorization by hand due to the large number of serial loads from memory. This is evidence of the inability for complete vectorization.

At first glance, it appears that we are already optimizing the lookup the best way possible despite having sparse lookups. The lookup table is  $20000*2*8/1024 \approx 312 \text{KB}$  meaning most can fit into a 256KB L2 cache. However, the squared distances mostly within a limited range (e.g., not many lookups are within a distance of  $120~a_0^2$  for the density of interest) so the most commonly used distances are stored in L1 so we are getting decent cache behaviors. As alluded to previously, if the density is increased or decreased, the squared distances vary more, causing caching performance to be worse. We are also providing similar lookups to the table by keeping the atoms in sorted order by their ideal position distances so we that we can increase cache efficiency as much as possible. In addition, the lookups cannot be vectorized either due to the lack of guarantee that consecutively computed squared distances result in consecutive memory lookups.

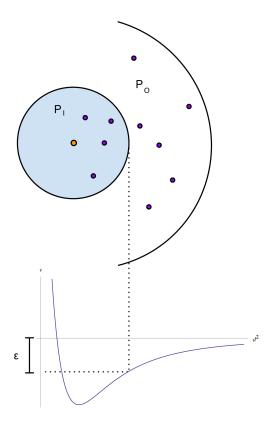

However, can the number of lookups be reduced? If the number of lookups can be reduced, we can save clock cycles since the table is larger than L1 and L2 caches on some systems. Looking at the behavior of the system, we can see that for each atom, there is a subset of interacting atoms that are, in the ideal case, the closest to the

Figure 3.6: Diagram of the inner and outer regions of neighbors

atom at hand,  $P_I$ . Likewise, there is a subset that are farther away from the atom at hand,  $P_O = P - P_I$ . This is shown in figure 3.6.

The  $P_I$  closest atoms have the highest contribution to the potential energy of the interacting pairs while  $P_O$  has the lowest. The potential energy can be split up into the sum of the potential energies as shown in equation 3.10

$$dv = \sum_{i=1}^{P} (v(d_{old,i}^{2}) - v(d_{new,i}^{2}))$$

$$= \sum_{i=1}^{P_{I}} (v(d_{old,i}^{2}) - v(d_{new,i}^{2}))$$

$$+ \sum_{i=P_{I}+1}^{P} (v(d_{old,i}^{2}) - v(d_{new,i}^{2}))$$

$$= dv_{P_{I}} + dv_{P_{O}}$$

(3.10)

Typically, a move is accepted as described section 3.2.4 and shown in equation 3.11 where URN is a uniform random number. Plugging 3.10 into 3.11 and moving terms around, the acceptance can be put in terms of  $dv_{PO}$  as shown in 3.12.

$$URN < e^{(dv*\Delta\tau)} \tag{3.11}$$

$$ln(URN) - dv_{P_I} * \Delta\tau < dv_{P_O} * \Delta\tau \tag{3.12}$$

Since the closest neighbor in the set of  $P_O$  outer neighbors,  $d_0^2 = min(d^2 \in P_O)$ , will have an energy of  $v(d_0^2) = \epsilon$  (as seen in figure 3.6), all of the remaining neighbors, if in the monotonically increasing section of the potential energy curve, must be within the range shown in equation 3.13

$$\epsilon <= v(r_i) < 0 \qquad \forall i \in P_0 \tag{3.13}$$

Each difference in potential energy for the new and old positions for the outer neighbors will be within this range. This means the summation of these energies is also within this range. That is,

$$dv_{P_O} = \sum_{i \in P_O} dv_{P_{O,i}} \le P_O * \epsilon \tag{3.14}$$

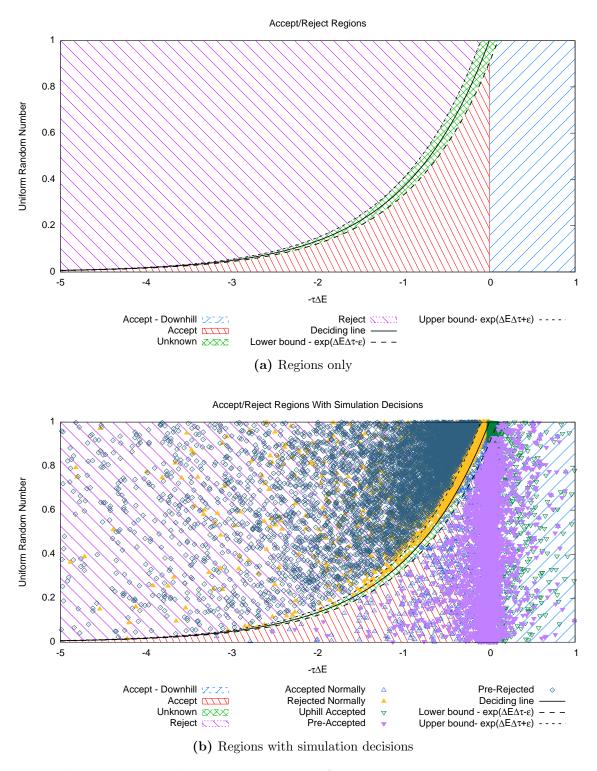

Now that we have this upper bound, how can we use this to reduce the computation time? If the closest outer interacting pair has a potential energy that is within the monotonically increasing portion of the potential energy curve, it is possible to decide if the remaining outer interacting pairs could have enough contribution to sway the acceptance or rejection decision. This can be done using equation 3.15 as visualized in figure 3.7a. The purple, red, and blue regions are ones that can be decided without having to calculate all of the energies based on the upper bound on the contribution from these energies. The green region indicates that the outer interacting pairs could have enough contribution to affect the acceptance or rejection

decision.

accept if:

$$ln(URN) - dv_{N_O} * \Delta \tau < N_I * \Delta \tau * |\epsilon|$$

reject if:  $ln(URN) + dv_{N_O} * \Delta \tau > N_I * \Delta \tau * |\epsilon|$  (3.15)

else, calculate rest of energies and accept/reject normally

How does this affect performance? This is dependent on the density of the crystal, the number of inner pairs, and the  $\Delta\tau$  time step that are used. If the crystal's density is high, meaning the atoms are closer together, there will be less moves that can be predetermined using this method due to the  $P_O$  neighbors having more potential energy contribution. If the density is smaller, meaning the atoms are farther apart, more moves can be predetermined. In a test case with a density of  $\rho = 0.004614$  and  $\Delta\tau = 500.0$ , roughly 97%-98% of the moves can be predetermined resulting in a 15% decrease in overall runtime. While this seems small, this is still a significant speedup when considering that the runtime of a full run is on the order of hours or days for big crystals and large numbers of replicas. This will be discussed in section 5.1.1. Figure 3.7b shows the accepted and rejected points that were both predetermined and calculated normally for a subset of a run on 1440 atoms with  $\rho = 0.004614$ , P = 56, and  $P_I = 18$ .

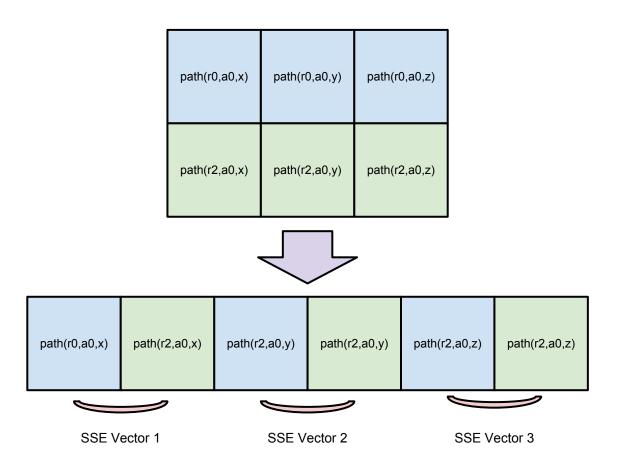

#### 3.3.2 Parallel - Vectorization

The computations done by QSATS on a single replica cannot easily be vectorized beyond what the compiler already takes care of because of sparse accesses to memory throughout the program. However, it is possible to vectorize across replicas, that is, execute multiple replica movements simultaneously. This is possible because all of the odd replicas are independent from each other and all the even replicas are independent. In this way, we can pack replica information into memory for easy recovery to reduce the amount of loads from memory. Refer to figure 3.8 to see how the memory is packed for an SSE vector. For SSE, two replicas are packed together

Figure 3.7: Predetermination regions for accepting or rejecting a move

Figure 3.8: Memory packing for SSE vectorization

since SSE vectors can hold 128 bits (i.e., 2 doubles). For AVX, four replicas are packed together since AVX vectors can hold 256 bits (i.e., 4 doubles).

The information for two replicas are interleaved and packed together so that any operation on, for example, the x coordinate of atom 0 in replica 0 will also be on the same atom in replica 2. This allows for random number generation (both uniform and Gaussian), squared distance calculation, and accept reject determinations to be performed in parallel. As mentioned in section 3.3.1, the neighbor information lookup cannot be vectorized due to the fact that atoms in different replicas might be looking at interaction neighbors that are consecutive in memory so this information must be serialized. Once this information is loaded from memory, the rest of the calculations can be vectorized. Also, since the replicas most likely have different

squared distance values, it is not possible to vectorize potential energy table lookups. However, once these are serialized and stored into vectors, the difference in potential energy calculations can be performed using vectors.

#### 3.3.3 Parallel - Threads

As mentioned in the previous section, it is possible to parallelize QSATS across even and odd replicas. This is an ideal situation for threaded implementations as there is little synchronization. The only synchronization that is needed is when switching from odd to even or even to odd numbered replicas. The cost of this synchronization is minimal because each thread is working on the same amount of data as the others. Therefore, each thread should complete their work at approximately the same time. Each thread works on R/T replicas thus performing R\*A/T iterations.

There are two libraries that can be used for the threaded implementations: pthreads and OpenMP. First, pthreads were used to implement the threaded version. In the initialization stage, QSATS forks off T threads and sticks them into a thread pool to wait for work to be issued to them. The main thread sends a signal to the threads informing them to wake up and start on their replicas. Each thread starts to work on the (thread id)<sup>th</sup> replica in the set. For example, thread 2 starts trying to move the atoms in replica 3 if the master thread tells the threads to work on the odd replicas and 2 if it is working on the even replicas. Once all of the threads finish moving all the atoms in their set of replicas, they signal to the master thread and go to sleep to wait for more work. At this stage, the master thread waits until it gets a signal from all the threads (synchronization). This process is repeated I times until the simulation is complete. In the case of snapshots, the worker threads continue to sleep while the master thread writes the snapshot file in order to prevent overwriting data needed for the snapshot.

The OpenMP implementation follows along with the same scheme. There is a pool of threads that waits until work is available. These threads are signaled to start

working through the use of a "parallel for". Once all the threads are completed with their work, they synchronize and wait for more work. The benefit of using OpenMP is that there are minimal code changes to achieve the same result.

To extend this threaded implementation one step further, an OpenCL [81] implementation has also been developed. Using OpenCL allows the exploration of code on multiple different architectures such as GPUs and microprocessors. This implementation is described in the GPU chapter so the reader is referred to chapter 4 for in depth details. However, as an overview, the OpenCL implementation for the CPU has a single kernel that performs the QSATS method where each thread executes the algorithm on a single replica. After each kernel call, the threads are synchronized before moving onto the next set of replicas. The benefit of using OpenCL is that the kernel can be compiled with automatic vectorization support without having to change any code. Because microprocessors do not have the texture units that GPUs have, the kernel is slightly altered from the GPU version to use global memory and software linear interpolation. Other than removing texture accesses, the kernel is the same as the GPU kernel code.

#### 3.3.4 Parallel - MPI

At this point, it is time to explore multi-node/process implementations. To do this, this work uses the Message Passing Interface (MPI) [31] to perform inter-node communications. As a first pass, this work uses the parallelization scheme used in [12]. In the original QSATS Fortran code, parallelization is achieved by using a master-worker model where a central process delegates work to a set of "worker" processes. This approach is a flexible parallel programming paradigm in that it is applicable to a wide range of applications and provides acceptable load balancing. In the QSATS application, parallelization is performed using the following approach.

**Note:** For all of the following implementations, vectorized versions are available using the approach described in section 3.3.2.

#### Master-Independent Workers