Doctoral Dissertations Graduate School

12-2012

# A Low-Power, Highly Stabilized Three-Electrode Potentiostat Using Subthreshold Techniques

Melika Roknsharifi mroknsha@utk.edu

#### Recommended Citation

Roknsharifi, Melika, "A Low-Power, Highly Stabilized Three-Electrode Potentiostat Using Subthreshold Techniques." PhD diss., University of Tennessee, 2012.

https://trace.tennessee.edu/utk\_graddiss/1557

This Dissertation is brought to you for free and open access by the Graduate School at Trace: Tennessee Research and Creative Exchange. It has been accepted for inclusion in Doctoral Dissertations by an authorized administrator of Trace: Tennessee Research and Creative Exchange. For more information, please contact trace@utk.edu.

#### To the Graduate Council:

I am submitting herewith a dissertation written by Melika Roknsharifi entitled "A Low-Power, Highly Stabilized Three-Electrode Potentiostat Using Subthreshold Techniques." I have examined the final electronic copy of this dissertation for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Doctor of Philosophy, with a major in Electrical Engineering.

Syed Kamrul Islam, Major Professor

We have read this dissertation and recommend its acceptance:

Benjamin J. Blalock, Jeremy Holleman, Mohamed Mahfouz

Accepted for the Council: Carolyn R. Hodges

Vice Provost and Dean of the Graduate School

(Original signatures are on file with official student records.)

| electronic copy of this dissertation f                       | for form and content and reco | nniques." I have examined the final ommend that it be accepted in partial ilosophy, with a major in Electrical |

|--------------------------------------------------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------|

|                                                              |                               | Syed Kamrul Islam, Major Professor                                                                             |

| We have read this dissertation and recommend its acceptance: |                               |                                                                                                                |

| Benjamin J. Blalock                                          |                               |                                                                                                                |

| Jeremy Holleman                                              |                               |                                                                                                                |

| Mohamed Mahfouz                                              |                               |                                                                                                                |

|                                                              | Accepted for the Council      |                                                                                                                |

|                                                              |                               |                                                                                                                |

I am submitting herewith a dissertation written by Melika Roknsharifi entitled, "A Low-Power, Highly

To the Graduate Council:

Vice Provost and Dean of the Graduate School (Original signatures are on file with official student records.)

Carolyn R. Hodges

# A Low-Power, Highly Stabilized Three-Electrode Potentiostat Using Subthreshold Techniques

A Dissertation Presented for the Doctor of Philosophy

Degree

The University of Tennessee, Knoxville

Melika Roknsharifi December 2012

### **DEDICATION**

I lovingly dedicate this thesis to my husband Ahamdreza Ghahremani and my parents Ghodsi Hamidi and Mehdi Roknsharifi, who supported me each step of the way, and also three of my great professors, Dr. Islam, Dr. Abrishamifar and Dr. Sharif bakhtiar.

I would also like to dedicate this work to all diabetic patients and I hope one day the improvement in science can help them enjoy a happy healthy life.

#### **ACKNOWLEDGMENTS**

It is a pleasure to thank those who made this thesis possible. First of all, I owe my deepest gratitude to my advisor Dr. Syed K. Islam, whose encouragement, guidance and support from the initial to here help me grow personally and professionally.

I also would like to thank my committee members Dr. Benjamin J. Blalock, Dr. Jeremy Holleman and Dr. Mohamed Mahfouz who tremendously helped me to improve the quality of my Ph.D. work and get a better understanding of analog circuit and system design.

I want to thank my parents Ghodsi Hamidi and Mehdi Roknsharifi, my husband Ahmadreza Ghahremani, for their endless support and encouragement during my Ph.D. work. Gratitude is also given to my grandmother Soghra Torabian and my sisters Shima and Mona Roknsharifi for their unconditional love and support.

I would also like to show my gratitude to all of my teachers who helped me in the path of my life to become who I am today. Among them I would like to specially thank Dr. Adib Abrishamifar and Dr. Mehrad Sharif Bakhtiar whom I learned all the basics of circuit design from.

Finally, I would like to thank my wonderful friends and colleagues at The University of Tennessee for their great help and suggestions. They are Dr. Kai Zhu, Emily Bean, Kimberly MacArthur, Dr. Liang Zuo, Fahmida Shaheen Tulip, Shahriar Jahan Pollob, Junjie Lu, Song Yuan, Terence Randall, Dr. Chiahung Su, Dr. Ashraf Bin Islam and Dr. Salwa Mostafa. I also want to thank my old friends from Iran University of Technology and Sharif University of Technology for all of their help and support through the years. They are Kiarash Gharibdoust, Hanieh Khalilian, Maryam Nikpay, Majid Sodagar, Salar Bagherzade Sohrabi, Amin Eftekharian, Milad khoshnegar, Seyed Hossein Seyedmehdi, Omid Talebi Amiri, Nastaran Asadi Zanjani, Farnaz Foroughian, Sahar Ziaee and Farzin Azami.

#### **ABSTRACT**

Implantable micro- and nano- sensors and implantable microdevices (IMDs) have demonstrated potential for monitoring various physiological parameters such as glucose, lactate, CO<sub>2</sub>, pH, etc. Potentiostats are essential components of electrochemical sensors such as glucose monitoring devices for diabetic patients. Diabetes is a metabolic disorder associated with insufficient production or inefficient utilization of insulin. The most important role of this enzyme is to regulate the metabolic breakdown of glucose generating the necessary energy for human activities. Diabetic patients typically monitor their blood glucose levels by pricking a fingertip with a lancing device and applying the blood to a glucose meter. This painful process may need to be repeated once before each meal and once 1- 4 hour after meal. Patients may need to inject insulin manually to keep the blood glucose level at 3.9-6.7 mmol [mili mol] /liter.

Frequent glucose measurement can help reduce the long term complication of this disease which includes kidney disease, nerve damage, heart and blood vessel diseases, gum disease, glaucoma and etc. Having an implanted close loop insulin delivery system can help increase the frequency of glucose measurement and the accuracy of insulin injection. The implanted close loop system consists of three main blocks: (1) an electrochemical sensor in conjunction with a potentiostat to measure the blood glucose level, (2) a control block that defines the level of insulin injection and (3) an implanted insulin pump.

To provide a continuous health-care monitoring the implantable unit has to be powered up using wireless techniques. Minimizing the power consumption associated with the implantable system can improve the battery life times or minimize the power transfer through the human body. The focus of this work is on the design of low-power potentiostats for the implantable glucose monitoring system.

This work addresses the conventional structures in potentiostat design and the problems associated with these designs. Based on this discussion a modification is made to improve the stability without

increasing the complexity of the system. The proposed design adopts a subthreshold biasing scheme for the design of a highly-stabilized, low-power potentiostats.

### **Table of Contents**

| C | HAPTER 1 – Introduction                                                                  | 1  |

|---|------------------------------------------------------------------------------------------|----|

|   | 1.1. Metabolism                                                                          | 1  |

|   | 1.1.1. Regulation and Control                                                            | 2  |

|   | 1.1.2. Metabolic Disorder                                                                | 2  |

|   | 1.2. Diabetes                                                                            | 3  |

|   | 1.2.1. Different Types of Diabetes                                                       | 3  |

|   | 1.2.2. Home Monitoring of Blood Sugar                                                    | 4  |

|   | 1.2.3. Importance of Frequent Glucose Monitoring for Diabetes                            | 5  |

|   | 1.2.4. Using an Implantable System for More Frequent and More Convenient Glucose Measure |    |

|   | 1.2.5. Electrochemical Principle in Glucose Sensing                                      | 8  |

|   | 1.2.6. Measuring Other Blood Factors Using Potentiostat                                  | 9  |

|   | 1.3. Challenges in Designing a Potentiostat for an Implantable Glucose Sensor            | 10 |

|   | 1.3.1. Power Conditioning for Implantable Systems                                        | 10 |

|   | 1.3.2. Low Power Design Techniques                                                       | 11 |

|   | 1.3.3. Design of a Stable Potentiostat                                                   | 13 |

|   | 1.4. Research Goals                                                                      | 14 |

|   | 1.5. Original Contribution                                                               | 15 |

|   | 1.6. Overview of the Dissertation                                                        | 16 |

| C | HAPTER 2 – EKV Model and Subthreshold Design                                             | 17 |

|   | 2.1. EKV Model                                                                           | 17 |

|   | 2.2. Subthreshold Design Considerations                                                  | 25 |

|   | 2.2.1. Mismatch                                                                          | 25 |

|   | 2.2.2. Noise                                                                             | 27 |

|   | 2.2.3. Drain Induced Barrier Lowering (DIBL)                                             | 28 |

|   | 2.2.4. Process-Voltage-Temperature (PVT) Variation                                       | 29 |

|   | 2.3 Subthreshold Design Evamples                                                         | 20 |

| 2.3.1. Amplifier Design for Neural Recording                     | 30 |

|------------------------------------------------------------------|----|

| 2.3.2. Linearization Technique for Subthreshold Amplifiers       | 31 |

| CHAPTER 3 – Literature Review on Potentiostat                    | 36 |

| 3.1. Resistive-Based Potentiostat                                | 37 |

| 3.2. Capacitive-Based Potentiostat                               | 40 |

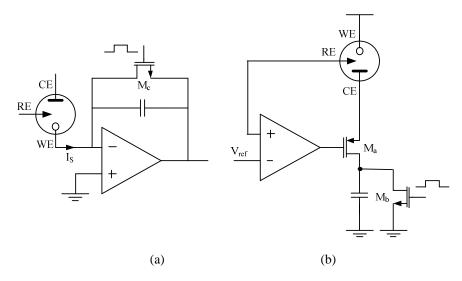

| 3.3. Current Mirror-Based Potentiostat                           | 43 |

| CHAPTER 4 – Proposed Structure                                   | 46 |

| 4.1. Analysis of the Conventional Design                         | 46 |

| 4.2. Proposed Structure                                          | 48 |

| 4.2.1. Stability Analysis using Miller Capacitor                 | 50 |

| 4.2.2. Proposed Opamp for the Proposed Structure                 | 51 |

| 4.3. Design Considerations in the Complete System Structure      | 57 |

| 4.3.1. System Offset                                             | 58 |

| 4.3.2. System Noise                                              | 59 |

| 4.3.3. System Power Supply Rejection Ratio (PSRR)                | 59 |

| CHAPTER 5 – Signal Processing Unit (SPU)                         | 61 |

| 5.1. Introduction                                                | 61 |

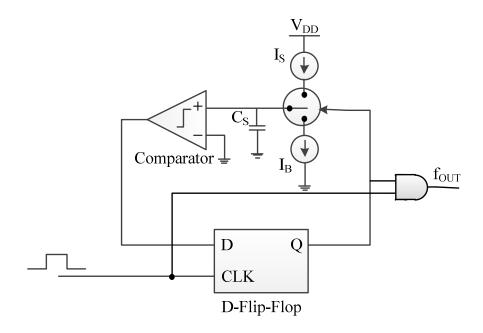

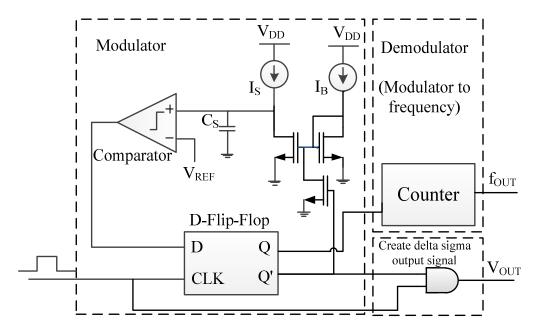

| 5.2. Proposed Structure                                          | 62 |

| 5.3. Demodulation Scheme                                         | 64 |

| CHAPTER 6 – Simulation and Test Results                          | 68 |

| 6.1. Opamp Simulation Result                                     | 68 |

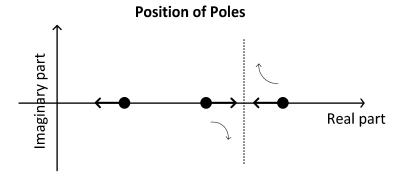

| 6.1.1. Position of Poles and Zeros of the Proposed Opamp         | 68 |

| 6.1.2. Noise Performance of the Proposed Opamp                   | 70 |

| 6.1.3. Common Mode Rejection Ratio (CMRR) of the Proposed Opamp  | 71 |

| 6.1.4. Power Supply Rejection Ratio (PSRR) of the Proposed Opamp | 72 |

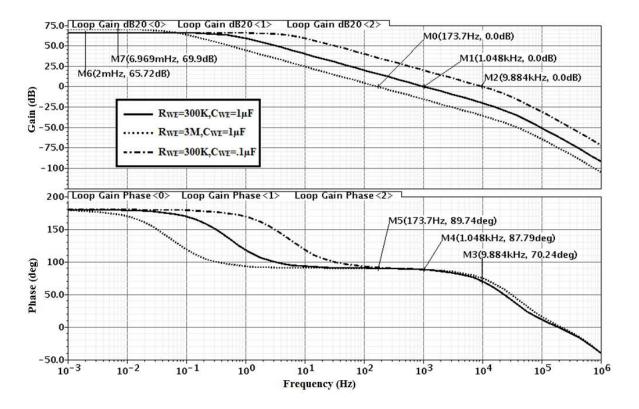

| 6.2. Potentiostat Simulation and Test Result                     | 73 |

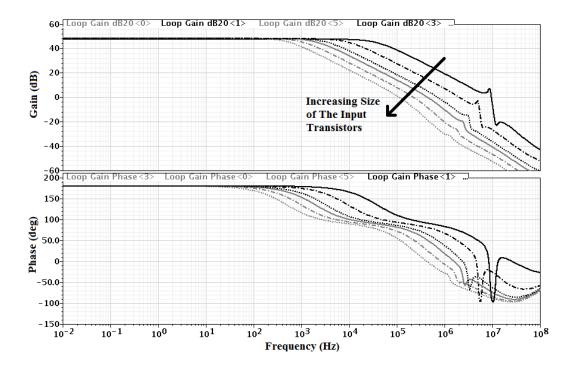

| 6.2.1. Simulation Result for Open Loop Gain and Phase Margin     | 73 |

| 6.2.2. Test Results of the Complete System                       | 75 |

| 6.2.3. Offset Simulation and Test Result                         | 78 |

| 6.2.4. Noise Performance Simulation and Test Result              | 79 |

| 6.3 Simulation and Test Results of the Signal Processing Unit    | 83 |

| CHAPTER 7 – Conclusion and Future Work | 87  |

|----------------------------------------|-----|

| 7.1. Conclusion                        | 87  |

| 7.2. Future Work                       | 89  |

| LIST OF REFERENCES                     | 90  |

| Appendix A                             | 95  |

| Appendix B                             | 97  |

| Appendix C                             | 98  |

| Appendix D                             | 105 |

| VITA                                   | 109 |

### **List OF Tables**

| Table. 2. 1. Drain Current in Strong and Weak Inversion Regimes [17]                               | 23   |

|----------------------------------------------------------------------------------------------------|------|

| Table. 4. 1. Defined Parameters Used in Equation (4.26)                                            | 55   |

| Table. 6. 1. Transistor Sizing and Bias Current for Folded Cascode Amplifier Shown in Fig. 4.5(b)  | 68   |

| Table. 6. 2. Summary of Circuit Parameter for $V_{DD}=1.8V$ (It also includes resistive divider po | ower |

| consumption)                                                                                       | 74   |

## **List OF Figures**

| Fig. 1. 1. An example of metabolic pathway showing a set of enzymes acting in series to                       |       |  |  |  |

|---------------------------------------------------------------------------------------------------------------|-------|--|--|--|

| molecule A to molecule E. Each enzyme catalyzes a particular chemical reaction while the enzyme is le         |       |  |  |  |

| unchanged [2]                                                                                                 | 2     |  |  |  |

| Fig. 1. 2. Close loop insulin delivery system that uses a computer to analyze the measured glucose va         | alue  |  |  |  |

| and sends a signal to the insulin pump to determine for the right amount of insulin to be delivered to        | the   |  |  |  |

| patient automatically. This process can be repeated every 5 minutes [6]                                       | 8     |  |  |  |

| Fig. 1. 3. Schematic block diagram of the glucose measurement block.                                          | 8     |  |  |  |

| Fig. 1. 4. Two different electrical model for human blood chemical solution                                   | 14    |  |  |  |

| Fig. 1. 5. R-C modeling of the electrode-electrolyte setup: (a) model with series-connected R-C elements.     | ents  |  |  |  |

| in each branch, (b) conversion of series-connected elements to parallel-connected elements, (c) mo            | odel  |  |  |  |

| with parallel-connected R-C elements in each branch and (d) final lumped R-C model [12]                       | 15    |  |  |  |

| Fig. 2. 1. Charges accumulated across the gate of a MOSFET.                                                   | 18    |  |  |  |

| Fig. 2. 2. Illustration of equation (2.1)-(2.3).                                                              | 18    |  |  |  |

| Fig. 2. 3. Current measurement as a subtract of forward and reverse current [17]                              | 21    |  |  |  |

| Fig. 2. 4. Summary of transistor modes of operation for different levels of source and drain voltages         | 21    |  |  |  |

| Fig. 2. 5. Transconductance efficiency in different regions of operation [18]                                 | 24    |  |  |  |

| Fig. 2. 6. Threshold voltage distribution for 8000 MOSFETs in a 0.5µm and 0.3µm CMOS process [2]              | 1].   |  |  |  |

|                                                                                                               | 26    |  |  |  |

| Fig. 2. 7. Schematic of a common neural amplifier [30].                                                       | 30    |  |  |  |

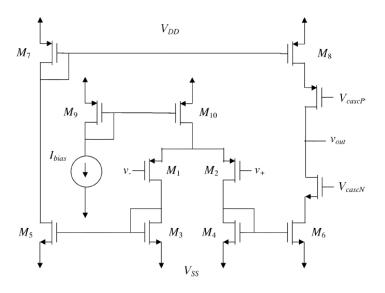

| Fig. 2. 8. Schematic of OTA used in Fig. 2.7 [30]                                                             | 31    |  |  |  |

| Fig. 2. 9. Subthreshold OTA using MIFG MOS transistors.                                                       | 32    |  |  |  |

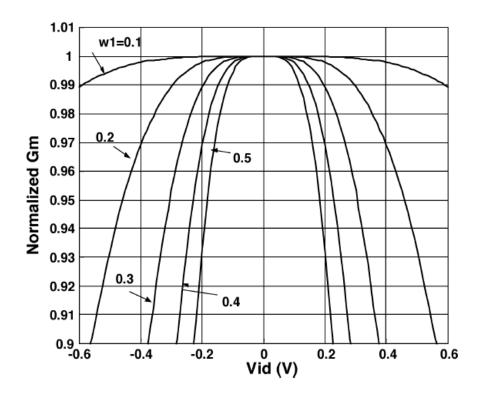

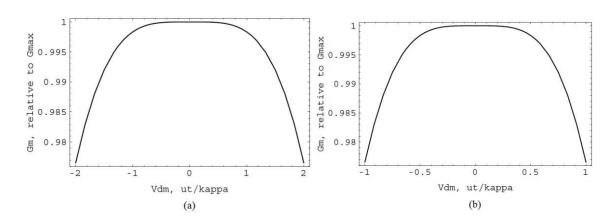

| Fig. 2. 10. Normalized transconductance versus differential input for different values of $\omega 1$          | 34    |  |  |  |

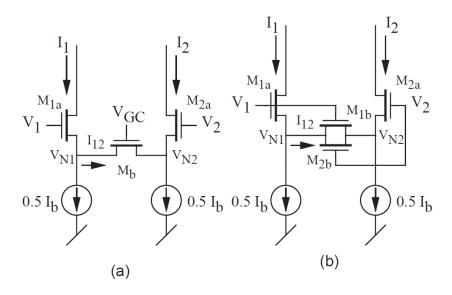

| Fig. 2. 11. One differential pair degenerated with: (a) one diffusor and (b) symmetric diffusors              | 34    |  |  |  |

| Fig. 2. 12. Simulation results for using degenerative technique via: (a) single diffusor and (b) symmetr      | ic    |  |  |  |

| diffusordiffusor                                                                                              | 35    |  |  |  |

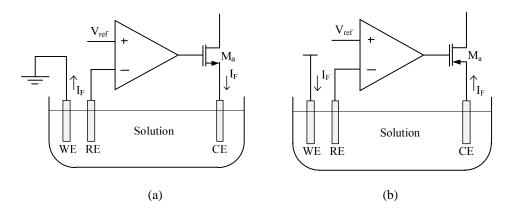

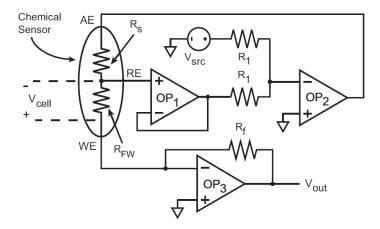

| Fig. 3. 1. a) A three-electrode electrochemical solution and potentiostat for $V_{WE}$ - $V_{RE}$ >0, b) A th | ıree- |  |  |  |

| electrode electrochemical solution and potentiostat for $V_{WE}$ - $V_{RE}$ <0                                | 37    |  |  |  |

| Fig. 3. 2. Generic equivalent circuit of an electrochemical cell [35]                                         | 37    |  |  |  |

| Fig. 3. 3. Basic current measurement configuration using resistor.                                         | . 38 |

|------------------------------------------------------------------------------------------------------------|------|

| Fig. 3. 4. L. Busoni et. al [37] design for improving the stability in potentiostat design                 | .38  |

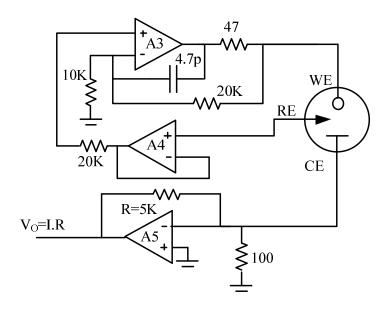

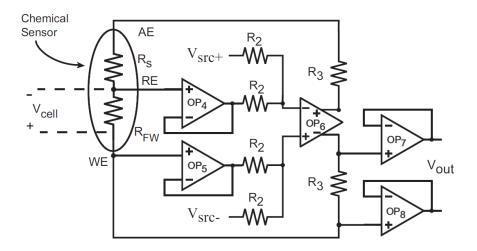

| Fig. 3. 5. Schematic of a single-ended potentiostat [38]                                                   | .39  |

| Fig. 3. 6. Schematic of a fFully potential potentiostat [38]                                               | . 39 |

| Fig. 3. 7. a) Current integration mostly used in current measurement using delta-sigma modulator.          | b)   |

| Current integration with a path of discharge which will be activated after capacitor reaches certain level | l of |

| voltage                                                                                                    | .41  |

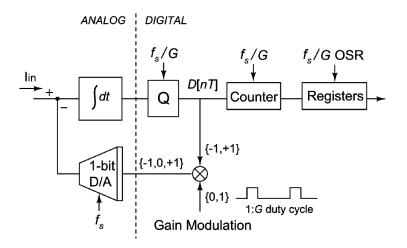

| Fig. 3. 8. Block diagram of a delta-sigma current measurement block of an accurate potentiostat [44]       | .41  |

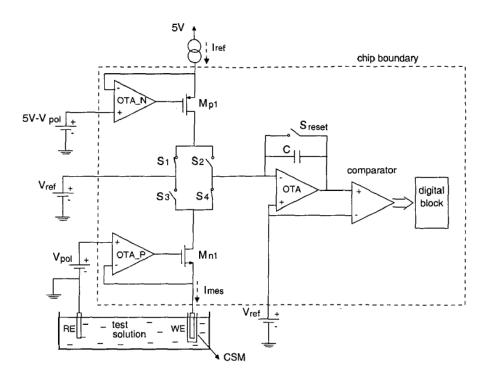

| Fig. 3. 9. The current measurement technique according to M. Breten [46].                                  | .42  |

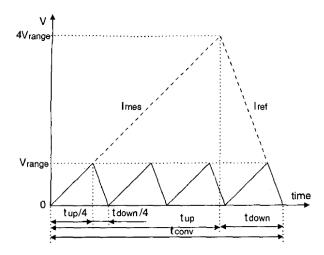

| Fig. 3. 10. Voltage across the capacitor in structure shown in Fig. 3.9.                                   | .43  |

| Fig. 3. 11. Current mirror configuration for separation between potentiostat and its current measurem      | ent  |

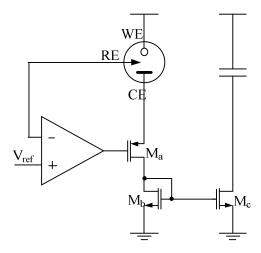

| (SPU) part.                                                                                                | .44  |

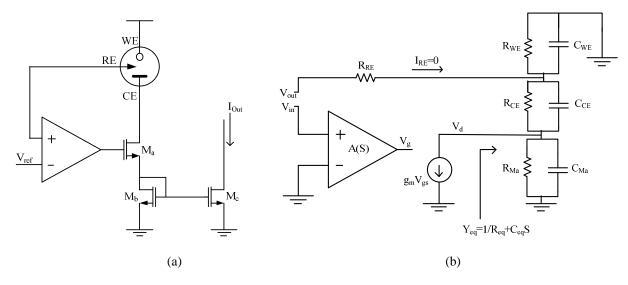

| Fig. 3. 12. A poentiostat structure for improved the stability according to M. M. Ahmadi et al. [35]       | .44  |

| Fig. 3. 13. M. M. Ahmadi et al. [35] implementation of structure shown in Fig. 3.12                        | .45  |

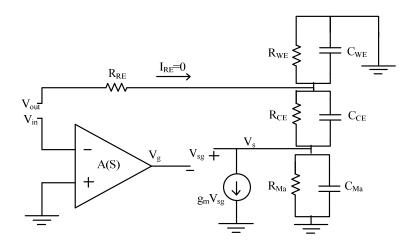

| Fig. 4. 1. Schematic of the AC equivalent circuit of a potentiostat.                                       | . 47 |

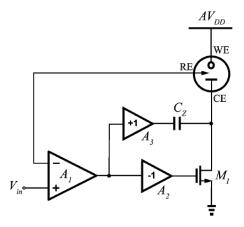

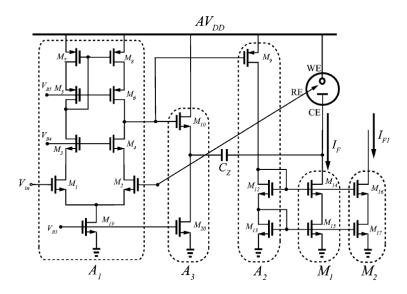

| Fig. 4. 2. a) Proposed structure. b) AC equivalent circuit for calculating the open loop transfer function | ı of |

| the system                                                                                                 | .49  |

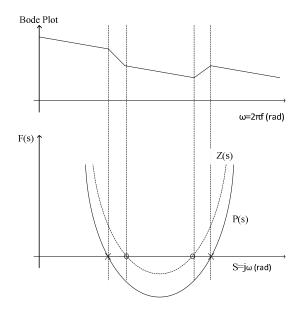

| Fig. 4. 3. The bode plot of an imaginary system with the fixed position of poles but variable gain. T      | his  |

| figure illustrate the fact that in this system, higher open loop gain results in lower stability or ph     | ase  |

| margin.                                                                                                    | .51  |

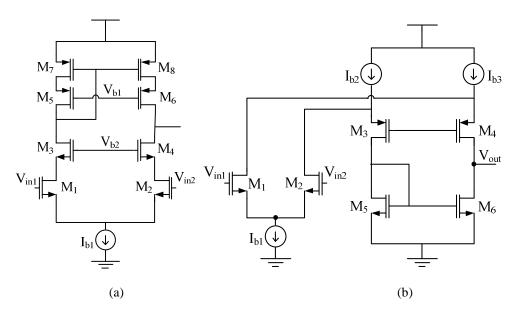

| Fig. 4. 4. Schematic of :a) Telescopic amplifier structure, b) Folded cascode amplifier structure          | . 52 |

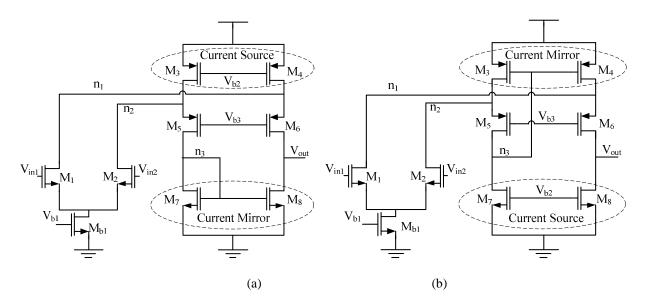

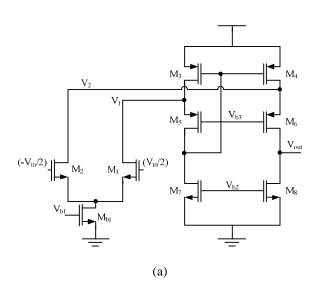

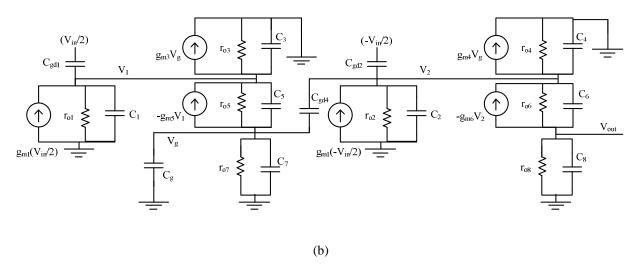

| Fig. 4. 5. a) Folded cascode structure. b) Proposed transconductance amplifier by modifying a folder       | ded  |

| cascode Structure.                                                                                         | .54  |

| Fig. 4. 6. Bode plots showing that extra poles and zeros created from the different AC signal paths        | can  |

| cause a non-uniform structure in the AC frequency response of the system.                                  | .56  |

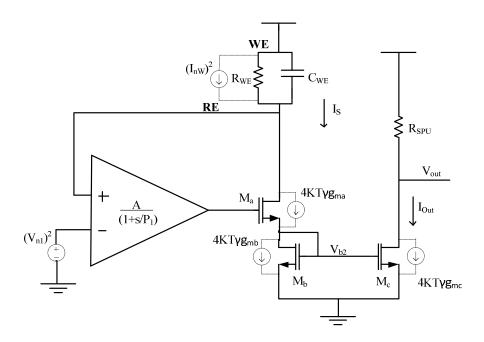

| Fig. 4. 7. Schematic of the proposed potentiostat structure.                                               | . 58 |

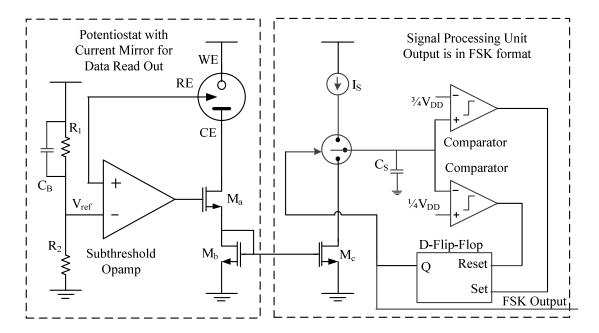

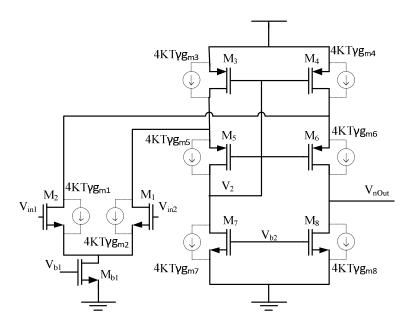

| Fig. 5. 1. Schematic of the proposed SPU structure                                                         | .64  |

| Fig. 5. 2. Schematic of the modified SPU structure.                                                        | .66  |

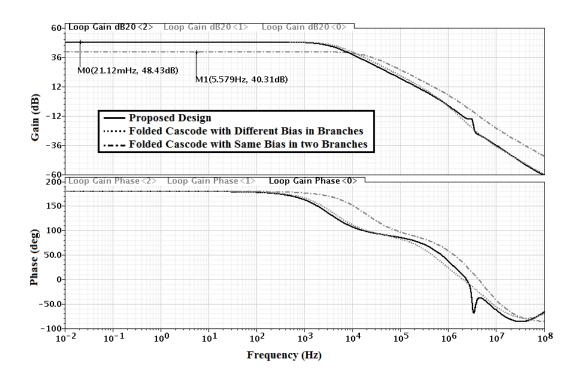

| Fig. 6. 1. Bode plot of the proposed opamp with different sizes of M <sub>1-2</sub> transistors            | . 69 |

| Fig. 6. 2. Change in position of poles with changing the sizes of transistors $M_{1-2}$                    | .69  |

| Fig. 6. 3. Comparison between the AC frequency response of the proposed folded cascode structure a         | and  |

| the conventional folded cascode structure.                                                                 | . 70 |

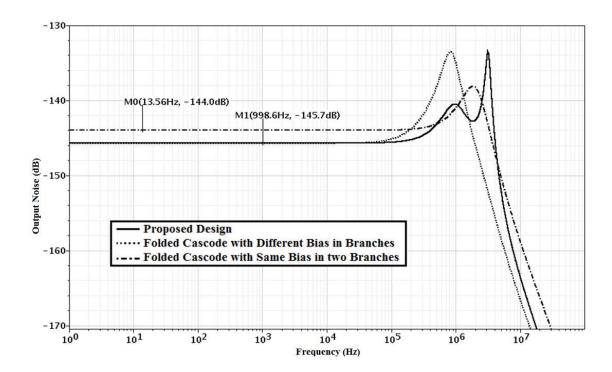

| Fig. 6. 4. Noise performance comparison between the proposed opamp and the conventional                | folded  |

|--------------------------------------------------------------------------------------------------------|---------|

| cascode opamp.                                                                                         | 71      |

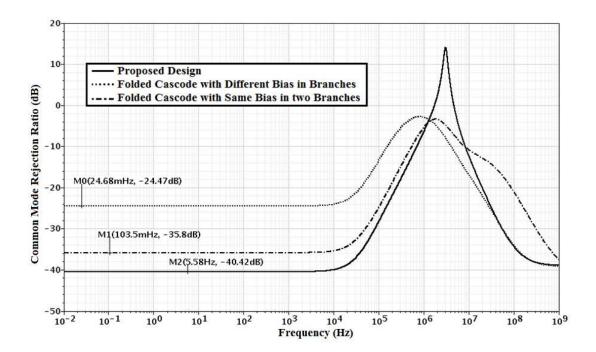

| Fig. 6. 5. Comparison of CMRR result for the proposed opamp with the conventional folded ca            | ascode  |

| opamp                                                                                                  | 72      |

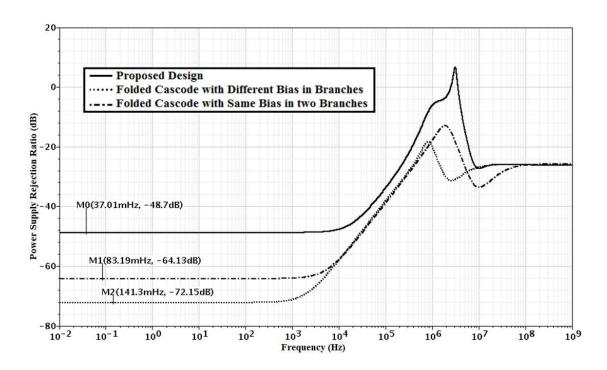

| Fig. 6. 6. Comparison of PSRR result for the proposed opamp with the conventional folded ca            | ascode  |

| opamp                                                                                                  | 73      |

| Fig. 6. 7. System stability response for three different solution models.                              | 74      |

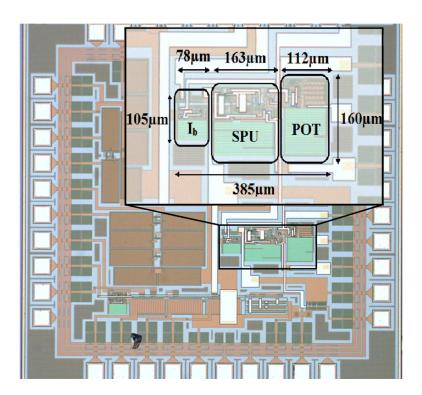

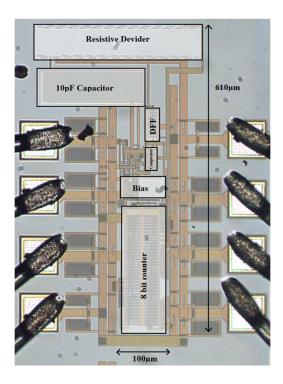

| Fig. 6. 8. Chip microphotograph showing various system building blocks.                                | 75      |

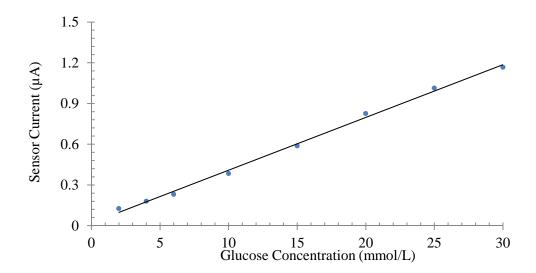

| Fig. 6. 9. Sensor current based on glucose concentration in the solution.                              | 76      |

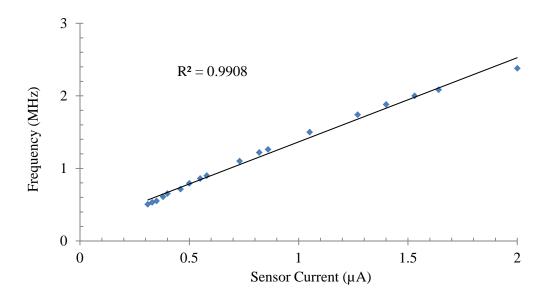

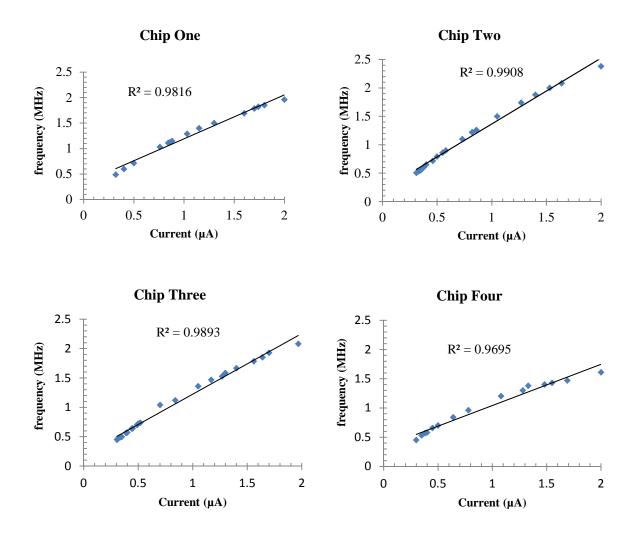

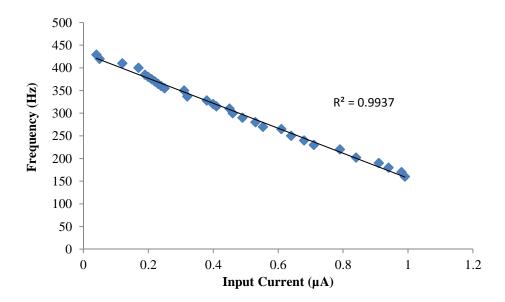

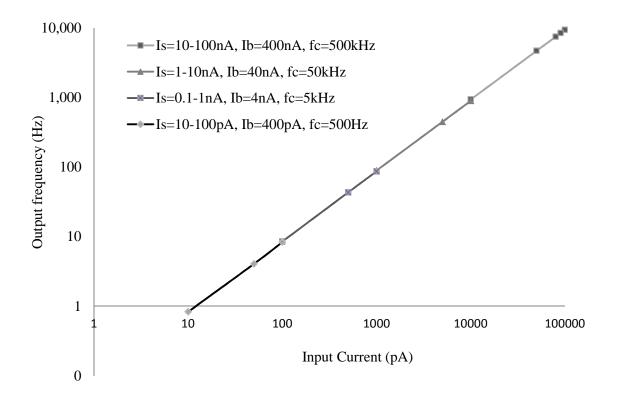

| Fig. 6. 10. Measurement results of the output frequency for different values of the sensor current     | 76      |

| Fig. 6. 11. Chip output frequency result for different values of the sensor current for four different | chips   |

|                                                                                                        | 77      |

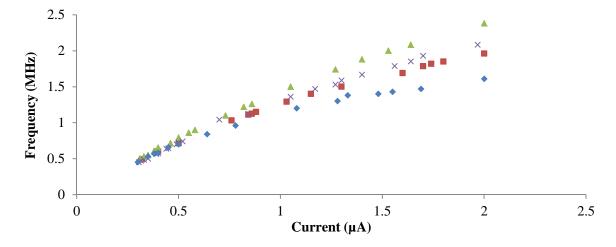

| Fig. 6. 12. Comparison between the test results for four chips.                                        | 77      |

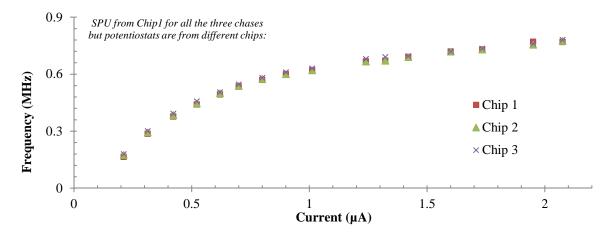

| Fig. 6. 13. Effect of the process variation in potentiostat on the system output results               | 78      |

| Fig. 6. 14. Offset between two inputs of the opamp in the potentiostat structure which also represent  | nts the |

| variation of $(V_{WE}-V_{RE})$ by process and mismatch variation.                                      | 78      |

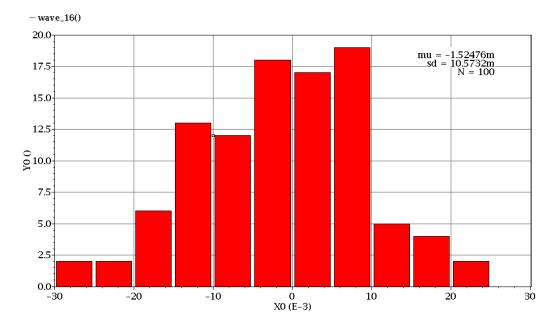

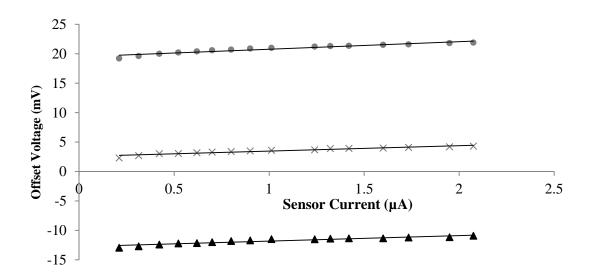

| Fig. 6. 15. Offset measurement results for three different chips in a 0.5µ CMOS process                | 79      |

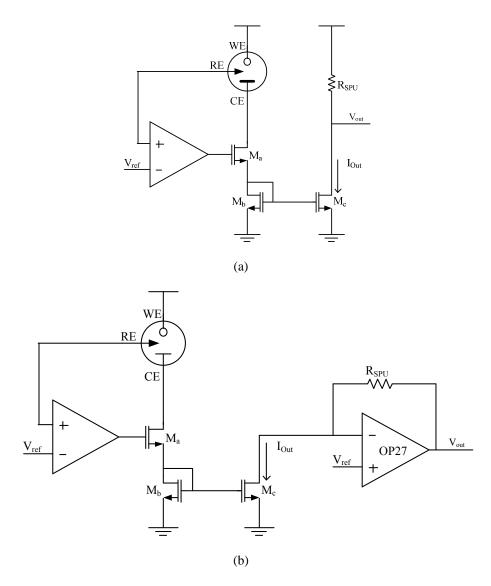

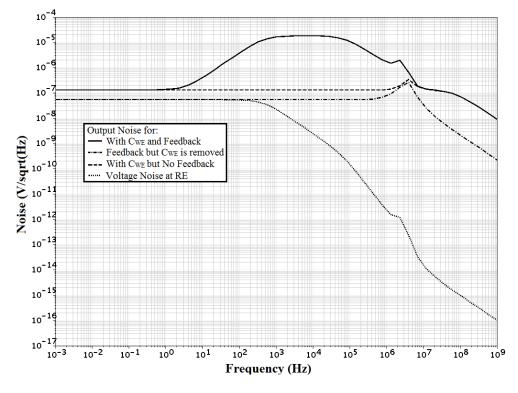

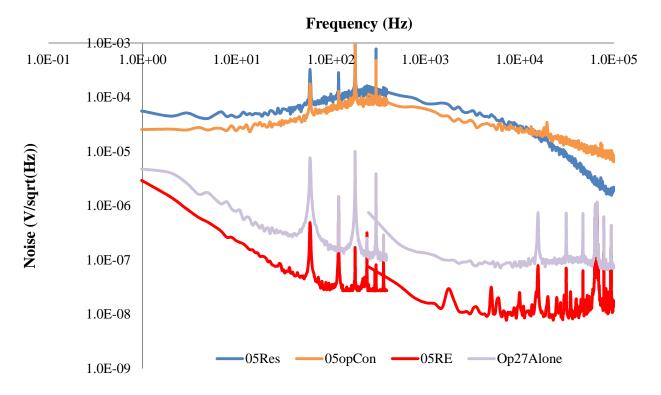

| Fig. 6. 16. Circuit configuration for noise measurement.                                               | 80      |

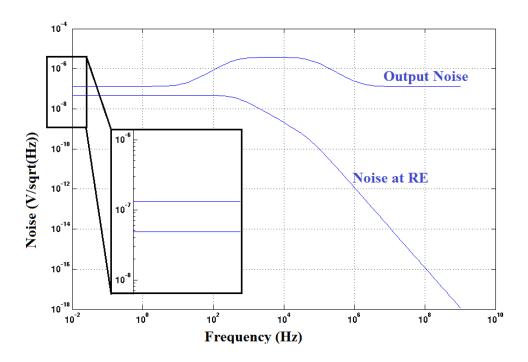

| Fig. 6. 17. The MATLAB simulation result for the derived noise power density in Appendix D             | 81      |

| Fig. 6. 18. Simulation Result for current noise using a resistor in the path of the current            | 81      |

| Fig. 6. 19. Test Result for current noise measurement using a resistor in the path of the current and  | OP27    |

| with a resistor in feedback in the path of the current.                                                | 82      |

| Fig. 6. 20. Chip microphotograph showing the signal processing unit in a $0.35\mu m$ CMOS process      | 83      |

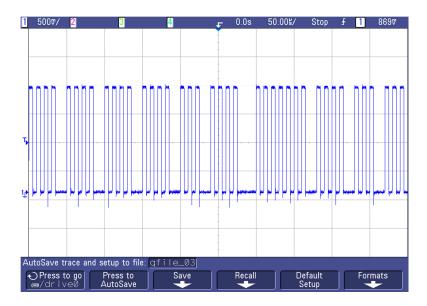

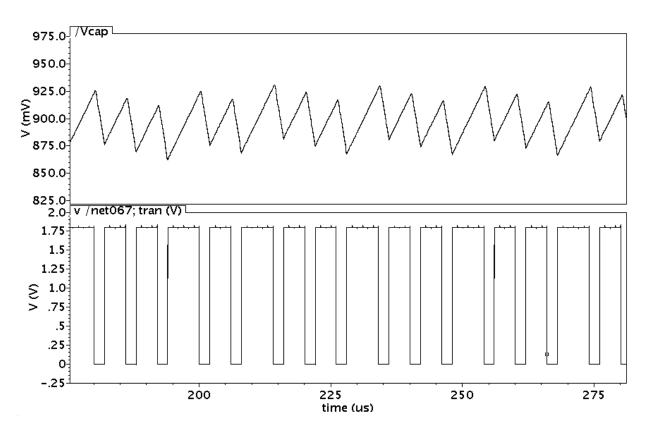

| Fig. 6. 21. The measured output signal of the structure shown in Fig. 5.2.                             | 84      |

| Fig. 6. 22. Chip test results after adding an eight-bit counter to the output.                         | 84      |

| Fig. 6. 23. The capacitor voltage and the output signal of the comparator.                             | 85      |

| Fig. 6. 24. The modified SPU output frequency vesrus the input current                                 | 86      |

| Fig. C. 1. a) The proposed transconductance amplifier. b) The small signal model for the pro-          | posec   |

| structure.                                                                                             | 98      |

| Fig. D. 1. Simplified potentiostat structure with the feedback for noise measurement.                  | 105     |

| Fig. D. 2. Potentiostat structure with the demonstration of the thermal noise on the transistors       | 106     |

### **CHAPTER 1 – Introduction**

Diabetes is one of the body metabolic disorders that have affected millions of peoples in the United States and over 100 million people around the world. It is one of the leading causes of death in the United States responsible for more than hundred thousand deaths each year. According to American Diabetes Association (ADA) the cost associated with complications of the diabetes is more than 40 billion dollar [1]. These complications are mostly due to the poor glucose monitoring which result in inaccurate diagnosis of the condition of the patients. Therefore there are a number of research groups working on improving the quality of the glucose measurement and monitoring schemes as well as the quality of the life of the diabetic patients. This chapter provides a brief introduction to this disease and introduces potentiostat design in conjunction with a chemical sensor that can work in a close loop with implantable insulin pump as a solution for this dilemma.

#### 1.1. Metabolism

Metabolism is the never-ending streams of chemical reactions that occur in the cells to sustain energy for living, grow, reproduce and maintain the cell structures from the food intake. Metabolism includes two different sets of reactions: catabolism and anabolism. Breaking down the organic molecules such as amino acids, sugars, nucleotides and lipids into energy is called catabolism and using this energy to construct the cells components such as nucleic acids and proteins is called anabolism.

These chemical reactions can normally occur only at very high temperatures that cannot exist inside the cell. Therefore for these reactions to happen, a catalyzer is required. Each reaction takes place using a different type of protein as catalyzer known as enzyme. Enzymes are crucial for metabolism pathway since they help these reactions proceed quickly and efficiently. Several enzymes may be used in one

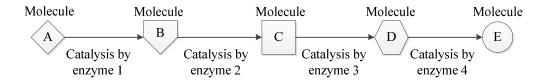

metabolic pathway as illustrated in Fig. 1.1. For example, glucose metabolism is controlled by an enzyme called insulin. This enzyme is produced in response to the increase in the blood glucose levels. Then using a cascade of kinases enzyme, the cells can convert glucose into storage molecules such as glycogen and fatty acids.

Fig. 1. 1. An example of metabolic pathway showing a set of enzymes acting in series to convert molecule A to molecule E. Each enzyme catalyzes a particular chemical reaction while the enzyme is left unchanged [2].

#### 1.1.1. Regulation and Control

To maintain a constant condition inside the cells, while the environment of most of the organisms is constantly changing, the reactions of metabolism must be perfectly regulated. Metabolic pathways are controlled by two concepts: regulation and control. Regulation is the increase or decrease in enzyme activity in response to a signal (large changes mean high regulation) while 'control' refers to the effect of these changes in the overall rate of the pathway.

#### 1.1.2. Metabolic Disorder

Metabolic disorders result in a large number of genetic diseases. Majority of these diseases are due to the defects of a single gene that represents the code for enzymes that is working as catalyzer in many metabolic reactions. The problem in most of these disorders is the accumulation of matters which are toxic or the reduced ability of synthesizing essential compounds. The metabolic disorders that are based on inborn genetic defect are known as congenital metabolic diseases or inherited metabolic diseases. In the past the inherited metabolic diseases were considered to only contain the disorders of carbohydrate, amino acid and organic acid metabolism. Recently many new inborn metabolisms have been discovered.

Diabetes is known to be the most common metabolic disorder that is a result of defect in the enzyme named insulin. In the rest of this chapter this disease will be studied in more details.

#### 1.2. Diabetes

Diabetes is a metabolic disorder due to the defect in producing insulin, the digestive enzyme. The organ that is responsible for producing this enzyme is pancreas which is a small organ located below the stomach. This organ secretes insulin from 2% of its mass that is called islets and contains pancreatic beta cells. Insulin has many important roles in human body and therefore it is known as the master hormone of the body. The most important role of insulin is the regulation of the metabolic breakdown of glucose and generation of the energy required for all of the human activities. The beta cells help secreting the right amount of insulin by detecting the blood glucose concentration [3].

In diabetes, a misdirected autoimmune reaction can wash off some of the beta cells. This can prevent the pancreas form secretion of the right amount of insulin. Therefore some of the glucose cannot enter the cells resulting in glucose build up in the bloodstream. In severe type of diabetes, this can lead to a cellular starvation while there is extra glucose in the blood. This situation is known as hyperglycemia and can cause a serious health problem. To resolve this situation, the patient needs to manually inject insulin. But if the injected insulin is too much, the rapid fall in glucose concentration can lead to hypoglycemia or low blood glucose. Therefore the patient needs to adjust the insulin level constantly. Diabetes can also be the cause of many other health problems such as kidney failure, loss of vision etc. Presently diabetes is estimated to affect 2-4% of the population [3].

#### 1.2.1. Different Types of Diabetes

There are two major types of diabetes, known as type 1 and type 2. The type 1 diabetes is due to the insufficient production of insulin or production of defective insulin (which is not common). The type 1 diabetes is also known as insulin dependent diabetes mellitus (IDDM) or juvenile onset diabetes mellitus.

Abnormal antibodies have been found in the body of patients with this type of diabetes that can be the cause of pancreas disorder. Type 1 diabetes usually occurs before the age of thirty. However there are some patients who can start to have this type of diabetes at older age.

Type 2 diabetes is due to the inability of cells to use insulin properly and efficiently. This problem mostly affects the muscular cells and fat tissues and is known as insulin resistance diabetes. The type 2 diabetes is also known as non-insulin dependent diabetes mellitus (NIDDM) or adult onset diabetes mellitus (AODM). Although the body still produces insulin, it is relatively inadequate due to insulin resistance or lack of sensitivity of the cells to the insulin. Type 2 diabetes mostly occurs at the ages of thirty or higher but recently it has been reported to be more common in the children as well.

#### 1.2.2. Home Monitoring of Blood Sugar

Testing the blood sugar at home is very important part of controlling the blood sugar levels in diabetic patients. Blood sugar is usually measured at bedtime, before meal and 1-4 hours after meal depending on the kind of the food served. The idea is to keep the glucose level of the blood near 70-120mg/dl which is a normal range and keep it below 140mg/dl two hours after the meal.

The blood sugar level measurement at home is normally performed by pricking a fingertip with a lancing device and applying the blood to a glucose meter which reads the glucose concentration. There are many different types of meters in the market today each of which has its own advantages and disadvantages. From the result of glucose measurement the patient can adjust his/her medicine, diets and physical activities.

At present, patients need to use "finger-sticking" for collecting a drop of blood many times a day to measure their blood glucose concentration. They need to check the measured glucose and keep it around the desired value by injecting the right amount of insulin. Injection can be performed either by syringes or insulin pen. The advantages of using the pen instead of syringe is that they are more convenient and easier to transport than traditional vial and syringe and are also more accurate and easier to use with less discomfort and pain. The problem with this method is that the level of blood glucose can change in less

than fifteen minutes and it not convenient for the patients to inject insulin more than twice a day, especially for parents who need to inject insulin to an infant.

#### 1.2.3. Importance of Frequent Glucose Monitoring for Diabetes

Frequent glucose measurement in diabetes is very essential to prevent the long term complications that can affect many different parts of the human body. Long-term complications of diabetes are often the result of higher blood sugar level over a long period of time. The other important source of these problems can be found in genes. Some of these long-term problems happen after many years or decades of having diabetes, because these problems usually develop silently and gradually over time. Therefore even if the patients do not have any signs of long term complication there is still chance to develop them eventually.

The organs that can be affected by diabetes in the long time are eyes, kidneys, nerves, heart and blood vessels, gums and feet. A brief description of the problems that can be caused by diabetes in any of these organs is provided below [4]:

**Eye Problems:** Three different types of eye problem can be developed in patients with diabetes: cataracts, retinopathy and glaucoma.

- Cataracts: The thickening and clouding of the lens of the eye is called cataracts. The lens is the part of the eye that helps focusing. This disease can make the patient's vision blurry or make the vision weak at nights. Doctors believe that people with diabetes who have high blood sugar levels over a long period of time are more susceptible to develop cataracts. In advanced level of this problem patients need to go through surgery to improve their vision.

- *Retinopathy:* Retinopathy is the eyes problem that involves changes in the retina. Retina is the layer at the back of the eye that is light-sensitive. The source of these changes can be the damage or the problem growth in the small blood vessels of the retina. This disease normally does not show until several years with diabetes with high blood sugar levels over this long period of time. In advanced level of this problem, laser treatment may be needed to prevent vision loss.

• *Glaucoma:* Another eye problem that patients with diabetes are susceptible to is glaucoma. In glaucoma the pressure inside the eye goes high that results in decreasing blood flow to the retina and the optic nerves which can cause damage. Although it does not change the vision a lot at first but in long time it can cause loss of vision. This problem is more prevalent in older people with long history of diabetes. This case also requires a surgery to solve the problem.

**Kidney Disease:** The high level of sugar in the blood can cause damage to the blood vessels in the kidneys that can lead to kidney disease. If the patients with diabetes do not control their blood sugar for a long time, they are more likely to get kidney disease that is a serious health problem. The kidney problem can become worse by high blood pressure or using tobacco. If the kidney disease is detected early enough, the damage can sometimes be reversed with proper treatment. But in a very rare case that the kidney problem gets worse the patient may develop kidney failure and require kidney transplant or dialysis. Therefore to protect the kidneys it is important to control the blood sugar.

**Nerve Damage:** Diabetic neuropathy is the nerve damage that can happen to patients with long history of diabetes. Numbness, tingling, or sharp pains in the feet can be the symptoms of the diabetic neuropathy. The numbness can cause a simple cut to be a serious problem because the patient can not realize the existence of the cut. The nerve damage in any part of the body can cause problem in that organ that may include heart, eyes and urinary system.

Diagnosis of this problem is normally done by a physical exam or a biopsy and patients are advised to see a neurologist. Controlling the blood sugar level can help reduce the patient's risk of developing the nerve damage.

**Heart and Blood Vessel Diseases:** The patients with diabetes have a high risk of developing cardiovascular diseases that may include heart attack, stroke or blockage of blood vessels in legs and feet. Heart attack and stroke can be the result of a blockage in the blood vessels supplying blood to the heart or the brain. The blood sugar management is very important for controlling the blood vessel problems.

**Gum Disease:** Too much plaque on the teeth and not enough saliva and having higher level of sugar in the mouth can cause tooth decay. Also loss of collagen and poor blood circulation can cause gum

problems. Bleeding, sensitive and painful gums are the symptoms of the gum disease. Gum disease can also be prevented by managing the blood sugar levels.

**Foot Problems:** Poor flow of the blood and nerve damage in patients with diabetes can develop foot problems.

# 1.2.4. Using an Implantable System for More Frequent and More Convenient Glucose Measurement

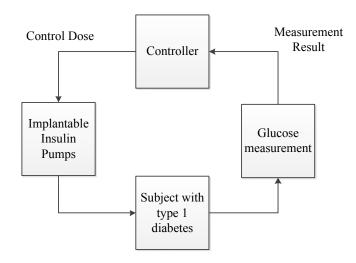

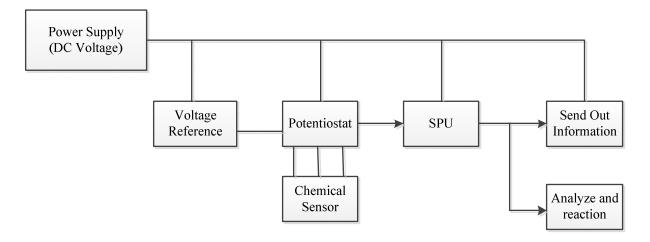

A miniature implanted glucose sensor in the body can continuously record the blood glucose level and display the value on the external watch-like receiver. This device can be programed to warn the hyperglycemia or hypoglycemia condition while monitoring the blood glucose minute by minute. Eventually this device can be coupled to an implanted insulin pump to automatically deliver the required amount of insulin. The implantable insulin pump has already been developed and by developing the implantable glucose sensor, the close control of blood glucose can be achievable [3]. Fig. 1.2 Shows the idea of the closed loop glucose measurement and insulin delivery for diabetes introduced by El-Khatib et al. in 2010 [5]. The implanted close loop system consists of three main blocks: (1) an electrochemical sensor in conjunction with a potentiostat to measure the blood glucose level, (2) a control block that defines the level of insulin injection and (3) an implanted insulin pump. The focus of this work is on the glucose measurement block shown in Fig. 1.3. As shown in this figure, a glucose measurement block consists five main sub-blocks. 1) DC supply, 2) voltage reference, 3) potentiostat, 4) signal processing unit and 5) telemetry unit. The focus of this work is on analyzing and optimizing the design of the potentiostat and the signal processing unit.

Fig. 1. 2. Close loop insulin delivery system that uses a computer to analyze the measured glucose value and sends a signal to the insulin pump to determine for the right amount of insulin to be delivered to the patient automatically. This process can be repeated every 5 minutes [6].

Fig. 1. 3. Schematic block diagram of the glucose measurement block.

#### 1.2.5. Electrochemical Principle in Glucose Sensing

One promising method of glucose sensing involves the use of a family of biological catalyzer known as enzymes or glucose oxidase. Based on the type of the catalyzer the reaction might be different. The output of these reaction can contain  $H_2O$  (water) and  $H_2O_2$  (hydrogen-peroxide).

One type of enzyme such as glucose oxidase (GOD), L-glutamate oxidase (GIOD) and cholesterol oxidase (COD) can be reduced by accepting two hydrogen atoms. Then the initial structure can be

restored by oxidizing the reduced enzyme. The reduced enzyme loses hydrogen that will combine with  $O_2$  and with the loss of two electrons a  $H_2O_2$  molecule can be created. Naming this group of enzyme, "flavin adenine dinucleotide (FAD)", the equation for these reactions can be written as below [7]:

$$FAD + substrate \rightarrow FADH_2 + product$$

(1)

$$FADH_2 + O_2 \rightarrow H_2O_2 + FAD \tag{2}$$

There is also another type of enzyme that is named "flavin mononucleotide (FMN)" that works the same way as FAD. The final product for both of these types is the reaction below [7]:

$$2H_2O_2 \rightarrow 2H_2O + O_2^+ + 4e^-$$

(3)

This reaction can take place by applying a difference potential to the electrochemical cell. In this case the function of the potentiostat is to provide this constant difference potential while collecting the generated electrons through its collecting electrode.

#### 1.2.6. Measuring Other Blood Factors Using Potentiostat

Potentiostats can be used to measure other important blood factors such as oxygen and lactate. Measuring these parameters along with the blood glucose level is of a great importance to the patient with multiple diseases. Measuring of blood oxygen can be applied to any one suffering from unstable oxygenation such as patients with hypoxemia. In hypoxemia patients suffer from the partial drop of pressure in their blood. The high levels of oxygen can damage lungs and central nervous system while low levels of oxygen can cause anemia. In addition, monitoring of lactate is particularly useful for athletes to check if they are over working or not. Potentiostat can help measuring these factors by applying a different difference potential to the electrodes of the electrochemical sensor designed to measure these parameters.

#### 1.3. Challenges in Designing a Potentiostat for an Implantable Glucose Sensor

There are three main challenges in designing a potentiostat working in conjunction with an implantable glucose sensor: (a) the total amount of power consumption, (b) the size of the chip which should be as small as possible to make it convenient for the patient to have it implanted and (c) the generated current should be sensed in a stable structure before it be sent to the telemetry system. In the following sections, the importance of decreasing the total amount of power consumption and increasing the stability of the system is discussed. To show the importance of having a potentiostat with low-power consumption, first a brief discussion over the possible methods for generating power is addressed here. In the next section, different techniques of low-power circuit design are also discussed. These techniques need to be applied to the circuits existing in all of the blocks of an implantable system.

#### 1.3.1. Power Conditioning for Implantable Systems

To power up an implantable system, three different sources of power can be used: 1) battery, 2) inductive link and 3) optical power transfer using photodiodes/photo cells. A brief discussion on these powering techniques and their practical limitations are discussed below.

#### 1.3.1.1. Powering System Using Battery

Batteries can be only used in cavity areas of the human body. However, they are typically bulky and pose a risk of leakage which is toxic and potentially can result is series health risks to the patient. In addition, the batteries need replacement after being used for a period of time. Decreasing the system power consumption can help increase the total battery life time and reduce the need for frequent replacement.

#### 1.3.1.2. Powering System Using Inductive Link

In comparison with batteries, inductive links can be implemented using smaller area without introducing leakage issues. In addition, because they utilize the energy being supplied from outside of the body, they do not need replacement. But these advantages come at the expense of lower efficiency. Due to the transmission of large amount of energy between the input and the output inductors through the human tissues, the area of human tissue can heat up by these inductors which can cause a series health problem as well. Therefore decreasing the total system power consumption can decrease the amount of power transferred through the tissues and improve the safety level of the entire system.

#### 1.3.1.3. Powering System via Optical Means

Optical coupling is another method for sending power to the implanted system through the human body. Similar to the inductive links, a high amount of power transfer through the tissues can cause heat accumulation and create tissue burn in the area of power transfer [8]. Therefore this method can be only used in very low power implantable systems.

From the above discussion, it can be concluded that providing a continuous health-care monitoring using an implantable unit requires low-power circuit design for the entire implantable system. The design requirements for the implantable system such as sensitivity, bandwidth, stability and input common mode range make the low-power circuit design for these applications more challenging [9]. Therefore in the next section different techniques used for the low-power circuit design are discussed.

#### 1.3.2. Low Power Design Techniques

Four major techniques in low-power circuit design are: 1) bulk-driven technique, 2) floating gate technique, 3) subthreshold biasing technique and 4) low-voltage design techniques. These techniques are briefly discussed in this section. Among these techniques, subthreshold design is chosen for this project and is discussed in more details in chapter 2.

#### 1.3.2.1. Bulk-Driven Technique

In the bulk-driven technique the gate voltages of the transistors are kept high enough to make sure that these MOSFETs are always on. Then the AC signal is applied to the body (substrate) of the transistors. In this technique there is no threshold voltage limiting factor and therefore this design can be employed in the low-voltage circuit design. The disadvantage of this technique is the lower body transconductance. In addition the input DC voltage should be kept in a range that the body diodes are completely off during the variation of the AC input signal.

#### 1.3.2.2. Floating Gates Technique

Floating gate is a polysilicon gate surrounded by silicon dioxide. Charge on the floating gates can be stored permanently. Therefore this technique has been used for long term memories. The level of this charge can be controlled by ultraviolet light or a large voltage. The trapped charge can be used to reduce the threshold voltage of the transistor to decrease the DC supply voltage requirement and therefore decrease the total power consumption [10].

#### 1.3.2.3. Subthreshold Biasing Technique

Subthreshold bias means applying a difference potential lower than the threshold voltage to the gate-source of the transistor as its DC bias voltage. This level of gate-source voltage can weakly invert the transistor channel and therefore this level of inversion is also known as weak inversion. In comparison with the strong inversion circuit design that requires that the gate-source voltage of the transistors be higher than the threshold voltage, this technique can achieve higher transconductance efficiency for the same level of current.

#### 1.3.2.4. Low-Voltage Design Technique

The low-voltage design technique includes all of the different circuit techniques that are designed to work in lower level of DC power supply voltage. These techniques can be applied along with the other

low-power design techniques to reduce both the DC power supply voltage and the current consumption of the system. Among the first three techniques, subthreshold technique is chosen as the low-power technique for this design.

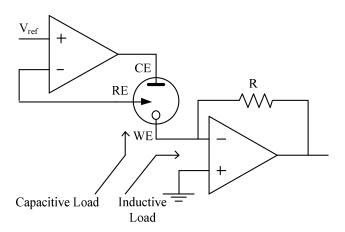

#### 1.3.3. Design of a Stable Potentiostat

Another important challenge in potentiostat design is achieving the system stability for all ranges of change in electrochemical solution model. The instability in the system can show itself like a noise at the output and makes it hard to detect the data. The main source of instability is the wide range of change in the electrical behavior of the electrode and the charge transfer medium in the blood during the oxidation. The instability problem in potentiostats has been discussed by the authors in [11, 12]. The authors in [11] mentioned that due to a pole contributed of the electrode in the charge transfer medium there is a good chance of instability. Commercial electrochemical potentiostats often report of oscillatory behavior of the system and the need for adding a large capacitor to achieve the stability [13]. Therefore it is very important to analyze the stability of the closed loop potentiostat circuits particularly when it is working with a solution that has a variable electrical behavior. Therefore to measure the blood glucose using a potentiostat it is important to have a clear understanding of its electrical behavior or its equivalent electrical circuit model.

#### 1.3.3.1 Finding the Electrical Circuit Model for the Human Blood

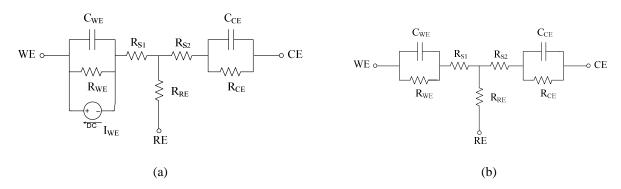

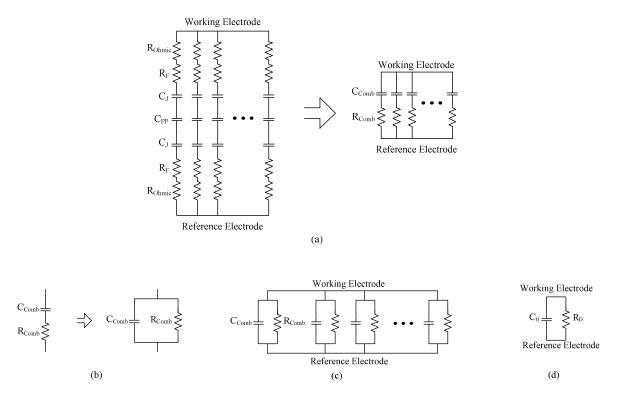

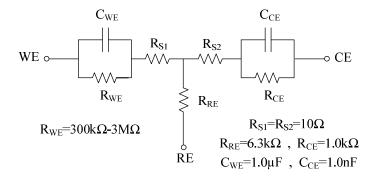

The difference potential that is required to be applied between the working and the reference electrodes of a glucose measurement system is usually in the range of several hundred milli-volts, while the generated current from the sensor is usually in the range of hundreds of nA that can vary widely. A number of different models have been reported for modeling the microelectrodes and the chemical solution. Once of the models includes a parallel combination of a current source ( $I_{WE}$ ) and a parasitic lumped R-C impedance [2] and another is just a combination of passive elements like resistors and capacitors. These two models are shown in Fig. 1.4(a) and 1.4(b), respectively. In either of these models,

the impedance is the combination of the voltage dependent polarized electrode junction capacitance and the double-layer parallel plate. Fig. 1.5 displays an R-C impedance approximation model between the electrochemical sensing electrodes [12]. In Fig. 1.5(a) each RC branch represents the electronic model of each working and reference electrodes. The resistors and capacitors in each branch can be combined into one parallel R-C network as shown Fig. 1.5(b) and therefore the final structure can be represented by a simple R-C combination as shown in Fig. 1.5(c) and Fig. 1.5(d).

Fig. 1. 4. Two different electrical model for human blood chemical solution.

### 1.4. Research Goals

Based on the above discussion, using one of the low-power design techniques to reduce the implantable system power consumption as well as improving the stability of the potentiostat system are the goals of this research. The main focus of this work is on the potentiostat block and the signal processing unit block which are the central blocks of this system. These two blocks are also the major power consumers in this system.

Measurement block can be realized utilizing fiber optics [14]. But electrochemical biosensors (potentiostats) are more economical and convenient [15]. Therefore the main focus of this work is based on electrochemical potentiostats.

Fig. 1. 5. R-C modeling of the electrode–electrolyte setup: (a) model with series-connected R-C elements in each branch, (b) conversion of series-connected elements to parallel-connected elements, (c) model with parallel-connected R-C elements in each branch and (d) final lumped R-C model [12].

#### 1.5. Original Contribution

In this work, a modification is applied to the traditional structure of potentiostat to solve its stability issue. The unconditional stability for wide range of current and models of chemical solution is achieved without adding any complexity or compensating technique. The simplicity of this structure and using fewer branches of current can help reduce the total power consumption of the implantable system.

This design also adopts the subthreshold biasing technique to reduce tremendous amount of power consumption and achieve the required stability. Correct sizing of transistors and redesigning the configuration of a folded cascode transconductance amplifier help this amplifier's open loop gain and its first dominant pole to be easily tunable. These important stability factors of this amplifier are set for maximum stability and minimum power consumption of the implantable potentiostat. In addition, the

accuracy of the electrochemical sensor current measurement is improved by designing a new current measurement technique.

#### 1.6. Overview of the Dissertation

This dissertation is organized as follow: In chapter 2 subthreshold biasing technique which is the low-power design technique used in this work is introduced. In this chapter also the EKV model of transistors which is a dedicated model for low-voltage and low-current design including subthreshold design has been addressed. In chapter 3 an overview on conventional potentiostat structures is provided. In chapter 4, the stability problem of conventional designs is analyzed and the new structure is proposed. In chapter 5, the proposed signal processing unit has been introduced. Chapter 6 contains the design simulation and test results of the proposed circuits realized in 0.5µm and 0.35µm CMOS processes. Finally chapter 7 provides a conclusion of this work.

### CHAPTER 2 – EKV Model and Subthreshold Design

For better understanding of the transistor behavior biased in subthreshold region, the EKV model is discussed first. The EKV model introduces an analytical model for transistors in all regions of operation. This model is also dedicated to the low-voltage and low-current designs. In this section, this model is discussed for better understanding of the subthreshold region of operation. Studying this model can help understand the physical reasons for the equations used in circuit design. Considering the effect of all of the physical parameters on the voltage and the current can improve the quality of the design and the robustness of the system.

#### 2.1. EKV Model

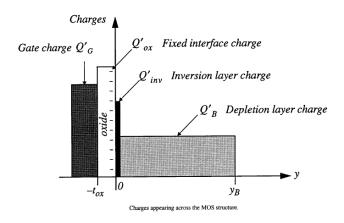

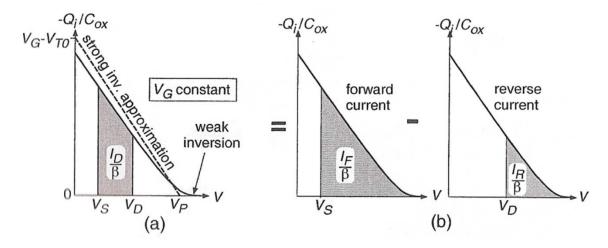

EKV is a fully analytical MOS transistor model based on Enz, Krummenacher and Vittoz work in 1995 [16]. This model is dedicated to low-voltage, low-current designs. It also describes the behavior of the transistors in all levels of inversion with one unique equation. The elements in this model are all defined with respect to the body voltage. Therefore  $V_G$  means  $V_{GB}$ , the gate-body voltage and in the same way  $V_S$  means  $V_{SB}$  and  $V_D$  means  $V_{DB}$ . To derive the equation of the transistor current at any level of inversion, the accumulated charges around the gate in one tiny area have been surveyed first. The voltage under the gate in the semiconductor area (surface potential) for this small area can be considered constant. Different types of accumulated charges in this area are shown in Fig. 2.1. In this figure,  $Q'_{inv} + Q'_{B}$  is the charge generated across  $C'_{ox}$  ( $C'_{ox}$  is the oxide capacitor ( $C_{ox}$ ) divided by unit area). The voltage that gathers the charge across  $C'_{ox}$  includes the gate voltage, difference between metal and semiconductor work functions (flat band voltage ( $V_{FB}$ )) and the surface potential ( $\Psi_S$ ). The accumulated charge can be calculated from equation below:

$$Q_B' + Q_{inv}' = -C_{ox}'(V_G - V_{FB} - \Psi_s)$$

(2.1)

Here,  $Q'_{inv}$  is the inversion layer charge and is the part of the charges that can generate current. From equation (2.1) and considering  $Q'_B = -\Gamma_b C_{ox} \sqrt{\Psi_s}$ , this charge can be calculated to be:

$$Q'_{inv} = -C'_{ox} (V_G - V_{FB} - \Psi_S - \Gamma_b \sqrt{\Psi_S}) = -C'_{ox} (V_G - V_{TB})$$

(2.2)

Fig. 2. 1. Charges accumulated across the gate of a MOSFET.

Fig. 2. 2. Illustration of equation (2.1)-(2.3).

Here  $V_{TB}$  can be defined to be:

$$V_{TB} = V_{FB} + \Psi_S + \Gamma_b \sqrt{\Psi_S} \tag{2.3}$$

where  $\Gamma_b = \frac{\sqrt{2qN_b\epsilon_{si}}}{c_{ox}}$ . From equation (2.3), it can be seen that as the voltage in the semiconductor area  $(\Psi_s)$  changes, the value of  $V_{TB}$  also changes. Fig. 2.2 shows the  $V_{TB}$  variation as a function of  $V_{ch}$  (which is the voltage under the gate area generated by the drain and the source voltages known as channel voltage  $(V_{ch} = \Psi_s - \Psi_0)$ ) which is independent of the gate voltage  $(V_G)$ . From equation (2.2),  $V_G = V_{TB} - \frac{Q'_{inv}}{C'_{ox}}$  ( $Q'_{inv}$  is a negative number) and is shown in Fig. 2.2. From this figure, it is obvious that to bias a transistor in saturation region for a fixed  $V_G$ , the channel voltage  $(V_{ch})$  needs to be reduced. Pinch-off voltage  $(V_p)$  is the value of  $V_{ch}$  at which no charges (or small charges) accumulate under the gate area. The transistor in this level of bias voltage represents "weak inversion" region.

From Fig. 2.2 the equation (2.3) can be linearized to the form below:

$$V_{TB} = V_{T0} + nV_{ch} (2.4)$$

where n can be defined to be:

$$n = \frac{dV_{TB}}{d\Psi_S} = 1 + \frac{\Gamma_b}{2\sqrt{\Psi_S}} \tag{2.5}$$

In equation (2.4),  $V_{TB}$  is equal to  $V_G$  when  $V_{ch}$  is equal to  $V_P$ . Therefore  $V_P$  can be calculated to be:

$$V_p = \frac{V_G - V_{T0}}{n} \tag{2.6}$$

From semiconductor physics,  $Q_{inv}$  is proportional to an exponential function of  $\Psi_s$ ,  $\Phi_f$  and  $V_{ch}$  as shown below:

$$Q_{inv} \propto exp \frac{\Psi_s - 2\Phi_F - V_{Ch}}{U_T} \tag{2.7}$$

A derivation from this equation results in:

$$U_T \frac{dQ_{inv}}{Q_{inv}} = d\Psi_S - dV_{Ch} \tag{2.8}$$

Recalling from equation (2.5),

$$n = \frac{dV_{TB}}{d\Psi_s} = \frac{d^{Q'_{inv}}/c'_{ox}}{d\Psi_s} = \frac{d^{Q_{inv}}/c_{ox}}{d\Psi_s}|_{small\ area}$$

(2.9)

Substituting equation (2.9) in equation (2.8), it can be rewritten as below:

$$\frac{dV_{Ch}}{U_T} = \frac{dQ_i}{nU_T C_{ox}} - \frac{dQ_{inv}}{Q_{inv}} \tag{2.10}$$

If  $v_{ch} = \frac{v_{Ch}}{v_T}$  and  $q_i = \frac{Q_{inv}}{(-2nC_{ox}U_T)}$ , the above equation can be simplified to the form:

$$-dv_{ch} = 2dq_i + dq_i/q_i \tag{2.11}$$

Integrating this equation results in:

$$Con_1 - v_{ch} = 2q_i + lnq_i \tag{2.12}$$

where  $Con_1$  is a constant value. Here the boundary condition for  $V_p$  can be used to calculate  $Con_1$  to be equal to  $V_p/U_T$ . Therefore defining  $v_p = V_p/U_T$ , the final equation is:

$$v_p - v_{ch} = 2q_i + lnq_i (2.13)$$

Equation (2.13) defines the relationship between the accumulated charge and the voltage channel in each node of the channel. Therefore to calculate the current in the transistor channel, all the gathered charges under the gate area need to be integrated from the beginning node of the channel (source area) to its end (drain area) using the equation below:

$$I_D = \int_{v_S}^{v_d} q_i dv_{ch} \tag{2.14}$$

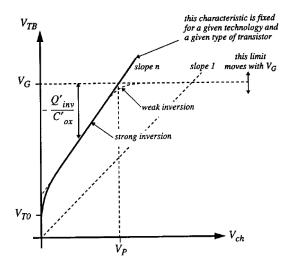

Fig. 2. 3. Current measurement as a subtract of forward and reverse current [17].

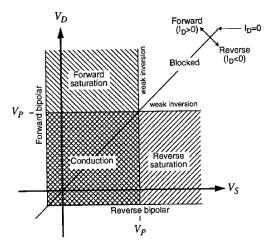

Fig. 2. 4. Summary of transistor modes of operation for different levels of source and drain voltages.

Another method of measuring the current is illustrated n in Fig. 2.3. In this figure it is assumed that  $V_S$  and  $V_D$  are both less than  $V_P$ . The small  $V_{DS}$  means that the transistor is biased in the linear region and because for a constant  $V_G$ ,  $V_S$  is lot less than  $V_P$ , this transistor is biased in strong inversion. The summary of the transistor modes of operation based on its source and drain voltages is provided in Fig. 2.4. For calculations in each situation the current can be divided into two components: a forward current and a reverse current. For the forward current  $V_D$  is assumed to be equal to infinity and the current is measured just for the value of  $V_S$  from the equation below:

$$i_f = \frac{I_F}{I_{snec}} = \int_{v_s}^{\infty} q_i dv_{ch}$$

(2.15)

where  $I_{spec} = 2n\mu C_{ox} \left(\frac{W}{L}\right) U_T^2 = 2n\beta U_T^2$  and W is gate width, L is gate length,  $\mu$  is transistor mobility and  $\beta = \mu C_{ox} \left(\frac{W}{L}\right)$ . The reverse current can be calculated the same way by assuming  $V_S$  to be equal to infinity. Then the final transistor current  $I_D$  is calculated by subtracting these two currents.

By substituting  $dv_{ch}$  from equation (2.11) to equation (2.15), for both the forward and the reverse currents, one can find:

$$i_{f,r} = \int_0^{q_{s,d}} (2q_i + 1)dq_i = q_{s,d}^2 + q_{s,d}$$

(2.16)

where  $q_{s,d}$  is charge density at node source or drain. From this equation  $q_{s,d}$  can be calculated based on  $i_{f,r}$  from the equation below:

$$q_{s,d} = \frac{\sqrt{1+4i_{f,r}}-1}{2} \tag{2.17}$$

From the equations (2.17) and (2.13), the relationship between the forward and the reverse currents with the source and the drain voltages can be found as follows:

$$v_p - v_{s,d} = \sqrt{1 + 4i_{f,r}} + \ln(\sqrt{1 + 4i_{f,r}} - 1) - (1 + \ln 2)$$

(2.18)

The reverse version of this equation can be estimated to be:

$$i_{f,r} = \ln^2(1 + exp\frac{v_p - v_{s,d}}{2})$$

(2.19)

From equation (2.19), two current values, one for forward current ( $i_f$ ) and the other for reverse current ( $i_r$ ), can be derived. The maximum value of this two is called "inversion coefficient (IC)" which defines the direction of current can be expressed as:

$$IC = \max(i_f, i_r) \tag{2.20}$$

In other modeling of NMOS transistors the drain current is the dominant current and therefore IC can be expressed as:

$$IC = i_d = \frac{I_D}{I_S} \tag{2.21}$$

From this equation it is evident that the drain current in strong and weak inversion regimes can be estimated as summarized in Table 2.1.

Table. 2. 1. Drain Current in Strong and Weak Inversion Regimes [17].

| Mode                  | Weak Inversion                                                                                                                                             | Strong Inversion                                                                                                                  |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Conduction            | $k_{\omega}.\beta.U_T^2.e^{V_P/U_T} \\ .[e^{-V_S/U_T} - e^{V_D/U_T}] \qquad \text{for } \begin{cases} V_S > V_P \\ V_D > V_P \\ V_S \cong V_D \end{cases}$ | $n. \beta. \left[ V_p - \frac{V_S + V_D}{2} \right] $ $. (V_D - V_S) $ for $\begin{cases} V_S \le V_P \\ V_D \le V_P \end{cases}$ |

| Forward<br>Saturation | $k_{\omega} \cdot \beta \cdot U_T^2 \cdot e^{\frac{V_P - V_S}{U_T}}$ for $\begin{cases} V_S > V_P \\ V_D > V_P \\ V_D - V_S \gg U_T \end{cases}$           | $\frac{n.\beta}{2}.(V_P - V_S)^2 \qquad \text{for } \begin{cases} V_S \le V_P \\ V_D > V_P \end{cases}$                           |

| Blocked               | $0 \qquad \text{for } \begin{cases} V_S \gg V_P \\ V_D \gg V_P \end{cases}  \text{or}  V_S = V_D$                                                          | $ \begin{array}{c} 0 & \text{for } \begin{cases} V_S > V_P \\ V_D > V_P \end{cases} \end{array} $                                 |

Using equation (2.19), the transconductance  $(g_m)$  of a transistor at all levels of inversion can be calculated. To calculate the  $g_m$  based on gate, drain and source voltages, the effect of small variation of each of these values on current variation need to be investigated as follows:

$$\Delta I_D = \frac{\partial I_D}{\partial V_G} \Big|_{V_S, V_D} \Delta V_G + \frac{\partial I_D}{\partial V_S} \Big|_{V_G, V_D} \Delta V_S + \frac{\partial I_D}{\partial V_D} \Big|_{V_S, V_G} \Delta V_D$$

(2.22)

By keeping  $V_S$  and  $V_D$  constant,  $g_m$  based on the gate variation can be calculated as below:

$$g_m = \frac{\partial I_D}{\partial V_G}\Big|_{V_S, V_D} \Delta V_G \cong \frac{I_D/_{I_S} U_T}{\sqrt{I_D/_{I_S} + 1/_2 \cdot \sqrt{I_D}/_{I_S} + 1}}$$

(2.23)

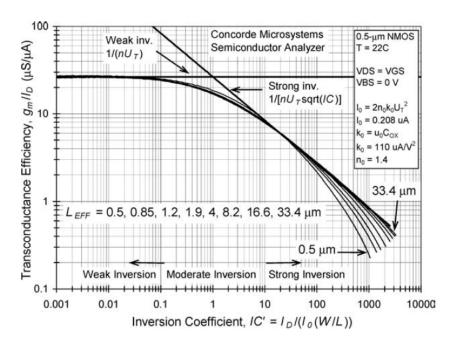

Fig. 2. 5. Transconductance efficiency in different regions of operation [18].

Based on equation (2.23),  $g_m$  for two conditions of strong inversion (S.I.) and weak inversion (W.I.) can be simplified as below:

$$g_{m} = \begin{cases} \sqrt{2n\beta I_{D}} & I_{D}/I_{S} > 10 \ (S.I.) \\ \frac{I_{D}}{nU_{T}} & I_{D}/I_{S} < 0.1 \ (W.I.) \end{cases}$$

(2.24)

Fig. 2.5 shows the transconductance efficiency  $(g_m/I_D)$  based on its level of conversion. From this figure it is evident that transistors achieve their maximum transconductance efficiency in W.I. Similar to the BISIM model the EKV model includes many second order effects such as mobility degradation due to vertical field, velocity saturation and channel length modulation [19].

# 2.2. Subthreshold Design Considerations

In this section the main important issues associated with MOSFETs operating in subthreshold region, such as mismatch, noise, drain induced barrier lowering (DIBL) and process- voltage-temperature (PVT) variation are discussed.

## 2.2.1. Mismatch

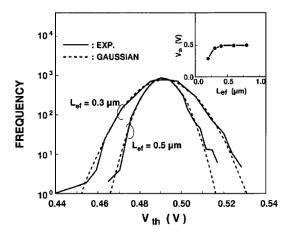

The two major source of mismatch in transistors are the difference between the threshold voltages  $(\Delta V_T)$  and the difference between the current factors  $(\Delta \beta)$ . These difference values have normal random distribution with zero mean value. The variance of these differences is dependent to the device size as presented by [20]:

$$\sigma^2(\Delta V_T) = \frac{A_{VT}^2}{W.L} \tag{2.25}$$

$$\left(\frac{\sigma(\Delta\beta)}{\beta}\right)^2 = \frac{A_\beta^2}{W.L} \tag{2.26}$$

where  $A_{VT}$  and  $A_{\beta}$  are technology dependent parameters. T. Mizuno et al [21] measured the threshold voltage  $(V_T)$  of 8000 transistors and derived the distribution histogram shown in Fig. 2.6. A. Asenov [22] estimated threshold voltage variance to be;

$$\sigma(\Delta V_T) = 3.19 \times 10^{-8} \frac{t_{ox} N_A^{0.4}}{\sqrt{LW}}$$

(2.27)

To calculate the effect of mismatch on circuit performance,  $M_1$  and  $M_2$  can be considered to be a pair of matched transistors used in a current mirror where the threshold voltage of  $M_{1,2}$  has a deviation of  $\delta V_{T1,2}$  form its mean value of  $V_{T0}$ . Therefore  $\Delta V_T = \delta V_{T1} - \delta V_{T2}$  and similarly,  $\Delta \beta = \delta \beta_1 - \delta \beta_2$ . In this case, the mismatch between  $M_1$  and  $M_2$  biased in saturation can be derived as:

$$\left(\frac{\sigma(\Delta I_{DS})}{I_{DS}}\right)^2 = \left(\frac{\sigma(\Delta\beta)}{\beta}\right)^2 + \left(\frac{g_m}{I_{DS}}\right)^2 \sigma^2(\Delta V_T)$$

(2.28)

$$\sigma^{2}(\Delta V_{GS}) = \sigma^{2}(\Delta V_{T}) + \left(\frac{I_{DS}}{g_{m}}\right)^{2} \left(\frac{\sigma(\Delta \beta)}{\beta}\right)^{2}$$

(2.29)

Fig. 2. 6. Threshold voltage distribution for 8000 MOSFETs in a 0.5µm and 0.3µm CMOS process [21].

From equations (2.28) and (2.29), the maximum  $g_m/I_{DS}$  achieved in W.I. improves voltage matching but it degrades the current matching.

Another source of mismatch is the gate leakage. Taking the gate leakage variation into account, the total current variation can be measured to be [23]:

$$\frac{\sigma_{Ids}^2}{I_{DS}^2} = \left(\frac{A_{VT}}{\sqrt{W.L}} \cdot \frac{g_m}{I_{DS}}\right)^2 + \left(\frac{0.03}{\sqrt{W.L}} \cdot \frac{I_G}{I_{DS}}\right)^2 \tag{2.30}$$

where  $I_G$  is the gate leakage current.

### 2.2.2. Noise

There are mainly two sources of noise: flicker noise and thermal noise. Flicker noise is generally important in low-frequency circuit design and is thought to be caused by crystal defects and contaminations [24]. Input referred flicker noise can be represented by:

$$\overline{v_t^2} = \left(\frac{K_f}{WLC_{ox}f}\right) \Delta f \tag{2.31}$$

From equation (2.31) it is obvious that increasing transistor size can help decrease this source of noise in low-frequency design. Another important source of noise is thermal noise, which is due to random thermal motion of electrons, and therefore it is directly proportional to the temperature (T). The input referred thermal noise of a MOSFET can be represented by [24]:

$$\overline{v_i^2} = 4kT\left(\frac{2}{3g_m}\right)\Delta f \tag{2.32}$$

From equation (2.32) it can be seen that the input referred thermal noise has a reverse relationship with transistor transconductance  $(g_m)$ . Thermal noise can be decreased with higher values of power consumption.

For the same level of current, biasing the transistor in W.I. can help maximize  $g_m$  and improve the input referred noise. Besides, to bias the transistor in this level of inversion, the size of transistor need to be increased which also helps decreasing the flicker noise. Therefore subthreshold design can be a very good option for low noise, low-frequency designs.

To compare the efficiency of circuits based on their current consumption and their input referred noise a noise efficiency factor has been defined in [25] to quantify this tradeoff:

$$NEF = V_{rms,in} \sqrt{\frac{2.I_{tot}}{\pi.U_T.4kT.BW}}$$

(2.33)

where  $V_{rms,in}$  is the input referred noise.

## 2.2.3. Drain Induced Barrier Lowering (DIBL)

In long channel devices the drain and the source are separated far enough so that their depletion regions do not affect each other. However, in shorter channel devices the drain voltage can influence the depletion region and change the channel potential. This can affect the leakage current by reducing the transistor threshold voltage. This phenomena is called drain induced barrier lowering (DIBL) [26]. Higher drain voltage or shorter channel length increases the DIBL effect. Therefore this phenomenon is more obvious in submicron technology. The bias current of MOS devices operating in subthreshold region considering DIBL and body effect can be modeled as below [27]:

$$I_{DS} = \mu_0 C_{ox} \frac{W}{L} (m-1) U_T^2 e^{\frac{V_G - V_T}{mU_T}} \left( 1 - e^{\frac{-V_{DS}}{U_T}} \right)$$

(2.34)

where  $V_T$  is the threshold voltage,  $\mu_0$  is the zero bias mobility and m is the subthreshold swing coefficient (body effect coefficient) and is equal to:

$$m = 1 + \frac{c_{dm}}{c_{ox}} = 1 + \frac{\frac{\epsilon_{si}}{w_{dm}}}{\frac{\epsilon_{ox}}{t_{ox}}} = 1 + \frac{3t_{ox}}{w_{dm}}$$

(2.35)

where  $C_{dm}$  is the capacitance of the depletion layer,  $t_{ox}$  is the gate oxide thickness and  $W_{dm}$  is the maximum depletion layer width.

## 2.2.4. Process-Voltage-Temperature (PVT) Variation

From Table 2.1 and equation (2.6) for  $V_P$ , the transistor current in subthreshold region can be derived in the form as shown below:

$$I_{DS} = K_{\omega} \beta U_T^2 e^{\frac{V_G - V_{T0}}{n}} \left( e^{\frac{-V_S}{U_T}} - e^{\frac{-V_D}{U_T}} \right)$$

(2.36)

From equation (2.36) it can be seen that there is an exponential relationship between the drain current and the transistor gate voltage. Therefore a small change in the gate voltage or the threshold voltage can result in a large change in the drain current. This sensitivity can be useful in the circuits with wide current tuning range but it also represents high sensitivity to PVT variation [19].

# 2.3. Subthreshold Design Examples

From the above discussion it can be concluded that the subthreshold design can be used in low-power, low-noise and low-frequency circuit design. The exponential relationship between the drain current and the gate voltage makes this mode of operation suitable for wide current tuning range circuits but also makes them more susceptible to PVT variation. This exponential relationship (similar to BJT transistors) limits the input voltage linear range. For a simple operational transconductance amplifier (OTA) biased in subthreshold, this range can be as low as 80mV [28, 29]. Therefore this design scheme can be only applied to the circuits that have no or low linearity requirements. For circuits with more input

linear range requirement, linearization techniques can be applied. Some examples of this scheme are discussed in the following section.

### 2.3.1. Amplifier Design for Neural Recording

Small signal level of neural signal makes neural recording less sensitive to linearity and more sensitive to noise level [24]. Therefore subthreshold design can be a good option for neural recording circuit design. Fig. 2.7 shows a common structure in neural amplifier design. R. R. Harrison et. al [30] used OTA structure shown in Fig. 2.8 biased in subthreshold region to improve the noise efficiency factor (NEF) and reduce the power consumption of this structure. Although the circuit topology used for OTA is a standard design, the sizing of the transistors is critical for low-noise low-power design.

Fig. 2. 7. Schematic of a common neural amplifier [30].

To improve the efficiency of this structure (and decrease the NEF defined in equation (2.33)), the input referred noise must be designed to be as low as possible. For this circuit the input referred noise is calculated to be:

$$\overline{v_{in,thermal}^2} = \left[ \frac{16kT}{3g_{m1}} \left( 1 + 2\frac{g_{m3}}{g_{m1}} + \frac{g_{m7}}{g_{m1}} \right) \right] \Delta f$$

(2.37)

From equation (2.37) it is evident that improving the input referred noise requires high transconductance of the input transistors ( $g_{m1}$  and  $g_{m2}$ ) and low transconductance of the current mirror transistors (( $g_{m1}$  and  $g_{m2}$ )>>( $g_{m3}$  and  $g_{m7}$ )). Therefore  $M_1$  and  $M_2$  are biased in subthreshold region to achieve the maximum transconductance efficiency and  $M_3$  and  $M_7$  are biased in strong inversion to get lower values of the transconductance. The thoughtful choice of the transistor sizing in this work reduces the input referred noise to  $2.2\mu V_{rms}$  and the NEF to 2.9 with a power consumption of  $80\mu W$ .

Fig. 2. 8. Schematic of OTA used in Fig. 2.7 [30].

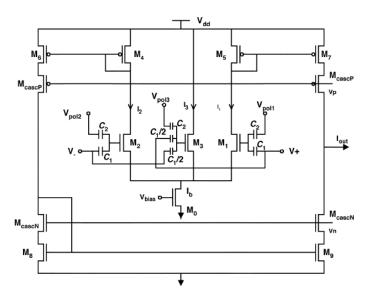

#### 2.3.2. Linearization Technique for Subthreshold Amplifiers

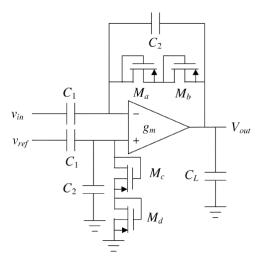

Many techniques have been proposed to improve the input linear range of the subthreshold amplifiers. An example using multiple input floating gate (MIFG) is discussed in [31]. Fig. 2.9 shows the OTA structure in this design. This design uses cubic-distortion-term-canceling technique for improving the linearity.

In the structure shown in Fig. 2.9, transistor  $M_3$  is added to average the difference of the input voltages. All of the transistors are biased in subthreshold region of operation and their bodies are connected to ground. With  $V_{pol1} = V_{pol2} = V_{pol3} = V_{dd}$  the current  $i_1$ ,  $i_2$  and  $i_3$  can be expressed as:

$$i_1 = I_{D01} \exp\left(\frac{\kappa(\omega_1 V_+ + \omega_2 V_{dd}) - V_S}{U_T}\right) \tag{2.38}$$

$$i_2 = I_{D02} \exp\left(\frac{\kappa(\omega_1 V_- + \omega_2 V_{dd}) - V_S}{U_T}\right)$$

(2.39)

$$i_3 = I_{D03} \exp\left(\frac{\kappa\left(\frac{\omega_1}{2}(V_+ + V_-) + \omega_2 V_{dd}\right) - V_S}{U_T}\right)$$

(2.40)

Fig. 2. 9. Subthreshold OTA using MIFG MOS transistors.

where  $\kappa$  is the electrostatic coupling coefficient between the floating gate and the channel,  $\omega_i$  is given by  $C_i/C_T$  ratio and  $V_S$  is the source voltage. Therefore  $I_{out}$  can be calculated to be:

$$I_{out} = I_2 - I_1 = I_b \frac{\sinh(x)}{\cosh(x) + A}$$

(2.41)

Where  $x = \omega_1(\kappa V_{id}/2U_T)$  and  $A = \frac{(W/L)_3}{2(W/L)_{1,2}}$ . Expanding equation (2.41) in the Taylor series gives:

$$I_{out} = \left(\frac{1}{1+A}\right)I_b \left[x + \left(\frac{1}{6} - \frac{1}{2(1+A)}\right)x^3 + \left(\frac{1}{120} - \frac{3}{24(1+A)} + \frac{1}{4(1+A)^2}\right)x^5 + \cdots\right]$$

(2.42)