University of Tennessee, Knoxville Trace: Tennessee Research and Creative Exchange

**Doctoral Dissertations**

Graduate School

12-2011

# Packaging Design of IGBT Power Module Using Novel Switching Cells

Shengnan Li sli14@utk.edu

#### **Recommended** Citation

Li, Shengnan, "Packaging Design of IGBT Power Module Using Novel Switching Cells." PhD diss., University of Tennessee, 2011. https://trace.tennessee.edu/utk\_graddiss/1205

This Dissertation is brought to you for free and open access by the Graduate School at Trace: Tennessee Research and Creative Exchange. It has been accepted for inclusion in Doctoral Dissertations by an authorized administrator of Trace: Tennessee Research and Creative Exchange. For more information, please contact trace@utk.edu.

To the Graduate Council:

I am submitting herewith a dissertation written by Shengnan Li entitled "Packaging Design of IGBT Power Module Using Novel Switching Cells." I have examined the final electronic copy of this dissertation for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Doctor of Philosophy, with a major in Electrical Engineering.

Leon M. Tolbert, Major Professor

We have read this dissertation and recommend its acceptance:

Fred Wang, Benjamin J. Blalock, Rao V. Arimilli

Accepted for the Council: <u>Carolyn R. Hodges</u>

Vice Provost and Dean of the Graduate School

(Original signatures are on file with official student records.)

# **Packaging Design of IGBT Power Module**

**Using Novel Switching Cells**

A Dissertation Presented for the Doctor of Philosophy Degree The University of Tennessee, Knoxville

Shengnan Li

December 2011

## Acknowledgements

First and foremost, I would like to express my great appreciation to my major advisor Dr. Leon Tolbert. He is a very devoted professor, very supportive advisor, and very nice person. The opportunity he provided is one of the best. Many thanks to his guidance, supervision in my research, and help in my life.

My sincere gratitude is also to Dr. Fred Wang. His knowledge and insight helped me a lot. The discussions with Dr. Wang were always inspiring. His guidance makes great contribution in my research.

Special thanks to Dr. Zhenxian Liang, Dr. Puqi Ning, Dr. Burak Ozpinezi and Madhu Sudhan Chinthavali from the National Transportation Research Center. Dr. Liang is very experienced and helpful. Without his help, I couldn't tackle the many challenges in my work. Puqi offered generous help on module fabrication. Whenever I have a question about module packaging, I can always count on him. Burak and Madhu are always supportive. I benefited a lot from their help.

It is a great pleasure to be a member of the UT Power and Energy Lab, which is now CURENT. The academic and friendly atmosphere is desirable. I will always remember the inspiring discussions with the students, from which I have learned a lot. I enjoyed the happy time we spend together.

My thanks are also to Ming Li and my parents. Their endless love is the origin of my happiness.

## Abstract

Parasitic inductance in power modules generates voltage spikes and current ringing during switching which cause extra stress in power electronic devices, increase electromagnetic interference (EMI), and degrade the performance of the power converter system. As newer power devices have faster switching speeds and higher power ratings, the effect of the parasitic inductance of the power module is more pronounced. This dissertation proposes a novel packaging method for power electronics modules based on the concepts of novel switching cells: P-cell and N-cell. It can reduce the stray inductance in the current commutation path in a phase-leg module and hence improve the switching behavior.

Taking an insulated gate bipolar transistor (IGBT) as an example, two phase-leg modules, specifically a conventional module and a P-cell and N-cell based module were designed. Using Ansoft Q3D Extractor, electromagnetic simulation was carried out to extract the stray inductance from the two modules. An ABB 1200 V / 75 A IGBT model and a diode model were built for simulation study. Circuit parasitics were extracted and modeled. Switching behavior with different package parasitics was studied based on the Saber simulation.

Two prototype phase-leg modules were fabricated. The parasitics were measured using a precision impedance analyzer. The measurement results agree with the simulation very well. A double pulse tester was built in laboratory. Several approaches were used to reduce the circuit and measuring parasitics. From the switching characteristics of the two modules, it was verified that the larger stray inductance in the layout causes higher voltage overshoot during turn off, which in turn increases the turn off losses.

Multichip (two in parallel) IGBT modules applying novel switching cells was also designed.

The parasitics were extracted and compared to a conventional design. The overall loop inductance was reduced in the proposed module. However, the mismatch of the paralleled branches was larger.

## TABLE OF CONTENTS

| Cha | apter | •                                                                   | Page   |

|-----|-------|---------------------------------------------------------------------|--------|

| 1   | Intr  | roduction                                                           | 1      |

|     | 1.1   | Background                                                          | 1      |

|     | 1.2   | Motivation and Strategy                                             |        |

|     | 1.3   | Dissertation Outline                                                | 6      |

| 2   | Lite  | erature Review                                                      | 7      |

|     | 2.1   | Wire Bonding Technology                                             | 7      |

|     |       | 2.1.1 Material Selection                                            | 7      |

|     |       | 2.1.2 Fabrication Process                                           |        |

|     | 2.2   | Study on Parasitics Induced by Packaging                            |        |

| 3   | Lay   | yout Design of IGBT Phase-leg Module                                |        |

|     | 3.1   | Introduction of P-cell and N-cell                                   |        |

|     |       | 3.1.1 Definition of P-cell and N-cell                               |        |

|     |       | 3.1.2 DC-DC Converters Constructed from P-cell and N-cell           |        |

|     |       | 3.1.3 Constructing Voltage Source Inverters from the P-cell and N-c | ell 30 |

|     | 3.2   | Package Layout Design Using the Novel Switching Cells               |        |

|     |       | 3.2.1 Electromagnetic Simulation Methodology                        |        |

|     |       | 3.2.2 Layout Design Using Q3D Extractor                             |        |

|     |       | 3.2.3 Simulation Results                                            |        |

|     | 3.3   | Summary                                                             |        |

| 4   | Ele   | ectrical Evaluation Based on Simulation                             |        |

|     | 4.1   | Parasitics Extraction from PCB                                      |        |

|     | 4.2   | IGBT and Diode Device Modeling                                      |        |

|     |       | 4.2.1 Modeling of Diode 5SLY12F1200                                 |        |

|   | 4.2.2 Modeling of IGBT 5SMY12J1280                                          | 46  |

|---|-----------------------------------------------------------------------------|-----|

|   | 4.3 Switching Characterization                                              | 49  |

|   | 4.4 Modeling and Analysis of Switching Behaviors                            | 52  |

|   | 4.5 Summary                                                                 | 54  |

| 5 | Experimental Verification                                                   | 55  |

|   | 5.1 Parasitics Measurement                                                  | 55  |

|   | 5.2 Static Characteristics Testing                                          | 61  |

|   | 5.3 Switching Characterization                                              | 64  |

|   | 5.3.1 Double Pulse Tester                                                   | 65  |

|   | 5.3.2 On Board Inductance Calibration                                       | 70  |

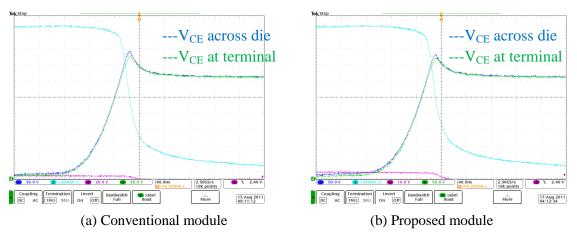

|   | 5.3.3 IGBT Die Voltage Measurement                                          | 75  |

|   | 5.3.4 Experimental Results                                                  | 77  |

|   | 5.3.5 Comparison of Experiment with Simulation results                      | 81  |

|   | 5.4 Summary                                                                 | 83  |

| 6 | Utilizing Novel Switching Cells in Multichip IGBT Module                    | 85  |

|   | 6.1 Layout Design of Multichip Power Modules Based on Novel Switching Cells | 85  |

|   | 6.2 Switching Characteristic of Multichip Power Module                      | 89  |

|   | 6.3 Measurement of the Parasitics in the Multichip Power Modules            | 92  |

|   | 6.4 Summary                                                                 | 97  |

| 7 | Conclusion and Future Work                                                  | 98  |

|   | 7.1 Conclusion                                                              | 98  |

|   | 7.1.1 Summary of the Work                                                   | 98  |

|   | 7.1.2 Power Module Design Considerations and Influence of Parasitics        | 100 |

|   | 7.1.3 Contributions of This Dissertation                                    | 101 |

|   | 7.2 Future Work                                                             | 102 |

| References |  |

|------------|--|

|            |  |

| Vita       |  |

## LIST OF FIGURES

| Figure 1.1. SEMiX product family.                                                                | 2    |

|--------------------------------------------------------------------------------------------------|------|

| Figure 1.2. 1200 A, 3300 V IGBT module                                                           | 2    |

| Figure 1.3. Fully integrated intelligent power module in single-in-line and dual-in-line housing | g. 3 |

| Figure 1.4. SKiM63 (300 A, 1200 V) and HybridPack (400 A, 600 V)                                 | 3    |

| Figure 2.1. Structure of an IGBT power module                                                    | 8    |

| Figure 2.2 Package inductance                                                                    | . 19 |

| Figure 3.1. Basic canonical cell.                                                                | . 22 |

| Figure 3.2. Two basic switching cells: P-cell and N-cell.                                        | . 24 |

| Figure 3.3. Four classic DC-DC converters and their P-cell and N-cell representation             | . 25 |

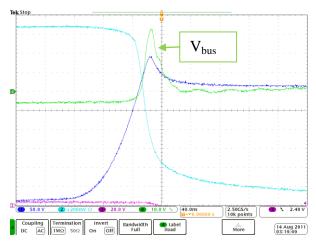

| Figure 3.4. Simulation results for P-cell and N-cell buck converter.                             | . 26 |

| Figure 3.5. Experimental output voltage ripple (100mV/div) of buck converter.                    | . 27 |

| Figure 3.6. Experimental output voltage of Ćuk converters                                        | . 30 |

| Figure 3.8. Full bridge inverter with package parasitics                                         | . 33 |

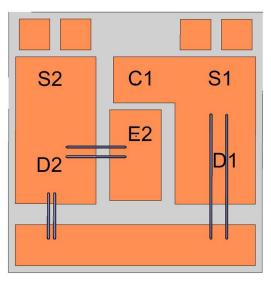

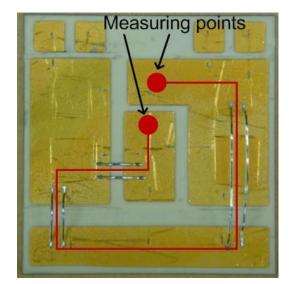

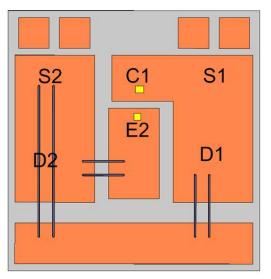

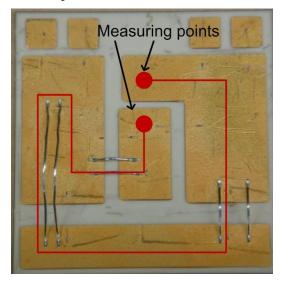

| Figure 3.9. Phase-leg module layout                                                              | . 37 |

| Figure 3.10. Phase-leg modules with measuring points.                                            | . 39 |

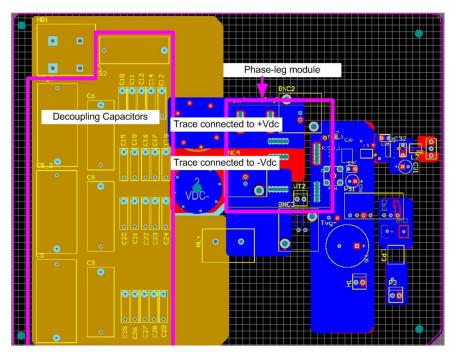

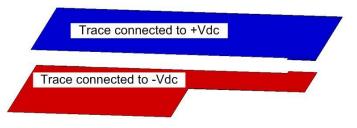

| Figure 4.1. PCB used for double pulse tester                                                     | . 42 |

| Figure 4.2. DC link in double pulse tester PCB                                                   | . 43 |

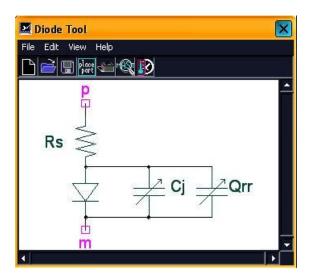

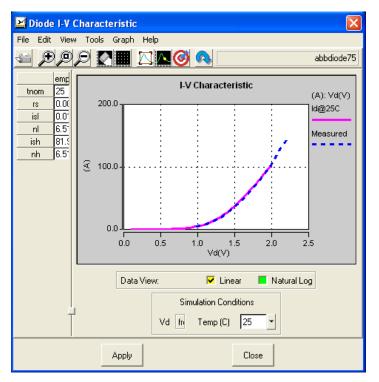

| Figure 4.4. Saber diode model user interface.                                                    | . 45 |

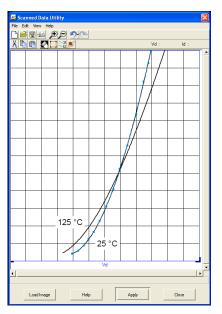

| Figure 4.5. Scanned I-V curve from datasheet                                                     |

|--------------------------------------------------------------------------------------------------|

| Figure 4.6. I-V characteristic after curve fitting from the loaded I-V curve                     |

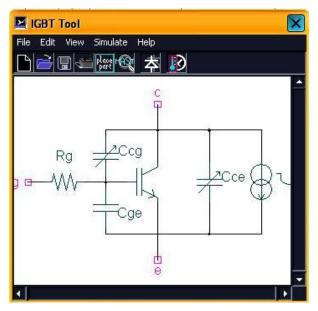

| Figure 4.7. Saber IGBT model user interface                                                      |

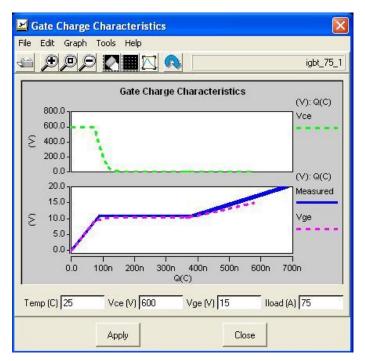

| Figure 4.8. Verification of gate charge                                                          |

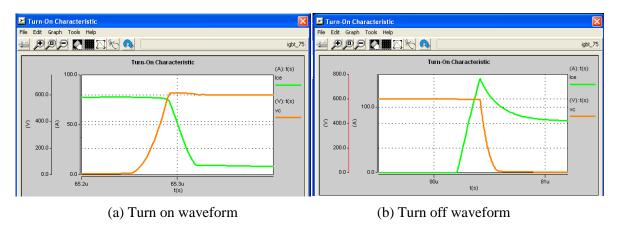

| Figure 4.9. Verification of switching waveform                                                   |

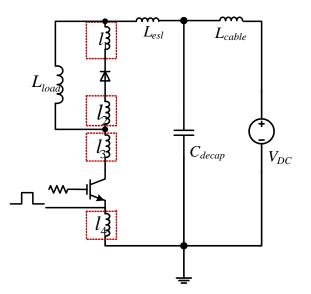

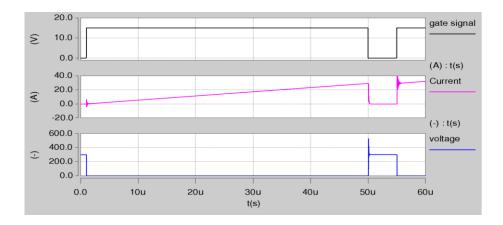

| Figure 4.10. Schematic of double pulse tester                                                    |

| Figure 4.11 Typical waveforms of double pulse tester                                             |

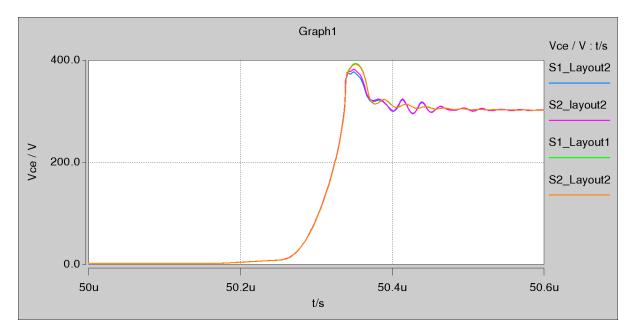

| Figure 4.12. Switching behaviors under module parasitics                                         |

| Figure 4.13. Switching transient circuit model                                                   |

| Figure 5.1 Conventional module DBC pattern with bonding wires designed for parasitie             |

| measurement                                                                                      |

| Figure 5.2. Proposed module DBC pattern with bonding wires designed for parasiti                 |

| measurement                                                                                      |

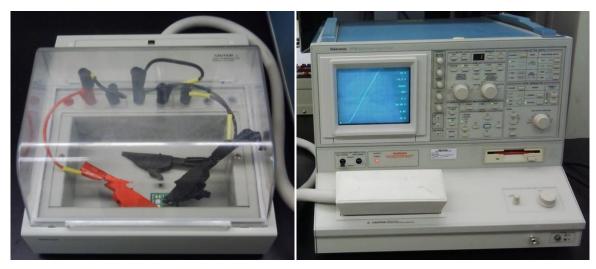

| Figure 5.3. Impedance analyzer and probe fixture for parasitic measurement                       |

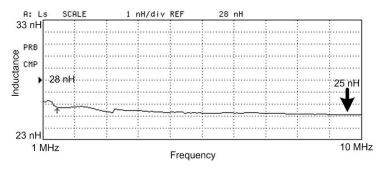

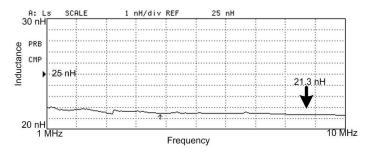

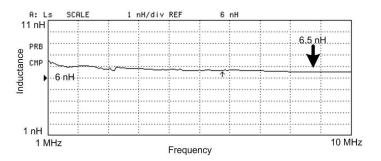

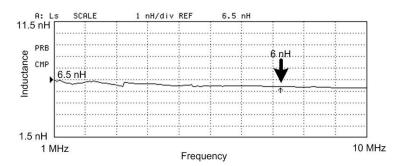

| Figure 5.4. Measured results                                                                     |

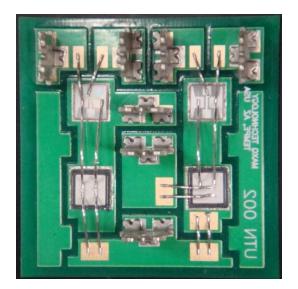

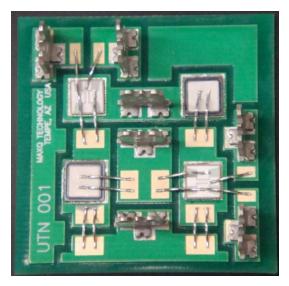

| Figure 5.5. Fabricated modules (Conventional one in the left and the proposed one in the right)6 |

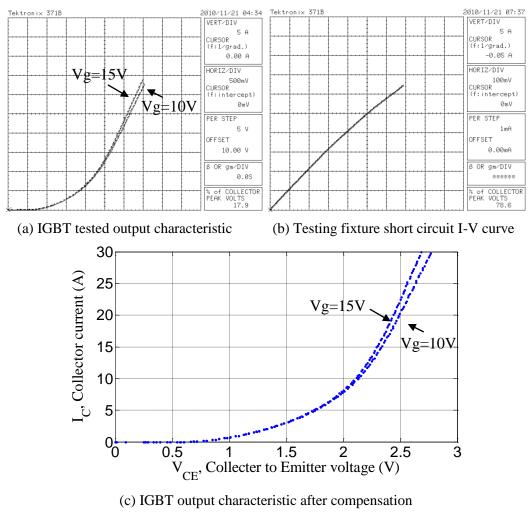

| Figure 5.6. Tektronix 371B curve tracer                                                          |

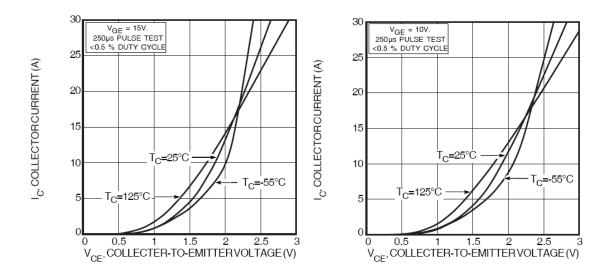

| Figure 5.7 Measured IGBT output characteristic                                                   |

| Figure 5.8. IGBT output characteristic from datasheet                                            |

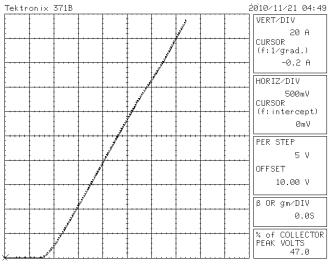

| Figure 5.9. FWD I-V curve                                                                        |

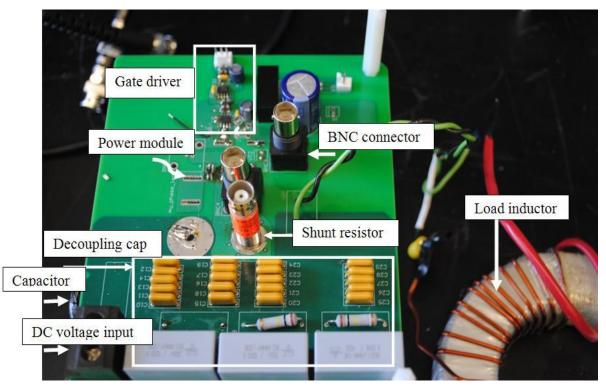

| Figure 5.10. Printed circuit board of DPT                                                   |

|---------------------------------------------------------------------------------------------|

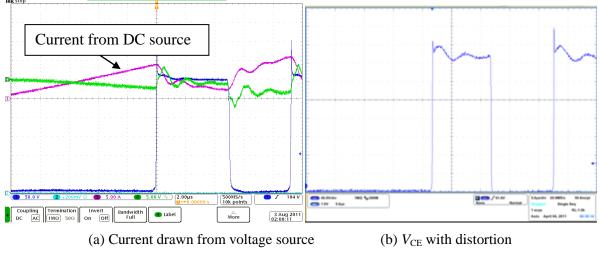

| Figure 5.11. Demonstration of the cable stray inductance effect                             |

| Figure 5.12. Gate drive circuit                                                             |

| Figure 5.13. Reduced tip-to-ground loop using a probe-tip adaptor                           |

| Figure 5.14. Measurement result of the bus impedance                                        |

| Figure 5.15. Measurement results of decoupling capacitance on board                         |

| Figure 5.16. Stray inductance measurement results of the PCB73                              |

| Figure 5.17. Layout of DC bus in PCB73                                                      |

| Figure 5.18. Voltage on module terminals during turn off74                                  |

| Figure 5.19. Voltage on module terminals during turn off after correction                   |

| Figure 5.20. Illustration of measuring points                                               |

| Figure 5.21. Module with wire connection from IGBT die76                                    |

| Figure 5.22. Turn off voltage of IGBT at different measuring points                         |

| Figure 5.23. Enlarged waveform of turn off voltage of IGBT at different measuring points 77 |

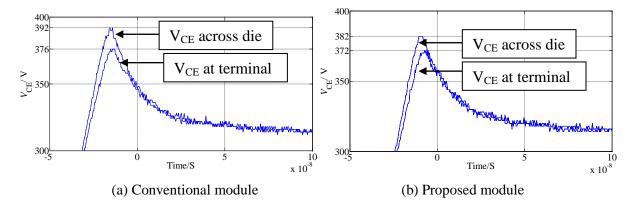

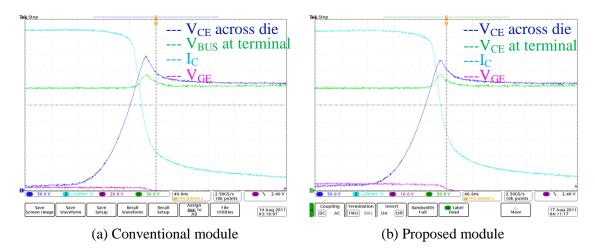

| Figure 5.24. Turn off voltage and current                                                   |

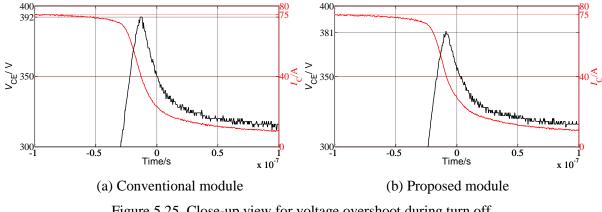

| Figure 5.25. Close-up view for voltage overshoot during turn off                            |

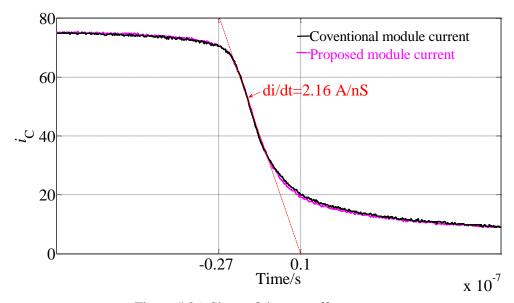

| Figure 5.26. Slope of the turn off current                                                  |

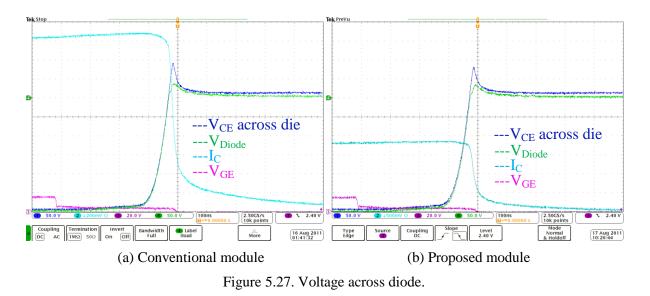

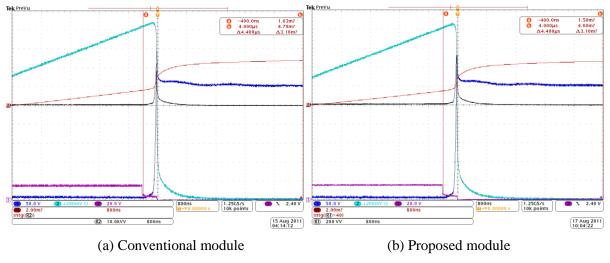

| Figure 5.27. Voltage across diode                                                           |

| Figure 5.28. Turn off loss calculation                                                      |

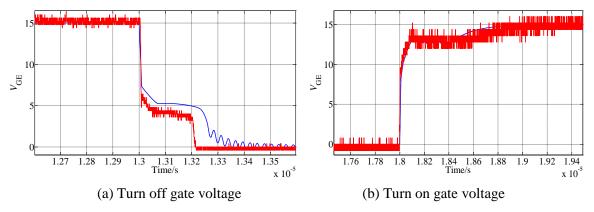

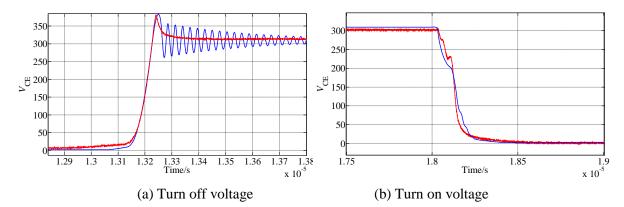

| Figure 5.29. Comparison of experiment and simulation of gate voltage (red is experiment; blue is |

|--------------------------------------------------------------------------------------------------|

| simulation)                                                                                      |

| Figure 5.30. Comparison of experiment and simulation of IGBT voltage                             |

| Figure 5.31. Comparison of experiment and simulation of IGBT current                             |

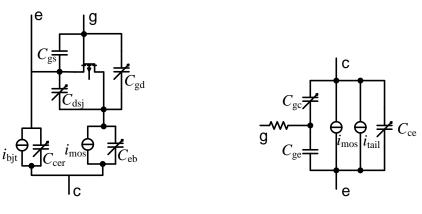

| Figure 5.32. Analog circuit representation of IGBT model                                         |

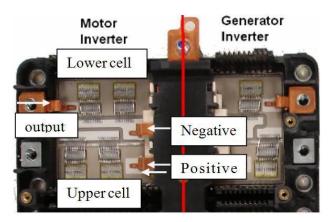

| Figure 6.1. A commercial inverter IPM                                                            |

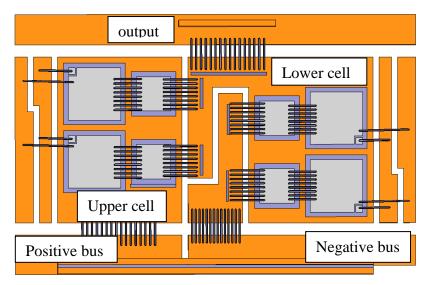

| Figure 6.2. Conventional layout of an IGBT module with paralleled dice                           |

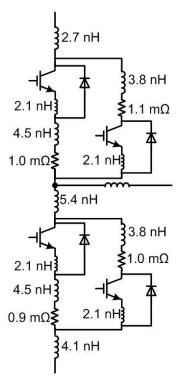

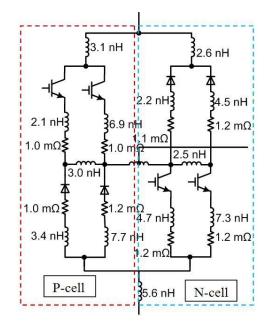

| Figure 6.3. Parasitics extraction of the conventional multichip module                           |

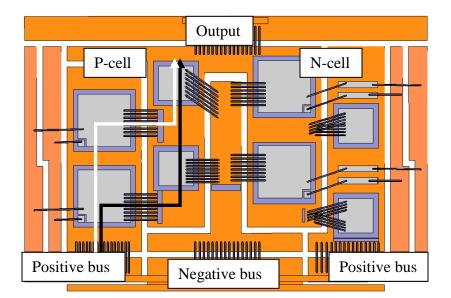

| Figure 6.4. Layout design of a paralleled IGBT module using novel switching cells                |

| Figure 6.5. Parasitics extraction of the conventional multichip module                           |

| Figure 6.6. Turn off voltage of IGBTs                                                            |

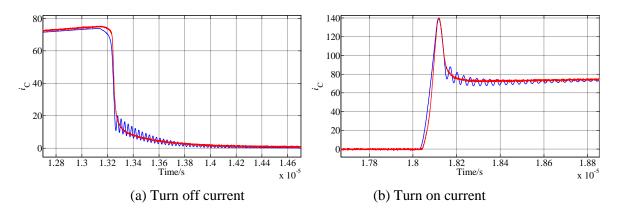

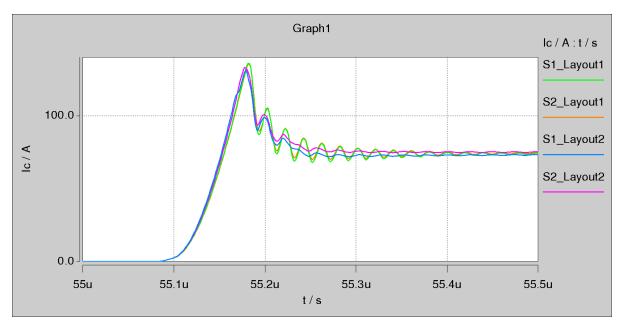

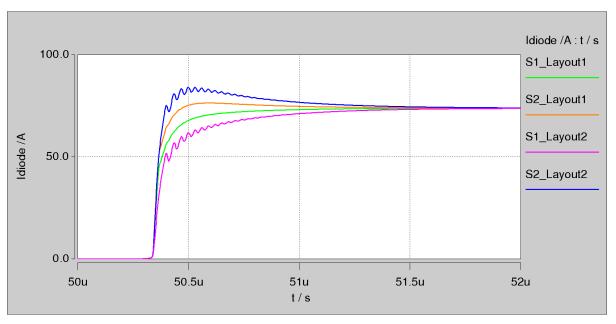

| Figure 6.7. Turn on current of IGBTs91                                                           |

| Figure 6.8. Turn on current of diodes                                                            |

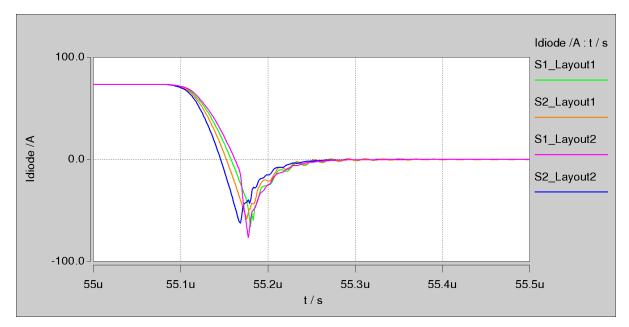

| Figure 6.9. Turn off current of diodes                                                           |

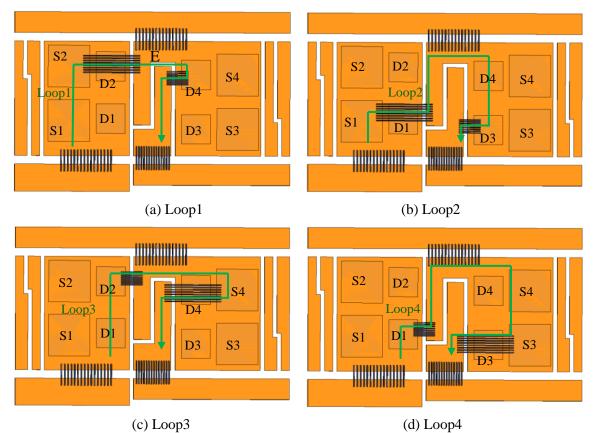

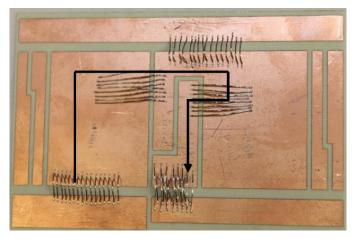

| Figure 6.10. Commutation loops in the conventional layout                                        |

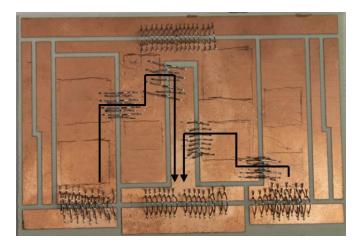

| Figure 6.11. Commutation loops in the proposed layout                                            |

| Figure 6.12. Fabricated commutation loops in the conventional layout                             |

| Figure 6.13. Fabricated commutation loops in the proposed layout                                 |

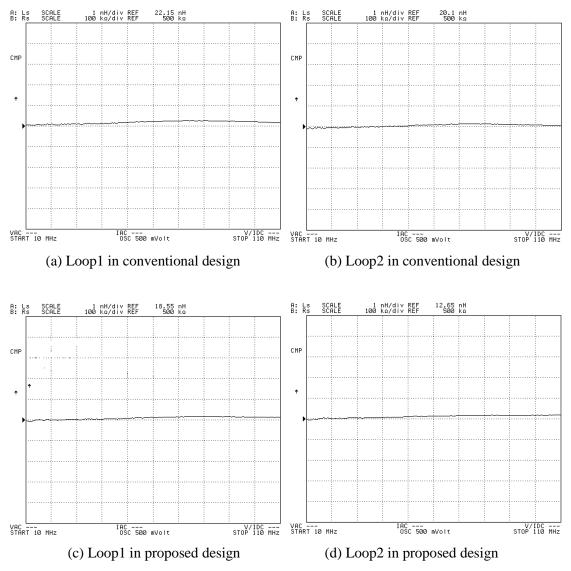

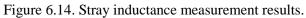

| Figure 6.14. Stray inductance measurement results                                                |

## LIST OF TABLES

| Table 2.1. Properties of Insulating Substrate                                 | 9  |

|-------------------------------------------------------------------------------|----|

| Table 2.2. Maximum Current for Aluminum Wire Size                             | 12 |

| Table 2.3. Summary of Parasitic Inductance in Power Modules                   | 15 |

| Table 2.4. Comparison of Parasitics in Conventional and U-series Power Module | 19 |

| Table 2.5. Summary of Methods to Reduce Inductance                            | 19 |

| Table 3.1. Power Module Components Dimensions                                 | 38 |

| Table 3.2. Power Module Materials                                             | 38 |

| Table 3.3. Simulation Results of the Phase-leg Module Stray Inductance        | 40 |

| Table 4.1. Parameters in Double Pulse Tester                                  | 50 |

| Table 5.1. Stray Inductance Comparison of the Measurement and Simulation      | 61 |

| Table 5.2. Circuit parameters                                                 | 65 |

| Table 5.3 Comparison of measured and calculated inductance.                   | 79 |

| Table 6.1. Test Condition of DPT                                              | 89 |

| Table 6.2. Comparison of the simulation and measurement results.              | 97 |

### **1** Introduction

Power semiconductor modules play a key role in a power electronic system, such as switching mode power supply, motor drive, UPS, and so on. Generally, a power semiconductor module may be defined as a device which contains more than one semiconductor chip and provides an electric path and a heat flux path [1]. The first power semiconductor module was established in the mid seventies of the past century. For the first time, two chips were combined by being soldered together with electrical contacts on metalized ceramic substrates and by being put in a common plastic housing. Power electronic systems became much more compact, cost efficient and reliable, which necessitated advanced device packaging and integration technology. As decades went by, power device and module packaging technology has evolved through multiple generations, each with incremental improvements in performance and reliability. However, the requirements for lower cost, small size, light weight and more reliable power modules have not ceased.

#### 1.1 Background

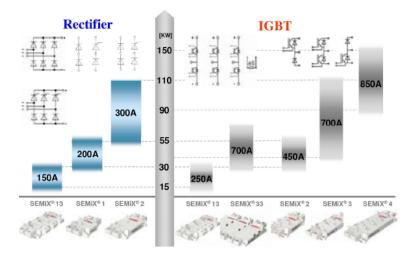

At present, the insulated gate bipolar transistor (IGBT) has become the device of choice for a wide range of industrial power conversion applications because of the superior switching characteristics, low losses, and simple gate drive. IGBTs make up 43% of the power module market [1] with 56% of the IGBT applications being motor drives. Figure 1.1 shows a series of IGBT modules from SEMiX in this application area, it offers rectifiers and IGBTs for 15 kW to 150 kW in a package outline with standard 17 mm terminal height. Another application is traction, which is the highest power condition an IGBT can handle. IGBT modules for traction are shown in Figure 1.2 (Photo of ABB Semiconductors). Intelligent power module (IPM) as shown in Figure 1.3 (Photos of Fairchild Semiconductors, International Rectifier, Mitsubishi Electric) is another popular application area. Moreover, two emerging market segments will be highlighted as well. One is power modules for renewable energy applications, in particular wind power, and the other is automotive applications. Power modules in wind power are basically similar as in traction. However in automotive, thermal behavior is critical because of the vehicle environment, hence the IGBT module packaging is usually of high temperature. As an example, Figure 1.4 shows a commercial automotive module designed by Semikron.

Figure 1.1. SEMiX product family.

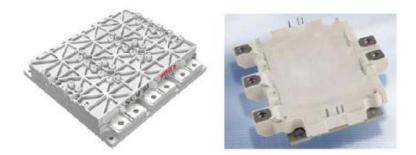

Figure 1.2. 1200 A, 3300 V IGBT module.

Figure 1.3. Fully integrated intelligent power module in single-in-line and dual-in-line housing.

Figure 1.4. SKiM63 (300 A, 1200 V) and HybridPack (400 A, 600 V).

High reliability and long term stability are essential in high power applications. According to [8], a 30-year lifetime, 338,000 long-term cycles, and 12 million short-term temperature changes are required for traction applications. As stated above, IGBTs are being extensively used for relatively high current and high frequency applications. A scenario that is commonly used to explain the IGBT failure is the coefficient of thermal expansion (CTE) mismatch between the silicon and substrate during thermal cycling. Actually, in application, some failures are caused by parasitic effects. One example is the voltage spike during switching, which is a function of total dc loop inductance. It can only be controlled effectively by the gate resistance of the other commutated IGBT at the expense of high turnon loss. After the IGBT fails, it is commonly found, that one or two bonding wires were opened, or the chip surface at the bonding joints is cracked [19].

Excessive overshoot voltage is harmful to the IGBT safe operation area and even causes IGBT destruction. In addition to the voltage spikes, another problem is current ringing due to the resonance of the parasitic inductance in the power module and the parasitic capacitance of the devices. It is a source of electromagnetic interference (EMI) and leads to extra power loss. Last but not the least is the current sharing problem in multichip modules because of the discrepancy of the parasitics.

In order to solve the problems mentioned above to the most extent, it is important to reduce module internal inductance [7]. Much research work has been done to study the parasitics in the power module, basically the parasitic inductance is distributed in the terminal leads, bonding wires and substrate.

#### **1.2 Motivation and Strategy**

As the demand of power rating and switching speed of the power electronics devices increases, the current slope, di/dt, is getting larger, the role of the stray inductance inside the module is more and more important. The objective of this work is to design the packaging layout based on the concepts of two novel switching cells to reduce the stray inductance to the most extent.

The dominant technology in power module packaging will still be wire bond technology. Therefore, this technology is used as the packaging method in this dissertation. Power IGBT modules will be the focus of discussion owing to its rising popularity. However, the results of this work are general and can be used in other types of power devices and package technology as well.

First, the IGBT module will be modeled using electromagnetic field simulation software Q3D Extractor from Ansoft, which is a 3-D and 2-D parasitic extraction software tool for designing printed circuit boards (PCB), electronic packaging, and power electronic

equipment. Specifically, Method of Moments (integral equations) and Finite Element Methods were used to compute capacitance, conductance, inductance, and resistance matrices [9]. With this simulation tool, the design process will be much easier and cost effective, since the parasitics can be studied in detail before the module prototype is fabricated.

After the layout design was done and all the parasitics were extracted, circuit simulation was carried out to characterize the circuit behavior. Synopsys Saber is used as the simulation tool in this case. Saber was a multi-domain modeling and simulation environment that enables full-system virtual prototyping for applications in analog/power electronics, electric power generation/conversion/distribution and mechatronics. Saber has been used for design validation and optimization for automotive, aerospace, and industrial systems [10]. In this work, IGBT turn-on and turn-off behaviors were selected as the index for the electrical evaluation, since the packaging parasitics mainly affect the switching behavior. A double pulse tester (DPT) which is the standard circuit for switching characterization was used in the simulation.

After a clear picture of the parasitics in power modules and the circuit behavior under the module parasitics was obtained from the simulations, real power modules were fabricated and tested. The module internal parasitics were measured and an experimental DPT was built and tested to verify the proposed concept and simulation.

The novel switching cells concept was next extended to the multichip power modules. The same approaches were used to study the effects of the module stray inductance.

#### **1.3 Dissertation Outline**

According to the strategy discussed above, the outline of the dissertation is listed as follows.

Chapter 2 is the literature survey. The dominant packaging technology nowadays, wirebonding technology, is discussed in the beginning. Then the techniques of layout design and other considerations in terms of power module electrical behaviors are reviewed.

Chapter 3 presents the layout design of the power module. This layout design originates from the concepts of P-cell and N-cell. A conventional phase-leg module and the proposed phase-leg module are built in Q3D extractor.

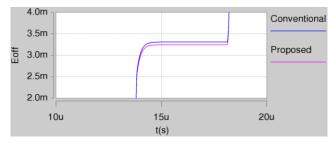

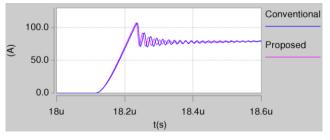

Chapter 4 is the DPT Saber simulation under the extracted parasitics. The turn-on and turn-off overshoot voltages and ringing current are compared for two different packages. Also, analytical modeling and analysis for both turn-on and turn-off is done.

Chapter 5 is the module parasitic measurement and experimental results of DPT.

Chapter 6 discusses stray inductance in modules with paralleled devices. Based on the parasitics extraction and the circuit simulation, both the advantages and disadvantages of the proposed design layout is discussed.

Chapter 7 concludes the work that has been done in the dissertation, summarizes the main contributions and the possible future work.

### 2 Literature Review

Power electronics packaging technology has been developed for several generations, involving material upgrading, structure improvement, and interconnection technique innovation. For instance, in high power situations, a press pack is used to reduce bonding wires and solder attachment. Also, planar technology has gained much interest in certain applications (such as hybrid electric vehicles) since double sided cooling is enabled. In most commercial modules, nevertheless, wire bonding is still the main choice of packaging due to its maturity and reliability.

#### 2.1 Wire Bonding Technology

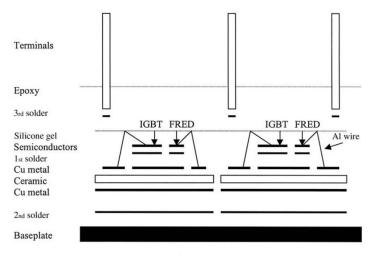

In general, a power module construction is composed of different layers, as shown in Figure 2.1 [11]. The base layer is the baseplate, which is a thick layer of metal used for mechanical fixation and heat transfer. Direct bonded copper (DBC), which consists of two copper layers and one ceramic layer, is soldered on the baseplate. Power semiconductor dice and terminals are then soldered on the top layer of the DBC. Moreover, aluminum wires are used for interconnection of dice and terminals. The module is put in a plastic case. Finally, encapsulant such as silicone gel is filled in the case for protection and insulation. In fact, power module fabrication involves many different processes and techniques, and several key factors of them will be discussed in detail in this chapter.

#### 2.1.1 Material Selection

The materials involved in a power module design cover a wide range from insulators, conductors, and semiconductors to organics. Since these materials behave differently under

various environmental, electrical, and thermal conditions, proper selection of these materials and the assembly processes are critical.

#### A. Substrate selection

Substrate as shown in Figure 2.1 is one of the most important parts in a power module. Typically, there are three layers for the substrate, i.e., two conduction layers and an insulation layer in between. Specially, the top metal layer is the printed circuit of the power module. The insulation layer serves as the supporting structure for the circuitry [12]. This layer is mechanically a base to support all active and passive chip components, and electrically an insulator to isolate various conductive paths of the circuit. The bottom metal layer is for thermal expansion balancing.

Figure 2.1. Structure of an IGBT power module.

Two commonly used materials for the substrate are Aluminum Nitride (AlN) and Alumina ( $Al_2O_3$ ). The properties of concern are listed in Table 2.1.

| Material   |                                                                     | Al <sub>2</sub> O <sub>3</sub> (96%) | Al <sub>2</sub> O <sub>3</sub> (99%) | AlN                    |

|------------|---------------------------------------------------------------------|--------------------------------------|--------------------------------------|------------------------|

| Electrical | Electrical     Resistivity (W-cm)       Dielectric Strength (kV/mm) |                                      | > 10 <sup>14</sup>                   | > 10 <sup>14</sup>     |

|            |                                                                     |                                      | 12                                   | 15                     |

|            | Dielectric Constant at 1 MHz                                        | 9.2                                  | 9.9                                  | 8.9                    |

| Thermal    | Thermal conductivity (W/m °K)                                       | 24                                   | 33                                   | 150-180                |

|            | CTE (ppm/°C)                                                        | 6.0                                  | 7.2                                  | 4.6                    |

|            | Heat Capacity (J/kg-°C)                                             | 765                                  | 765                                  | 745                    |

|            | Maximum Use Temperature (°C)                                        | 1600                                 | 1600                                 | >1000                  |

|            | Melting Point (°C)                                                  | 2323                                 | 2323                                 | 2677                   |

| Mechanical | Tensile Strength (MPa)                                              | 127.4                                | 206.9                                | 310                    |

|            | Flexural Strength (MPa)                                             | 317                                  | 345                                  | 360                    |

|            | Density (kg/m <sup>3</sup> )                                        |                                      | 3970                                 | 3260                   |

|            | Elastic Modulus (GPa)                                               |                                      | 345                                  | 310                    |

|            | Hardness                                                            | 2000K                                | 9MH                                  | 1200K                  |

|            | Surface Finish (µm)                                                 | 1.0                                  | 1.0                                  | 1.0                    |

| Others     | Metalizability                                                      | All, except thin film                | All                                  | All, except thick film |

|            | Machine ability                                                     | Good                                 | Good                                 | Good                   |

|            | Relative cost                                                       | 1                                    | 2                                    | 4                      |

Table 2.1. Properties of Insulating Substrate

The top and bottom metallization also have some requirements for power electronics application. Some of the key requirements are listed below [11]:

- High thermal conductivity (> 200 W/k-m).

- -High current density.

- Strong adhesion to the substrate.

- Photoetchable.

According to the requirements above, DBC becomes the most popular choice for the

substrate. DBC technology uses a high-temperature process to achieve an intimate bond between the copper and the ceramic. There is no solder or any other catalyst used in the interface between the copper and the ceramic surface. Here, the combination of copper and ceramic is heated to a temperature of about 1070°C which is slightly below copper's melting point, in a nitrogen atmosphere. At this temperature, the copper oxide forms a eutectic melt that wets and, when cool, produces a strong bond between copper and ceramic. Copper thickness is typically 8 to 20 mils.

#### B. Bonding material

Besides substrate, bonding materials also play a key role in a power module. It provides the vital functions of mechanical, thermal, and electrical linkages between the power semiconductor chips, the terminals, the insulating substrates, and the metal base plate. Therefore, bonding must be properly designed to ensure that the power IGBT module is a mechanically reliable and thermally efficient system.

Solder becomes the bonding choice after comparing with other materials such as epoxy and silver filled glass. Solders are essentially alloys of two or more metals. When these metals are alloyed together, the melting point of the alloy can be considerably less than the melting point of either of the individual starting metals (a phenomenon which makes the soldering process possible). In the soldering process, the solder is placed between two metal surfaces to be soldered. During melting, the molten solder dissolves a portion of these two surfaces and, when the solder cools, a junction or solder joint is formed, joining the two metal surfaces.

Selection of the solder alloys is based on the following criteria [13]:

• Melting temperature range in relation to service temperatures. Due to the CTE mismatch between the power chip, the insulating substrate, and the metal base plate, the processing temperature of the solder should be as low as possible and is preferred to be at or below 350°C. This processing or soldering temperature is typically 20 °C to 40°C above the solder melting temperature. Usually, Tj of the IGBT chip can be as high as 150°C. Thus, the solder melting temperature must be at least 10°C higher to prevent any remelting.

– Processing restrictions. Usually, the power chips are first attached to the insulating substrate using a high temperature solder. The insulating substrate is then attached to the metal baseplate with a lower-temperature solder to avoid remelting of the first solder. This is done so that the two solder attachments can be optimized independently. These two soldering temperatures should be at least 40°C apart. According to this, the melting temperature ranges for the two solders should be as follows: first solder - 200°C to 310°C, and second solder - 160°C to 270°C.

• Availability. The solder should be available in both preform and paste form.

• Compatibility with the metallization of the power chips, the insulating substrate, and the metal baseplate.

Also, the criteria include high mechanical strength, low elasticity, high-creep, highfatigue resistance and so on.

The most commonly used alloy systems in semiconductor assembly are:

- Gold/Tin hard solder

- Tin/lead soft solder

#### C. Power interconnection material

The interconnection part in a power module is bonding wires that are used between the top aluminum metallization of the IGBT/Free-wheel diode (FWD) surface and the electroplated substrate, and terminal leads, which are used to connect to outside circuit.

Aluminum wire is preferred for wire bonding because of its low electrical resistivity, reliable attachment to the chip metallization surface and substrate, and also its affordable price. The standards for aluminum wire selection is listed in Table 2.2.

| Material           | Diameter | Maximum Current (A) |            |

|--------------------|----------|---------------------|------------|

|                    | (Inch)   | L < 0.040"          | L > 0.040" |

| Aluminum (Al/1%Mg) | 0.001    | 0.7                 | 0.5        |

|                    | 0.002    | 2.0                 | 1.4        |

|                    | 0.005    | 7.8                 | 5.4        |

|                    | 0.008    | 15.7                | 10.9       |

|                    | 0.012    | 28.9                | 20.0       |

|                    | 0.015    | 40.4                | 28.0       |

|                    | 0.022    | 71.8                | 49.6       |

Table 2.2. Maximum Current for Aluminum Wire Size

In terms of terminal connections, the requirements for this material are high conductivity, high mechanical strength, and elasticity for molding and so on. Copper based alloys such as beryllium/copper (BeCu, C170, C172) and phosphor/bronze, are commonly used because of the property of low resistivity, high tensile strength, ease of fabrication and reshape, high fatigue endurance and wear resistance. The terminals are formed by soldering to the substrate or by integrating into the case, and connect to the chip or substrate using aluminum wires.

#### 2.1.2 Fabrication Process

The procedures of the fabrication process include cleaning the devices, soldering, wire bonding and encapsulating. This session reviews the major techniques: soldering and wire bonding.

#### Devices and terminals soldering

As mentioned briefly earlier, the common method for component attachment in IGBT module assembly is a two-solder process. First, power chips will be soldered to the substrate using the first solder. After the chips are put at the correct position on the substrate with the solder preform, the assembly is moved automatically onto the conveyer belt of the reflow oven for soldering. Ceramic substrate, power terminal and connecting bridge attachments are usually done manually by using a graphite fixture or a graphite fixture with alignment sheets. A graphite fixture is in the shape of a block with detachable parts for the placement of base plate, ceramic substrate terminals, and bridges. Solder can be either screen-printed or dispensed onto the baseplate and ceramic substrate. For graphite fixture with alignment sheets, it is a flat graphite plate about 10 mm thick with guided pins that are in line with the mounting holes of the baseplate and the sheets. The sheets or frames are metallic, usually stainless steel of 1 to 4 mm thick, and have windows etched out for the placement of different components. The guided pins are designed with stops to control the height of these sheets above the base plate.

The second solder is for attaching the terminals/connecting bridges to the ceramic substrate and the ceramic substrate to the metal base plate. Generally, the first solder has a melting temperature of about 25°C to 40°C higher than the second solder [11].

#### Ultrasonic wire bonding

After the solder attachment is finished, the interconnection inside the module will be done using wire bonding. A bonding machine and aluminum wires are involved in this process. During bonding, the wedge presses the wire against the metal termination pad, and ultrasonic energy (usually 20 to 60 kHz) is applied to the wedge. The wire is rubbed against the contact, causing local heating and a metallurgical weld. The thin oxide coating on the aluminum wire is ruptured, and the oxide tends to help the friction heating process, giving a very reliable bond.

#### 2.2 Study on Parasitics Induced by Packaging

Parasitic inductance exists from the IGBT chip collector and emitter to their terminal connections, no matter what kind of packaging technique is used. The parasitic inductance stores energy whenever the current flows through the interconnections inside the module when the IGBT is on. When it turns off, the energy is released directly as a voltage spike if there is no external snubber capacitor in the current loop. This spike is a function of inductance and di/dt rate. Even with careful layout of the power stage, a snubber capacitor is usually needed to absorb this energy. If the snubber loop equivalent series resistance (ESR) is small, a high oscillatory current is produced. If the ESR is large, the current waveform is improved, at the expense of circuit loss and heating. Although the IGBT is designed to remove the conventional heavy-duty snubbers such as resistor-capacitor-diode, it cannot survive without some form of snubber circuit in most applications. How to deal with the parasitics effect will ultimately affect the EMI, efficiency, and performance of the converter [19]. In the design and layout of IGBT packages and power stages with both high switching speed and high power handling requirements, reducing parasitics is extremely important.

The package stray inductance can be classified into three categories, as follows [6]:

- 1. Inductance due to DBC substrate pattern;

- 2. Inductance due to bonding wires;

- 3. Inductance of electrode.

The substrate inductance is the smallest among the three. The inductance in the bonding wires depends on the length. Usually, the length of wire is minimized and hence the induced inductance is not a big concern. The terminal conductors have a relatively large dimension, thus the largest inductance exists in this part. Table 2.3 lists the parasitics in a 300 A 1200 V commercial power module [19], which provides a rough idea of the scale and how the parasitics are distributed in a power module.

Table 2.3. Summary of Parasitic Inductance in Power Modules

|                      | Bonding<br>wire | Emitter conductor<br>trace | Collector conductor<br>trace | Terminal conductors |

|----------------------|-----------------|----------------------------|------------------------------|---------------------|

| Parasitic inductance | 10-15 nH        | 5-7 nH                     | 4-5 nH                       | 30-40 nH            |

Although the stray inductance induced by the bonding wires is not the biggest concern in the module parasitics, there is a special issue with the paralleling of the wires. Table 2.2 shows the current capabilities of the different aluminum wires. 12 mil and 15 mil diameter wires are most commonly used for IGBT modules. Very often, the length of the wire connection is longer than 40 mils. Therefore the current capability of a single wire is 20 A for 12 mil wire and 28 A for 15 mil wire. A single IGBT die can have current capability up to 300 A. Considering no overload margin, twenty 15 mil thick wires are needed to parallel for a 300 A IGBT. The paralleling of the bonding wires can cause the following problems [19]:

1. Proximity Effects between Bonding Wires

In the transients where the current rises and falls quickly, the equivalent high frequency contents are concentrated. At this moment, the mutual coupling effect between the paralleled wires become so significant that the wires in the edge appear as a low impedance path compared to the middle wires. Those wires carry more current than the others. Meanwhile, because of the non-uniform bonding wires on the chip, the steady state current distribution is affected. This can possibly load the IGBT cells inside the silicon differently. The current distribution in different wires during transient is illustrated in [19]. The turn on current overshoot in the wire in the edge can be as large as three times of that in the middle wire.

#### 2. Mechanical Stress on Bonding Wires

It is known that a magnetic force will be generated on a conductor carrying current when it is exposed to a magnetic field. The force generated on a particular wire can be regarded as:

$$f_{\rm i} = {\rm B}i_{\rm i}L_{\rm i}$$

where,  $i_i$  and  $L_i$ , are the current and the length of the i-th wire, and B is the magnetic flux density at that position The magnetic flux density is the sum of the flux density generated by all the other bonding wires, if we assume that the wires are perfectly in parallel, and its length is much longer compared to their distance. The flux density contributed by wire *k* to *i* can be written as:

$$B_{i,k} = i_k \mu_0 / (2\pi \delta_{i,k})$$

where  $\delta_{i,k}$  is the distance between the two wises,  $i_k$  is the current magnitude in wire k. With this simplified model, the magnetic force generated on the bonding wires can be simulated. The amplitude of the stress applied to the bonding wires may not be a significant number. But under temperature change and power cycling, with this repetitive switching frequency lateral force, there is a bonding fatigue mechanism as the wires try to peel the metallization off the chip surface, which can increase the on-voltage drop of the device. This explains why the wire-bond modules are more fragile under large repetitive transient current.

High reliability and long term stability are essential in high power applications. Therefore, reducing package stray inductance is an important issue. There are several considerations and improvements in the structure of the package to reduce the parasitics of the module. They are discussed as follows:

#### 1. Terminal arrangement

As stated previously, in a power module the dominant stray inductance is the terminal. Several methods were proposed to reduce this stray inductance. For example, a laminated structure has smaller self inductance. Also, when paralleling the positive and negative terminals, it enables the coupling of the two inductors to the most extent. Theoretically, the equivalent loop inductance equals the two self-inductances minus the mutual inductance. A larger mutual inductance will give smaller total equivalent loop inductance. Therefore, when designing the terminals, the best way is to put two parallel laminated bus bars as close as possible.

#### 2. Bond wires consideration

First, the interconnection of bond wires should be as short as possible. Second, the direction of substrate current, which flows under the emitter bonding wires, is designed to be opposite to the direction of current flow in bonding wires. This wiring construction on the substrate is also achievable by employing multi-layered DBC technology. Consequently, the

bonding wires effect on the module internal inductance can become practically negligible.

#### 3. Utilizing the substrate area

Although the substrate has the smallest inductance, large substrate area can still make the inductance considerably large. It is especially true for high power modules because the paralleling of the power devices enlarges the substrate area. To accommodate the bonding wire connection, the substrate area has to be larger than the footprint of the semiconductor dice. When doing the substrate layout, maximum utilization of the full substrate area should be done.

#### 4. The "U-package" technology [6]

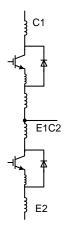

Mitsubishi made a major improvement on the bus bar structure in the sense of reduced stray inductance in 1996. Specifically, the bus bars are molded into the sides of the case, aluminum wires are used to connect the substrate or die to the terminal. Paralleling the main electrodes and narrowing the space are easily made. The distance between both electrodes can be reduced to benefit from the eddy current effect. This also relieves "S" bends that are needed in the electrodes of conventional modules. Elimination of these "S" bends helped to further reduce the electrode inductance. Overall, as a result of these inductance reducing features, the new package has about one third the inductance of conventional modules. Table 2.4 shows the package inductance comparison between conventional and the new concept of U series.

Figure 2.2 Package inductance

Table 2.4. Comparison of Parasitics in Conventional and U-series Power Module

| Inductance between terminals | Conventional | U series |

|------------------------------|--------------|----------|

| C1-E1C2                      | 51           | 17       |

| E1C2-E2                      | 34           | 24       |

| C1-E2                        | 58           | 16       |

For ease of reference, some general rules to reduce the parasitic inductance are summarized in Table 2.5 [6].

| Classification          | Inductance reduction methods                                                     |

|-------------------------|----------------------------------------------------------------------------------|

| DBC substrate pattern   | 1. Widen the pattern width                                                       |

|                         | 2. Shorten the pattern length                                                    |

| Bonding wires           | 1. Shorten the wire length                                                       |

|                         | 2. Increase the number of Al-wires                                               |

|                         | 3. Increase the diameter of the wires                                            |

| Inductance of electrode | 1. Shorten the length                                                            |

|                         | 2. Increase the width                                                            |

|                         | 3. Parallel the main electrodes and reduce the space between the main electrodes |

|                         | 4. Use eddy current effect                                                       |

Table 2.5. Summary of Methods to Reduce Inductance

People are making every effort to reduce the stray inductance inside the module. However, one important issue has been neglected, i.e., the effective stray inductance while the module is operating. Actually, the stray inductance is everywhere in a module, the focus is that in the conduction path during switching on and switching off. The following chapter will introduce concepts of two basic switching cells in power converters, reveal the mechanism of how the switching cell works as a functional unit, and show how it can affect power module packaging.

### 3 Layout Design of IGBT Phase-leg Module

As the basic elements, switching devices (mainly MOSFET and IGBT) and diodes along with inductors and capacitors are used in power electronic circuits to perform dc-dc, dc-ac, and ac-ac power conversion. In a piece-wise fashion, many circuits have been invented, proposed, and demonstrated to perform these power conversion uses [20]. The classical dcdc converters like buck, boost, buck-boost and Ćuk converters are used in various applications, and the modeling of these various structures is very important to design the control circuits for these converters [20]-[28]. However, these circuits have rarely been examined and investigated in terms of their relationships, topological characteristics and their basic building blocks. After examining the basic building blocks of these dc-dc converters and dc-ac inverters, two basic switching cells are proposed [29].

These basic switching cells function as the fundamental elements in power electronic circuits, which cannot be further broken down or apart and should be used as the basis for manufacturing/layout of single, dual, and 6-pack modules that semiconductor manufacturers are producing. Actually, existing well-known circuits can easily be represented and configured from the basic switching cells. Moreover, some new conversion topologies can be derived by rearrangement of basic switching cells.

#### 3.1 Introduction of P-cell and N-cell

#### 3.1.1 Definition of P-cell and N-cell

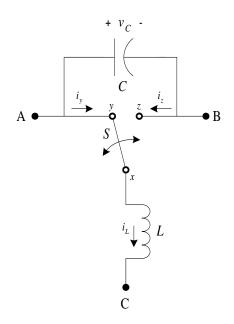

The introduction of the switching cell concept started with the canonical cell [31][32], where an inductor, a capacitor, and a single-pole double throw switch form a basic canonical

switching cell as shown in Figure 3.1. This cell has three terminals A, B and C, and each of them can be used as an input/output/common terminal. For instance, if terminal A is used as an input, B as an output and C as the common terminal, the canonical circuit forms one type of dc-dc converter. Six different combinations can be formed by changing the function of the three terminals for different combinations [20]. Among these six combinations, only three distinct effective circuits are found whereas the others are functionally the same. Thus, using these three combinations, the buck, boost and buck-boost converters can be formed.

Figure 3.1. Basic canonical cell.

Besides the canonical switching cell, there are many reported methods of modeling power electronic converters out of some switching modules or blocks. According to [32], the classical converters can be grouped into two major converter families - buck converter and boost converter. The buck family converters' small signal models can be expressed in terms of h-parameters, while those for the boost families are expressed by g-parameters. When a unity feedback is applied in the buck converter, the buck-boost converter is obtained. Using the technique presented in [33], the classical PWM converters can be represented by only the buck and boost converter connected in cascaded arrangement. This method is reported as the graft scheme, which presents a unified and systematic method to synthesize and model transformer-less PWM dc-dc converters. To do that, 4 different basic unit cells were presented where the cells are made from two transistors. Then using the graft scheme, the diode-transistor realization of those 4 cells was derived.

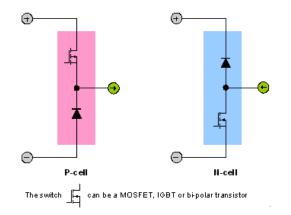

Figure 3.2 shows the two basic switching cells defined in this paper. Each cell consists of one switching device (a MOSFET or IGBT) and one diode connected to three terminals: (+), (-), and ( $\rightarrow$ ) /or ( $\leftarrow$ ). Each cell has a common terminal which is shown as ( $\rightarrow$ ) /or ( $\leftarrow$ ) on the schematic. For the P-cell, this common terminal is connected to the positive terminal of a current source or an inductor. For the N-cell, this common terminal is connected to the negative of a current-source or an inductor. The active switching device in a P-cell is connected between the (+) and common terminal, whereas in an N-cell, the switching device is connected between the (-) terminal and the common terminal. Thus, the P-cell is essentially the mirror circuit of the N-cell and vice versa [29][30].

The aforementioned basic switching cells are the practical implementation of the canonical switching cell found in [20]. Although the switching cells have only two components, they can be connected in different combinations to create various power electronic circuits.

Figure 3.2. Two basic switching cells: P-cell and N-cell.

#### 3.1.2 DC-DC Converters Constructed from P-cell and N-cell

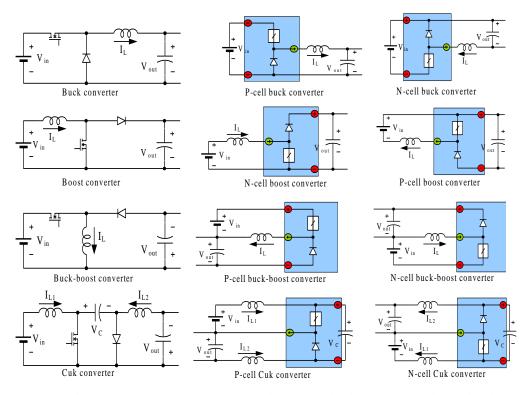

Figure 3.3 summarizes the four classical converters and their cell structures. In Figure 3.3, there are three columns and each column has 4 figures. The figures in the left most column show the four major classical converters. These converters are made from inductors, capacitors, diodes and controlled switches. Each of these conventional converters can be expressed using the basic switching cells and the corresponding circuits are summarized in the middle column. The converters in this column are made from either N-cell or P-cell. Thus it is seen that except the boost converter, all of the conventional converters have an inherent P-cell structure where the active switching element is connected to the positive power supply terminal. The conventional boost converter is inherently an N-cell boost converter.

Theoretically, all of these classical converters also have a mirror circuit representation. When the P-cell in a buck converter is replaced with an N-cell, the circuit takes a different configuration. In this way, the classical boost converter can be re-constructed using a P-cell, rather than an N-cell. The buck and boost converters can be easily decomposed into a P-cell and N-cell based circuit, respectively. However, this procedure is not so obvious for the buck-boost and Ćuk (boost-buck) converters; they inherently take the P-cell structure. The mirror circuit representation of each dc-dc converter is shown in the rightmost column of Figure 3.3.

(a) Classical dc-dc converters, (b) Formation by the basic cells, (c) Mirror circuits. Figure 3.3. Four classic DC-DC converters and their P-cell and N-cell representation

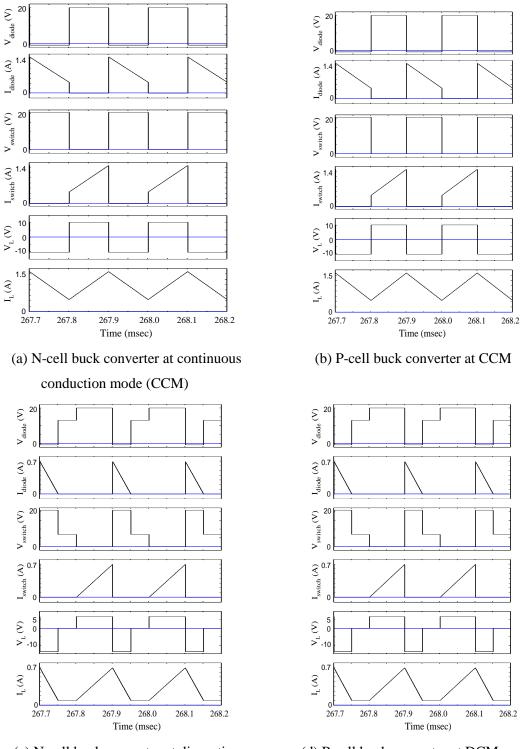

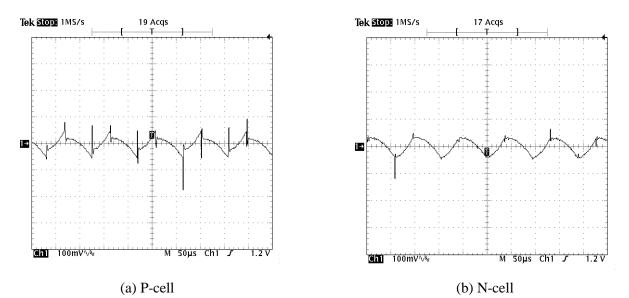

To validate the concept of the P-cell and N-cell mirror relationship, a buck converter was simulated and tested under continuous and discontinuous conduction mode. The simulations were done in PSIM, and the results are shown in Figure 3.4. Actually, there was no difference found in the simulation results, implying that there is a mirror relationship between the N-cell and P-cell structures. Then for further verification, a pair of buck converters (one P-cell and one N-cell) were constructed from discrete components and tested in the lab in continuous conduction mode. The operating and loading conditions of the N-cell buck converter and the P-cell circuit were the same, but some minor differences were observed in their output voltage. The test results are shown in Figure 3.5.

(c) N-cell buck converter at discontinuous conduction mode (DCM)

(d) P-cell buck converter at DCM

Figure 3.4. Simulation results for P-cell and N-cell buck converter.

The parameters of the test setup are as follows:  $V_{in} = 20$  V, D = 0.4,  $f_S = 10$  kHz,  $C_1 =$

100  $\mu$ F,  $L_1 = 1$  mH,  $D_1 =$  MURB1020CT-1,  $S_1 =$  IRG4BC30U and  $R_L = 20 \Omega$ .

For an input voltage of 20 V and duty cycle of 0.4, the dc output voltage for the N-cell structure was 6.82 V and for the P-cell buck converter, it was 7.07 V. Figure 3.5 (a) and (b) show the output ripple components of the P-cell and N-cell structures respectively. The fundamental frequency component present in the ripple was the same for both topologies. However, the N-cell structure produces a cleaner output because of the ground-referenced gate drive circuit.

Figure 3.5. Experimental output voltage ripple (100mV/div) of buck converter.

The conventional Ćuk converter has an especially unique structure [23]. A Ćuk converter has continuous input and output current, and the energy is transferred from the input to the output side by means of a capacitor. The classical Ćuk converter has an inherent P-cell structure, and the N-cell Ćuk converter can also be achieved. A Ćuk converter is shown in Figure 3.3 (a), and the switching cell realization is shown in Figure 3.3 (b). The main limitation of the Ćuk converter is that it uses one additional inductor and capacitor. However, simplification can be done using the basic switching cells and a new version of

Ćuk converter can be obtained. In Figure 3.3 (a), during the time when  $S_1$  is on, the rate of change of currents in  $L_1$  and  $L_2$  is the following [34]:

$$dI_{Ll}/dt = V_{in}/L_l \tag{1}$$

$$dI_{L2}/dt = \left[-V_{out} - (-V_C)\right]/L_2 = \left(V_C - V_{out}\right)/L_2$$

(2)

where

$$V_{out} = (t_{on} / t_{off})V_{in}$$

(3)

and

$$V_C = (T / t_{off}) V_{in} \tag{4}$$

Inserting (4) into (2), we get

$$dI_{L2} / dt = (1 / L_2)[(TV_{in} - t_{on}V_{in}) / t_{off}] = V_{in} / L_2$$

(5)

Using the same procedure, the rate of change of currents in  $L_1$  and  $L_2$  can be found while  $S_1$  is off. Specifically, when  $S_1$  is off,

$$dI_{L1} / dt = -(1 / L_1)(t_{on} / t_{off})V_{in}$$

(6)

$$dI_{L2} / dt = -(1 / L_2)(t_{on} / t_{off})V_{in}$$

<sup>(7)</sup>

Thus, from (1) and (5) - (7), it is concluded that if  $L_1 = L_2$ , the rate of change of currents in  $L_1$  and  $L_2$  are the same. Moreover,

$$I_{L1(avg)} / I_{L2(avg)} = I_{in} / I_{out} = D / (1 - D)$$

(8)

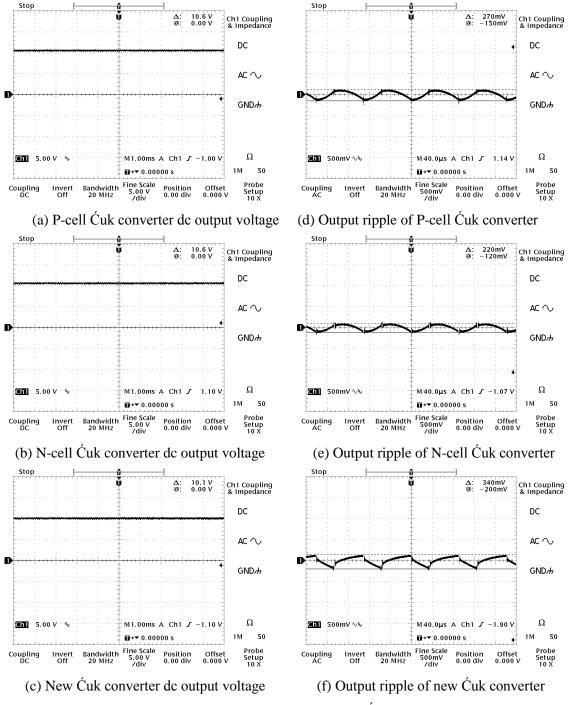

From (8), it is found that, for a specific case when the duty ratio D is 0.5, both inductors will have the same average value of current. If  $L_1 = L_2$ , they will have the same current slope. Hence, the two inductors can be equivalently moved to the center rail and consolidated into one inductor. If the converter is not operating at D = 0.5 or if  $L_1 \neq L_2$ , there will be a current mismatch between  $L_1$  and  $L_2$ , and the new Ćuk converter configuration will perform slightly differently from the original Ćuk converter. Figure 3.6 shows the output voltages of these converters for a 20  $\Omega$  resistive load with a supply voltage of 20 V. The duty cycle of the gate drive was kept at approximately 0.33, and for this duty cycle, the output voltage of a Ćuk converter should be around 10 V. In Figure 3.6 (d) - (f), the output ac ripple is shown by zooming the dc output voltage.

Figure 3.6 shows that these three converters are fairly equivalent. For the same duty cycle, the P-cell and the N-cell structures produce a 10.6 V dc output, while the new combined inductor topology produces 10.1 V dc output. These are shown in Figure 3.6 (a), (b) and (c) respectively. The ripple component in the N-cell circuit has the lowest amplitude of 220 mVp-p, compared to the P-cell structure producing 270 mVp-p. However, the new topology with the two combined inductors produces a ripple of 340 mVp-p, which is slightly higher than the other two topologies. Figure 3.6 (d)-(f) show the ripple components in the three configurations.

Figure 3.6. Experimental output voltage of Ćuk converters.

## 3.1.3 Constructing Voltage Source Inverters from the P-cell and N-cell

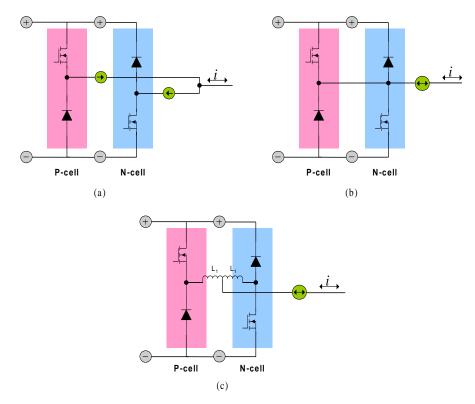

Like the dc-dc converters, inverters can be constructed by the use of basic cells in a similar way. Figure 3.7 (a) shows that the parallel combination of the P- and N- cells creates

a phase-leg providing bi-directional current flow. Figure 3.7 (b) shows the conventional antiparallel diode/transistor configuration to create a bi-directional current flow. The parallel connection of a P-cell and an N-cell shown in Figure 3.7 (a) has some distinct advantages over the conventional IGBT with an anti-parallel diode.

Figure 3.7. Topologies of phase-legs: (a) An inverter phase-leg with bidirectional current flow by paralleling the P- and N-cells, (b) Conventional connection of anti-parallel diode, (c) Placing two inductors between P-cell and N-cell common terminals to control the current.

To create a bi-directional current port in a VSI, two transistors in a phase-leg are switched periodically. However, there is a requirement of dead time between the switching periods of the two transistors that prevents a short circuit of the dc link. When an inductor is placed in the paralleled P-cell and N-cell configuration, it takes the shape of Figure 3.7 (c). In this case, a dead time is not required because the additional inductor and the stray inductance of the interconnections limit the current if there is any overlap in the switching of the P-cell and N-cell devices. Therefore, IGBT-diode modules configured as the P- and N-cell are

better suited for inverter operation, and at any instant of time, the load current only goes through the P-cell during the positive half cycle and through the N-cell during the negative half cycle of the current. Moreover, for a modulation scheme that can detect the direction of current to the load, only the switch that provides the current path needs to be switched while the other can be kept off. In the VSI circuit shown in Figure 3.7 (b), when the current is going to the load, the transistor in the P-cell is switched on and the transistor in the N-cell is kept off. In the voice with the current is coming back from the load, it flows through the transistor in the N-cell which is switched on, and the transistor in the P-cell is kept off.

The basic switching cell concept creates a new vision to analyze the conventional power electronic converters by segregating them into smaller modular blocks. This modeling approach is not limited to the use of basic switching cells for analysis of existing power electronic circuits. Rather, it is a means to find different modular patterns in power electronic circuits, which can lead to several new circuit topologies.

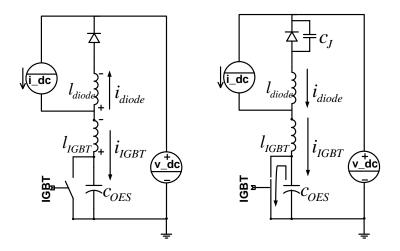

## 3.2 Package Layout Design Using the Novel Switching Cells

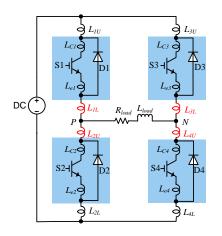

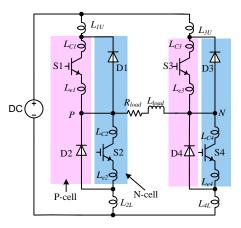

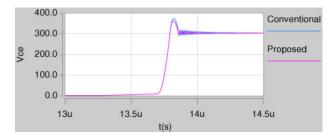

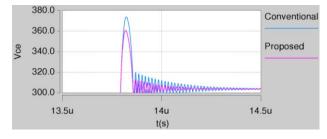

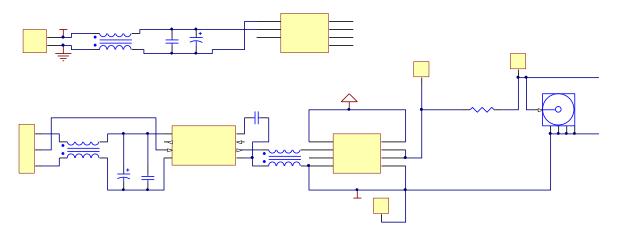

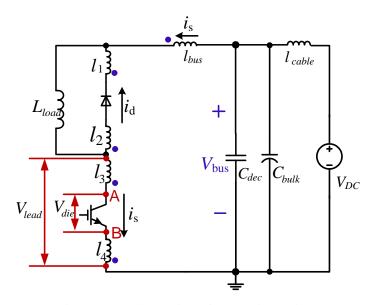

As discussed above, a P-cell and a N-cell can construct a phase-leg that has some benefits compared to the traditional anti-parallel phase-leg. Figure 3.8 shows the diagrams of the two different inverter configurations, one uses conventional phase-leg while the other uses P-cell and N-cell phase-leg. Under inductive load condition, current commutation is between  $S_1$  and  $D_2$  as shown in Figure 3.8(a) when current direction is from load terminal P to N, or between  $S_2$  and  $D_1$  when current is from N to P. Therefore, in terms of natural current commutation pass, it is more reasonable to construct a phase-leg by P-cell and N-cell, as shown in Figure 3.8(b). Load current flows into the phase-leg through an N-cell and goes out of the phase-leg through a P-cell. Figure 3.8 also shows the stray inductance within each phase-leg module. This stray inductance model is referred from [37].  $L_{1U}$  and  $L_{2L}$  are introduced by terminal leads;  $L_{1L}$  and  $L_{2U}$  are the stray inductors of internal bus connecting the upper and lower unit; the values of these four inductors are relatively large.  $L_{C1}$ ,  $L_{e1}$ ,  $L_{C2}$ and  $L_{e2}$ , are associated with the die and wire bond, which are relatively small. Since the physical distance between the two commutating devices is reduced, the inductance is thus reduced. Comparing Figure 3.8 (a) and (b), inductances  $L_{1L}$  and  $L_{2U}$  introduced by the internal bus for the left phase-leg are reduced in the cell structure.

(a) Conventional full bridge inverter Figure 3.8. Full bridge inverter with package parasitics.

(b) Proposed phase-leg

The switching cells are the basic building blocks of almost all power electronics converters in terms of topology characteristic and operating unit, and they should be used as

the base for manufacturing layout of single, dual and 6-pack modules that semiconductor

manufacturers are produce.

Building power modules and verifying the concept proposed in last section are extremely expensive and time consuming. However, this process can be simplified by the aid of simulation. Also, modifying and optimization of the design can be carried out. Ansoft Q3D Extractor is used to do this job. The software uses Method of Moments (integral equations) and Finite Element Method to compute capacitance, conductance, inductance and resistance matrices. Providing the correct dimensions, material properties (resistivity of conductors and permittivity of insulators) and boundary conditions (the conductors and current paths), the software can extract the structural impedances of any arbitrary geometry. Thus, the module parasitics can be understood thoroughly before modules are fabricated.

#### 3.2.1 Electromagnetic Simulation Methodology

Q3D Extractor is software from Ansoft. It conducts electromagnetic field simulation employing a combination of the finite element method and the method of moments. In general, the finite element method divides the full problem space into smaller regions (tetrahedral elements) and represents the field in each sub-region with a local function. The method of moments divides the surface (or volumes) of conductors and dielectrics into many triangular (or tetrahedral) elements to represent the charges and currents present [38].

A finite element solver stores the value of a field quantity (such as electric potential) at each mesh node of a triangular or tetrahedral element. Inside each element, the field is interpolated from the values stored at the mesh nodes using local finite element basis functions. Maxwell's partial differential equations of the field quantities are linearized and can be transformed into a sparse matrix of linear algebraic equations that can be solved using traditional direct or iterative numerical methods. In the method of moments, field quantities are also interpolated over elements, but typically with simpler basis functions than in the finite element method. For capacitance problems, the field quantity of interest is the charge density on the surface of a conductor or dielectric interface. Triangular elements are used, and the charge density is approximated with a piecewise-constant basis function. For inductance problems, the field quantity is a vector (current density), and again piecewiseconstant basis functions are used. For DC inductance problems, the elements are tetrahedra (volume currents), and for AC inductance problems the elements are triangles (surface currents.) Green's function is used to represent the electrical interaction between any pair of elements. Using integrals of the Green's function and the basic functions, a dense matrix of linear equations is derived. An iterative method is used solve large problems.

The procedures of conducting the simulation are described in the following subsection.

#### 3.2.2 Layout Design Using Q3D Extractor

#### A. Build the three dimensional model of the power device module and specify material

The three dimensional model can be drawn in Q3D Extractor or imported from other software, such as Auto CAD or Protel. Any of the following formats can be opened and edited: 3D Modeler file (\*.sm3), SAT file (\*.sat), STEP file (\*.step,\*. stp), IGES file (\*.iges, \*.igs) and ProE files (\*.prt, \*.asm) in Q3D Extractor.

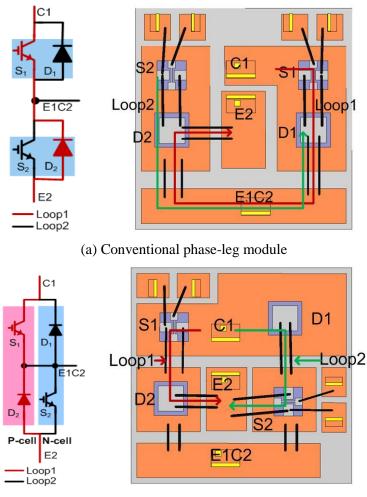

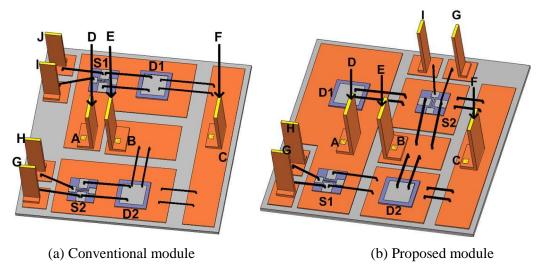

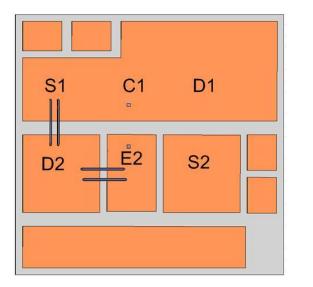

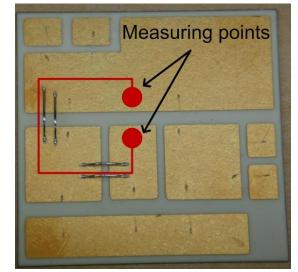

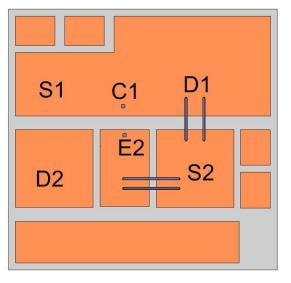

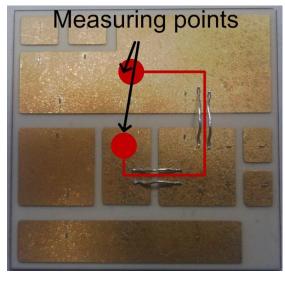

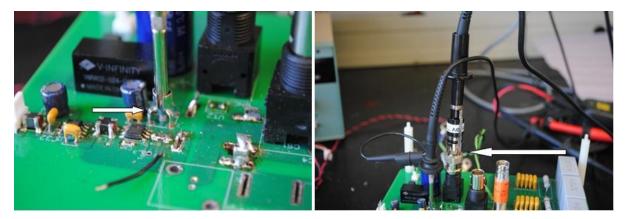

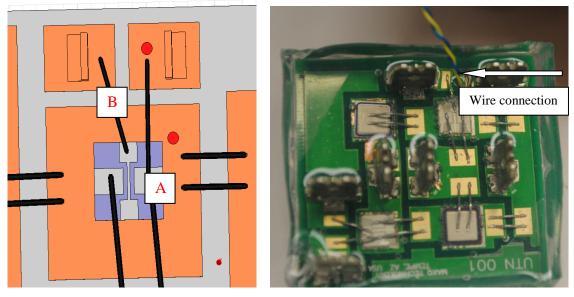

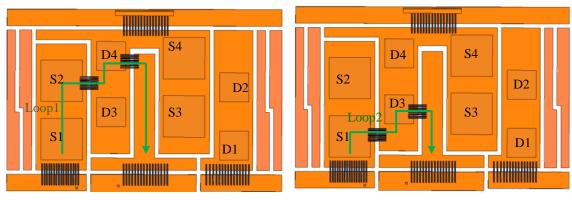

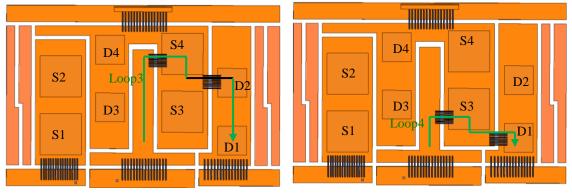

The proposed phase-leg and the conventional phase-leg are drawn using Q3D Extractor. The diagrams of the phase-legs are shown in Figure 3.9, the marked loop1 and loop 2 are two current commutation loops in a phase-leg, that is, from upper IGBT to lower diode and from lower IGBT to upper diode. In a conventional module, the upper leg devices  $S_1$  and  $D_1$  are seated at one side, while the lower leg, namely  $S_2$  and  $D_2$  are seated at the other side. The layout designs are shown in Figure 3.9. The purpose here is to compare the stray inductance in the modules, therefore the base plate, case and encapsulant, which do not affect the electrical characteristic of the module, are neglected in the drawings. In the three dimensional modules, the bottom layer is DBC, the semiconductor dice are seated on the DBC, the black lines represent the bonding wires. The terminals are marked as in the figures. The physical distance for loop1 is shown as the red trace in Figure 3.9 (b). It starts from lead C1 and passes through  $S_1$ , two groups of bond wires, output bus E1C2 and more wires to  $D_2$ . Loop2 is shown as the green line, and the length for loop2 is similar with loop1. In the proposed P-cell and N-cell modules in Figure 3.9 (b), the two devices in the commutation loop are seated at the same side. Thus, the physical length of the commutation loop is reduced. For example, loop1 shown as the red trace also starts from C1, goes through only one group of wires, and then reaches  $D_2$ . This is much shorter than the same loop in a conventional module. For a better comparison purpose, the two modules are similar in terms of substrate size and lead frame position. The physical size is listed in Table 3.1.

After the geometries of the modules are built in Q3D Extractor, materials for each of the components are assigned, which are shown in Table 3.2.

#### B. Analysis Setup

The next step is to assign excitations, which includes source and sink, representing the current in terminal and current out terminal, respectively. The parasitics of the path between source and sink is calculated. If there are multiple paths, the mutual parasitics between the paths will also be calculated. The results are stored in a matrix. Specifically, the items in the diagonal line are the self inductance (capacitance or resistance), and others are mutual values. It is necessary to point out that the size of the excitations can affect the results. For example, the larger the area of the excitations, the smaller the parasitic inductance is. Although it is not a dominant factor, to have the similar condition, it is better to draw the area as the real excitation contact area in the measurement.

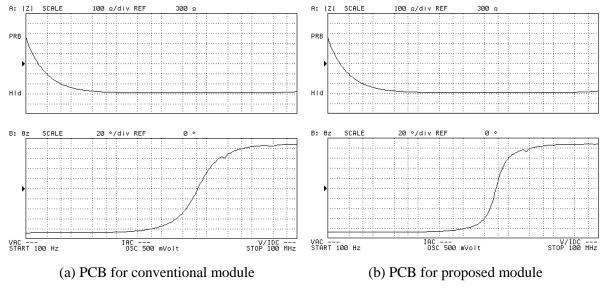

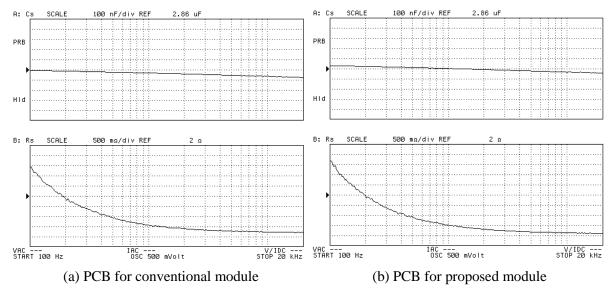

When setting up the solver, there are options for DC or AC excitation source. When

using DC excitation, current is distributed evenly in the geometry, while using AC excitation, skin effect is considered. The default frequency for AC excitation is 100 kHz, the parasitic inductance is not affected when changing frequency, and capacitance does not change either; only resistance is scaled with the factor of  $(f_{\text{new}}/f_{\text{old}})^{1/2}$ . For inductance, which is the focus in this work, the DC result is larger than the AC result because the volume considered in DC simulation is larger.

Figure 3.9. Phase-leg module layout.

|                              | Conventional module | Proposed module    |

|------------------------------|---------------------|--------------------|

| DBC size (mm)                | 37.0×38.0           | 37.5×38.5          |

| DBC thickness (mil)          | 8(Cu), 25(Alumina)  | 8(Cu), 25(Alumina) |

| IGBT (mm)                    | 5×5                 | 5×5                |

| Diode (mm)                   | 5.85×5.85           | 5.85×5.85          |

| Bond wires (diameter×number) | 8 mil×5             | 8 mil×5            |

Table 3.1. Power Module Components Dimensions

Table 3.2. Power Module Materials

| Components        | Materials                          |  |

|-------------------|------------------------------------|--|

| DBC insulator     | Alumina, permittivity 9.2          |  |

| DBC metallization | Copper, conductivity 58000000S/m   |  |

| Dice              | Silicon, permittivity 11.9         |  |

| Bond wires        | Aluminum, conductivity 38000000S/m |  |

#### 3.2.3 Simulation Results

The parasitic inductance associated with the module is studied thoroughly. The source and sink points are shown in Figure 3.10 as the yellow area. The simulation results are listed in Table 3.3.

The path from point A to point B is the commutation loop from the positive bus to the negative bus. There are two conduction paths: through S1-D2 which is loop1 shown in Figure 3.9, and through S2-D1 which is loop2. The simulation is conducted this way: when calculating loop1, the materials of S1 and D2 are set to copper while S2 and D1 is set to silicon, so that only the S1-D2 path conducts; the other path is calculated the same way. The inductance of the bus bar is also calculated separately. The path from A to D is the positive

bus bar, the path from B to E is the negative one, and the path from C to F is the AC output bus bar. They should have the same value since the same structure is used. In a commercial module, bus bars usually have larger dimensions and complex shape, however to simplify the fabrication process, the simulation uses a simpler copper bar. From H to G and from J to I are the gate drive loops.

It can be seen that the commutation loop inductances in the conventional module are both around 20 nH, while in the proposed module they are less than 10 nH. As expected, the rearrangement of the dice layout has an obvious effect on reducing the inductance of the DBC trace. For the other values, there are no large differences.

Figure 3.10. Phase-leg modules with measuring points.

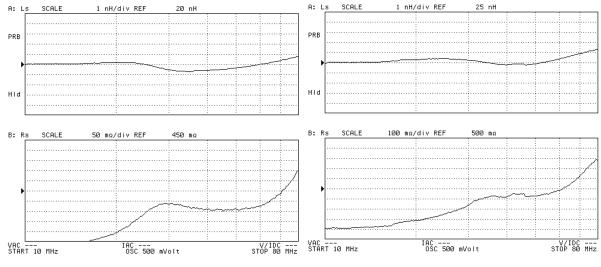

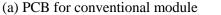

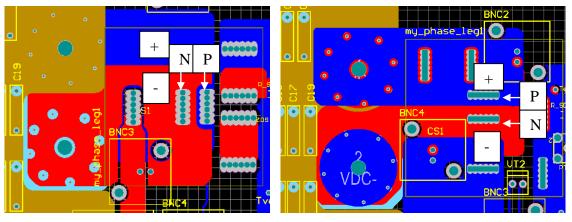

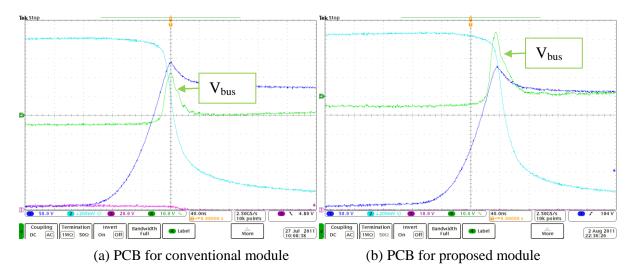

|                          | Conventional Layout |               | Proposed Layout |               |