#### University of Tennessee, Knoxville

## TRACE: Tennessee Research and Creative **Exchange**

**Doctoral Dissertations**

Graduate School

5-2012

# Real-Time Selective Harmonic Minimization for Multilevel Inverters Using Genetic Algorithm and Artificial Neural Network **Angle Generation**

Faete Jacques Teixeira Filho ffilho@utk.edu

Follow this and additional works at: https://trace.tennessee.edu/utk\_graddiss

Part of the Electrical and Electronics Commons, and the Power and Energy Commons

#### **Recommended Citation**

Filho, Faete Jacques Teixeira, "Real-Time Selective Harmonic Minimization for Multilevel Inverters Using Genetic Algorithm and Artificial Neural Network Angle Generation. " PhD diss., University of Tennessee, 2012.

https://trace.tennessee.edu/utk\_graddiss/1309

This Dissertation is brought to you for free and open access by the Graduate School at TRACE: Tennessee Research and Creative Exchange. It has been accepted for inclusion in Doctoral Dissertations by an authorized administrator of TRACE: Tennessee Research and Creative Exchange. For more information, please contact trace@utk.edu.

To the Graduate Council:

I am submitting herewith a dissertation written by Faete Jacques Teixeira Filho entitled "Real-Time Selective Harmonic Minimization for Multilevel Inverters Using Genetic Algorithm and Artificial Neural Network Angle Generation." I have examined the final electronic copy of this dissertation for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Doctor of Philosophy, with a major in Electrical Engineering.

Leon M. Tolbert, Major Professor

We have read this dissertation and recommend its acceptance:

Burak Ozpineci, Bin Hu, Fred Wang

Accepted for the Council:

Carolyn R. Hodges

Vice Provost and Dean of the Graduate School

(Original signatures are on file with official student records.)

# Real-Time Selective Harmonic Minimization for Multilevel Inverters Using Genetic Algorithm and Artificial Neural Network Angle Generation

A Dissertation Presented for the

Doctor of Philosophy

Degree

The University of Tennessee, Knoxville

Faete Jacques Teixeira Filho

May 2012

Copyright © 2012 by Faete Filho

All rights reserved.

#### Acknowledgements

This thesis would not possible without the support, guidance and feedback of the professors, staff, colleagues and friends. First and foremost I am very thankful to Dr. Tolbert for the opportunities offered and the assistance given during the course of my studies. I owe my deepest gratitude to Dr. Burak, Dr. Wang and Dr. Hu for their valuable advice. I was very grateful to have a dedicated staff in the department that was always ready to assist the students. I am indebted to many of the people who worked with me in the laboratory, my coworkers and friends that in some way help me or assisted me.

Last but not least, I would like to thank my family in Brazil and also the very encouraging friends in US for giving me the support and the strength to accomplish my goals.

#### **Abstract**

This work approximates the selective harmonic elimination problem using Artificial Neural Networks (ANN) to generate the switching angles in an 11-level full bridge cascade inverter powered by five varying DC input sources. Each of the five full bridges of the cascade inverter was connected to a separate 195 W solar panel. The angles were chosen such that the fundamental was kept constant and the low order harmonics were minimized or eliminated. A non-deterministic method is used to solve the system for the angles and to obtain the data set for the ANN training. The method also provides a set of acceptable solutions in the space where solutions do not exist by analytical methods. The trained ANN is a suitable tool that brings a small generalization effect on the angles' precision and is able to perform in real time (50/60 Hz time window).

## **Table of Contents**

| Chapter 1 Solar power, multilevel inverters and harmonic control: An       |

|----------------------------------------------------------------------------|

| introduction1                                                              |

| 1.1 Solar-electric power market1                                           |

| 1.2 Photovoltaic inverters for high power5                                 |

| 1.3 Multilevel converters6                                                 |

| 1.3.1 Cascade multilevel inverter motivation in solar applications8        |

| 1.4 Cascade multilevel inverter topology8                                  |

| 1.4.1 Innovation on system architecture for solar electric conversion $10$ |

| 1.5 Performance and reliability11                                          |

| 1.6 Symmetry considerations in a 60Hz sinusoidal grid system13             |

| 1.7 The Fourier series14                                                   |

| 1.8 Harmonic decomposition general formulation15                           |

| 1.9 Eleven level cascade inverter equations16                              |

| 1.10 Selective harmonic elimination for equal and unequal DC sources 18    |

| 1.11 Selective harmonic elimination vs. sinusoidal pulse-width modulation  |

| 19                                                                         |

| 1.12 Proposed ANN-based selective harmonic minimization                    |

| 1.13 Chapter summary22                                                     |

| Chapter 2 Real-time harmonic control literature review                     |

| 2.1 Selective harmonic elimination23                                       |

| 2.2 Solar cell model32                                               |

|----------------------------------------------------------------------|

| 2.3 Artificial neural networks35                                     |

| 2.4 Genetic algorithms                                               |

| 2.5 Final remarks                                                    |

| 2.6 Chapter summary39                                                |

| Chapter 3 Dataset and real-time angle generation40                   |

| 3.1 Genetic algorithms40                                             |

| 3.1.1 Individual representation42                                    |

| 3.1.2 Selection operator43                                           |

| 3.1.3 Crossover operator44                                           |

| 3.1.4 Mutation operator45                                            |

| 3.1.5 Algorithm initialization and termination criteria              |

| 3.2 A single GA run for SHE minimization46                           |

| 3.3 Artificial Neural Networks56                                     |

| 3.3.1 Learning from data58                                           |

| 3.4 Chapter summary60                                                |

| Chapter 4 Multilevel cascade H-bridge inverter DC voltage estimation |

| through output voltage sensing                                       |

| 4.1 Introduction62                                                   |

| 4.2 Level voltage estimation63                                       |

| 4.3 On-state resistance                                              |

| 4.4 Conduction loss estimation70                                     |

| 4.5 Control algorithm                                          | 70    |

|----------------------------------------------------------------|-------|

| 4.6 Experimental results on cells voltage estimation           | 72    |

| 4.7 Chapter summary                                            | 76    |

| Chapter 5 Real-time angle generation experimental results      | 78    |

| 5.1 Photovoltaic cell model                                    | 78    |

| 5.2 Genetic algorithm settings                                 | 82    |

| 5.3 Data set size                                              | 85    |

| 5.4 Dataset obtained through a GA run                          | 87    |

| 5.4.1 Trained ANN obtained through the GA dataset              | 88    |

| 5.4.2Fitting performance of ANN compared to GA found results   | 94    |

| 5.5 GA exploration of the search space                         | 97    |

| 5.6 Neural network real time implementation                    | 99    |

| 5.7 Experimental results                                       | 101   |

| 5.7.1 Experimental results with load                           | 110   |

| 5.7.2 Seven-level experimental results with solar panels       | 117   |

| 5.8 Chapter summary                                            | 121   |

| Chapter 6 Conclusions and future steps towards harmonic contro | ıl122 |

| 6.1 Conclusions                                                | 122   |

| 6.1.1 ANN improvement                                          | 123   |

| 6.1.2 Stochastic search methods                                | 123   |

| 6.1.3 DSpace and DSP implementation                            | 124   |

| 6.1.4 Experimental results                                     | 124   |

| 6.1.6 Main contributions summary | 124 |

|----------------------------------|-----|

| 6.1.5 Future work                | 125 |

| List of References               | 127 |

| Vita                             | 133 |

## List of Tables

| Γable 1. Installed system price (\$/W)[60]                                          | 5  |

|-------------------------------------------------------------------------------------|----|

| Γable 2. Five-level CHB under equal and unequal voltage supply2                     | 6  |

| Γable 3. Problem definition for the GA4                                             | 7  |

| Γable 4. Objective function coefficients of equation (30).                          | 9  |

| Γable 5. GA results for best individual after 80 generations5                       | 0  |

| Γable 6. GA results for best individual after 71 generations5                       | 2  |

| Γable 7. GA results for best individual after 26 generations5                       | 4  |

| Γable 8. IRFS4127 power MOSFET relevant parameters6                                 | 9  |

| Γable 9. Estimated individual cell voltage for Figure 337                           | 4  |

| Γable 10. Simulated parameters for equation 177                                     | 8  |

| Γable 11. Sanyo HIT photovoltaic electrical specifications7                         | 9  |

| Γable 12. Experimental and simulated Fill Factor8                                   | 1  |

| Γable 13. Genetic algorithm initial settings8                                       | 2  |

| Fable 14. Objective function coefficients used in Figure 37 and Figure 388          | 5  |

| Γable 15. Combinatorial possibilities for seven-level CHB with 40 V and 42 V levels | s. |

| 8                                                                                   | 6  |

| Γable 16. Eleven-level CHB dataset for ANN training8                                | 7  |

| Γable 17. Seven-level CHB dataset for ANN training8                                 | 8  |

| Fable 18. Exact and ANN approximation of the output switching angles                | 6  |

| Table 19. GA and ANN performance for fundamental voltage and THD | until the 5 <sup>th</sup> |

|------------------------------------------------------------------|---------------------------|

| harmonic                                                         | 97                        |

| Table 20. Parameters used for LC and RLC loads                   | 110                       |

## List of Figures

| Figure 1 – Solarbuzz retail module price index [59]2                                     |

|------------------------------------------------------------------------------------------|

| Figure 2 – 48 MW Copper Mountain solar electric power plant project in Nevada            |

| [71]3                                                                                    |

| Figure 3 – 30 MW Cimarron solar electric power plant project in New Mexico [72]4         |

| Figure 4 - Eleven level cascade H-bridge inverter (a) and level shifted modulation       |

| (b)9                                                                                     |

| Figure 5 - Low loss low switching frequency multilevel inverter waveforms                |

| Figure 6 – Generic waveform (a) and H-bridge inverter waveform with quarter wave         |

| symmetry (b)                                                                             |

| Figure 7 – Output waveform generation for (a) equal and (b) unequal input DC             |

| sources                                                                                  |

| Figure 8 – Actual output voltage waveform using SHE (a) and SPWM (b) for a seven-        |

| level CHB with equal DC sources ( $V_{dc}$ =1 p.u.; $V_{an1}$ =3 p.u. peak; $f_m$ =60Hz; |

| f <sub>cr</sub> =540Hz)20                                                                |

| Figure 9 – Proposed artificial neural network based selective harmonic                   |

| minimization22                                                                           |

| Figure 10 – Power converter drives classification [3]                                    |

| Figure 11 – Seven-level cascade H-bridge inverter (a) and inverter modulation (b).       |

| 25                                                                                       |

| Figure 12 – Seven-level cascade H-bridge inverter and possible voltage profiles 28       |

| Figure 13 - Techniques employed in selective harmonic elimination and                 |

|---------------------------------------------------------------------------------------|

| minimization32                                                                        |

| Figure 14 – Photovoltaic cell single diode model representation                       |

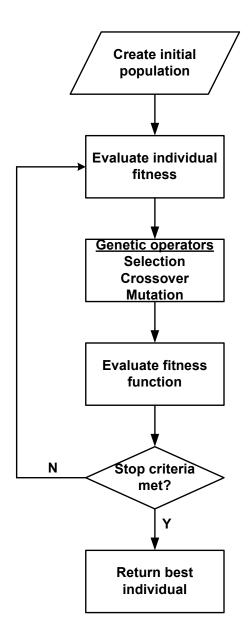

| Figure 15 – Flow chart of a continuous GA41                                           |

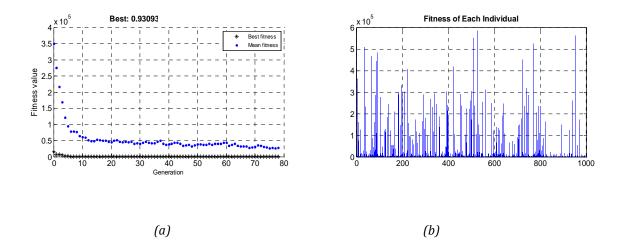

| Figure 16 – GA average and best individual per generation (a) and final population    |

| fitness (b)49                                                                         |

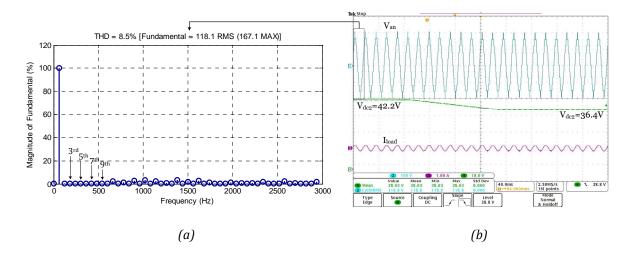

| Figure 17 – Eleven-level waveform ( $m_i$ =0.67) and fundamental voltage (a) and      |

| frequency spectrum (b)50                                                              |

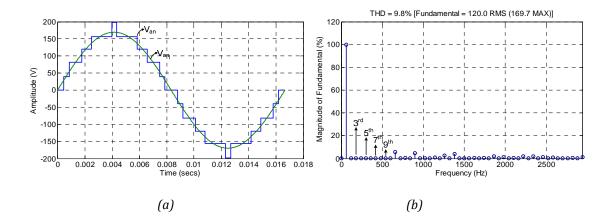

| Figure 18 – GA average and best individual per generation (a) and final population    |

| fitness (b)51                                                                         |

| Figure 19 – Nine-level waveform ( $m_i$ =0.65), fundamental voltage (a) and frequency |

| spectrum (b)52                                                                        |

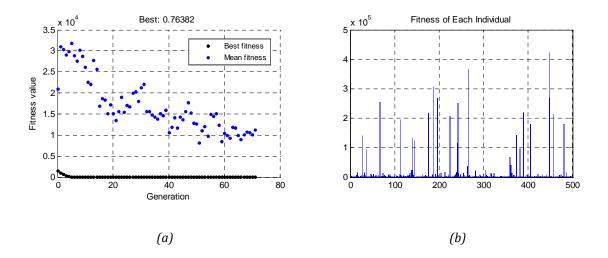

| Figure 20 – GA average and best individual per generation (a) and final population    |

| fitness (b)53                                                                         |

| Figure 21 – Seven-level waveform ( $m_i$ =0.80) and fundamental voltage (a) and       |

| frequency spectrum (b)54                                                              |

| Figure 22 - Eleven-level inverter switching angles (a) and output voltage and         |

| harmonics (b)56                                                                       |

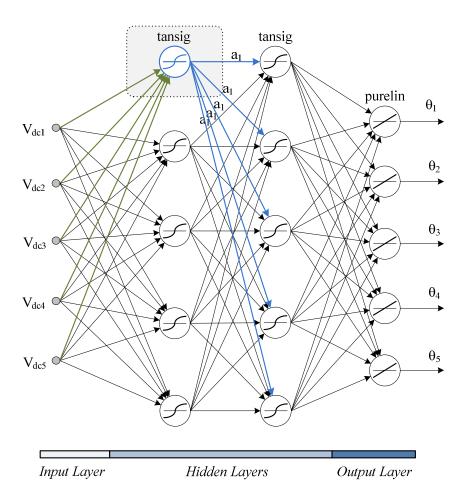

| Figure 23 – Multilayer feed-forward perceptron neural network topology 57             |

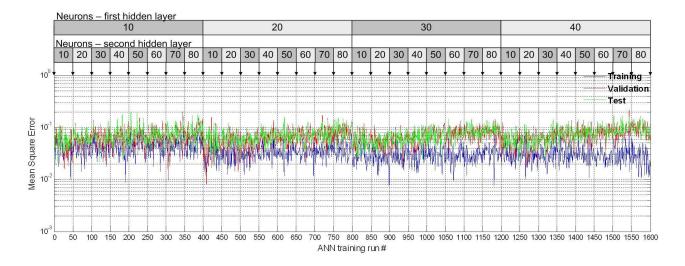

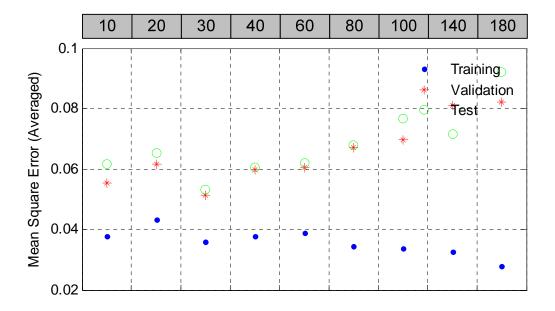

| Figure 24 – ANN performance results for different number of hidden layer neurons      |

| in an 11-level inverter60                                                             |

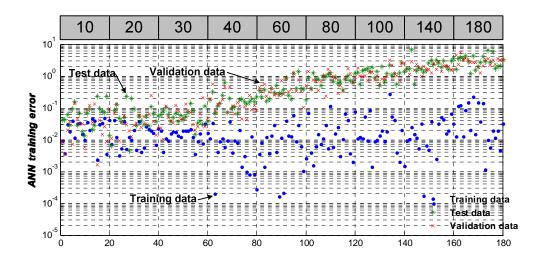

| Figure 25 – ANN performance results for different number of hidden layer neurons     |

|--------------------------------------------------------------------------------------|

| in an 7-level inverter60                                                             |

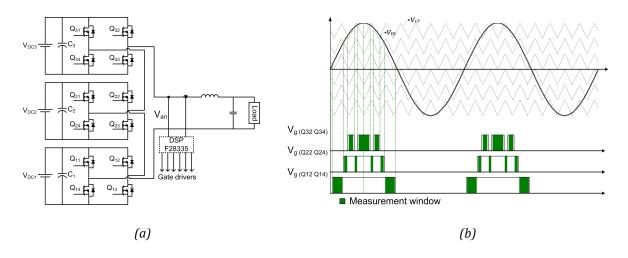

| Figure 26 – Seven-level cascade multilevel inverter (a) and level-shifted modulation |

| at f <sub>cr</sub> = 540 Hz (b)64                                                    |

| Figure 27 – Measurement window for a full cycle using level-shifted modulation at    |

| different carrier frequencies in an (a) 7 level, (b) 9 level and (c) 11 level        |

| multilevel cascade inverter                                                          |

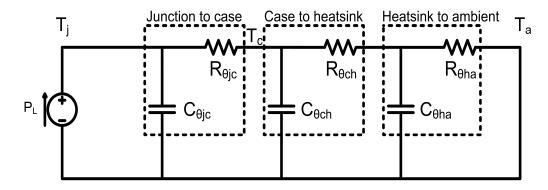

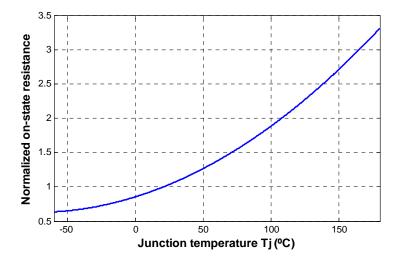

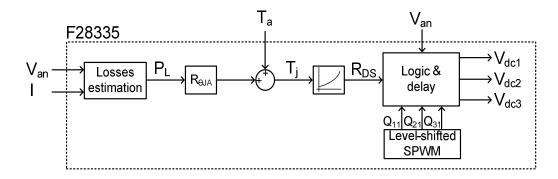

| Figure 28 – System equivalent thermal path model                                     |

| Figure 29 – On-state resistance dependence on junction temperature                   |

| Figure 30 – Control algorithm for voltage level estimation                           |

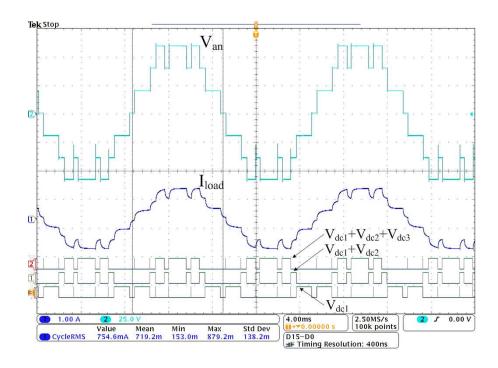

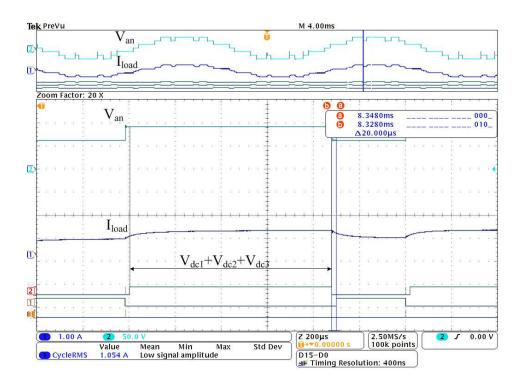

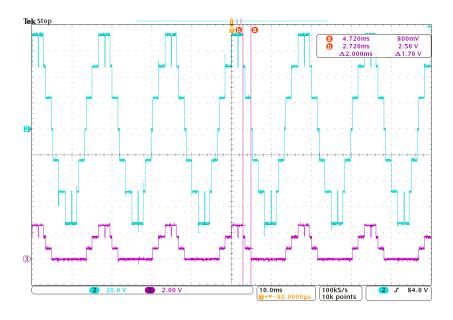

| Figure 31 – CHB output voltage, current, and switching signals for the measurement   |

| window (botton)73                                                                    |

| Figure 32 – Detailed view for the waveform of Figure 31 (Ts=20 us)75                 |

| Figure 33 – Output voltage waveform (blue) at 540Hz and signal processed by the      |

| DSP (purple)76                                                                       |

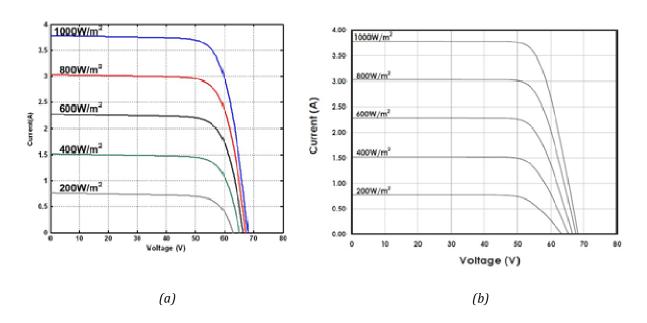

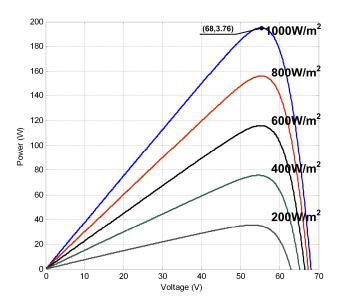

| Figure 34 - Simulated (a) and experimental (b) I-V curves for Sanyo HIT 195          |

| photovoltaic module79                                                                |

| Figure 35 – Power versus voltage for Sanyo HIT 195 photovoltaic module 80            |

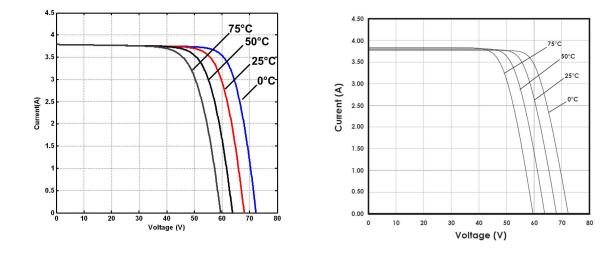

| Figure 36 – Temperature variation of simulated (a) and experimental (b) I-V curves   |

| for Sanyo HIT 195 photovoltaic module81                                              |

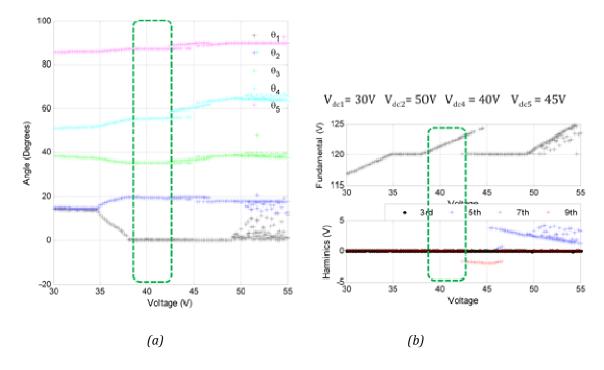

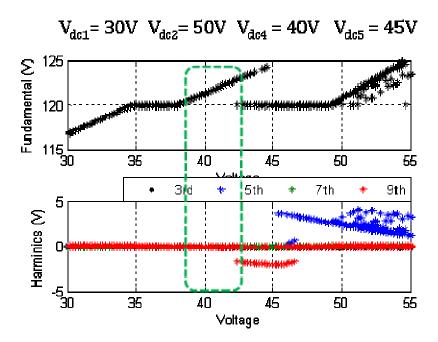

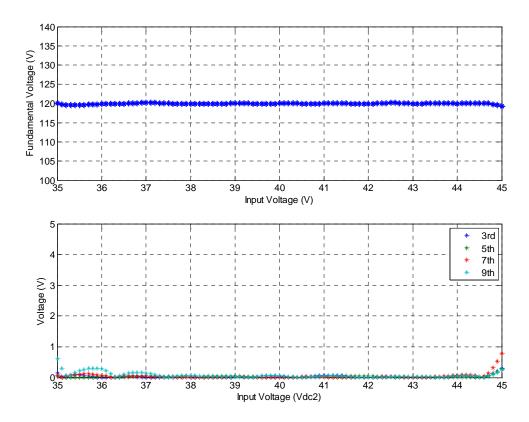

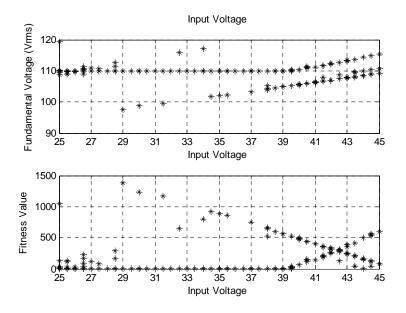

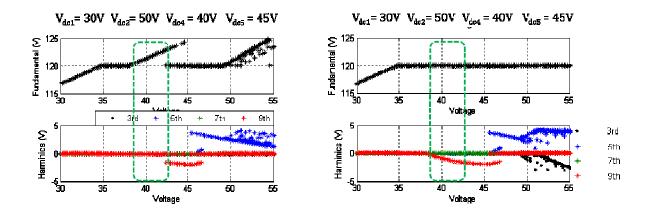

| Figure 37 – Fundamental component (upper) and harmonics (lower) under Vdc3           |

| variation                                                                            |

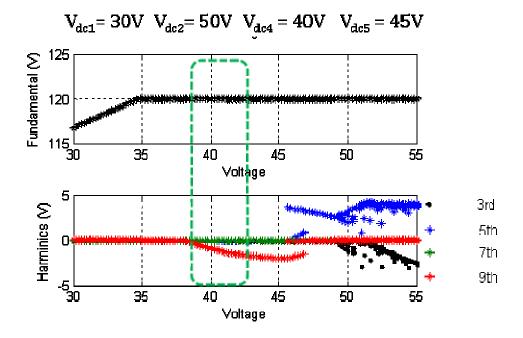

| Figure 38 - Fundamental component (upper) and harmonics (lower) under Vdc3           |

|--------------------------------------------------------------------------------------|

| variation with fitness function weighted towards fundamental voltage 84              |

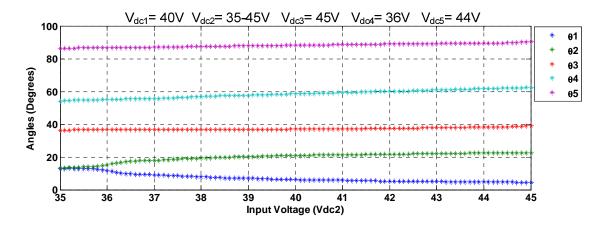

| Figure 39 -Neural network generalized angles output under DC input voltage           |

| variation89                                                                          |

| Figure 40 –Output voltage characteristics (upper) and harmonic content (lower) for   |

| angles generated by Figure 3990                                                      |

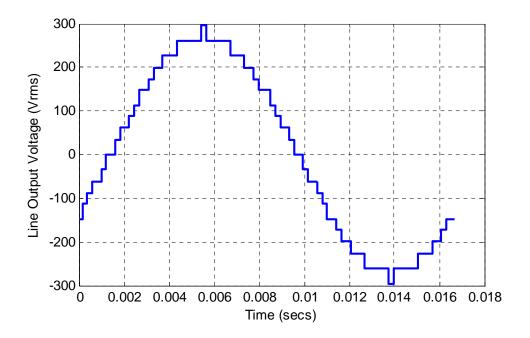

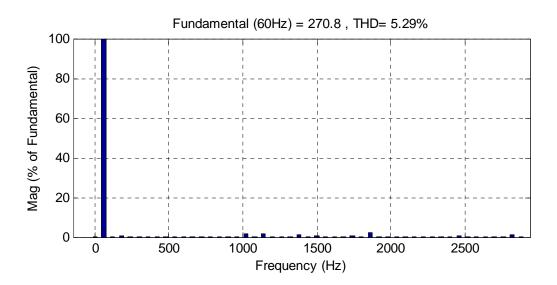

| Figure 41 – Multilevel inverter line output voltage waveform91                       |

| Figure 42 – Output voltage frequency spectrum for Figure 41                          |

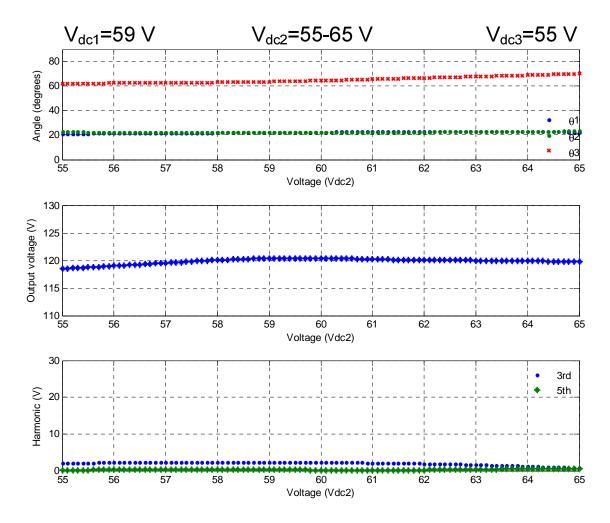

| Figure 43 –Neural network generalized angles, output voltage and harmonic content    |

| for cascade 7-level inverter93                                                       |

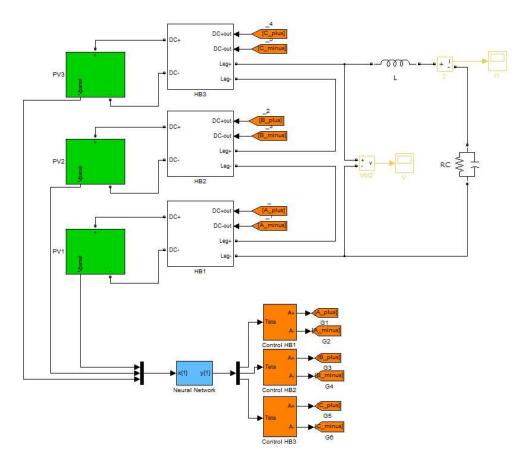

| Figure 44 –Simulink model of the overall real time system: multilevel inverter,      |

| neural network and solar panels94                                                    |

| Figure 45 –ANN performance results for different number of neurons in a 7-level      |

| inverter95                                                                           |

| Figure 46 – Output voltage as a function of DC source input variation and quality of |

| solutions measured by genetic algorithms fitness value98                             |

| Figure 47 – Fundamental component (upper) and harmonics (lower) under Vdc3           |

| variation for different GA search parameters99                                       |

| Figure 48 – DS1103 PPC controller board100                                           |

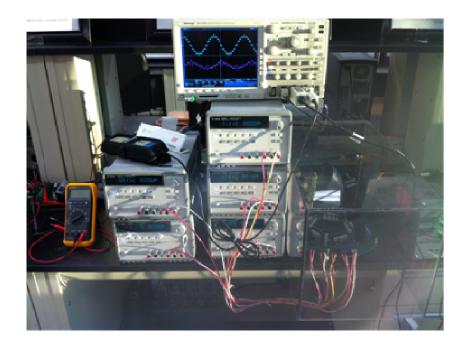

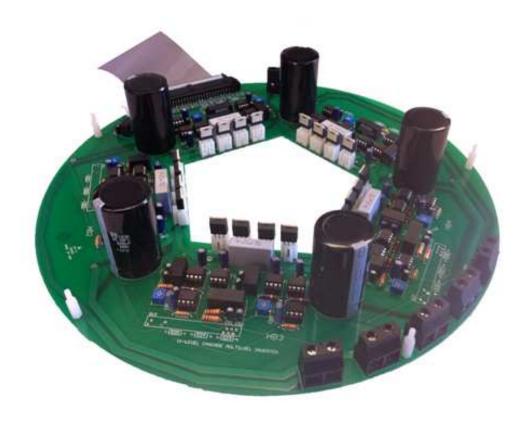

| Figure 49 – Eleven-level cascade multilevel inverter setup                           |

| Figure 50 – Eleven-level cascade multilevel inverter hardware103                     |

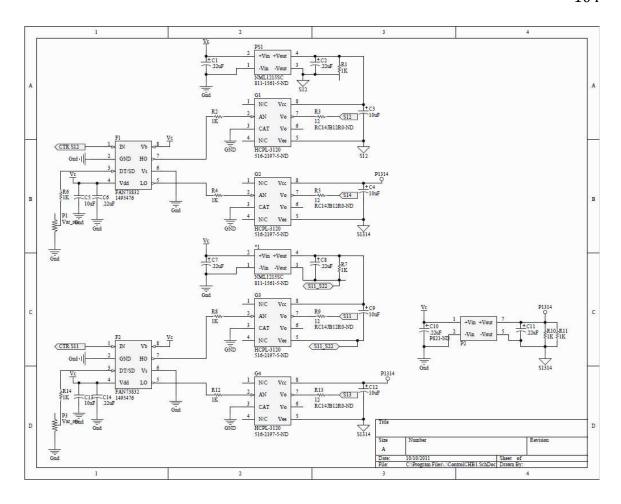

| Figure 51 – Eleven-level cascade multilevel schematic view of the logic control104   |

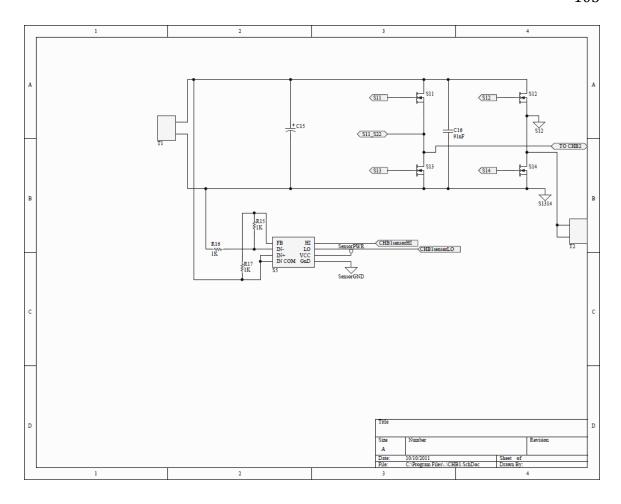

| Figure 52 – | Eleven-level cascade multilevel schematic view of one H-bridge and the     |

|-------------|----------------------------------------------------------------------------|

| voltage     | sensor                                                                     |

| Figure 53 – | Photovoltaic panels' setup                                                 |

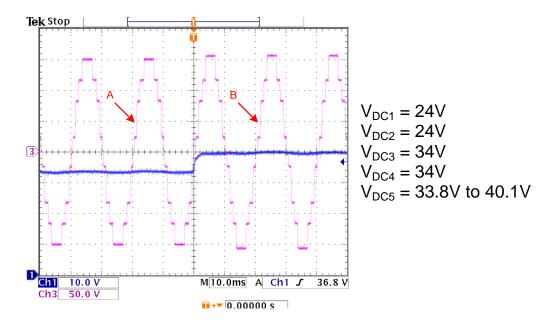

| Figure 54 - | System response to a DC input source step change (blue) and the            |

| inverte     | r output voltage (purple) reconfiguration response107                      |

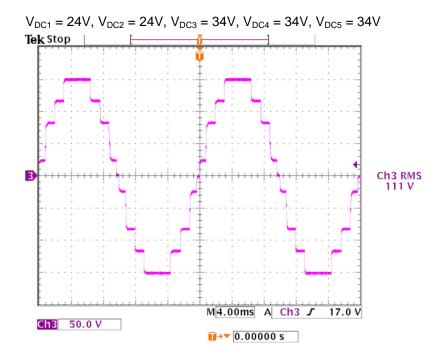

| Figure 55 – | Experimental output voltage waveform108                                    |

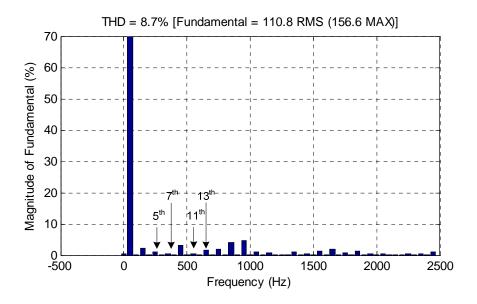

| Figure 56 – | Frequency spectrum of output voltage waveform for Figure 55108             |

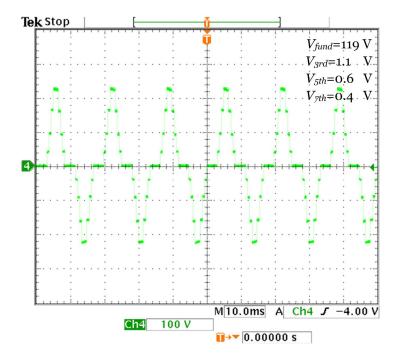

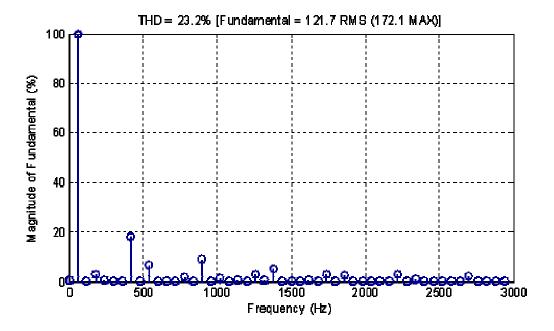

| Figure 57 – | Multilevel CHB output voltage and harmonic content109                      |

| Figure 58 – | Multilevel inverter connection diagram for load test in Table 20111        |

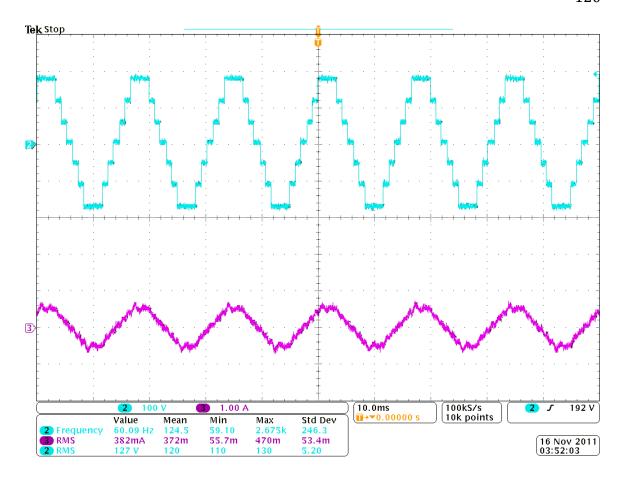

| Figure 59 – | Output voltage (cyan) and load current (purple) for case 1 in Table 20.    |

|             | 112                                                                        |

| Figure 60 – | Output voltage frequency spectrum of Figure 59113                          |

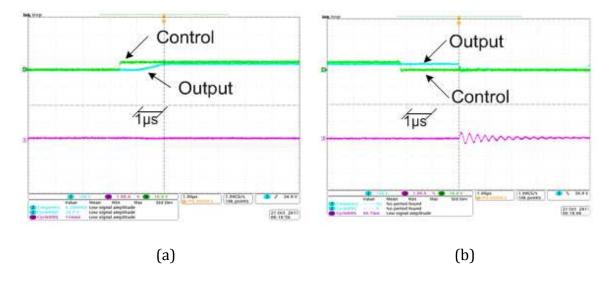

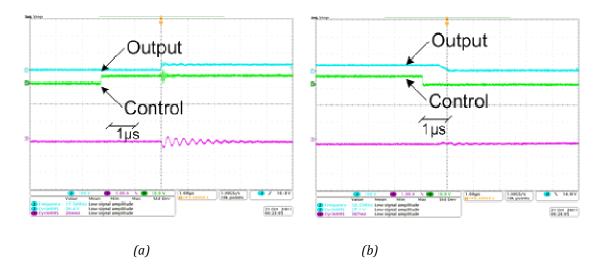

| Figure 61 – | Signal delay propagation during (a) turn-on and (b) turn-off113            |

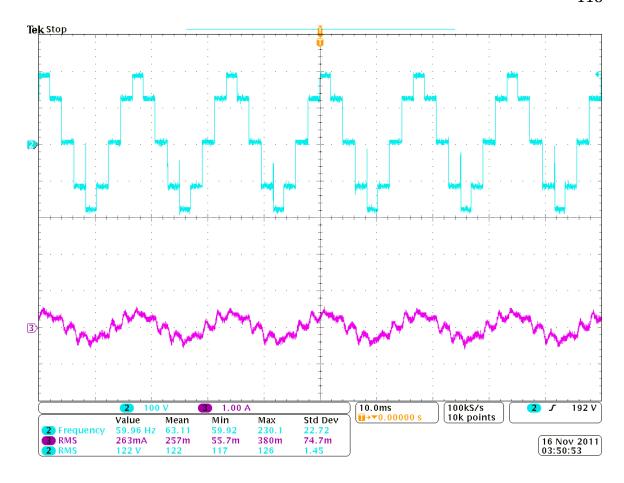

| Figure 62 – | Output voltage (cyan) and load current (purple) for case 2 in Table 20.    |

|             | 114                                                                        |

| Figure 63 – | Output voltage frequency spectrum of Figure 62115                          |

| Figure 64 – | Signal delay propagation during (a) turn-on and (b) turn-off under RLC     |

| load of     | case 2115                                                                  |

| Figure 65 – | Output voltage (cyan) and load current (purple) for R=107 $\Omega$ and L=5 |

| mH          | 116                                                                        |

| Figure 66 – | Output voltage harmonic content (a) and real-time ANN response (b)         |

| hefore      | V <sub>dc2</sub> variation                                                 |

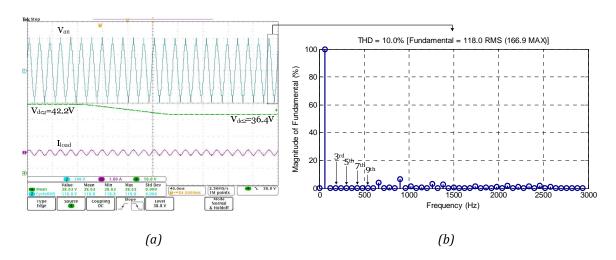

| Figure 67 – Output voltage harmonic content (a) and real-time ANN response (b)   |

|----------------------------------------------------------------------------------|

| after $V_{dc2}$ variation117                                                     |

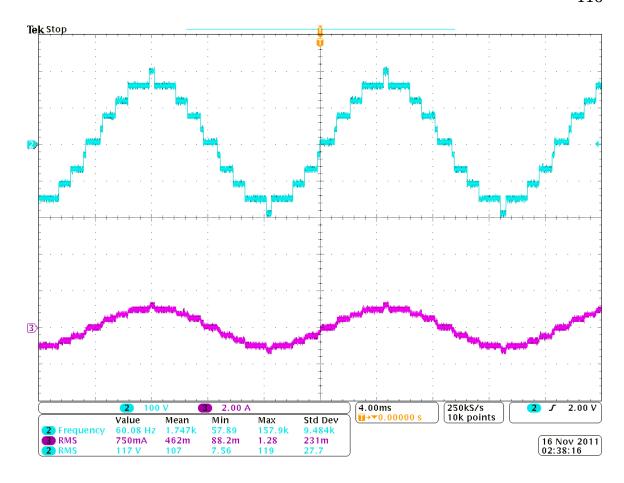

| Figure 68 - Output voltage (green) and load current (purple) for 7-Level cascade |

| under load condition (500 $\Omega;$ 5 mH;10 $\mu F).$ 118                        |

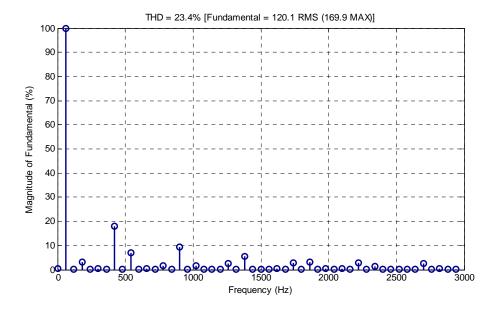

| Figure 69 – Output voltage frequency spectrum of Figure 69119                    |

| Figure 70 - Output voltage (green) and load current (purple) for 7-Level cascade |

| under load condition (333.3 $\Omega;$ 5 mH;10 $\mu F).$                          |

| Figure 71 – Output voltage frequency spectrum of Figure 70121                    |

#### Chapter 1

# Solar power, multilevel inverters and harmonic control: An introduction

This chapter will discuss current solar power development level, key features of multilevel inverters and introduce the cascade H-bridge converter. Next, the Fourier decomposition of the output waveform will be derived for an 11-level inverter for selective harmonic elimination of its higher order components. Unequal and equal DC source cases will be covered and compared with standard sinusoidal pulse width modulation. As a final point, the need and significance of real time angle calculation will be covered.

#### 1.1 Solar-electric power market

Solar power is the process in which sunlight is converted into electricity, either directly using photovoltaic (PV) cells, or indirectly, for example, using concentrating solar power (CSP).

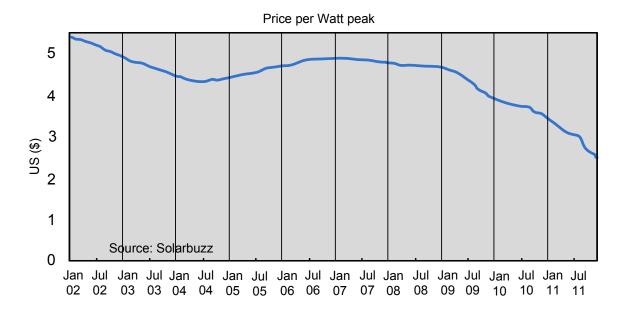

Solar panel research and development was documented in the 18<sup>th</sup> century by Charles Fritts. Almost a century later, a silver-selenide version was constructed by Bruno Lange at 1% efficiency. Later, in the 1940s with more research invested in solar technology, efficiencies of 4.5-6% were achieved at 286 USD/watt [58]. Further investments into research and development of solar electric cells brought this technology to a commercial level with prices of 2.49 USD/watt as shown in Figure 1. According to [59], 245 solar modules in the market today are priced below

\$2.00 per watt. The price drop, which is shown in this figure, according to recent surveys [59] shows that there is little evidence that it will slow down.

Figure 1 – Solarbuzz retail module price index [59].

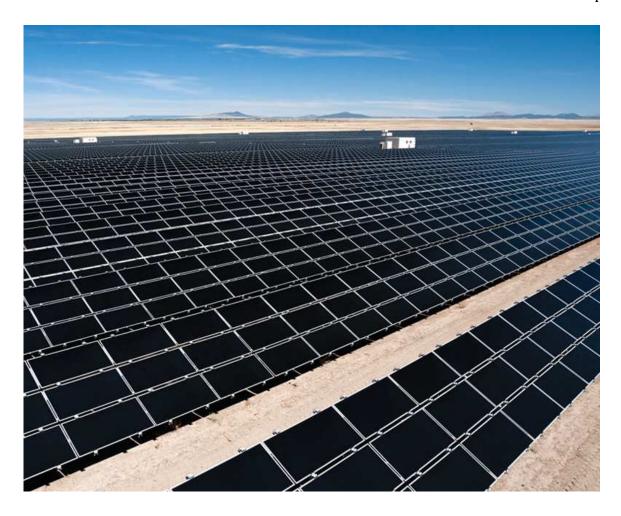

A total of 15.9 GW in solar installations were accomplished in 2010 according to PVinsights, which reported a growth of 117% in solar PV installation on an annual basis. The 2010 Solar Electric Power Association (SEPA) report on solar power energy installed by utilities compiled all the solar power plant investments done by utilities in 2010 [58]. It shows that the solar electric market continues to expand across the country and is being seen as an important factor in the supply of energy, planning and customer management utilities. This report also points to two trends that are shifting the profile of solar electric energy in US: centralized projects and utility ownership. Centralized projects are gaining momentum as more utility companies invest in PV power plants such as the one shown in Figure 2 and Figure

3. Although the cost of the power electronics in those systems is not the dominant part, it has the shortest lifetime. While solar panels are warranted 25-35 years, the converters usually come with a 10-15 year warranty. A modular design for power converters would allow an increased reliability while reducing maintenance costs. Multilevel converters are one of the alternatives available that can achieve a low cost at a modular level.

Figure 2 – 48 MW Copper Mountain solar electric power plant project in Nevada [71].

Figure 3 – 30 MW Cimarron solar electric power plant project in New Mexico [72].

A cost breakdown for a typical PV installation is shown in Table 1. The module cost contributes to almost half of the price leaving the other half to installation costs and balance-of-system (BOS). All the components with the exception of the solar modules and power electronics are considered BOS. It is worth to note that the power electronics have a lifetime of almost half of the solar modules. This reliability issue could be addressed by modularity in design of power converters such as the one proposed in this work.

Table 1. Installed system price (\$/W)[60].

|                   | 2010   |

|-------------------|--------|

| Module            | \$1.70 |

| BOS/Installation  | \$1.48 |

| Power Electronics | \$0.22 |

| Total             | \$3.40 |

#### 1.2 Photovoltaic inverters for high power

Research has been conducted in photovoltaic (PV) inverters to address key points such as cost, robustness, and efficiency. The modularity and low cost of multilevel converters positions them as a candidate for the next generation of efficient, robust, and reliable grid-connected solar power converters. The multilevel inverter architecture has the potential provide active, reactive support and smart grid capabilities that enhance grid stability. By deploying this architecture, system reliability is enhanced and production costs are lowered. This system architecture can reduce the cost and improve the performance of medium and large PV systems. In addition to regulating real power flow, it is also possible to achieve voltage regulation, frequency regulation, harmonic compensation, and damping of transients.

Many new multilevel topologies have been introduced as variations of the three popular multilevel converter architectures (cascaded, diode clamped and capacitor clamped). These architectures have been commercialized for applications such as STATCOMs (static synchronous compensators) and large variable speed drives [2-3]. Journals and conference papers have discussed various configurations of inverters for solar applications that focus on efficiency and better utilization of individual panel power. Most attention has been given to a centralized DC bus with modularized DC-DC converters as a more efficient and cost effective way to connect solar panels. In this proposal, the use of DC-AC cascade multilevel inverters is proposed as an attractive option to a centralized DC bus. The same or better performance can be realized with one modularized and easily maintained inverter.

A centralized DC bus approach requires individual control boards for each device connected to the bus, and a centralized DC-AC inverter. Although the DC-DC converters can be modularized, the DC-AC inverter is often overrated in case more photovoltaic panels are added later. For this reason, cost may be higher with the standard architecture.

#### 1.3 Multilevel converters

Multilevel converters make it possible to achieve medium voltage generation using low to medium voltage switches, preventing high dv/dt stress and the need for series connection of switches while allowing higher converter power rating. Multilevel converters have less filter requirements, generate a staircase waveform, have better harmonic profile (lower total harmonic distortion), and have less switching losses. However, they need more components, driver isolation becomes complex since additional levels need isolated power supplies, and the cost is higher compared to conventional single-cell topologies.

Cascade H-bridge (CHB), diode-clamped and capacitor-clamped are among the most common topologies and are well documented in the literature [44]. More emphasis will be given here to the features related to the CHB, since it is the topology to be used here for harmonic control.

The cascade multilevel topology and its universal module have several advantages over the traditional customized converter architecture including:

- Increased reliability: if one module fails, the system can reconfigure itself and continue operation until the faulty module is replaced.

- Reduced cost: the modular topology eliminates the need for a custom design for each installation, resulting in higher unit volumes with lower manufacturing costs.

- Serviceability: modules can be easily replaced thus reducing system downtime, increasing the availability of power, and reducing the cost of maintenance.

- Increased system lifetime: a standardized design will enable incremental continuous improvements in module hardware as experienced with standard utility equipment.

- Modularity and scalability: more PV capacity can be added in parallel to increase current carrying capacity or in series for higher voltage applications.

- Energy storage and backup power interface: adding energy storage (capacitors or batteries) is as convenient as adding another PV module.

#### 1.3.1 Cascade multilevel inverter motivation in solar applications

The cascaded H-bridge multilevel inverter topology requires a separate DC source for each H-bridge so high power and/or high voltage can result from the combination of the multiple modules in a multilevel inverter. To maximize the energy harvested from each string, a maximum power point tracking (MPPT) control algorithm can be utilized for solar applications. The cascaded topology allows independent MPPT control for each separate PV array, which can increase the efficiency of the PV system in case of mismatches due to variability and shading. Development of modular H-bridge units will help yield standard power electronic converters that will have lower installation and operating costs for the overall system. Incorporating autonomous fault current limiting and reconfiguration capabilities into the modules and having redundant modules will lead to a durable and robust converter that can withstand the rigors of utility operation for more than 30 years and meet the lifetime requirements of the utility industry [61].

#### 1.4 Cascade multilevel inverter topology

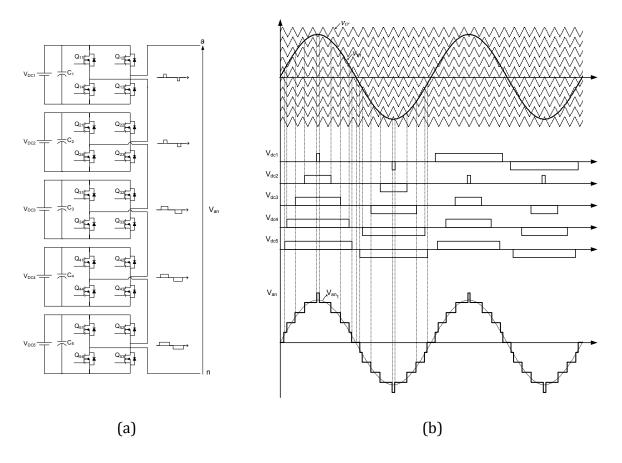

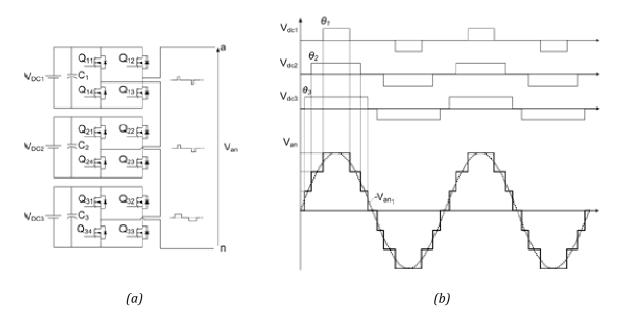

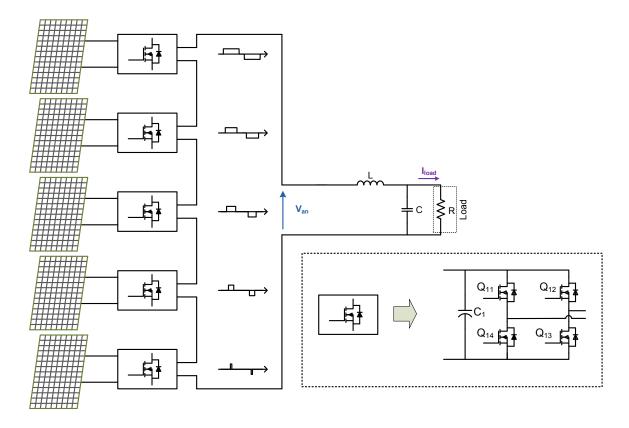

The 11-level cascade inverter topology is presented in Figure 4 (a). It has five full bridge series connected configuration with five isolated input DC supplies that may have different voltage levels. Each switch is subject to the dv/dt caused by its own power supply adding up in series to generate the staircase waveform. Levelshifted carriers  $v_{cr}$  are compared with the modulating signal  $v_m$  to generate the gate signals to the H-bridges, as shown in Figure 4 (b).

Figure 4 - Eleven level cascade H-bridge inverter (a) and level shifted modulation (b).

An m-level topology requires  $2^*(m-1)$  switches and (m-1)/2 isolated power supplies. The eleven-level inverter shown above requires twenty switches and five DC sources. The number of levels of the output voltage can be increased without the addition of extra isolated supplies by using lower voltage level multiples. For example, with two H-bridges with voltages E and 2E, it is possible to generate seven levels instead of five. Two additional levels are introduced by the voltage difference. In this case, the inverter loses its modularity and the redundant states are reduced. Although unequal voltage sources will be covered in this work, modulation will still

be done using staircase modulation, without considering the additional steps produced by the voltage difference due to constant variation of voltage over time.

Modulation can be accomplished using phase shifting or level shifting. Figure 4 (b) shows the level-shifted in-phase disposition modulation. Each level has its own set of carriers  $v_{cr}$  to produce both positive and negative pulses. Additionally, duty cycle swapping can be employed to allow equal average power drawn from each cell module, as shown in the second cycle of Figure 4 (b). Modulation can also be accomplished by determining the angles so as to generate the staircase waveform with predefined harmonic contents, as will be shown in the following sections.

#### 1.4.1 Innovation on system architecture for solar electric conversion

Cascade multilevel converters feature several DC links, making possible the independent voltage control and the tracking of the MPP in each PV string, which can maximize the efficiency of the whole PV system. In addition, the output waveform will consist of voltage steps for each of the levels or H-bridges as well as multilevel PWM to achieve a higher fidelity waveform or eliminate harmonics in the output even if the DC link voltages are unequal. Multilevel PWM and harmonic elimination are techniques that can be used in cascade multilevel inverters in order to achieve voltage waveforms with low total harmonic distortion (THD) with minimum switching losses and low filtering requirements [5-12].

Using a multilevel layout, an effective high switching frequency can be achieved in the output voltage waveform with each of the H-bridge modules having a relatively low switching frequency as shown in Figure 5. This approach will enable

increased converter efficiency. Reducing the filtering requirements would help to reduce the cost and improve the reliability and dynamic performance of the whole system.

*Figure 5 - Low loss low switching frequency multilevel inverter waveforms.*

#### 1.5 Performance and reliability

The cascaded H-bridge multilevel inverter has the potential to increase the reliability of the grid-connected PV system by bypassing a faulty H-bridge or failed PV array [62]. Output phase voltages of the multilevel inverter can be used as diagnostic signals to detect faults and their locations. Previous work has shown that all fault features in both open and short circuit cases can be detected using Fast Fourier Transform and a neural network. After failure identification and isolation of

a single module, the remaining modules in a converter installation can continue to operate.

Generally, passive protection devices in a utility installation will disconnect the power sources whenever a fault occurs. Cascaded multilevel inverter architecture has the ability to tolerate a fault for several cycles but if the fault type and location can be detected and identified, switching patterns and the modulation index of other active cells can be adjusted to maintain the operation under a balanced load condition. The remaining switches can be controlled such that the faulty switch is bypassed. Additionally, the control signal can be adapted such that for lower modulation indices, there is no noticeable difference in the output voltage after fault reconfiguration. For higher modulation indices the converter can continue to operate in an over modulation mode which may result in some moderate increased distortion in the output voltage of the converter. With faster control hardware presently available, it is anticipated that fault detection and the reconfiguration described could be done in less than 50 ms and possibly as fast as 30 ms. This enables the system to continue to operate even with hardware failures. This is a unique feature of multilevel converters that can help ensure higher reliability for utility applications even though the converter has more switches than conventional converters.

Another innovation enabled by this topology is the use of energy storage such as batteries or capacitors. With a capacitive small energy source connected in parallel with the renewable energy source, a multilevel converter can provide static

VAR compensation even when there is no power from the photovoltaic source. With banks of batteries or large capacitors on the DC bus, the multilevel converter can provide significant ride-through capability for voltage sags or load swings experienced at the utility interface connection [63-64].

The proposed architecture would also potentially improve power quality on the grid since both the line voltage and current are almost sinusoidal with the use of small output filters on the experimental converter. Electromagnetic interference (EMI) and common-mode voltage are also inherently less because of the low switching frequency, low dv/dt, and near sinusoidal voltage output. The switching angles that generate the staircase waveform of the cascade inverter can be controlled to eliminate low order harmonics as shown in the next sections.

#### 1.6 Symmetry considerations in a 60Hz sinusoidal grid system

Before starting the mathematical treatment to characterize harmonic content in multilevel converters, some assumptions must be taken in order to formulate the problem as a practical application.

The output voltage waveform for many applications, such as motors and most loads, has a periodic, polarity-changing nature. In a full bridge topology, it is reasonable to assume that during one cycle of the fundamental frequency no voltage variation occurs, so the waveform with quarter wave symmetry can be obtained. Those assumptions are illustrated in Figure 6 (b).

Figure 6 – Generic waveform (a) and H-bridge inverter waveform with quarter wave symmetry (b).

Figure 6 (b) shows the basic assumptions of constant DC voltage over a full cycle and quarter wave symmetry that will be assumed in the work proposed here. Thus, the DC voltage level and the switching angle are the parameters needed to fully characterize the waveform shape and the harmonic profile that will be analyzed.

#### 1.7 The Fourier series

This mathematical tool was first introduced by Joseph Fourier (1768-1830) to solve a heat equation in a metal plate. It decomposes any periodic function into a sum of periodic sine and cosine functions [35]. For any periodic integrable function f(x) in the interval  $[0,2\pi]$ , f(wt) can be written as a sum of sine and cosine functions such that f(wt) approximates f(x) as the number of coefficients N tend to infinity:

$$f(wt) = \frac{a_0}{2} + \sum_{n=1}^{N} [a_n \cos(nwt) + b_n \sin(nwt)]$$

(1)

The sine and cosine coefficients  $a_n$  and  $b_n$  are the Fourier coefficients and are defined as follows:

$$a_n = \frac{1}{\pi} \int_0^{2\pi} f(wt) \cos(nwt) dwt \quad (n \ge 0)$$

(2)

$$b_n = \frac{1}{\pi} \int_0^{2\pi} f(wt) \sin(nwt) dwt \quad (n \ge 1)$$

(3)

Equation (1) shows that a periodic function can be broken into an infinite number of trigonometric components at different frequencies or multiples of w (nw or  $n2\pi f$ ). The waveform f(x) can be understood as composed of a fundamental frequency component (n=1), a DC component ( $a_0$ ), and harmonic components ( $n\geq 2$ ).

For the square wave shown in Figure 2 (b), operating under a constant DC input source, the output voltage in terms of the harmonic contents can be derived from Equation (1) as:

$$f(wt) = \sum_{n=1,3,5,\dots}^{\infty} \left[ \left( \frac{4V_{dc}}{n\pi} \cos(n\alpha_1) \right) \sin(nwt) \right]$$

(4)

Only odd harmonics are present as a consequence of the constant DC power supply considered; also  $a_0$  is zero as a result of the wave form symmetry. The peak value of the sinusoidal is determined by  $b_n$  alone.

#### 1.8 Harmonic decomposition general formulation

Equation (4) shows the harmonic content for the waveform shown in Figure 6 (b). Quarter wave symmetry was assumed as it is the case in a full bridge with constant DC source. In a cascade inverter, there may be more than one level with different DC voltages for each level. In addition, there may be more than one switching angle for each level.

In [16], a general formulation is derived for a single- and three-phase system for an m switching cells with  $\alpha_n$  switching angles case as in Equation (5):

$$b_n = \frac{4}{n\pi} \left( V_1 \sum_{i=1}^{p_1} (-1)^{i+1} \cos(n\alpha_i) \pm V_2 \sum_{i=p_1+1}^{p_2} (-1)^i \cos(n\alpha_i) \pm \dots \pm V_m \sum_{i=p_{m-1}+1}^{p_m} (-1)^i \cos(n\alpha_i) \right)$$

(5)

where,

$b_n$ : peak value of the n-th harmonic component

*n*: harmonic component

$V_m$ : voltage level of the m-th converter cell

$p_m$ : number of switching angles on the m-th converter cell

$\alpha_i$ : *i*-th switching angle

The  $\pm$  polarity symbol is positive if  $P_{m-1}$  is an odd number. As long as the waveform has quarter wave symmetry, Equation (5) can be used for any number of switching angles per cell for any number of cells under any voltage level. Voltage variation under the same period is not taken into account in this equation.

#### 1.9 Eleven level cascade inverter equations

This topology has, as mentioned previously, five cells and they can have five DC inputs varying in a practical scenario. First, it will be considered that the inputs have the same value and if variation occurs it happens equally between them, and then a second set of equations will be derived to consider variation as indicated in Figure 7.

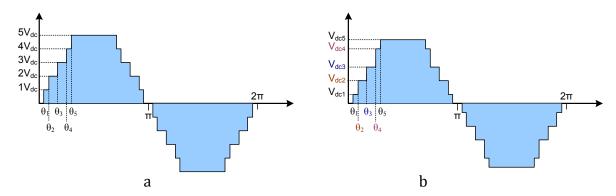

Figure 7 – Output waveform generation for (a) equal and (b) unequal input DC sources.

By manipulating Equation (5) for an eleven-level CHB with five switching angles, case *a* in Figure 7 becomes:

$$V(wt) = \sum_{n=1,3.5...}^{\infty} \left[ \frac{4V_{dc}}{n\pi} \left( \cos(n\theta_1) + \cos(n\theta_2) + \cos(n\theta_3) + \cos(n\theta_4) + \cos(n\theta_5) \right) \sin(nwt) \right]$$

(6)

And for case *b*:

$$V(wt) = \sum_{n=1,3,5,...}^{\infty} \left[ \frac{4}{n\pi} (V_{dc1} \cos(n\theta_1) + V_{dc2} \cos(n\theta_2) + V_{dc3} \cos(n\theta_3) + V_{dc4} \cos(n\theta_4) + V_{dc5} \cos(n\theta_5)) \sin(nwt) \right]$$

(7)

The modulation index  $m_i$  can be defined for Equation (7) as the peak value of the fundamental voltage ( $b_1$ ) divided by the peak value of the maximum fundamental voltage achievable for each cell. If each cell is switching a square wave with amplitude  $V_{dc}$ , then the peak value of the fundamental component will be  $4V_{dc}/\pi$ . The modulation index defined in Equation (8) will be then in the range  $0 \le m_i \le 1$ . A modulation index equals to one means that all converter cells are switching with a zero degree switching angle (square wave) [16]. That differs from the definition for sinusoidal pulse-width modulation (SPWM) where  $m_i=1$  is the linear region limit where over-modulation starts.

$$m_i = \frac{b_1}{\frac{4}{\pi} \sum V_{dc_n}} \tag{8}$$

#### 1.10 Selective harmonic elimination for equal and unequal DC sources

As shown in Equation (7), the output voltage is composed of a fundamental component (n=1) and harmonic components (n>1). Each component of the output voltage can be expressed by:

$$V_{n-th}(wt) = \left[\frac{4}{n\pi}(V_{dc1}\cos(n\theta_1) + V_{dc2}\cos(n\theta_2) + V_{dc3}\cos(n\theta_3) + V_{dc4}\cos(n\theta_4) + V_{dc5}\cos(n\theta_5))\right]\sin(nwt)$$

(9)

where  $V_{n-th}$  is the n-th harmonic component,  $V_{dc1}$  is the voltage level of cell one,  $\theta_1$  is the switching angle of cell one ( $V_{dc1}$ ),  $\theta_2$  is the switching angle for voltage  $V_{dc2}$ , and so on.

The five free variables  $\theta_1$  through  $\theta_5$  in Equation (9) can be used to form a system of five equations so that the zeros can be arbitrarily chosen to keep the fundamental value at its nominal value while four harmonics can be brought down to zero. The fundamental voltage can be set to 110 V or 120 V as shown in Equation (10) [15].

$$V_{fund}^{RMS} = \frac{4}{\pi\sqrt{2}} \left[ V_{dc1} \cos(\theta_1) + V_{dc2} \cos(\theta_2) + V_{dc3} \cos(\theta_3) + V_{dc4} \cos(\theta_4) + V_{dc5} \cos(\theta_5) \right] = 120V$$

(10)

The target harmonics to be canceled can be arbitrarily set. For example, the 5<sup>th</sup>, 7<sup>th</sup>, 11<sup>th</sup> and 13<sup>th</sup> can be set as the target harmonics since the 3<sup>rd</sup> and 9<sup>th</sup> are canceled in the line-to-line voltage in three-phase applications. For single-phase applications the 3<sup>rd</sup> and 9<sup>th</sup> have to be included in the system of equations to be

solved. Consequently, the five equations to be solved are Equation (10) plus any four out of the six Equations (11) through (16).

$$V_{3^{rd}}^{RMS} = \frac{4}{3\pi\sqrt{2}} \left[ V_{dc1} \cos(3\theta_1) + V_{dc2} \cos(3\theta_2) + V_{dc3} \cos(3\theta_3) + V_{dc4} \cos(3\theta_4) + V_{dc5} \cos(3\theta_5) \right] = 0$$

(11)

$$V_{5^{th}}^{RMS} = \frac{4}{5\pi\sqrt{2}} \left[ V_{dc1}\cos(5\theta_1) + V_{dc2}\cos(5\theta_2) + V_{dc3}\cos(5\theta_3) + V_{dc4}\cos(5\theta_4) + V_{dc5}\cos(5\theta_5) \right] = 0$$

(12)

$$V_{7^{rd}}^{RMS} = \frac{4}{7\pi\sqrt{2}} \left[ V_{dc1} \cos(7\theta_1) + V_{dc2} \cos(7\theta_2) + V_{dc3} \cos(7\theta_3) + V_{dc4} \cos(7\theta_4) + V_{dc5} \cos(7\theta_5) \right] = 0$$

(13)

$$V_{g^{rMS}}^{RMS} = \frac{4}{9\pi\sqrt{2}} \left[ V_{dc1} \cos(9\theta_1) + V_{dc2} \cos(9\theta_2) + V_{dc3} \cos(9\theta_3) + V_{dc4} \cos(9\theta_4) + V_{dc5} \cos(9\theta_5) \right] = 0$$

(14)

$$V_{11^{rds}}^{RMS} = \frac{4}{11\pi\sqrt{2}} \left[ V_{dc1} \cos(11\theta_1) + V_{dc2} \cos(11\theta_2) + V_{dc3} \cos(11\theta_3) + V_{dc4} \cos(11\theta_4) + V_{dc5} \cos(11\theta_5) \right] = 0 \quad (15)$$

$$V_{13^{rd}}^{RMS} = \frac{4}{13\pi\sqrt{2}} \left[ V_{dc1} \cos(13\theta_1) + V_{dc2} \cos(13\theta_2) + V_{dc3} \cos(13\theta_3) + V_{dc4} \cos(13\theta_4) + V_{dc5} \cos(13\theta_5) \right] = 0$$

(16)

All those equations are nonlinear and transcendental, therefore, multiple solutions may be possible. In addition, many local minima may be possible which make it difficult to solve using some numerical methods. A non-deterministic method will be adopted here to solve for switching angles that will give exact solutions and approximate solutions even for cases where no solution exists. The algorithm developed in this proposal will show advantages in finding approximate solutions compared to algorithms that solve the equations exactly.

#### 1.11 Selective harmonic elimination vs. sinusoidal pulse-width modulation

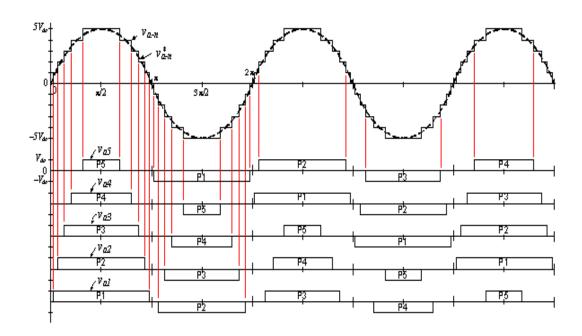

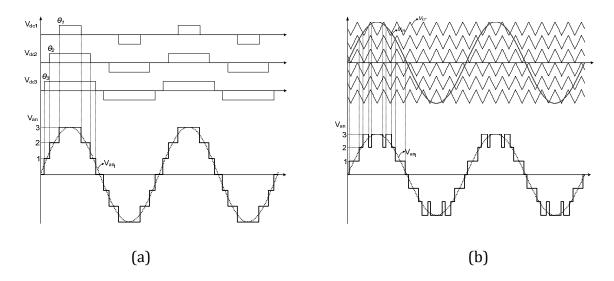

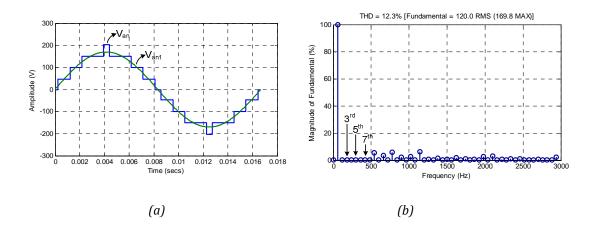

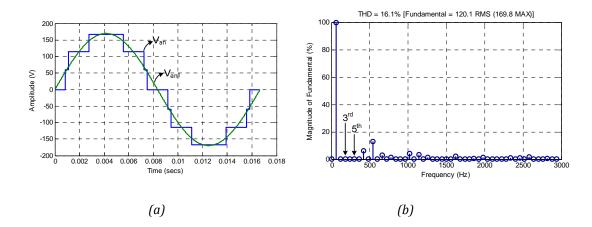

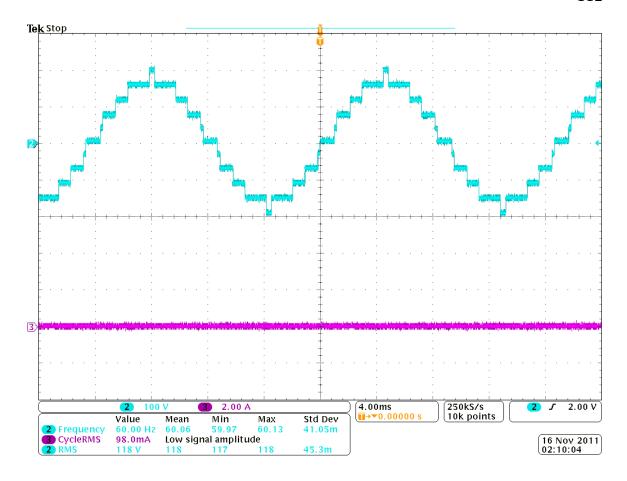

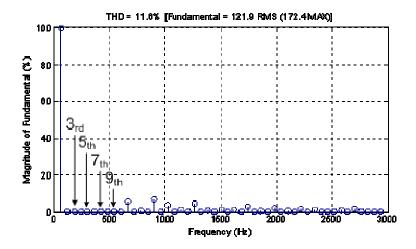

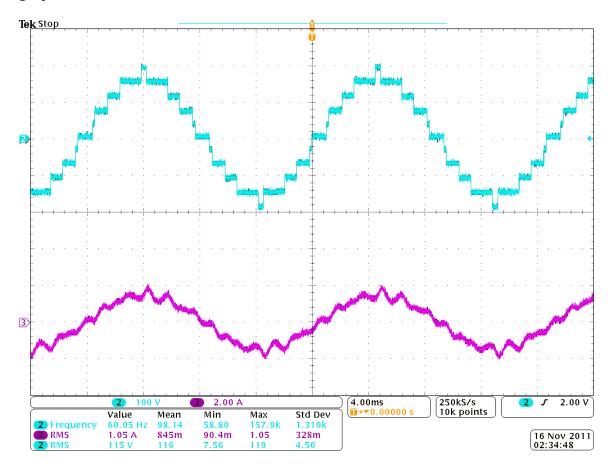

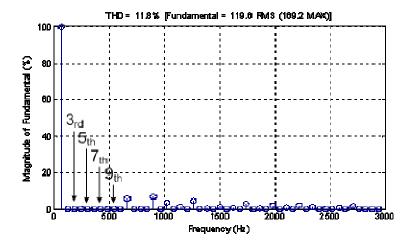

A seven-level CHB was modulated to produce a fundamental voltage  $V_{an1}$ =3 p.u. in Figure 8. The selective harmonic elimination (SHE) method uses the switching angles  $\theta_1$ =57.106°,  $\theta_2$ =28.717° and  $\theta_3$ =11.504° to produce the 3 p.u. peak

fundamental at 12.5% total harmonic distortion (THD) and switching at the fundamental frequency as shown in Figure 8 (a). The SPWM method employs the carrier ( $f_{cr}$ =540Hz) comparison with the modulating wave ( $f_{m}$ =60Hz) to switch the bridges as shown in Figure 8 (b). In this case, a 20% THD is obtained with an average switching frequency of 90 Hz ( $f_{cr}$ /(m-1)) since duty cycle swapping is considered [45].

Figure 8 – Actual output voltage waveform using SHE (a) and SPWM (b) for a seven-level CHB with equal DC sources ( $V_{dc}$ =1 p.u.;  $V_{an1}$ =3 p.u. peak;  $f_m$ =60Hz;  $f_{cr}$ =540Hz).

Although attractive, due to its performance, the SHE approach has some limitations. The angles must first be calculated within the required precision and then stored in the CPU's memory. Memory size requirements will vary according to the precision for interpolation and number of angles. The modulation index can be used to control the voltage if equal steady DC sources are used. The problem becomes complex when the voltage level variations are considered as the memory

requirements grow exponentially proportional to the number of levels. An alternate methodology is required for this last case.

## 1.12 Proposed ANN-based selective harmonic minimization

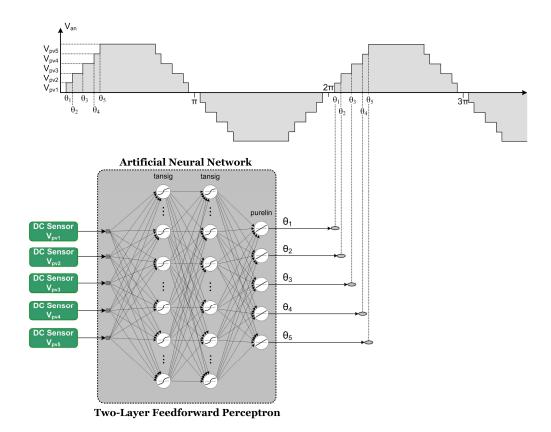

In this context, the work developed here proposes a methodology for providing switching angles for varying DC sources so that the required fundamental is achieved, the lower harmonics are minimized, and the system can be implemented in real time with low memory requirements. Genetic algorithm (GA) will be the stochastic search method to find the solution for the set of equations where the input voltages are the known variables and the switching angles are the unknown variables. With the dataset generated by GA, an artificial neural network (ANN) will be trained as one possibility to store the solutions without excessive memory storage requirements. This trained ANN will then sense the voltage of each cell and output the switching angles as shown in Figure 9. ANN and GA will be explored in the following chapters and their role in this work clarified.

Figure 9 – Proposed artificial neural network based selective harmonic minimization.

# 1.13 Chapter summary

In this chapter an introduction to solar and power converters was done. The advantages and drawback of multilevel converters were presented and the potential of this topology in solar application and harmonic control was covered. The next section of this dissertation is organized as follows. In chapter 2 a literature review of real-time harmonic control, genetic algorithm, neural networks and multilevel converters will be done. Those techniques will be applied to generate the dataset for real-time angle generation in chapter 3. A technique to estimate the individual cell voltages of a multilevel converter will be presented in chapter 4. Experimental results will be shown in chapter 5 and conclusion and future work in chapter 6.

# Chapter 2

## Real-time harmonic control literature review

In this chapter, a literature review of the current state of art on selective harmonic elimination, genetic algorithm and artificial neural network will be presented. Their role in this work will be justified and explained and their contribution to the application here will be explored.

## 2.1 Selective harmonic elimination

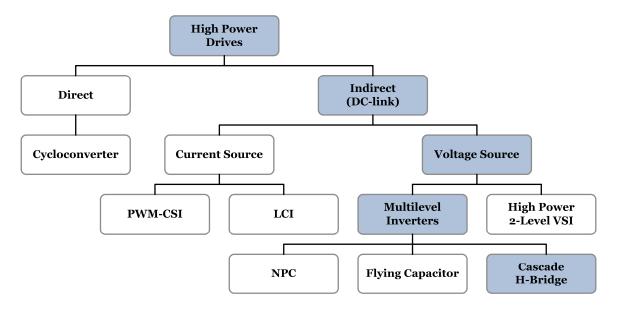

A number of technical papers using selective harmonic elimination (SHE) or minimization have been reported for fundamental frequency operation using the most common multilevel (ML) inverter topologies [1-4]. In [1] multilevel topologies such as cascade, diode-clamped, capacitor-clamped, and hybrid topologies are presented. The advantages and disadvantages, control schemes and main applications for each topology are covered in [3].

High-frequency staircase switching modulation will result in a high switching frequency for the switches in each cell at the cost of a low THD. Switching at low frequency can be achieved using multilevel topologies at near fundamental frequency by properly choosing the switching angle. A classification of converters for high power drives is presented in Figure 6. Cascade H-bridge (CHB) is among the most popular topologies used in industrial applications [3]. Its structure makes it a suitable candidate for selective harmonic control as each cell switches both the positive and negative cycle in single-phase applications.

Figure 10 – Power converter drives classification [3].

The cascade H-bridge multilevel configuration has independent DC sources for each level that may have different voltages. Figure 11 shows a seven-level CHB and its modulation at fundamental frequency. As discussed before, SHE can provide better harmonic profile and lower switching frequency. However, SPWM is easy to implement. If SHE is chosen, then a methodology for finding and storing the switching angles is required.

For different voltage levels that are steady in terms of voltage variation, SHE can be applied to the inverter at the fundamental frequency with a look-up table of stored switching angles as shown in [5]. In this way, an m-level staircase can be synthesized using (m-1)/2 separate DC sources. If the DC source voltages have a steady value, then a relation between voltage and modulation index can be found that is simple enough to be stored in a look-up table. If one of those DC voltages vary than a new relation has to be found and stored in the memory. This becomes

increasingly complex as the number of DC supplies allowed to vary increases. For example, if 32-bit floating point numbers (4 bytes per number) are considered then a set of five DC voltages and their respective switching angles will require 40 bytes (10x4) per row. This is approximately 1 KB per 26 lines.

Figure 11 – Seven-level cascade H-bridge inverter (a) and inverter modulation (b).

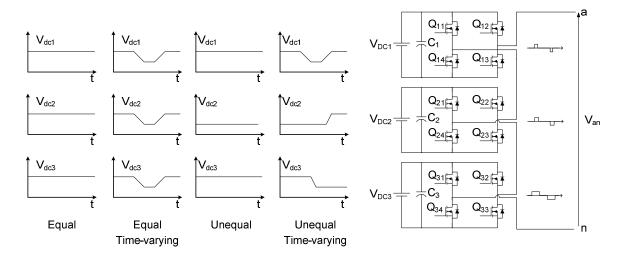

The converter DC sources might be capacitors, fuel cells, or solar panels, and they will consequently bring a voltage unbalance, depending on the system dynamics. Thus, the assumption of steady voltage sources for each level is not practical for some applications. Table 2 illustrates both cases of equal and unequal DC sources. The voltage can have equal values and vary as in the first column or it can be not balanced as shown in the second column.

Table 2. Five-level CHB under equal and unequal voltage supply.

| <b>Unbalanced voltage</b> |

|---------------------------|

| [Vdc1 Vdc2]               |

| [20V 20V]                 |

| [20V 25V]                 |

| [20V 30V]                 |

| [25V 20V]                 |

| [25V 25V]                 |

| [25V 30V]                 |

| [30V 20V]                 |

| [30V 25V]                 |

| [30V 30V]                 |

|                           |

Numerous papers have used selective harmonic elimination or minimization for controlling the switches in cascade multilevel inverters. In [6], genetic algorithms were used to determine the optimal switching angles for DC sources of equal values. A seven-level cascade inverter with three equal DC source had its fundamental kept at 120 V and the fifth and seventh harmonics eliminated. A binary-coded GA was implemented and provided.

Analytical solutions for this problem using the theory of symmetric polynomials were also reported for unipolar and bipolar schemes [7-8]. In [7] the set of equations for a three-phase seven-level case is solved using the method of

resultants from elimination theory for the polynomial form of the equations. This approach considers different voltage sources with steady values. Thus, a look-up table is needed to store the switching angles. Solutions were found for a modulation index up to 2.5 ( $m_{imax}$ =3), where the modulation index was defined as:

$$m_i = \frac{b_1}{\frac{4}{\pi} V_{dc}} \tag{17}$$

The voltage sources are said to be steady if they do not vary significantly with time. That means that a 50 V power supply will stay at 50 V with some transient voltage depending upon the load characteristics. With a steady-state voltage, the solution set for the SHE equations can be easily found and stored to be used offline. This is illustrated in [50] where a three-level flying capacitor multilevel inverter is controlled using SHE for HVDC transmission.

If the voltage sources are unequal and varying with time, the solution set increases exponentially and also the number of switching angles increase. As a consequence, the degree of the polynomials increase and more time is required to solve it. To deal with these high order polynomials, the theory of symmetric polynomials is applied to reduce the dimension of the problem [8] and find the solutions for an eleven-level inverter.

In [9] analytical solutions are found for a five- and seven-level cascade H-bridge (CHB) in which each level has five switching angles. A five-level CHB has two full bridges and with five switching angles for each cell a total of 10 switching angles are obtained. This gives a system of 10 equations to keep the fundamental voltage at

the desired level and eliminate 9 harmonic components. The five-level CHB can eliminate up to the 31<sup>st</sup> harmonic and the seven-level can eliminate up to the 43<sup>rd</sup> component. Since those papers target a three-phase application, they do not eliminate the triplen harmonics. In a three-phase application, the triplen harmonics are canceled out in the line-to-line voltage. The methodology in [8-9] cannot find solutions analytically for all the modulation index range; even subsets inside the modulation index might not have solutions. All possible solutions were found when they existed.

Figure 12 – Seven-level cascade H-bridge inverter and possible voltage profiles.

The four possibilities for the cell's voltage profile are illustrated in Figure 12. In addition to equal and unequal voltages they can also vary with time. All of the previous papers assumed that the DC sources are equal or unequal but with steady state voltages that do not vary with time. Thus, not all points in the second column of Table 2 were considered. If the voltage level changes, a new set of solutions needs to be found to keep the high-order harmonics eliminated. In addition, the number of

levels will add complexity to the problem as the equations will have higher order and take longer to solve.

One solution would be to use look-up tables as proposed in [10] that require exponentially proportional look-up tables as the number of angles and levels increases. Equal area criteria was used in [11] for a wide range of modulation indexes. The system of equations in this case is obtained by comparing the sinusoidal reference with the staircase waveform so that in the intersection they share the same area between levels. The whole set of solutions can be found by the analytical approach proposed. In [12-14], algorithms to solve for the angles have been proposed for seven- and nine-level topologies. In [13] a homotopy algorithm is proposed for finding the solutions of simplified high-order nonlinear transcendental equations. This algorithm solves for the switching angles with a simpler formulation for unequal DC sources.

In [15-16], a more general approach is formulated for the m-level n-harmonic case. Simplification of the basic SHE equations could allow the system to find solutions online for certain cases. A generalized formulation for quarter-wave symmetry is proposed in [51] for equal DC sources with a simple formulation. In this paper the solutions are still found off-line mainly to prove the methodology but they can be stored for real time operation. The bipolar and unipolar case is covered in a general approach that does not take into account waveform symmetry [15]. In this technique, angles can be arbitrarily distributed over the cycle to create the

waveform. Although a formulation is given for *m*-level *n*-switching angles, only two and three levels are discussed in detail.

In [16], a general formulation is derived for an *m*-level *n*-angles case considering quarter wave symmetry. Different voltage levels are taken in account, as well as the number of phases. Phase and line-to-line voltages and harmonics are included in the coefficients. The number of angles, number of levels, voltage levels, and target harmonics can be chosen according to the topology to be implemented. Results are shown for some selected cases. All of these papers use computationally intensive time consuming equations to solve for the angles. Those equations can easily increase in complexity as the number of levels or angles increases. The switching angles are calculated off-line in all the previous cases, as the computational burden does not allow real-time SHE.

The authors of [17-18] have developed methods to calculate the switching angles in real-time; however, their approach was not extended for unequal DC sources. In [17], the switching angles were generated comparing a reference sine wave with the voltage levels so as to calculate the volt-sec area of the waveform. This volt-sec area is matched with the volt-sec area of the staircase waveform of the inverter to obtain the switching angles. This approach performs better than the conventional one at low modulation indexes.

In [18] a method to solve for the angles was proposed with a simple set of equations that can be solved online using the Newton-Raphson method. That methodology was implemented for a seven-level CHB where a DSP board was used

to implement real-time calculation of the angles. In this case, the voltage sources are varying, but have the same value as in the first column of Table 2. Thus, all the voltage sources have the same value at any time, and they vary keeping the same relative value. In addition, THD was the target of the minimization instead of specific harmonic components. A mathematical proof was presented to show that the minimum THD obtained is the minimum achievable.

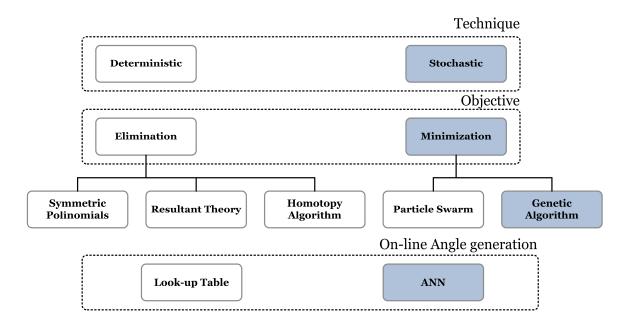

As shown before, an alternate approach to determining the optimum switching angles in real-time for varying DC sources is to calculate the switching angle solutions off-line and store the solutions in a look-up table as shown in Figure 13. Accurate representation of solutions for every different DC source case would require a huge look-up table. Such a lookup table would require an amount of memory and speed processing that can easily go beyond the processor capacity. Even then, for some operating points, the solutions might be missing and some type of interpolation would be required. For a three DC sources case [19], it is possible to avoid overhead and solution issues by using the generalization and parallelism of artificial neural networks (ANN) to quickly generate the switching angles for any number of levels and switching angles.

Figure 13 – Techniques employed in selective harmonic elimination and minimization.

In this work instead of using a look-up table, an ANN is employed, which, if well trained, has the inherent capability of generalizing solutions [19]. The missing points in the solution set are handled using genetic algorithms. If the correct range of data is used for training, and if the ANN is not over-trained, the network will extrapolate properly. Since ANN runs quickly, switching angles can be quickly determined to establish real-time control.

#### 2.2 Solar cell model

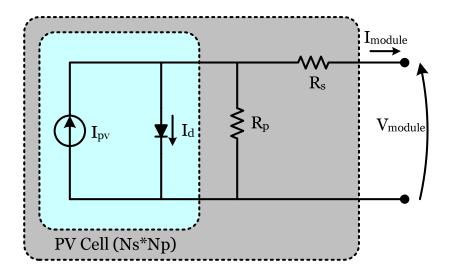

A suitable model was derived to simulate the PV module behavior that reflects the experimental curves of the solar panel with relative accuracy. The single diode model was adopted, as shown in Figure 10, to simulate the PV module under different irradiance and temperature levels. A number of approaches and models

can be found in the literature to analyze the behavior of PVs that can grow in complexity in case better accuracy is needed [20-22].

The suitable model then becomes application dependent. In [21] a more complex model is derived that takes into account temperature, irradiance, and wind speed for long term and transient analysis. A model was developed in [22] to consider and study the shading effect on solar panels connected in series. Wind speed and other features add in complexity for the model, reflecting a more realistic behavior. Those features are not the main focus in this work. The main parameters desired are the influence of temperature and irradiance on the panel's voltage and current.

The PV cell model used in this work is a more intuitive model based on the single diode cell in Figure 14 and derived in [23]. The inputs used are those obtained directly from the PV module datasheet parameters, which are readily available from a panel's manufacturer. This model greatly simplifies the modeling task, once the iterations and nonlinear equations are solved. Equation (18) is the basic formula and the solar panel's datasheet provides the parameters to solve for the unknowns.

Figure 14 – Photovoltaic cell single diode model representation.

$$I = I_{pv} - I_0 \left[ e^{\left( \frac{V + R_S I}{V_r a} \right)} - 1 \right] - \frac{V + R_S I}{R_p}$$

(18)

where,

*I*: photovoltaic module output current

*V*: photovoltaic module output voltage

$I_{pv}$ : photovoltaic current

$I_0$ : saturation current

$V_t$ : thermal voltage

$R_s$ : equivalent series resistance

$R_p$ : equivalent parallel resistance

#### a: diode ideality constant

The results using this approach will be presented in the next chapter. The fill factor is another important parameter for solar panel modeling. It is defined as the percentage of area covered by voltage  $(V_{mpp})$  and current  $(I_{mpp})$  at the maximum power point and the area covered by open circuit voltage  $(V_{oc})$  and short circuit current  $(I_{sc})$ . It is defined as shown in Equation (19) [52].

$$fill\ factor = \frac{P_{\text{max}}}{I_{sc}V_{oc}} = \frac{I_{mpp}V_{mpp}}{I_{sc}V_{oc}}$$

(19)

Since this methodology takes into account all of the parameters in Equation 19, the fill factor will naturally match in all conditions.

# 2.3 Artificial neural networks

Artificial neural networks have found a number of applications in engineering, such as pattern recognition, control and classification, and others [24-27]. One of the main factors for choosing this technique is its generalization ability in nonlinear problems that are complex in nature and/or calculation intensive [28].

Artificial neural networks are computational models that were inspired by biological neurons [24]. They use a series of nodes with interconnections where mathematical functions are applied to do an input/output mapping. That means, for example, the information contained in a lookup table can be stored in an ANN. The challenge is to know how many neurons will be needed to train an ANN for a specific application. This will be dependent on complexity of the input/output relation,

number of inputs and number of outputs. This requires some trial and error in the first stage until a suitable ANN is found [25-26].

An important feature of the ANN that makes it suitable for this problem is its flexibility to generalize (interpolate) its output inside its domain, as well as work with the nonlinear nature of the problem [29-32]. The fundamentals are presented in [30-31], while application is the focus in [29], where many inverter control examples are covered, as well as training and types of ANNs.

The size of the ANN has to be determined in such a way to have maximum performance with minimum number of neurons. That becomes more challenging as the data set size increases and how complex is the function to be mapped. Methodologies to determine ANN topology has been proposed in [53]. One approach is to grow an ANN by increasing the number of neurons, training, and evaluating the performance. This is done until the required performance is obtained to determine the minimum ANN. That strategy will be employed here for a two layer ANN.

The data set presented to the ANN is not complete in terms of resolution, and not all combinations or solutions were obtained by the GA. For that reason ANN is employed here since it has enough flexibility to interpolate and extrapolate the results. Chapter 3 will cover ANN performance and results in more detail. The main reason to use ANN is the possibility of real-time angle generation. The ANN features, for example, make it suitable for common problems encountered in power electronics such as fault detection [33] and harmonic diagnostics [34].

ANNs are generally time consuming to train but fast to run and can be easily parallelized once accordingly trained. Its weights can be stored in a flash memory of a CPU, DSP, or FPGA for real-time processing of the outputs. It has the potential to replace lookup tables since an increase in the number of DC sources in the problem will exponentially increase the size of the look-up table. Look-up tables require extrapolation and comparisons, leading to time consuming algorithms. In addition, analytical approaches must deal with the computational time required for the task. In both cases, a methodology has to be found to handle the no-solution range. One promising candidate is genetic algorithms.

## 2.4 Genetic algorithms

Different approaches can be used to solve for the angles and the choice is application dependent. As the number of dimensions increases, the complexity and time to solve the equations increase. Analytical or numerical approaches may need computational power beyond current mathematical software. That is the case illustrated in [54] where the harmonic minimization problem is solved using Particle Swarm Optimization (PSO) to find 15 switching angles. Another stochastic technique is Genetic Algorithm which will be adopted in this work mainly because it is well known and documented technique with a matured Matlab toolbox.

Genetic algorithm (GA) is a technique based on the evolutionary process, where individuals are constantly adapting to a changing environment in order to survive [36]. It mimics the behavior of populations during generations, based on the idea that the best-suited individuals have greater probability to survive and pass on

their genetic codes to their descendants. Through generations, the quality of the population tends to improve. The obtained best individual is an end product containing the best elements of previous generations, where the attributes of a stronger individual are carried forward into the following generation [37-42].

In the SHE problem environment, many analytical solutions have been reported, as presented previously. If it is desired to keep the fundamental and eliminate the lower-order harmonics, the analytical formulation will solve the problem faster, and a more complete solution can be achieved. This technique (GA) is used for its ability to deal with complicated problems where analytical formulation is not yet possible or practical [37-38]. In the multiobjective SHE problem, if there is no set of angles that will satisfy the SHE equation, the analytical approach will not return an answer. The GA, on the other hand, will always return an answer that will not solve exactly for all variables but instead will give answers that are very close. Thus, instead of eliminating the harmonics it minimizes them [39].

#### 2.5 Final remarks

The proposed approach in this work will be done in two steps: First a genetic algorithm (GA) will be implemented to find the switching angles (off-line) for a set of pre-determined input voltages for an 11-level cascade inverter; Then, with the previous data set, the ANN will be trained to give the set of angles for each voltage situation in real-time.

An important feature of the GA for this approach is that for the range space where there is no analytical solution the GA will find the nearest solution providing a smooth data set that is desired for the neural network training. In addition, such a complex technique can find a solution that might not be found by the analytical solution that is acceptable in terms of the current standards. For example, GA might find a solution that produces an output fundamental voltage of 110 V within  $\pm 5\%$  while other analytical approaches find no solution or states that there is no solution.

## 2.6 Chapter summary

In this chapter, a thorough literature review was conducted in the area of harmonic elimination, genetic algorithms, and artificial neural networks. The technique proposed in this work was based on an extensive research of previous work. Solar cell models were revised and a model fit for the work requirement was proposed. GA and ANN were reviewed and its application to selective harmonic minimization has shown to be of great potential for real time angle generation. This is one of the main challenges that have not yet been proposed.

The techniques previously presented will be applied to generate the dataset for real-time angle generation in chapter 3.

# Chapter 3

# Dataset and real-time angle generation

This chapter will cover the theory behind genetic algorithms and neural networks. This will include their main features and drawbacks, as well as an illustrative example to prove their efficacy.

## 3.1 Genetic algorithms

A genetic algorithm (GA) is a stochastic search method shown to be well suited for problems where many global minimum and/or highly dimensional search spaces are possible. Each individual of a set has an associated cost value, referred to as "fitness function" that is a measure of how well this individual performs in the population. In previous works, analytical solutions were found partially in the range space of input voltage variation; however, this approach still uses GA first, because this range is used to calibrate it to perform in the range where there is no analytical solution. Therefore, the correct GA parameters are found to bias the algorithm through the desired solution. Also, it is possible to adjust the algorithm to arrive at its solutions looking at the previous results giving a future solution, or switching angles, in this case, which are smooth so that the ANN can be easily trained. The basic continuous GA execution flow is shown in Figure 15.

Figure 15 – Flow chart of a continuous GA.

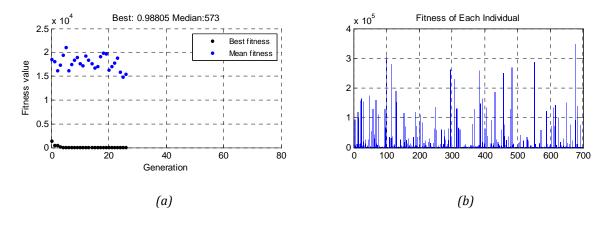

The algorithm starts with a population of individuals that represent a set of possible solutions to the problem. The fitness function will return a value that gets closer to zero as the five set of SHE equations (out of Equations (11) to (16)) gets closer to zero. A fitness equal to zero means that an exact solution was found. Next, the genetic operators will act in the current population to generate the next

population using decision rules, so that on average, the solutions (individuals) will be improved. The new population is again evaluated (fitness), and if a satisfactory solution is found, the algorithm stops. In case the stop criteria are not satisfied, the algorithm keeps evolving its population until this occurs.

Deterministic methods use information extracted from the problem such as the gradient or the hessian matrix to determine the next point. Stochastic methods, such as GA, base searches in a set of stochastic decision rules to determine the next point [39]. Those decision rules and GA steps are explained in the following sections. The algorithm was written using Matlab toolbox for GA implementation. This toolbox has the main GA functions and routines implemented with a number of visualization options to help fine tune the GA for a specific problem. A code was written for the fitness function and the different settings for the SHE challenge were investigated. The following sections will show the main GA settings followed by a GA run to prove the settings chosen can find the solutions.

#### 3.1.1 Individual representation

Many options exist for representing a single individual. In the original work by Goldberg [36], binary representation was used to introduce and explain the concept. Integer numbers, vectors, matrices or floating point numbers could represent a single individual inside the population. This work employed real-valued representation, as continuous or real-valued GA better relates the problem to its representation, and higher precision can be achieved compared to binary representation.

#### 3.1.2 Selection operator

The next step requires choosing from the pool of individuals those who will reproduce based on their fitness. The fitness function describes how well the actual solution will perform. If a minimization problem is being analyzed, the fittest individuals are those nearest a global minimum, or that best satisfy the set of equations.

Many methods have been used as the selection operator, such as roulette, scaling techniques, tournament selection, elitist models and rank methods. In the roulette method adopted here, each individual is assigned a probability  $P_i$  of being chosen as presented below:

$$P_i = \frac{F_i}{\sum_{j=1}^{PopSize} F_j} \tag{20}$$

The fittest individuals will have a better chance to be chosen, as their fitness  $F_i$  will give them a bigger slot  $(P_i)$  in the roulette .

One disadvantage of this method arises when an individual with a very high fitness appears in the population and is more likely to have a comparatively higher probability. The population is then steered toward that individual, causing the algorithm to stop exploiting and exploring the search space, ultimately leading to premature convergence. Such behavior was observed in this work as premature convergence to local minima, so an alternative roulette with normalized ranking was used instead.

Using normalized geometric ranking rather than the roulette will minimize convergence problems. In this approach, the fitness function is used to sort individuals in the population and the probability of each individual  $P_i$  is chosen according to Equation (21).