University of Tennessee, Knoxville Trace: Tennessee Research and Creative Exchange

#### **Doctoral Dissertations**

Graduate School

12-2010

# Characterization and Fabrication of Active Matrix Thin Film Transistors for an Addressable Microfluidic Electrowetting Channel Device

Seyeoul Kwon University of Tennessee - Knoxville, skwon1@utk.edu

#### **Recommended** Citation

Kwon, Seyeoul, "Characterization and Fabrication of Active Matrix Thin Film Transistors for an Addressable Microfluidic Electrowetting Channel Device." PhD diss., University of Tennessee, 2010. https://trace.tennessee.edu/utk\_graddiss/892

This Dissertation is brought to you for free and open access by the Graduate School at Trace: Tennessee Research and Creative Exchange. It has been accepted for inclusion in Doctoral Dissertations by an authorized administrator of Trace: Tennessee Research and Creative Exchange. For more information, please contact trace@utk.edu.

To the Graduate Council:

I am submitting herewith a dissertation written by Seyeoul Kwon entitled "Characterization and Fabrication of Active Matrix Thin Film Transistors for an Addressable Microfluidic Electrowetting Channel Device." I have examined the final electronic copy of this dissertation for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Doctor of Philosophy, with a major in Materials Science and Engineering.

Philip D. Rack, Major Professor

We have read this dissertation and recommend its acceptance:

Michael L. Simpson, Thomas T. Meek, Syed K. Islam

Accepted for the Council: Carolyn R. Hodges

Vice Provost and Dean of the Graduate School

(Original signatures are on file with official student records.)

To the Graduate Council:

I am submitting herewith a dissertation written by Seyeoul Kwon entitled "Characterization and Fabrication of Active Matrix Thin Film Transistors for an Addressable Microfluidic Electrowetting Channel Device." I have examined the final electronic copy of this dissertation for form and content and recommend that it be accepted in partial fulfillment of the requirements for the degree of Doctor of Philosophy, with a major in Materials Science and Engineering.

Philip D. Rack, Major Professor

We have read this dissertation and recommend its acceptance:

Michael L. Simpson

Thomas T. Meek

Syed K. Islam

Accepted for the Council:

<u>Carolyn R. Hodges</u> Vice Provost and Dean of Graduate School

(Original signatures are on file with official student records.)

Characterization and Fabrication of Active Matrix Thin Film Transistors for an Addressable Microfluidic Electrowetting Channel Device

> A Dissertation Presented for the Doctor of Philosophy Degree The University of Tennessee, Knoxville

> > Seyeoul Kwon December 2010

Dedicated to Jung Yun, June Esther, and my parents

#### ABSTRACT

The characterization and fabrication of active matrix thin film transistors (TFTs) has been studied for an addressable microfluidic electrowetting channel device as application. A new transparent semiconductor material, Amorphous Indium Gallium Zinc Oxide (a-IGZO), is used for TFT, which shows high electrical performance rather than amorphous silicon based TFT; higher mobility and even higher transparency. The purpose of this dissertation is to optimize each TFT process including the optimization of a-IGZO properties to achieve robust device for application. To minimize hysteresis of TFT curves, the gate dielectric is discussed extensively in this dissertation. By optimizing gas ratio of  $NH_3/SiH_4$ , it is found that the TFT with  $NH_3$  rich  $SiN_x$  gate dielectric deposited with  $NH_3/SiH_4 = 5.1$  and stoichiometric SiO<sub>2</sub> demonstrates best condition to reduce hysteresis. a-IGZO films is investigated as a function of power and substrate bias effect which affects to electrical performance; the higher power and substrate bias increase the carrier density in the film and mainly cause threshold voltage( $V_T$ ) to shift in the negative gate voltage direction and mobility to increase, respectively. In addition, the powerful method to estimate the electrical properties of a-IGZO is proposed by calculating O<sub>2</sub> and IGZO flux during sputtering in which the incorporation ratio with O<sub>2</sub>/IGZO ≈1 demonstrates the optimized a-IGZO film for TFT. It is confirmed that both physical and chemical adsorption affects the electrical property of a-IGZO channel by studying TFT-IV characteristics with different pressure and analyzing X-ray photoelectron spectroscopy (XPS), which mainly affects the V<sub>T</sub> instability. The sputtered SiO<sub>2</sub> passivation shows better electrical performance. To

achieve electrically compatible (lower back channel current) a-IGZO film to SiO<sub>2</sub> sputter passivated device, a-IGZO TFTs require oxygen rich a-IGZO back channel by employing two step a-IGZO deposition process ( $2^{nd}$  10nm a-IGZO with PO<sub>2</sub> = 1.5mTorr on 1<sup>st</sup> 40nm a-IGZO with PO<sub>2</sub>=1mTor). Electrowetting microfluidic channel device as application using a-IGZO TFTs is studied by doing preliminary test. The electrowetting channel test using polymer post device platform is candidate for addressable electrowetting microfluidic channel device driven by active matrix type a-IGZO TFT.

#### ACKNOWLEDGEMENTS

I thank God to give me opportunity to study and take care of my family so far. I would like to thank my advisor Dr. Philip D. Rack for his support, valuable advice, and encouragement to study. I also would like to thank Dr. Jason Heikenfeld and Dr. Manjeet Dhinsha, and Dr. Ian Papautsky in University of Cincinnati. I have been happy to work together. The members of my dissertation committee, Dr. Michel L. Simpson, Dr. Thomas T. Meek, and Dr. Syed K. Islam, have generously served their expertise to my study. I would like to thank Dr. Seung-Ik Jun for giving valuable mentoring and counsel and I also appreciate Dr. Jung won Park for spending valuable time to work together. I would like to thank the members of our research group for their contribution to my work, Dr. Joo Hyon Noh for his valuable advices, Dr. Jason Fowlkes, Dr. Matthew Lassiter, Dr. Daryl Smith, Dr. Nicholas Roberts, Jonathan Peak, Yueying Wu, Siwei Tang, and especially Jiyong Noh for helping me. I am greatly appreciate people who works in Center for Nanophase Materials Science in Oak Ridge National Laboratory for helping me to work, Dr. Laura Edwards, Darrell Thomas, Daryl Briggs, Dale Hensley, Teri Subich, Dr. Scott Retterer, and Dr. Nickolay Lavrik. I would like to thank Dr. Jae Kyeung Jeong in Inha University and Jaechul Park in Samsung in Korea, giving me valuable tips to approach study and also thank my former bosses in Samsung Mobile Display, Dr. Yeon-Gon Mo and Dr. Ki-Yong Lee. I would like to thank Dr. Duck-Kyun Choi, graduate advisors in Korea,. Most of all, I would like to thank my family, Jun Yun Hwang have given endless love, support, and pray for me and June Esther Kwon have given me happy to see her growth. I am especially grateful for the support and pray from my parents in Korea.

## TABEL OF CONTENTS

# **Chapter 1 Introduction**

| 1.1 Motivation of this work                                                                                                                                                       | 1                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 1.2 Thin film transistor (TFT)                                                                                                                                                    | 4                          |

| 1.2.1 Historical background                                                                                                                                                       | 4                          |

| 1.2.2 Basic TFT operation                                                                                                                                                         | 4                          |

| 1.2.3 TFT structures                                                                                                                                                              | 7                          |

| 1.2.4 Electrical characterization of TFT                                                                                                                                          | 11                         |

| 1.2.5 Oxide semiconductor based TFT                                                                                                                                               | 16                         |

| 1.2.5.1 Overview of transparent oxide semiconductors                                                                                                                              | 16                         |

| 1.2.5.2 Electronic structure and carrier transport in oxide                                                                                                                       |                            |

| semiconductor                                                                                                                                                                     | 16                         |

| 1.2.5.3 Amorphous indium gallium zinc oxide TFT (a-IGZO TFT)                                                                                                                      | 24                         |

|                                                                                                                                                                                   |                            |

| 1.2.5.3.1 Structural and optical properties                                                                                                                                       |                            |

| 1.2.5.3.1 Structural and optical properties                                                                                                                                       | 24                         |

|                                                                                                                                                                                   | 24                         |

| 1.2.5.3.2 Carrier conduction                                                                                                                                                      | 24<br>27                   |

| 1.2.5.3.2 Carrier conduction                                                                                                                                                      | 24<br>27<br>29             |

| 1.2.5.3.2 Carrier conduction                                                                                                                                                      | 24<br>27<br>29<br>29       |

| 1.2.5.3.2 Carrier conduction         Chapter 2 Device fabrication and characterization         2.1. Fabrication of TFT         2.1.1 Gate electrode                               | 24<br>27<br>29<br>29<br>32 |

| 1.2.5.3.2 Carrier conduction         Chapter 2 Device fabrication and characterization         2.1. Fabrication of TFT         2.1.1 Gate electrode         2.1.2 Gate dielectric | 24<br>27<br>29<br>32<br>32 |

| 2.1.6 Post annealing                                                             |

|----------------------------------------------------------------------------------|

| 2.2. Conclusion                                                                  |

| Chapter 3 Gate dielectric                                                        |

| 3.1 Introduction                                                                 |

| 3.2 Experimental45                                                               |

| 3.3 Result and discussion48                                                      |

| 3.4 Conclusion61                                                                 |

| Chapter 4 Semiconductor; a-IGZO                                                  |

| 4.1 Basic a-IGZO TFT properties with sputtering parameters                       |

| 4.1.1 Introduction62                                                             |

| 4.1.2 Experimental62                                                             |

| 4.1.3 Results and discussion63                                                   |

| 4.1.4 Conclusion83                                                               |

| 4.2 Quantitative calculation of oxygen incorporation in sputtered IGZO films and |

| the impact on the electron transport and TFT properties                          |

| 4.2.1 Introduction                                                               |

| 4.2.2 Experimental85                                                             |

| 4.2.3 Results and discussion85                                                   |

| 4.2.4 Conclusion                                                                 |

| 4.3 The device characteristics of a-IGZO TFTs sputter deposited with different   |

| substrate biases                                                                 |

| 4.3.1 Introduction                                                               |

| 4.3.2 Experimental                                                             |

|--------------------------------------------------------------------------------|

| 4.3.3 Results and discussion101                                                |

| 4.3.4 Conclusion                                                               |

| Chapter 5 Passivation                                                          |

| 5.1 Introduction 111                                                           |

| 5.2 Experimental113                                                            |

| 5.3 Results and discussion114                                                  |

| 5.4 Conclusion                                                                 |

| Chapter 6 Application: Microfluidic electrowetting channel device              |

| 6.1 Introduction132                                                            |

| 6.2 Generation I device platform (VACNFs electrowetting posts + a-Si TFT) 136  |

| 6.2.1 Passive electrowetting scaffolds136                                      |

| 6.2.2 Process issues for passive and active addressable electrowetting         |

| scaffolds 140                                                                  |

| 6.3 Generation II device platform (photoactive polymer posts + a-IGZO TFT) 142 |

| 6.3.1 Electrowetting test using polymer posts142                               |

| 6.4 Design and issues of addressable electrowetting microfluidic device        |

| 6.5 conclusion150                                                              |

| Chapter 7 Conclusions                                                          |

| * List of Reference                                                            |

| *Appendix: Run sheet for a-IGZO TFT168                                         |

# LIST OF TABLES

| Table 1-1. Comparison of silicon based semiconductor TFT and oxide based                                                        |

|---------------------------------------------------------------------------------------------------------------------------------|

| semiconductor TFT3                                                                                                              |

| Table 3-1. Deposition conditions and resulting optical and electrical properties of                                             |

| different stoichiometric SiN <sub>x</sub> and SiO <sub>2</sub> films47                                                          |

| Table 3-2 Capacitance and dielectric properties with different dielectrics 60                                                   |

|                                                                                                                                 |

| Table 4-1. Summary of electrical characteristics of a-IGZO TFT different oxygen                                                 |

| partial pressure and rf power at $V_{DS}$ = 5.1V at the TFT dimension of                                                        |

| W/L=70μm/6μm67                                                                                                                  |

| Table 4-2. Electrical properties ( $\mu_{FE,}$ S, V <sub>T</sub> , and I <sub>off</sub> /I <sub>off</sub> ) of a-IGZO TFTs with |

| oxygen partial pressure and deposition rate                                                                                     |

| Table 4-3. Electrical properties ( $\mu_{FE,}$ S, I $_{off}$ and V_T) of a-IGZO TFTs, surface                                   |

| roughness[root mean square(RMS)], deposition rate, refractive index                                                             |

| (n), and stress of a-IGZO film as function of substrate bias voltage 105                                                        |

| Table 5-1. Experimental plan to study passivation with different process condition 122                                          |

| Table 7-1. The summary of optimum condition for each process of a-IGZO TFT                                                      |

| to achieve robust device155                                                                                                     |

### LIST OF FIGURES

| Figure 1-1. (a) basic structure of a TFT and corresponding energy band diagram                   |

|--------------------------------------------------------------------------------------------------|

| as viewed through the gate with bias conditions: (b) equilibrium, (c) $V_{\text{GS}}$            |

| < 0 V, and (d) $V_{GS}$ > 0V                                                                     |

| Figure 1-2. Cross section of the various TFT structures: (a) coplanar type TFT                   |

| structure, (b) Inverted staggered type TFT structure, (c) Normal                                 |

| staggered type TFT structure9                                                                    |

| Figure 1-3. Two type of TFT structures in inverted staggered type TFT structure                  |

| and (b) E/S type TFT structure10                                                                 |

| Figure 1-4. Cross-sectional view of the channel region of a TFT used to derive                   |

| the gradual channel approximation12                                                              |

| Figure 1-5. General transfer characteristic of a-IGZO for graphical definition of I              |

| <sub>ON/OFF</sub> and (b) subthreshold gate swing (S)15                                          |

| Figure 1-6.Graphhical extrapolation of $V_{T}$ in the saturation region                          |

| Figure 1-7.Schematic orbital drawings for the carrier transport paths at the                     |

| conduction band bottoms in amorphous and crystalline                                             |

| semiconductors; (a) crystalline and (c) amorphous silicon with covalent                          |

| bonds with strongly directive $sp^3$ orbitals and (b) crystalline and (d)                        |

| amorphous oxide semiconductors with post-transition-metal cations 20                             |

| Figure 1-8. Formation of energy gap, (a) covalent semiconductor (silicon), and (b,               |

| c) ionic semiconductor (M <sup>2+</sup> O <sup>2-</sup> ), (b) Energy levels of neutral atoms in |

| vacuum, (c) The atoms are ionized I a crystal structure and form large           |

|----------------------------------------------------------------------------------|

| Madelung potential and large bandgap21                                           |

| Figure 1-9.Relationship between Hall mobility and electron concentration for     |

| single-crystalline InGaO $_3$ (ZnO) $_5$ (sc-IGZO) and a-IGZO film22             |

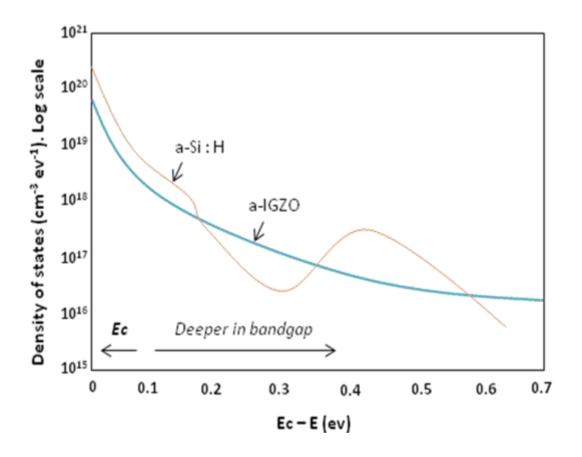

| Figure 1-10.Subgap trap density of states in a-IGZO in comparison with a-Si:H 23 |

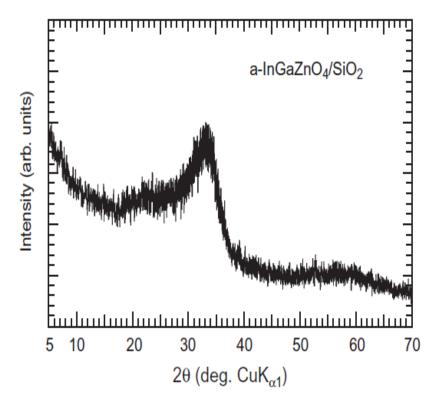

| Figure 1-11. X-ray diffraction pattern of the a-IGZO film deposited on SiO2 a    |

| glass substrate at room temperature25                                            |

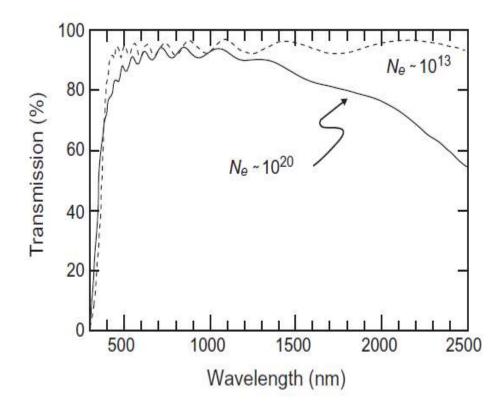

| Figure 1-12. Optical transmission spectra of a-IGZO film with different carrier  |

| concentration ~ $10^{13}$ cm <sup>-3</sup> and ~ $10^{20}$ cm <sup>-3</sup>      |

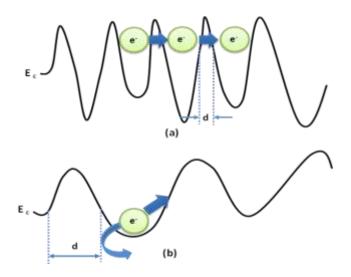

| Figure 1-13. Energyband diagram: (a) hopping conduction by quantum               |

| mechanical tunneling and (b) conduction by percolation mechanism 28              |

| Figure 1-14.The conduction model suggested by Nomura, et al. (a) The Fermi       |

| level (blue plane) is very low than conduction band edge, (b) located            |

| above the edge of conduction (percolation conduction), and high                  |

| enough on the edge of conduction(degenerate conduction)                          |

| Figure 2-1. a-IGZO TFT fabrication with BCE type of a-IGZO TFT structure; (a)    |

| gate dielectric/ patterned gate electrode (Cr) on buffer SiO <sub>2</sub> /Si    |

| substrate, (b) sputtered a-IGZO island formation, (c) source-drain               |

| electrode formation by wet etching, (d) passivation deposition and via           |

| hole patterning by dry etching, and (e) cross-section SEM image of               |

| TFT                                                                              |

| Figure 2-2 The etch depth of a-IGZO as function of time in the BOF (0.1%)        |

| Figure 3-1.Schematic transfer characteristics ( $I_{DS}$ vs. $V_{GS}$ ) of n-type                                      |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| semiconductor TFT, (a) lower BSC hysteresis and (b) higher BSC                                                         |  |  |  |  |

| hysteresis                                                                                                             |  |  |  |  |

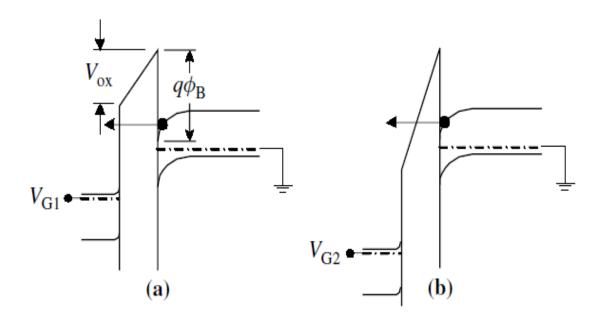

| Figure 3-2.MOS band diagrams for (a) Vox < $q\Phi_B$ (direct tunneling) and (b) Vox >                                  |  |  |  |  |

| q $\Phi_{B}$ (Fowler-Nordheim tunneling)                                                                               |  |  |  |  |

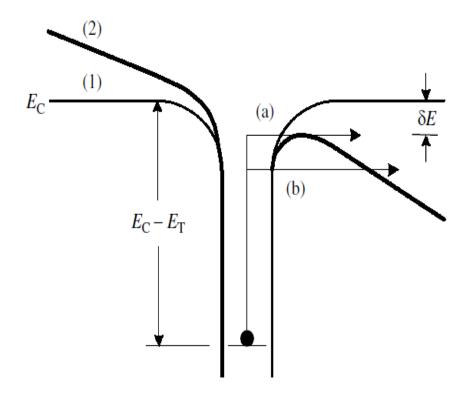

| Figure 3-3. Electron energy diagram in equilibrium (1) and in the presence of an                                       |  |  |  |  |

| electric field (2) showing field-enhanced electron emission: (a) Poole-                                                |  |  |  |  |

| Frenkel emission, (b) phonon-assisted tunneling                                                                        |  |  |  |  |

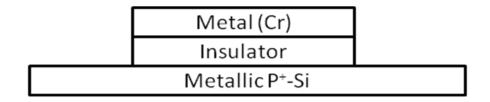

| Figure 3-4. The metal-insulator-semiconductor device structure for capacitance-                                        |  |  |  |  |

| voltage (CV) and current-voltage (IV) measurement                                                                      |  |  |  |  |

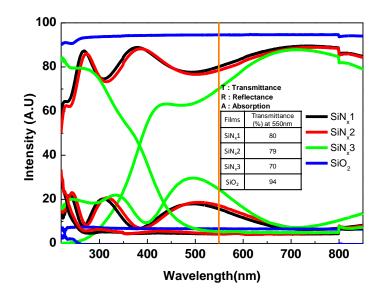

| Figure 3-5. The transmittance with different gate dielectric of $SiN_x1(200nm)$ ,                                      |  |  |  |  |

| SiN <sub>x</sub> 2(200nm), SiN <sub>x</sub> 3(200nm), and SiO <sub>2</sub> (100nm), the inset compares                 |  |  |  |  |

| the transmittance at 500nm49                                                                                           |  |  |  |  |

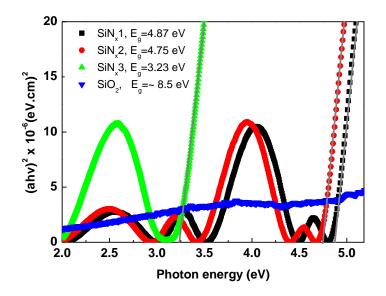

| Figure 3-6 Optical band extraction from $(\alpha hv)^2$ plotted as a function of photon                                |  |  |  |  |

| energy for SiN <sub>x</sub> 1, SiN <sub>x</sub> 2, SiN <sub>x</sub> 3, and SiO <sub>2</sub> with 200nm in thickness 49 |  |  |  |  |

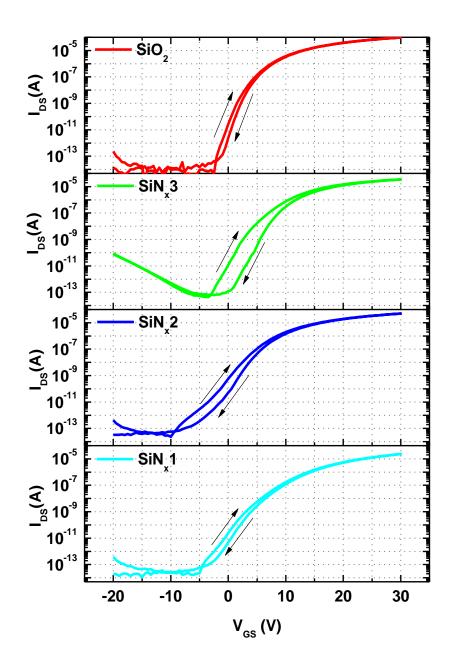

| Figure 3-7. The representative transfer curves with different stoichiometric $SiN_{x}$                                 |  |  |  |  |

| and SiO <sub>2</sub> as gate dielectric at $V_{DS} = 5.1V$                                                             |  |  |  |  |

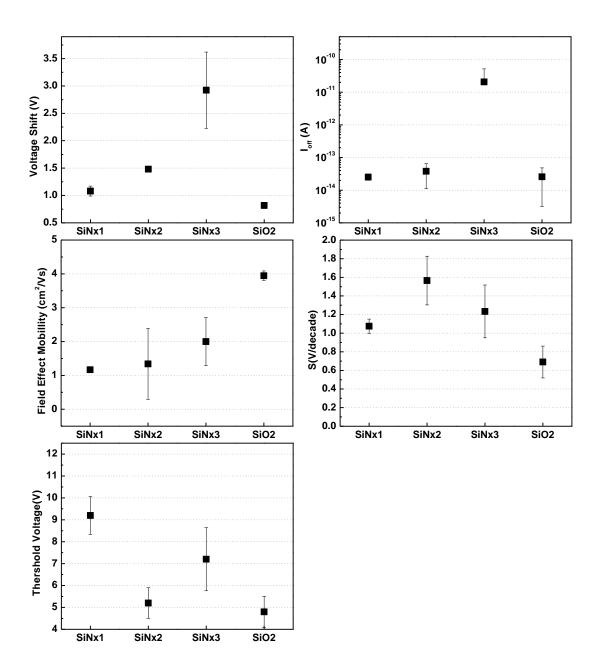

| Figure 3-8. Comparision of electrical performance of a-IGZO TFT52                                                      |  |  |  |  |

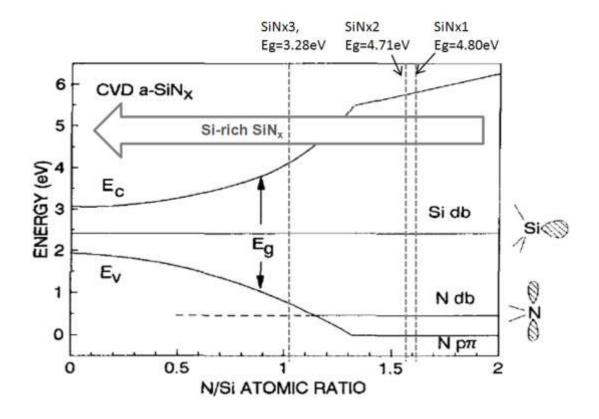

| Figure 3-9. Band diagram for amorphous $SiN_x$ with different N/Si atomic ratio 54                                     |  |  |  |  |

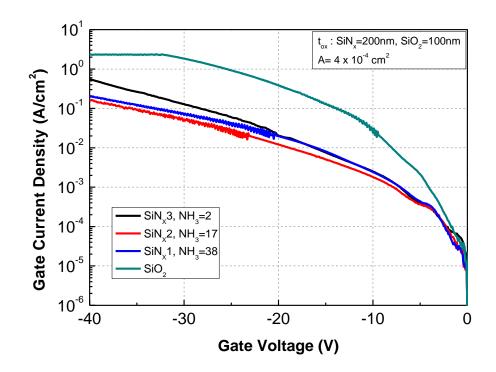

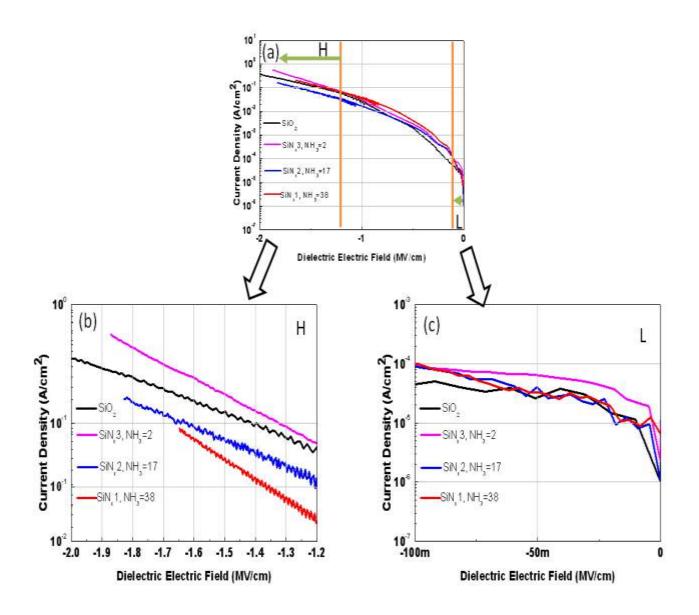

| Figure 3-10. The averaged gate current density as a function of gate voltage with                                      |  |  |  |  |

| different gate dielectrics56                                                                                           |  |  |  |  |

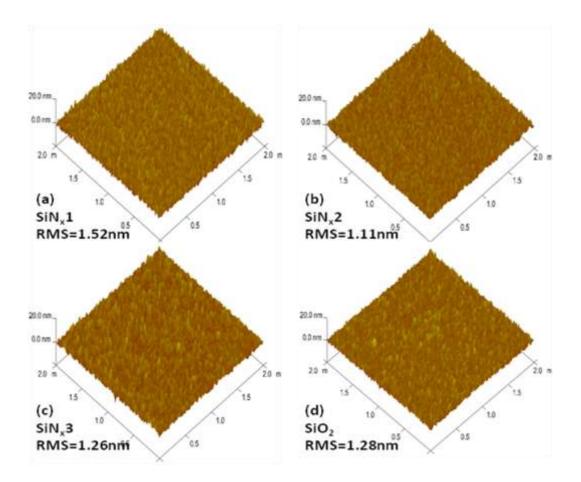

Figure 3-12. The surface roughness of gate dielectrics using atomic force microscopy(AFM), (a) SiN<sub>x</sub>1, (b) SiN<sub>x</sub>2,(c) SiN<sub>x</sub>3, and (d) SiO<sub>2</sub>......60

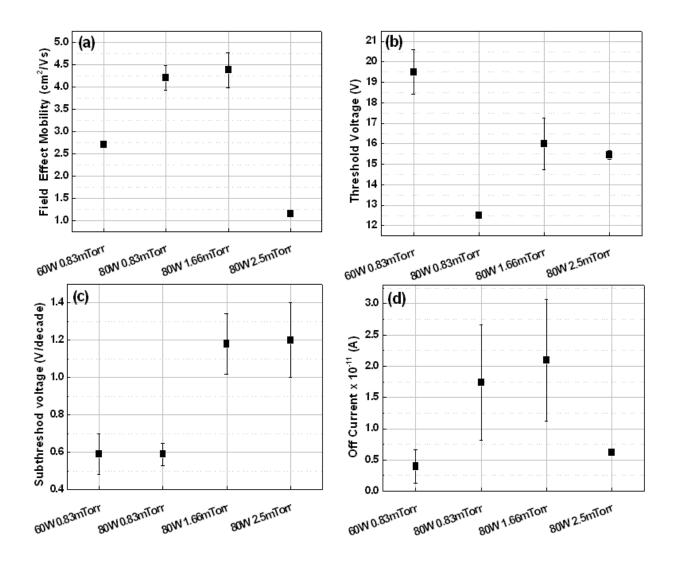

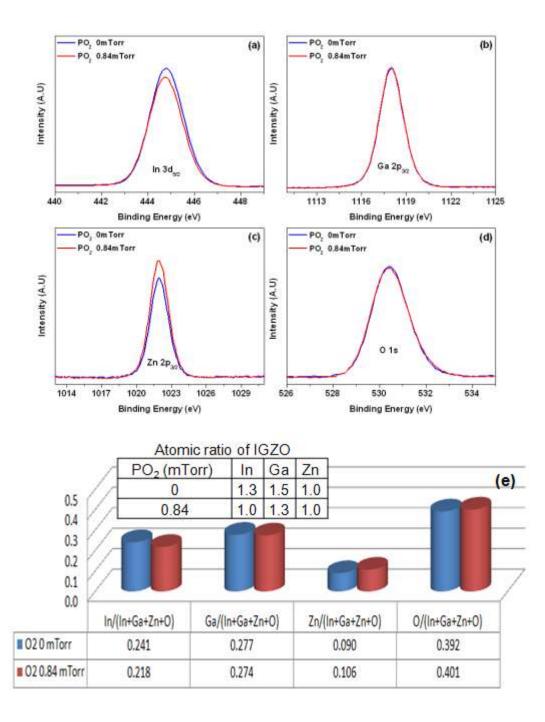

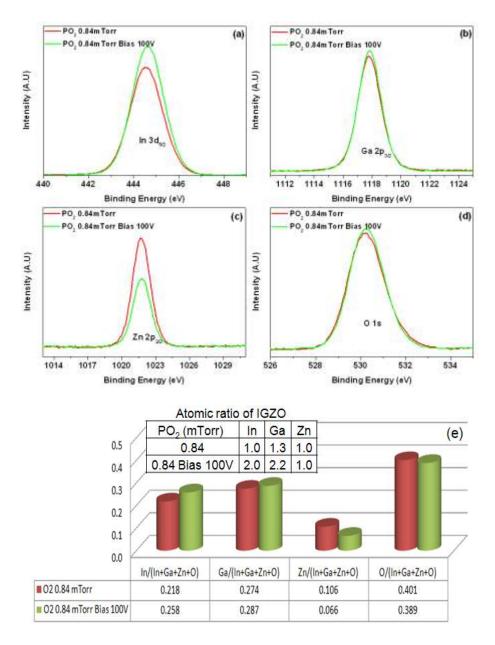

Figure 4-3. Core-level XPS spectra of the a-IGZO films, (a),(b),(c), and (d) and the atomic concentration ratios obtained from the area of XPS spectra curves, (e) which is normalized by total atom concentration for comparison with oxygen pressure; PO<sub>2</sub> = 0 mTorr verse PO<sub>2</sub> = 0.84 mTorr.

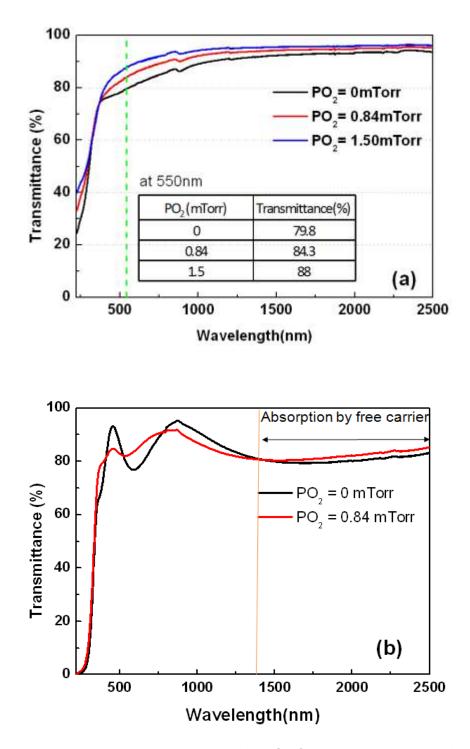

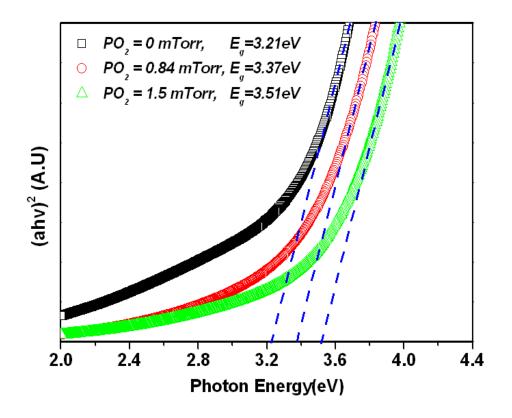

Figure 4-4. a) the optical transmission spectra of a-IGZO films sputtered in different PO<sub>2</sub> and (b) the decreased transmittance by free carrier

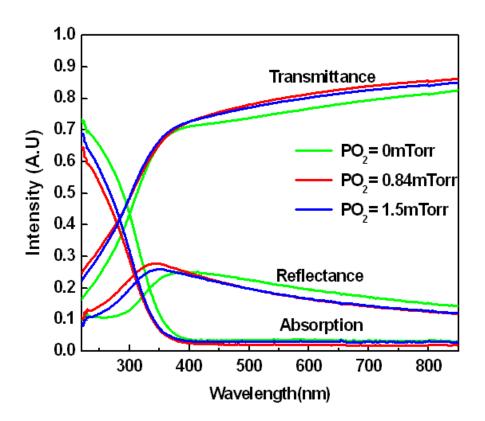

| Figure 4-5. The plot of transmittance, reflectance, and absorption in the range of                       |

|----------------------------------------------------------------------------------------------------------|

| wave length from 220 nm to 880 nm (UV-VIS range) with different                                          |

| oxygen partial pressure (PO <sub>2</sub> =0 mTorr, PO <sub>2</sub> =0.84 mTorr, and PO <sub>2</sub> =1.5 |

| mTorr)75                                                                                                 |

| Figure 4-6. Optical band gap with $PO_2$ ; optical band gap was increased from 3.21                      |

| eV to 3.51 eV for PO <sub>2</sub> =0 mTorr and PO <sub>2</sub> =1.5mTorr, respectively77                 |

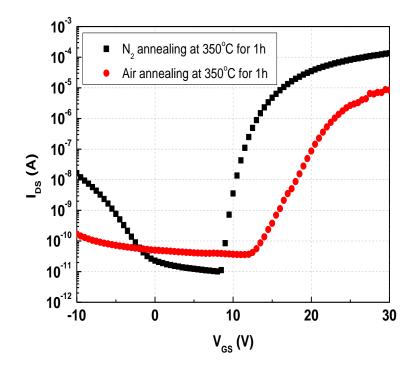

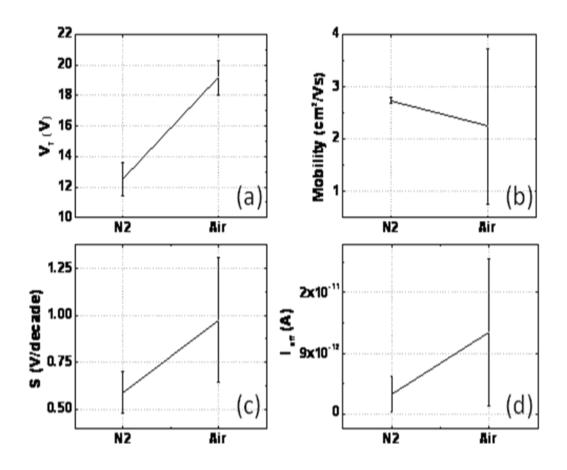

| Figure 4-7.T he representative TFT transfer curves after annealing ambient in $N_2$                      |

| and air at 350°C for 1hr79                                                                               |

| Figure 4-8. The comparison of electrical characteristics annealed for $N_2$ verse air                    |

| for 1h 80                                                                                                |

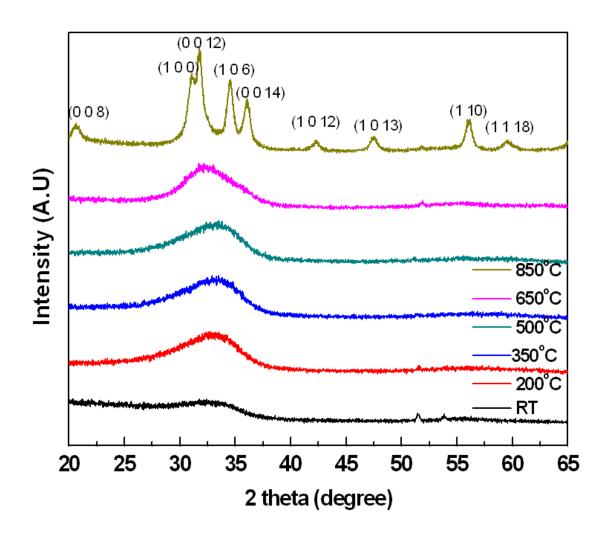

| Figure 4-9. X- ray diffraction analysis as a function of the annealing temperature                       |

| in N <sub>2</sub> for a-IGZO film82                                                                      |

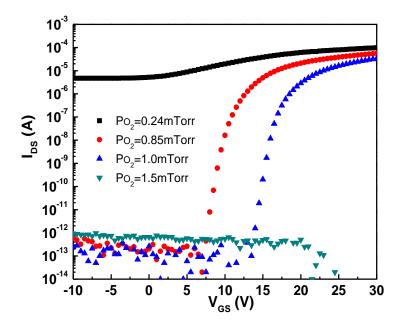

| Figure 4-10. The TFT transfer curve at $V_{DS}$ = 5.1V with different oxygen partial                     |

| pressure                                                                                                 |

| Figure 4-11. The surface roughness of a-IGZO with different oxygen partial                               |

| pressure, (a) 0mTorr, (b) 0.85mTorr, and (c) 1mTorr                                                      |

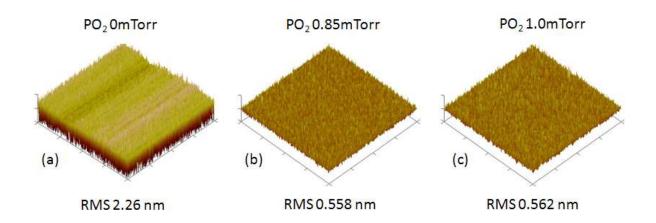

| Figure 4-12. Molecules incorporation of IGZO and $O_2$ with oxygen partial                               |

| pressure in growing IGZO film during sputtering                                                          |

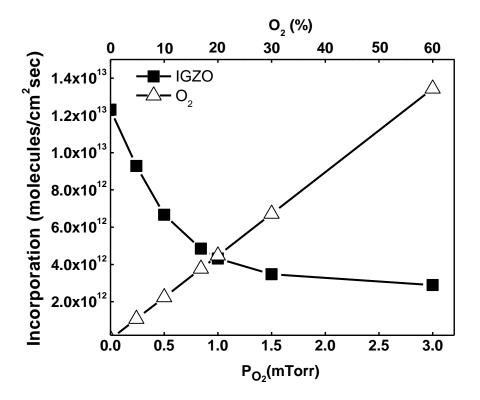

| Figure 4-13. (a) IGZO resistivity and $O_2/IGZO$ incorporation ratio as function of                      |

| oxygen partial pressure and (b) IGZO resistivity with $O_2/IGZO$                                         |

| incorporation ratio92                                                                                    |

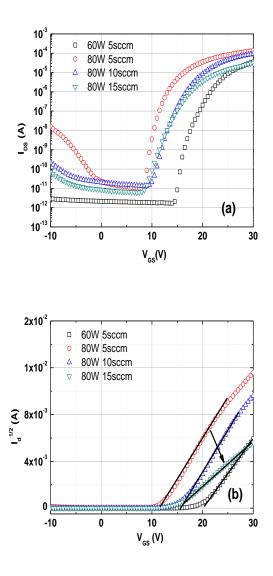

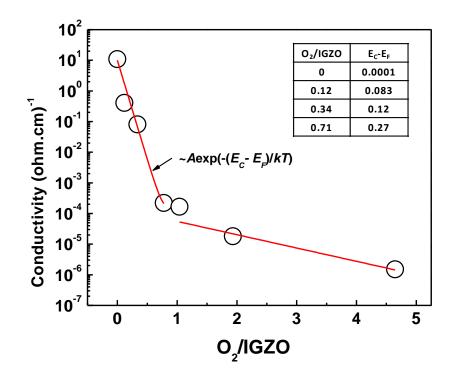

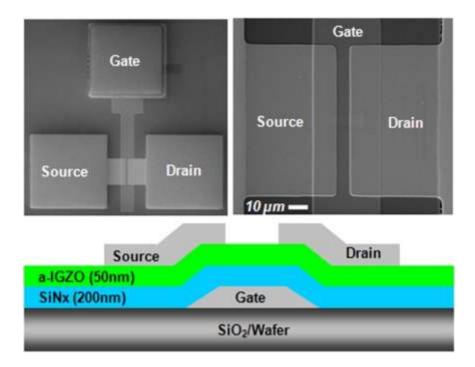

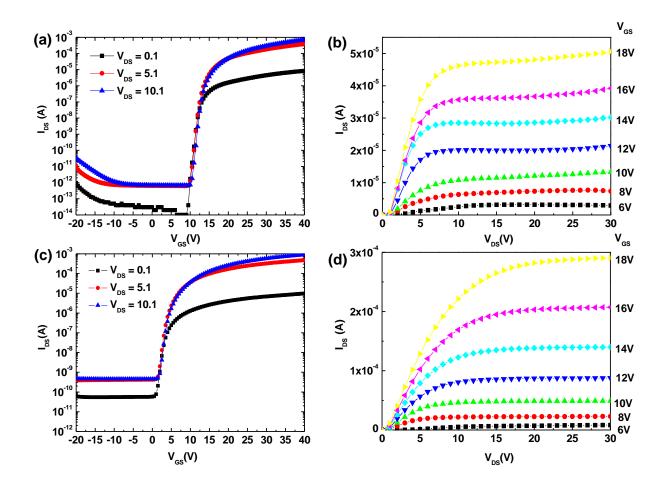

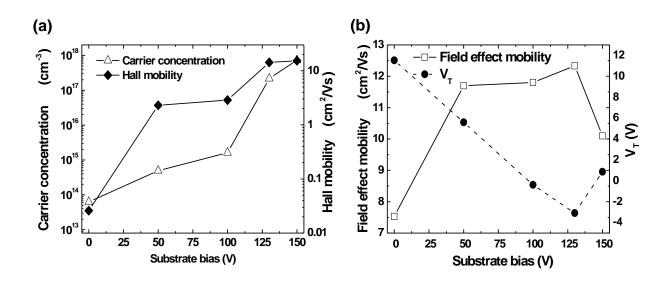

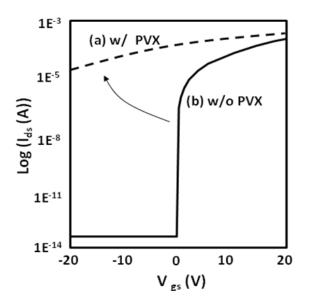

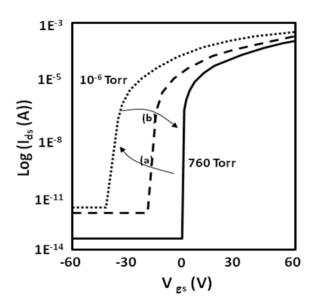

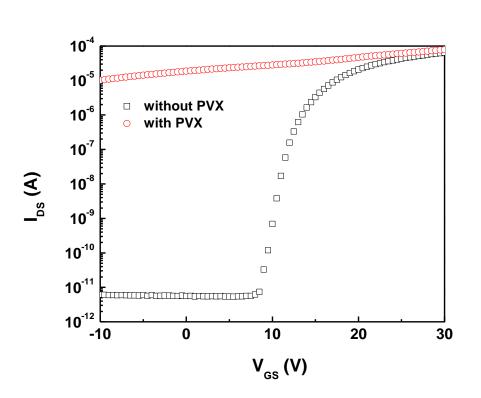

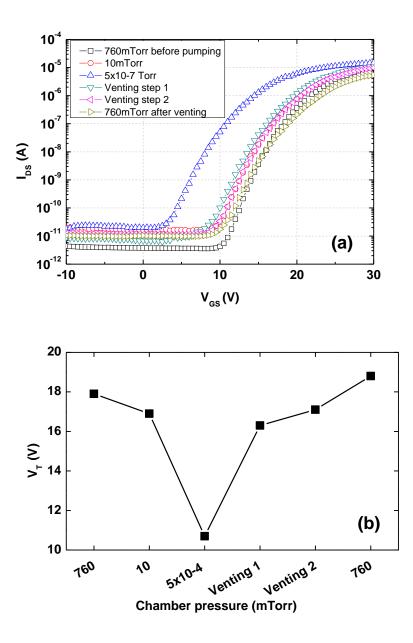

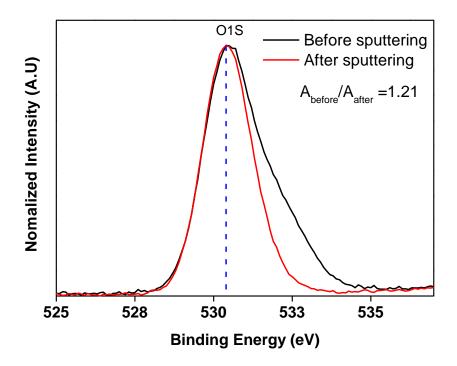

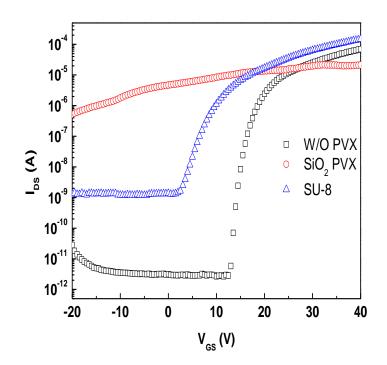

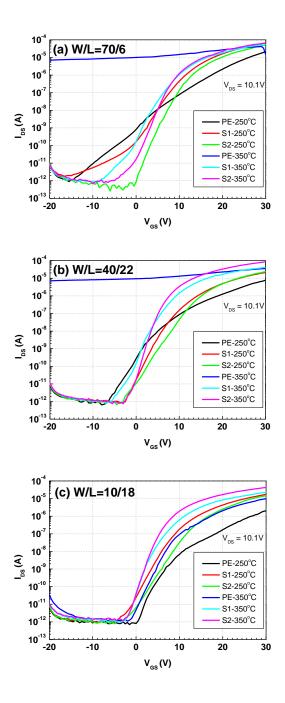

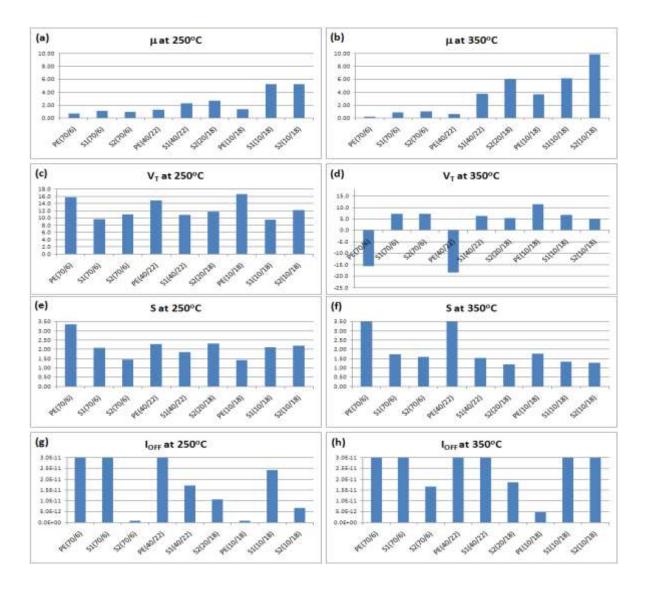

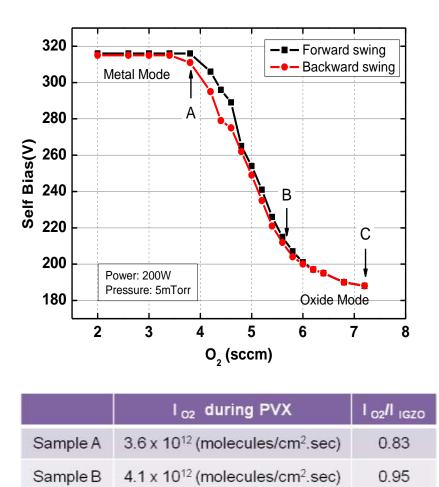

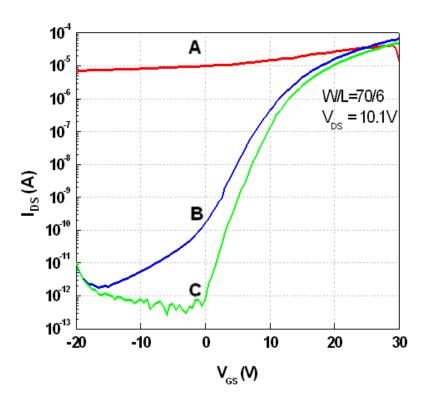

Figure 4-14. Electrical conductivity with  $O_2/IGZO$  incorporation ratio and  $E_C - E_F$ with O<sub>2</sub>/IGZO incorporation (inset table)......94 Figure 4-15. A schematic and SEM micrographs of the fabricated device structure of a-IGZO TFTs with an inverted staggered bottom gate Figure 4-16. Comparison of a-IGZO TFTs with bias: (a) transfer characteristics and (b) output characteristics of unbiased (0V) a-IGZO TFTs, (c) transfer characteristics and (d) output characteristics of biased (150V) Figure 4-17. The dependence of substrate bias on (a) Hall mobility and carrier concentration in the a-IGZO film (50nm) and (b) the  $V_T$  and field effect mobility of the a-IGZO TFTs......103 Figure 4-18. Comparison of core-level XPS spectra of the IGZO film deposited with substrate bias (green color) and without substrate bias (red color), (a), (b), (c), and (d) and the atomic concentration ratios obtained from the area of XPS spectra curves, (e) which is normalized by total atom Figure 5-1. Transfer characteristic of TFTs: (a) TFT with (w/) PVX and (b) TFT Figure 5-2. The shift of transfer curves at different pressure; (a) decreasing pressure and (b) increasing pressure ......112

| Figure 5-3. The transfer curve of a-IGZO TFT without passivation and with                 |

|-------------------------------------------------------------------------------------------|

| sputter SiO <sub>2</sub> passivation at $V_{DS}$ =5.1V                                    |

| Figure 5-4. (a) the transfer curve shift with different pressure and (b) $V_T$ shift with |

| changing pressure117                                                                      |

| Figure 5-5. Oxygen core-level XPS spectra of the a-IGZO film before and after             |

| sputtering surface treatment118                                                           |

| Figure 5-6. TFT transfer curve with different passivation layer; 1) w/o passivation,      |

| 2) sputtered SiO <sub>2</sub> , and 3) spin-coated SU-8                                   |

| Figure 5-7. Comparison of transfer curves with deposition method (sputter vs.             |

| PECVD), annealing temperature (250°C vs. 350°C), and W/L ratio                            |

| (70μm/6μm, 40μm/22 μm, and 10μm /1μm)                                                     |

| Figure 5-8. Summary of electrical properties with different deposition conditions 125     |

| Figure 5-9. Hysteresis curve with oxygen during reactive $SiO_2$ sputtering for           |

| passivation                                                                               |

| Figure 5-10. Transfer curves of a-IGZO TFT passivated with different oxygen               |

| incorporation rate130                                                                     |

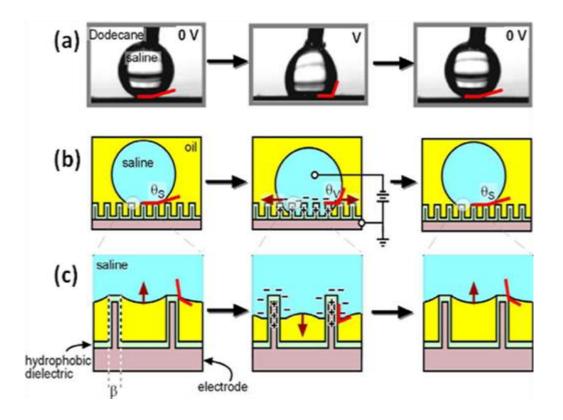

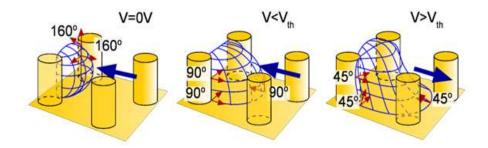

| Figure 6-1. Schematic electrowetting effect mechanism with applying voltage, (a)          |

| contact angle change on 2 dimensional surface, (b), and (c) contact                       |

| angle change and electrolyte separation on 3 dimensional surface                          |

| (post structure)133                                                                       |

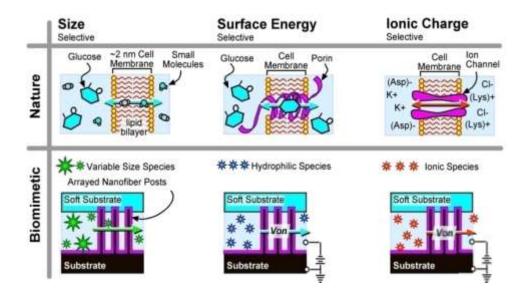

| Figure 6-2. Biomimetic transport mechanism and proposed schematic device 135              |

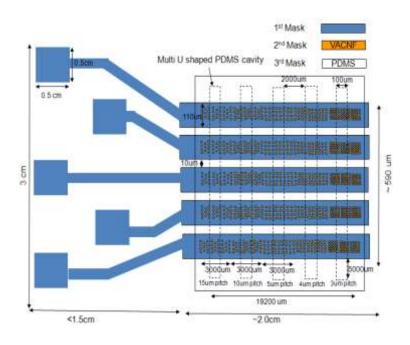

| Figure 6-3. Multidimensional agile fluidic transport system                               |

| Figure 6-4. Layout of passive electrowetting scaffold 138                        | 8 |

|----------------------------------------------------------------------------------|---|

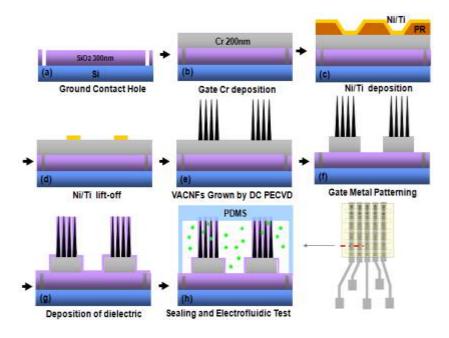

| Figure 6-5. The fabrication process of VACNFs on array for passive               |   |

| electrowetting scaffolds139                                                      | 9 |

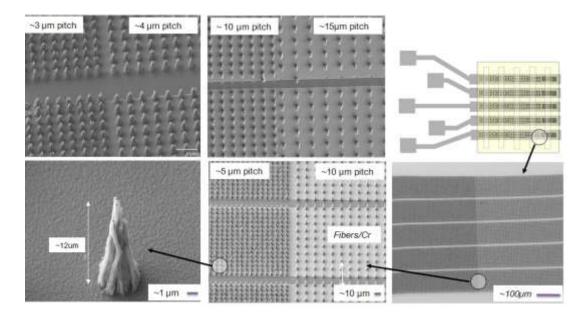

| Figure 6-6. The SEM images of fabricated VACNFs on addressable device with       |   |

| different pitch sizes139                                                         | 9 |

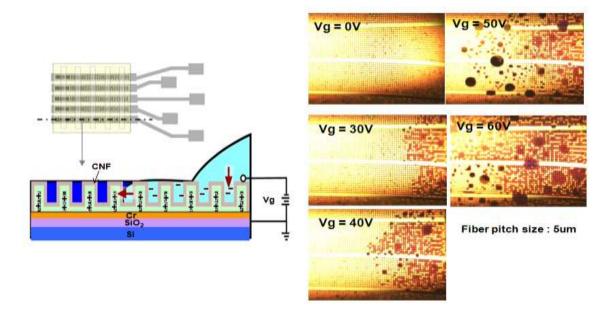

| Figure 6-7. The demonstration of addressable electrowetting device to form agile |   |

| liquid channels                                                                  | 0 |

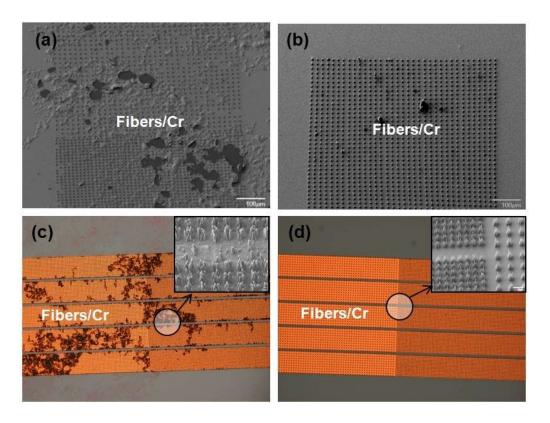

| Figure 6-8. The process issues for addressable electrowetting device, (a) Cr     |   |

| electrode delaminating issue because of tensile Cr film, (b) stress              |   |

| optimized Cr electrode with fibers, (c) surface plasma arcing defect             |   |

| (carbon residues) due to surface plasma charging effect during fiber             |   |

| growth using DC-PECVD , and (d) fiber on Cr after solving plasma                 |   |

| arcing by forming ground contact paths142                                        | 2 |

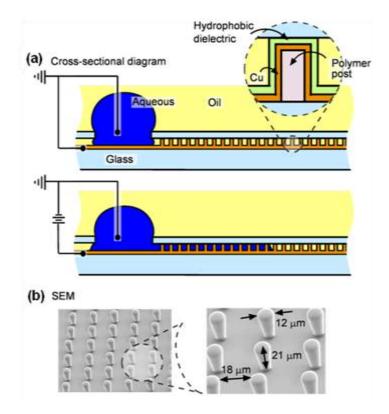

| Figure 6-9. (a) cross-sectional device diagram, (b) SEM image of completed       |   |

| post-arrays144                                                                   | 4 |

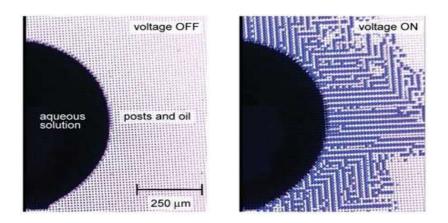

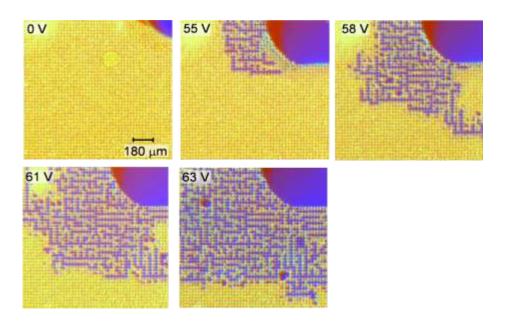

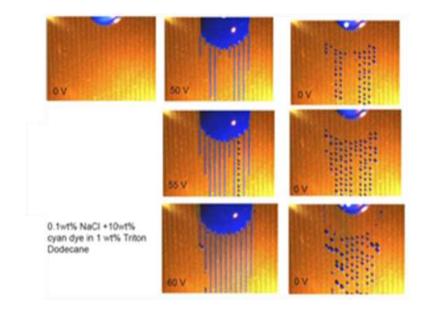

| Figure 6-10. The image of channel formation by post-guided electrowetting,       |   |

| voltage OFF and voltage ON146                                                    | 6 |

| Figure 6-11. Diagram of the mechanism of post-guided electrowetting              | 6 |

| Figure 6-12. Channel formation and propagation with applied voltage              | 9 |

| Figure 6-13. Time lapse photographs of directional channel formation             | 9 |

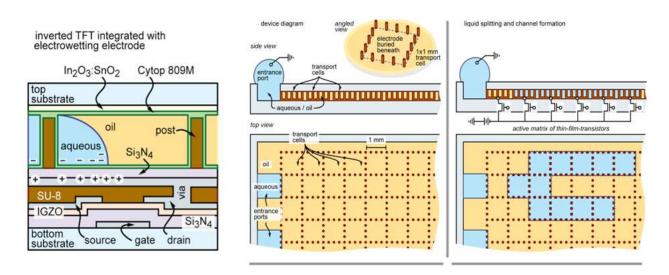

| Figure 6-14. Integrate TFT with electrowetting platform and proposed agile and   |   |

| re-programmable microfluidic device150                                           | 0 |

# Chapter 1 Introduction

#### 1.1 Motivation of this work

Thin film transistors (TFTs) have been used as key elements in order to control, switch, and drive electronic devices. Conventionally, one of the main applications for TFTs has been flat panel display such as liquid crystal displays (LCDs) and organic light emission displays (OLEDs) in which amorphous silicon (a-Si) and polycrystalline silicon (poly-Si) usually have been used as the semiconductor active layer. In spite of the many benefits of silicon based semiconductors, there has been growing limits due to their intrinsic material properties in some applications such as transparent, high speed switching, and large area device due to electrical device requirements [1],[2]. For example, a-Si-TFT with low mobility (< 1 cm<sup>2</sup>/Vs) cannot be applied to high speed switching device in spite of its excellent electrical uniformity and poly-Si TFT with high mobility  $(10 \sim 400 \text{ cm}^2/\text{Vs})$  still shows unstable electrical characteristics, namely: first, an non-uniformly formed grain size and protrusions of poly-Si after crystallization induced by laser annealing and second, the high off-current level of TFT through metal residue in the active layer formed by metal catalysis crystallization method such as metal induced crystallization(MIC) and metal induced lateral crystallization (MILC) [3],[4],[5]. These crystallization methods are not adequate to use high performance device such as OLEDs display which requires high electrical uniformity and performance for field effect mobility and electrical stability with time lapse on the whole TFT array panel [6],[7]. In order to improve these issues, Hosono's group proposed amorphous indium gallium zinc oxide (a-IGZO) as an oxide semiconductor material for

1

active layer by which a-IGZO TFT may offer an attractive alternative for replacing silicon based TFTs. Table 1 compares silicon based TFT properties with oxide based TFT properties. Oxide TFTs provides better electrical uniformity such as threshold voltage  $(V_{TH})$ , field effect mobility ( $\mu_{FE}$ ), subthreshold gate swing (S), and leakage current level in the off-state because of its amorphous property and in addition, in spite of its amorphous phase, a-IGZO TFT shows a high mobility of  $> 10 \text{ cm}^2/\text{Vs}$  which can be used for driving TFT with high speed switching and high current level. Moreover, this attractive a-IGZO material is transparent and can be deposited at room temperature so that it is an attractive semiconductor material for flexible displays [2], [8]. In spite of these merits, oxide TFTs still have inherent problem to be improved for their commercial application: 1) electrical instability due to environmental changes; 2) correlation of gate dielectric with transfer characteristic; 3) understanding the effects of passivation layers on device characteristics; 4) sensitive properties with different sputtering conditions [9],[10]. In this study, we study of a-IGZO TFTs, which will include device designs, material characterization, process developments, and device characterization. Our motivation is to realize a robust TFT using a-IGZO semiconductor for flat panel display as well as to drive other applicable devices. For example, in this study, an active matrix type TFT will be applied to an addressable microfluidic electrowetting channel device.

# Table 1-1 Comparison of silicon based semiconductor TFT and oxide based

semiconductor TFT, Nikkei Electronics Asia, Oct 24, 2007 (LG electronics courtesy).

|                                        | a-Si TFT             | Poly-Si TFT           | Oxide TFT            |

|----------------------------------------|----------------------|-----------------------|----------------------|

| Phase                                  | amorphous            | polycrystalline       | amorphous            |

| Channel Mobility                       | 1 cm²/Vs             | ~ 200 cm²/Vs          | 10~40 cm²/Vs         |

| Switching<br>characteristics (S)       | 0.4 ~ 0.5 V/decade   | 0.2~0.3 V/decade      | 0.09 ~ 0.6 V/decade  |

| S/D Leakage<br>current                 | ~10 <sup>-13</sup> A | ~ 10 <sup>-12</sup> A | ~10 <sup>-13</sup> A |

| Characteristic<br>uniformity           | Good                 | Not good              | Good                 |

| Long-term TFT<br>reliability           | Low                  | High                  | Unknown              |

| Maximum process<br>Temperature         | ~ 250°C              | ~ 400-500°C           | RT to 350°C          |

| Manufacturing cost<br>(Number of mask) | Low (4~6)            | High(7~11)            | Very low (4~6)       |

| Application display                    | LCD                  | LCD, OLED             | LCD, OLED            |

#### 1.2 Thin film transistor

#### 1.2.1 Historical background

The first thin film transistor was demonstrated by P.K Weimer (1962) who used a top-gate staggered structure with a microcrystalline cadmium sulfide (CdS) active layer [11]. Since Weimer's work, TFTs based on a wide variety of semiconductor materials including organic and inorganic, and amorphous and polycrystalline have been developed. Currently, the most dominant TFT technology is based on a-Si:H and poly-Si as active layer, which is commonly used as switching and driving devices in activematrix type displays such as active-matrix liquid crystal displays (AMLCDs) and activematrix organic light emission displays (OLEDs)[12],[13],[14],[15], [16]. In addition to silicon TFTs, another type of TFTs consists of those which employ organic materials as the channel layer in spite of low mobility of  $10^{-3} \sim 1 \text{ cm}^2/\text{V}$ .s because the low mobility of these organic TFTs can be offset by low cost and easy processing such as spin coating or printing methods [17]. In addition, this technology allows plastic substrates to be used for flexible devices because the process temperature for fabrication of device, most of all, can be decreased below 250°C. Currently promising oxide based TFTs are emerging since they are transparent and demonstrate high performance for advanced TFT applications, [2], [18].

#### 1.2.2 Basic TFT operation

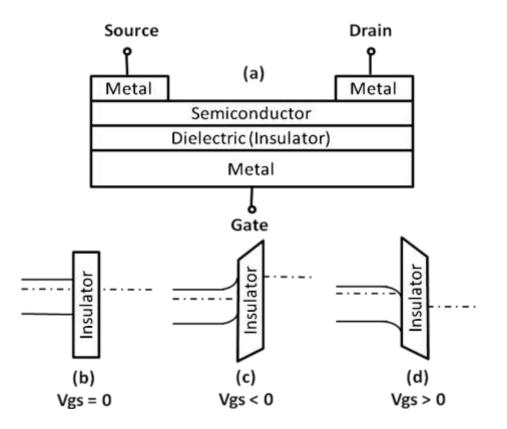

Fig. 1 shows the basic structure of a TFT and several energy band diagrams as viewed through the gate of an n-semiconductor, accumulation-mode TFT. The energy band diagram of Fig.1- 1(b) shows the device at equilibrium, with 0V applied to the

source, drain, and gate. Fig.1-1(c) shows an energy band diagram with the gate negatively biased. The applied negative bias repels mobile electrons from the semiconductor, leaving a depletion region near the insulator-semiconductor interface. When compared to Fig. 1-1 (b), this biasing condition has a reduced conductance due to the reduced number of mobile electrons in the semiconductor. Fig.1-1(d) shows an energy band diagram with the gate positively biased. The applied positive bias attracts mobile electrons, forming an accumulation region near the insulator-semiconductor interface. These excess mobile electrons lead to an increase in the channel conductance. Beginning with the case where the gate is biased positively and accumulation is established, i.e., Fig.1-1(d), consider the effect of an applied drainsource voltage, V<sub>DS</sub>. Initially the semiconductor is modeled as a resistor, i.e. linearly increasing current with V<sub>DS</sub>. As V<sub>DS</sub> increases, accumulation near the drain decreases. As V<sub>DS</sub> is increased further, the region near the drain eventually begins to deplete. The voltage at which the semiconductor region near the drain is fully depleted of carriers is denoted the pinch off voltage. Therefore, application of V<sub>DS</sub> greater than the pinch-off voltage results in a saturated drain current characteristic.

Fig.1-1. (a) basic structure of a TFT and corresponding energy band diagram as viewed through the gate with bias conditions: (b) equilibrium, (c)  $V_{gs} < 0 V$ , and (d)  $V_{gs} > 0V$ .

#### 1.2.3 TFT structure

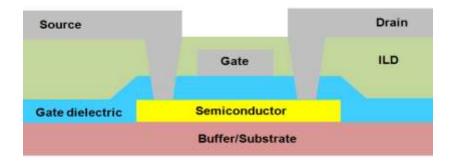

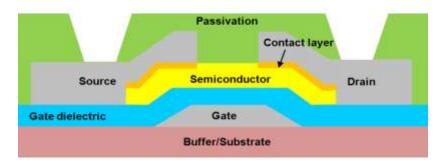

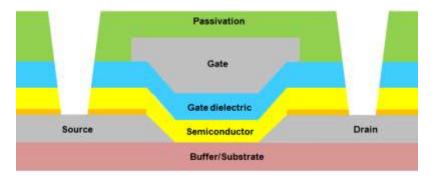

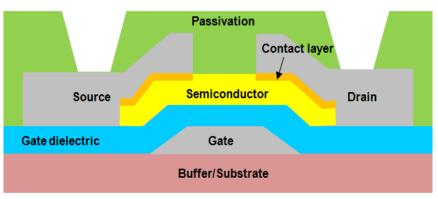

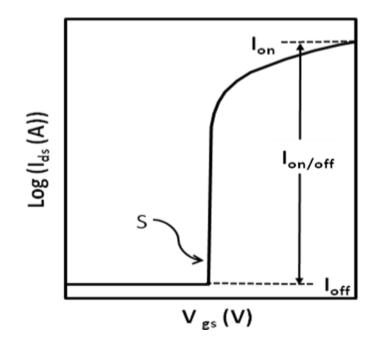

There are two types of TFT structures for silicon based TFTs. Fig. 1-2 shows representative TFT structures. First, the coplanar type is that source/drain and gate are on the same plane as shown Fig.1-2 (a). This type structure is usually used for polycrystalline TFT because of the higher quality of crystalline film and the convenience of crystallization. Second, the staggered type TFT as shown Fig.1-2 (b) is divided into two type of structures depending on the location of gate; 1) the structure with gate under active layer is inverted staggered (bottom gate) type and 2) the structure with gate on active layer is normal staggered (top gate) type. Normal staggered type TFT was proposed earlier than inverted staggered type as shown Fig.1-2 (c). However, the complicated process step to pattern Ohmic contact layer and the exposure of silicon surface before the deposition of gate dielectric degrades the TFT properties. While inverted staggered type TFT is commonly used for a-Si TFT because the interface between gate dielectric and semiconductor (a-Si) including Ohmic contact layer (n<sup>+</sup> a-Si) can be formed without exposing in air therefore the electrical properties can be improved. In addition, the TFT process is simple because  $n^+$  a-Si and a-Si can be etched by using a single source/drain mask. The inverted staggered type is divided into back channel etch (BCE) type (Fig.1-3 (a)) and etch stopper (E/S) type (Fig.1-3 (b)). In spite of simple structure of BCE type of TFT, the over etching or chemical damage on semiconductors deteriorates the characteristic uniformity of a TFT array panel. On the other hand, the E/S type of TFT has higher stability for TFT properties because the E/S layer

protects semiconductor layer against chemical damage or non-uniform over etching problem in spite of relatively complicated process; n+ a-Si is separately deposited on E/S layer with a-Si layer after E/S layer pattern.

### (a) Coplanar type TFT structure

### (b) Inverted staggered type TFT structure

### (c) Normal staggered type TFT structure

Fig.1-2. Cross section of the various TFT structures: (a) coplanar type TFT structure, (b) Inverted staggered type TFT structure, (c) Normal staggered type TFT structure.

(a) BCE type TFT structure

(b) E/S type TFT structure

Fig. 1-3.Two type of TFT structures in inverted staggered type TFT structure, (a) BCE type TFT structure and (b) E/S type TFT structure.

#### 1.2.4 Electrical characterization of TFT

There are two operational regimes in a typical MOSFET (metal oxidesemiconductor field- effect transistor): the linear region and the saturation region. In the linear region, the drain current increases linearly with drain voltage ( $V_D \ll V_G$ ), as in Ohmic conduction. On the other hand, the drain current is constant with increasing drain voltage in the saturated region.

#### Linear region

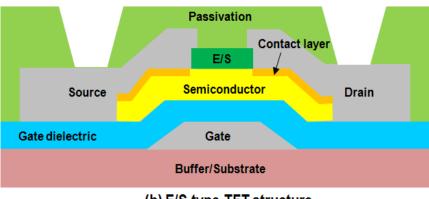

Fig. 1-4 shows cross-sectional view of the channel region of a TFT used to derive the gradual channel approximation. The carrier density per unit area in the channel depends on the potential V(y) caused by the drain potential V<sub>D</sub>. When the gate potential is higher than the threshold, V<sub>T</sub>, the mobile charge Q<sub>I</sub> in the channel is related to the gate potential V<sub>G</sub> via

$$Q_I = -C_{SINX}(V_G - V_T) \tag{1.1}$$

where  $C_{SiNx}$  is the capacitance per unit area of the SiN<sub>x</sub> gate dielectric. The channel potential V in Eq. (1) is assumed to be zero; however, the induced charge Q<sub>I</sub> is a function of y, so Eq. (1) is replaced by the following equation:

$$Q_{I} = -C_{SiNx}(V_{G} - V_{T} - V)$$

(1.2)

On the other hand, the current induced by majority carriers can be written as

$$I_D = W\mu_n Q_I E_y \tag{1.3}$$

Where W is channel width,  $\mu_n$  is the electron mobility, and  $E_y$  is the electric field at y. The equation is a simplified form of the current density formula where the diffusion term has been assumed to be negligible:

Fig. 1-4. Cross-sectional view of the channel region of a TFT used to derive the gradual channel approximation.

$$J_n = \frac{I_n}{A} = q \left( \mu_n nE + D_n \frac{dn}{dx} \right)$$

(1.4)

By substituting  $E_y = dV/dy$  and Eq. (2) into Eq. (3) we obtain

$$I_D dy = W \mu_n C_{SiNx} (V_G - V_T - V) dV$$

(1.5)

By integration from y = 0 to L, that is, from V = 0 to  $V_D$  the gradual channel expression for the drain current is:

$$I_{D} = \mu_{n} C_{SiNx} \frac{W}{L} \left[ (V_{G} - V_{T}) V_{D} - \frac{1}{2} V_{D}^{2} dV \right]$$

(1.6)

In the linear region ( $V_D << V_T$ ) the drain current can be written as

$$I_d = \mu_n C_{SiNx} \frac{W}{L} (V_D - V_T) V_D$$

(1.7)

Therefore, field-effect mobility in the linear region is obtained from Eq. (7).

#### Saturation region

The gate field-induced carrier density at the drain disappears as the drain potential increase. When  $V_D = V_G - V_T$ , the electron channel becomes completely pinched off, the drain current saturated. For  $V_D > V_G - V_T$ , Eq. (6) is no longer effective. Therefore, the saturation drain current can be obtained by substitution of  $V_D = V_G - V_T$  into Eq. (6),

$$I_{D} = \frac{C_{SiNx} \mu_{n} W}{2L} (V_{G} - V_{T})^{2}$$

(1.8)

The field-effect mobility in the saturation region can be obtained by taking the square root of Eq. (8) and differentiating with respect to  $V_G$ , and given by,

$$\mu_n = \left( \left( \frac{d\sqrt{I_D}}{d\sqrt{V_G}} \right) \frac{1}{\sqrt{C_{OX} \frac{W}{2L}}} \right)^2$$

(1.9)

In this study, we will extract the field effect mobility from the saturation region because this region is relatively insensitive to the magnitude of the source-drain resistance (contact resistance); independent of  $V_D$ , unlike the linear region.

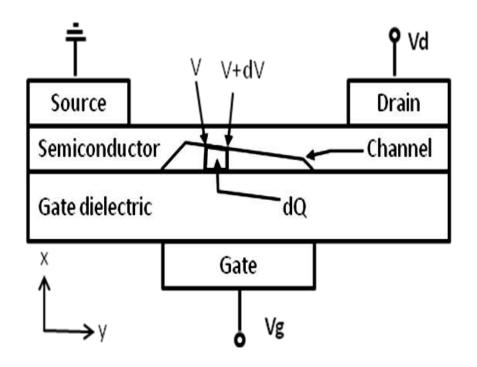

Fig.1-5 shows the general transfer characteristic of a-IGZO TFT and graphical definition of the on/off current ratio in the curve. The on/off current ratio is important for performing active switching in each pixel in the device where the on – current determines the rate of pixel or capacitor charging and off- current is associated with the leakage of the pixel or capacitor voltage. In this study, we will take the lowest drain current value for off-current in the transfer characteristics and on-current will be measured at 20 V ( $V_{GS}$ ) shifted negatively from  $V_T$ .

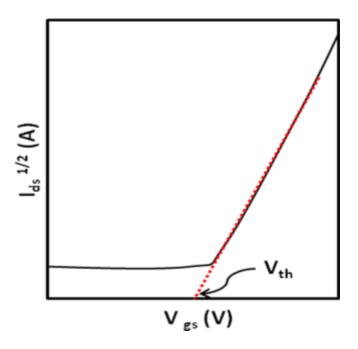

$V_T$  will be extracted by extrapolating in the saturation region on the  $I_{DS}$   $^{1/2} - V_{GS}$  characteristic plot as shown in Fig.1-6. The subthreshold gate swing, *S*, defined as the voltage required to increase the drain current by a factor of 10 and determined from the

equation:  $S = \frac{dV_{GS}}{d(\log I_{DS})}$ , note that S is given by the maximum slop in the transfer curve

as shown Fig. 1-6.

Fig.1-5. General transfer characteristic of a-IGZO for graphical definition of I  $_{on/off}$  and (b) subthreshold gate swing (*S*).

Fig. 1-6. Graphical extrapolation of  $V_T$  in the saturation region.

#### 1.2.5 Oxide semiconductor based TFT

#### 1.2.5.1 Overview of transparent oxide semiconductors

Transparent conductive oxides (TCOs) are being studied for flat panel display application as active layer because of transparency and electrical properties[2],[19],[20], [21], where transparency and high conductivity are somewhat contradictory because optical transparency requires band gaps larger than 3.3 eV and such a large band gap makes carrier conduction very difficult [22]. In this sense, TCOs materials are exceptional materials. Historically TCO materials such as  $In_2O_3$ :Sn (ITO), SnO<sub>2</sub>, and ZnO have been only commercially applied to TFTs as transparent electrodes and interconnections because of the absence of p-type TCOs [23]. In 1997, the discovery of a p-type TCO, CuAlO<sub>2</sub> by Hosono's group significantly gave a rise to new functional device which was difficult to realize by Si-based device; specifically a fully transparent flat panel displays. Recently, Samsung SDI demonstrated the 12 inch-transparent OLED display using the TCO amorphous indium gallium zinc oxide. This realization using these materials is due to significant different electronic structure and transport in oxide semiconductor which shows higher Hall mobility (> 10cm<sup>2</sup>/Vs) as compared to amorphous silicon material in spite of room temperature process for semiconductor deposition. In this chapter, the electrical structure and carrier conduction of TCOs will be reviewed, including the properties of a-IGZO material [24].

#### 1.2.5.2 Electronic structure and carrier transport

There are significantly different conduction mechanisms between silicon based semiconductor and oxide based semiconductors. Usually, amorphous silicon has poor

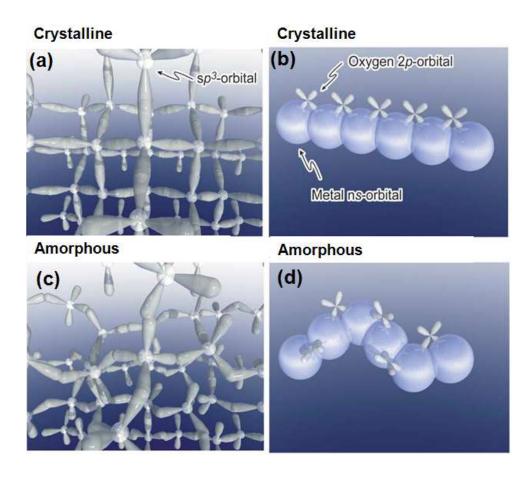

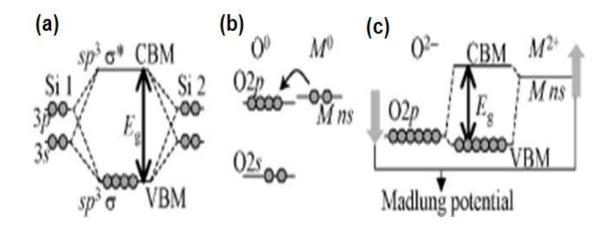

carrier transport properties ( $\sim 1 \text{ cm}^2/\text{V.s}$ ) relative to crystalline silicon materials ( $\sim 500$ cm<sup>2</sup>/Vs). This is fundamentally because the chemical bond in the covalent silicon semiconductors which are made of  $sp^3$  or p-type orbitals with strong spatial directivity as shown in Fig.1-7 (a) and (c). Therefore, for amorphous silicon, the strained and disordered chemical bonds form rather deep and high-density of localized states below conduction band minimum (CBM) and above valence band maximum (VBM), causing carrier trapping. On the other hand, for n-type TCOs, amorphous oxide semiconductors (AOSs) containing post-transition-metal cations make high mobility possible in spite of their amorphous structure because CBMs are made of spherical extended s orbitals of metal ions containing high ionicity and overlapping with neighboring metal s orbitals which are not influenced largely by disordered local structure. Therefore, the electronic levels near the CBM are insensitive to locally strained bonds, and the electron transport is not affected significantly as shown in Fig.1-7(d) [8]. In a sense of formation of energy gap, Kamiya et al. more clearly described the electronic structures of oxides [25]. Fig.1-8 shows the formation of energy gap with a different type of bond. As already described, for Si, CBMs and VBMs are made of anti-bonding ( $sp^3 \sigma *$  and bonding states ( $sp^3 \sigma$ ) of Si sp<sup>3</sup> hybridized orbitals forming its bandgap by energy splitting of the  $\sigma * - \sigma$  levels (Fig. 1-8 (a)). On the other hand, for oxides materials, CBMs and VBMs are formed by different ionic species. In order to study electronic structure, most of all, it is important to understand the Madelung potential in ionic crystals. When metal atoms and oxygen come close, charge transfer occurs due to largely different electron affinity and ionization potential, ionizing these atoms (Fig. 1-8 (b)). As a result, Madelung potential from the difference between anions and cations by virtue of their opposing charges

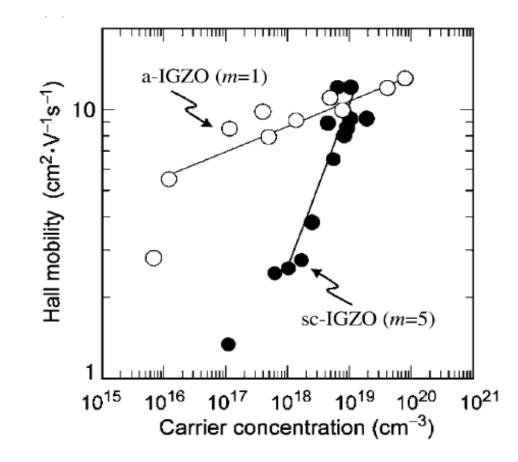

consequently stabilizes the ionized states in the crystal structure (Fig. 1.8 (c)); the Madelung potential induce energy splitting. Therefore CBMs and VBMs are mainly made of metal cations and oxygen 2p orbitals, respectively. CBMs are mainly made of s orbitals with a large principle quantum number *n* in which *s* orbitals have large spatial size and form large hybridization with second neighbor metal cations. Because of this, TCOs have small electron effective masses. In fact the above electronic structure, there are mainly two representatively electrical merits for oxide based TFTs. First, the small effective mass make high density carrier doping possible in order to improve electron mobility [26], [27]]. Fig. 1-9 shows the relationship between Hall mobility and electron concentration for single-crystalline  $InGaO_3$  (ZnO) 5 (sc-IGZO) and a-IGZO film. Hall mobility increases with increasing carrier concentration. In fact, carrier transport is controlled by thermal activation at low temperature, however, according to Takagi et al., when carrier concentration exceeds a threshold value  $N_{th}$ = 4 x10<sup>18</sup> cm<sup>-3</sup>, the degenerated conduction occurs for both a-IGZO and sc-IGZO. These behaviors are significantly different from conventional semiconductor such as silicon because the carrier mobility typically decreases with increasing carrier concentration due to ionized impurity scattering in highly doped semiconductors, where this peculiar behavior will be explained in the following chapter with percolation conduction model in a-IGZO film. Second, subthreshold voltage swing (S) value is improved due to relatively lower subgap traps. Fundamentally, as already mentioned, the origin of the bandgap of oxide is from the Madelung potential, and therefore, the nonbonding levels of metal cations are located in the vicinity of the conduction band [28]. Even if defective levels are formed in the bandgap, they are generally occupied by two electrons in n-type oxides

and electrically inactive for an electron-only device; the defects in oxides such as oxygen vacancies do not cause strongly active traps because of its strong ionicity and the electronic structure. Indeed, it has been reported that a-IGZO has far fewer subgap traps than a-Si: H even when it is deposited at room temperature. Fig.1-10 shows the comparison of trap density in a-IGZO and a-Si:H. The density of states of a-IGZO near conduction band are much lower than a-Si:H. The low defect densities in the a-IGZO film make possible the low voltage operation for the TFTs because the operating voltage is largely determined by the subthreshold voltage swing (*S*), which is related to the subgap density of states  $D_{sg}$  (cm<sup>-2</sup>eV<sup>-1</sup>) by

$$S = \frac{dV_g}{d\log I_g} = \ln 10 \frac{k_B T}{e} \left( 1 + \frac{eD_{sg}}{C_g} \right) = S_0 \left( 1 + \frac{eD_{sg}}{C_g} \right)$$

(1.10)

where  $k_B$  is the Boltzmann constant, T is the temperature,  $C_g$  is the gate capacitance per unit area,  $S_0$  is temperature dependent constant.

Fig. 1-7. Schematic orbital drawings for the carrier transport paths at the conduction band bottoms in amorphous and crystalline semiconductors; (a) crystalline and (c) amorphous silicon with covalent bonds with strongly directive sp<sup>3</sup> orbitals and (b) crystalline and (d) amorphous oxide semiconductors with post-transition-metal cations.

K. Nomura, T. Kamiya, H. Ohta et al., Applied Physics Letters, vol. 85, no. 11, pp. 1993-1995, Sep 13, (2004)

Fig. 1-8. Formation of energy gap, (a) covalent semiconductor (silicon), and (b, c) ionic semiconductor ( $M^{2+}O^{2-}$ ). (b) Energy levels of neutral atoms in vacuum. (c) The atoms are ionized I a crystal structure and form large Madelung potential and large bandgap.

T. Kamiya, H. Hosono, T. Kamiya et al., International Journal of Applied Ceramic Technology, vol. 2, no. 4, pp. 285-294, (2005)

Fig. 1-9. Relationship between Hall mobility and electron concentration for singlecrystalline  $InGaO_3$  (ZnO)  $_5$  (sc-IGZO) and a-IGZO film.

T. Kamiya, H. Hosono, T. Kamiya et al., International Journal of Applied Ceramic Technology, vol. 2, no. 4, pp. 285-294, (2005)

Fig.1-10. Subgap trap density of states in a-IGZO in comparison with a-Si:H.

## 1.2.5.3 Amorphous indium gallium zinc oxide TFT (a-IGZO TFT)

The first TFT using a-IGZO can be credited to Hosono's group [29]. They proposed transparent flexible TFTs using a-IGZO semiconductors at room temperature, and characterized the material properties and electrical characteristics of the TFTs. The key element to perform high electrical performance was incorporating Ga ions into the semiconductor. The Ga ions can suppress carrier generation via oxygen vacancy formation because the Ga ions forms stronger chemical bonds with oxygen than Zn and In ions; the carrier concentration can be controlled by Ga contents in film and achieve a low off current and large on/off current ratio.

# 1.2.5.3.1 Structural and optical properties

Takagi *et al.* demonstrated the structure and optical properties of a-IGZ [30]. Fig. 1-11 shows the X-ray diffraction pattern of a-IGZO film deposited on a substrate. Because no sharp peaks are observed in the plot, the film is amorphous. Fig. 1-12 shows optical transmission spectra of a-IGZO films with different carrier concentrations of ~  $10^{13}$  cm<sup>-3</sup> and ~  $10^{20}$  cm<sup>-3</sup>. Transmissions of both the films are greater than 80% in the visible region. Large optical absorption appears in the wavelength region > 1600nm in the high carrier concentration film, which can be attributed to free carrier absorption. Tauc's plots give optical band gaps of ~ 3.1 eV and ~3.3 eV for the films with carrier concentrations of ~  $10^{13}$  cm<sup>-3</sup> and ~  $10^{20}$  cm<sup>-3</sup>, respectively. They explained these results due to a Burstein-Moss (BM) effect, in which the raise of the Fermi level in the conduction band in a degenerate state increases the optical absorption edge energy

using the relationship,  $\Delta E_g^{BM} = \frac{h^2}{2m_e} (3\pi r^2 n_e)^{2/3}$ .

Fig. 1-11. X-ray diffraction pattern of the a-IGZO film deposited on SiO2 a glass substrate at room temperature.

A. Takagi et al., vol. 486, no. 1-2, pp. 38-41, Aug 22, (2005).

Fig. 1-12. Optical transmission spectra of a-IGZO film with different carrier concentration  $\sim 10^{13}$  cm  $^{-3}$  and  $\sim 10^{20}$  cm  $^{-3}$ .

A.Takagi et al., vol. 486, no. 1-2, pp. 38-41, Aug 22, (2005)

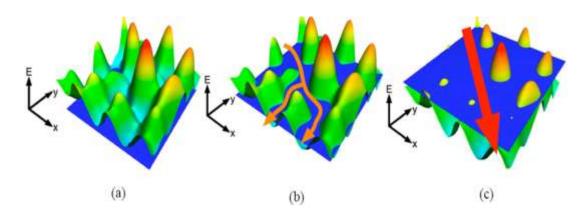

1.2.5.3.2 Carrier conduction in a-IGZO: Percolation conduction model

The quantum mechanical hopping (Fig. 1-13 (a)), which usually describes conduction mechanism of silicon semiconductor in CBM, is excluded from a conduction mechanism for a-IGZO semiconductor because of the relatively long average distance between mono-energetic states as compared in Fig. 1-13 (b). To explain conduction in a-IGZO, Nomura et al. proposed that electron carriers in the edge of conduction band move around 3- dimensional energy barriers without tunneling, thus calling it a percolation conduction mechanism in a-IGZO films. When the Fermi level is very low relative to the edge of conduction band, there are not enough electrons induced above the conduction edge as shown Fig. 1-14 (a). When the Fermi level is below that of the highest energy barriers, which are associated with the random distribution of Ga<sup>3+</sup> and  $Zn^{2+}$  ions in a single crystal structure InGaO<sub>3</sub> (ZnO)<sub>5</sub>, electron conduction is exclusively dominated by the percolation mechanism where electrons travel between the valley of potential energy barriers as shown in Fig. 1-14 (b), and the conductivity temperature dependence goes as T<sup>-1/4</sup>. However, once the Fermi level is located above the energy peaks of potential conduction band, the carrier density is high enough to fill all of the valleys in the tail regions and electron transport is dominated by a temperatureindependent, degenerate mechanism as shown Fig. 1-14 (c).

Fig. 1-13. Energyband diagram: (a) hopping conduction by quantum mechanical tunneling and (b) conduction by percolation mechanism.

Fig. 1-14. The conduction model suggested by Nomura, et al. (a) The Fermi level (blue plane) is very low than conduction band edge, (b) located above the edge of conduction (percolation conduction), and high enough on the edge of conduction(degenerate conduction).

The figures are from Hoshino, MS dissertation, Oregon State University, 2008.

#### Chapter 2

# Device fabrication and characterization

#### 2.1 Fabrication of a-IGZO TFT

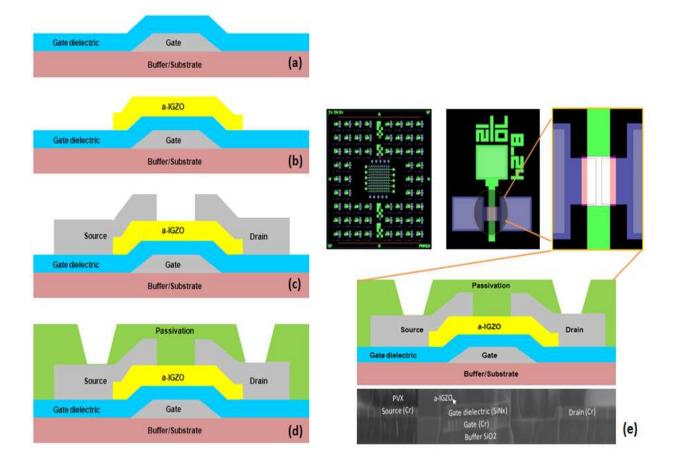

In this study, an inverted staggered bottom gate structure is preferred for a-IGZO TFT structure since the interface between the semiconductor and gate dielectric can be formed without exposure to air, which typically has better electrical properties. Fig.2-1 shows a schematic process flow of the fabricated device structure of a-IGZO TFTs for the BCE type TFT structure.

# 2.1.1 Gate electrode

The selection of a metal electrode material for gate electrode as well as source and drain electrodes has been considered to be one of the important parameters to design a device for interconnection such as a microchip and a flat panel display for large area application because the resistance in the metal line results in a voltage drop through the metal line inducing signal delay and possible switching problems to drive the device Therefore, the resistance of metal line must be sufficiently low from followed equation:

$$R = \rho \frac{L}{A} = \rho \frac{L}{Wd} = \frac{\rho}{d} \frac{L}{W} = R_s \frac{L}{W}$$

(2.1)

Where  $\rho$  is resistivity of metal electrode, L and W are the length and the width of metal line, the d is the thickness of metal line, and R<sub>s</sub> is the sheet resistance. In this study, chromium (Cr) was used for gate electrode because it has a reasonably low resistivity ( $\rho_{Cr} = \sim 1 \times 10^{-5}$  ohm-cm) comparable to Al and Cu ( $\rho_{Al} = 4 \sim 5 \times 10^{-6}$  and  $\rho_{Cu} = 3 \sim 4 \times 10^{-6}$

ohm-cm) and in addition, has a high etching selectivity during fluorine based plasma etching. The chromium bottom gate layer was rf magnetron sputter deposited (typically ~150 nm) with DC substrate bias of 5W (120V) and lithographically patterned and wet etched by Cr etchant (CR-14) (9%(NH<sub>4</sub>)<sub>2</sub>Ce(NO<sub>3</sub>)<sub>6</sub> + 6%(HClO<sub>4</sub>) + H<sub>2</sub>O) onto a 300nm SiO<sub>2</sub> coated silicon wafer (100mm diameter) at a room temperature without agitation. Because of wet etching process is isotropic the sidewall angles are typically shallow (~ 45°) which facilitates good step coverage for next deposition process as shown in Fig. 2-1 (a) and in the SEM image (e).

Fig. 2-1. a-IGZO TFT fabrication with BCE type of a-IGZO TFT structure; (a) gate dielectric/ patterned gate electrode (Cr) on buffer  $SiO_2$  /Si substrate, (b) sputtered a-IGZO island formation, (c) source-drain electrode formation by wet etching, (d) passivation deposition and via hole patterning by dry etching, and (e) cross-section SEM image of TFT.

# 2.1.2 Gate dielectric material

The gate dielectric material in metal oxide semiconductor (MOS) structures requires a high electrical resistance to minimize gate leakage current at the overlapped region of source/drain as well as high compatibility to semiconductor layer such as interface properties and inter-reaction [31]. For a silicon oxide-silicon nitride gate dielectric, the properties depend on the relative atomic concentrations of silicon, nitrogen, and hydrogen [32], [33]. In this study,  $SiN_{x}$  (200 nm) gate dielectric material was deposited by plasma enhanced chemical vapor deposition (PECVD). The standard deposition condition of PECVD SiNx film were 40W RF power, 1200 mTorr pressure, 5%SiH<sub>4</sub>-Ar/NH<sub>3</sub>/N<sub>2</sub> (150/2/790 sccm) gas flow, and 350°C temperature. The deposition rate was 14.28nm/min. This SiN<sub>x</sub> film was optimized for a Si-rich SiN<sub>x</sub> with lower film stress as described previously by Park [34]. In chapter 3, the electrical performance and instability with different gate dielectrics which include  $SiO_2$  and  $SiN_x$  and with plasma gas chemistry in SiN<sub>x</sub> will be presented in order to understand the relationship between gate dielectric property and electrical TFT properties in detail. Fig. 2-1 (a) shows the schematic structure after completion of gate dielectric on gate electrode.

#### 2.1.3 Semiconductor; a-IGZO

As mentioned in chapter 1, compared to Si based TFTs, a-IGZO TFTs have a very unique electrical transport mechanism and sensitive to deposition conditions. To characterize the properties of a-IGZO TFTs, a-IGZO active layers (50 nm) were rf magnetron sputter deposited using an 50mm diameter a-IGZO target ( $In_2O_3$ : Ga<sub>2</sub>O<sub>3</sub>: ZnO = 1:1:1 mol %) with different sputtering parameters .The standard sputtering

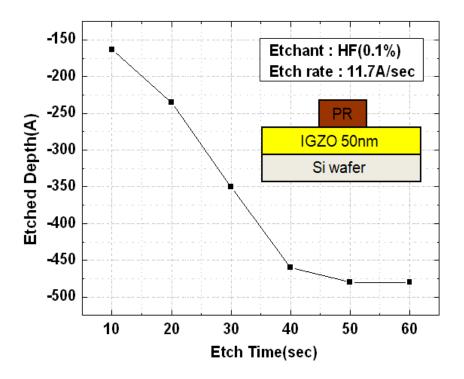

parameters for the a-IGZO films were: system base pressure was  $5 - 9 \times 10^{-7}$  Torr; rf sputtering power was 60 W with 170 V target bias; sputtering pressure was 5 mTorr Ar-O<sub>2</sub> gas mixture (75% Ar-25% O<sub>2</sub>). The a-IGZO was wet etched by BOE (0.1%) solution. a-IGZO layers were defined by wet etching and is schematically shown Fig. 2.1 (b). Fig. 2-2 shows an etch depth of a-IGZO as function of etch time in the Buffered Oxide Etchant (BOE, 0.1%). The a-IGZO 50nm was completely etched out after ~50 sec in the solution, showing 1.17nm/sec in etching rate. The diluted BOE (0.1%) minimally etches the gate dielectric; meaning the IGZO has high etching selectivity for the SiNx gate dielectric. For BCE type TFT structure as shown Fig. 1, after active layer deposition, Cr (~200 nm) source and drain (S/D) electrodes were also sputter deposited. For E/S type TFT structure as shown Fig. 1-3 (b), E/S layer with SiO<sub>2</sub> 100nm (in this study, it will be called channel passivation (CPVX) layer) was deposited on the a-IGZO without breaking vacuum and CPVX SiO<sub>2</sub> is patterned and etched via a dry etching process (Fig. 2-1 (b)).

#### 2.1.4 Source and drain electrode

Cr was also used for source and drain electrode. To select source and drain metal electrode of a-IGZO semiconductor, the work function difference between metal and a-IGZO was considered in order to form an Ohmic contact as well as the materials of low resistivity. There are two types of metal-semiconductor contact. First, Ohmic contacts, metal work function ( $\Phi_M$ ) is lower than semiconductor work function ( $\Phi_S$ ) which yield linear or quasi-linear current-voltage characteristics. The contact must be able to supply the necessary device

current, and the voltage drop across the contact should be small compared to the voltage drop across the active device regions and the metal electrodes. An Ohmic contact should not degrade the device to any significant extent. Secondly, the Schottky contact of the metal-semiconductor barrier occurs as  $\Phi_S$  $< \Phi_M$  which results in unnecessary voltage drop cross contact region. According to earlier reports, inverted staggered a-IGZO TFTs were shown to be contactlimited electrical behavior because of Schottky contact between a-IGZO and metal electrode which have relatively higher  $\Phi_M$  [35], [36], [37]. In this study, to realize an Ohmic contact and a better etching selectivity with a low resistivity, chromium (Cr) metal is used as gate and source-drain electrode since Cr has a high etch selectivity during fluorine based plasma etching as well as the work function of Cr with 4.5eV is lower than that of a-IGZO semiconductors with 5.01eV~ 4.3eV [38]. The Cr source/drain layers were deposited with 200nm in thickness with the same sputtering conditions as the gate electrode. Similarly the source/drain layers were patterned by photolithographically, and wet etched by CR 14S solution. Prior to wet etching the Cr, Cr/a-IGZO selectivity by Cr etchant (CR-14s) was tested in order to confirm the BCE TFT structure was possible without an E/S layer on a-IGZO by wet etching process. It was confirmed that the wet Cr etching process was possible based on the determined etch selectivity of Cr/a-IGZO = 13. Fig. 2-1 (c) shows the schematic structure after the formation of source and drain electrode pattern by the above described process.

Fig. 2-2. The etch depth of a-IGZO as function of time in the BOE (0.1%).

## 2.1.5 Passivation

A passivation (PVX) layer in the TFT commonly has been used to protect the device from subsequent processing and environmental effects. However, a-IGZO TFT with passivation shows peculiar characteristics because of sensitive nature of the a-IGZO backchannel to external conditions such as plasma and environmental ambient [39], [40], [41]. This topic will be studied in detail in chapter V. In this study, PVX layers were divided into two kind of PVX notation for convenience; 1) channel passivation (CPVX) is the layer that only passivate the channel area, minimizing plasma or chemical damage on following processes such as sputtered source and drain layer and chemically wet etching process of source and drain metal on the a-IGZO channel. The standard process consisted of a 100nm SiO<sub>2</sub> film as passivation layer which was deposited by rf sputtering method with the following deposition parameters. The system base pressure was  $5 \sim 9 \times 10^{-7}$  Torr. rf sputtering power was 200 W and sputtering pressure was 5 mTorr Ar-O<sub>2</sub> gas mixture. After photolithographic patterning, in order to contact the gate electrodes, for BCE TFT structure (without CPVX), via hole etching was performed by a combined wet etch using diluted HF etchant and dry etching process using a SF<sub>6</sub> + Ar gas chemistry and for E/S TFT structure (with CPVX), via hole etching was done by only dry etching process using a SF<sub>6</sub> + Ar gas chemistry. Fig. 2.1 (d) shows the final TFT structure after the via hole etching process.

## 2.1.6 Post annealing

a-IGZO TFTs were typically thermally activated by furnace annealing in an  $N_2$  ambient with 70 sccm in flow rate at 350°C for 1hr. The temperature ramping rate was ~ 15°C/min and naturally cooled down to room temperature. Before ramping up temperature, a sufficient circulation time with 20min with  $N_2$  was performed to minimize unnecessary gas contamination during annealing. In chapter 4, the post annealing effect with annealing conditions will be studied in detail.

# 2.2 Conclusion

The BCE type with an inverted staggered bottom gate structure was used for a-IGZO TFTs for better electrical performance. Cr metal was used for gate because of low electrical resistivity and easy wet etching process and gate dielectric (SiN<sub>x</sub>) was deposited by PECVD. a-IGZO as semiconductor was deposited by rf sputtering and patterned. S/D pad using Cr was deposited by rf sputtering and patterned by wet etching method. To contact gate, the via hole was formed by dry etching method. Finally, the device was post annealed at 350°C in N<sub>2</sub> ambient for 1hr. The fabrication process was summarized in Fig. 2-1.

#### Chapter 3

### **Gate dielectric**

# 3.1 Introduction

The gate dielectric film in the MOSFET device is one of the important functional materials, which enables a device to work such that it controls carrier generation and accumulation to the semiconductor by the induced electric field as well as it affects the optical transparency of a device [31]. The gate dielectric in a metal oxide semiconductor field effect transistor (MOSFET) can be simply modeled as a parallel plate capacitor, C =  $(k\varepsilon_0 A)/t$ , where A is the capacitor area, *k* is the relative dielectric constant of the material (i.e. ~ 3.9 for SiO<sub>2</sub> and ~ 7.1 for SiN<sub>x</sub>),  $\varepsilon_0$  is the permittivity of free space (8.85 x 10<sup>-14</sup> F/cm), and *t* is the thickness of the capacitor (dielectric).

There are several important parameters to control transfer characteristics of TFT through a gate dielectric such as dielectric breakdown strength, capacitance, and the interface states between a gate dielectric and a semiconductor, in which parameters are usually governed by the growing film deposition conditions such as gas ratio, power, temperature, and process pressure, affecting the density, structure, stoichiometry, and trap density in the film and thereby they cause the electrical properties to change. In particular they can vary the electrical instability, especially with regard to a threshold voltage shift by carrier injection or capture into traps in the gate dielectric (SiN<sub>x</sub>) [31]. The hydrogenated SiN<sub>x</sub> deposited by PECVD usually exhibits different physical, optical, and electrical properties due to different stoichiometry by controlling the content of Si-H, N-H, Si-Si, and S-N in the film.

A hysteresis study, investigating  $\Delta V_T$  at constant drain voltage, from a transfer curve of TFT device is one of the useful methods to evaluate electrical performance and instability. For the hysteresis study, the parameters that affect  $V_T$  in the accumulation mode given by:  $V_T=qn_0 d/C_i + V_{FB}$ . Where  $V_{FB}$  is the flat-band voltage, which accounts for work function difference between semiconductor and the gate metal, *q* is the elementary charge,  $n_0$  is the density of free carriers, and *d* is the thickness of semiconductor. Based on this equation,  $\Delta V_T$  through the forward and reverse scan occurs and a hysteresis can be expected if: 1)  $n_0$  changes (i.e., due to trapping of free carriers), 2)  $C_i$  changes (i.e., charge injection from the gate into dielectric), and 3)  $V_{FB}$  changes (i.e., structural changes in the semiconductor).  $V_{FB}$  is usually assumed to be constant in this study because a-IGZO semiconductors were deposited with the same sputtering conditions [42].

It is known that a hysteresis in TFT transfer curve as well as other electrical performance such as S,  $\mu_{FE}$ , and V<sub>T</sub> is strongly dependent on microscopic structural and charge effects with the following types. In Si-SiO<sub>2</sub> system, four general types of charge defects are known [31]: 1) interface-trapped charge are defects or impurities at the interface, 2) fixed charge in oxide is a positive charge due to structural defects, 3) trapped charge in oxide are electrons or holes trapped in the bulk of the oxide which can be introduced during device fabrication or operation, and 4) mobile charge in the oxide are mainly alkali metal cations and H<sup>+</sup> such that mobile Na<sup>+</sup> ions in gate dielectric (SiO<sub>2</sub>) cause V<sub>T</sub> shifts in the device. In addition, Garros *et al.* reported that high-k dielectrics increase the number of traps and thereby the size of hysteresis [43].

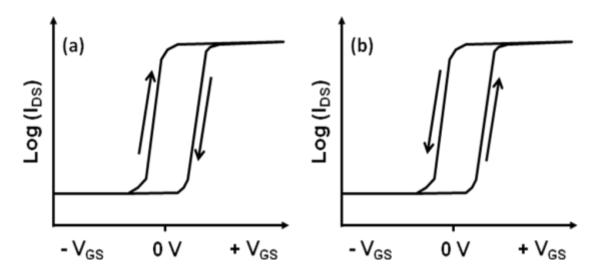

The hysteresis behaviors from transfer curve swing strongly depend on sweep rate; if the rate of release of charge from such a trap is sufficiently low, the sweep rate may be faster than the time necessary to reach thermal equilibrium, which results in hysteresis effects in the electrical characteristics of TFT. Fig. 3-1shows the two types of schematically depicted transfer characteristics of n-type semiconductor where, Fig. 3-1 (a), the back sweep current (BSC) is lower than the forward sweep current, called lower BSC hysteresis and Fig. 3-1 (b), the BSC is higher than the forward sweep current, called higher BSC hysteresis. It is known that the lower BSC hysteresis is due to following reasons: 1) trapped majority or minority charges at the semiconductor/dielectric interface (here, the minority trap effect is minor because a-IGZO features a degenerated electronic structure showing electron carrier conduction), 2) charge injection from a semiconductor into a dielectric, and 3) mobile ions in the semiconductor (in case of n-type semiconductor, positive mobile charges) which causes a decrease of the carrier density of semiconductor; decreasing I<sub>DS</sub>, causing lower BSC hysteresis. While the higher BSC hysteresis depicted in Fig. 3-1 (b) is usually due to mobile ions in gate dielectric. As on-gate voltage (a positive V<sub>GS</sub>) is applied to gate metal, the cations move towards the interface between gate dielectric and semiconductor and when V<sub>GS</sub> is swept back to 0 V (backward sweep), the ions stay close to the semiconductor, thereby retaining the diminishing field and causing higher BSC hysteresis [44].

Although the gate dielectric (usually oxide) resistivity is on the order of 10<sup>15</sup> ohm.cm, it is not infinite. Hence currents flow through a gate oxide for any gate voltage. However, for higher gate oxide electric fields, gate currents increase rapidly with voltage.