# Clemson University **TigerPrints**

All Dissertations Dissertations

12-2017

# Acceleration of High-Fidelity Wireless Network Simulations

Madhabi Manandhar Clemson University

Follow this and additional works at: https://tigerprints.clemson.edu/all\_dissertations

#### Recommended Citation

$Man and har, Madhabi, "Acceleration of High-Fidelity Wireless Network Simulations" (2017). \textit{All Dissertations}. 2054. \\ \underline{https://tigerprints.clemson.edu/all\_dissertations/2054}$

This Dissertation is brought to you for free and open access by the Dissertations at TigerPrints. It has been accepted for inclusion in All Dissertations by an authorized administrator of TigerPrints. For more information, please contact kokeefe@clemson.edu.

#### Acceleration of High-Fidelity Wireless Network Simulations

A Dissertation

Presented to

the Graduate School of

Clemson University

In Partial Fulfillment

of the Requirements for the Degree

Doctor of Philosophy

Electrical Engineering

by Madhabi Manandhar December 2017

Accepted by:

Dr. Daniel L. Noneaker, Committee Chair Dr. Harlan B. Russell, Committee Co-Chair Dr. Melissa C. Smith Dr. James Martin

#### Abstract

Network simulation with bit-accurate modeling of modulation, coding and channel properties is typically computationally intensive. Simple link-layer models that are frequently used in network simulations sacrifice accuracy to decrease simulation time. We investigate the performance and simulation time of link models that use analytical bounds on link performance and bit-accurate link models executed in Graphical Processing Units (GPUs). We show that properly chosen analytical bounds on link performance can result in simulation results close to those using bit-level simulation while providing a significant reduction in simulation time. We also show that bit-accurate decoding in link models can be expedited using parallel processing in GPUs without compromising accuracy and decreasing the overall simulation time.

## Acknowledgments

I would like to thank my advisor Dr. Daniel Noneaker for his guidance and support all through my graduate studies in Clemson. I would also like to thank Dr. Harlan Russell, Dr. Melissa Smith and Dr. James Martin for taking the time to serve as members of my committee and helping me with my dissertation.

A special thank you to my friends here in Clemson and back home for their help and support. And lastly, I thank my parents and my husband, Anjan for their constant support and encouragement in all my pursuits.

## Table of Contents

| $T_i$            | tle F                        | ${f Page}$                                                       |

|------------------|------------------------------|------------------------------------------------------------------|

| $\mathbf{A}$     | bstra                        | ct                                                               |

| $\mathbf{A}_{0}$ | ckno                         | wledgments i                                                     |

| $\mathbf{Li}$    | $\operatorname{st}$ of       | Tables                                                           |

| Li               | $\operatorname{st}$ of       | Figures                                                          |

| 1                | Intr                         | oduction                                                         |

| 2                | $\operatorname{Lit}\epsilon$ | erature Review                                                   |

| 3                | Sys: 3.1 3.2 3.3             | tem Description                                                  |

| 4                | Lin 1 4.1 4.2                | k Modeling with Off-Line Decoder Simulation                      |

| 5                | <b>App</b> 5.1 5.2 5.3       | Closed-form approximations to the probability of code-word error |

| 6                | <b>GP</b> 6.1 6.2 6.3 6.4    | U-Accelerated On-Line Viterbi Decoder Simulation                 |

| 7  | Net   | work Simulation with GPU-Accelerated Viterbi Decoding  | 63  |

|----|-------|--------------------------------------------------------|-----|

|    | 7.1   | Accelerating network simulation with PBVD algorithm    | 64  |

|    | 7.2   | Network simulation performance with the PBVD algorithm | 66  |

| 8  | Link  | Modeling in Large-Network Simulation                   | 76  |

|    | 8.1   | Simulation performance with the various link models    | 77  |

| 9  | GPU   | U-Based TDMP Decoding for LDPC codes                   | 85  |

|    | 9.1   | WiMax-standard LDPC code                               | 86  |

|    | 9.2   | TDMP algorithm                                         | 87  |

|    | 9.3   | Implementing the TDMP algorithm on a GPU               | 89  |

|    | 9.4   | Performance evaluation of TDMP algorithm               |     |

|    |       | using CPU and GPU                                      | 90  |

| 10 | Net   | work Simulation with GPU-Accelerated TDMP Decoding     | 96  |

|    | 10.1  | Simulation of the small network with TDMP decoding     | 97  |

|    | 10.2  | Simulation of the large network with TDMP decoding     | 100 |

| 11 | Con   | clusion                                                | 115 |

| Αį | open  | $\operatorname{dices}$                                 | 118 |

|    | Ā     | Computation complexity of Viterbi Algorithm            | 119 |

|    | В     |                                                        | 121 |

| Bi | bliog | graphy                                                 | 123 |

## List of Tables

| 3.1        | Main flow and interfering flows in the large network for various scenarios                                               | 17  |

|------------|--------------------------------------------------------------------------------------------------------------------------|-----|

| 4.1        | Time for bit-accurate simulation of one second of network activity                                                       | 27  |

| 5.1<br>5.2 | Link models for simulation systems considered                                                                            | 36  |

|            | inter-flow distance=2400 m                                                                                               | 40  |

| 7.1        | Time required to simulate one second of network activity, inter-flow distance=2400 m                                     | 74  |

| 7.2        | Time required to simulate one second of network activity with and without selective decoding, inter-flow distance=2400 m | 75  |

| 8.1        | Time required to simulate 1s of elapsed time, main flow spanning at least 4 hops                                         | 81  |

|            | Time required to simulate one second of network activity Time to simulate one second of elapsed time,                    | 111 |

|            | main flow spanning at least 3 hops                                                                                       | 112 |

# List of Figures

| 3.1<br>3.2 |                                                                                                                            | 14<br>16 |

|------------|----------------------------------------------------------------------------------------------------------------------------|----------|

| 4.1        | Performance with Viterbi decoding and two Gaussian channel models.                                                         | 29       |

| 4.2        | Performance with TDMP decoding and two Gaussian channel                                                                    | 30       |

| 4.3        | Throughput with bit-accurate and off-line table look-up Viterbi                                                            | 31       |

| 4.4        | Throughput with bit-accurate and off-line table look-up Viterbi                                                            | 32       |

| 4.5        | Throughput with bit-accurate and off-line table look-up TDMP                                                               | 33       |

| 5.1        | Throughput of $flow 1$ for various inter-flow distances and two interference probabilities, node E located at $(0, 3052)$  | 41       |

| 5.2        | Throughput of $flow\ 1$ for various inter-flow distances and two interference probabilities, node E located at $(0, 3352)$ | 42       |

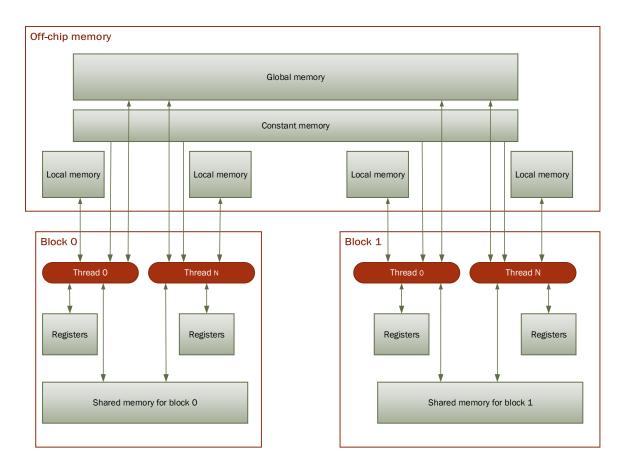

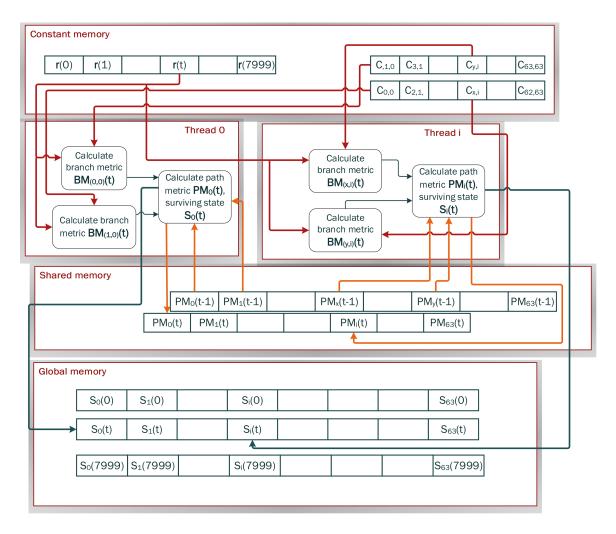

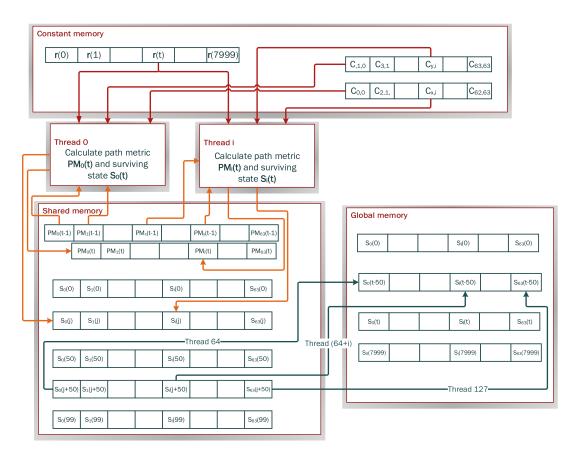

| 6.1<br>6.2 | Data flow for time step $t$ in the forward-pass phase of the Viterbi                                                       | 47<br>51 |

| 6.3        | Data flow diagram for Viterbi decoding with post computation data                                                          | 55       |

| 6.4        | 9                                                                                                                          | 60       |

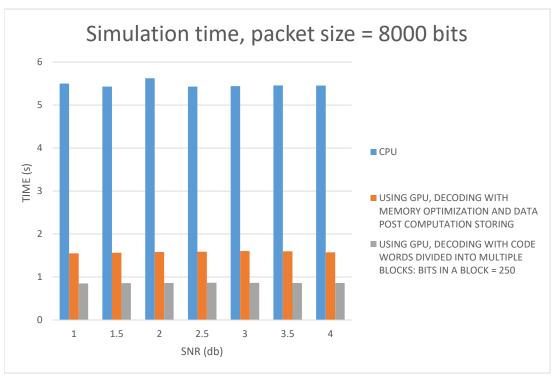

| 6.5        | Simulation time for packet sizes 16000 bits and 200 bits                                                                   | 61       |

| 6.6        | Simulation time for packet sizes 2000 bits and 8000 bits                                                                   | 62       |

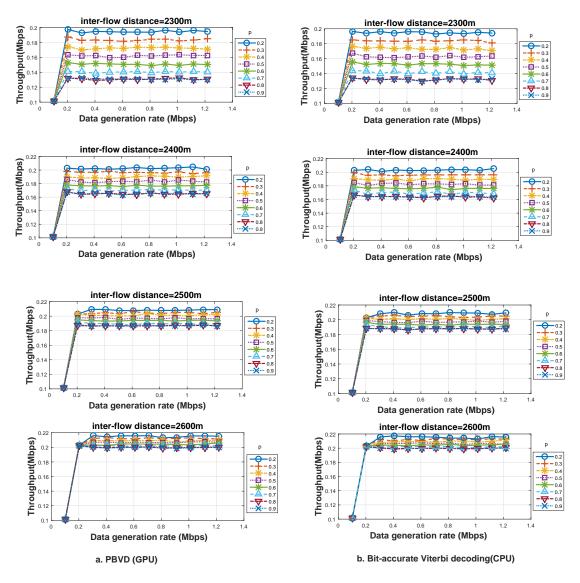

| 7.1        | Throughput with PBVD (GPU) and bit-accurate Viterbi decoding (CPU), node E located at (0, 3352)                            | 69       |

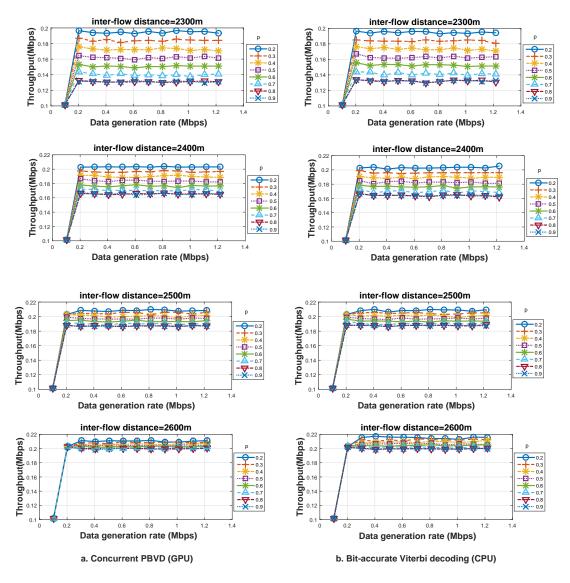

| 7.2        | Throughput with concurrent PBVD (GPU) and bit-accurate Viterbi                                                             | 70       |

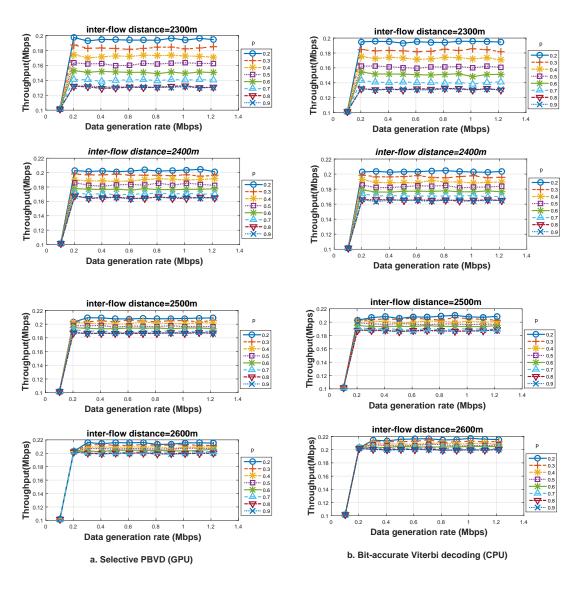

| 7.3        | Throughput with selective PBVD (GPU) and selective bit-accurate                                                            |          |

|            |                                                                                                                            | 71       |

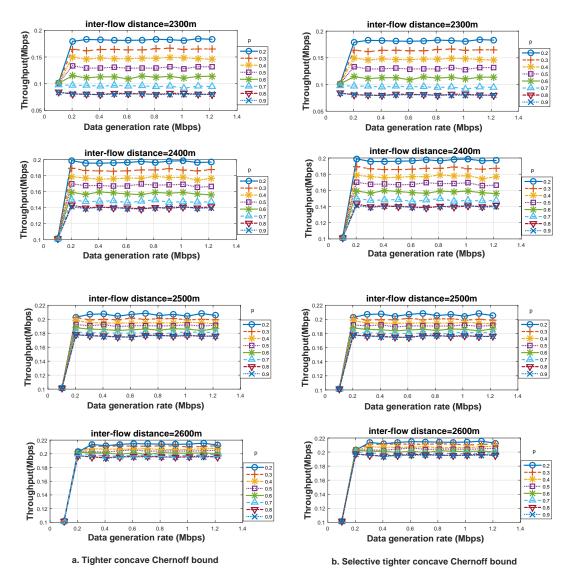

| 7.4<br>7.5 | Throughput with tighter concave-Chernoff bound and selective tighter concave-Chernoff bound, node E located at $(0, 3352)$ Throughput with concave integral bound and selective concave integral | 72       |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|            | bound, node E located at $(0, 3352)$                                                                                                                                                             | 73       |

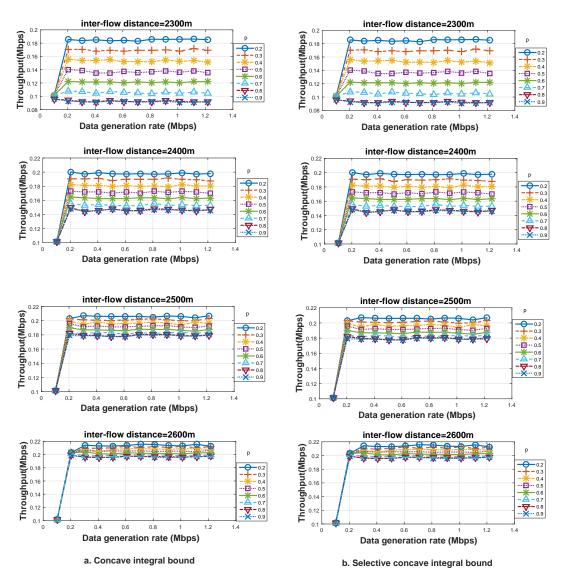

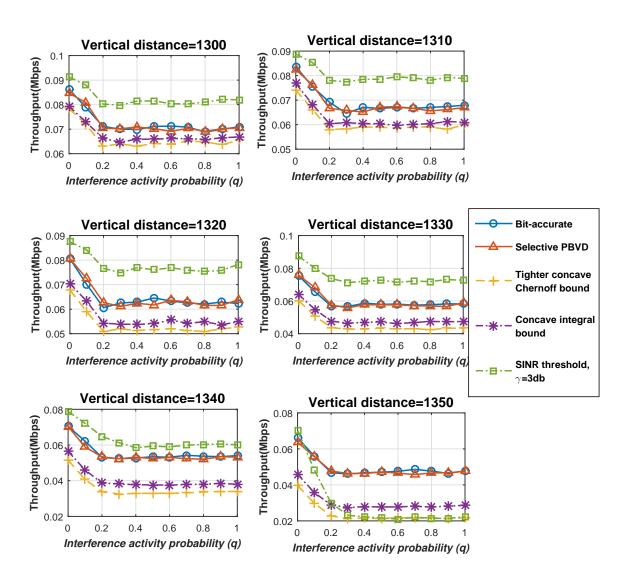

| 8.1        | Comparison of mainflow's throughput, mainflow spanning                                                                                                                                           | 0.0      |

| 8.2        | at least 3 hops                                                                                                                                                                                  | 82       |

| 8.3        | at least 4 hops                                                                                                                                                                                  | 83       |

|            | at least 5 hops                                                                                                                                                                                  | 84       |

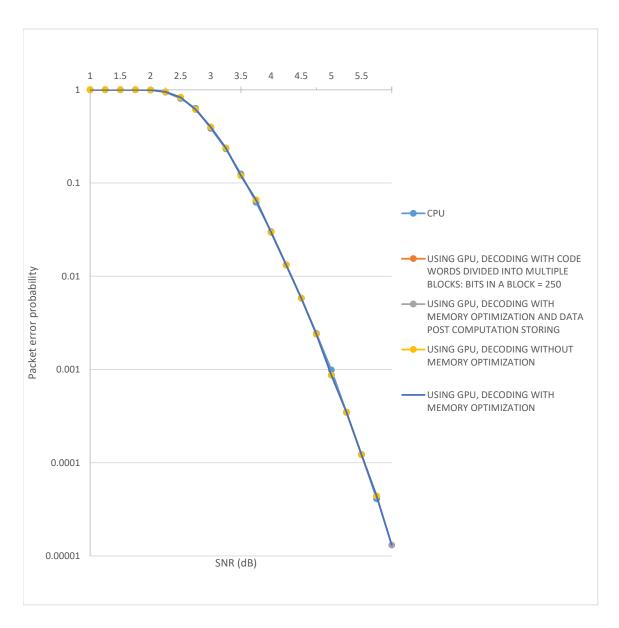

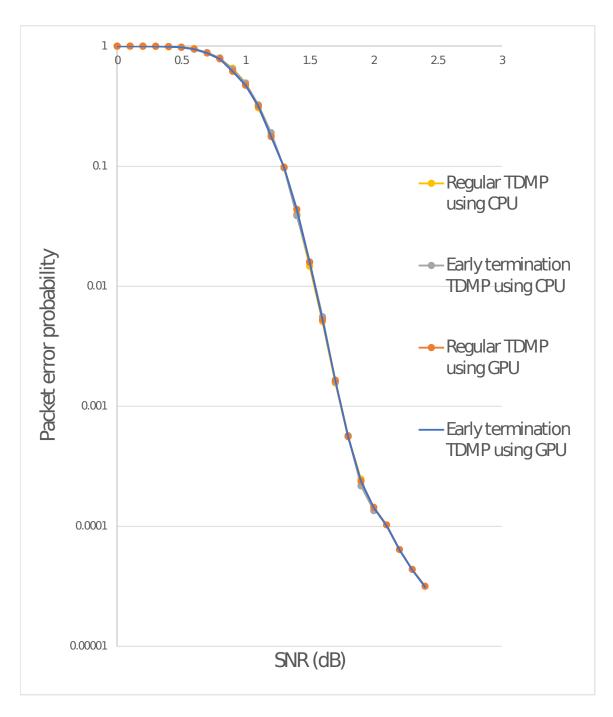

| 9.1        | Packet error probability for TDMP decoding of (2304,1152)                                                                                                                                        | 05       |

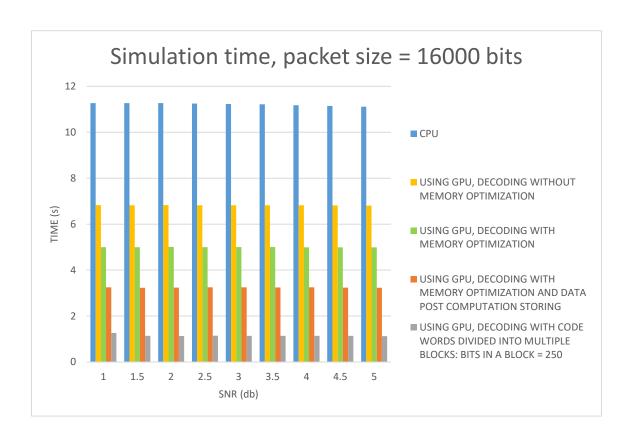

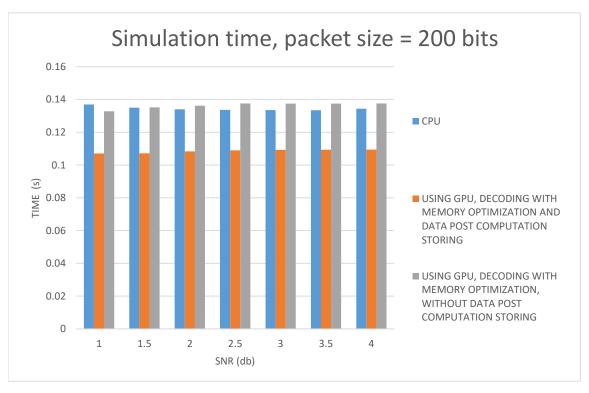

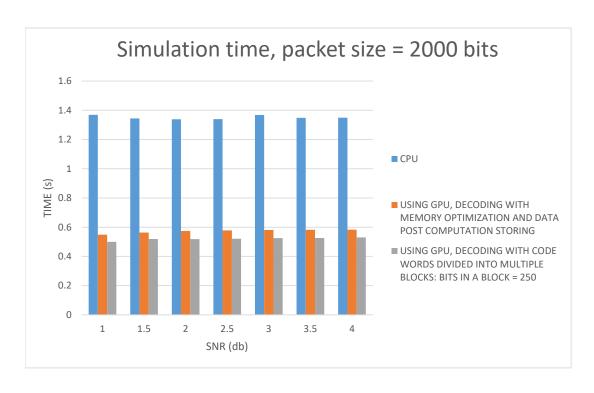

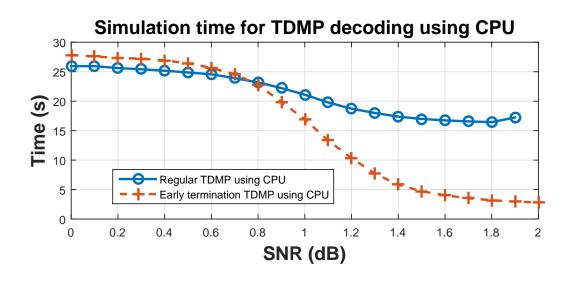

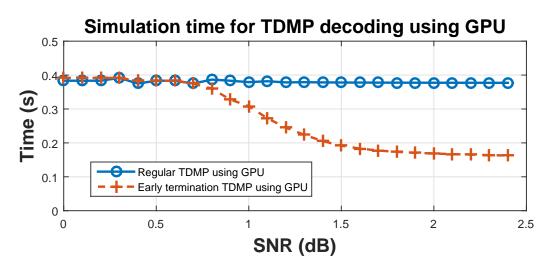

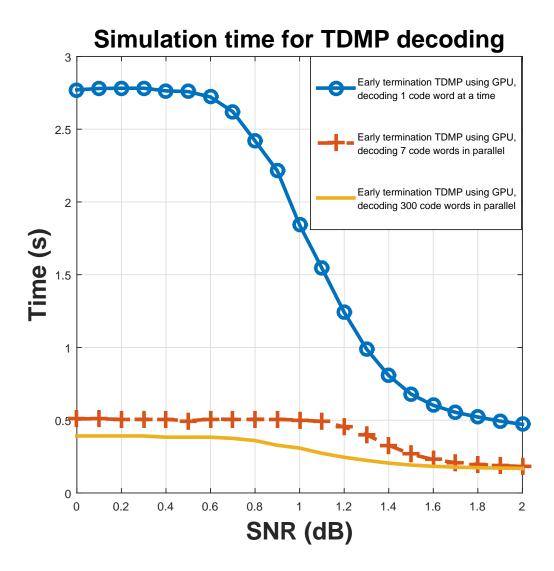

| 9.2<br>9.3 | LDPC code                                                                                                                                                                                        | 93<br>94 |

|            | LDPC code                                                                                                                                                                                        | 95       |

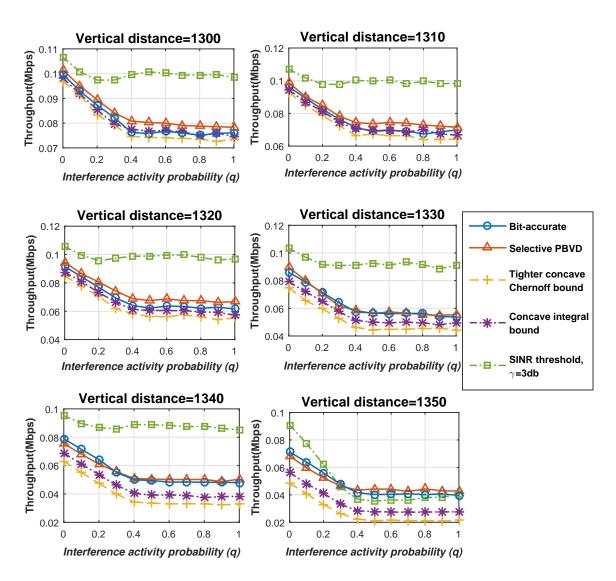

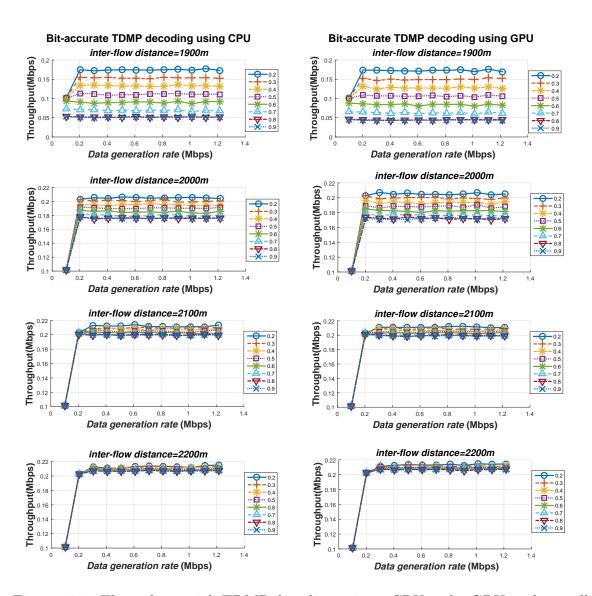

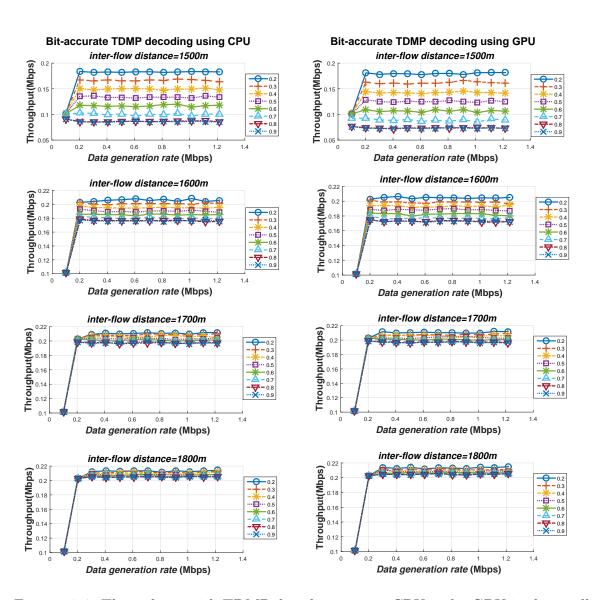

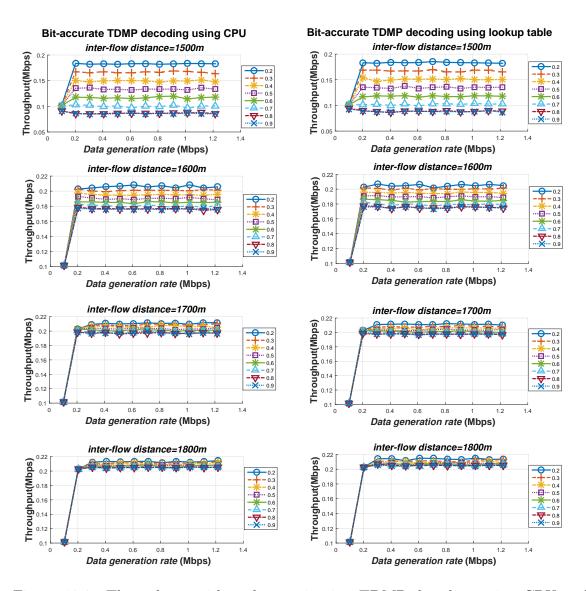

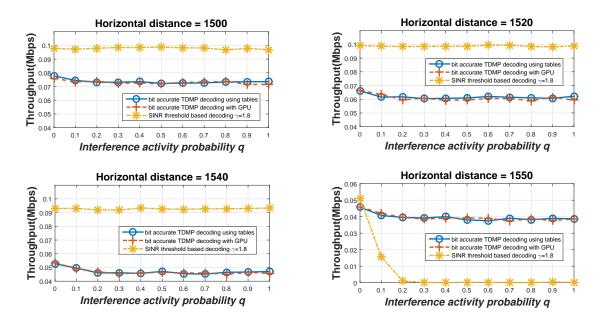

| 10.1       | Throughput with TDMP decoding using a CPU and a GPU in the small network, node E located at (0, 3052)                                                                                            | 103      |

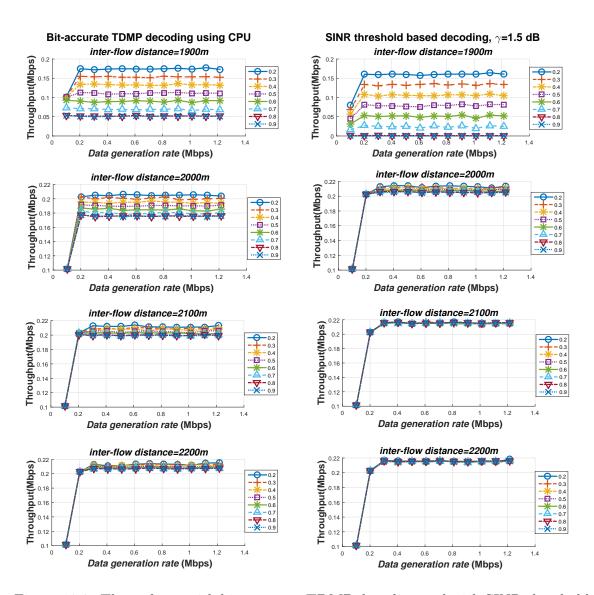

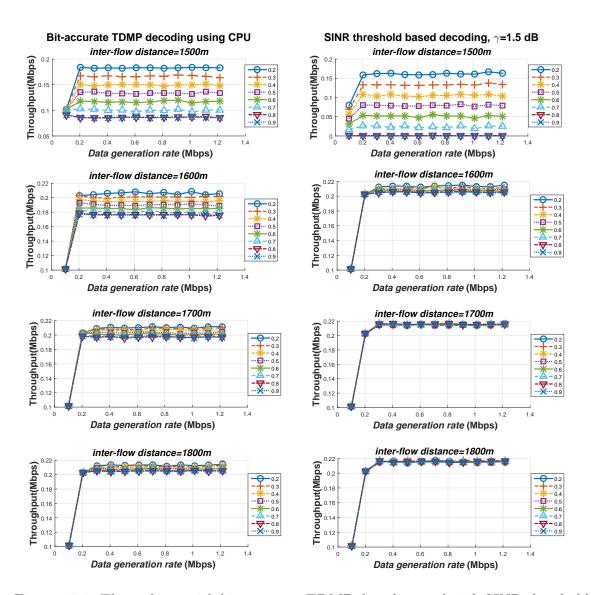

| 10.2       | Throughput with bit-accurate TDMP decoding and with SINR threshold $\gamma = 1.5$ dB in the small network, node E located at $(0, 3052)$                                                         | 104      |

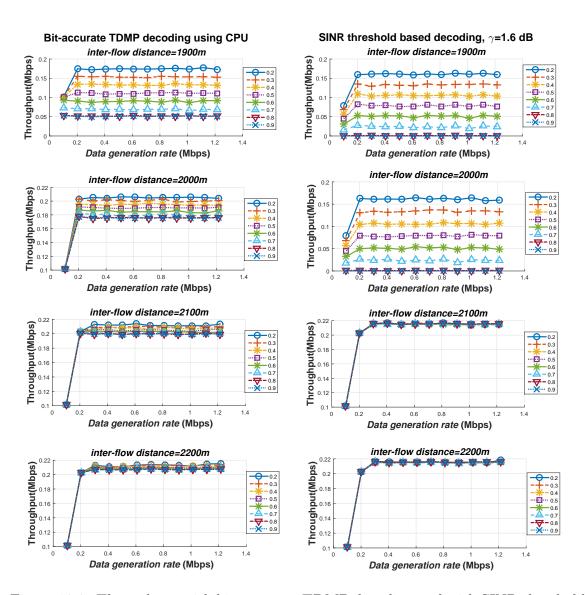

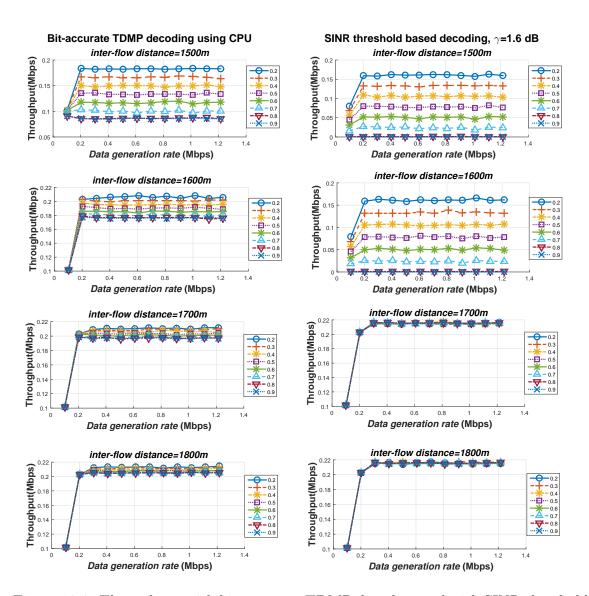

| 10.3       | Throughput with bit-accurate TDMP decoding and with SINR threshold $\gamma = 1.6$ dB in the small network, node E located at $(0, 3052)$                                                         | 105      |

| 10.4       | Throughput with TDMP decoding using a CPU and a GPU in the small network, node E located at (0, 3352)                                                                                            | 106      |

| 10.5       | Throughput with bit-accurate TDMP decoding and with SINR threshold $\gamma = 1.5$ dB in the small network, node E located at $(0, 3352)$                                                         | 107      |

| 10.6       | Throughput with bit-accurate TDMP decoding and with SINR thresh-                                                                                                                                 |          |

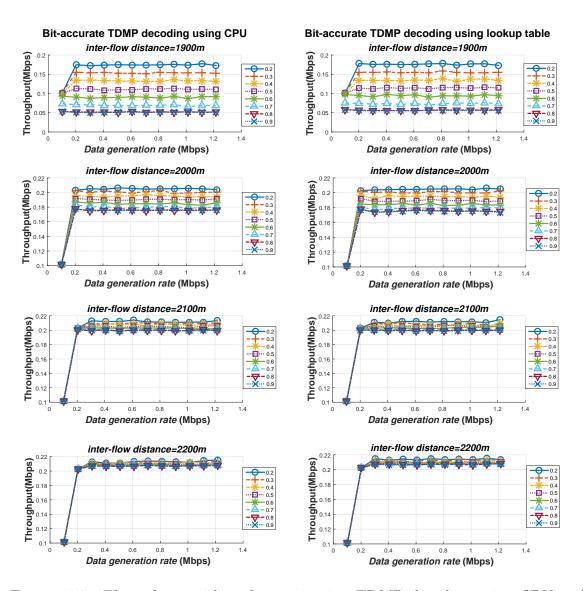

| 10.7       | old $\gamma = 1.6$ dB in the small network, node E located at $(0, 3352)$ Throughput with TDMP decoding using CPU and bit-accurate lookup                                                        | 108      |

| 10.0       | table, node E located at (0, 3052)                                                                                                                                                               | 109      |

| 10.8       | table, node E located at (0, 3352)                                                                                                                                                               | 110      |

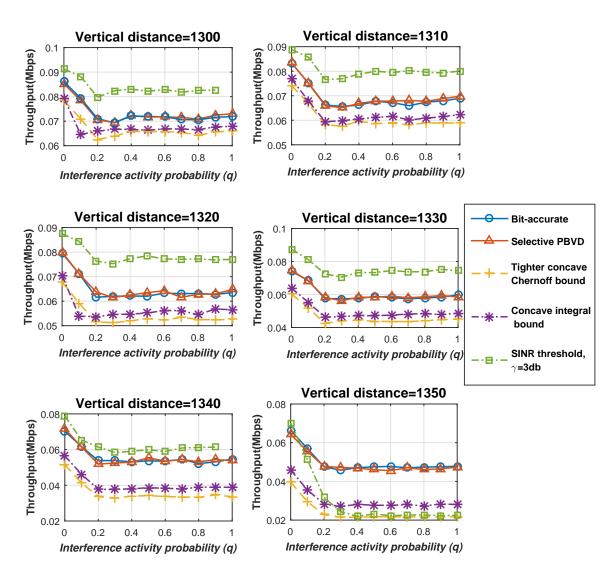

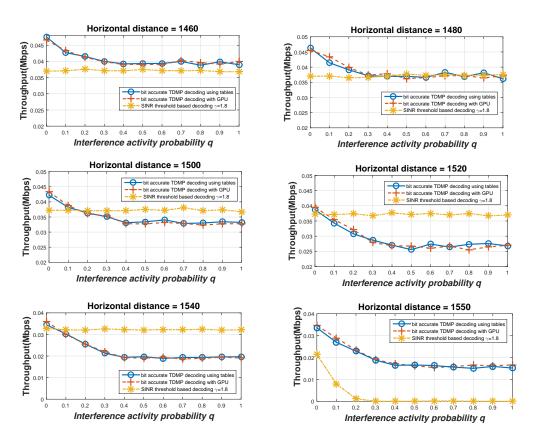

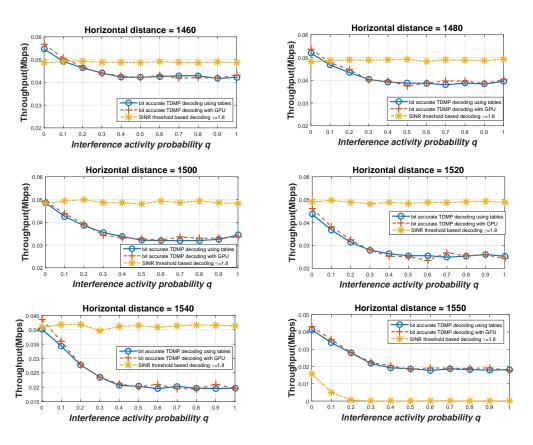

| 10.9       | Throughput of main flow, main flow spanning at least 3 hops                                                                                                                                      | 112      |

|            | OThroughput of main flow, main flow spanning at least 4 hops                                                                                                                                     | 113      |

| 10.11      | 1 Throughput of main flow, main flow spanning at least 5 hops                                                                                                                                    | 114      |

#### Chapter 1

#### Introduction

Ad hoc radio networks are widely used to provide reliable communication in environments that lack physical communication infrastructure. The need for increased efficiency in the use of the limited radio spectrum and the desire for a wider range of services in wireless networks stimulates ongoing research into the development of protocols that provide greater spectral efficiency, increased end-to-end throughput, and a better quality of service in ad hoc radio networks. Both research and development require thorough testing of the various protocols, radio communication techniques, and applications under consideration in a wide range of realistic operating conditions.

The difficulty and cost of achieving wide-ranging testing of a radio network with hardware prototypes dictates extensive use of network simulation as a tool for characterizing the performance achieved in the network. A well-designed network simulation with an accurate bit-level model of each radio communication link in the network can reflect the behavior of the actual network with high fidelity. The components of each link include the format of its radio transmissions, the properties of the radio channel, and the architecture and algorithms in its radio receiver.

Unfortunately, this level of fidelity comes at the cost of a complicated link

model which can result in extremely long simulations to obtain the desired performance data. (The most computationally intensive part of an accurate bit-level link model is frequently the implementation of the decoding algorithm for the error-correction code used in the link transmission.) The network simulation time can be reduced substantially if a link model of low complexity is used instead, but the time savings comes at the cost of reduced accuracy in the results. This trade-off between the fidelity and computation time in the simulation of an ad hoc radio network is the focus of this dissertation, with particular attention paid to the choices in modeling the radio links of the network and in the computational platform that is used to implement the computationally intensive decoding algorithm for the link model.

Among the simplest link models used in a wireless network simulation is the free-space path-loss model [1]. A radio transmission results in a signal power at a receiving node in the network which is determined based on the antenna gains at the transmitting node and the receiving node in the direction of the communication, the distance-dependent path-loss model used for the channel, and the distance between the two nodes. A transmission is treated as successful within the simulation if the received power is greater than a predefined threshold. A drawback of this model is that it does not take into account interference that might be present in the network during the packet reception process. Alternatively, the distance between the transmitter and the receiver can be used directly in the simulation to determine the success of a transmission for given antenna gains and a given transmission format [2, 3]. In this transmission range model, a transmitting node only communicates with a receiving node that is within its "transmission range".

Another link model regularly used in wireless network simulation is the *capture threshold model* [4]. Unlike the free-space path loss model, this model calculates the signal-to-interference-plus-noise-ratio (SINR) at the receiver but accounts for only

one interferer at a time. The SINR for each interferer is calculated separately and successful reception of a packet is only confirmed if all the SINRs are greater than a designated threshold. This model is implemented in the ns-2 discrete-event network simulator [5], and research focused on higher-layer protocols that uses ns-2 as a network simulation tool often uses the default capture threshold model [6–8]. A better approach is to consider the aggregate effect of all interferers in determining the the received signal, which in fact reflects the true SINR at the receiver. The additive interference model [4] implements this by considering all the unwanted received signals as equivalent Gaussian noise. A transmission is considered successful in this model only if the received SINR is above a predetermined threshold. The additive interference model is the default channel model in the ns-3 discrete-event network simulator [9].

A more precise approach to link modeling accounts explicitly for the errorcorrection coding and the corresponding decoding algorithm used in the link. This is

often the most computationally intensive part of bit-accurate link simulation, which

can be mitigated at the time of network simulation by use of a predetermined look-up

table for the probability of error at the decoder output. The look-up table is indexed

by one or a few simple link parameters, and if the index parameter provide sufficient

flexibility in the link scenarios that are reflected, the computation time to construct

the table can be amortized over many network simulations.

The computational cost of constructing a fine-resolution look-up table increases with the range of transmission formats (error-correction code, modulation format, packet size), types of interference environment, and decoding algorithms considered in the network simulations. Consequently, the bit-accurate link model is often replaced by a simpler model that uses the additive interference model [10–12] with a threshold chosen according to the modulation and coding used in the system.

Alternatively, some classes of links are amenable to analytical methods for determining a closed-form expression that gives or approximates the probability of error in a link transmission. For example, bounds on the code-word error probability for convolutional coding and hard-decision Viterbi decoding over an independent, identically distributed (i.i.d.) Gaussian noise channel is obtained using the first-event error probability [13]. Similarly, bounds on the probability of code-word error that are applicable to soft-decision Viterbi decoding for a broader class of Gaussian noise channels is developed in [14]. Each provides flexibility in accounting for different error-correction codes and packet lengths. The resulting expression can be evaluated for each simulated link transmission as the basis for determining the outcome of that transmission.

The development of the graphical processing units (GPU) as a tool for general-purpose computing has helped stimulate increased interest in the use of hardware parallel architectures for error-correction decoding. It has included investigations of parallel implementation of Viterbi decoding for convolutional codes [15], [16], [17]. Some newer classes of error-correction codes, such as quasi-cyclic low-density parity-check (LDPC) codes are designed specifically to support a high level of parallelism in decoding algorithms for the codes [18], [19], [20]. This introduces the possibility of incorporating parallel processing for error-correction decoding in a network simulation as a component of bit-accurate link modeling in order to reduce the computation time of the simulation.

The first part of this dissertation is focused on bit-accurate simulation of Viterbi decoding of a convolutional code and approximations of the resulting error probability using various analytical bounds. We analyze the effects of the resulting link models on the accuracy of the simulation of a small ad hoc radio network. GPU-based parallel processing of the Viterbi decoder and its implementation in the network

simulation is also examined. The analysis of link models and parallel processing is extended to their use in the simulation of a large ad hoc radio network as well. In the second part of the dissertation, the same questions are addressed for a network in which LDPC codes are used in the link transmissions. GPU-based parallel implementation of a decoder for LDPC codes and its incorporation into a network simulation is considered. The simulation tool ns-3 along with the external library it++ [21] is used for all the network simulations, together with custom-developed modules for some of the link-layer models.

The remainder of the report is organized in the following manner. A review of related research is presented in Chapter 2. Chapter 3 describes the system and channel considered in the dissertation. Chapter 4 is focused on the use of off-line generated look-up tables of the probability of code-word error with Viterbi decoding for convolutional codes and a decoding algorithm for LDPC codes. In Chapter 5, the performance of the Viterbi decoder and its approximations using different types of analytical bounds is studied. Chapter 6 and 7 address parallel implementation of Viterbi decoding and its incorporation into ns-3. The various link models with Viterbi decoding are considered in the context of the large network in Chapter 8. Parallel decoding of LDPC codes and its implementation in ns-3 is presented in Chapters 9 and 10. And summary of conclusions from the research is presented in Chapter 11.

### Chapter 2

#### Literature Review

Earlier studies on network layer research and scheduling algorithms did not emphasize a lot on the channel models and interference present in the network. Since detailed channel and interference models have higher complexity, these research only focused on the network layout to design scheduling algorithm widely known as graph based scheduling [22], [23], [24]. These algorithms provide transmission and scheduling using the graph based approach that completely avoids secondary interference in the network i.e. interference from other transmitters present nearby. Eventually new research popularized the concept of interference-based scheduling that includes interference present in the network to build more realistic scenarios. The difference in performance using a graph based scheduling and a new scheduling that uses full knowledge of the interference environment is shown in [25]. The interference model computes the signal-to-interference ratio and adds an extra condition for the received SIR to be greater than a threshold before allowing a set of links to transmit simultaneously. It concludes that by acknowledging the interference in the network, the new scheduling can avoid poor channel conditions that results in better network performance compared to the graph-based scheduling. In [26], the performance of a graph-based scheduling algorithm on two different physical layer models namely the Protocol Interference Model and Physical Interference Model is compared to show how its performance deteriorates if a channel model that accounts for network interference is used.

Newer network layer research use more developed interference models to calculate the received SINR for more accurate results as seen in [27] and [28]. However, these models assume communications are perfect if the received SINR is greater than a predefined threshold. More precise results can be obtained if the received SINRs are used to probabilistically determine if packets are received correctly or not, based on the physical and link layers of the system. The importance of using accurate physical layer models in wireless network simulations and uses a statistical approach to develop empirical models for mobile wireless networks based on several field experiments is discussed in [29]. Similarly, the differences in system performance when using efficient simple models to a more computationally complex yet comprehensive models like SIRCIM [30] is detailed in [31]. It emphasizes on the use of accurate physical layer models that uses bit error rates for packet reception in wireless network research and also presents ideas on parallel executions using scalable simulation library GloMoSim [32]. An even more detailed discussion on the necessity of accurate physical layer modeling of MANETs is given in [33]. It also compares the performance of GloMoSim with ns-2.

Network simulators provide a convenient tool to simulate and examine wireless network protocols and applications. OPNET [34], network simulator 1, 2 and 3, OMNET++ [35], GloMoSim, QualNet are some well known wireless network simulators. Over the years network simulators have also seen development both in terms of complexity and accuracy. Simulators like ns-3, OMNET++, OPNET, GloMoSim have comprehensive interference and physical layer models. These simulators also

have BER based signal reception along with SNR threshold based reception. However, they don't have bit-accurate implementation of link-layer models. Some of them though have link layer models that use tables with packet error probabilities for the link layer codes used, as shown in [36]. There have been studies to obtain alternate ways to model the link-layer codes used without having to use tables or encoders and decoders in the network simulation [13]. The research provides an upper bound on the code-word error probability for convolutional coding and hard-decision Viterbi decoding over an independent, identically distributed (i.i.d.) Gaussian noise channel. The upper bound obtained here can be easily implemented in a wireless network simulator to carry out packet reception based on packet error probabilities of the link-layer codes used. Similarly, upper bounds on the probability of code-word error to soft-decision Viterbi decoding for Gaussian noise channels is developed in [14] and bounds on Viterbi decoding in direct-sequence code-division multiple-access (DS-CDMA) systems using binary convolutional coding, quaternary modulation with quaternary direct-sequence spreading is developed in [37]. These bounds can also be directly applied in the network simulators available.

The straightforward way to use bit-accurate link-layer models is to implement bit-accurate decoders in network simulation. However, the large simulation time required by link-layer decoders discourage users to include them in network simulators. There have been various researches to accelerate link-layer decoders. The idea of parallely decoding Convolutional codes in software defined radio using GPUs is introduced in [15]. It shows that Viterbi decoders can be sped up by carrying out the calculations of each state in parallel by assigning the calculations of each state to a single thread. The same parallel decoding is further accelerated in [16] by the tiled Viterbi decoding algorithm (TVDA). TVDA divides each block of received words into multiple chunks and carries out parallel Viterbi decoding as shown in [15] for each

of the chunk in parallel. After the calculations, the results from individual chunks are merged to obtain a surviving path from the trellis. Another version of parallel decoding of Viterbi codes referred to as the parallel block-based Viterbi decoder (PBVD) implemented in CUDA is presented in [17]. The PBVD algorithm also divides the received words into multiple chunks and carries out computations in the individual chunks independently. The final merging step is not required in this algorithm. Similarly parallel decoding of LDPC codes have also been a topic of interest as LDPC codes are widely used in wireless network communications. The parallel version of the belief propagation algorithm for decoding LDPC codes is presented in [19]. Similarly a scalable and flexible implementation of LDPC decoder on a GPU is shown in [20]. Furthermore, the turbo decoding message passing algorithm, which is a form of layered belief-propagation algorithm is parallelized in [18]. It uses the offset-min-sum TDMP algorithm to decode quasi-cyclic LDPC codes in parallel using stream processors.

## Chapter 3

### System Description

We consider two ad hoc radio networks as examples for the numerical results in this dissertation. The first network consists of four nodes with static single-hop routes and a single non-coordinated source of interference. The network is referred to as the *small network*, and it provides a simple scenario for gaining insights into the network-level tradeoffs provided by the use of different methods of link-layer modeling and simulation. The inter node distances in the small network are selectable parameters which permit the identification of extremal conditions in the tradeoffs.

The second network contains 64 nodes and employs dynamic multiple-hop routing. It is referred to as the *large network*. The performance of the large network for different methods of link-layer modeling and simulation permits a comparison of the tradeoffs among the different approaches when they are applied to the simulation of an ad hoc radio network of practical interest. Performance results for each network are obtained by simulating the network in ns-3 [9].

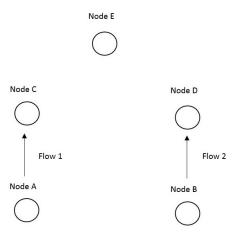

#### 3.1 Small network

The topology of the small network is shown in Figure 3.1. Network nodes A, B, C, and D are placed at the corners of a rectangle. Node A generates packets directed to node C at a fixed rate. The data flow from node A to node C is referred to as flow 1. Similarly, node B generates packets for node D at a fixed rate, and the data flow from node B to node D is called flow 2. The distance between nodes A and C is the transmission distance, and the distance between nodes A and B is referred to as the inter-flow distance. The transmission distance is fixed at 2600 m and the inter-flow distance is varied from 2000 m to 5000 m to analyze various network conditions. Node E is a non-coordinated transmitter (i.e., a jammer) located on the line that is the perpendicular bisector of the line joining nodes A and B. If the line connecting nodes A and B is considered as the x-axis and its perpendicular bisector is considered as the y-axis, the location of node E can be expressed in Cartesian coordinates as (0, y). All distances are expressed in meters, and the network performance is considered for different values of the transmission distance and the inter-flow distance and for two values of y.

The network nodes use the 802.11b [38] protocol with a maximum data-symbol rate of 1 Mbps for both data and control messages. Nodes A and B transmit data packets of size 2016 bytes which convey information from a constant-bit-rate source in each of the two nodes. (Each source is implemented in the simulation by a constant-bit-rate generator available in ns-3.) The data rate of each of the two sources, referred to as the *data generation rate*, can be varied to generate data at a specified bit rate up to the maximum. The media access control (MAC) sub-layer [39] is configured in ad hoc mode [40]; so that each node is capable of operating as a router and is able to both transmit and forward data packets. The nodes in the simulation for the small

network contain a trivial network layer, however, so that no dynamic routing occurs in the example scenarios. The nodes use UDP [39] at the transport layer.

The ad hoc mode of the 802.11b MAC sub-layer uses an "RTS/CTS" protocol in which the link's data source node transmits a Ready-to-Send (RTS) control packet addressed to its intended link destination mode to request reservation of the destination's attention for a subsequent data packet transmission. If the intended destination replies with a Clear-to-Send (CTS) control indicating it is available to receive a data transmission, the source node transmits a data (DATA) packet addressed to the destination node. If the destination node acquires the data packet, successfully detects the data payload of the packet, and confirms that it is the intended recipient of the packet, it returns an acknowledgment (ACK) packet to the data source node. The CTS packet is also detected by third-party nodes in the network. It allows them to recognize that a subsequent data packet transmission is imminent; thus, it serves the additional function of reserving the channel in the local area of the intended destination for the duration of the packet data transmission. The control packet and data packet transmissions are unslotted.

In the physical layer of each network node, the received word (i.e., symbol-rate samples) for each data or control packet that is acquired are decoded based on the system's error-correction code. If the received word is not decoded correctly, the packet is ignored. Each successfully detected physical-layer packet payload is forwarded to the MAC sub-layer. The MAC sub-layer determines the MAC packet type and its addressed destination. Each data and control packet not addressed to the current node is used to update the node's network allocation vector (NAV) and then dropped, but the MAC-layer payload of a data packet addressed to the node is passed to the next higher protocol layer. Each control packet addressed to the current node is utilized in the MAC sub-layer as described in the previous paragraph.

In the physical layer of the node, an error-correction code is used to encode each data or control packet in a single code word per packet. Two codes are considered here: the NASA standard rate-1/2, convolutional code [41] and the WiMax standard rate-1/2, (2304,1152) low-density parity-check (LDPC) code [42]. Since powerful LDPC codes of an appropriate length are not available for the (short) control packets, the convolutional code is used to encode the control packets even if the data packets are encoded with the LDPC code. The physical layer also follows the 802.11b protocol with a few changes. Instead of differential binary phase-shift keyed (differential BPSK) modulation, coded data bits are transmitted using BPSK direct-sequence spread-spectrum (DS/SS) modulation with a spreading factor of  $N_S = 22$ . All transmissions occur with the same power.

The jammer, node E, uses a time-slotted transmission of data packets in time slots of 3 s duration. The jammer is transmitting or silent in each of the sequence of time slots according to a sequence of independent, identically distributed Bernoulli random variables with a transmission probability p (the *interference probability*). The transmitter power for the jammer is 8 dB more than the transmitter power for other nodes in the network. The transmissions of node E use the same packet format as the data packets transmitted by the network nodes. Node E does not transmit 802.11b control packets, and its transmissions are not addressed to any of the network nodes. As p is increased, the four network nodes experience an increased probability of interference from the jammer. Besides p, the location p of node E can also be changed along the perpendicular bisector to alter the interference power at the network nodes.

The free-space channel is modeled by the Friis propagation equation [43]. Both thermal noise with power spectral density  $\frac{N_0}{2}$  and interference from other transmissions affect the received signal. The interference power at a receiver from either the jammer or other network nodes (or both) may vary within the reception interval of

Figure 3.1: 5 node wireless ad hoc network.

a packet since the transmissions of the nodes are asynchronous. Thus, the received signal-to-interference-plus-noise ratio (SINR) is not necessarily constant throughout the packet reception interval. At a given time instant, with either rate-1/2 code, the received SINR at node j for the flow from node i to node j is given by

$$SINR_{i,j} = \frac{2P_i N_s T_c}{\left(N_0 + \sum_{\forall k \neq i,j} P_k T_c\right)}$$

where  $P_k$  is the power received from node k and  $T_c$  is the chip duration of the DS/SS transmission. In the small network simulation, the transmitter powers for the network nodes are chosen such that the received signal to noise ratio (SNR) at transmission distance = 2600 m is 12.022 dB when there is no interference from neighboring nodes and the jammer node.

The receiver in each network node uses a coherent, matched-filter detector with the optimal sampling time for each symbol. Each received word is decoded at

the physical layer and passed to the MAC sub-layer. The throughput of each flow is measured in the MAC sub-layer. Soft-decision Viterbi decoding [44] is used for decoding each received word if the physical layer uses the convolutional code, and the turbo-decoding message-passing (TDMP) algorithm [18] is used for decoding each received word if the physical layer uses the LDPC code.

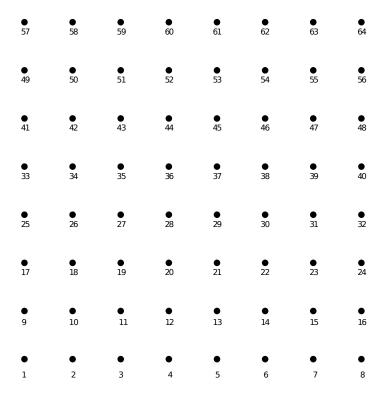

#### 3.2 Large network

The 64 nodes of the large network are arranged on a grid of 8 rows by 8 columns as shown in Figure 3.2. The horizontal distance between two adjacent nodes is fixed at 900 m and the vertical distance is varied from 1300 m to 1350 m in order to vary the received signal power. The Optimized Link State Routing (OLSR) protocol [45] is used in the network layer to enable packet forwarding with dynamic multiple-hop routing. The transport-layer protocol, the data link layer protocol (including the MAC sub-layer protocol), and the physical-layer protocol options are the same for the nodes in the large network as for the network nodes in the small network.

In the examples considered here, the performance metrics focus on one data flow (the main flow), a UDP connection between two widely separated nodes which employs a dynamic route that spans multiple hops at each point in time. The main flow's source node generates packets at a very high rate and therefore always has a packet to transmit to the destination node. The other data flows in the network are UDP connections between two nodes that are either horizontally adjacent or vertically adjacent in the rectangular array of nodes. The route for each one thus nominally consists of a single hop. They are considered as interfering flows to the main flow.

The locations of the interfering flows are chosen such that they have minimal effect on the RTS/CTS transmissions in the main flow, but the multiple-access in-

Figure 3.2: 64 node ad hoc radio network.

terference may have a significant effect on the reception of data packets in the main flow. Each source node for an interfering data flow generates packets according to a time-slotted packet generation schedule with 3 seconds slots, and it generates a single packet at the start of a slot with a probability of q. (The sources of the interfering flows are not synchronized so that the slot boundaries of their respective generation schedules are randomized.) If q=0, none of the source nodes in the interfering flows generate packets over the entire simulation period and if q=1, each source node generates a packet in each of its packet-generation slots. Thus, q is proportional to the average interference power a node in the main flow encounters and is referred to as the *interference activity probability*. (Note that the slotted structure applies only to packet generation for the given interfering data flow; the MAC protocol used in each node employs unslotted channel access.)

| link layer code    | minimum | main flow                                | interfering flows                                            |

|--------------------|---------|------------------------------------------|--------------------------------------------------------------|

|                    | hops in |                                          |                                                              |

|                    | main    |                                          |                                                              |

|                    | flow    |                                          |                                                              |

|                    | 3       | $node 1 \rightarrow node 28$             | $3 \to 2, 41 \to 33, 45 \to 37$                              |

| convolutional code |         |                                          |                                                              |

|                    | 4       | $node 1 \rightarrow node 37$             | $  4 \rightarrow 3, 41 \rightarrow 33, 43 \rightarrow 35,  $ |

|                    |         |                                          | $13 \to 21, 16 \to 24, 58 \to 50,$                           |

|                    |         |                                          | $60 \rightarrow 52,  63 \rightarrow 55$                      |

|                    |         |                                          |                                                              |

|                    | 5       | $\mathrm{node}\ 1 \to \mathrm{node}\ 46$ | $  4 \rightarrow 3, 41 \rightarrow 33, 43 \rightarrow 35,  $ |

|                    |         |                                          | $13 \to 21, 16 \to 24, 58 \to 50, 64 \to 56, 7 \to 6$        |

|                    |         |                                          | $64 \rightarrow 56, 7 \rightarrow 6$                         |

|                    |         |                                          |                                                              |

|                    | 3       | $node 1 \rightarrow node 4$              | $43 \to 35, 45 \to 37, 41 \to 33$ ,                          |

| LDPC code          |         |                                          | $17 \rightarrow 9, 42 \rightarrow 34$                        |

|                    |         |                                          |                                                              |

|                    | 4       | $\mathrm{node}\ 1 \to \mathrm{node}\ 5$  | $25 \to 17, 28 \to 20, 32 \to 24,$                           |

|                    |         |                                          | $41 \rightarrow 33$                                          |

|                    |         |                                          |                                                              |

|                    | 5       | $\mathrm{node}\ 1 \to \mathrm{node}\ 6$  | $25 \to 17, 28 \to 20, 32 \to 24,$                           |

|                    |         |                                          | $43 \rightarrow 35$                                          |

Table 3.1: Main flow and interfering flows in the large network for various scenarios.

In the dissertation, we simulate various network scenarios changing the sourcedestination pairs of the main flow and the interfering flows in the large network for the two different error-correction codes used. Table 3.1 shows the source and destination nodes of the main flow and interfering flows for the various simulation scenarios considered.

Instead of the Friis propagation model, the log-distance path-loss model [1] with three distance fields is used with the large network. (It is available as a standard model in ns-3.) The model divides the entire range of reception into near, middle and

far distance fields and calculates the path loss in dB as

$$L = \begin{cases} 0 & d < d_0 \\ L_0 + 10 \ n_0 \log_{10} \left(\frac{d}{d_0}\right) & d_0 \le d < d_1 \\ L_0 + 10 \ n_0 \log_{10} \left(\frac{d}{d_0}\right) + 10 \ n_1 \log_{10} \left(\frac{d}{d_1}\right) & d_1 \le d < d_2 \\ L_0 + 10 \ n_0 \log_{10} \left(\frac{d}{d_0}\right) + 10 \ n_1 \log_{10} \left(\frac{d}{d_1}\right) + 10 \ n_2 \log_{10} \left(\frac{d}{d_2}\right) & d_2 \le d \end{cases}$$

where, L is the total path loss in dB, d is the distance between transmitter and receiver in meters,  $d_0$ ,  $d_1$ ,  $d_2$  are the distance fields in meters,  $n_0$ ,  $n_1$ ,  $n_2$  are the path loss distance exponent for each field and  $L_0$  is the reference path loss. The default values of the parameters used in the simulation are:  $d_0 = 1$  m,  $d_1 = 200$  m,  $d_3 = 500$  m,  $n_0 = 1.9$ ,  $n_1 = n_2 = 3.8$ ,  $L_0 = 46.47$  dB.

#### 3.3 Approximations considered in the simulations

The dissertation includes consideration of several approximations to the probability of error in the detection of a code word at the receiver of a packet transmission, some of which are addressed in greater detail in subsequent chapters. Simulation diagnostics demonstrates that failure of packet acquisition at the receiver is a negligible factor in the network performance with 802.11b packet format and receiver considered here; thus, the presence of an acquisition preamble in the transmitted packet and the occurrence of acquisition failures at the receiver are neglected in the simulations. Similarly, the effects of symbol-timing error and carrier (phase and frequency) reference errors at the receiver are ignored. Furthermore, the (potentially) time-varying power of multiple-access interference during the reception of a packet is accounted for by approximating the mixed-distribution interference by a stationary Gaussian interferer with power equal to the average power of the mixed-distribution interference over the

interval of the packet [14]. The stationary Gaussian approximation to multiple-access interference is utilized in three approximations to the probability of code-word detection error if the link is employing convolutional coding with soft-decision Viterbi decoding.

The first of the decoder performance approximations, the tighter concave-Chernoff bound [14], provides an upper bound on the probability of code-word error under the stationary Gaussian approximation. The second of these uses the integral form of the concave bound [14] (also referred to as the concave-integral bound), which yields a tighter upper bound on the probability of code-word error than does the tighter concave-Chernoff bound. With either approximation, a Bernoulli trail is conducted for each packet transmission with a probability of packet error equal to the probability of code-word error determined by the corresponding bound. The third decoder performance approximation is an SINR-threshold based model in which received packets are assumed to be detected correctly if the received SINR is greater than a predetermined threshold  $\gamma$  but detected incorrectly otherwise.

A well-chosen cyclic redundancy check (CRC) outer code in the packet format and a corresponding outer CRC decoder in the receiver results in a negligible probability of undetected code-word error. While the presence of the CRC encoder and decoder is not incorporated into the simulations, it is assumed that each code-word error at a receiver results in a *known* decoder failure, allowing the MAC layer to react accordingly.

#### Chapter 4

### Link Modeling with Off-Line

#### **Decoder Simulation**

The highest fidelity model of a link transmission in a network simulation employs (on-line) bit-level simulation of the detection of each transmission on each link. The approach uses a simulation-generated sample outcome for each receiver symbol-rate statistic for each transmission based on the transmission format, the type of symbol-rate detection employed in the receiver, and the probabilistic model of the underlying communications environment (i.e., the channel) for each link. It also employs bit-accurate implementation of error-correction decoding.

On-line bit-accurate simulation reflects the effect of correlation among the receiver statistics for a given transmission. In those instances when it is significant, the simulation can also be designed to reflect correlation among the receiver statistics for distinct transmissions on the link and among the statistics for transmissions on different links. It permits great flexibility in examining the performance of the network in different topologies and propagation and interference environments and with different transmission formats (such as different packet sizes, error-correction codes, and mod-

ulation formats) and different receiver algorithms. The high fidelity and modeling flexibility of on-line bit-accurate simulation is achieved at a high computational cost, however.

The other end of the spectrum in terms of the computational cost at the time of network simulation occurs with the use of a look-up table indexed by the values of key link parameters to determine the probability of error in given a transmission. The probability of error is then employed as the parameter of a Bernoulli random variable, and a pseudo-random outcome for the random variable determines the success or failure of the transmission. This method is referred to as Off-line Tabular simulation of link transmissions. Each use of the look-up table determines the outcome for a single link transmission with minimal computation during a network simulation, but at the cost of extensive off-line link simulation to build the table. Furthermore, the fidelity it provides within the network simulation is constrained by the tradeoff between the number of parameters required for high-fidelity modeling of the possible link conditions and the computation required to build the table.

In this chapter, we consider off-line tabulation of transmission error probabilities and compare the accuracy of the network simulation results that they yield. (Accuracy is measured by comparison with the results obtained using bit-accurate on-line simulation.) Specifically, within the context of the network model defined in Chapter 3, we consider off-line tabulation of the probability of code-word error at the output of the decoder in a link. The channel of each link for a given transmission is determined by the fixed path loss of the link and the interference effects on different receiver statistics for the transmission.

The unslotted MAC protocol results in asynchronous interference with the desired packet transmission so that the SINR varies among the statistics for the transmission. We consider the effects of the time-varying SINR at the receiver within

the detection interval of the packet, which implicitly results in the network simulation accounting for the time-varying correlation of the interference among different links in the network. (The secondary effects of the phase offset and symbol-timing offset of the interferers relative to the desired signal are approximated by averaging their effects in the simulation of each link.)

The variation in the SINR for a single link transmission is simulated exactly in the reference bit-accurate on-line simulation results. Accounting for the variation exactly in the off-line tabular method would require a table of dimensionality equal to the number of code symbols in the code word contained in the packet, or at least several dimensions to reflect the collection of time instances within the packet interval in which the SINR changes and the SINR within each such interval. This would result in both a large multi-dimensional look-up table and large off-line computation time to populate the table, thus reducing some of the benefits of the approach. Instead, we consider off-line tabular simulation that uses the stationary Gaussian approximation to a mixed-distribution channel [14] in which the average received SINR during the packet interval is assumed to exist throughout the interval, thus reducing the dimensionality of the look-up table to one for a given combination of packet size, error-correction code, modulation format, and receiver algorithms.

# 4.1 Stationary approximation of a mixed-distribution channel

The stationary Gaussian approximation to a mixed-distribution channel is an independent, identically distributed Gaussian noise channel with a variance that is equal to the average interference variance over the entire packet interval for the time-

varying interference channel it is used to approximate. If a packet transmission is divided into J interference epochs such that each epoch has a constant received SINR and the noise variance for the  $i^{th}$  epoch is  $\frac{N_i}{2}$ , the average noise variance for the received packet is given by

$$\operatorname{Var}(\tilde{n}_i) = \sum_{i=1}^{J} \eta_i \frac{N_i}{2}$$

where  $\eta_i$  is the fraction of the transmission time occupied by the  $i^{th}$  epoch. The approximation can have varying effects on the probability of code-word error depending on the error-correction code. In this section, the accuracy of the stationary Gaussian channel approximation is investigated for the NASA-standard convolutional code and the WiMax-standard (2304, 1152) LDPC code by comparing their performance in a mixed-distribution Gaussian channel to their performance in the approximating stationary Gaussian channel. A single transmitter and receiver are considered.

In the example with the convolutional code, a data packet of size 7800 bits is encoded then interleaved using a pseudo-random interleaver [46] prior to modulation and transmission. In the example with the LDPC code, a data packet of size 1152 bits is encoded so that each packet consists of a single LDPC code-word. The code symbols are transmitted without interleaving. The channel consists of two Gaussian noise epochs, each spanning 50% of the transmission duration. The noise variance in the first epoch is  $\frac{N_0}{2}$ , and in the second epoch it is  $N_0$ . The mixed Gaussian channel is approximated using a stationary Gaussian channel with the noise variance

$$\frac{N}{2} = \frac{1}{2} \frac{N_0}{2} + \frac{1}{2} N_0 = \frac{3}{2} \frac{N_0}{2}.$$

The received word for each packet containing a convolutional code word is de-interleaved prior to decoding.

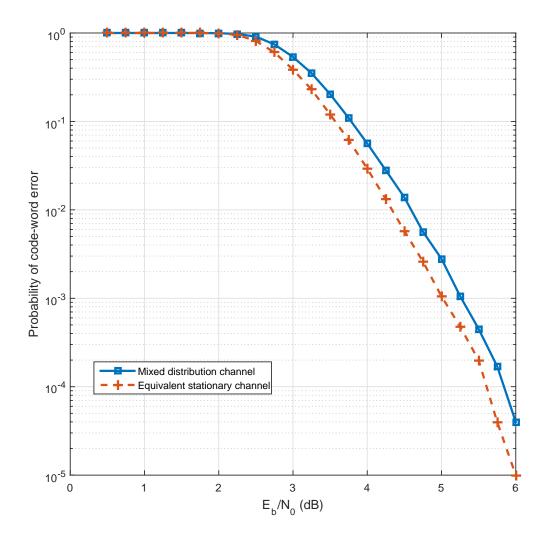

The performance of the system using the convolution code and Viterbi decoding is shown in Figure 4.1 for both the mixed-distribution channel and its stationary Gaussian approximation. Performance is shown as the probability of code-word error at the output of the decoder, and it is shown as a function of the signal-to-noise ratio  $\frac{E_b}{N_0}$  at the receiver (where  $E_b$  is the energy per bit of information at the receiver). The probability of code-word error in the mixed-distribution channel is higher than with its stationary Gaussian channel approximation for a given signal-to-noise ratio. The difference in performance with the two channel models does not exceed 0.25 dB for any probability of code-word error above  $4 \times 10^{-4}$ , however. Thus, the stationary approximation somewhat underestimates the actual probability of error of the system.

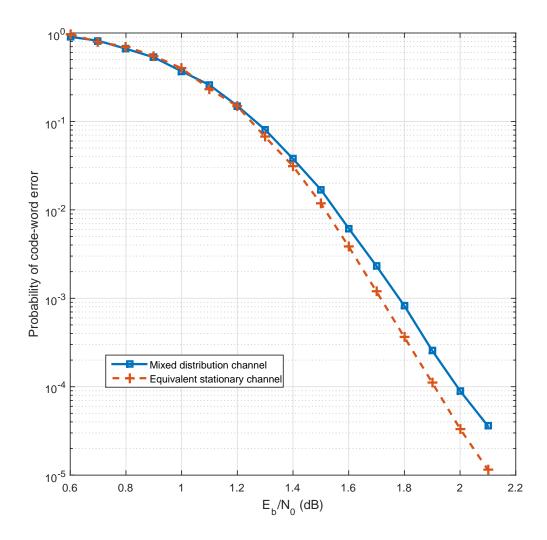

The performance of the system using the LDPC code is shown in Figure 4.2. For small values of the signal-to-noise ratio, the probability of code-word error is similar for the two channels. As  $\frac{E_b}{N_0}$  increases, the performance difference with the two channel models also increases. As with the convolutional code, the probability of code-word error with the LDPC code is always higher in the mixed-distribution channel than in its approximating stationary channel. The difference does not exceed 0.1 dB for any probability of code-word error above  $4 \times 10^{-4}$ , however.

# 4.2 Network performance using link modeling with off-line decoder simulation

As illustrated in the previous section, a mixed-distribution Gaussian channel can be approximated by a stationary Gaussian channel with a penalty of at most a few tenths of one dB in the accuracy of the link performance. The use of the stationary channel approximation for each packet transmission allows the use of a one-

dimensional look-up table for off-line tabular simulation of link performance instead of the high-dimensional table that would be required with an exact model of the time-varying interference in the networks we are considering. It results in a substantial acceleration of the network simulation in comparison with bit-accurate on-line link simulation. For the simulation of the small network, a single table is generated for each packet size with error probabilities for SINR ranging from 0 dB to 6 dB with increments of 0.1 dB.

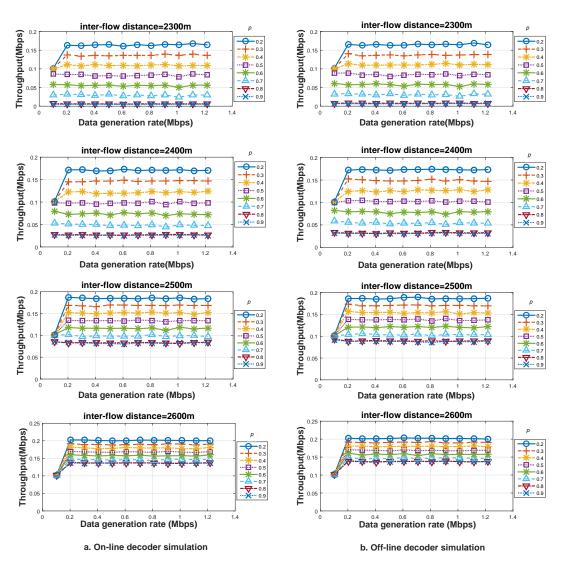

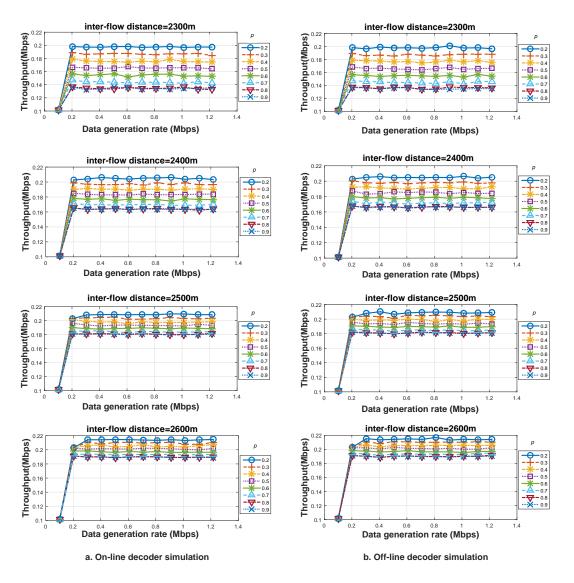

The performance of the small network that is determined from both bitaccurate on-line simulation and off-line tabular simulation of each transmission on a link is shown in Figure 4.3, Figure 4.4, and Figure 4.5. The performance is measured as the MAC-layer throughput of flow 1 (which is equal to the throughput of flow 2 due to the symmetry of the network and the equality of the data generation rates of the two sources). Figure 4.3 shows the throughput with the two link simulation methods for different values of the inter-flow distance if interfering node E is located at position (0, 3052). If the data generation rate is increased from 0.1 Mbps to 1.2 Mbps for a given error-correction code, inter-flow distance, and interference probability, p, the throughput of flow 1 increases initially and then saturates at a limiting value. The limiting value, denoted as the maximum throughput, is the maximum achievable throughput of the link under the specified conditions. As seen in Figure 4.3, for lower values of the inter-flow distance, the throughput is heavily dependent on the interference probability. In this circumstance, most of the packets received while the jammer node is active are decoded in error and only the packets that are received in the absence of a jammer signal are decoded correctly. For example, if the inter-flow distance is 2400 m, the maximum throughput with bit-accurate decoding decreases 85% from 0.17 Mbps to 0.025 Mbps as the interference probability is increased from 0.2 to 0.9. In contrast, if the inter-flow distance is 2600 m, the maximum throughput decrease only 33% from 0.2 Mbps to 0.135 Mbps with the same increase in the interference probability. It is also seen that for a given interference probability, the maximum throughput increases as the inter-flow distance is increased. Similar qualitative observations are obtained from the results in Figure 4.4 in which the interfering node is located farther away from the four network nodes and in Figure 4.5 in which transmission use the LDPC code instead of the convolutional code.

The results in Figures 4.3, 4.4, and 4.5 illustrate that the throughput obtained from the network simulations changes only negligibly if a single-dimensional look-up table for the probability of code-word error is used in place of on-line bit-accurate simulation. This occurs in spite of the modest difference in the simulation results with the mixed-distribution channel and its stationary approximation noted in the previous section. Though there is an improvement in the link performance if the mixed-distribution channel is replaced by a stationary Gaussian approximation channel, only a fraction of the received words in the simulations encounter time-varying interference in the scenarios considered here. And of those that do, the modest difference in the performance resulting from the two channel models is not sufficient to significantly alter the overall throughput.

Further observations of interest arise from comparison of the results in the three figures. A comparison of the results in Figures 4.3 and 4.4 illustrates that the impact of the interferer on the network performance is sensitive to the location of the interferer. The 10% increase in the distance of the interferer from the reference point of the network significantly increases the throughput for large values of the interference probabilities and dramatically decreases the sensitivity of performance to the interference probability. The results of Figures 4.3 and 4.5 illustrate that the greater link robustness provided by the LDPC code in comparison with the convolutional code similarly decreases the impact of the interferer on the throughput.

The time required to simulate one second of network activity with on-line bit-accurate simulation and with off-line tabular simulation is compared in Table 4.1. A two-core 2.40 GHz Intel Xeon E5-2665 processor is used to simulate both bit-accurate on-line simulation and off-line tabular simulation. The simulation times are shown for the circumstance in which node E is located at position (0, 3052), the interference probability is 0.5, and the data generation rate is 1 Mbps. It is seen that off-line tabular simulation requires only a few tenths of a seconds to simulate one second of network operation, whereas on-line bit-accurate decoding requires several seconds for the networks using either error-correction code.

| Link Model         | Inter-flow dis- | On-line decoder | Off-line decoder |

|--------------------|-----------------|-----------------|------------------|

|                    | tance (m)       | simulation (s)  | simulation (s)   |

| Convolutional code | 2300            | 4.11            | 0.16             |

| with Viterbi       | 2400            | 5.24            | 0.19             |

|                    | 2500            | 6.93            | 0.30             |

| decoding           | 2600            | 7.16            | 0.33             |

|                    | 2300            | 4.67            | 0.32             |

| LDPC code with     | 2400            | 4.68            | 0.25             |

| TDMP decoding      | 2500            | 4.52            | 0.31             |

|                    | 2600            | 5.84            | 0.41             |

Table 4.1: Time for bit-accurate simulation of one second of network activity.

The examples considered in this section indicate that the use of off-line link simulation to build a low-dimensional look-up table for use in network simulations has the potential to reduce network simulation time dramatically compared with bit-accurate simulation without compromising the fidelity of the simulation results significantly. What is not accounted for in this comparison is the initial (one-time) computational cost of building the look-up table. For either a single long simulation run or a large number of simulations that utilize the same look-up table, the initial computational cost is likely to be minimal compared with the savings that result. It thus represents a good choice in this circumstance as long as a high fidelity in the

network simulation results is achieved for the scenarios under investigation.

The limitations of the table look-up approach are encountered in circumstances in which a wide range of possible link parameters may be of interest in the network simulation, such as various choice of the packet size, error-correction code rate or type, modulation format, signal propagation model, interference model, and type of receiver architecture (including the decoding algorithm). In fact, variation in the transmission parameters and the receiver algorithms is inherent in the simulation of networks with links employing adaptive transmission protocols. A data source, the transport-layer protocol, and the network-layer protocol may also generate packets of many different sizes. In some instances, there may also be a desire to execute a large number of relatively short network simulations using different models and parameters as part of system design process or to assess the network performance under a wide range of topologies and channels.

The generation of an off-line look-up table to cover all of these circumstances may not be a cost-effective use of the available computational resources and may involve time-consuming analytical evaluation to exercise sound judgement about how to select the indexing parameters for the table. In subsequent chapters, we consider on-line approximations that can provide greater flexibility in accommodating some types of changes in the network design parameters and the network environment. We will make use of off-line tabular link simulations in Chapter 8, however.

Figure 4.1: Performance with Viterbi decoding and two Gaussian channel models.

Figure 4.2: Performance with TDMP decoding and two Gaussian channel models.

Figure 4.3: Throughput with bit-accurate and off-line table look-up Viterbi decoder simulation, node E located at (0,3052).

Figure 4.4: Throughput with bit-accurate and off-line table look-up Viterbi decoder simulation, node E located at (0, 3352).

Figure 4.5: Throughput with bit-accurate and off-line table look-up TDMP decoder simulation, node E located at (0,3052).

## Chapter 5

# Approximations in On-Line Viterbi Decoder Simulation

Several closed-form expressions for an upper bound on the probability of codeword error at the output of a Viterbi decoder have been developed for a system using convolutional coding and binary antipodal modulation (such as BPSK modulation). In this chapter, the tightest two such upper bounds from the literature are considered as approximations that are used in on-line determination of link transmission outcomes in a network simulation. The closed-form expression for each bound is evaluated with modest computation for each transmission and is applicable to an arbitrary convolutional code and packet length without the need for significant on-line storage. Approximation of link transmission outcomes based on an SINR threshold is also considered.

# 5.1 Closed-form approximations to the probability of code-word error

Numerous closed-form bounds have been developed for the probability of codeword error for convolutional coding with Viterbi decoding over an additive white Gaussian noise channel [14]. The two tightest bounds to date for a receiver using soft-decision Viterbi decoding are the tighter concave-Chernoff bound and the concave integral bound [14]. The tighter concave-Chernoff bound for code word of block length L is given by

$$P_e \le 1 - (1 - P_{t-ch})^L \tag{5.1}$$

where

$$P_{t-ch} = Q\left(\sqrt{\frac{2d_{free}E_c}{N_0}}\right) \left. exp\left(\frac{d_{free}E_c}{N_0}\right) T(W)\right|_{W=exp\left(-\frac{E_c}{N_0}\right)}.$$

Here,  $d_{free}$  is the minimum free Hamming distance of the code,  $E_c$  is the energy per channel symbol,  $N_0$  is the noise power spectral density, and T(W) is the path enumerator of the code [44].

Similarly the concave integral bound for the code can be expressed in terms of the first-event union bound  $P_u$  as

$$P_e \le 1 - (1 - P_u)^L \tag{5.2}$$

where

$$P_u = \frac{1}{\pi} \int_0^{\frac{\pi}{2}} T(W) \big|_{W = exp\left(-\frac{E_c}{N_0 sin^2 \theta}\right)} d\theta.$$

Application of the bounds in Equations (5.1) and (5.2) requires knowledge of the path enumerator and the minimum free Hamming distance of the code. For

| System | Link model                                 |

|--------|--------------------------------------------|

| 1      | bit-accurate soft-decision Viterbi decoder |

| 2      | tighter concave-Chernoff bound             |

| 3      | concave-integral bound                     |

| 4      | SINR threshold                             |

Table 5.1: Link models for simulation systems considered.

the NASA-standard convolutional code used in the examples, T(W) is given in [47] and the minimum free Hamming distance is  $d_{free} = 10$ . Either bound is applied in the network simulation by first approximating the mixed-distribution by the equivalent stationary Gaussian channel and then using the noise power spectral density of the equivalent stationary channel in the expression for the bound. For each link transmission outcome, the value of the bound is determined and used to generate an outcome of a correspondingly weighted Bernoulli random variable.

# 5.2 Threshold-based approximation to the probability of code-word error

The threshold-based approximation utilizes the SINR at the receiver based on the noise power spectral density of the equivalent Gaussian channel. For each link transmission outcome, the SINR is compared against a preset threshold. If the SINR exceeds the threshold, the transmission is modeled as successful in the simulation. Otherwise, it is modeled as a failure. The threshold is determined by running the network simulation for different threshold values and choosing the value that produces results closest to the online bit-accurate simulations.

#### 5.3 Comparison of simulation results

The performance of the small network is simulated using bit-accurate link simulation and each of the three approximations described in the previous sections. The models using the different link models are denoted as Systems 1, 2, 3, and 4. System 1 denotes the simulation using the bit-accurate soft-decision Viterbi decoding. System 2 and System 3 denote the simulations using the tighter concave-Chernoff bound and concave-integral bound link approximations, respectively. And System 4 denotes the simulation employing the SINR threshold link approximation. (The SINR threshold for System 4 is 3.2 dB in the examples.) Table 5.1 lists the four systems.

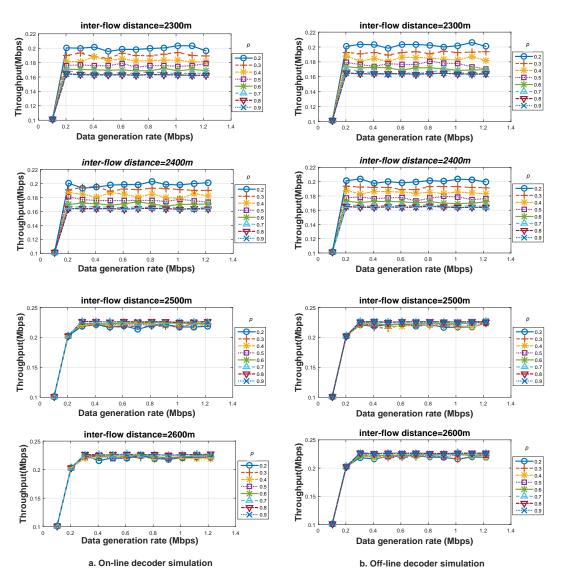

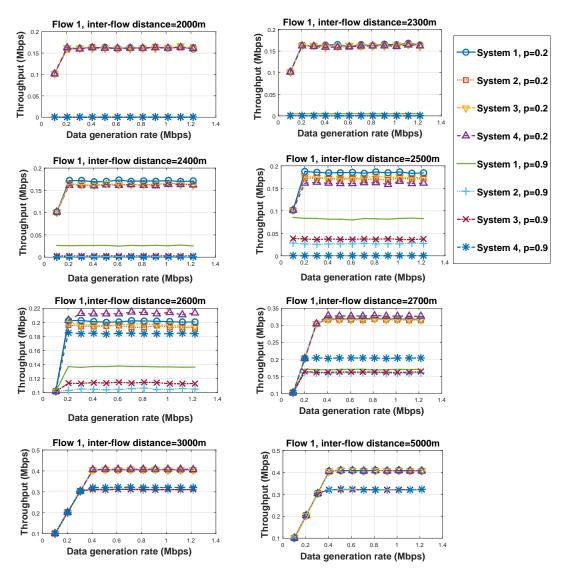

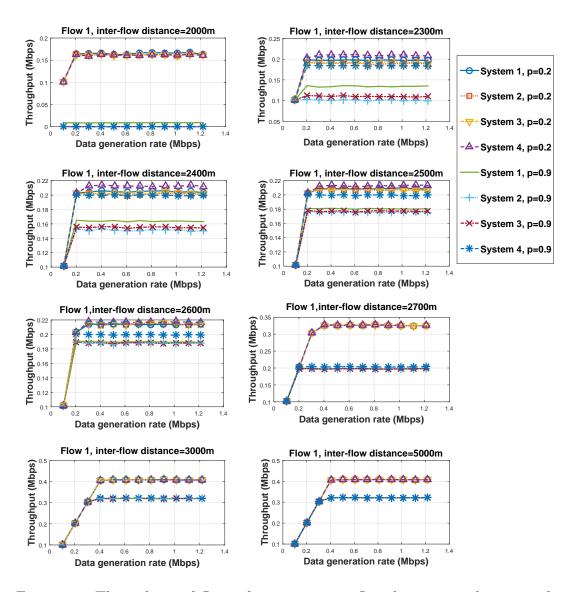

Figure 5.1 shows the throughput of flow 1 in the small network as a function of the data generation rate in simulation Systems 1 to 4 if node E is located at position (0,3052). The throughput is shown for different values of the inter-flow distance and two values of the interference probability, p = 0.2 and p = 0.9. For each system, the throughput increases with either an increasing inter-flow distance or a decreasing interference probability as is consistent with a reasonable link model.

The throughput is essentially the same in each system if the inter-flow distance is either small or large. If the inter-flow distance is 3000 m or greater, interfering signals from the jammer and the other network nodes are very weak at each receiver, resulting in a large SINR at the receiver even in the presence of interference. Channel-access contention between the two flows is moderate, and data transmissions are successful with a fairly high probability even in the presence of the jamming signal. Both closed-formed bounds yield an accurate approximation to the probability of code-word error with a high SINR and thus Systems 2 and 3 yield a similar throughput to System 1. A properly tuned SINR threshold also yields similar results with System 4.

If the inter-flow distance is only 2300 m, in contrast, the interference probability has a dramatic effect on the maximum throughput in each system. The maximum throughput is limited by the significant channel-access contention between the two flows if the interference probability is small, and it is limited by the strong jammer signal if the interference probability is large. Most successful data packet transmissions occur only if the jammer is inactive in which case the SINR at the receiver is large, in which circumstance the link models yield similar results. Thus the throughput for all four systems is similar if p = 0.2. If p = 0.9, the interference precludes significant throughput in all four systems.

If the inter-flow distance is intermediate between 2300 m and 3000 m, however, greater variability among the four simulation systems is observed. A data transmission occurring in the presence of jammer interference in this range of distances results in an SINR at the receiver which is large enough to result in successful transmission with a non-negligible probability but small enough that the two bounds substantially overestimate the probability of code-word error. Consequently, the maximum throughput determined by simulation Systems 2 and 3 is slightly lower than the throughput determined by System 1 if the interference probability is small, and it is much lower if the interference probability is large. If p = 0.9 and the inter-flow distance is 2400 m, the maximum throughput of System 1 is 0.025 Mbps, but the bounds used in Systems 2 and 3 result in negligible throughput. If instead the inter-flow distance is 2500 m, the maximum throughput of System 3 is approximately one-half that of System 1, and the maximum throughput of System 2 is even less. For larger values of the inter-flow distance, the difference in the maximum throughput among Systems 1, 2, and 3 decreases considerably, as seen for example if the inter-flow distance is 2700 m.

In each circumstance shown in Figure 5.1, simulation Systems 2 and 3 approx-

imate the performance of the bit-accurate simulation System 1 more closely than does System 4 (which uses the SINR threshold). For inter-flow distances up 2500 m, System 4 underestimates the network performance more severely than does either System 2 or System 3. For inter-flow distances of 2600 m and above, System 4 overestimates the network performance, most severely if the interference probability is large. For example, it overestimates the performance by 30% if the inter-flow distance is 2600 m and p = 0.9.

Similar observations arise from Figure 5.2 which shows the performance of the four simulation systems under the same circumstances as in Figure 5.1 except that node E is located farther away at position (0, 3352). If the inter-flow distance is either small or large, Systems 2, 3 and 4 yield results similar to those of System 1. But for intermediate values of the inter-flow distance, the maximum throughput of System 2 and System 3 matches the maximum throughput of System 1 more closely than does the maximum throughput of System 4. The mismatch of results from System 4 is pronounced for these values of the inter-flow distance if the interference probability is large.

Table 5.2 shows the time required to simulate 1s of network activity using a 2 core 2.70 GHz Intel Xeon E5-2680 processor for simulation of Systems 1-4 if the inter-flow distance is 2400m and the data generation rate is 1 Mbps. Simulation times are shown for interference probabilities of 0.2 and 0.9 and with the interfering node in either of the two locations considered above. It is observed that for a given link model, the simulation time increases as the throughput increases. Bit-accurate Viterbi decoding involves numerous calculations that increase the simulation time of System 1 by several-fold compared with Systems 2-4. The evaluation of an integral function in the concave-integral bound results in System 3 exhibiting the next greatest simulation time. System 2 and 4 have the smallest simulation times because they require only

| Node E's location | p   | System | Link layer model               | Time (s) |

|-------------------|-----|--------|--------------------------------|----------|

| (0. 2052)         | 0.2 | 1      | bit-accurate Viterbi decoding  | 5.17     |

|                   |     | 2      | tighter concave-Chernoff bound | 0.2      |

| (0,3052)          |     | 3      | concave-integral bound         | 0.64     |

|                   |     | 4      | SINR threshold                 | 0.23     |

|                   |     | 1      | bit-accurate Viterbi decoding  | 6.33     |

| (0.2252)          | 0.2 | 2      | tighter concave-Chernoff bound | 0.24     |

| (0,3352)          | 0.2 | 3      | concave-integral bound         | 0.64     |

|                   |     | 4      | SINR threshold                 | 0.29     |

|                   |     | 1      | bit-accurate Viterbi decoding  | 1.06     |

| (0,3052)          | 0.9 | 2      | tighter concave-Chernoff bound | 0.07     |

| (0, 3032)         |     | 3      | concave-integral bound         | 0.47     |

|                   |     | 4      | SINR threshold                 | 0.02     |

|                   |     | 1      | bit-accurate Viterbi decoding  | 6.56     |

| (0, 3352)         | 0.9 | 2      | tighter concave-Chernoff bound | 0.22     |

| (0, 3332)         | 0.9 | 3      | concave-integral bound         | 0.52     |

|                   |     | 4      | SINR threshold                 | 0.28     |

Table 5.2: Time required to simulate 1s of elapsed time, inter-flow distance=2400 m.