## **Clemson University TigerPrints**

All Dissertations Dissertations

12-2013

# EXPLORING MULTIPLE LEVELS OF PERFORMANCE MODELING FOR HETEROGENEOUS SYSTEMS

Venkittaraman Vivek Pallipuram Krishnamani Clemson University, kpallip@clemson.edu

Follow this and additional works at: https://tigerprints.clemson.edu/all\_dissertations

Part of the Computer Engineering Commons

#### Recommended Citation

Pallipuram Krishnamani, Venkittaraman Vivek, "EXPLORING MULTIPLE LEVELS OF PERFORMANCE MODELING FOR HETEROGENEOUS SYSTEMS" (2013). All Dissertations. 1232.

https://tigerprints.clemson.edu/all dissertations/1232

This Dissertation is brought to you for free and open access by the Dissertations at TigerPrints. It has been accepted for inclusion in All Dissertations by an authorized administrator of TigerPrints. For more information, please contact kokeefe@clemson.edu.

# EXPLORING MULTIPLE LEVELS OF PERFORMANCE MODELING FOR HETEROGENEOUS SYSTEMS

A Dissertation

Presented to

The Graduate School of

Clemson University

In Partial Fulfillment

of the Requirements for the Degree

Doctor of Philosophy

Computer Engineering

By Venkittaraman Vivek Pallipuram Krishnamani December 2013

Accepted by:

Dr. Melissa C. Smith, Committee Chair

Dr. Haiying (Helen) Shen

Dr. Walter Ligon III

Dr. Amy Apon

#### **ABSTRACT**

The current trend in High-Performance Computing (HPC) is to extract concurrency from clusters that include heterogeneous resources such as General Purpose Graphical Processing Units (GPGPUs) and Field Programmable Gate Array (FPGAs). Although these heterogeneous systems can provide substantial performance for massively parallel applications, much of the available computing resources are often under-utilized due to inefficient application mapping, load balancing, and tuning. While several performance prediction models exist to efficiently tune applications, they often require significant computing architecture knowledge for reliable prediction. In addition, they do not address multiple levels of design space abstraction and it is often difficult to choose a reliable prediction model for a given design.

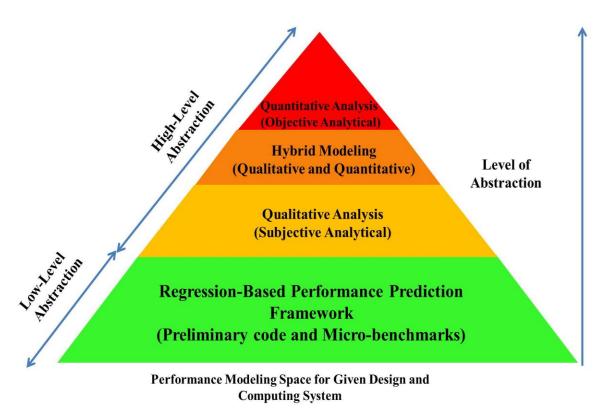

In this research, we develop a multi-level suite of performance prediction models for heterogeneous systems that primarily targets *Synchronous Iterative Algorithms* (SIAs). The modeling suite aims to produce accurate and straightforward application runtime prediction prior to the actual large-scale implementation. This suite addresses two levels of system abstraction: 1) *low-level* where partial knowledge of the application implementation is present along with the system specifications and 2) *high-level* where the implementation details are minimum and only high-level computing system specifications are given. The performance prediction modeling suite is developed using our proposed *Synchronous Iterative GPGPU Execution* (SIGE) *model* for GPGPU clusters, motivated by the *RC Amenability Test for Scalable Systems* (RATSS) *model* for FPGA clusters.

The low-level abstraction for GPGPU clusters consists of a regression-based performance prediction framework that statistically abstracts system architecture characteristics, enabling performance prediction without detailed architecture knowledge. In this framework, the overall execution time of an application is predicted using regression models developed for host-device computations and network-level communications performed in the algorithm. We have used a family of Spiking Neural Network (SNN) models and an Anisotropic Diffusion Filter (ADF) algorithm as SIA case studies for verification of the regression-based framework and achieved over 90% prediction accuracy compared to the actual implementations for several GPGPU cluster configurations tested. The results establish the adequacy of the low-level abstraction model for advanced, fine-grained performance prediction and design space exploration (DSE). The high-level abstraction consists of the following two primary modeling approaches: qualitative modeling that uses existing subjective-analytical models for computation and communication; and quantitative modeling that predicts computation and communication performance by measuring hardware events associated with objective-analytical models using micro-benchmarks. The performance prediction provided by the high-level abstraction approaches, albeit coarse-grained, delivers useful insight into application performance on the chosen heterogeneous system. A blend of the two high-level modeling approaches, labeled as hybrid modeling, is explored for insightful preliminary performance prediction.

The performance prediction models in the multi-level suite are verified and compared for their accuracy and ease-of-use, allowing developers to choose a model that best satisfies their design space abstraction. We also construct a roadmap that guides user from optimal Application-to-Accelerator (A2A) mapping to fine-grained performance prediction, thereby providing a hierarchical approach to optimal application porting on the target heterogeneous system. The end goal of this dissertation research is to offer the HPC community a thorough, non-architecture specific, performance prediction framework in the form of a hierarchical modeling suite that enables them to optimally utilize the heterogeneous resources.

### **DEDICATION**

I dedicate this dissertation to my mother, father, academic advisor, and all teachers that shaped my life. I also dedicate this dissertation to my younger brother, cousins, close family members, and friends; they are the source of my happiness. Special dedications to three symbols in my life: Saraswati (Knowledge), Ganesh (Success), and Hanuman (Strength).

#### **ACKNOWLEDGMENTS**

Five years of graduate school at Clemson were the golden years of my life. I was able to advance myself intellectually, physically, and spiritually. I owe heartfelt thanks to my advisor Dr. Melissa C. Smith for making my graduate life an enriching experience; I could not have asked for a better mentor. She encouraged me at each turn with her wisdom and insightful suggestions that made research, writing, and teaching enjoyable. I sincerely hope to follow in her footsteps. I would like to thank my committee members: Dr. Helen Shen, Dr. Walter Ligon, and Dr. Amy Apon for reviewing my dissertation work. They taught me several aspects of parallel computing and provided me with necessary resources that contributed significantly to this dissertation research. I would also like to thank Dr. Smith, Dr. Ligon and Dr. Apon for providing me with several opportunities to represent Clemson at top-tier conferences including Super-Computing (SC), which contributed significantly to my professional development.

Many thanks to the National Science Foundation (NSF) for their support with research grant (NSF Career Award #1149644), resources provided by XSEDE, Clemson University CITI, and NSF MRI Grant #1228312 that made this dissertation possible.

Special thanks to my professional family at Future Computing Technologies (FCTLab) group here at Clemson University for all the jovial and fun-filled discussions.

Finally, I would like to thank my parents for their unwavering support and teaching me valuable life lessons. My friends Abhishek, Koushik, Chinmay, Sudershan, Jyoti, Vijay, CM, Raj, and many others that I undoubtedly missed, I can't thank enough for having you in my life. Go Tigers!

### TABLE OF CONTENTS

|         |                                                                                                                                | Page           |

|---------|--------------------------------------------------------------------------------------------------------------------------------|----------------|

| TITLE P | AGE                                                                                                                            | i              |

| ABSTRA  | ACT                                                                                                                            | ii             |

| DEDICA  | TION                                                                                                                           | v              |

| ACKNO   | WLEDGMENTS                                                                                                                     | vi             |

| LIST OF | TABLES                                                                                                                         | X              |

| LIST OF | FIGURES                                                                                                                        | xvi            |

| СНАРТЕ  | ER                                                                                                                             |                |

| I.      | INTRODUCTION                                                                                                                   | 1              |

|         | Motivation  Dissertation Research  Method of Study  Dissertation Outline                                                       | 3<br>7         |

| II.     | LITERATURE REVIEW                                                                                                              | 9              |

|         | Performance Modeling: GPGPU-Based Systems Performance Modeling: FPGA-Based Systems Network-level Modeling SNNs and ADF Summary | 19<br>20<br>21 |

| III.    | BACKGROUND                                                                                                                     | 25             |

|         | GPGPU Architecture  Spiking Neural Networks (SNNs) and Large-Scale  SNN Simulations                                            |                |

|         | Non Linear Anisotropic Diffusion Filter (ADF)                                                                                  | 34             |

|         | Summary                                                                                                                        | 37             |

| Table of Contents (Continued) |                                                    | Page |

|-------------------------------|----------------------------------------------------|------|

| IV.                           | EXPERIMENTAL SET-UP, MAPPING,                      |      |

|                               | ORCHESTRATION, AND                                 |      |

|                               | PERFORMANCE ANALYSIS STUDY                         | 39   |

|                               | Experimental Set-up                                | 39   |

|                               | SNN Mapping and Orchestration                      | 41   |

|                               | ADF Mapping and Orchestration                      | 44   |

|                               | Performance Analysis Study: SNNs                   | 47   |

|                               | Performance Analysis Study: ADF                    | 56   |

|                               | Summary                                            | 62   |

| V.                            | SIGE MODEL AND MULTI-LEVEL PERFORMANCE             |      |

|                               | MODELING SUITE                                     | 64   |

|                               | Synchronous Iterative GPGPU Execution (SIGE) Model | 64   |

|                               | Multi-level Modeling Suite: Low-Level Abstraction  | 69   |

|                               | Multi-level Modeling Suite: High-Level Abstraction |      |

|                               | Summary                                            | 73   |

| VI.                           | THE LOW-LEVEL ABSTRACTION                          | 75   |

|                               | Multiple Regression Analysis                       | 75   |

|                               | Low-Level Abstraction: Regression-Based Framework  | 77   |

|                               | GPGPU DSE Using Low-Level Abstraction              | 91   |

|                               | Summary                                            | 100  |

| VII.                          | VERIFICATION OF THE                                |      |

|                               | LOW-LEVEL ABSTRACTION                              | 102  |

|                               | Verification Results: SNNs                         |      |

|                               | Verification Results: ADF                          | 113  |

|                               | Results and Analysis for DSE                       | 119  |

|                               | SWO Analysis of the Regression-Based Framework     | 125  |

|                               | Summary                                            | 131  |

| VIII.                         | THE HIGH-LEVEL ABSTRACTION                         | 133  |

|                               | Qualitative Modeling                               | 133  |

|                               | Quantitative Modeling                              |      |

|                               | Summary                                            | 151  |

| Table of 0 | Contents (Continued)                            | Page |

|------------|-------------------------------------------------|------|

| IX.        | VERIFICATION OF THE                             |      |

|            | HIGH-LEVEL ABSTRACTION                          | 154  |

|            | Verification Results: Qualitative Modeling      | 154  |

|            | Verification Results: Quantitative Modeling     | 157  |

|            | Hybrid Modeling                                 |      |

|            | Strengths, Weaknesses, and, Opportunities (SWO) |      |

|            | Analysis                                        | 176  |

|            | Summary                                         |      |

| X.         | CONCLUSIONS AND FUTURE RESEARCH                 | 180  |

|            | Dissertation Summary                            | 180  |

|            | Model Selection Criteria                        |      |

|            | Contributions and Outcomes.                     |      |

|            | Future Work                                     |      |

| BIBLIOC    | GRAPHY                                          | 197  |

| APPEND     | IX A                                            | 209  |

|            | Tying-it-all-Together:                          |      |

|            | Application-to-Accelerator Roadmap              | 209  |

| APPEND     | OIX B                                           | 213  |

|            | List of Frequently Used Acronyms                | 213  |

### LIST OF TABLES

| Table |                                                                                   | Page |

|-------|-----------------------------------------------------------------------------------|------|

| 3.1   | FLOPs/Byte Ratio for SNN Models                                                   | 33   |

| 4.1   | HH model: Statistical-Average Runtime Values (in milliseconds)                    | 48   |

| 4.2   | HH model: multi-GPGPU vs. MPI-only Implementation                                 | 50   |

| 4.3   | ML model: Statistical-Average Runtime Values (in milliseconds)                    | 51   |

| 4.4   | Wilson model: Statistical-Average Runtime Values (in milliseconds)                | 52   |

| 4.5   | Izhikevich model: Statistical-Average Runtime Values (in milliseconds)            | 53   |

| 4.6   | Izhikevich model: multi-GPGPU vs. MPI-only Implementation                         | 55   |

| 4.7   | ADF: Statistical-Average Kernel Runtimes (ms)                                     | 57   |

| 4.8   | PSNR Values (in dB) for Varying Test Image Sizes                                  | 58   |

| 4.9   | Final output PSNR Values (in dB) for Varying Images Sizes and Node Configurations | 58   |

| 4.10  | ADF: Statistical-Average Runtime Values (ms)                                      | 59   |

| 4.11  | ADF: Scaling Efficiency Values, η (%)                                             | 59   |

| 4.12  | Speed-up Values: Multi-GPGPU Implementation vs. MPI-only Implementation           | 62   |

| 6.1   | GPGPU Kernel Execution Time for SNN Models                                        | 80   |

| 6.2   | FLOPs, Bytes, and FLOPs/Byte ratio per Data Element                               | 81   |

| Table |                                                                                  | Page |

|-------|----------------------------------------------------------------------------------|------|

| 6.3   | $V_{max}$ (MB/sec) and $K_m$ (MB) for Scatter and Gather Operations              | 84   |

| 6.4   | Regression Models for <i>sendrecv</i> Operation in ADF Algorithm                 | 85   |

| 6.5   | $V_{max}$ (MB/sec) and $K_m$ (MB) for PCI-Ex Download and Read-back              | 87   |

| 6.6   | Regression Models for Download and Read-back Throughput (MB/sec)                 | 88   |

| 7.1   | HH model: Estimated and Experimental Time Values for Computation Component       | 104  |

| 7.2   | HH model: Estimated and Experimental Time Values for Communication Component     | 105  |

| 7.3   | HH model: Estimated Runtime, Experimental Runtime, And Error Rate                | 105  |

| 7.4   | ML model: Estimated and Experimental Time Values for Computation Component       | 107  |

| 7.5   | ML model: Estimated and Experimental Time Values for Communication Component     | 107  |

| 7.6   | ML model: Estimated Runtime, Experimental Runtime, And Error Rate                | 108  |

| 7.7   | Wilson model: Estimated and Experimental Time Values for Computation Component   | 109  |

| 7.8   | Wilson model: Estimated and Experimental Time Values for Communication Component | 109  |

| 7.9   | Wilson model: Estimated Runtime, Experimental Runtime, And Error Rate            | 110  |

| Table |                                                                                      | Page |

|-------|--------------------------------------------------------------------------------------|------|

| 7.10  | Izhikevich model: Estimated and Experimental Time Values for Computation Component   | 111  |

| 7.11  | Izhikevich model: Estimated and Experimental Time Values for Communication Component | 112  |

| 7.12  | Izhikevich model: Estimated Runtime, Experimental Runtime, and Error Rate            | 112  |

| 7.13  | Izhikevich model: Estimated and Experimental Time Values for Computation Component   | 114  |

| 7.14  | Izhikevich model: Estimated and Experimental Time Values for Communication Component | 115  |

| 7.15  | Izhikevich model: Estimated Runtime, Experimental Runtime, and Error Rate            | 115  |

| 7.16  | ADF: Estimated and Experimental Time Values for Computation Component                | 117  |

| 7.17a | ADF: Estimated and Experimental Time Values for Communication Component              | 117  |

| 7.17b | ADF: Prediction Error in Communication Component                                     | 118  |

| 7.18  | ADF: Estimated Runtime, Experimental Runtime, And Error Rate                         | 118  |

| 7.19  | Observed and Predicted Runtime Values (in ms) for Implementation 1                   | 120  |

| 7.20  | Observed and Predicted Runtime Values (in ms) for Implementation 2                   | 121  |

| 7.21  | Observed and Predicted Runtime Values (in ms) for Implementation 3                   | 122  |

| Table |                                                                                         | Page |

|-------|-----------------------------------------------------------------------------------------|------|

| 7.22  | Observed Kernel Runtime Values for Three Design Space Implementations                   | 123  |

| 7.23  | Predicted Kernel Runtime Values for Three Design Space Implementations                  | 124  |

| 7.24  | HH Model on Fermi: Observed and Predicted Values for Total Execution Time (ms)          | 126  |

| 7.25  | ML Model on Fermi: Observed and Predicted Values for Total Execution Time (ms)          | 126  |

| 7.26  | Wilson Model on Fermi: Observed and Predicted Values for Total Execution Time (ms)      | 127  |

| 7.27  | Izhikevich Model on Fermi: Observed and Predicted Values for Total Execution Time (ms)  | 127  |

| 7.28  | HH Model on Kepler: Observed and Predicted Values for Total Execution Time (ms)         | 127  |

| 7.29  | ML Model on Kepler: Observed and Predicted Values for Total Execution Time (ms)         | 128  |

| 7.30  | Wilson Model on Kepler: Observed and Predicted Values for Total Execution Time (ms)     | 128  |

| 7.31  | Izhikevich Model on Kepler: Observed and Predicted Values for Total Execution Time (ms) | 128  |

| 8.1   | Overhead (ms) and Message Gap (ms/KB)<br>for Scatter Time                               | 149  |

| 8.2   | Overhead (ms) and Message Gap (ms/KB) for Gather Time                                   | 149  |

| 8.3   | Overhead (ms) and Message Gap (ms/KB) for Sendrecv Time                                 | 149  |

| Table |                                                                             | Page |

|-------|-----------------------------------------------------------------------------|------|

| 8.4   | Overhead (ms) and Message Gap (ms/KB) for Download and Read-back Time       | 151  |

| 9.1   | HH Model: Observed and Estimated Kernel Runtime Values (ms)                 | 155  |

| 9.2   | ML Model: Observed and Estimated Kernel Runtime Values (ms)                 | 156  |

| 9.3   | Wilson Model: Observed and Estimated Kernel Runtime Values (ms)             | 156  |

| 9.4   | Izhikevich Model: Observed and Estimated Kernel Runtime Values (ms)         | 156  |

| 9.5   | ADF: Observed and Estimated Kernel Runtime Values (ms)                      | 156  |

| 9.6   | Kepler (K20) GPGPU Device<br>Parameter Values                               | 158  |

| 9.7   | SNN Models: Application Specific Parameters                                 | 158  |

| 9.8   | HH Model: Objective-Analytical Model Parameter Values; 4-Node Configuration | 159  |

| 9.9   | SNN Models: Observed and Estimated Kernel Runtime Values (ms)               | 160  |

| 9.10  | HH Model: Observed and Predicted Time Values for Computation Component      | 169  |

| 9.11  | HH Model: Observed and Predicted Time Values for Communication Component    | 170  |

| 9.12  | HH Model: Observed and Predicted Execution Time Values                      | 170  |

| lable | Pa                                                                               | age |

|-------|----------------------------------------------------------------------------------|-----|

| 9.13  | ML Model: Observed and Predicted Time Values for Computation Component           | 71  |

| 9.14  | ML Model: Observed and Predicted Time Values for Communication Component         | 71  |

| 9.15  | ML Model: Observed and Predicted Execution Time Values                           | 71  |

| 9.16  | Wilson Model: Observed and Predicted Time Values for Computation Component       | 72  |

| 9.17  | Wilson Model: Observed and Predicted Time Values for Communication Component     | 72  |

| 9.18  | Wilson Model: Observed and Predicted Execution Time Values                       | 72  |

| 9.19  | Izhikevich Model: Observed and Predicted Time Values for Computation Component   | 73  |

| 9.20  | Izhikevich Model: Observed and Predicted Time Values for Communication Component | 73  |

| 9.21  | Izhikevich Model: Observed and Predicted Execution Time Values                   | 74  |

| 9.22  | ADF: Observed and Predicted Time Values for Computation Component                | 74  |

| 9.23  | ADF: Observed and Predicted Time Values for Communication Component              | 75  |

| 9.24  | ADF: Observed and Predicted Execution Time Values 17                             | 75  |

### LIST OF FIGURES

| Figure |                                                           | Page |

|--------|-----------------------------------------------------------|------|

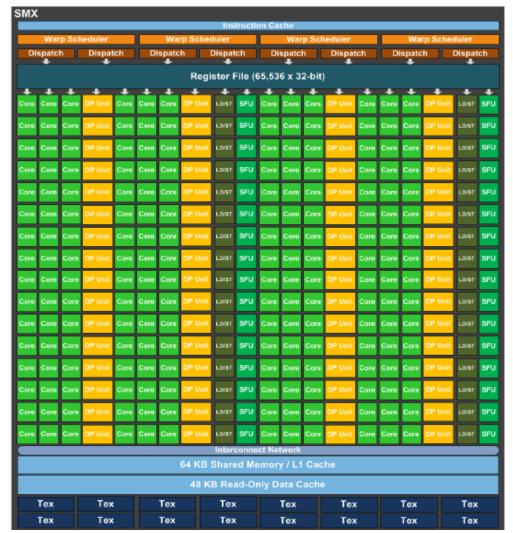

| 3.1    | An SMX in Kepler GK110 Architecture                       | 28   |

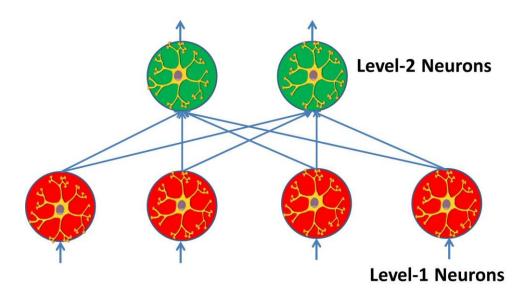

| 3.2    | Two-Level Character Recognition Network                   | 34   |

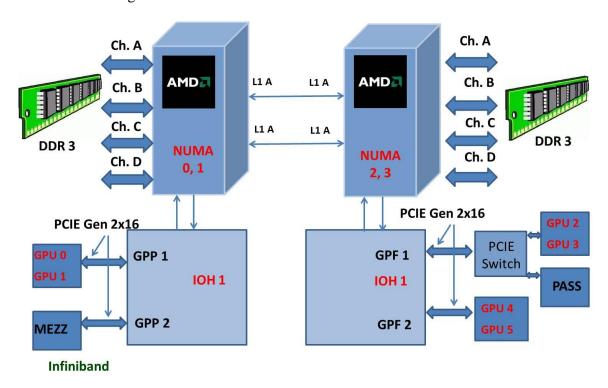

| 4.1    | An Example Layout of a server in the NCSA Forge Cluster   | 40   |

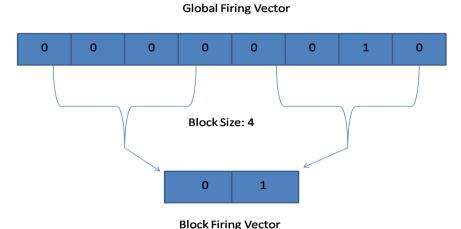

| 4.2    | The Concept of Block Firing Vector                        | 42   |

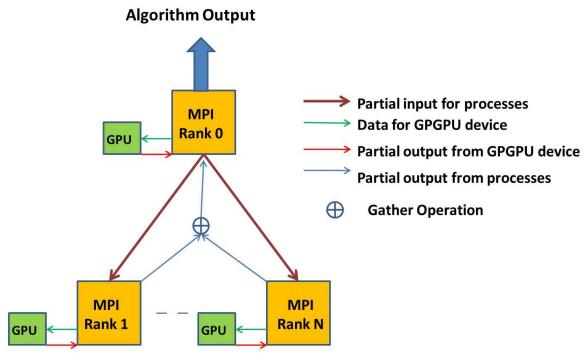

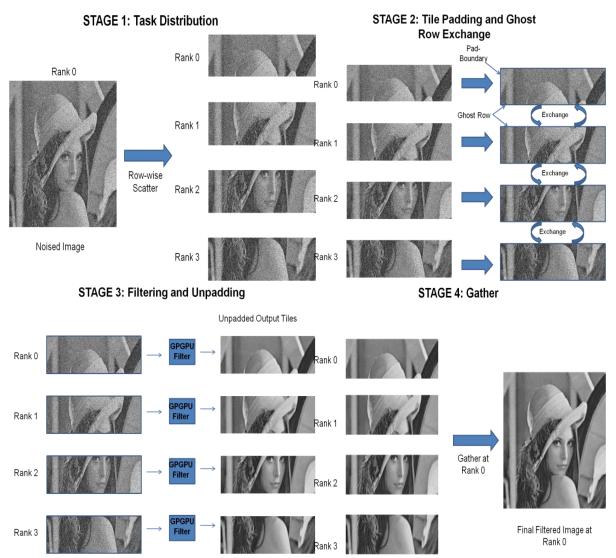

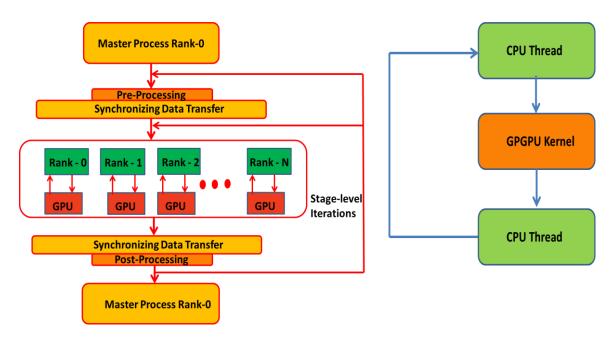

| 4.3    | Multi-GPGPU Orchestration using Master-Worker Paradigm    | 44   |

| 4.4    | Four Stages in Multi-GPGPU Orchestration                  | 47   |

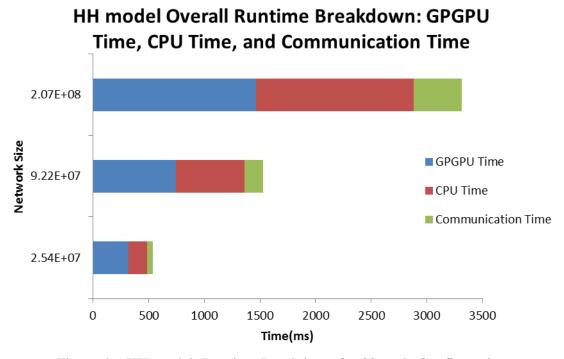

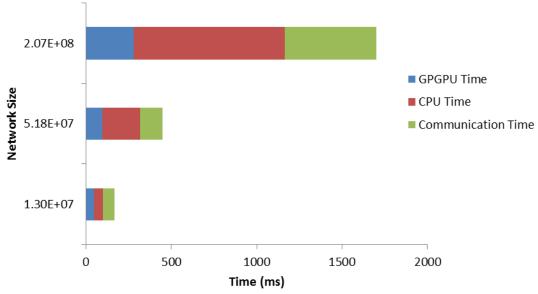

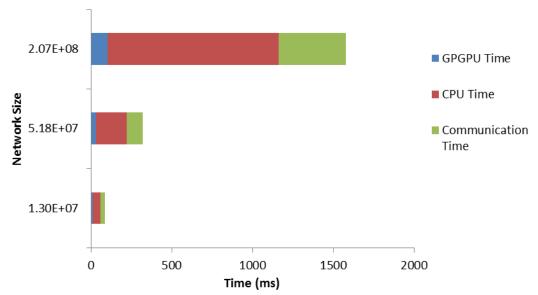

| 4.5    | HH model: Runtime Breakdown for 32-node Configuration     | 49   |

| 4.6    | ML model: Runtime Breakdown for 32-node Configuration     | 51   |

| 4.7    | Wilson model: Runtime Breakdown for 32-node Configuration | 53   |

| 4.8    | Izhikevich: Runtime Breakdown for 32-node Configuration   | 54   |

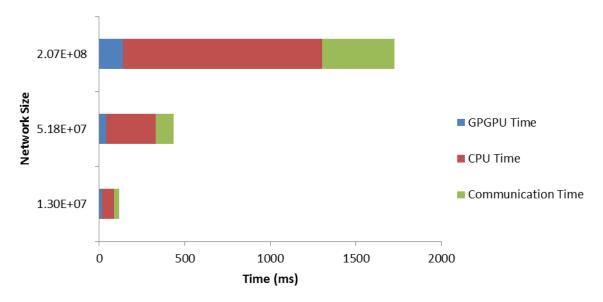

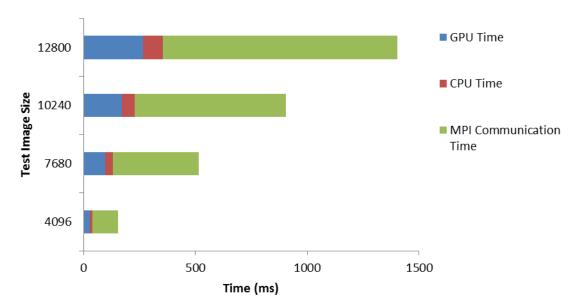

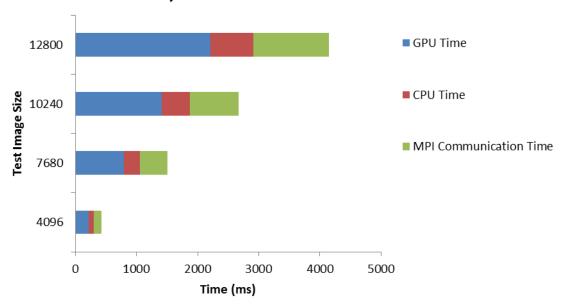

| 4.9    | Overall Runtime Breakdown for 32-node Configuration       | 60   |

| 4.10   | Overall Runtime Breakdown for 4-node Configuration        | 61   |

| 5.1a   | SIGE Model                                                | 66   |

| 5.1b   | 1:1 Host-Device Pair                                      | 66   |

| 5.2    | The Multi-Level Performance Modeling Suite                | 73   |

## List of Figures (Continued)

| Figure |                                                                                        | Page |

|--------|----------------------------------------------------------------------------------------|------|

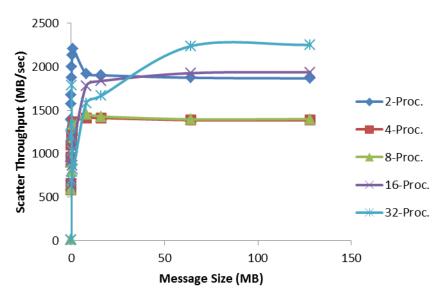

| 6.1    | Scatter Throughput vs. Message Size                                                    | 83   |

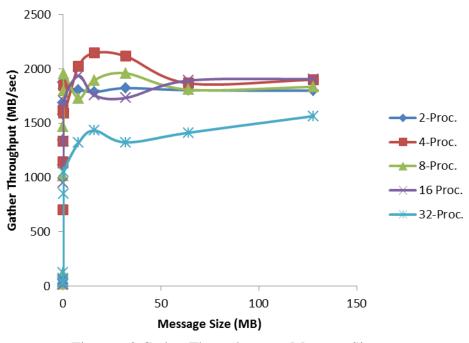

| 6.2    | Gather Throughput vs. Message Size                                                     | 83   |

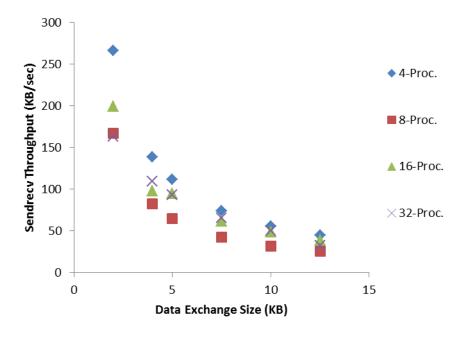

| 6.3    | Sendrecv Throughput vs. Data Exchange Size                                             | 84   |

| 6.4    | Download Throughput vs. Message Size                                                   | 86   |

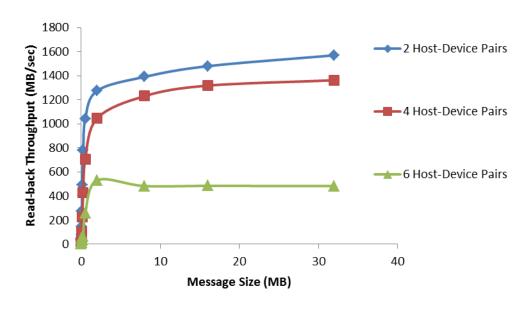

| 6.5    | Read-back Throughput vs. Message Size                                                  | 87   |

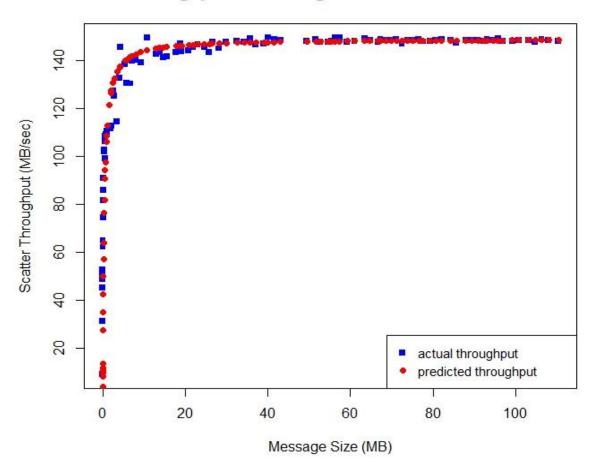

| 6.6    | Scatter Throughput Prediction for 8-node Configuration Using Michaelis-Menten Kinetics | 90   |

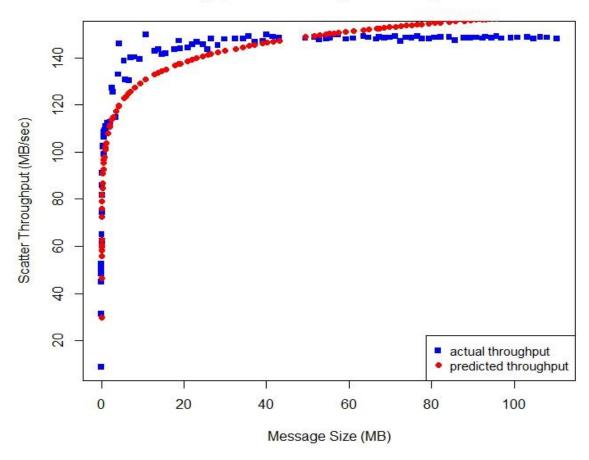

| 6.7    | Scatter Throughput Prediction for 8-node Configuration Using Log-Transformation        | 91   |

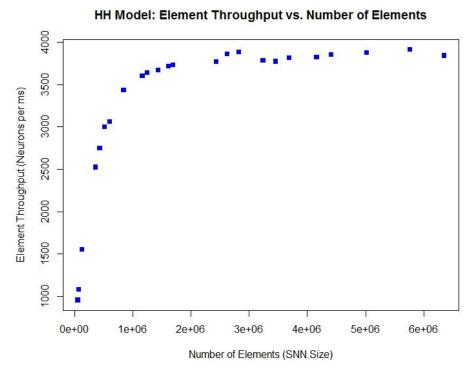

| 8.1    | HH Model: Element Throughput vs. Number of Elements                                    | 136  |

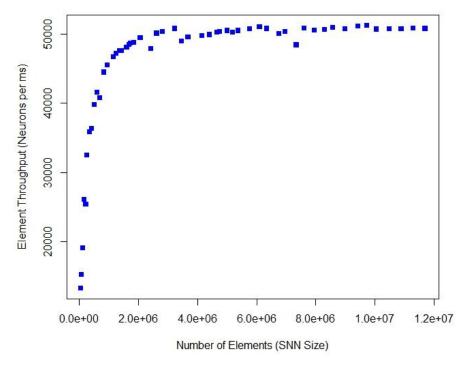

| 8.2    | ML Model: Element Throughput vs. Number of Elements                                    | 136  |

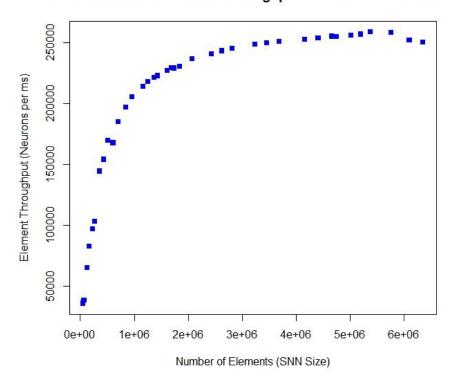

| 8.3    | Wilson Model: Element Throughput vs. Number of Elements                                | 137  |

| 8.4    | Izhikevich Model: Element Throughput vs. Number of Elements                            | 137  |

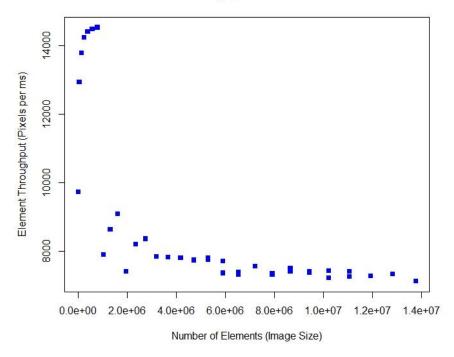

| 8.5    | ADF: Element Throughput vs. Number of Elements                                         | 140  |

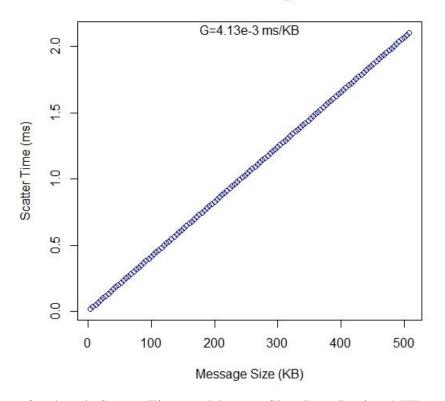

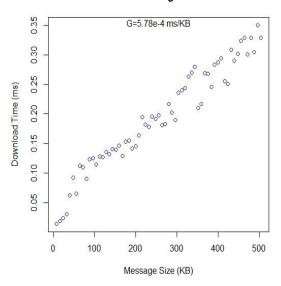

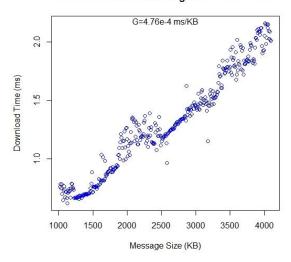

| 8.6    | 4-node Scatter Time vs. Message Size: Data Region 1 KB – 512 KB                        | 147  |

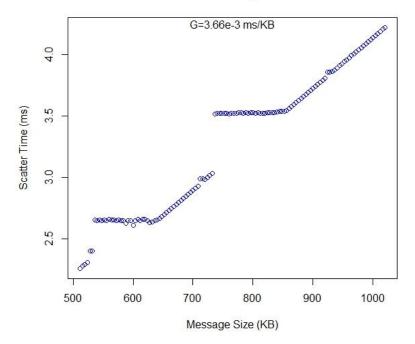

| 8.7    | 4-node Scatter Time vs. Message Size: Data Region 512 KB – 1024 KB                     | 147  |

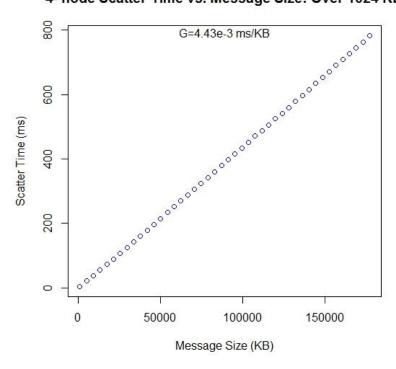

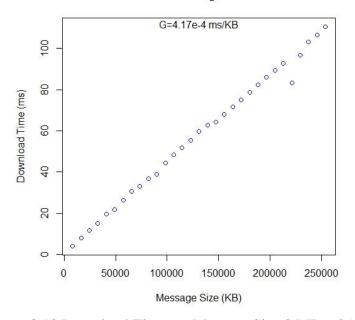

| 8.8    | 4-node Scatter Time vs. Message Size: Data Region Over 1024 KB                         | 148  |

## List of Figures (Continued)

| Figure |                                                                     | Page |

|--------|---------------------------------------------------------------------|------|

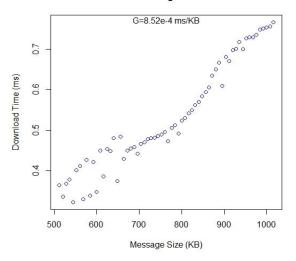

| 8.9    | Download Time vs. Message Size 1 B – 8 KB                           | 150  |

| 8.10   | Download Time vs. Message Size 8 KB – 512 KB                        | 150  |

| 8.11   | Download Time vs. Message Size 512 KB – 1024 KB                     | 150  |

| 8.12   | Download Time vs. Message Size 1 MB – 8 MB                          | 150  |

| 8.13   | Download Time vs. Message Size 8 MB – 256 MB                        | 151  |

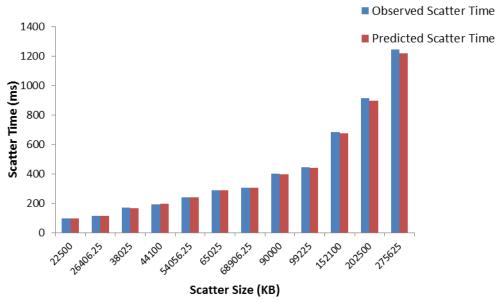

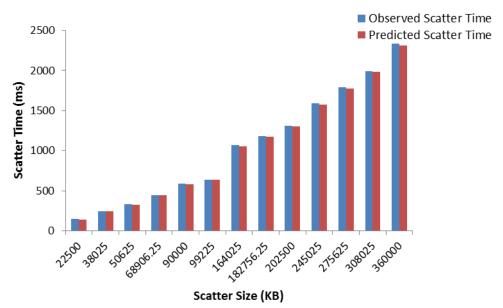

| 9.1    | Scatter Time Prediction for 4-Node Configuration                    | 161  |

| 9.2    | Scatter Time Prediction for 8-Node Configuration                    | 161  |

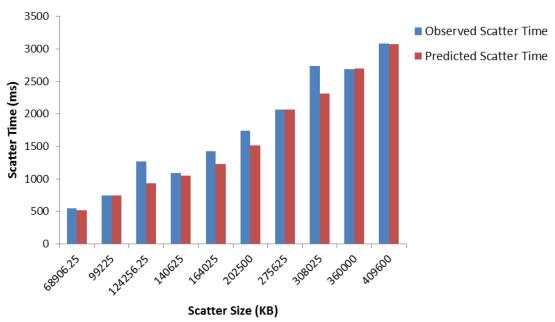

| 9.3    | Scatter Time Prediction for 16-Node Configuration                   | 162  |

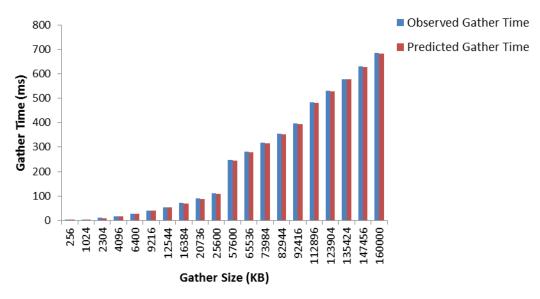

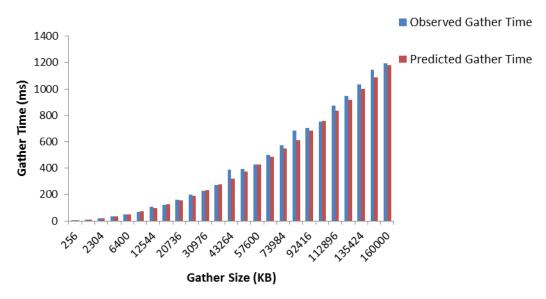

| 9.4    | Gather Time Prediction for 4-Node Configuration                     | 163  |

| 9.5    | Gather Time Prediction for 8-Node Configuration                     | 163  |

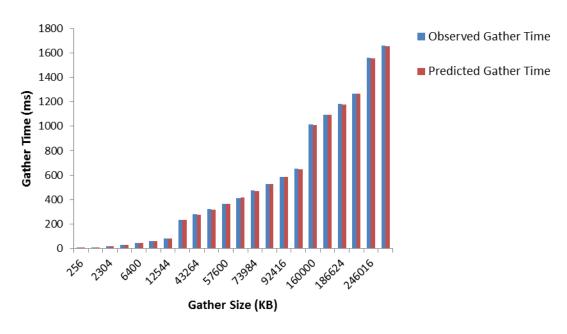

| 9.6    | Gather Time Prediction for 16-Node Configuration                    | 164  |

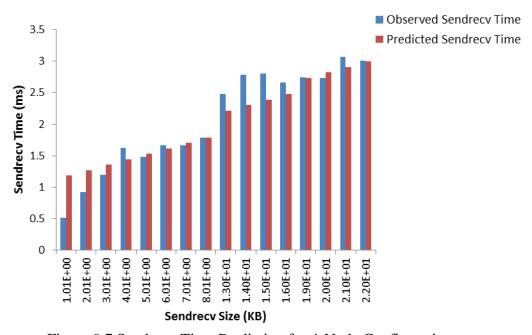

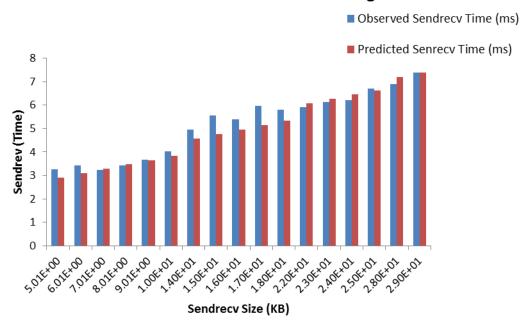

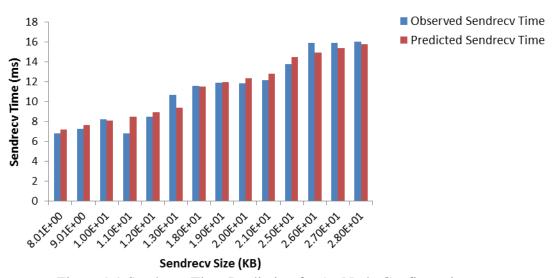

| 9.7    | Sendrecv Time Prediction for 4-Node Configuration                   | 164  |

| 9.8    | Sendrecv Time Prediction for 8-Node Configuration                   | 165  |

| 9.9    | Sendrecv Time Prediction for 16-Node Configuration                  | 165  |

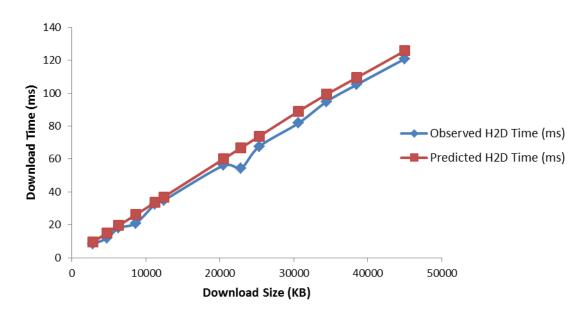

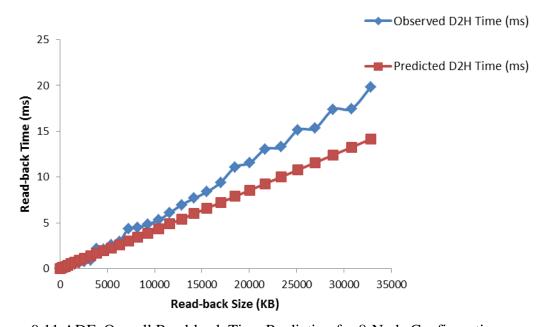

| 9.10   | HH model: Overall Download Time Prediction for 8-Node Configuration | 167  |

| 9.11   | ADF: Overall Read-back Time Prediction for 8-Node Configuration     | 167  |

| A.1    | Application-to-Accelerator Roadmap                                  | 210  |

### **CHAPTER 1**

#### INTRODUCTION

#### 1.1 MOTIVATION

There is widespread speculation that the principles of the Moore's law for increasing the single-core processor performance will no longer hold [1]. Because of power and memory clock limitations, the industrial trend has shifted to multi-core and many-core processors. Many vendors including IBM, AMD, and Intel are demonstrating many-core processor prototypes that can theoretically achieve performance over 1 Teraflops. Intel's Many Integrated Core (MIC) architecture is one such initiative that claims to surpass the Exascale performance barrier using a combination of several MICs [2]. However, amongst these advancements, hybrid accelerators such as the General Purpose Graphical Processing Units (GPGPUs) and Field Programmable Gate Arrays (FPGAs) continue to remain effective and popular in the High-Performance Computing (HPC) community. These architectures have been reported to provide several orders of magnitude higher performance compared to traditional sequential processors. Furthermore, the aforementioned architectures provide high floating-point operations per second per watt (FLOPS/watt) performance, an increasingly important parameter in green super-computing [3]. With the advent of GPGPUs and FPGAs in HPC, the conventional methods of seeking concurrency in a homogeneous environment no longer apply. The current trend is to extract concurrency from heterogeneous clusters that include GPGPU and FPGA clusters [4 and 5]. Current state-of-the-art heterogeneous systems are composed of several thousand compute nodes

where each node consists of multiple CPU-cores in conjunction with one or more hybrid accelerators.

Although these heterogeneous systems can provide substantial performance for massively parallel applications, much of their computing resources are often under-utilized due to inefficient application mapping, load-balancing, and tuning, ultimately leading to poor application speed-up and sub-optimal scaling efficiency. This inefficiency further leads to secondary effects such as long job queue delays and increased power consumption [6]. To achieve optimal utilization of heterogeneous resources, it is important to perform efficient loadbalancing between the CPU-cores and accelerators. Several performance prediction models exist that enable developers to efficiently tune applications via design space exploration [6, 7, and 8]. Typically, the performance prediction models are used to predict application runtime prior to the actual execution, allowing developers to further fine-tune their applications. Although existing performance prediction models are sufficiently accurate, they do not address multiple levels of design space abstraction and it is often difficult to choose a reliable prediction model for the given design goals. Additionally, the existing performance prediction models often require intricate knowledge of the underlying computing architecture for accurate prediction, making the modeling task difficult. With the above as motivation, we formally introduce the problem statement:

Design a straightforward and accurate performance prediction framework for heterogeneous clusters that addresses multiple levels of design space abstraction, allowing developers to choose an effective performance model that best fits their design needs and goals.

#### 1.2 DISSERTATION RESEARCH

We develop a multi-level suite of performance prediction models for heterogeneous systems that primarily targets *Synchronous Iterative Algorithms* (SIAs). The modeling suite aims to accurately predict application runtime with a user-friendly approach prior to actual large-scale implementation. The application runtime prediction is also employed to perform Design Space Exploration (DSE) that enables researchers to ultimately map an optimal implementation to the target heterogeneous cluster, thereby facilitating high application performance. The modeling suite addresses two levels of system abstraction: 1) *low-level* where partial knowledge of the implementation is present along with the target system specifications and 2) *high-level* where the implementation details are minimum and only high-level computing system specifications are given. The multi-level performance modeling suite is developed using our proposed *Synchronous Iterative GPGPU Execution* (SIGE) *model* for GPGPU clusters, motivated by the existing *RC Amenability Test for Scalable Systems* (RATSS) *model* [9] for FPGA clusters. These execution models describe the execution flow of SIAs on GPGPU and FPGA clusters, respectively.

The low-level abstraction of the modeling suite consists of a regression-based performance prediction framework that statistically abstracts the system architecture characteristics, thereby enabling performance and scalability prediction without detailed system architecture knowledge. The regression-based framework is broken into two primary components: the *computation component* that models the hybrid accelerator and host computations; and the *communication component* that models the network-level communications. The regression models for the computation component use algorithm characteristics such as the number of floating-point operations (FLOPs) performed and total number of bytes required as predictor variables. It is worth mentioning that FLOPS and FLOPs are two distinct parameters; FLOPS (floating-point

operations per second) is a measure of computer performance, whereas FLOPs is the number of floating-point operations performed in an algorithm. The regression models are trained using several small instrumented executions of an SIA set with a range of communication-to-computation requirements. The communication component of the regression-based framework is broken into two sub-components: 1) inter-processor communication over Infiniband [10] and 2) CPU-host/GPGPU-device (host-device) communication over Peripheral Interconnect Express (PCI-Ex) bus [11]. The regression models for the communication component are developed using micro-benchmarks and employ data transfer size and processor count as predictor variables.

The high-level abstraction of the modeling suite relies on minimum implementation details and high-level system specifications to model the computations and communications. The high-level abstraction consists of the following two primary modeling approaches: *Qualitative Modeling* and *Quantitative Modeling*. The qualitative modeling uses *subjective-analytical models* for the computation and communication components. The quantitative modeling approach predicts computation and communication performance by measuring hardware events associated with *objective-analytical models* using micro-benchmarks. The measurement of hardware events such as arithmetic operation throughput, device memory bandwidth, latency and bandwidth of the network (and interconnects), etc. in conjunction with algorithm characteristics enables the developer to estimate the application execution time. The qualitative and quantitative approaches are combined to yield an intermediate *hybrid* approach where a few performance components are estimated analytically, while the remaining components are estimated by employing micro-benchmarks. In this dissertation research, we show that amongst the high-level

abstraction approaches, the *hybrid* approach is a viable paradigm to perform high quality performance prediction on the chosen computing platform.

The two levels of the modeling suite are verified with large-scale SNN simulations and a non-linear anisotropic diffusion filter (ADF) algorithm for massive images as SIA case studies. We implemented both applications on the National Center for Supercomputing Applications (NCSA) Forge GPGPU cluster [12] and achieved significantly high performance versus the Message Passing Interface (MPI)-only implementations. The multi-GPGPU based large-scale SNN simulations scale up to 200 million neurons using a 32-node cluster configuration and achieves speed-up as high as 253x compared to an equivalent MPI-only implementation [13]. The multi-GPGPU implementation of the ADF is capable of processing images as large as 156 mega-pixels and achieves 11.5x speed-up using a 32-node GPGPU cluster configuration when compared to an equivalent MPI-only implementation [14].

The multi-level performance prediction models are compared for their accuracy and ease-of-use, thereby providing *model selection criteria* that allow developers to choose a prediction model that best satisfies their design space abstraction. The verification of the low-level abstraction reports average prediction accuracy over 90% compared to the actual implementations for several tested GPGPU cluster configurations, making it practicable for advanced, fine-grained performance prediction and design space exploration. Predictions with the two high-level abstraction approaches were found to be coarse-grained; however the *hybrid approach*, a suitable combination of these two modeling strategies, is an efficacious paradigm that provides significant insight into application performance, ergo highly suitable for preliminary performance prediction on the chosen or potential heterogeneous systems.

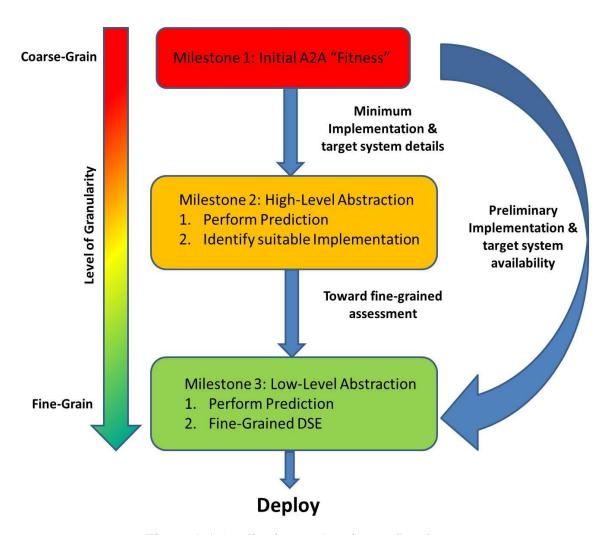

The dissertation research also provides a roadmap for users to perform optimal Application-to-Accelerator (A2A) mapping by means of appropriate architecture identification and performance prediction (preliminary and advanced). In this roadmap, the first milestone is A2A mapping that identifies an optimal accelerator for the application. The next milestone is preliminary performance prediction, facilitated by the high-level abstraction approach, to obtain an insight into application performance on the selected accelerator platform. This task also enables the identification of plausible optimization techniques for high application performance. The last milestone is constituted by the low-level abstraction that determines the best implementation for the target system via DSE. The A2A roadmap facilitates a hierarchical approach to optimal application porting on the heterogeneous system. It is worth mentioning that we follow a bottom-up approach to construct the performance modeling suite (low-level abstraction to high-level abstraction). However, the A2A roadmap seeks a top-down approach (high-level abstraction to low-level abstraction) for application performance prediction that is most useful for developers.

The end goal of this dissertation research is to offer the HPC community a thorough performance prediction framework in the form of a hierarchical modeling suite that enables them to optimally utilize the heterogeneous resources without requiring intricate knowledge of the low level architectures or restricting the specific architectures or accelerators used. The outcomes and contributions of this doctoral dissertation research are summarized below.

- 1) Development of synchronous iterative execution model (SIGE) for GPGPU clusters.

- 2) Development of a multi-level performance modeling suite for heterogeneous systems encompassing multiple levels of system abstraction.

- 3) Verification of the modeling suite using Synchronous Iterative Algorithms (SIAs) with a range of computation-to-communication requirements.

- 4) Application of the low-level abstraction for Design Space Exploration (DSE).

- 5) Performance analysis of SIAs on the chosen heterogeneous systems (to confirm the implementations achieve sufficient efficiency and scaling).

- 6) Tying-it-all-Together: A roadmap for users to perform optimal A2A mapping.

#### 1.3 METHOD OF STUDY

The set of highly biologically accurate SNN models and ADF algorithm, both SIAs, offer a range of communication and computation requirements, making them valuable case studies to verify the hierarchical performance model for this algorithm domain; these algorithms are used to perform large-scale SNN and image filtering simulations, respectively.

The planned experiments are conducted on available heterogeneous clusters by varying the problem size (neural network size, image size, etc.) and scaling the number of nodes in the cluster. The heterogeneous resources include NCSA Forge GPGPU cluster [12] and GPGPU-augmented Palmetto cluster [15]. In addition to verifying the performance prediction models for accurate runtime prediction, performance and scalability studies are also conducted on the NCSA Forge cluster to confirm the implementations achieve sufficient efficiency and scaling. Initial verification of the regression-based framework (low-level abstraction) for GPGPU clusters using the SNN models and ADF algorithm [16] is completed on the NCSA Forge GPGPU cluster. The GPGPU DSE using low-level abstraction and high-level abstraction studies are performed on the GPGPU-augmented Palmetto cluster.

#### 1.4 DISSERTATION OUTLINE

Chapter 2 provides a literature review of important work done in the field of heterogeneous performance modeling. Following the literature survey, Chapter 3 provides the background on the base GPGPU architectures and the SNN and ADF algorithms. Chapter 4 details the experimental set-up, SIA mapping methodology and multi-node orchestration. This chapter also provides the performance analysis study of SNN-ADF SIAs on the NCSA Forge cluster. The development of SIGE model and multi-level performance prediction suite is explained in Chapter 5. The low-level abstraction approach is elaborated in Chapter 6 followed by the verification results provided in Chapter 7. The high-level abstraction approach is elucidated in Chapter 8 and verified in Chapter 9. The dissertation is concluded in Chapter 10 with conclusions and directions for future research. Appendix A provides the A2A roadmap.

### **CHAPTER 2**

### LITERATURE REVIEW

Systematic architecture studies conducted on heterogeneous systems including GPGPU- and FPGA-based clusters are widely documented in the literature. Several research activities have focused on important performance modeling aspects that include runtime prediction, architecture parameter study, load-balancing, programming models for HPC, and network-level modeling; making them relevant to this dissertation research. The two SIA case studies discussed, namely Spiking Neural Networks (SNNs) and Anisotropic Diffusion Filtering (ADF) have been implemented on several leading architectures. In this chapter, we examine some of the prominent heterogeneous performance modeling efforts targeting GPGPU- and FPGA-based systems and several architecture studies using SNNs and ADF. The chapter is structured as follows. Section 2.1 examines performance modeling studies conducted on GPGPU-based systems, the primary heterogeneous platform investigated in this research. We also review load-balancing studies, performance tuning for applications, and programming models for GPGPU architectures. The discussion of performance models for FPGA-based systems, influential in this research, follows in Section 2.2. Section 2.3 reviews some of the important network-level modeling research. Section 2.4 highlights the architecture studies conducted using SNNs and ADF. The chapter is concluded with a summary in Section 2.5.

#### 2.1 PERFORMANCE MODELING: GPGPU-BASED SYSTEMS

In [17], the authors proposed an analytical model that estimates the execution time of GPGPU kernels for massively parallel applications by estimating the number of memory requests (memory-warp parallelism) and the number of computations (computation-warp parallelism). Based on these warp-level parallelisms, the analytical model estimates the costs of memory requests and computations, thereby estimating the overall execution time of the application. The authors achieved geometric mean error rate of 5.4% for micro-benchmarks and 13.3% for other GPGPU applications. Although sufficiently accurate, the model proposed in [17] requires meticulous evaluation of the warp-level parallelism for accurate runtime prediction. Additionally, their analytical model is tightly-coupled to the Nvidia Tesla architecture used in the GeForce-8 series, which is significantly different from subsequent GPGPU architectures.

In [7], the authors designed an analytical model to provide performance information to an auto-tuning compiler, thereby assisting the fine-tuning of GPGPU implementations. The analytical model interprets the GPGPU kernel as an abstract work-flow graph to estimate the execution time. The authors used micro-benchmarks to characterize GPGPU micro-architecture events such as incoherent memory accesses, shared memory bank conflicts, and control flow divergence. The authors validated their model using commonly used benchmarks and observed good agreement between the predicted and observed measurements. Similar to the research work presented in [17], the model requires significant GPGPU micro-architecture knowledge for accurate runtime prediction for complex applications.

In [18], the authors proposed a performance model for the Nvidia GeForce 200-series GPGPUs using micro-benchmarks. The proposed model targets three major components of the GPGPU execution time: instruction pipeline, shared memory accesses, and global memory

accesses. Using real-world matrix problems, the authors achieved prediction performance with 5-15% error rate. While the approach is expected to satisfactorily predict the aforementioned architecture components, quantitative modeling of other micro-architecture events such as thread block synchronization may not be trivial. A similar quantitative approach is presented in [19] where the authors developed a micro-benchmark suite that measures CUDA-visible architectural characteristics of the Nvidia GTX 280. The suite also measures several undisclosed architectural features that impact program performance and correctness. Although the proposed suite is very thorough with respect to the Nvidia GTX 280 architecture, continual revision of the microbenchmark suite is required to accommodate new architectural features as the GPGPU architecture evolves.

In [8], the authors developed a methodology to predict the execution time of GPGPU applications using runtime information from a single GPGPU implementation while varying the number and configuration of GPGPU devices. The authors define *per-element average* as the average time taken by the reference GPGPU device to execute a single computational entity in a given algorithm. The authors then use the per-element average information to extrapolate the algorithm execution time on *M* GPGPU devices, where *M* is the number of devices. The authors estimate the performance of the PCI-Ex bus and network-level transactions using microbenchmarked throughput values and peak theoretical network bandwidth, respectively. The authors used their prediction framework on six applications and achieved 11% average error rate. Although straightforward, this approach to predicting the GPGPU execution time lacks statistical rigor. Several algorithm parameters, including but not limited to floating-point operations (FLOPs) and computational bytes, affect the GPGPU execution time. Therefore, it is extremely important to characterize the relationship between GPGPU execution time and algorithm

parameters. A similar argument can be used for predicting the performance of the PCI-Ex bus and network-level transactions, where the data transaction behavior can be characterized using statistical analysis.

Regression-based methods have been previously investigated for GPGPU design space exploration. In [20], the authors proposed an automated tool developed using step-wise regression modeling to evaluate the GPGPU performance. The tool randomly samples parameter values from the GPGPU design space and simulates regression designs. The tool then selects the most significant architecture parameters and their interactions to construct an estimator. The authors reported less than 1.1% error rate for 11 GPGPU applications. Unlike the statistical approach described in [20], the low-level abstraction of our proposed multi-level performance modeling suite relies on easily accessible algorithm parameters such as FLOPs and computational bytes for runtime prediction, thereby statistically capturing the architectural behavior.

In [21], the authors developed an analytical tool called TEG (Timing Estimation tool for GPU) to estimate the GPGPU device performance. The inputs to TEG are constituted by kernel binary code and instruction trace obtained using *cuobjdump* [22] and Barra simulator [23], respectively. TEG analyzes the binary code and instruction trace to generate information regarding the type of instructions and operands used in the GPGPU kernel. The analytical tool then uses instruction latency information obtained from micro-benchmarks [19] to evaluate the total number of execution cycles. The authors used dense matrix multiplication as a case study and achieved less than 10% error rate in execution cycle prediction. The authors admit that TEG does not model other important parameters such as instruction pipeline stages and memory

behavior. Additionally, their modeling methodology only supports a specific Nvidia GPGPU device.

Similar to the work described in [21], Parallel Thread eXecution (PTX) kernels [24] have been analyzed to solidify the understanding of GPGPU architectures. As mentioned in [24], PTX defines a virtual machine and instruction set architecture (ISA) for parallel thread execution on GPGPU devices. In [25], the authors proposed a set of metrics for GPGPU workloads to analyze the behavior of GPGPU programs. The authors analyzed over 50 CUDA kernels from Nvidia CUDA SDK [26] and UIUC's Parboil benchmark suite [27]. The analysis was conducted to study control flow, data flow, and memory behavior of CUDA programs using a PTX functional emulator developed by the same authors. The authors also used the PTX functional emulator to quantify the effects of common CUDA optimizations such as branch divergence reduction, synchronization, etc. However, as mentioned in [21], direct PTX analysis is not always desirable since resource allocations occur at the compiling stage from PTX to binary code. In [21], the authors claim that since binary code is the native code that executes on the GPGPU device, this level of analysis is more suitable for performance modeling and related studies.

In [28], the authors proposed a performance prediction model for GPGPU-based systems that incorporates various components of the GPGPU architecture including warp scheduling, memory hierarchy, and pipelining. The model is developed with a combination of the BSP model of Valiant [29], the PRAM model of Fortune and Wyllie [30], and the extension to the PRAM model proposed by Gibbons et al. called the QRQW model [31]. The proposed model derives a relationship among the various components of the GPGPU architecture including the number of cores, effects of memory latency, memory access conflicts, computing cost, scheduling, and pipelining to analyze pseudo-code for a CUDA kernel and finally predicts the performance of an

application. Unlike the regression-based framework developed in this research, the model in [28] does not consider the performance of texture memory along with global and shared memories, thereby providing limited insight into the GPGPU design space exploration (DSE).

In [32], the *GPGPURoofline* model was proposed to empirically guide the optimizations on GPGPU devices with limited knowledge of the GPGPU architecture. The model explores the potential performance bottlenecks and evaluates the impact of specific optimization techniques on the overall kernel performance. The authors optimized representative applications, namely matrix transpose, Laplace transform, and face detection on NVIDIA and AMD GPGPU devices and achieved 3.74 to 14.8 times speed-up compared to the naïve implementations. The modeling approach, similar to the popular Roofline model by Williams et al. [33] for multi-core architectures, is primarily intended to evaluate the GPGPU performance optimizations. Unlike the low-level abstraction methods developed in this dissertation research, the performance prediction facilitated by the *GPURoofline* model is expected to be coarse-grained, hence of limited value for accurate runtime and scalability predictions.

In [34], the authors introduced a metric that accurately estimates the effect of control flow divergence on application performance. The metric targets computation-bound GPGPU kernels with control flow divergence and is used as a value function for thread re-grouping algorithms to eliminate the divergence. The authors claim that their metric enables performance modeling more efficiently versus the previous control flow divergence metrics such as divergent warps and divergent branches. The authors tested the proposed metric on CUDA SDK examples [26] and two real-world applications including 3D sound localization [35] and stereo-matching [36]. The authors reported application performance improvement up to 3.19x using thread re-grouping [37]

guided by the proposed metric. Similar to the study presented in [32], the research in [34] solely aims at guiding users to perform kernel optimizations that improve the overall performance.

In [38], the authors presented an approach to analytical modeling by constructing a domain specific language (DSL) called *Aspen*. *Aspen* includes a formal specification of an application's performance behavior and an abstract machine model. The DSL allows scientists to write structured models of their applications and architecture, thereby describing the application behavior and abstract machine model. The authors demonstrated the use of *Aspen* to express a performance model for 3D Fast Fourier Transform (FFT), in addition, showed how *Aspen* allows model composition by incorporating 3D FFT model for use in molecular dynamics. Although an efficient tool for quick performance estimation, the proposed DSL is based on analytical models that often provide coarse-grained predictions.

Recently, application specific performance models have been proposed to predict the application execution time on GPGPU devices. In [39], the authors proposed an integrated analytical and profile-based performance model to predict the CUDA kernel execution time for Sparse Matrix Vector Multiplication (SpMV). The modeling approach involves two phases. In the first phase, benchmark matrices are generated based on the GPGPU architectural features. These benchmark matrices are then executed on the target GPGPU device to obtain the execution time. In the second phase, the authors derive an analytical model that establishes a relationship between the maximum number of rows that the target GPGPU device can execute at a time, the number of non-zero elements per row in the target matrix, and execution times of the benchmark matrices. Although the authors report less than 10% error rate for 32 test cases, the prediction approach is tightly coupled to the SpMV application and must be revised as the GPGPU architecture changes.

The literature also reports multi-GPGPU studies that assist in the characterization and performance modeling of GPGPU clusters. In [40], the authors studied Non-Uniform Memory Access (NUMA) contention effects for shared system resources, quantified the contention effects, and presented guidelines to maximize the performance. The authors conducted their tests using the Scalable Heterogeneous Computing (SHOC) benchmark suite [41] and High-Performance Linpack (HPL) [42] and concluded that significant NUMA contention effects prevail in dual-IO hub multi-GPGPU systems. The authors claim that the severity of the contention penalty depends on several factors such as computational density, number of kernel executions per PCI-Ex transfer, and the fraction of the application ported to the GPGPU devices. The authors suggest that sharing GPGPU devices among a small number of MPI tasks or threads can increase GPGPU device utilization. The authors also suggest splitting MPI communication and GPGPU traffic into different threads to alleviate the contention penalties and promote maximum GPGPU bandwidth. The SHOC benchmark [41] proposed by the same authors is a valuable tool to measure throughput values for several device related operations such as arithmetic computations, host-device transfers, and hierarchical memory transactions (global, shared, texture, and constant). The throughput values of the above mentioned parameters in turn assist with the quantitative analysis of GPGPU performance.

In addition to performance modeling and GPGPU architecture studies, several research activities have focused on load-balancing issues for GPGPU systems. These studies are interesting since optimal performance is achieved only with efficient application tuning that further aides in consolidated performance analysis. In [43], the authors presented a task-based dynamic load-balancing solution in the form of a task queue scheme for single- and multi-GPGPU systems. The authors assert that their scheme provides a load-balancing solution at a

finer granularity compared to the Nvidia CUDA SDK [26]. The authors verified their scheme using micro-benchmarks and a molecular dynamics application and achieved significant performance improvement over other implementations. In [44], the authors proposed a technique that distributes iso-surfacing load (used for scientific visualization) to GPGPU devices in a cluster. The load-balanced implementation by the same authors is reported to exhibit strong scalability and yield performance as high as 250 million triangles per second on 24 GPGPUs. In [45], the authors studied different load-balancing schemes including: static task list, blocking dynamic task queue, lock-free dynamic task queue, and task stealing to improve the performance of GPGPU quicksort algorithm. The authors concluded that lock-free methods achieve better scaling and higher performance over blocking methods for the quicksort algorithm on GPGPUs.

The programming models for GPGPU devices, such as the Compute Unified Device Architecture (CUDA) [22] and Open Computing Language (OpenCL) [46], are integral for high application performance. Although programming models are not commonly incorporated into performance modeling, their study provides useful insight into application-on-accelerator behavior. In what follows, we mention important programming model comparison studies and recent programming paradigms developed for GPGPU devices. In [47], the authors accelerated an EMRI modeling application using Nvidia's C1060 as one of the accelerators and achieved similar performance for both CUDA and OpenCL. In [48], the authors used the Adiabatic Quantum Algorithms (AQUA), which are Monte Carlo simulations, to compare CUDA and OpenCL on Nvidia's GTX-260 (Compute capability 1.3). They compared the programming models for data transfer time, kernel execution time and end-to-end runtime. They concluded that CUDA implementations perform consistently better than the OpenCL implementations. In [49], the authors studied the performance portability of OpenCL and concluded that the

performance is not portable. They implemented TRSM and GEMM (both SGEMM and DGEMM) from the BLAS library [50] for their studies on both Nvidia Fermi [51] and AMD Radeon [52] architectures. Based on the above literature review for CUDA and OpenCL programming paradigms, we conclude that CUDA programming model is an optimal choice for high application performance on Nvidia GPGPU architectures.

Recently, directive-based programming models have emerged that provide different levels of abstraction and require different levels of programming effort to port and optimize applications on GPGPU devices. The examples of directive-based programming models include Hicuda [53], OpenMPC [54], PGI Accelerator [55], and OpenACC [56]. In [57], the authors evaluated these directive-based programming models by porting thirteen application kernels from various scientific fields on CUDA GPGPU devices. Their evaluation reported that the directive-based models can achieve reasonable performance versus the traditional hand-written GPGPU kernel codes. They also concluded that the high-level abstraction provided by the directive-based programming models will better assist in code portability for future architectures that combine GPUs and CPUs onto the same die [58].

In this sub-section, some of the prominent GPGPU performance modeling and architecture studies documented in the literature were discussed. Although the performance modeling schemes discussed are sufficiently accurate, they present a number of shortcomings. Both the analytical and quantitative models discussed require intricate GPGPU architecture knowledge for viable performance prediction. The accuracy of qualitative models is highly sensitive to the precise evaluation of model parameters. The quantitative models are prone to miss non-measurable architecture parameters, leading to imprecise predictions. Additionally, the quantitative approach is often tightly coupled to a specific GPGPU architecture, rendering them

invalid/incomplete for future generations. Therefore, it is not always a clear choice for developers to select a reliable prediction model for a given application. Unlike the performance modeling approaches discussed in this sub-section, our research aims to provide a user-friendly performance prediction framework that addresses multiple levels of design space abstraction, thereby allowing developers to choose the best model for the given design goals and the level of knowledge regarding the algorithm and architecture(s).

### 2.2 PERFORMANCE MODELING: FPGA-BASED SYSTEMS

Several research activities have focused on performance modeling of High-Performance Reconfigurable Computing (HPRC) systems. Although our research does not include FPGAbased systems, we mention relevant HPRC modeling studies that inspired the research work in this dissertation. In [59], the author proposed a model for shared resource load imbalance, dedicated resource imbalance, and communications in distributed applications utilizing shared resources. The author validated the model using four implementations: Boolean Satisfiability, Matrix-Vector Multiplication, Encryption, and CHAMPION demo algorithms. In [60], the authors proposed the RC Amenability Test (RAT) model that provides a framework to predict speed-up of applications on single-node FPGA-based systems. In [9], the authors extended the RAT model for multi-node FPGA systems. The RATSS (RC Amenability Test for Scalable Systems) model proposed in [9] predicts the application runtime by separately modeling the node computations using the RAT model and inter-node communications using LogGP model [61]. The authors validated the RATSS model using 2D Probability Density Function (PDF) estimation and image processing algorithms. The research presented in this dissertation is motivated by the multi-FPGA-based system modeling studies presented in [9].

### 2.3 NETWORK-LEVEL MODELING

In addition to performance analysis of node-level computations (device kernels, host computations, and host-device transactions), it is imperative to perform efficient analysis of the network-level transactions to accurately predict the application runtime on heterogeneous clusters. In this sub-section, we discuss some of the important network-level modeling techniques documented in the literature. In [62], the authors proposed the logP model that attempts to capture important bottlenecks in parallel computing with a limited number of parameters that include latency, overhead, bandwidth of communication, and the number of processors. The authors claim that the logP model can sufficiently describe the performance characteristics of several parallel machines. An extension to the logP model, parameterized logP (plogP), provided in [63], incorporates the message size for measurements. The plogP model defines five parameters, namely the number of processors, end-to-end latency, sender overhead, receiver overhead, and bandwidth for a given message size. Although logP and plogP models are state-of-the-art parallel machine models, the logGP model [61] is currently the most popular and widely used parallel machine model. The logGP model adds the gap term, G for long messages to the logP model. The experimental data collected by the authors in [61] shows that the logGP model can accurately predict the communication performance for both long and short messages. In [64], the authors derived a new logGP parameter assessment technique, netgauge that does not saturate the network for measurements. The authors also proposed a methodology to detect network protocol changes in the underlying communication system.

While the logP, PlogP, and logGP models constitute the foundation of any network-level performance analysis, several other derivatives of the logP model exist that explain the secondary network characteristics. The logGPG model [65] adds a network contention parameter

to the traditional logGP model. The logGPS model [66] captures the synchronization needed prior to sending long messages by high-level communication libraries. As mentioned in [66], the logGPS model adds the parameter S that defines the threshold for message length above which the synchronous messages are sent. In [67], the authors developed the logfP model that characterizes the small message performance over Infiniband. The logfP model adds the parameter f to the logP model, which indicates the number of messages where a small message gap has not been accounted.

In our research, we develop a variant of the above mentioned performance models for network communication, specifically in the high-level abstraction of the modeling suite. Although the above mentioned models adequately describe the network characteristics, communication transactions in heterogeneous systems often exhibit randomness in their behavior as explored ahead in Chapter 7. Therefore, regression analysis of communications (both PCI-Ex and network-level) enables us to capture the data transaction behavior statistically, thereby abstracting high-level architecture details. Regression-based techniques for modeling the communications using Michaelis-Menten kinetics [68] are expounded in Chapter 7.

### 2.4 SNNs and ADF

### 2.4.1 SNNs

Spiking Neural Networks (SNNs) are very popular in the neuroscience community for modeling the mammalian brain to understand its functional and operational principles. The ability of spiking neurons to reproduce most of the neuronal properties with high accuracy makes them amenable for brain related studies [69]. Biologically inspired SNNs are popular in other fields such as pattern recognition [70], artificial intelligence [71], and smart control of power

grids [72]. In this section, we discuss some of the prominent architecture studies conducted using large-scale SNN simulations.

In [73], the authors studied the mammalian brain neo-cortex and simulated a rat-size cortex in 42% of real-time and a cat-size cortex in 23% of real-time on a 442-node Dell Xeon cluster. In [74], the authors successfully utilized the Izhikevich SNN model to simulate a cat-size cortical model with 10<sup>9</sup> neurons and 10<sup>13</sup> synapses using the BlueGene/P machine [75] with 147,456 processors and 144 TB of main memory. The authors claim their simulation scale is roughly 1-2 orders of magnitude smaller than the human cortex and 2-3 orders of magnitude slower than real-time.

Heterogeneous architectures such as GPGPUs are now being investigated for biologically realistic simulations. In [76], the authors implemented Izhikevich's random network on Nvidia's GTX-280 with 1 GB memory and achieved a speed-up for a 100K neuron network simulation. They also discussed mapping strategies on the GPGPU to efficiently utilize the memory bandwidth and parallelism. In [77], the authors investigated GPGPU cluster-based implementations of the Hodgkin-Huxley (HH) and Izhikevich SNN models using a two-level character recognition network. They reported GPGPU speed-ups of 24.6x and 177x for the Izhikevich and HH models, respectively. Their 16 GPGPU-based MPI implementation on a 32-node Tesla S1070 NCSA cluster was successful in scaling the network up to 150 million neurons and achieved 17910 millisecond runtime for the HH model.

### 2.4.2 ADF

The non-linear anisotropic diffusion filter (ADF) investigated in this research belongs to the class of stencil-based algorithms for image processing. Several research activities have been motivated by the cluster and grid computing paradigms for stencil-based image processing

applications. In [78], the authors implemented an anisotropic diffusion filter for parallel and distributed systems. Their implementation was parallelized with point-to-point and collective communications using LAM-MPI [79] on a heterogeneous cluster of workstations. The anisotropic filtering technique adopted by the authors used 30 iterations and a neighborhood factor of 15. Their point-to-point and collective communication implementations achieved performance gains of 81.9% and 93.8%, respectively, when compared to the execution time on a single computing node. The authors observed that their collective communication implementation was 21% more efficient when compared to the point-to-point communication implementation.

The CUDA and hybrid CUDA/MPI paradigms have recently gained interest for stencil-based image processing applications. In [80], the authors proposed a new method to remove Rician noise from magnetic resonance images using GPGPU devices. The authors designed an anisotropic diffusion filter that characterizes the direction of diffusion and pixel properties using Eigen-values and Eigen-vectors. To preserve the edges, the authors coupled the proposed anisotropic diffusion filter with a shock filter based on fuzzy sets. The authors compared their filter implementation with the traditional anisotropic diffusion filter and wavelet based methods and reported an average gain of 0.01 dB in PSNR values. Additionally, their GPGPU implementation (kernel computation only) performed approximately 9 times faster than the CPU-only implementation.

In [81], the authors implemented the gradient domain processing technique for massive images using MPI, threading, and a GPGPU-based component. The authors successfully stitched giga-pixel size panoramas and demonstrated performance and scalability on two GPGPU

clusters. The authors achieved over 60% scaling efficiency for both clusters even when scaled beyond 60 nodes.

### 2.5 SUMMARY

In this chapter, we discussed some of the recent performance modeling studies targeting GPGPU- and FPGA-based heterogeneous systems. While the GPGPU performance prediction models discussed are accurate, they require significant knowledge of the underlying system architecture. In addition, they do not address the multiple levels of design space abstraction, making the model selection and implementation task difficult. Unlike the modeling efforts discussed in this chapter, our research addresses two levels of design space abstraction in the form of a multi-level performance modeling suite: *low-level* where some implementation details are present along with the system specifications; and *high-level* where the implementation details are minimum and only high-level system specifications are available. The proposed multi-level suite aims to provide straightforward and accurate runtime prediction, allowing developers to choose a performance prediction model that best satisfies their design space.

In addition to performance models for heterogeneous systems, we also discussed several architecture studies conducted using SNNs and ADF. Since our current research focuses on GPGPU-based systems, the next chapter provides additional details on the base GPGPU architectures and SNN-ADF SIA case studies.

### **CHAPTER 3**

### **BACKGROUND**

In this chapter, we provide background on Nvidia's Fermi and Kepler GPGPU architectures and the Compute Unified Device Architecture (CUDA) framework, and discuss the algorithmic details of the SNN-ADF SIAs studied in this research. The chapter is structured as follows. Section 3.1 describes the Fermi and Kepler GPGPU architectures and the CUDA framework for general purpose graphics computing. Section 3.2 provides background on the Spiking Neural Network (SNN) models along with the large-scale SNN simulation performed in the form of a two-level character recognition network. The non-linear anisotropic diffusion filtering (ADF) is described in Section 3.3. The chapter is concluded in Section 3.4 with a summary.

### 3.1 GPGPU ARCHITECTURE

The GPU architecture, initially intended as a fixed many-core processor dedicated to transforming 3D scenes to a 2D image composed of pixels, has undergone several innovations to meet the computationally demanding needs of the supercomputing research community. The traditional GPU pipeline came with several disadvantages for HPC including limited data reuse in the pipeline, excessive variations in hardware usage, and lack of integer instructions coupled with weak floating-point precision. In November 2006 [82], NVIDIA introduced the GeForce 8800 GTX with a novel unified pipeline and shader architecture. In addition to overcoming the limitations of the traditional GPU pipeline, the GeForce 8800 GTX architecture added the concept of a *streaming processor* (SMP) architecture that is highly pertinent to current GPGPU

programming. SMPs can work together in close proximity with extremely high parallel processing power. The outputs produced can be stored in fast cache and used by other SMPs. SMPs have instruction decoder units and execution logic performing similar operations on the data. This architecture allows SIMD instructions to be efficiently mapped across groups of SMPs. The streaming processors are accompanied by units for texture fetch (TF), texture addressing (TA), and caches. The structure is maintained and scaled up to 128 SMPs in the GeForce 8800 GTX. The SMPs operate at 2.35 GHz in the GeForce 8800 GTX, which is separate from core clock operating at 575 MHz. Several GPGPUs used thus far for HPC applications have architectures that are concurrent with the GeForce 8800 GTX. However, introduction of the Fermi architecture by Nvidia in September 2009 [51] has radically changed the contours of the GPGPU architecture, as discussed in this section.

### 3.1.1 Nvidia Fermi GPGPU Architecture

The Compute Unified Device Architecture (CUDA) programming framework [22] views the GPGPU architecture as an array of streaming multi-processors (SMPs), each containing a set of scalar processors (referred to as CUDA cores), a double-precision (DP) unit, shared memory for thread cooperation, and texture addressing and texture fetch units. The GPGPU functionality in CUDA is expressed by writing GPGPU user-defined functions, referred to as *kernels*, that are executed by all threads created in an application. While a single thread is executed on a CUDA core, a group of threads called a thread block is executed on the SMPs. The thread blocks are further divided into warps (a group of 32 concurrent threads) and half-warps (a group of 16 concurrent threads). Threads in a thread block can synchronize with each other using shared memory.

The 20-series architecture, codenamed Fermi [51], has brought numerous innovations versus previous architectures. The 512 CUDA cores are organized as 16 SMPs with 32 cores each gathered around an L2 cache. A Gigathread scheduler dispatches thread blocks to the SMP thread schedulers. The GPGPU has the capability of supporting 6 GB of GDDR 5 DRAM memory. SMPs in Fermi have an instruction cache, dual warp schedulers and dispatch units, two sets of 16 CUDA cores, 4 special function units for transcendental functions, 16 load/store units, a hefty register file, and most importantly, a configurable 64 KB of shared memory/L1 cache. The SMPs share a second level L2 cache. More information about the architecture can be found in [51]. The Fermi-based Tesla M2070 used for this research can theoretically offer 1.03 Teraflops of single-precision floating-point performance and 515 Gigaflops of double-precision floating-point performance. This GPGPU architecture is used for the verification and Strengths, Weaknesses, and Opportunities (SWO) analysis of the regression-based framework (low-level abstraction).

### 3.1.2 Kepler GK110 (K20) Architecture