## Clemson University TigerPrints

## All Dissertations

Dissertations

12-2014

## High Frequency Devices and Circuit Modules for Biochemical Microsystems

Jiwei Sun Clemson University, jiweis@g.clemson.edu

Follow this and additional works at: https://tigerprints.clemson.edu/all\_dissertations Part of the <u>Electrical and Computer Engineering Commons</u>

## **Recommended** Citation

Sun, Jiwei, "High Frequency Devices and Circuit Modules for Biochemical Microsystems" (2014). *All Dissertations*. 1457. https://tigerprints.clemson.edu/all\_dissertations/1457

This Dissertation is brought to you for free and open access by the Dissertations at TigerPrints. It has been accepted for inclusion in All Dissertations by an authorized administrator of TigerPrints. For more information, please contact kokeefe@clemson.edu.

## HIGH FREQUENCY DEVICES AND CIRCUIT MODULES FOR BIOCHEMICAL MICROSYSTEMS

A Dissertation Presented to the Graduate School of Clemson University

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy Electrical Engineering

> by Jiwei Sun December 2014

Accepted by: Dr. Pingshan Wang, Committee Chair Dr. Todd H. Hubing Dr. Eric G. Johnson Dr. Apparao M. Rao

## ABSTRACT

This dissertation investigates high frequency devices and circuit modules for biochemical microsystems. These modules are designed towards replacing external bulky laboratory instruments and integrating with biochemical microsystems to generate and analyze signals in frequency and time domain. The first is a charge pump circuit with modified triple well diodes, which is used as an on-chip power supply. The second is an on-chip pulse generation circuit to generate high voltage short pulses. It includes a pulse-forming-line (PFL) based pulse generation circuit, a Marx generator and a Blumlein generator. The third is a six-port circuit based on four quadrature hybrids with 2.0~6.0 GHz operating frequency tuning range for analyzing signals in frequency domain on-chip. The fourth is a high-speed sample-and-hold circuit (SHC) with a 13.3 Gs/s sampling rate and ~11.5 GHz input bandwidth for analyzing signals in time domain on-chip. The fifth is a novel electron spin resonance (ESR) spectroscopy with high-sensitivity and wide frequency tuning range.

#### ACKNOWLEDGMENTS

First of all, I would especially like to acknowledge my advisor Dr. Pingshan Wang for his advice and guidance throughout my Ph.D. time at Clemson University. Dr. Wang's knowledge and critical thinking on microwave engineering and analog circuit design are very helpful for my research. His useful suggestions directly led to the accomplishment of my research projects. I would like to gratefully acknowledge Dr. Haibo Wang from Southern Illinois University Carbondale for his guidance on integrated circuit design.

I would like to express my sincere gratitude to my committee members, Dr. Todd H. Hubing, Dr. Eric G. Johnson and Dr. Apparao M. Rao. Their valuable comments and profound insight have significant influence on my dissertation and academic pursuit. I would also like to acknowledge Dr. John J. Komo for his suggestions on my papers and English.

I would like to acknowledge my present group members and many friends for their help and friendship during the past few years. The help and encouragement from our former group members: Dr. Hanqiao Zhang, Dr. Chaojiang Li, Dr. Chunrong Song, Dr. Yang Yang, Dr. Yongtao Geng, and Ms. Yuxi He are appreciated as well.

Last but not least, I would like to thank my wife, Zhiyun Li, and my parents for their infinite support and love.

## TABLE OF CONTENTS

| Page |

|------|

|------|

| TITLE PA  | \GE                                                                                  | i   |

|-----------|--------------------------------------------------------------------------------------|-----|

| ABSTRA    | СТ                                                                                   | ii  |

| ACKNOW    | VLEDGMENTS                                                                           | iii |

| LIST OF 7 | TABLES                                                                               | vi  |

| LIST OF I | FIGURES                                                                              | vii |

| CHAPTEI   | R                                                                                    |     |

| I.        | INTRODUCTION                                                                         | 1   |

|           | References                                                                           | 5   |

| II.       | HIGH VOLTAGE CHARGE PUMP WITH TRIPLE WELL DIODES IN A 0.13 $\mu m$ BULK CMOS PROCESS | 8   |

|           | Introduction<br>Modified Triple Well Diodes                                          |     |

|           | Charge Pump Circuit Implementation                                                   |     |

|           | Conclusions                                                                          |     |

|           | References                                                                           |     |

| III.      | CMOS HIGH VOLTAGE SHORT PULSE GENERATORS                                             | 25  |

|           | Introduction                                                                         | 25  |

|           | CMOS PFL-based High Voltage Pulse Generation Circuit                                 |     |

|           | Reducing Power-Supply and Ground Noise Induced Timing                                | ,   |

|           | Jitter in PFL-Based Pulse Generation Circuits                                        | 45  |

|           | On-chip Marx Generator                                                               |     |

|           | An On-chip Blumlein Pulse Generator                                                  |     |

|           | Conclusions                                                                          |     |

|           | References                                                                           | 67  |

| IV.       | A HIGHLY RECONFIGURABLE LOW-POWER CMOS                                               |     |

|           | DIRECTIONAL COUPLER AND SIX-PORT CIRCUIT                                             | 74  |

Table of Contents (Continued)

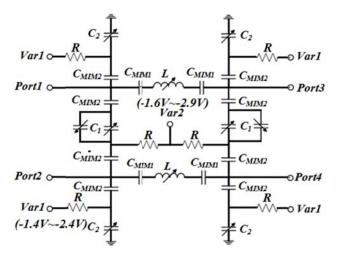

|        | A Highly Reconfigurable Low-power CMOS Directional Coupler<br>A Broadband and Highly Reconfigurable CMOS Six-port Circuit<br>References | 94  |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------|-----|

| V.     | A SPATIAL SAMPLING BASED 13.3 Gs/s SAMPLE-AND-HOLD<br>CIRCUIT                                                                           | 106 |

|        | Introduction                                                                                                                            |     |

|        | A CMOS SHC Based on Spatial Sampling Techniques<br>CMOS Sample-and-Hold Circuit Implementation and                                      | 108 |

|        | Measurement Results                                                                                                                     | 112 |

|        | Conclusions                                                                                                                             | 119 |

|        | References                                                                                                                              | 119 |

| VI.    | BROADBAND HIGH-SENSITIVITY ELECTRON SPIN<br>RESONANCE SPECTROSCOPY                                                                      | 122 |

|        | Introduction                                                                                                                            | 122 |

|        | ESR System Design Considerations                                                                                                        |     |

|        | ESR System Experiments                                                                                                                  |     |

|        | Discussions and Conclusions                                                                                                             |     |

|        | References                                                                                                                              | 130 |

| VII.   | CONCLUSION                                                                                                                              | 132 |

| APPEND | ICES                                                                                                                                    |     |

| A:     | Appendix A                                                                                                                              | 135 |

## LIST OF TABLES

| Table |                                                                    | Page |

|-------|--------------------------------------------------------------------|------|

| 2.1   | Modified triple well diode model parameters                        | 13   |

| 3.1   | Modeled and simulated parameters for high voltage switch           | 39   |

| 3.2   | Simulated output pulse with and without connection system          | 44   |

| 3.3   | LHS design for timing jitter modeling                              | 50   |

| 3.4   | Maximum timing jitter                                              | 54   |

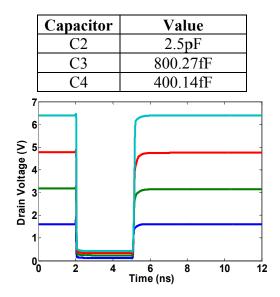

| 3.5   | Design parameters for capacitors in switch                         | 59   |

| 4.1   | Circuit parameters of the active inductor                          | 83   |

| 4.2   | Couplers with coupling coefficients and tunable center frequencies | 93   |

| 5.1   | Dynamic performance parameters of the three sampling channels      | 115  |

| 5.2   | SHC circuit performance summary and comparison                     | 118  |

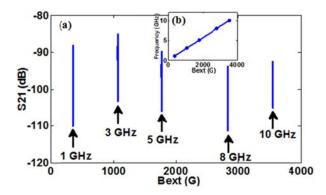

| 6.1   | Summary of DPPH ESR signals at different frequencies               | 128  |

## LIST OF FIGURES

| Figure | Page                                                                                                                                                |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.1    | Cross section of n+/p-well CMOS triple well diode with a guard-ring10                                                                               |

| 2.2    | A photograph of the triple well diode11                                                                                                             |

| 2.3    | Measured I-V curves of the triple well diodes11                                                                                                     |

| 2.4    | Measured and simulated triple well diode characteristics12                                                                                          |

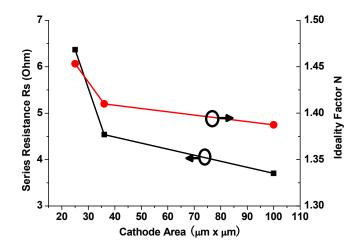

| 2.5    | Relationship among cathode area, ideality factor and series resistance13                                                                            |

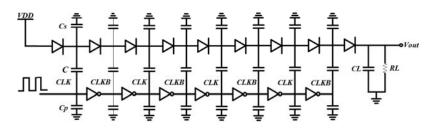

| 2.6    | Eight-stage charge pump circuit realized with 9 triple well diodes14                                                                                |

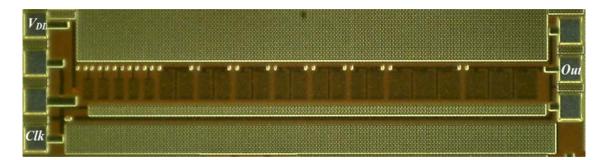

| 2.7    | A photograph of the twelve-stage charge pump with triple well diodes 16                                                                             |

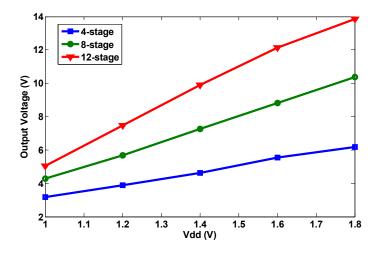

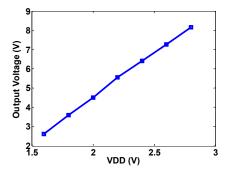

| 2.8    | Measured output voltages of charge pump circuits under different $V_{DD}$ 17                                                                        |

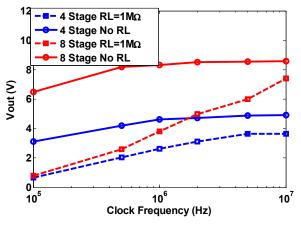

| 2.9    | Measured output voltages of charge pump circuits for different<br>clock frequencies                                                                 |

| 2.10   | Measured output voltages of the four-stage charge pump circuits with<br>the 1 M $\Omega$ resistor and without the resistor under different $V_{DD}$ |

| 2.11   | Measured power efficiency of four-stage and eight-stage charge pump 19                                                                              |

| 2.12   | Measured and simulated output voltages of the four-stage and<br>eight-stage charge pump circuits                                                    |

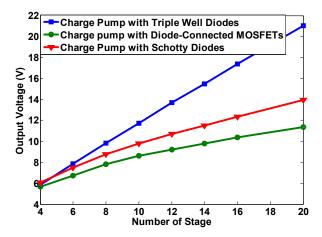

| 2.13   | A comparison of the simulated output voltages of different charge pump circuits as the number of stage increases                                    |

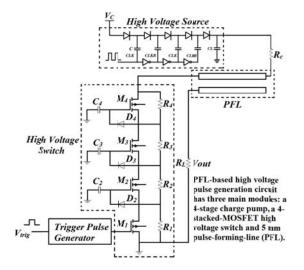

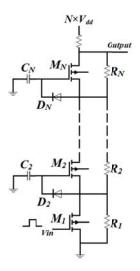

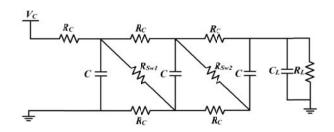

| 3.1    | An on-chip PFL-based high-voltage pulse generation circuit                                                                                          |

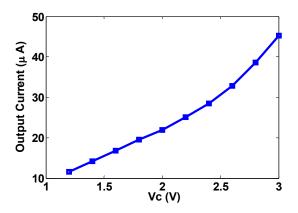

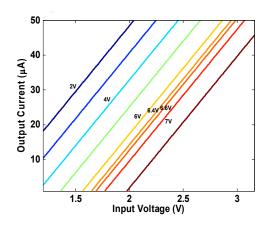

| 3.2    | Simulated output current from the charge pump to ground with different $V_{dd}$ voltages                                                            |

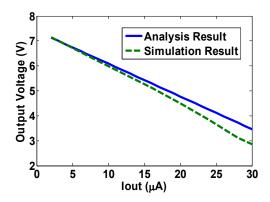

| 3.3    | Comparison of output voltage between analysis and simulation                                                                                        |

| 3.4    | Determination of input voltage to the charge pump                                                                                                   |

| Figure |                                                                                                                              | Page |

|--------|------------------------------------------------------------------------------------------------------------------------------|------|

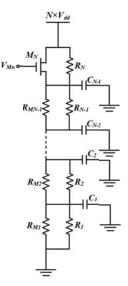

| 3.5    | Schematic of N stacked-MOSFET high-voltage switch                                                                            | .32  |

| 3.6    | An equivalent circuit for the high voltage switch in region I                                                                | .33  |

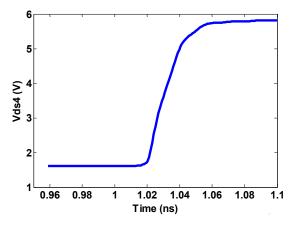

| 3.7    | Transient response $V_{ds4}(t)$ for the switch with four-stacked MOSFETs                                                     | .34  |

| 3.8    | Derivative of transient response $V_{ds4}(t)$                                                                                | .34  |

| 3.9    | Simulated and modeled output voltage of the high voltage switch                                                              | .38  |

| 3.10   | Modeled switch performance with different MOSFET sizes                                                                       | .39  |

| 3.11   | Modeled and simulated output voltage for PFL-based pulse generator                                                           | .40  |

| 3.12   | Measured output voltages of the charge pump with diode-connected zero $V_{th}$ MOSFETs under different power supply voltages | .41  |

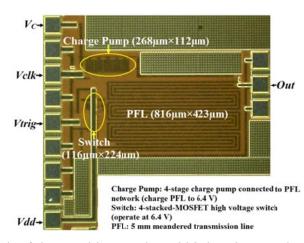

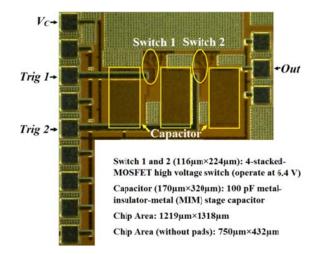

| 3.13   | Micrograph of the on-chip PFL-based high voltage pulse generator                                                             | .41  |

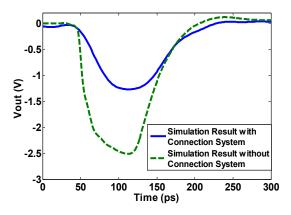

| 3.14   | Simulated output pulse with and without measurement connection                                                               | .42  |

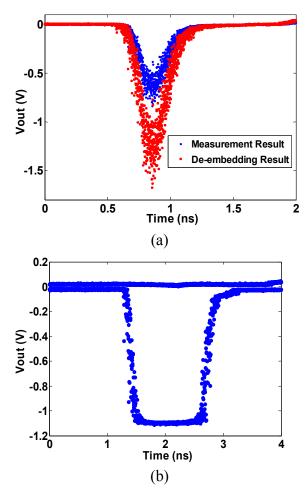

| 3.15   | Measured output pulses                                                                                                       | .43  |

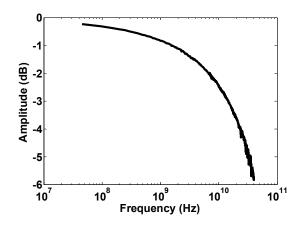

| 3.16   | Frequency response of the connection system                                                                                  | .43  |

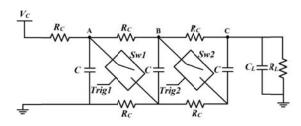

| 3.17   | A schematic of a PFL-based on-chip short pulse generator                                                                     | .46  |

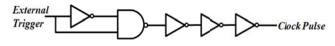

| 3.18   | On-chip trigger pulse generator                                                                                              | .46  |

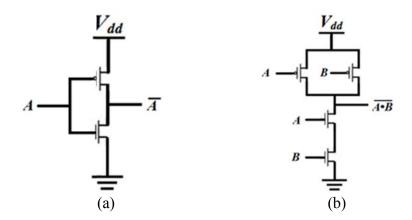

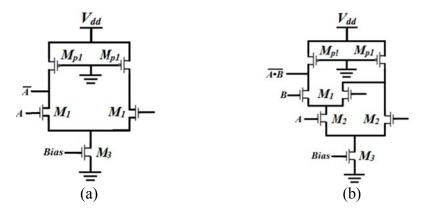

| 3.19   | Schematic of conventional CMOS (a) inverter (b) NAND gate                                                                    | .47  |

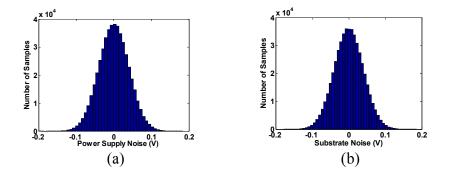

| 3.20   | Histogram of (a) power-supply noise (b) ground noise                                                                         | .48  |

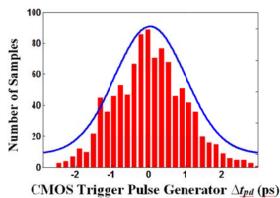

| 3.21   | Histogram of the propagation delay variations for CMOS trigger pulse generator                                               | .48  |

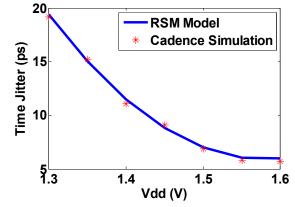

| 3.22   | Comparison of timing jitter obtained by RSM and Cadence Simulations                                                          | . 50 |

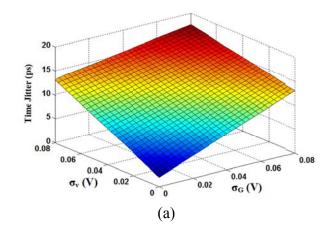

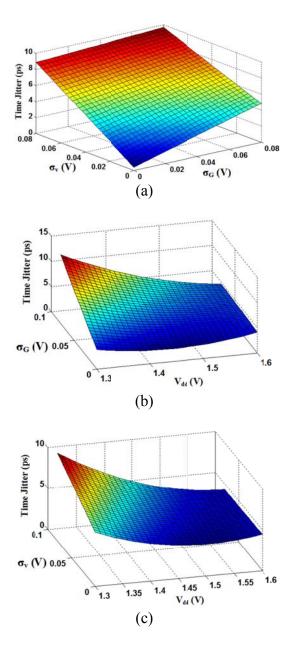

| 3.23   | CMOS short pulse generator timing jitter function (a) $V_{dd}$ =1.4 V<br>(b) $\sigma_V$ =0.04 V (c) $\sigma_G$ =0.04 V       | .51  |

| Figure |                                                                                                                                                                             | Page |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 3.24   | Schematic of MCML (a) inverter (b) NAND gate                                                                                                                                | 52   |

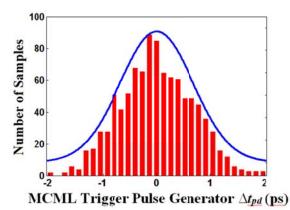

| 3.25   | Histogram of the propagation delay variations for MCML trigger pulse generator                                                                                              | 53   |

| 3.26   | MCML short pulse generator timing jitter function (a) $V_{dd}$ =1.4 V<br>(b) $\sigma_V$ =0.04 V (c) $\sigma_G$ =0.04 V                                                      | 54   |

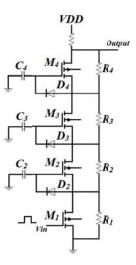

| 3.27   | The schematic of the proposed 3-stage CMOS Marx generator                                                                                                                   | 56   |

| 3.28   | Equivalent circuit of Marx generator under charging mode                                                                                                                    | 57   |

| 3.29   | Equivalent circuit of Marx generator under discharging mode                                                                                                                 | 57   |

| 3.30   | Four stacked MOSFET high voltage switch                                                                                                                                     | 59   |

| 3.31   | Simulation results of stacked MOSFETs in series                                                                                                                             | 59   |

| 3.32   | Micrograph of the on-chip Marx generator                                                                                                                                    | 60   |

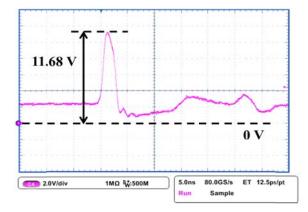

| 3.33   | Measured waveform of 3-stage Marx generator circuit                                                                                                                         | 61   |

| 3.34   | Output voltages under different charging voltages                                                                                                                           | 61   |

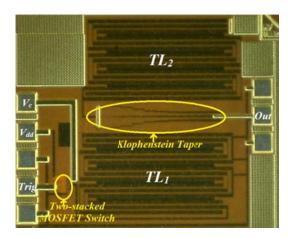

| 3.35   | Proposed on-chip Blumlein generator with a Klophenstein taper                                                                                                               | 63   |

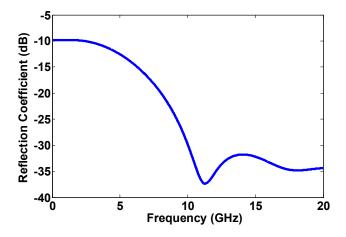

| 3.36   | Simulated result of on-chip Klophenstein taper                                                                                                                              | 64   |

| 3.37   | A micrograph of on-chip Blumlein generator                                                                                                                                  | 65   |

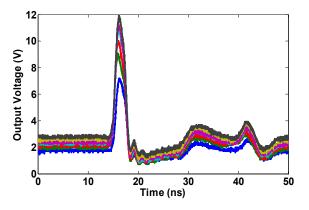

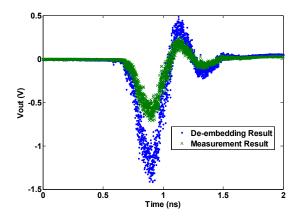

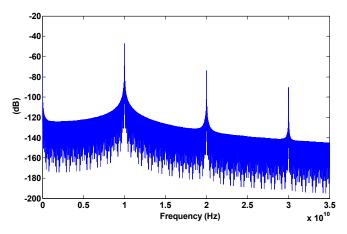

| 3.38   | Measured output pulses of on-chip Blumlein generator                                                                                                                        | 66   |

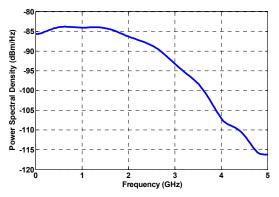

| 3.39   | Power spectrum of the output of on-chip Blumlein generator                                                                                                                  | 66   |

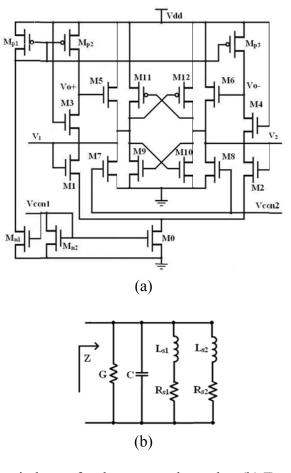

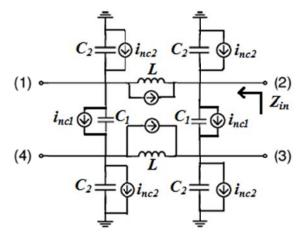

| 4.1    | The proposed directional coupler circuit                                                                                                                                    | 76   |

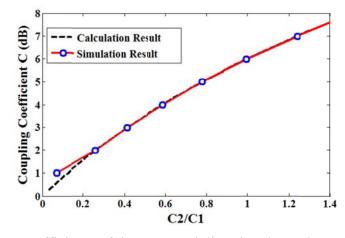

| 4.2    | Coupling coefficients of the proposed directional coupler                                                                                                                   | 79   |

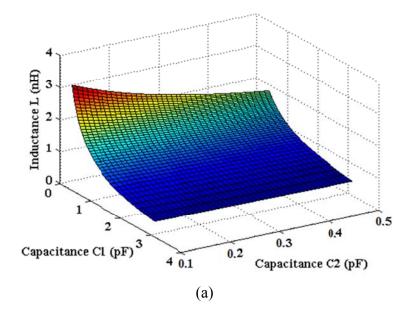

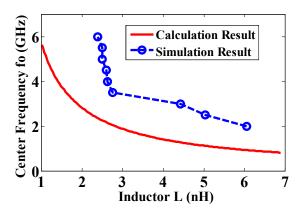

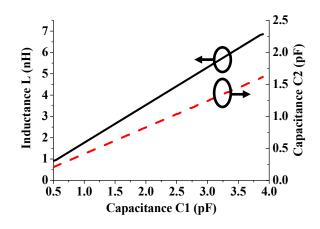

| 4.3    | <ul> <li>(a) The relationship of C<sub>1</sub>, C<sub>2</sub> and L for f<sub>o</sub>=4 GHz</li> <li>(b) different C<sub>1</sub>, and given C<sub>2</sub> values</li> </ul> | 80   |

| Figure | Р                                                                                                | Page |

|--------|--------------------------------------------------------------------------------------------------|------|

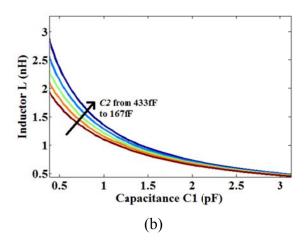

| 4.4    | The operating center frequency for a 3dB nominal coupling-coefficient                            | 81   |

| 4.5    | The tuning of $C_2$ and $L$ with $C_1$ for the 3dB coupling-coefficient operations in Fig. 4.4   | 81   |

| 4.6    | (a) The active inductor for the proposed coupler (b) Equivalent circuit of the inductor          | 83   |

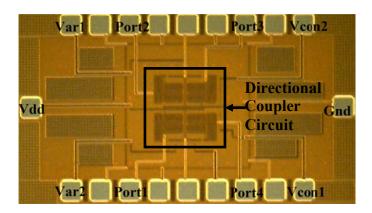

| 4.7    | A die micrograph of the CMOS directional coupler                                                 | 84   |

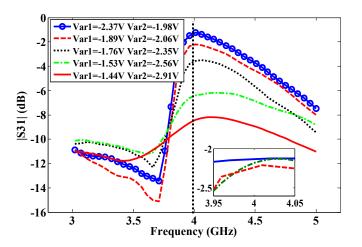

| 4.8    | Tuning the coupling coefficients at $f_o$ =4 GHz                                                 | 85   |

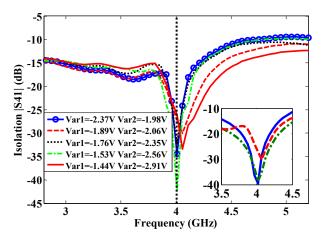

| 4.9    | Measured isolation $ S_{41} $ for the coupling coefficients in Fig. 4.8                          | 86   |

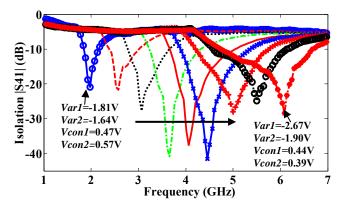

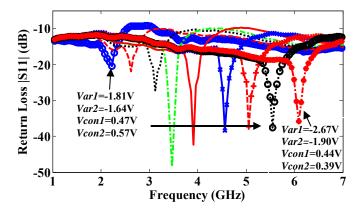

| 4.10   | Measured return loss for the coupling coefficients in Fig. 4.8                                   | 86   |

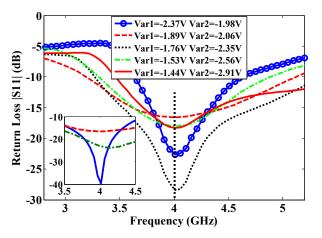

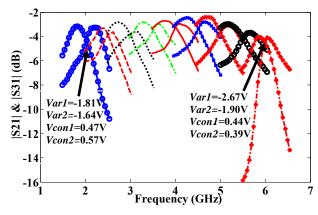

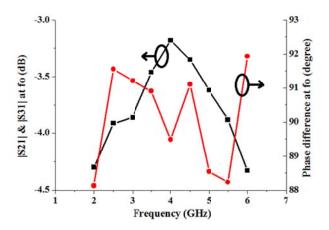

| 4.11   | Measured magnitude $S_{21}$ and $S_{31}$ versus frequency for<br>different operating frequencies | 87   |

| 4.12   | Measured magnitude $S_{21}$ and $S_{31}$ at different operating frequencies                      | 87   |

| 4.13   | Measured isolation $ S_{41} $ versus frequency for different $f_o$ in Fig. 4.11                  | 88   |

| 4.14   | Measured return loss $ S_{II} $ for different $f_o$ in Fig. 4.11                                 | 88   |

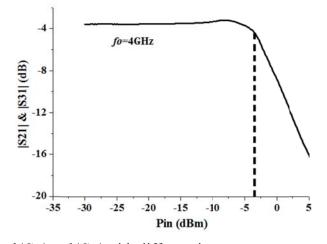

| 4.15   | Measured $ S_{21} $ and $ S_{31} $ with different input power                                    | 89   |

| 4.16   | Noise current sources for the analysis of the proposed<br>directional coupler                    | 89   |

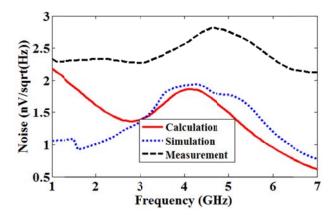

| 4.17   | Calculated, simulated and measured output noise voltages at port 2                               | 91   |

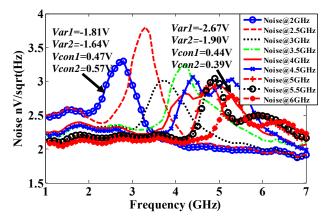

| 4.18   | Measured noise for different <i>f</i> <sub>o</sub>                                               | 91   |

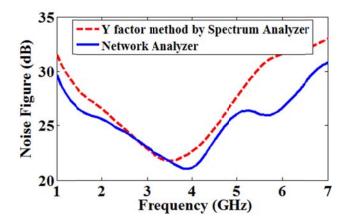

| 4.19   | Noise figure measured by a Y-factor method and a network analyzer                                | 93   |

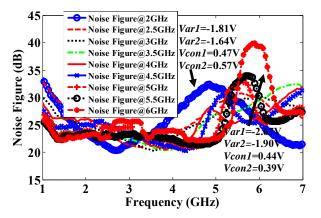

| 4.20   | Measured noise figure for different operating center frequencies                                 | 93   |

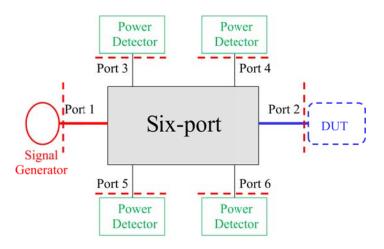

| 4.21   | A six-port network                                                                               | 95   |

| Figure | Page                                                                                                                                                                 |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

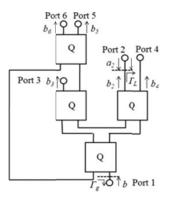

| 4.22   | The schematic of the proposed six-port circuit                                                                                                                       |

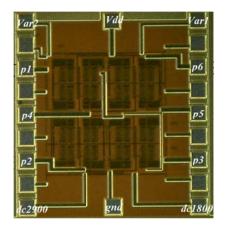

| 4.23   | The micrograph of the proposed six-port circuit                                                                                                                      |

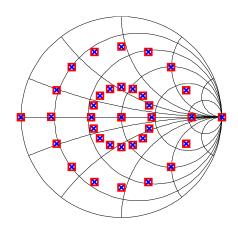

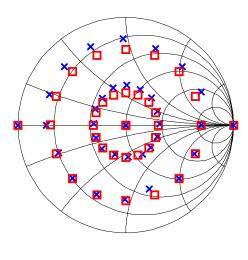

| 4.24   | Simulation results of six-port circuit at (a) 2GHz and (b) 6 GHz98                                                                                                   |

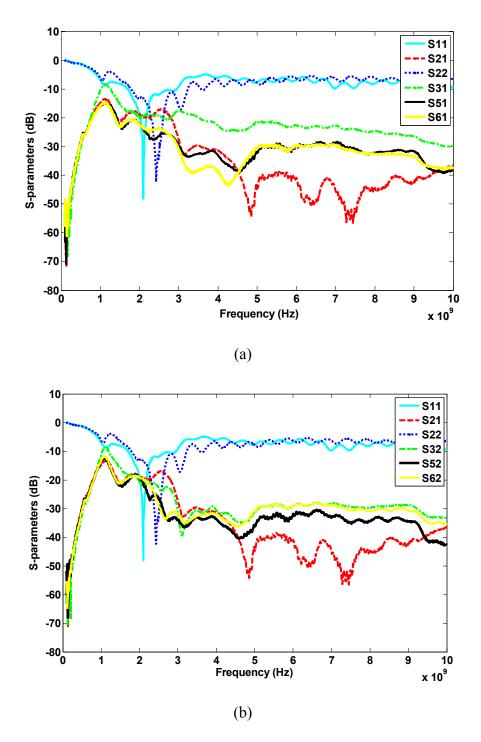

| 4.25   | Measured transmission coefficients from (a) port 1 to port i<br>(i=2, 3, 4, 5, 6) (b) port 2 to port i (i=3, 5, 6)99                                                 |

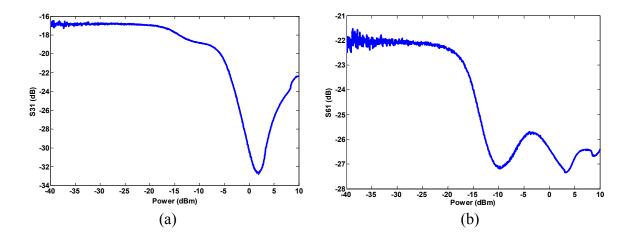

| 4.26   | Measured (a) $ S_{31} $ (b) $ S_{61} $ with different input power                                                                                                    |

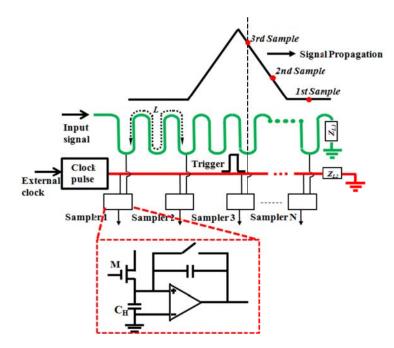

| 5.1    | A CMOS sample-and-hold circuit based on spatial sampling108                                                                                                          |

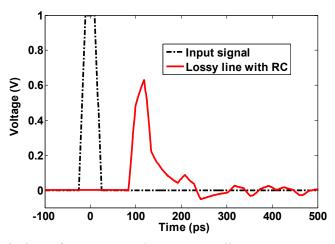

| 5.2    | The transmission of a narrow pulse on CPW lines                                                                                                                      |

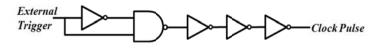

| 5.3    | On-chip clock pulse generator                                                                                                                                        |

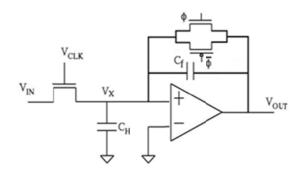

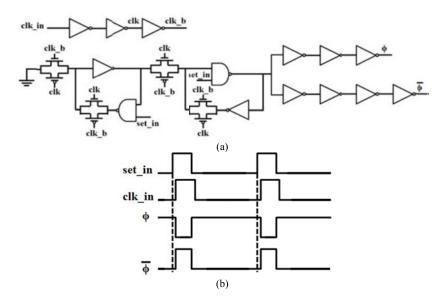

| 5.4    | The schematic of charge amplifier circuit                                                                                                                            |

| 5.5    | Clock signal $\phi$ generation circuit (a) schematic (b) timing sequence<br>when the charge amplifier in amplification mode                                          |

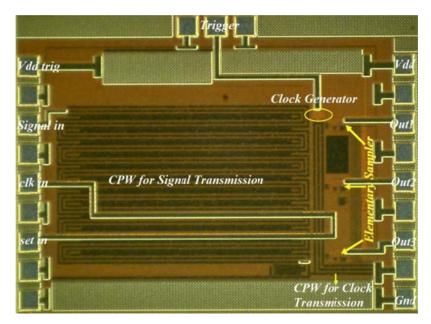

| 5.6    | The micrograph of the proposed high-speed SHC113                                                                                                                     |

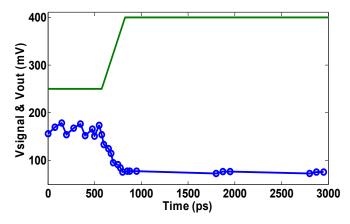

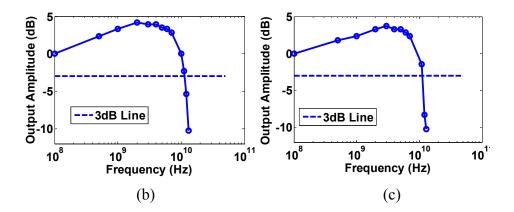

| 5.7    | SHC outputs with a step waveform with 200 ps rise time114                                                                                                            |

| 5.8    | SHC with a single pulse (a) Input pulse (b) Simulated output pulse                                                                                                   |

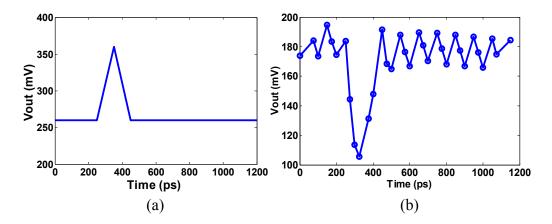

| 5.9    | The FFT plot for the second sampling channel115                                                                                                                      |

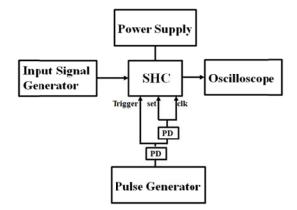

| 5.10   | Measurement setup                                                                                                                                                    |

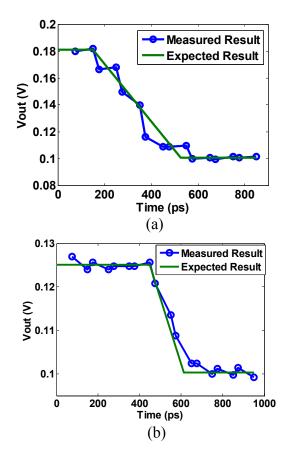

| 5.11   | Measured waveforms for input signals with (a) 350 ps and (b) 130 ps 117                                                                                              |

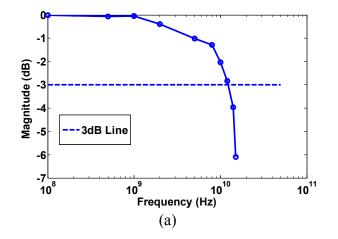

| 5.12   | <ul> <li>(a) Simulated input bandwidth of the sample-and-hold circuit</li> <li>(b) Measured output frequency response for channel 1</li> <li>(c) Channel 2</li></ul> |

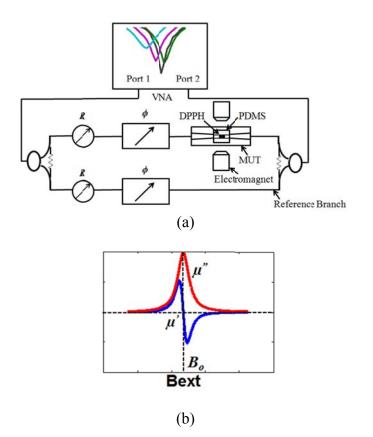

| 6.1    | (a) The schematic of the interference based ESR system. (b) Permeability real and imaginary parts versus external magnetic field                                     |

| Figure |                                                                                                                                                                                             | Page |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

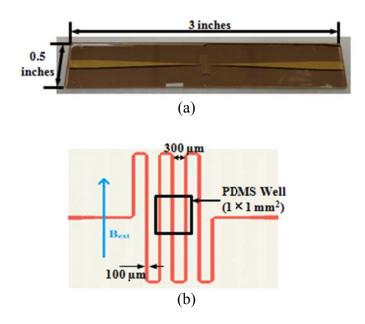

| 6.2    | (a) A photo of a meandered microstrip line. (b) Layout of<br>the meandered microstrip line at the sensing zone                                                                              | 125  |

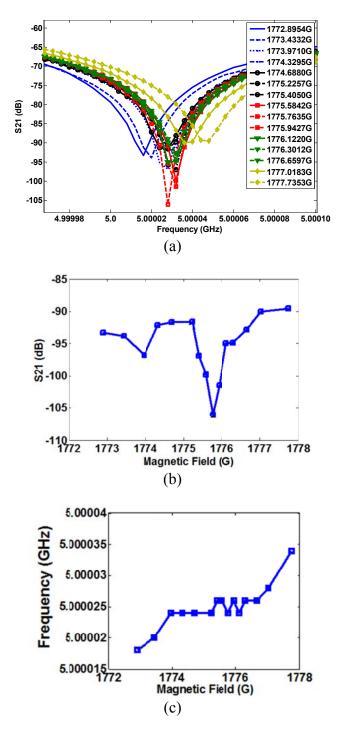

| 6.3    | <ul> <li>(a) Measured  S<sub>21</sub>  changes for external magnetic field-swept ESR at 5 G</li> <li>(b) Summary of minimum  S<sub>21</sub>  from Fig. 6.3 (a). (c) Frequency of</li> </ul> |      |

|        | minimum $ S_{21} $ from Fig. 6.3 (a)                                                                                                                                                        | 127  |

| 6.4    | <ul><li>(a) External magnetic field-swept ESR for various frequencies</li><li>(b) Position of the absorption peak minimum for all</li></ul>                                                 | 100  |

|        | measured spectra shown in Fig. 6.4 (a)                                                                                                                                                      | 128  |

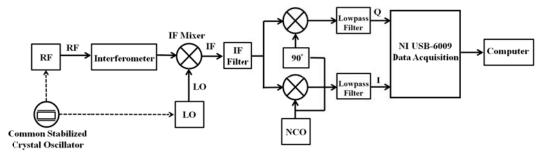

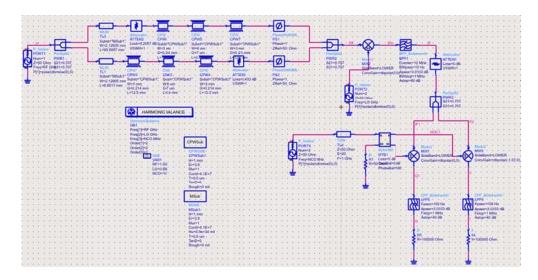

| A-1    | Schematic diagram of miniaturized VNA                                                                                                                                                       | 136  |

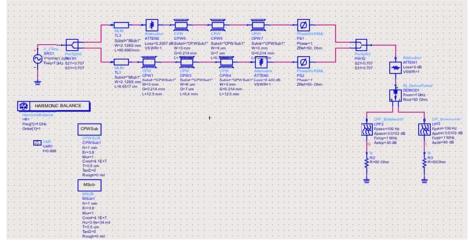

| A-2    | ADS ideal model of the miniaturized VNA                                                                                                                                                     | 136  |

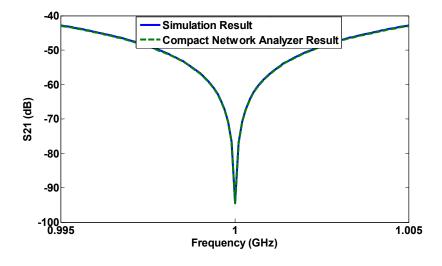

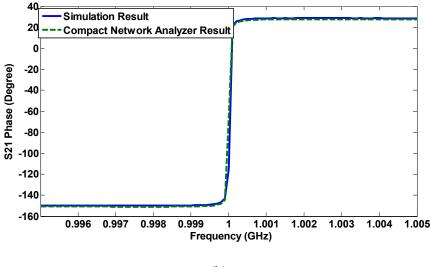

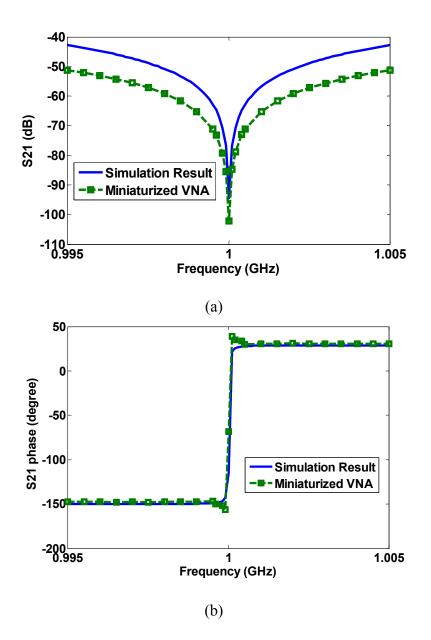

| A-3    | $S_{21}$ (a) magnitude (b) phase obtained from ideal miniaturized VNA                                                                                                                       | 137  |

| A-4    | ADS real model of the miniaturized VNA                                                                                                                                                      | 137  |

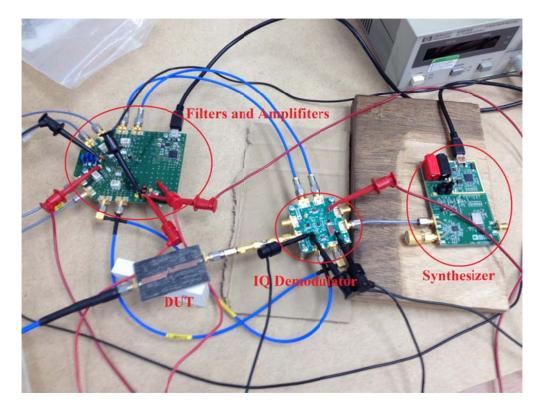

| A-5    | $S_{21}$ (a) magnitude (b) phase obtained from real miniaturized VNA                                                                                                                        | 138  |

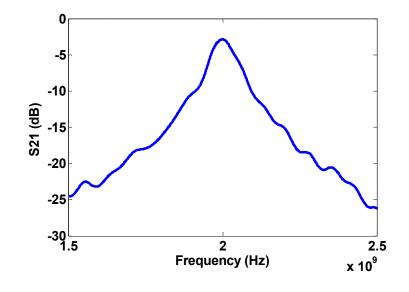

| A-6    | Measurement setup of the miniaturized VNA                                                                                                                                                   | 139  |

| A-7    | <i>S</i> <sub>21</sub> magnitude of the resonator obtained from (a) a commercial VNA (b) our miniaturized VNA                                                                               | 140  |

#### CHAPTER ONE

## INTRODUCTION

Over the past 25 years, there is a rapid development and increasing interest of micro total analysis systems (µTAS) [1.1]-[1.5]. Micro total analysis system, sometimes called lab-on-a-chip, is used to integrate one or several laboratory functions on a single chip. In 1975, the first analytical miniaturized device [1.6], a gas chromatographic analyzer, was developed to separate a simple mixture of compounds in a matter of seconds. In 1990, a miniaturized open-tubular liquid chromatograph based on silicon chip technology was presented by Manz and co-workers [1.7]. At the same time, the concept of "miniaturized total chemical analysis system" or µTAS was proposed by Manz, in which silicon chip analyzers incorporating sample pretreatment, separation, and detection devices were used to integrate a capillary electrophoresis on a chip [1.8]. Applications of micro total analysis systems span basic-science research, clinical medicine, diagnostics, environment, cellular studies, and field work. During the last several years, micro total analysis systems have extended their usefulness into many new fields. They are relatively new group of analytical tools, capable of analyzing DNA, proteins, cells, macromolecules, toxins or pathogens [1.9]. The ability of performing laboratory functions on a chip has opened new ways in modern analytical chemistry, medicine, genetic, cell biology and many other research areas.

Recently, microfluidic and nanofluidic devices are as a subject of extensive research, for molecular analysis, biodefence, molecular biology and microelectronics [1.10]. They can obtain high sensitivity and high resolution by using very small volumes

of samples and fluids, which are regarded as the most powerful advantage of  $\mu$ TAS or lab-on-chip. For organism studies, microfluidic devices have provided controllable and sensitive analysis of small organisms, such as plants, protozoa, zebrafish, and worms [1.11]. Recent microfluidic technology has generated on chip mimics of angiogenesis and mechanical stimuli of organ systems [1.12]-[1.13]. Microfluidic and nanofluidic devices have been used for wide range of practical applications, including drug screening, drug synthesis, packaging, and formulation, water testing, biomedical science, cell biology, and chemistry [1.14]-[1.15]. Until now, successful microfluidic and nanofluidic devices have been used for clinical analysis with the following functions: handing of soluble, detecting pathogens in blood, and analysis of intact cells [1.16].

Although micro total analysis systems have gradually gained maturity, many of them need to connect to off-chip bulky instruments, including sampling units, electronic units and detector units, which cannot realize true lab-on-a-chip. A true lab-on-a-chip should not require an external laboratory to support its operation. These external units are used to provide signals to  $\mu$ TAS and analyze signals generated by  $\mu$ TAS in frequency and time domain. Thus, the benefits of small size and low complexity that have contributed to the popularity of microsystems have been somewhat lost. For further developing and minimizing  $\mu$ TAS, some external instruments for generating and analyzing signals are needed to be demonstrated to realize on chip. When fully developed, micro total analysis systems, which in themselves are completely equipped laboratory units applied to diagnostic, point-of-care (POC), clinical and environmental laboratory, are claimed to be low-cost, easy-to-use, portable and equipment-free. In the developing countries, with limited resources, the healthcare infrastructure is less well developed. In this case,  $\mu$ TAS that do not rely on complicated instrumentation for result interpretation are extremely useful platform to provide affordable disease diagnosis and environmental monitoring to people living in the developing world.

Up to this time, our group members have successfully reported label-free and non-invasive detection methods for the development of micro-total-analysis-systems. In [1.17], a high-sensitive on-chip radio frequency (RF) device is proposed to detect small dielectric property changes in microfluidic channels. In [1.18], Yang demonstrated a simple, ultra sensitive RF sensor to detect a single yeast cell and distinguish its viability in a microfluidic channel. In [1.19], Cui reported a tunable and highly sensitive RF sensor with tunable attenuators and phase shifters to measure the permittivity of materials in a microfluidic channel or nanofluidic channel. These proposed sensors are suited for biochemical applications, bio-analysis, biomedical, cell biology studies and clinical disease diagnostics. In the dissertation, a few integrated RF/microwave circuits and devices have been designed and demonstrated for the development of on-chip analytical tools, pulse generators and electron paramagnetic resonance (EPR) spectroscopy. These RF circuits, instead of some external bulky laboratory instruments, can be integrated with our biochemical microsystems and sensors to generate and analyze signals in frequency and time domain, which is great interest of the development of laboratory chips fully equipped laboratory units.

Below is an outline of this dissertation, each chapter covers a high frequency circuit or device topic:

Chapter II presents charge pump circuits with modified triple well diodes as charge transfer switches. Model parameters of the modified triple well diode are extracted based on measured diode characteristics.

Chapter III presents three types of CMOS pulse generation circuits, including a PFL-based pulse generation circuit with the stacked-MOSFET high voltage switch, an on-chip Marx generator and a Blumlein pulse generator. Generating high voltage short pulses is important for functionality integration, such as micro/nano electromechanical systems (MEMS/NEMS) actuation, electrophoresis, electroporation. The high voltage switch and the PFL-based pulse generation circuit are modeled and analyzed. All these pulse generators are implemented in a 0.13 µm CMOS process.

Chapter IV presents a highly reconfigurable, low-power, and compact directional coupler. The active inductors and varactors are used in this directional coupler to tune operating frequencies and coupling-coefficients. The noise, noise figure, nonlinearity, and power consumption of the proposed directional coupler are analyzed and measured. A six-port circuit based on four quadrature hybrids is also proposed, designed and simulated for analyzing signals in frequency domain on chip.

Chapter V presents a high-speed sample-and-hold circuit based on spatial sampling with CMOS transmission lines (TLs) for analyzing signals in time domain on chip. This circuit contains three main parts: an on-chip meandered coplanar waveguide for signal transmission, a clock signal generator, and elementary samplers. Each elementary sampler has an N-type field effect transistor as the sampling switch, a charge

holding capacitor, and a charge amplifier. Signal propagation on periodically loaded CMOS TLs is analyzed and simulated.

Chapter VI presents a novel electron paramagnetic resonance spectroscopy with high sensitivity and multi-frequency operation for the development of micro-totalanalysis-systems. A radio frequency sensor with tunable attenuators and phase shifters is designed to simultaneously address the sensitivity and multi-frequency operation challenges in the development of EPR techniques. The EPR signals of 60 µg 1,1diphenyl-2picrylhydrazyl (DPPH) are measured from 1 GHz to 10 GHz.

## References

[1.1] D. R. Reyes, D. Iossifidis, P.-A. Auroux, and A. Manz, "Micro total analysis systems. 1. Introduction, theory, and technology," *Anal. Chem.*, vol. 74, pp. 2623–2636, 2002.

[1.2] P.-A. Auroux, D. Iossifidis, D. R. Reyes, and A. Manz, "Micro total analysis systems. 2. Analytical standard operations and applications," *Anal. Chem.*, vol. 74, pp. 2637–2652, 2002.

[1.3] P. S. Dittrich et al., "Micro total analysis systems: Latest advancements and trends," *Anal. Chem.*, vol. 78, pp. 3887–3908, 2006.

[1.4] J.West, M.Becker, S. Tombrink and A. Manz, "Micro total analytical systems: latest achievements," *Anal. Chem.*, vol.80, pp.4403-4419, 2008.

[1.5] A. Arora, et al., "Latest Developments in Micro Total Analysis Systems", *Anal. Chem.*, vol. 82, pp. 4830-4847, 2010.

[1.6] S. C. Terry, J. H. Jerman, and J. B. Angell, "A gas chromatographic air analyzer fabricated on a silicon wafer," *IEEE Trans. Electron. Devices*, vol. ED-26, pp. 1880–1886, Dec. 1979.

[1.7] A. Manz, Y. Miyahara, J. Miura, Y. Watanabe, H. Miyagi, and K. Sato, "Design of an open-tubular column liquid chromatograph using silicon chip technology," *Sens. Actuators*, vol. 1, pp. 249–255, 1990.

[1.8] A. Manz, N. Graber, and H. M. Widmer, "Miniaturized total chemical analysis systems: A novel concept for chemical sensing," *Sens. Actuators*, vol. B1, no. 1–6, pp. 244–248, Jan. 1990.

[1.9] Lisowski, Piotr, and Paweł K. Zarzycki. "Microfluidic Paper-Based Analytical Devices (μPADs) and Micro Total Analysis Systems (μTAS): Development, Applications and Future Trends." *Chromatographia*, vol.76, pp. 1201-1214, 2013.

[1.10] G. M. Whitesides, "The origins and the future of microfluidics," *Nature*, vol. 442, no. 7101, pp. 368–373, Jul. 27, 2006.

[1.11] M.L. Kovarik, D.M. Ornoff, A.T. Melvin, N.C. Dobes, Y.Wang, A.J. Dickinson, et al., "Micro total analysis systems: fundamental advances and applications in the laboratory, clinic, and field," *Anal. Chem.* vol. 85, pp. 451–472, 2013.

[1.12] J. H. Yeon, H. R. Ryu, M. Chung, Q. P. Hu, and N. L. Jeon, "In vitro formation and characterization of a perfusable three-dimensional tubular capillary network in microfluidic devices," *Lab Chip*, vol. 12, no. 16, pp. 2815–2822, 2012. [1.13] J. Wikswo, et al. "Engineering Challenges for Instrumenting and Controlling Integrated Organ-on-Chip Systems." *IEEE Bio-med. Eng.*, vol. 60, no. 3, pp. 682-690, 2013.

[1.14] V. Srinivasan, V. K. Pamula, and R. B. Fair, "An integrated digital microfluidic lab-on-a-chip for clinical diagnostics on human physiological fluids," *Lab Chip*, vol. 4, no. 4, pp. 310–315, Aug. 2004.

[1.15] P. Dittrich and A. Manz, "Lab-on-a-chip: Microfluidics in drug discovery," *Nature Reviews Drug Discovery*, vol. 5, no. 3, pp. 210–218, Mar. 2006.

[1.16] S. J. Lee and S. Y. Lee, "Micro total analysis system (μ-TAS) in biotechnology", *Appl Microbiol Biotechnol*, vol. 64, pp. 289–299, Jan. 2004.

[1.17] C. Song and P. Wang, "A radio frequency device for measurement of minute dielectric property changes in microfluidic channels," *Appl. Phys. Lett.*, vol. 94, no. 2, pp. 023901–023901, 2009.

[1.18] Y. Yang, H. Zhang, J. Zhu, G. Wang, T. R. Tzeng, X. Xuan, K. Huang, and P. Wang, "Distinguishing the viability of a single yeast cell with an ultra-sensitive radio frequency sensor," *Lab Chip*, vol. 10, no. 5, pp. 553–555, Mar. 2010.

[1.19] Y. Cui, J. Sun, Y. He, Z. Wang, and P. Wang, "A simple, tunable, and highly sensitive radio-frequency sensor," *Appl. Phys. Lett.*, vol. 103, no. 6, pp. 062906-062906-3, 2013.

7

#### CHAPTER TWO

# HIGH VOLTAGE CHARGE PUMP WITH TRIPLE WELL DIODES IN A 0.13 $\mu m$ BULK CMOS PROCESS

This chapter presents charge pump circuits with modified triple well diodes as charge transfer switches for charging on-chip pulsed-power systems in a low-voltage bulk CMOS process. Guard-rings and isolation deep n-wells are used to improve the breakdown voltages and reduce leakage currents of the diodes. Model parameters of the triple well diode are extracted based on measured diode characteristics. These parameters are then used to analyze our charge pump. The proposed charge pump circuits are implemented in a commercial 0.13µm bulk CMOS process. The output voltage of the four-stage charge pump circuit can be up to 18.1V, which is much higher than the n-well/p-substrate breakdown voltage (~10V) of the given process.

## 2.1 Introduction

Charge pump circuits are often used to generate high voltages from a low voltage supply for a variety of applications, including driving nonvolatile memories [2.1], actuating MEMS devices [2.2] and charging on-chip pulsed-power systems [2.3]. In addition to high power transfer efficiencies, high output voltages are critical for charge pump circuits.

A Dickson charge pump [2.4] is the most common charge pump circuit topology, in which charge transfer switches are critical components. Traditionally, diode-connected MOSFETs are used as the switching devices. However, the increase of threshold voltages due to body effects [2.5] degrades circuit performance. Several methods are proposed to reduce such effects at the cost of auxiliary circuits and more power consumption [2.5]-[2.8]. A floating-well technique [2.9] can also help reduce body effects, but it may generate substrate currents and affect other circuits on the same chip. Pn-junction diodes are also widely used in charge pump circuits. Yet, the output voltage level is limited by the breakdown of parasitic p-n junctions between the n+ region and the p-substrate [2.10]. The silicon-on-insulator (SOI) process [2.11] and polysilicon diodes [2.10] overcame such limitations. However, the intrinsic polysilicon layer [2.10] is not available in standard bulk CMOS processes, and the SOI CMOS processes for high voltage generation is of great interest.

In this chapter, a charge pump circuit utilizing triple well diodes with guard rings as charge transfer switches is presented. Compared with standard triple well diodes that were attempted in a charge pump [2.12] to obtain 6-10 V output voltages from a 3.3V power supply, guard rings improve the breakdown voltages. Additionally, the anode and cathode of the diodes are completely isolated from bulk substrate by a buried deep n-type layer. Thus, the proposed charge pump circuit is not limited by the breakdown of parasitic p-n junctions and their leakage currents. The analysis of the modified triple well diode is presented in Section 2.2. Section 2.3 gives the results of the circuits implemented in a commercial 0.13µm bulk CMOS process. Section 2.4 concludes the chapter.

#### 2.2 Modified Triple Well Diodes

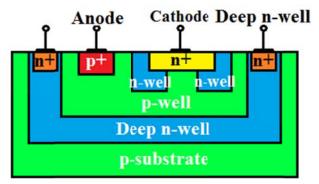

Fig. 2.1 shows the cross section of our triple well diode, which derives from the single photon avalanche diode (SPAD) [2.13]-[2.18]. A deep n-well layer is used for substrate isolation. The parasitic vertical p-n-p bipolar transistor, which consists of p-well, deep n-well and p-substrate, is off since the base and emitter are tied together. As a result, substrate leakage current that exists in conventional p-n junctions is suppressed.

Figure 2.1 The cross section of n+/p-well CMOS triple well diode with a guard-ring.

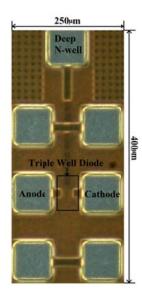

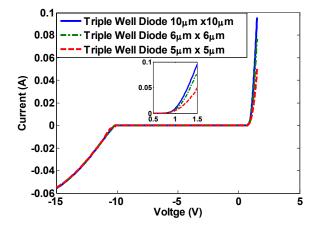

The triple well diode (n+/p-well diode) consists of an n+/p-well junction surrounded by low-doping-level n-well, which acts as a guard ring to prevent edge breakdown [2.13]-[2.15] and improve diode breakdown voltages. Such improvement is important for high-voltage generations. However, appropriate separations between the nwell regions are needed to prevent full depletion of the area under n+ cathode [2.16]-[2.17]. P+ and n+ implantations in Fig. 2.1 are surrounded by Shallow Trench Isolation (STI) [2.18]. The deep n-well fully isolates n+ cathode and p+ anode from p-substrate. Therefore, the triple well diodes can be applied to the charge pump circuit without the limitation of the parasitic junctions. The proposed triple well diodes with different n+ cathode area have been fabricated in IBM 0.13 $\mu$ m CMOS technology. Fig. 2.2 shows a photograph of a triple well diode with 10 $\mu$ m×10 $\mu$ m n+ cathode area. Fig. 2.3 shows the I-V characteristics of the diodes. The cut-in voltages are almost the same (~0.52 V) for diodes of different n+ cathode areas. The reverse breakdown voltages of these diodes are also similar (~10.1 V).

Figure 2.2 A photograph of the triple well diode.

Figure 2.3 Measured I-V curves of the triple well diodes with different n+ cathode area.

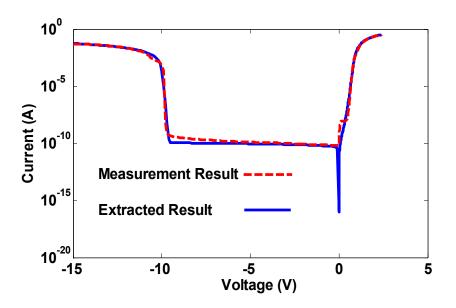

The diode model parameters, shown in Table 2.1, are extracted for circuit simulations. The initial values of these parameters were calculated from measured diode characteristics, including recombination, high-level injection, and series resistance effect. Then these values are globally optimized by curve fitting with a modified least squares method, which greatly improves extraction accuracy and efficiency. Fig. 2.4 shows a comparison between simulated and measured diode characteristics. The simulation is based on the parameters listed in Table. 2.1. These curves are almost identical, which shows that the extracted model parameters can accurately describe the DC behavior of the triple well diodes. Fig. 2.5 shows the relationship among n+ cathode area, ideality factor N and series resistance  $R_S$ . It also shows that when the n+ cathode area increases, the recombination current and resistance in the space charge region between the n guard ring and the p-well under the n+ cathode have the less effect on the characteristics of the triple well diodes.

Figure 2.4 Measured and simulated triple well diode characteristics.

Figure 2.5 Relationship among cathode area, ideality factor and series resistance.

| Model Parameter | Value    |

|-----------------|----------|

| $I_S$           | 1.39 pA  |

| N               | 1.3874   |

| $R_S$           | 3.7033 Ω |

| IKF             | 4.76 mA  |

| ISR             | 46.8 pA  |

| NR              | 2.4944   |

| BV              | 10.06 V  |

| IBV             | 5.81 mA  |

TABLE 2.1

Modified Triple Well Diode Model Parameters

2.3 Charge Pump Circuit Implementation

## 2.3.1 Circuit Design

Fig. 2.6 shows an eight-stage charge pump circuit with 9 triple well diodes. *CLK* and *CLKB* are two out-of-phase clocks with an amplitude  $V_{CLK}$  equivalent to  $V_{DD}$ . Because the breakdown voltage of the capacitors in our CMOS process is ~7V, stacked capacitors are used for higher voltages.

Figure 2.6 Eight-stage charge pump circuit realized with 9 triple well diodes.

The output voltage of the charge pump circuit can be expressed as [2.19]

$$V_{out} = V_{DD} + N \left[ \left( \frac{C}{C + C_s} \right) V_{CLK} - V_D - \frac{I_{out}}{(C + C_s)f} \right] - V_D .$$

(2.1)

where  $V_{CLK}$  is the voltage amplitude of the clock signal, C is pumping capacitance,  $C_S$  is parasitic capacitance at each switching node,  $I_{out}$  is the output current,  $V_D$  is the cut-in diode voltage, N is the number of stages in the charge pump circuit, and f is the clock frequency.

The switching node parasitic capacitance  $C_S$  and the clocked-plate parasitic capacitance  $C_P$  increase the energy loss in a charge pump circuit. To maximize the output voltage, clocking the bottom plate of the stage capacitors is chosen as the connection method in our charge pump. In the bottom-plate connection,  $C_S$  is the combination of the top-plate parasitic capacitance and the triple well diode parasitic capacitance.  $C_P$  consists of the bottom-plate parasitic capacitance, which is generally more than an order of magnitude larger than that of the top plate [2.20]. And the parasitic capacitance in the triple well diode is lower than that in the p+/n-well diode [2.21]. From (2.1), only the switch-node parasitic capacitance  $C_S$  affects the output voltage. Since  $C_S$  is small, clocking the bottom plate results in more output voltage. Assuming that  $I_{out}$  is small enough and  $V_{CLK}$  is the same as  $V_{DD}$ , we have

$$V_{out} = (N+1) \times (V_{DD} - V_D).$$

(2.2)

And the power efficiency of the charge pump is defined as [2.20]

$$\eta = \frac{V_{\text{out}} \times I_{\text{out}}}{V_{DD} \times I_{DD}}$$

(2.3)

The total current consumption of an N-stage charge pump can be expressed as [2.11]

$$I_{DD} = (N+1) \times I_{OUT} + N \times I_P + (2N+1) \times I_S$$

(2.4)

where  $I_p$  is the current charging and discharging the clocked-plate parasitic capacitance, and  $I_S$  is the current charging and discharging the switch-node parasitic capacitance. Also,  $I_p$  and  $I_S$  for our proposed charge pump can be respectively given by [2.11]

$$I_p = C_p \times V_{CLK} \times f \tag{2.5}$$

$$I_s = C_s \times \Delta V_n \times f \tag{2.6}$$

where  $\Delta V_n$  is the voltage swing across the pumping capacitor,  $C_P$  is the bottom-plate parasitic capacitance and  $C_S$  is the combination of the top-plate and diode parasitic capacitance. As the bottom plate is driven by the clock in our charge pump,  $C_S$  is small enough to neglect  $I_S$  in (4) and the bottom-plate parasitic capacitance can be expressed as

$$C_{p} = \frac{I_{DD} - (N+1) \times I_{OUT}}{N \times V_{CLK} \times f}$$

$$(2.7)$$

#### 2.3.2 Measurement Results

Four-stage, eight-stage and twelve-stage charge pump circuits with 6-pF metalinsulator-metal (MIM) pumping capacitors, a 6-pF MIM load capacitor and triple well diodes with  $10\mu$ m×10 $\mu$ m n+ cathode area have been fabricated in an IBM 0.13 $\mu$ m CMOS process. The photograph of the twelve-stage charge pump circuit is shown in Fig. 2.7.

Figure 2.7 A photograph of the twelve-stage charge pump with triple well diodes. The fabricated chip is 570  $\mu$ m ×2485  $\mu$ m.

Fig. 2.8 shows the measured output voltage of the four-stage, eight-stage and twelve-stage charge pump circuits with different power-supply voltages to drive the capacitive output load. The output voltage of the twelve-stage charge pump circuit is as high as 12.3 V from 1.6 V power supply voltage corresponding to a voltage gain of ~7.7, which is much higher than the n-well/p-substrate junction breakdown voltage (~10V), which is also the maximum junction breakdown in the given 0.13µm bulk CMOS process. At 12.3 V, the voltage across each triple well diode doesn't exceed the reverse breakdown voltages of the triple well diodes. Fig. 2.9 shows the measured output voltages of the four-stage and eight-stage circuits under different clock frequencies, where the power supply voltage is 1.6 V. When the clock frequency is increased, the output voltages of the charge pump circuit are also increased due to less charge leaking to parasitic capacitors.

Figure 2.8 Measured output voltages of the charge pump circuits with triple well diodes to drive capacitive loads under different  $V_{DD}$ . The clock frequency is 5MHz.

Figure 2.9 Measured output voltages of the four, and eight-stage charge pump circuits for different clock frequencies. The power supply is 1.6V.

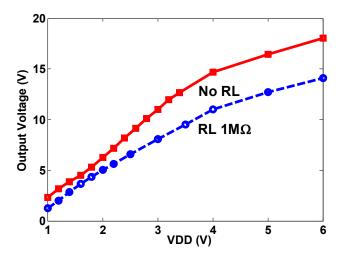

Fig. 2.10 shows the measured output voltage of the four-stage circuit with  $1M\Omega$  output resistors and without output resistor at a 5MHz clock frequency. In Fig. 2.10, the output voltage of the charge pump circuit realized with the triple well diodes can be as high as ~18.1 V. Fig. 2.11 shows the measured power efficiency of the proposed four-

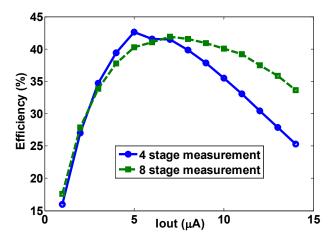

stage and eight-stage charge pump. The measured peak power efficiencies of these two charge pumps are about 42.59% at  $I_{OUT}$  of 5 µA and about 41.92% at  $I_{OUT}$  of 7 µA, respectively. From (2.3), the clocked-plate parasitic capacitance  $C_p$  has the main effect on the power efficiency. In a bottom-plate connection, a large bottom parasitic capacitance of stage capacitors results in lower power efficiency. Clocking the top plate of the stage capacitors will reduce  $C_p$ , which can result in higher power efficiency. Also, this topplate connection will cause the decrease in the voltage gain of each stage of the charge pump, which results in a lower output voltage.

Currents  $I_{DD}$  and  $I_{OUT}$ ,  $I_{DD}$ =81.75 µA and  $I_{OUT}$ =7 µA, for the eight-stage charge pump shown in Fig. 2.7 are measured with a Keithley 2612 system source meter, where the clock frequency is 5 MHz and the power supply is 1.6 V. From (2.7),  $C_P$  can be calculated as 0.85 pF, which is used for a proposed charge pump simulation.

Figure 2.10 Measured output voltages of the four-stage charge pump circuits with the 1M $\Omega$  resistor and without the resistor under different  $V_{DD}$ . The clock amplitude is always equal to  $V_{DD}$ .

Figure 2.11 Measured power efficiency of the proposed four-stage and eight-stage charge pump circuits.

## 2.3.3 Discussion

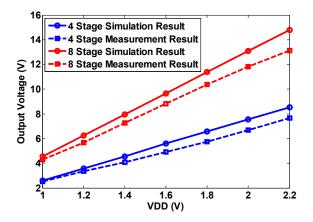

The model parameters of the triple-well diode in Table 2.1 and the parasitic capacitance,  $C_p$ =0.85 pF, are used to obtain the simulation results in Fig. 2.12. It shows that results from simulations and measurements agree with each other reasonably well. This further validates our model parameter extraction (Table 2.1) and circuit design processes. Compared with ideal charge pumps, the measured output voltage increase is ~16% lower while the simulated voltage increase is only ~6% lower when the supply voltage increases by  $\Delta V$ . This discrepancy is likely due to the leakage currents from parasitic capacitors of triple well diodes and the voltage loss caused by the measurement system including contact pads, probes, connectors and cables.

Figure 2.12 Measured and simulated output voltages of the proposed four-stage and eight-stage charge pump circuits to drive capacitive loads.

Fig. 2.13 shows a comparison of our charge pump circuit with circuits that use diode-connected MOSFETs and Schotty diodes as switches in the same technology. The simulations were conducted with 1.6V  $V_{DD}$  for a different number of stages. It shows that for 5-stages or less, the circuit with Schottky diodes has higher output voltages due to lower cut-in voltages (~0.3V). When the number of stage increases, our circuit generates much higher voltages. For diode-connected MOSFETs, the increase of threshold voltage ( $V_{th}$ ) due to body effects affects the output voltage and power efficiency. For Schotty diode circuits, the output voltage is limited by the breakdown of parasitic p-n junctions and leakage current to the substrate. Thus, the voltage gain per stage in the charge pump circuits with diode-connected MOSFETs or Schotty diodes decreases as the number of stages increases as discussed in the introduction. The output voltage of our proposed charge pump circuit is not limited by the breakdown voltages of the parasitic p-n junctions. Although the power efficiency of our charge pump is adversely affected by the

bottom-plate parasitic capacitance and high cut-in voltage of the diodes. As shown in Fig. 2.10, the output voltage of our circuit can drive a purely capacitive load up to ~18.1V.

Figure 2.13 A comparison of the simulated output voltages of the charge pump circuits with triple well diodes, diode-connected MOSFETs and Schotty diodes as the number of stage increases. The clock frequency is 5 MHz.

## 2.4 Conclusions

Triple well diodes with guard rings and deep n-well isolation are designed and modeled for high-voltage operation in standard bulk CMOS processes. Four-stage, eight-stage and twelve-stage charge pump circuits with triple well diodes as charge transfer switches have been implemented in a commercial 0.13µm bulk CMOS process. Compared with circuits that use diode connected FETs and Schottky diodes as switches, our circuits generate much higher output voltages. When a 6-pF capacitor is used as the load, the measured output voltage can be up to 18.1V, using a 5MHz two-phase nonoverlapping clock. The achieved voltage is much higher than the p-n junction breakdown voltages of the given processes.

#### References

[2.1] A. Umezawa, et al, "A 5-V-only operation 0.6-µm Flash EEPROM with row decoder scheme in triple-well structure," *IEEE J. Solid-State Circuits*, vol. 27, pp. 1540-1546, Nov. 1992.

[2.2] J. A. Starzyk, Y.-W. Jan, and F. Qui, "A DC-DC charge pump design based on voltage doublers," *IEEE Trans. Circuits Syst. I: Fundam. Theory Appl.*, vol. 48, no. 3, pp. 350-359, Mar. 2001.

[2.3] Y. T. Geng, H. Zou, C. J. Li, J. W. Sun, H. B. Wang, and P. S. Wang, "Short pulse generation with on-chip pulse-forming lines," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 20, no. 9, pp.1553-1564, Sep. 2012.

[2.4] J. F. Dickson, "On-chip high-voltage generation in MNOS integrated circuits using an improved voltage multiplier technique," *IEEE J. Solid-State Circuits*, vol. SC-11, no. 3, pp. 374-378, Jun. 1976.

[2.5] J. S. Shin, I. Y. Chung, Y. J. Park, and H. S. Min, "A new charge pump without degradation in threshold voltage due to body effect," *IEEE J. Solid-State Circuits*, vol. 35, no. 8, pp. 1227-1230, Aug. 2000.

[2.6] M. D. Ker, S. L. Chen, and C. S. Tsai, "Design of charge pump circuit with consideration of gate-oxide reliability in low-voltage CMOS processes," *IEEE J. Solid-State Circuits*, vol. 41, no. 5, pp. 1100-1107, May. 2006.

[2.7] A. N. Richelli, L. Colalongo, L. Mensi, A. Cacciatori, and Z. M. Kovacs-Vajna, "Charge pump architectures based on dynamic gate control of the pass-transistors," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 17, no. 7, pp. 964–967, Jul. 2009. [2.8] R. Pelliconi, D. Iezzi, A. Baroni, M. Pasotti, and P. L. Rolandi, "Power efficient charge pump in deep submicron standard CMOS technology," *IEEE J. Solid-State Circuits*, vol. 38, no. 6, pp. 1068-1071, Jun. 2003.

[2.9] K. –H. Choi, J. –M. Park, J. –K. Kim, T. –S. Jung, and K. –D. Suh, "Floating-well charge pump circuits for sub-2.0V single power supply flash memories," in *Symp. VLSI Circuits Dig. Tech. Papers*, 1997, pp. 61-62.

[2.10] M. –D. Ker and S. –L. Chen, "Ultra-high-voltage charge pump circuit in low-voltage bulk CMOS processes with polysilicon diodes," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 54, no. 1, pp. 47-51, Jan. 2007.

[2.11] M. R. Hoque, T. Ahmad, T. R. McNutt, H. A. Mantooth, and M. M. Mojarradi, "A technique to increase the efficiency of high-voltage charge pumps," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 53, no. 5, pp. 364-368, May 2006.

[2.12] S. Kobayashi et al, "A 3.3V-only 16Mb DINOR flash memory," in *Proc. ISSCC Dig. Tech. Papers*, Feb. 1995, pp. 122-123.

[2.13] M. Dandin, A. Akturk, B. Nour, N. Goldsman, and P. Abshire, "Characterization of single-photon avalanche diodes in a 0.5 μm standard CMOS process—Part 1: Perimeter breakdown suppression," *IEEE Sens. J.*, vol. 10, no. 11, pp. 1682-1690, Nov. 2010.

[2.14] J. A. Richardson, E. A. G. Webster, L. A. Grant, and R. K. Henderson, "Scaleable single-photon avalanche diode structures in nanometer CMOS technology," *IEEE Tran. Electron Devices*, vol. 58, no. 7, pp. 2028-2035, Jul. 2011.

23

[2.15] M. Ghioni, A. Gulinatti, I. Rech, F. Zappa, and S. Cova, "Progress in silicon single-photon avalanche diodes," *IEEE J. Sel. Topics Quantum Electron.*, vol. 13, no. 4, pp. 852-862, Jul./Aug. 2007.

[2.16] D. Palubiak, M. M. El-Desouki, O. Marinov, M. J. Deen, and Q. Y. Fang, "High-speed, single-photon avalanche-photodiode imager for biomedical applications," *IEEE Sens. J.*, vol. 11, no. 10, Oct. 2011.

[2.17] Y. S. Kim, I. S. Jun, and K. H. Kim, "Design and Characterization of CMOS avalanche photodiode with charge sensitive preamplifier," IEEE Tran. Nuclear Science, vol. 55, no. 3, pp. 1376-1380, Jun. 2008.

[2.18] C. Niclass, M. Gersbach, R. Henderson, L. Grant, and E. Charbon, "A single photon avalanche diode implemented in 130-nm CMOS technology," *IEEE J. Sel. Topics Quantum Electron.*, vol. 13, no. 4, pp. 863-869, Jul./Aug. 2007.

[2.19] F. Pan and T. Samaddar, *Charge Pump Circuit Design*. New York: McGraw-Hill, 2006.

[2.20] G. Palumbo, D. Pappalardo, and M. Gaibotti, "Charge pump circuits: powerconsumption optimization," *IEEE Trans. Circuits Syst. I, Fundam. Theory Appl.*, vol. 49, no.11, pp. 1535-1542, Nov. 2002.

[2.21] S. S. Chen, T. Y. Chen, T. H. Tang, J. K. Chen and C. H. Chou, "Low-leakage diode string designs using triple-well technologies for RF-ESD applications," *IEEE Electron Device Lett.*, vol. 24, no. 9, pp. 595-597, Sep. 2003.

#### CHAPTER THREE

#### CMOS HIGH VOLTAGE SHORT PULSE GENERATORS

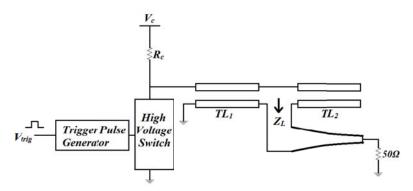

We present three types of on-chip pulse generation circuits. The first is based on CMOS pulse-forming-lines (PFLs). It includes a four-stage charge pump, a four-stacked-MOSFET switch and a 5 mm long PFL. The circuit is implemented in a 0.13  $\mu$ m CMOS process. Pulses of ~1.8 V amplitude with ~135 ps duration on a 50  $\Omega$  load are obtained. The obtained voltage is higher than 1.6 V, the rated operating voltage of the process. The second is a high-voltage Marx generator which also uses stacked MOSFETs as high voltage switches. The output voltage is 11.68 V, which is higher than the highest breakdown voltage (~10 V) of the CMOS process. The third is a CMOS Blumlein generator including a two-stacked-MOSFET high voltage switch, a Blumlein PFL network, and an on-chip Klophenstein taper. Gaussian-like pulses of 725 mV peak-to-peak amplitude, ~126 ps duration and 3.18 GHz bandwidth are measured on a 50  $\Omega$  load. After de-embedding the connection system and Klophenstein taper, the pulses of 1.88 V and 114 ps duration are obtained. These results significantly extend high-voltage short pulse generation capabilities of CMOS technologies.

#### 3.1 Introduction

Generating high voltage short pulses on chip is important for functionality integration, such as micro/nano electromechanical systems (MEMS/NEMS) actuation [3.1], electrophoresis [3.2], electroporation [3.3] and cellular investigation [3.4]-[3.5]. Short electrical pulse is also important for various other applications, such as clocking

high-speed analog-to-digital converters (ADC) [3.6], synthesizing ultra-wideband (UWB) signals for UWB communications [3.7], and developing inexpensive terahertz (THz) pulse technologies. Nevertheless, techniques for high voltage pulse generations on chip are still under exploration.

Digital circuits generate pulses with  $V_{dd}$  as the maximum available output voltages and fan-out-four (FO4) propagation delay as the shortest pulses on a load of 4inverters, which are usually much lighter than a 50  $\Omega$  load. Traditional analog circuits could generate higher voltage pulses, but limited by  $V_{dd}$  and breakdown voltages of the given technology. High-voltage CMOS processes may not be able to exploit the highspeed capabilities of standard digital CMOS processes without incurring higher costs. Photoconductive switching [3.8] and transmission line discontinuities [3.9] generate short pulses. However, it is difficult to implement these circuits in a standard CMOS process. Nonlinear transmission lines (NLTL) [3.10]-[3.11], which consist of long transmission lines and dozens of varactors, can sharpen pulse edges. But these circuits occupy large chip areas and their high-voltage generation capabilities need to be demonstrated. The CMOS UWB pulse generators, which are based on a pulsed oscillator and a pulse shaping filter [3.12] or a distributed waveform generator [3.13], generate pulses with high bandwidth (4.5 GHz [3.12] and 6 GHz [3.13]). These circuits are also not applied for high voltage generations. In [3.14]-[3.15], we proposed a pulse-forming-line (PFL) based CMOS generator, which significantly extends the high voltage short pulse generation capabilities of CMOS technologies. Nevertheless, the obtained pulses are modest, with 180 mV voltages and ~160 ps full-width-at-half-magnitude (FWHM) on a 50  $\Omega$  load. A 0.13  $\mu$ m CMOS technology was used for circuit implementation.

In this effort, we further expand our previous work to generate high output voltages. We also present a high-voltage CMOS Marx generator circuit and an on-chip Blumlein generator. Such circuits have not been reported so far. This chapter is organized as follows. Section 3.2 presents the proposed CMOS PFL-based pulse generation circuit, including a charge pump circuit, a high voltage switch and a PFL network. Section 3.3 proposes a study of reducing the timing jitter induced by power-supply and ground noise in PFL-based pulse generation circuits. Section 3.4 presents an on-chip Marx generator. Section 3.5 presents a CMOS Blumlein generator with an on-chip Klophenstein taper. Section 3.6 concludes this chapter.

## 3.2 CMOS PFL-based High Voltage Pulse Generation Circuit

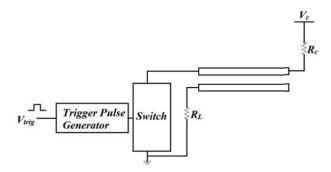

The basic idea of a CMOS high voltage pulse generation circuit is to achieve high voltage (e.g. higher than 10 V, the breakdown voltages of N-well/Substrate of our given CMOS process) by exploiting the much higher voltage handling capabilities of the dielectric insulation layers between interconnect metals [3.16]. Figure 3.1 shows the on chip PFL-based high voltage pulse generation circuit, including a four-stage charge pump, a four-stacked-MOSFET switch and a 5 mm PFL. The four-stage charge pump is used as a high voltage source to generate the DC voltages higher than the power-supply voltage ( $V_{dd}$ ). The four stacked MOSFET switch can operate at  $4 \times V_{dd}$  (6.4 V) to overcome the limitation of breakdown voltages of MOSFETs, where  $V_{dd}$  (1.6 V) is the rated voltage of our given process [3.17]-[3.20]. When the switch is turned on by the

trigger signal, which is sharpened by a trigger pulse generator, the PFL discharges through load  $R_L$  (50  $\Omega$ ). The output pulse is then generated with an ideal amplitude of 3.2 V and 77 ps FWHM.

Figure 3.1 An on-chip PFL-based high-voltage pulse generation circuit.

3.2.1 Charge Pump Design and Analysis

The charge pump module in Fig. 3.1 is connected to a pulse forming line network. A Dickson charge pump [3.21] topology is used. Zero  $V_{th}$  MOSFETs are used as charge transfer switches due to their lower cut-in voltages (~0.1 V). The output capacitor,  $C_L$ , at the end of the charge pump in Fig. 3.1, acts as a local power source and filter that reduces noise generated from the power supply.

The output voltage of the charge pump is [3.22]-[3.23]

$$V_{out} = V_{dd} + N \left[ \left( \frac{C}{C + C_s} \right) V_{CLK} - V_D - \frac{I_{out}}{(C + C_s)f} \right] - V_D,$$

(3.1)

where  $V_{CLK}$  is the voltage amplitude of the clock signal, C is the pumping capacitance,  $C_S$  is the parasitic capacitance at each switching node,  $I_{out}$  is the output current,  $V_D$  is the cut-

in diode voltage, N is the number of stages in the charge pump circuit, and f is the clock frequency.

The reliable operation of the stacked-MOSFET switch determines the maximum charge pump output voltage. For the four stacked MOSFETs in Fig. 3.1, the pulse forming line network can be charged to  $4 \times V_{dd}$  (~6.4 V). Thus a four-stage charge pump is chosen to obtain ~6.4 V output voltages from a 1.6 V power supply even though the ideal output voltage from this charge pump is 8 V. The voltage loss is due to charge loss through the current path formed by the voltage division resistors of the switch and the transmission lines. The output current (simulated) of the charge pump when imbedded in the circuit in Fig. 3.1 is shown in Fig. 3.2. It shows that the output current depends on the input power supply to the charge pump. Therefore, it is necessary to take into account this load effect when generating a given voltage. Fig. 3.3 shows the comparison of output voltage between analysis and simulation with different output currents. It is seen that the analysis results agree reasonably well with simulation results. Thus, Eq. (3.1) accurately describes the output voltage behavior of the charge pump circuit.

Figure 3.2 Simulated output current from the charge pump to ground with different  $V_{dd}$  voltages.

Figure 3.3 Comparison of output voltage between analysis and simulation with different output currents. The power supply voltage is 1.6 V and the clock frequency is 5 MHz.

Fig. 3.4 shows the required  $V_{dd}$  for a targeted  $V_{out}$  and a given load (i.e.  $I_{out}$ ), obtained from Eq. (1), of the charge pump circuit. For 6.4 V output voltage,  $V_{dd}$  is less than 2.5 V, and the maximum output current is less than 30  $\mu$ A. In our experimental test in section 3.4, a 2.4 V  $V_{dd}$  was chosen. Figure 3.4 shows that  $I_{out}$  is less than 30  $\mu$ A and the output voltage is 6.6V, which is 0.2 V above 6.4 V. It should be pointed out that the 2.4V  $V_{dd}$  is above the 1.2 V-1.6 V operating voltage of our given 0.13  $\mu$ m CMOS process. Nevertheless, the MOSFETs in the stacked switch operate around 1.6 V. Furthermore, the breakdown voltage between gate/drain/source and the body of the MOSFETs in the technology is ~4.0 V. Thus, a 2.4 V  $V_{dd}$  does not cause breakdown issues in the charge pump circuit module.

Higher output voltages can be achieved without using  $V_{dd}$  larger than 1.6 V. One approach is to add more stages in the charge pump circuit module. However, due to body effect for diode-connected MOSFETs [3.24] or breakdown of parasitic p-n junctions for diodes [3.25], output voltages of charge pump circuits are limited and cannot be a linear function of the number of stages. Thus, modified triple well diodes are used as charge transfer switches to help solve this problem. In chapter two, we used modified triple well diodes in a 12 stage charge pump circuit and obtained as high as ~12.3 V output voltages to drive the 6 pF capacitive load from a 1.6  $V_{dd}$  supply without breakdown concerns, which is much higher than the n-well/p-substrate junction breakdown voltage (~10 V). From Fig. 3.2, when  $V_{dd}$  is 1.6 V, the 8 stage charge pump with modified triple well diodes can generate ~6.4 V under ~12  $\mu$ A output current to ground.

Figure 3.4 Determination of input voltage to the charge pump for the given requirements.

### 3.2.2 High Voltage Switch Design and Analysis

Fig. 3.5 shows the high voltage switch with *N* stacked-MOSFETs, which can switch  $N \times V_{dd}$ . Before the bottom  $M_1$  is turned on, the resistors  $(R_1 \sim R_N)$  equally divide  $N \times V_{dd}$  into  $V_{dd}$  across each MOSFET. When  $M_1$  is turned on, its drain is discharged. Thus, its drain voltage is decreased. Then  $M_2$  is on, and similarly all the other MOSFETs  $(M_2 \sim M_N)$  are turned on. Through setting the turn-on capacitance, the gate-source voltage for each transistor in the stack can be expressed as [3.17]

$$V_{gs(i)} = \frac{C_{(i)}}{C_{(i)} + C_{p(i)}} \times \left( (i-1) \times \left( \frac{V_{ddh}}{N} \right) - V_{diode} \right) + \frac{C_{(i)}}{C_{(i)} + C_{p(i)}} \times (-V_{diode}), i = 2 \sim N,$$

(3.2)

where *N* is the number of transistors in the stack, *i* is the specific device being considered,  $V_{ddh}$  is the desired high voltage ( $N \times V_{dd}$ ),  $V_{diode}$  is the voltage across the diode ( $D_2 \sim D_N$ ), *C* is the turn-on capacitance, and  $C_p$  is the total parasitic capacitance across the gate-source of each MOSFET in series.

Figure 3.5 Schematic of N stacked-MOSFET high-voltage switch

Assume that each MOSFET in the switch has equal size and turn-on gate-source voltage, the turn-on capacitances can be defined as [3.17]

$$C_{i} = C_{p(i)} \left( \frac{V_{gs} + V_{diode}}{(i-1) \times \left(\frac{V_{dd}}{N}\right) - \left(V_{gs} + V_{diode}\right)} \right), i = 2 \sim N.$$

(3.3)

The operating process of the high voltage switch can be divided into two regions, Region I and Region II. During Region I, the MOSFETs  $(M_I \sim M_{N-I})$  are turned on and discharge capacitances at each drain node without affecting the output node in Fig. 3.5. During Region II,  $M_N$  is turned on, pulling the output node to ground. Region I: Transistor  $M_N$  is off and transistors  $M_I$  to  $M_{N-I}$  are all non-saturated. For Region I, the high voltage switch can be modeled as the equivalent circuit shown in Fig. 3.6. Resistors  $(R_{MI} \sim R_{MN-I})$  represent the on-resistances from MOSFETs  $(M_I \sim M_{N-I})$ . The capacitors  $(C_{MI} \sim C_{MN-I})$ , which represent the capacitance at the drain nodes of MOSFETs in series, can be expressed as

$$C_{M(i)} = C_{db(i)} + C_{gd(i)} \times (1 - A_{v1}) + C_{ds(i)} \times (1 - A_{v2}), i = 1, 2, \cdots, N - 1,$$

(3.4)

where *i* is the *i*<sub>th</sub> drain capacitance being considered,  $A_{vI}$  and  $A_{v2}$  are used to approximate the Miller effect resulting from  $C_{gd}$  and  $C_{ds}$ .

Figure 3.6 An equivalent circuit for the high voltage switch in region I.

In region I, the voltage across  $M_N$  increases from  $V_{dd}$  to  $\sim N \times V_{dd}$ , which is a monotonic transient response and can be expressed as

$$V_{dsN}(t) = V_N - V_{N-1}, \qquad (3.5)$$

where  $V_N$  and  $V_{N-1}$  are the drain voltages of  $M_N$  and  $M_{N-1}$ , respectively. Then  $T_1$  in region I can be approximately expressed as [3.26]-[3.27]

$$T_{1} = \int_{0}^{\infty} t V_{dsN}(t) dt.$$

(3.6)

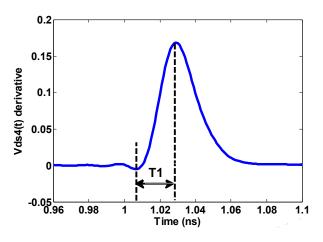

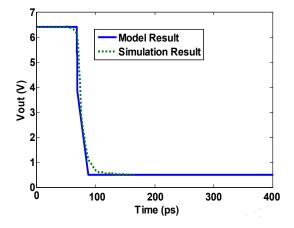

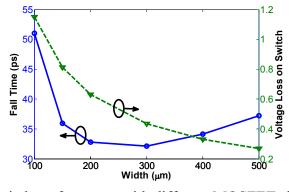

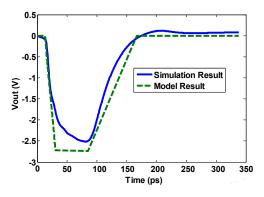

Figure 3.7 shows the transient response  $V_{ds4}(t)$  for the switch with four stacked MOSFETs. Its derivative  $\frac{dV_{ds4}(t)}{dt}$  is shown in Fig. 3.8. The definition of  $T_1$  is illustrated in Fig. 3.8 [3.27].

Figure 3.7 Transient response  $V_{ds4}(t)$  for the switch with four stacked MOSFETs.

Figure 3.8 Derivative of transient response  $V_{ds4}(t)$ .

The transfer function for the equivalent circuit shown in Fig. 3.6 can be defined as

$$T(s) = \frac{1 + a_1 s + a_2 s^2 + \dots + a_n s^n}{1 + b_1 s + b_2 s^2 + \dots + b_m s^m}.$$

(3.7)

By dividing the numerator with the denominator of the transfer function, Eq. (3.7) becomes

$$T(s) = 1 - (b_1 - a_1)s + (b_1^2 - a_1b_1 + a_2 - b_2)s^2 + \cdots$$

(3.8)

If a unit impulse is applied to the circuit in Fig. 3.6, the transfer function has the relationship with  $\frac{dV_{ds4}(t)}{dt}$  through Laplace transformation as

$$T(s) = \int_{0}^{\infty} V'_{dsN}(t) \times e^{-st} dt.$$

(3.9)

Expanding  $e^{-st}$  in a power series in *st*, Eq. (3.9) becomes

$$T(s) = 1 - s \int_{0}^{\infty} t \times V'_{dsN}(t) dt + \frac{s^{2}}{2!} \int_{0}^{\infty} t^{2} \times V'_{dsN}(t) dt - \dots$$

(3.10)

Comparing Eq. (3.8) and Eq. (3.10), we have

$$T_{1} = b_{1} - a_{1} = \int_{0}^{\infty} t V_{dsN}(t) dt, \qquad (3.11)$$

where  $b_1$  and  $a_1$  are the sum of the pole and zero at each node in the high voltage switch, respectively. Assuming that  $a_1$  is zero,  $T_1$  can be obtained as

$$T_{1} = \frac{\left(\frac{R_{M1}}{R_{M1}}\right) \times \left(\frac{R_{M2}}{R_{M1}}\right) \times \left(\frac{R_{M2}}{R_{2}}\right) \times \left(\frac{R_{M1}}{R_{2}}\right) \times \left(\frac{R_{M$$

When the MOSFETs in series are the same size, the on-resistances and drain capacitances are all equal.

$$R_{M1} = R_{M2} = \dots = R_{MN-1} = R_{on}$$

(3.13)

$$C_{M1} = C_{M2} = \dots = C_{MN-1} = C \tag{3.14}$$

Assuming that the dividing resistances  $R_i$  are much larger than the on-resistances  $R_{Mi}$ , based on Eq. (3.13) and Eq. (3.14), Eq. (3.12) can be simplified as [3.26]

$$T_{1} = \frac{R_{on} \times C \times N \times (N-1)}{R_{N} + (N-1) \times R_{on}} \left[ \frac{R_{N}}{2} + R_{on} \times \left( \frac{N}{6} - \frac{1}{3} \right) \right].$$

(3.15)

Region II: After Region I,  $M_N$  is turned on and the series transistors start discharging the load capacitance at the drain node of the topmost transistor. When the load capacitance is large compared to the drain/source capacitance, a Sakurai model is used to model time  $T_2$  in Region II [3.28]. In a Sakurai model, the delay degradation factor  $F_D$ , defined as the ratio of the delay of series-connected MOSFETs to the delay of a single MOSFET, can be calculated as [3.28]

$$F_{D} = \frac{I_{dsat}}{I_{dN}} = 1 + \frac{1}{2} \times \alpha \times \frac{V_{dsat}}{V_{dd} - V_{th}} \times (1 + \gamma_{1}) \times (N - 1),$$

(3.16)

where  $\gamma_I$  is the body-bias factor and  $I_{dN}$  is the current for N series-connected MOSFETs.

During time  $T_2$ , the current discharging  $C_L$  can be calculated from Eq. (3.16), therefore,

$$T_2 = \frac{C_L \times V_{dd}}{I_{dN}} = \frac{C_L \times V_{dd} \times F_D}{I_{dsat}}.$$

(3.17)

Now the  $\alpha$ -power law is used to model the topmost MOSFET  $M_N$ . The I-V equations are [3.28]

$$I_{ds} = I_{dsat} \times \left(2 - \frac{V_{ds}}{V_{dsat}}\right) \times \frac{V_{ds}}{V_{dsat}}$$

triode region (3.18a)

$$I_{ds} = I_{dsat} \times \left(\frac{V_{gs} - V_{th}}{V_{dd} - V_{th}}\right)^{\alpha}, \qquad \text{saturation region} \quad (3.18b)$$

where  $I_{dsat}$  is the drain current when  $V_{gs} = V_{ds} = V_{dd}$ ,  $V_{dsat}$  is the drain saturation voltage

when  $V_{gs} = V_{dd}$ , and  $\alpha$  is the velocity saturation index and is closely related to the velocity saturation of carriers.

The differential equation that describes the discharge of the drain capacitance of the topmost transistor in the stacked switch is given by